# A Reconfigurable GPS/Galileo Receiver Front-end for Space Applications

Arash Noroozi

# A Reconfigurable GPS/Galileo Receiver Front-end for Space Applications

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K. C. A. M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op dinsdag 16 juli 2013 om 15:00 uur

door

Arash NOROOZI

ingenieur elektrotechniek Master of Science van Technische Universiteit Delft, Nederland geboren te Teheran, Iran Dit proefschrift is goedgekeurd door de promotor: Prof. dr. E. K. A Gill

Copromotor: Dr. ir. C. J. M. Verhoeven

Samenstelling promotiecommissie:

| Rector Magnificus            | voorzitter                                          |

|------------------------------|-----------------------------------------------------|

| Prof. dr. E. K. A. Gill      | Technische Universiteit Delft, promotor             |

| Dr. ir. C. J. M. Verhoeven   | Technische Universiteit Delft, copromotor           |

| Prof. dr. M. Bousquet        | Institut Supérieur de l'Aéronautique et de l'Espace |

| Prof. dr. A. R. Pratt        | University of Nottingham                            |

| Prof. ir. P. Hoogeboom       | Technische Universiteit Delft                       |

| Dr. ir. G. L. E. Monna       | SystematIC B.V.                                     |

| Ir. W. De Wilde              | Septentrio N.V.                                     |

| Prof. dr. C. I. M. Beenakker | Technische Universiteit Delft, reservelid           |

|                              |                                                     |

ISBN 978-94-6191-802-4

#### Copyright © 2013 Arash Noroozi

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

Printed by Ipskamp Drukkers, Enschede, The Netherlands

To My Parents

# Contents

| List of Tables v |         |          |                                                |     |

|------------------|---------|----------|------------------------------------------------|-----|

| Lis              | st of F | igures   |                                                | vii |

| Lis              | st of A | cronym   | IS                                             | xi  |

| 1                | Ove     | rview    |                                                | 1   |

|                  | 1.1     | Naviga   | tion Systems                                   | 1   |

|                  |         | 1.1.1    | Navigation Using Natural Sources               | 2   |

|                  |         | 1.1.2    | Navigation Using Man-made Sources              | 3   |

|                  | 1.2     | Overvi   | ew of GNSS Systems - GPS                       | 5   |

|                  | 1.3     | GNSS A   | Applications                                   | 6   |

|                  |         | 1.3.1    | Navigation                                     | 7   |

|                  |         | 1.3.2    | Timing                                         | 8   |

|                  |         | 1.3.3    | Real-time Tracking                             | 8   |

|                  |         | 1.3.4    | Search and Rescue                              | 8   |

|                  |         | 1.3.5    | Surveying and Mapping                          | 8   |

|                  |         | 1.3.6    | Agriculture                                    | 9   |

|                  |         | 1.3.7    | Fun and Gaming                                 | 9   |

|                  |         | 1.3.8    | Earth Gravity Modeling                         | 9   |

|                  |         | 1.3.9    | High Resolution Ionospheric Sounding           | 9   |

|                  |         | 1.3.10   | Atmospheric Limb Sounding                      | 10  |

|                  |         | 1.3.11   | GNSS Reflectometry                             | 10  |

|                  | 1.4     |          | Receivers in Space                             | 10  |

|                  | 1.5     | State-c  | of-the-art IC Technology                       | 12  |

|                  |         | 1.5.1    | Standard IC Technology in Space                | 12  |

|                  |         | 1.5.2    | Trends in IC Technology for Space Applications | 13  |

|                  |         | 1.5.3    | System Integration                             | 15  |

|                  | 1.6     |          | Objectives                                     | 16  |

|                  | 1.7     | Thesis   | Structure                                      | 18  |

| 2                | GNS     | S Receiv |                                                | 19  |

|                  | 2.1     | Funda    | mentals of Satellite Positioning System        | 19  |

|   | 2.2                                                  | GNSS                                                                                                              | Signals                                   | 25                                                                                                                                             |

|---|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                      | 2.2.1                                                                                                             | GPS Signal Structure                      | 26                                                                                                                                             |

|   |                                                      | 2.2.2                                                                                                             | Galileo Signal Structure                  | 30                                                                                                                                             |

|   | 2.3                                                  | GNSS                                                                                                              | Receiver Architecture                     | 32                                                                                                                                             |

|   |                                                      | 2.3.1                                                                                                             | Digital Back-end Architecture             | 33                                                                                                                                             |

|   |                                                      | 2.3.2                                                                                                             | Carrier Tracking Loop                     | 37                                                                                                                                             |

|   | 2.4                                                  | Space                                                                                                             | Capable GNSS Receivers                    | 38                                                                                                                                             |

|   |                                                      | 2.4.1                                                                                                             | General Requirements                      | 38                                                                                                                                             |

|   |                                                      | 2.4.2                                                                                                             | Requirements for Operation in Space       | 43                                                                                                                                             |

|   | 2.5                                                  | Summ                                                                                                              | ary                                       | 48                                                                                                                                             |

|   |                                                      |                                                                                                                   | -                                         |                                                                                                                                                |

| 3 | GNS                                                  |                                                                                                                   | ver Front-end Architectures               | 49                                                                                                                                             |

|   | 3.1                                                  | Existin                                                                                                           | ng Radio Receiver Front-end Architectures | 50                                                                                                                                             |

|   |                                                      | 3.1.1                                                                                                             | Direct Sampling                           | 50                                                                                                                                             |

|   |                                                      | 3.1.2                                                                                                             | Heterodyne                                | 52                                                                                                                                             |

|   |                                                      | 3.1.3                                                                                                             | Direct Conversion (Zero-IF or Homodyne)   | 55                                                                                                                                             |

|   |                                                      | 3.1.4                                                                                                             | Front-end Architecture Comparison         | 59                                                                                                                                             |

|   | 3.2                                                  | Propos                                                                                                            | sed Front-end Architecture                | 62                                                                                                                                             |

|   |                                                      | 3.2.1                                                                                                             | Proposed Front-end Characteristics        | 63                                                                                                                                             |

|   |                                                      | 3.2.2                                                                                                             | Integrated Receiver Architecture          | 64                                                                                                                                             |

|   | 3.3                                                  | Summ                                                                                                              | hary                                      | 65                                                                                                                                             |

| 4 | From                                                 | nt-end F                                                                                                          | Receiver Circuit Design                   | 67                                                                                                                                             |

| т | 4.1                                                  |                                                                                                                   | hnology Selection                         | 67                                                                                                                                             |

|   | 4.1                                                  |                                                                                                                   | n Level Specifications                    | 68                                                                                                                                             |

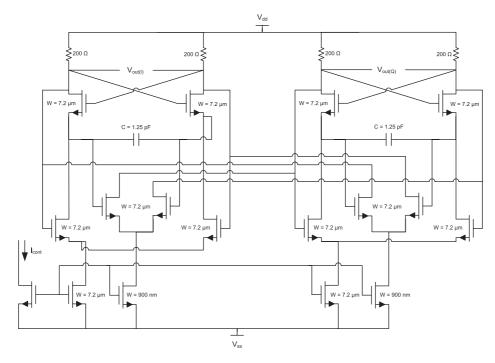

|   | 4.3                                                  | Mixer                                                                                                             | -                                         | 70                                                                                                                                             |

|   | 4.5                                                  |                                                                                                                   |                                           |                                                                                                                                                |

|   |                                                      |                                                                                                                   | Miyor Docign Constraints                  | /·)                                                                                                                                            |

|   |                                                      | 4.3.1                                                                                                             | Mixer Design Constraints                  | 72<br>73                                                                                                                                       |

|   | 1 1                                                  | 4.3.2                                                                                                             | Proposed Solution                         | 73                                                                                                                                             |

|   | 4.4<br>4.5                                           | 4.3.2<br>Oscilla                                                                                                  | Proposed Solution                         | 73<br>80                                                                                                                                       |

|   | 4.5                                                  | 4.3.2<br>Oscilla<br>Amplif                                                                                        | Proposed Solution                         | 73<br>80<br>85                                                                                                                                 |

|   |                                                      | 4.3.2<br>Oscilla<br>Amplif<br>Analog                                                                              | Proposed Solution                         | 73<br>80<br>85<br>87                                                                                                                           |

|   | 4.5<br>4.6                                           | 4.3.2<br>Oscilla<br>Amplif<br>Analog<br>4.6.1                                                                     | Proposed Solution                         | 73<br>80<br>85<br>87<br>89                                                                                                                     |

|   | 4.5                                                  | 4.3.2<br>Oscilla<br>Amplif<br>Analog<br>4.6.1                                                                     | Proposed Solution                         | 73<br>80<br>85<br>87                                                                                                                           |

| 5 | 4.5<br>4.6<br>4.7                                    | 4.3.2<br>Oscilla<br>Amplif<br>Analog<br>4.6.1<br>Summ                                                             | Proposed Solution                         | 73<br>80<br>85<br>87<br>89                                                                                                                     |

| 5 | 4.5<br>4.6<br>4.7                                    | 4.3.2<br>Oscilla<br>Amplif<br>Analog<br>4.6.1<br>Summ                                                             | Proposed Solution                         | 73<br>80<br>85<br>87<br>89<br>90                                                                                                               |

| 5 | 4.5<br>4.6<br>4.7<br>GPS                             | 4.3.2<br>Oscilla<br>Amplif<br>Analog<br>4.6.1<br>Summ                                                             | Proposed Solution                         | 73<br>80<br>85<br>87<br>89<br>90<br><b>91</b>                                                                                                  |

| 5 | 4.5<br>4.6<br>4.7<br><b>GPS</b><br>5.1               | 4.3.2<br>Oscilla<br>Amplif<br>Analog<br>4.6.1<br>Summ<br>/Galileo<br>Design                                       | Proposed Solution                         | 73<br>80<br>85<br>87<br>89<br>90<br><b>91</b><br>91                                                                                            |

| 5 | 4.5<br>4.6<br>4.7<br><b>GPS</b><br>5.1               | 4.3.2<br>Oscilla<br>Amplif<br>Analog<br>4.6.1<br>Summ<br>/Galileo<br>Design<br>Mixer                              | Proposed Solution                         | 73<br>80<br>85<br>87<br>89<br>90<br><b>91</b><br>91<br>94                                                                                      |

| 5 | 4.5<br>4.6<br>4.7<br><b>GPS</b><br>5.1               | 4.3.2<br>Oscilla<br>Amplif<br>Analog<br>4.6.1<br>Summ<br>/Galileo<br>Design<br>Mixer<br>5.2.1<br>5.2.2            | Proposed Solution                         | <ul> <li>73</li> <li>80</li> <li>85</li> <li>87</li> <li>89</li> <li>90</li> <li>91</li> <li>91</li> <li>94</li> <li>95</li> <li>96</li> </ul> |

| 5 | 4.5<br>4.6<br>4.7<br><b>GPS</b><br>5.1<br>5.2        | 4.3.2<br>Oscilla<br>Amplif<br>Analog<br>4.6.1<br>Summ<br>/Galileo<br>Design<br>Mixer<br>5.2.1<br>5.2.2<br>Oscilla | Proposed Solution                         | 73<br>80<br>85<br>87<br>90<br>91<br>91<br>94<br>95<br>96<br>123                                                                                |

| 5 | 4.5<br>4.6<br>4.7<br><b>GPS</b><br>5.1<br>5.2<br>5.3 | 4.3.2<br>Oscilla<br>Amplif<br>Analog<br>4.6.1<br>Summ<br>/Galileo<br>Design<br>Mixer<br>5.2.1<br>5.2.2<br>Oscilla | Proposed Solution                         | 73<br>80<br>85<br>87<br>90<br>91<br>91<br>94<br>95<br>96<br>123<br>128                                                                         |

|     |                          | 5.4.2 Comparator                        |  |

|-----|--------------------------|-----------------------------------------|--|

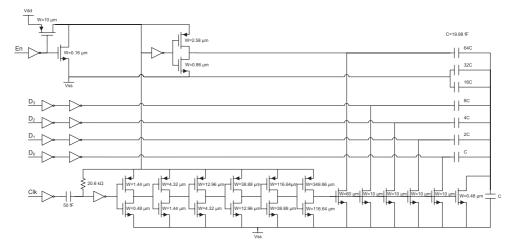

|     |                          | 5.4.3 Digital to Analog Converter (DAC) |  |

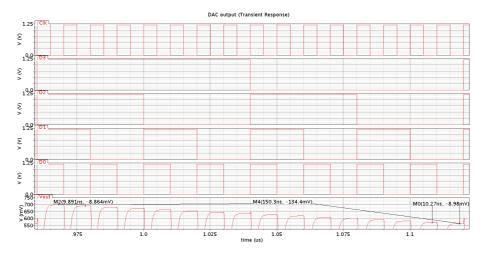

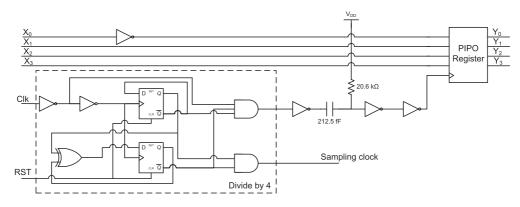

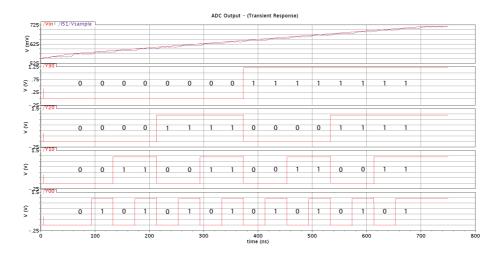

|     |                          | 5.4.4 Complete ADC Simulation           |  |

|     | 5.5                      | Experiences on the Design               |  |

|     | 5.6                      | Summary                                 |  |

| 6   | Cond                     | lusions and Recommendations 14          |  |

|     | 6.1                      | Motivation and Objectives               |  |

|     | 6.2                      | Summary and Results                     |  |

|     | 6.3                      | Recommendations                         |  |

|     | 6.4                      | Outlook                                 |  |

| Bił | oliogr                   | iphy 15                                 |  |

| Su  | Summary 165              |                                         |  |

| Sai | Samenvatting 167         |                                         |  |

| Lis | List of Publications 169 |                                         |  |

| Ac  | know                     | edgment 17                              |  |

| Cu  | rricu                    | um Vitae 173                            |  |

# List of Tables

| 1.1 | Characteristics of selected space capable GNSS receivers             | 11  |

|-----|----------------------------------------------------------------------|-----|

| 1.2 | SWOT analysis of standard IC technology used in space                | 15  |

| 2.1 | Galileo signal frequencies, bandwidth and services                   | 31  |

| 2.2 | GNSS Carrier frequencies of selected GNSS                            | 33  |

| 2.3 | Radiation types and their sources                                    | 46  |

| 3.1 | Comparison of different front-end architectures                      | 59  |

| 3.2 | Pugh matrix for selecting the front-end architecture                 | 61  |

| 3.3 | The ADC operation modes and their sampling frequencies               | 63  |

| 4.1 | List of available IC technologies through EUROPRACTICE               | 68  |

| 4.2 | GPS/Galileo receiver front-end link budget                           | 71  |

| 4.3 | Comparison of passive and active mixer architectures                 | 72  |

| 4.4 | The truth table of an exclusive-or (XOR) logic gate                  | 77  |

| 4.5 | Comparison of different oscillator architectures                     | 85  |

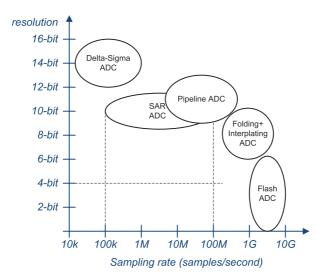

| 4.6 | Comparison of different ADC architectures                            | 88  |

| 5.1 | Mixer design specifications                                          | 94  |

| 5.2 | Simulation of carrier phase reconstruction from the baseband out-    |     |

|     | put signal                                                           | 96  |

| 5.3 | Selected parameter values and the resulting noise figure, conver-    |     |

|     | sion gain and IIP3 of HF mixer                                       | 99  |

| 5.4 | Comparison of target and achieved mixer design specifications        |     |

| 5.5 | Comparison of target and achieved oscillator design specifications . |     |

| 5.6 | List of ADC requirements                                             |     |

| 5.7 | Comparison of target and achieved ADC design specifications          | 142 |

# List of Figures

| 1.1  | Trend of time measurement accuracy improvement over the last      |    |

|------|-------------------------------------------------------------------|----|

|      | 1000 years                                                        | 3  |

| 1.2  | Frequency plans of GNSS systems in space                          | 4  |

| 1.3  | GPS system segments                                               | 5  |

| 1.4  | Speed of IC technology development vs. space mission develop-     |    |

|      | ment duration                                                     | 13 |

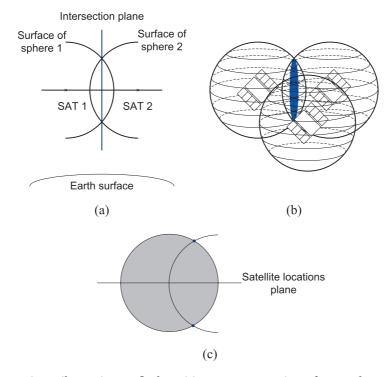

| 2.1  | Using trilateration to find position                              | 20 |

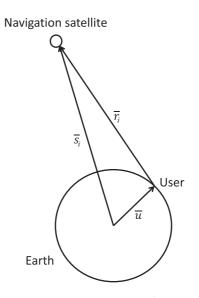

| 2.2  | Vector representation of user position                            | 21 |

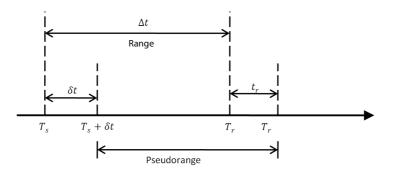

| 2.3  | Range measurement timing relationship                             | 22 |

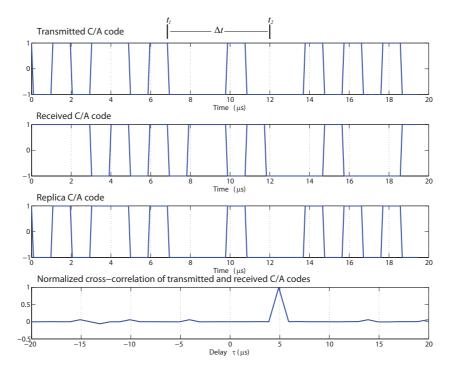

| 2.4  | Use of replica code to determine satellite code transmission time | 24 |

| 2.5  | GPS and Galileo frequency plans                                   | 25 |

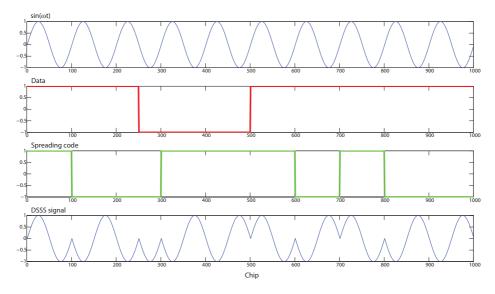

| 2.6  | DSSS Signal generation                                            | 27 |

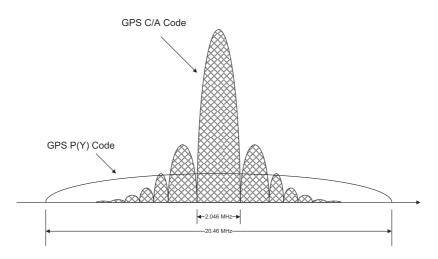

| 2.7  | GPS C/A and P code spectrum                                       | 28 |

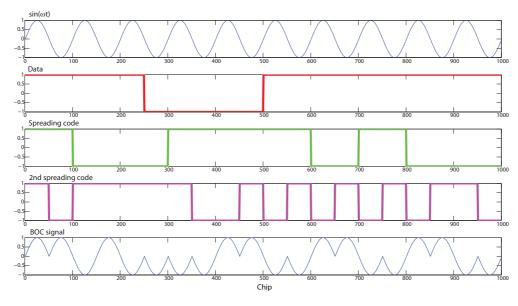

| 2.8  | BOC signal generation                                             | 29 |

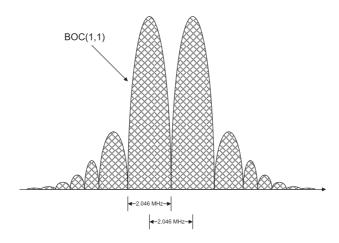

| 2.9  | BOC(1,1) spectrum                                                 | 30 |

| 2.10 | Values of coefficient $k(t)$ used in AltBOC modulation            | 32 |

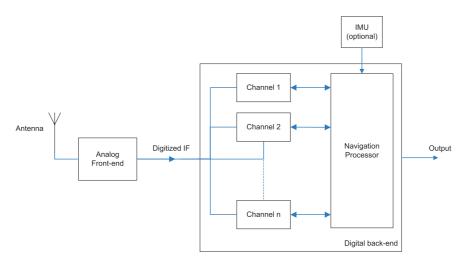

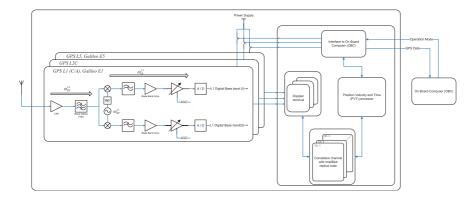

| 2.11 | A generic GNSS block diagram                                      | 33 |

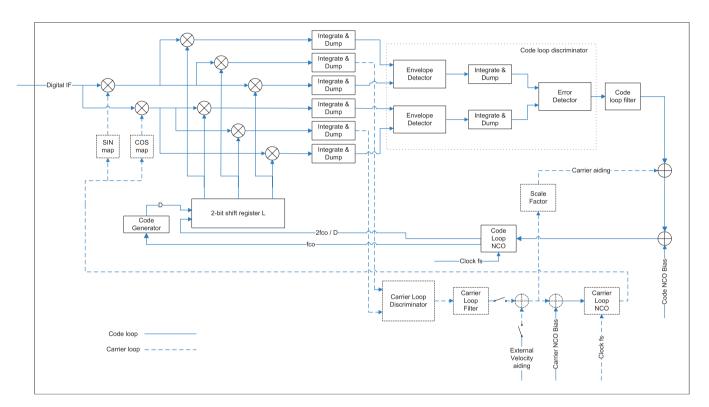

| 2.12 | GPS block diagram code and carrier tracking loops                 | 35 |

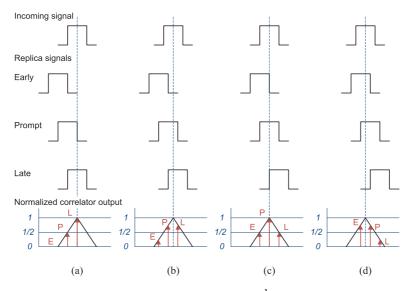

| 2.13 | Code correlation phases                                           | 36 |

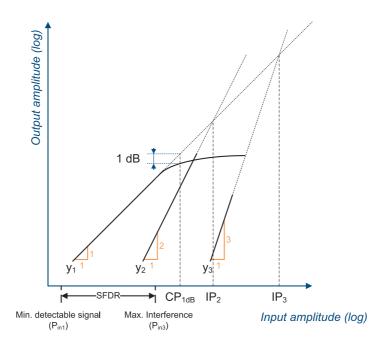

| 2.14 | 1-dB compression point, Intercept points and spurious free dy-    |    |

|      | namic range                                                       | 41 |

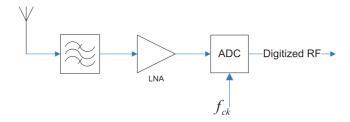

| 3.1  | Direct sampling architecture                                      | 50 |

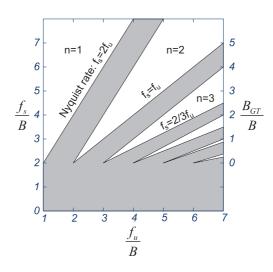

| 3.2  | The allowed and disallowed uniform sampling rates versus the      |    |

|      | band position                                                     | 51 |

| 3.3  | Heterodyne architecture                                           | 52 |

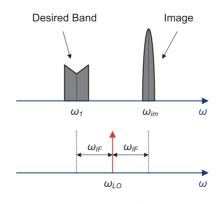

| 3.4  | Image frequency                                                   | 53 |

| 3.5  | Dual-IF Heterodyne architecture                                   | 54 |

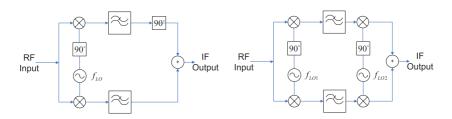

| 3.6  | Hartley and Weaver architectures                                  | 55 |

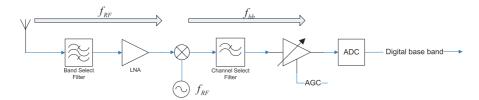

| 3.7  | Direct conversion architecture                                    | 55 |

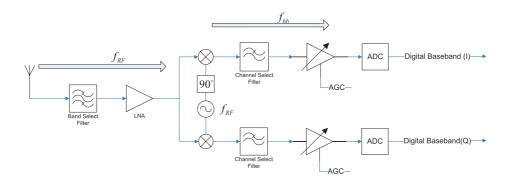

| 3.8  | Quadrature direct conversion architecture                         | 56 |

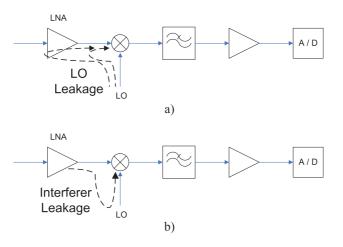

| 3.9  | Self-mixing of LO signal and a strong interferer in zero-IF mixer      | 58  |

|------|------------------------------------------------------------------------|-----|

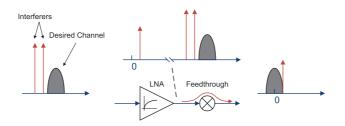

| 3.10 | Effect of even order distortion                                        | 58  |

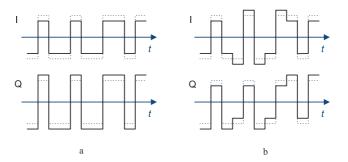

| 3.11 | Effect of I-Q mismatch on the quadrature zero-IF output                | 59  |

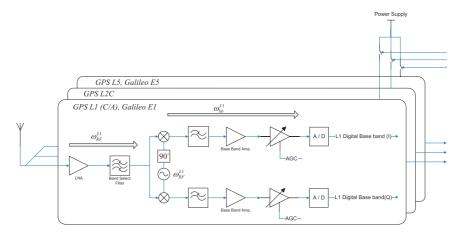

| 3.12 | Proposed GPS/Galileo receiver front-end architecture                   | 63  |

| 3.13 | Proposed GPS/Galileo receiver front-end architecture                   | 65  |

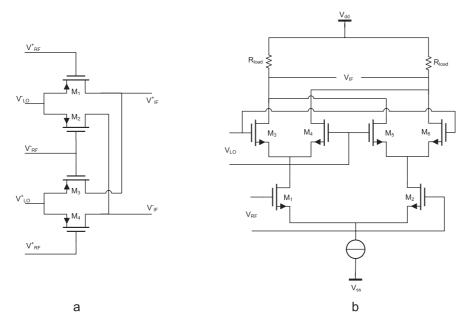

| 4.1  | Passive and active mixers                                              | 73  |

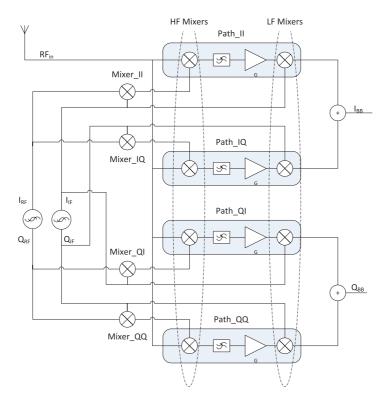

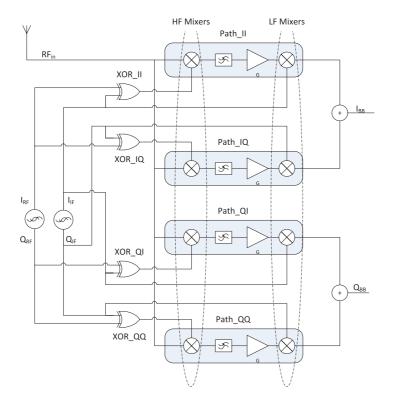

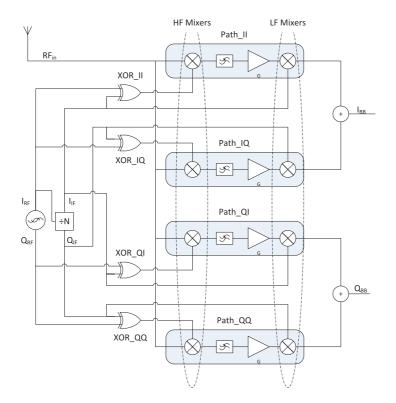

| 4.2  | Proposed mixer architecture                                            | 74  |

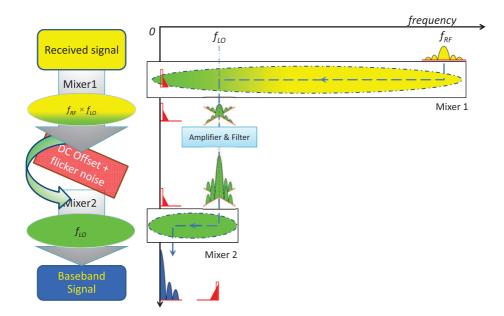

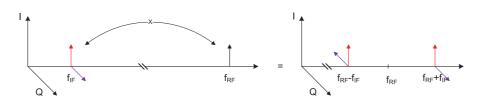

| 4.3  | Conversion process by the proposed mixer                               | 75  |

| 4.4  | Frequency spectrum of the dual-tone oscillator inputs of the HF        |     |

|      | mixers in Path_II and Path_IQ                                          | 76  |

| 4.5  | Proposed mixer architecture with digital implementation                | 78  |

| 4.6  | Proposed mixer architecture with frequency divider implementation      | 80  |

| 4.7  | Ring Oscillator                                                        | 81  |

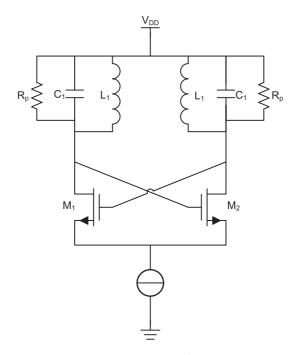

| 4.8  | A cross-coupled LC oscillator                                          | 82  |

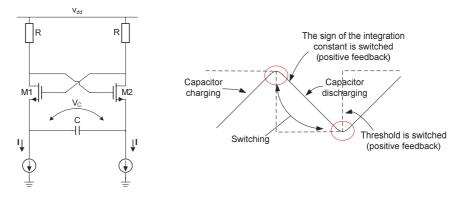

| 4.9  | a) Relaxation Oscillator b) Capacitor voltage behavior                 | 83  |

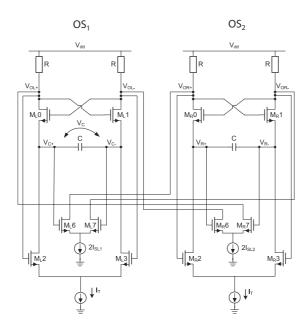

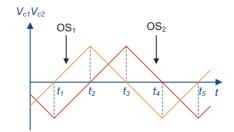

| 4.10 | Cross coupled Relaxation Oscillator                                    | 84  |

| 4.11 | Voltage variation of the capacitors of a cross-coupled relaxation os-  |     |

|      | cillator                                                               | 85  |

| 4.12 | Feedback system                                                        | 86  |

|      | Comparison of ADC architectures vs. resolution and sample rate         | 88  |

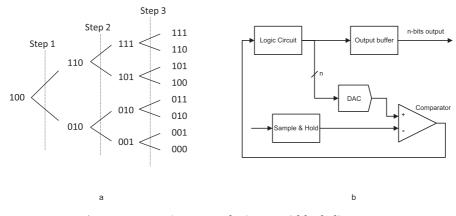

| 4.14 | a) Binary tree, b) SAR ADC block diagram                               | 89  |

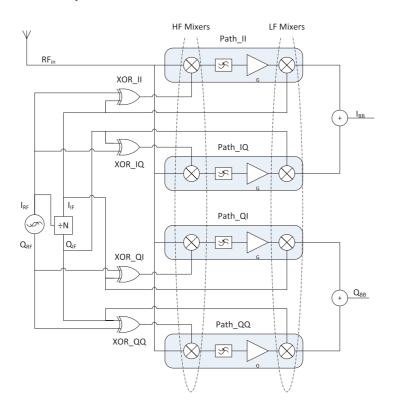

| 5.1  | Proposed mixer architecture with frequency divider implementation      | 93  |

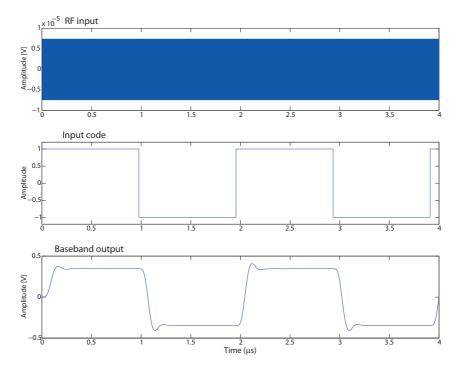

| 5.2  | System level simulation of the Zero IF mixer                           | 94  |

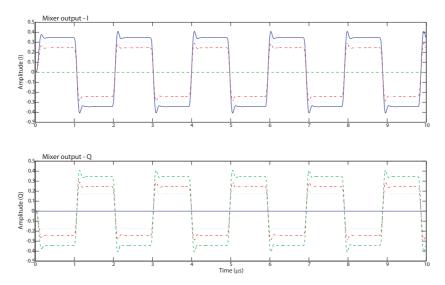

| 5.3  | Output of the Zero IF mixer at different carrier phases, $\theta_{RF}$ | 95  |

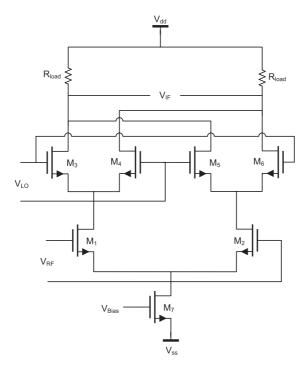

| 5.4  | The double balanced Gilbert mixer                                      | 97  |

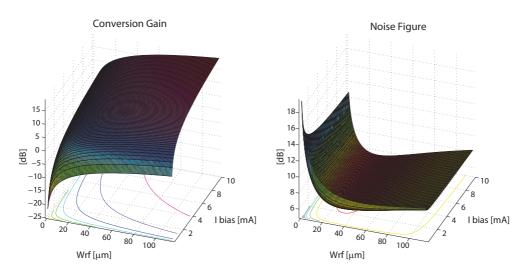

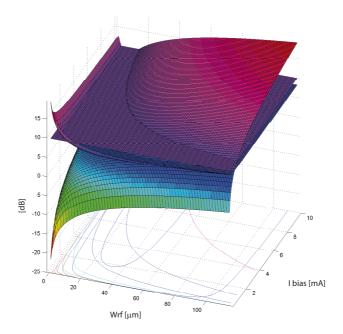

| 5.5  | Resulting conversion gain and noise figure of Gilbert mixer as a       |     |

|      | function of biasing current and RF transistor width                    | 98  |

| 5.6  | Intersecting conversion gain and noise figure with a 10 dB plane       | 99  |

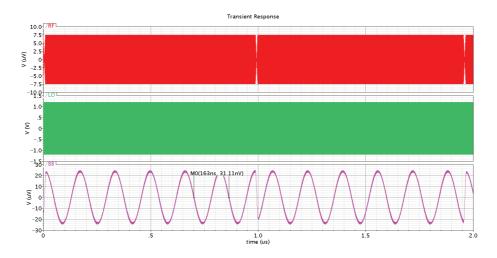

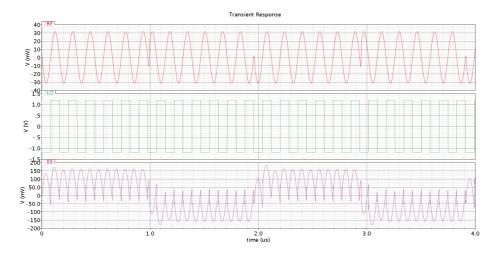

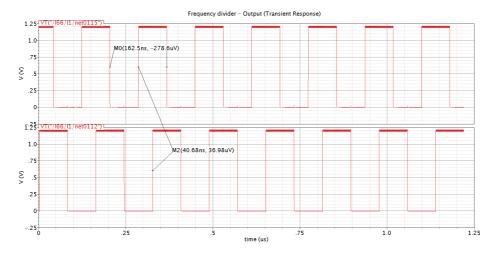

| 5.7  | Transient response of the HF mixer                                     | 100 |

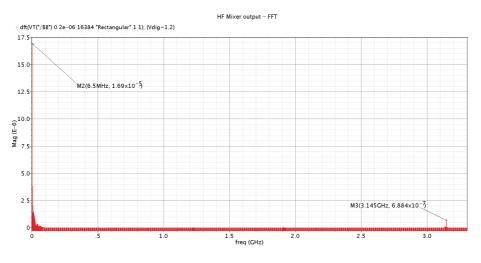

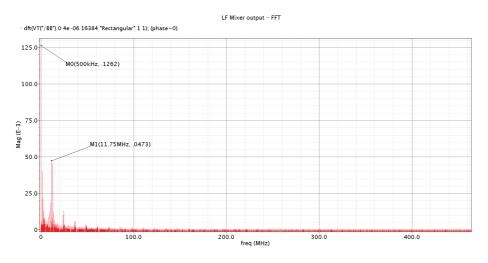

| 5.8  | Frequency spectrum of the HF mixer output                              | 101 |

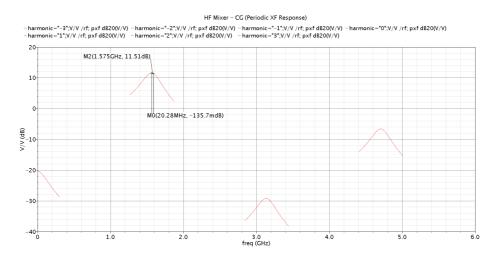

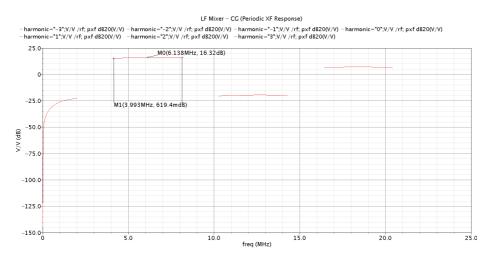

| 5.9  | Conversion gain of the HF mixer                                        | 102 |

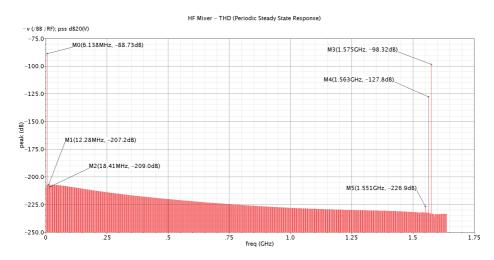

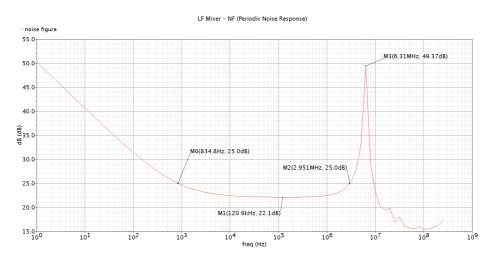

| 5.10 | Harmonic distortion of the HF Mixer                                    | 103 |

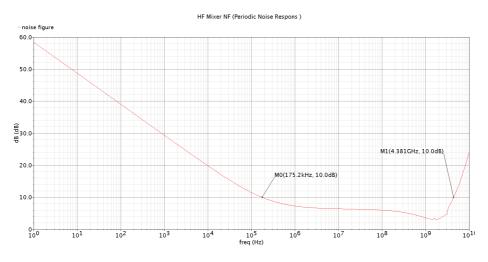

|      | Noise figure of the HF Mixer                                           |     |

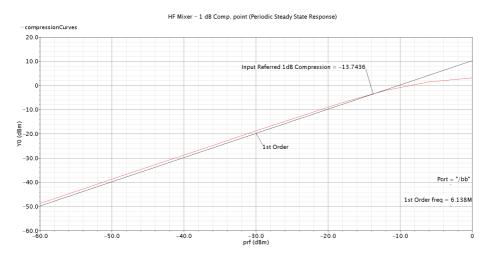

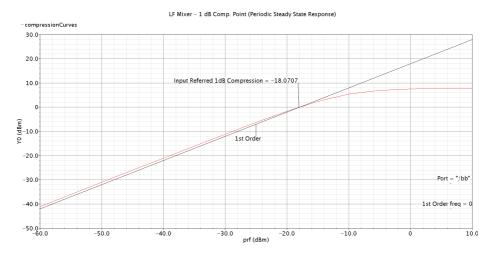

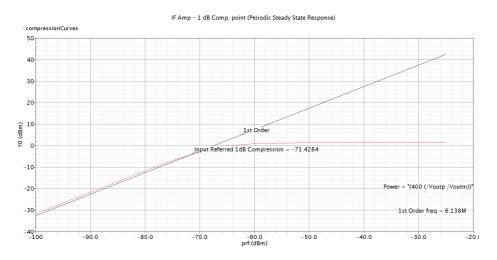

| 5.12 | 1-dB compression point of HF Mixer                                     | 104 |

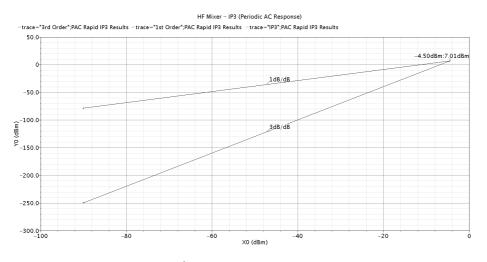

| 5.13 | 3 <sup>rd</sup> order intercept point of the HF mixer                  | 105 |

| 5.14 | Transient response of the LF mixer                                     | 106 |

| 5.15 | Frequency spectrum of the LF mixer output                              | 107 |

|      | Conversion gain of the LF mixer                                        |     |

|      | Noise figure of the LF Mixer                                           |     |

| 5.18 | 1-dB compression point of LF Mixer                                     | 109 |

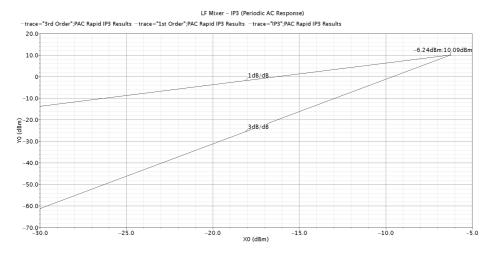

| 5.19 | 3 <sup>rd</sup> order intercept point of the HF mixer              | 110 |

|------|--------------------------------------------------------------------|-----|

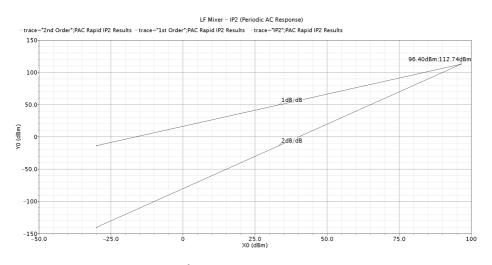

| 5.20 | 2 <sup>nd</sup> order intercept point of the LF mixer              | 110 |

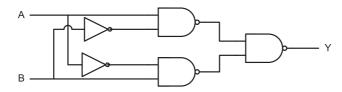

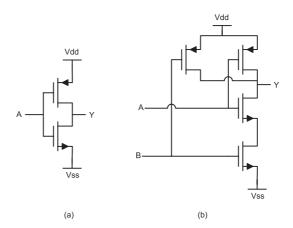

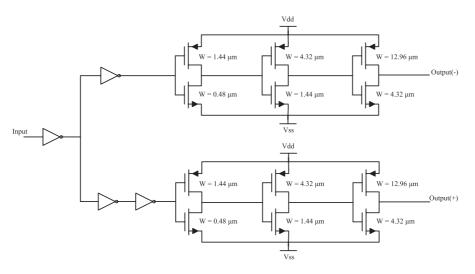

|      | Logic implementation of an XOR circuit                             |     |

| 5.22 | Transistor level implementation of a) inverter b) NAND gate        | 112 |

| 5.23 | Single to differential converter                                   | 113 |

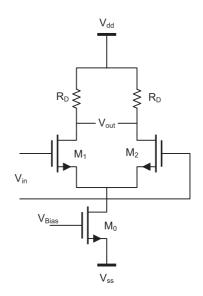

| 5.24 | Differential amplifier with resistive load                         | 114 |

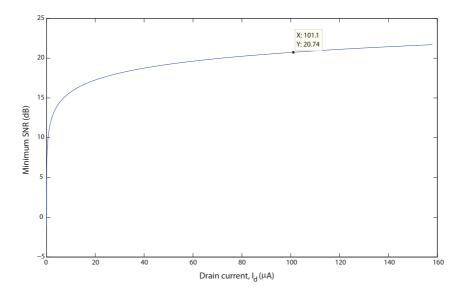

| 5.25 | SNR of a differential pair in different biasing currents           | 115 |

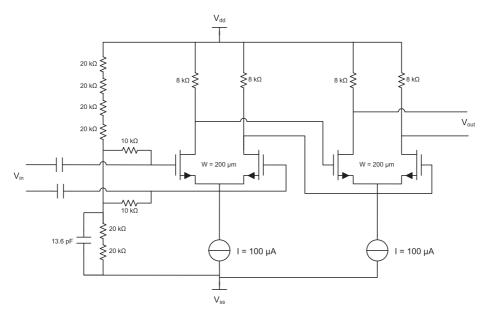

| 5.26 | Designed differential amplifier                                    | 116 |

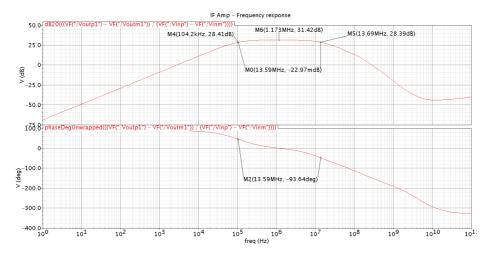

| 5.27 | Frequency response of a single IF amplifier                        | 117 |

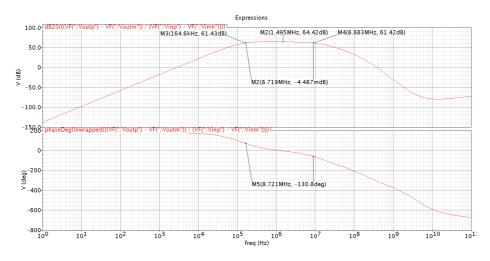

|      | Total frequency response of two cascaded IF amplifiers             |     |

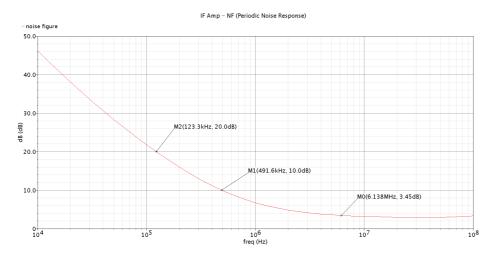

| 5.29 | Noise figure of the IF amplifier                                   | 119 |

| 5.30 | 1-dB compression point of IF amplifier                             | 120 |

| 5.31 | 3 <sup>rd</sup> order intercept point of the IF amplifier          | 120 |

| 5.32 | Frequency spectrum and the transient response of the output of the |     |

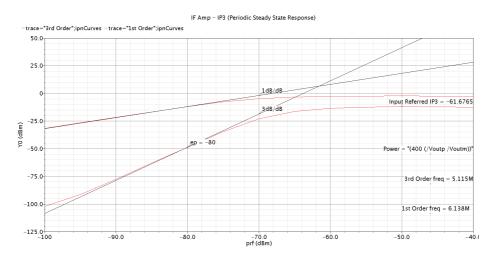

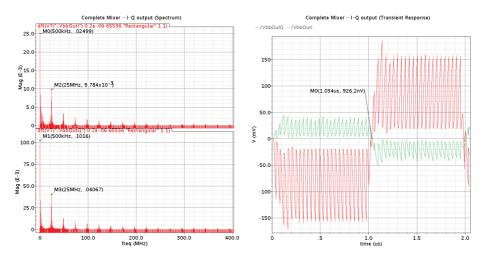

|      | complete mixer                                                     | 122 |

|      | Quadrature relaxation oscillator circuit                           |     |

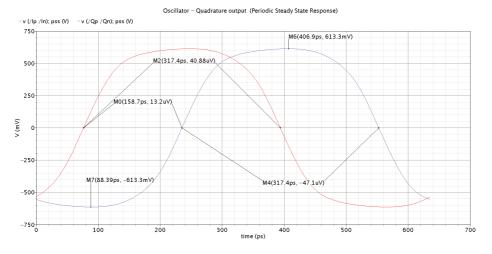

| 5.34 | Designed oscillator output signals                                 | 124 |

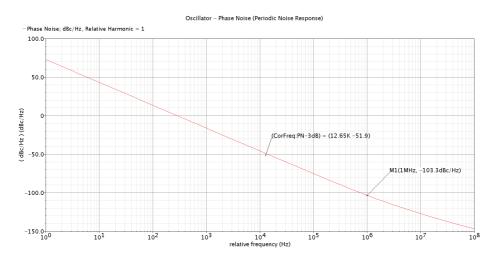

|      | Phase noise of the designed oscillator                             |     |

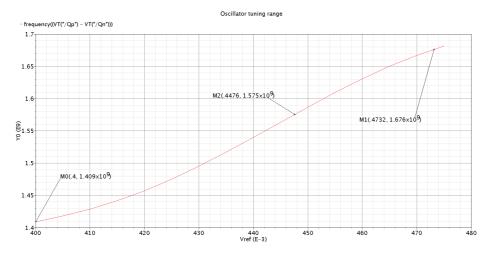

|      | Tuning frequency range of the designed oscillator                  |     |

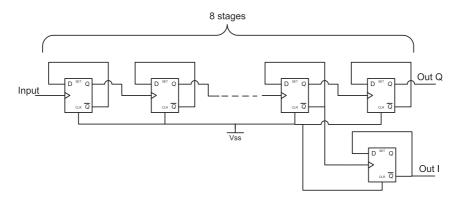

|      | $2^8$ I-Q frequency divider circuit                                |     |

|      | I and Q outputs of the $2^8$ I-Q frequency divider                 | 127 |

| 5.39 | On resistance of NMOS and PMOS devices as a function of input      |     |

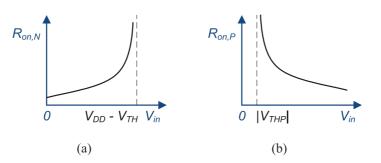

|      | voltage                                                            | 129 |

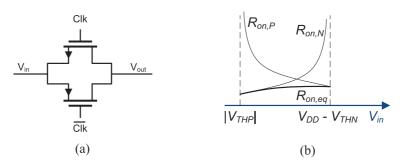

| 5.40 | Complementary switch or transmission gate (TG) (a) on-resistance   |     |

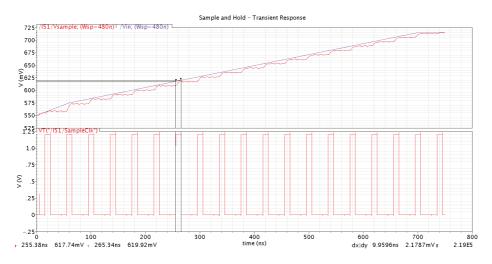

|      | of the TG (b)                                                      | 130 |

| 5.41 | 1 1 0 1                                                            |     |

|      | the sample and hold output. The bottom figure depicts the sam-     |     |

|      | pling clock                                                        |     |

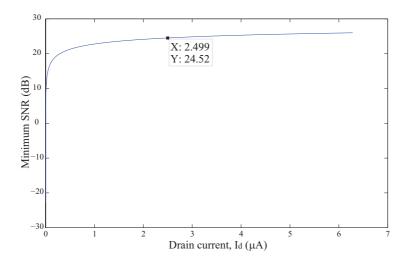

|      | Minimum SNR vs. NMOS drain current in a differential pair          |     |

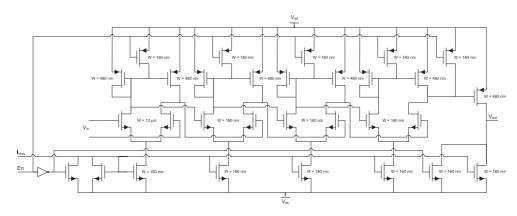

|      | Designed comparator for SAR ADC                                    |     |

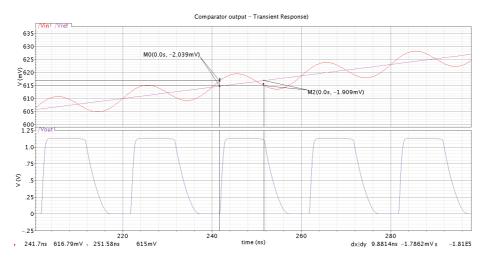

|      | Comparator output for a ramp and ramp+sine inputs                  |     |

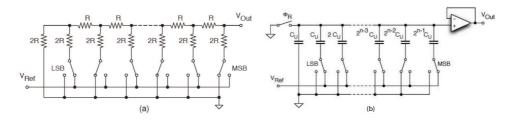

|      | Resistive and capacitive DAC circuits                              |     |

|      | 4-bit capacitive DAC circuit                                       |     |

|      | Results from the 4-bit capacitive DAC simulation                   |     |

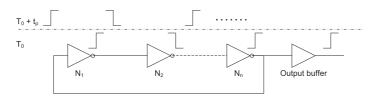

|      | Output buffer of the designed SAR ADC                              |     |

| 5.49 | ADC output for a ramp input                                        | 141 |

# List of Acronyms

| ADC    | Analog to Digital Converter                                         |

|--------|---------------------------------------------------------------------|

| AGC    | Automatic Gain Control                                              |

| AltBOC | Alternative Binary Offset Carrier                                   |

| AOCS   | Attitude and Control System                                         |

| ASIC   | Application-Specific Integrated Circuit                             |

| BJT    | Bipolar Junction Transistor                                         |

| BOC    | Binary Offset Carrier                                               |

| BPSK   | Binary Phase Shift Keying                                           |

| BSIM   | Berkeley Short-channel Insulated-gate field-effect transistor Model |

| C/NAV  | Commercial Navigation Message                                       |

| CBOC   | Composite Binary Offset Carrier                                     |

| CDMA   | Code Division Multiple Access                                       |

| CHAMP  | CHAllenging Mini-satellite Payload                                  |

| CML    | Current Mode Logic                                                  |

| CMOS   | Complementary Metal-Oxide Semiconductor                             |

| CNAV   | Civil Navigation Data                                               |

| COTS   | Commercial-Off-The-Shelf                                            |

| cps    | chips per second                                                    |

| CS     | Commercial Service                                                  |

| D-FF   | D-type Flip Flop                                                    |

| DAC    | Digital to Analog Converter                                         |

| DC     | Direct Current                                                      |

| DLL    | Delay Locked Loop                                                   |

| DSB-AM | Double Side Band-Amplitude Modulation                               |

| DSSS   | Direct Sequence Spread Spectrum                                     |

| EGNOS   | European Geostationary Navigation Overlay Service         |

|---------|-----------------------------------------------------------|

| EKF     | Extended Kalman Filter                                    |

| ENOB    | Effective Number Of Bits                                  |

| ESA     | European Space Agency                                     |

| EU      | European Union                                            |

| F/NAV   | Free access Navigation Message                            |

| FAA     | Federal Aviation Administration                           |

| FDMA    | Frequency Division Multiple Access                        |

| FLL     | Frequency Locked Loop                                     |

| FPM     | Functional Performance Metric                             |

| GA      | Ground Antennas                                           |

| GAGAN   | GPS Aided Geo-Augmented Navigation                        |

| GCM     | Greatest Common Divisor                                   |

| GIS     | Geographic Information System                             |

| GLONASS | GLObal NAvigation Satellite Systems                       |

| GNC     | Guidance, Navigation and Control                          |

| GNSS    | Global Navigation Satellite Systems                       |

| GOCE    | Gravity field and steady-state Ocean Circulation Explorer |

| GPS     | Global Positioning Satellite System                       |

| GRACE   | Gravity Recovery and Climate Experiment                   |

| I/NAV   | Integrity Navigation Message                              |

| IC      | Integrated Circuit                                        |

| IF      | Intermediate Frequency                                    |

| IMU     | Inertial Measurement Unit                                 |

| IM      | Intermodulation                                           |

| IP      | Intercept Point                                           |

| IRR     | Image Rejection Ratio                                     |

| ITU-RR  | International Telecommunication Union Radio Regulations   |

| LEO     | Low Earth Orbit                                           |

| LNA     | Low Noise Amplifier                                       |

| LO      | Local Oscillator                                          |

| LORAN | LOng RAnge Navigation                          |

|-------|------------------------------------------------|

| LPF   | Low-Pass Filter                                |

| LSB   | Least Significant Bit                          |

| MCS   | Master Control Station                         |

| MEMS  | Micro Electro-Mechanical System                |

| MOS   | Metal-Oxide Semiconductor                      |

| MS    | Monitor Station                                |

| MSAS  | Multi-functional Satellite Augmentation System |

| MSB   | Most Significant Bit                           |

| NCO   | Numerically Controlled Oscillator              |

| NF    | Noise Figure                                   |

| NMOS  | N-channel Metal Oxide Semiconductor            |

| OBC   | On-Board Computer                              |

| OS    | Open Service                                   |

| РСВ   | Printed Circuit Board                          |

| PLL   | Phase Locked Loop                              |

| PMOS  | P-channel Metal Oxide Semiconductor            |

| POD   | Precise Orbit Determination                    |

| PRN   | Pseudo Random Noise                            |

| PRS   | Public Regulated Service                       |

| PSD   | Power Spectral Density                         |

| PSK   | Phase Shift Keying                             |

| PVT   | Position, Velocity and Time                    |

| QPSK  | Quadrature Phase Shift Keying                  |

| QZSS  | Quasi-Zenith Satellite System                  |

| RF    | Radio Frequency                                |

| RHBD  | Radiation Hardening By Design                  |

| RINEX | Receiver Independent Exchange                  |

| SAR   | Search And Rescue                              |

| SAR   | Successive Approximation Register              |

| SBAS  | Satellite-Based Augmentation Systems           |

| SDR      | Software Defined Radio                        |

|----------|-----------------------------------------------|

| SEE      | Single-Event Effect                           |

| SEFI     | Single-Event Functional Interrupt             |

| SEGR     | Single-Event gate rupture                     |

| SEL      | Single-Event Latch-up                         |

| SET      | Single-Event Transient                        |

| SEU      | Single-Event Upset                            |

| SFDR     | Spurious Free Dynamic Range                   |

| SI       | System Integrity                              |

| SIP      | System In Package                             |

| SNR      | Signal to Noise Ratio                         |

| SOC      | System On Chip                                |

| SoL      | Safety of Life                                |

| sps      | symbols per second                            |

| SSB      | Single Side Band                              |

| SV       | Space Vehicle                                 |

| SWOT     | Strengths, Weaknesses, Opportunities, Threats |

| T-FF     | T-type Flip Flop                              |

| TG       | Transmission Gate                             |

| TID      | Total Ionizing Doze                           |

| TM-BOC   | Time-Multiplexed Binary Offset Carrier        |

| TRL      | Technology Readiness Level                    |

| TU Delft | Delft University of Technology                |

| UCLA     | University of California, Los Angeles         |

| US       | United States                                 |

| UTC      | Coordinated Universal Time                    |

| UWB      | Ultra Wide-Band                               |

| VGA      | Variable Gain Amplifier                       |

| WAAS     | Wide Area Augmentation System                 |

| ZOH      | Zero Order Hold                               |

|          |                                               |

Where am I? Where is my target? What is the best way to reach the target? These are questions that many of us ask ourselves everyday.

During history, mankind tried to answer these questions as accurate as possible. People used natural resources, invented instruments and combined the knowledge of different disciplines to improve these answers. The results of these efforts became an important field of science and engineering called navigation. As the technology develops in different areas, the navigation technology is developed likewise and new applications and technologies are introduced.

In this thesis, novel concepts for improved navigation technologies will be developed, characterized and verified which can contribute to ongoing development in the field of navigation.

## 1.1 Navigation Systems

Navigation systems have developed during history starting from basic landmark detections to state-of-the-art satellite based navigation systems. Each of these navigation systems use reference points and a measurable quantity. A number of these navigation systems use natural resources as their reference points while for others, dedicated man-made systems are developed and operated. In general, navigation can be based on two approaches: using natural sources (stars, land-marks, etc.) and using man-made sources as reference points. In the following, a

brief overview of these two will be provided.

#### 1.1.1 Navigation Using Natural Sources

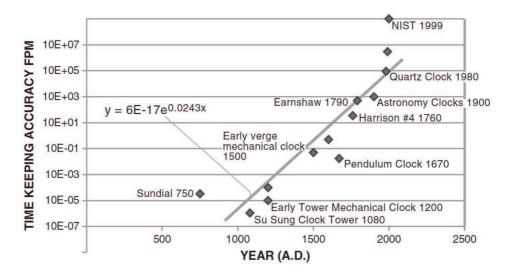

Since the early ages, people have been using natural resources to find their position, their directions and to navigate. These resources are for example stars, landmarks or the Earth magnetic field. In general, navigation has been a challenging task and especially navigation at sea in early times was the main driver for the development of instruments for navigation. Instruments and tools have been developed such as maps, timers, compasses, astrolabes, sextants, gyroscopes, accelerometers, star cameras, etc. by which the user could determine his position based on the landmarks, Earth magnetic field, star charts, motion behavior and so forth whenever the information was available. Eventually, the accuracy of using these methods increased by developments in different technology areas and combining the knowledge from different disciplines. For example, keeping an accurate track of time has always been an important task in navigation which has been evolved. The usage and the accuracy requirement of time keeping has been changed from the early times where rotation of the Earth and the time dependency of the positions of the stars had to be taken into account till today where accurate timing in the order of pico-second is an essential part of the position calculation. Fig. 1.1 depicts the trend of time measurement accuracy improvement over the last 1000 years. In this figure, in order to better demonstrate the effect of technological advances, functional performance metric (FPM) of timekeeping is expressed as exponential of accuracy (1/drift) divided by volume of the timepiece since the accuracy of the clock can almost always be improved by increasing its size, even though it is not always practical [1].

An example of combining different state-of-the-art technologies to use natural resources is pulsar navigation. Pulsars, i.e. rapidly rotating neutron stars, are another natural source which can be used for navigation. However, it was not possible to use them till recently due to the lack of required technology. Pulsars are extremely fast rotating neutron stars. The typical diameter of a pulsar is about 20 km and the rotation period is in the range of milliseconds to tens of seconds. They emit ultra wide-band (UWB) electromagnetic waves which are observed as periodic pulses. Each pulsar has its own unique signature, i.e. pulse period and pulse shape, which makes it distinguishable from others. Study shows that pulsars can be used for navigation and accurate timing. There are several teams at Delft University of Technology (TU Delft), University of California, Los Angeles (UCLA) and other research institutes working to develop the technology in the fields of receiver design and signal processing for pulsar navigation [2–6].

However, the accuracy or availability of these systems using natural sources is either limited and insufficient for advanced applications or their usage is still too

Figure 1.1: Trend of time measurement accuracy improvement over the last 1000 years [1]

complicated. Thus, new dedicated navigation systems have been developed as will be explained in the following section.

#### 1.1.2 Navigation Using Man-made Sources

Rapid technology developments in the 20<sup>th</sup> century provided the opportunity to develop new navigation systems. Thus, new techniques were employed to develop and operate more accurate and easier-to-use navigation systems than navigation using natural sources. One of the early navigation systems was LORAN (LOng RAnge Navigation), a ground-based system. The first generation of this system, LORAN-A, was developed during the second world war by the United States (US) and was based on 40  $\mu$ s pulses transmitted at 1950 kHz. The navigation error was high with position error of 28 miles ( $\approx$  45 km) in 1400 miles ( $\approx$  2253 km) flight. The next LORAN generations, LORAN-B and LORAN-C improved the absolute position accuracy to about 460 m and repeatable accuracy of about 18 - 90 m [7]. LORAN-C went out of commission in 2010 [8].

When space became accessible in the 60's of the 20<sup>th</sup> century, the next generations of the navigation systems moved towards global and space-based systems. These Global Navigation Satellite Systems (GNSS) are: NAVSTAR Global Positioning System (GPS) which is developed and operated by the US, GLObal NAvigation Satellite Systems (GLONASS) developed and operated by Russia, the Galileo satellite navigation system which is being developed by the European Union (EU) and the Compass (Beidou) satellite navigation system by China. To improve the

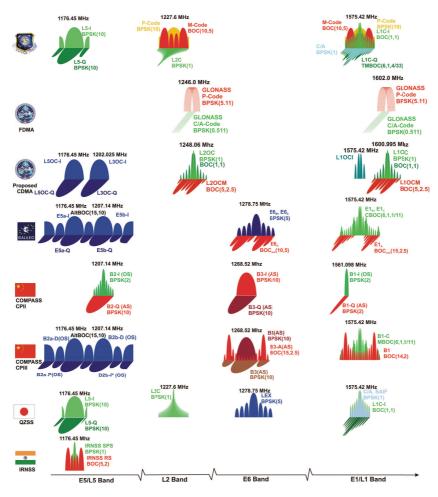

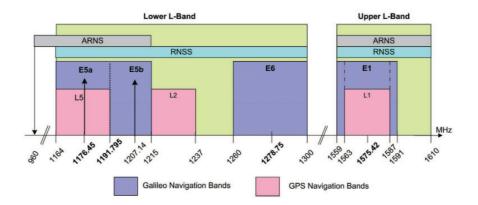

Figure 1.2: Frequency plans of GNSS systems in space [9]

performance of these GNSS systems, several satellite-based augmentation systems (SBAS) are in operation or are under development. Examples of SBAS are: the Wide Area Augmentation System (WAAS), operated by the United States Federal Aviation Administration (FAA), the European Geostationary Navigation Overlay Service (EGNOS), operated by the European Space Agency (ESA), the Multifunctional Satellite Augmentation System (MSAS) system, operated by Japan, the Quasi-Zenith Satellite System (QZSS), under development by Japan and the GPS aided geo-augmented navigation or GPS and geo-augmented navigation system (GAGAN), being developed by India. Fig. 1.2 depicts some of these space-based navigation systems with their frequency allocations.

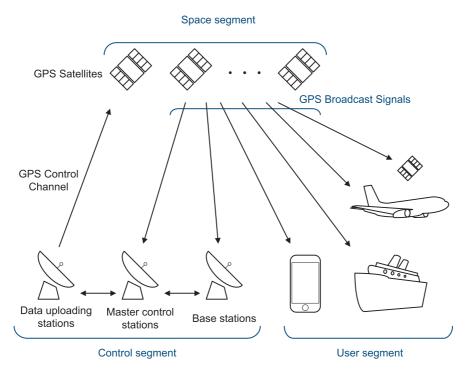

Figure 1.3: GPS system segments

### 1.2 Overview of GNSS Systems - GPS

The operation principle of space-based navigation systems is similar. Since GPS is the most commonly used GNSS system<sup>1</sup>, the operation principle of GPS will be briefly described in this section.

GPS is a space-based radio-positioning and time transfer system which provides accurate position, velocity and time (PVT) information to its users. GPS consists of three major system segments: space segment, control segment and user segment as depicted in Fig. 1.3.

The space segment consists of a nominal constellation of 24 satellites in semisynchronous orbits. The satellites are arranged in six orbital planes with an inclination angle of 55° relative to the equator and an orbital period of about 12 hours. Each orbital plane comprises four satellites with an average altitude of 20,200 km. The satellites transmit ranging signals on three frequency bands: L1 at 1575.42 MHz, L2 at 1227.6 MHz and L5 at 1176.45 MHz. The legacy satellite signals are modulated with two spreading codes: C/A code and P(Y) code with chipping

$<sup>^1{\</sup>rm GLONASS}$  and Compass satellite navigation systems are also opening their way to the consumer market

rates of 1.023 MHz and 10.23 MHz, respectively [10]. The GPS signal structure will be explained in more detail in chapter 2.

The control segment consists of a master control station (MCS) plus monitor stations (MS) and ground antennas (GA) which are located around the Earth. The MCS is the central processing facility and monitors and manages the satellite constellation. Its functions include control of satellite station-keeping maneuvers, reconfiguring of redundant satellite equipment, regularly updating navigation messages and various other satellite health monitoring and maintenance activities. The monitor stations track all GPS satellites in view and collect ranging data from each satellite. This information is transmitted to the MCS. The ground antennas are used by MCS to upload the ephemeris and clock data to each satellite for updating their navigation message [10].

The user segment comprises systems for terrestrial, maritime, aviation and space users which all employ GPS receivers as their core component. Based on the tracking of GPS signals received from various GPS satellites simultaneously, the receiver is able, together with the timing and position information modulated on the GPS signals, to determine its position and time. Details on the navigation algorithm are described in chapter 2. The user segment systems treat the GPS information in different manners depending on their applications. In the next section, different applications will be introduced that use GPS signals (in a more general term GNSS signals) as their main input. Understanding various applications and their common and exclusive needs is important for developing the specific GNSS receiver.

## **1.3 GNSS Applications**

GNSS signals have been primarily designed for navigation purposes, i.e. the determination of the position, velocity and time (PVT) of the receiver. By further using and investigating the GNSS signal structures as well as environmental effects on the signals, more valuable information has been found to be extractable from these signals which significantly broadens the applications of GNSS.

Some of the applications use the PVT information as their main source of information. Such applications are mainly based on positioning, navigating and time synchronization. Other applications use the indirect information, for example, velocity variations of electromagnetic waves in different media to study environmental effects or various physical models of the Earth. These applications are the result of combining different sciences such as physics, oceanography, geology, weather studies and so forth by making use of GNSS technology and its systems. In the following, a list of a selected number of these applications is compiled which will be explained briefly in this section:

- Navigation

- Timing

- Real-time tracking

- Search and rescue

- Surveying and mapping

- Agriculture

- Fun and gaming

- Earth gravity modeling

- · High resolution ionosphere imaging

- · Atmospheric limb sounding

- GNSS reflectometry.

The number of applications is increasing due to advances in different areas of hardware and software technologies and changing user needs. Different applications typically will use different GNSS equipment and processes depending on their needs. As an example, surveying and mapping may require differential navigation technique using advanced costly receivers and highly sophisticated software processes.

#### 1.3.1 Navigation

The primary output of a typical GNSS receiver is the receiver's position, velocity and time. Combining this information with a digital map enables terrestrial navigation. Nowadays, many people use GPS navigators in their cars to find the correct route to their destinations. Integration of a navigator with other systems, such as mobile Internet connection, provides the fastest route to the users in real-time which saves time and fuel. Navigation using GNSS signals has improved safety and increased the time and fuel efficiency in aviation and maritime applications as well.

Space systems themselves are also users as well and benefit greatly from GNSS signals. As long as a space vehicle (SV) is within the field of view of GNSS satellites, it can use GNSS signals. The navigation output of the receiver can be used for navigation, precise orbit determination (POD), attitude determination, timing solutions, clock stability estimation, data time stamping and on-board autonomy. A low earth orbit (LEO) satellite is an example of such a space vehicle which is always in the field of view of several GNSS satellites and thus can benefit from the new technology developments of the GNSS receivers as will be discussed later.

#### 1.3.2 Timing

GNSS signals are generated by using highly accurate atomic clocks on-board the GNSS satellites. The drift and errors of these high accuracy clocks are tracked and corrected by the GNSS control segment and are a part of the navigation data. Thus, the GNSS signals can be used for accurate correction of the receiver clock or system clock as well as tracking the time, e.g., for time tagging data [11].

#### 1.3.3 Real-time Tracking

Logistics may be an important part of a business. There are many companies that need to know how their movable assets are distributed. For example, if a transport company can track its vehicles in real-time, it could manage its resources more efficiently. Also, for railway management, the knowledge of position of each train, service vehicles, etc. will improve its resource allocation, response time and services. There are many other situations where the concept of tracking using GNSS receivers can be beneficial [12–14].

#### 1.3.4 Search and Rescue

In any successful rescue operation, response time is very critical. The knowledge of the location of the endangered people as well as emergency service resources, landmarks, streets and buildings reduces rescue time and potentially saves lives. Using GNSS signals helps rescue teams to faster find the location of distress and the necessary resources. Intelligently combining the position information with information from other sensors can lead to effective location prediction which can further reduce the response time even if the environment has changed, e.g. after an earthquake. In addition, Galileo search and rescue (SAR) service enables Galileo satellites to pick up signals from emergency beacons carried on ships, planes or persons and relay them to national rescue centers [15].

#### 1.3.5 Surveying and Mapping

The system which is used to capture, store, analyze, and display geographically referenced information is called Geographic information system (GIS). GIS is an important part of navigation. Generating GIS data is a time and resource consuming task. Very complex and accurate instruments are used for this purpose. Adding GNSS technology to the surveying equipments increases their accuracy while reducing the time and labor hours. In addition, it provides additional features such as autonomous map generation which can be used to monitor changing the landmark positions during the time with higher temporal resolution [16].

#### 1.3.6 Agriculture

In order to automate agricultural processes, position and time are two important information sets which are locally available in real-time using GNSS signals. Using GNSS receivers in the fields improves the precision of field mapping and farm planning, e.g. adding the position and time information to sampled soil. In implanting and harvesting processes, the information of position and time can be added to relevant machinery and the process can be automated which reduces man power and increases the performance of agriculture [17, 18].

#### 1.3.7 Fun and Gaming

Availability of position and time information has also shown its value in games and social activities. Many games have been designed based on the low-cost GNSS receivers and wide accessibility to them within smart phones and electronic tablets. The type of social activities have significantly been influenced by such means. Tourism and entertainment industries, as well as many other activities, are adapting themselves to this new technology [19].

#### 1.3.8 Earth Gravity Modeling

One of the interesting applications of the GNSS signals is the Earth gravity modeling. In order to do so, at least one LEO satellite orbits the Earth and records the raw navigation data which includes observations and ephemerides. These records are then transmitted to the ground station and processed to determine an accurate gravity model of the Earth [20, 21]. There are two types of gravity field modeling: static and temporal. Static gravity model provides the information about the general mass distribution of the earth while temporal gravity field provides the information such as accumulative continental water and water mass distribution of oceans [22]. There are currently two missions that provide data for Earth gravity modeling: Gravity Field and Steady-State Ocean Circulation Explorer (GOCE) [23] and Gravity Recovery and Climate Experiment (GRACE) [24, 25].

#### 1.3.9 High Resolution Ionospheric Sounding

One of the layers of the Earth's atmosphere is the ionosphere which consists of charged particles (electrons and protons) generated by solar radiations. Using GNSS signals, it is possible to sound the Earth's ionosphere. The ionospheric sounding process uses the effect of the ionosphere on the GNSS signals in order to map the ionosphere. The group refractive index determines the propagation velocity of the GNSS signals in a medium [26]. The delay caused by the medium is

frequency dependent. Thus, two frequency bands are used in ionosphere sounding using GNSS signals. Since the code and data are known beforehand, the delays can be calculated and, by knowing the positions of the signal sources and receiver, the model of the ionosphere can be generated [27]. In GNSS applications where single frequency receivers are used, this ionospheric effect is a major source of error and, by utilizing the ionospheric map, this error can be largely removed [28].

#### 1.3.10 Atmospheric Limb Sounding

Electromagnetic signals bend while passing through an atmosphere, depending on the pressure, temperature and humidity of the medium. These atmospheric parameters can be measured by using the bending property of the GNSS signals. The measurement can be performed by a LEO satellite for example. In this case, the LEO satellite is searching for GNSS signals which are transmitted at low elevation angles. Since the received GNSS signals are bent in the atmosphere as they pass through it, the parameters can be calculated by knowing the accurate position of the LEO satellite (from the GNSS signals in view) and positions of the GNSS satellites [29, 30]. One mission that has provided valuable information on atmospheric limb sounding was Challenging Mini-satellite Payload (CHAMP) satellite which completed its mission on 19<sup>th</sup> September 2010 [31].

#### 1.3.11 GNSS Reflectometry

Measuring and monitoring the ocean and sea levels, wave height as well as the near surface wind speed and directions are of interest to meteorologists. Having these measurements in real-time provides a powerful means for disaster warning and monitoring. GNSS signals can be used for this purpose. Antennas of the GNSS receiver on-board a LEO satellite are placed in such a way that they receive both direct GNSS signals and the GNSS signals reflected from the surface of the ocean. The reflected signals are affected by the ocean level, wave height and the near surface wind speed and direction. Analyzing the characteristics of the reflected signals allows to provide those information [32–34].

### 1.4 GNSS Receivers in Space

In the previous sections, some applications have been introduced which rely on GNSS receivers operating in space. In addition, the current trend of commercialization of space missions calls for flexible, low-power and low-cost spacecraft. Subsystems and sensors of these spacecraft shall meet stringent criteria such as low power, small size and mass in addition to compliance to the environmental

| Receiver model | Manufacturer | GNSS signal | Frequency bands | Power consumption [W] | Mass [g] |

|----------------|--------------|-------------|-----------------|-----------------------|----------|

| Phoenix [37]   | DLR          | GPS         | L1              | 0.85                  | 20       |

| SGR-05U [38]   | SSTL         | GPS         | L1              | 0.8                   | 40       |

| SPACENAV [39]  | BAE Systems  | GPS         | L1              | 6                     | 1600     |

| SGR-10 [40]    | SSTL         | GPS         | L1              | 5.5                   | 950      |

| BlackJack [41] | JPL          | GPS         | L1 + L2         |                       |          |

| IGOR [42]      | JPL          | GPS         | L1 + L2         | 16                    | 4600     |

| OEM4-G2 [43]   | NovAtel      | GPS         | L1 + L2         | 2.5                   | 85       |

| PolaRx2 [44]   | Septentrio   | GPS         | L1 + L2         | 5                     | 120      |

|                |              | SBAS        | L1              |                       |          |

| TriG [45]      | JPL          | GPS         | L1 + L2 + L5    | 50                    | 6        |

|                |              | Galileo     | E5a             |                       |          |

Table 1.1: Characteristics of selected space capable GNSS receivers

requirements for space applications. One of the most important subsystems on a satellite is the guidance, navigation and control (GNC) subsystem. The addition of GNSS receiver in the GNC subsystem of low-cost and small spacecraft improves their performance and provides new opportunities for new applications. Missions BIRD [35] and PRISMA [36] are two small satellite missions demonstrating such improvements. As mentioned earlier, extra requirements shall be considered for space capable subsystems, thus for GNSS receivers which are addressed in more details in section 2.4.2. Traditional spaceborne GNSS receivers can be bulky and power hungry. Table 1.1 provides a list of selected space capable GNSS receivers.

The results of previous studies show that commercial-off-the-shelf (COTS) integrated circuit (IC) technologies can be used to provide flexible, low-power, lowmass, low-cost and flexible solutions for spaceborne GNSS receivers [46]. Thus, by using the latest microelectronics technology, small, flexible and low-power GNSS receivers can be designed and implemented which are suitable for new space missions which is the approach of this work.

### 1.5 State-of-the-art IC Technology

IC technology developers in terrestrial applications have been focusing on lowpower and miniaturized systems for the last decades. These new technologies have the potential to be implemented in space as well. Thus, the trend of space technology developments is also moving from high power consuming, bulky and costly systems towards low-power, small, low-cost and flexible systems.

The developments in new technologies especially in microelectronics, microelectro-mechanical systems (MEMS) and their packaging provide opportunities for innovations in spacecraft design. Such innovations have the potential to reduce the development costs and time to market. Obtaining such ability provides a chance to define and develop new and innovative space applications. This is especially true for applications which ask for short time to market that were not feasible due to the traditionally long development times of space missions and their dedicated space capable components.

Applications drive the type of space missions. It could be a single spacecraft mission where one spacecraft is sufficient to achieve the objectives or a multispacecraft system which collectively performs the task [47]. In either case, the spacecraft can benefit from multi-purpose and flexible systems which can be lowpower and low-cost by employing new technology. Using such spacecraft provides the opportunity of designing more sophisticated missions which can perform, e.g. even in-situ reconfiguration of the mission. One example of such system is a GNSS receiver capable of adapting the number of used frequency bands depending on its power constraint and the required accuracy. There are operation scenarios, e.g. in scientific missions, where multiple GNSS bands are essential to achieve high accuracy results which in turn means high power consumption. During the operation, it is possible that available power becomes limited. Thus, operation mode can switch to a simple single-band navigation until the nominal power is restored. Such a GNSS receiver would provide an extra degree of freedom in operation in terms of real-time accuracy-power balance. However, such flexible receivers are not yet existing.

#### 1.5.1 Standard IC Technology in Space

Due to special environment requirements of space missions, space-qualified electronics technology is extremely expensive. This rules out the use of such technology for low-cost applications and mass production. On the other hand, developments in standard IC technologies, i.e. IC technology used in terrestrial applications, as well as the more demanding design requirements for their applications, make them promising to be used in space as well.

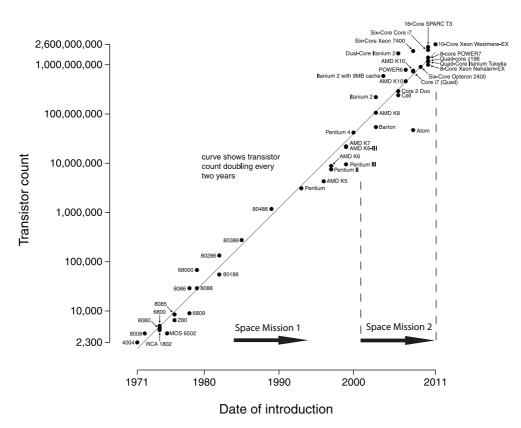

**Figure 1.4:** Speed of advances in IC technology in time (Moor's law) in comparison with average space mission development duration (~ 10 years)

In order to be able to use standard IC technologies in space, there are a number of parameters which shall be considered for space applications. These parameters, all together, assure the operability and fault tolerance of the spacecraft during the mission. Thermal and vacuum conditions and radiation tolerance are the most important parameters for designing electronic systems for space which will be addressed later. The dimensions of the ICs are in the range of millimeters which are very small compared to the exposed maximum sinusoidal vibration wavelength of typically larger than 3 m in air [48, 49]. The vibration effects are of mechanical nature and will not be discussed in this thesis.

#### 1.5.2 Trends in IC Technology for Space Applications

In traditional spacecraft design, the spacecraft is divided in a number of subsystems and the payload. Each of these subsystems and payload is designed separately based on the requirements which are defined by systems engineers and originated from requirements at mission level. The complete spacecraft is then developed by integrating all these subsystems and payload [50,51]. In this approach, each spacecraft is custom-made and the development time is long. With development times of up to 25 years for some missions, the employed technologies would be out-dated by the time the mission is ready to launch because of the fast developments in those technologies. For example, advances in commercial IC technology have been following Moore's law which states that the number of transistors on integrated circuits doubles approximately every two years [52]. Thus, each spacecraft is designed specifically based on the state-of-the-art technology at the time of the preliminary design which may result in bulky and expensive spacecraft with moderate functionality. Fig. 1.4 depicts the speed of advances in IC technology in time (Moore's law) in comparison with average space mission development duration. Considering an average space mission development time of about 10 years, it can be observed that IC technology has faced huge development. However, this traditional design methodology is suitable for designing special and task-specific spacecraft.

The current state-of-the-art IC technology is suitable for designing components for fast time-to-market applications. This experience can be spun into space mission design. Using the standard IC technology in space applications provides opportunities to define new approaches in spacecraft design as well as many new applications based on multi-purpose, flexible, low-power and low-cost spacecraft. The trend of commercialization of space missions demands for reduction in cost as well as time-to-market of new applications to dominate the market.

In order to satisfy such demands, the spacecraft design methodology should be modified. The modifications can start at subsystems which are common in many spacecraft such as communication and navigation. Traditionally, these subsystems are part of the system bus. Since these are similar for different spacecraft, a common design can be used for them. Moreover, it is possible to add reconfigurability to the design such that a subsystem can be adapted and used for several missions. In this case, the concept of mass production, demonstrated for some missions in the past, like Iridium [53], could become feasible as common production approach [54].

Similar to other mass productions, a smart, tunable (or reconfigurable) system should be designed to cover various needs. Mass production is motivated by not only the cost reduction but also the fast time to market of new applications. The state-of-the-art technology will not drastically change during the mission design which makes it possible to use the same technology in many missions which can lead to plug-and-play design concepts. On the other hand, availability of components and design libraries can render modifications of the spacecraft faster at later stages.

| Strengths                      | Weaknesses                          |  |  |

|--------------------------------|-------------------------------------|--|--|

| - Mature technology            | - Lower radiation tolerance         |  |  |

| - Low cost                     | - Insufficient technology readiness |  |  |

| - Fast time-to-market          | level (TRL) for space use           |  |  |

| Opportunities                  | Threats                             |  |  |

| - Mass production              | - Acceptance by space community     |  |  |

| - New space applications       | - Availability                      |  |  |

| - Plug and play design         |                                     |  |  |

| - New approaches in spacecraft |                                     |  |  |

| design                         |                                     |  |  |

Table 1.2: SWOT analysis of standard IC technology used in space

Table 1.2 shows the SWOT analysis of the usage of standard IC technologies in space. The standard IC technology is used to develop millions of devices used daily in terrestrial applications from highly critical systems up to consumer electronics. Thus, it is of high maturity level. The cost of its research and development makes it an expensive technology. However, considering the huge number of units and applications using it, the final product can still be considered as low-cost. The time-to-market is reduced due to the developed experience of experts who are using standard IC technology in their application developments.

As explained previously in this section, mass production, new space applications, plug and play design and new approaches in spacecraft design are opportunities awaiting for exploration and realization.

The standard IC technology is mainly developed for terrestrial applications. Thus, harsh environmental conditions such as radiation should be taken into account when adopting it for space applications. Since it has been incorporated in a limited number of space missions, its technology readiness level (TRL) is typically still insufficient for space applications. It should be investigated when the space community is ready to accept standard IC technology as regular practice for their missions and what design concepts it would apply (e.g. redundancy FDIR). Furthermore, the extend to which non-space industries would be interested to make themselves available for such developments remains to be clarified.

#### 1.5.3 System Integration

Printed circuit boards (PCB) are the commonly used to integrate electronic circuits of subsystems. On these PCBs, electrical and electronic (discrete) components such as connectors, fuses, resistors, capacitors, transistors, ICs, etc. are placed and connected properly. The state-of-the-art IC technology provides means to further

miniaturize the subsystems. In this way, more discrete components are integrated in chips. Ultimately, the complete subsystem can be integrated in a single chip.

There are two different ways to integrate systems on a chip. It can be system on chip (SOC) or system in package (SIP). In SOC, all subsystems are ready as IC design libraries and will be placed together in the final layout and sent for fabrication. An IC design library is a set of fully functional and tested designs which are ready to be manufactured. However, SOC requires all design libraries to be in the same IC technology process, e.g. 0.13  $\mu$ m Complementary Metal-Oxide Semiconductor (CMOS) technology. Once a design library is validated in a certain CMOS technology, in most situations, it can be transferred to other feature sizes as well.

Forcing designers to follow a specific technology may increase the development time. In order to avoid such problems, SIP is a suitable solution. In SIP, different subsystems are integrated in the same IC package even though they are on separate dies. Using SIP also provides the opportunity to integrate MEMS systems in the same package. The interconnections between the subsystems can be with bond wires. Although the bond wires are secured during packaging they can be a point of failure.

As an alternative, a wireless internal communication between subsystems has been proposed in the framework of MicroNed research program [55]. In this approach, the bus, subsystems and payload will contain wireless communication units which follow the same communication protocol to establish an internal network. The complete spacecraft can be integrated by securing them in the same package. In this way, the total mass of the complete system will be a few grams and the total size will be a few square millimeters.

#### **1.6 Thesis Objectives**

In the previous sections, the trends of spacecraft electronic system development have been discussed. There are two main developments in this trend: incorporating standard IC technology in space and integrating multiple subsystems (or functions) on a single chip. The type of subsystems gathered on a chip depends on the commonalities and the relations between them.

One of the subsystems in a spacecraft is the GNC subsystem. The purpose of navigation can be one or more of the applications as introduced in section 1.3. At the time of writing this thesis, GPS and GLONASS are fully operational and Galileo and Compass are partially in operations. However, there are few receivers which can use all of these navigation systems at the same time.