# A Low-Cost Universal Integrated Interface for Capacitive Sensors

Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft op gezag van de rector Magnificus prof. ir. K.C.A.M. Luyben voorzitter van het College voor Promoties,

in het openbaar te verdedigen

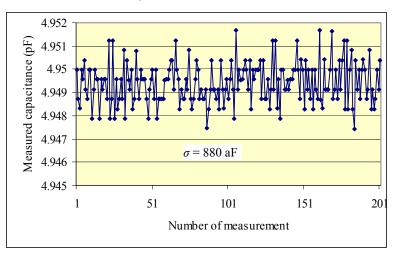

op vrijdag 11 juni 2010 om 10 uur

door

### Ali HEIDARY

Master of Science Electrical Engineering, Electronic Tehran University, Tehran, Iran

geboren te Langroud, Iran

Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. ir. G. C. M. Meijer

Samenstelling promotiecommissie:

| Rector Magnificus,             | voorzitter                              |

|--------------------------------|-----------------------------------------|

| Prof. dr. ir. G. C. M. Meijer  | Technische Universiteit Delft, promotor |

| Prof. dr. G. R. Lahiji         | Universiteit Michigan, USA              |

| Prof. dr. E. Charbon           | Technische Universiteit Delft           |

| Prof. dr. ir. P. P. L. Regtien | Universiteit Twente                     |

| Prof. dr. R Puers              | Katholieke Universiteit Leuven          |

| Prof. dr. J. R. Long           | Technische Universiteit Delft           |

| Dr. ir. M. A. P. Pertijs       | Technische Universiteit Delft           |

Printed by ISBN: 978-94-6113-013-6

Copyright © 2010 by Ali Heidary

All rights reserved. No part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of the author.

Printed in the Netherlands

To my family

# TABLE OF CONTENT

| Cha  | upter 1. Introduction                                         | 1  |  |  |

|------|---------------------------------------------------------------|----|--|--|

| 1-1. | Capacitive-sensor systems                                     | 1  |  |  |

| 1-2. | A universal interface for capacitive sensors                  | 2  |  |  |

| 1-3. | Statement of the problems                                     | 3  |  |  |

| 1-4. | Organization of this thesis                                   | 3  |  |  |

| 1-5. | References                                                    | 4  |  |  |

| Cha  | apter 2. Physical principle of capacitive sensors             | 5  |  |  |

| 2-1. | The concept of capacitance                                    | 5  |  |  |

| 2-2. | Structures of capacitive sensors                              | 6  |  |  |

|      | 2-2-1. The D-type capacitive sensor                           | 7  |  |  |

|      | 2-2-2. The A-type capacitive sensor                           | 9  |  |  |

|      | 2-2-3. The $\varepsilon$ -type capacitive sensors             | 10 |  |  |

| 2-3. | Differential capacitive sensor                                | 12 |  |  |

| 2-4. | Stability of capacitive sensor                                |    |  |  |

| 2-5. | . The effects of connection cable on capacitive sensor        |    |  |  |

| 2-6. | Conclusion                                                    | 13 |  |  |

| 2-7. | References                                                    | 13 |  |  |

| Cha  | apter 3. Measurement technique for capacitances               | 15 |  |  |

| 3-1. | Introduction                                                  | 15 |  |  |

| 3-2. | Excitation and A-D conversion                                 | 15 |  |  |

|      | 3-2-1. Capacitance measurement based on sigma-delta converter | 16 |  |  |

|      | 3-2-2. Capacitance measurement based on a period modulator    | 17 |  |  |

| 3-3. | Circuit- and system-level techniques                          | 18 |  |  |

|      | 3-3-1. Auto-calibration                                       | 18 |  |  |

|      | 3-3-2. Two-port measurement technique                         | 19 |  |  |

|      | 3-3-3. Chopper                                                | 19 |  |  |

| 3-4. | The techniques selected for the capacitive-sensor interfaces  | 20 |  |  |

|      | 3-4-1. The structure of the interface                         | 20 |  |  |

|      | 3-4-2. Capacitance-to-voltage converter (CVC)                 | 21 |  |  |

|      | 3-4-3. Voltage to period converter (VPC)                      | 22 |  |  |

| 3-5.             | Some of important characteristics of the interface                               | 24       |  |

|------------------|----------------------------------------------------------------------------------|----------|--|

|                  | 3-5-1. Flexibility                                                               | 24       |  |

|                  | 3-5-2. Stability                                                                 | 24       |  |

|                  | 3-5-3. No error due to ripple                                                    | 24       |  |

|                  | 3-5-4. No significant error due to clock feedthrough and switch-charge injection | 24       |  |

| 3-6.             | Conclusion                                                                       | 26       |  |

| 3-7.             | References                                                                       | 26       |  |

| Cha              | oter 4. A universal interface for capacitive-sensors                             | 27       |  |

| <b>4-</b> 1.     | Introduction                                                                     | 27       |  |

| 4-2.             | The interface                                                                    | 28       |  |

| 4-3.             | Capacitance range                                                                | 30       |  |

| 4-4.             | Oscillator frequency                                                             | 31       |  |

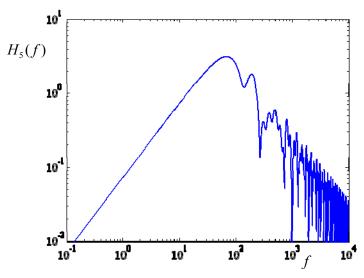

| 4-5.             | The band-limited comparator                                                      | 33       |  |

| 4-6.             | Noise analysis of the interface                                                  | 37       |  |

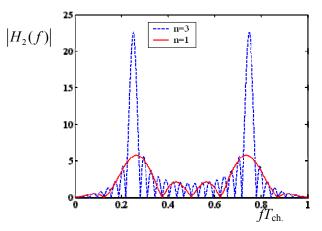

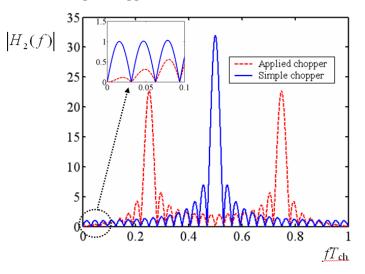

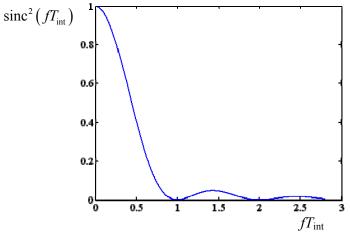

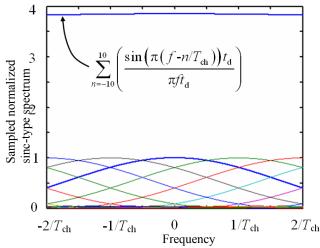

|                  | 4-6-1. Filtering effects in the interface                                        | 38       |  |

|                  | 4-6-1-1. Filtering effect of the chopper with frequency divider                  | 38       |  |

|                  | 4-6-1-2. Filtering effect of the integration                                     | 40       |  |

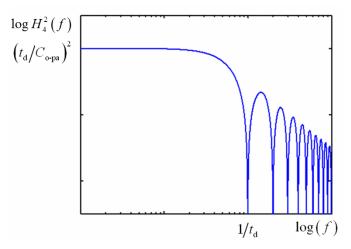

|                  | 4-6-1-3. Filtering effect of band limitation of the comparator                   | 41       |  |

|                  | 4-6-1-4. Filtering effect of auto-calibration including integration              | 43       |  |

|                  | 4-6-2. Effect of different noise sources on the output jitter                    | 44       |  |

|                  | 4-6-2-1. Calculation of jitter in output period caused                           |          |  |

|                  | by the noise in the integration current                                          | 44       |  |

|                  | 4-6-2-2. Calculation of jitter in the output period as caused by noise           |          |  |

|                  | in the sampling and charge-transfer circuit                                      | 48       |  |

|                  | 4-6-2-3. Calculation of jitter in output period as caused by sampled             |          |  |

|                  | noise voltage at the input of the capacitor-to-voltage converter CVC             | 51       |  |

|                  | 4-6-2-4. Calculation of jitter in output period caused by                        |          |  |

|                  | The sampled noise voltage of integrator amplifier                                | 52       |  |

|                  | 4-6-2-5. Calculation of jitter in the output period caused by the noise          |          |  |

|                  | voltage of the CVC amplifier, integrator amplifier and                           | 54       |  |

|                  | comparator in continues state                                                    | 54<br>59 |  |

|                  | 4-6-3. Quantization noise                                                        | 59<br>60 |  |

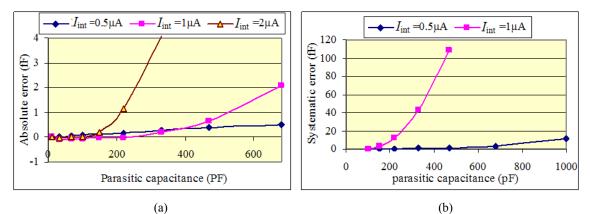

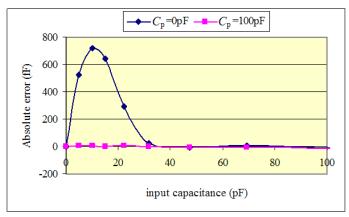

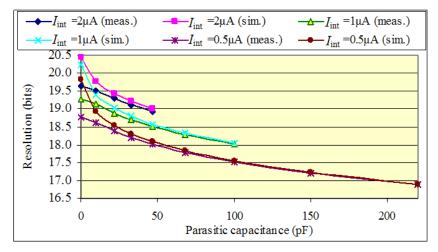

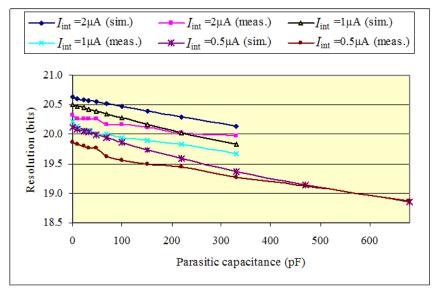

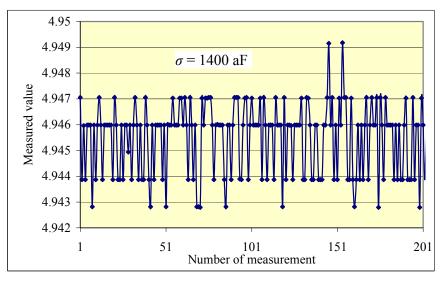

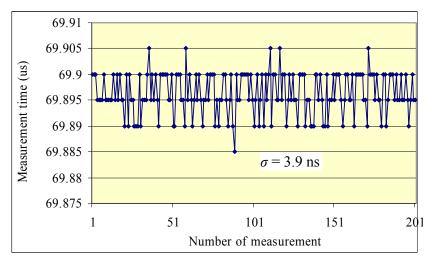

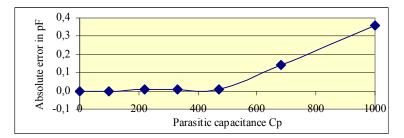

| 4-7.             | 4-6-4. Translation of jitter to the resolution The effect of PCB parasitic       | 60<br>61 |  |

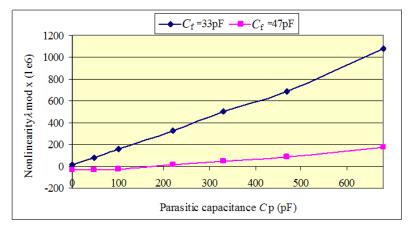

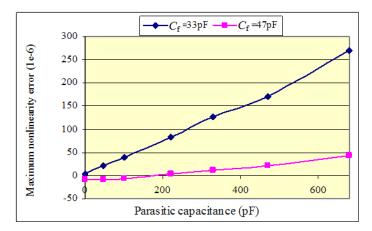

| 4-7.<br>4-8.     | The effect of PCB parasitic<br>The poplinearity error                            | 63       |  |

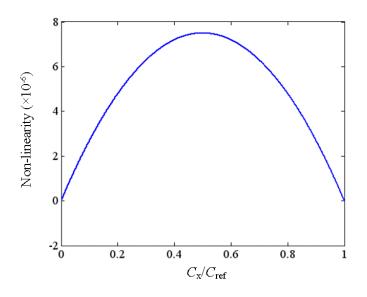

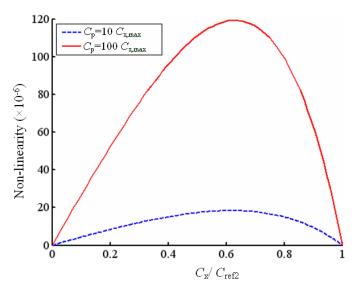

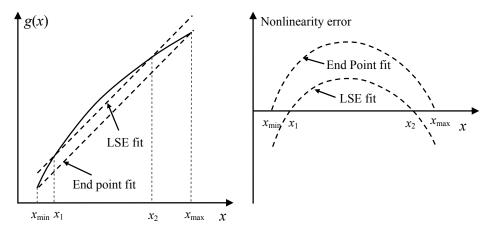

| <del>4</del> -0. | The nonlinearity error 63                                                        |          |  |

|       | 4-8-1. The nonlinearity of capacitance to voltage converter                | 63 |  |

|-------|----------------------------------------------------------------------------|----|--|

|       | 4-8-1-1. The nonlinearity of CVC due to limited open loop gain             | 63 |  |

|       | 4-8-1-2. The nonlinearity of the CVC due to the nonlinear                  |    |  |

|       | Of the open loop gain                                                      | 64 |  |

|       | 4-8-2. Nonlinearity of the interface caused by the                         |    |  |

|       | voltage dependency of the integrated capacitor                             | 67 |  |

|       | 4-8-3. Nonlinearity of the interface caused by                             |    |  |

|       | dielectric absorption of the capacitors                                    | 67 |  |

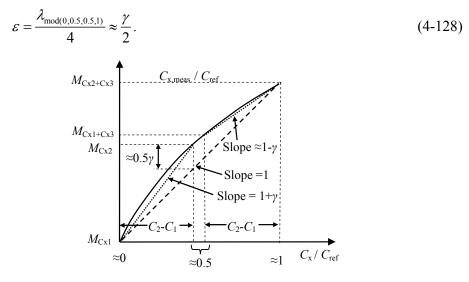

| 4-9.  | A method for measurement of the nonlinearity                               | 68 |  |

| 4-10. | Conclusion                                                                 | 72 |  |

| 4-11. | References                                                                 |    |  |

| Chap  | <i>pter 5.</i> A flexible high-resolution interface for floating capacitor | 75 |  |

| 5-1.  | Introduction                                                               | 75 |  |

| 5-2.  | Design considerations for the interface                                    | 75 |  |

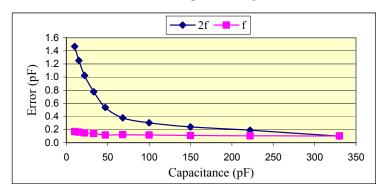

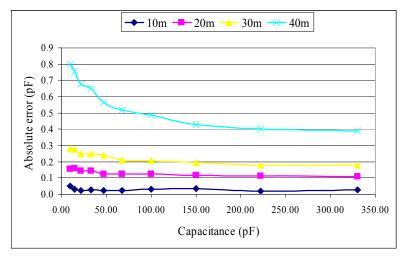

| 5-3.  | Source of errors                                                           | 77 |  |

|       | 5-3-1 Settling error                                                       | 78 |  |

|       | 5-3-2 Error due to slewing                                                 | 80 |  |

|       | 5-3-3 Charge-loss error                                                    | 81 |  |

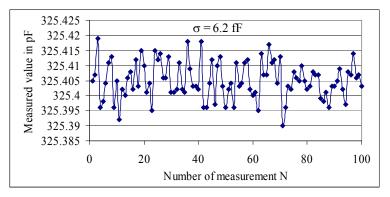

| 5-4.  | Noise performance                                                          | 81 |  |

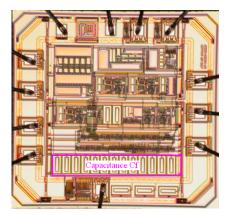

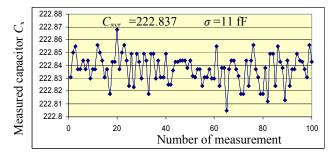

| 5-5.  | Implementation and measurement results                                     | 83 |  |

|       | 5-5-1 Implementation                                                       | 83 |  |

|       | 5-5-2 Settling error                                                       | 83 |  |

|       | 5-5-3 Slewing error                                                        | 85 |  |

|       | 5-5-4 Charge-loss error                                                    | 86 |  |

|       | 5-5-5 Maximum capacitance range                                            | 86 |  |

|       | 5-5-6 Noise error                                                          | 87 |  |

|       | 5-5-7 Maximum measurement speed and required sampling frequency            | 89 |  |

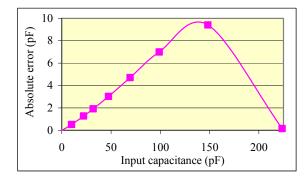

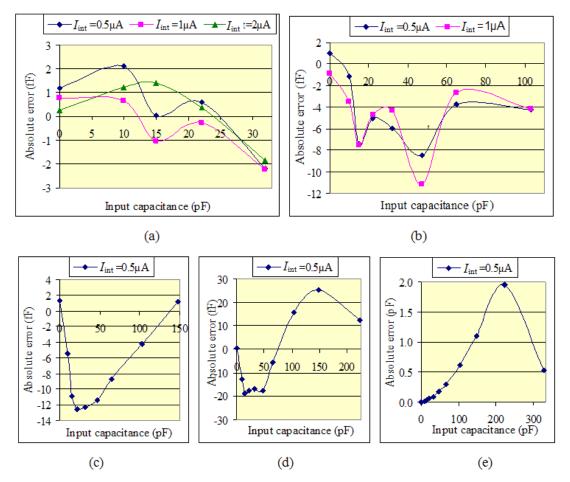

|       | 5-5-8 Nonlinearity                                                         | 91 |  |

| 5-6.  | User guide                                                                 | 93 |  |

| 5-7.  | Conclusion                                                                 | 94 |  |

| 5-8.  | References                                                                 | 95 |  |

| Chap  | oter 6. A novel interface with very high linearity                         | 97 |  |

| 6-1.  | Introduction                                                               | 97 |  |

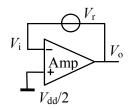

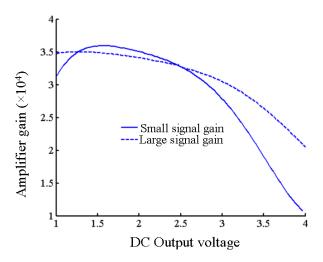

| 6-2. | . The interface with negative feedback                    |     |

|------|-----------------------------------------------------------|-----|

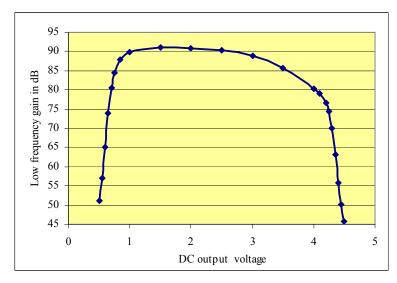

| 6-3. | Condition to be met for proper operation                  | 99  |

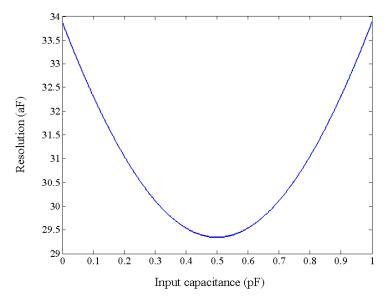

| 6-4. | Noise performance of the interface with negative feedback | 102 |

| 6-5. | Implementation and measurement results                    | 104 |

| 6-6. | Conclusion                                                | 108 |

| 6-7. | References                                                | 108 |

|      |                                                           |     |

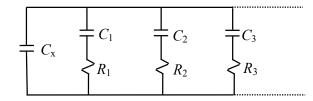

| Chaj | pter 7. An Integrated Interface for Leaky Capacitive sensors           | 109 |

|------|------------------------------------------------------------------------|-----|

| 7-1. | Introduction                                                           | 109 |

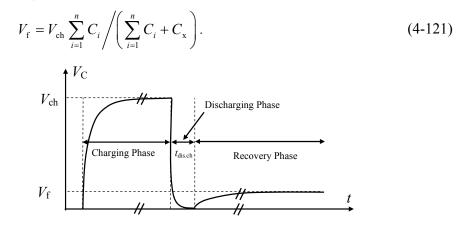

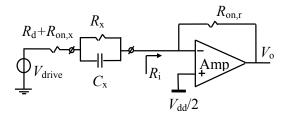

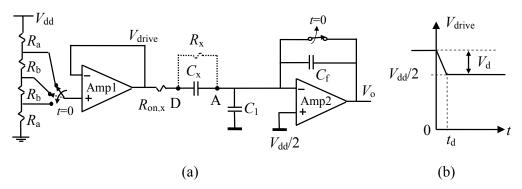

| 7-2. | Circuit principles                                                     |     |

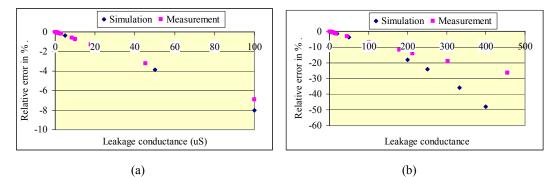

| 7-3. | Error analysis                                                         | 110 |

|      | 7-3-1. Error caused by leakage during the charging phase               | 110 |

|      | 7-3-2. Errors caused by leakage during charge-transfer phase           | 112 |

|      | 7-3-2-1. The error caused by a DC-voltage difference across the sensor | 112 |

|      | 7-3-2-2. The error caused by a voltage difference                      |     |

|      | across the sensor at transient moments                                 | 112 |

|      | 7-3-2-2-1. Error caused by finite fall time                            | 113 |

|      | 7-3-2-2. Error caused by $R_1 = R_d + R_{on,x}$                        | 114 |

|      | 7-3-2-2-3. Error caused by finite bandwidth of the op-amp              | 114 |

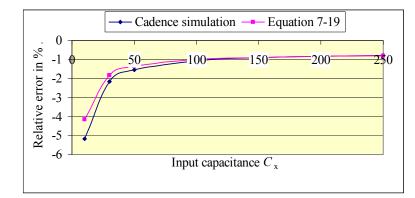

|      | 7-3-3. Total error before auto-calibration                             | 115 |

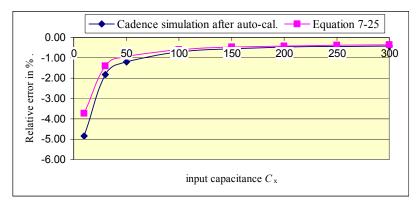

|      | 7-3-4. The total error after auto-calibration                          | 116 |

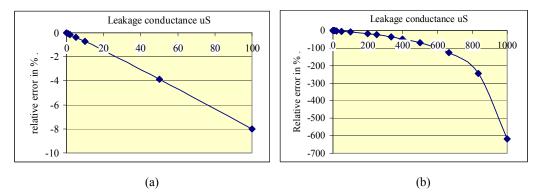

|      | 7-3-5. Effect of leakage resistance on the transient voltage           | 117 |

| 7-4. | Implementation and measurement results                                 | 117 |

| 7-5. | Conclusion                                                             | 120 |

| 7-6. | References                                                             | 121 |

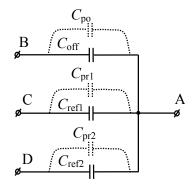

| Cha  | pter 8. An Integrated Interface for grounded Capacitive Sensors        | 123 |

| 8-1. | Introduction                                                           | 123 |

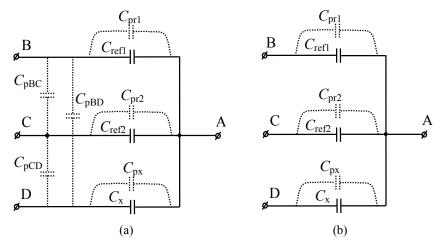

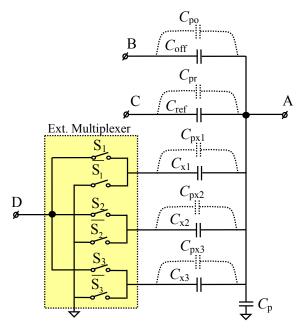

| 8-2. | System setup and front-end circuit                                     | 124 |

| 8-3. | Effects of component imperfections                                     | 126 |

|      | 8-3-1. The Offset                                                      | 126 |

|      | 8-3-2. Switch ON resistance, R <sub>on</sub>                           | 127 |

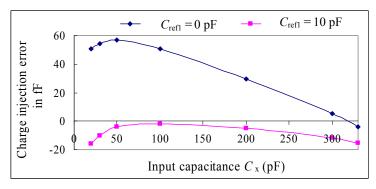

|      | 8-3-3. Switch-charge injection                                         | 129 |

|      | o 5 5. Switch charge injection         | 12) |

|------|----------------------------------------|-----|

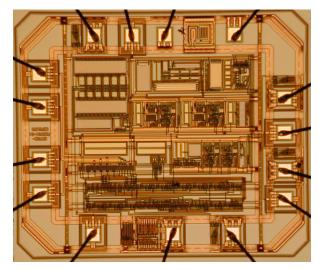

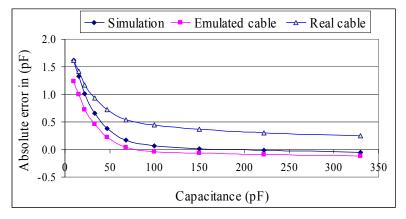

| 8-4. | Implementation and measurement results | 130 |

| 8-5. | Conclusion                             | 133 |

| 8-6.                | References        |                        | 134 |

|---------------------|-------------------|------------------------|-----|

| Ori                 | ginal contribu    | ition                  | 135 |

| App                 | oendix A: Ter     | minology               | 137 |

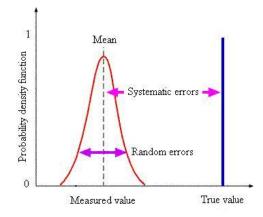

| A-1                 | Error and uncer   | tainty                 | 137 |

| A-2                 | Error sources     |                        | 137 |

|                     | A-2-1 Systemat    | tic errors             | 137 |

|                     | A-2-1-a           | Loading errors         | 137 |

|                     | A-2-1-b           | Calibration errors     | 137 |

|                     | A-2-1-c           | Dynamic errors         | 138 |

|                     | A-2-2 Random      | errors                 | 138 |

|                     | A-2-2-b           | Environmental errors   | 138 |

|                     | A-2-2-b           | Quantization error     | 138 |

|                     | A-2-2-c           | Drift                  | 138 |

|                     | A-2-2-d           | Noise                  | 138 |

| A-3                 | Specifications of | of measurement systems | 139 |

| A-4                 | References        |                        | 140 |

| Sum                 | mary              |                        | 141 |

| Samenvatting        |                   | 143                    |     |

| List of Publication |                   | 145                    |     |

| Abo                 | ut the author     |                        | 147 |

| Ack                 | nowledgement      |                        | 149 |

# CHAPTER 1

# Introduction

### 1-1 Capacitive-sensor systems

Capacitive sensor elements can be applied in many applications to measure many different types of signals such as displacement, proximity, humidity, acceleration, liquid level, gas concentration, etc., [1], [2]. They can be implemented on printed-circuit boards [3], glass substrates, silicon chips, or other types of material [4]. Because the electrodes of a capacitive sensor element do not need to be in mechanical contact with each other, they are suited for small-range contact-less sensing [3]. The attractive properties of capacitive sensors are that they consume very little power, that their cross sensitivity to temperature is very low, and that shielding stray electric fields is less complex than shielding, for instance, inductive sensors from magnetic disturbances [2]. The main drawbacks of capacitive sensors concern their sensitivity to contamination and condensation, and their sensitivity to Electro-Magnetic Interference (EMI). However, in this thesis we will show that some of these drawbacks can be overcome by proper design.

Depending on the application, capacitive sensor can be floating (i.e. sensors in which neither of the electrodes is grounded) or grounded (i.e. sensors in which one of the electrodes is grounded) [5]. Based on the properties of the electrode structure and the dielectric material, the electrical properties of capacitive sensors can differ significantly. For instance, they can demonstrate pure capacitive behavior or have resistive leakage [6]. Their values can range from less than one pF up to hundreds of pF or even to nF. Sometimes their values can change very fast, such as in displacement sensors for servo systems, while in other applications their values can be semi-static. Besides the aforementioned sensor conditions, the effects of parasitic capacitances of the connecting wires should also be taken into account.

At present, a number of interface ICs for capacitive sensors can be found in the market. Examples of such interfaces are the capacitance-to-digital converters for floating capacitors AD7745 and AD7746 of Analog Devices [7], and the AD7747 for grounded capacitors. Additionally, the same company offers the AD7150, which is a low-power (300  $\mu$ W) capacitive-sensors interface. With all of these interfaces, the maximum capacitance that can be measured amounts to 8 pF, while the maximum allowable parasitic capacitance is 100 pF. The measurement results of all of these interfaces are very sensitive to the effects of resistive leakage.

Another capacitive-sensor interface in the market is the MS3110 of Irvin sensors [8]. For this interface, the range for the input capacitances is limited to only 10 pF.

The work presented in this thesis concerns an interface that is based on and is complementary to Smartec's UTI (Universal Transducer Interface) [9]. For the capacitive modes of the UTI some major limitations are:

- 1. High sensitivity to resistive leakage currents;

- 2. The interface is only suited for floating capacitors and not for grounded ones;

- 3. The input ranges for the capacitive modes are programmable for only three discrete levels: 2pF, 12 pF and 300 pF, while for the 300 pF range the excitation voltage is decreased, which decreases the resolution;

- 4. The fastest data acquisition rate is up to 100 samples per second.

Due to the severe limitations of these interfaces, they are only suitable for a very limited number of applications. For instance, in many applications the range of capacitance values does not fit into the dynamic ranges of these interfaces. Moreover, the cable parasitic capacitance can be much larger than what these interfaces can handle. In many applications, the required data acquisition rate is much higher than what is offered by these interfaces. To solve these problems, in this thesis a universal interface for capacitive sensor with improved performance is introduced.

# 1-2 A universal interface for capacitive sensors

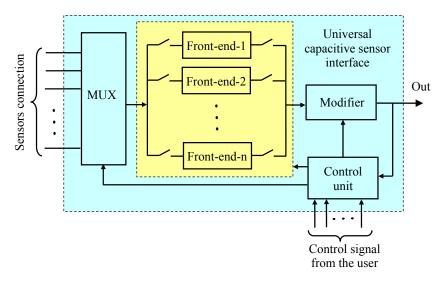

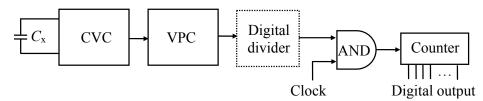

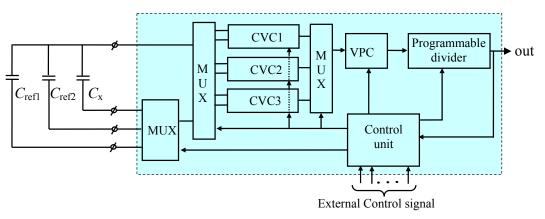

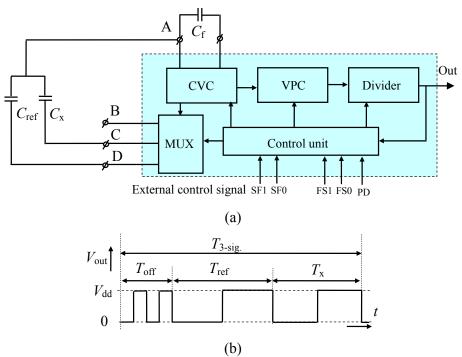

In order to achieve the best performance, we need to optimize the interface for each specific application. This means that for each application we should develop different electronic circuits. From an economical point of view, this approach is not attractive. Moreover, it requires the effort of many highly-specialized expertise. To solve this problem, this thesis describes a flexible universal interface which can be used for different applications. The main part of the interface is common to all applications. The main difference is implemented in a relatively small part: the front-end. Figure 1-1 shows a block diagram of this interface.

Fig. 1-1: The universal capacitive sensor interface.

Just with a logic control signal that can be set by the user, the measurement configuration is modified for different applications and has the following properties:

- This interface is suited for both floating and grounded capacitive sensors;

- It has also a front-end for leakage-immune measurements of floating capacitors;

- It can be optimized for short or long connection cables;

- The input dynamic range is adjustable over a wide range;

- The excitation voltage can be chosen by the user;

- The period and measurement times can be chosen for optimum values, which are application-dependent.

All these options make the proposed interface suitable for a wide variety of capacitive sensor applications.

# **1-3** Statement of the problems

The objective of the work presented in this thesis is to design an integrated universal capacitive sensor interface with emphasis on maximizing the performance in relation to the costs. To begin with, some typical applications and sensor elements are considered for this design. Next, the electrical properties of the capacitive sensors are characterized as accurately as possible. Then, the most important interface requirements for different applications are considered. The final step is to make a trade-off between the number of modes, the number of control signals, and the performance. A further increase in the number of modes will decrease the user friendliness and increase the test-related costs. Therefore, the number of modes should be kept to a minimum, with a minimum sacrifice of performance and application range.

# 1-4 Organization of this thesis

The text in this thesis is organized as follows:

- Chapter 2 covers general physical aspects of capacitive sensors.

- Chapter 3 deals with the concepts for capacitance measurements.

- Chapter 4 presents a detailed analysis of the applied circuits.

- The design presented in chapter 5, are based on the analysis presented in chapter 4 together with an experimental evaluation.

- A novel interface with negative feedback is introduced in chapter 6, together with an experimental evaluation.

- Chapter 7 deals with interface circuits for leaky capacitive sensors, along with an experimental evaluation.

- The analysis and design of a switched capacitor front-end for grounded capacitive sensors is presented in chapter 8, together with an experimental evaluation.

- Chapter 9 covers the original contribution in this work.

- A brief overview of some basic measurement principles is presented in Appendix A.

### References

[1] G. C. M. Meijer (ed), Smart sensor systems, Chichester, UK: Wiley, 2008.

[2] L. K. Baxter, Capacitive sensors, design and applications, New York: IEEE Press, 1997.

[3] X. Li, Low-cost smart capacitive sensors, PhD thesis, Delft University of Technology, The Netherlands, 1997.

[4] C. Lu, B. E. Boser, and M. Lemkin, "A monolithic surface micromachined accelerometer with digital output", IEEE J. Solid-State Circuits, vol. SC-30, pp. 1367–1373, December 1995.

[5] S. M. Huang, A. L. Stott, R. G. Green, and M. S. Beck, "Electronic transducers for industrial measurement of low value capacitances", J. Phys. E: Sci. Instrum., vol. 21, pp. 242-250, 1988.

[6] X. Li and G. C. M. Meijer, "Elimination of shunting conductance effect in a low-cost capacitive-sensor interface", IEEE Trans. Instrum. Meas.,vol. 49, no. 3, pp. 531-534, June 2000.

[7] Analog Device, http://www.analog.com

[8] Irvin Sensors Corporation, "Universal capacitive readout", http://www.irvine-sensors.com/

[9] Smartec, "Universal transducer interface", http://www.smartec.nl/interface\_uti.htm

# **CHAPTER 2**

# Physical principles of capacitive sensors

### 2-1 The concept of capacitance

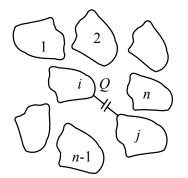

Capacitors belong to the oldest types of electrical devices [1]. The capacitor was invented in 1746 by Cuneus and Mussenbroek, who worked at the University of Leiden, and was originally called the 'Leidsche fles'. For a good, fundamental understanding of the concept of capacitance we have to reconsider the original definition of capacitance given by Maxwell in 1873 [2]. If we have a configuration made up of any number of electrodes (Fig. 2-1), then the capacitance between two of the electrodes (say, *i* and *j*) is given by the quotient of the charge induced on one of the electrodes due to the potential difference between the two electrodes, and that difference in potential. When written as an equation this gives:

$$C_{ij} = \frac{Q_{ij}}{V_i - V_j},\tag{2-1}$$

where  $C_{ij}$  is the capacitance between electrodes *i* and *j*;  $Q_{ij}$  is the charge on electrode *i* (and in contrasting form on *j*) induced by the potential difference  $(V_i - V_j)$ ; and  $V_i$  and  $V_j$  are the potentials on electrodes *i* and *j*, respectively. For all the other electrodes (except *i* and *j*) not their potential, but their presence contributes to the capacitance between the electrodes *i* and *j*.

Fig. 2-1: Fundamental representation of capacitance between conductors.

When only the capacitance between two of the conductors is of interest, the presence of other conductors is an undesirable complication. To deal with this, it is customary to distinguish between two-terminal and multi-terminal capacitors and their measurements.

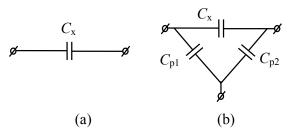

In a two-terminal capacitor (Fig. 2-2(a)) the somewhat indefinite contributions of the other conductors to the capacitance of interest might be negligible/acceptable. To reduce their influence, one of the conductors of primary interest surrounds the other one, so that the capacitance between them is independent of the location of all other bodies except for those in the vicinity of the terminals.

A three-terminal capacitor (Fig. 2-2(b)) represents the common situation of two active electrodes surrounded by a shield conductor. The direct capacitance  $C_x$  between the two active

electrodes is the capacitance of interest. When shielded leads are used, this capacitance is independent of the location of all other conductors except for that of the shield.

Fig. 2-2: (a) Two and (b) three-terminal capacitors.

In the case of just two electrodes, the capacitance depends on their size, shape, distance, and the permittivity of the medium. When these parameters are actually known, the capacitance between the electrodes can be calculated. However, analytical calculations are only applicable for simple structures. In general, a finite element method (FEM) is used to find an approximated solution. Fortunately, in capacitive sensors, we are usually interested in *changes* of capacitances as caused by a measurand rather than in *absolute values* of these capacitances. When designing electrode structures, care should be taken to determine precisely how the measurand influences the capacitance. This often leads to electrode structures that have a high degree of similarity with flat electrodes, which are often in parallel, flat or cylindrical planes. Because this thesis is dedicated to electronic interfaces for measuring capacitive sensors, a study focusing on the details of capacitive-sensor structures is beyond the scope of this work. Yet, understanding the basic principles of capacitive sensor will help in designing a better measurement system. Therefore, the basic principles of these sensors will be reviewed here.

### 2-2 Structures of capacitive sensors

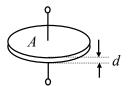

The simplest structure of a capacitive sensor is that of two flat parallel plates with area A and distance d (Fig. 2-3).

Fig. 2-3: A capacitor with flat, parallel plates.

When d is much smaller than the plate dimensions, the value of the capacitance can be approximated as:

$$C = \varepsilon_r \varepsilon_0 \frac{A}{d} , \qquad (2-2)$$

where  $\varepsilon_0$  is the permittivity of the vacuum ( $\varepsilon_0 = 8.85 \times 10^{-12}$  F/m), and  $\varepsilon_r$  is the relative permittivity of the dielectric in between the two electrodes.

Equation (2-2) is only valid for that condition specified. Yet, also for other types of capacitors, the capacitance value increases with an increase in the effective area or the

permittivity of the medium, and decreases with an increase in the effective distance. Accordingly, three types of capacitive sensors can be distinguished:

- Capacitive sensors with fixed values of A and d, where the measurand modifies the dielectric properties (ε-type);

- Capacitive sensors with fixed values of A and  $\varepsilon$ , where the measurand modifies the distance (D-type);

- Capacitive sensors with fixed values of d and  $\varepsilon$ , where the measurand modifies the effective area (A-type).

Since relative permittivity is not a very fundamental quantity, and can be either temperaturedependent, inhomogeneous or anisotropic for certain materials, the accuracy of  $\varepsilon$ -type sensor is limited.

The *D*-type capacitive sensors are very effective for short-range displacement measurements. However, sensitivity decreases significantly with increasing distance. In contrast to this, an *A*-type can also be used for very large measurement ranges.

Some example of the three different types of capacitive sensors will now be discussed.

## 2-2-1 The D-type capacitive sensors

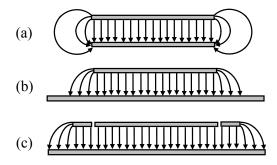

As mentioned in the previous section, the value of parallel-plate capacitors can be calculated with Equation 2-2, provided that the distance *d* between the two plates is much smaller than the dimensions of the plates itself. However, due to fringes of the fields (Fig. 2-4(a)), the actual capacitance value is always slightly larger than the one calculated. Since this difference depends on the distance *d*, fringe fields can cause non-linearity in the measurement. Another problem with the structure of figure 2-4(a) concerns its sensitivity to lateral movement. This problem can be solved simply by making one of the plates bigger (Fig. 2-4(b)). The homogeneity of the electric field can be significantly improved by incorporating guard rings into the sensor (Fig. 2-4(c)), as suggested by Thomson [3]. A guard ring is an electrode that encloses the sensing electrode; the two electrodes are separated by an insulator but operated at the same electric potential. For high accuracy, the width of the guard electrodes should be 3 to 5 times larger than the electrode distance *d* [1].

Fig. 2-4: A capacitive displacement sensor: (a) simple parallel-plate capacitor, (b) parallel-plate capacitor insensitive to lateral movement, (c) parallel-plate capacitor with guard ring.

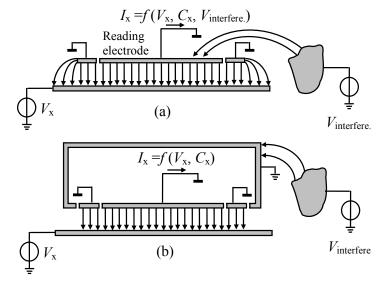

As will be shown in chapter 3, one way to measure a capacitor is to drive one terminal of the capacitor with a voltage source and to measure the induced charge or current at the other terminal (floating capacitive sensor). Then, in unshielded capacitive sensors (Fig. 2-5(a)), in addition to the real excitation terminal of the capacitor, any interfering voltage  $V_{\text{interfere}}$ .

connected to neighboring conductors (Fig. 2-5(a)) can induce charge as well. Shielding the whole system will remove this effect. However, usually this is not applicable. As an alternative, the reading terminal can be shielded (Fig. 2-5(b)), which can remove the main part of the interference. Filtering in the electronic circuit can further reduce the effect of interfering signals if they are in different frequencies.

Fig. 2-5: Reading a capacitive displacement sensor (a) with and (b) without shielding.

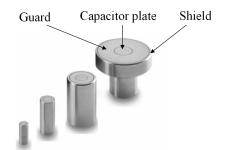

The *D*-type capacitive displacement sensors are sometimes divided into the categories: single and dual plate [4]. Single-electrode capacitive sensors (Fig. 2-6) use a conductive target surface as a second electrode. The size of the sensor head can be different and is chosen in relation to the target range and the target shape [5]. In single-plate capacitive sensors, the contra electrode (the target) is usually connected to ground. In that case the measurement concept of figure 2-5 cannot be applied. The measurement of such grounded capacitive sensors will be discussed in chapter 8.

Fig. 2-6. Capacitive sensor heads for displacement measurement. For different target ranges and shapes different sizes are available (with courtesy of micro-epsilon).

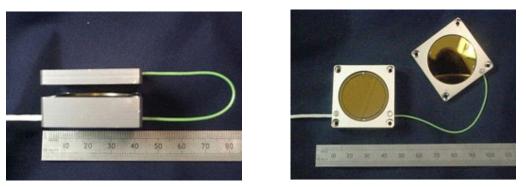

Since the accuracy of single-electrode capacitive sensors depends on the quality of the target surface, which is usually less flat than that of the sensor head, for high accuracy, dual-plate capacitive sensors (Fig. 2-7) are preferable.

Fig. 2-7: Dual plate capacitive sensor for displacement measurement (courtesy of Queensgate Instruments).

Moreover, in dual-plate capacitive sensors, both electrodes are available, so that the capacitance can be read by special interface circuits that are intrinsically immune to stray capacitances [6].

### 2-2-2 The A-type capacitive sensors

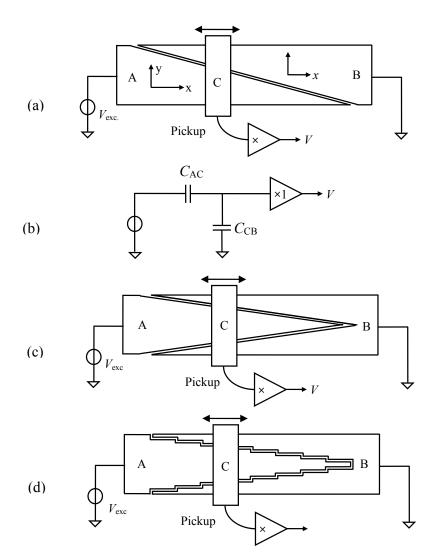

The *A*-type capacitive sensors have been investigated extensively by, for instance, de Jong [8], Zhu [7], and Li [9]. Figure 2-8(a) shows a capacitive motion encoder [10] the principle of which is based on the measurement of area variations. While the pick-up plate (plate C) moves from left to right, the effective area between plate A and plate C (i.e. the associated capacitance,  $C_{AC}$ ) decreases. At the same time the capacitance  $C_{CB}$  between plate B and plate C increases. When the pick-up plate moves from the right end to the left end, the output voltage  $V_0$  of the buffer amplifier (Fig. 2-8(b)) changes from the excitation voltage  $V_{exc.}$  to zero. The structure of figure 2-8(a) is sensitive to tilt in two axes: The effect of tilt around the vortical (*x*) axis causes a large error in the measured position. To reduce this error, the modified ramp pattern of figure 2-8(c) can be used. It can be seen that close to the right and the left end, the pickup voltage is a nonlinear function of the position [10]. However, with the pattern shown in figure 2-8(d), this nonlinearity problem can be reduced [10]. Similar to the *d*-type capacitive sensor, we need guard and shield electrodes around the pickup plate.

The accuracy of *A*-type capacitive sensors highly depends on the mechanical accuracy. The major mechanical non-idealities originate from the non-idealities of the electrodes, such as non-flatness of the electrode surface, obliqueness, deformation, frayed edges, and gaps [9].

Fig. 2-8: A capacitive motion encoder according to [10]: (a) Basic structure, (b) the electrical equivalent circuit, (c) a modified structure which is immune to tilt around the horizontal (*x*) axis, and (d) a modified version with less nonlinearity at the ends.

### 2-2-3 ε-type capacitive sensors

The  $\varepsilon$ -type capacitive sensors may be used to characterize materials or to determine the position of the interface between various types of liquids. Well-known examples of such sensors are capacitive humidity sensors and liquid level gauges. In these sensors resistive leakage can be an important issue, which needs to be considered in interface design.

Figure 2-9 shows an example of a liquid-level gauge [11] which is used to measure the level of conductive liquids. The isolated probe and the conductive-liquid can be considered as two plates of a capacitor, while the electrode isolation layer acts as the dielectric medium. With a set of dual probe, non-conductive-liquid levels can also be detected. In this case, the two probes act as the two electrodes of a capacitor and the non-conductive liquid acts as the dielectric medium.

Fig. 2-9: A capacitive level sensor, reproduced with permission of Omega engineering, INC, Stamford, CT 06907 USA, <u>WWW.OMEGA.COM</u>.

The probe, which can be rigid or flexible [11], commonly employs conducting wire insulated with polytetrafluoroethene, PTFE (Teflon). In the case of conductive liquid in conductive fluid vessels, the use of insulated wire is inevitable. Flexible probes must be used when there is insufficient clearance for a rigid probe, or in applications that demand very long lengths. Rigid probes offer higher stability, especially in turbulent systems [11].

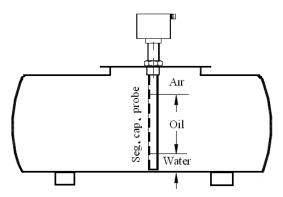

The use of a capacitance array implemented with a large number of segmented electrodes [8] can improve the repeatability, resolution, and even functionality of the sensor. In segmented capacitive level gauges, a first-course level measurement is performed by a fast measurement. Next, a more accurate (fine) measurement is performed using interpolation of the capacitances of the electrodes close by the liquid-gas interface [8], [12]. With a single-electrode capacitive probe, only one interface, usually the interface of liquid with air, can be measured. However, with a segmented capacitive probe, more than one interface, for instance the interface between water and oil at the bottom of the tank and the interface between oil and air at the top, can be measured with one probe. Figure 2-10 shows the installation of a segmented capacitive level sensor to measure these interfaces in a storage tank.

Fig. 2-10: Installation of a segmented capacitive level sensor to measure the two interfaces between water, oil and air.

# 2-3 Differential capacitive sensor

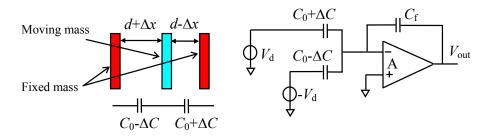

In some applications, the change in capacitance value due to a measurand is much less than the sensor rest (offset) capacitance [13]. When this offset capacitance is not stable, this will cause a resolution problem. A possible solution for this problem can be found in the use of differential capacitive sensors. As an example, figure 2-11 shows a differential capacitive sensor for a MEMS accelerometer with capacitive readout [13]. In addition to reducing the resolution problem, the applied half-a-bridge structure has the advantages of CM rejection of interfering effects, including temperature drift.

Fig. 2-11: (a) MEMS accelerometer and (b) the read-out circuit.

# 2-4 Stability of capacitive sensor

Environmental changes such as temperature, humidity and pressure will change the capacitance value. Since controlling these environmental factors is not simple in most measurement systems, the stability of the sensor is limited. Therefore, amongst other causes, environmental changes limit the minimum detectable variation of the measurand.

The sensitivity of a capacitance value to these parameters comes from both the thermal expansion of the electrodes or their distance, and the sensitivity of dielectric constant to environmental parameters. Most common metals and alloys have a temperature coefficient of linear expansion in the range of  $(9 \text{ to } 29) \times 10^{-6}$ /°C [14].

Moreover, the dielectric constant is quite sensitive to temperature, humidity and pressure. For instance, as their basic property, some capacitive humidity sensors use the  $\varepsilon$ -dependency on humidity. A capacitive sensor with air as the dielectric constant (which is quite stable) is quite simple to build and has many applications. The sensitivity of the dielectric constant of air to temperature, humidity and pressure, amounts to about  $5 \times 10^{-6}$ /°C,  $1.4 \times 10^{-6}$ /%RH and  $100 \times 10^{-6}$ /atm, respectively [10, p. 73]. Even these small sensitivities can limit the accuracy of the sensor.

The environmental effects can be compensated by either differential structure (section 2-3), or by building a reference capacitor that is similar to the sense capacitors and using a balanced bridge detector [15] with auto-calibration [16].

# 2-5 The effect of connection cables on capacitive sensors

In addition to the capacitive sensor itself, the connection cable also needs to be shielded. Figure 2-5(b) shows the case for when both the receiving electrode of capacitive sensor and the current detector (electronic interface) are within a shielded box. However, often the electronic interface is far from the sensor. In that case, at least the current sensing wire needs

to be shielded (Fig. 2-12).

Fig. 2-12: (a) Floating capacitive sensor with shielded connection cable and (b) the first order equivalent circuit.

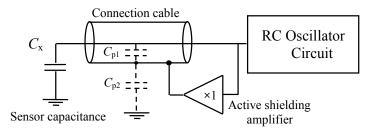

Floating capacitors can be measured with interface circuits that are intrinsically immune to parasitic capacitances to the ground [6]. However, in the case of a grounded capacitive sensor, the shield should be connected to the same potential as the core using active guarding (Fig. 2-13) [6, 17]. The concept of active guarding is explained with more detail in chapter 8.

Fig. 2-13: Active guarding for a grounded capacitive sensor.

# 2-6 Conclusion

The basic principles of capacitive sensors have been presented. The concepts of two-terminal and three-terminal capacitor were explained. A short explanation about shielding and guarding was presented. Three different types of capacitive sensor -A-type, D-type and  $\varepsilon$ -type– were shown together with some examples. Segmented and differential capacitive sensors and their benefits were also discussed. Finally, shielding requirements of connection cables and the concept of active guard for grounded capacitive sensor were referred to.

### References

[1] W. C. Heerens. Review Article: Application of capacitance techniques in sensor design.

[2] J. C. Maxwell, A treaties on electricity and mMagnetism, Oxford: Clarendon, 1873.

[3] Sir W. Thomson. Report of British Association. Dundee, 1867.

[4] http://www.physikinstrumente.com/en/products/capacitive\_sensor/index.php

[5] R. R. Vallance, E. R. Marsh, and P. T. Smith, "Effect of spherical targets on capacitive displacement measurement", Journal of Manufacturing Science and Engineering, vol. 126, pp. 822-829, Nov. 2004.

[6]. S. M. Huang, A. L. Stott, R. G. Green, M. S. Beck, "Electronic transducers for industrial measurement of low value capacitances", J. Phys. E: Sci. Instrum., vol. 21, pp. 242-250, 1988.

[7] F. Zhu, "Development of capacitive position transducer through a mechatronic approach", PhD thesis, Delft University of Technology, The Netherlands, April 1992.

[8] G. De Jong, "Smart capacitive sensors, physical, geometrical and electronic aspects", PhD thesis, Delft University of Technology, The Netherlands, April 1994.

[9] X. Li "Low-cost smart capacitive sensors", PhD thesis Delft University of Technology, The Netherlands, 1997.

[10] L. K. Baxter, "Capacitive sensors: design and applications", New York: IEEE Press, 1997.

[11] www.omega.com

[12] F. N. Toth "A design methodology for low-cost, high-performance capacitive sensors", PhD thesis, Delft University of Technology, The Netherlands, 1997.

[13] B. E. Boser, "Capacitive sensor interfaces", Lecture notes, Berkeley sensor and actuator center, University of California, Berkeley.

[14] http://en.wikipedia.org/wiki/Coefficient\_of\_thermal\_expansion

[15] P. P. L. Regtien, F. van derHeiden, M. J. Korsten, and W. Olthuis, "Measurement science for engineering", University of Twente, The Netherlands, Second Edition.

[16] G. C. M. Meijer (ed), Smart sensor systems, Chichester, UK: Wiley, 2008.

[17]. F. Reverter, X. Li, and G.C.M. Meijer, "A novel interface circuit for grounded capacitive sensors with feedforward-based active shielding", Meas. Sci. Tech., vol. 19, Feb. 2008.

# CHAPTER 3

# **Measurement Techniques for Capacitances**

# **3-1 Introduction**

This chapter discusses basic principles of techniques used to measure capacitances with high precision and with a high immunity for the effects of parasitics. When implementing these techniques in a universal sensor interface, the design challenges are:

- 1. In most cases, the sensor capacitance value is very low, in the range of a few pF or less;

- 2. Often it is necessary to measure a small sensor capacitor in the presence of much larger parasitic ones;

- 3. Often complete shielding of capacitive sensors is not possible (Fig. 2-5(b)). In that case, they can easily pick up interference from their environment. As a result, the amount of interference needs to be reduced with appropriate filtering techinques;

- 4. In sensors with a large signal bandwidth, it is rather challenging to achieve the required resolution.

It will be shown that using new circuit techniques together with IC technology, most of the problems can be overcome while still using low-cost interface technology.

# **3-2** Excitation and A-D conversion

To measure a sensor capacitance, we need to excite the capacitor with a voltage or a current. In principle, the excitation signal can have any type of waveform. However, usually either sine waves or square waves are used. Therefore, we will compare two types of the capacitance measurement system: with sine-wave excitation and with square-wave excitation.

Measurement systems based on sine-wave excitation can have a high resolution, but meeting the requirements of cost minimization, power [3] and maximization of flexibility is difficult. Therefore, we focus on capacitance measurement based on square-wave excitation. In that case, the interface circuit can be implemented using switched-capacitor (SC) techniques. Since SC circuits are implemented with switches and capacitors, CMOS technology is highly suited for such implementations. Moreover, the complexity and power dissipation of SC circuits are quite low.

For sensor systems, the signal bandwidth is rather moderate. However, often a high resolution and a high accuracy are required. To perform analog-to-digital (A-D) conversion, the best option is to use the principles of indirect conversion [4, 5, 6 and 7]. Two popular indirect conversion principles are a) those of sigma-delta converters [6], and b) the conversion of the analog signal to a period time and then digitizing the period time with a counter [8, 9]. In the following sections, we will summarize these basic principles as they are applied to capacitance-to-digital conversion. In this chapter we will limit ourselves to the case of floating capacitors.

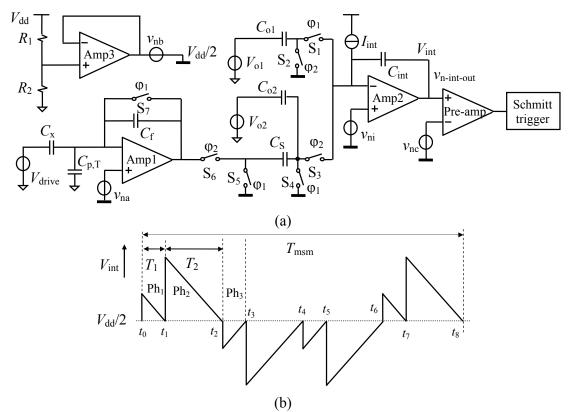

#### 3-2-1 Capacitance measurement based on sigma-delta converter.

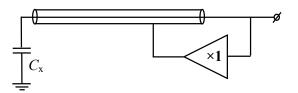

Figure 3-1(a) shows a basic circuit diagram of a sigma-delta converter.

Fig. 3-1: Principles of a Sigma-Delta ADC: (a) a circuit diagram and (b) some related signals.

To understand how the circuit works, let us suppose that at t = 0, the integrator output is negative, and  $V_{ref} > V_{in}$ . Consequently, the comparator output voltage in the first clock cycle is zero. During this first clock cycle, the sampling capacitor  $C_S$  is charged to  $V_{in}$  and on the descending edge of ck, this charge is transferred to integrator capacitor  $C_{int}$ , which increase the integrator output voltage to jump with the value of  $C_S V_{in}/C_{int}$ . As long as the integrator output is negative, this process is repeated and finally brings the integrator output voltage to the positive level. With the first clock pulse after that, the charge of  $C_S (V_{in} - V_{ref})$  is transferred to  $C_{int}$ , with which the above assumption  $(V_{ref} > V_{in})$  renders the integrator output voltage negative. Since the amounts of charge transferred by  $V_{in}$  and  $V_{ref}$  should ultimately compensate each other, in a long stream of zeros and ones, the ratio of number of ones to the total clock cycle is equal to the ratio of  $V_{in}/V_{ref}$ . Extracting this ratio is done by a decimation filter. To eliminate the resulting quantization noise, we need a large number of clock cycles to do the conversion. However, the quantization noise can be decreased using a higher-order loop filter (noise shaping) [6].

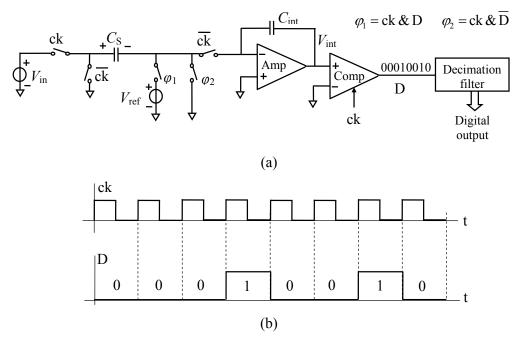

With a simple circuit modification, the *voltage*-to-digital converter (VDC) of figure 3-1(a) can be used as a *capacitance*-to-digital converter (CDC). The modified circuit is shown in figure 3-2.

When the comparator output is zero (low), the charge of  $C_x V_{ref}$  is transferred to  $C_{int}$ , and when the comparator output is one (high), the charge ( $C_x - C_{ref}$ )  $V_{ref}$  is transferred to  $C_{int}$ . Therefore, because of charge balancing at the integrator input, in a long stream of zeros and ones, the ratio of the number of ones and the total number of clock cycles equals the ratio of  $C_x / C_{ref}$ . This principle has been used in the chips AD7745, AD7746, AD7747 and AD7150 of Analog Devices [10].

Fig. 3-2: A capacitance-to-digital converter (CDC) using sigma-delta principles.

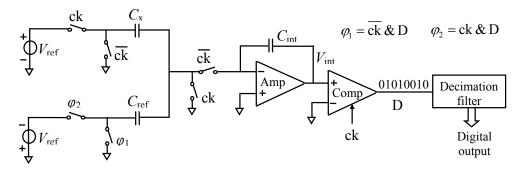

#### 3-2-2 Capacitance measurement based on a period modulator.

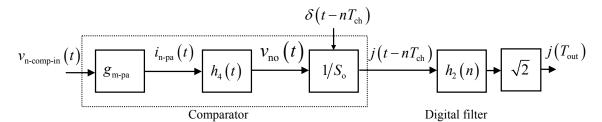

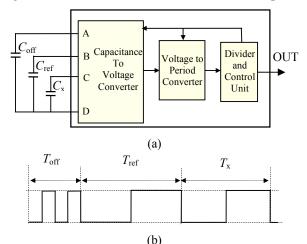

In this method the sensor capacitance is used in a free-running (relaxation) oscillator. The variation-in-capacitance values modulate the period of the oscillator output signal [8, 9]. This period can easily be digitized by a counter which is usually implemented in a microcontroller. In this way, the conversion of a capacitance value into a period time is very straightforward. However, as we will see in chapter 4, section 4-3, using a capacitance-to-voltage converter (CVC) in front of the free running oscillator for a universal interface has some distinctive advantages. In this case, the oscillator acts as a voltage-to-period convertor (VPC). The corresponding block diagram of the resulting capacitance-to-digital converter (CDC) is shown in figure 3-3.

Fig. 3-3: The block diagram of a capacitance-to-digital converter (CDC) using a period modulator (VPC).

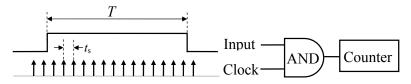

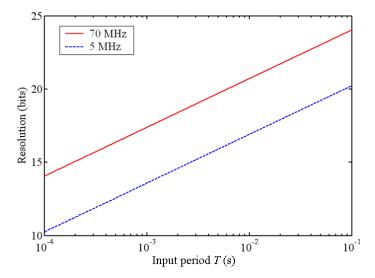

To achieve *p* bits of resolution, it is necessary that:

$$f_{\rm clock} \ge \frac{2^p}{T_{\rm max}},\tag{3-1}$$

where  $T_{\text{max}}$  is the maximum value of the output period. For instance for  $T_{\text{max}} = 100 \,\mu\text{s}$  and 13 bits of resolution, the clock frequency should be higher than 80 MHz<sup>1</sup>. Usually, the sensor signal bandwidth is quite low. Therefore, a digital divider (Fig. 3-3) can be applied after the oscillator to decrease the oscillator frequency to the required data-acquisition rate. For instance, supposing a sensor signal bandwidth of 100 Hz, the oscillator frequency can also be decreased to 100 Hz. In that case, a clock frequency of 800 kHz would be enough to obtain 13 bits of resolution. It should be mentioned that due to different practical limitations, such as leakage current and reducing the values of on-chip capacitances, in most applications the oscillator frequency will be much higher than the sensor-signal bandwidth.

<sup>&</sup>lt;sup>1</sup> Since we do not want to consume the whole error budget for the quantization noise, using a counting clock with a frequency of, for instance, 200 MHz will be better.

### 3-3 Circuit and system-level techniques

In this section, the major circuit and system-level techniques used in our interface are briefly explained.

### 3-3-1 Auto-calibration.

Auto-calibration is used to reduce the effects of systematic errors and of low-frequency noise. The principle of this technique can be understood by considering a linear system for which it holds that:

$$y = ax + b, \tag{3-2}$$

where x and y are the input and output signals of the system, respectively, and a and b are the transfer parameters of the linear system. The parameters a and b can be set by the designer. Therefore, it may have been said that by measuring the system output y and knowing the parameters a and b, the system input x can be extracted. However, problems occur when these parameters are not well-know or when they drift with time or temperature.

The undesired effects of transfer-parameter changes can be eliminated in various way, for instance by auto-calibration [3]. During auto-calibration, a sufficient number of reference signals  $x_{\text{ref},i}$  are measured in exactly the same way as the sensor signal  $x_s$  that has to be measured. For a linear system (Eq. 3-2), two reference signals are sufficient [3]. For two references and the sensor signal we have:

$$y_{\text{ref,1}} = ax_{\text{ref,1}} + b,$$

(3-3)

$$y_{\text{ref},2} = ax_{\text{ref},2} + b,$$

(3-4)

$$y_{\rm s} = ax_{\rm s} + b. \tag{3-5}$$

The sensor signal can be extracted as:

$$x_{\rm s} = M \left( x_{\rm ref2} - x_{\rm ref1} \right) + x_{\rm ref1} , \qquad (3-6)$$

where for *M* it holds that:

$$M = \frac{y_{\rm s} - y_{\rm ref1}}{y_{\rm ref2} - y_{\rm ref1}}.$$

(3-7)

Note that M and consequently the derived values of  $x_s$  are independent of a and b and are thus immune from any variation in these parameters, as long as these values do not change during a single measurement cycle.

As a non-ideality, this system can show some nonlinearity. To minimize the effect of this nonlinearity it is better to select  $x_{ref,1}$  and  $x_{ref,2}$  to be almost equal to the minimum and maximum value of sensor signal. However, for the sake of simplicity, it might be convenient to select one reference to be zero ( $x_{ref,1} = 0$ ) and the other one ( $x_{ref,2} = x_{ref}$ ) at the maximum value of the sensor signal. Therefore:

$$x_{\rm s} = M x_{\rm ref}. \tag{3-8}$$

With auto-calibration, in addition to the effects of thermal drift and uncertainty in the parameters a and b, the effect of input-independent, switch-charge injections can also be removed.

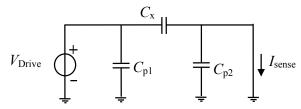

### 3-3-2 Two-port measurement technique.

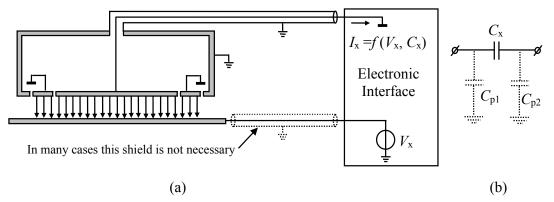

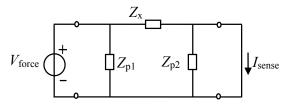

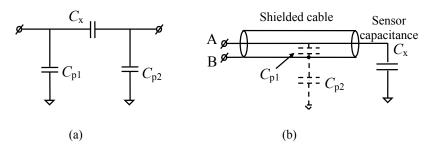

For the designer of capacitive sensor systems, understanding the two-port measurement technique [3] is very important. This technique is applied to eliminate the parasitic effects of connecting wires. In one version of this technique the effect of the parasitic series impedance of wires is eliminated, which is important for low-ohmic passive sensing elements, such as Pt100 resistors. In another version of the two-port measurement technique, the effect of parasitic shunting impedances of the connection wires is eliminated. This technique is important for high-ohmic passive sensing elements, such as our capacitive sensors. Figure 3-4 shows the concept of the later technique, which is used to measure a high-ohmic sensing element with impedance  $Z_x$ . The parasitic capacitances  $C_{p1}$  and  $C_{p2}$  of the cables of the sensing element connected to their shields can be much larger than the sensor capacitance, which with an impropriate connection can pose large problems. In the setup of figure 3-4, this problem is solved by using a low-ohmic excitation and a low-ohmic current read-out. The current through  $Z_{p1}$  does not effect the measurement of  $I_{sense}$ , while the current through  $Z_{p2}$  is negligible. Therefore, for the measurement of capacitive sensors, excitation with a low-ohmic voltage source and detection with a low-ohmic current meter should be chosen. In that case, the effect of parasitic capacitances of the connecting wires to their shields is eliminated.

Fig. 3-4: The concept of the two-port measurement technique for high-ohmic sensor impedance  $Z_x$ .

### 3-3-3 Chopper.

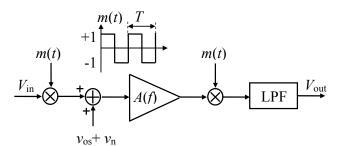

Most sensor output signals are located in the low-frequency band, where many interfering signals such as op-amp offset, 1/f noise, and main-supply interferences are also located. A good way to separate the sensor signal from the above-mentioned undesired interfering signals is to modulate the sensor signal to a higher frequency, so that it can be processed to eliminate 1/f noise, offset and main-supply interference. After required processing, it can be demodulated back to the baseband frequency.

Modulation can easily be performed with choppers (Fig. 3-5). The two choppers act as a modulator and a demodulator, respectively. After the second chopper the original input signal is demodulated and amplified with a factor A, while the op-amp input noise and offset are chopped by the square wave signal m(t) with chopping frequency  $f_{ch}=1/T$ . A low-pass filter removes these modulated offset at the chopper signals [11].

Fig. 3-5: A chopper amplifier.

In our design, we use a chopper signal that is fully synchronized with the input voltage  $V_{in}$ . As compared to the chopper in figure 3-5, this has the important advantage of no remaining ripple. The chopper applied has the additional advantage of using the (+ - +) principle described in [8, 9]. The applied chopper will be described in section 3-4 and in depth in chapter 4, section 4.6.1.1.

# 3-4 The technique selected for the capacitive-sensor interfaces

From the two methods for indirect A/D conversion –sigma-delta and period-modulated methods– we selected the latter. Some of the reasons for this selection are:

- 1. Simplicity. In many modern control systems, there is at least one microcontroller; therefore, digitization and any further filtering can be performed without extra cost. It means that extra counter and filtering are not necessary in our interface.

- 2. Spread of power consumption. Usually, in order to eliminate noise, interference, etc., the analog signal needs to be converted to digital as soon as possible. In the system shown in figure 3-3, the analog-to-digital conversion takes place in the counter. In fact, before the counter, the period-modulated signal is a sampled analog signal. However, in the voltage domain, which determines its sensitivity to noise and interference, the signal is digital. Because the frequency of the signal is in the same range as the bandwidth of the sensor signal, with the maximum frequency of a few kHz, it can be transferred via a long cable without any problems. This is very important, for instance, in sensor heads which are very sensitive to thermal expansion [12]. In this case, the interface can be attached to the sensor head in order to minimize the effect of the parasitic capacitance of the sensor cable. The more energy-consuming part of the signal processing can be performed far away from the sensitive parts. In the case of a sigma-delta converter, sending high-frequency bit-streams via a long cable is not easy.

- 3. Compatibility with UTI [13]. Many users of UTI believe that the UTI is very userfriendly. However, its maximum data acquisition rate is only about 80 Hz. Moreover, the UTI is suited for neither grounded nor leaky capacitors. Last but not least, for many applications its resolution and linearity are not sufficient.

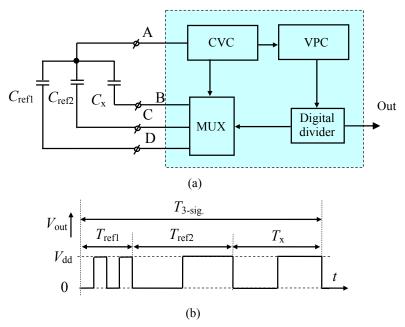

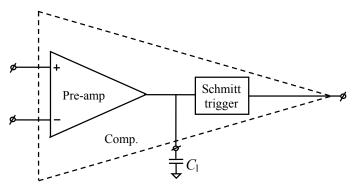

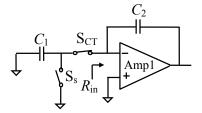

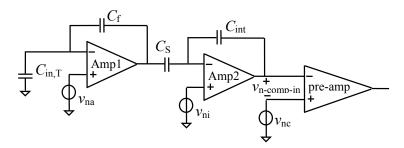

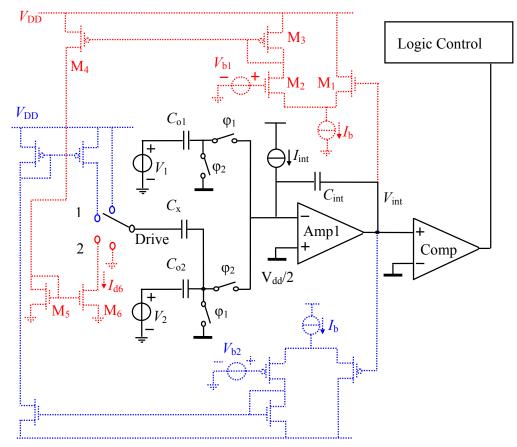

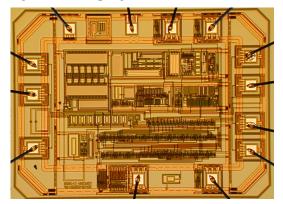

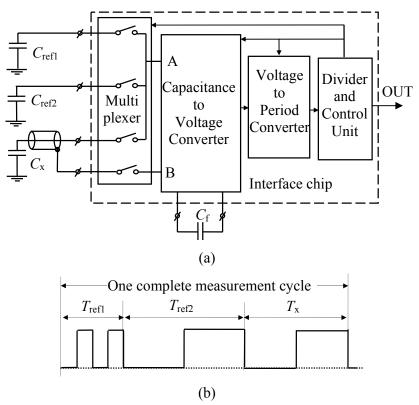

## *3-4-1 The structure of the interface*

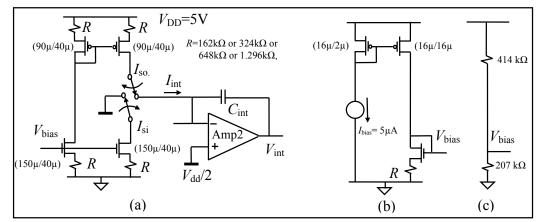

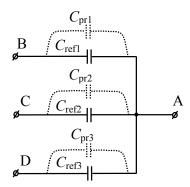

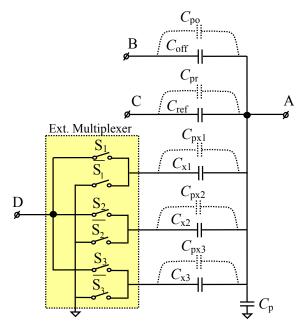

Figure 3-6(a) shows the block diagram of the interface which is based on figure 3-3 with an additional multiplexer to perform auto-calibration.

Figure 3-6(b) shows the interface output signal. Auto-calibration, a two-port measurement technique and chopping are used. Our work is based on the work presented in [8, 9]. However, we added dedicated front-ends for grounded capacitors (see chapter 8) and leaky capacitors (see chapter 7). In addition to that, in this project the interface properties were improved with respect to the features of noise, nonlinearity and measurement speed.

According to the three-signal auto-calibration technique (section 3-3-1), a single measurement cycle consists of three phases: two phases to measure the two reference capacitor  $C_{\text{refl}}$  and  $C_{\text{ref2}}$ , and a third one to measure the sensor capacitor  $C_x$ . The time intervals  $T_{\text{ref1}}$ ,  $T_{\text{ref2}}$  and  $T_x$ , are the output signals that correspond to the values of  $C_{\text{ref1}}$ ,  $C_{\text{ref2}}$  and  $C_x$ , according to the equations:

Fig. 3-6: (a) Simplified diagram of the interface structure for floating capacitors;

(b) the interface output signal [8, 9].

$$T_{\rm refl} = aC_{\rm refl} + b, \tag{3-9}$$

$$T_{\rm ref2} = aC_{\rm ref2} + b,$$

(3-10)

$$T_{\rm x} = aC_{\rm x} + b, \,. \tag{3-11}$$

By measuring the lengths of the three different periods, and knowing the values of the two reference capacitors, the value of  $C_x$  can be calculated according to the equation:

$$C_{\rm x} = \left(\frac{T_{\rm x} - T_{\rm ref1}}{T_{\rm ref2} - T_{\rm ref1}}\right) \left(C_{\rm ref2} - C_{\rm ref1}\right) + C_{\rm ref1} \,. \tag{3-12}$$

For identification purposes, time interval  $T_{refl}$  is split into two short periods [8, 9].

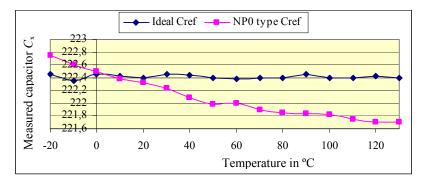

Equations (3-9) to (3-12) are valid when the applied capacitance-to-time conversion is linear. To reduce the effect of resolution limitations caused by noise and interference,  $C_{\text{ref1}}$  and  $C_{\text{ref2}}$  should be selected to be close to the minimum and maximum value of the sensor capacitance  $C_x$ . However, for convenience and to eliminate an (expensive) reference capacitor, one reference capacitor is often set at zero.

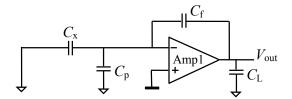

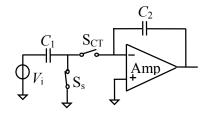

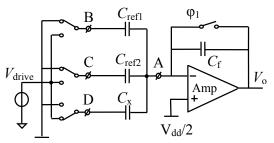

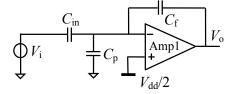

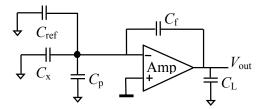

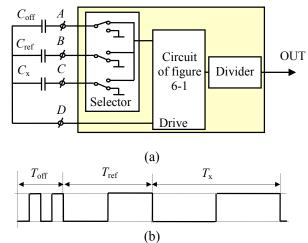

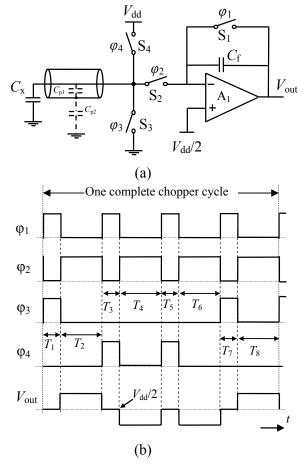

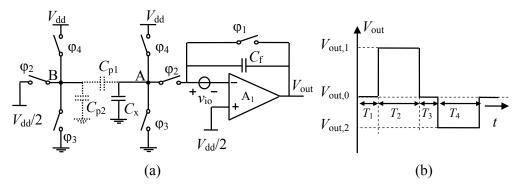

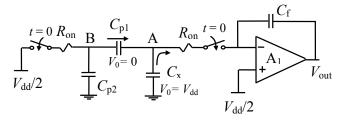

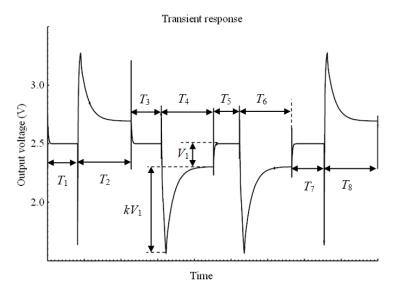

### 3-4-2 Capacitance-to-voltage converter (CVC)

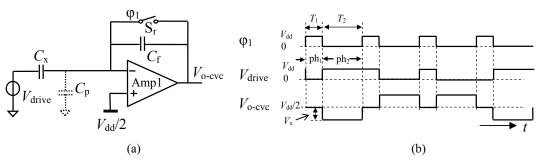

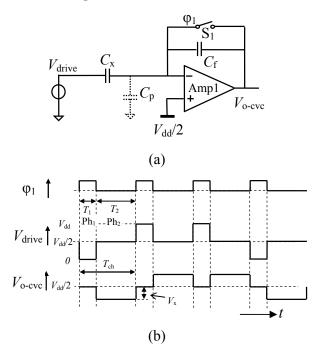

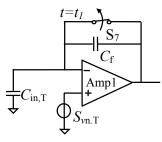

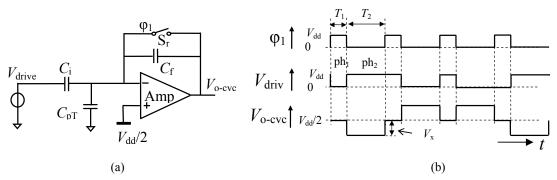

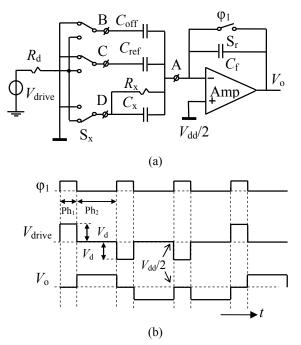

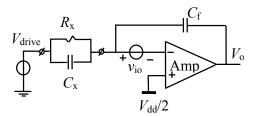

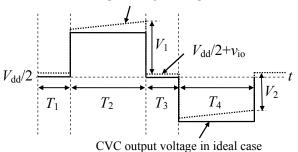

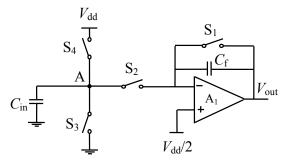

Figure 3-7(a) shows the CVC for floating capacitors [8, 9]. Some important signals are shown in figure 3-7 (b). The reasons for creating the output voltage as shown in figure 3-7(b) can be found in [8, 9].

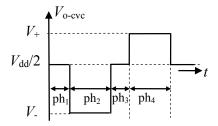

In order to prevent the loss of any charge,  $S_r$  is opened before the occurrence of the transition in the drive voltage  $V_{drive}$ . In this CVC the drive voltage has two levels: 0 V and  $V_{dd}$ . During the sampling phase ph<sub>1</sub>,  $S_r$  is closed, and the voltage  $V_{drive} - V_{dd}/2$  is sampled on  $C_x$ . At the end of phase 1 (ph<sub>1</sub>), S<sub>r</sub> is opened. Next, at the beginning of ph<sub>2</sub> (the charge-transfer phase), because the drive-voltage rise from 0V to  $V_{dd}$ , a charge  $C_x V_{dd}$  is pumped into  $C_f$ , which results in a voltage drop of  $V_x = C_x V_{dd} / C_f$  at the output. The other parts of the CVC output voltage  $V_{o-cvc}$  can be found in a similar way.

Fig. 3-7: (a) The CVC for a high-quality floating capacitor and (b) the related signals.

During ph<sub>2</sub>, the DC voltage across  $C_x$  is not zero but  $V_{dd}/2$ , which causes the circuit of figure 3-7(a) to be sensitive to resistive leakage of  $C_x$ . In chapter 4, section 4-2 and in depth in chapter 7, we will show how this front-end can be modified to be leakage-immune.

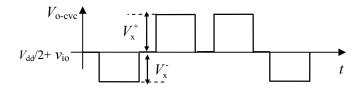

Moreover, the presence of amplifier offset  $v_{io}$  will cause asymmetry in the CVC output voltage (Fig. 3-8); however, it can easily be proven that the peak-to-peak value of this output voltage is independent of amplifier offset. In section 3-4-3 it will be shown that the output of the VPC is proportional to the peak-to-peak of CVC output voltage.

Fig. 3-8: The CVC output voltage at the presence of amplifier offset.

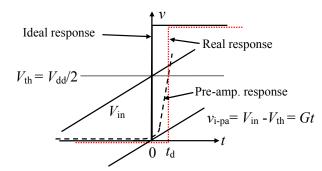

### 3-4-3 Voltage-to-period converter (VPC)

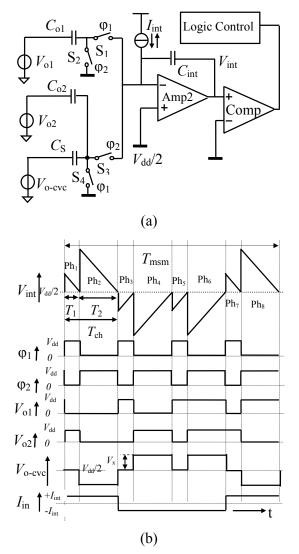

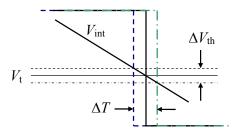

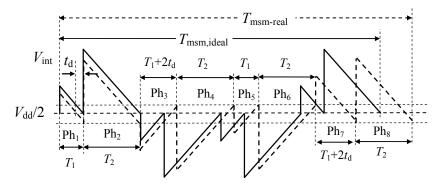

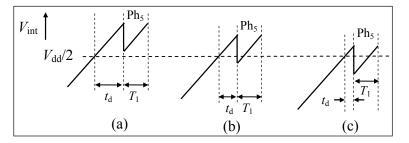

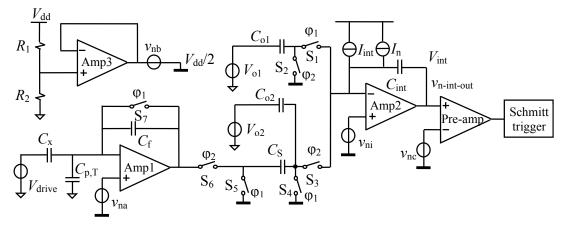

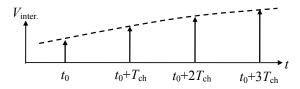

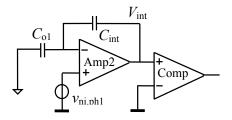

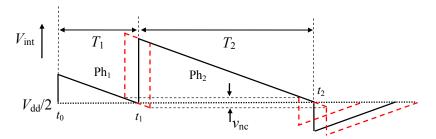

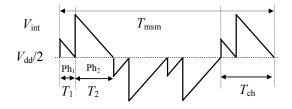

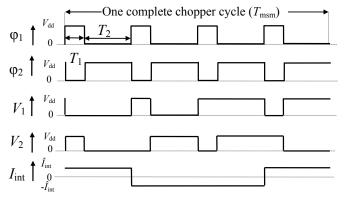

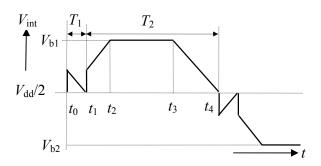

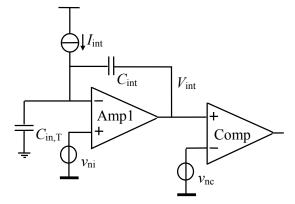

Figure 3-9(a) shows the principle of the voltage-to-period converter (VPC) [8, 9]. Figure 3-9(b) shows some important signals.

The voltages  $V_{o1}$  and  $V_{o2}$  are block-shaped and have voltage levels of 0 or  $V_{dd}$ . At the start of phase 1 (Ph1), the charge of  $Q_1 = V_{dd}C_{o1}$  of  $C_{o1}$  is pumped into the integrator capacitor. Next, this charge is removed by integrating  $I_{int}$ . At the start of Ph2, the summed charge  $Q_2$  of  $C_{o2}$  and  $C_s$ , which equals  $V_{dd} C_{o2} + V_x C_s$ , is pumped into the integrator capacitor. This charge is also removed by integrating  $I_{int}$ . This procedure is repeated with inverted polarities and current directions, which completely eliminates the effect of the offset voltage of Amp2. In this way the principle of a synchronous chopper is implemented according to the principles described in [8, 9]. Four of these events complete the measurement cycle within a time interval  $T_{msm}$  (Fig. 3-9(b)). This time interval represents the output signal of the converter, which amounts to:

$$T_{\rm msm} = \frac{4\left(V_{\rm dd}\left(C_{\rm o1} + C_{\rm o2}\right) + V_{\rm x}C_{\rm S}\right)}{I_{\rm int}}.$$

(3-13)

Fig. 3-9: (a) The voltage-to-period converter and (b) the most important signals.

In the case of an asymmetrical CVC output voltage, with the same analysis, it can be proven that:

$$T_{\rm msm} = \frac{2\left(2V_{\rm dd}\left(C_{\rm ol} + C_{\rm o2}\right) + \left(V_{\rm x}^{+} + V_{\rm x}^{-}\right)C_{\rm S}\right)}{I_{\rm int}},$$

(3-14)

where  $V_x^+$  and  $V_x^-$  are shown in figure 3-8. It means that the VPC output is proportional to the peak-to-peak value of CVC output voltage.

The output signal of the capacitance-to-voltage converter (CVC) is also proportional to the supply voltage  $V_{dd}$  ( $V_x = C_x V_{dd}/C_f$ ). In order to make the measurement time  $T_{msm}$  independent of the supply voltage, the integrating current  $I_{int}$  should also be proportional to the supply voltage.

# 3-5 Some important characteristics of the interface

Compared to other types of interfaces, the interface presented in figure 3-6 has some attractive features which are quite important for our universal-capacitive sensor interface. Two of them (simplicity and spread of power consumption) have already been discussed in section 4-4, some otheres will be summarized in this section.

# 3-5-1 Flexibility.

Flexibility is necessary to make the interface suitable for a wide range of applications. For instance, the interface needs to be flexible in terms of optimizing the range of the interface for capacitive sensors from 1pF to 1 nF; the data-acquisition rate from 20 Hz up to 10 kHz; for various types of external elements, for instance, grounded, floating or leaky capacitive sensor and also for different ranges of parasitic capacitance. In chapter 4 we will show how simple it is for the user to modify the designed interface for a specific application.

# 3-5-2 Stability.

Due to auto-calibration, the stability of the measurement is quite high. As a consequence, the output signal is immune to the effects of aging and changes of the interface temperature as long as these changes are not significant during the time  $T_{3-\text{sig.}}$  (Fig. 3-6(b)) of a single measurement.

## 3-5-3 No error due to ripple.

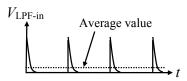

In the chopper configuration of figure 3-5, the signal at the input of the low-pass filter is the amplified input signal with the modulated offset voltage on top. A low-pass filter (LPF) is used to remove the modulated offset. However, depending on the ratio of the chopping frequency and the bandwidth of the LPF, part of the modulated offset will appear at the output as ripple. In many applications, decreasing this ripple is an important issue and several techniques to reduce its amplitude can be found in the literature [14, 15]. However, in our system the chopper action is completely synchronized with the excitation signal so that no residual effects of ripple remaining. When, for instance, the amplifier offset decreases the time interval in phase 1 and phase 2, it will increase the time interval the same amount in phase 3 and phase 4. Therefore, the sum of time interval in phase 1 to phase 4 is completely offset-free. More details will be discussed in chapter 4, section 4-6-1-1.

## 3-5-4 No error due to clock feedthrough and switch-charge injection.

In the next discussion we deal with the effects of switch-channel charge injection, although the discussion is also valid for switch-clock feedthrough [16]. Moreover, since our discussion is valid regardless of the switch type (NMOS, PMOS or CMOS switch), we do not specify the polarity of the charges.

In most switched-capacitor circuits, the effect of switch-charge injection is an important issue. For instance in a typical chopper, as depicted in figure 3-5, there is some error due to residual offset which originates from a mismatch between the input-chopper switches. Therefore, the charge injections do not fully compensate each other. This causes a spike voltage, as shown in figure 3-10 at the input of the LPF (Fig. 3-5) [17]. The average of these spikes appears as residual offset at the output of the LPF. The amount of this residual offset depends on the

level of mismatches and also on the source impedance. This effect causes the residual offset of the chopper amplifiers.

Fig. 3-10: The spike voltage at the input of LPF caused by clock feedthrough and switch-charge injection.

The chopper in our system, which is based on the synchronous (+ - +) principle described in [8, 9], is implemented by inverting the drive voltage and integrator current. It has been shown [8, 9] that this way of chopping in combination with auto calibration removes any residual effect of clock feedthrough and switch-charge injection of all switches in our interface.

For instance, when the reset switch  $S_r$  in figure 3-7(a) is switched to the OFF position, some charge is pumped into the feedback capacitor  $C_f$ . When  $S_r$  is ON, the channel voltage is always  $V_{dd}/2$ . Therefore for all switching events in the OFF position, the switch charge injection is the same. Therefore, this effect cannot change the peak-to-peak value of the CVC output  $V_+ - V_-$  (Fig. 3-11). Consequently, this effect is removed by chopper. Moreover, because the situation is exactly the same for the three different input capacitors  $C_{ref1}$ ,  $C_{ref2}$  and  $C_x$ , any residual effect will be removed by auto-calibration.

Fig. 3-11: The CVC output voltage, at the presence of clock feedthrough and switch-charge injection of reset switch S<sub>r</sub>.

For switches  $S_1$  to  $S_4$  in the VPC (Fig. 3-9(a)) it can be shown that there is a first-order compensation for the charge injection of switches  $S_1$  and  $S_3$ . However, due to mismatch of these two switches, there will be some residual charge injection in each phase. If we consider one complete measurement cycle  $T_{msm}$ , the total charge pumped to the negative input of the CVC amplifier from each of these switches is compensated by the amount of charge drawn from this node by the same switch at the opposite transition. In other words, the switch-charge injection of these two switches will not affect the measurement cycle  $T_{msm}$ , in principle. For switches  $S_2$  and  $S_4$ , however, the conditions are different. Because at the moment of switching ON, the required channel charge is provided by the bias voltage  $V_{dd}/2$ , while at the moment of switching OFF, the channel charge will be pumped to the right side of the capacitors  $C_{o1}$ ,  $C_{o2}$ and  $C_S$ , and then to the integrator capacitor  $C_{int}$ . Since these charges are always in the same direction, their effect is removed by the chopper, and further suppressed by auto-calibration.

# **3-6** Conclusion

In this chapter we showed two different methods of capacitance measurement: the sigma-delta method, and the period-modulated or oscillator-based method. It was shown that the period-modulators have the attractive features of being simple and flexible. Furthermore, a number of important measurement techniques to be applied for high-performance sensor interfaces were briefly presented. These techniques include auto-calibration, two-port method and chopping. It was shown that the chopper action is synchronized with the input voltage, which enables removal of the offset voltage effects of the op-amp without leaving any ripple. Moreover, it appears that the effects of switch-charge injection are fully eliminated by the combined effects of chopping and auto-calibration.

### References

[1] L. K. Baxter, "Capacitive sensors, design and applications", New York: IEEE Press, 1997.

[2] S. M. Huang, A. L. Stott, R. G. Green, M. S. Beck, "Electronic transducers for industrial measurement of low value capacitances", J. Phys. E: Sci. Instrum., vol. 21, pp. 242-250, 1988.

[3] G. C. M. Meijer, "Interface electronics and measurement techniques for smart sensor systems", in G. C. M. Meijer (ed), Smart sensor systems, Chapter 2, Chichester, UK: Wiley, 2008.

[4] J. Robert, G. C. Temes, V. Valencic, F. Dessoulavy, P. Deval, "A 16 bit low-voltage CMOS A/D converter", IEEE Journal of Solid-State Circuit, vol. SC-22, no. 2, pp. 157-163, April 1987.

[5] F. van der Goes, P. De Jong and G. C. M.Meijer, "Concept for accurate A/D converter for transducer", Proc 7<sup>th</sup> Int. Conf. Solid-State Sensor and Actuators, Yokohama, Japan, pp. 331-334, June 1993.

[6] R. Schreier and G. C. Temes, Understanding delta-sigma data converter, New York: IEEE Press, 2005.

[7] P. G. A. Jespers, Integrated converters, Oxford: OUP, 2001.

[8] F. van der Goes, Low-Cost Smart Sensor Interfacing, PhD thesis, Delft University of Technology, The Netherlands, 1996.

[9] F. van der Goes, and G. C. M. Meijer, "A universal transducer interface for capacitive and resistive sensor element", Analog integrated circuit and signal processing, vol. 14, pp. 249-260, 1997.

[10] Analog Device, http://www.analog.com

[11] C. C. Enz and G. C. Temes, "Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling and chopper stabilization", Proc. IEEE, vol. 84, no. 11, pp. 1584-1614, Nov. 1996.

[12] S. Nihtianov "High Performance Capacitive Sensor Electronic Interfaces for Displacement Measurement in Industrial Applications", Sensor and test, Nuremburg, Germany, 26-28 May 2009.

[13] Smartec, "Universal Transducer Interface". http://www.smartec.nl/interface\_uti.htm

[14] J. F. Witte, J. H. Huijsing, K. A. A. Makinwa, "A current-feedback instrumentation amplifier with 5mV offset for bidirectional high-side current-sensing", J. Solid-State Circuits, vol. 43, no. 12, pp. 2769-2775, Dec. 2008.

[15] R. Wu, K. A. A. Makinwa, J. H. Huijsing, "A chopper current-feedback instrumentation amplifier with a 1mHz 1/f noise corner and an AC-coupled ripple reduction loop", J. Solid-State Circuits, vol. 44, no. 12, pp. 3232-3243, Dec. 2009.

[16] B. J. Sheu and C. Hu, "Switched-induced error voltage on a switched capacitor", J. Solid-State Circuits , vol. Sc19, no. 4, Aug. 1984.

[17] A. Bakker, K. Thiele, J. H. Huijsing, "A A CMOS nested-chopper instrumentation amplifier with 100-nV offset", J. Solid-State Circuits, vol. 35, no., 12, pp. 1877-1883, Dec. 2000.

## CHAPTER 4

## A Universal Interface for Capacitive Sensors

### **4-1 Introduction**

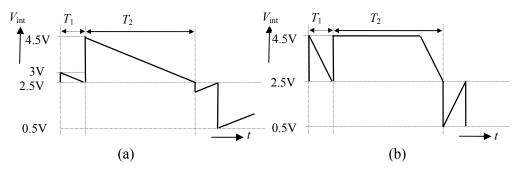

To design an interface for capacitive sensors the requirements and constraints related to the proposed applications should be taken into account. For the interface, the sensor element is an external component. However, the electrical properties of the element interact with those of the interface itself. For instance, depending on the application, capacitive sensors can be electrically floating or grounded [1]. They can show pure capacitive behavior or have resistive leakage [2]. Their values can be in a wide range from less than one pF up to hundreds of pF or even a few nF. In some cases their values can change very fast, and in other cases their values are semi-static. For different applications, the parasitic capacitances of the connecting wires can also be very different. Using an interface which could simply be optimized for the aforementioned applications would be a cost-effective solution.

The universal interface for capacitive sensors is designed to cover the following selected group of capacitive sensors:

- 1. Capacitive sensors with electrically-floating electrodes.

- 2. Capacitive sensors with one grounded electrode.

- 3. Leaky capacitive sensors.

- 4. Capacitive sensors with a rapid response time and a high accuracy.

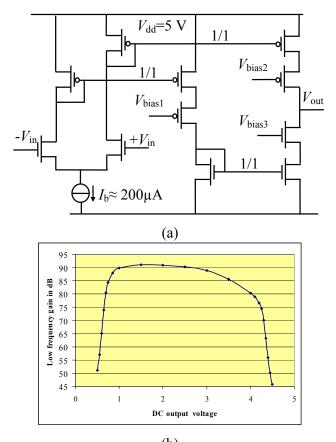

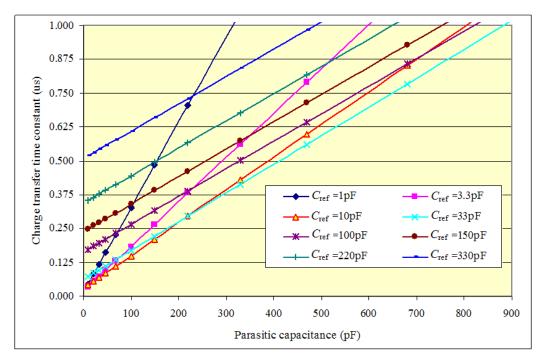

One of the target specifications for this interface is that it should be possible to set the range at any value up to 1 nF. For specific modes, it should be possible to vary the measurement time from about 100  $\mu$ s to 50 ms. Furthermore, for other modes it is preferable that cable lengths up to 30 meters can be handled.

For a specific sensor system, the error budget can be divided over different error sources such as nonlinearity, limited resolution, offset, finite settling time, etc.. However, when designing a universal interface, making an error budget is not possible. For the main part, this is because parts of the errors originate from the sensor side and the chip-designer does not know the sensor details. Even when the sensor is ideal, before registering the sensor signal characteristic, such as the dynamic range, the bandwidth, etc., it is not possible for the interface designer to make an error budget for the whole system.

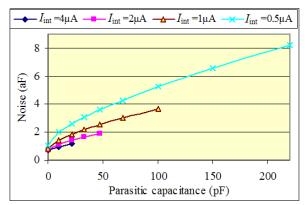

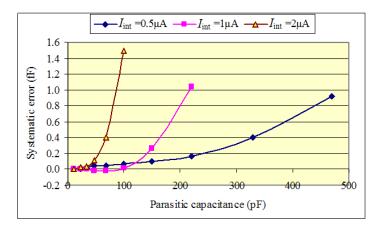

There are different sources of error [Appendix A]. In our design, ,error sources such as gain errors, offset errors, drift errors, and many others are suppressed significantly using auto-calibration. However, nonlinearity errors and resolution errors cannot be suppressed by this technique. Moreover, in capacitance measurements, the effect of PCB parasitic capacitances at the connection terminals of the capacitors can cause gain and offset errors which cannot be suppressed by auto-calibration. This is because during an auto-calibration cycle, these parasitic capacitances are not constant. Therefore, as will be shown in this chapter, the three main sources of error are nonlinearity, noise and parasitic capacitances at the connection terminals. It should be mentioned that in many applications we are not interested in absolute accuracy. In such cases, offset errors or gain errors are not important anymore.