# A CMOS PROCESS COMPATIBLE CHARGE-MODULATED FGFET BASED ION SENSOR FOR INTEGRATION INTO ORGAN-ON-CHIP PLATFORMS

by

### Rajarshi Sinha

in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering

at the Delft University of Technology, to be defended on Wednesday, November 28th, 2018 at 10:00 AM.

Supervisor: Prof. dr. ir. P. M. Sarro

Thesis committee: Prof. dr. P. J. French, TU Delft

Dr. M. Mastrangeli, TU Delft Ir. W. F. Quiros Solano, TU Delft

This thesis is confidential and cannot be made public until November 28th, 2021.

An electronic version of this thesis is available at

http://repository.tudelft.nl/

Copyright © by:

R. Sinha 4506162 R.Sinha-1@student.tudelft.nl.

All rights reserved.

### **ABSTRACT**

Drug development is an entire area of research that partly exploits the developments from biomedical research. Understanding the diseases that affect humanity fatally is critical to our existence. Researchers have studied various molecules and genetic compounds that are responsible for the proliferation of these diseases in the human body. For this purpose, by-far, animal testing has been used most extensively in drug development. Several human physiological models have also been developed to test the efficacy of new therapies. However, it is very difficult to accurately model human diseases in-vitro which has led to failure of several potential drugs.

Consequentially, Organ-on-Chip (OOC) platforms have been developed to serve this purpose. They are specially designed to mimic human organs on a microlevel. Within such controlled microenvironments, biological and electrochemical cues can be well monitored. Stretchable Microelectrode Arrays (SMEA) are commonly used membrane based OOC platforms with suspended electrodes on the stretchable membrane, that are responsible for electrical stimulation. Additionally, several configurations of ion sensors such as Organic Electrochemical Transistors (OECT), Organic Thin-Film Transistors (OTFT) and so on have also been used for integration into OOCs. However, most such devices make use of reference electrodes for biasing the transistors that do not provide for easy integration into standard CMOS fabrication technology. Further, the reference electrodes also can disintegrate and affect the electrolyte over extended periods of biasing.

In this thesis, a reference electrode-less floating gate ion sensor has been proposed that can be realized with low-cost standard CMOS technology. The Charge-modulated Floating Gate FET (FGFET) has been designed, microfabricated and electrically characterized. The device makes use of a standard transistor design with a built-in control capacitor that acts as the reference electrode and sets the working point of the transistor. The gate electrodes are extended on an active sensing area that is bound by a glass cylinder containing the electrolyte. This delimits the rest of the device from the ionic solution. The change in current output of the device in response to ionic charge variation with different concentrations of the electrolyte was tested and the results have been shown here-in. The device shows a sensitivity of 0.4 ampere per molar concentration of electrolyte or 0.4A/M, which is very good for research purposes as was intended in this study. Further, the sensing area is fabricated as a free-standing PDMS membrane with suspended gate electrode extensions, which further validates the potential of the Charge-modulated FGFET to be integrated into stretchable OOC platforms. The easy microfabrication process and good sensitivity of the device presented in this work is an important step towards the integration of ion sensors for OOC applications.

### **ACKNOWLEDGEMENTS**

This thesis concludes my Electrical Engineering Master programme at the TU Delft. I would be failing in my duties if I didn't thank all those people who helped me complete this journey successfully. I would first like to thank my supervisor Prof. Dr. Lina Sarro for giving me the opportunity to work on this project and for all the support that she provided me throughout. I would also like to thank my mentor and daily supervisor William for guiding me in this work. Thank you so much William for being ever-so-patient with me and helping me understand all the concepts so clearly. Without your knowledge and guidance, this work would not have come to fruition.

I would also like to take out time to thank all the cleanroom technicians and my colleagues at EKL, especially Henk, Hitham and Gianpaolo for their scientific advise. My good friend and colleague, Sarat, also deserves a special mention here. I still remember the day I had messed up my entire batch of wafers; 3 weeks worth of work destroyed during etching. Gianpaolo helped me through the implantation process of the fresh batch, repeatedly that evening while Sarat stayed along, always smiling and ready to help in any way possible.

I would also like to thank the huge circle of friends that I made in these 3 years. Firstly and most importantly to La Familia, the three lovely people that mean the most to me, my surrogate family here in Delft. Thank you Ainhoa and Giovanni for your support and all the hugs that you guys always had for me whenever I felt down. I love you both to the moon and back. And Diana! I really don't know what I would do in Delft if it wasn't for you. Thank you for always talking some sense into me whenever I needed a push and for always having my back no matter what. You have always tried your best to drive me higher and to make me a better person than I am. Thank you for saving me dinner almost every other night, when I had to spend long evenings in the CR. There is so much more you do for me everyday, that I could go on forever. ¡Gracias por formar parte de mi vida, Dianita! ¡Eres mi roca! ¡Te amo mucho! I would also like to thank all the other master students in ECTM for their friendship and mental support both within and outside working hours. Special thanks to Jin for always taking out time from his PhD schedule and helping me out with the preliminary measurements in Cascade. I would also like to thank my old roommates (too many to mention) in Aan 't Verlaat and my new ones (Chris, both the Deniz and Will) in Oude Langendijk for sticking around during both good and hard times. It was always nice to come back home to a smiling face that I could have a relaxed chat over dinner with.

Finally, I would like to thank the two most important people in my life, my parents for their monumental, unwavering support and encouragement at all times, even from miles away. I would never be the man I am right now, without their love. Ma, Baba, you both mean the world to me and thank you for believing in me and in my dreams more than I ever did.

Rajarshi Sinha Delft, November 2018

## **CONTENTS**

| Lis | t of Figures                                                                                                                                                                                                                                                                       | ix                                     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Lis | t of Tables                                                                                                                                                                                                                                                                        | xiii                                   |

| 1   | Introduction  1.1 Organ-on-Chip  1.1.1 Lung-on-Chip  1.1.2 Brain-on-Chip  1.1.3 Cancer-on-Chip  1.1.4 Heart-on-Chip  1.2 Need for sensor-integration in OOCs  1.2.1 Monitoring chemical gradients and electrical parameters.  1.3 Scope of the thesis.  1.4 Outline of the thesis. | 1<br>3<br>3<br>4<br>5<br>6<br>9<br>9   |

|     | Ion-sensing Technologies for OOC Applications  2.1 State-of-the-Art                                                                                                                                                                                                                | 11<br>11<br>13<br>16<br>17<br>17<br>19 |

| 4   | 3.2 Working Principle                                                                                                                                                                                                                                                              | 20<br>21<br>23<br><b>25</b>            |

| 7   | 4.1 Single Die Layout                                                                                                                                                                                                                                                              | 25                                     |

| 5   | Electrical and Electrochemical Characterization Results  5.1 Device Electrical Characterization                                                                                                                                                                                    | 37<br>37<br>37<br>39                   |

VIII CONTENTS

|    | 5.2<br>5.3<br>5.4<br>5.5<br>5.6 | Devic<br>5.3.1<br>5.3.2<br>Devic<br>Discu | ncubation Device Characteristics                                         | 41<br>42<br>42<br>47 |

|----|---------------------------------|-------------------------------------------|--------------------------------------------------------------------------|----------------------|

| 6  | Con                             | clusio                                    | n and Future Scope                                                       | 49                   |

| A  | App                             | endix l                                   | Mask Design                                                              | 51                   |

| В  | App                             | endix l                                   | Detailed Flowchart                                                       | 61                   |

| C  | App                             | endix l                                   | Electrical and Electrochemical Measurement Data                          | 83                   |

|    | C.1                             | PMOS                                      | 3 2:25                                                                   | 83                   |

|    |                                 | C.1.1                                     | Transfer Characteristics                                                 | 83                   |

|    |                                 | C.1.2                                     | Output Characteristics                                                   | 84                   |

|    |                                 |                                           | Post-incubation                                                          | 86                   |

|    |                                 |                                           | Transfer Characteristics at varying Ionic Concentrations of Electrolyte. | 89                   |

|    | C.2                             | NMO                                       | 8 2:25                                                                   | 94                   |

|    |                                 | C.2.1                                     | Transfer Characteristics                                                 | 94                   |

|    |                                 | C.2.2                                     | Output Characteristics                                                   | 96                   |

|    |                                 |                                           | Transfer Characteristics for varying Ionic Concentrations of the Elec-   |                      |

|    |                                 |                                           | trolyte                                                                  | 98                   |

|    |                                 | C.2.4                                     | Post PDMS membrane release                                               | 102                  |

| Bi | bliog                           | raphy                                     |                                                                          | 107                  |

### **LIST OF FIGURES**

| 4  |                                                                                                                                                                                                                                          | 1.1 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | Conceptualization of the device [23]. The tumor and metastatic site are separated by a porous PDMS membrane. The direction of movement of the cancer                                                                                     | 1.2 |

| 5  | cells is from the tumor to the metastatic site, via the porous membrane that represents the blood-vessels.                                                                                                                               |     |

| 6  | Co-culture of 3D tumor cells and a 2D endothelial cell monolayer separated by a porous membrane [23]                                                                                                                                     | 1.3 |

|    | side of the culture for adding of wires. These wires allow direct and continu-                                                                                                                                                           | 1.4 |

| 7  | ous measurements without the help of external devices [28]                                                                                                                                                                               | 1.5 |

| 8  | electrodes connected to PCB [29]                                                                                                                                                                                                         |     |

|    | and Philips [29]. a) A SEM image of the Cytostretch chip from the back b) Inset                                                                                                                                                          | 2.1 |

| 12 | depicts the area highlighted in (a) showing the transversal micro-grooves, the exposed TiN electrodes and parylene insulation of the metal tracks.[29]                                                                                   |     |

|    | A schematic cross-section of a conventional OECT with PEDOT:PSS conduc-                                                                                                                                                                  | 2.2 |

| 13 | tive channel                                                                                                                                                                                                                             | 2.3 |

|    | ing applied between the drain and the source, there is no current flow in the channel. When the drain to source voltage is negative, the polymer channel begins to conduct. As the gate to source voltage is positively biased, ion pen- | 2.0 |

| 13 | etration begins from the electrolyte into the conductive PEDOT:PSS channel.                                                                                                                                                              | 2.4 |

| 14 | dipped in the analyte solution of interest. And ion-selective membrane separates the gel electrolyte from the analyte being studied.                                                                                                     |     |

| 15 | performed using ion selective OECT (IS-OECT) [46]                                                                                                                                                                                        | 2.5 |

| 16 | A schematic of the device fabricated by Benfenati <i>et al.</i> [38] for extracellular recording.                                                                                                                                        | 2.6 |

| 16 |                                                                                                                                                                                                                                          | 2.7 |

| 19 |                                                                                                                                                                                                                                          | 3.1 |

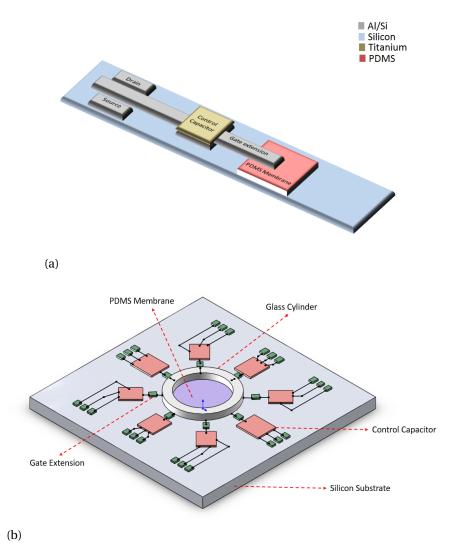

| 20 | a) Simplified 3D diagram of the proposed Charge-modulated FGFET. Here, the sensing area with the PDMS membrane can be seen more clearly. b) Experimental setup view                                                                      | 3.2 |

| 21 |                                                                                                                                                                                                                                          | 3.3 |

X LIST OF FIGURES

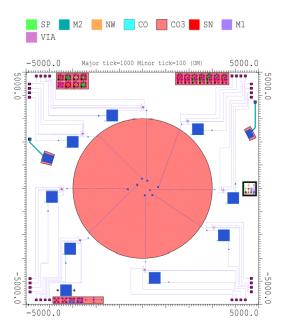

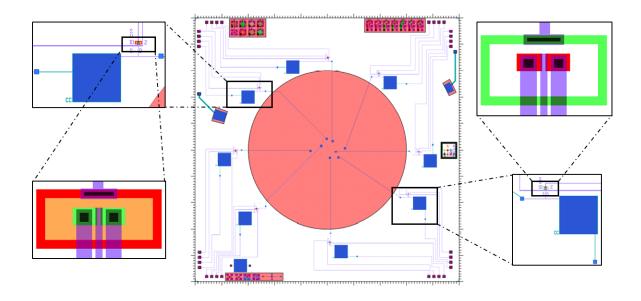

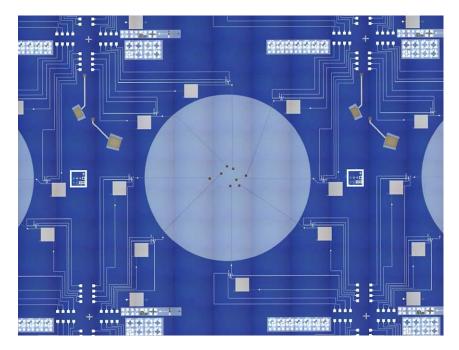

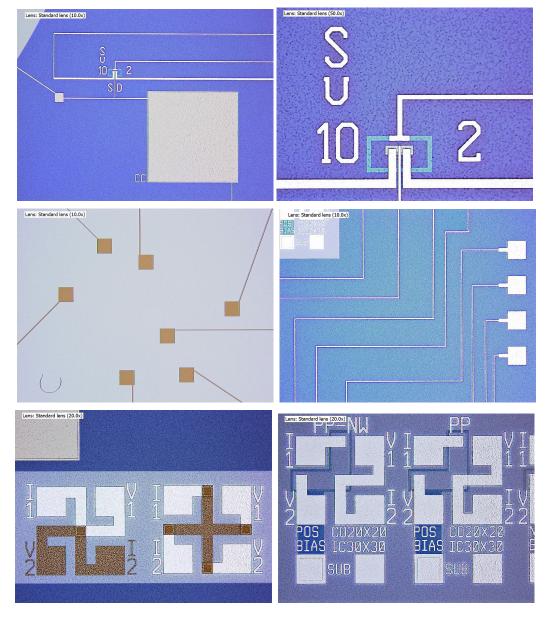

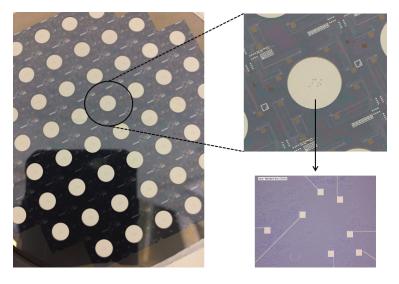

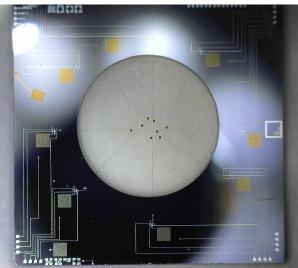

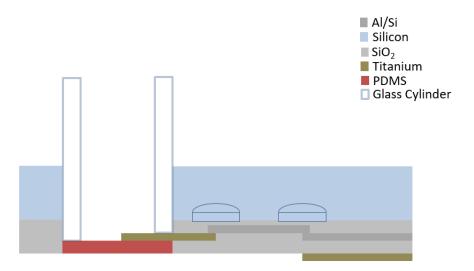

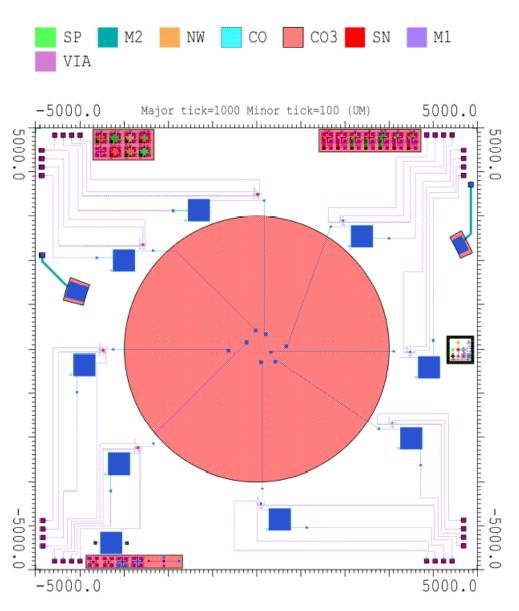

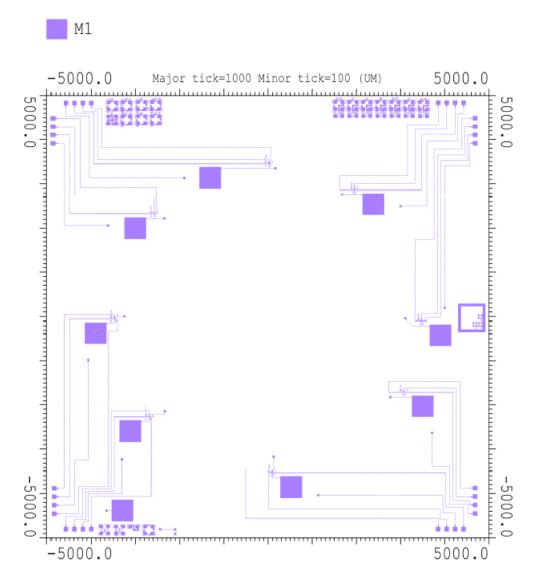

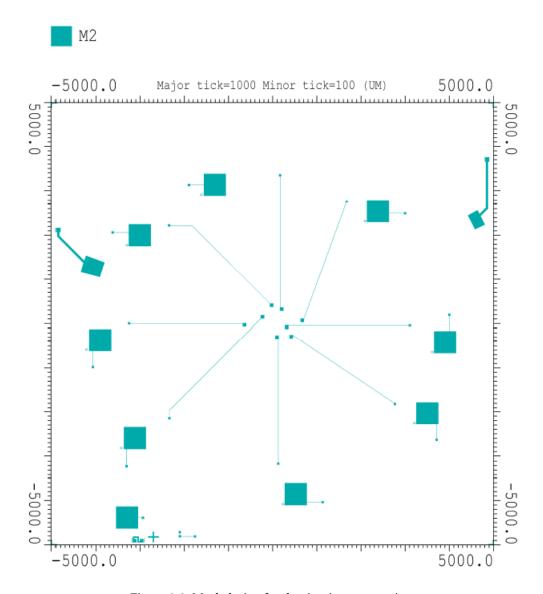

| 4.  | The layout of one single die. The die size is $10,000 \times 10,000 \mu m$ and every colour depicts an individual mask. The bondpads are visible on each of the four corners of the die. The red circle in the center is the active sensing area where the free-standing PDMS membrane is fabricated. The blue squares |          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.2 | depict the control capacitors that act as the reference electrode                                                                                                                                                                                                                                                      | 25       |

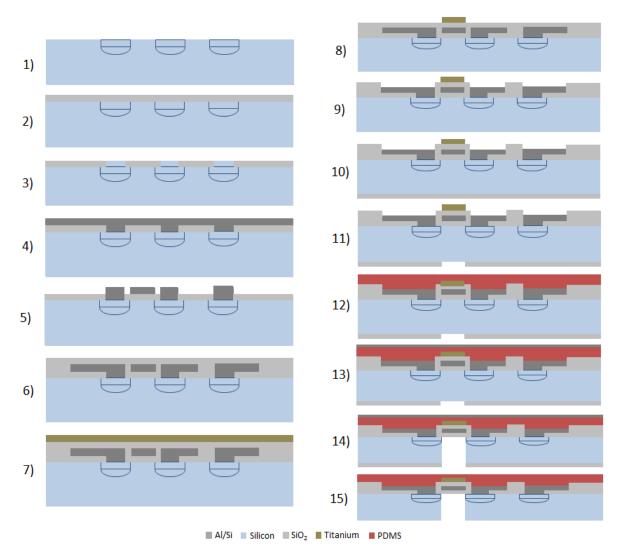

| 4.3 | zoomed into                                                                                                                                                                                                                                                                                                            | 26<br>28 |

| 4.4 | 4 Cross-sectional schematic of the Charge-modulated FGFET after membrane                                                                                                                                                                                                                                               |          |

| 4.  | release                                                                                                                                                                                                                                                                                                                | 28<br>29 |

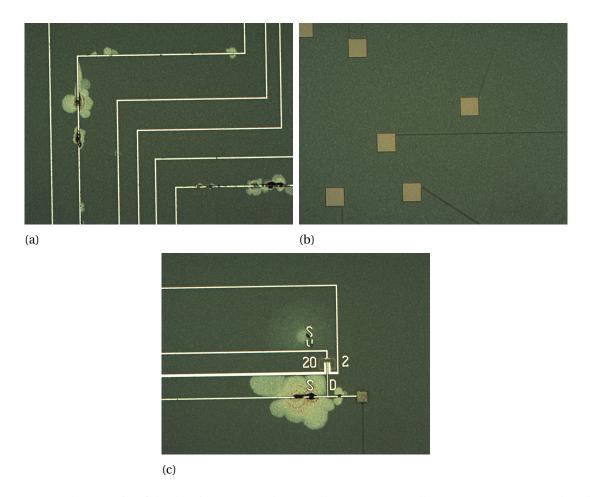

| 4.0 | Photographs of the die after a 30 sec plasma etch. a) Titanium still present in interconnect bend corners. b) Titanium appeared to have been completely etched away from the sensing area leaving cleanly patterned gate extensions. c) Areas around some transistors showed over-etch of the oxide layer under-       |          |

| 4.  | after 25 sec plasma etch. c) and d) are the areas of oxide over-etch leaving                                                                                                                                                                                                                                           | 30       |

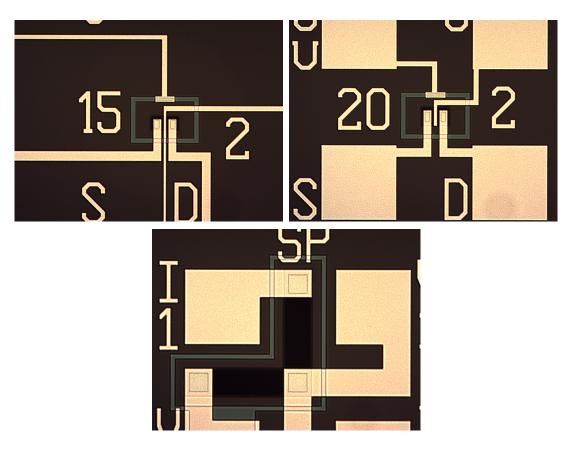

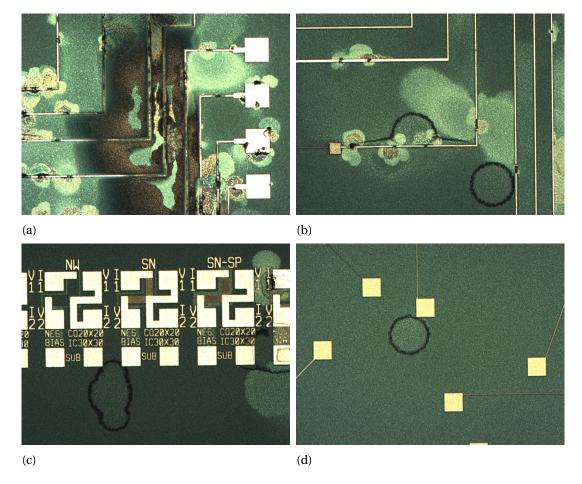

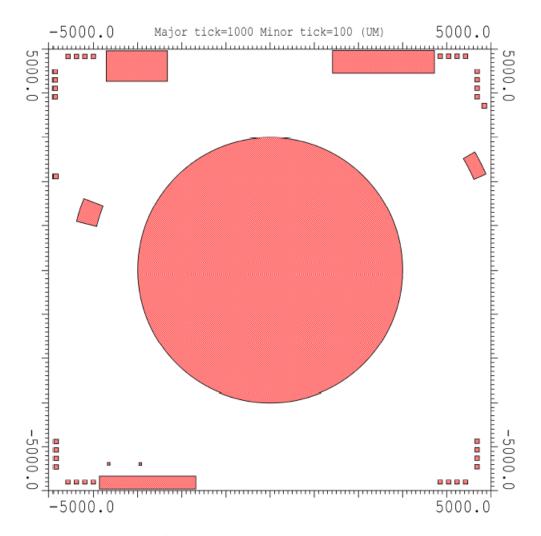

| 4.8 | behind large circular spots on the die.  A complete layout of one die in a wafer before PDMS membrane deposition                                                                                                                                                                                                       | 31       |

| 4.0 | and release                                                                                                                                                                                                                                                                                                            | 32       |

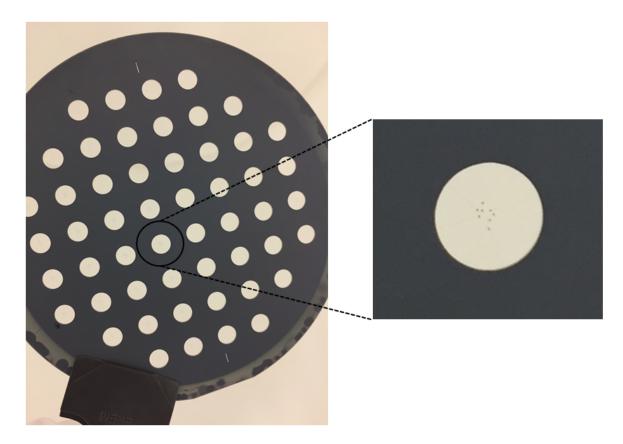

| 4.9 | has to be deposited and released, to prove the ability of the devices to be in-                                                                                                                                                                                                                                        | 20       |

| 4   | tegrated in an OOC platform                                                                                                                                                                                                                                                                                            | 32<br>33 |

| 4.  | 11 Suspended gate electrode extensions on the transparent PDMS membrane.  12 Backside of the wafer after PDMS membrane release. The transparency of the membrane is highlighted by the inset where-in the gate extensions are clearly                                                                                  | 33       |

| 4.  | visible                                                                                                                                                                                                                                                                                                                | 34       |

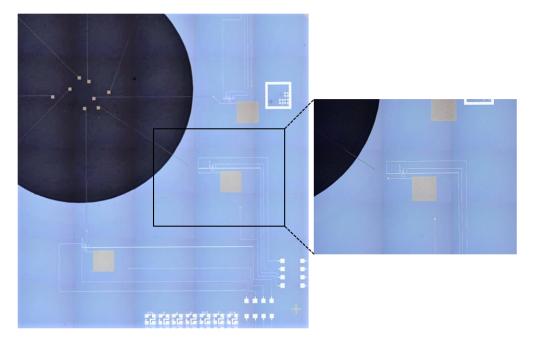

|     | microscope. The membrane is transparent and hence appears black as the stage of the microscope is black in color. The inset shows a close-up of the                                                                                                                                                                    | 2.4      |

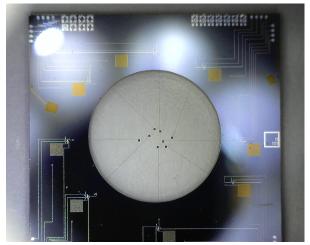

| 4.  | transistor structure completely preserved.  14 Microscope pictures of a final die with the PDMS membrane released. There appears to be a lot of reflection coming off the chip, as keeping the microscope light on was necessary to obtain clear view of the features. The tiny                                        | 34       |

|     | particles that are visible are dirt particles from the storage box                                                                                                                                                                                                                                                     | 35       |

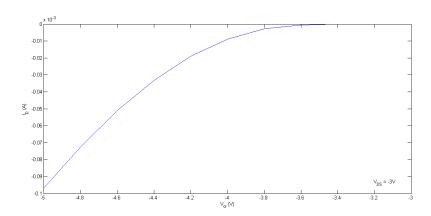

| 5.  | ,                                                                                                                                                                                                                                                                                                                      |          |

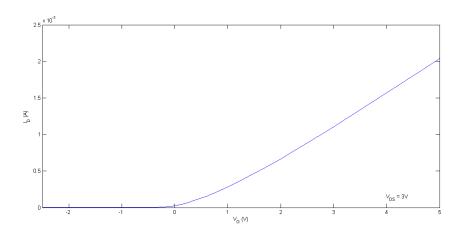

| 5.2 | ,                                                                                                                                                                                                                                                                                                                      |          |

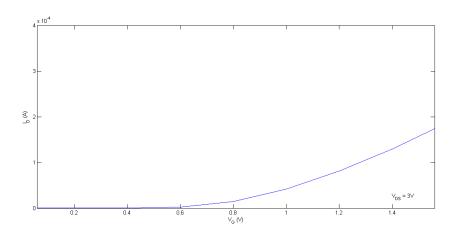

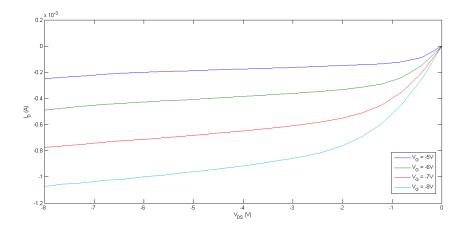

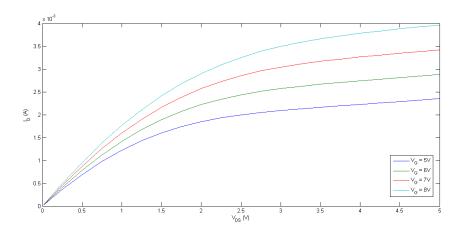

| 5.3 | <ul><li>Zoomed-in transfer characteristics plot for the Charge-modulated FGFET, NMO</li><li>2:25. The threshold voltage appears to be around 0.6V.</li></ul>                                                                                                                                                           | 5<br>38  |

| 5.4 |                                                                                                                                                                                                                                                                                                                        | 39       |

| 5.  | Measured output characteristics of the Charge-modulated FGFET, NMOS 2:25.                                                                                                                                                                                                                                              | 39       |

| 5.0 | 1                                                                                                                                                                                                                                                                                                                      | 40       |

| 5.  | Measured transfer characteristics of the PMOS 2:25 a) before incubation and b) post incubation at 37°C and 90% humidity for 7 days.                                                                                                                                                                                    | 40       |

LIST OF FIGURES xi

| 5.8        | Measured output characteristics of the PMOS 2:25 a) before incubation and              |    |

|------------|----------------------------------------------------------------------------------------|----|

|            | b) post incubation at 37°C and 90% humidity for 7 days                                 | 40 |

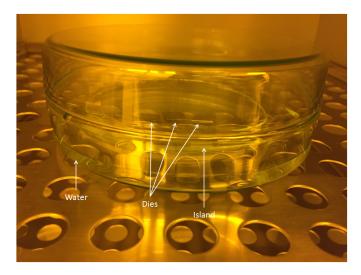

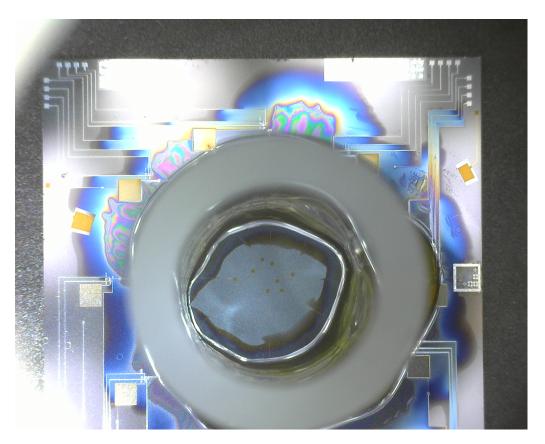

| 5.9        | Epoxy bleeding in a cylinder attached die                                              | 41 |

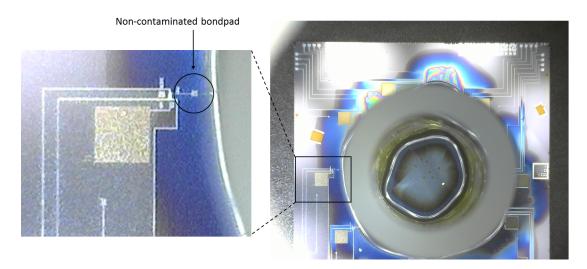

| 5.10       | Example of a cylinder attached die with all bondpads intact                            | 42 |

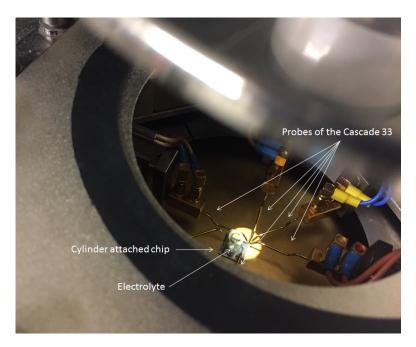

| 5.11       | Electrochemical Measurement Setup in the Cascade 33                                    | 43 |

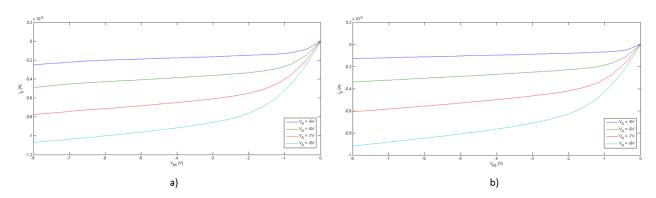

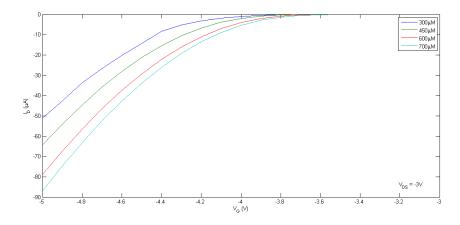

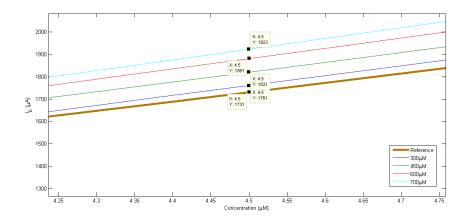

| 5.12       | Transfer characteristics of the Charge-modulated FGFET, PMOS 2:25, for vary-           |    |

|            | ing ionic concentrations                                                               | 43 |

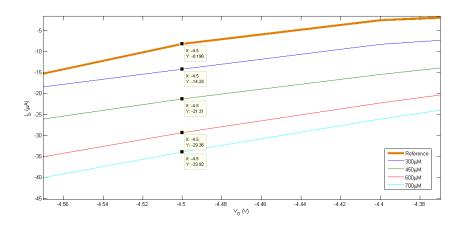

| 5.13       | Plot to obtain $\Delta I_D$ for varying ionic concentrations, for the Charge-modulated |    |

|            | FGFET, PMOS 2:25                                                                       | 44 |

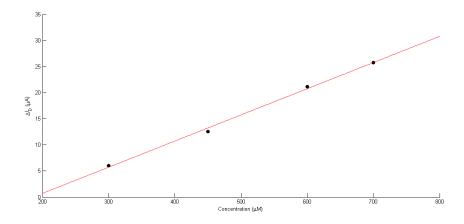

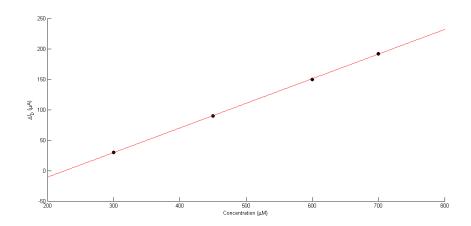

| 5.14       | Calibration curve for the Charge-modulated FGFET, PMOS 2:25                            | 45 |

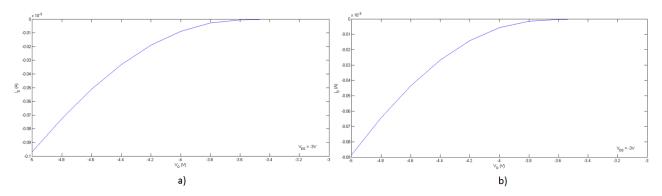

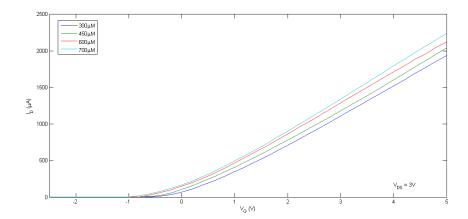

|            | Transfer characteristics of the charge-modulated FGFET, NMOS 2:25, for vary-           |    |

|            | ing ionic concentrations                                                               | 45 |

| 5.16       | Obtaining $\Delta I_D$ from the transfer characteristics plot at varying concentra-    |    |

|            | tions of the electrolyte for the Charge-modulated FGFET, NMOS 2:25                     | 46 |

| 5.17       | Calibration curve for the Charge-modulated FGFET, NMOS 2:25                            | 46 |

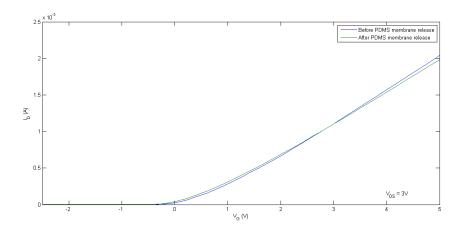

|            | Transfer characteristics for the Charge-modulated FGFET, NMOS 2:25, before             |    |

|            | and after PDMS membrane release, plotted together                                      | 47 |

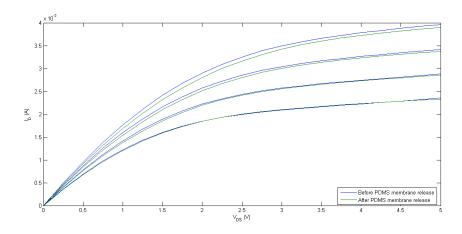

| 5.19       | Ouput characteristics for the Charge-modulated FGFET, NMOS 2:25, before                |    |

|            | and after PDMS membrane release, plotted together                                      | 47 |

|            |                                                                                        |    |

| 6.1        | Possible setup for electrochemical characterization after membrane release.            |    |

|            | The chip is flipped over and the cylinder attached to the backside of the die          | 49 |

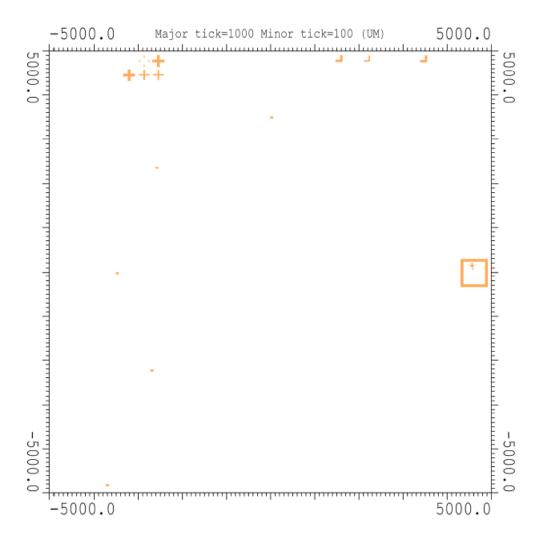

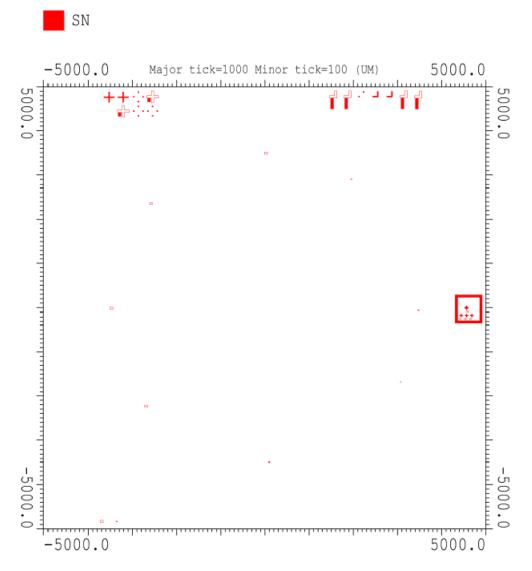

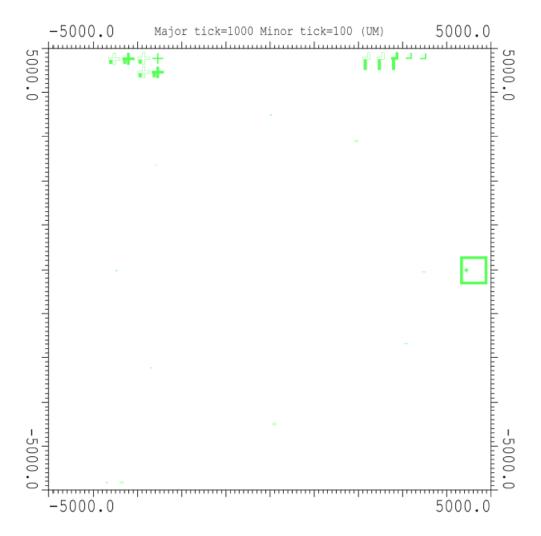

| A.1        | Full mask layout with all layers                                                       | 51 |

| A.2        | Mask design for the N-Well definition                                                  | 52 |

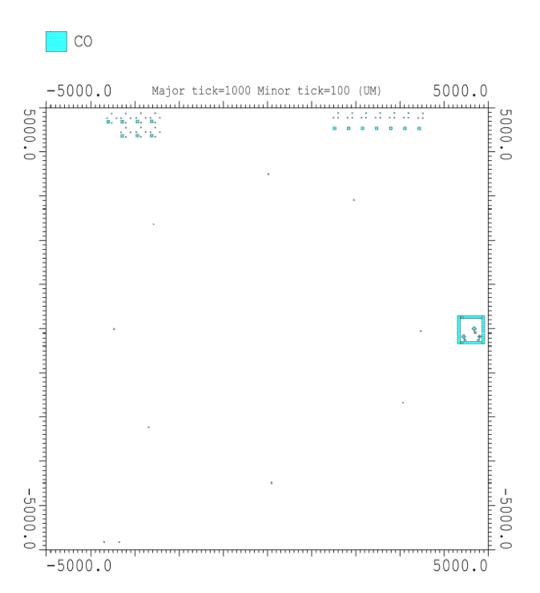

| A.3        | Mask design for the shallow-N layer definition.                                        | 53 |

| A.4        | Mask design for the shallow-P layer definition                                         | 54 |

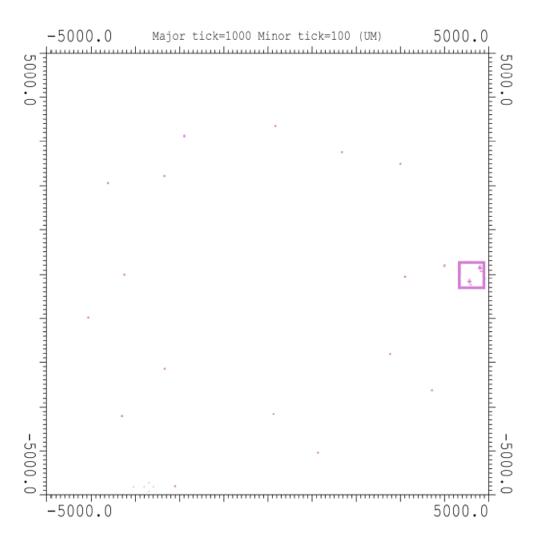

| A.5        | Mask design for the contact openings in the gate oxide before first metalization.      | 55 |

| A.6        | Mask design for the IC definition.                                                     | 56 |

| A.7        |                                                                                        | 57 |

| <b>A.8</b> | Mask design for the titanium patterning                                                | 58 |

| A.9        | Mask design for defining the contacts opening for the bondpads and the sens-           |    |

|            | ing area for electrical characterization.                                              | 59 |

|            |                                                                                        |    |

## **LIST OF TABLES**

| 3.1 | Geometric and Process Parameters [55]                        | 22 |

|-----|--------------------------------------------------------------|----|

| 3.2 | Process Parameter Values                                     | 24 |

| 5.1 | Electrolyte Concentration Values                             | 42 |

| 5.2 | $\Delta I_D$ for PMOS 2:25 at different ionic concentrations | 44 |

| 5.3 | $\Delta I_D$ for NMOS 2:25 at different ionic concentrations | 46 |

1

### INTRODUCTION

Biomedical research nowadays encompasses a broad scientific field that has the potential to prevent and treat rare and fatal diseases in humans. This general field of research includes many areas of both life and physical sciences. Thus, this synergy enables biomedical researchers to study biological processes and diseases with a vision to develop effective treatments and eventually cures.

Drug development forms a whole area of research that partly exploits the developments from biomedical research. It begins with the understanding of the diseases that affect animals, mostly at the cellular or molecular level. It is by understanding of these disease processes and pathways that targets for new treatments are identified. This could possibly be a protein or another molecular compound that is indispensable for the disease process. These compounds could react with the new treatment drugs, for example, by blocking an essential receptor [1]. Once a potential target has been identified, researchers will then search for a molecule or compound that acts on this target. Historically, plants, fungi as well as marine animals have been studied as they generate compounds that can essentially provide the base for potential drugs. However, in recent times, scientists have also begun to create new molecules for these studies. Genetic and molecular biology studies have played a key role in this front. With current knowledge, it is possible to investigate a large pool of such compounds and streamline them down to just 10 or 20 that could theoretically interfere with diseases. It is after this, that the next step is majorly to confirm whether the drugs and molecules are safe for humans. However, before any foreign molecules are tested on humans, it is necessary to conduct safety tests to determine if the molecules will react with the human body. This is usually done via the means of some computerized pathophysiological models, or by animal testing. Only about half of these new potential compounds make it through this stage. The 5 out of 10 compounds that remain are now ready for human-testing.

Evidently, the discovery and development of new medicines and therapies is a complex process and requires careful scientific research. Pharmaceutical companies, nowadays spend tens of billions of dollars in testing of several potential drugs. Most of this testing techniques rely on in-vitro testing. However, many human diseases are still unable to be accurately modelled in-vitro, limiting understanding and therapy development. In-vitro

2 1. Introduction

testing is limited in its ability to prove the efficacy of new therapies as cells might not react the same way as they would when outside their natural environment.

The failure of in-vitro testing and its subsequent consequences can be demonstrated by the example of Vioxx, a drug that was developed in the year of 1999 [2]. The pharmaceutical company Merck introduced this new arthritis drug after consultation and approval by the Food and Drug Administration (FDA). Coming at a time when arthritis was affecting a massive number of people in and around the world, this drug proved to be a huge success in the pharmaceutical market. More than 80 million prescriptions and 2 million daily users were reported already by the end of September [3]. However, inspite of this, Merck voluntarily decided to call this drug off of the market on September 30, 2004. It was determined, that the drug was known to cause or even induce heart attacks and strokes and a variety of other side-effects. The death toll were estimated to be around 50,000 to even 500,000. Since a large part of the data is derived from drug testing on animals, the corresponding results could not easily be translated onto human patients. Had the drug been tested before using a much reliable method, especially for that of toxicity, this would have improved patient safety and guaranteed quality of human life. It is quite clear that testing on animals is expensive and comes with numerous ethical issues, in addition to the fact that they are not able to mimic human physiology and genomic models well enough to accurately test the effects of these on human life.

The majority of these tests, so far, have relied on bulk optical techniques such as those of immunofluorescence end-point detection, microscopic cell imaging among others. These methods are beneficial to acquire and analyze the information of cell cultured microenvironments [4]. The intrinsic inability of purely optical methods to capture in vivo biological phenomenon is a major limitation in these methods which causes specific data to be missing from measurements. These in addition involve mechanical, chemical and topographical cues. For instance, a more complete view can be easily obtained if contractile stresses, bioelectrical activities, pH level, calcium, potassium and oxygen concentration could be quantitatively measured in a spatio-temporal manner for a culture of heart cells [5]. Monitoring bioelectrical activity of heart cells has been studied by several groups and many of them report several novel approaches to monitor this electrical extracellular activity by using microelectrode arrays in cell cultures [6]. Alternative detection and analysis methods are still necessary to enable the monitoring of some biochemical, physical and mechanical signals within these microenvironments, specifically with a quantifiable and real-time approach[7]. Likewise, an intrinsic limitation is its poor scalability since most of the characterization techniques used by this technology are bulky and so restricting the full integration and mass implementation of the technology [8]. Further, it encompasses several ethical issues, faced by animal testing which are widely contested today. Debate surrounding the breeding of test animals for medical research is increasing day-by-day. It is also an expensive process, partly because of the necessary testing required for human toxicity and efficacy of drugs. Such limitations of current planar, static cell culture systems or animal models result in the high drug failure rates seen in clinical trials, a limitation that can cost pharmaceutical companies billions of dollars.

These issues highlight the urgent need for more physiologically relevant models of human

1.1. Organ-on-Chip

organs, and have fuelled the development of organs-on-chips. As a result of this, the necessity of developing self-integrated monitoring structures was identified as crucial. Microfabricated Organ-on-Chip (OOC) platforms are such devices that are developed for satisfying this need, and are highly studied in current academia as well as the industry. The end goal is that these models will lead to more accurate detection of toxicity or efficacy problems and reduce the amount of drugs failing in human clinical trials.

### 1.1. ORGAN-ON-CHIP

Organ-on-Chips are relatively new and novel cell culture platforms that overcome the limitations of conventional drug-testing methodologies. These devices are specially designed to mimic the minimal unit of human organs. To do so, different cell types and tissues are cultured in specially designed microstructures that resemble such particular microenvironments of the human body. Within such controlled microenvironments, biochemical and mechanical cues can be well controlled and monitored. It is to be noted that even for these devices, research is still in a very early stage.

OOC models are potentially valuable for the development of new drug compounds and as drug screening devices [9]. Some reports [10] [11] have also indicated that in-vitro human stem cell based models are, in a few cases, already far more accurate than animal models. iPS technology is a recently developed experimental method that allows in vitro culturing of well defined and reproducible human tissue with a certain genomic profile [12]. This technique is actually beneficial in creating stem cell models which can explain to researchers, the various ways in which human cells would normally respond in-vivo. This would further allow researchers to study investigate the functioning of both healthy and diseased tissues under the influence of new drugs. This would also be far superior to animal models, more ethical and cost-efficient since mass production is possible.

Several OOC models have been studied in the academia. The following subsection offers an insight to some such models.

### 1.1.1. LUNG-ON-CHIP

The development of new solutions to treat pulmonary diseases has become a goal of primary importance today. Globally, pulmonary diseases are the fifth major cause of death in the world and are soon predicted to become the third by 2020 [13] [14]. In this context, it is critical to be able to develop lung-on-chip models to facilitate newer and better treatments.

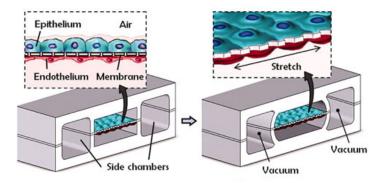

The team of Huh *et al.* [14] from the Wyss Institute of Biologically Inspired Design at Harvard were one of the first in the world to have successfully been able to manage to reproduce and subsequently observe the functions of the human body in-vitro or outside the human body. The model fabricated by them has been shown in Fig. 1.1. The lung-on-chip developed trough softlithography comprises of two microchannels separated by a porous membrane. The entire device was fabricated using polydimethylsiloxane (PDMS) and the mebrane covered in collagen for better cell adhesion. This enabled the separation of epithelial cells in contact with air on one side and endothelial cells in contact with nutritions fluid (in lieu of blood) on the other side.

4 1. Introduction

Figure 1.1: Lung-on-Chip as fabricated by Huh et. al. [14]

Further, in order to test the functioning of the chip in reproduction to a normal human lung, Huh *et al.* [14] introduced bacterial cultures in the air flow and white blood cells in the blood flow. Just like in the human body, The inflammatory response of the white blood cells was triggered as they moved to the epithelial cells side to fight the bacteria. However, sensors to detect the barrier movement, or fluid flow, pressure or even migration of the cells haven't yet been integrated in such a device.

### 1.1.2. Brain-on-Chip

Brain-on-Chip are modular devices in which the neuronal cells and the device itself follow a close transfer of information with each other. Neuronal stimulation has been achieved with devices that are interfaced with the cell-culture medium directly [15]. The tissue is present in an electrolyte form and contained in a glass vessel on the surface of the device. The device has a voltage-sensitive site, which has several metal electrodes that are inturn connected to the readout circuitry [16]. Micro-electrode Arrays (MEA) have been used commercially in the market for electrical stimulation on the surface of the device. These consist of a 2D array of electrodes branched out from each other with an insulator medium in between. These electrodes serve as monitoring or electrical stimulation structures are key in electrochemical characterization of the brain cells. They provide for a better understanding of the electrical activity of our brain.

Research has also been able to reproduce a small part of the brain, the blood-brain barrier on a chip [17]. This barrier has an essential function, as it protects the brain from all pathogens in the blood flow and only lets through nutrients to the brain. However, it also restricts some active sites from accessing the brain tissue, for example the medicine to treat Parkinson's disease [18]. Hence, in such a case, the development of brain-on-chip is sought-after as these devices allows to test the fluid flow under physiologically relevant conditions [19]. This mimics the flow of blood and allows the brain cells to properly differentiate and mature. Nowadays, brain-on-chips have proved to be more accurate than static cultures to predict permeability of the blood-brain barrier [18] [20].

Recently, a drug-delivery system for integration into OOC platforms has been fabricated by the Delft University of Technology in collaboration with Philips Research Center [21]. The device fabricated is a PDMS membrane enclosing a microchannel for drug-delivery of the chemical required for cortical spreading depression (CSD) onto a site that houses

1.1. Organ-on-Chip 5

the brain tissue. The electrical activity of the brain cells is then studied before and after the drug introduction. However, this electrical monitoring is performed with an external readout circuitry. The integration of sensors for monitoring such electrical activity is yet to be realized.

### 1.1.3. CANCER-ON-CHIP

It has also been made possible nowadays to mimic the metastasis of such tumor cells. The invasion of carcinogenic cells from the main tumor-site in the body to other secondary sites of the organs is called metastasis [22]. It is interesting to note here that a tumor can easily be compared to an organ as it also has a micro-environment which provides the tumor cells with certain biochemical and mechanical stimulation which, in-turn, provides these tumor cells to become cancerous and metastasize into furthermore cancerous cells. This kind of metastasis progression of cancer is a very special phenomenon and most of the factors trigerring it are still unknown to us. Thus, the concept of Organ-on-Chip is of particular interest due to its capability to replicate the tumor micro-environment and also to study the periodic activation of this environment that leads towards the metastasis.

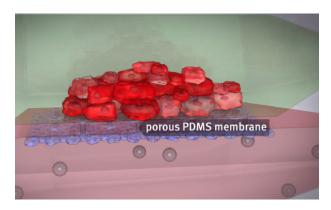

Figure 1.2: Conceptualization of the device [23]. The tumor and metastatic site are separated by a porous PDMS membrane. The direction of movement of the cancer cells is from the tumor to the metastatic site, via the porous membrane that represents the blood-vessels.

An example of this is a device developed by the Eindhoven University of Technology in the form of a multi-chamber microfluidic device [23]. This device enables us to study cancer cell migration through the blood stream, before it finally reaches the second metastatic site, as shown in Fig 1.2. The tumor and the metastatic site are conceived as endothelial cells seperated by a porous membrane. This represents the blood-vessel lining in the human body. This porous membrane is where the transition to cancer and invasion of the blood vessels occurs and is a very important feature of the device as shown in Fig. 1.3.

6 1. Introduction

Figure 1.3: Co-culture of 3D tumor cells and a 2D endothelial cell monolayer separated by a porous membrane [23].

As was pointed out for lung-on-chips, it would perhaps be beneficial to integrate sensors in the device, that can give monitor cell behaviour or the fluid flow properties across the porous barrier.

### 1.1.4. HEART-ON-CHIP

In the mammalian body, the heart is one of the most vital organs. It is responsible for supplying nutrients and oxygen to the organs via the pumping of blood. It has a very important characteristic of autorhythmicity, which is also modulated by the endocrine and nervous systems.

Cardiovascular (CVD) diseases are a condition of the body that fatally affect the heart. CVDn nowadays has become major cause of death globally. It was established in 2012, that 17.5 million people died of CVDs globally. This has sparked a major interest in researchers investigating the cause for these diseases and their subsequent treatment. The need to understand the heart better has lead to the development of heart-on-chip models. With the help of microfabrication technology, this has now turned into a plausible reality. Just like the previous models for drug-testing, these models also allow for in-vitro testing of drugs and pathogens that plague the heart and cause CVDs.

A heart-on-chip is a novel and simple method to reproduce the cardiac tissue in three dimensions and measuring the effects of the organ's exposure to foreign substances. This makes it possible to study the response of cardiomyocytes to external stimuli.

Several physiologically relevant models have been studied for drug and cardiotoxicity screening. In 2014, Xiao Y. *et al.* [24], demonstrated that human embryonic stem cells and rat neonatal derived cardiomyoctyes could be used microfabricate a cardiac biowire bioreactor for pharamceutical drug testing. The spontaneous beating of the biowires could be slowed down by treatment with nitric oxide, carried by the medium into the chamber. There have also been examples of microfluidic devices that generate cardiac-like flow in a continuous closed-culture system [25]. The heart is also a rare organ with active tissues that show tissue contractions. These tissues are known to have a better cardiac differentiation when stimulated by a stretching pulse, as demonstrated by Zhuang et. al. [26].

1.1. Organ-on-Chip

For drug development, it is also necessary for these devices to be able to respond to chemical stimuli within a varying range of doses. Agarwal *et al.* [27] tested isprotenerol, a medicine used to treat heart failure or bradycardia, on a rat cells based heart-on-chip, in doses between 1nM and 0.1mM. The experiments, although conducted on non-human cells, demonstrate the potential of heart-on-chips to test a wide range of medicinal concentrations.

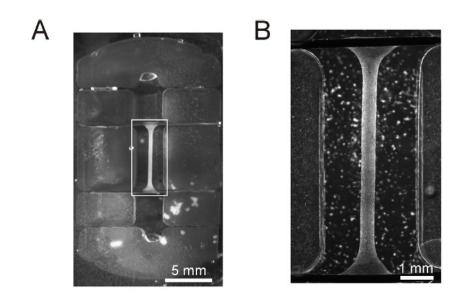

Moreover, the I-Wire Heart-on-Chip is a device created at Vanderbilt University by the team of Sidorov et. al., [28]. Described more precisely, the team developed a PDMS casting mold and added it into a six-well plate, as shown in Fig. 1.4, with a channel on each side for insertion of titanium anchoring wires. Following this, a 3D cardiac tissue was then engineered and and cultured in this plate using ventricular cells. As explained by them, different types of cells are necessary in order to generate the proper cardiac tissue structure. Hence, they used both cardiomyocytes as well as cells from the the extra-cellular matrix formation. For easier culturing, the cells were placed in a culture medium and within 5-6 days of culture, the cells begun to beat synchronously and within 13-15 days, muscular fibers were formed. The contractions occurring as a result of this, were monitored via the means of an optical microscope with a cantilever probe attached to the condensor of the microscope. The action potential was also measured using electrodes. A silver chloride electrode was used to serve as the reference electrode [28]. Moreover, the anchoring titanium wires were used for voltage stimulation.

Figure 1.4: A) Six parts PDMS casting mold is obervable [28]. B) Two channels on each side of the culture for adding of wires. These wires allow direct and continuous measurements without the help of external devices [28].

This study was however limited to the use of external electrodes for sensing and monitoring the electrochemical activity of the cells. To accurately measure and model the human body functions, such as the ionic activity occurring when the heart pumps blood to vital organs, this cellular model is not sufficient. This has lead to new investigation in the field of heart-on-chips.

8 1. Introduction

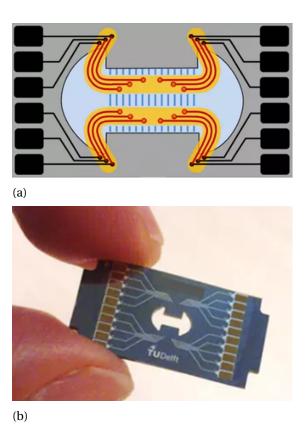

The lack of electrical monitoring techniques for these platforms has recently motivated the development of a robust model with integrated sensing technology. Mostly, nowadays for cardiotoxicity screening, Multi-Electrode-Arrays based devices are fabricated and characterized with human heart cell cultures. In a project by Gaio et. al. [29], the authors have fabricated a low-cost and accurate heart-on-chip device. This concept was developed by the Delft University of Technology in collaboration with the Leiden University Medical Center and Philips Research Center and is called the Cytostretch [29]. It works by addressing certain challenges and to create a more physiologically relevant environment for the heart muscle cells to mature, resulting in a more reliable heart model. The basic model of the platform consists of a stretchable microelectrode-array, made in silicon with polydimethylsiloxane (PDMS) as the flexible substrate for the cells. Titanium nitride interconnects that are stretchable, are fabricated on the thin PDMS membrane. These are meant to connect the electrodes to the bondpads, that are patterned on the edge of the device. Additionally, there are microgrooves that are etched on the PDMS membrane that permit the cells to be aligned in a specific direction only. It has a dog-bone structure, as can be seen in Fig. 1.5. This specifically allows for the straining of the cells in the direction perpendicular to the length of the device. This novelty along with the microgrooves allow for the cells to be aligned in a specific direction on the membrane. This also makes the unidirectional straining of cells possible. Through experiments, it was found that after 3 days of culturing cardiomyocytes on top of the Cytostretch, the cells started beating on top of the stretchable PDMS membrane, signifying good functionality and viability.

Figure 1.5: a) Schematic of the Cytostretch device. b) The actual SMEA chip with the electrodes connected to PCB [29].

Thus the cytostretch proved to be a fully microfabricated heart-on-chip device that allows for a dynamic environment for the cell culture through stretching of the PDMS membrane. During the experiments, the Cytostretch device also worked by measuring change in the extracellular field potential of cardiomyocytes to indicate possible heart failure. If the membrane is inflated above the regular value, this mimics increased cardiac activity. Most importantly, this device provided for a platform to integrate sensing electrodes in a flexible membrane thereby better resembling physiological conditions.

### 1.2. NEED FOR SENSOR-INTEGRATION IN OOCS

The field of OOCs is continuously evolving. Although the Cytostretch already makes up for an OOC with integrated sensing electrodes, there is still a need for more sophisticated sensor integrated OOCs that can provide continuous information about the electrical or chemical activities of cell cultures on the device in real-time. To achieve such a goal, several criteria need to be ensured. One of the key criteria is to integrate these sensors into the devices to monitor the physical and electrochemical characteristics associated with the functioning of OOC models.

### 1.2.1. MONITORING CHEMICAL GRADIENTS AND ELECTRICAL PARAMETERS

Chemical stimulation is an important parameter that has to be taken in to account to develop and maintain physiologically relevant OOC platforms. Thanks to microfluidic devices integrated with detection platforms, it is possible to control and tune the fluid flow of the chemical agents in such OOC devices. This has been made possible through a microfluidic device that operates with the pressure feedback control from the drug delivery technique in the chip [30], that delivers the drug to the tissue site via a fluid pumping technique. It is also possible to use a small amount of chemicals to generate, measure and control an oxygen gradient inside microfluidic channels [31].

Additionally, measurement of dissolved oxygen (DO), even combined with sensors for pH, glucose and lactate, are important criteria for the development of OOC devices. The first widespread DO sensor configuration commonly adopted was proposed by Wolf *et al.*, [32], consisting of a platinum working electrode as the cathode and a silver chloride electrode as the reference electrode, and anode for detecting the current from oxygen reduction reaction [32]. Several different elements are present in our body in ionic form which regulate our bodily functions on a day-to-day basis. They help regulate body fluids, muscular activity, blood pressure and so on. Electrochemical sensor architecture is getting more and more important nowadays especially with the emergence of various sensor configurations to detect such ions on OOC platforms. Hence, other solutions were considered such as transistor based sensors, for detection of ions. Several optical sensors have also been studied [33] [34], but relying on optical techniques, optrodes suffer from small-range measurements [35].

### **1.3.** Scope of the thesis

In a changing scenario of such biomedical electronic devices, considerable effort has been put into the development of more and more transistor-based devices for biosensing and electrophysiological monitoring of electrogenic cells. However, the ability of such devices 1. Introduction

to be incorporated in standard CMOS technology has been fairly debatable. Also important is the detection of ions in this regard, as several different ions are present in the human body that regulate our cardiovascular, neural, muscular activities amongst others. The failure of optrodes in the electrochemical measurement regard, has prompted the use of transistor based solutions to sense ions in OOCs. In this context, the goal of the thesis is to develop and integrate a charge-modulated FET based ion sensor ( $Ca^{+2}, K^+, H^+$ ) for integration into an OOC platform developed with standard CMOS process technology. The possibility of several transistor-based configurations for the development and integration of an ion sensor into an OOC platform has been studied. Keeping in mind the standard CMOS fabrication process for the sensor relevant, a novel design for such an integratable ion sensor has been proposed, designed, fabricated and characterized.

### **1.4.** OUTLINE OF THE THESIS

Chapter 2 deals with the state-of-the-art and the background technology already available for such sensors. Chapter 3 talks about the design and modeling of the sensor itself. Chapters 4 and 5 are mainly about with the fabrication process and the electrochemical characterization of the device respectively.

# 2

## ION-SENSING TECHNOLOGIES FOR OOC APPLICATIONS

Now that the importance of integrating ion-sensing technologies for OOC platforms has been established, it is important to study the different arrangements for sensors for the detection of ions that have been developed in the past. It is important to be able to successfully integrate these ion sensors in standard microfabrication technology for easier mass scale reproduction. Some of the most important configurations in this regard have been made with soft materials where low cost or high-throughput fabrication is desired. Mechanical compatibility with soft tissue is also a very important characteristic that is required. Some of these technologies will be studied in the following section.

### 2.1. STATE-OF-THE-ART

The invention of the transistor in the year 1947 heralded the era of microelectronics [36]. Occupying a particularly major part of the semiconductor manufacturing industry, these miniaturized devices are mainly made of semiconductors, dielectrics and metals[36]. They are usually the core of integrated circuits, which are the building blocks of any electronic device. Organ-on-Chips are no exception to this. Transistor based devices have, and are currently being used as sensors in OOC platforms [37] [38]. However, in addition to this, there are several organic material based designs that are being used to develop these OOCs as well. These are truly multidisciplinary devices, combining both biology with engineering.

### 2.1.1. (STRETCHABLE) MICROELECTRODE ARRAYS

The most conventional method that has been used to detect and quantify the bio-electrical activity of cells is the usage of microelectrode arrays. Microelectrode arrays are useful tools in studying the electrophysiology of living cells seeded on the devices. Excitable cells under the influence of electrical stimuli would produce extra-cellular field potentials. These MEAs enable researchers to quantify and map this electrical response [39]. However, MEAs traditionally have been fabricated on rigid substrates. This therefore limits the study of insitu mechanical stimulation of the OOC device. Thus embedding the electrode array onto the surface of a stretchable membrane enables the application of physiologically relevant mechanical stretch to the cardiomyocytes cultured on the membrane. These devices can

replicate the in vivo stretching and contraction of cells during electrical measurement and also enables in situ maturation of the cultured stem cell derived cardiomyocytes.

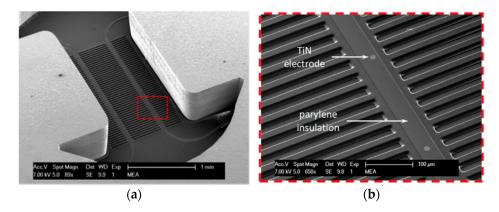

Lately, SMEAs have become important tools in biomedical research. As the substrate is no longer rigid, this allows for mechanical stimulation under the presence of electrical stimuli and thus enables better investigation on the mechanobiology of the cultured cell medium. Although the metallic interconnects might be robust in the relaxed state of the membrane, it is also important to check the strain of these electrode interconnects under strain when the membrane bends. This has lead to the study of several alternative materials to fabricate the electrical interconnects in such SMEAs as conventionally metals are more commonly used which are not inherently stretchable [40] [41]. A good example of an SMEA with suspended electrodes is the Cytostretch discussed in Chapter 1. A more detailed image of the Cytostretch has been shown in Fig. 2.1.

Figure 2.1: The Cytostretch, a conventional SMEA platform as developed by the TU Delft and Philips [29]. a) A SEM image of the Cytostretch chip from the back b) Inset depicts the area highlighted in (a) showing the transversal micro-grooves, the exposed TiN electrodes and parylene insulation of the metal tracks.[29]

Currently, SMEAs are usually fabricated directly on PDMS. Additionally, they use stretchable conducting materials for the electrical interconnects that are not compatible with standard microfabrication techniques [42]. Although, it is possible to fabricate stretchable interconnects by using other conductive materials such as liquid metal alloys and conductive particle doped elastomers, these materials are not suited for standard microfabrication processing technology [39]. It is also possible to design the interconnects in serpentine patterns which can accommodate the strain exerted during membrane stretching and bending. However, they are limited by the fact that they occupy a large surface area on the die and can result in degrading of the surface topography of the device. Since interconnects should minimally alter the surface property of the device, this is not particularly desirable in SMEA fabrication. Additionally, the fatigue lifetime of the interconnects is reduced after repeated bending and stretching of the membrane [39] Thus it would be beneficial to find a way to integrate electrodes into the stretchable membranes in OOCS without altering the main topography of the device as much.

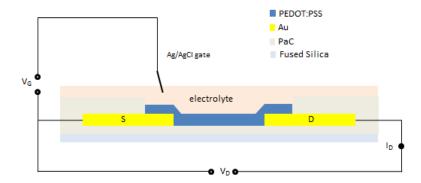

### 2.1.2. Organic Electrochemical Transistor

Interest in organic materials and particularly their potential for low-cost fabrication over large areas led to the development of a new type of sensing device design. A particular organic transistor configuration that is of special interest in the context of Organ-on-Chip platforms is the organic electrochemical transistor (OECT). Originally developed by White *et al.* in the 1980s [43], OECTs are planar devices consisting of three electrodes. The source and the drain are connected by a conductive polymer which acts as the channel. The channel and the gate electrode are further separated by an electrolyte which acts as the gate dielectric. The organic semiconductor film is in contact with an electrolyte, in which the gate is immersed. Refer Fig. 2.2.

Figure 2.2: A schematic cross-section of a conventional OECT with PEDOT:PSS conductive channel.

The OECT mainly relies on ions that are injected from the electrolyte into the organic film, thereby changing its doping state and hence its conductivity. The operation is controlled by the voltages applied to the gate  $(V_G)$  and to the drain  $(V_D)$ , which are in turn referenced by the source electrode.

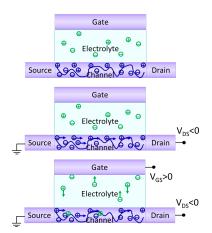

Figure 2.3: The functioning of an OECT explained schematically [44]. Without any biasing applied between the drain and the source, there is no current flow in the channel. When the drain to source voltage is negative, the polymer channel begins to conduct. As the gate to source voltage is positively biased, ion penetration begins from the electrolyte into the conductive PEDOT:PSS channel.

The functioning of the OECT can be explained by the way charge modifications occur in the conductive polymer channel as shown in Fig. 2.3. A commonly used polymer for

this purpose is poly(3,4-ethylenedioxy-thiophene):poly(styrene sulfonate) (PEDOT:PSS), a polythiophene derivative. This polymer has the property of becoming a p-type semiconductor when doped with PSS. In its pristine state PEDOT:PSS is partially doped. When a negative potential is applied to the drain with respect to source, ionic charge variations occur in the conducting polymer channel and current flow is established. Keeping the gate positively biased, the polymer channel is penetrated by ions arising from the electrolyte. This neutralizes the PSS charge in the PEDOT:PSS and semiconductor de-doping occurs according to the chemical reaction:

$$PEDOT^{-}:PSS^{-} + M^{-} + e^{-} <=> PEDOT^{-}:PSS^{0} + M^{+}:PSS^{-}$$

Thus, the gate potential modulates the electrochemical de-doping of the semiconductor.

#### ION SELECTIVE OECT

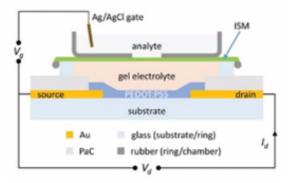

The importance of detecting specific ions has prompted the development of ion-selective organic electrochemical transistor sensors (IS-OECT). The first development in this front was reported by Sessolo *et al.* [45] and then by another team independently worked on the coupling of such OECTs with polymeric membranes that permits the passage of specific ions [46]. Fig. 2.4 shows the schematic of one such IS-OECT.

Figure 2.4: Cross section schematic of an IS-OECT. A reference electrode can be seen dipped in the analyte solution of interest. And ion-selective membrane separates the gel electrolyte from the analyte being studied.

A polyvinylchloride based potassium-selective membrane was chosen to be placed between a gel-electrolyte and the analyte of interest, separating the channel from the OECT gate. It was observed, that by increasing the concentration of the analyte there was an increase in the drain current which was proportional to the ionic concentration of the potassium  $(K^+)$  ions. This was, in turn, attributed to the increase in the number of  $K^+$  ions penetrating the channel and de-doping it, or even to the decrease of the electrolyte resistance.

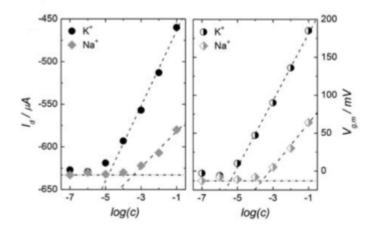

Fig. 2.5 shows the calibration curve of the drain current and the effective membrane voltage versus ion concentration for pure KCl and NaCl solutions. The sensitivity of the membrane to  $K^+$  ions is an order of magnitude higher than that of the  $Na^+$  ions, and hence confirms the ion-selectivity of the membrane in question.

Figure 2.5: Calibration curves ( $I_d$ ,  $V_{gm}$ , vs. concentration) of pure KCl and NaCl solutions performed using ion selective OECT (IS-OECT) [46].

#### THE ORGANIC TFT

OECT configurations allow for the addressing of a wide variety of novel applications of biosensors ranging from in-vitro to in-vivo cell biology. They also qualitatively address the unsolved problems of mechanical adaptability. OECTs, however, branch out to a broader transistor type, called Organic Thin Film Transistors (OTFTs). OTFTs have not yet comprehensively been developed for the purposes of OOC. This could essentially be due to two important reasons: 1) they usually need to be operated at relatively high voltages (usually tens of volts); 2) the charge carrier mobility in organic semiconductors is orders of magnitude smaller than what generally is measured in their standard inorganic counterparts, putting a serious limit on the frequency range of the electrical signals that might be applied as input to the organic amplifiers [37]. They have, by-far, been based on conjugated polymers, oligomers, or other molecules that have been envisioned as a viable alternative to more traditional, mainstream thin-film transistors (TFTs) based on inorganic materials.

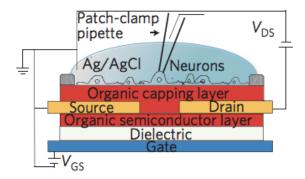

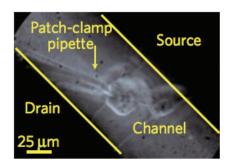

Recently Benfenati V. et. al [38], were successful in fabricating an organic transistor to record the bidirectional stimulation of neurons, as shown in Fig. 2.6. However the organic transistor employed in the experiments is always operated in the off-state and thus, cannot be described as an actual amplifying transducer for cell activity. A SEM image of the active channel of the device has been shown in Fig. 2.7. Also, device fabrication of OTFTs necessitates the use of organic materials and polymers. Working with polymers, fabrication processes with several complex steps are necessary in order to process/fabricate an OTFT of the simplest nature.

Due to the relative low mobility of the organic semiconductor layers, OTFTs cannot rival the performance of field-effect transistors based on single-crystalline inorganic semiconductors, such as Si and Ge, which have charge carrier mobilities about three orders of magnitudes higher.

Most of the new techniques for detection of molecular charges share the advantage of a direct electronic readout and label-free detection [45]. Their fabrication can be carried out using relatively low-cost techniques. They also offer high current modulation and have

Figure 2.6: A schematic of the device fabricated by Benfenati et al. [38] for extracellular recording.

Figure 2.7: SEM image of the active channel of the device fabricated by Benfenati et al. [38].

higher SNR and lower detection limit, thereby achieving higher sensitivity and higher amplification of response [47]. Several OECTs have been developed with high stability in aqueous medium [48] [49]. Further they can also be used to locally amplify the signal even at very low voltages.

### 2.1.3. ION-SENSING FIELD EFFECT TRANSISTOR

Ionic species in the device incorporated during manufacturing of insulated gate field effect transistors (IGFET) introduce variations in the threshold voltage. The concept introduced by P. Bergveld in 1970 was that of a novel Ion-Sensing Field Effect Transistor [50]. It was based on the idea of measuring the activity of an ionic species in an aqueous solution to which the gate insulator is directly exposed. It is a potentiometric device and is very often, conventionally referred to as a pH sensor. They also have the advantage of being solid-scale micro devices with characteristic short response time and are produced using established electronics manufacturing.

### EXTENDED GATE ISFET

Starting from the 1980s, a sensitive film could be incorporated on top of the floating gate giving rise to an extended gate Field-Effect transistor [51]. This type of technology can be well applied in the context of ion sensors applicable in Organ-on-Chip platforms as extended gate ion-sensing FETs (EG-ISFET). The EG-ISFET can be seen as a special type of MOSFET, with the gate electrode extended at a certain distance from the channel. When a positive voltage is applied to the common gate with respect to the source of n-channel MOSFET, electrons (which are the minority carrier in the substrate) are attracted to the surface and create a conducting channel between the source and the drain. The conduc-

tivity of this channel can thus be modulated by the strength of the electric field that exists in the gate insulator between the poly-gate electrode and the silicon.

Ishige et. al., developed another extended gate ISFET based enzyme sensor that was capable of detecting and measuring changes in the redox potential derived from enzyme-catalyst reaction [52]. However, this sensor was not able to detect changes in pH or ionic concentrations in the cell medium. Thus, it is likely that the changes in potential are caused due to the enzyme-catalyzed reaction and not the variation of ionic charge concentration under the gate extension of the FET sensor. More recently, in order to improve the performance of general ISFETs, another type of ISFET, the so-called region ISFET (RISFET), has been proposed by Risveden *et al.* [53]. The most interesting feature of the RISFET is that it has a specific region on the device that is lined with sensing electrodes. This area is where the ionic reactions from the electrolyte occur and result in changes in the threshold voltage of the RISFET.

### 2.2. CHALLENGE OF THE REFERENCE ELECTRODE BASED DESIGN

Ion sensors offer several advantages that are beneficial for their integration in OOC devices. At the same time, however, most of them also do share one major drawback which limits their performance and present some challenges in fabrication. This is essentially the need for reference electrodes. These electrodes are needed to set the voltage drop between the solution containing the molecules and the substrate and are most commonly shared by all sensors on the chip. This also sets the operating point of the transistor. The integration of these reference electrodes should largely be determined by their ease of fabrication. This is done either using standard CMOS processes or a combination of standard CMOS process coupled with organic materials and various different polymers. However, the electrodes are usually fabricated with Ag/AgCl, which cannot be easily integrated into a standard CMOS process thus preventing the realization of extremely low-cost, disposable devices. Further these electrodes, when dipped into the culture medium for a long time, result in continuous dissolution of the AgCl layer into the solution causing slow degradation of the electrode potential over time [54]. This can change the potential being read from the electrolyte, as the ionic activity of the solution will also change. Also, applying biasing voltage to the cell culture can affect the cell or lipid bilayer integrity over an extended period of biasing.

### 2.3. THE CHARGE-MODULATED FGFET BASED DESIGN

Since the OECTs usually also encompass the use of several polymer layers, it also poses a challenge to ease of fabrication. Hence, an easy-to-implement design is necessary in the case of such an ion sensor, that can easily be integrated in standard CMOS processing. Keeping these criteria in mind, the design for a Charge-Modulated Floating-Gate Field-Effect-Transistor or Charge-modulated FGFET has been proposed. This device eliminates the use of a reference electrode, by biasing the transistor by means of a floating capacitor. The sensing area delimits the rest of the device from the electrolyte and is flanked by the gate extensions on all sides, only which remain in contact with the ions.

A detailed study of the design, modeling, fabrication and characterization of the device is presented in the following chapters.

## DESIGN OF THE CHARGE-MODULATED FGFET

As discussed in chapter 2, the model of an FG-ISFET was selected for developing the ion sensor. A solid-state device has been proposed that is capable of detecting change in current from changes in the surface charge density in the active sensing area due to the presence of ions without the means of a biasing electrode. It allows direct detection of small changes in ionic activity with no need for complex, additional process steps and can completely be integrated into a CMOS and inexpensive process.

### 3.1. CONCEPT

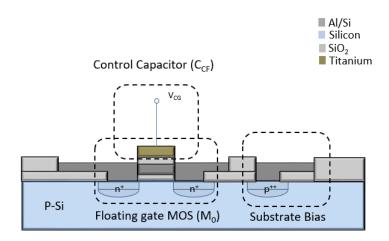

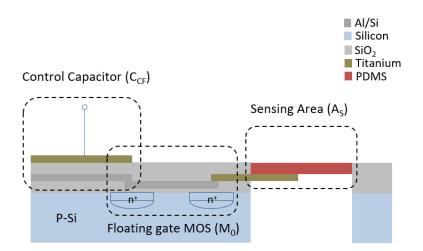

The device structure proposed is based on an evolution of the floating-gate MOS transistor device developed by Barbaro *et al.* [55]. A cross section of the proposed transistor is shown in Fig. 3.1 The structure is composed of a floating gate transistor ( $M_0$ ), a control gate that acts as a reference electrode ( $V_{CG}$ ) and an active sensing area operated by charge induction ( $A_S$ ), which is located behind the cross-sectional schematic where the floating gate electrode is extended and suspended on the free-standing PDMS membrane. This is more clearly illustrated in Fig. 3.2.

Figure 3.1: Cross-sectional schematic of the proposed Charge-modulated FGFET device.

The sensing area can be reached via a standard opening in the  $SiO_2$  passivation layer. The gate extensions on the free-standing PDMS membrane are bound by a glass ring containing the cell culture.

Figure 3.2: a) Simplified 3D diagram of the proposed Charge-modulated FGFET. Here, the sensing area with the PDMS membrane can be seen more clearly. b) Experimental setup view

### 3.2. WORKING PRINCIPLE

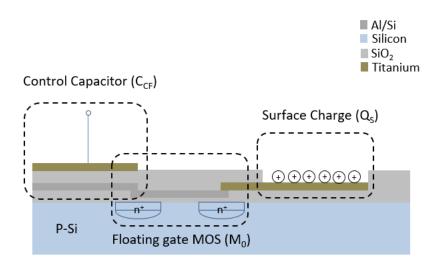

The sensing principle of the device is based on the changes in threshold voltage  $(V_{TH})$  introduced due to changes in ionic charge concentrations occurring in close proximity of the sensing area. A schematic of the working of this Charge-modulated FGFET has been shown in Fig. 3.3. This change in the  $V_{TH}$  of the MOS transistor causes a modulation of the charge carrier density inside the channel. Consequentially a variation in the output current  $I_D$  is expected. Thus the control capacitor and the active area together determine the actual voltage difference  $V_{FG}$  between the floating gate and silicon bulk so they determine the drain current of the MOSFET transistor. The final voltage is determined by the superposition of each source.

The need for a reference electrode is eliminated since the capacity to turn-on the FET is regulated by the presence of an integrated control electrode capacitively coupled to the floating-gate of the MOS transistor. This essentially sets the working point of the transistor. Hence, the detection mechanism is triggered by the differences in the effective threshold voltage. and not by absolute values.

Figure 3.3: Working Principle.

The active area plays a very key role in this design. Without the active sensing area, the device structure could simply be called a conventional floating gate transistor. The device basically behaves as governed by the electrostatic laws of induction. The surface charge  $Q_S$ that is bound within the sensing area creates an electric field, thereby causing a separation of charges in the silicon layer. This results in a charge  $Q_i$  being induced on the top surface of the floating gate. Now according to the principle of conservation of charge, the total charge appearing in the actual gate should remain constant. This generates another layer of charges of the opposite nature  $-Q_i$  to appear on the bottom surface as well. This results in significant charge mobility underneath the active sensing area. The carriers are either attracted or repelled. This causes an electric field to be generated and thus results a voltage drop  $(V_{FG})$  between the bulk of the substrate and the floating gate. Hence the device may be activated depending on the voltage  $V_{FG}$  and thus produce a drain current. It should be noted here that since the bulk is p-type and the surface bound charge  $Q_S$  is positive, the transistor device would be turned-on as the voltage drop  $V_{FG}$  is positive. Thus considering the application and effect of the control capacitor, it is possible to model the device as a conventional MOS transistor with a threshold voltage that is adapted to this design.

#### 3.3. Mathematical Modeling

The mathematical modeling for the Charge-modulated FGFET has been designed based on a previous study undertaken by Barbaro *et al.* [55]. In this device, the floating gate voltage  $(V_{FG})$  w.r.t the silicon body, is basically set by two major functionings. As the charge

| Parameter           | Meaning                                                | Units |

|---------------------|--------------------------------------------------------|-------|

| $\overline{V_{FG}}$ | Voltage between silicon substrate and floating gate    | V     |

| $V_{CG}$            | Control voltage of the capacitor                       | V     |

| $V_{TH}$            | Threshold voltage                                      | V     |

| $V_{THF}$           | Effective threshold voltage                            | V     |

| $C_{CF}$            | Capacitance of the control capacitor                   | F     |

| $C_{FB}$            | Capacitance between the floating gate and silicon body | F     |

| $Q_S$               | Surface charge in sensing area                         | C     |

| $Q_i$               | Induced charge on silicon due to $Q_S$                 | С     |

| $Q_{F0}$            | Trapped electric charge in the floating gate           | C     |