# **Energy-Efficient Capacitive- Sensor Interfaces**

# **Energy-Efficient Capacitive- Sensor Interfaces**

#### Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.dr.ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties,

> in het openbaar te verdedigen op dinsdag 11 juni 2013 om 12:30 uur

> > door

# **Zhichao TAN**

Master of Engineering Peking University, Beijing, China

geboren te Shaanxi, P. R. China

Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. ir. G. C. M. Meijer

Copromotor:

Dr. ir. M. A. P. Pertijs

Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof. dr. ir. G. C. M. Meijer, Technische Universiteit Delft, promotor

Dr. ir. M. A. P. Pertijs, Technische Universiteit Delft, copromotor

Prof. dr. K. A. A. Makinwa, Technische Universiteit Delft

Prof. dr. W. M. C. Sansen, Katholieke Universiteit Leuven

Prof. ir. A. J. M. van Tuijl, Uinversiteit Twente

Prof. dr. ir. A. H. M. van Roermund, Technische Universiteit Eindhoven

Dr. Y. Chae, Yonsei University

Prof. dr. P. J. French, Technische Universiteit Delft, reservelid

Printed by Ipskamp Drukkers B.V., Enschede

ISBN: 978-94-6186-165-8

Copyright © 2013 by Zhichao Tan

Cover Design: Amber Jiawen

All rights reserved. No part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of the author.

Printed in the Netherlands

To my beloved parents 致我亲爱的父母亲

# Table of Contents

| 1. Introduction                                                 | 1    |

|-----------------------------------------------------------------|------|

| 1.1 Motivation                                                  | 1    |

| 1.2 Background and Challenges                                   | 3    |

| 1.3 Organization of the Thesis                                  | 5    |

| 1.4 References                                                  | 6    |

| 2. Energy-Efficient Capacitive-Sensor Interfaces: An Overview   | 8    |

| 2.1 Introduction                                                | 8    |

| 2.2 Capacitive Sensing Elements                                 | 9    |

| 2.2.1 Classification of Capacitive Sensing Elements             | 9    |

| 2.2.2 Modeling of Capacitive Sensor Elements                    | 9    |

| 2.3 Capacitive-Sensor Interfacing Approaches                    | . 11 |

| 2.3.1 Capacitive-Sensor Interfaces Using Period Modulation      | . 12 |

| 2.3.2 Capacitive-Sensor Interfaces Using Delta-Sigma Modulation | . 13 |

| 2.4 Energy-Efficient System-Level Techniques                    | . 14 |

| 2.4.1 Charge Balancing.                                         | . 14 |

| 2.4.2 Auto-Calibration                                          | . 15 |

| 2.4.3 Baseline Compensation and Zooming                         | . 17 |

| 2.4.4 System-Level Chopping Technique                           | . 20 |

| 2.5 Circuit-Level Considerations                                | . 21 |

| 2.5.1 Analysis of Current Consumption                           | . 21 |

| 2.5.2 Conventional OTA Topologies                               | . 24 |

| 2.5.3 Inverter-Based OTA                                        | . 25 |

| 2.6 Conclusions                                                 | . 26 |

| 2.7 References                                                  | . 27 |

| 3. Energy-Efficient Capacitive-Sensor Interface                 |      |

| using Period Modulation                                         | . 30 |

| 3.1 Introduction                                                | . 30 |

| 3.2 Operating Principle                                         | . 31 |

|    | 3.2.1 Capacitance-to-Time Conversion                       | . 31 |

|----|------------------------------------------------------------|------|

|    | 3.2.2 Chopping                                             | . 34 |

|    | 3.2.3 Auto-Calibration                                     | . 34 |

|    | 3.3 Output Swing Reduction                                 | . 36 |

|    | 3.3.1 Period Modulator with Negative Feedback              | . 36 |

|    | 3.3.2 Design Trade-offs                                    | . 38 |

|    | 3.4 Circuit Implementation                                 | . 40 |

|    | 3.5 Measurement Results                                    | . 42 |

|    | 3.5.1 Measurements Results of the Changing Input Capacitor | . 42 |

|    | 3.5.2 Measurements Results of Changing Parasitic Capacitor | . 45 |

|    | 3.5.3 Measurements Results of Linearity and PSRR           | . 46 |

|    | 3.6 Conclusion                                             | . 47 |

|    | 3.7 References                                             | . 47 |

| 4. | . Energy-Efficient Capacitive-Sensor Interfaces            |      |

| u  | sing Delta-Sigma Modulation                                | . 50 |

|    | 4.1 Introduction                                           | . 50 |

|    | 4.2 System Background                                      | . 51 |

|    | 4.2.1 RFID Application Introduction                        | . 51 |

|    | 4.2.2 Capacitive Humidity-Sensing Elements                 | . 52 |

|    | 4.3 Energy-Efficient Capacitive-Sensor Interface           | . 55 |

|    | 4.4 Energy-Efficient Capacitive Humidity Sensor I          | . 61 |

|    | 4.4.1 Circuit Implementation                               | . 61 |

|    | 4.4.2 Measurement Results                                  | . 62 |

|    | 4.5 Energy-Efficient Capacitve Humidity Sensor II          | . 65 |

|    | 4.5.1 Circuit Implementation                               | . 65 |

|    | 4.5.2 Measurement Results                                  | . 69 |

|    | 4.6 Conclusions                                            | . 73 |

|    | 4.7 References                                             | . 74 |

| 5. | . Conclusions                                              | . 76 |

|    | 5.1 Benchmark                                              | . 76 |

|    | 5.1.1 Capacitive-Sensor Interfaces                         | . 76 |

| 5.1.2 Humidity Sensors     | 78 |

|----------------------------|----|

| 5.2 Main Findings          | 79 |

| 5.3 Original Contributions | 80 |

| 5.4 References             | 81 |

| Summary                    | 84 |

| Samenvatting               | 88 |

| List of Publications       | 92 |

| Acknowledgements           | 95 |

| About the Author           | 99 |

# Chapter 1

# Introduction

This thesis describes the theory, design and realization of energy-efficient capacitive-sensor interfaces that are dedicated to energy-constrained applications [1,2]. The goal of this work is to explore energy-efficient capacitive-sensor interface design techniques both at the system and the circuit level.

In this chapter, the motivation and objectives of this work are described, and an overview of the prior art is given. At the end of this chapter, the highlights and structure of the thesis are presented.

#### 1.1 Motivation

Capacitive sensors are based on the modulation of electrical capacitance by a physical or chemical parameter of interest. This principle is widely used, for instance, in pressure sensors, liquid-level gauges, accelerometers and humidity sensors [1]. Merging a capacitive sensing element, an analog interface circuit, an analog-to-digital converter and a bus interface into one single chip results in a smart capacitive sensor [1]. This type of sensor is widely used in emerging sensing applications, such as battery-powered implant devices in medical care applications or wireless environmental monitoring applications [2]. In these types of applications, the energy consumption of the smart capacitive sensor has increasingly become a more limiting factor, because the systems usually only contain a low volume

battery or rely on energy harvesting, restricting the energy available for sensors.

A good example of a high-volume application that requires energy-efficient smart sensors is the monitoring of perishable food products, in which the use of RFID technology enables wireless measurement of key parameters such as temperature, humidity, and CO<sub>2</sub> concentration at various stages in the supply chain [2,3]. The information thus obtained enables a better prediction of shelf life and a significant reduction in the waste caused by spoilage [2,3]. Such a solution, however, is only economically viable if the tags can be produced in large volumes at very low cost. This calls for the use of both CMOS-compatible sensors that can be co-integrated with RFID circuitry, and low-cost printed batteries, or even no batteries at all (passive RFID). The availability of energy-efficient sensors is a key requirement for the realization of such an application.

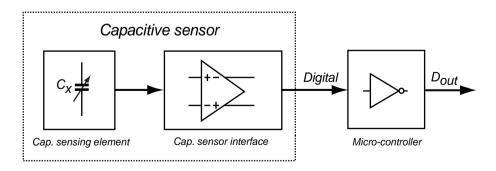

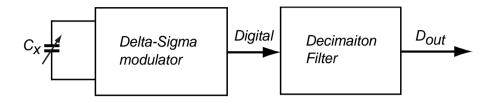

A capacitive sensor usually includes a sensing element and an interface circuit which converts capacitance values into the digital domain. Thus, a modern capacitive-sensor interface usually refers to a capacitance-to-digital-converter (CDC), which is illustrated in Fig. 1. Since capacitive sensing elements do not consume static power, they are very suitable for use in low-power and energy-constrained applications. However, the energy consumption of this interface circuit typically dominates the overall energy consumption of the capacitive sensor. Hence, for such applications, an energy-efficient capacitive-sensor interface is an essential building block.

Figure 1.1: System diagram of a typical capacitive-sensor system.

This thesis will focus on interface circuits for capacitive sensor that are tailored for applications that require a high resolution (> 10bits). Several new techniques to improve the energy efficiency of capacitive-sensor interfaces will be introduced. Three prototypes based on both delta-sigma modulation and period modulation will be presented to demonstrate the effectiveness of these techniques. These prototypes achieve the highest energy efficiency reported to date for these types of interfaces.

## 1.2 Background and Challenges

When quantifying and comparing the energy efficiency of different capacitive-sensor interfaces, it is important to take into account that energy consumption can typically be traded for performance metrics such as resolution, accuracy and speed. Different applications may require different levels of performance, and hence a direct comparison of the energy consumed by capacitive-sensor interfaces designed for different applications makes no sense. To enable a quantitative comparison of different designs, one option is to normalize the energy consumption in relation to the performance using a so-called figure-of-merit (FoM), which takes the energy performance trade-offs into account.

In this work, a FoM is adopted that is similar to the Walden FoM often used for comparing the efficiency of general-purpose analog-to-digital converters (ADCs) [4]. This approach makes sense, since many capacitive-sensor interfaces are structurally very similar to ADCs. This FoM relates the energy consumption per measurement ( $E_{meas}$ ) to the interface's effective number of bits (ENOB):

$$FoM = \frac{E_{meas}}{2^{ENOB}} (1-1)$$

This FoM normalizes the energy consumption by dividing energy consumption by the effective number of conversion steps. The ENOB is defined as:

$$ENOB = \frac{SNR_{dB} - 1.76}{6.02} , \qquad (1-2)$$

which expresses the signal-to-noise ratio (SNR) in terms of the SNR of an ideal ADC with a output length of the ENOB bits. The SNR, in units of dB, is defined in the following equation:

$$SNR_{dB} = 20\log_{10}(\frac{C_{range}}{C_{resolution}}) \qquad , \tag{1-3}$$

in which  $C_{\text{range}}$  is the input range of the capacitive-sensor interface and  $C_{\text{resolution}}$  is capacitance resolution of the interface.

TABLE I. PRIOR ART OF ENERGY-EFFICIENT OR LOW-POWER CAPACITIVE-SENSOR INTERFACES.

|     | Туре | Tech.  | Supply voltage | Current cons. | Meas.<br>time | Capacitance range | ENOB   | FoM        |

|-----|------|--------|----------------|---------------|---------------|-------------------|--------|------------|

| [5] | SAR  | 0.18µm | 1.4V           | 169μΑ         | 3.8µs         | 3pF               | 6.8bit | 7.9pJ/step |

| [6] | PM   | 0.7µm  | 5V             | 1mA           | 1s            | 5.8pF             | 20bit  | 4.7nJ/step |

| [7] | PWM  | 0.32µm | 3V             | 28μΑ          | 33µs          | 0.5pF~0.76pF      | 8bits  | 10pJ/step  |

| [8] | ΔΣ   | 0.35µm | 1.8V           | 460μΑ         | 0.025ms       | n.a.              | 10bit  | 17pJ/step  |

Table I gives a survey of the prior art capacitive-sensor interfaces up to the year of 2008 when this thesis work started. The interfaces are based on four commonly used architectures: successive approximation register [5], period modulation [6], pulse-width modulation [7], and delta-sigma modulation [8]. These interfaces achieve at best a FoM of 10pJ/step. State-of-the-art voltage-input ADCs, in contrast, achieve a FoM well below 5fJ/step [9], with average designs reaching well below 1 pJ/step. This shows that capacitive-sensor interfaces, in spite of their similarity to ADCs, are at least one order of magnitude less energy efficient.

One practical reason for the efficiency gap between general-purpose ADCs and capacitive-sensor interfaces is that capacitive sensors are associated with a certain parasitic capacitance  $C_p$  which also needs to be charged and discharged during readout, even though the parasitic capacitor does not contribute any signal. Moreover, for many practical capacitive sensors, only a relatively small variation  $\Delta C_x$  on a much larger baseline capacitance  $C_x$  carries information about the measurand, which also decreases the achievable signal-to-noise ratio [10]. An analysis of these effects will be presented in Chapter 2. However, even when taking these effects into account, a gap remains, indicating that there is room for improvement. In the rest of this thesis, system and circuit design techniques for improving the energy efficiency of the capacitive-sensor interface will be presented, and prototype designs will be presented to verify the effectiveness of the proposed approaches.

# 1.3 Organization of the Thesis

The remainder of this thesis has been divided into four chapters.

Chapter 2 gives an overview of energy-efficient capacitive-sensor interfaces. It begins by addressing capacitive sensing elements. This is followed by a discussion of the various architectures of capacitive-sensor interfaces. Then, system-level and circuit-level techniques for improving the energy efficiency of capacitive-sensor interface are presented in detail.

Chapter 3 presents energy-efficient capacitive-sensor interfaces based on period modulation. The operation principle of such interfaces is discussed in detail. A prototype is then presented in which the system-level techniques proposed in Chapter 2 are employed to improve energy efficiency by two orders of magnitude compared to prior interfaces based on period modulation.

Chapter 4 presents energy-efficient capacitive-sensor interfaces based on delta-sigma modulation. Two prototypes are described that are tailored for the readout of a capacitive humidity sensor. These prototypes demonstrate the use of both circuit- and system-level techniques. The second prototype

achieves a figure-of-merit of 1.4pJ/step, which is state-of-the-art among all delta-sigma based capacitive-sensor interfaces reported to date.

Chapter 5 concludes the thesis. The benchmark of the proposed designs in this thesis is presented. The original contributions and main findings of this thesis are also highlighted.

#### 1.4 References

- [1] L. K. Baxter, *Capacitive Sensors: Design and Applications*. New York: IEEE Press, 1997.

- [2] G. C. M. Meijer, Smart Sensor Systems. Chichester, UK: Wiley, 2008.

- [3] E. Abad, F. Palacio, M. Nuin, A. González de Zárate, A. Juarros, J.M. Gómez, S. Marco, "RFID smart tag for traceability and cold chain monitoring of foods: Demonstration in an intercontinental fresh fish logistic chain," Journal of Food Engineering, vol. 93, pp. 394-399, Aug. 2009.

- [4] R. H. Walden, "Analog-to-digital converter survey and analysis," *IEEE Journal on Selected Areas in Communications*, vol. 17, pp. 539-550, Apr. 1999.

- [5] K. Tanaka et al., "A 0.026mm<sup>2</sup> capacitance-to-digital converter for biotelemetry applications using a charge redistribution technique," in *Proc. IEEE Asian Solid-State Circuits Conference (A-SSCC)*, Nov. 2007, pp. 244-247.

- [6] A. Heidary and G. C. M. Meijer, "Features and design constraints for an optimized SC front-end circuit for capacitive sensors with a wide dynamic range," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 7, pp. 1609-1616, July 2008.

- [7] P. Bruschi, N. Nizza and M. Dei, "A low-power capacitance to pulse width converter for MEMS interfacing," in *Proc. European Solid-State Circuits Conference (ESSCIRC)*, Sept. 2008, pp. 446-449.

- [8] S. A. Jawed et al., "A 828µW 1.8V 80dB dynamic range readout interface for a MEMS capacitive microphone," in *Proc. European Solid-State Circuits Conference (ESSCIRC)*, Sept. 2008, pp. 442-445.

- [9] M. van Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, E. Klumperlink, B. Nauta, "A 1.9μW 4.4fJ/conversion-step 10b 1MS/s charge-redistribution ADC," in *International Solid-State Circuits Conference Dig. Tech. Papers*, pp. 244-245, 2008.

- [10] M. A. P. Pertijs and Z. Tan, "Energy-efficient capacitive sensor interfaces," in *Analog Circuit Design*, A. Baschirotto, A. H. M. van Roermund and M. Steyaert, Eds. New York: Springer, 2012, pp. 129-147.

# Chapter 2

# Energy-Efficient Capacitive-Sensor Interfaces: An Overview

#### 2.1 Introduction

Capacitive sensors are widely used, for instance, in pressure sensors, liquidlevel gauges, accelerometers and humidity sensors [1]. Since capacitive sensors do not consume static power, they are very suitable for use in lowpower, energy-constrained applications [2]. In such applications, however, the energy consumption of the capacitive sensor will be dominated by that of the interface circuit, which converts capacitance values to the digital domain. Hence, for such applications, an energy-efficient capacitive-sensor interface is an essential building block. This chapter will provide an overview and detailed discussion of the interface circuit, which is dedicated to highresolution and high-accuracy applications, along with the design-based period modulation (Chapter 3) and delta-sigma modulation (Chapter 4).

## 2.2 Capacitive Sensing Elements

### 2.2.1 Classification of Capacitive Sensing Elements

The simple capacitive sensor is a parallel-plate capacitor which comprises two metal plates with area A and distance d. When d is much smaller than the plate dimensions, its capacitance is given by following equation:

$$C = \varepsilon \frac{A}{d} \qquad , \tag{2-1}$$

where  $\varepsilon$  is the dielectric constant of the material between the two electrodes. By modulating one of the three parameters in this equation by a measurand of interest, a capacitive sensor is obtained. Capacitive sensors can thus be classified based on the parameter that is modulated. For modulation of distance (d), the sensor has fixed values for A and  $\varepsilon$ , and the measurand modifies the distance. This type of sensor finds application in displacement sensors, pressure sensors, touch screens, etc. [1]. For modulation of area (A), the sensor has fixed values for  $\varepsilon$  and d, and the measurand modifies the area. This type of sensor finds application in angular detectors [2]. Lastly, for modulation of the dielectric constant  $(\varepsilon)$ , the sensor has fixed values for d and d, and the measurand modifies the dielectric constant. This type of sensor finds application in humidity sensors, gas sensors, DNA sensors, etc. [2].

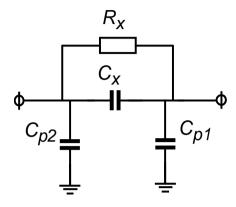

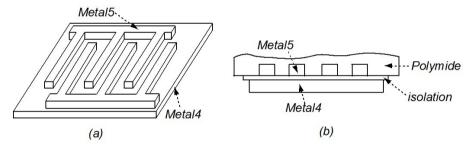

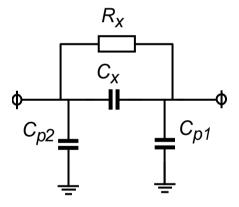

# 2.2.2 Modeling of Capacitive Sensor Elements

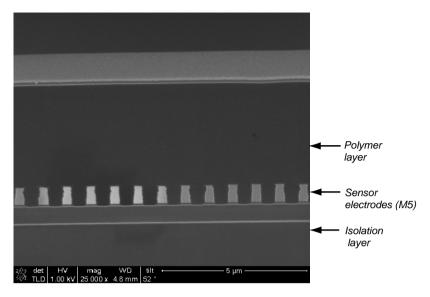

The characteristics of capacitive sensing elements can be quite different from one application to another. To better understand the sensing element, an electrical model is needed. Figure 2.1 shows an example of such a model [3]. Besides the sensing element itself, it also includes a parasitic shunt resistor  $R_x$  and two parasitic capacitors  $C_{p1}$  and  $C_{p2}$  at the two terminals of the sensing element. The parasitic capacitors are particularly important for the energy efficiency of a capacitive-sensor system, as they tend to increase the energy consumption. Minimizing them, e.g. by co-integrating the sensor

and interface circuit on a single chip or in a single package, can be an important way to improve energy efficiency.

Figure 2.1: Electrical model of the capacitive sensing element.

The model should also describe how the measurand modulates  $C_x$ . Often, only a small fraction of  $C_x$  varies. To model this, we define the mean, or baseline, capacitance  $C_0$  and the modulation index  $\alpha$  as [3]:

$$C_0 = \frac{C_{x,\min} + C_{x,\max}}{2}$$

(2-2)

$$\alpha = \frac{C_{x,\text{max}} - C_{x,\text{min}}}{C_0} \qquad , \tag{2-3}$$

where  $C_{x,max}$  and  $C_{x,min}$  are the maximum and minimum capacitance for the range of measurand values of interest. In most applications,  $\alpha$ , which expresses the capacitance variation relative to the baseline value, is only around 0.1. For a given energy per measurement, a lower value of  $\alpha$  tends to lead to a lower signal-to-noise ratio (SNR). Conversely, to obtain a given SNR, more energy is needed for lower values of  $\alpha$ . Hence, this is another important parameter that should be optimized for energy efficiency.

# 2.3 Capacitive-Sensor Interfacing Approaches

The measuring of capacitors involves either measuring the charge displacement associated with a change in the voltage across the capacitor, or measuring voltage resulting from a given amount of charge on the capacitor. The electrical voltage or current signal which charges or discharges the capacitor can be any type of waveform. In most measurement applications the excitation signals have a sinusoidal or a square-wave shape [4].

Capacitive-sensor interfaces employing sinusoidal excitation need to generate a sinusoidal driving voltage or current, which complicates the interface circuit design significantly. Thus achieving the requirements of sine-wave excitation can be rather costly, and the extra sinusoidal-generated blocks make the whole system power hungry [4]. On the other hand, square-wave excitation is usually implemented with switches which can be readily implemented in CMOS technology. Moreover, with fewer driving building blocks, the complexity and power consumption of switched-capacitor (SC) circuits can be lower than the interfacing approach based on sinusoidal input. Therefore, this thesis will only focus on the switched-capacitor technique, which is essentially a square-wave excitation approach.

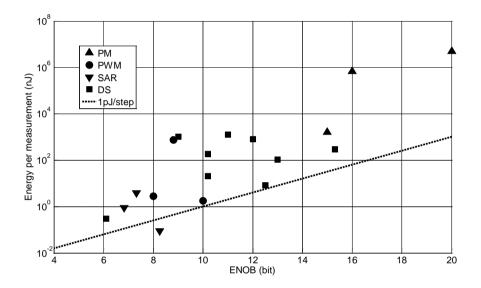

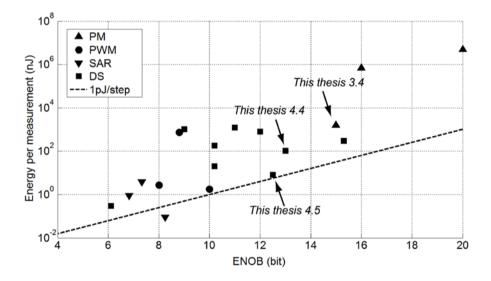

For various types of interfaces, Fig. 2.2 shows a survey of how much energy is used per measurement versus the effective number of bits (ENOB) [5]. This survey includes interfaces based on successive approximation register (SAR), delta-sigma modulation (DS), pulse-width modulation (PWM) and period-modulation (PM). Since many of the capacitive-sensor interfaces included in the survey are structurally very similar to voltage-input ADCs, it is instructive to compare their energy efficiencies. The dotted line is the figure-of-merit (FoM) of 1pJ/step. State-of-the-art voltage-input ADCs achieve FoMs as low as 10fJ/step, with average designs reaching below 1pJ/step. In contrast, most of the capacitive-sensor interfaces included fail to achieve 1pJ/step. This shows that capacitive-sensor interfaces, in spite of their similarity to ADCs, are at least one order of magnitude less energy efficient. Figure 2.2 also clearly shows that the different types of interfaces cover a resolution range from 6 bits to 20 bits. The SAR- and PWM-based designs cover the low end of the resolution range. The delta-sigma-based

designs show high flexibility with the resolution ranging from 6 bits to 16 bits. The period-modulation based designs, on the other hand, can achieve high resolution from 15 bits to 20 bits. Since the focus of this thesis is mainly on high-resolution, high-accuracy applications, the design-based period modulation (Chapter 3) and delta-sigma modulation (Chapter 4) will be discussed in great detail in this thesis.

Figure 2.2: Survey of the energy consumption per measurement for various capacitive-sensor interfaces according to [5].

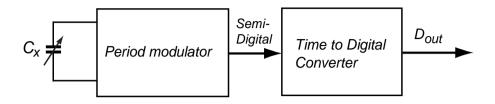

# 2.3.1 Capacitive-Sensor Interfaces Using Period Modulation

Interfaces using period modulation are essentially relaxation oscillators that convert the sensor's capacitance into a period of time which can easily be digitized using a digital counter, e.g. with a microcontroller [2]. An attractive feature of these interfaces is that they are operated asynchronously and thus do not require a clock signal. This can be an important advantage in applications where the interface is located close to the sensor and is connected using a limited number of wires to a remote microcontroller. Figure 2.3 shows a block diagram of an interface circuit based on period modulation. The sensing capacitor  $C_x$  is inserted into a relaxation oscillator.

The changing capacitance changes the length of the oscillator period, which is a measure of  $C_x$  and can be captured by a time-to-digital converter.

Figure 2.3: Interface using time period modulation.

In this type of converter, the period can be digitized by counting its duration in terms of the clock cycles of a faster reference clock. For an *N*-bit resolution requirement, the counter frequency should obey the following equation [4, 6]:

$$f_{clk} \ge 2^N \times f_{out} \qquad , \tag{2-4}$$

where  $f_{out}$  is the output frequency of the period modulator which is inverse to the time interval, and  $f_{clk}$  is the required clock frequency.

*Example 2.1:* If the period time is 100μs and 13-bit resolution is required, then the reference clock frequency should be higher than 80MHz [4].

In Chapter 3, it will be shown that interfaces using period modulation can be very flexible and energy efficient.

# 2.3.2 Capacitive-Sensor Interfaces Using Delta-Sigma Modulation

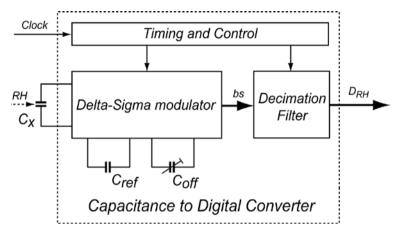

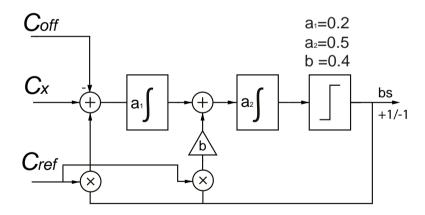

Figure 2.4 shows a block diagram of an interface using delta-sigma modulation. A delta-sigma modulator transfers the sensor capacitance into a bit-stream which is a pure digital signal. The information of interest is modulated into the bit-stream density of the bit-stream, which is demodulated by the decimation filter. Chapter 4 will present capacitive-sensor interfaces using delta-sigma modulation. It will be shown that such

interfaces can achieve high resolution which ranges from 12 bits to 21 bits while achieving a high energy efficiency which can be as low as 1pJ/step. This explains why these interfaces are rather popular nowadays [5].

Figure 2.4: Interface using delta-sigma modulation.

### 2.4 Energy-Efficient System-Level Techniques

In this section, the system-level techniques for improving the energy efficiency of capacitive-sensor interface will be discussed. It will be shown in the rest of the thesis (Chapters 3 and 4) that designs using these techniques can achieve state-of-the-art energy efficiency within their respective categories.

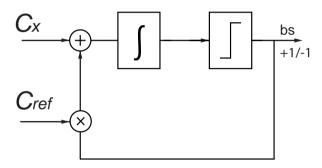

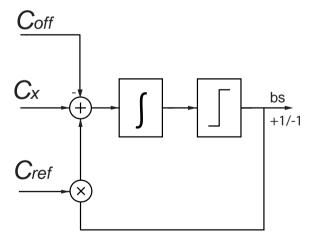

# 2.4.1 Charge Balancing

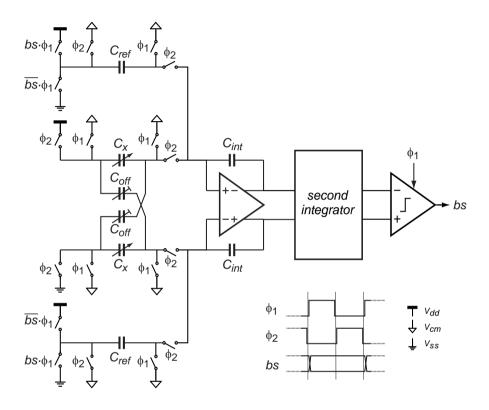

Charge balancing is a technique to integrate the charge of an unknown sensing capacitor together with that of a reference capacitor, so that both charges are in balance with each other. After the subtraction of both charges and integration of the residue, the final averaged charge becomes zero. Figure 2.5 shows the core part of an interface using a delta-sigma modulator with a single-bit quantizer. The sensor capacitance  $C_x$  is embedded as the sampling capacitor of the loop filter. In every clock cycle, a charge proportional to  $C_x$  is integrated in addition to a charge proportional to  $C_{ref}$ , the polarity of which depends on the bit-stream output bs. The negative feedback in the modulator ensures that the former charge is balanced by the latter, resulting in a zero average charge flowing into the loop filter. When the ratio of the number of HIGH bits and the total number of bits (which is the HIGH + LOW bits) amounts to  $\mu$  ( $0 \le \mu \le 1$ ), then the bit-density of the bit-stream becomes:

$$NC_x - \mu NC_{ref} + (1 - \mu)NC_{ref} = 0$$

(2-5)

Solving  $\mu$  gives:

$$\mu = \frac{C_x}{2C_{ref}} + \frac{1}{2} \qquad , \tag{2-6}$$

which is the desired ratiometric function of  $C_x$ . As  $C_{ref}$  is assumed to be constant,  $C_x$  can be precisely expressed by the bit-stream density  $\mu$ , which is accurately generated in the delta-sigma modulator.

Figure 2.5: Charge balancing of first-order delta-sigma modulator.

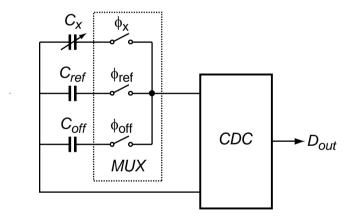

#### 2.4.2 Auto-Calibration

Auto-calibration can be used to reduce the effects of systematic errors and low-frequency noise [4]. Figure 2.6 shows an auto-calibration concept that in principle can be applied to any capacitive-sensor interface [7]. At the input of the interface, a multiplexer is added which selects one of three capacitors: a sensor capacitor  $C_x$ , a reference capacitor  $C_{ref}$ , or an offset capacitor  $C_{off}$ . When no explicit offset capacitor  $C_{off}$  is used, the associated terminals of the multiplexer are left floating. In this case, when  $C_{off}$  is selected, the input capacitance amounts to the sum of the parasitic capacitances and the offset of the capacitive-sensor interface. The capacitive-sensor interface is assumed to provide a digital output  $D_{out}$  which is a linear function of the capacitor  $C_i$  applied to its input:

$$D_{out} = aC_i + b . (2-7)$$

Often the coefficients a and b are poorly defined, e.g. subject to device-todevice variation, long-term drift, power-supply variations, etc. If the multiplexer is employed, so that successively  $(C_x + C_{off})$ ,  $(C_{ref} + C_{off})$  and  $C_{off}$ are digitized, in the final result M, the uncertainty due to a and b can be eliminated by means of the following digital post-processing:

$$M = \frac{D_{out,Cx+Coff} - D_{out,Coff}}{D_{out,Cref} + Coff} - D_{out,Coff}} = \frac{C_x}{C_{ref}}$$

(2-8)

Herewith, it is assumed that the coefficients a and b, although being poorly defined, do not change during the time needed for the three successive conversions. Thus,  $C_x$  is measured ratiometrically with respect to  $C_{ref}$  and differentially with respect to the offset  $C_{off}$ , and a measurement result M is obtained which is independent of a, b and  $C_{off}$ .

Figure 2.6: Capacitive-sensor interface with auto-calibration.

This auto-calibration approach comes at the cost of the extra energy consumed by the conversions of  $C_{off}$  and  $C_{ref}$ . In return, it strongly relaxes the offset- and gain-accuracy requirements of the capacitive-sensor interface. In some cases this can be translated into a significant reduction in energy consumption. In interfaces based on period modulation, for instance, the

propagation delay of the comparator introduces a poorly defined offset error. Without auto-calibration, the error needs to be reduced to a level that fulfills the overall accuracy requirements of the interface. By means of auto-calibration, the error is canceled, so that a slow, but energy-efficient comparator can be used [7].

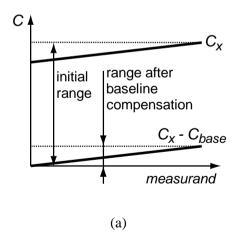

## 2.4.3 Baseline Compensation and Zooming

As addressed in Eqs. (2-2) and (2-3), the response of sensing capacitors to the measurand is often small compared to their baseline value. Directly using an interface-read capacitive sensor will lead to a waste of the dynamic range of the interface, which also has an unnecessarily high oversampling ratio and measurement time. In capacitive-sensor interfaces, employing methods to reduce the oversampling ratio can help to improve energy efficiency. For capacitive-sensor interfaces based on delta-sigma modulation, for example, this can be done by using higher-order loop filters, multi-bit feedback or cascaded architectures [8].

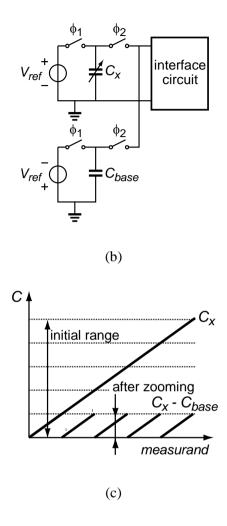

In this section we discuss an alternative approach that is based on preventing baseline or offset capacitance from consuming part of the input-capacitance range of capacitive-sensor interfaces. The same resolution of the sensor system can be maintained while reducing the range of the interface, which leads to a reduction in the required degree of oversampling, and hence, at least in principle, a reduced energy consumption. This concept is illustrated in Fig. 2.7(a).

A straightforward implementation of this approach is shown in Fig. 2.7(b): a compensation capacitor  $C_{base}$  is driven with a voltage of opposite polarity as that of the sensor capacitor, so that the effective charge delivered to the interface is proportional to  $(C_x - C_{base})$ . This approach can be applied both to interfaces based on charge balancing, e.g. delta-sigma capacitive-sensor interfaces [9,10,11] as well as to interfaces based on charge redistribution, e.g. SAR capacitive-sensor interfaces [12]. While this approach relaxes the resolution requirements of the capacitive-sensor interface, it does increase thermal noise because the noise charge sampled on  $C_{base}$  adds to that sampled on  $C_x$ . Moreover, charging and discharging  $C_{base}$  consumes extra

energy. In this sense,  $C_{base}$  plays a similar role to that of the parasitic capacitance  $C_p$ . Nevertheless, it still makes sense to add this capacitor, as long as these drawbacks do not overshadow the energy reduction associated with the lower oversampling ratio.

If the baseline value is an invariable part of the sensor capacitance, a fixed compensation capacitor can be used, or a capacitor that is adjusted once after fabrication [9]. The baseline-compensation concept can also be extended by adjusting the compensation capacitor dynamically to track variations in the sensor capacitance [10,11]. This leads to a two-step conversion process that is sometimes referred to as zooming (Fig. 2.7(c)) [11]. In the first step,  $C_{base}$  is adjusted to approximate  $C_x$ . In the second step,  $(C_x - C_{base})$  is digitized. Depending on how fast  $C_x$  changes, it may not be necessary to repeat the first step for every measurement. Typically, a successive approximation algorithm is used in the first step, while the second step may consist of a SAR conversion or a conversion based on delta-sigma modulation. The resolution requirement of the second step is relaxed by the number of subranges that can be distinguished in the first step.

Figure 2.7: Compensation for baseline capacitance: (a) principle; (b) implementation using a baseline-compensation capacitor; (c) extension to zooming.

In the capacitive-sensor interface based on zooming, the limited linearity of the adjustable compensation capacitor may cause discontinuities in the digital output as the sensor capacitance moves from one sub-range to the next. This problem can be addressed by introducing some overlap between the sub-ranges so that  $C_x$  can be measured in two adjacent sub-ranges when it moves from one sub-range to the next, allowing the discontinuity to be digitally corrected. An alternative is to employ an auto-calibration approach in which the capacitive-sensor interface itself is used to accurately measure

$C_{base}$  [11]. While such an auto-calibration step may be relatively energy-hungry due to the high resolution required, it need not be performed for every measurement, and thus need not dominate the system's energy consumption.

# 2.4.4 System-Level Chopping Technique

Most capacitive-sensor signals are low-frequency signals. Many interfering signals such as offset, 1/f noise, and mains-supply interferences are also located at low frequencies and may therefore corrupt the sensor signal [4]. The chopping technique can separate the sensor signal from the undesired signals mentioned above. The sensor signal is modulated to a higher frequency so that it can be processed without being affected by 1/f noise, offset and supply interference. After processing, the wanted signal can be demodulated back to the baseband.

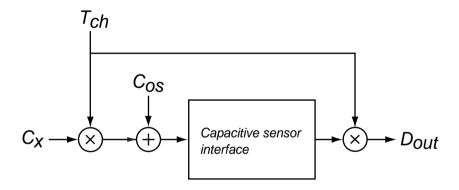

Figure 2.8: System chopping technique.

Figure 2.8 shows how the chopping technique can be applied to a capacitive-sensor interface at the system level. At both the input and output of the interface processing chain, chopper switches have been added which reverse the signal polarity. From this, we can obtain two outputs. Averaging these two outputs will eliminate the effect of  $C_{os}$ .

#### 2.5 Circuit-Level Considerations

The capacitive-sensor interfaces proposed in this thesis are all implemented using switch-capacitor (SC) circuits, since this naturally allows the sensing capacitor to be used as the sampling capacitor of the front-end. The power consumption of a SC implementation is usually dominated by the OTAs used to establish the charge transfer. Therefore, the design of an energy-efficient OTA implementation provides the key for improving the overall energy efficiency of a SC-based interface. In this section, we will discuss some low-power circuit-design techniques which can improve the energy efficiency of capacitive-sensor interfaces.

## 2.5.1 Analysis of Current Consumption

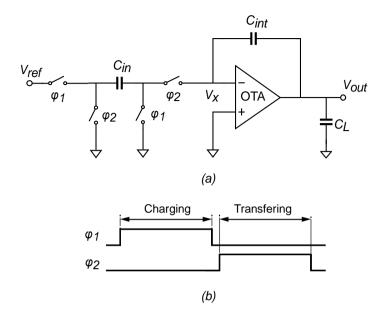

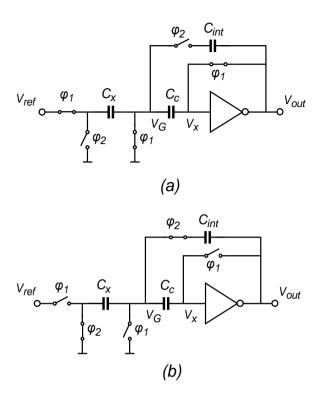

Figure 2.9 shows the circuit model of an integrator that is controlled by a two-phase non-overlapping clock. The input capacitor  $C_{in}$  can represent the sensing capacitor  $C_x$ . During phase  $\varphi_1$ ,  $C_{in}$  is charged to a reference voltage  $V_{ref}$  and during phase  $\varphi_2$ , the resulting charge is transferred to the integration capacitor  $C_{int}$ . This transfer will be typically associated with exponential settling behavior. Figure 2.10(a) shows the circuit model of the settling phase and Fig. 2.10(b) shows a typical waveform at the integrator's output. To ensure accurate settling, the clock period  $\varphi_2$  has to be long enough compared to the time constant of the charge-transfer process.

Figure 2.9: Circuit model of the first integrator in the delta-sigma modulator.

Figure 2.10: Circuit model of the integrator in the settling phase.

If the circuit is a one-pole system, then its transfer function can be described as:

$$H(s) = \frac{V_{out}(s)}{V_{in}(s)} = \frac{G_o}{1 + s\tau}$$

, (2-9)

where the  $G_o$  equals

$$G_o = \frac{1}{\beta + 1/A_o} \approx \frac{1}{\beta} = 1 + \frac{C_{in}}{C_{int}}$$

, (2-10)

in which  $A_o$  is the DC gain of the OTA in the integrator. The time constant  $\tau$  is defined by following equation:

$$\tau = \frac{C_o}{\beta g_m} \qquad , \tag{2-11}$$

where  $g_m$  is the transconductance of the OTA. The capacitance  $C_o$  depends on the implementation of the OTA. For a single-stage OTA,  $C_o$  is

$$C_o = \frac{C_{\text{int}}C_{in}}{C_{\text{int}} + C_{in}} + C_L \qquad , \tag{2-12}$$

where  $C_L$  is load capacitor. To achieve enough accuracy, the settling time has to satisfy the condition:

$$\frac{T_{clk}}{2} \ge (m+1)\tau \ln 2$$

, (2-13)

where m is the target accuracy of the system in bits. Substitution of (2-11) and (2-12) in (2.13) yields:

$$g_m \ge 2 \ln 2 \frac{(m+1)}{T_{clk}} (C_{in} + C_L + \frac{C_{in}C_L}{C_{int}})$$

(2-14)

This condition reveals the minimum transconductance of the OTA used in the integrator for a clock period under certain loading conditions and resolution requirements. For many OTA implementations, the transconductance directly dictates the supply current and hence the energy consumption. We define the current-efficiency factor  $\gamma$  of an OTA implementation as follows:

$$\gamma = \frac{g_m}{I_{tot}} \qquad , \tag{2-15}$$

where  $I_{tot}$  is the total current consumption of the OTA, which directly links with the transconductance requirement. An energy-efficient design starts with minimizing the  $g_m$  requirement for the given specifications based on Eq. (2-14) and then finding the OTA structure that has the highest current-efficiency factor  $\gamma$ . The latter will be addressed in the following section.

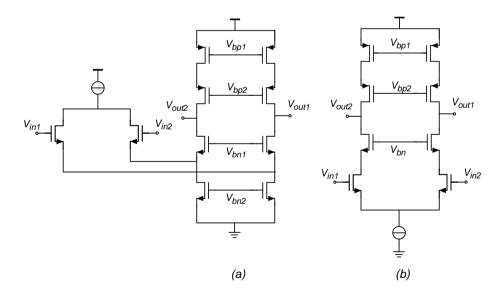

## 2.5.2 Conventional OTA Topologies

This section reviews several OTA topologies and their current-efficiency factor  $\gamma$  (Eq. (2-15)).

Figure 2.11: Two commonly used OTA structures: (a) folded-cascode OTA; (b) telescopic OTA.

The first topology reviewed is the frequently used folded-cascode OTA, which is shown in Fig. 2.11(a). It provides a reasonable output swing and high DC gain, which make this structure quite popular. Assuming that the input transistors as well as the cascode transistors are biased at a current  $I_d$ , the total current consumption is  $4I_d$ . If the associated transconductance equals  $g_{m0}$ , the current-efficiency factor  $\gamma_{FC}$  of this OTA is:

$$\gamma_{FC} = \frac{g_{m0}}{4I_d} \qquad (2-16)$$

The second topology is the telescopic OTA, which is shown in Fig. 2.11(b). With only two currents legs, the total current consumption decreases to  $2I_d$ . As compared to the OTA of Fig 2.11(a), this boosts the current-efficiency factor by a factor of two so that:

$$\gamma_{TE} = \frac{g_{m0}}{2I_d} \qquad (2-17)$$

This improved current efficiency comes at the price of a lower output swing, which is due to the headroom requirement of the tail current at the bottom [13].

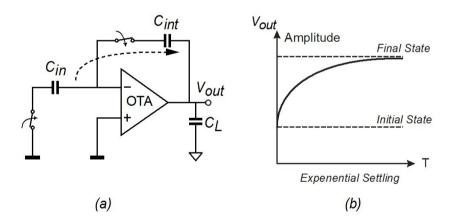

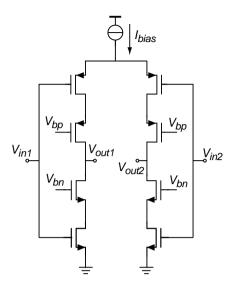

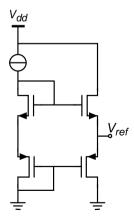

#### 2.5.3 Inverter-Based OTA

An inverter-based SC circuit outperforms the designs based on conventional OTAs in terms of current efficiency since both the PMOS and NMOS transistor of an inverter contribute transconductance while sharing the same supply current [14,15,16]. Figure 2.12 shows a differential version of an inverter-based OTA. If we assume that the PMOS and the NMOS have the same transconductance  $g_{m0}$ , the current-efficiency factor  $\gamma$  of Fig. 2.12 is:

$$\gamma_{INV} = \frac{2g_{m0}}{2I_d} = \frac{g_{m0}}{I_d} \qquad (2-18)$$

Figure 2.12: Inverter used as an OTA.

As a result, the intrinsic current efficiency of an inverter-based OTA is two times higher than that of a telescopic OTA and four times higher than that of a folded-cascode OTA. The inverter-based capacitive-sensor interface will be presented in Chapter 4.

#### 2.6 Conclusions

An overview of energy-efficient capacitive-sensor interfaces has been presented in this chapter. In the case of a simple parallel-plate capacitor, a capacitive sensing element can be realized by making the capacitor's area (A), distance (d) or dielectric constant  $(\varepsilon)$  dependent on a physical or chemical parameter of interest.

This chapter has presented the system-level techniques that can be applied to design energy-efficient capacitive-sensor interfaces. Auto-calibration can be used to reduce the effects of systematic errors and low-frequency noise. Although this technique comes at the cost of an increase in energy consumed by the conversions of  $C_{off}$  and  $C_{ref}$ , in return, it strongly relaxes the offset-and gain-accuracy requirements of the capacitive-sensor interface. In some cases this can be translated into a significant reduction in energy consumption [7]. The baseline-compensation technique can cancel the effect

of unchanged baseline capacitance in order to use the dynamic range of the interface more efficiently, which in some cases may also save energy. The system-level chopping technique can separate the sensor signal from undesired interfering signals by modulating the sensor signal to a higher frequency, so that it can be processed to eliminate the 1/f noise, offset and supply interference.

Several low-power circuit-design techniques for capacitive-sensor interfaces have also been presented in this chapter. Since many capacitive-sensor interfaces are based on a switch-capacitor implementation, the OTA is used to transfer charge from the sensor capacitor to an integration capacitor for further processing. An analysis of the energy consumption of such circuit has been presented and a settling behavior analysis of switch-capacitor circuits revealed the minimum current consumption of the OTA used in the integrator for a clock period under certain loading conditions and resolution requirements. Several OTA structures have been reviewed along with their energy efficiency. It has been concluded that structures with fewer current legs have better energy efficiency. Finally, inverter-based SC circuits have been presented. The inverter-based OTA outperforms designs based on conventional OTAs since both the PMOS and NMOS transistor of an inverter contribute transconductance while sharing the same supply current.

The next chapter will discuss energy-efficient capacitive-sensor interfaces using period modulation.

#### 2.7 References

- [1] L. K. Baxter, *Capacitive Sensors: Design and Applications*. New York: IEEE Press, 1997.

- [2] G. C. M. Meijer, Smart Sensor Systems. Chichester, UK: Wiley, 2008.

- [3] W. Bracke, R. Puers and C. Van Hoof, *Ultra Low Power Capacitive Sensor Interfaces*. Dordrecht, the Netherlands: Springer, 2007.

- [4] A. Heidary, "A low-cost universal integrated interface for capacitive sensors," Ph.D. dissertation, Delft University of Technology, Delft, the Netherlands, 2011.

- [5] M. A. P. Pertijs and Z. Tan, "Energy-efficient capacitive sensor interfaces," in *Analog Circuit Design*, A. Baschirotto, A. H. M. van Roermund and M. Steyaert, Eds. New York: Springer, 2012, pp. 129-147.

- [6] G. C. M. Meijer, "Interface electronics and measurement techniques for smart sensor systems," in *Smart Sensor Systems*, G. C. M. Meijer, Ed. Chichester, UK: Wiley, 2008, pp. 23-54.

- [7] Z. Tan, S. Heidary, G. C. M. Meijer and M. A. P. Pertijs "An energy-efficient 15-bit capacitive-sensor interface based on period modulation," *IEEE Journal of Solid-State Circuits*, pp. 1703-1711, July 2012.

- [8] S. R. Norsworthy, R. Schreier and G. C. Temes, Eds., *Delta-Sigma Data Converters: Theory, Design and Simulation*. Piscataway, NJ: IEEE Press, 1997.

- [9] Z. Tan, R. Daamen, A. Humbert, K. Souri, Y. Chae, Y. V. Ponomarev and M. A. P. Pertijs, "A 1.8V 11μW CMOS smart humidity sensor for RFID sensing applications," in *Proc. A-SSCC*, 2011, pp. 105-108.

- [10] D.-Y. Shin, H. Lee and S. Kim, "A delta-sigma interface circuit for capacitive sensors with an automatically calibrated zero point," *IEEE Trans. Circuits and Systems II*, vol. 58, no. 2, pp. 90-94, Feb. 2011.

- [11] S. Xia, K. A. A. Makinwa and S. Nihtianov, "A capacitance-to-digital converter for displacement sensing with 17b resolution and 20µs conversion time," in *ISSCC Dig. Tech. Papers*, 2012, pp.197-198.

- [12] K. Tanaka et al., "A 0.026mm<sup>2</sup> capacitance-to-digital converter for biotelemetry applications using a charge redistribution technique," in *Proc. A-SSCC*, Nov. 2007, pp. 244-247.

- [13] W. M. C. Sansen, Analog design essentials. The Netherlands: Springer, 2008.

- [14] B. Nauta, "A CMOS transconductance-C filter technique for very high frequencies," *IEEE Journal of Solid-State Circuits*, vol. 27, no. 2, pp. 142-153, Feb. 1992.

- [15] J. H. Huijsing, K. De Langen, R. Hogervorst and R. G. H. Eschauzier, "Low-voltage low-power opamp based amplifiers," *Journal of Analog Integrated Circuits and Signal Processing*, vol. 8, no. 1, pp. 49-67, July 1995.

- [16] Y. Chae and G. Han, "Low voltage, low power, inverter-based switched-capacitor delta-sigma modulator," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 2, pp. 458-472, Feb. 2009.

# Chapter 3

# Energy-Efficient Capacitive-Sensor Interface using Period Modulation

This chapter discusses the system design and circuit implantation of the energy-efficient capacitive-sensor interface using period modulation. After the operating principle is discussed, the system-level techniques for the energy-efficient design are addressed in detail. The system stability requirement and the design trade-offs are also analyzed, followed by the circuit implementation and measurement results.

#### 3.1 Introduction

Interfaces based on period-modulation are essentially relaxation oscillators that convert the sensor's capacitance into a period time, which can then be easily digitized using a digital counter, e.g. in a microcontroller [1,2,3]. An attractive feature of these interfaces is that they are operated asynchronously and thus do not require a clock signal. This can offer an important advantage in applications where the interface is located close to the sensor and is

connected using a limited number of wires to a remote microcontroller. Moreover, period-modulation-based capacitive-sensor interfaces can be quite flexible, in that resolution can be easily traded for measurement time by measuring the duration of multiple output periods using a simple digital divider [4,5]. Furthermore, they can be designed to handle a very large input capacitance range with high resolution [6,7]. However, compared with alternative approaches based on delta-sigma modulation [8-14] or capacitance-to-pulse-duration conversion [15,16], prior period-modulation-based interfaces [5,7] are much less energy-efficient. With supply currents in the mA range, these interfaces are not suitable for use in energy-constrained applications, such as wireless-sensor networks or autonomous sensor systems.

This chapter describes an energy-efficient period-modulation-based capacitive-sensor interface [8]. This interface employs a combination of negative-feedback loops [6,7], time-domain chopping and three-signal auto-calibration techniques [2,3] to enable the use of simple, energy-efficient analog building blocks. It is shown that the energy consumption of the resulting interface is limited by its ability to operate in the presence of parasitic capacitors around the sensor capacitor. While maintaining the ability to handle parasitic capacitors up to five times larger than the sensor capacitance, the proposed interface consumes almost two orders of magnitude less energy than those reported in previous work [5,7].

# 3.2 Operating Principle

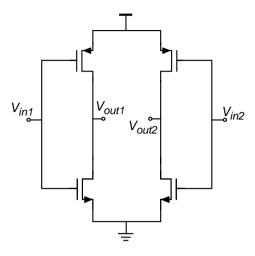

# 3.2.1 Capacitance-to-Time Conversion

Capacitive-sensor interfaces based on period modulation perform a capacitance-to-time conversion [3]. Figure 3.1 illustrates how this conversion is performed in the interface presented in this chapter. During phase  $\varphi_1$  of a two-phase non-overlapping clock, the sensor capacitance  $C_x$  is connected between the supply voltage  $V_{dd}$  and a mid-supply common-mode reference  $V_{cm}$ . During the subsequent phase  $\varphi_2$ , it is connected between  $V_{ss}$  and the virtual ground of an active integrator, which is also biased at  $V_{cm}$ . As a result, a charge  $V_{dd}C_x$  is transferred to the integration capacitor  $C_{int}$ ,

causing the output voltage  $V_{int}$  of the integrator to step up. A constant integration current  $I_{int}$  then removes the charge from  $C_{int}$ , bringing  $V_{int}$  back to its original level. A comparator at the output of the integrator detects when this happens. The time interval  $T_{msm}$  that passes from the start of phase  $\varphi_2$  until  $V_{int}$  crosses the comparator's threshold is then proportional to  $C_x$ :

$$T_{msm} = \frac{V_{dd}}{I_{int}} C_x \qquad (3-1)$$

This time interval can therefore be used as a measure of  $C_x$  and can be digitized by counting its duration in terms of the clock cycles of a faster reference clock. This digitization can be easily performed, for instance, by a counter in a microcontroller.

Figure 3.1: Operating principle of capacitance-to-time conversion: (a) simplified circuit diagram; (b) associated waveforms.

Figure 3.2: Block diagram of a period-modulator-based capacitive-sensor interface.

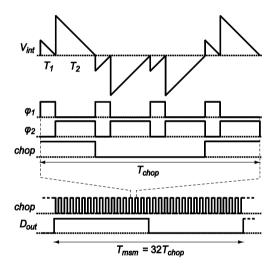

Figure 3.3: Timing diagram of the interface shown in Fig. 3.2.

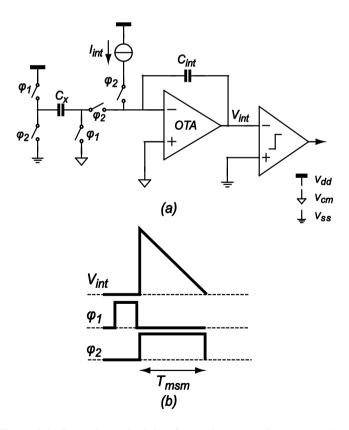

Figure 3.2 shows how this basic principle can be applied in an asynchronously operating relaxation oscillator that self-generates the non-overlapping clock phases  $\varphi_1$  and  $\varphi_2$  [3]. Figure 3.3 shows the associated waveforms. In addition to the clock phases  $\varphi_1$  and  $\varphi_2$ , the interface also self-generates a control signal chop, which will be discussed in more detail shortly. For now, we will assume that CHOP is HIGH. The switched-capacitor branch containing the sensor capacitor  $C_x$  then operates as before, giving rise to an output period  $T_2$  proportional to  $C_x$ . Meanwhile, a small auxiliary capacitor  $C_0$  is charged to the supply voltage. After the threshold

crossing, when phase  $\varphi_1$  is high, the charge on  $C_0$  is then transferred to the integrator capacitor  $C_{int}$  and removed by  $I_{int}$ , giving rise to a short output period  $T_1$  proportional to  $C_0$ . This period, in turn, is used to charge  $C_x$  again, giving rise to a continuous oscillation with a period  $T_1 + T_2$  proportional to  $C_x + C_0$ .

#### 3.2.2 Chopping

To eliminate errors due to the low-frequency noise and offset of the interface circuit, the polarity of the integrated charge is periodically reversed in successive clock cycles under the control of the chop signal. This is done by switching capacitors  $C_x$  and  $C_0$  from  $V_{dd}$  to  $V_{ss}$  when CHOP is HIGH, and switching them from  $V_{ss}$  to  $V_{dd}$  when CHOP is LOW. At the same time, the integration current  $I_{int}$  is switched between sourcing when CHOP is HIGH and sinking when CHOP is LOW, as shown in Fig. 3.2. One chopping cycle  $T_{chop}$  consists of four clock cycles in which the CHOP signal changes state twice. This chopping operation strongly suppresses the effects of the low-frequency noise of the integrator and the comparator, since the associated time errors change polarity in successive clock cycles and thus average out in the duration  $T_{chop}$  of a complete chopping period [2,3]. A complete measurement, in turn, consists of several successive chopping periods. In the present design, a total of 32 chopping periods are used, leading to a measurement-time period  $T_{msm}$  equal to:

$$T_{msm} = 32T_{chop} = 128 \frac{V_{dd}}{I_{int}} (C_x + C_0) = aC_x + b$$

, (3-2)

which is a linear function of  $C_x$ .

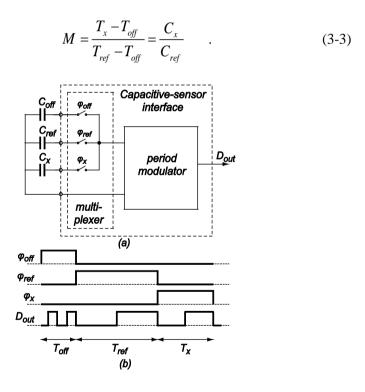

#### 3.2.3 Auto-Calibration

The gain and offset coefficients a and b in Eq. (3-2) are poorly defined, as they are affected by process variability and various circuit non-idealities, such as comparator delay, supply-voltage variations, component tolerances and their temperature dependencies. Therefore, the period time  $T_{msm}$  cannot be readily used to digitize  $C_x$  accurately. An auto-calibration technique is

applied to eliminate the uncertainty due to a and b [3]. As shown in Fig. 3.4, a multiplexer is added to the interface allowing either an offset capacitor  $C_{off}$ , a reference capacitor  $C_{ref}$ , or the sensor capacitor  $C_x$  to be measured. Thus, three consecutive measurements are performed, yielding three period times  $T_{off}$ ,  $T_{ref}$ , and  $T_x$ , respectively. This sequence of three measurements repeats continuously, allowing the three period times to be measured by a digital counter using a single-wire interface. To allow this counter to identify which period is which, the control logic that generates the output signal produces two (short) output periods during time interval  $T_{off}$ , as illustrated in Fig. 3.4 [3]. Thus, it can be distinguished from time periods  $T_{ref}$  and  $T_x$ , during which only a single, typically much longer output period is generated. A digital representation M of  $C_x$ , independent of a and b, can then be obtained by performing the following calculation in digital post-processing:

Figure 3.4: Period-modulation-based interface employing three signal-auto-calibration: (a) circuit diagram; (b) associated timing diagram.

This approach only requires the period modulator to be linear, i.e. the coefficients a and b to be independent of  $C_x$  and stable throughout the autocalibration sequence. Since in M, this auto-calibration technique eliminates the effects of comparator delay, a low-speed energy-efficient comparator can be used, as long as its delay time does not become excessive compared to the clock period.

#### 3.3 Output Swing Reduction

#### 3.3.1 Period Modulator with Negative Feedback

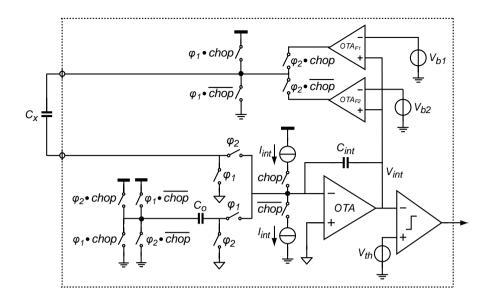

The energy consumption of the interface is dominated by the OTA in the integrator, whose transconductance needs to be large enough to guarantee accurate charge transfer, as addressed in Chapter 2. To obtain this transconductance at a minimum supply current, a current-efficient OTA implementation is required. In this work, a simple cascoded telescopic OTA is used which outperforms the more frequently used folded-cascode OTA in current-efficiency, but at the expense of a smaller output-voltage swing.

In the interface of Fig. 3.2, the voltage swing at the output of the integrator is determined by the voltage step associated with charge transfer from  $C_x$  to  $C_{int}$ . Therefore, to reduce the output swing for a given value of  $C_x$ , a larger integration capacitor can be used. This solution, however, increases the load of the integrator, thus increasing the required transconductance. Moreover, it also increases the die size, in particular when large sensor capacitances need to be handled, since the integration capacitor will have to be larger than the sensor capacitance to keep the output swing within the supply rails.

To reduce the swing at the integrator's output without using a large integration capacitor, we employ negative feedback loops that regulate the charge transfer from  $C_x$  to  $C_{int}$  [7].

Figure 3.5: Block diagram of the period-modulator-based capacitive-sensor interface with negative feedback.

Figure 3.6: Timing diagram of the interface with the negative feedback shown in Fig. 3.5.

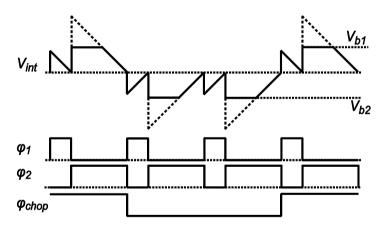

Figure 3.5 1 shows how this has been implemented (omitting the input multiplexer used for auto-calibration for simplicity). The switches that

<sup>1</sup> Initially, this technique was introduced in [6] as a way to extend the dynamic range of the interface circuit. Later on, in [7] the favorable noise properties of this circuit

37

connect  $C_x$  to  $V_{ss}$  and  $V_{dd}$  have been replaced by two feedback OTAs: OTA<sub>F1</sub> and OTA<sub>F2</sub>. Figure 3.6 shows their effect on the waveforms in the modulator. Depending on the chop signal, either  $OTA_{F1}$  or  $OTA_{F2}$  drives  $C_x$ during phase  $\varphi_2$ . We will refer to this OTA as OTA<sub>F</sub>. Initially, the current provided by  $OTA_F$  is larger than  $I_{int}$ , causing the output of the integrator to increase. When the output of the integrator reaches the control voltage  $V_h$ , however, the current provided by  $OTA_F$  becomes equal to  $I_{int}$ , causing the output of the integrator to saturate at  $V_b$ . This situation continues until  $C_x$  is almost fully discharged. Then, the output of the integrator and the current of  $OTA_F$  go down, while  $I_{int}$  continues to remove the remaining charge stored in  $C_{int}$  until the integrator's output reaches the threshold level of the comparator. Since no charge is lost during this whole operation, the final amount of charge which is transferred from  $C_x$  to the integrator is not affected by these feedback loops. Thus, accurate capacitance-to-time conversion is maintained, i.e. Eq. (3-1) still holds. The control voltages  $V_{b1}$ and  $V_{b2}$ , which determine the high and low levels at which the integrator's output saturates, are chosen to fit the limited output swing of the telescopic OTA.

# 3.3.2 Design Trade-offs

The negative feedback loops employed to limit the integrator output swing are not unconditionally stable: the presence of parasitic capacitors from the terminals of the sensing capacitor to ground can give rise to instability [7] or can prevent the interfaces from oscillating, as will be explained below. This leads to a trade-off between power consumption and the ability to handle parasitic capacitances.

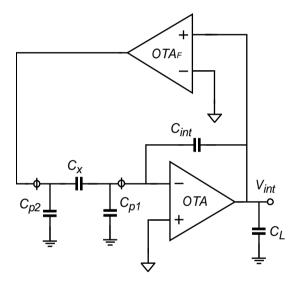

Figure 3.7 shows a simplified representation of the interface connected to a sensor with parasitic capacitors when phase  $\varphi_2$  is HIGH<sup>2</sup>. In practice, the parasitic capacitors  $C_{p1}$  and  $C_{p2}$  can typically be assumed to be constant, while the sensor capacitance  $C_x$  varies across a certain range from  $C_{x,min}$  to

were pointed out. In this thesis it will be shown that this remarkable circuit also has attractive features which lower power consumption.

<sup>&</sup>lt;sup>2</sup> We assume that when  $\varphi$  is HIGH, the corresponding switches are conductive (closed), while when  $\varphi$  is LOW, these switches are non-conductive (opened).

$C_{x,max}$ . When  $C_{p2}$  is significantly larger than  $C_{x,min}$ , a substantial part of the current provided by OTA<sub>F</sub> is absorbed by  $C_{p2}$ . Assuming OTA<sub>F</sub> has a transconductance  $g_{mF}$ , it provides a current  $g_{mF} \cdot (V_b - V_{th})$  at the start of phase  $\varphi_2$ . A fraction  $C_x / (C_x + C_{p2})$  of this current flows into  $C_x$ . To ensure proper operation of the interface, this fraction should be larger than the integration current  $I_{int}$ . Otherwise, insufficient current is available to transfer charge to the integration capacitor, which will stop the oscillation. This leads to the following minimum transconductance requirement for the feedback OTAs:

Figure 3.7: Simplified circuit diagram of the interface during phase  $\varphi_2$ .

$$g_{mF} > \frac{I_{\text{int}} \left( C_{x,min} + C_{p2} \right)}{\left( V_b - V_{th} \right) C_{x,min}} \tag{3-4}$$

This equation shows that to handle parasitic capacitance at the drive side of the sensor capacitor, a larger feedback transconductance is required.

The feedback loop consisting of  $OTA_F$ , the sensor and the integrator is not unconditionally stable: the transconductance  $g_m$  of the integrator's OTA should be large enough to provide enough phase margin. Taking again the

current division between  $C_x$  and  $C_{p2}$  into account, the unity-gain frequency of this loop equals:

$$\omega_0 = \frac{g_{mF} C_x}{C_{int} \left( C_x + C_{p2} \right)} \qquad (3-5)$$

Assuming the load capacitance of the integrator (which is dominated by the input capacitance of the comparator) is negligible compared to  $C_{p1}$ , the loop has a pole at a frequency  $\omega_p$  of  $g_m / C_{p1}$ . To ensure a minimum phase margin of 45°,  $\omega_p$  should be larger than  $\omega_0$ . This leads to a minimum required transconductance  $g_m$  of the integrator OTA:

$$g_m > g_{mF} \frac{C_{p1}C_{x,max}}{C_{int}(C_{x,max} + C_{p2})}$$

(3-6)

where  $C_{x,max}$  has been substituted for  $C_x$  to obtain the worst-case value across the sensor-capacitance range. By combining (3-6) and (3-4), a minimum  $g_m$  can be calculated for which stability is ensured over a given range of sensor capacitances and for given parasitic capacitances. Thus, the current consumption of the OTA can be minimized too.

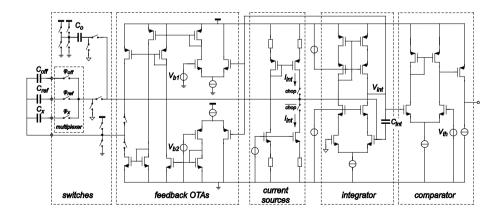

# 3.4 Circuit Implementation

Figure 3.8 shows the complete transistor-level implementation of the interface. Using the approaches discussed in Section 3.2, a fairly compact implementation is obtained. The left part shows the two feedback OTAs, each of which consists of a simple differential pair biased at a tail current of 1  $\mu$ A, and a current mirror that scales up the output current of the differential pair by a factor of 6. In line with the discussion in Section 3.3, this current-mirror ratio is a trade-off between the ability to handle parasitic capacitance and power consumption. This design is optimized to handle parasitic capacitances up to five times larger than the sensor capacitance. The integrator employs a telescopic OTA with an integration capacitor  $C_{int}$  of 4 pF. The transconductance of this OTA is optimized using Eq. (3-6). To

obtain the required transconductance at a minimum supply current, the input transistors of the OTA are sized to operate in weak inversion, resulting in a current consumption of  $34\mu$ A. The control voltages  $V_{b1}$  and  $V_{b2}$  are designed to be 2.6V and 1.4V, respectively, which is in line with the output swing of the telescopic OTA.

The comparator consists of a simple differential pair with a current-mirror load, followed by a common-source stage. The errors due to its propagation delay are eliminated by the three-signal auto-calibration. On the other hand, the delay introduced by comparator should not be so large that it stops the oscillation. As a compromise, for the comparator we selected a supply current of only  $9~\mu A$ .

The integration currents  $I_{int}$  of  $1\mu A$  are generated by degenerated MOS current sources using large MOS transistors to achieve a low flicker-noise corner frequency. This is of particular importance, since errors due to the low-frequency noise of these current sources are not reduced by the chopping technique. The auto-calibration does reduce these errors, but only to the extent that they are correlated between the successive measurements of the offset, reference and sensor capacitances. The current source are sized such that their 1/f noise corner is low enough to ensure that this is the case for measurement times up to 100ms, which corresponds to sensor capacitance values up to 100pF.

Figure 3.8: Complete transistor-level implementation of the interface.

The clock signals  $\varphi_1$ ,  $\varphi_2$ , and the chop are derived from the output of the comparator using a simple on-chip digital state machine (not shown). For test purposes, the control voltages  $V_{b1}$  and  $V_{b2}$  and the threshold voltage  $V_{th}$  are generated off-chip in the current prototype, but they can be easily generated on-chip without significantly increasing the supply current or die size, using simple diode-connected MOS transistors biased at currents far below the supply current of the OTA.

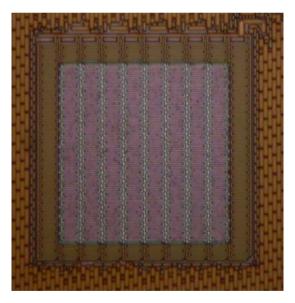

#### 3.5 Measurement Results

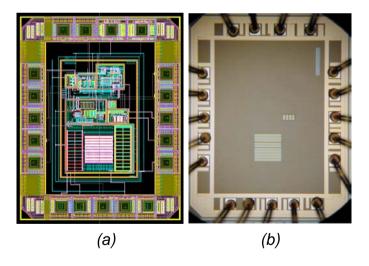

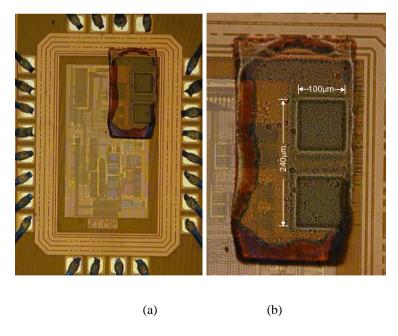

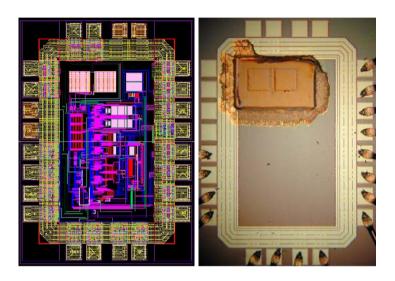

The proposed interface has been designed and fabricated in standard 0.35µm CMOS technology. The techniques applied in the interface do not rely on any particular features of this technology and are therefore expected to be equally applicable to designs in more modern CMOS technologies. Figure 3.9 shows a chip photograph. Since details of the layout are invisible due to the metal exterior, a layout plot is also shown in this figure. The active area (excluding pads) is 0.51 mm<sup>2</sup>.

Figure 3.9: (a) Layout plot and (b) photograph of the chip.

# 3.5.1 Measurements Results of the Changing Input Capacitor

The performance of the chip has been evaluated experimentally using discrete ceramic capacitors up to 50pF for  $C_x$  and  $C_{ref}$ . The offset

capacitance  $C_{off}$  needed to perform auto-calibration consists of the combined parasitic capacitances on the chip and the test PCB. The output signal of the interface (encoded as shown in Fig. 3.4) was digitized by a counter in a microcontroller, which also performed the digital post-processing required for auto-calibration. A 60MHz clock frequency was used for the counter, which is high enough to ensure that the quantization noise associated with the counting is much lower than the thermal noise of the interface.

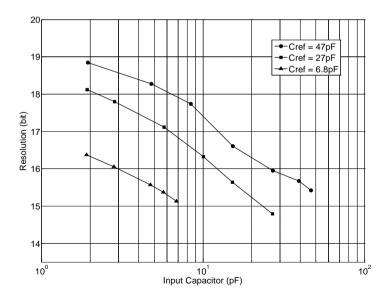

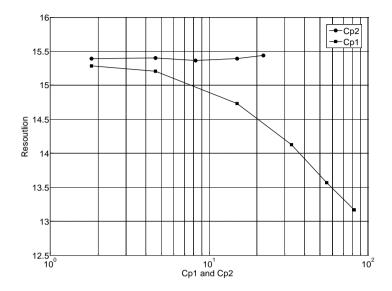

To determine the resolution of the interface, we measured the standard deviation of the post-processed output M as a function of  $C_x$ . To demonstrate that the negative feedback loops of the interface can readily extend the input-capacitance range without increasing the integration capacitor  $C_{int}$ , the resolution was measured across three  $C_x$  ranges, corresponding to the ranges of 6.8pF, 27pF and 47pF. The results are shown in Fig. 3.10. Two trends can be observed in this figure: the measured resolution decreases with an increase in  $C_x$ , and with a decrease in  $C_{ref}$ . In spite of this, the measured resolution exceeds 15 bits for almost all the capacitance values measured.

Figure 3.10: Measured resolution as a function of  $C_x$  for three values of  $C_{ref}$ , for  $C_p = 0$  pF.

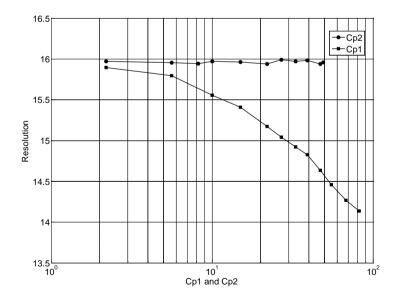

Figure 3.11: Measured resolution as a function of  $C_{p1}$  and  $C_{p2}$  for  $C_x = 5.6 \mathrm{pF}$  and  $C_{ref} = 6.8 \mathrm{pF}$ .

Figure 3.12: Measured resolution as a function of  $C_{p1}$  and  $C_{p2}$  for  $C_x = 12 \mathrm{pF}$  and  $C_{ref} = 27 \mathrm{pF}$ .

The quantitative analysis of the resolution of the interface is presented in following. The trends that can be observed in Fig. 3.10 can be explained by considering how time jitter on the three period times  $T_x$ ,  $T_{ref}$  and  $T_{off}$  affects the auto-calibrated measurement result M given by Eq. (3-3). Assuming that the standard deviation of the jitter on these period times equals  $\sigma(T_x)$ ,  $\sigma(T_{ref})$  and  $\sigma(T_{off})$ , respectively, and assuming that  $T_{off}$  is much smaller than  $T_x$  and  $T_{ref}$ , the resulting standard deviation of M can be written as:

$$\sigma^{2}(M) = \left(\frac{\sigma(T_{x})}{T_{ref}}\right)^{2} + \left(\frac{\sigma(T_{ref})T_{x}}{T_{ref}^{2}}\right)^{2} \qquad (3-7)$$

This equation readily shows that for a given value of  $C_x$  (and hence a given value of  $T_x$  and  $\sigma(T_x)$ ),  $\sigma(M)$  can be reduced (and thus the resolution increased) by using a larger  $C_{ref}$  to obtain a larger  $T_{ref}$ . Conversely, for a given value of  $C_{ref}$ , the resolution drops for larger values of  $C_x$  (and hence larger values of  $T_x$ ), because the effect of  $\sigma(T_{ref})$  increases. Moreover,  $\sigma(T_x)$  will also increase for larger values of  $C_x$ , because the noise gain of the integrator increases.

# 3.5.2 Measurements Results of Changing Parasitic Capacitor

Figures 3.11 and 3.12 show the effect of the parasitic capacitors  $C_{pl}$  and  $C_{p2}$  on the measured resolution for two combinations of  $C_x$  and  $C_{ref}$ . The resolution stays almost constant as  $C_{p2}$  increases until the point that  $C_{p2}$  becomes too large and draws too much current from the feedback loop, preventing the interface from working, as discussed in Section 3.3. The point at which this happens is in reasonable agreement with the design target of  $5C_x$ . Increasing  $C_{p1}$  has two effects on the system performance. Similar to an increase in  $C_x$ , it increases the noise gain of the integrator, resulting in a decreased resolution, as shown in Figs. 3.11 and 3.12. Moreover, it will increase the loading of the integrator and thus decrease the phase margin of the negative feedback loop, as discussed in Section 3.3. For sensor capacitances beyond the end points of the curves in Figs. 3.11 and 3.12, this lack of phase margin prevents the interface from producing a proper output signal.

#### 3.5.3 Measurements Results of Linearity and PSRR

The non-linearity of the interface has been determined using the method presented in [7,18]. By measuring four combinations of three stable reference capacitors:  $C_1$ ,  $C_2$ ,  $C_1 + C_3$  and  $C_2 + C_3$ , the non-linearity can be determined from the corresponding measurement results  $M_1$ ,  $M_2$ ,  $M_{1+3}$  and  $M_{2+3}$  as:

$$\lambda = \frac{M_{2+3} - M_{1+3}}{M_2 - M_1} - 1 \tag{3-8}$$

This expression is accurate even in the presence of parasitic capacitors, provided these capacitors are equal for the four measurements. Using combinations of the discrete capacitors 2.1pF, 4.2pF, 10pF and 22pF, a non-linearity less than  $2\times10^{-4}$  was obtained, corresponding to a linearity of better than 12 bits.

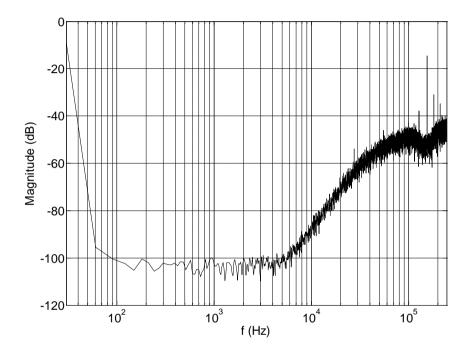

To evaluate the energy consumption of the interface, the measurement time and power consumption are of interest. Since the measurement time increases for larger values of  $C_x$ , the longest measurement time is obtained when  $C_x$  equals  $C_{ref}$ , assuming that  $C_x \leq C_{ref}$ . For a  $C_{ref}$  of 6.8pF, this maximum is 7.6ms. The chip consumes 64 $\mu$ A from a 3.3V supply, which then corresponds to an energy per measurement of 1.6 $\mu$ J. The majority of the supply current (49 $\mu$ A) is static current consumed by the analog circuitry, while 15 $\mu$ A concerns dynamic current consumed by the digital circuitry.

Due to the auto-calibration technique applied in the interface, variations in its supply voltage  $V_{dd}$  should have little effect on the measured capacitance, provided the supply voltage remains stable during the three consecutive measurements of the auto-calibration sequence. This has been verified by sweeping the supply voltage from 2.6V to 3.7V for fixed values of  $C_x$  and  $C_{ref}$  of 6.8pF each. The measured capacitance value only changes by less than 23 ppm across this range, which corresponds to a supply sensitivity of less than 21 ppm/V.

#### 3.6 Conclusion

An energy-efficient capacitive-sensor interface has been presented. The interface circuit is based on the use of a period modulator implemented with compact, energy-efficient building blocks. Auto-calibration is employed to achieve a well-defined transfer function in spite of the non-idealities of these building blocks. This enables the use of a simple telescopic OTA in the integrator and a slow, low-power comparator. The limited output swing of the OTA is accommodated using negative feedback loops. Measurement results show, in comparison with previous interfaces based on period modulation, not only comparable resolution and linearity, but also a significant improvement in energy efficiency.

#### 3.7 References

- [1] L. K. Baxter, *Capacitive Sensors: Design and Applications*. New York: IEEE Press, 1997.

- [2] G. C. M. Meijer, Smart Sensor Systems. Chichester, UK: Wiley, 2008.

- [3] F. van der Goes, "Low-cost smart sensor interfacing," Ph.D. dissertation, Delft University of Technology, Delft, the Netherlands, 1996.

- [4] X. Li and G. C. M. Meijer, "An accurate interface for capacitive sensors," *IEEE Trans. Instrum. Meas.*, vol. 51, no. 5, pp. 935-939, Oct. 2002.

- [5] A. Heidary, S. Heidary Shalmany and G. C. M. Meijer, "A flexible low-power high-resolution integrated interface for capacitive sensors," in *Proc. IEEE Int. Symp. on Industrial Electronics (ISIE)*, Bari, Italy, July 2010, pp. 3347-3350.

- [6] G. C. M. Meijer and V. P. Iordanov, "SC front-end with wide dynamic range," *Electron. Letters*, vol. 37, no. 23, pp. 1377-1378, Nov. 2001.

- [7] A. Heidary and G. C. M. Meijer, "Features and design constraints for an optimized SC front-end circuit for capacitive sensors with a wide dynamic range," *IEEE J. Solid-State Circuits*, vol. 43, no. 7, pp. 1609-1616, July 2008.

- [8] W. Bracke, R. Puers and C. Van Hoof, *Ultra Low Power Capacitive Sensor Interfaces*. Dordrecht, the Netherlands: Springer, 2007.

- [9] D.-Y. Shin, H. Lee and S. Kim, "A delta-sigma interface circuit for capacitive sensors with an automatically calibrated zero point," *IEEE Trans. Circuits and Systems II*, vol. 58, no. 2, pp. 90-94, Feb. 2011.

- [10] S. A. Jawed, D. Cattin, M. Gottardi, N. Massari, A. Baschirotto, and A. Simoni, "A 828µW 1.8V 80dB dynamic range readout interface for a MEMS capacitive microphone," in *Proc. ESSCIRC*, Edinburgh, UK, Sept. 2008, pp. 442-445.

- [11] AD7156 datasheet, Analog Devices [Online]. http://www.analog.com.

- [12] M. Paavola, M. Kämäräinen, E. Laulainen, M. Saukoski, L. Koskinen, M. Kosunen and K. A. I. Halonen, "A micropower  $\Delta\Sigma$ -based interface ASIC for a capacitive 3-axis micro-accelerometer," *IEEE J. Solid-State Circuits*, vol. 44, no. 11, pp. 3193-3210, Nov. 2009.

- [13] H. Danneels, K. Coddens and G. Gielen, "A fully-digital, 0.3V, 270nW capacitive sensor interface without external references," in *Proc. ESSCIRC*, Helsinki, Finland, Sept. 2011, pp. 287-290.

- [14] Z. Tan, R. Daamen, A. Humbert, K. Souri, Y. Chae, Y. Ponomarev and M. A. P. Pertijs, "A 1.8V 11µW CMOS smart humidity sensor for RFID sensing applications," in Proc. *A-SSCC*, Jeju, Korea, Nov. 2011, pp. 105-108.

- [15] P. Bruschi, N. Nizza and M. Piotto, "A current-mode, dual slope, integrated capacitance-to-pulse duration converter," *IEEE J. Solid-State Circuits*, vol. 42, no. 9, pp. 1884-1891, Sept. 2007.

- [16] P. Bruschi, N. Nizza and M. Dei, "A low-power capacitance to pulse width converter for MEMS interfacing," in *Proc. ESSCIRC*, Edinburgh, UK, Sept. 2008, pp. 446-449.

- [17] Z. Tan, M. A. P. Pertijs and G. C. M. Meijer, "An energy-efficient 15-bit capacitive sensor interface," in *Proc. ESSCIRC*, Helsinki, Finland, Sept. 2011, pp. 283-286.

- [18] A. Heidary, "A low-cost universal integrated interface for capacitive sensors," Ph.D. dissertation, Delft University of Technology, Delft, the Netherlands, 2011.

# Chapter 4

# Energy-Efficient Capacitive-Sensor Interfaces using Delta-Sigma Modulation

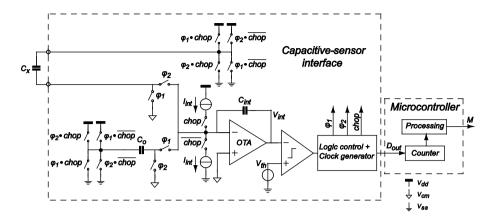

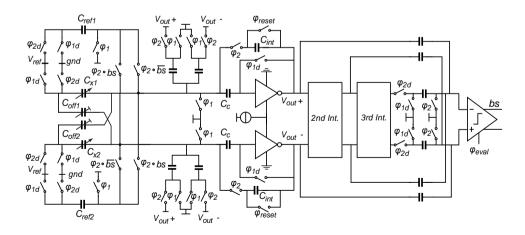

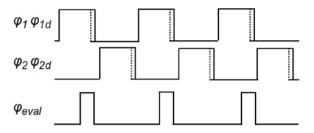

#### 4.1 Introduction

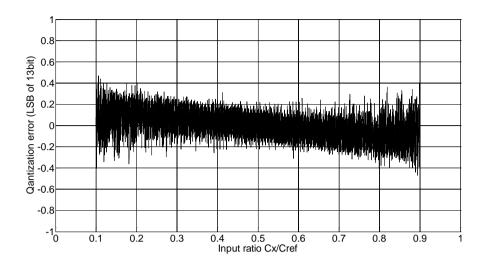

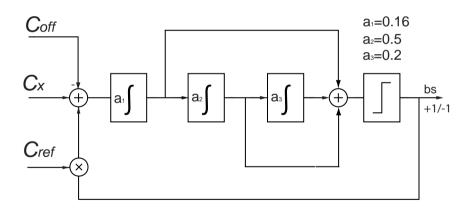

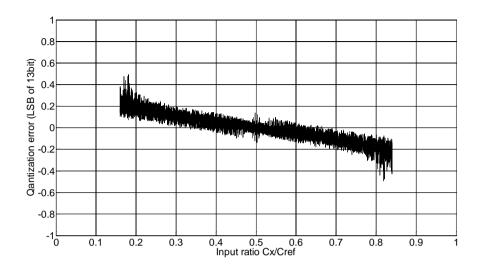

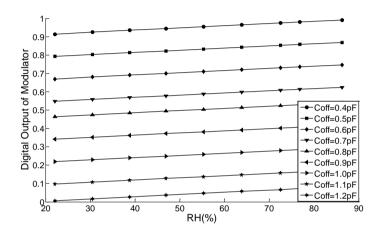

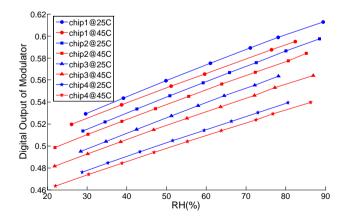

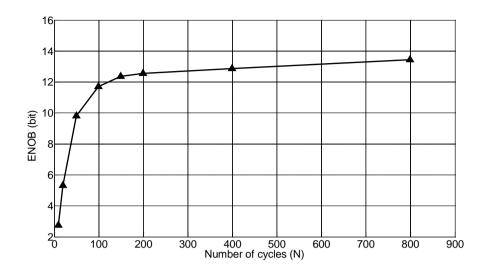

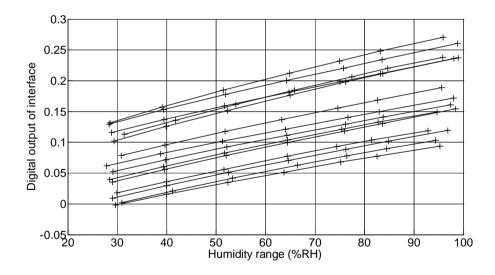

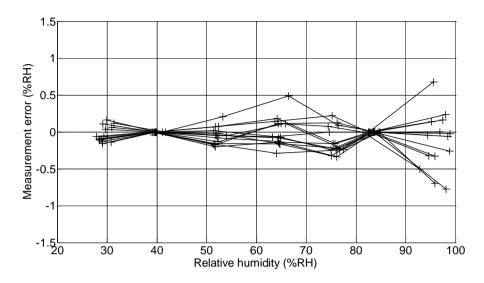

This chapter discusses the system design and circuit implementation of energy-efficient capacitive-sensor interfaces using delta-sigma modulation. The interfaces presented in this chapter are dedicated for humidity sensing in RFID applications. For a better understanding of the motivation and specifications of the interface design, it is beneficial to start with the background of RFID applications. Afterwards, the sensing element will be discussed and the system-level design of the delta-sigma modulator for capacitive-sensor interface is addressed in detail. Two state-of-the-art prototypes will be presented which have been implemented in  $0.16\mu m$  CMOS technology. Measurement results show that the first design achieves a 13-bit effective resolution for a measurement time of 10.2ms while consuming only  $5.86\mu A$  from a 1.8V supply. The second design achieves a

12.5-bit effective resolution for a measurement time of 0.8ms while consuming only  $8.6\mu A$  from a 1.2V supply.

#### 4.2 System Background

#### **4.2.1 RFID Application Introduction**