# Benchmarking and Algorithm Optimization for SENeCA

A RISC-V-based Neuromorphic Processor

Kevin Shidqi

# Benchmarking and Algorithm Optimization for SENeCA

## A RISC-V-based Neuromorphic Processor

by

Kevin Shidqi Embedded Systems: Embedded Computer Architecture Student Number: 5234948 Email: KevinShidqi@student.tudelft.nl

Supervisor: Professor Said Hamdioui Duration: December 2021 - November 2022

#### Committee Members:

Prof. dr. S. Hamdioui, TU Delft, supervisor Prof. or. o. no....

Dr. A. Gebregiorgis,

TU Delit,

TU Delft TU Delft, supervisor

A. Yousefzadeh, Ph.D., IMEC The Netherlands G. van Schaik, IMEC The Netherlands

This thesis is confidential and cannot be made public until November 30, 2023.

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## **Abstract**

With recent breakthroughs in AI (Artificial Intelligence) technology, the impact of AI on society can be felt in various fields. The market for AI software, for example, reached a valuation of \$62 billion in 2022. A growing number of new computer architectures specialized in running these AI software were also developed. At first they were run on conventional CPUs (Central Processing Unit) and GPUs (Graphical Processing Units), but then more specialized hardware emerged, such as the TPU (Tensor Processing Unit). However, since algorithms in these AI software are generally data-intensive, the power consumption became a problem. Therefore, as many of these algorithms were based on biological neural networks, there is a growing interest to develop hardware similarly based on principles found these networks as well to replicate their efficiency. This new architecture is known as neuromorphic architecture.

However, a new architecture does not come without challenges. As a nascent and fragmented field, neuromorphic computing in general lacks a standardized benchmarking suite or methodology. In other, more mature fields, benchmarks are a standard way of evaluating the performance of different designs objectively and fairly. This thesis aims to propose and demonstrate a benchmarking methodology and implementation flow for neuromorphic processors. This methodology aims to measure the important performance metrics for a neuromorphic processor, both on the small scale of individual synaptic operations, and the large scale of performing an actual workload. The chosen workload is a keyword spotting program based on a simple DNN architecture, which detects a specific phrase in an audio recording. This workload was chosen due to its potential application in an environment where energy is limited, such as an embedded device.

The neuromorphic processor that is the target of this benchmarking is SENeCA (short for Scalable Energy-efficient Neuromorphic Computer Architecture), a flexible and scalable design developed at IMEC The Netherlands. To implement the keyword spotting program on SENeCA, the keyword spotting program was rewritten and parsed. Since no physical chip implementation of SENeCA exists at the time of writing, the program was run on SENeCA using a HDL simulator. The execution time of the program is measured in detail, taking into account not only the total time, but also the time required to complete the specific stages of program. Afterwards, the power consumption of SENeCA during the execution of the program was measured using a power estimation software, both for the entire chip and its individual components. This is done both in average mode, obtaining the average power consumption over the total execution time, and in time-based mode, providing insight to the peak power and fluctuations over time. Then, the energy to solution is calculated using the execution time and power consumption. This process is done in multiple iterations, with a specific optimization done each iteration using SENeCA's accelerators. This provides insight into the impact of each optimization to power consumption and performance. Finally, a measurement of the energy consumption of SENeCA per individual synaptic operations is also done, allowing estimates of the energy consumption of future implementations.

# unec

The work in this thesis was supported by IMEC The Netherlands. Their cooperation is hereby gratefully acknowledged.

Copyright ©2022 Kevin Shidqi All rights reserved.

# Contents

| Αb | stract                                                                                                                                                                                                                                                                                                                                                                                        | i                                                |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Αb | stract                                                                                                                                                                                                                                                                                                                                                                                        | i                                                |

| Pr | eface                                                                                                                                                                                                                                                                                                                                                                                         | ix                                               |

| 1  | Introduction  1.1 Motivation                                                                                                                                                                                                                                                                                                                                                                  | 1<br>1<br>3<br>3<br>5<br>5                       |

| 2  | Neuromorphic Architectures and Benchmarking  2.1 Artificial Neural Network  2.2 Limits of Traditional CPU  2.3 GPU and TPU  2.4 Principles of Neuromorphic Architectures  2.4.1 Usage of Non-von Neumann Architecture  2.4.2 Low Overhead of Information Transmission  2.4.3 Sparsity of Data Streams  2.5 Examples of Current Neuromorphic Architectures  2.5.1 TrueNorth  2.5.2 Intel Loihi | 7<br>8<br>11<br>12<br>14<br>14<br>15<br>15<br>15 |

|    | 2.5.3 SpiNNaker 2.5.4 Tianjic  2.6 Benchmarking of Neuromorphic Processors 2.6.1 Closed-loop Neuromorphic Benchmark 2.6.2 The Nengo Platform for Benchmarking 2.6.3 Benchmarking SpiNNaker With DNA Sequence Matching Algorithm 2.6.4 SNABSuite 2.6.5 Hand Gesture Recognition Benchmark 2.6.6 Keyword Spotting Benchmark                                                                     | 17<br>18<br>18<br>20<br>23<br>23<br>25<br>27     |

| 3  | Architecture of SENeCA  3.1 Introduction  3.2 Detailed Architecture  3.2.1 RISC-V Core (Ibex)  3.2.2 Axon Messaging Interface (AMI)  3.2.3 Shared Memory Pre-fetch Unit  3.2.4 Neuron Co-Processor (NCP)  3.2.5 Network on Chip (NoC)  3.2.6 Synthesis Results  3.3 Comparison of SENeCA with Other Architectures  3.3.1 With SpiNNaker  3.3.2 With IBM TrueNorth  3.3.3 With Intel Loihi     | 31<br>32<br>33<br>34<br>35<br>36<br>37           |

| 4  | Software Architecture and Implementation 4.1 Keyword Spotting                                                                                                                                                                                                                                                                                                                                 | <b>42</b><br>43                                  |

Contents

| Α  | Brea                      | kdown of Power Consumption by Component 116                                                                                                                                                                                                                                 |

|----|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Re | ferer                     | ces 110                                                                                                                                                                                                                                                                     |

| 7  | 7.1                       | Clusion         107           Overview            Discussion and Future Work            108                                                                                                                                                                                 |

|    | 6.6<br>6.7<br>6.8         | Ideal Power Calculation       100         Accuracy Comparison       102         Summary of Results and Discussion       103                                                                                                                                                 |

|    | 0.0                       | 6.5.2 Execution Time Measurements       97         6.5.3 Power Measurements       99                                                                                                                                                                                        |

|    | 6.5                       | 6.4.2 Execution Time Measurements       90         6.4.3 Power Measurements       92         Results of Version 7: Final Version       93         6.5.1 Optimization Method and Implementation       93                                                                     |

|    | 6.4                       | 6.3.2 Execution Time Measurements       85         6.3.3 Power Measurements       87         Results of Version 6: Utilization of the Loop Buffer       88         6.4.1 Optimization Method and Implementation       88                                                    |

|    | 6.3                       | 6.2.2 Execution Time Measurements       81         6.2.3 Power Measurements       83         Results of Version 5: Utilization of the Event Capture Unit       84         6.3.1 Optimization Method and Implementation       84                                             |

|    | 6.2                       | 6.1.2 Execution Time Measurements       77         6.1.3 Power Measurements       78         Results of Version 4: Loop Unrolling With 4 Elements       79         6.2.1 Optimization Method and Implementation       79         6.3.3 Execution Time Measurements       81 |

| 6  |                           | mizations and Final Results       74         Results of Version 3 : Loop Unrolling With 2 Elements       75         6.1.1 Optimization method and Implementation       75                                                                                                   |

|    | 5.6                       | Power Estimation of Basic NPE Operations                                                                                                                                                                                                                                    |

|    | 5.5                       | 5.4.1 Execution Time Measurements       63         5.4.2 Power Measurements       65         Results for Version 2 : Baseline NPE Implementation       67         5.5.1 Execution Time Measurements       67         5.5.2 Power Measurements       68                      |

|    | 5.4                       | 5.3.1 Average Power Estimation       62         5.3.2 Time-based Power Estimation       62         Results for Version 1 : RISC-V Implementation       63                                                                                                                   |

| 5  | Meti<br>5.1<br>5.2<br>5.3 | odology and Preliminary Results56Experiment Setup and Flow57Execution Time Measurements60Power Measurements61                                                                                                                                                               |

|    | 4.3                       | Implementation on SENeCA       47         4.3.1 RISC-V Only Implementation       47         4.3.2 Baseline NPE Implementation       50                                                                                                                                      |

# List of Figures

| 1.1  | Revenues from the artificial intelligence for enterprise applications market worldwide, adapted from [31] | 1  |

|------|-----------------------------------------------------------------------------------------------------------|----|

| 2.1  | An illustration of a biological neuron [29]                                                               | 8  |

| 2.2  | An illustration of an artificial neuron [106]                                                             | 9  |

|      | An illustration of a simple ANN [2]                                                                       | 9  |

| 2.4  | Memory hierarchy of the von Neumann architecture [44]                                                     | 11 |

| 2.5  | TPU Block Diagram [55]                                                                                    | 12 |

| 2.6  | Roofline performance model of TPU (stars), GPU (triangles), and CPU (circles) [57]                        | 13 |

| 2.7  |                                                                                                           | 16 |

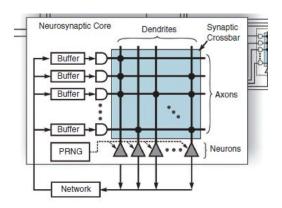

|      | TrueNorth Architecture (single core) [23]                                                                 | 17 |

| 2.8  | Loihi Core Top-Level Microarchitecture [22]                                                               |    |

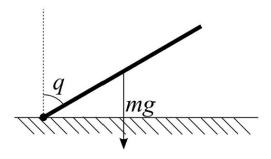

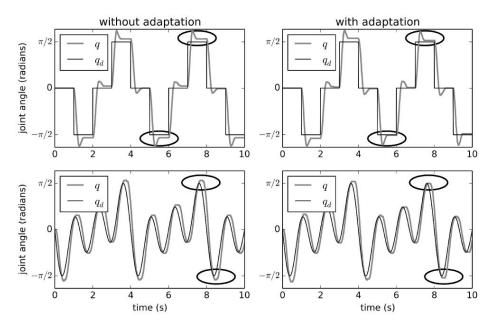

| 2.9  | Depiction of the adaptive motor control task [92]                                                         | 19 |

|      | Adaptive control results [92]                                                                             | 19 |

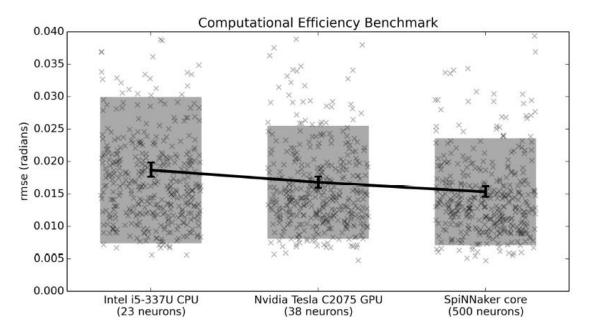

| 2.11 | Comparisons of the adaptive control algorithm run on a CPU, GPU and Neuromorphic                          |    |

|      | Processor, adjusting for power consumption [92]                                                           | 20 |

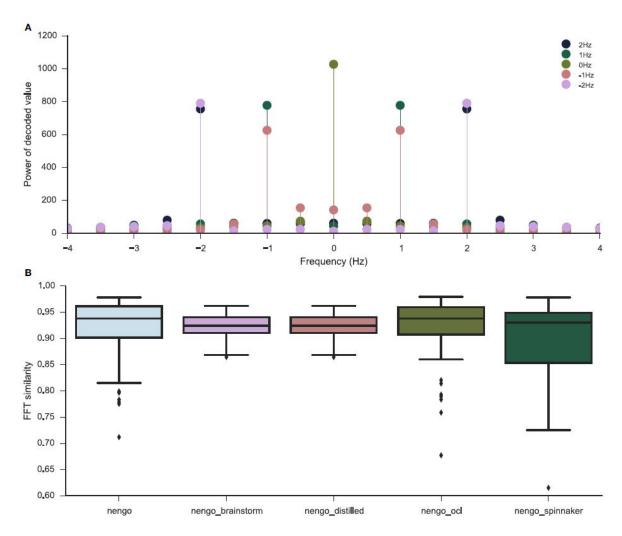

|      | Results of the basal ganglia sequence model benchmarking accuracy [10]                                    | 22 |

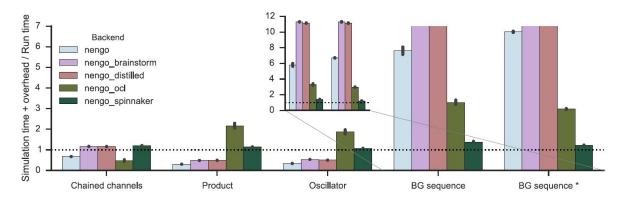

|      | Run speed for each model on each backend [10]                                                             | 22 |

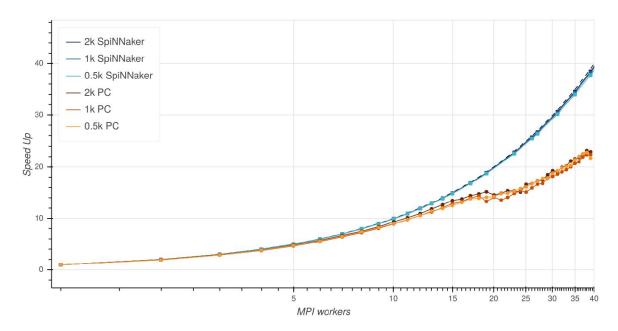

|      | Comparison of speed-up for MPI-FED on a general-purpose CPU and SpiNNaker [99] .                          | 23 |

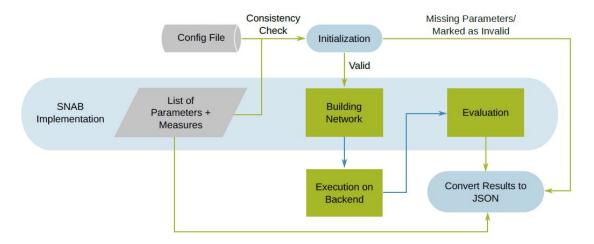

|      | Flowchart of the SNABSuite framework [76]                                                                 | 24 |

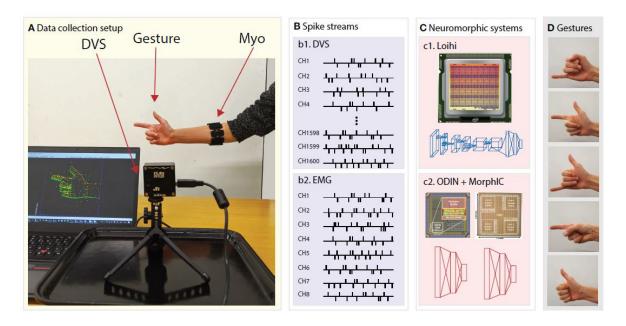

|      | System overview of the hand gesture recognition benchmark [17]                                            | 25 |

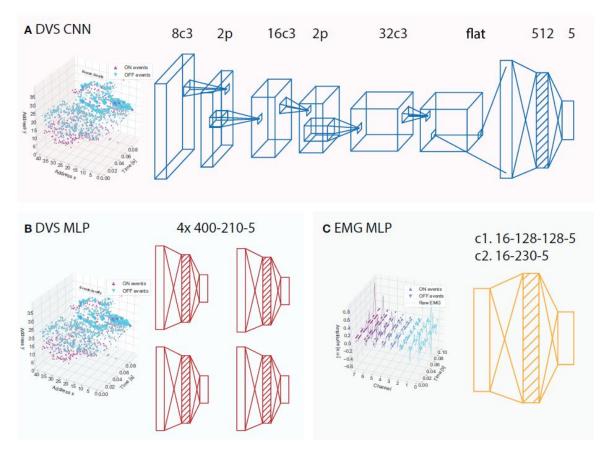

| 2.17 | Architecture overview of the neural networks used in the hand gesture recognition bench-                  |    |

|      | mark [17]                                                                                                 | 26 |

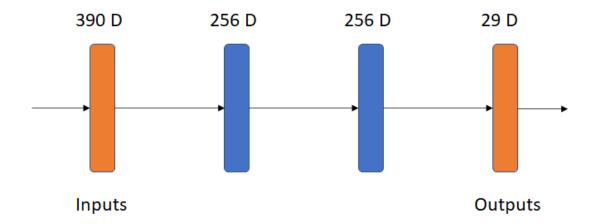

|      | Architecture of the keyword spotting DNN [14]                                                             | 28 |

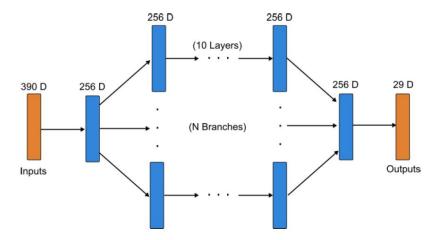

| 2.19 | Architecture of the expanded DNN used for scaling analyses. Note that the size of the                     |    |

|      | network is a function of a configurable parameter N [14]                                                  | 29 |

| 2.20 | Architecture of the keyword spotting DNN [14]                                                             | 29 |

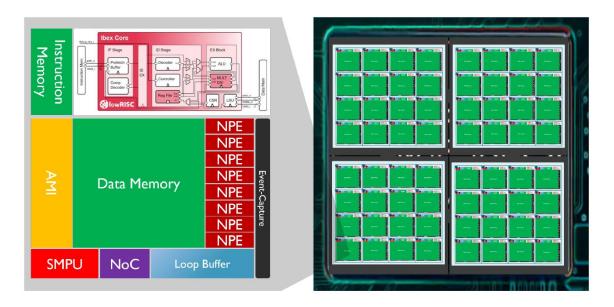

| 3.1  | An example implementation of SENeCA, containing 64 Neuron Compute Clusters (cores)                        | 00 |

|      | [109]                                                                                                     | 33 |

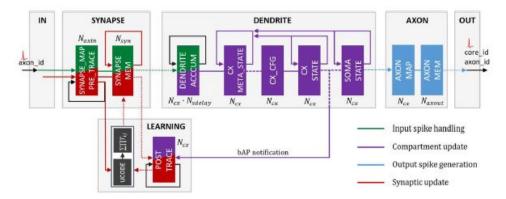

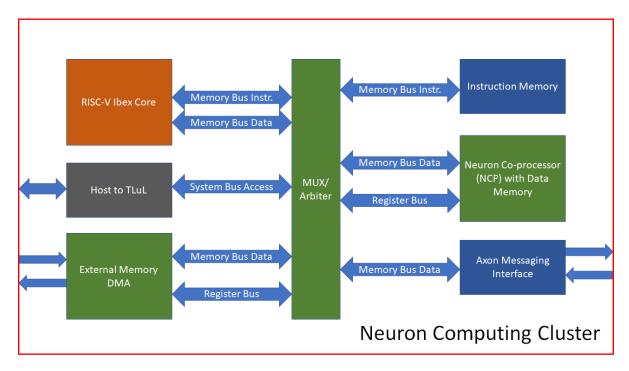

| 3.2  | Illustration of a single SENeCA core (Neuron Computing Cluster)                                           | 34 |

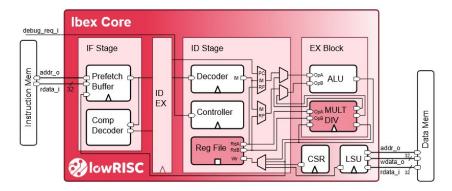

| 3.3  | Block diagram showing the small parametrization of the lbex core with a 2-stage pipeline,                 |    |

|      | IF and ID/EX [5]                                                                                          | 34 |

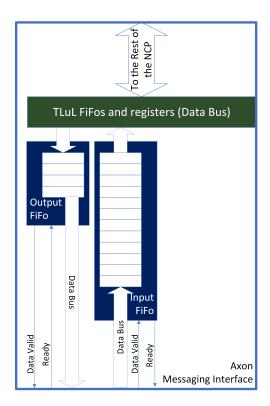

| 3.4  | Illustration of the Axon Messaging Interface                                                              | 36 |

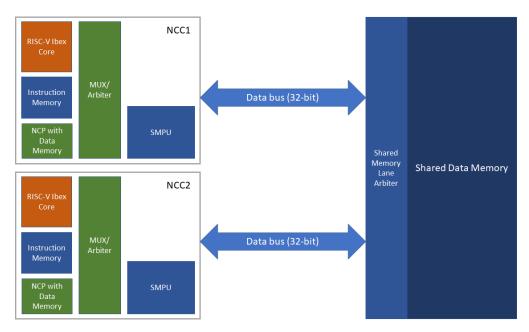

| 3.5  | Illustration of shared memory, with the Shared Memory Pre-fetch Unit in every core                        | 37 |

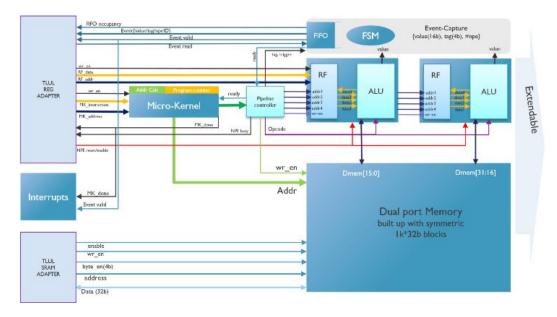

| 3.6  | Block diagram of the NCP, with the blocks above the dual port memory containing an RF                     |    |

|      | block and an ALU being individual NPEs                                                                    | 38 |

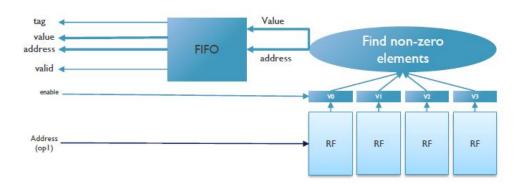

| 3.7  | Block diagram of the Event Capture Unit                                                                   | 39 |

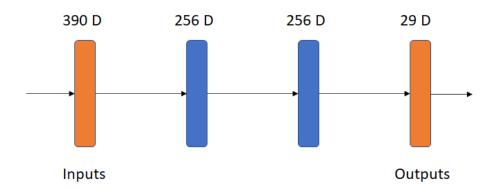

| 4.1  | Network topology for the keyword spotter DNN. All layers are fully connected (FC). Adapted                |    |

|      | from [14]                                                                                                 | 44 |

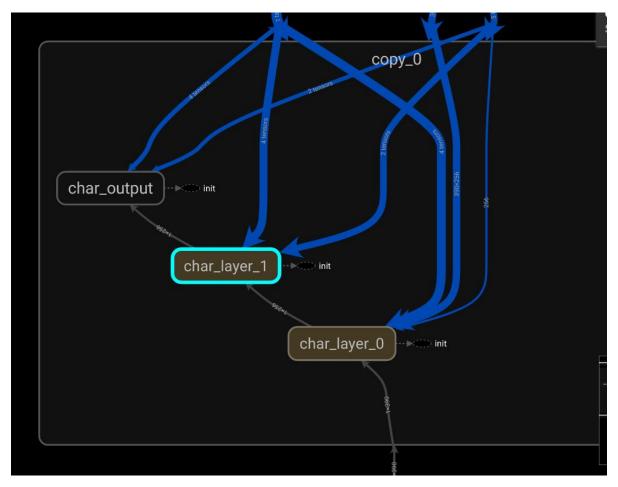

| 4.2  | TensorBoard visualization of the main network. The rounded rectangles represent the                       |    |

|      | layers, while the arrows represent the flow of data                                                       | 45 |

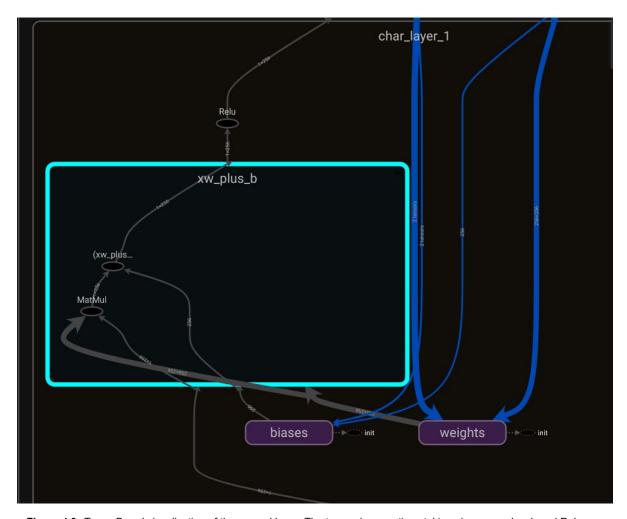

| 4.3  | TensorBoard visualization of the second layer. The two main operations taking place,                      |    |

|      | xw_plus_b and Relu, are shown here.                                                                       | 46 |

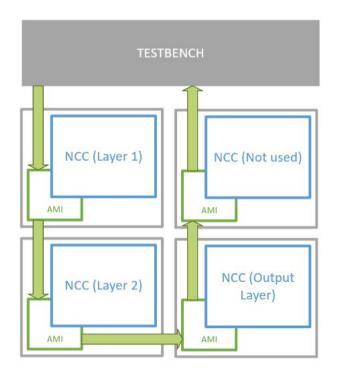

| 5.1  | SENeCA instantiation for this study.                                                                      | 57 |

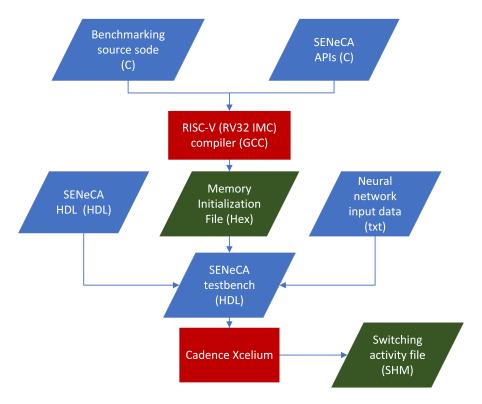

| 5.2  | Experiment flow for performance measurements                                                              | 58 |

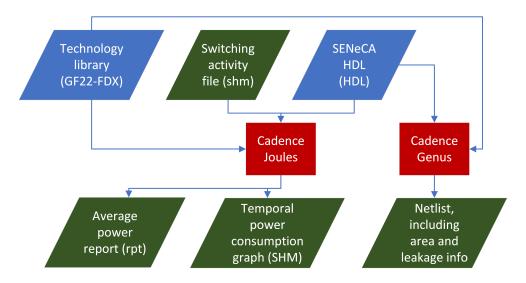

| 5.3  | Experiment flow for power consumption measurements                                                        | 59 |

| 5.4  | Breakdown of                                                                                              | 59 |

List of Figures vi

| 5.5  | Example of a simulation run. The timestamps are displayed on the left, while the text messages indicate a specific task completed | 60  |

|------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.6  | Example of a graph produced by time-based power estimation                                                                        | 63  |

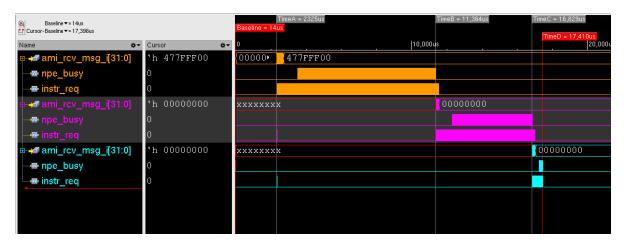

| 5.7  | Output messages obtained from SENeCA while running the simulation with version 1.                                                 | 64  |

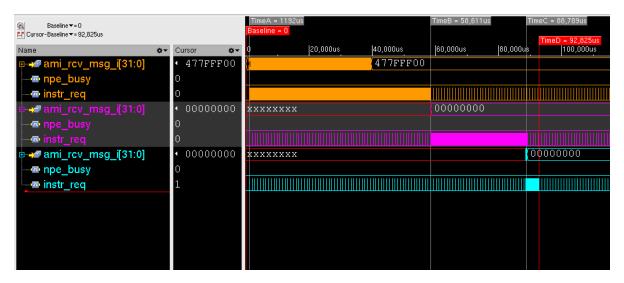

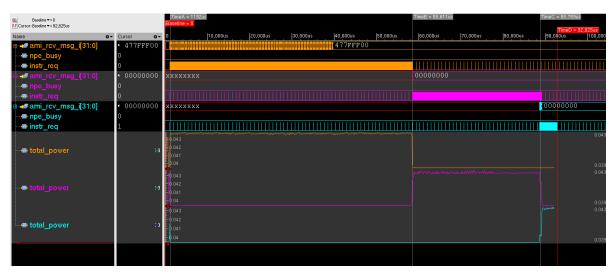

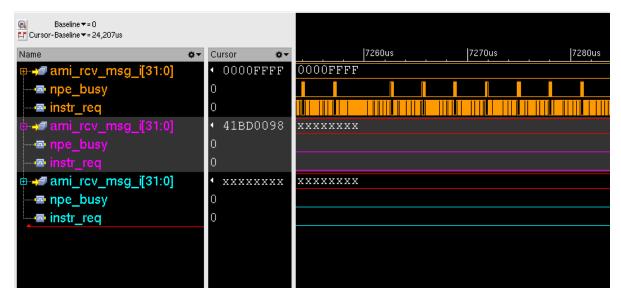

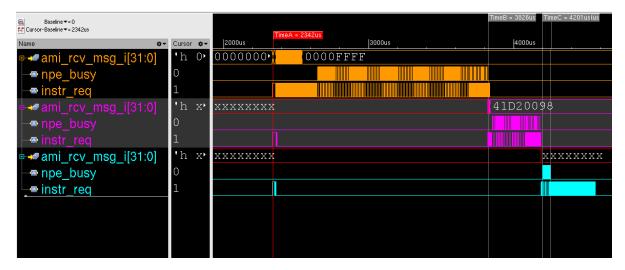

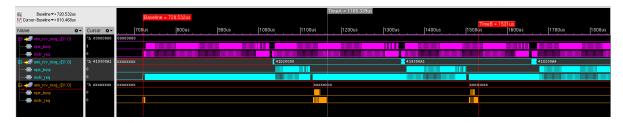

| 5.8  | Waveforms of the signals produced by SENeCA when simulated using version 1 of the                                                 | •   |

| 0.0  | benchmark                                                                                                                         | 65  |

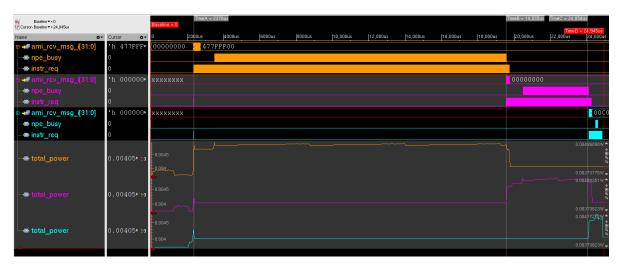

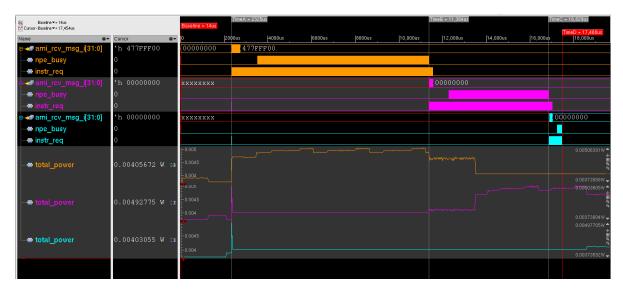

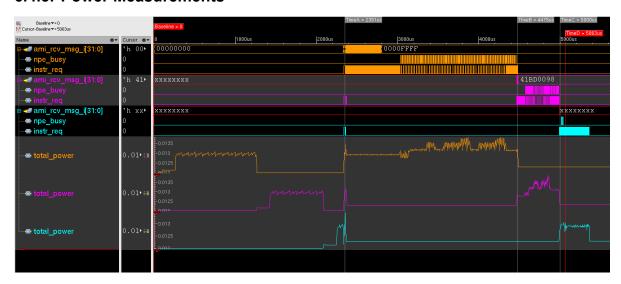

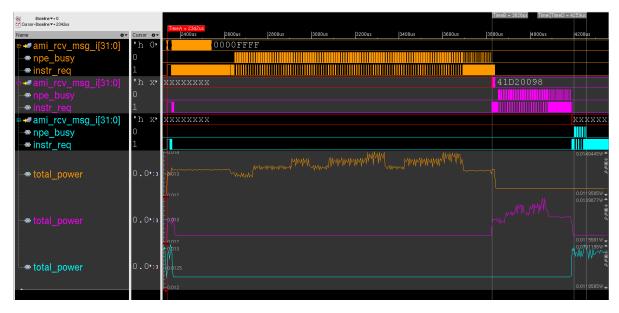

| 5.9  | Time-based power graph of version 2 together with several signals.                                                                | 65  |

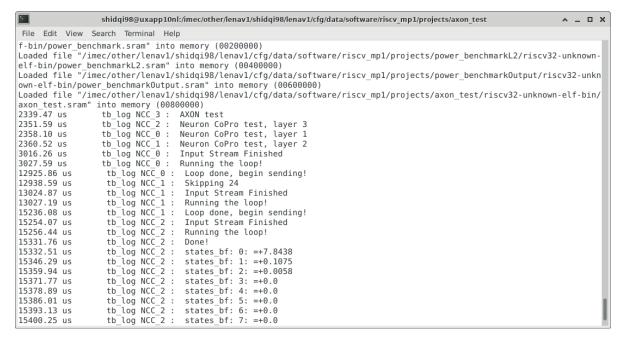

|      | Output messages obtained from SENeCA while running the simulation with version 2.                                                 | 67  |

|      | Time-based power graph of version 2 together with several signals.                                                                | 68  |

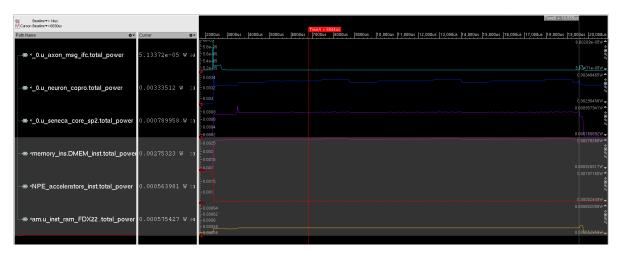

|      | Time-based power graph of version 2, broken down into components                                                                  | 69  |

|      | Time based power consumption graph of individual NPE operations.                                                                  | 71  |

| 5.15 | Time based power consumption graph of individual NFE operations                                                                   | / 1 |

| 6.1  | Output messages obtained from SENeCA while running the simulation with version 3                                                  | 77  |

| 6.2  | Time-based power graph of version 3 together with several signals                                                                 | 78  |

| 6.3  | Time-based power graph of version 3, broken down into components (core 1)                                                         | 78  |

| 6.4  | Output messages obtained from SENeCA while running the simulation with version 4                                                  | 81  |

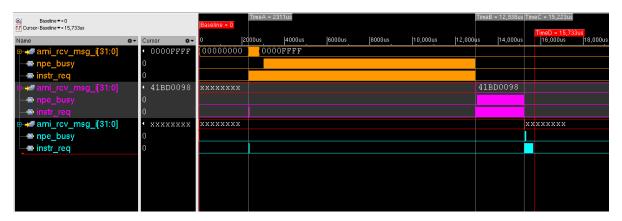

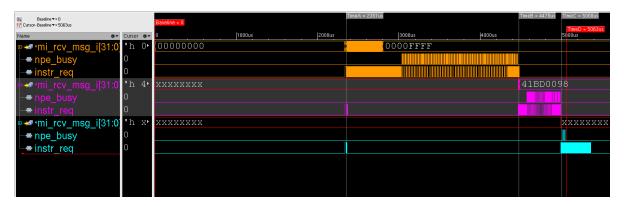

| 6.5  | Waveforms of the signals produced by SENeCA when simulated using version 4 of the                                                 |     |

|      | benchmark                                                                                                                         | 82  |

| 6.6  | Time-based power graph of version 4 together with several signals                                                                 | 83  |

| 6.7  | Output messages obtained from SENeCA while running the simulation with version 5                                                  | 85  |

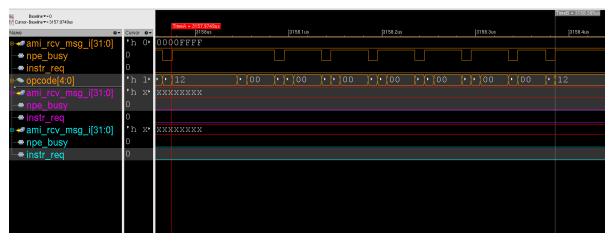

| 6.8  | Waveforms of the signals produced by SENeCA when simulated using version 5 of the                                                 |     |

|      | benchmark                                                                                                                         | 86  |

| 6.9  | The time period in which cores 2 and 3 are active is magnified here to provide a more                                             |     |

|      | detailed look                                                                                                                     | 87  |

| 6.10 | Time-based power graph of version 5 together with several signals                                                                 | 87  |

| 6.11 | Output messages obtained from SENeCA while running the simulation with version 6                                                  | 90  |

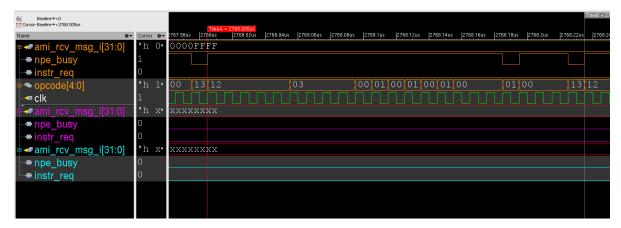

| 6.12 | Waveforms of the signals produced by SENeCA when simulated using version 6 of the                                                 |     |

|      | benchmark                                                                                                                         | 91  |

| 6.13 | A more detailed look of the MM loop pipeline in version 6                                                                         | 91  |

| 6.14 | Time-based power graph of version 6 together with several signals                                                                 | 92  |

| 6.15 | Output messages obtained from SENeCA while running the simulation with version 7.                                                 | 97  |

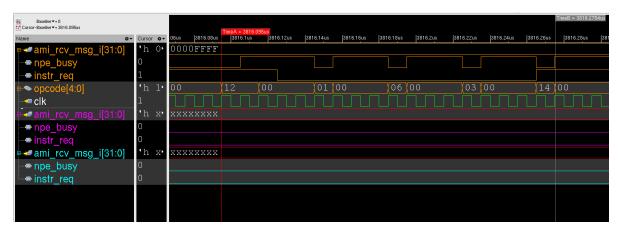

|      | Waveforms of the signals produced by SENeCA when simulated using version 7 of the                                                 |     |

|      | benchmark                                                                                                                         | 98  |

| 6.17 | A more detailed look of the MM loop pipeline in version 7                                                                         | 98  |

| 6.18 | A more detailed look of the bias and activation function loop pipeline in version 7                                               | 99  |

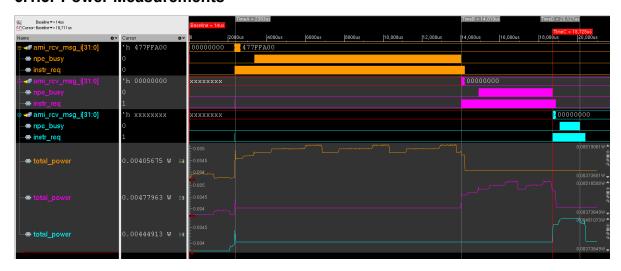

| 6.19 | Time-based power graph of version 7 together with several signals                                                                 | 99  |

|      | Simulation run of version 7, showing the number of events per layer                                                               | 101 |

|      | Multi-input run waveforms of version 7                                                                                            | 102 |

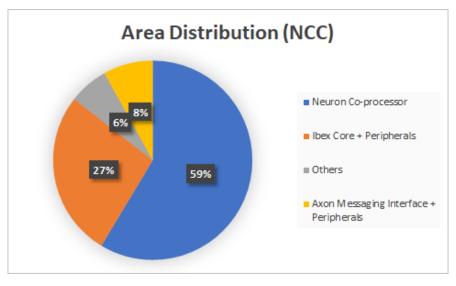

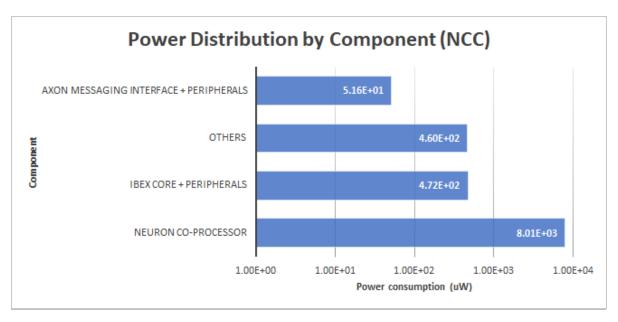

|      | Breakdown of power consumption by component for a single core (NCC)                                                               | 105 |

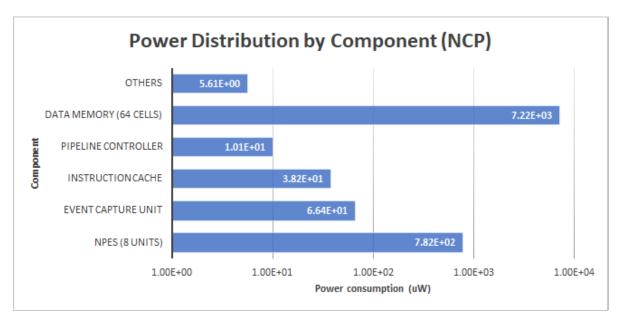

|      | Breakdown of power consumption by component for a single NCP                                                                      | 106 |

# **List of Tables**

| 2.1        | Results of benchmarking a network to measure maximum frequency of neurons in SNAB-Suite [77]                                                                                 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2<br>2.3 | Results of benchmarking a network for solving Sudoku puzzles in SNABSuite [77] Results of benchmarking the gesture recognition system using different architectures          |

| 2.4        | and platforms [17]                                                                                                                                                           |

| 3.1        | Available instructions for the ALU of an NPE. Operations 2 to 6 are arithmetic, 7 to 12 are comparisons, 14 to 17 are bitwise, while 18 and 19 are memory operations         |

| 3.2<br>3.3 | Area consumption of the main components of a single NCC                                                                                                                      |

| 4.1        | Dimensions and sizes in memory of the weight matrices of the 3 layers. Sizes are denoted in KBytes                                                                           |

| 4.2        | Dimensions and sizes in memory of bias vectors of the 3 layers. Sizes are denoted in KBytes                                                                                  |

| 4.3        | Program to perform multiply and accumulate operations by the NPE. Five NPE registers are used out of the 16 available.                                                       |

| 4.4        | Program to perform bias addition and activation function by the NPE. Six NPE registers of the 16 available are used.                                                         |

| 5.1        | An overview of the software used in this study.                                                                                                                              |

| 5.2<br>5.3 | Parameters of the SENeCA instance used                                                                                                                                       |

| 5.4<br>5.5 | Execution time measurements for version 1. All times are in microseconds ( $\mu$ s) Average power consumption of version 1, during the active time of core 1 (Active 1). All |

| 5.6        | power values are in Watts                                                                                                                                                    |

| 5.7        | power values are in Watts                                                                                                                                                    |

| 5.8<br>5.9 | power values are in Watts                                                                                                                                                    |

|            | power values are in Watts                                                                                                                                                    |

|            | power values are in Watts                                                                                                                                                    |

| 5.11       | Average power consumption of version 2, during the active time of core 3 (Active 3). All power values are in Watts                                                           |

|            | List of NPE operations whose energy consumption is to be measured                                                                                                            |

| 6.1<br>6.2 | Execution time measurements for version 3. All times are in microseconds ( $\mu$ s) Average power consumption of version 3, during the active time of core 1 (Active 1). All |

| 6.3        | power values are in Watts                                                                                                                                                    |

|            | power values are in Watts                                                                                                                                                    |

List of Tables viii

| 6.4  | Average power consumption of version 3, during the active time of core 3 (Active 3). All power values are in Watts  | 79  |

|------|---------------------------------------------------------------------------------------------------------------------|-----|

| 6.5  | Execution time measurements for version 4. All times are in microseconds ( $\mu$ s)                                 | 82  |

| 6.6  | Average power consumption of version 4, during the active time of core 1 (Active 1). All power values are in Watts  | 83  |

| 6.7  | Average power consumption of version 4, during the active time of core 2 (Active 2). All power values are in Watts. | 83  |

| 6.8  | Average power consumption of version 4, during the active time of core 3 (Active 3). All power values are in Watts. | 83  |

| 6.9  | Execution time measurements for version 5. All times are in microseconds ( $\mu$ s)                                 | 86  |

|      | Average power consumption of version 5, during the active time of core 1 (Active 1). All power values are in Watts  | 88  |

| 6.11 | Average power consumption of version 5, during the active time of core 2 (Active 2). All power values are in Watts  | 88  |

| 6.12 | Average power consumption of version 5, during the active time of core 3 (Active 3). All power values are in Watts. | 88  |

| 6 13 | Execution time measurements for version 6. All times are in microseconds ( $\mu$ s)                                 | 90  |

|      | Average power consumption of version 6, during the active time of core 1 (Active 1). All power values are in Watts. | 92  |

| 6 15 | Average power consumption of version 6, during the active time of core 2 (Active 2). All                            | 32  |

| 0.10 | power values are in Watts                                                                                           | 92  |

| 6.16 | Average power consumption of version 6, during the active time of core 3 (Active 3). All power values are in Watts  | 93  |

| 6.17 | Execution time measurements for version 7. All times are in microseconds ( $\mu$ s)                                 | 97  |

|      | Average power consumption of version 7, during the active time of core 1 (Active 1). All                            |     |

|      | power values are in Watts                                                                                           | 100 |

|      | Average power consumption of version 7, during the active time of core 2 (Active 2). All power values are in Watts  | 100 |

|      | Average power consumption of version 7, during the active time of core 3 (Active 3). All power values are in Watts  | 100 |

| 6.21 | Ideal energy consumption of the 3 types of loops found in the benchmarking program. All values are in nanojoules    | 101 |

| 6.22 | Ideal number of operations and energy consumption (in nJ) of the benchmarking pro-                                  | 400 |

|      | gram, shown per layer                                                                                               | 102 |

| 6.23 | Accuracy comparisons of the baseline model implemented on a PC with with version 7 on SENeCA.                       | 103 |

| 6.24 | Summary of the optimization implemented in each software version                                                    | 104 |

| 6.25 | Summary of the power and energy of all versions and Loihi from [14]                                                 | 104 |

### **Preface**

This M.Sc. thesis report concludes the amazing two years I spent in Delft as an Embedded Systems student. The subject of neuromorphic engineering sparked my interest the first time it was mentioned in a lecture, and during the work performed for this thesis, it has only grown. I hope that you, the reader, can also learn about it and AI in general while reading this thesis. While this thesis is long, more than 100 pages, I have tried my best to keep it as engaging to the reader as possible.

There are multiple people I would like to thank since it was their support that made most of the work for this thesis possible. First I would like to thank my supervisors, Prof. Said Hamdioui and Anteneh Gebregiorgis, for their advice and feedback during the few progress meetings that we had, and also for proofreading and giving suggestions to improve this thesis. I would also like to thank my supervisors at IMEC The Netherlands, Amirreza Yousefzadeh and Gert-Jan van Schaik, for your enourmous help during the implementation. I realize that this work is only a small part of the SENeCA project being developed at IMEC, but I hope that my small contribution can be of use.

Furthermore, I would like to thank my friends at DH06, especially Johanna, Bas, Boris, Niels, and Maddy, and my fellow Indonesians at PPI Delft, you made an academic year during the pandemic bearable. Also, I would like to thank my fellow thesis students at IMEC, Prithvish and Alexandra, for making the long hours in the library and office enjoyable. I would also like to thank my family on the other side of the world for their unconditional and unending love and support. Last but not least, I would like to thank Aina, for always being by my side.

Kevin Shidqi Delft, November 2022

## Introduction

#### 1.1. Motivation

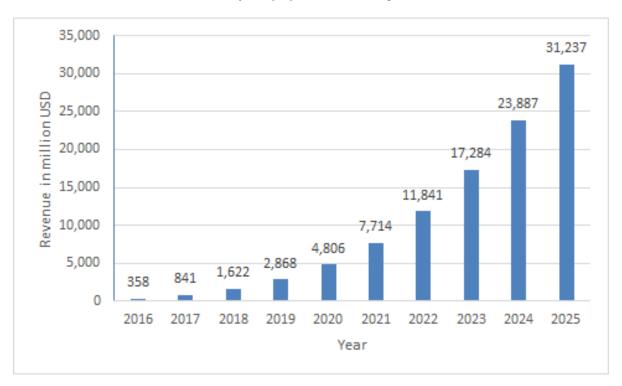

The market of Artificial Intelligence (AI) software is growing rapidly, reaching a valuation of \$62 billion in 2022. That is an increase of around 21% compared to 2021 [38]. Meanwhile, the revenue from AI for enterprise applications has increased more than tenfold between 2017 and 2022, and is expected to continue to increase in 2022 and beyond [31], as shown in Figure 1.1.

Figure 1.1: Revenues from the artificial intelligence for enterprise applications market worldwide, adapted from [31]

While the majority of the users are still the computer and software industries, the adoption of Al tools and methods is also being carried out in various other fields, as mentioned in a report by O'Reilly [65]. Examples of the potential application of Al in various aspects of our daily lives are listed in the following.

1. Healthcare: Several Al applications can perform as good as, or in some cases better than, clini-

1.1. Motivation 2

cians in diagnostics [85]. In the future, AI applications may be used to improve the availability of diagnostic services and reduce their cost.

- 2. Business: Enterprise Cognitive Computing (ECC) is the use of AI to enhance business operation. This is achieved by using AI applications to perform repetitive tasks, improving efficiency [97].

- 3. Education: The usage of Al in education includes the automation of administrative tasks, the condensing of textbooks to useful exam preparation tools, and the development of an Al-based tutoring system [96].

- 4. Agriculture: The automatic detection of objects of interest, such as fruits, in orchards or farms using unmanned vehicles [69] and the monitoring of soil parameters [37] are two possible cases in which Al algorithms can be applied in agriculture, potentially helping farmers and agronomists with automation of labor-intensive tasks.

- 5. Network Security: The use of AI algorithms to observe internet traffic and detect unusual traffic to distinguish a security threat was demonstrated in [60].

The examples and numbers above show the growth and potential of AI applications. Many of algorithms used in these applications are based on information processing systems found in biological, mainly human, brains. These information systems are noted for their ability to perform tasks with remarkable efficiency in terms of energy.

The implementations of these algorithms on digital computers, such as GPUs (Graphical Processing Units), was proven to be possible [74]. The parallel structure of GPUs, originally developed to tackle the parallel nature of graphical applications, allow them to handle the computationally intensive nature of AI algorithms. However, these implementations still lack the energy efficiency of biological systems [70] upon which these algorithms were developed. The main cause of the energy problem with the implementation of AI algorithms on von Neumann computers (the most widely used architecture, including GPUs) is the so-called memory wall [80]. In von Neumann computers, the processing unit and the memory are separated, usually on different chips or different parts of a chip, and they are connected by a data bus. This causes the energy consumption of a memory access operation to be as much as 1,000 times higher than that of an arithmetic operation [48]. Since AI applications are also data-intensive, requiring a large number of read/write operations to the memory, the distance between the processor and the memory becomes a major bottleneck and cause of inefficiency in terms of energy [49]. Some of the applications of AI sofware take place in environments where energy for performing computations is limited (e.g. in embedded applications such as in [69]), worsening this problem.

To solve the problems above, in recent years, a new type of computer architecture has emerged that departs from the conventional von Neumann architecture. It specializes in data-intensive AI algorithms and aims to use the principles of biological neurons to replicate their energy efficiency. These new architectures are termed "Neuromorphic processors". Research on analog versions of neuromorphic processors was done as early as 1995 [28]. Currently, several prototype chips have already been published, such as Loihi[22], TrueNorth[71], and SpiNNaker[35]. Another chip, which is still in the developmental stage, is SENeCA [109]. SENeCA, named after the Roman philosopher, stands for Scalable Efficient Neuromorphic Computer Architecture. It is designed to be a flexible and scalable architecture that can accommodate future neural network architectures.

However, to accelerate the development of these neuromorphic processors, there needs to be a standardized process or suite to perform benchmarking [20]. A similar concept already exists in conventional CPU, such as Standard Performance Evaluation Corporation (SPEC), an American non-profit organization that aims to produce a standardized set of performance benchmarks for computers [91]. It is argued that one of the factors that drove the rapid development of CPUs was this benchmarking standard, and to truly unleash the potential of neuromorphic chips, a similar benchmarking suite or standard should be developed for neuromorphic architecture. Similarly, an effort to produce "fair and useful benchmarks" for the field of machine learning is being made by MLPerf [67]. For neuromorphic computing to reach maturity as a field, a similarly standardized and systematic methodology or suite for benchmarking is surely needed.

1.2. Problem Statement 3

#### 1.2. Problem Statement

The goal of Neuromorphic Computing as a field is quite ambitious, namely, to decipher the secrets of the biological brain that allow the unparalleled efficiency and flexibility of brain-based computing. As the challenge is quite daunting, there is a need to focus on measuring quantitative metrics to prove real-world value by benchmarking, instead of open-ended exploration [20]. This might seem difficult, since the designs that have been published vary widely in their features and purpose [86]. Furthermore, there is no standardized language yet for neuromorphic processors at the time of writing, such as the C language that was used in SPECint benchmarks in the case of conventional CPUs.

In many fields, however, benchmarking has provided great value by allowing for a fair and useful comparison between architectures or algorithms. For example, in conventional von Neumann architectures, the SPECint [91] benchmarks were developed. For systems programming, Dhrystone was widely used [102]. More recently, the MLPerf benchmark suite was developed for machine learning algorithms [67]. A good benchmark serves to motivate researchers to solve a particular problem that can represent a wider class of useful problems, improving the real-world value of their field.

Benchmarks also allow designers to measure and make tradeoff decisions in their design. In particular, for a nascent field like neuromorphic computing, the impact of specific design choices might not be fully understood. Thus, it will be useful to perform a quantitative evaluation of the relative features, flexibility, and performance of existing platforms to help future designers understand the advantages and disadvantages of the design choices in those platforms and their impact on performance. This will lead to better designs in the future, helping to unleash the potential of neuromorphic computing to accelerate the applications of AI software to solve real-world problems.

As the goal of neuromorphic processors is to efficiently process neural networks, the focus of these hypothetical benchmarks should be on measuring performance and energy efficiency. Furthermore, a proper benchmarking suite would measure these metrics not only when running a full application but also when executing simple neural operations. This study aims to perform a systematic benchmarking process using one of the applications mentioned in [20] on SENeCA. The most important metrics to be measured, since the goal of SENeCA and neuromorphic processors as a whole, is to execute neural network operations in an energy-efficient manner, are energy-to solution and inference time. Other than that, peak and average power consumption, as well as chip area will also be measured.

#### 1.3. State of the Art

This section will explore the published research on the topic of neuromorphic benchmarking. Most of the published architectures have some kind of demonstration section in which a certain algorithm is run on the architecture. The publication of Loihi [22] has a section which evaluates Loihi running a locally competitive spiking algorithm (LCA). Tianjic [26], meanwhile, was benchmarked with an unmanned bicycle controller with multiple ANN / SNNs. TrueNorth [71], had a framework built specifically for it to implement CNNs. Another design, MorphIC [33], was tested with the MNIST image classification database. The algorithms that were chosen to be tested on these architectures are mainly well suited to the architecture. While this is necessary to highlight the performance of these chips, the lack of a standard program or benchmarking methodology makes it difficult to perform a fair and objective comparison.

Several studies have been published that focused on developing a benchmarking suite. Ostrau, et al., developed a framework to develop benchmarks for neuromorphic processors named SNABSuite [76], based on the Cypress framework [93]. They used the framework to perform benchmarking with several programs, including a Sudoku solver and a simple program to measure the frequency of neuron firing on the four supported platforms [77]. The four supported platforms are BrainScaleS [82], Spikey [83], NEST [39], and SpiNNaker [35]. They measured important metrics such as energy, accuracy, and time to solution.

1.3. State of the Art

Another framework for developing software for neuromorphic architectures, Nengo [11], was also used for benchmarking [10]. Nengo has several backend platforms to generate SNN-based code to run of various platform, and one backend, SpiNNaker, was run in this benchmarking study on the eponymous hardware, while four other backend platforms were run on more conventional hardware. Five different applications were used for benchmarking, all of them related to simulating large-scale brain models. The speed and accuracy while running these five applications were measured.

Other published studies focused more on using a application specific to other fields to demonstrate the capabilities of neuromorphic processors through benchmarking. A benchmark based on hand gesture recognition, for example, was performed by Ceolini, et. al. [17]. This study uses event-based camera input and signals from a sensor capable of measuring electrical signals from the forerarm muscle to detect hand gestures performed by humans. The neuromorphic chips used were Loihi [22] and a combination of ODIN [34] and MorphIC [33]. They were compared against a baseline implementation of more traditional machine learning based algorithm running on an NVidia Jetson hardware.

A benchmarking of neuromorphic processors using closed-loop applications, where the output of the processor is likely to affect its future input, was performed by Stewart, et. al., in 2015 [92]. The application is a relatively simple adaptive control program of a motor, where a neural network based algorithm is used by the program to improve its response in presence of disturbances that is randomized every time the benchmark is run. Instead of using a physical robot, they used a method known as Minimal Simulation [53] to introduce the variation in disturbances that is likely present in a physical system. They compared the performance of a neuromorphic processor (SpiNNaker) against a CPU and a GPU.

Instead of neural-network based applications, the capabilites of neuromorphic processors to perform more conventional, Message Parsing Interface (MPI) based parallel processing programs were tested in a benchmarking study by Urgese, et. al. [99], using a program for DNA sequence matching that is based on a text searching algorithm [61]. SpiNNaker was also used in this study, and it was compared against a server with two conventional CPUs.

Other than the publications mentioned above, there have also been several publications that aim to perform comparative studies on different platforms, both on neuromorphic architectures or other accelerators. In 2019, a study was conducted to compare the performance of Loihi with other more traditional architectures, on which this project is largely based [14]. The project used a keyword spotting algorithm based on a DNN architecture to measure the performance of Loihi compared to a CPU, GPU, and other accelerators such as NVidia Jetson and Movidius. Another similar study was conducted in 2020, pitting Loihi against SpiNNaker to compare their performance [107]. A more comprehensive discussion of these benchmarking studies is presented in Chapter 2.

Although evidently some progress has been made in the benchmarking of neuromorphic processors, the publications mentioned above vary in terms of metrics that were measured and the methodology used to measure them. Moreover, most of the comparative studies done focused more on comparing a neuromorphic architecture against a more conventional one, such as [99], [92], and [14]. Others that perform comparisons on two or more neuromorphic processors, such as [17] and [77] do not focus on going into detail to reveal which aspect or design choice of the benchmarked neuromorphic architecture gave the most impact in performance. As argued by Davies [20], one of the benefits of benchmarking is obtaining knowledge on the effects of design choices on performance, which is especially relevant in an emerging field such as neuromorphic computing. In general, we identified several areas in which improvements could be made:

- Since SENeCA is a new neuromorphic architecture, no benchmarking or comparative studies have been performed on it. Applying one of the benchmarks mentioned above on it will yield more insight, providing value to both the developers of SENeCA and future researchers.

- Most benchmarking studies mentioned above only have one/two workloads that represent real-world problems. While this is not an issue by itself, a real-world workload combined with a workload that benchmarks individual synaptic operations can provide an way of quantitatively comparing the fine-grained performance of different designs. This is similar to micro-benchmarks, which have been used to measure the fine-grained performance of GPUs [98] and network processors [9].

1.4. Contribution 5

No benchmarking publication thus far goes into the detail of measuring the power/energy consumption of individual components of the neuromorphic processor, instead they only the overall power/energy consumption. Knowing the power/energy consumption of individual components can reveal rooms for improvement in the design.

This study aims to perform benchmarking on SENeCA using an already existing benchmarking program that involves several iterations, with each iteration having a new optimization that involves a component in the architecture, to give better insight into the effect of the design choices present in the architecture on performance. Also, a secondary workload that benchmarks individual operations by SENeCA's neural processors will also be included. To do this, we will build upon the existing research by adapting the program used in [14] for SENeCA [109], instead of developing an entirely new benchmark. Regarding the metrics to be measured, we will base these upon [77], [17], and [14], which measure power consumption, time-to-solution, accuracy, and energy per inference, because they are more comprehensive than the measured metrics in [11], [92], and [99].

#### 1.4. Contribution

The main goal of this thesis is to further improve the knowledge about neuromorphic architecture and neuromorphic benchmarking. The main contributions of this thesis are summarized in the following.

- A new benchmarking methodology for neuromorphic processors: As mentioned by Davies [20], there is a strong need for standardized benchmarking suites for neuromorphic processors, and that is where we hope this thesis can contribute. More specifically, the multiple iteration approach, with each iteration having a specific optimization, in the methodology used here can give insight into the design of individual components and the effect of these deisgn choices on the performance. Furthermore, the inclusion of a micro-benchmark workload to benchmark individual synaptic operations can give more insight into the fine-grained performance. Although we do not claim to have a fully developed benchmarking suite, we hope that the methodology used here can serve as a reference for future researchers.

- Application of the new methodology on SENeCA: SENeCA [109] is a neuromorphic architecture that is designed to be flexible enough to accommodate future neural network designs. As it will be made open source to researchers with an academic background, we hope that by performing benchmarking on it, the design choices of SENeCA and their impact on performance can be better understood, such that other designs can build upon it.

- A new benchmarking implementation flow: As the aim of neuromorphic processors is to run an application based on neural networks in an energy efficient manner, the power-aware implementation flow can be of reference for future developers.

To summarize, this thesis proposes a new benchmarking and application development flow for neuromorphic processors, and implements this flow on one design, SENeCA.

#### 1.5. Thesis Organization

This thesis is divided into 7 chapters and an appendix. The organization of this thesis is summarized as follows:

- Chapter 1: this chapter will present the motivation, state-of-the-art analysis, problem statement, as well as the contribution of this research.

- Chapter 2: this chapter describes the necessary background information, mainly related to the field of neuromorphic processors. First, a brief history of artificial intelligence and computer architecture is presented, which leads to the motivation for neuromorphic computing. Then the basic

principles of neuromorphic computing are described, as well as several existing prototypes. Finally, an exploration of the literature related to the benchmarking of neuromorphic processors is presented.

- Chapter 3: this chapter describes in detail the architecture of the prototype neuromorphic processor that is the target of this research, SENeCA. First, an introduction to SENeCA is presented, along with its design principles and purpose. Then, a breakdown of SENeCA and its components is described, with a detailed explanation for each component. This chapter also includes a comparison of SENeCA with other existing prototype neuromorphic processors.

- Chapter 4: this chapter explains the design and implementation of the benchmarking software.

It begins with a description of the neural network model and architecture upon which the software

is based. Then, two sections will detail how this model is implemented in a PC and SENeCA,

respectively. The section describing the implementation on SENeCA is divided into 2 versions of

the software.

- Chapter 5: this chapter explains the experimental setup and methodology to measure the required performance metrics. Furthermore, this methodology will be implemented to the first 2 versions described in the previous chapter, and the results of those experiments will be presented. Furthermore, a section detailing an experiment to measure individual operations performed in SENeCA is also included.

- Chapter 6: this chapter describes the optimization process to obtain a faster and more energyefficient software implementation. There are five versions in total, each obtained by analyzing the previous version to find room for improvement. For every version, an explanation of the optimization technique and implementation, performance measurement results, and power consumption measurement results are described. This chapter also includes a section dedicated to the measurement of accuracy of the SENeCA implementation.

- Chapter 7: in the final chapter, a summary and ideas about future work are described.

# Neuromorphic Architectures and Benchmarking

This chapter introduces the necessary background information and dives more deeply into the literature currently available on neuromorphic architectures and benchmarking. First, Section 2.1 introduces Artificial Neural Networks (ANN). Section 2.2 will elaborate on why standard CPUs were limited for ANN operations. Section 2.3 will explain other architectures used for ANN operations before neuromorphic chips. Next, Section 2.4 will explain the design principles of neuromorphic architecture. Afterwards, Section 2.5 will dive into the available literature on neuromorphic chips. Finally, Section 2.6 will dive into the literature on bencmarking neuromorphic processors.

#### 2.1. Artificial Neural Network

In the early days of artificial intelligence (AI), a field developed to realize man's dream of a machine that can think, problems that were difficult for humans but straightforward for computers were rapidly tackled. These problems could be described formally by mathematical rules without much difficulty. The real challenge came with problems that were difficult to describe but easy for humans to solve. These are the problems that we solve intuitively that feel automatic to us. These problems include recognizing faces from photographs and recognizing spoken words from an audio recording [40].

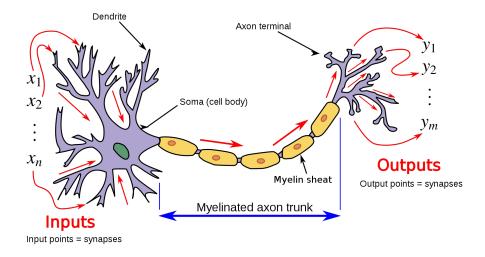

Figure 2.1: An illustration of a biological neuron [29]

The multilayer perceptron, another name for the Artificial Neural Network (ANN), is a solution for these more intuitive problems, as conventional algorithms had little success. This solution is based on the architecture of the human brain [40]. In general, ANNs consist of artificial neurons, which are based on the biological neuron cell found in human brains. Figure 2.1 depicts a biological neuron, also known as a nerve cell. Put simply, the neuron consists of the dendrites, the cell body (soma), the axon trunk, and the axon's terminals. The dendrites receive input signals from other neurons. The dendrites then transmits these signals to the soma, with "adjustments". These adjustments depend on the dendrite's "weight" values, and depending on these values, dendrites can either amplify or diminish the signals sent to the soma. The soma then performs a summation of the signals from the dendrites. Every time the summation value in the soma exceeds a certain value, it emits a pulse signal and then sends it further to the axon. The axon's synaptic terminals, which are connected to other neuron's dendrites, pass the signal on to other neurons, repeating the process [73].

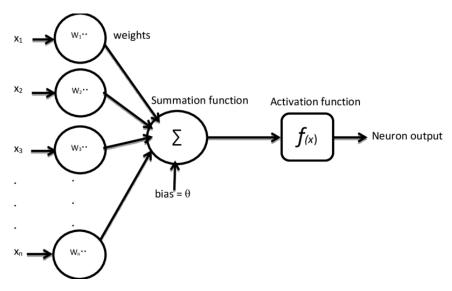

Figure 2.2: An illustration of an artificial neuron [106]

The artificial neuron is a mathematical model of the biological neuron [6]. Figure 2.2 depicts the model. In this analogy, the dendrites can be seen as the input of the artificial neuron. Each dendrite has a "weight" value, and the input of that dendrite is multiplied by its weight value. This models the amplifying or diminishing action done by biological dendrites. The soma can be seen as the node, where the summation of the weighted input values from the dendrites takes place. After that, a bias term is added to the sum, and then it is passed through a non-linear activation function, producing an output. These are analogous to the threshold value of the soma. The output of the neuron, analogous the axon, sends the output value to other neurons [40].

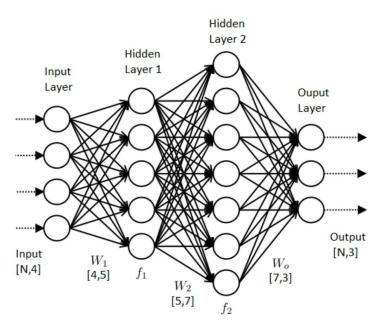

Figure 2.3: An illustration of a simple ANN [2]

An ANN is a network consisting of artificial neurons described above. Since the artificial neurons have a node and connections with other neurons, the network can be represented with a graph, with the neurons being the nodes and the connections being the edges. Figure 2.3 illustrates an example ANN. Each ball is a neuron, and each arrow represents a connection between the neurons. Here, the neurons are divided into four layers. Here, a neuron in a hidden layer receives inputs from all

neurons in preceding layer, and sends its output to all neurons in the following layer. Since the data flows in a single direction, these type of ANNs are called feedforward networks. This is known as a Fully-connected, or dense, network [8]. The number of neurons and the layer configuration can vary based on the application.

As explained above, each neuron in a layer has connections to all neurons in the preceding layer. Also, each connection has a weight value assigned to it. In Figure 2.3, for example, each neuron in layer f1 (Hidden Layer 1) receives inputs from the four Input Layer neurons. Therefore, each neuron of layer f1 has four weight values. Since there are five neurons in layer f1, we can represent the 20 (four times five) weight values with a 4X5 matrix, named W1. Each layer has its own weight matrix, whose size depends on the number of neurons in that layer and the preceding layer. The weight matrices for the next layers are termed W2 and Wo. Also, each neuron has a bias term which is added to the sum of the inputs. The bias terms of neurons of a layer can be represented by a vector b, whose number of elements correspond to the number of neurons in the layer. Likewise, the inputs and outputs of a layer can also be represented by vectors, here termed x and a.

The relationship of the input vector, weight matrix, bias vector, and output vector of a layer L is defined by a function [40]. Typically, it takes the form of Equation 2.1.

$$Output_L = A_j = F(\sum_{i=0}^{n} W_{ij}.X_i + b_j)$$

(2.1)

F is the activation function,  $A_j$  is the output vector,  $X_i$  is the input vector,  $W_{ij}$  is the weight matrix and  $b_j$  is the bias vector of that layer, with j=(0,..,m) and i=(0,..,n) where m and n are the number of neurons of layer L and the preceding layer, respectively. In other words, to obtain the output, a weighted sum of all inputs is calculated. Then, a bias term is added to the weighted sum and an activation function is applied. Various activation functions are used, such as the Heaviside function (Equation 2.2) and the Rectified Linear Unit (ReLU) (Equation 2.3) [42].

$$F(x) = \begin{cases} 1 & \text{if } x > 0 \\ 0 & \text{if } x \le 0 \end{cases}$$

(2.2)

$$F(x) = max(0, x) \tag{2.3}$$

In essence, the objective of the neural network (NN) is to approximate a certain function. The multilayer feedforward ANNs are proven to be universal approximators [47]. An example of the application of ANN is described in [13], where images of handwritten digits are classified according to the digit in the image. In this case, the input is the pixel values of the images, while the output is a vector of probabilities for each number (0-9). To do this, the parameters of the neural network (weight values, bias values) are adjusted based on the learning process [40]. There are various forms of learning, generally divided into supervised and unsupervised learning. Unsupervised learning attempts to cluster unlabeled datasets by discovering hidden patterns in the data [45]. In supervised learning, the NN is presented with a labeled dataset, also known as the training data. During the learning process, the dataset is fed as input to the NN, and the output of the NN is compared against the correct output (the label), which produces an error value. This value is used to adjust the weights in such a way as to minimize the error value. A common method used the adjust the connection weights is backpropagation using stochastic gradient descent [84]. When this process is run repeatedly, the error rate may decrease. After the learning process in complete, the NN can be fed with actual data (also known as the test data) to evaluate its performance. This is known as the inference process [40].

From Equation 2.1, we can see that the majority of the arithmetic operations are done in the  $\sum_{i=0}^n W_{ij}.X_i$

summation, which is basically a matrix multiplication. In ANNs that are designed to approximate complex functions, the number of neurons may be very large. For example, AlexNet, a neural network used to classify images of the ImageNet database, has over 650,000 neurons and 6 million parameters [63].

A subset of these parameters have to be accessed every time calculations take place, making it a very data-intensive application.

#### 2.2. Limits of Traditional CPU

In computers that are based on the von Neumann architecture, the memory and the computing elements are separated from each other [80]. The computing element is a processor that executes sequences of machine instructions, such as arithmetic and logic operations. The memory is an element that can store the data. Typically, a Random Access Memory (RAM) is the type of memory used to store working data and machine instruction.

As argued in [48], the amount of energy required to read or write data to the RAM can be 1,000 times higher than the energy required to execute one computing operation. In addition, the maximum throughput at which data from the RAM can be transferred to the processor is usually limited by the width of the data bus (that connects the processor to the RAM), and much lower than the rate at which the processor can process the data. This results in latency and processor downtime while it waits for the data to arrive. This makes the bus that connects the processor and the RAM a significant bottleneck. This phenomenon is known as the Memory Wall. Many innovations in computer architecture have been developed to solve this bottleneck problem [80].

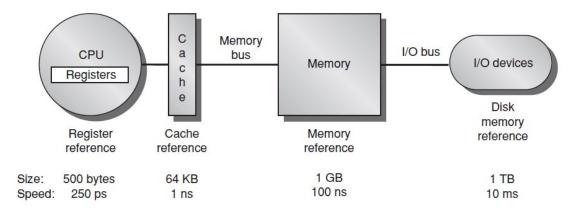

One solution to this problem is the introduction of a memory element closer to the processing unit. Modern processors usually have several layers of memory accessible to it, ranging from registers (small memory cells that are quickly accessible) to several layers of caches, to the RAM which is usually located on a separate chip [44]. Memory that is located close to the processor can be accessed quickly with little energy, but the size of the memory is limited. Accessing data located in the off-chip RAM, for example, requires a relatively large amount of time and energy compared to accessing data in the L1 cache. Figure 2.4 illustrates this point.

Figure 2.4: Memory hierarchy of the von Neumann architecture [44]

In architectures such as the one illustrated by 2.4, the weight matrix of ANNs described in Section 2.1 will most likely be stored in the RAM, since for most networks the weight matrix will be too large to store in the memory closer to the processor. Thus, the processor will often need to perform a read operation on the RAM to obtain the required weights or inputs (since the input vector is also likely to be stored in the RAM). As mentioned above, the data bus will limit the speed at which the operations can be executed. Furthermore, the number of weights increases exponentially depending on the number of neurons, inputs, and layers. This means that for larger networks, the time required to transfer the data will dominate the execution time [51].

2.3. GPU and TPU

Recent architectures, such as the AMD 3D V cache [104], attempt to solve this problem by introducing a larger cache. These caches, which can comprise around 40% of the chip area, can provide tens of megabytes of fast memory. Depending on the size of the network, this might allow the entire weight matrix of an ANN to be stored in the cache, allowing faster execution. Strategies to decrease the execution time for CPUs, such as speculative execution, branch prediction, and others mentioned in [80], are not applicable for ANNs, since the execution order is known beforehand. Other solutions depart from the traditional CPU architecture, such as the Graphics Processing Unit (GPU) and Tensor Processing Unit (TPU) architectures.

#### 2.3. GPU and TPU

The GPU was initially developed to handle computer graphics [80]. It provides multiple streaming multiprocessors. These processors are smaller and slower than a typical CPU, but since there are several of them, calculations of multiple neurons can be executed simultaneously. Also, these streaming multiprocessors have large register files that can be used to store data from various contexts. If a single context currently has an operation that has a large latency, such as a memory read operation, the processor can execute instructions from other contexts instead. Regarding memory throughput, manufacturers such as NVIDIA began adding High Bandwidth Memory (HBM), bringing the memory throughput to 1.5 TB/s in the A100 architecture, released in 2020 [4].

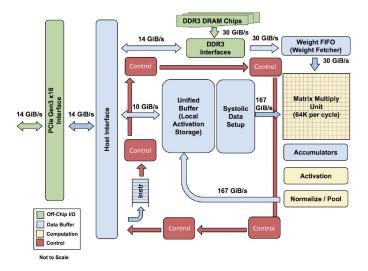

A more recent architecture that is more specialized in neural network operations is the TPU, introduced by Google in 2015 [55]. This architecture attempts to solve the memory bandwidth problem by using systolic arrays in combination with software-controlled memory. At its heart lies a computational device that consists of 256x256 8-bit multiply-and-accumulate computational units. This is shown in Figure 2.5 as the Matrix Multiply Unit. Each unit has a memory that can store a weight value and is connected to four other units in a two-dimensional matrix. It performs two operations. First, it multiplies the input received from the unit above by the weight and adds that result to the number received from the unit to the left. Then it sends the input received from above to the unit below it without changing it and passes the sum obtained previously to the right. Essentially, it performs matrix multiplication in a pipeline, which is, as mentioned previously, the most time-consuming operation of an ANN. Also, this concept aims to minimize the number of operations that involve the memory, especially the storage and retrieval of intermediate results, since these are mostly stored in the memory of the MAC processors themselves.

Figure 2.5: TPU Block Diagram [55]

2.3. GPU and TPU 13

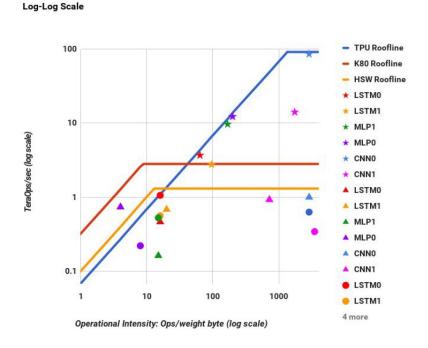

In 2017, a performance test was published that compared the TPU architecture with other architectures mentioned above (CPU and GPU) [57]. The CPU and GPU were the Haswell (HSW) and K80 architectures, respectively. The study used six DNN applications run on three architectures. The study findings can be summarized in Figure 2.6. This uses the Roofline Performance model [103]. The performance of a specific architecture (in TeraOps/sec) is plotted against the operational intensity (in Ops/weight byte). Without enough operational intensity, the programs will be memory-bound, represented by the slanted part of the roofline. The flat part of the roofline represents the computation-bound area, where the processor speed becomes the bottleneck. As can be seen in the graph, the performance of the applications is quite close to the roofline for the TPU and lower for the CPU and GPU.

Figure 2.6: Roofline performance model of TPU (stars), GPU (triangles), and CPU (circles) [57]

The architecture of the TPU was shown to be more efficient in running DNN programs than the GPU and the CPU architectures [56]. Compared to the GPU, it was 15 times faster, while it was 29 times faster when the power consumptions of both are taken into account. Against the CPU, the numbers were 29 and 83, respectively. Several factors enable the TPU to have such a performance advantage:

- 1. The 2D Matrix Multiplication Unit of the TPU is more suited to matrix multiplication operations compared to the 1D multiplication units of the CPU and GPU.

- 2. The applications run on the TPU use 8-bit integers instead of 32-bit floating points.

- 3. The 2D arrangement of the processing units of the MMU allows for systolic arrays, reducing register access and energy consumption.

- 4. The TPU has only one thread, instead of the 13 threads of the GPU and 18 threads of the CPU, enabling it to save energy.

The TPU and GPU architectures have shown that they can run neural network programs faster and more energy-efficient compared to the traditional CPUs. However, these architectures are mainly designed for large-scale computing. For example, the Thermal Design Power (TDP) of the TPU in [55] is 75 W, while that of the K80 GPU architecture is 150 W. While that may be acceptable for computers in offices or datacenters, the power consumption may be too high for other situations, such as Edge AI or embedded applications. Thus, another type of architecture, termed "Neuromorphic Architecture", tries to fill this gap by focusing more on energy efficiency [1].

#### 2.4. Principles of Neuromorphic Architectures

Information processing systems found in animals are very different from von Neumann architectures that are used in traditional computers [40]. Although these computers excel at performing operations such as arithmetic calculations, they are much less efficient in tackling problems whose input data are ill-conditioned and whose computation can be relatively specified. These problems include fields such as voice recognition, image processing, and others that have been influential in recent years. For tackling these kinds of problems, biological systems are orders of magnitude more efficient compared to traditional digital computers in terms of energy [70].

Despite the advances in architecture mentioned above, there are still gaps between the efficiency of animal brains and digital computers. Thus, the application of other design principles present in the brain structure can also possibly lead to further improvements. In recent years, this has led to the birth of neuromorphic computing.

The term neuromorphic engineering is a concept that was first developed by Carver Mead [70], and it was used to describe the use of VLSI (Very Large Scale Integration) systems containing electronic analog circuits to mimic neuro-biological architectures present in the nervous system [1]. More recently, the term neuromorphic architectures is generally used to describe analog, digital, and software systems that implement several models of neural systems [1]. It takes inspiration from the brain to develop energy-efficient circuits and systems for information processing. Several properties of neuromorphic architectures have been identified and explained by Ivanov et al., which appear to be useful in creating computer systems that can solve real-life problems [51]. Also, a taxonomy of neuromorphic architecture was presented by Bose, et al., in [15]. These principles differentiate neuromorphic architectures from the others.

- 1. Usage of non-von Neumann architecture, memory and computing are interspersed

- 2. Impulse nature of information transmission, low overhead for signal transmission

- 3. Sparsity of data streams, event-driven signal processing

An explanation of each principle is presented in the following.

#### 2.4.1. Usage of Non-von Neumann Architecture

When performing neural network operations on a CPU, one core (or several cores, depending on the exact processor used) models a large number of neurons, sequentially switching context between them [51]. This creates a significant time and energy overhead to read/write the neuron state values or weights back and forth to the memory. A biological neuron, on the other hand, is simultaneously a device capable of storing its state and weights (by its membrane potential and strength of synaptic connections), and a computing device. This approach is free from the traditional von Neumann memory wall, rooted in physical separation of the memory and the processor. A possible implementation in silicon computers is to have each core of a neuromorphic processor model a single neuron only [50]. In digital implementations, it is possible to have several neurons modeled by a single core with limited context switching.

#### 2.4.2. Low Overhead of Information Transmission

GPUs, while more efficient at performing neural network operations than a CPU, is still not optimally suited when energy consumption is factored in [16]. One reason is that in GPUs, the shared memory, which is a large (relative to the memory of the streaming multiprocessors) memory block able to be accessed by all the multiprocessors, is usually used for data transmission between neurons [74]. In biological systems, the information transmission occurs differently.

As explained in Section 2.1, a biological neuron generates electrical pulses that travel down its axon to communicate with other neurons. Sensory neurons, for example, are spiking neurons, and they change the temporal pattern of their electrical pulses depending on the external stimuli (light, sound, etc.) [1]. A sequence of pulses is also known as a spike train, and these spikes convey information based on their firing rate. Other neurons, such as specialized graded potential neurons, can communicate through

spikes containing graded potentials [87]. These neurons have the advantage of higher information rates, because they are capable of encoding more states in a single spike than the spiking neurons. Both of these communication schemes are used in neuromorphic processors. For example, Loihi uses the rate coding approach [22], while SENeCA uses the graded potential spikes approach [109].

#### 2.4.3. Sparsity of Data Streams

Studies of the brain show that only a small part of the brain, around 10%, is active at any time simultaneously [88]. This sparsity may be one of the reasons why the brain is much more energy efficient compared to a digital computer that runs a neural network program. It is very different from the execution of the inference phase of a classical ANN program, where every neuron is involved in calculations. Several factors explain this difference.

First, there are several cases in which subsequent inputs are quite similar to each other. An example is a Dynamic Vision Sensor (DVS), containing a computer vision program designed to detect an object that receives input from a stationary camera [90]. This allows traffic to be drastically decreased by transmitting only the differences between frames, instead of information from every pixel all the time. This is called temporal sparsity.

The second factor is the threshold value of the membrane potential. This threshold allows a neuron not to output any signal even though it has received input. This leads to spatial sparsity. In an ANN, this concept is implemented using biases that are added at the end of matrix multiplication operations and subsequent application of the activation function [40]. A neuron that does not fire would be similar to an artificial neuron that has an output of zero. In many CPU or GPU architectures, exploiting these fine-grained sparsities will not result in any performance benefit.

The third and last factor is the sparseness of the neural connection graph. As noted in [18], synaptic pruning occurs during the development of the human brain, resulting in the elimination of connections between neurons that are not needed. This results in a network with relatively few connections compared to the number of neurons, as opposed to a fully connected ANN. Each neuron has a rather limited number of connections (around 5000). This is called structural sparsity.

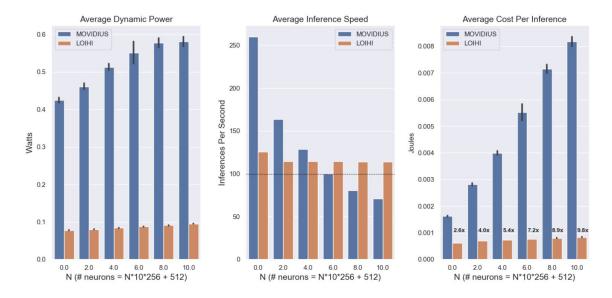

#### 2.5. Examples of Current Neuromorphic Architectures