# **A Compact Sub-1V Capacitively-Biased BJT-Based Temperature Sensor**

By

Sanja Kastratović

Supervisors:

Prof. dr. K.A.A. Makinwa

Dr. Z. Tang

In partial fulfilment of the requirements for the degree of

**Master of Science in Electrical Engineering**

At the Department of Microelectronics

Faculty of Electrical Engineering, Mathematics and Computer Science

Delft University of Technology

To be defended on November 30<sup>th</sup>, 2023

Student number: 5506239

Thesis Committee: Prof. Dr. K.A.A. Makinwa

Dr. D.G. Muratore

Dr. K. Souri

# Abstract

This thesis presents the design of a low-power, sub-1V, BJT-based temperature sensor. It is based on a capacitively-biased (CB) BJT front-end, in which capacitors are discharged across diode-connected BJTs to obtain proportional-to-temperature (PTAT) and complementary-to-temperature (CTAT) voltages. These voltages are then digitised by a switched-capacitor Delta-Sigma Modulator (DSM), which employs energy-efficient inverter-based amplifiers that can operate from a sub-1V supply. To mitigate the effects of component mismatch and 1/f noise, dynamic error-cancellation techniques such as chopping, auto-zeroing and dynamic element matching are used in both the front-end and the DSM. After a 1-point temperature calibration, the sensor achieves a simulated inaccuracy of  $\pm 0.20^\circ\text{C}$  ( $3\sigma$ ) over temperatures ranging from  $-55^\circ\text{C}$  to  $125^\circ\text{C}$ . From simulations, it does this while operating from a 0.9V supply and dissipating only 270nW. It occupies an estimated area of  $0.066\text{mm}^2$  in a 180nm CMOS process. Compared to previous CB temperature sensors, this design occupies 3.8x smaller area and dissipates 3x less power.

# Acknowledgements

The last two years have been a journey of personal and professional growth. Here, I would like to thank those who were there to share the happiest moments as well as help me push through the many difficulties encountered. Without them, I wouldn't have been able to reach this point in my life.

First and foremost, I would like to thank my supervisor, Prof. Dr. Kofi Makinwa, for giving me the opportunity to join the EI group and work on such an interesting project. During the past year, he shared his wisdom, knowledge and guidance, providing me with enough support and also independence to build myself into the engineer I am today.

Secondly, I would like to thank my daily supervisor Dr. Zhong Tang who provided enormous support throughout the past year and without whom this thesis couldn't have been completed. Even though he left the lab a few months into my thesis, he was always willing to have hours-long technical discussions and encourage me whenever I felt falling behind.

I would like to extend my enormous gratitude to SiTime, specifically Dr. Kamran Souri, soon-to-be Dr. Jan Angevare and Dr. Saleh Shalmany, for stepping in when I felt completely lost about my thesis and giving me the helping hand to move forward. They invested invaluable time and I am grateful for all the knowledge I gained from them. It was an incredible experience having both input from an academic and industrial perspective and I hope to keep this in my mind moving forward in my career.

I want to thank the Microelectronics Department for the scholarship that allowed me to come to Delft in the first place and pursue this degree.

I want to thank the EI team, all the PhDs and other MSc students on the 15<sup>th</sup> floor, for the shared discussions, laughter, food, and late nights filled with work. Among them, I want to extend special thanks to Avish, Jida, Shenyang, Giorgos, Sundeep, Nandor and Miloš. I want to thank all the friends I met in Delft, for sharing all the good memories and making me feel at home in this city: Shruti, Nivedita, Chieh, Maciej, İlker, Andrea, Deb, Sari, and the list goes on. Additionally, I want to thank my friends scattered across the world who provided me with emotional support throughout these two years despite the time zones: Nouf, Mariam, Mao, Ahmad, Hadi, Milena and Adrian.

Last but not least, I want to thank my family for always having my back, never judging me and always believing in me. I wouldn't have been here without their continuous love and support.

# Table of Contents

|               |                                                                              |           |

|---------------|------------------------------------------------------------------------------|-----------|

| <b>1</b>      | <b>Introduction .....</b>                                                    | <b>11</b> |

| <b>1.1</b>    | <b>Motivation .....</b>                                                      | <b>11</b> |

| <b>1.2</b>    | <b>Types of CMOS temperature sensors .....</b>                               | <b>11</b> |

| <b>1.2.1</b>  | <b>Operating principle of BJT-based temperature sensors .....</b>            | <b>12</b> |

| <b>1.3</b>    | <b>Capacitive Biasing .....</b>                                              | <b>13</b> |

| <b>1.4</b>    | <b>CBD-based temperature sensors .....</b>                                   | <b>15</b> |

| <b>1.4.1</b>  | <b>State-of-the-art CBD-based temperature sensor .....</b>                   | <b>17</b> |

| <b>1.5</b>    | <b>Project goals .....</b>                                                   | <b>20</b> |

| <b>1.6</b>    | <b>Organisation of the thesis .....</b>                                      | <b>21</b> |

| <b>2</b>      | <b>System level design .....</b>                                             | <b>23</b> |

| <b>2.1</b>    | <b>Reducing the area of the CBD SC temperature sensor .....</b>              | <b>23</b> |

| <b>2.2</b>    | <b>Scaling the front-end .....</b>                                           | <b>24</b> |

| <b>2.3</b>    | <b>Charge balancing readout scheme .....</b>                                 | <b>28</b> |

| <b>2.4</b>    | <b>Scaling the autozero capacitors <math>C_{AZ}</math> .....</b>             | <b>29</b> |

| <b>2.3.1</b>  | <b>Amplifier choppers .....</b>                                              | <b>32</b> |

| <b>2.5</b>    | <b>Summary .....</b>                                                         | <b>35</b> |

| <b>3</b>      | <b>Circuit implementation .....</b>                                          | <b>36</b> |

| <b>3.1</b>    | <b>CBD Front-end .....</b>                                                   | <b>36</b> |

| <b>3.1.1</b>  | <b>Scaling down the PNP .....</b>                                            | <b>36</b> |

| <b>3.1.2</b>  | <b>Scaling down the front-end sampling capacitor, <math>C_s</math> .....</b> | <b>39</b> |

| <b>3.1.3.</b> | <b>Front-end biasing voltage generator .....</b>                             | <b>43</b> |

| <b>3.2</b>    | <b>Delta-sigma modulator readout .....</b>                                   | <b>44</b> |

| <b>3.2.1</b>  | <b>DSM topology .....</b>                                                    | <b>44</b> |

| <b>3.2.3</b>  | <b>Amplifier design .....</b>                                                | <b>44</b> |

| <b>3.2.3</b>  | <b>Implementation of the 2<sup>nd</sup> integrator .....</b>                 | <b>51</b> |

| <b>3.3</b>    | <b>Timing control .....</b>                                                  | <b>52</b> |

| <b>3.3.1</b>  | <b>Clock boosters .....</b>                                                  | <b>53</b> |

| <b>3.3</b>    | <b>Area estimation .....</b>                                                 | <b>55</b> |

| <b>3.4</b>    | <b>Summary .....</b>                                                         | <b>56</b> |

| <b>4</b>      | <b>Simulation results .....</b>                                              | <b>57</b> |

|                                                              |    |

|--------------------------------------------------------------|----|

| <b>4.1 Modulator behaviour .....</b>                         | 57 |

| <b>4.2 Accuracy.....</b>                                     | 59 |

| <b>4.2.1 Power supply sensitivity of the front-end .....</b> | 62 |

| <b>4.3 Layout and area estimation .....</b>                  | 63 |

| <b>4.4 Power dissipation .....</b>                           | 64 |

| <b>4.5 Resolution.....</b>                                   | 66 |

| <b>4.5.1 Figure of merit.....</b>                            | 67 |

| <b>4.6 Summary.....</b>                                      | 68 |

| <b>5 Conclusion and future work.....</b>                     | 69 |

| <b>5.1 Conclusion .....</b>                                  | 69 |

| <b>5.2 Future work .....</b>                                 | 69 |

| <b>5.2.1 Reducing the conversion period .....</b>            | 69 |

| <b>5.2.2 Reducing digital power.....</b>                     | 69 |

| <b>5.2.3 Reducing analog power.....</b>                      | 69 |

| <b>Bibliography.....</b>                                     | 74 |

# List of Figures

|                                                                                                                                                                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1 Working principle of a BJT-based temperature sensor.....                                                                                                                                                                                        | 12 |

| Figure 1.2 CTAT and PTAT behaviour of VBE and $\Delta VBE$ [4].....                                                                                                                                                                                        | 13 |

| Figure 1.3 a) Static-biased diode; b) Capacitively-biased diode.....                                                                                                                                                                                       | 14 |

| Figure 1.4 Working principle of a capacitively-biased diode [1] .....                                                                                                                                                                                      | 14 |

| Figure 1.5 Switch-capacitor CBD-based sensor circuit [2].....                                                                                                                                                                                              | 16 |

| Figure 1.6 CBD-based temperature sensor with DTMOST as sensing element: a) VCTAT generator; b) DTMOST sensing code; c) relaxation oscillator [7].....                                                                                                      | 17 |

| Figure 1.7 Block diagram of a CBD-based temperature sensor [13].....                                                                                                                                                                                       | 17 |

| Figure 1.8 Single-sided switched-capacitor (SC) integrator with embedded CB PNP front-end [1] .....                                                                                                                                                        | 18 |

| Figure 1.9 Block level architecture of the CBD sensor proposed in [1].....                                                                                                                                                                                 | 19 |

| Figure 1.10 Measured bitstream average $3\Delta VBEVBE$ 1 over temperature of chip [1] .....                                                                                                                                                               | 19 |

| Figure 1.11 Measured bitstream average $\mu = 3\Delta VBEVBE$ across temperature for a time ratio $p=32$ and $p=64$ .....                                                                                                                                  | 20 |

| Figure 2.1 Die micrograph of chip in [1].....                                                                                                                                                                                                              | 23 |

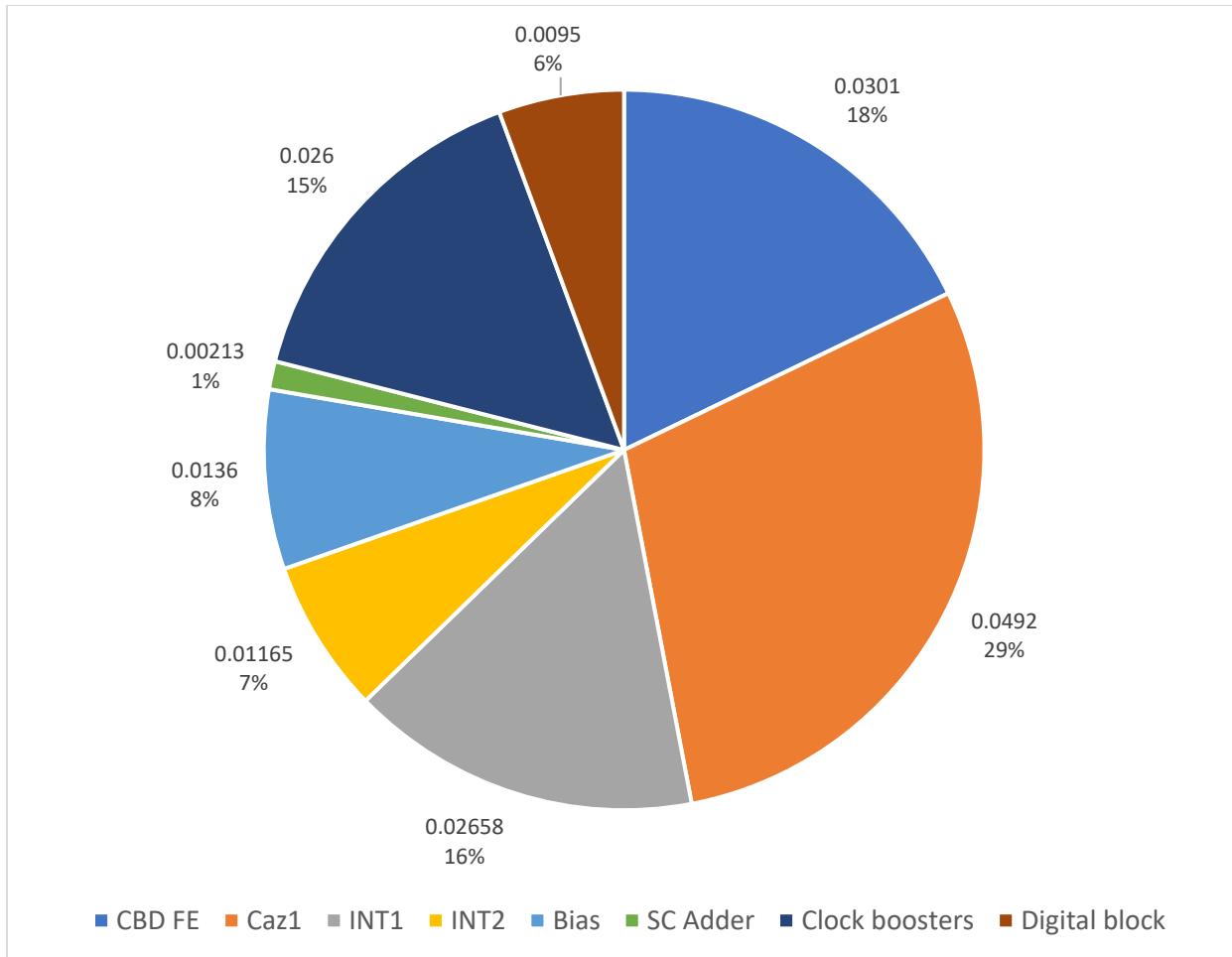

| Figure 2.2 Area distribution of the chip in [1] in $mm^2$ .....                                                                                                                                                                                            | 24 |

| Figure 2.3 Current through a diode ( $ID$ ) versus discharge time ( $t$ ) for different CS sizes from $500fF$ to $16pF$ .....                                                                                                                              | 25 |

| Figure 2.4 BJT's $\beta$ variation with respect to emitter current $I_E$ .....                                                                                                                                                                             | 26 |

| Figure 2.5 a) Temperature error in $\Delta VBE$ at different $I_{bias}$ currents; b) Static biasing of two BJTs. ....                                                                                                                                      | 27 |

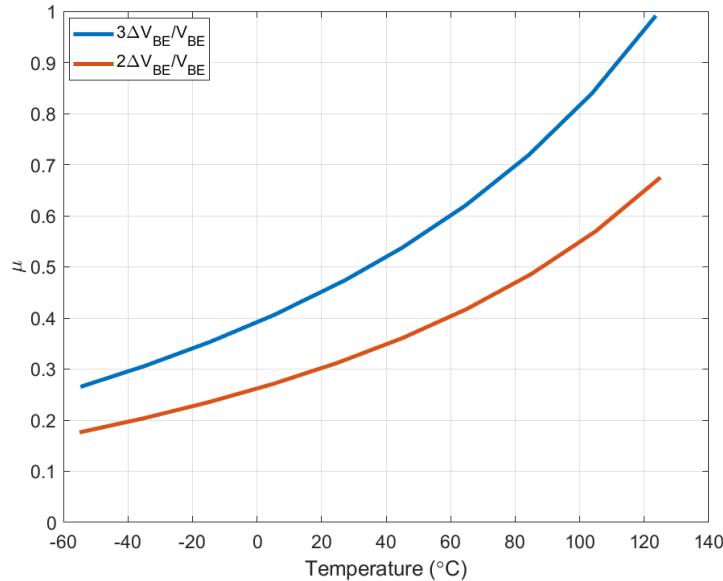

| Figure 2.6 Simulated value of $\mu = 3\Delta VBEVBE$ and $\mu = 2\Delta VBEVBE$ across temperature, for $p = 32$ ..                                                                                                                                        | 28 |

| Figure 2.7 Proposed charge balancing scheme.....                                                                                                                                                                                                           | 28 |

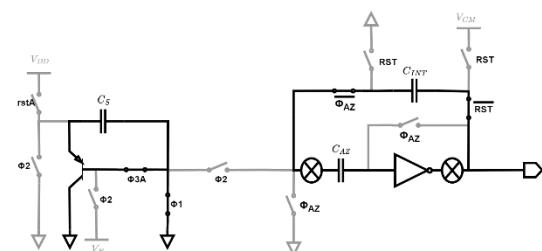

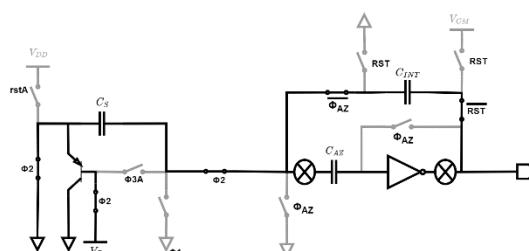

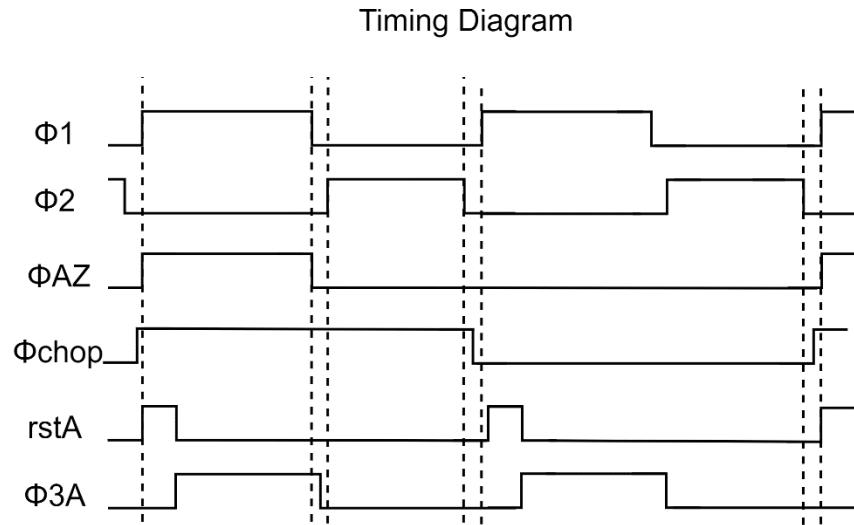

| Figure 2.8 a) Front-end and the inverter-based integrator and b) their timing diagram.....                                                                                                                                                                 | 29 |

| Figure 2.9 Single-sided inverter-based amplifier in a) autozero phase; b) integration phase. ....                                                                                                                                                          | 30 |

| Figure 2.10 Noise folding due to autozeroing. ....                                                                                                                                                                                                         | 31 |

| Figure 2.11 Chopper added to the first integrator: a) autozero phase; b) integration phase.....                                                                                                                                                            | 32 |

| Figure 2.12 Noise power spectral density (PSD) versus frequency with a) autozero; b) autozero and chopping for $f_{CH} < f_{AZ}$ ; c) autozero and chopping for $f_{CH} \geq f_{AZ}$ . ....                                                                | 32 |

| Figure 2.13 Chopping sampled noise on CAZ in the time domain.....                                                                                                                                                                                          | 33 |

| Figure 2.14 a) Integrator behaviour; b) Timing diagram. ....                                                                                                                                                                                               | 35 |

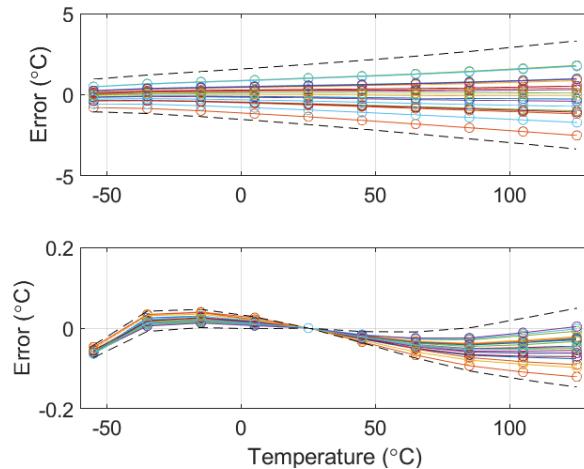

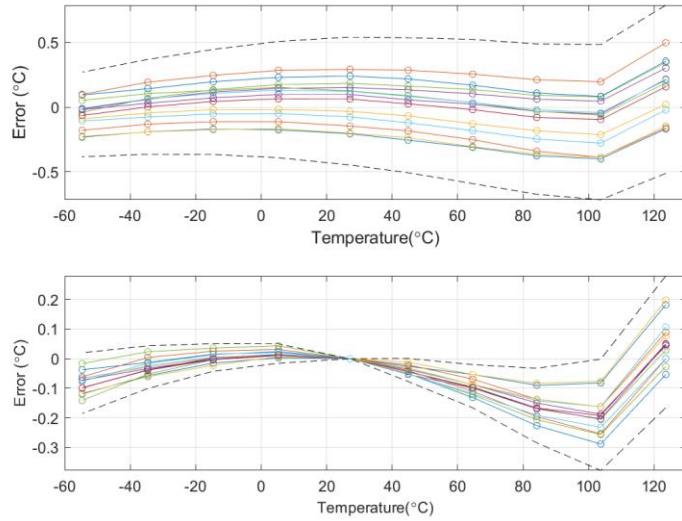

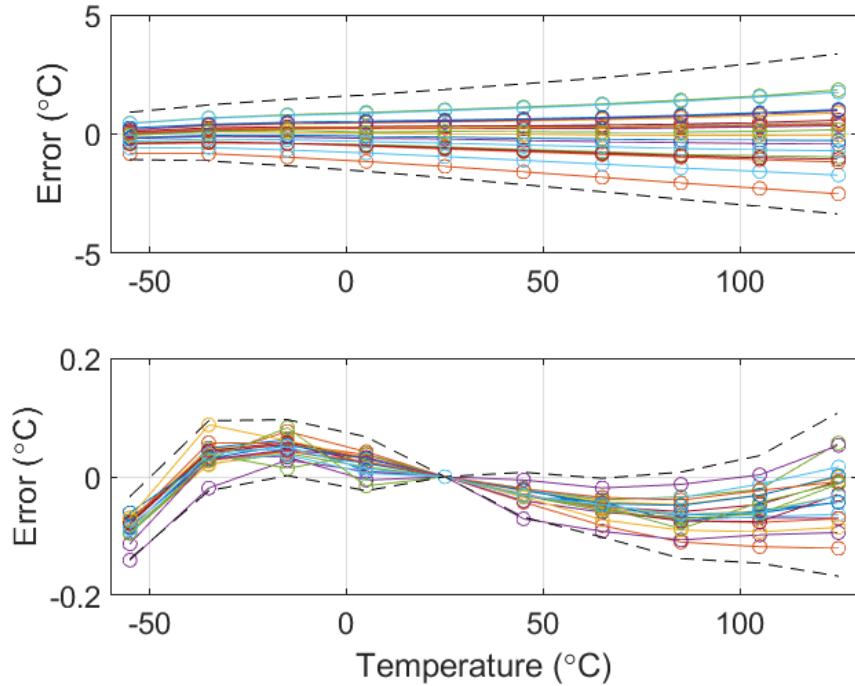

| Figure 3.1 Monte Carlo (20 points, mismatch and process spread) SC CBD inaccuracy with ideal switches and $C_S = 490fF$ , $VDD=0.9V$ and $p = 32$ without (top) and with a 1-point PTAT trim at $25^\circ C$ (bottom).....                                 | 36 |

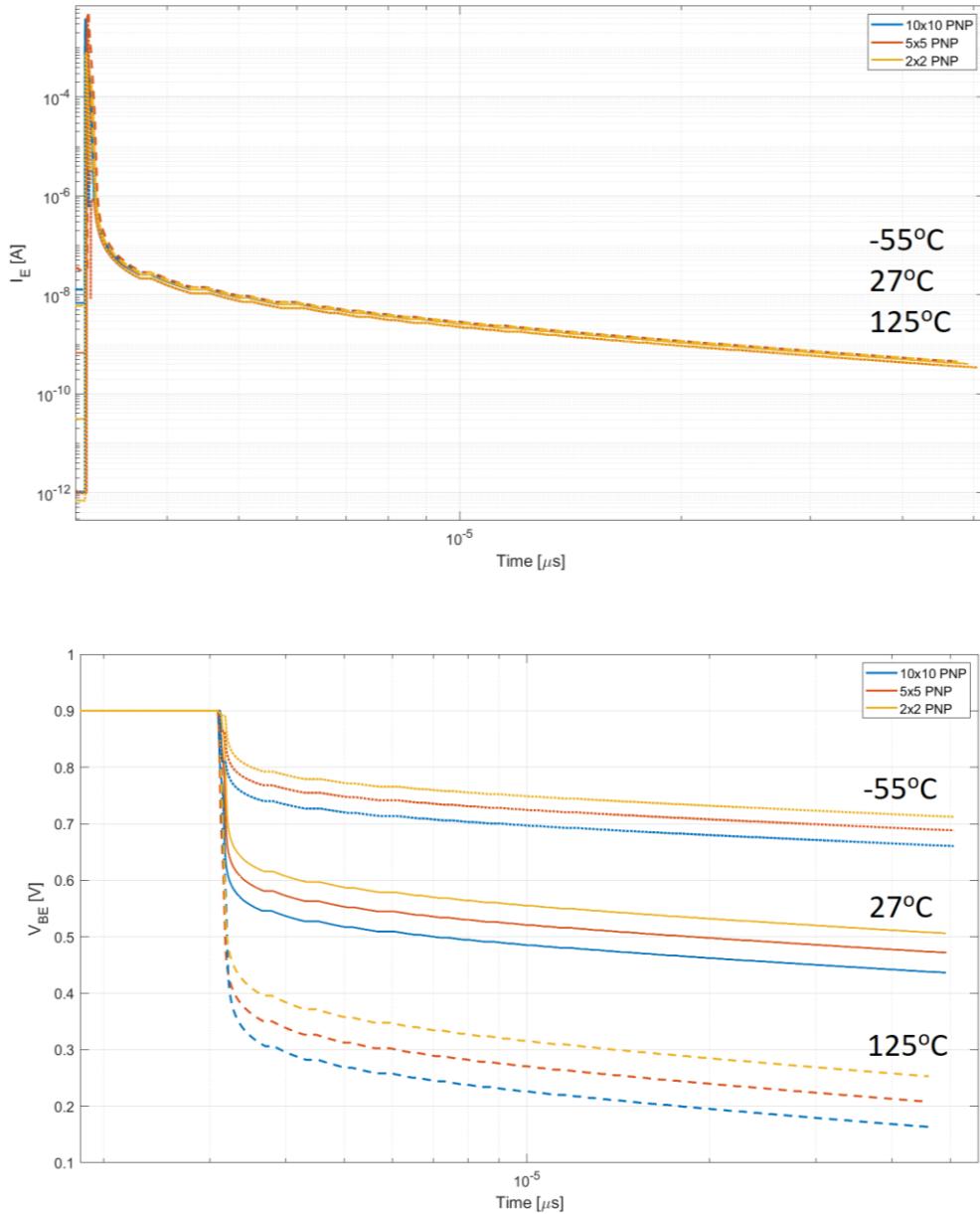

| Figure 3.2 a) $I_E$ and b) $V_{BE}$ versus time for PNPs of different areas with $C_S = 490fF$ and $VDD=0.9V$ across temperature.....                                                                                                                      | 37 |

| Figure 3.3 Monte Carlo (20 points, mismatch and process spread) SC CBD inaccuracy with real switches and $C_S = 490fF$ , $VDD=0.9V$ and $p = 32$ without (top) and with a 1-point PTAT trim at $25^\circ C$ (bottom) for a) $2x2$ PNP; b) $10x10$ PNP..... | 38 |

| Figure 3.4 Decimated output over temperature for a $2x2$ , $5x5$ and $10x10$ PNP device with $C_S = 490fF$ and $p = 32$ for a) $VDD = 0.9V$ and b) $VDD = 0.95V$ .....                                                                                     | 38 |

| Figure 3.5 CBD Front-end with NPN device.....                                                                                                                                                                                                              | 39 |

|                                                                                                                                                                                                                                                                                      |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

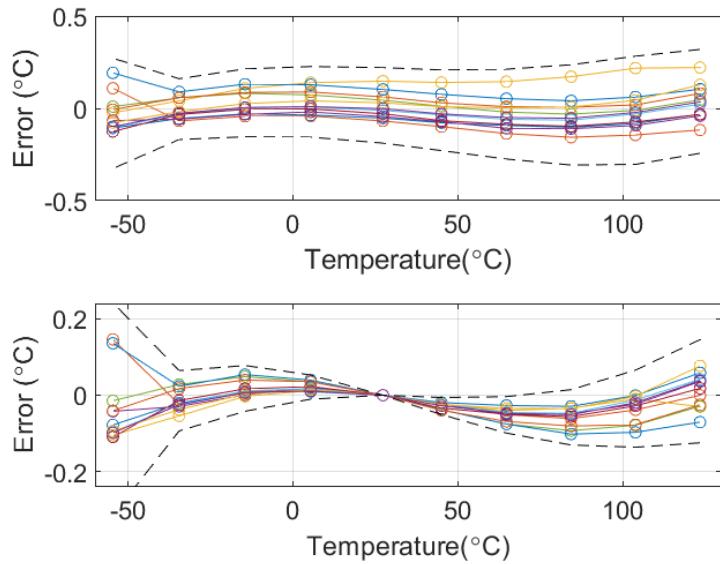

| Figure 3.6 Measured inaccuracy of a 1x1 NPN-based CBD front end without (top) and with a 1-point PTAT trim at 25°C (bottom).....                                                                                                                                                     | 39 |

| Figure 3.7 Measured inaccuracy of a 5x5 PNP-based CBD front end with $C_s = 0.8\text{pF}$ without (top) and with a 1-point PTAT trim at 25°C (bottom).....                                                                                                                           | 40 |

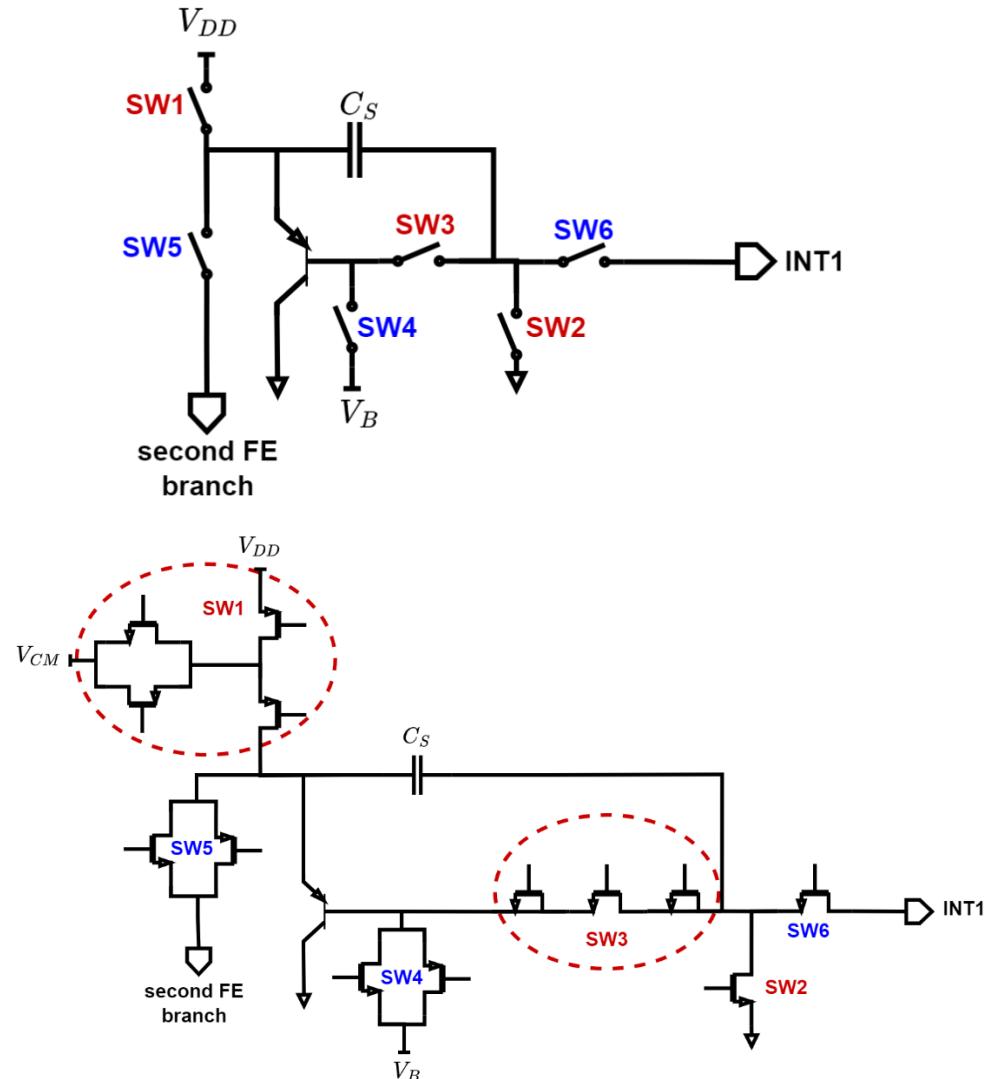

| Figure 3.8 Single-sided front-end with switches a) representation; b) real implementation.....                                                                                                                                                                                       | 41 |

| Figure 3.9 Monte Carlo (20 points, mismatch and process spread) SC CBD inaccuracy with real switches and $C_s = 800\text{fF}$ and $p = 32$ without (top) and with a 1-point PTAT trim at 25°C (bottom) for a) $V_{DD} = 0.9\text{V}$ and b) $V_{DD} = 0.95\text{V}$ .....            | 42 |

| Figure 3.10 Monte Carlo (20 points, mismatch and process spread) SC CBD inaccuracy with real switches and $C_s = 800\text{fF}$ and $p = 32$ , for halved discharge time $t_1$ and $t_2$ without (top) and with a 1-point PTAT trim at 25°C (bottom) for $V_{DD} = 0.9\text{V}$ ..... | 43 |

| Figure 3.11 Front-end biasing circuit and its timing diagram.....                                                                                                                                                                                                                    | 43 |

| Figure 3.12 DSM Block architecture.....                                                                                                                                                                                                                                              | 44 |

| Figure 3.13 Switch-capacitor implementation of first integrator.....                                                                                                                                                                                                                 | 45 |

| Figure 3.14 Single-sided inverter-based amplifier in a) autozero phase; b) integration phase.....                                                                                                                                                                                    | 46 |

| Figure 3.15 a) Monte Carlo amplifier's DC gain; b) Amplifier's input-referred noise at room temperature.....                                                                                                                                                                         | 47 |

| Figure 3.16 OTA Biasing circuit.....                                                                                                                                                                                                                                                 | 47 |

| Figure 3.17 First integrator with choppers.....                                                                                                                                                                                                                                      | 49 |

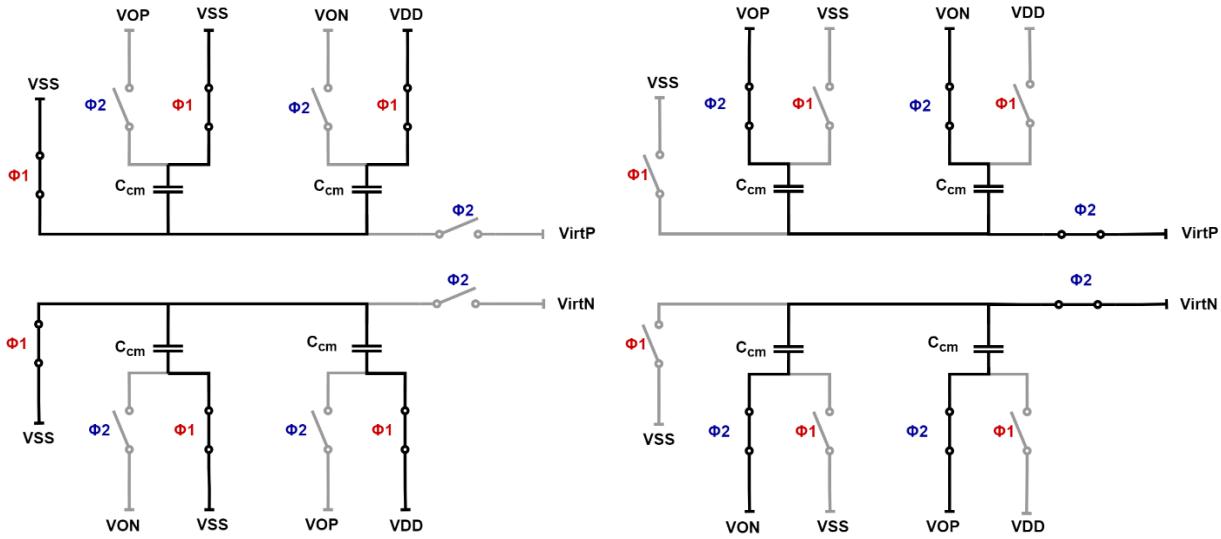

| Figure 3.18 CMFB circuit during a) $\Phi_1$ and b) $\Phi_2$ .....                                                                                                                                                                                                                    | 50 |

| Figure 3.19 a) Front-end VCM shift circuit diagram; b) Voltage across $C_S$ and parasitic capacitors during sampling and integration phase.....                                                                                                                                      | 51 |

| Figure 3.20 Second integrator.....                                                                                                                                                                                                                                                   | 52 |

| Figure 3.21 System-level chopping.....                                                                                                                                                                                                                                               | 53 |

| Figure 3.22 Dynamic element matching (DEM) timing diagram.....                                                                                                                                                                                                                       | 53 |

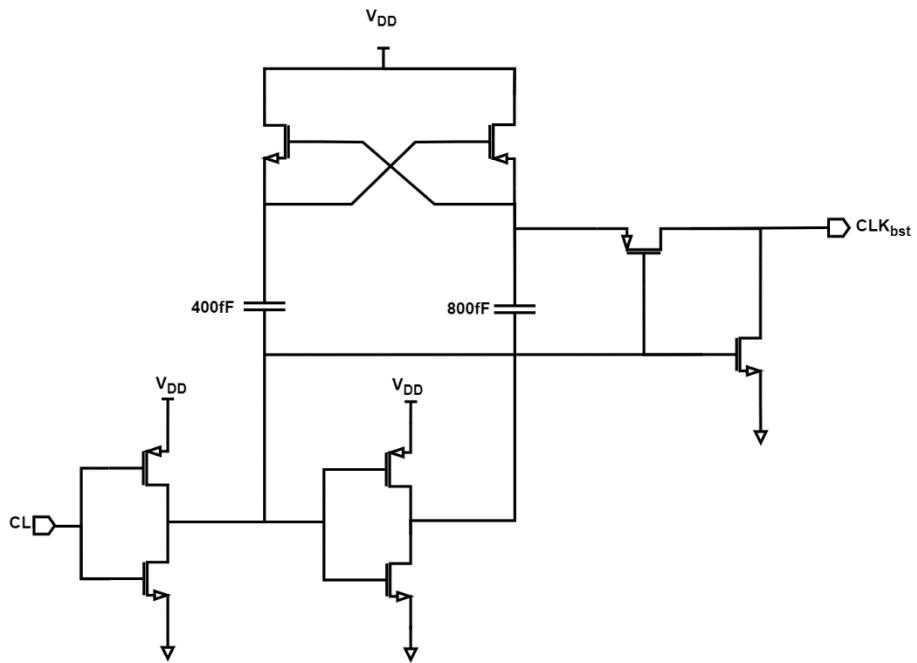

| Figure 3.23 Circuit schematic of the implemented single-capacitor clock booster [16].....                                                                                                                                                                                            | 54 |

| Figure 3.24 Circuit schematic of the clock boosters in [1].....                                                                                                                                                                                                                      | 54 |

| Figure 3.25 Area distribution in $\text{mm}^2$ of each block in a) design in [1]; b) this design.....                                                                                                                                                                                | 55 |

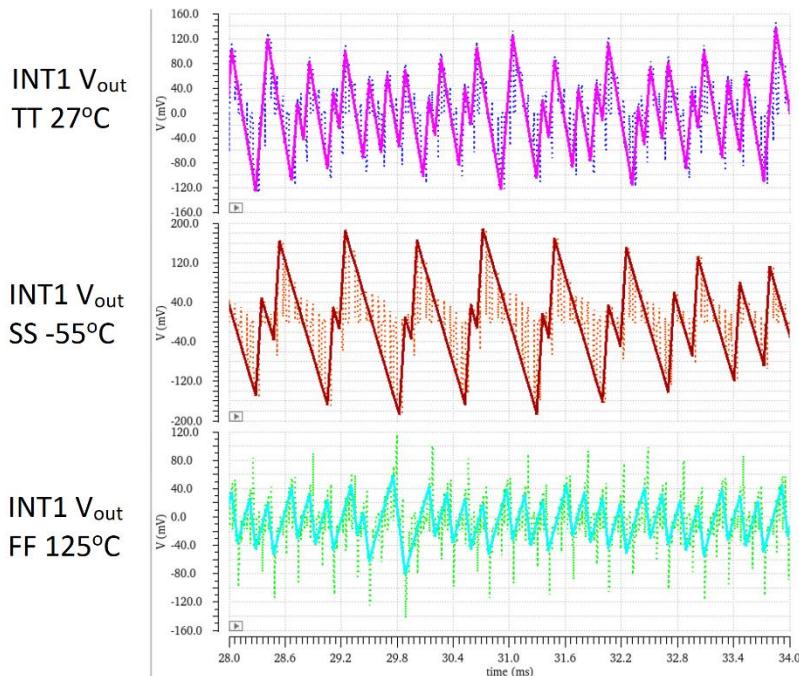

| Figure 4.1 Output swing of the first integrator across corner and temperature.....                                                                                                                                                                                                   | 57 |

| Figure 4.2 Output swings of the a) 2nd integrator; and b) the SC adder across corners and temperature.....                                                                                                                                                                           | 58 |

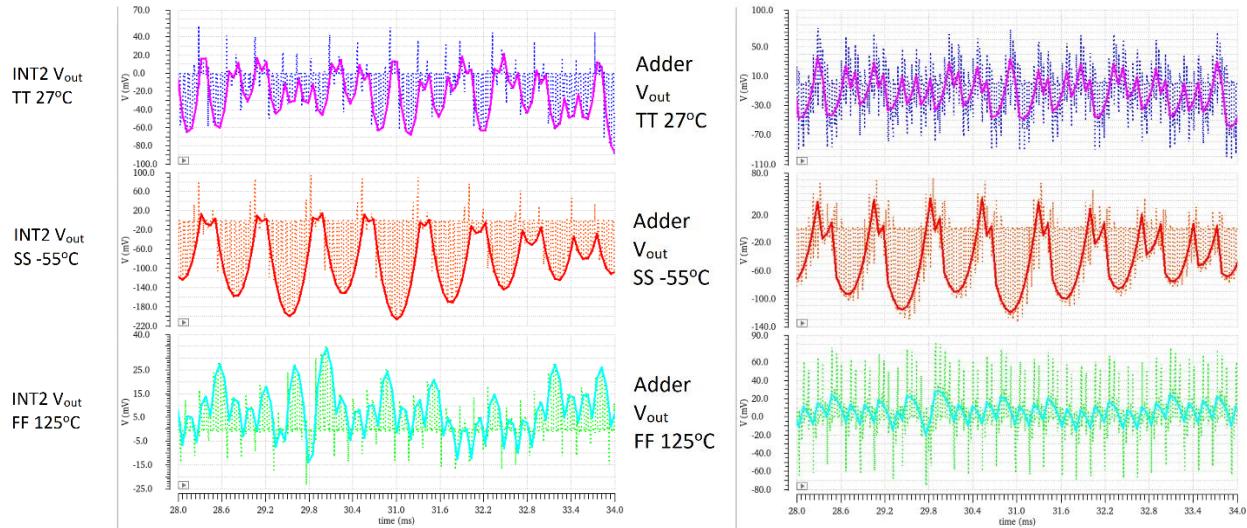

| Figure 4.3 Output VCM of the a) 1st integrator and b) 2nd integrator across temperature and corner.....                                                                                                                                                                              | 59 |

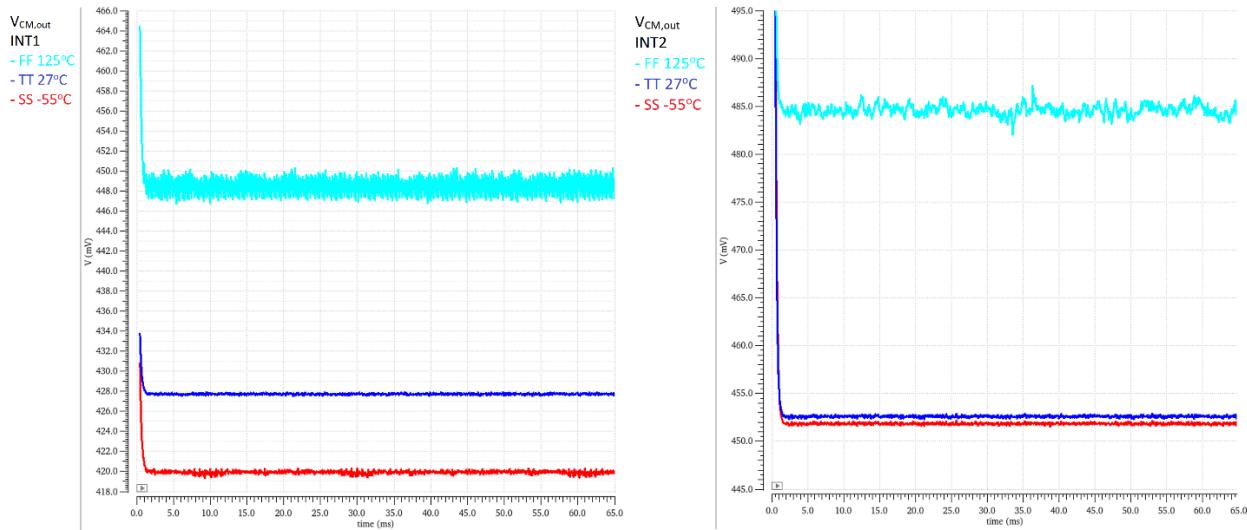

| Figure 4.4 Input VCM of the front-end across temperature and corner.....                                                                                                                                                                                                             | 59 |

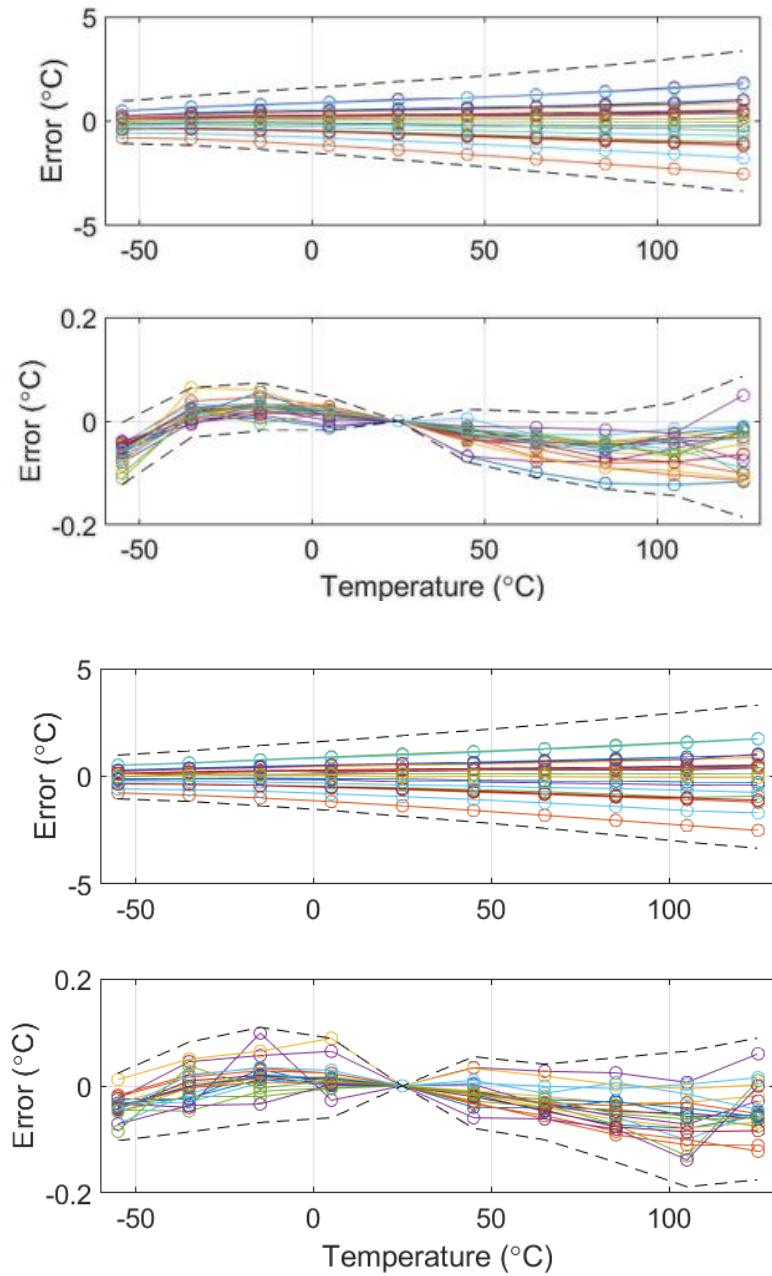

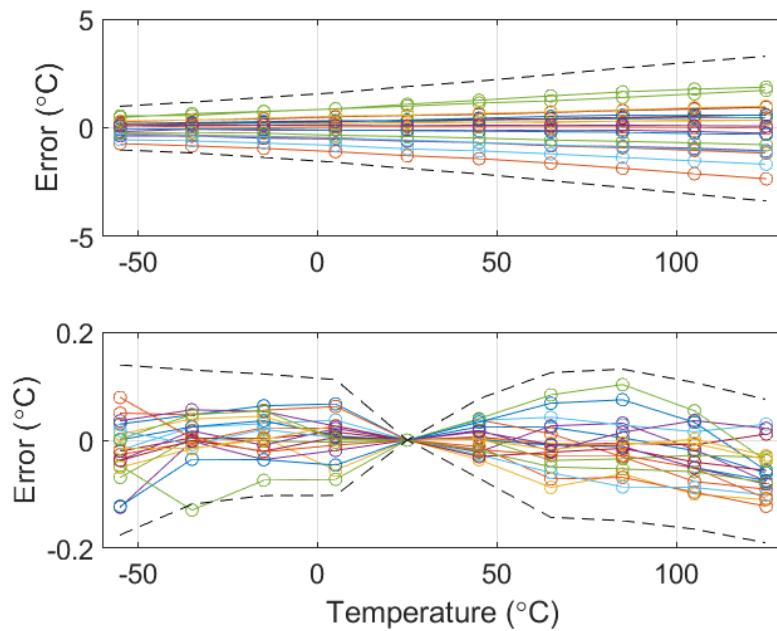

| Figure 4.5 Monte Carlo (20 points, mismatch and process spread) inaccuracy of the front-end and first integrator (without OTA choppers) with $C_s = 800\text{fF}$ , $V_{DD}=0.9\text{V}$ and $p = 32$ without trimming (top) and with a 1-point PTAT trim at 25°C (bottom).....      | 60 |

| Figure 4.6 Monte Carlo (20 points, mismatch and process spread) inaccuracy of the front-end and first integrator with OTA choppers with $C_s = 800\text{fF}$ , $V_{DD}=0.95\text{V}$ and $p = 32$ without (top) and with a 1-point PTAT trim at 25°C (bottom).....                   | 61 |

| Figure 4.7 Monte Carlo (20 points, mismatch and process spread) inaccuracy of the front-end and first integrator with OTA choppers with $C_s = 800\text{fF}$ , $V_{DD}=0.95\text{V}$ and $p = 32$ without (top) and with a 1-point PTAT trim at 25°C (bottom).....                   | 61 |

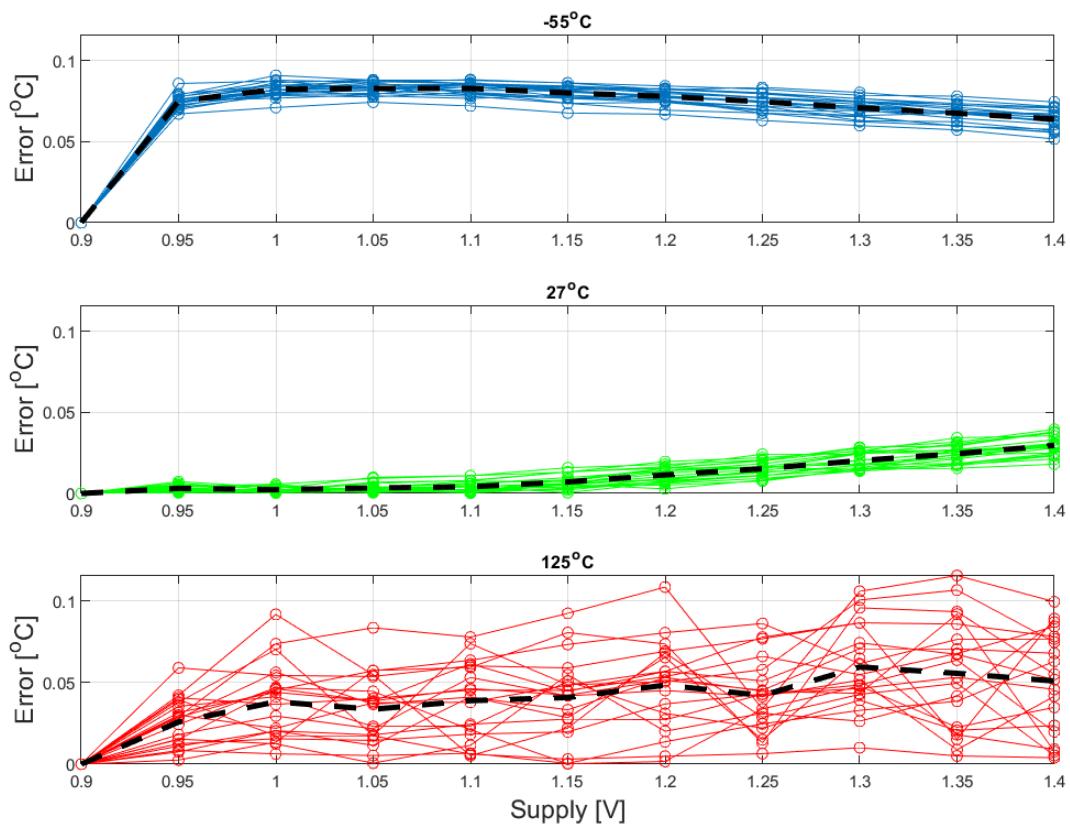

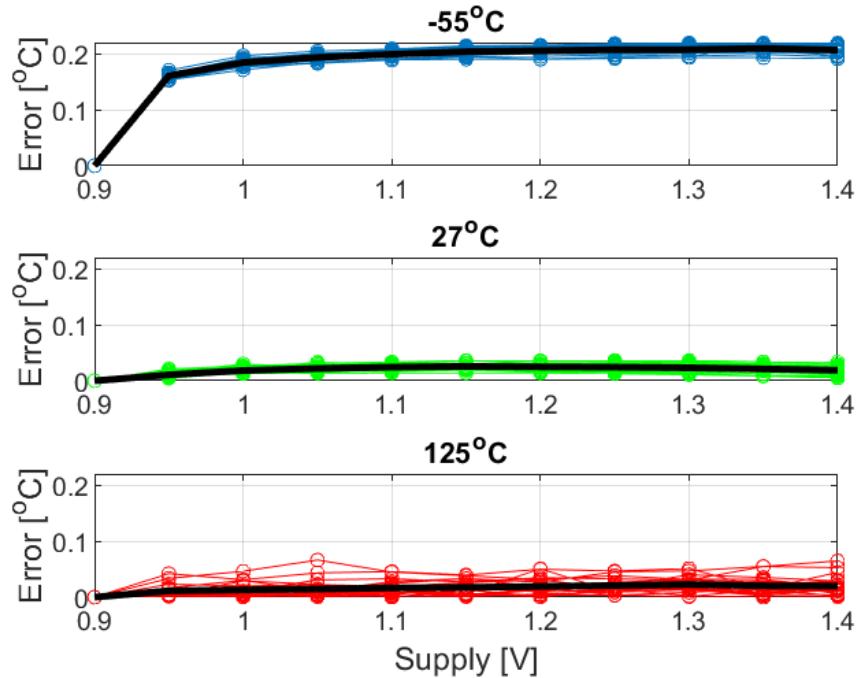

| Figure 4.8 Monte Carlo (20 points, process spread) simulation of power-supply sensitivity (PSS) at a) SS - 55°C; b) TT 27°C; c) FF 125°C.....                                                                                                                                        | 62 |

|                                                                                                                                                                                |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <i>Figure 4.9 Monte Carlo (20 points, process spread) simulation of power-supply sensitivity (PSS) with halved discharge time at a) SS -55C; b) TT 27oC; c) FF 125oC. ....</i> | 63 |

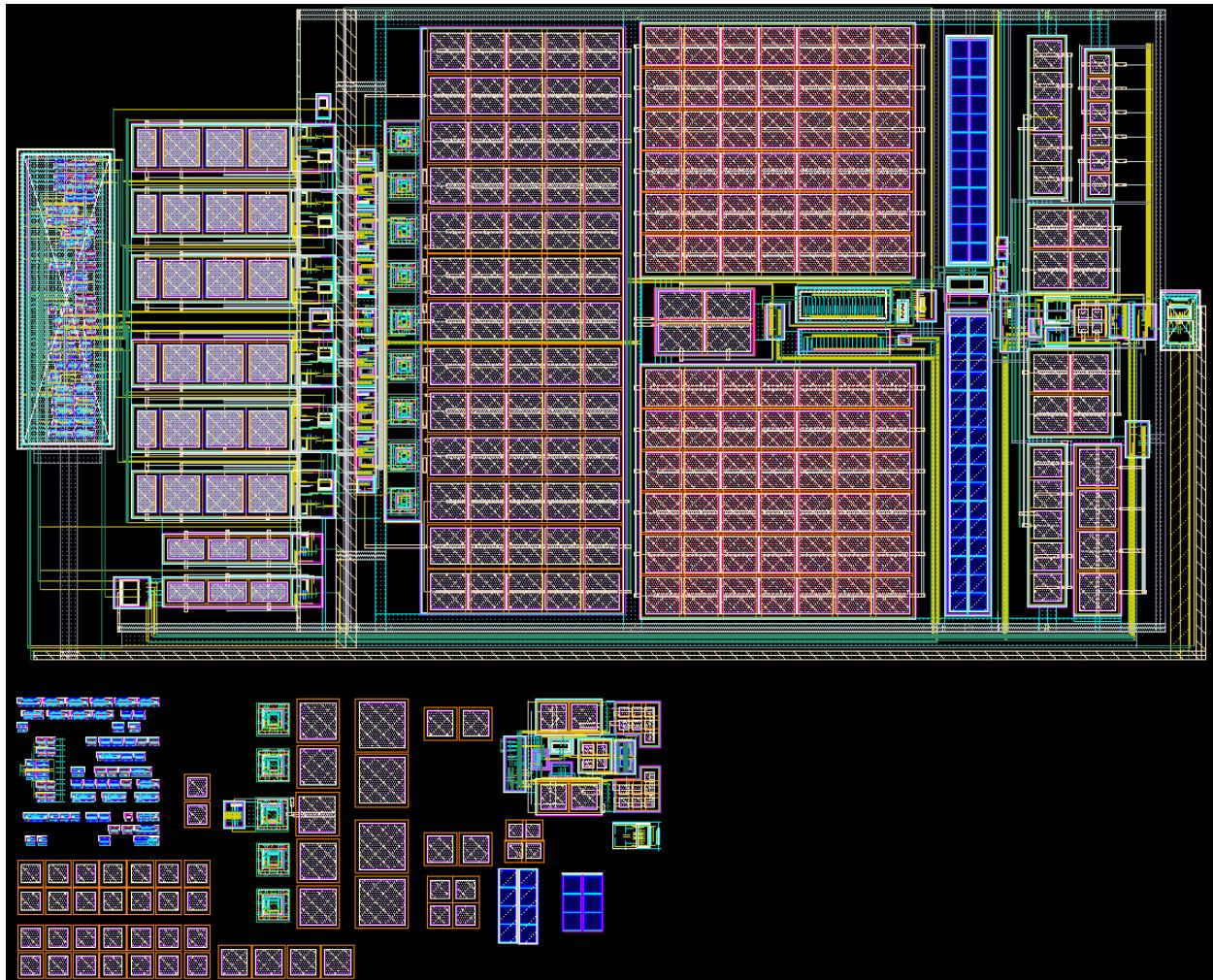

| <i>Figure 4.10 Area comparison of design in [1] (top) and estimated layout of this design (bottom). ....</i>                                                                   | 64 |

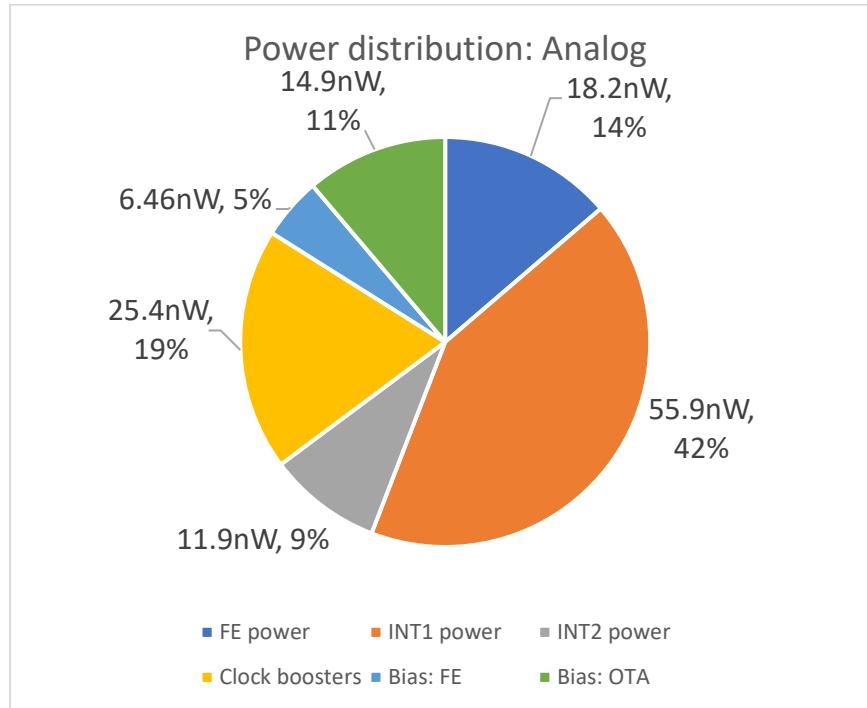

| <i>Figure 4.11 Simulated analogue power consumption breakdown per block at 0.9V supply. ....</i>                                                                               | 65 |

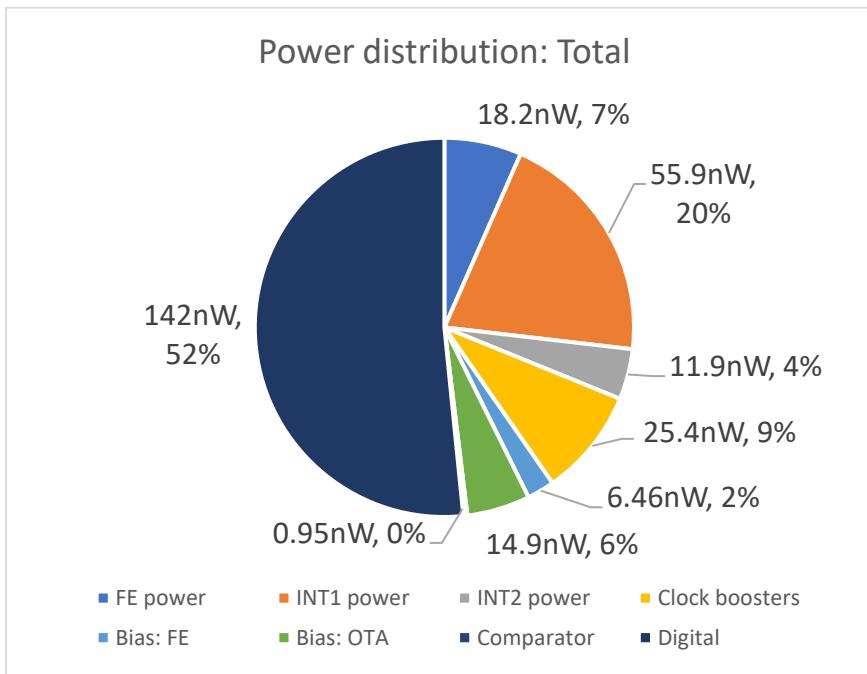

| <i>Figure 4.12 Simulated total power consumption breakdown per block at 0.9V supply. ....</i>                                                                                  | 65 |

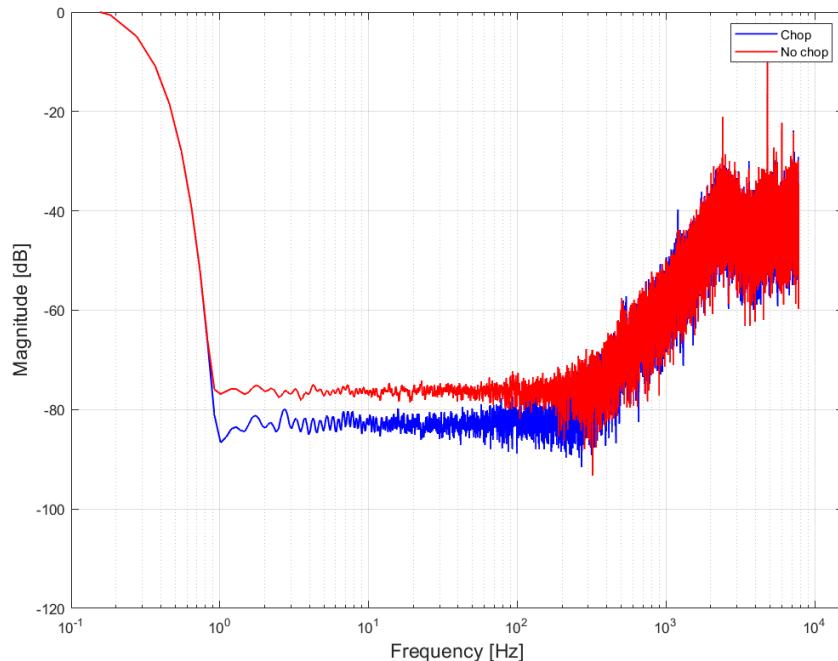

| <i>Figure 4.13 Modulator's frequency response with and without chopping. ....</i>                                                                                              | 66 |

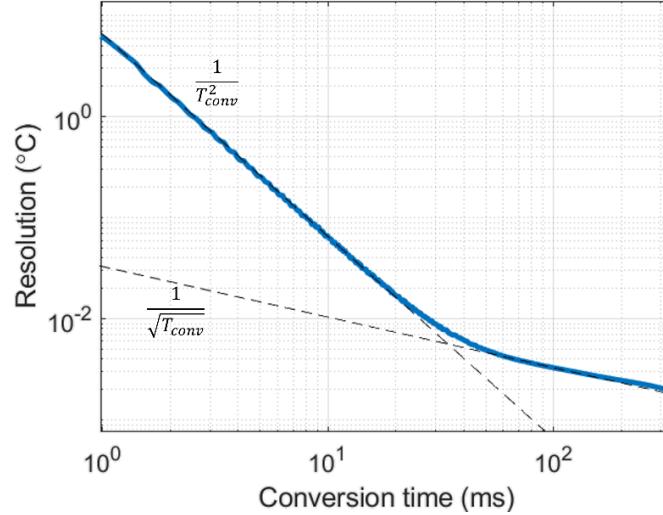

| <i>Figure 4.14 Resolution versus conversion time. ....</i>                                                                                                                     | 67 |

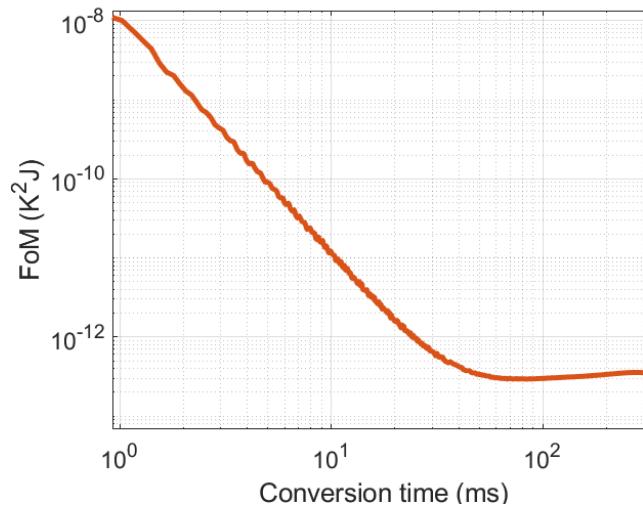

| <i>Figure 4.15 Figure of Merit versus conversion time. ....</i>                                                                                                                | 67 |

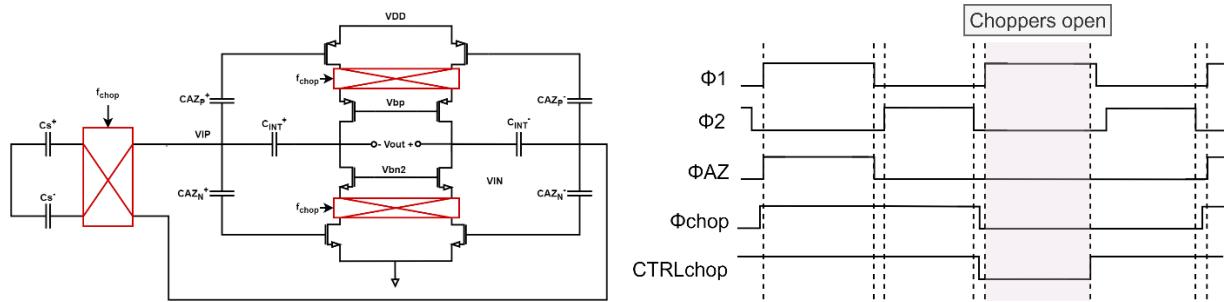

| <i>Figure 5.1 a) Schematic of the first amplifier and b) choppers timing signal. ....</i>                                                                                      | 70 |

| <i>Figure 5.2 Opreation of the proposed ping-pong front-end with its timing diagram. ....</i>                                                                                  | 72 |

# List of Tables

|                                                                                                                                              |    |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| <i>Table 1.1 Comparison of the state-of-the-art low-supply temperature sensors.</i> .....                                                    | 21 |

| <i>Table 3.1 Coefficients for the implemented DSM.</i> .....                                                                                 | 44 |

| <i>Table 3.2 Dominant capacitor values in the original [1] and this design.</i> .....                                                        | 56 |

| <i>Table 4.1 Output swings of the a) 1st integrator; b) 2nd integrator; c) switched-capacitor adder across temperature and corner.</i> ..... | 58 |

| <i>Table 4.2 Comparison of power consumption between the original [1] and this design at VDD = 1V.</i> .....                                 | 66 |

| <i>Table 4.3 Performance summary and comparison to the state-of-the-art.</i> .....                                                           | 68 |

# List of Abbreviations

|        |                                        |

|--------|----------------------------------------|

| ADC    | analog-to-digital converter            |

| BJT    | bipolar junction transistor            |

| BS     | bitstream                              |

| CB     | capacitively-biased                    |

| CBD    | capacitively-biased diode              |

| CMFB   | common mode feedback                   |

| CTAT   | complementary to absolute temperature  |

| DEM    | dynamic element matching               |

| DSM    | delta-sigma modulator                  |

| FoM    | figure of merit                        |

| GBW    | gain bandwidth                         |

| HVT    | high threshold voltage                 |

| IoT    | internet of things                     |

| OSR    | oversampling ratio                     |

| OTA    | operational transconductance amplifier |

| PSD    | power spectral density                 |

| PSS    | power supply sensitivity               |

| PTAT   | proportional to absolute temperature   |

| RIA    | relative inaccuracy                    |

| SC     | switched-capacitor                     |

| S(Q)NR | signal to (quantisation) noise ratio   |

| TD     | thermal diffusivity                    |

# 1 Introduction

## 1.1 Motivation

Temperature is one of the most extensively measured environmental parameters due to its influence on the behaviour of nearly all physical, chemical, mechanical, and biological systems. Therefore, temperature sensors find broad application in various fields, including healthcare and the automotive industry, particularly for the purpose of correcting temperature-induced inaccuracies in analog circuits. Given the accuracy, low cost and digital output capabilities of temperature sensors in modern CMOS technologies, significant research effort has been dedicated to their design. Recently, the advent of the Internet of Things (IoT) has heightened the interest in ultra-low power sensors that can maintain good accuracy across a wide temperature range. Hence, the primary focus of this thesis is the design of such sensors in CMOS technology.

## 1.2 Types of CMOS temperature sensors

Within CMOS technology, many circuit elements are available for temperature sensing. The selection of a sensing element then depends on the specific requirements dictated by the intended application, encompassing factors such as accuracy, resolution, power consumption and cost.

For decades, bipolar junction transistors (BJTs) have been extensively used as temperature sensors and bandgap voltage references. When a BJT is biased at a fixed current, its base-emitter voltage ( $V_{BE}$ ) demonstrates complementary-to-absolute temperature (CTAT) behaviour. By biasing two BJTs at different current densities, the difference between their base-emitter voltages, denoted as  $\Delta V_{BE} = V_{BE1} - V_{BE2}$ , exhibits proportional-to-absolute temperature (PTAT) behaviour. Due to the exponential relationship between the BJT's collector current  $I_C$  and  $V_{BE}$ , this approach also cancels the effect of current variations, rendering  $\Delta V_{BE}$  relatively insensitive to process variations. As it turns out, the spread in  $V_{BE}$  can be effectively corrected through a low-cost, one-point PTAT trim [4], resulting in inaccuracies as low as 0.06°C (3 $\sigma$ ) from -55°C to 125°C. Using the box method, i.e. by dividing the peak-to-peak inaccuracy (3 $\sigma$ ) by the temperature range, this translates into a relative inaccuracy (RIA) of 0.06% [9].

When biased in the sub-threshold region, a MOSFET's drain current ( $I_D$ ) is a temperature-dependent exponential function of its gate-source voltage ( $V_{GS}$ ). Typically,  $V_{GS} < V_{BE}$ , enabling MOSFET-based temperature sensors to function at lower supply voltages than their BJT-based counterparts. However,  $I_D$  is determined by the oxide capacitance ( $C_{ox}$ ) and the threshold voltage ( $V_{TH}$ ), both of which are spread with process. Consequently, MOSFET-based sensors usually require a two-point temperature calibration to achieve low inaccuracies, such as 0.1% [12].

In recent studies [10], it has been demonstrated that resistor-based temperature sensors can achieve higher resolution and energy efficiency than either BJT or MOSFET-based sensors. They can also operate from sub-1V supplies. Nevertheless, to achieve competitive accuracy, they require at least two-point

trimming due to the sensitivity of resistors to process spread. After a two-point trim, relative inaccuracies as low as 0.03% can be achieved [10], whereas a single-point trim results in only 0.56% [10].

Thermal diffusivity (TD) sensors measure the delay of heat pulses propagating through a silicon substrate. This delay is a function of the thermal diffusivity of silicon, a well-defined parameter that exhibits a significant dependence on temperature. TD sensors use heating elements to generate heat pulses, which then diffuse through the silicon substrate and are detected by a temperature sensor, usually a thermopile. A major drawback of TD sensors is their power consumption, typically a few milliwatts, which renders them unsuitable for low-power applications [4]. Nevertheless, they can achieve relative inaccuracies of 0.2% without trimming [11].

Of the four types of sensors, BJT-based temperature sensors are the most widely used because they can achieve excellent accuracy after a low-cost, one-point calibration with a relatively low power consumption.

### 1.2.1 Operating principle of BJT-based temperature sensors

The base-emitter voltage ( $V_{BE}$ ) of a BJT, where  $I_C \gg I_S$ , can be expressed as:

$$V_{BE} = \frac{\eta kT}{q} \ln \left( \frac{I_C}{I_S} \right) \quad (1.1)$$

where  $\eta$  is the diode non-ideality factor (for an ideal diode  $\eta=1$ ),  $k$  is the Boltzmann constant ( $1.38 \times 10^{-23} \text{ J/K}$ ),  $T$  is the absolute temperature in Kelvin,  $q$  is the electron charge ( $1.6 \times 10^{-19} \text{ C}$ ),  $I_S$  is the saturation current, and  $I_C$  is the collector current of the BJT. Due to the strong temperature-dependence of  $I_S$  ( $\sim T^4$ ),  $V_{BE}$  exhibits a temperature coefficient of approximately  $-2 \text{ mV/}^\circ\text{C}$ , leading to its CTAT characteristic.

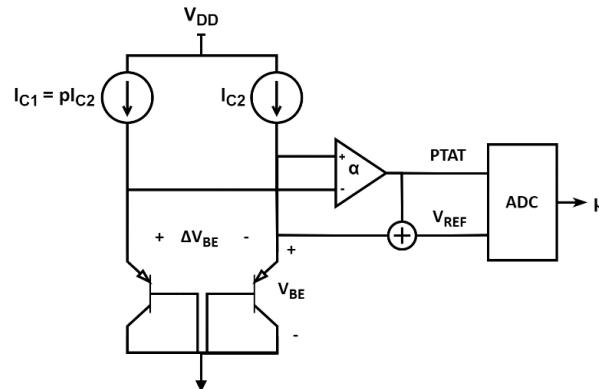

When two BJTs are biased at different current densities (Figure 1.1), the difference in their base-emitter voltages,  $\Delta V_{BE}$ , demonstrates PTAT behaviour as:

$$\Delta V_{BE} = \frac{\eta kT}{q} \ln \left( \frac{I_{C1}}{I_{C2}} \right) \quad (1.2)$$

It can be seen that  $\Delta V_{BE}$  only depends on the ratio of the biasing currents,  $p = \frac{I_{C1}}{I_{C2}}$ , which can be accurately defined by good layout, as well as circuit techniques such as dynamic-element matching.

Figure 1.1 Working principle of a BJT-based temperature sensor.

In general, the front-end of a BJT-based temperature sensor employs two diode-connected BJTs, as shown in *Figure 1.1*. With  $V_{BE}$  and  $\Delta V_{BE}$  established, a temperature-independent reference voltage ( $V_{REF}$ ) (*Figure 1.2*) can be generated as:

$$V_{REF} = V_{BE} + \alpha \Delta V_{BE}$$

Figure 1.2 CTAT and PTAT behaviour of  $V_{BE}$  and  $\Delta V_{BE}$  [4].

Using the PTAT voltage  $\Delta V_{BE}$  as the input and  $V_{REF}$  as the reference for an analog-to-digital converter (ADC), its digital output can be expressed as:

$$\mu = \frac{V_{PTAT}}{V_{REF}} = \frac{\alpha \Delta V_{BE}}{V_{BE} + \alpha \Delta V_{BE}} \quad (1.3)$$

A final digital output,  $D_{out}$ , in degrees Celsius can be acquired through linear scaling:

$$D_{out} = A\mu + B \quad (1.4)$$

Where  $A \sim 600K$ ,  $B \sim -273K$  and the value of  $\alpha$  typically ranges between 8 and 20 [4].

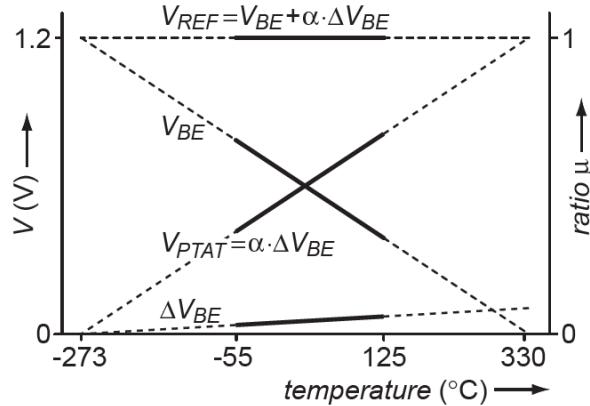

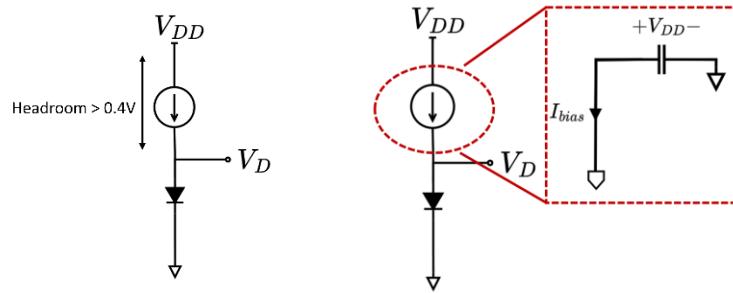

### 1.3 Capacitive Biasing

In conventional BJT- or diode-based temperature sensors, the BJTs (or diodes) are biased by current sources (*Figure 1.3a*). In addition to  $V_{BE}$ , the headroom they require increases the sensor's minimum supply voltage to approximately 1.2V. Alternatively, the BJT (or diode) can be biased by a capacitor pre-charged to  $V_{DD}$ , as depicted in *Figure 1.3b*. In this setup, the capacitor functions as a dynamic current source devoid of  $1/f$  noise and requires little headroom.

Figure 1.3 a) Static-biased diode; b) Capacitively-biased diode.

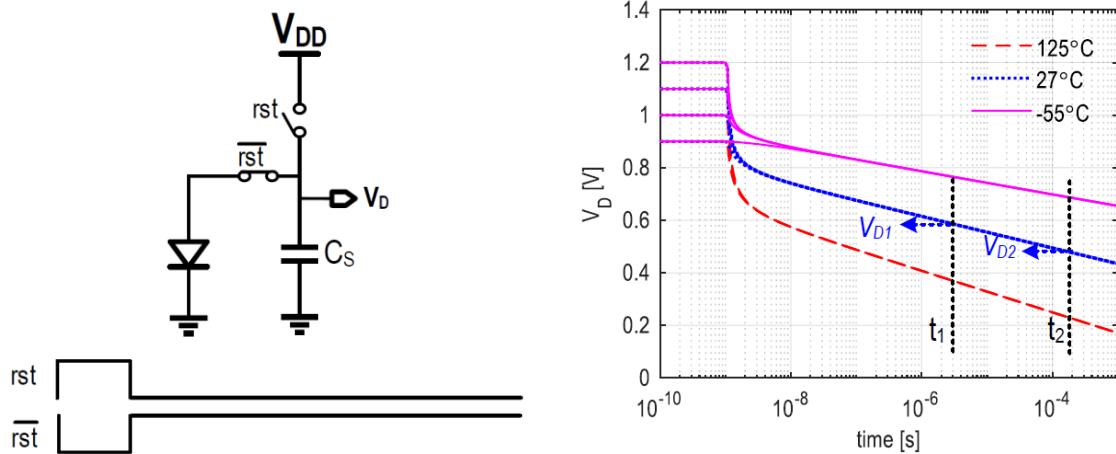

The working principle of a temperature sensor based on the capacitively-biased diode (CBD) technique is illustrated in *Figure 1.4*. In an initial phase (rst), a capacitor ( $C$ ) is pre-charged to  $V_{DD}$ . In a second phase, the capacitor is connected across the diode. After a brief period (tens of nanoseconds), the voltage across the capacitor ( $V_D$ ) will be a logarithmic function of time. This relationship can be expressed as [2]:

$$V_D(t) \simeq -\eta V_T \ln \left( \frac{I_S}{C\eta V_T} t \right) \quad (1.5)$$

where  $\eta$  is the diode ideality factor (1 for an ideal diode,  $\sim 2$  for silicon diodes with small currents),  $V_T$  is the thermal voltage and  $I_S$  is the diode saturation current. Likewise, the diode current ( $I_D$ ) is well-defined and proportional to  $1/t$  [2].

$$I_D(t) \simeq \frac{\eta C V_T}{t} \quad (1.6)$$

Figure 1.4 Working principle of a capacitively-biased diode [1].

A notable feature of the CBD technique is that, following the initial settling period,  $V_D$  becomes independent of the initial voltage ( $V_{DD}$ ). The exact expression for the voltage across the diode is [3]:

$$V_D(t) = -\eta V_T \ln \left[ 1 - \left( 1 - \exp \left( -\frac{V_{DD}}{\eta V_T} \right) \right) \exp \left( -\frac{I_S}{C\eta V_T} t \right) \right] \quad [2] \quad (1.7)$$

As depicted in *Figure 1.4*, we can identify two primary regions in the discharging process. Firstly, when

$$-\frac{I_S}{C\eta V_T} t \ll -\frac{V_{DD}}{\eta V_T} \quad [2] \quad (1.8)$$

the voltage on the diode is approximately  $V_{DD}$ . Secondly, when

$$-\frac{I_S}{C\eta V_T} t > -\frac{V_{DD}}{\eta V_T} \quad [2] \quad (1.9)$$

the exponential term containing  $V_{DD}$  becomes insignificant, and  $V_D$  undergoes a logarithmic decay independent of the initial voltage. This implies that sampling  $V_D$  in this region yields a voltage that is insensitive to supply voltage noise.

Additionally, the minimum supply voltage is only slightly higher than the diode's forward voltage drop, which is approximately 0.8V at cold temperatures. No additional headroom is necessary for other components, such as current sources. Moreover, in comparison to current source biasing, a CBD-based front-end requires fewer components, potentially enhancing accuracy.

To extract temperature information, the temperature-dependent voltage is sampled on the capacitor. At a specific time,  $t$ , the diode is disconnected from the capacitor, sampling  $V_D$  on  $C$ . When the diode is replaced by a diode-connected BJT, the voltage  $V_D = V_{BE}$  is shown by Equation (1.1). By sampling the voltage at two different time instances,  $t_1$  and  $t_2$ , and taking their difference, a PTAT voltage,  $\Delta V_{BE}$  can be obtained.

$$\Delta V_{BE} = \frac{kT}{q} \ln \left( \frac{I_{C1}}{I_{C2}} \right) \simeq \eta \frac{kT}{q} \ln \left( \frac{t_2}{t_1} \right) \quad (1.10)$$

Here, it is evident that the PTAT voltage ( $\Delta V_{BE}$ ) is dependent on the time ratio,  $t_2/t_1$ , rather than on the absolute discharge time. As explained in the previous subsection, the sampled voltages  $V_{BE}$  and  $\Delta V_{BE}$  can then be used to obtain the temperature in degrees Celsius.

A drawback of the CBD technique is the  $kT/C$  noise associated with sampling  $V_{BE}$  on a capacitor. Additionally, it is sensitive to variations in the master clock period, since the bias current in the diode is set by the discharge time of the capacitor. However, it is worth noting that such errors will only impact  $V_{BE}$  and not  $\Delta V_{BE}$ , which is defined by a time ratio. The clock sensitivity of CBD-based temperature sensors is  $\sim 0.13 \text{ }^{\circ}\text{C}/\%$  of clock variation, which is not a major source of error considering that on-chip clocks with inaccuracies below 0.1% can be achieved.

## 1.4 CBD-based temperature sensors

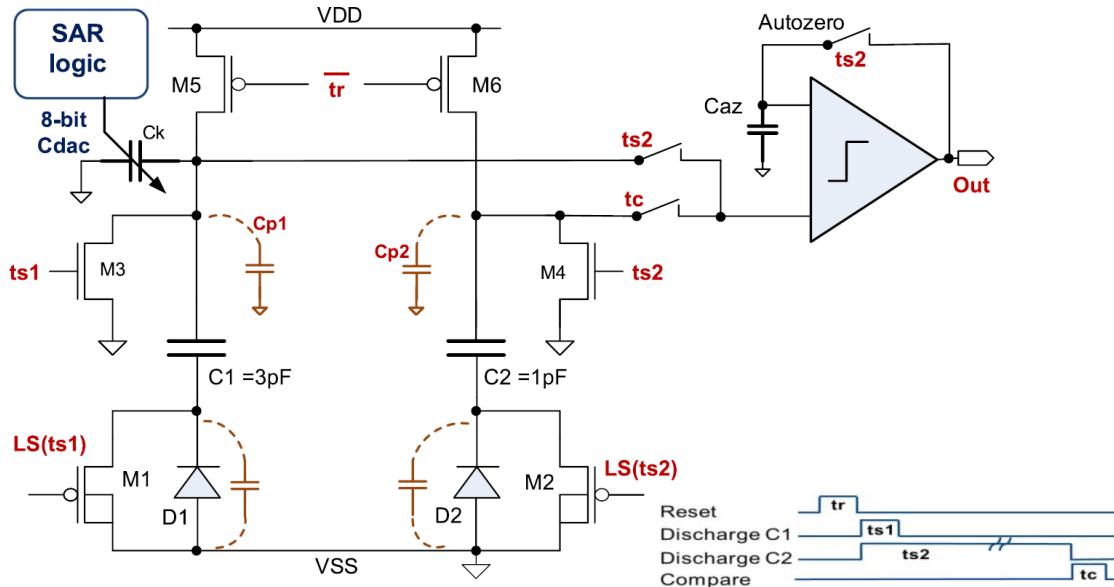

The first CBD-based temperature sensor was presented in [2]. As shown in *Figure 1.5*, its temperature sensing element is a bulk diode. During a reset phase, switches M1, M2, M5 and M6 are closed, leading to the charging of capacitors  $C_1$  and  $C_2$ . Afterwards,  $C_1$  and  $C_2$  are discharged by closing switches M3 and M4 during the time intervals  $t_{S1}$  and  $t_{S2}$ , respectively. At the end of  $t_{S1}$ , the sampled voltage  $V(C_1)$  is scaled by a capacitive DAC and transferred to  $C_{az}$ , while the comparator is auto-zeroed. At the end of  $t_{S2}$ , the sampled voltage  $V(C_2)$  is compared with the result, during the comparison step (tc). Using an 8-step SAR

algorithm, the setting of the capacitor DAC is adjusted until  $V(C_1) \sim V(C_2)$ . The required DAC setting is then a digital representation of temperature.

Operating from supply voltages as low as 0.85V, the sensor achieves a relative inaccuracy of 2.8%. It is also quite compact, occupying an area of only 0.0025 mm<sup>2</sup>, partially due to its implementation in a 16-nm FinFET technology. However, its power supply sensitivity (PSS) is on the high side at 1.5°C/V and it dissipates 18μW [2].

Figure 1.5 Switch-capacitor CBD-based sensor circuit [2].

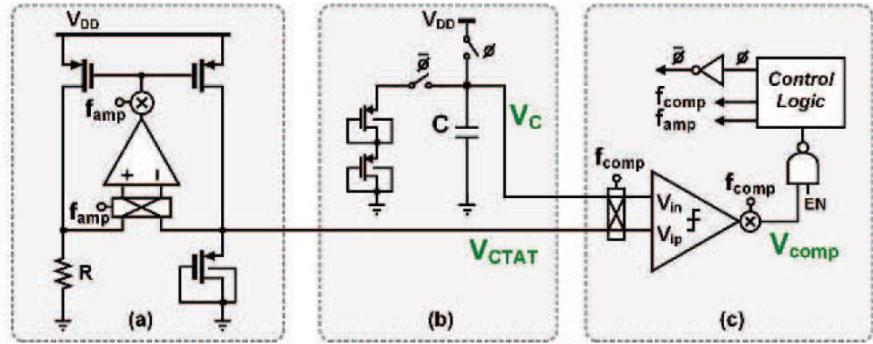

Capacitive biasing can be applied to diodes, BJTs and MOSFETs. The design illustrated in *Figure 1.6* is based on a DTMOST, enabling operation at a supply voltage of 0.85V and achieving a supply sensitivity of 0.27°C/V. It operates by discharging the capacitor C across the diode-connected DTMOSTs and sampling the temperature-dependent voltage  $V_C$  (*Figure 1.6b*). This voltage is then compared to a reference voltage  $V_{CTAT}$  provided by a conventional CTAT generator circuit (*Figure 1.6a*). Lastly, the comparator detects when  $V_C$  reaches  $V_{CTAT}$  and generates the output clock signals (*Figure 1.6c*), that control the charge and discharge times of the sensing core.

However, the design achieves a poor relative inaccuracy of 1.8% with one-point trim, mainly due to the spread in the DTMOSTs present in both the sensing core and in the  $V_{CTAT}$  generator. Furthermore, at cold temperatures, the slowly-decaying CBD-voltage fails to reach the reference voltage. This limits its temperature range to -10°C to 90°C. It is compact, occupying 0.017 mm<sup>2</sup> in a 28nm process, but it dissipates a relatively large power of 33.75 μW [7].

Figure 1.6 CBD-based temperature sensor with DT莫斯 as sensing element: a) VCTAT generator; b) DTmos sensing code; c) relaxation oscillator [7].

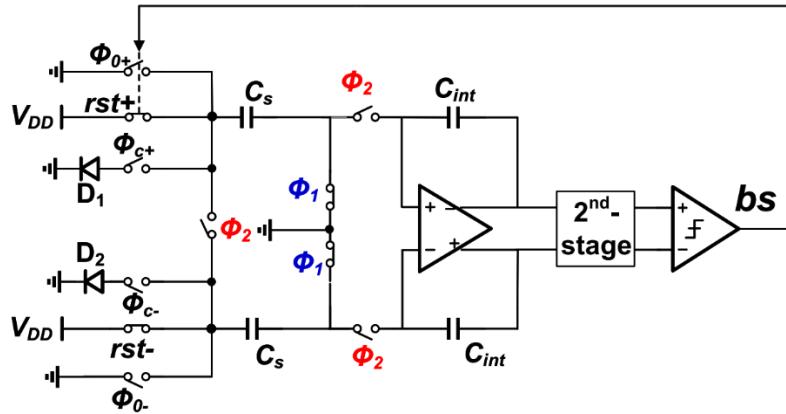

A sensor that achieves better relative inaccuracy (0.67%) is depicted in Figure 1.7. In this design, the sampling capacitors of a delta-sigma modulator are also used to generate two temperature-dependent voltages,  $V_{D1}$  and  $V_{D2}$ , across two P+/Nwell diodes. A CB pair consists of two such circuits that differentially transfer the charge sampled on two  $C_s$  to the integrator. The second  $C_s$  can sample  $V_{D2}$  by discharging across an identical diode for a duration  $t_2$  that sets the current ratio  $p = \frac{t_2}{t_1}$ . This way,  $\Delta V_D$  is differentially transferred to the integrator. Alternatively, the second  $C_s$  can remain discharged, and the CBD pair in the front-end transfers only one  $V_D$  to the integrator.

The sensor operates from a 1V supply voltage, which is primarily limited by the amplifiers used in the modulator. Additionally, it covers the military temperature range: from -55°C to 125°C. With a power consumption of 2.2 $\mu$ W, it occupies a chip area of 0.021mm<sup>2</sup> [13].

Figure 1.7 Block diagram of a CBD-based temperature sensor [13].

#### 1.4.1 State-of-the-art CBD-based temperature sensor

A state-of-the-art CBD-based temperature sensor, which is an improved version of the design in [13], is shown in Figure 1.8. Based on diode-connected PNPs, it attains an impressive relative inaccuracy of 0.17%

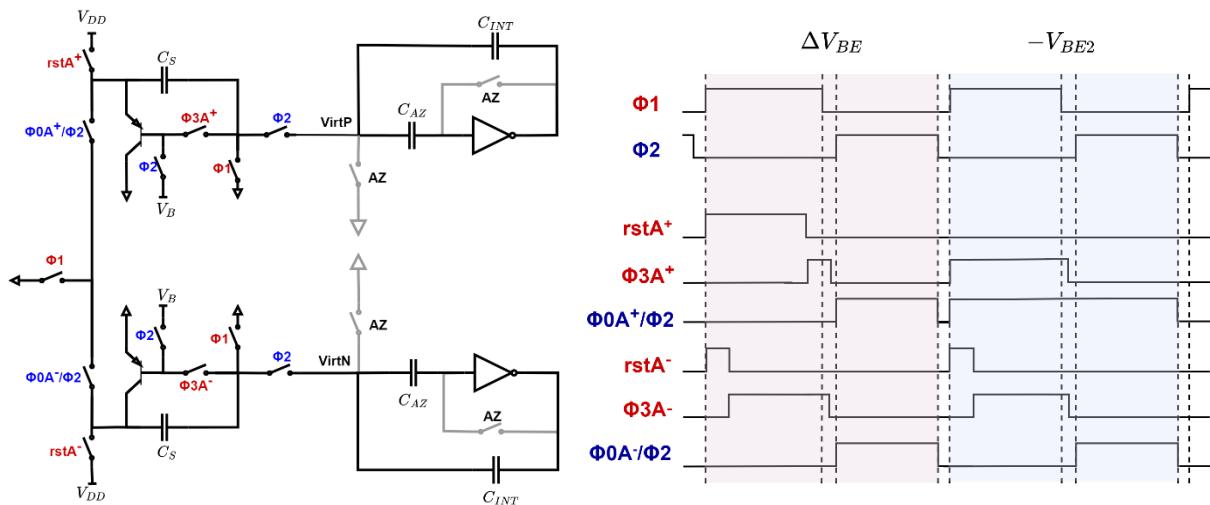

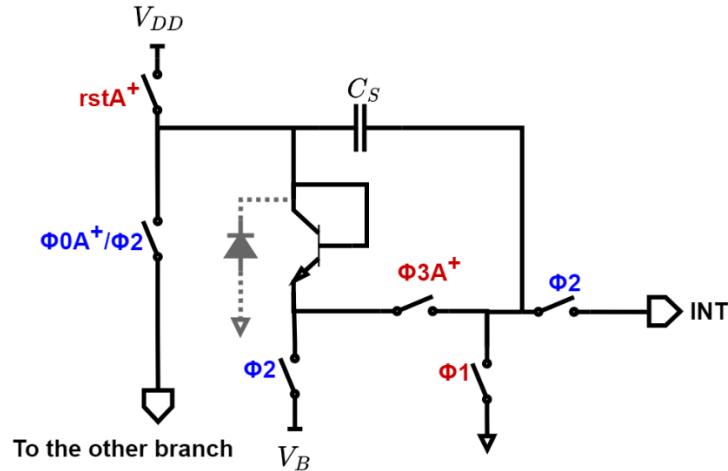

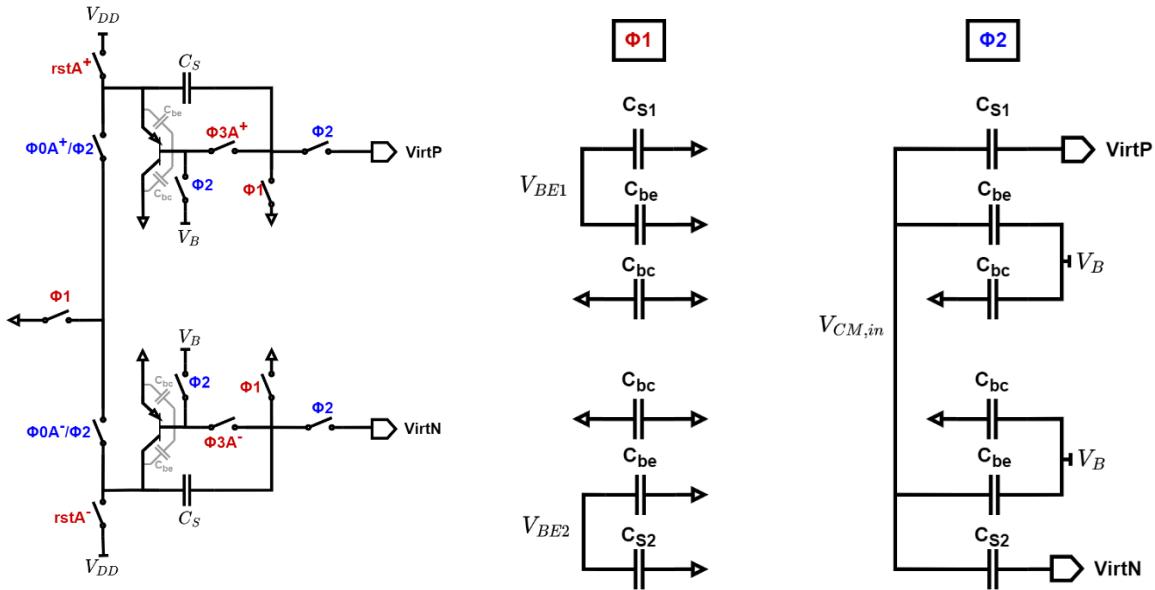

after a one-point trim. The discharging currents through the PNPs are turned off by switching their bases, thus avoiding errors in the sampled  $V_{BE}$  due to the PVT-dependent voltage drop across a switch in series with the BJT. Furthermore, the modulator employs inverter-based pseudo-differential amplifiers, allowing the sensor to operate from a 0.95V supply voltage [1].

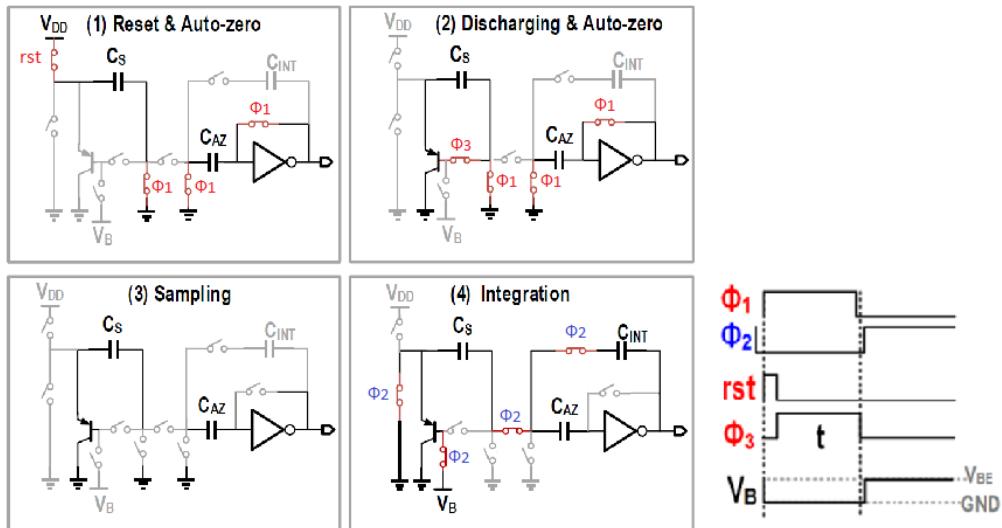

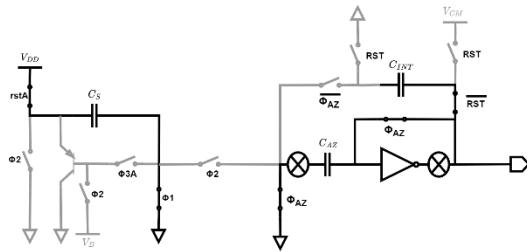

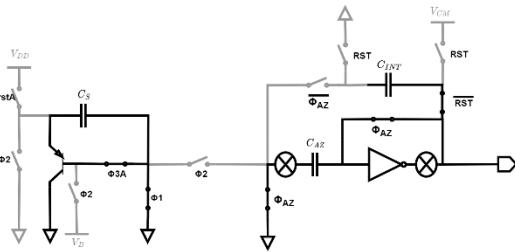

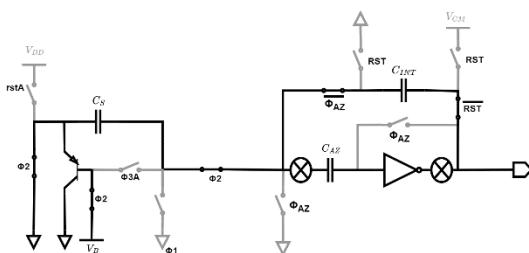

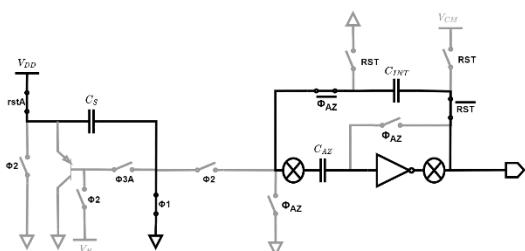

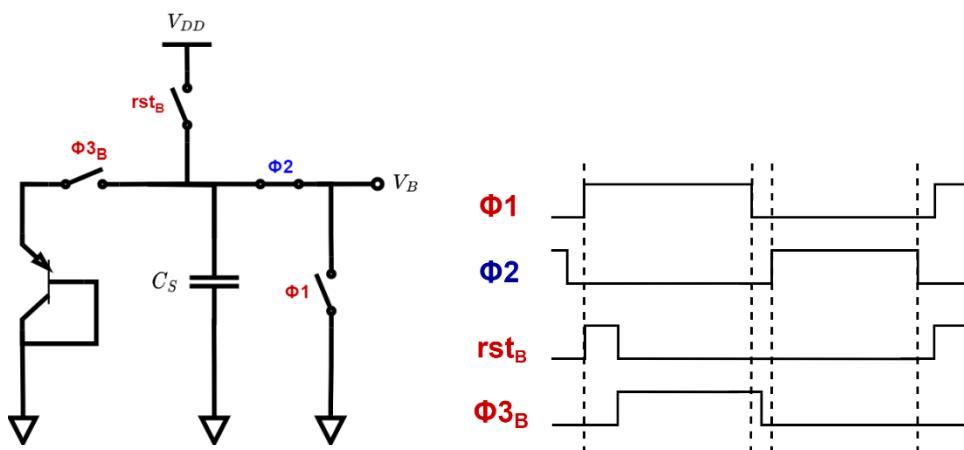

Figure 1.8 shows the detailed single-sided operation of the CBD front-end along with the first integrator. The sampling phase ( $\Phi_1$ ) can be divided into two parts: the precharge phase (rst) and the discharge phase ( $\Phi_3$ ). During the rst phase, the sampling capacitor  $C_S$  is precharged to  $V_{DD}$  (Figure 1.8.1). When  $\Phi_3$  is high (Figure 1.8.2),  $C_S$  is disconnected from the supply voltage and the PNP is turned on by connecting its base to the ground.  $C_S$  discharges through the diode-connected PNP for a duration of  $t$ , controlled by the  $\Phi_1$  and  $\Phi_3$  switches. The BJT is turned on through its base and not through other connections (e.g. the emitter side) to minimise the voltage drop across the switch. Additionally, switch  $\Phi_3$  opens shortly after  $\Phi_1$  to prevent charge injection from sampling onto  $C_S$ . The voltage  $V_{BE}$  is sampled on the capacitor  $C_S$  during this process (Figure 1.8.3). During the same phase ( $\Phi_1$ ), the integrator is autozeroed to mitigate its offset and 1/f noise and is biased in the correct operating region.

In  $\Phi_2$ , the PNP is turned off in a supply-independent manner by connecting its base to a voltage  $V_B \sim V_{BE}$ . This  $V_B$  is generated by an auxiliary CB PNP. Finally, the front-end is connected to the integrator, facilitating the transfer of charge from  $C_S$  to  $C_{INT}$  for integration.

Figure 1.8 Single-sided switched-capacitor (SC) integrator with embedded CB PNP front-end [1].

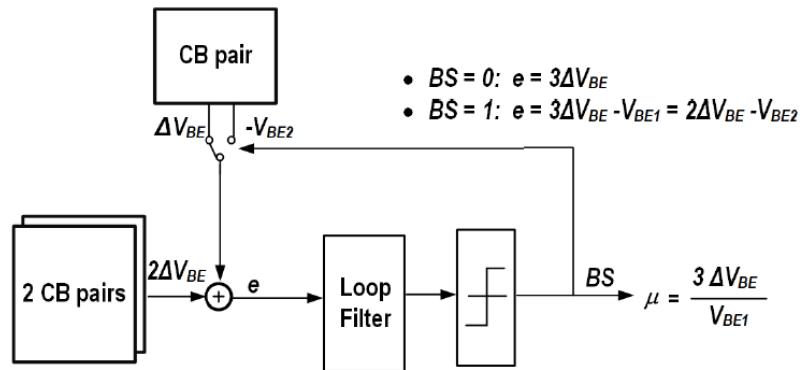

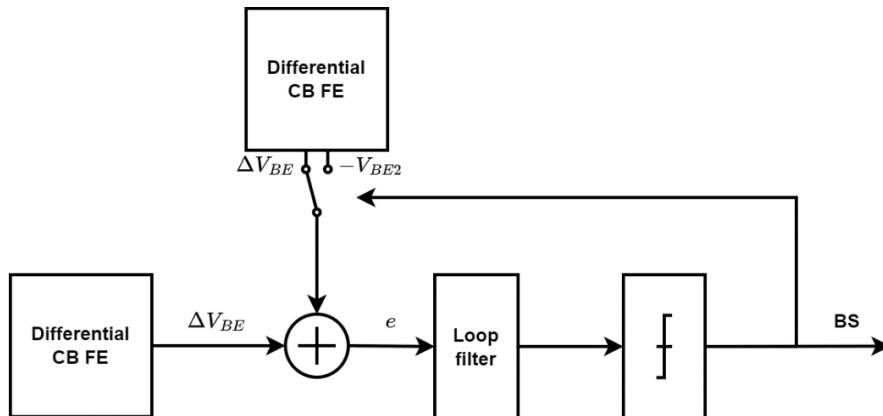

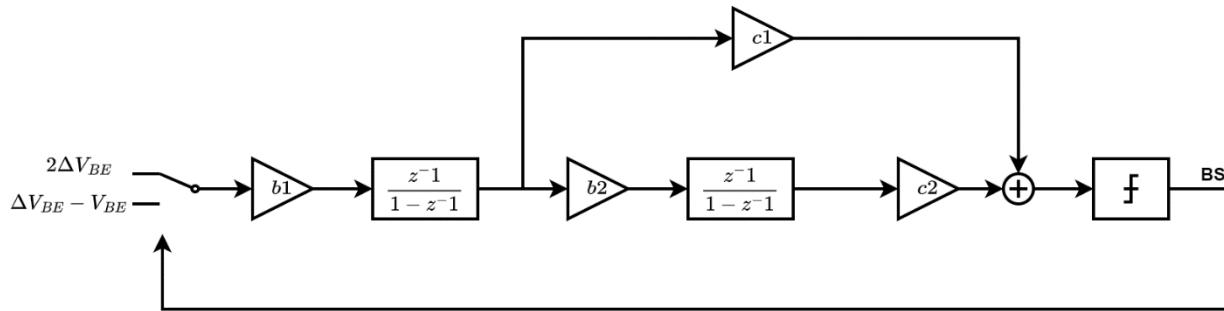

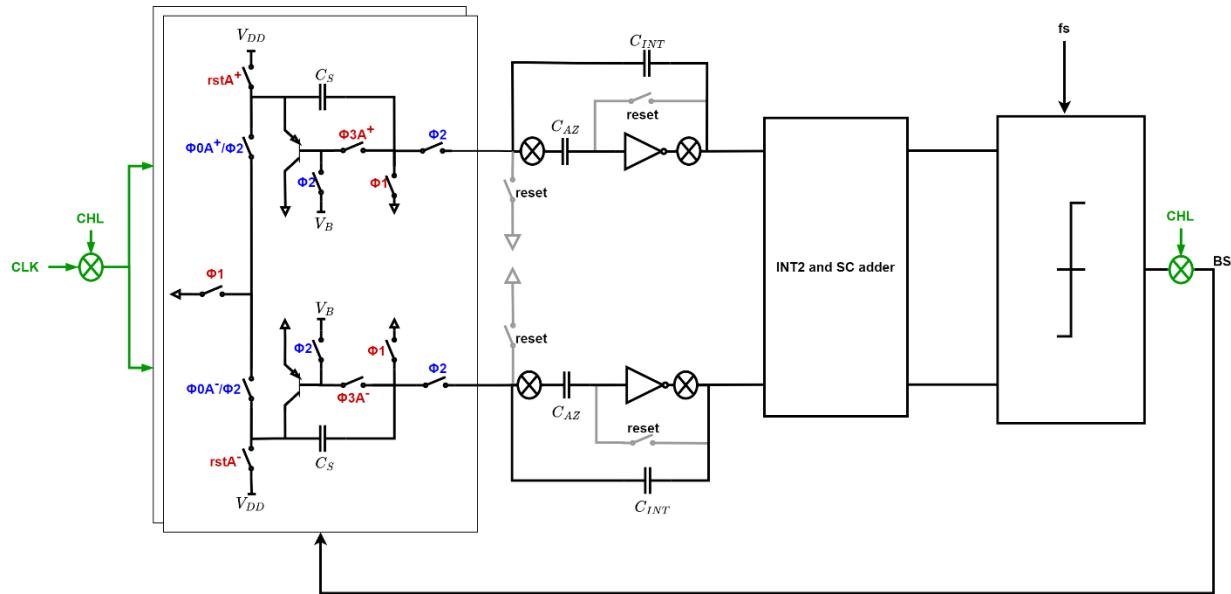

The block-level architecture of the design proposed in [1] is depicted in Figure 1.9. This design incorporates three differential CB pairs to drive a second-order single-bit delta-sigma modulator (DSM). The clock signals of each CB pair are controlled by the bitstream (BS) output. In this way, a differential charge proportional to either  $V_{BE}$  or  $\Delta V_{BE}$  can be transferred to the modulator, as follows:

$$BS = 0: \quad e = k\Delta V_{BE}$$

$$BS = 1: \quad e = (k - 1)\Delta V_{BE} - V_{BE2}$$

Where  $k$  is the number of CB pairs in the front-end, which is 3 here. This gives a bitstream average,  $\mu$ :

$$(1 - \mu)k\Delta V_{BE} + \mu((k - 1)\Delta V_{BE} - V_{BE2}) = 0 \quad (1.11)$$

$$\mu = \frac{k\Delta V_{BE}}{V_{BE1}} = \frac{3\Delta V_{BE}}{V_{BE1}} \quad (1.12)$$

The resulting  $\mu$  makes good use of the modulator's dynamic range, as shown in *Figure 1.10*. The decimated output can be linearised as follows:

$$\mu_{lin} = \frac{\alpha\mu}{\alpha\mu + 1} = \frac{3\alpha\Delta V_{BE}}{3\alpha\Delta V_{BE} + V_{BE1}} \quad (1.13)$$

which can be further digitally processed and converted into temperature:

$$T = A\mu_{lin} + B \quad (1.14)$$

where  $\alpha$ ,  $A$  and  $B$  are fitting coefficients.

Figure 1.9 Block level architecture of the CBD sensor proposed in [1].

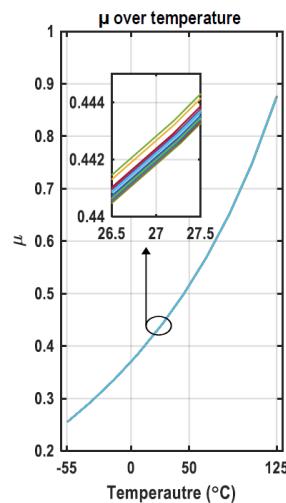

Figure 1.10 Measured bitstream average  $\frac{3\Delta V_{BE}}{V_{BE1}}$  over temperature of chip [1].

As an experiment, a version of the sensor with smaller sampling capacitors  $C_s = 800\text{fF}$  was taped out to investigate whether the design could be scaled down further. However, measurements on 10 chips showed that this version only achieves an inaccuracy of  $\pm 0.31^\circ\text{C}$  ( $3\sigma$ ), after a PTAT trim at room temperature.

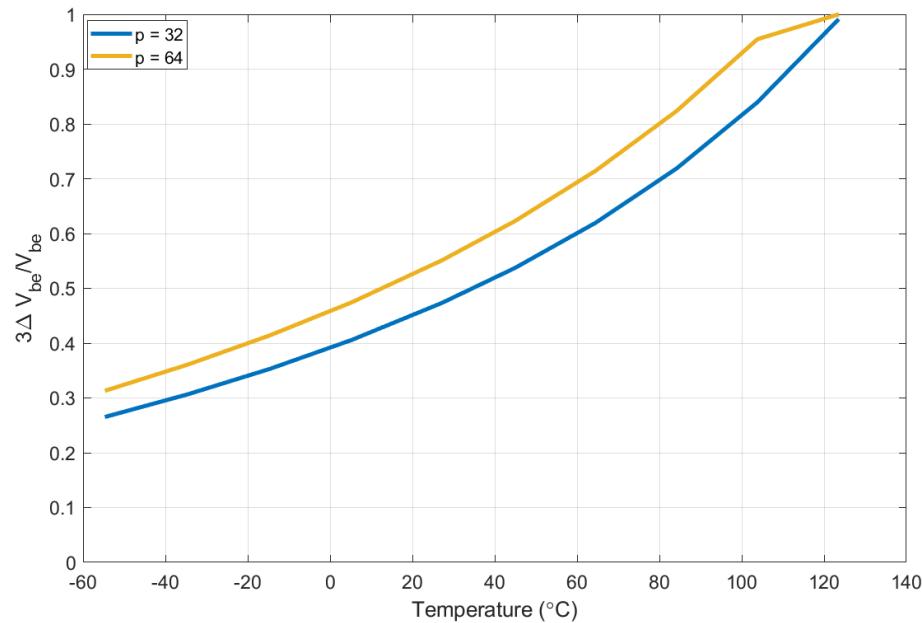

The measured bitstream average  $\mu = \frac{3\Delta V_{BE}}{V_{BE}}$  for two different sampling time ratios ( $t_1/t_2 = 32$  and  $64$ ) is shown in *Figure 1.11*. It can be seen that for large time ratios, the ADC clips at high temperatures. This is because from Equation (1.6), reducing  $C$  reduces the bias current, which, in turn, reduces  $V_{BE}$ , while  $\Delta V_{BE}$  increases with larger time ratios. To avoid this, the charge-balancing scheme must be modified, as will be discussed in the following chapter. However, these results show that the area and power dissipation of this design can be further optimised, while maintaining good accuracy over the military temperature range.

Figure 1.11 Measured bitstream average  $\mu = \frac{3\Delta V_{BE}}{V_{BE}}$  across temperature for a time ratio  $p=32$  and  $p=64$ .

## 1.5 Project goals

The performance of state-of-the-art CBD-based temperature sensors with low supply voltages and low power characteristics are summarised in *Table 1.1*.

Table 1.1 Comparison of the state-of-the-art low-supply temperature sensors.

|                                       | 2019 [2]          | 2020 [7]             | 2021 [13]              | 2023 [1]               | Design goals |

|---------------------------------------|-------------------|----------------------|------------------------|------------------------|--------------|

| <b>Technology</b>                     | 16nm FinFET       | 28nm                 | 55nm                   | 180nm                  | 180nm        |

| <b>Type</b>                           | Bulk diode<br>SAR | DTMOST<br>OSC        | P+/Nwell DT<br>ΣΔ      | PNP<br>DT ΣΔ           | PNP<br>DT ΣΔ |

| <b>Area [mm<sup>2</sup>]</b>          | 0.0025            | 0.017                | 0.021                  | 0.25                   | < 0.125      |

| <b>Supply [V]</b>                     | 0.85 – 1          | 0.85 – 1.15          | 1 – 1.2                | 0.95 – 1.4             | < 0.9        |

| <b>T. Range [°C]</b>                  | -15 – 105         | -10 – 90             | -55 – 125              | -55 – 125              | -55 – 125    |

| <b>3σ Error [°C]<br/>(Trim point)</b> | +1.5/-2.0 (0)     | ±2.0 (0)<br>±0.9 (1) | ±1.4 (0)<br>±0.6** (1) | ±0.45 (0)<br>±0.15 (1) | < ±0.20 (1)  |

| <b>R.I.A. [%]<br/>(Trim point)</b>    | 2.9 (0)           | 4 (0)<br>1.8 (1)     | 1.6 (0)<br>0.67 (1)    | 0.5 (0)<br>0.17 (1)    | < 0.22 (1)   |

| <b>Power [μW]</b>                     | 18                | 33.75                | 2.2                    | 0.81                   | < 0.30       |

| <b>Tconv [ms]</b>                     | 0.013             | 0.1                  | 6.4                    | 128                    | 128          |

| <b>Res. [mK]</b>                      | 300               | 10.2                 | 15                     | 1.8                    | < 20         |

| <b>PSS [°C/V]</b>                     | 1.5               | 0.27                 | 3.7                    | 0.2                    | ~0.2         |

| <b>Res. FoM<br/>[pJK<sup>2</sup>]</b> | 21                | 0.36*                | 3.1                    | 0.34                   | < 0.34       |

\* Needs an additional frequency-to-digital converter

\*\* With systematic error correction

Note that the resolution FoM, a metric of their energy efficiency, is calculated as:

$$\text{Res. FoM} = \frac{\text{Energy}}{\text{Conversion}} \times \text{Resolution}^2 \quad (1.15)$$

From this table, it is evident that the design in [1] achieves the best relative inaccuracy of 0.17%, after a one-point trim. However, despite its low power dissipation (810nW) and excellent performance in other respects, it occupies more area (0.25 mm<sup>2</sup> in 180nm CMOS) than the other designs. As we will see in the following chapter, most of this area is occupied by capacitors. By reducing their size, both the area and the power consumption of the sensor could be further minimised.

With this objective in mind, the goal of this project is to design a sub-1V CBD-based temperature sensor in the same 180nm technology with less area (<0.125 mm<sup>2</sup>) and lower power dissipation (<300 nW). The sensor should also maintain a competitive inaccuracy of <0.2°C over the military temperature range, -55°C to 125°C, after a one-point trim.

## 1.6 Organisation of the thesis

The remaining chapters of the thesis are organised as follows.

Chapter 2 introduces the proposed architecture. System-level techniques are described to reduce capacitor size and obtain a compact, low-power CBD temperature sensor.

Chapter 3 explores the circuit-level implementation of the sensor. Two subsections are discussed here: the implementation of the CBD front-end and the realisation of the delta-sigma modulator (DSM).

Chapter 4 presents the simulated results of the sensor design, encompassing accuracy, resolution, estimated area, and power consumption.

Lastly, Chapter 5 concludes the project with a discussion on future improvements.

# 2 System level design

To design a compact, low-power, yet high-accuracy sub-1V temperature sensor, this project builds upon the existing state-of-the-art CBD sensor described in [1]. This chapter elaborates on the chosen architecture and discusses the design choices made to improve the previous work.

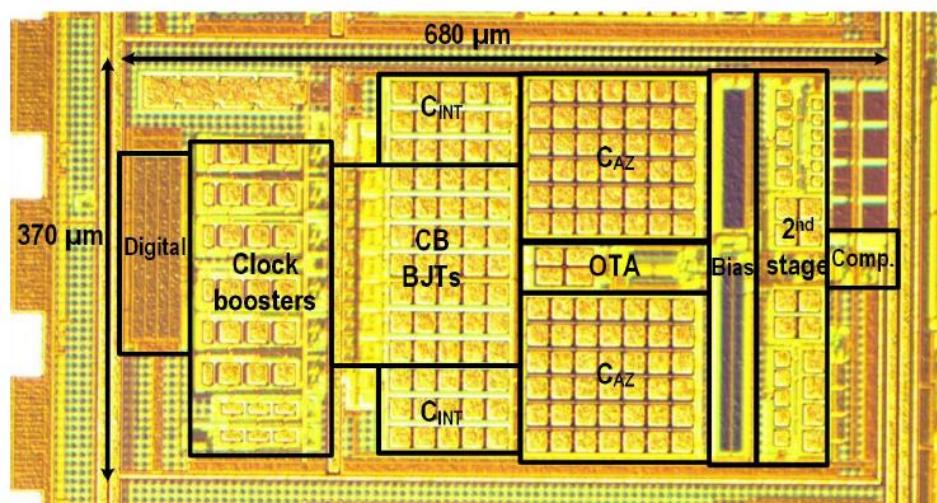

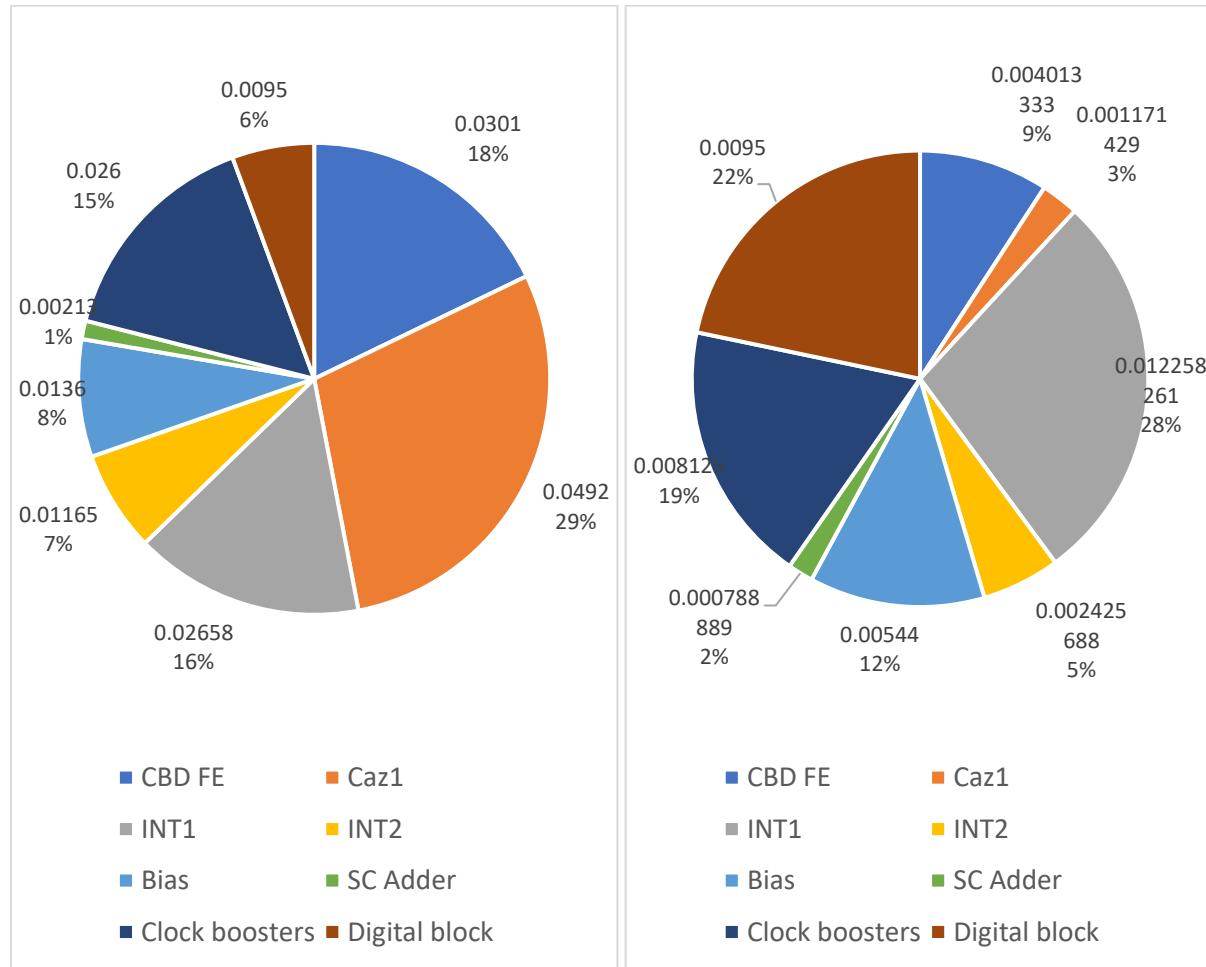

## 2.1 Reducing the area of the CBD SC temperature sensor

*Figure 2.1* shows the die micrograph of the existing CBD temperature sensor [1], while *Figure 2.2* shows how much area is occupied by each circuit block. As can be seen, the area is dominated by the CBD front-end and the autozero capacitors of the first integrator. The area of the digital part is dominated by the clock booster capacitors. In the following, different ways of reducing the size of these capacitors will be discussed. As will be seen, this also improves other aspects, such as power consumption, while maintaining the good accuracy and energy efficiency of the original design.

*Figure 2.1 Die micrograph of chip in [1].*

Figure 2.2 Area distribution of the chip in [1] in mm<sup>2</sup>.

## 2.2 Scaling the front-end

The sampling capacitors ( $C_S$ ) dominate the front-end area. Decreasing it, both the front-end area and dynamic power will be reduced, as given by:

$$P_{FE} = C_S \times f_S \times V_{DD}^2 \quad (2.1)$$

where  $f_S$  is the sampling frequency of the front-end (and DSM in this case).

By reducing their size, the current through the BJT and the sampled voltage are also affected. For a given discharge time,  $t$ , the BJT's emitter current as a function of  $C_S$  is given by:

$$I_E(t) \cong \frac{C_S V_T}{t} \quad (2.2)$$

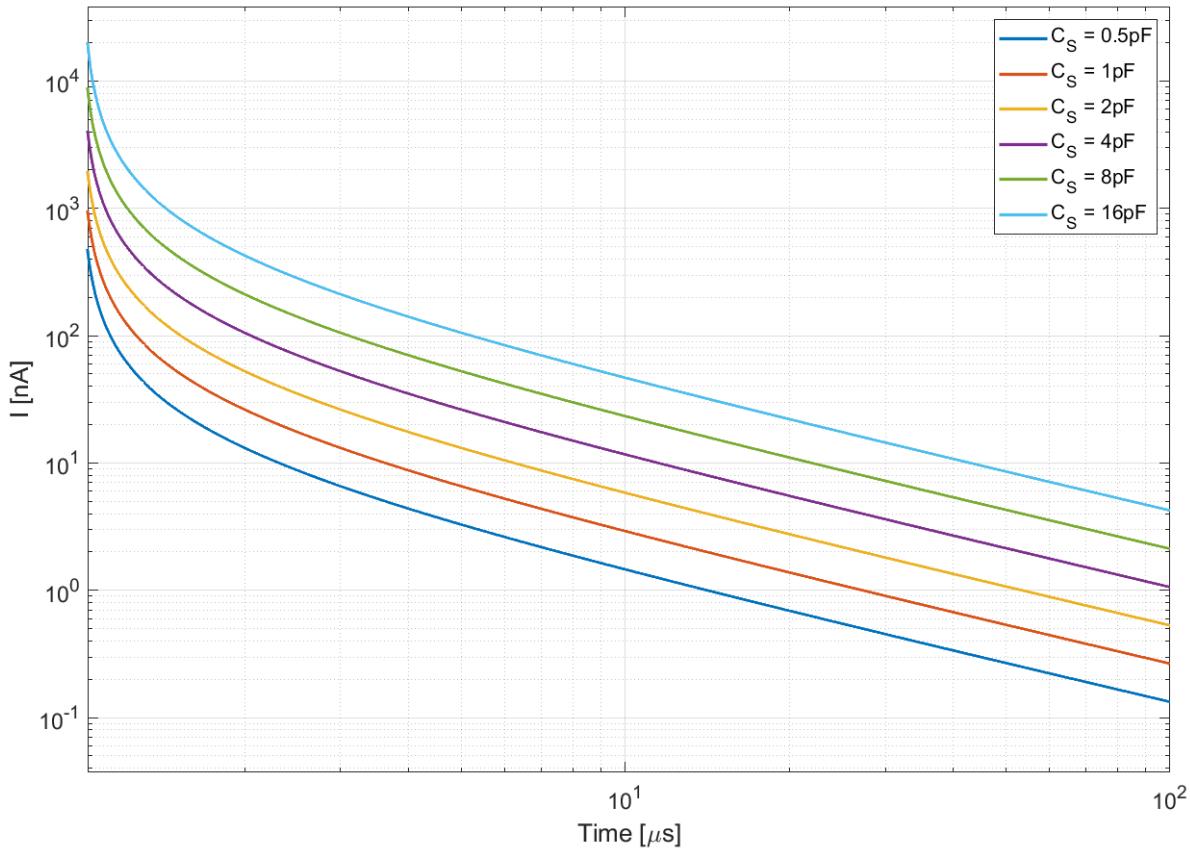

Figure 2.3 shows this relationship for different values of  $C_S$ . It can be seen that  $I_E$  decreases as  $C_S$  decreases. For the design in [1],  $I_E$  is as low as 3.7nA at the end of the discharge. Reducing this further reduces front-end's accuracy due to the following reasons.

Figure 2.3 Current through a diode ( $I_D$ ) versus discharge time ( $t$ ) for different  $C_S$  sizes from  $500fF$  to  $16pF$ .

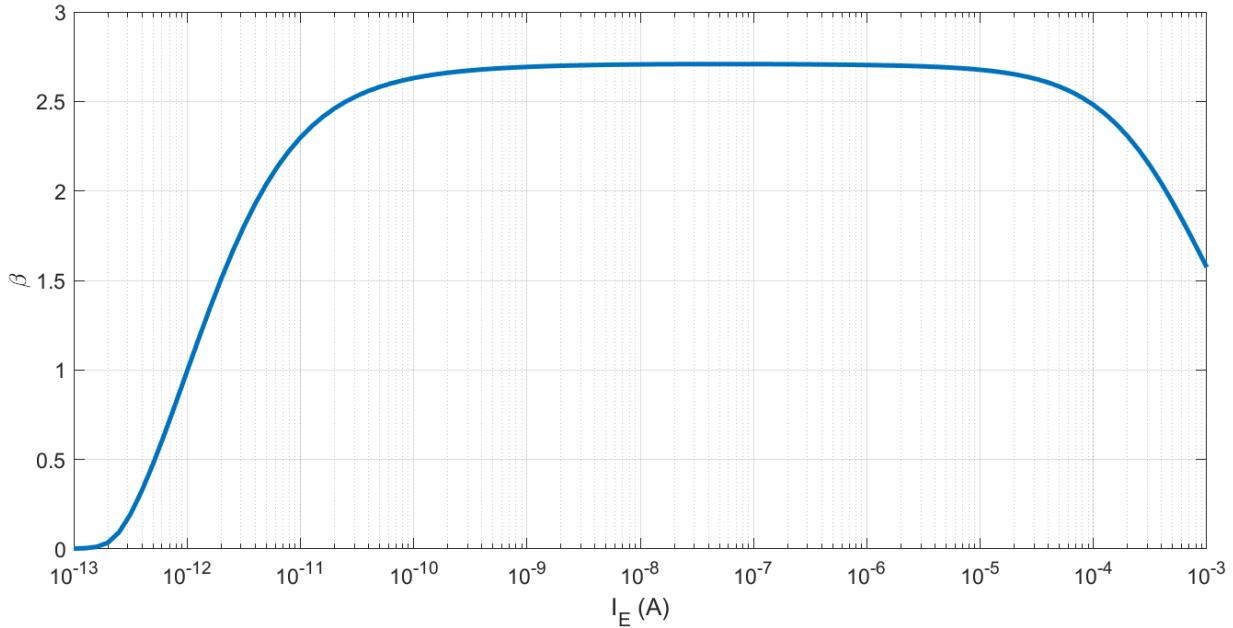

First, the BJT's current gain,  $\beta$ , decreases rapidly for small values of  $I_E$ , as shown in [Figure 2.4](#). Since the PNPs are biased via their emitters, variations in  $\beta$  will affect their collector currents and thus, their ratios. The resulting the error in  $\Delta V_{BE}$  is given by:

$$\Delta V_{BE,error} = \frac{kT}{q} \frac{\Delta \beta}{(\beta_1 + 1)(\beta_2 + 1)} \quad (2.3)$$

where  $\beta_1$  and  $\beta_2$  are the current gains of the two BJTs, and  $\Delta \beta$  is their difference.

To reduce  $\Delta \beta$ ,  $I_E$  should be chosen such that the BJTs are operated in a region where  $\beta$  is relatively constant. In [Figure 2.4](#), we see that this occurs when  $I_E$  is greater than  $\sim 100$  pA.

Figure 2.4 BJT's  $\beta$  variation with respect to emitter current  $I_E$ .

Second, as the collector current reduces, the non-linear error due to the BJT's finite saturation current ( $I_S$ ) increases, affecting the accuracy as follows:

$$\Delta V_{BE,error} = \frac{kT}{q} \left( \frac{pI_C + I_S}{I_C + I_S} \right) \quad (2.4)$$

To reduce the effect of  $I_S$  non-linearity,  $I_E$  should be chosen such that  $I_C \gg I_S$ .

Considering these BJT non-idealities, an estimation of the minimum  $I_E$  and with that smallest  $C_S$  can be made, using the temperature sensitivity of the readout:

$$D_{out} = A\mu_{lin} + B \quad (2.5)$$

to  $\Delta V_{BE}$  and  $V_{BE}$ , as well as the gain  $\alpha$ , as derived in [4], where  $\mu_{lin} = \frac{\alpha\Delta V_{BE}}{V_{BE} + \alpha\Delta V_{BE}}$ .

$$S_{V_{BE}}^{D_{out}}(T) \simeq -\frac{T}{V_{REF}} \quad (2.6)$$

$$S_{\Delta V_{BE}}^{D_{out}}(T) \simeq \frac{A - T}{V_{REF}} \alpha \quad (2.7)$$

$$S_{\alpha}^{D_{out}}(T) \simeq \frac{T}{\alpha} \left( 1 - \frac{T}{A} \right) \quad (2.8)$$

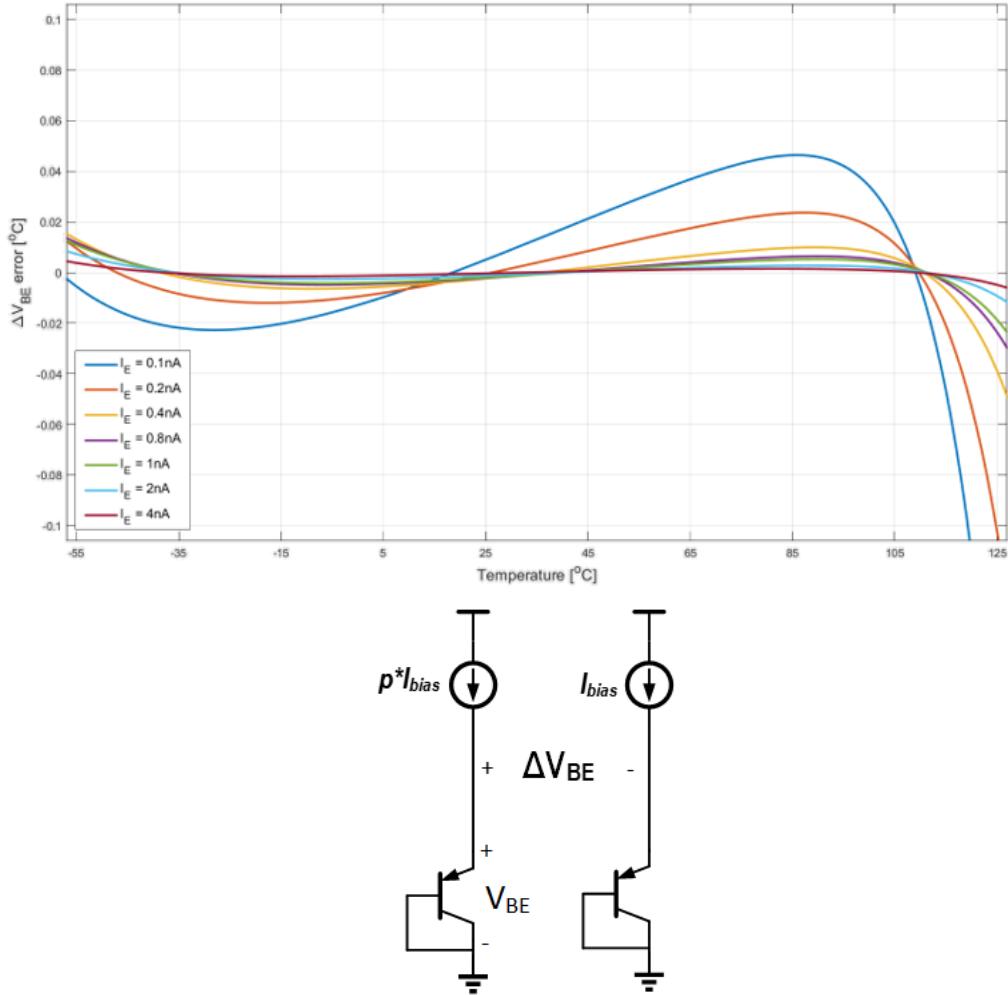

From these equations, it can be seen that the sensitivity of  $D_{out}$  to errors in  $\Delta V_{BE}$  is the most significant. Figure 2.5a shows the temperature error in  $\Delta V_{BE}$  for  $25\mu\text{m}^2$  PNPs biased at different  $I_E$  with a current ratio of  $p = 32$ , using the testbench shown in Figure 2.5b. This is the same as the current ratio used in [1], which achieved state-of-the-art accuracy. As  $I_E$  decreases, the temperature errors due to  $I_S$  and  $\beta$  increase, setting 400pA as a lower limit for achieving the target inaccuracy of  $0.18^\circ\text{C}$  over the military temperature range.

This leaves enough margin for additional sources of error, e.g. amplifier non-idealities, so that an inaccuracy of  $0.20^\circ\text{C}$  can be achieved for the whole design. As in [1], the discharge times are,  $t_1 = 32\mu\text{s}$  and  $t_2 = 1\mu\text{s}$ , which result in a minimum sampling capacitor of  $490\text{fF}$ .

Figure 2.5 a) Temperature error in  $\Delta V_{BE}$  at different  $I_{bias}$  currents; b) Static biasing of two BJTs.

Besides the accuracy, another thing to consider when decreasing the size of  $C_s$  is the increase in the sampled noise ( $kT/C$ ). For an inaccuracy of  $0.18^\circ\text{C}$ , it would be reasonable to design a sensor with  $\sim 10$  times better resolution, meaning  $18\text{mK}$  at most. In the original SC CBD-based front-end design in [1],  $C_s$  of  $4\text{pF}$  results in a resolution of  $1.7\text{mK}$ . This means that for a resolution limit of  $18\text{mK}$ ,  $C_s$  can be reduced by a factor of  $10^2$  to a minimum value of  $40\text{fF}$ . This is much smaller than the limit on  $C_s$  set by the accuracy requirements, and so, resolution will not be a limiting factor.

In conclusion,  $C_s$  can be chosen as  $490\text{fF}$  to reduce the front-end's area and power as well as the following stages of the modulator while maintaining good accuracy.

## 2.3 Charge balancing readout scheme

The last thing to be considered is the effect of reducing  $I_E$  on the charge balancing scheme. This decreases the sampled  $V_{BE}$ , which may cause the ADC to clip, as shown in Chapter 1. This can be prevented by scaling  $\mu$  appropriately, as will be discussed in the following section.

For  $C_S = 490\text{fF}$  at  $125^\circ\text{C}$ , simulations show that:

$$\frac{\Delta V_{BE}}{V_{BE1}} \sim 0.35$$

so a gain of  $k=3$  will make the ADC clip. To prevent this,  $k=2$  was chosen in this design, as shown in *Figure 2.6*. The new charge balancing scheme with two front-ends is shown in *Figure 2.7*.

Figure 2.6 Simulated value of  $\mu = \frac{3\Delta V_{BE}}{V_{BE}}$  and  $\mu = \frac{2\Delta V_{BE}}{V_{BE}}$  across temperature, for  $p = 32$ .

Figure 2.7 Proposed charge balancing scheme.

## 2.4 Scaling the autozero capacitors $C_{AZ}$

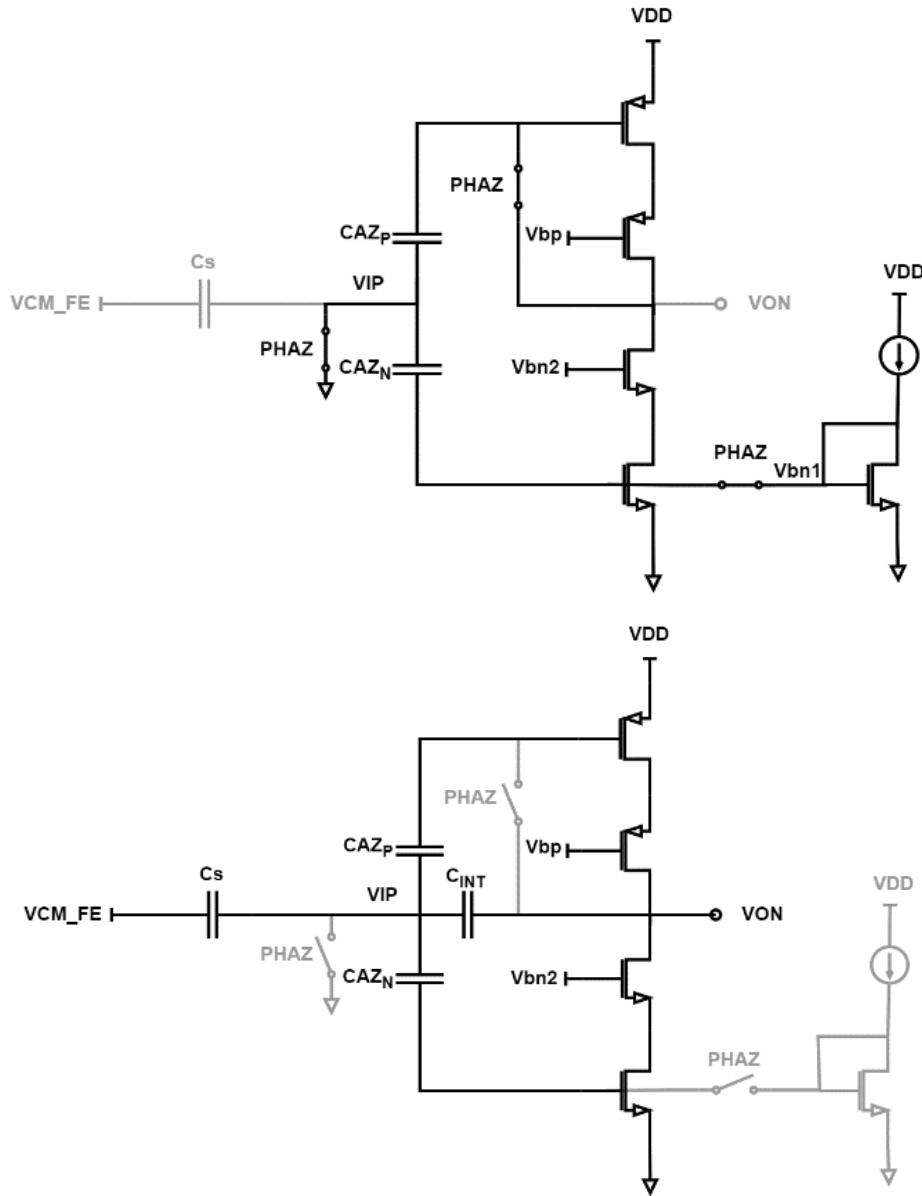

From the die micrograph shown in [Figure 2.1](#) and [Figure 2.2](#), the second largest elements are the autozero capacitors,  $C_{AZ}$ , of the first integrator; therefore, they are the next candidate for area reduction.

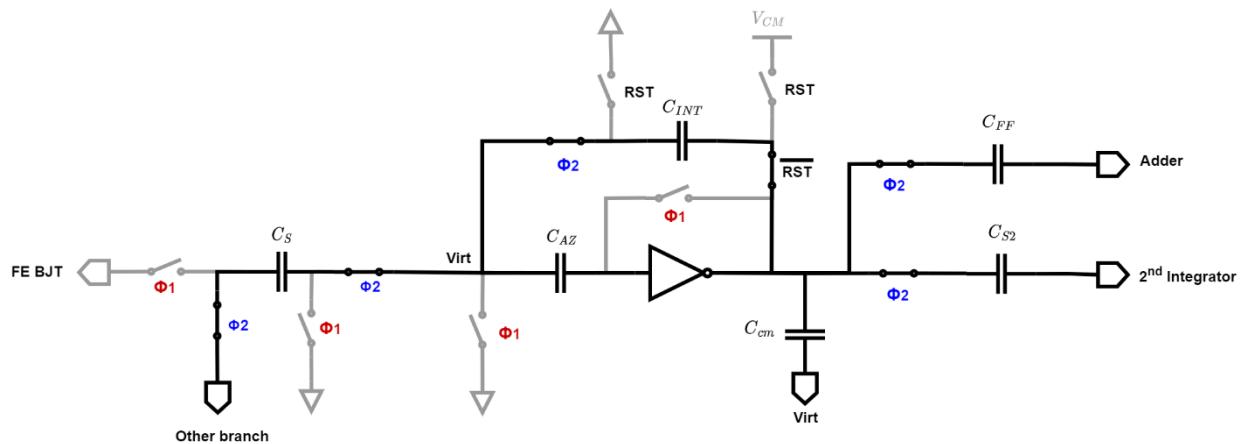

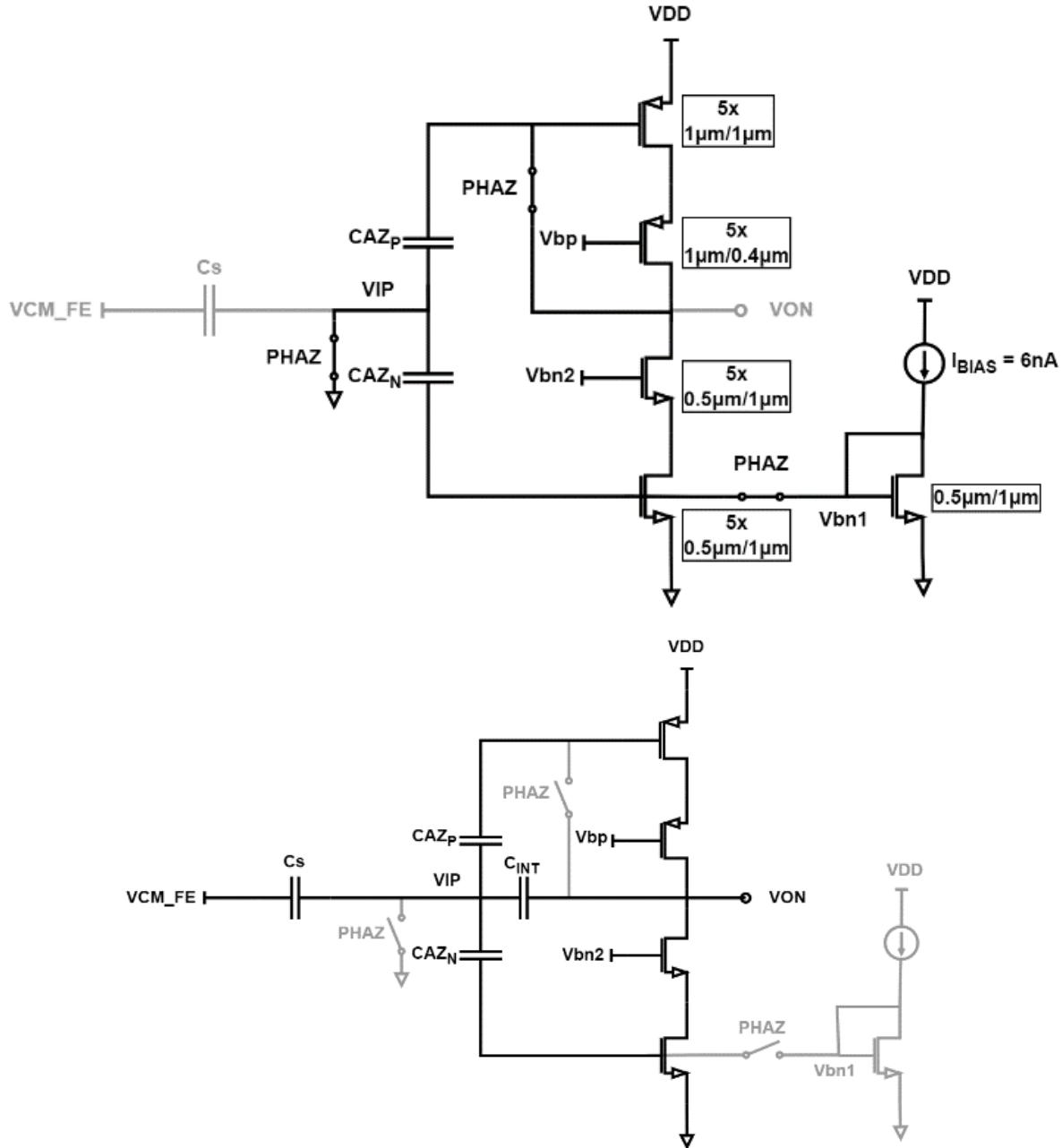

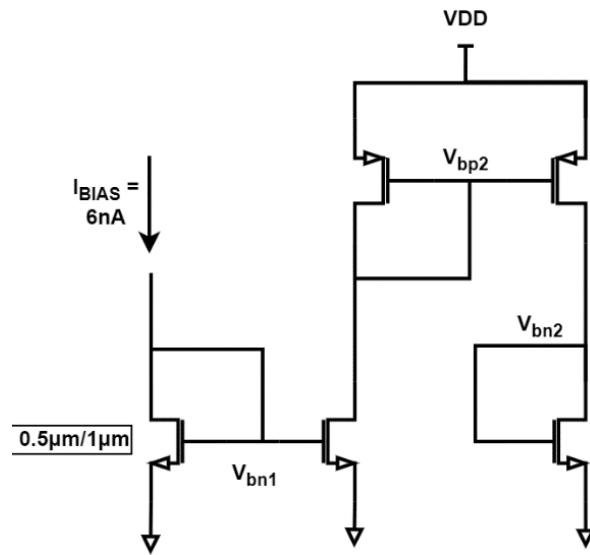

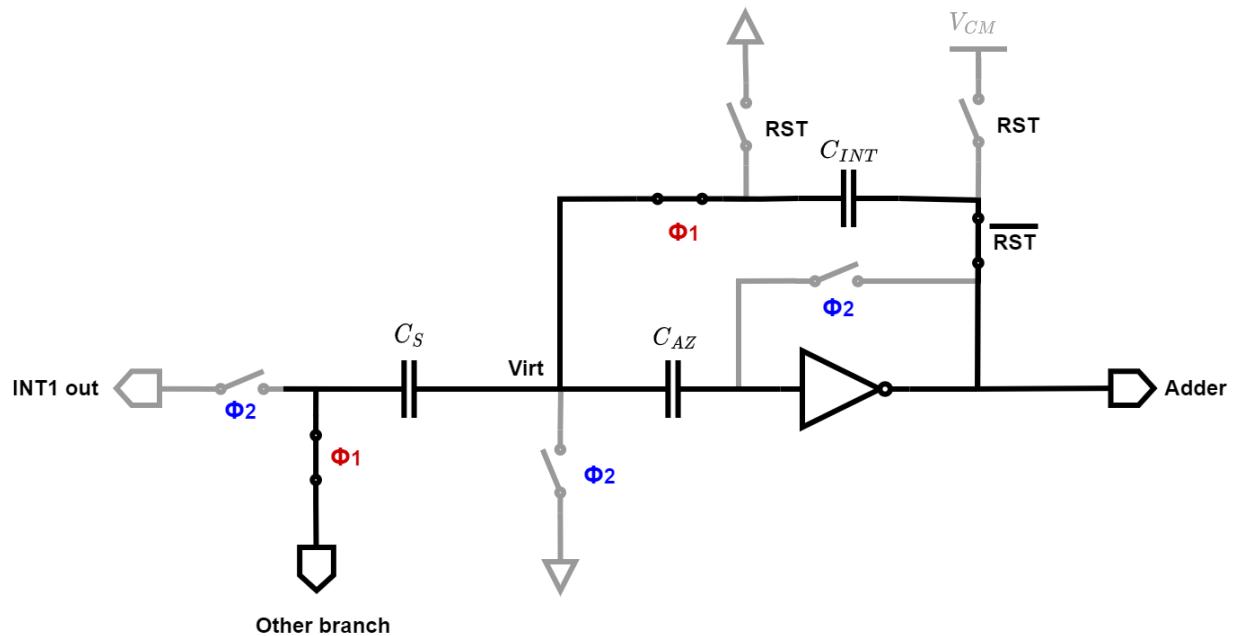

Figure 2.8 shows the front-end and the first integrator of the modulator. An inverter-based amplifier is used because it can operate from a sub-1V supply. The capacitors  $C_{AZ}$  work as level shifters, enabling the amplifier's virtual ground (VirtP and VirtN) to be set at a 0V input common mode ( $V_{CM}$ ). They also act as autozero capacitors, sampling the offset from the output during one phase and subtracting it during the integration phase.

Figure 2.8 a) Front-end and the inverter-based integrator and b) their timing diagram.

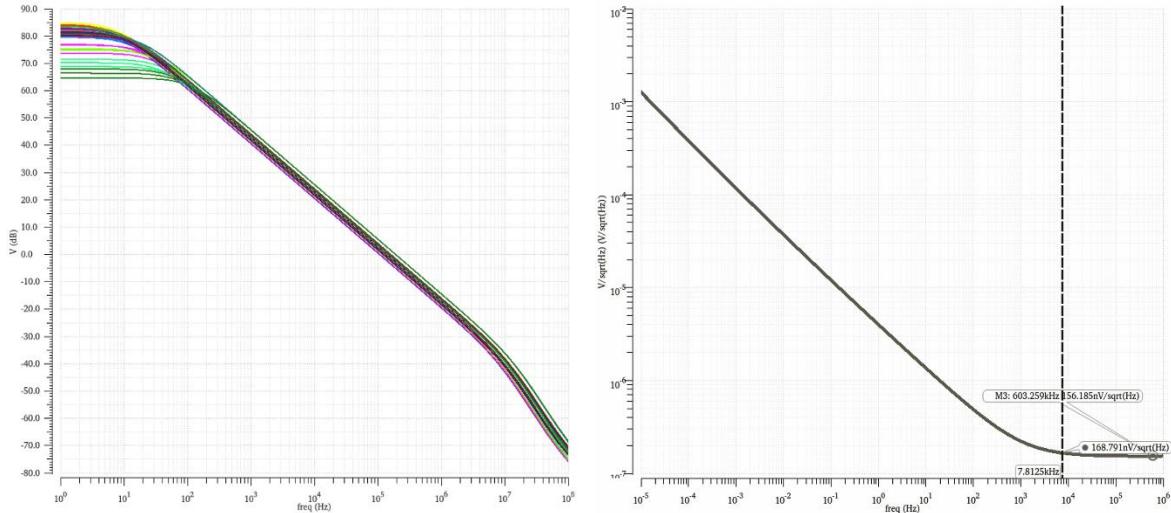

The single-sided operation of the autozeroed inverter-based amplifier is shown in more detail in *Figure 2.9*. During the autozero (also biasing) phase (*Figure 2.9a*), the front-end is disconnected, and the PHAZ switches are closed. The OTA's bias current (originally 160nA) is set by the NMOS current mirror, and a voltage  $V_{bn1}$  is stored on the  $C_{AZ,N}$  capacitor. The bias current is generated using a constant-gm circuit. Similarly, the PMOS input transistor's biasing voltage is set on the  $C_{AZ,P}$  capacitor. Since the amplifier is connected in unity gain, along with the bias voltage, the offset voltage is also stored on  $C_{AZP}$ .

During the integration phase (Figure 2.9b), the PHAZ switches are open: the biasing circuit is disconnected, and the front-end and integration capacitor  $C_{INT}$  are connected for integration, while the autozero capacitors are connected in series with the input to remove offset and provide the bias voltage to the input pairs. The cascode transistors ensure a large gain  $>80\text{dB}$  across PVT. Here, it can be seen that the minimum supply voltage for the OTA is  $V_{gs} + 2V_{dsat}$ , thus permitting sub-1V operation.

Figure 2.9 Single-sided inverter-based amplifier in a) autozero phase; b) integration phase.

The size of the autozero capacitors impacts the amplifier's noise and bias stability as will be discussed in the following.

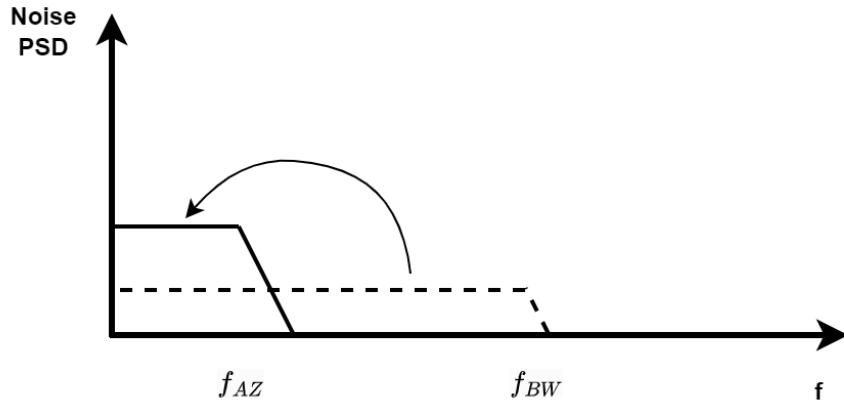

Due to the sampling nature of the autozeroing, some of the amplifier's noise will be under-sampled and folded back to low frequencies (Figure 2.10). The magnitude of the folded-back noise is proportional to the bandwidth of the amplifier during the autozero phase ( $f_{BW}$ ) and inversely proportional to the autozeroing frequency ( $f_{AZ}$ ), and the noise amplification factor at low frequencies is given by [14]:

$$N = \frac{2f_{BW}}{f_{AZ}} \quad (2.9)$$

Furthermore,  $f_{BW}$  directly depends on the size of the autozero capacitor as follows:

$$f_{BW} = \frac{1}{2\pi} \frac{Gm}{C_{AZ}} \quad (2.10)$$

This means that the smaller the  $C_{AZ}$ , the more noise falls in the band due to autozeroing. To ensure that the front-end sensor dominates the noise, the autozero capacitors in [1] were made 4x larger than the sampling capacitors.

Figure 2.10 Noise folding due to autozeroing.

The size of  $C_{AZ}$  also determines how long it can hold the bias voltage in the presence of the leakage currents flowing through the open switches at the gates of the input transistors. The smaller the capacitors, the shorter the duration. Two types of drift are possible: differential drift and common mode drift. Differential drift unequally changes the voltage at the inputs of the differential amplifier's positive and negative sides and causes offset. This is due to the mismatch between the differential half circuits. Common mode drift causes the bias gate voltages of the input pair to change in the same direction, taking the input transistors out of their desired operating region and potentially turning them off. This problem can be resolved either by choosing a large enough  $C_{AZ}$ , optimising the autozero switches for low leakage or reducing the duration for which  $C_{AZ}$  has to hold its charge.

Lastly, the PHAZ switches will inject charge onto the  $C_{AZ}$  capacitors when they open. The smaller the  $C_{AZ}$ , the larger the resulting voltage error. Similar to the leakage of the bias voltage from  $C_{AZ}$  described above, charge injection can lead to a differential drift, resulting in an offset, or a common mode drift. Since charge injection is dependent on the size of the switches, as well as the size of parasitic capacitors at the gate of the amplifier's input pair,  $C_{AZ}$  scaling is a matter of circuit implementation and will be discussed in Chapter 3. However, the issues of noise down-sampling and the offset due to differential drift and charge injection can be resolved by chopping, as will be explained below.

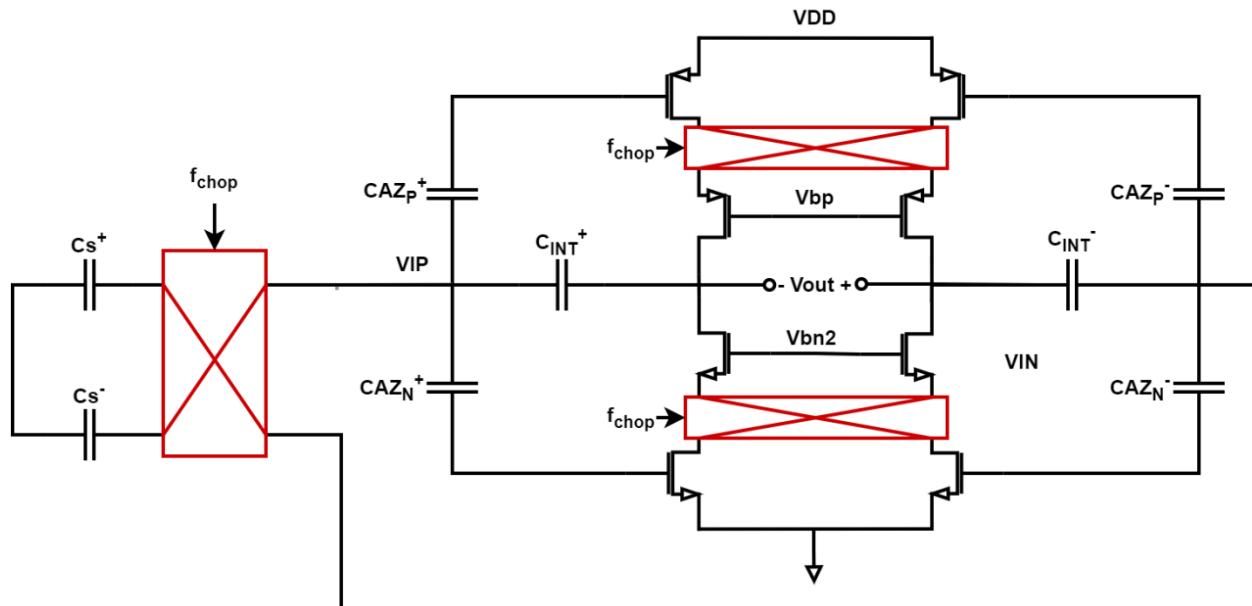

### 2.3.1 Amplifier choppers

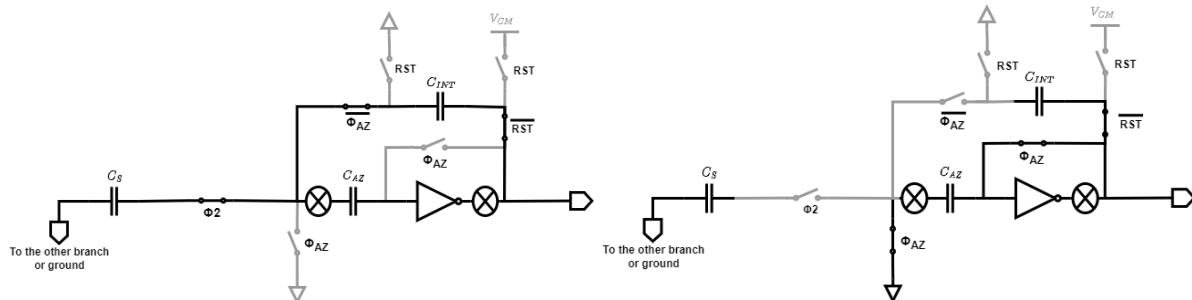

To enable the use of smaller autozero capacitors, the main amplifier can be chopped, as shown in *Figure 2.11*.

Figure 2.11 Chopper added to the first integrator: a) autozero phase; b) integration phase.

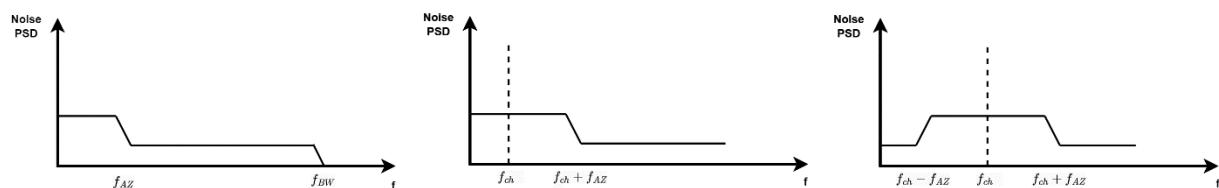

The choppers will upmodulate the offset and noise sampled on  $C_{AZ}$  to the chopping frequency  $f_{CH}$ , as shown in *Figure 2.12*. The chopping frequency should be at least as high as the autozero frequency. If the autozero frequency is larger than  $f_{CH}$ , then as shown in *Figure 2.12b*, some noise will fall in band (around DC). By choosing the chopping and autozeroing frequencies to be at least the same, *Figure 2.12c* shows how the sampled noise on  $C_{AZ}$  is upmodulated out of band.

*Figure 2.13* shows in the time domain how the choppers eliminate the noise and offset sampled on  $C_{AZ}$  for a frequency  $f_{CH} = f_{AZ}$ . Here, during one integration cycle, choppers are in positive polarity, and the noise sampled on  $C_{AZ}$  is positive. During the next integration cycle, the choppers change their polarity, and so does the noise on  $C_{AZ}$ . On average, the noise cancels out across one chopping period (which is two integration cycles). In the next cycle, the amplifier is autozeroing again, and new  $kT/C$  noise is sampled on  $C_{AZ}$ , which is once again cancelled out at the end of one whole chopping period.

Figure 2.12 Noise power spectral density (PSD) versus frequency with a) autozero; b) autozero and chopping for  $f_{CH} < f_{AZ}$ ; c) autozero and chopping for  $f_{CH} \geq f_{AZ}$ .

Figure 2.13 Chopping sampled noise on CAZ in the time domain.

One additional benefit of the choppers is that they can remove the amplifier's flicker noise. By reducing the sampling and integration capacitors, the amplifier's bandwidth increases, or for the same bandwidth requires less current. To reduce the inverter-based amplifier's current, while keeping the same  $gm/Id$ , the transconductance ( $gm$ ) decreases as well. To reduce  $gm$ , the input pair's size decreases, increasing the flicker noise since it is proportional to  $\frac{1}{WL}$ , the inverse of the MOSFET area. The flicker noise corner sets the lower boundary on  $f_{CH}$  (and with that  $f_{AZ}$ ).

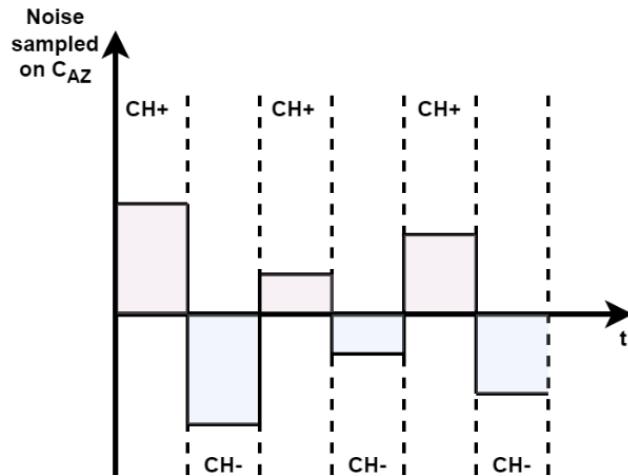

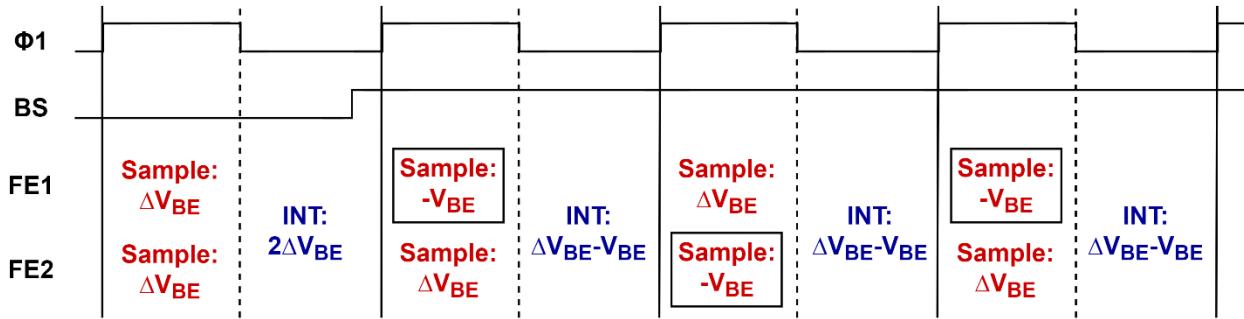

The integrator operates once during each state of the choppers, setting the chopping frequency to be at most  $f_s/2$ . Consequently, the modulator's behaviour can be depicted in Figure 2.14, as explained below.

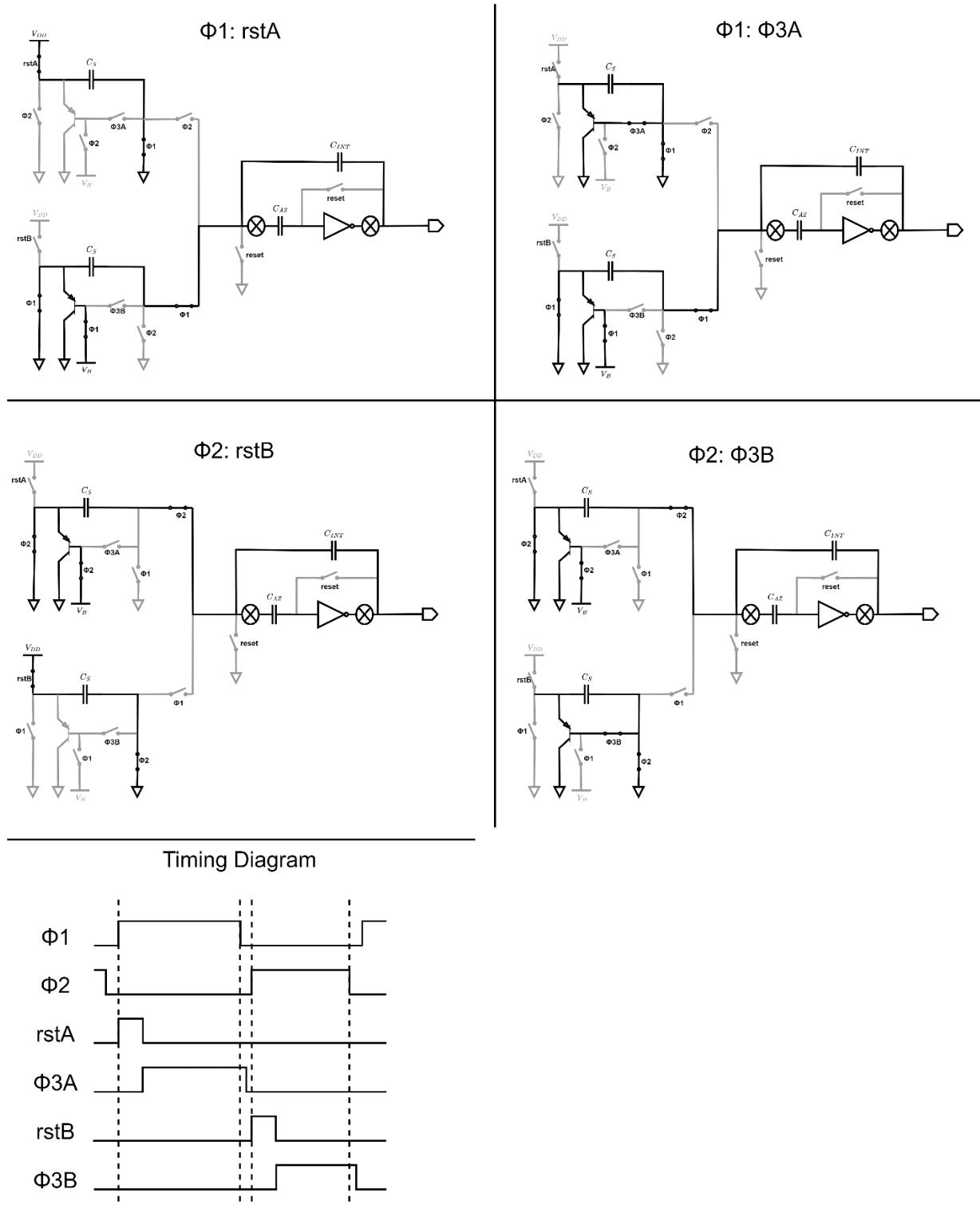

Here we see that during  $\Phi_1$  (Figure 2.14(1,2)) the front-end is sampling the temperature-dependent voltage by precharging the sampling capacitor to supply voltage  $V_{DD}$  and then discharging it across the diode-connected PNP for a specific time. In the meantime, the integrator that is disconnected from the front-end and is autozeroing. Its offset and biasing voltage are stored on the  $C_{AZ}$  capacitor. Then, during  $\Phi_2$  (Figure 2.14(3)) the sampling capacitor is connected to the integrator and the charge is transferred for integration.

In the next  $\Phi_1$  (Figure 2.14(4,5)), the choppers change their polarity, and once again, the front-end samples the temperature-dependent voltage. This time, the integrator is not autozeroing. Instead, it is set in a "do nothing" mode where the charge on the integration capacitors is stored, and no events are happening with the amplifier. Then, once again, in  $\Phi_2$  (Figure 2.14(6)), the charge from  $C_s$  is integrated in an incremental mode. After this, the choppers' polarity is reversed to its original values, and the offset, flicker and thermal noise sampled on the  $C_{AZ}$  are chopped. Afterwards, the amplifier can be autozeroed again.

(1)  $\Phi 1$ :  $\text{rstA}$ ,  $\text{AZ}$ (2)  $\Phi 1$ :  $\Phi 3A$ ,  $\text{AZ}$ (3)  $\Phi 2$ : INT(4)  $\Phi 1$ :  $\text{rstA}$ , Do Nothing(5)  $\Phi 1$ :  $\Phi 3A$ , Do Nothing(6)  $\Phi 2$ : INT

Figure 2.14 a) Integrator behaviour; b) Timing diagram.

## 2.5 Summary

This chapter discussed the system-level design of the proposed temperature sensor built upon the CB temperature sensor given in [1]. In addition to the advantages of the proposed changes, drawbacks were also discussed with proposed methods to mitigate them. These will be taken into consideration when designing the circuit in the following chapter.

# 3 Circuit implementation

In this chapter, the circuit implementation of two main blocks is discussed: the CBD front-end and the delta-sigma modulator readout. After this, the clock control logic is described.

## 3.1 CBD Front-end

Most of the front-end area is occupied by the six sampling capacitors; therefore, as discussed in Chapter 2, they should be made as small as possible (estimated  $C_s = 490\text{fF}$ ) while maintaining good accuracy. However, the choice of BJT also affects the accuracy so this must be decided first.

### 3.1.1 Scaling down the PNP

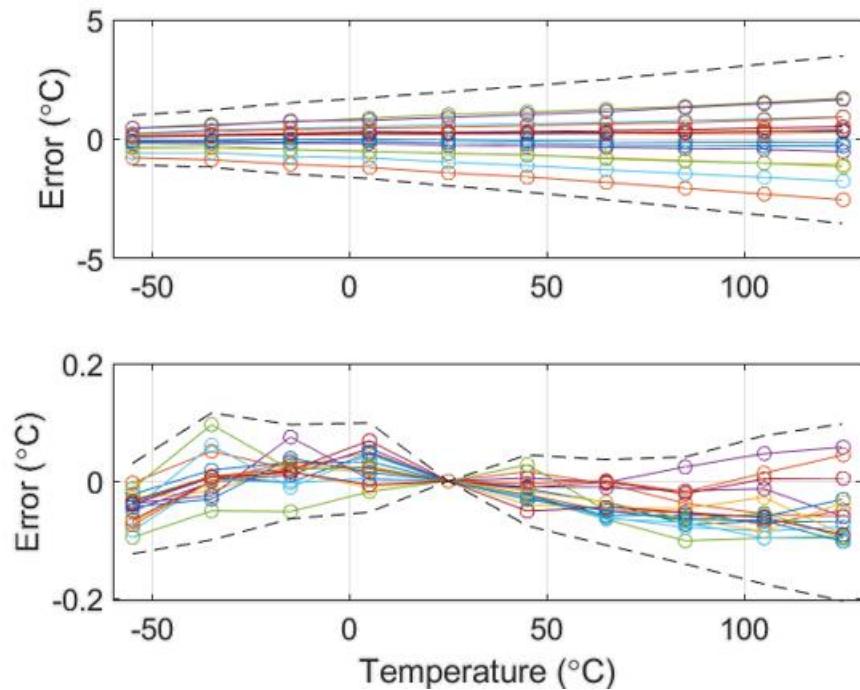

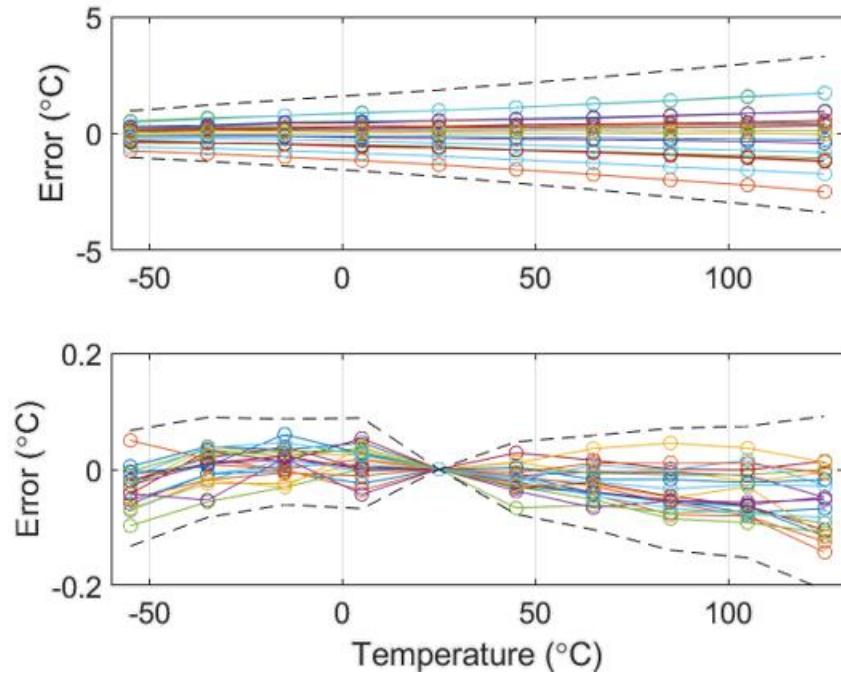

The original design employed  $5 \times 5 \mu\text{m}^2$  PNPs [1]. Implementing the CB front-end shown in *Figure 2.8* with  $C_s = 490\text{fF}$ , a  $5 \times 5 \mu\text{m}^2$  PNP and an ideal readout results in a  $3\sigma$  inaccuracy of  $0.15^\circ\text{C}$  across the temperature range of  $-55^\circ\text{C}$  to  $125^\circ\text{C}$  for a time ratio 32 ( $t_1=32\mu\text{s}$ ,  $t_2=1\mu\text{s}$ ), as seen in *Figure 3.1*. This is in excellent agreement with the measurement results, indicating that the BJTs in this process are well-modelled.

*Figure 3.1* Monte Carlo (20 points, mismatch and process spread) SC CBD inaccuracy with ideal switches and  $C_s = 490\text{fF}$ ,  $VDD=0.9\text{V}$  and  $p = 32$  without (top) and with a 1-point PTAT trim at  $25^\circ\text{C}$  (bottom).

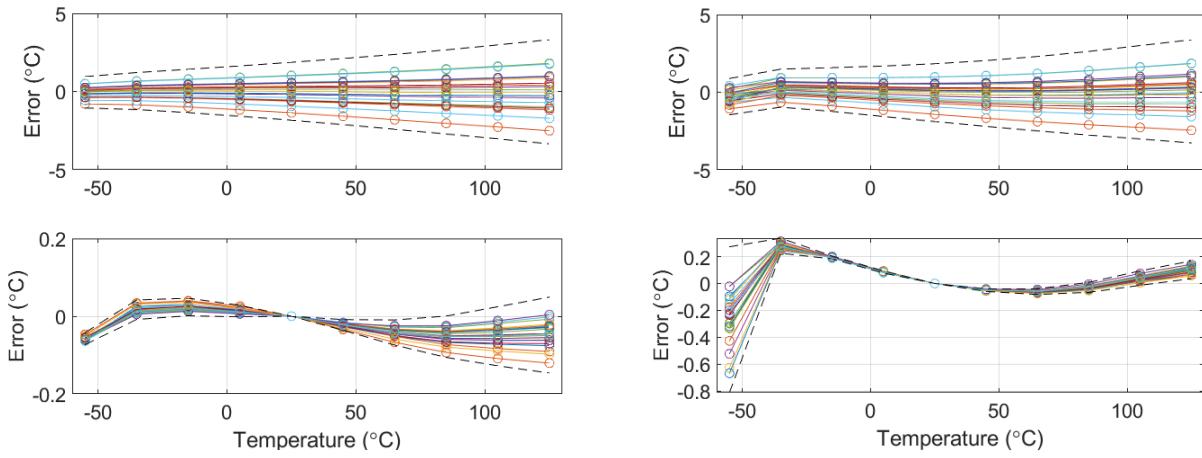

Using a smaller PNP ( $2 \times 2 \mu\text{m}^2$ ) increases the emitter current density, and thus increases  $V_{BE}$ , as shown in *Figure 3.2*. Compared to the  $5 \times 5 \mu\text{m}^2$  device, the accuracy is quite similar ( $3\sigma = 0.16^\circ\text{C}$  *Figure 3.3<sup>[08]</sup>a*), but the ADC range is reduced, resulting in a longer conversion time for equal resolution *Figure 3.4<sup>[08]</sup>a*.

A larger BJT, such as a  $10 \times 10 \mu\text{m}^2$  PNP, would be expected to spread less, and thus achieve better accuracy at the cost of area. Additionally,  $V_{BE}$  will be smaller (*Figure 3.2*) resulting in larger ADC range and shorter conversion time (*Figure 3.4*). However, a larger BJT will have larger parasitic capacitors,  $C_p$ , between emitter and ground, which will decrease the initial voltage across  $C_s$ . If this drops below  $V_{BE}$ , which is highest at low temperatures, it will result in significant errors, as shown in *Figure 3.3b*. To avoid this, the supply voltage needs to be increased above 1V to compensate for the initial voltage drop.

Figure 3.2 a)  $I_E$  and b)  $V_{BE}$  versus time for PNPs of different areas with  $C_s = 490\text{fF}$  and  $VDD=0.9\text{V}$  across temperature.

Figure 3.3 Monte Carlo (20 points, mismatch and process spread) SC CBD inaccuracy with real switches and  $C_S = 490fF$ ,  $VDD=0.9V$  and  $p = 32$  without (top) and with a 1-point PTAT trim at  $25^\circ C$  (bottom) for a)  $2 \times 2$  PNP; b)  $10 \times 10$  PNP.

Figure 3.4 Decimated output over temperature for a  $2 \times 2$ ,  $5 \times 5$  and  $10 \times 10$  PNP device with  $C_S = 490fF$  and  $p = 32$  for a)  $VDD = 0.9V$  and b)  $VDD = 0.95V$ .

Alternatively, an NPN can be used to generate the temperature-dependent voltages  $V_{BE}$  and  $\Delta V_{BE}$ , as shown in Figure 3.5. This was tried in an earlier tape-out, but as can be seen from the measurements shown in Figure 3.6, the resulting sensor exhibits significant non-linearity at high temperatures due to the leakage through the parasitic diode between the deep-n-well collector and the p-substrate. Considering that the area of this diode was minimized by using a custom device with a  $1 \times 1 \text{ mm}^2$  emitter area, it was decided not to use NPNs in this design.

To conclude, a  $5 \times 5 \mu\text{m}^2$  PNP will still be used as the sensing device in the SC front-end.

Figure 3.5 CBD Front-end with NPN device.

Figure 3.6 Measured inaccuracy of a 1x1 NPN-based CBD front end without (top) and with a 1-point PTAT trim at 25°C (bottom).

### 3.1.2 Scaling down the front-end sampling capacitor, $C_S$

Besides the BJT non-idealities discussed in Chapter 2, the minimum size of  $C_S$  is also limited by switch leakage. A version of the SC CBD-based temperature sensor given in [1] with 0.8pF  $C_S$  was taped out, resulting in an inaccuracy of  $0.31^\circ\text{C}$  ( $3\sigma$ ) with  $\text{VDD} = 0.95\text{V}$  (Figure 3.7). Apart from the poor performance of two chips at low temperatures, the sensor's accuracy was limited by leakage at high temperatures, mainly through SW4 and SW5 (Figure 3.8), which will be optimized in this design.

Figure 3.7 Measured inaccuracy of a 5x5 PNP-based CBD front end with  $C_s = 0.8\text{pF}$  without (top) and with a 1-point PTAT trim at  $25^\circ\text{C}$  (bottom).

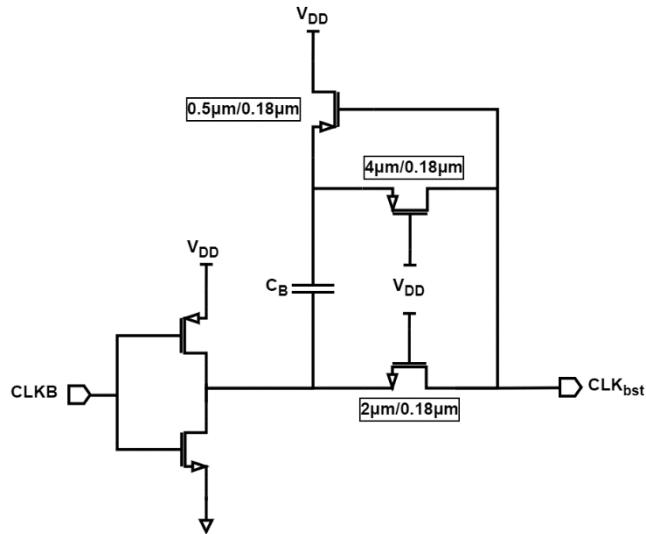

There are two types of leakage: subthreshold leakage from the drain to the source of the switches and leakage through the source/substrate and drain/substrate PN junctions, which become exponentially worse at higher temperatures. To reduce their leakage, the switches were implemented with long NMOS transistors of size  $W/L = 220\text{nm}/700\text{nm}$ . Since  $V_{BE}$  is larger at lower temperatures, an additional PMOS switch of the same size is added in parallel to take over the switch's function at colder temperatures. Additionally, SW5 is implemented with a high-threshold voltage (HVT) NMOS device driven by a boosted  $2V_{DD}$  clock signal. This way, over PVT, the largest leakage current is  $1.12\text{pA}$  through SW4 and  $4.5\text{pA}$  through SW5. They are much smaller than the minimum  $I_E$  of  $880\text{pA}$  at  $125^\circ\text{C}$ .

The reset switch SW1 also shows high leakage and is implemented with a minimum-size PMOS T-switch, resulting in a leakage current of maximum  $1.8\text{pA}$  across PVT.

The SW3 switch was implemented with an NMOS switch of size  $W/L = 4\mu\text{m}/350\text{nm}$ , with a boosted clock signal of  $2V_{DD}$  for low on-resistance of  $270\Omega$  to minimise the voltage drop due to the base current. Additionally, SW3 is surrounded by half-sized dummy switches for low charge-injection.

Lastly, switches SW2 and SW6 are implemented with simple NMOS devices of sizes  $W/L = 500\text{nm}/180\text{nm}$  and  $W/L = 220\text{nm}/180\text{nm}$ , respectively. SW2 was made wider to reduce its on-resistance and the associated voltage drop across it when  $C_s$  is discharging through the BJT.

Figure 3.8 Single-sided front-end with switches a) representation; b) real implementation.

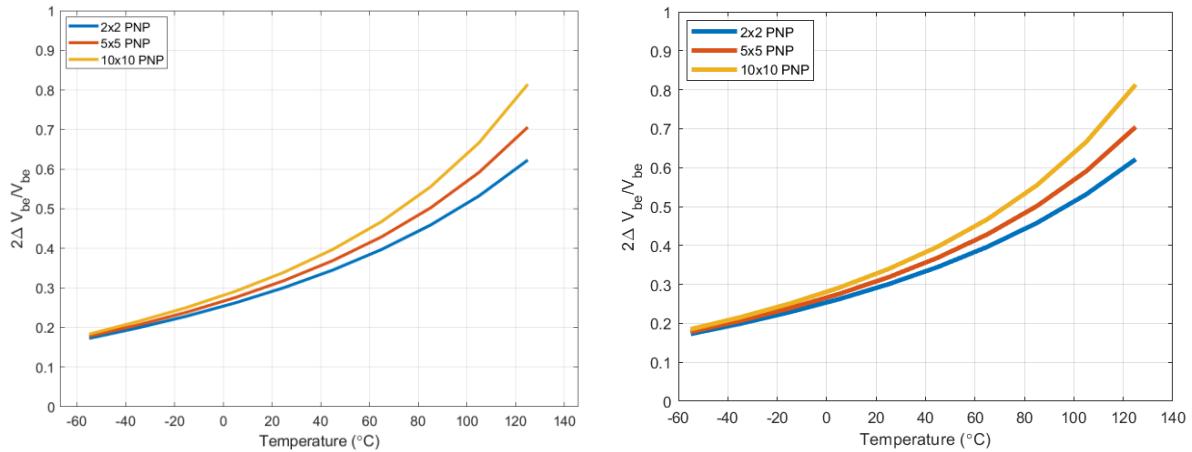

Despite optimising the switch leakage, simulations showed that the bias current had to be increased to 650pA to achieve the target inaccuracy. This choice results in  $C_S = 800\text{fF}$ , and a front-end inaccuracy of  $0.18^\circ\text{C}$  after a single-point PTAT trim at a supply voltage of 0.9V, (Figure 3.9a). Similarly, the inaccuracy at a supply voltage of 0.95V is  $0.19^\circ\text{C}$  (Figure 3.9b).

For the case of shorter discharge times of  $t_1 = 16\mu\text{s}$  and  $t_2 = 0.5\mu\text{s}$ , the inaccuracy plots are shown in Figure 3.10 and result in a  $3\sigma$  inaccuracy of  $0.17^\circ\text{C}$  at a supply voltage of 0.9V.

As a result, the front-end area is approximately five times less than that in [1].

Figure 3.9 Monte Carlo (20 points, mismatch and process spread) SC CBD inaccuracy with real switches and  $C_S = 800fF$  and  $p = 32$  without (top) and with a 1-point PTAT trim at  $25^\circ C$  (bottom) for a)  $VDD = 0.9V$  and b)  $VDD = 0.95V$ .

Figure 3.10 Monte Carlo (20 points, mismatch and process spread) SC CBD inaccuracy with real switches and  $CS = 800fF$  and  $p = 32$ , for halved discharge time  $t1$  and  $t2$  without (top) and with a 1-point PTAT trim at  $250^\circ C$  (bottom) for  $VDD = 0.9V$ .

### 3.1.3. Front-end biasing voltage generator