# Design of a highly efficient charger for Nickel-Iron batteries

# Anil Kumar Ananda

DC Systems, Energy Conversion and Storage

# Design of a highly efficient charger for Nickel-Iron batteries

MASTER OF SCIENCE THESIS

For the degree of Master of Science in Electrical Power Engineering at Delft University of Technology

Anil Kumar Ananda

August 24, 2015

Faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS)  $\cdot$  Delft University of Technology

The work in this thesis was supported by E-stone Batteries Incorporated. Their cooperation is hereby gratefully acknowledged.

### DESIGN OF A HIGHLY EFFICIENT CHARGER FOR NICKEL-IRON BATTERIES

by

Anil Kumar Ananda

in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering

at the Delft University of Technology, to be defended publicly on 28th August, 2015.

Student number: Supervisor: Daily Supervisor: Thesis committee: 4306368 Prof. Dr. Ir. Jelena Popovic - Gerber Ir. Frans Pansier

Prof. Dr. Ir. Pavol Bauer, TU Delft Prof. Dr. Ir. Rene Van Swaaij, TU Delft

An electronic version of this thesis is available at http://repository.tudelft.nl/.

Master of Science Thesis

Anil Kumar Ananda

### Abstract

Obtaining good performance from stand-alone PV systems requires successful integration of batteries that are reliable, effective, long lasting, environmental-friendly and affordable as it is crucial to deal with variable solar illumination throughout the year. Nickel Iron battery technology (Ni-Fe) is a perfect fit for the solar-powered households as it is satisfies all the requirements. Charge controllers need to be efficiently designed for Ni-Fe batteries for protection from overcharge/discharge.

This thesis concentrates on selecting the best topology from  $B^2R$  converters from the patent 550 of ESA to be applied for designing the charge controller for Ni-Fe batteries. An analysis is carried out to determine the advantage of  $B^2R$  converters in the patent over conventional buck-boost topologies like SEPIC or Cuk and evaluate their utility for charge control applications. The focal point of topological selection will be the evaluation of topologies on the basis of efficiency and complexity for realistic adaptation into a charge controller. After defining the load power parameters, the operation of the topologies in two different modes of conduction (BCM & CCM) is investigated and an analytical model is developed for losses. Significant factors that play a role in determining the efficiency for varying source parameters (input voltage) are scrutinized. The relative merits of using BCM/CCM for design are inspected by carrying out simulations for loss calculations using the analytical model with data-sheet parameters from realistic components for their suitability for the application. Component selection is done by keeping in mind the prevalent technologies in the market that are costeffective and the procedure followed in the design of magnetics for the topologies in different modes of conduction and its impact on efficiency is discussed and an assessment is carried out on the performance of the components with variations in input voltage for the same power level.

The proposed analytical models for switching losses in MOSFETs and overall losses topologies are validated by carrying out experiments on the prototypes of two best topologies in both conduction modes. The results critique the accuracy of the analytical model in determining the actual efficiency of the topologies, the margin of deviation by means of comparison with the experimental results and concludes with suggestions for selecting the most efficient topology and recommends a mode of conduction for best results.

# **Table of Contents**

| 1 | Intro | oductio      | n                                  | 1  |

|---|-------|--------------|------------------------------------|----|

|   | 1-1   | Object       | ives of the thesis                 | 1  |

|   |       | 1-1-1        | Research questions                 | 2  |

|   |       | 1-1-2        | Methodology and thesis layout      | 2  |

| 2 | Stat  | e of Ar      | rt                                 | 3  |

|   | 2-1   | Changi       | ing world order - PV proliferation | 3  |

|   | 2-2   | Nickel       | Iron batteries                     | 4  |

|   | 2-3   | Batter       | y charge control                   | 5  |

|   | 2-4   | Role of      | f power converters                 | 6  |

|   | 2-5   | Topolo       | ogical evaluation                  | 6  |

|   | 2-6   | Modes        | of operation                       | 9  |

|   | 2-7   | Efficier     | ncy calculations                   | 10 |

|   | 2-8   | Conclu       | ision                              | 11 |

| 3 | Тор   | ologies      |                                    | 13 |

|   | 3-1   | $B^2 R \; L$ | DC-DC converter topologies         | 13 |

|   | 3-2   | Topolo       | ogies overview                     | 14 |

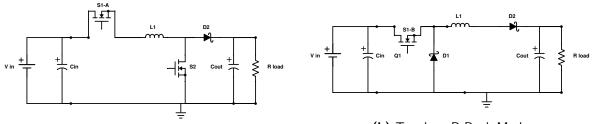

|   |       | 3-2-1        | Topology B                         | 14 |

|   |       | 3-2-2        | Topology A and C                   | 16 |

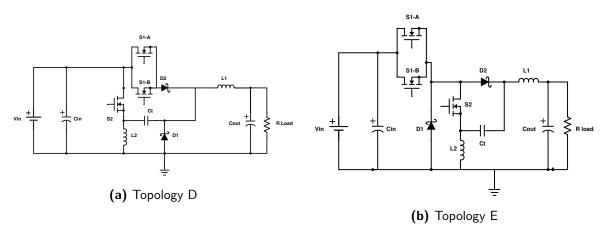

|   |       | 3-2-3        | Topology D and E                   | 16 |

|   | 3-3   | Necess       | sity of switches S1-A and S1-B     | 17 |

|   | 3-4   |              | ng the topology for design         | 18 |

|   | 3-5   |              | arison of the topologies           | 19 |

|   |       | 3-5-1        |                                    | 19 |

|   |       | 3-5-2        | Complexity                         | 19 |

|   |       | 5 5-2        | complexity                         | 10 |

Anil Kumar Ananda

|   | 20    | N / I          | C                                                          |   |       |       |       |   | 10 |

|---|-------|----------------|------------------------------------------------------------|---|-------|-------|-------|---|----|

|   | 3-6   |                | of operation                                               |   |       |       |       |   |    |

|   |       | 3-6-1          | When can BCM become advantageous over CCM?                 |   |       |       |       |   |    |

|   |       | 3-6-2          | Condition for BCM                                          |   |       |       |       |   |    |

|   |       | 3-6-3          | Frequency effects                                          | • | <br>• | <br>· | <br>• | • | 21 |

|   |       | 3-6-4          | Change in magnetics                                        |   |       |       |       |   | 22 |

|   | 3-7   | Conclu         | sion                                                       |   |       | <br>• |       |   | 23 |

| 4 | Loss  | es and         | component selection                                        |   |       |       |       |   | 25 |

|   | 4-1   | Losses         | overview                                                   |   |       |       |       |   | 25 |

|   |       | 4-1-1          | Ripple current and its effect on the device selection      |   |       |       |       |   |    |

|   | 4-2   | Capacit        | tor losses                                                 |   |       |       |       |   | 28 |

|   | 4-3   | Diode I        | losses                                                     |   |       |       |       |   | 29 |

|   |       | 4-3-1          | Modelling forward characteristics                          |   |       |       |       |   |    |

|   |       | 4-3-2          | Modelling recovery characteristics                         |   |       |       |       |   |    |

|   | 4-4   | MOSE           | ET losses                                                  |   |       |       |       |   |    |

|   |       | 4-4-1          | Models for analysis                                        |   |       |       |       |   |    |

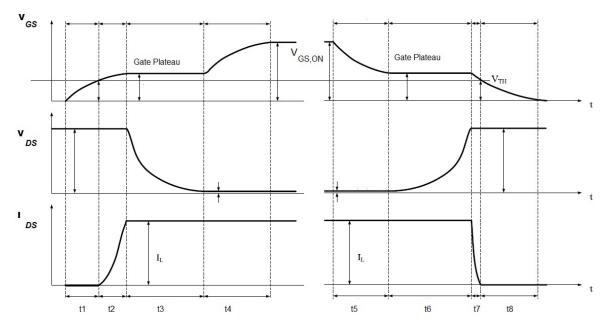

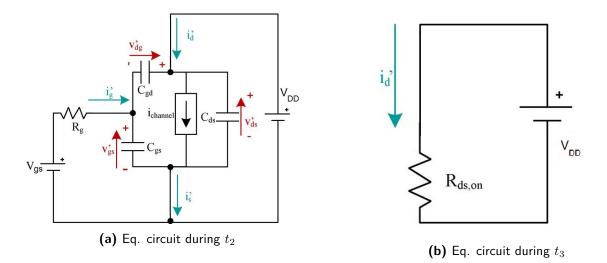

|   |       | 4-4-2          | Switching transitions in CCM                               |   |       |       |       |   |    |

|   |       | 4-4-3          | Switching loss calculations in CCM                         |   |       |       |       |   |    |

|   |       |                | Switching loss calculations in BCM                         |   |       |       |       |   |    |

|   | 4 5   | 4-4-4          | 0                                                          |   |       |       |       |   |    |

|   | 4-5   |                | or losses                                                  |   |       |       |       |   |    |

|   |       | 4-5-1<br>4-5-2 | Core loss calculations                                     |   |       |       |       |   |    |

|   |       | -              | Winding loss calculation for CCM                           |   |       |       |       |   |    |

|   | 4-6   |                | nent selection                                             |   |       |       |       |   |    |

|   | 4-7   |                | or selection                                               |   |       |       |       |   |    |

|   |       | 4-7-1          | Core selection                                             |   |       |       |       |   |    |

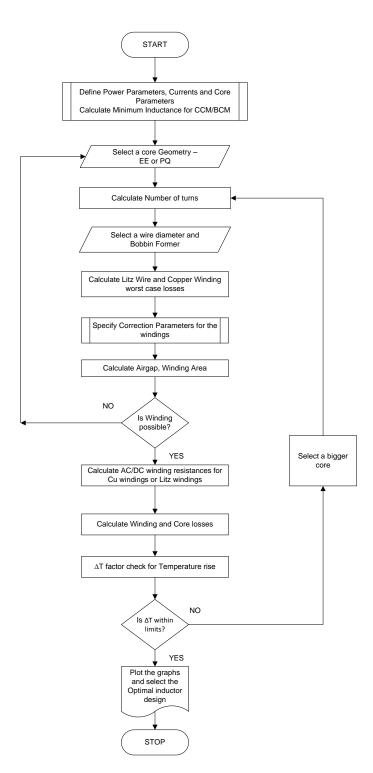

|   |       | 4-7-2          | Design of the inductor                                     |   |       |       |       |   |    |

|   |       | 4-7-3          | Optimising the design                                      |   |       |       |       |   |    |

|   |       | 4-7-4          | Windings - Litz wires                                      |   |       |       |       |   |    |

|   |       | 4-7-5          | Conduction mode based design $\ldots \ldots \ldots \ldots$ |   | <br>• |       |       | • | 45 |

|   | 4-8   | Capacit        | tor selection                                              |   |       |       |       |   | 46 |

|   |       | 4-8-1          | Significance of selecting transfer capacitance             |   |       |       |       |   | 46 |

|   |       | 4-8-2          | Ripple ratings of capacitors                               |   |       |       |       |   | 47 |

|   | 4-9   |                | on of active devices                                       |   |       |       |       |   |    |

|   | -     | 4-9-1          | Initial parameters for diode and switch selection          |   |       |       |       |   |    |

|   | 4-10  | Diode s        | selection                                                  |   |       |       |       |   |    |

|   | •     | 4-10-1         | Selection of diode technology                              |   |       |       |       |   |    |

|   | 4-11  |                | ET selection                                               |   |       |       |       |   |    |

|   |       |                | MOSFET selection parameters                                |   |       |       |       |   |    |

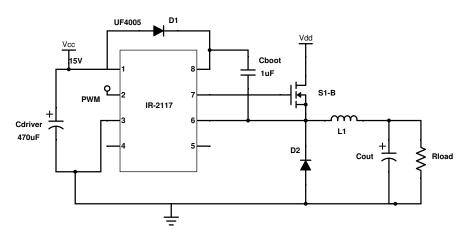

|   | 4-12  |                | ET drivers                                                 |   |       |       |       |   |    |

|   |       |                | High side and Low side drivers                             |   |       |       |       |   |    |

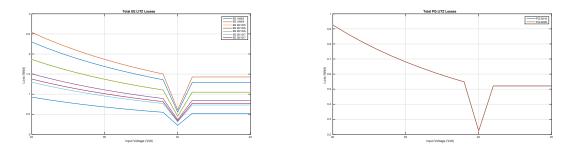

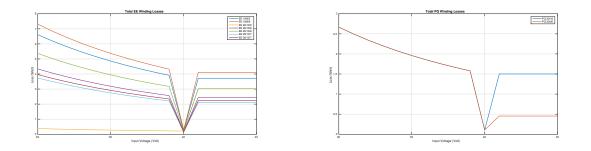

|   | 4-13  |                | tion results of analytical models                          |   |       |       |       |   |    |

|   | . 10  |                | Inductor losses                                            |   |       |       |       |   |    |

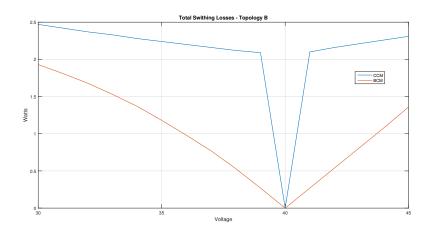

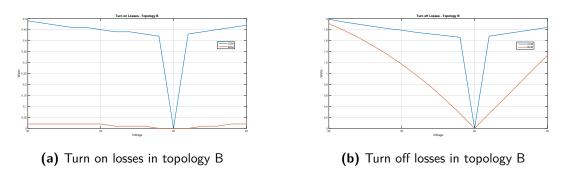

|   |       |                | Switching losses                                           |   |       |       |       |   |    |

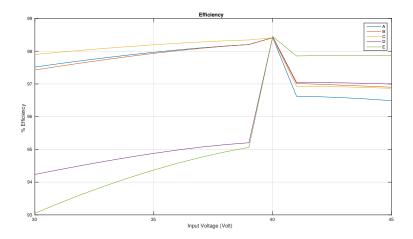

|   |       |                | Overall efficiency                                         |   |       |       |       |   |    |

|   | 1 1 1 |                | sion                                                       |   |       |       |       |   |    |

|   | 4-14  | CONCIUS        | 51011                                                      |   |       |       |       |   |    |

Anil Kumar Ananda

Master of Science Thesis

| 5 | Pro | totypes | and Experimental Results                                     | 59 |

|---|-----|---------|--------------------------------------------------------------|----|

|   | 5-1 | Overvi  | iew of Measurements                                          | 59 |

|   |     | 5-1-1   | Bandwidth of the Oscilloscope                                | 59 |

|   |     | 5-1-2   | Voltage measurement                                          | 60 |

|   |     | 5-1-3   | Current measurement                                          | 60 |

|   | 5-2 | Topolo  | ogy B and C experiments                                      | 60 |

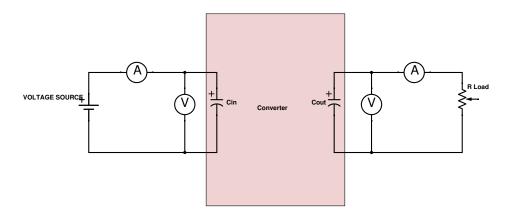

|   |     | 5-2-1   | Experimental set-up                                          | 61 |

|   |     | 5-2-2   | Experimental determination of efficiency                     | 62 |

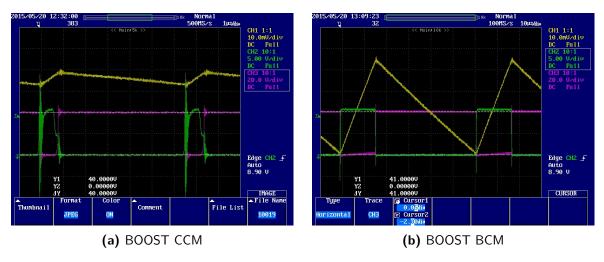

|   |     | 5-2-3   | Topology B in CCM and BCM                                    | 63 |

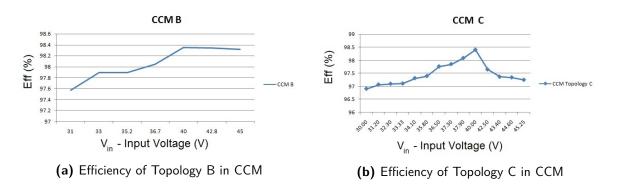

|   |     | 5-2-4   | Topology C in CCM and BCM                                    | 64 |

|   |     | 5-2-5   | Comparison with analytical model for efficiency calculations | 65 |

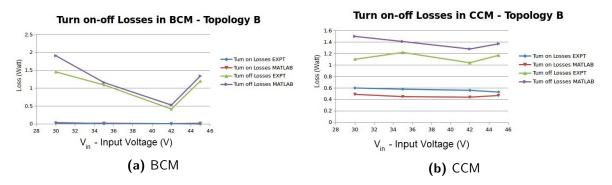

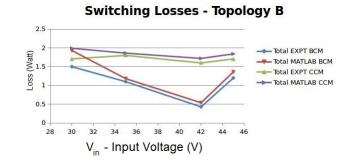

|   | 5-3 | Deterr  | nination of switching losses                                 | 66 |

| 6 | Con | clusion | s and future work                                            | 69 |

|   | 6-1 | Conclu  | usions                                                       | 69 |

|   | 6-2 | Sugge   | stions for future work                                       | 71 |

| 7 | Арр | endix   |                                                              | 73 |

# **List of Figures**

| 2-1 | Buck Boost Converter                                                                     | 7 |

|-----|------------------------------------------------------------------------------------------|---|

| 2-2 | Cuk Converter                                                                            | 7 |

| 2-3 |                                                                                          | 8 |

| 2-4 | Two inductors buck converter topologies $[1]$                                            | 8 |

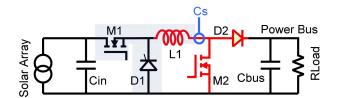

| 2-5 | Non-Inverted buck cascaded by a boost converter [1]                                      | 9 |

| 2-6 | Two inductors boost converter topologies [1]                                             | 9 |

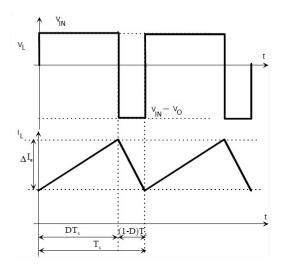

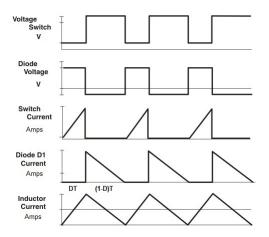

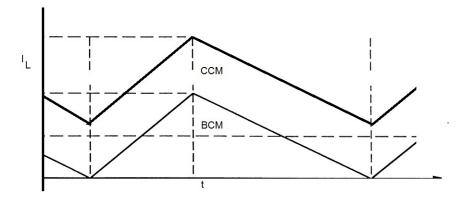

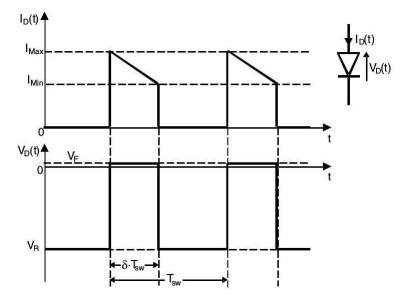

| 2-7 | CCM and BCM                                                                              | ) |

| 3-1 | Topology B                                                                               | 4 |

| 3-2 | Current and Voltage waveforms in Topology B in Boost mode                                | 5 |

| 3-3 | Current and Voltage waveforms in Topology B in Buck mode $\ldots$ $\ldots$ $\ldots$ $15$ | 5 |

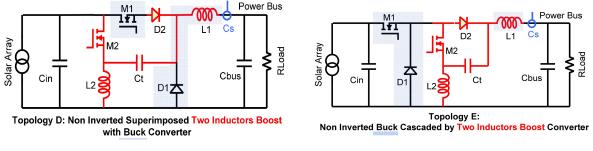

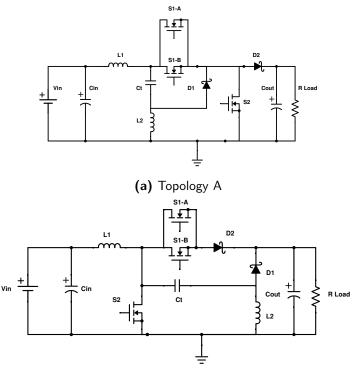

| 3-4 | Two inductors buck based converter topologies                                            | 6 |

| 3-5 | Two Inductor Boost Based Converter Topologies                                            | 7 |

| 3-6 | Necessity of S1-A and S1-B                                                               | 3 |

| 3-7 | Diff. in BCM and CCM Modes (Not to scale)                                                | 1 |

| 3-8 | BCM frequencies                                                                          | 2 |

| 4-1 | Losses Overview                                                                          | 6 |

| 4-2 | Current Wave-shapes                                                                      | 7 |

| 4-3 | Diode current waveform [2]                                                               | 9 |

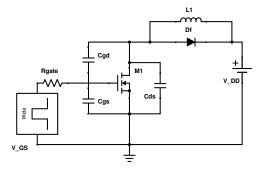

| 4-4 | Switching loss model                                                                     | 2 |

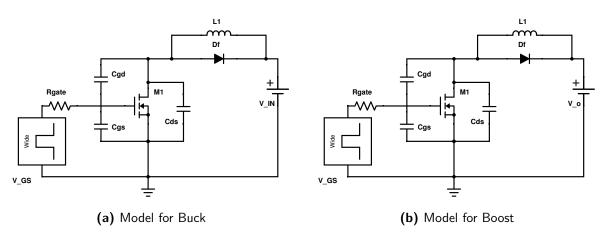

| 4-5 | Switching loss models for Buck and Boost                                                 | 2 |

| 4-6 | Switching transitions in CCM $\ldots$ $\ldots$ $\ldots$ $\ldots$ $34$                    | 4 |

| 4-7 | Turn on loss equivalent circuits [3]                                                     | 5 |

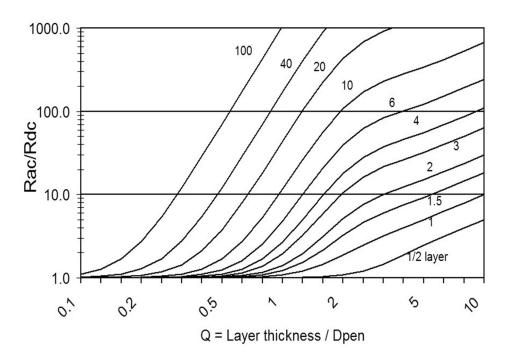

| 4-8 | Dowell's Curve [4]                                                                       | 9 |

| 4-9 | Flowchart for Inductor Design                                                            | 4 |

|     | -                                                                                        |   |

Anil Kumar Ananda

| 4-10 | IR-2117 Schematic                                                      | 51 |

|------|------------------------------------------------------------------------|----|

| 4-11 | LT-1910 Schematic                                                      | 52 |

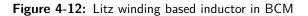

| 4-12 | Litz winding based inductor in BCM                                     | 53 |

| 4-13 | Copper winding based inductor in BCM                                   | 54 |

| 4-14 | Overall losses in both buck and boost regions in BCM and CCM           | 64 |

| 4-15 | Switching loss breakdown                                               | 55 |

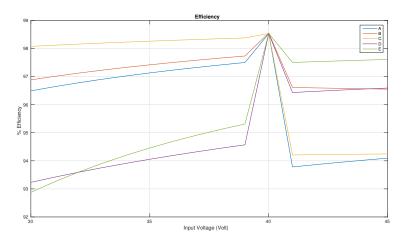

| 4-16 | Efficiency of Topologies in CCM                                        | 55 |

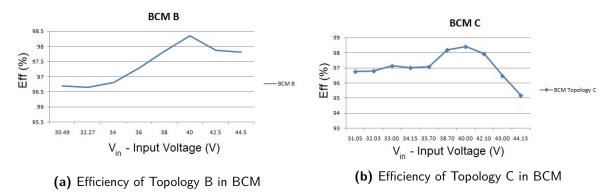

| 4-17 | Efficiency of Topologies in BCM                                        | 66 |

| 5-1  | Measurement points                                                     | 61 |

| 5-2  | CCM and BCM Boost                                                      | 63 |

| 5-3  | CCM experimental efficiencies in Topology B and C                      | 64 |

| 5-4  | BCM experimental efficiency in Topology B and C                        | 64 |

| 5-5  | Switch losses determination apparatus for boost mode                   | 66 |

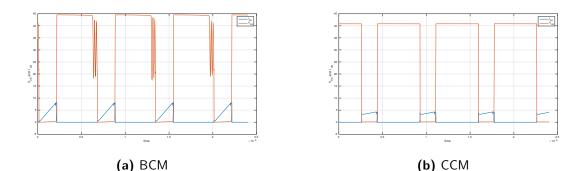

| 5-6  | Switching transitions in topology B in BCM and CCM                     | 67 |

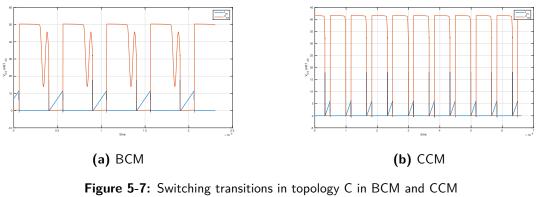

| 5-7  | Switching transitions in topology C in BCM and CCM                     | 67 |

| 5-8  | Recovery during switching on transitions in Topology B in Boost mode 6 | 68 |

| 5-9  | Turn on and off loss- Analytical Model validation                      | 68 |

| 5-10 | Switching loss - overall                                               | 68 |

| 6-1  | Synchronous Buck-Boost topology                                        | 71 |

\_\_\_\_\_

# **List of Tables**

| 2-1 | Risk Assessment for battery technologies [5] | 5 |

|-----|----------------------------------------------|---|

| 3-1 | Power parameters                             | 4 |

| 3-2 | Number of passive components                 | 9 |

| 4-1 | Switching losses in CCM                      | 4 |

| 4-2 | Litz wire reference table                    | 0 |

| 4-3 | Table for correspondence of K    4           | 1 |

| 5-1 | Component Values                             | 1 |

| 5-2 | Efficiency of Topology B in CCM              | 4 |

| 5-3 | Experimental efficiency of Topology B in BCM | 5 |

| 5-4 | Experimental efficiency of topology C CCM    | 5 |

| 5-5 | Experimental efficiency of topology C BCM    | 5 |

\_\_\_\_\_

# List of Abbreviations and Acronyms

| AC          | Alternating Current                                                   |

|-------------|-----------------------------------------------------------------------|

| BCM         | Boundary Conduction Mode                                              |

| BIPV        | Building Integrated Photo Voltaics                                    |

| BMS         | Battery Management System                                             |

| DET         | Direct Energy Transfer                                                |

| ESR         | Equivalent Series Resistance                                          |

| CCM         | Continuous Conduction Mode                                            |

| CSP         | Concentrated Solar Power                                              |

| DC          | Direct Current                                                        |

| DCM         | Discontinuous Conduction Mode                                         |

| ESA - ESTEC | European Space Agency - European Space Research and Technology Centre |

| GaN         | Gallium Nitride                                                       |

| MOSFET      | Metal Oxide Semiconductor Field Effect Transistor                     |

| Ni -Fe      | Nickel - Iron                                                         |

| PV          | Photo Voltaic                                                         |

| PVMD        | Photo Voltaic Materials and Devices                                   |

| RMS         | Root Mean Square                                                      |

| SEPIC       | Single Ended Primary Inductor Converter                               |

| SMPS        | Switch Mode Power Supplies                                            |

| VRLA        | Valve Regulated Lead Acid                                             |

| ZCS         | Zero Current Switching                                                |

## Acknowledgements

As I look back on my time at Delft,

I would like to appreciate and wholeheartedly thank my supervisor, Prof. Jelena Popovic, for her support, patience, kindness, humour, and insights shared during this year long journey of the master thesis which has rewarded me immensely. I am thankful for the many discussions and advice over the past few months and grateful for the opportunity to learn from someone like her.

I must also thank my adviser, Ir. Frans Pansier, for his guidance through every design process involved in the report. His experienced, scholarly outlook towards power supplies and witty presentation of concepts kept motivating me to try novel things. To meet someone and be associated with insightful breadth and depth of understanding has been an amazing experience I will cherish.

This project would not have been possible without the drive and support of Ir. Thomas Van Dijk, the head of E-stone batteries. I would like to thank him for trusting me with this idea and enabling me with good contacts and unconditional support for its fruition.

The power processing group (DCNS) is blessed with friendly, very erudite PhDs like Udai, Tsegay, Venugopal, Nishant and Laurens who have helped me during the course of my thesis for which I am thankful. I would also like to thank the faculty in the labs, Bart, Joris and Harry who helped me throughout my experimental analysis. The student room ensured a supportive and jovial environment during the course of the thesis with Vinay, Emanuelle, Nefeli and Nikos for which I am grateful.

Finally, my stay at the University would have been incomplete without my association and experiences in terms of travel, cooking, debates and banter with my closest friends Avinash, Soumya, Jaggu, Harsha, Debu and Murugan. Thank you guys!

Anil Kumar Ananda Delft, June 2015 This thesis is dedicated to my Appa, Amma and Ajji who have encouraged and supported me through all my endeavours. My salutations to you!

"Nothing in life is to be feared, it is only to be understood. Now is the time to understand more, so that we may fear less."

"Be less curious about people and more curious about ideas."

— Marie Sklodowska-Curie

"Dream is not that which you see while sleeping it is something that does not let you sleep."

— A.P.J. Abdul Kalam

## Chapter 1

## Introduction

The reliance on fossil fuels has seen a slight dip with the proliferation of economic integration of sources with cleaner, greener and sustainable renewable energy source in the  $21^{st}$  century. Photovoltaic energy generation is popular and perhaps the most promising emerging renewable energy generation due to the fact that the installation expenses of solar modules have decreased in the recent years and the whole system cost has reduced by as much too.

However, for its successful integration, PV resources are coupled with grids in most parts of Europe. In many developing countries, standalone systems are employed where grids do not exist. For the economical viability of a PV system in an off-grid environment, a reliable battery technology that is inexpensive will be key as the nature of solar insolation varies. As batteries become cheaper and more reliable, solar energy generation can reach high levels and evolve to power households. The main objective of this dissertation is to select the most appropriate DC-DC non-isolated buck-boost topology out of patent 550 [1] of ESA-ESTEC to implement battery charger for Ni-Fe batteries.

### 1-1 Objectives of the thesis

In cases where power electronic topologies are involved, specific details of the active/passive components and power parameters such as current and voltage through them will become crucial which will be explored in the parts of this report and an analytical model for losses is developed for boundary conduction mode (BCM) and continuous conduction mode (CCM) of operation. Experimental determination of results obtained by the analytical model will be verified under lab conditions and the deviation of values in terms of losses calculated will be reasoned with. The problem statement for the thesis will be as follows

#### 1-1-1 Research questions

- Which topology can be selected to build a highly efficient battery charger for Ni-Fe batteries in the patent 550 [1]?

- For the battery charging application, is BCM or CCM an optimum solution?

- What are the potential benefits of employing BCM/CCM control?

- What is the methodology followed to ensure that an optimum topology is chosen?

- Under BCM/CCM, how can one optimise the design for a specific application?

### 1-1-2 Methodology and thesis layout

This thesis is intended to analyse the viability and adapt the topologies for battery charging applications.

- In chapter 2, the recent advances in PV generation and battery storage are discussed along with the power electronics which forms the spine for charge control application. Recent trends in battery storage, PV generation for standalone systems and techniques followed to analyse topologies are discussed.

- In chapter 3, all the five topologies are discussed and several criteria including modes of operation and parameters that will aid in simplifying the selection are deliberated.

- In chapter 4, losses in the topologies, the analytical model for calculation in both modes of operation and magnetics associated are discussed and the chapter concludes based upon the results obtained from the simulations carried out for losses and magnetics designed.

- In chapter 5, experimental results are compared to simulations to understand the deviation from theoretically calculated values of the analytical models

- Summing up all the results and conclusion of the thesis is done in chapter 6. This will be followed by the appendix.

## Chapter 2

### State of Art

### 2-1 Changing world order - PV proliferation

The shift from fossil fuels to sustainable energy sources is inevitable. With depleting oil resources and greenhouse gas proliferation, it is an undeniable fact that there is a stress on conducting research on the same. The real challenge for the shift is to integrate the sustainable sources is to find viable methodologies to harness these renewable sources and convert the form of energy like wind/solar to practicable form - Electricity [6]. Due to a scarcity of high wind areas in domestic settlements, solar energy is much widely adopted. Ongoing research areas like photovoltaic materials and devices (PVMD) focus on developing effective ways of efficiently converting energy from the Sun, which is a limitless source of energy.

Concentrating solar power (E.g. DESERTEC) [7] and photovoltaics (panels) [8] are two common methods of converting energy from solar radiation to electricity. In case of concentrating solar plants (CSP), heliostats focus sunlight onto a tower providing heat for generation of electricity.

An increasingly popular trend that is enabled thanks to feed-in-tariff policies and price decrease is employing PV cells in modules to directly generate DC from the solar insolation. They are easy to install, making them viable for wider adoption. To meet the challenge in making solar energy cost much more competitive, the capital costs for hardware and installation of PV systems can become a bottleneck. To ease these constraints, governments have formulated policies to provide subsidies and feed-in tariffs.

With the growth of PV installations in the residential, utility and commercial segments to continue [6], one of the biggest hassles of PV technology to be adapted as a means of electricity generation is the intermittent behaviour of the source. Combining battery banks with PV systems in the off grid systems is beneficial in remote areas where a centralised grid is not accessible.

Recent advancements in battery technologies and in power electronics and control systems to monitor and control battery power levels, have enabled storage to be viable economically in combination with PV systems to utilise the energy stored during the day, in the evening after the sun has gone down [9].

### 2-2 Nickel Iron batteries

The battery storage can also be of great benefit commercially for those whose utility billing agreements have a requirement to pay demand charges for consuming power during off-peak hours [10]. Selection of a battery for applications is determined by the following parameters [11]

- Cycle life

- Nominal discharge rates

- Self-discharge rate

- Performance under extreme temperature

- Maximum current drain capacity (in Ampere-Hours)

- Watt-hours per unit weight

- Watt-hours per unit volume

- Maintenance over the life cycle

- Cost of operation per watt-hour

The above-discussed parameters are specific for applications. Desired characteristics for a PV battery in terms of performance is summarised in [11] as

- Moderately high cycle life

- High capacity appreciation at slow rate of discharge

- Highly reliable rates under conditions of cyclic discharge

- Necessity of low equalisation and boost charging

- Good watt-hour and ampere-hour efficiency under different SoC (State of Charge)

- Low self-discharge rates

- Broad temperature range under operating conditions

- Requirement for robust construction low maintenance

- Cost effectiveness to integrate with the system with low initial costs

Valve regulated lead acid (VRLA), Nickel-Metal-Hydride (NiMH), Nickel-Iron(Ni-Fe) and Lithium Ion (Li-ion) batteries are most commonly used battery technologies [10] . Ni-Fe batteries are typified by good mechanical strength and long life (up to 8 years) under well-maintained conditions. These batteries can remain non-functional at ambient temperatures of up to  $40^{\circ}$ C for a long duration under conditions of various SoC performing under negligible loss of charge and deterioration [5].

4

Battery life for Ni-Fe batteries is unaffected by overcharge at normal charge rates. They have high reversibility of charge/discharge reactions leading to long service life implying that the Ni-Fe batteries are well suited to be used for PV applications [12] [13].

Table 2-1 discusses the risk assessment of batteries of type Valve Regulated Lead Acid (VRLA), Lithium Ion, Ni-Fe and Zinc Bromide redox.

As seen from the table, VRLA and Zinc Bromide redox batteries pose maximum risk of

| Characteristic                | VRLA    | Li-ion          | Ni-Fe   | Zn- $Br$ - $Redox$ |

|-------------------------------|---------|-----------------|---------|--------------------|

| Fire ignition risk            | Minimal | Medium          | Minimal | High               |

| Self Ignition risk            | Minimal | High            | Nil     | Minimal            |

| Environmental<br>hazards      | High    | High            | Nil     | High               |

| Persistance<br>in environment | High    | Not established | Nil     | High               |

| Human Toxicity<br>risk        | High    | High            | Minimal | High               |

| Recycling<br>requirements     | High    | Not established | Nil     | High               |

| Overall hazard<br>rating      | Medium  | High            | Low     | Very High          |

Table 2-1: Risk Assessment for battery technologies [5]

toxic material to the environment. Lithium-ion battery type has the highest fire risk among the battery technologies. Minimal toxic material risk is observed from components in Ni-Fe batteries. It is environmentally safe to dispose of without any hazardous substance risk and they degrade very slowly with usage. However, Ni-Fe batteries have low capacity at a higher temperature and a very high weight to ampere-hour capacity ratio. Also, they have a selfdischarge of up to 1-2% of the rated capacity at 27°C per day [14] and as high as 8-10% of rated capacity per day when the operational temperature reaches 40°C which is a challenge for its successful integration. From the perspective of its utilisation for PV batteries, it can be preferably used for applications in which the duty schedule would allow a recharge at least once in two days so that at least 80% of the rated capacity will be available for the loads during discharge.

### 2-3 Battery charge control

A battery charge control device also known as charge controller maintains the battery array at the highest possible state of charge (SoC) protecting it from over-charge by the PV arrays connected to it and from over-discharge by the loads connected to it. Any system involving loads with high transients, high user intervention and undersized battery storage (economic reasons) has to employ battery charge control [15].

An optimum control strategy is a measure of the effectiveness of charging/discharging of the battery and utilisation of PV generation to meet the demand of the load. However, it should also feature protection against external factors such as temperature; voltage sense leads will

help maintain the battery health and extend its operating lifetime [16] [17].

### 2-4 Role of power converters

The heart of a charge controller is its power converter also known as charger is dedicated to adjust the power parameters suited to operate the battery charging and discharging safely and efficiently despite changing input conditions from the solar panels. The power converters can step-up or step-down or step-up/down the voltage depending upon the power parameters described by the battery and solar panel manufacturers. Normally used power converter topologies for step down, step up and step up/down are the buck, boost and buckboost/flyback topologies due to their ease of implementation. There are some primary factors to be considered for the purpose of power conversion in charging applications.

- Voltage and current parameters of solar array and battery stack

- Environmental conditions

- Battery technology

Power converters have proliferated in the form of Switched Mode Power Supplies (SMPS) in the past decade and they are turning out to be path-breaking in terms of increasing the power density and reducing the volume of the system [18]. Switches and diodes are undergoing massive face-lifts in their power capability at higher temperatures due to advances in the field of semiconductor technology [19]. Newer technologies like SiC and GaN are expected to improve the switching device efficiencies due to extremely low switching losses under higher temperatures for a higher range of power and frequencies [20] [21].

### 2-5 Topological evaluation

The basic requisites for determining a topology, its components and its design for a specific operation are

- Input voltage range  $(V_{in})$

- Output voltage (Vout)

- Output load current  $(I_{out})$

- Output power  $(P_{out})$

To evaluate topologies, it is very important to classify the requisite performance parameters for design. Loss mechanisms depend upon the type of semiconductor device used. Hence, development of an analytical model for comparative analysis which involves different power converters is riddled with complexity considering the parameters involved [22]. Some metrics for comparison can become significant

- Robustness

- Power density

- Efficiency

- Construction related aspects and complexity

- $\bullet \ {\rm Cost}$

Significant single switch topologies that can carry out step-up/step-down of input voltage are buck-boost, SEPIC and Cuk. They are as follows

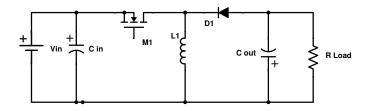

- Output voltage of a single switch buck-boost converter is the opposite polarity with respect to the input and the operating switch needs a high side driver as one of its terminals are not grounded as shown in figure 2-1.

- A Cuk converter has high number of reactive components, high current stresses on the switch, diode and the transfer capacitor  $C_t$  [23] as shown in figure 2-2.

- In a SEPIC converter, a maximum switch voltage is equal to the input voltage plus the output voltage. Thus voltage stresses in the switches in this types of converter are very high. Figure 2-3 shows a SEPIC converter topology.

Figure 2-1: Buck Boost Converter

Figure 2-2: Cuk Converter

Figure 2-3: SEPIC Converter

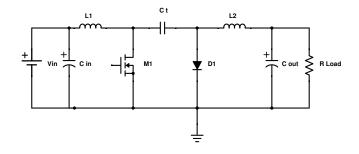

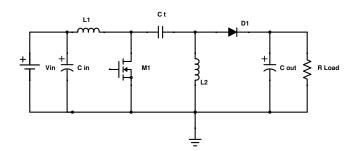

There are several disadvantages associated with a single switch buck-boost converter as discussed in the above section necessitating the study of topologies with cascaded buck-boost converters with two switches. The topologies on offer for evaluation by ESA for the thesis as summarised in [1] include

- 1. Non-Inverted buck cascaded by a boost converter figure 2-5

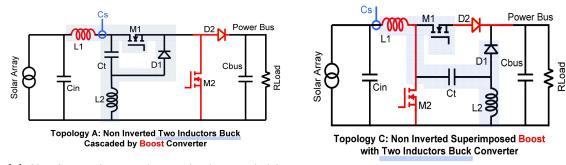

- 2. Non-Inverted two inductors buck cascaded by boost converter figure 2-4a

- 3. Non-Inverted superimposed boost with two inductors buck converter figure 2-4b

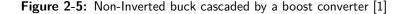

- 4. Non-Inverted superimposed two inductors boost with a buck converter figure 2-6a

- 5. Non-Inverted buck cascaded by two inductors boost converter figure 2-6b

(a) Non-Inverted two inductors buck cascaded by boost converter

**(b)** Non-Inverted superimposed boost with two inductor buck converter

Figure 2-4: Two inductors buck converter topologies [1]

All the topologies are two-switch converters and function as a step-up or step-down depending upon the input/output operating conditions of voltage [24]. Some new topologies have a better switch stress profile as compared to single switch topologies such as buck-boost, SEPIC and Cuk. These new topologies are cascaded, interleaved or superimposed. One way to evaluate topologies is by bringing into focus the active device ratings, their RMS/peak/average current and voltage stress [25].

In the conventional boost and buck converters, output power will contain two components. First component is the indirect power  $P_{indirect}$ , processed by switches by using the inductor for intermediate energy storage. Second component is the direct power,  $P_{direct}$ , which

Topology B: Non Inverted Buck Cascaded by Boost Converter

(a) Non-Inverted superimposed two inductors boost with a buck converter

(b) Non-Inverted buck cascaded by two inductors boost converter

Figure 2-6: Two inductors boost converter topologies [1]

flows directly to the output terminal by foregoing the intermediate process. In single-switch topologies (i.e. the single switch buck-boost, SEPIC and Cuk)

$$P_{direct} = 0 \tag{2-1}$$

This capability of providing direct energy path indicates lower stresses in the components, lower energy storage and as a result much better efficiency. To determine the most efficient topology is one of the objectives of this thesis as mentioned in chapter 1.

### 2-6 Modes of operation

Operation modes in power converters which are widely used are continuous conduction mode (CCM) and boundary conduction mode (BCM).

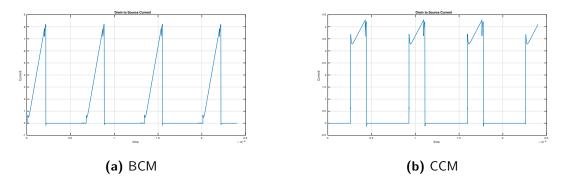

CCM and BCM are referred to depending upon the current flow through the inductance of the converter. BCM is the boundary of continuous conduction mode and discontinuous conduction mode [26] [27]. The nature of inductor current in case of CCM is continuous i.e. it never falls to a zero value as shown in figure 2-7a in case of boost operation. However, in case of BCM, a new switching period will be initiated when the value of inductor current dips to zero as shown in figure 2-7b in case of boost operation.

Evidently, BCM will have a higher inductor RMS current value depending upon the voltage parameters and the same higher values can be expected through MOSFETs and diodes. However, it helps in better switching conditions. This is because the reverse recovery in diodes is eliminated and the MOSFET is turned on with zero current effectively reducing the switching on loss [28]. Summarising BCM vis-a-vis CCM, it has following benefits

Master of Science Thesis

(a) Boost Converter in Continuous Conduction Mode

(b) Boost Converter in Boundary Conduction Mode

Figure 2-7: CCM and BCM

- Self-protection capability as the inductor current reaches a zero value every cycle

- Reduced turn-on losses

Discontinuous conduction mode is not discussed in the latter parts of the report as it was discarded due to its several disadvantages as mentioned below

- Ripple in the output capacitor is higher than the other two modes.

- At lower load condition, it has very low efficiency.

### 2-7 Efficiency calculations

Higher switching frequencies in an SMPS helps in reducing harmonics associated with the converters associated. However, this will cause significant switching power losses and efficiency degradation during the power conversion [29]. The fact that high switching frequencies can effect low conduction and magnetic core related losses is surveyed in [30]. The core losses of magnetic components are independent of the load current. Lower switching frequencies can have the opposite effects. Total losses in a system can be given by

$$P_{total} = P_{active} + P_{passive} \tag{2-2}$$

$$P_{active} = P_{MOSFET} + P_{diode} \tag{2-3}$$

$P_{passive} = P_{inductor} + P_{capacitor} \tag{2-4}$

$$P_{inductor} = P_{windings} + P_{core} \tag{2-5}$$

Anil Kumar Ananda

Master of Science Thesis

In case of CCM, higher switching frequencies can result in high core losses in inductor core and switching losses in MOSFETs.

In case of BCM, the frequency is dependent upon the difference between the input and output voltages. The frequency of operation is directly proportional to the difference between the input and output voltages.

The stresses in the active devices such as MOSFETs and Schottky diodes yield greater influence on topology metrics like cost, performance and efficiency [31]. The conduction losses in topologies that use MOSFETs as active switching devices rely on the voltage levels that are considered in the initial design specifications. This effect is important as the increase of overall losses impacts the design due to the fact that high volume heat sinks will become necessary to drain the heat. This effect has consequences on the size and volume of the converter [32].

### 2-8 Conclusion

This part of the report provided an insight into the state of the art on prevalent battery charging issues and discussed a few concepts on converter design that provide a basis to build on for evaluation of the topologies. Summarising chapter 2, following conclusions can be drawn,

- PV generation is evolving steadily to become one of the major sources of energy. For PV technology to power households without intermittent behaviour, batteries play a major role in the integration of PV technologies.

- Ni-Fe battery technology is undergoing advancements and will play a pivotal role in blending PV technology. Potentially it can be used for PV applications due to its safety standards, its robustness and inexpensive capital expenditures.

- Battery charge control is a must for any battery technology to ensure that highest SoC is maintained and overcharge or over discharge is prevented.

- To evaluate a topology, an analytical model of its performance under ideal conditions can work as a precursor to determining its suitability for an application. The capability of a topology in providing direct energy path is preferred for higher efficiency and low switch stresses.

- Efficiency calculations under different operation modes for power converters will depend on power parameters, operating frequency and application requirements.

## Chapter 3

## **Topologies**

In chapter 2, we focused on the current state of the art for building power converters for battery charging application and criterion for selection of topologies. Chapter 3 tries to establish basics of how topologies can be evaluated individually and then compared on the basis of modes of conduction.

### **3-1** $B^2R$ **DC-DC** converter topologies

Single-switch step-up/step-down converters (i.e. buck-boost, SEPIC and Cuk) have higher current stresses on active devices as compared to the conventional buck or boost converter. A buck-boost converter with a couple of independently controlled switches for buck and boost operation can help achieve lower stresses.

The patent 550 [1] showcases a new class of converters achieve buck-boost operation by utilising the cascade, interleaved and superimposed connections of buck and boost converters. There are 5 topologies to be checked for efficiency for the above parameters.

- Topology B Reference topology Non-Inverted buck cascaded by a boost converter

- Topology A Non-Inverted two inductors buck cascaded by boost converter

- Topology C Non-Inverted superimposed boost with two inductor buck converter

- Topology D Non-Inverted superimposed two inductors boost with a buck converter

- Topology E Non-Inverted buck cascaded by two inductors boost converter

To design a converter for a specific application effectively, it is very important to obtain the power parameters. The design of the converter will be carried out for parameters as shown in table 3-1. In each case, we determine conduction and switching losses for a varying input voltage of 30V to 45V.

| Maximum Output Power   | $P_{o,max}$  | 106.4W |

|------------------------|--------------|--------|

| Minimum output power   | $P_{o,min}$  | 21.28W |

| Fast charging current  | $I_{o,fc}$   | 2.66A  |

| Minimum input voltage  | $V_{in,min}$ | 30V    |

| Maximum input voltage  | $V_{in,max}$ | 45V    |

| Nominal output voltage | $V_o$        | 40V    |

| Switching frequency    | $f_{sw}$     | 150kHz |

Table 3-1: Power parameters

- 1. Boost mode, when the input voltage is between 30V and 39V.

- 2. Direct Energy Transfer (DET), when input voltage is equal to 40V.

- 3. Buck mode, when the input voltage is between 41V and 45V.

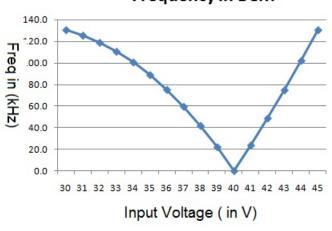

N.B. The switching frequency is fixed at 150 kHz for CCM only. The switching frequency varies with the variation in input voltage in case of BCM. This change will be discussed in the subsequent sections in this chapter.

### 3-2 Topologies overview

A buck-boost converter with two independently controlled switches can work as a boost or as a buck converter depending upon input-output conditions and thus achieves lower stresses on components.

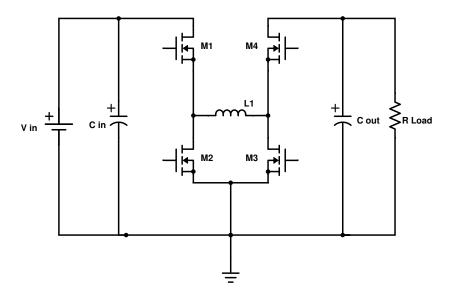

#### 3-2-1 Topology B

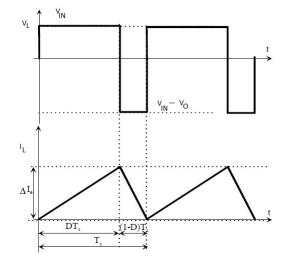

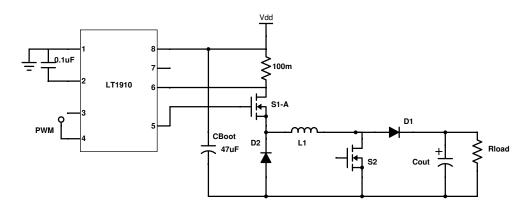

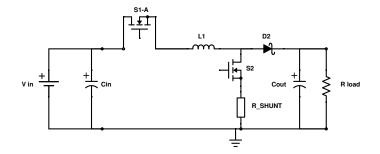

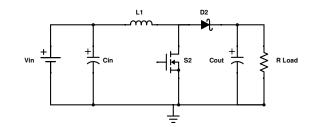

Figure 3-1: Topology B

Topology B is a Non-Inverted buck cascaded by a boost converter as shown in figure 3-1. This is practically the simplest power converter among the five topologies as it eliminates the need of an extra inductor and a capacitor with reverse current capability. The selection of components becomes straightforward in comparison to the other four topologies. This topology has the capability for implementing a direct energy path and it has a widely adjustable output voltage.

(In figure 3-1, we observe two switches S1-A and S1-B in place of a single switch S1. The

Anil Kumar Ananda

Master of Science Thesis

necessity for such a circuit is explained in the section 3-3.)

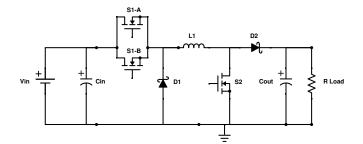

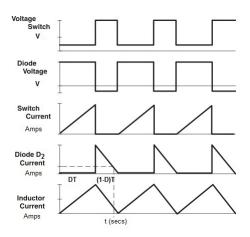

Figure 3-2: Current and Voltage waveforms in Topology B in Boost mode

Figure 3-3: Current and Voltage waveforms in Topology B in Buck mode

During boost operation, the control should enable the S1-A switch to be always on and S2 is switched for stepping up the voltage. Contrarily, during buck operation, S1-A and S2 are turned off and S1-B is switched. This control scheme enables minimum indirect power characteristic reducing the switch stresses.

The waveforms of currents through devices during buck operation is given in 3-3 and boost is given in 3-2. This topology displays increased conduction losses at the input as a result of MOSFET S1-A during the boost operation and diode conduction losses at D2 during the buck operation. Therefore, other two-switch buck-boost converter topologies are also considered (topology A, C, D, and E) and compared for their performances in metrics of component conduction losses and stresses.

#### 3-2-2 Topology A and C

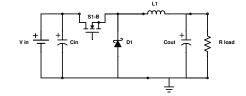

(b) Topology C

Figure 3-4: Two inductors buck based converter topologies

Topology A utilises a two inductor buck cascaded by a conventional boost converter topology for achieving the buck-boost conversion as shown in figure 3-4a. On the other hand, topology C utilises a two inductor buck superimposed by a conventional boost converter topology for achieving the buck-boost conversion as shown in figure 3-4b. Topology A and C operate as follows

- In boost mode, MOSFET S1-A is always switched on and S2 is switched with a PWM.

- In buck mode, MOSFETs S1-A and S2 are switched off and S1-B is switched with a PWM.

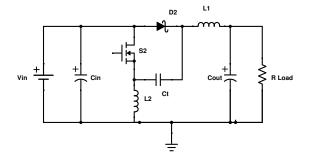

## 3-2-3 Topology D and E

Topology D contains a two inductor boost super-imposed with a conventional buck converter topology as shown in figure 3-5a. Topology E contains a conventional buck cascaded with a two inductor boost converter topology as shown in figure 3-5b. Topology D and E operate as follows

• In boost mode, MOSFET S1-A is always switched on and S2 is switched with a PWM.

Anil Kumar Ananda

Figure 3-5: Two Inductor Boost Based Converter Topologies

• In buck mode, MOSFETs S1-A and S2 are switched off and S1-B is switched with a PWM.

These topologies can be utilised in situations where a continuous current should be maintained to the load in situations when the output capacitors fail. Inductor  $L_1$  will ensure the current to the output remains continuous.

# 3-3 Necessity of switches S1-A and S1-B

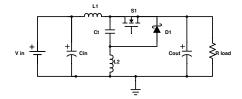

All topologies that are under discussion carry out the buck and boost operations through different switching duty cycles. Let us assume a possibility in which topology B is under operation.

There are two operations the MOSFET S1 is intended to do.

- Operate in 'overdrive' mode where the MOSFET will be conducting continuously in the boost mode when the input voltage is less than the output voltage as shown in figure 3-6a.

- Operate as a switch for a PWM to carry out buck operation when the input voltage is greater than the output voltage as shown in figure 3-6b.

To achieve these two operations, separate drivers need to be used. Connecting a single switch to two drivers is not advisable as the gate to source terminals connected to a high side driver will be shorted when it is not supplying a signal to the MOSFET for operation. Hence, a two switch solution is utilised where the high-side driver IR-2117 is used the MOSFET S1-B is operated in buck mode and PWM are to be supplied for its operation.

When the input voltage is lesser than the output and the operation is boost, the driver LT-1910 is used in driving S1-A in *'overdrive'* mode in which a continuous gate to source voltage is supplied to the MOSFET.

(a) Topology B Boost Mode

(b) Topology B Buck Mode

Figure 3-6: Necessity of S1-A and S1-B

# 3-4 Selecting the topology for design

#### Size

The converter designed will be used in the Battery Management System (BMS) that will be used along with the batteries. Since the system will be in operation in a domestic household or a storage room, it is safe to assume that size of the converter to be employed in the system does not have a restriction. Although the size of active devices used is negligible, the major size considerations will be the volume of the passive devices like capacitors and inductors. The effort is made to ensure that the use of a heat sink is avoided by means of effective natural convection.

To make a comparison of the size of the converters of each topology we consider the following parameters

- Energy storage in the passive components which is proportional to their size. The maximum stored energy for an inductor during a cycle is given by  $\frac{1}{2}LI_{L,Peak}^2$  and energy stored in the capacitor is given by  $\frac{1}{2}CV_{C,Peak}^2$ .

- Size of individual components sometimes it becomes necessary to provide thermal protection and spacing to passive components (with fans) and active components (with heat sinks) which might increase the size of the system [33].

Ni-Fe batteries are characterised by the low energy density and large physical dimensions; the overall size of the converter does not become paramount for selection [27].

#### **Overall efficiency**

In the process of evaluating topologies for selection, efficiency becomes an important parameter. A decrease in losses enables design with no necessity to use additional cooling methods. The overall efficiency of the system is one of the measures of selecting a suitable topology [34]. By increasing the efficiency, the best utilization of PV generation can be realized.

#### Complexity

The topology selected should be less complex to ensure that it is inexpensive and easier for construction. The complexity can be realised by the number and type of components [35].

# 3-5 Comparison of the topologies

## 3-5-1 Efficiency

The most important selection criterion for the topology in our case is the efficiency of the converter. Although it is possible to achieve high efficiency at the expense of costlier materials and technologies for components, efficiency and cost have to be optimised to ensure that trade-off among the two does not disrupt the design.

Of the power losses in a converter, special attention is given to the switching devices with regards to their switching and conduction losses. Package details for the diodes and switches also play an important role in terms of heat sinking capabilities and their losses due to thermal quantities [36].

Overall efficiency due to magnetics with the ferrite core and winding losses depend upon the switching frequency, the size and the geometry of the component. The output capacitance and input capacitance by employing a proper design are less significant as compared to active devices w.r.t. efficiency. The introduction of transfer capacitance  $C_t$  in the two inductor topologies can reduce the efficiency. A detailed analysis of efficiency will be carried out in the subsequent chapters of this thesis and will dominate the latter part of the analysis for selection of the topologies.

## 3-5-2 Complexity

Among all the topologies, topology B requires the least number of components. The topologies A, C, D and E involve two inductors and a transfer capacitor. The voltage ratings of input and output capacitors are not very high (50V); However, the current rating of  $C_t$ , transfer capacitor is very high. The analytical model for calculating currents, losses and designing the magnetics, as a result, is not straightforward either. Also, the extra magnetic component in the form of an inductor for a converter means that the optimum design will have to be carried out for the specific topology separately.

The number of inductors and capacitors is given by the table 3-2.

Table 3-2:

Number of passive components

|            | Inductors | Capacitors |

|------------|-----------|------------|

| Topology A | 2         | 3          |

| Topology B | 1         | 2          |

| Topology C | 2         | 3          |

| Topology D | 2         | 3          |

| Topology E | 2         | 3          |

# 3-6 Modes of operation

It is always an interesting prospect to decide on the mode of conduction in Non-Isolated topologies. In CCM (continuous conduction mode), the current through the inductor never

hits zero. On the contrary, in BCM (boundary condition mode), the switching time starts when the current through the inductor returns to zero. Both the modes have their own influence on switching losses and conduction losses. Also, the design of the circuit and the solutions to component selection change as well. Firstly, the three modes of power converters are

- 1. Continuous Conduction Mode

- 2. Boundary Conduction Mode

- 3. Discontinuous Conduction Mode

## Continuous Conduction Mode - CCM

In CCM, the current through the inductor has a non-zero positive value all the time. It has 2 components - ripple and DC. The DC value is quite often specified by the average value of the current through the inductor and ripple is defined in terms of peak to peak value which will be triangular. In this mode, the value of inductance will determine the ripple value in the inductor. The frequency of switching will be fixed for an application which utilises CCM.

## Boundary Conduction Mode - BCM

In BCM, the switching time starts when the current through the inductor returns to zero. Hence, the current waveshape is a triangular signal and it does not have a DC offset. In this mode, the inductance required will be limited and a variable frequency operation is adopted.

## Discontinuous Conduction Mode - DCM

In DCM, the current through the inductor always returns to zero before closing the switch. The converter characteristics will change when it enters DCM and it has several disadvantages

- Ripple in the output capacitor is higher than the other modes restricting its application.

- Lower efficiency at lower load condition as compared to other modes.

## 3-6-1 When can BCM become advantageous over CCM?

BCM mode has a higher value of RMS current in the inductor and active devices (diode and MOSFET) in conditions when the difference between input and output voltages is very high. But, it enables significantly better switching condition of the active devices. This is because reverse recovery of the devices are eliminated and a fast-recovery would not be quintessential. The switch (MOSFET) will be turned on when there will be zero current through the device reducing the switching on loss.

Upon switching on the MOSFET, the peak inductor current  $(I_{L,peak})$  and input Voltage  $(V_{in})$  are directly proportional. The current waveform is a triangular one with no DC offset implying

Figure 3-7: Diff. in BCM and CCM Modes (Not to scale)

that value of  $V_{avg}$  in one whole period is dependent upon the value of the input voltage and directly proportional.

For a particular power level, even though the peak inductor current  $(I_{L,peak})$  is higher for a BCM based topology, the power loss due to RMS value of current in the windings is less when the difference between input and output voltages is less (as frequency decreases) and the value of inductance required in the circuit will become much smaller. These advantages will be discussed in the coming sections.

#### 3-6-2 Condition for BCM

To assess if the converter is in BCM, CCM or DCM, the following procedure is employed. We define the current ripple ratio r as

$$r = \frac{\Delta I}{I_{dc}} \tag{3-1}$$

Where,

$I_{DC}$  = average value of current

$\Delta I =$  ripple current value - peak to peak

In case the value of 'r' is less than 2, CCM exists.

In case the value of 'r' is exactly 2, BCM exists.

Otherwise, the system enters DCM.

The currents through the devices in each mode is derived in the appendix-A and the inductor currents are described in Figure 3-7.

#### **3-6-3** Frequency effects

In case of BCM, the frequency can change depending upon a particular value of input voltage and a fixed output voltage. In buck mode, the frequency varies as seen in the eq. 3-2

$$f_{buck} = \frac{V_o^2 (V_{in} - V_o)}{2P_{o,max} V_{in} L}$$

(3-2)

Master of Science Thesis

Anil Kumar Ananda

In boost mode, it varies as shown in eq. 3-3

$$f_{bst} = \frac{V_{in}^2 D}{2P_{o,max} V_{in} L} \tag{3-3}$$

For example, an inductance value of  $8.13\mu H$  would have the following operating frequencies as shown in figure 3-8 for the power parameters mentioned in table 3-1 in page 14. From

## Frequency in BCM

Figure 3-8: BCM frequencies

figure 3-8, it is evident that a smaller inductance value can be utilised for the purpose of design in case of BCM as varying frequency maintains the ripple current in the inductor. In the topologies for comparison, to optimise the design for comparison, the inductance  $L_1$  is reduced to a lower value to switch it at close to 150 kHz when the highest voltage difference is observed between input and output voltages.

#### 3-6-4 Change in magnetics

The magnetics design will have to be optimised for BCM and CCM separately. This is due to the fact that the inductor currents are different for both modes.

#### BCM

In case of BCM, the ripple value will extend from zero to the peak value and is predominant. This significantly modifies the RMS values of currents through windings and it is much desired to reduce the value of AC resistance of the windings. These losses happen due to 'Skin effect ' and ' Proximity effect ' which can be averted by using customised specifications of windings. This customisation can be the usage of Litz wires [37].

The core losses might be significantly lesser due to the fact that the frequency changes to accommodate for a change in peak current value. This is the reason for which the core material selection in terms of shape and material quality is dependent on the extreme values of operation of the converter.

#### ССМ

In case of CCM, there are two parts to the inductor current. The DC offset value is usually equated to the average value and the AC component is given by the value of peak to peak ripple. This presents us with a diverse set of equations necessary for calculations.

The winding resistances plan an important part in the losses in the inductor. The DC resistance of the winding accounts for the losses due to the average current component and the AC component ensures that the losses due to the peak to peak ripple are taken care of. In case of CCM, it is possible to utilise the normal copper windings instead of Litz due to presence of a DC component and reduced skin effect/proximity effect based losses.

# 3-7 Conclusion

- The five topologies discussed are a new class of converters that work with independent switches by utilising cascade, interleaving and superimposition of buck and boost topologies to achieve buck-boost operation.

- Switches S1-A and S1-B need to be incorporated due to issues with the high side driver for achieving operation in both buck and boost modes.

- Topology selection for a power converter application can be done by assessing size requirements, efficiency and complexity of design.

\_\_\_\_\_

# Chapter 4

# Losses and component selection

In chapter 3, a discussion was carried out for the contender topologies for the design of the charger for Battery Management System (BMS) of a Ni-Fe battery. The necessary drivers for selection and their performance under different modes of conduction were examined. Efficiency becomes the focal point of selection for which a thorough analysis of losses and its impact on the performance of the topologies for the application has to be carried out. It is the norm to use switched mode power designs as compared to linear power design due to the fact that efficiency is a significant parameter. When a designer is challenged to decrease the power losses of a switched power supply, it is vital to understand the specifics of power dissipation and component selection as key parameters. In this chapter, an effort is made to understand, elucidate and develop analytical models for analysing losses. Component selection will be determined by losses and rating levels of components will depend upon the electrical parameters which the individual devices have to be designed.

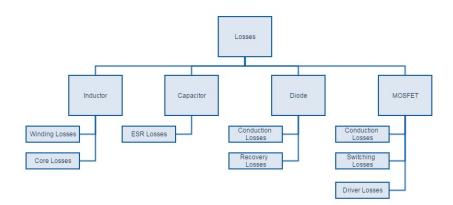

# 4-1 Losses overview

In case of inductors, the current through an inductor in CCM can be divided into average current and the ripple current. The purpose of such segregation can be justified due to the nature of winding losses. In case of resistances offered by inductors, due to skin effect, proximity and eddy current losses, an AC component of resistance can be assumed for the ripple in the inductor current. The DC resistance of the winding is first calculated and the AC resistance is calculated by virtue of the Dowell's curve [38].

In case the inductor runs in BCM mode, the total AC resistance is only taken into account to calculate winding losses as the waveform for current is a triangular wave with no DC offset. In case of core losses in the inductor, we observe the factor of frequency coming into play for the core material. The core material selected for the purpose is a ferroxcube 3C95 material and the losses are explained in the coming sections.

Losses in a capacitor are calculated by estimating the ESR value of the capacitor. In case of topology B, the capacitance  $C_t$  is absent. In all other topologies, it is significant as it carries a

Figure 4-1: Losses Overview

ripple current through it, indicative of the fact that a low ESR capacitor with reverse current handling capability becomes necessary. ESR also depends upon the frequency at which the ripples are passed through them which needs to be accounted for as well.

Losses in semiconductor elements in the topology can be divided into conduction and switching losses.

- <u>Switching losses</u> When a MOSFET or diode transitions from blocking to the conducting state and the other way around, there exists significant voltage and current between its terminals. The energy built up between transitions and later, if dissipated is calculated at each such existence.

- <u>Conduction losses</u> When the device is working in full conduction at rated values of current and voltage, these losses occur in a proportionality to that of the duty cycle.

To calculate the conduction losses in most of the devices,  $R_{device}$  can be DC resistance in case of an inductor, ESR in case of capacitor and  $R_{ds,on}$  in case of a MOSFET. However, there is an exception!

In case of a Schottky diode, there is a necessity to obtain the average and RMS value to account for non-linearity of its forward resistance characteristics.

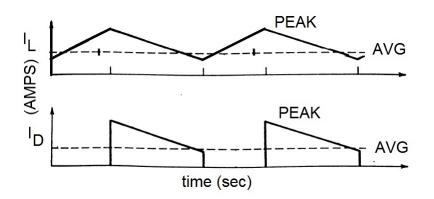

Since most device currents are either triangular/sawtooth (BCM) or triangular/sawtooth with an offset (CCM) as shown in figure 4-2, the following formula will be applied to find the RMS values of current. In case of a triangular signal

$$I_{rms} = \frac{I_{peak}}{\sqrt{3}} \tag{4-1}$$

In case of a DC offset-ed triangular signal

$$I_{rms} = I_{avg} \sqrt{1 + \frac{1}{3} \left(\frac{\Delta I_{peak}}{2I_{avg}}\right)^2} \tag{4-2}$$

In case of pulsating signal with linear ripple is given by.

$$I_{rms} = I_{avg}\sqrt{D}\sqrt{1 + \frac{1}{3}\left(\frac{\Delta I_{peak}}{2I_{avg}}\right)^2}$$

(4-3)

Anil Kumar Ananda

Figure 4-2: Current Wave-shapes

#### 4-1-1 Ripple current and its effect on the device selection

In case of inductor selection and design, ripple currents play a vital role. Ripple and inductance are inversely proportional.

In case of boost operation,

$$\Delta I_{L,pk-pk} = \frac{V_{in}D_{boost}}{L} \tag{4-4}$$

In case of buck operation,

$$\Delta I_{L,pk-pk} = \frac{(V_{in} - V_o)D_{buck}}{L} \tag{4-5}$$

In both circumstances, it can be observed that for a fixed frequency, higher the inductance value, lower the ripple. There exist two modes of operation for which we calculate the currents.

In case of CCM, this value needs to be optimised to achieve necessary operating conditions of ripple.

In case of BCM, this condition is not significant, as the frequency is changed to maintain a triangular signal without a DC offset which ensures that the signal is triangular (Ripple only). However, the  $\Delta I_{L,pk-pk}$  is equal to  $I_{L,peak}$  value in case of BCM.

## 4-2 Capacitor losses

Capacitor losses are assessed as they are crucial for their capability to regulate the voltage at the output, supply for the inductor ripple at the input and transfer of energy between the two inductors(in case of two inductor topologies).

Capacitors with high losses can lead to high leakage current during the operation resulting in an unwarranted temperature increase in them. Internal heat dissipation can aid evaporation of the electrolyte that will harm the quality of the capacitor.

From the datasheets, ESR (Equivalent Series Resistance) value has to be derived for a specific frequency of operation. The discernible power loss, when divided by the reactive power of the capacitor at a particular sinusoidal voltage of specified frequency, is given by

$$tan\delta = ESR(2\pi fC) \tag{4-6}$$

To find out the ESR at a particular frequency, frequency multipliers are provided in the data-sheets of electrolytic capacitors. Under most circumstances, the ESR of a capacitor is provided at 120 Hz or 100 Hz. Since we operate the switch at 150 kHz, the following conversion is used.

$$\left(\frac{I_{150kHz}}{I_{120Hz}}\right)^2 = \frac{ESR_{120Hz}}{ESR_{100kHz}} = freq.mult^2$$

(4-7)

The most important parameter in a data-sheet for a capacitor is the ripple current rating. The currents in the input, output and transfer capacitance in each mode is as follows,

#### Buck

$$I_{Cin,rms} = \sqrt{I_{sw,rms}^2 - I_{sw,avg}^2} \tag{4-8}$$

$$I_{Cout,rms} = \sqrt{I_{L,rms}^2 - I_{L,avg}^2}$$

$$\tag{4-9}$$

In case of Topologies A and C, through the transfer capacitor  $C_t$ , the RMS value of current is given by

$$I_{Ct,rms} = \sqrt{I_{L1,rms}^2 D_{buck} - I_{L,avg}^2 \left(1 - D_{buck}\right)}$$

(4-10)

#### Boost

$$I_{Cin,rms} = \sqrt{I_{L,rms}^2 - I_{L,avg}^2}$$

(4-11)

$$I_{Cout,rms} = \sqrt{I_{D,rms}^2 - I_{D,avg}^2} \tag{4-12}$$

In case of Topologies D and E

$$I_{Ct,rms} = \sqrt{I_{L1,rms}^2 D_{boost} - I_{L,avg}^2 \left(1 - D_{boost}\right)}$$

(4-13)

The transfer capacitor  $C_t$  is usually a film type as it can have a high current capability with low ESR.

The power loss in the capacitors in every case is given by

$$P_{cap,loss} = I_{cap,rms}^2 ESR_{cap} \tag{4-14}$$

Anil Kumar Ananda

## 4-3 Diode losses

Due to dynamic resistance property of the diode, it is not straightforward to calculate the conduction and reverse recovery losses of the device. In this segment, we discuss how the calculations are done, the manner in which the assumptions play a role and the parameters that can be neglected. A thorough analysis is done to carry out the conduction loss calculation in the diode for the buck-boost converters. The assumption made in the set of formulae used is that there exists a temperature dependence on the forward voltage and current when it is conducting. The 'On' state voltage drop  $V_F$  is one of the causes for diode losses and results

Figure 4-3: Diode current waveform [2]

in power losses and junction temperature increases [2]. Estimating them accurately holds the key to design circuits. The following terms are necessary for the calculation of diode On state losses.

- $f_{sw}$  Switching frequency, in our case 150kHz for CCM

- $T_{sw}$  Switching period, the reciprocal of switching frequency

- *D* Duty Cycle

- $I_{max}$  or  $I_{peak}$  Peak current value in forward bias

- $I_{min}$  Minimum current value in forward bias

- $V_f$  Forward voltage

The procedure for calculation will be as follows

• Average and RMS currents are calculated for a specific converter type and values of  $I_{f,av}$  and  $I_{f,rms}$  are used to obtain  $V_{t0}$  and  $R_d$  at two different junction temperatures. The values of  $\alpha_{Vt0}$  and  $\alpha_{rd}$  are obtained to obtain a dynamic equation of dynamic resistance and forward voltage dependence on junction temperature.

- Diode forward characteristics modelling -At specific junction temperatures  $V_{t0}$  and  $R_d$  are obtained. Later, thermal co-efficient  $\alpha_{Vt0}$  and  $\alpha_{rd}$  are obtained for a specific diode.

- Losses are calculated

#### 4-3-1 Modelling forward characteristics

Current versus Forward voltage waveforms for temperatures  $T_{ref1} = 25^{\circ}$ C and  $T_{ref2} = 150^{\circ}$ C are obtained for  $I_{max}$  and  $I_{min}$  respectively.  $V_{t0}$  and  $R_d$  are calculated for  $T_{ref1} = 25^{\circ}$ C and  $T_{ref2} = 150^{\circ}$ C from the data-sheet using the forward voltage versus current characteristics. Later,  $\alpha_{VT0}$  and  $\alpha_{RD}$  are calculated as follows

$$\alpha_{Vt0} = \frac{V_{t0}(T_{ref2}) - V_{t0}(T_{ref1})}{T_{ref2} - T_{ref1}}$$

(4-15)

$$\alpha_{rd} = \frac{R_d(T_{ref2}) - R_d(T_{ref1})}{T_{ref2} - T_{ref1}}$$

(4-16)

N.B.  $\alpha_{Vt0}$  is always less than zero and  $\alpha_{rd}$  is greater than zero for all diodes.

These are thermal coefficients calculated from two reference temperature data.

A junction temperature  $T_j$  is considered,  $V_F(I_F, T_j)$ ,  $V_{t0}$  and  $R_d$  are obtained for the same by using the following equations

$$V_F(I_F, T_j) = V_F(I_F, T_{jref1}) + (\alpha_{Vt0} + \alpha_{rd}I_F)(T_j - T_{jref1})$$

(4-17)

$$V_{t0}(T_j) = V_{t0}(T_{jref1}) + \alpha_{Vt0}(T_j - T_{jref1})$$

(4-18)

$$R_d(T_j) = R_d(T_{jref1}) + \alpha_{rd}(T_j - T_{jref1})$$

(4-19)

The final conduction loss is given by

$$P_{Cond}(T_j) = V_{t0}(T_j)I_{F(av)} + R_d(T_j)I_{F(rms)}^2$$

(4-20)

#### 4-3-2 Modelling recovery characteristics

Junction temperature ( $T_j$ ) and reverse voltage ( $V_R$ ) are used to calculate the reverse losses. In a Schottky diode, the reverse losses occur due to the reverse bias applied to the diode and the leakage current ( $I_R$ ), as a consequence. The leakage current ( $I_R$ ) exponentially increases as the junction temperature increases.

To calculate leakage current, the following steps are followed.

'c', the thermal coefficient is used as a parameter that is necessary to find out the relationship between leakage current  $(I_R)$  and the junction temperature. It is given by

$$c = \frac{1}{T_{j,ref2} - T_{j,ref1}} log(\frac{I_R(V_R, Tj, ref2)}{I_R(V_R, Tj, ref1)})$$

(4-21)

For the device we are using,  $T_{j,ref1} = 25$  and  $T_{j,ref2} = 125$ . Now, the value of leakage current is given by

$$I_R(V_R, T_j) = I_R(V_R, T_{ref})e^{c(T_j - T_{j, ref})}$$

(4-22)

Anil Kumar Ananda

Where,  $V_R$  = Reverse voltage across the diode. Hence, Power Loss due to reverse conduction is given by

$$P_{Rev,T_j} = (1-D)V_R I_R(V_R, T_{ref})e^{c(T_j - T_{j,ref})}$$

(4-23)

## 4-4 MOSFET losses

Higher the switching frequency, higher the number of changes from On to Off state and vice versa implying that switching losses are proportional to operating frequency. They can be categorised into

- Conduction Losses

- Switching Losses

Conduction loss is the product of current and voltage in a MOSFET or a Schottky diode in the state of conduction. It depends upon the On time of the device and hence becomes dependent on the duty cycle,  $t_{on}f_{sw}$ .

Switching losses occur when there exists a switching transition in a MOSFET between ON and OFF states. Number of transitions per unit time is a good measure of the switching losses and hence they are judged to be dependent on the frequency  $f_{sw}$ .

Gate drive losses occur due to the conduction loss in the MOSFET driver output to the gatesource terminal of the high side switches during the bucking operation.

In calculation of switching losses, we can divide the section into turn on and off transitions and then calculate the  $E_{on,dissipated}$  and  $E_{off,dissipated}$  losses respectively.

In this section, an analytical model is presented for such a calculation by means of simplification of the original MOSFET model and explanation is given as to why some assumptions omit a few parameters. Ideally, a MOSFET has the following properties.

- Zero On state resistance  $R_{ds,on}$

- Blocking drain to source voltage entirely without a +ve bias from gate to source

In reality, these properties do not exist and hence to simplify the loss models, the following assumptions are made for calculating the switching losses in both BCM and CCM Modes.

- Inductor current  $I_L$  remains constant during the switching process

- The free-wheeling diode  $D_f$  is ideal, i.e. junction capacitance and forward voltage drop are negligible

- Gate driver  $V_{g,driver}$  is ideal and a step voltage whose ON-state  $V_{GS_{ON}}$  and zero otherwise.

- Parasitic inductance is negligible in the switching devices

#### 4-4-1 Models for analysis

The general model used for analysing the switching transitions and then using the data from transitions to calculate losses is as shown in figure 4-4. References [3] and [39] are used to model the MOSFET devices for losses in this section of the report. Since the condition is considered to be that of a clamped inductive load, inductance  $L_1$  maintains a nearly constant load current. The MOSFET switching times and the load inductor current remain unchanged too. Only the switching current would commutate from the MOSFET to the freewheeling diode  $D_f$  during MOSFET turn-off and vice-versa during turn-on.