## Monolithic 3D Wafer Level Integration Applied for Smart LED Wafer Level Packaging

Kolahdouz Esfahani, Zahra

10.4233/uuid:ca460c12-bf40-4f40-9240-d6c8aa5c37ca

**Publication date**

**Document Version** Final published version

Citation (APA)

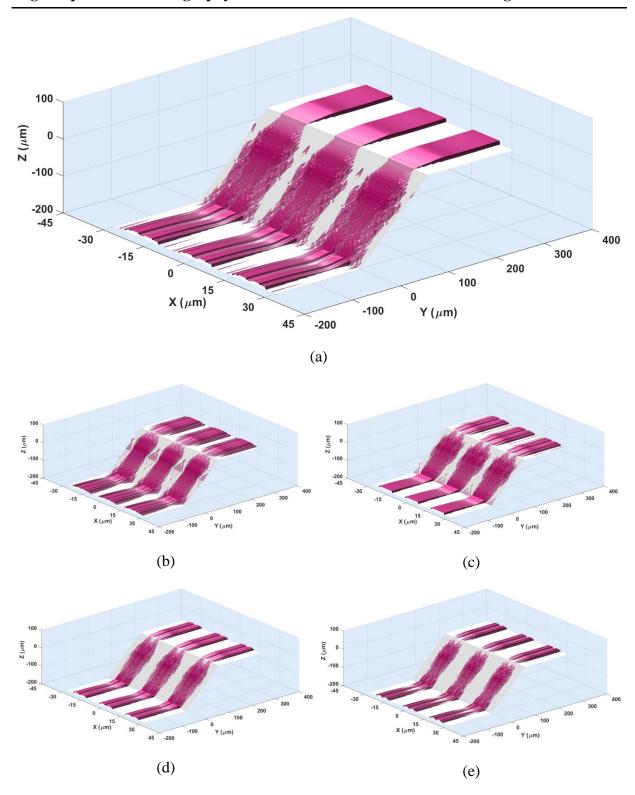

Kolahdoùz Esfahani, Z. (2017). Monolithic 3D Wafer Level Integration: Applied for Smart LED Wafer Level Packaging. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:ca460c12bf40-4f40-9240-d6c8aa5c37ca

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## Monolithic 3D Wafer Level Integration Applied for Smart LED Wafer Level Packaging

Zahra Kolahdouz Esfahani

## Monolithic 3D Wafer Level Integration Applied for Smart LED Wafer Level Packaging

## **Proefschrift**

ter verkrijging van de graad van doctor

aan de Technische Universiteit Delft,

op gezag van de Rector Magnificus prof.ir. K.C.A.M. Luyben;

voorzitter van het College voor Promoties,

in het openbaar te verdedigen op

donderdag 19 januari 2017 om 10:00 uur

door

## Zahra KOLAHDOUZ ESFAHANI

Master of Science in Electrical Engineering,

University of Tehran, Iran

geboren te Tehran, Iran

This dissertation has been approved by the

promotor: Prof. dr. G. Q. Zhang copromotor: Dr. ir. H. van Zeijl

## Composition of the doctoral committee:

Rector Magnificus, chairman

Prof. dr. G. Q. Zhang, Delft University of Technology Dr. ir. H. van Zeijl, Delft University of Technology

Independent members:

Prof. dr. P. M. Sarro,

Prof. dr. P. French,

Delft University of Technology

Prof. dr. U. Staufer,

Delft University of Technology

Delft University of Technology

Prof. dr. H. P. Urbach,

Delft University of Technology

Delft University of Technology

Tsinghua University, Beijing, China

Zahra Kolahdouz Esfahani,

Monolithic 3D Wafer Level Integration Applied for Smart LED Wafer Level Packaging, Ph.D. Thesis (with summary in Dutch),

Delft University of Technology.

Keywords: System-in-Package, 3D wafer-level integration, LED, high aspect ratio

lithography, multi-step imaging, smart silicon interposer, side-wall photodiode, blue/UV selective photodetector, sensor readout, BiCMOS process, wafer-level optic, multidisciplinary simulation, optical simulation.

Printed by: Ipskamp drukkers, The Netherlands

Front & back: Front side shows wafer-level integration of 3D silicon-based smart

interposer for LED System-in-Package (SiP), Back side shows a glowworm

as a natural lighting SiP (photo from www.deviantart.com).

Copyright © 2017 by Z. Kolahdouz Esfahani

ISBN/EAN: 978-94-028-0513-0

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

## **Table of Contents**

| Chapter 1 Introduction                                                        | 1        |

|-------------------------------------------------------------------------------|----------|

| 1.1 System in Package (SiP)                                                   | 2        |

| 1.1.1 SiP Concerns and Requirements                                           | 4        |

| 1.1.2 Heterogeneous Integration and Wafer Level Packaging                     | 5        |

| 1.2 Motivation for LED Wafer Level Packaging                                  | 6        |

| 1.3 Thesis Objectives                                                         | 7        |

| 1.4 Thesis Outline                                                            | 9        |

| 1.5 References                                                                | 12       |

| Part I: Monolithically Integrated Smart Silicon Interposer Utilized for 2D LE | D SiP15  |

| Chapter 2 Introduction to BiCMOS5/7 Process and Design Concept for S          | mart LED |

| Package                                                                       | 17       |

| 2.1 Introduction                                                              | 17       |

| 2.2 Methodology                                                               | 18       |

| 2.3 Layout of BiCMOS Test Die                                                 | 22       |

| 2.4 Design Framework Based on BICMOS 5/7                                      | 24       |

| 2.4.1 Device Modeling                                                         | 26       |

| 2.4.2 Circuit Design and Simulation                                           | 26       |

| 2.4.3 Layout Extraction and Design Check                                      | 27       |

| 2.4.4 Fabrication and Measurements                                            | 28       |

| 2.5 Smart LED Package Runs (SMACK)                                            | 29       |

| 2.6 Conclusions                                                               | 33       |

| 2.7 References                                                                | 35       |

| Chapter 3 Silicon-Based Multi-Functional Wafer-Level-Package for LEDs         | 37       |

| 3.1 Introduction                                                              | 37       |

| 3.2 Design of LED Wafer Level Package                                         | 39       |

| 3.2.1 Temperature and Light Sensors                                           | 41       |

| 3.2.2 Power Transistor                                                        | 41       |

| 3 2 3 Analog-to-Digital Converter                                             | 42       |

ii Table of Contents

| 3.3 Fabrication Process                                                  | 46          |

|--------------------------------------------------------------------------|-------------|

| 3.4 Implementation and Measurement Results                               | 48          |

| 3.5 Conclusions                                                          | 56          |

| 3.6 References                                                           | 58          |

| Chapter 4 Blue Light Evaluation for Phosphor-Based White LED WLP         | 61          |

| 4.1 Introduction                                                         | 61          |

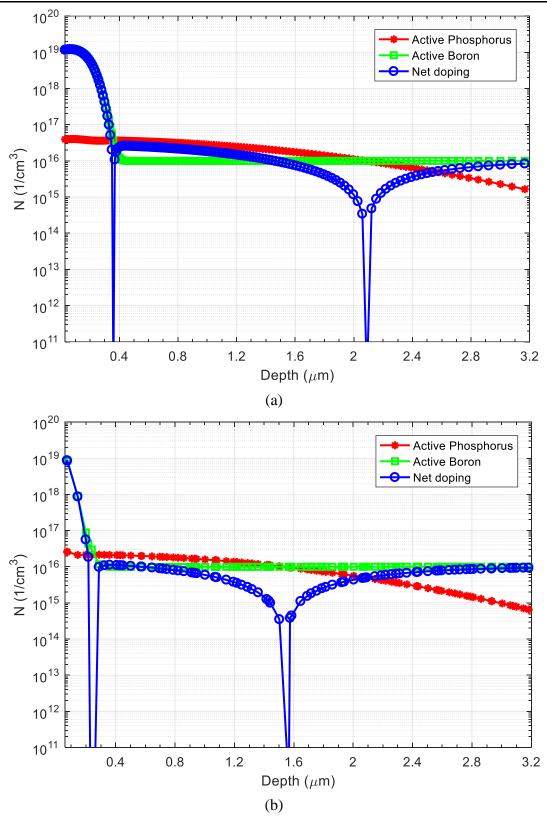

| 4.2 Photodiode Structure                                                 | 65          |

| 4.3 Simulation and Discussion                                            | 68          |

| 4.4 Device Fabrication and Characterization                              | 69          |

| 4.5 Wafer Level System Integration                                       | 72          |

| 4.6 Conclusion                                                           | 75          |

| 4.7 References                                                           | 77          |

| Chapter 5 Integration of Monolithic Light Feedback Control Circuit for B | lue/UV LED  |

| Smart Package                                                            |             |

| 5.1 Introduction                                                         | 80          |

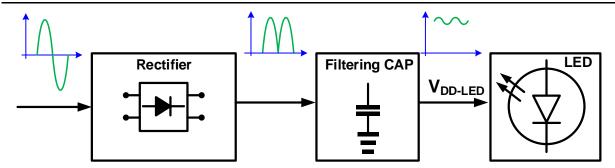

| 5.2 System-Level Design of Feedback Control Circuit                      | 80          |

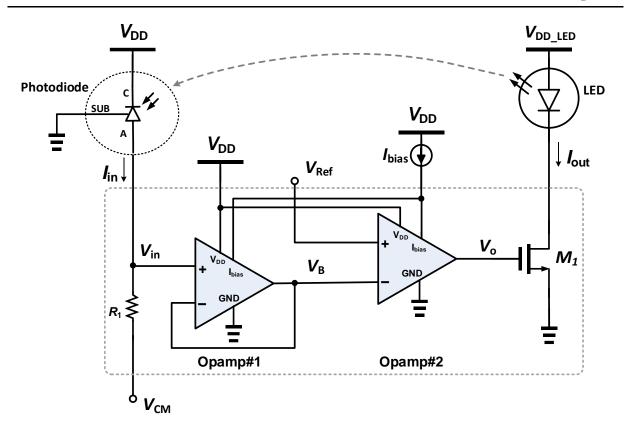

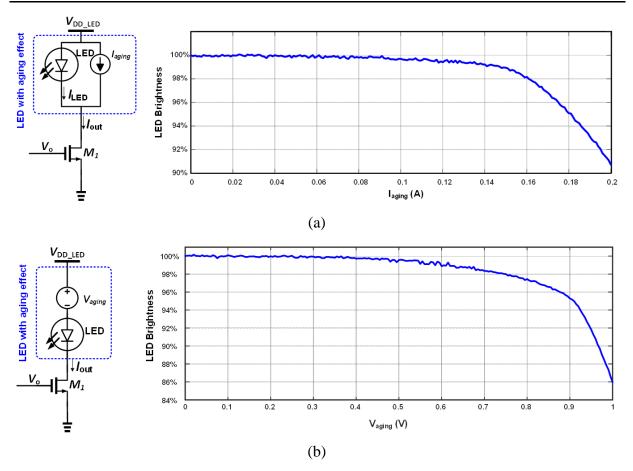

| 5.2.1 Feedback Circuit                                                   | 81          |

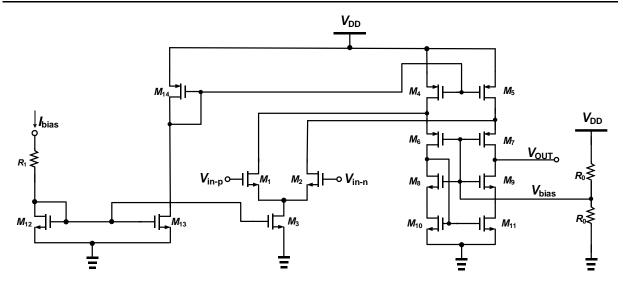

| 5.2.2 Opamp                                                              | 83          |

| 5.2.3 Power Transistor                                                   | 84          |

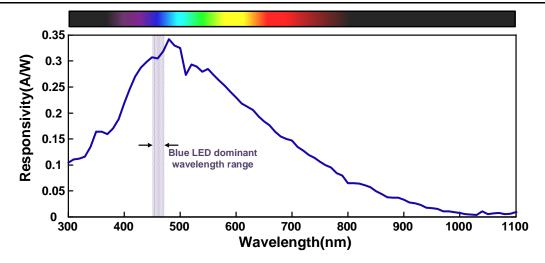

| 5.2.4 Blue-Selective Photodiode                                          | 85          |

| 5.2.5 Target LED                                                         | 85          |

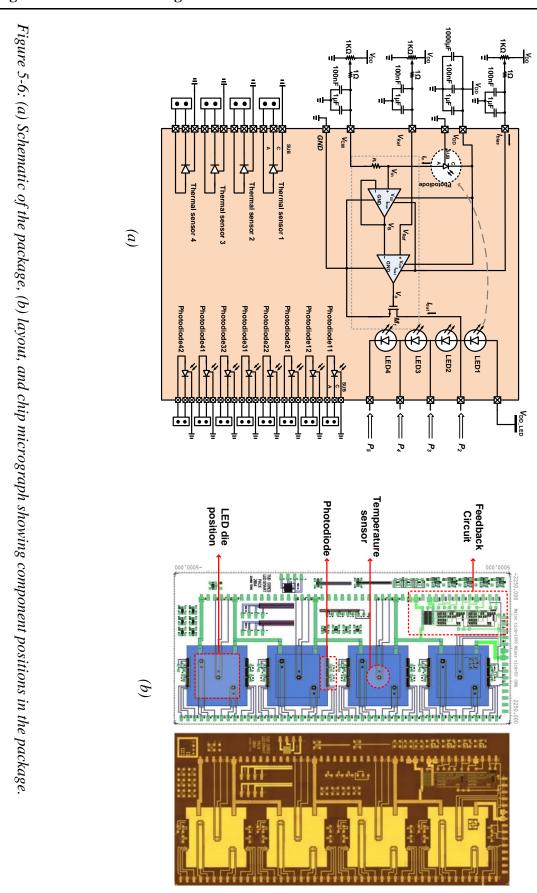

| 5.3 System Implementation                                                | 86          |

| 5.4 Measurement Results                                                  | 88          |

| 5.4.1 Opamps                                                             | 88          |

| 5.4.2 Feedback System                                                    | 90          |

| 5.4.3 Robustness against Variations                                      | 93          |

| 5.5 Conclusions                                                          | 94          |

| 5.6 References                                                           | 96          |

| Part II: 3D Wafer-Level Integration Approach Applied for LED SiP         | 99          |

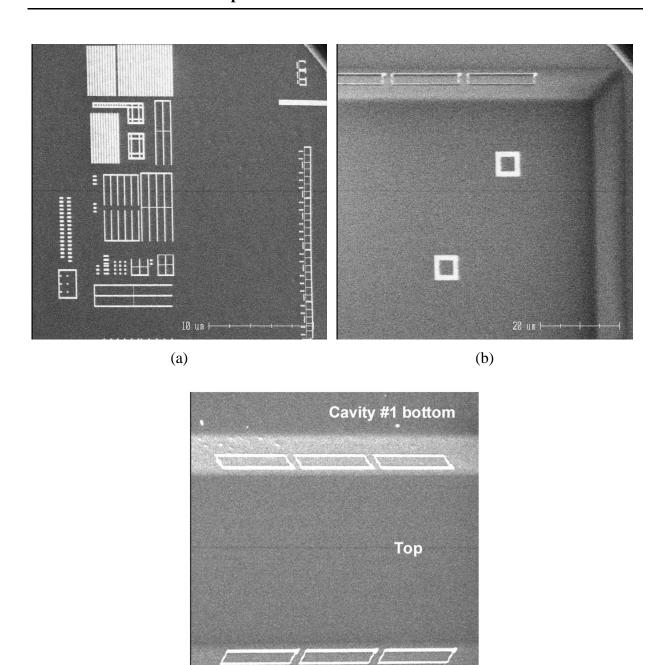

| Chapter 6 High-Aspect-Ratio Lithography for Litho-Defined Lateral Wire   | Bonding and |

| 3D Integration                                                           | Ü           |

| 6.1 Introduction                                                         | 102         |

Table of Contents iii

| 6.2 Outlook to Litho-Defined Lateral Interconnect for SiP     | 107 |

|---------------------------------------------------------------|-----|

| 6.3 Methodology                                               | 109 |

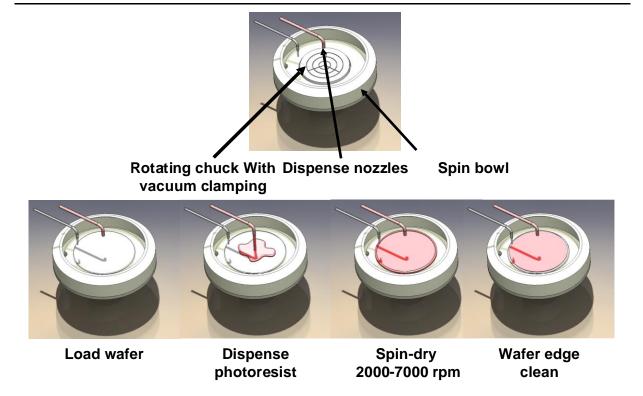

| 6.4 Resist Coating and Developing over High Topography        | 112 |

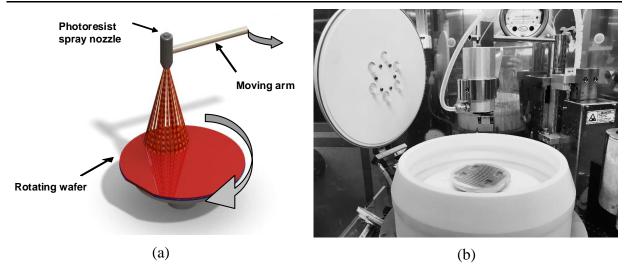

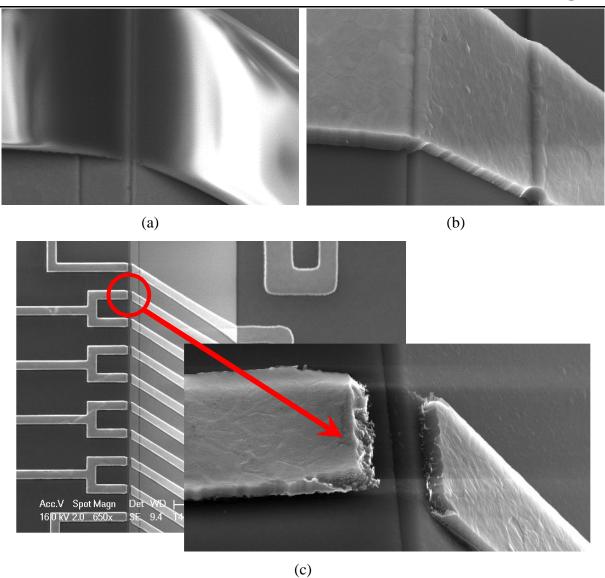

| 6.4.1 Resist Coating                                          | 112 |

| 6.4.2 Resist Development                                      | 114 |

| 6.5 Exposure over High Topography: Contact/Proximity Approach | 114 |

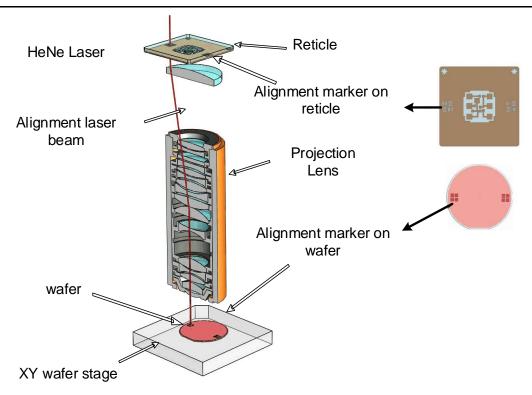

| 6.6 Exposure over High Topography: Projection Approach        | 116 |

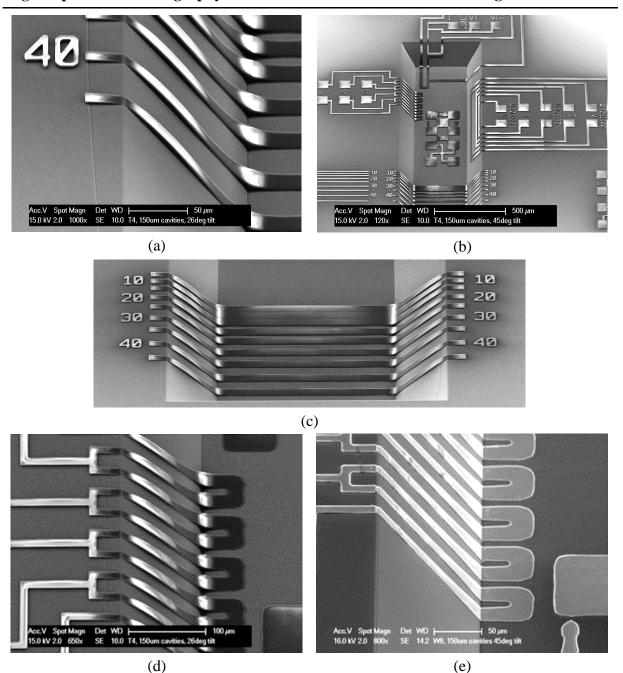

| 6.6.1 MSI with Single Mask                                    | 119 |

| 6.6.2 MSI with Split Masking                                  | 128 |

| 6.7 Conclusions                                               | 131 |

| 6.8 References                                                | 134 |

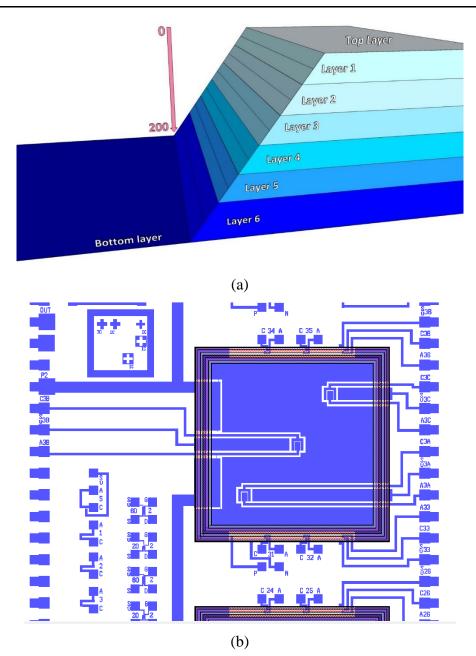

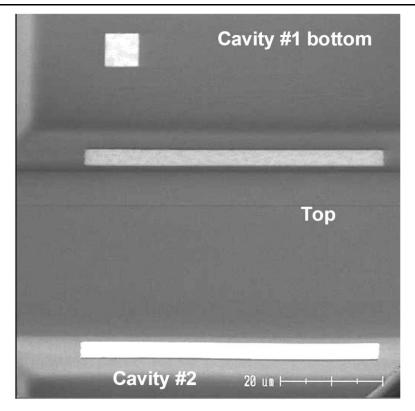

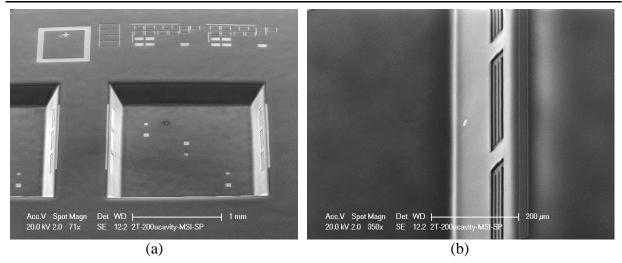

| Chapter 7 3D Silicon-Based Smart Interposer                   | 139 |

| 7.1 Introduction                                              | 139 |

| 7.2 Design of 3D Smart LED WLP                                | 142 |

| 7.2.1 Bottom Temperature Sensor                               | 143 |

| 7.2.2 Sidewall Light Sensor                                   | 144 |

| 7.2.3 Control Circuits                                        | 144 |

| 7.3 Fabrication Process                                       | 145 |

| 7.3.1 Lithography                                             | 145 |

| 7.3.2 Implantation                                            | 147 |

| 7.3.3 Process Details                                         | 149 |

| 7.4 Implementation and Measurement Results                    | 156 |

| 7.4.1 Bottom Temperature Sensor                               | 156 |

| 7.4.2 Sidewall Photodiode                                     | 159 |

| 7.4.3 Planar Devices                                          | 160 |

| 7.5 Conclusions                                               | 161 |

| 7.6 References                                                | 162 |

| Chapter 8 Conclusion                                          | 163 |

| 8.1 The Thesis Outcome                                        | 163 |

| 8.2 Suggestions for Future Developments                       | 166 |

| Summary                                                       | 169 |

| Samenvatting                                                  | 173 |

iv Table of Contents

| List of Publications                | 177 |

|-------------------------------------|-----|

| Journal Papers                      | 177 |

| Conference Papers and Presentations | 178 |

| Patents                             |     |

| List of Figures                     | 179 |

| List of Tables                      | 187 |

| Acknowledgement                     | 189 |

| About the Author                    | 193 |

## Introduction

Have you ever noticed the wonderful world of insects? There are well over 1 million different known species of insects in the world, and some experts estimate that there might be as many as 10 million. Different species with different ecosystems, body structures, and ways of life.

Let's consider insects as different kinds of systems packaged in various bodies. Systems which can be divided into widespread categories considering the functionality, existing environments, body structures, etc. Insects have segmented bodies supported by exoskeletons, the hard outer covering made mostly of chitin. The segments of the body are organized into three **distinctive but interconnected units**, or tagmata: a head, a thorax, and an abdomen. The head supports a pair of sensory antennae, a pair of compound eyes, and, if existing, one to three simple eyes (or ocelli) and three sets of variously modified appendages that form the mouthparts. The thorax has six segmented legs – one pair each for the prothorax, mesothorax and the metathorax segments making up the thorax – and, none, two or four wings. The abdomen comprises eleven segments, however in a few species of insects, these segments may be fused together or shrunk. The abdomen also contains most of the digestive, respiratory, excretory and reproductive internal structures. Significant deviation and many adaptations have happened in the body parts of insects, especially wings, legs, antenna, and mouthparts [1].

Going to electronics area, there is a similar world of systems in packages. According to International Technology Roadmap for Semiconductors (ITRS) [2], **System in Package (SiP)** is a combination of multiple active electronic components of different functionalities, assembled in a single unit that provides multiple functions associated with a system or a sub-system. A SiP

may optionally contain passives, MEMS, optical components, and other packages and devices; again, **distinctive but interconnected units.**

Package in place of body of system should provide four major functions: powering, signal distribution, mechanical protection and thermal management. Package as an outer shell, like what a chitin out covering does for an insect, is the interface of a system to outer domain holding the input and output paths. Different functionalities and operation environments lead to different kinds of packaging material and technologies.

## 1.1 System in Package (SiP)

System integration can be done at different levels. One is combining various functionalities in an IC, which is called System-on-Chip (SoC). An alternative is integrating different dies in a single package, entitled System-in-Package (SiP). In contrast to connecting different functional ICs and components on a board, the new integration methods offer higher efficiency and lower costs. System integrators are the major players for further innovation in electronic industry [3].

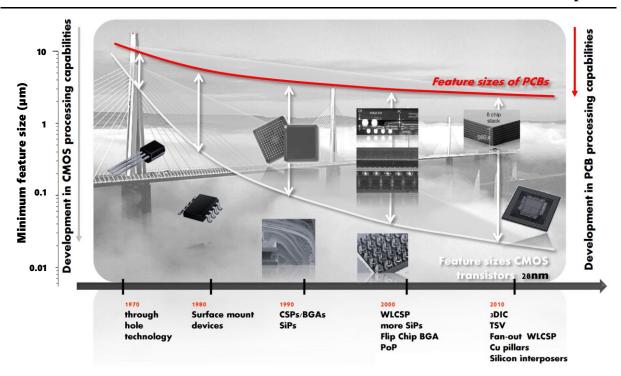

By rather fast development in consumer electronics industry, the SiP technology is receiving more attentions and efforts. It is known as one of the key technology to improve functionality density, in parallel to lowering the cost per function. That encourages the effective use of three dimensions rather than two in packaging and interconnect trends [4].

The main general drives for 3D integrations are [5], [6]:

- Lower form factor: it reduces system volume, weight, and footprint.

- Improved performance: first of all, integration density is increased. This reduces interconnect length leading to higher transmission speed and lower power consumption.

- Integration of different heterogeneous technologies: due to 2D SoC limitations for integrating different technologies, 3D platform is used to first make discrete dices, and then to combine them either on a substrate or 3D stacking. This has adaptability to a wide variety of microsystem applications.

- Low cost batch production: 3D integration decreases processing costs for mixed technologies.

- New application demands.

The 3D integration technologies can be grouped into 3 main classes, namely 3D on-chip integration, 3D IC-stacking, and 3D-packaging [6]. It should be clarified that if the

Introduction 3

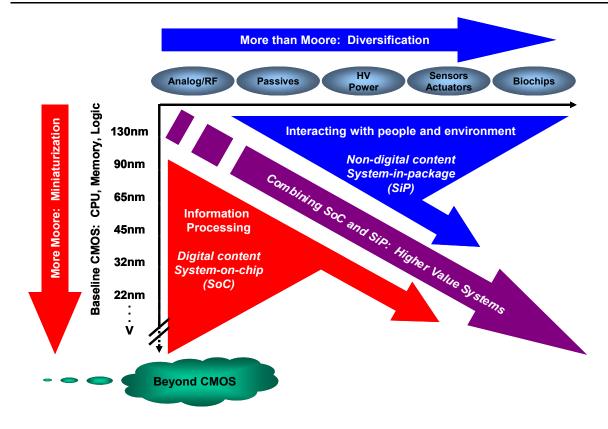

Figure 1-1: The combined need for digital and non-digital functionalities in an integrated system is translated as a dual trend in the International Technology Roadmap for Semiconductors: miniaturization of the digital functions ("More Moore") and functional diversification ("More-than-Moore") [7].

interconnections are made through Si vias (TSV), the technology is categorized as 3D IC-stacking, and if the interconnections are made outside of the die, then it has been categorized as 3D-packaging. Simultaneously, having all these together we have a complete 3D system package, one can call "System-in-Package."

Today, there are increasing industrial demands for smaller size, higher speed, lower power dissipation, better reliability, and more functionality. There is a dual trend for new systems. For digital electronics, there is a trend for continuous miniaturization and its related benefits in terms of performances which is labeled "More Moore". For analog circuits and systems, it is integration of diverse functionality, which is entitled "More-than-Moore". This combined needs for digital and non-digital functionalities in a product is depicted in Figure 1-1 [7].

While "More Moore" may be considered as the brain of a smart compact system, "More-than-Moore" refers to its skills to interact with the outside world and the users.

To cope with this dual trend, we should consider the challenges with both parts. First, in "More Moore" stream, it is important to figure out how to best use existing infrastructure available in IC industry, especially wafer level processing.

Next, in "More-than-Moore direction", we need advanced SiP, but the challenges are:

- 1) how to master the complexity and the different types of interconnects with the focus on the electronic domain;

- 2) how to combine different technologies often work in different domains for heterogeneous integration.

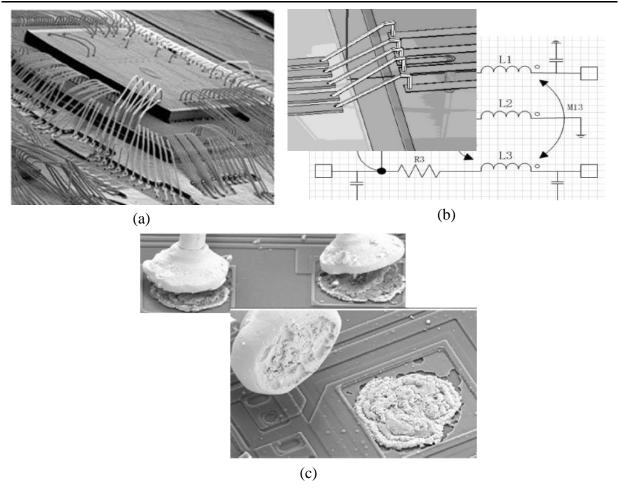

For both topics, the key is how to assemble and connect, or in another word having a reliable mechanical and electrical interconnect. In many technologies, the mechanical and electrical interconnect are coupled (solder bumps, cu-cu bonding etc.). In technologies like wire bonding, mechanical and electrical interconnect are de-coupled and can be optimized separately.

## **1.1.1 SiP Concerns and Requirements**

There are many concerns and challenges for SiP related to its diversity and 3D IC integration such as [8], [9]:

- Non-defined technology standards and industry parameters for optimal technology selection

- Lack of design guidelines, tools, and rules

- Lack of test methods and equipment

- Challenges for mixing chips with different speeds and sizes

- Equipment accuracy for alignments

- Wafer thinning and thin wafer handling during processes

- Thermal management issues

- Challenges with vertical interconnects (like TSV): design tools, high cost,

lacking/expensive high-volume production tools, etc.

These all indicate the importance of research efforts considering various aspects of the SiP related to the materials, technologies, design, fabrication, and reliability issues. In literature, detailed classifications could be found addressing the 'levels of integration' such as wafer-stack, chip-stack, and package/module-stack [10]. Interconnects technology have been addressed by Al-Sarawi [11].

The reliability factors for SiP products are the same as other areas but the relative importance

Introduction 5

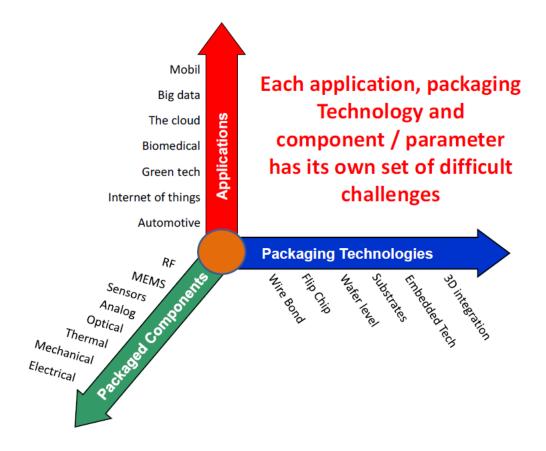

Figure 1-2: Complex SiP contains various types of elements through heterogeneous integration [7].

changes. They have higher thermal cycle count and mechanical stress, and wider range of storage and usage environments due to the use pattern of consumer electronics. Meeting the reliability requirements of future SiP components and systems will require tools and procedures that are not yet available. They should cover from failure mechanisms and standards to lifetime, reliability models, and characterization [2]. The factors that may affect the reliability concerns can be listed as follows: complexity, miniaturization, power, material selection, end use conditions, and interconnect [2], [12]–[14].

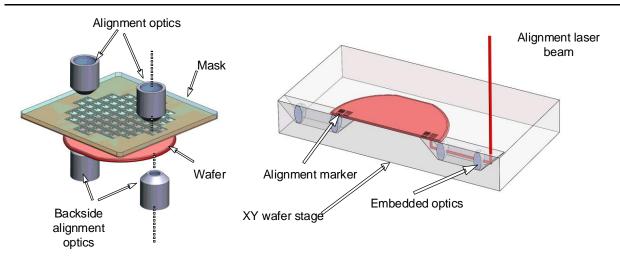

## 1.1.2 Heterogeneous Integration and Wafer Level Packaging

Heterogeneous integration comprises high level assembly of different separately manufactured components. It can enhance functionality and improve the operating characteristics. As SiP includes different elements (as shown in Figure 1-2), heterogeneous integration concerns should be addressed as well.

Wafer-Level Packaging is defined as a technology which all the packaging process are

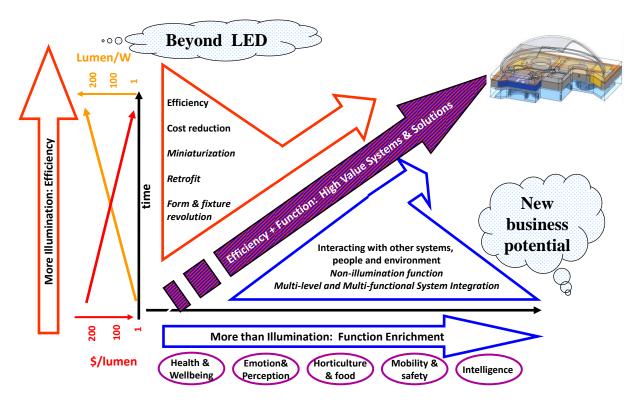

*Figure 1-3: New industrial / technology landscape of lighting.*

performed at the wafer level. It is one of the best potential options among different packaging technologies, because of lower costs, higher scale, superior yields, and higher accuracy. It can achieve highest density integration for hybrid applications. However, there are still some challenges for high accuracy domains [2], [6].

There are two major concerns in wafer-level 3D integration: final reliability and yield after stacking multiple wafers [15]. Wiring between the subsystems, known as "wiring crisis", is the main limitation for performance, multi- functionality, and reliability of 3D systems. It is one of the critical performance bottlenecks for current and future IC generations. So, the key technologies for 3D systems are wiring and wafer bonding, in another word *interconnection*. The quality of interconnection directly addresses the 2 concerns.

## 1.2 Motivation for LED Wafer Level Packaging

The similar trends of Figure 1-1 can also be observed in lighting landscape, as depicted in Figure 1-3. The vertical axis demonstrates the much more illumination trend, pointing to continuing of Haitz's law, in which Ronald Haitz predicted that every decade, the cost per lumen falls by a factor of 10, and the amount of light generated per LED package increases by a factor

Introduction 7

of 20, for a given wavelength (color) of light. This is considered the LED counterpart to Moore's law [16]. Besides, there is another trend for much more than miniaturization, lumen/\$, and lumen/Watt. It includes the increasing demands for multi-functionality, -discipline, -technology, -variability, -material, -interface, -process, -scale, -damage/failure mode, and -testing targets.

This trend introduces more attention not only in technology area but also for covering multi-application/market, -million investment, -innovation/complexity, -talent, -supply chain, -business models, -infrastructure, and -competition [17].

Taking part into this tremendous developing industry and market demands, wafer level packaging can be considered as a key processing point. At present, most LED components are made with single chip packaging technology. The main manufacturing processes follow conventional chip-based IC packaging. So, there is a need for LEDs to migrate to wafer level packaging to use the same benefits as IC's [18]. Nevertheless, there are different boundary conditions to adopt wafer level packaging of LEDs. For instance, there is limited usability of wafer level packaging processes on the LED device wafer directly [19]. But hybrid integration of LED chips on a Si interposer can reduce the cost, and moreover, eases the integration of various functional devices. Using Si devices and capabilities makes it possible to design and fabricate a smart lighting module as a SiP for broad applications especially in the Internet of Things (IoT) area. As IoT promises application diversification, the spotlight is now turned to advanced packages in order to answer market demands [20].

## 1.3 Thesis Objectives

In this work, we are going to introduce a methodology for monolithic wafer-level integration of 2D and 3D systems. It can be employed to fabricate a smart silicon-based interposer for broad range of applications such as MEMS/NEMS, communication and lighting modules. Such interposers can offer various benefits by also integrating some active components, circuits, and systems. One of the best fit application area is a smart solid-state lighting (SSL) unit.

LEDs are believed to dominate all lighting applications in near future. As mentioned before, integration and packaging are two of the critical issues that resolving them enables efficient and reliable solutions for lighting requirements. Wafer level packaging is a promising method to have a lower cost, higher scale, and superior yield.

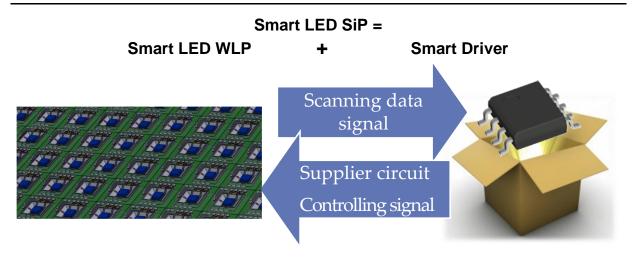

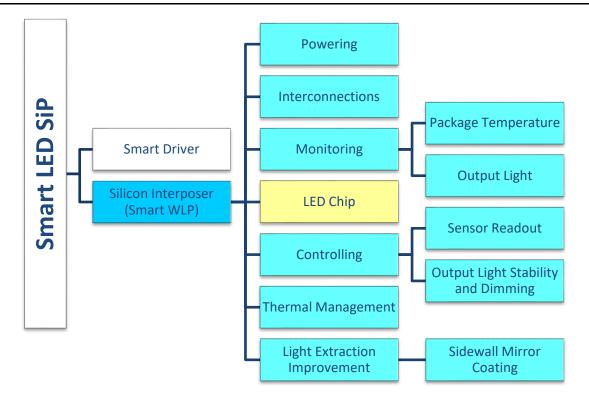

Figure 1-4: A smart LED system comprising a smart LED WLP and a smart driver.

In this dissertation, a new integration approach of a smart unit of LED lighting is introduced: LED SiP. It comprises a *smart LED wafer level package (WLP)* and a *smart driver*. This concept is depicted in Figure 1-4. Smart LED WLP is used as a Si based interposer for LED chips. Firstly, it integrates the wafer level optics, related interconnections, monitoring devices and powering circuits. LED chip would be later mounted. In addition, to make the package smart and leverage semiconductor process, as much controlling functions as possible can be integrated into the silicon interposer. Smart driver is the brain of the total system. It works both as a driver circuit to supply power and a controller. By getting real time sensing data of the package, it can have a better control over electrical and thermal management and so on. Also, wireless communication and remote control functions can be included. Due to rather large nature of LED chips, the final Si utilization yield of the interposer cannot get that high, but a simple low cost processing can compensate total cost of the package.

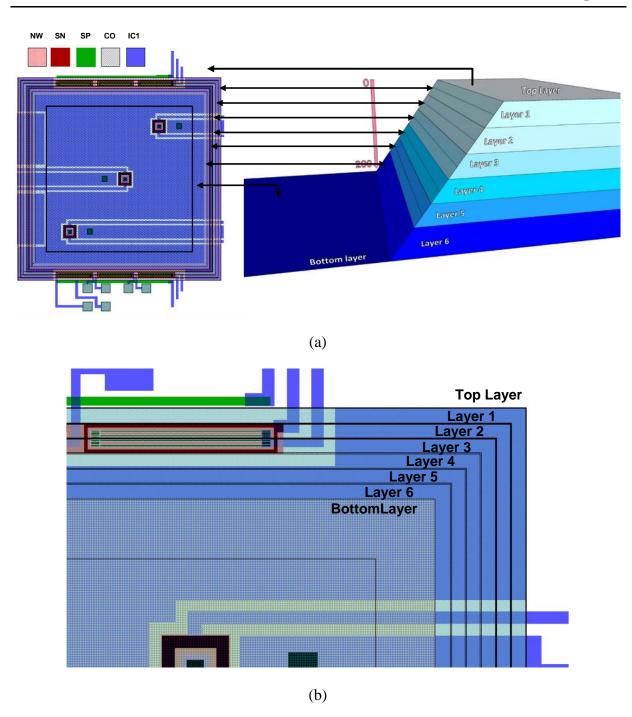

Main effort of this dissertation is on the smart WLP part. The final smart WLP is a high lumen output lighting module. It includes high current blue LEDs and different sensors in a reflector cavity. In this Si interposer with a high topography, lithography defined wiring is used as a reliable interconnect solution. Additionally, control circuit of the LED output light are integrated on the same die to reduce costs of any required external circuitry. In more details, the interposer monolithically integrates on-chip reflector cavity, sensors, remote phosphor layer, litho-defined wiring, power switching transistors, digital sensor readout circuit, and analog light feedback circuit into one smart LED wafer-level package.

Introduction 9

Figure 1-5: Different functions in a smart LED SiP (scope of this dissertation is shown in color).

Different functions and operation levels of this system is presented in Figure 1-5. The advantages of such a LED SiP are:

- Capability of wafer-level optics

- Capability of wafer-level phosphor remote coating for stable color uniformity

- Higher brightness efficiency: on chip reflector cup (cavity with mirror coating) reflects

the side light and improves light extraction efficiency up to 15%.

- Better thermal management: high thermal conductivity of Si substrate

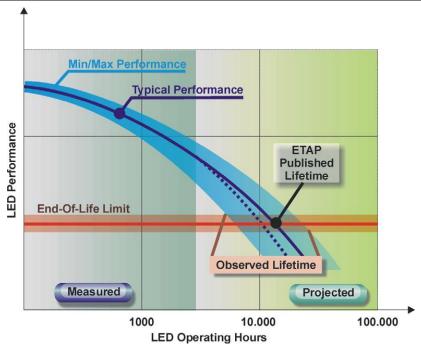

- Lifetime improvement: self-monitoring system

- High reliability: better interconnect reliability, closed-loop feedback circuit for stability and aging compensation

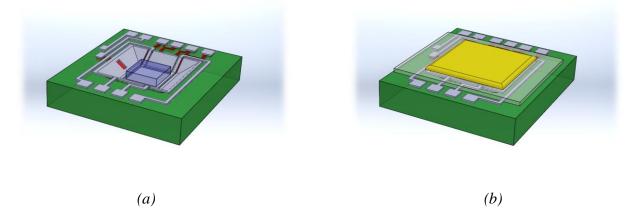

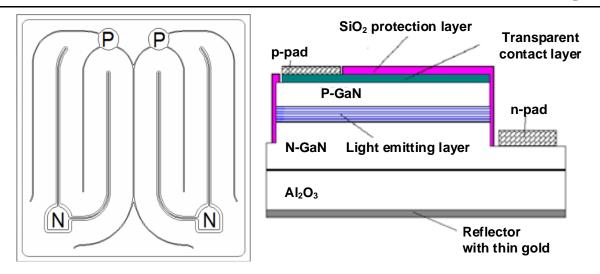

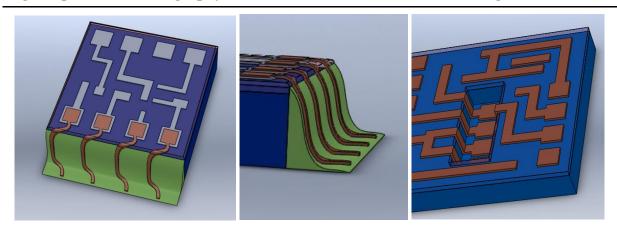

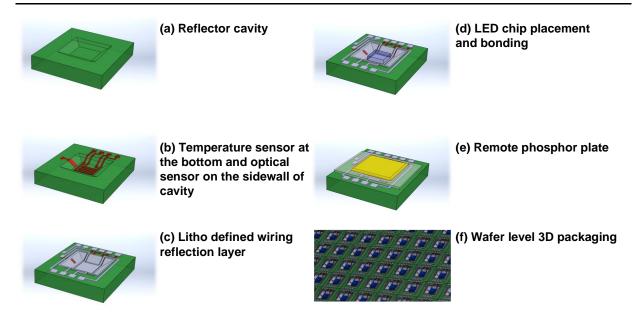

The 3D system integration processing comprises different steps. The final 3D package containing an active reflector cup and one LED chip is schematically shown in Figure 1-6.

## 1.4 Thesis Outline

This thesis is composed of two parts. In the first part, the principles, design and implementation of a monolithically integrated 2D LED SiP are covered. At first, the required low cost processing scheme is explained. It is followed by description of different components

Figure 1-6: Unit cell of a 3D LED WLP; (a) LED chip is mounted on an active reflector cup including sidewall light sensor, bottom temperature sensor and high aspect ratio litho defined wiring lines, and (b) placement of remote phosphor plate on top of the cup.

for using in monitoring and controlling blocks in 2D system. This part ends with demonstration of some measurement and simulation results. In the second part, challenges, design and implementation of 3D system are discussed and demonstrated. Primarily, a high aspect ratio (HAR) lithography approach is developed, which is a significant key for 3D processing. Next, the implementation of 3D package is described.

The first part starts from Chapter 2 by a short introduction of BiCMOS5/7 process and the design concept for smart LED package. A cost effective 5-7 mask (1-2 metal layers) BiCMOS process is proposed for integration in LED WLP. This simple BiCMOS process allows on-chip integration of different Si based sensors, functioning blocks and circuits to be used for an advanced lighting system. To utilize this process for IC fabrication, a complete framework from modeling to measurement is suggested.

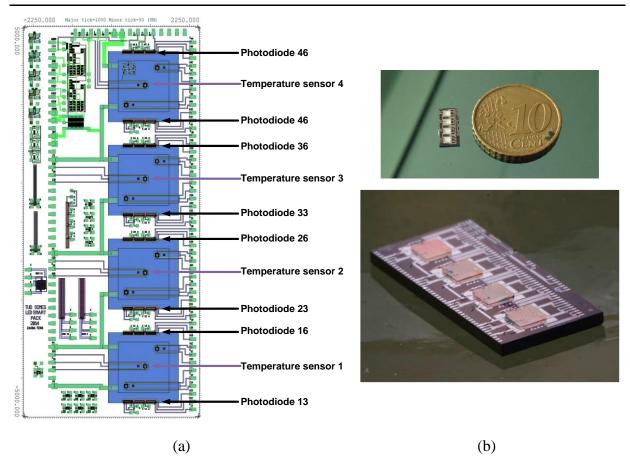

In Chapter 3, a Si based multi-functional WLP for phosphor-based white LED systems is discussed. The system is designed and manufactured using 7-mask BiCMOS process. This package integrates 4 high-power blue light LED dies with temperature sensors, and blue selective light sensors for monitoring the system performance. Sensors are part of the smart monitoring unit. An interdigitated power transistor and a 4-bit flash analog to digital converter were also integrated and described, which are integrated with sensors' readout and extra controlling functions.

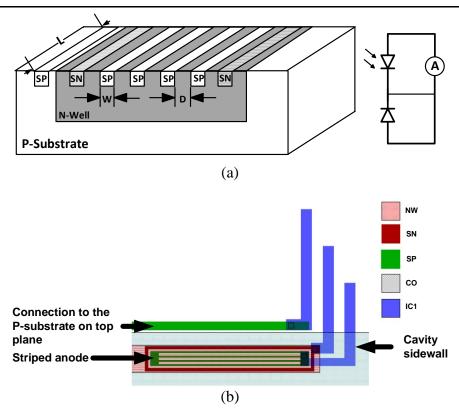

In Chapter 4, the blue selective photodiode is elaborated, which is used for output blue light

Introduction 11

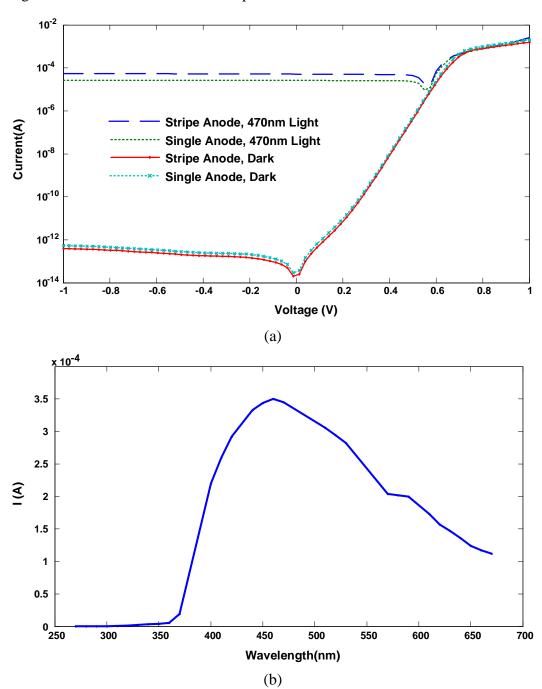

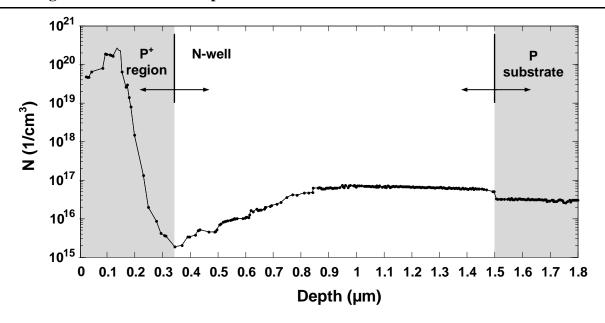

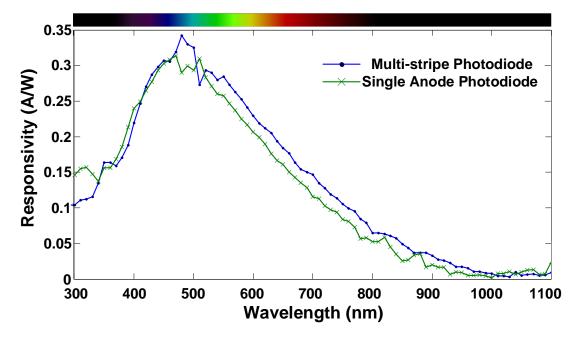

evaluation in previous system. It is composed of a Si stripe-shaped photodiode. This chapter presents how this detector shows a high selectivity to blue light with noticeable responsivity comparing to similar reported devices. The maximum responsivity at 480nm is matched with the target blue LED illumination. It also covers the physical simulation of the device and principles.

In Chapter 5, a monolithic light feedback control circuit is proposed. It is an opamp-based feedback circuit combined with a high-power transistor and the blue-selective photodiode, which controls the output light based on real-time sensor data. The new system guarantees a stable and reliable output light under different working conditions. Besides, integrating this module offers that the output light can be controlled linearly by a reference input voltage.

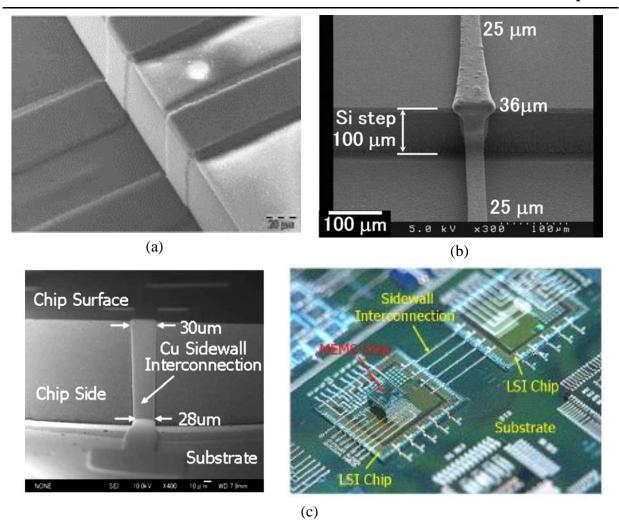

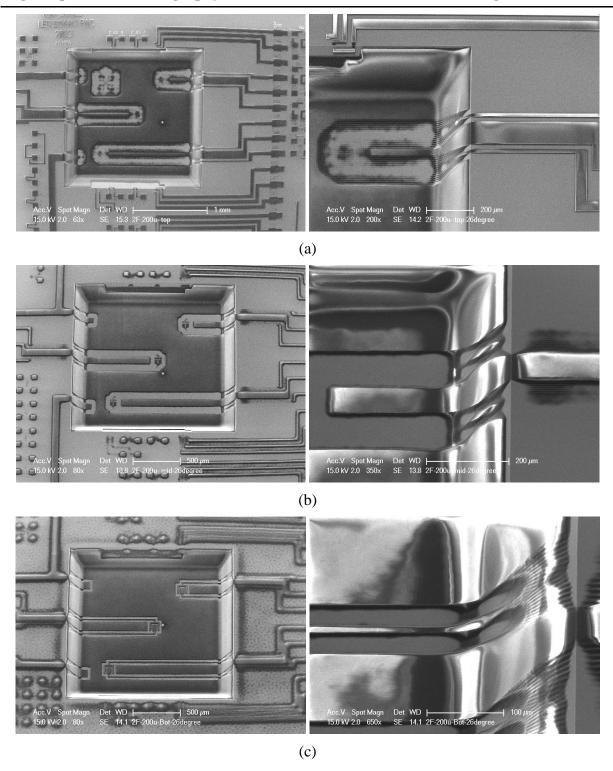

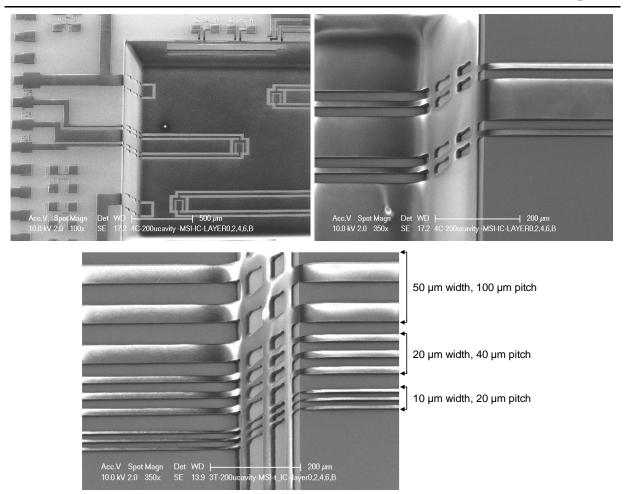

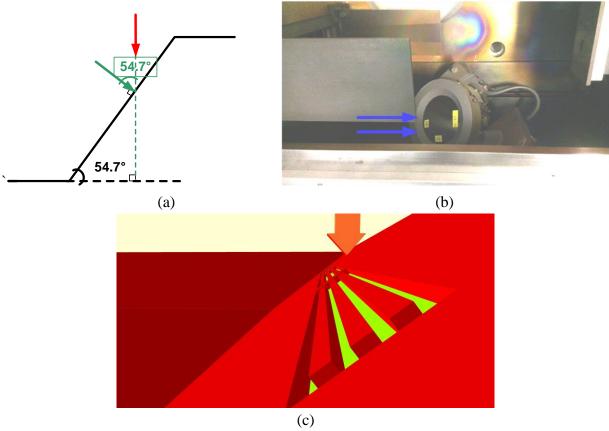

The second part elaborates on how to move our 2D SiP to a 3D package. In this case, a KOH etched cavity in Si interposer makes a high topography that brings up new challenges. It acts as a precision cavity with aluminum coating in place of sidewall mirror. The main challenge is the lithography process steps over a few hundred micrometer topography.

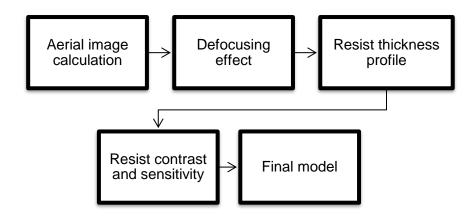

In Chapter 6, we are going to describe a high aspect ratio (HAR) lithography approach that can be used both for the 3D SiP and, in general, for litho-defined lateral wire bonding. Litho-defined wire bonding uses conventional CMOS interconnect toolset and processes in combination with multi-level lithography aiming for "wire bond like" interconnect structures and HAR interconnect. It also enables advanced heterogeneous integration of different components with less reliability issues and problems. This method consists of placing and attaching the chips on supporting substrate, passivation layer deposition, metal deposition and patterning through advanced HAR lithography. At the end, different simulation and experimental results are reported.

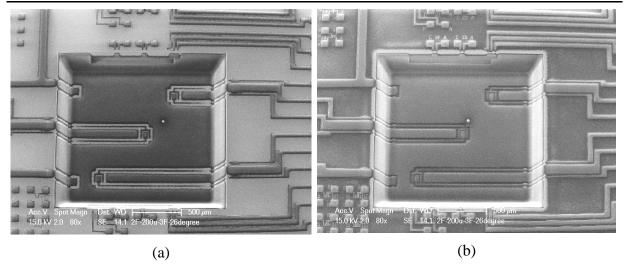

In Chapter 7, the final 3D LED SiP is described covering the design concepts, process flow, challenges, and some measurement results. It uses cavity not only as a precision LED site and for its sidewall mirrors, but also as an *active* reflector cup. It is active since the cavity bottom contains local temperature sensors and the sidewalls carry the output light detector in addition to the HAR interconnects. This is for the first time that an active device (the photodiode) is fabricated on sidewall of a silicon cavity. Other controlling circuit described in 2D package is also integrated on Si top surface.

Finally, Chapter 8 concludes this dissertation and presents suggestions for future developments.

## 1.5 References

- [1] Wikipedia, "Insects."

- [2] W. Chen, W. Bottoms, K. Pressel, and J. Wolf, "The next step in assembly and packaging: System level integration in the package (SiP)," *ITRS White Pap.*, pp. 1–127, 2008.

- [3] ITRS, "International Technology Roadmap for Semiconductors 2.0: Executive Report," 2015.

- [4] T. Tekin, "System-in-package technologies for photonics," in *SPIE*, 2010, vol. 7605, pp. 760506-760506-12.

- [5] M. Wolf and P. Ramm, "Technologies for 3D wafer level heterogeneous integration," in Design, Test, Integration and Packaging of MEMS/MOEMS, 2008. MEMS/MOEMS 2008. Symposium on, 2008, pp. 123–126.

- [6] D. D. Lu and C. P. Wong, Materials for advanced packaging. 2009.

- [7] W. Arden, M. Brillouët, P. Cogez, and M. Graef, "More-than-Moore white paper," *ITRS White Pap.*, 2010.

- [8] J. Lau and X. Zheng, "Failure analyses of 3D Sip (system-in-package) and WLP (wafer-level package) by finite element methods," *IEEE Proc. 16th IPFA*, 2009.

- [9] T. Tekin, "Review of Packaging of Optoelectronic," *IEEE J. Sel. Top. QUANTUM Electron.*, vol. 17, no. 3, pp. 704–719, 2011.

- [10] K. Morihiro, "The dawn of 3D packaging as system-in-package (SIP)," *IEICE Trans. Electron.*, 2001.

- [11] S. Al-Sarawi and D. Abbott, "A review of 3-D packaging technology," *Manuf. Technol.*, vol. 21, no. 1, pp. 2–14, 1998.

- [12] D. Lu and C. P. Wong, *Materials for Advanced Packaging*. Boston, MA: Springer US, 2009.

- [13] C. Uchibori and X. Zhang, "Effects of chip-package interaction on mechanical reliability of Cu interconnects for 65nm technology node and beyond," in *Interconnect Technology*, 2006, no. Vcc, pp. 196–198.

- [14] L. Mercado, C. Goldberg, and S. Kuo, "Analysis of flip-chip packaging challenges on copper/low-k interconnects," *IEEE Trans. DEVICE Mater. Reliab.*, vol. 3, no. 4, pp. 111–118, 2003.

- [15] C.-T. Ko, K.-N. Chen, W.-C. Lo, C.-A. Cheng, W.-C. Huang, Z.-C. Hsiao, H.-C. Fu, and

Introduction 13

Y.-H. Chen, "Wafer-level 3D integration using hybrid bonding," in 2010 IEEE International 3D Systems Integration Conference (3DIC), 2010, pp. 1–4.

- [16] "Haitz's law," Nat. Photonics, vol. 1, no. 1, p. 23, Jan. 2007.

- [17] W. D. van Driel and X. J. Fan, Eds., *Solid State Lighting Reliability*. New York, NY: Springer New York, 2013.

- [18] S. W. R. Lee, R. Zhang, K. Chen, and J. C. C. Lo, "Emerging trend for LED wafer level packaging," *Front. Optoelectron.*, vol. 5, pp. 119–125, 2012.

- [19] M. Hornung, "LED Wafer Level Packaging Motivation, Challenges and Solutions to Meet Future Cost Targets," *SUSS Rep. 02/2012*, 2012.

- [20] A. Ivankovic, T. Buisson, S. Kumar, A. Pizzagalli, and R. Beica (YOLE Developpement), "YOLE Report: Status of Advanced Packaging Industry," 2015.

## Part I: Monolithically Integrated Smart Silicon Interposer Utilized for 2D LED SiP

## Introduction to BiCMOS5/7 Process and Design Concept for Smart LED Package<sup>1</sup>

In this chapter, a cost effective 5-7 mask BiCMOS process, proposed for integration in LED WLP, is demonstrated. This straightforward BiCMOS process allows on-chip integration of different silicon-based sensors, functional blocks and circuits to be used for advanced lighting systems. To utilize this process for IC fabrication, a complete framework from modeling to measurement is suggested. This approach is also useful for heterogeneous integration in applications with rather large area and low cost requirements.

## 2.1 Introduction

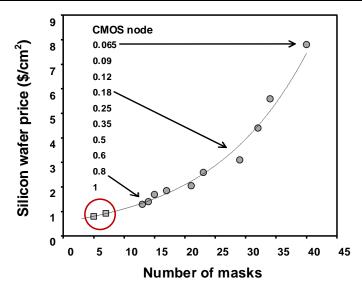

Currently, the advanced ICs are quite complex. Transistor count is the most common measure of IC complexity. Today, modern CPUs have over 7 billion transistors integrated in a chip and each device must perform a specific function [1]. The extremely high demands on the processing are pushing the equipment suppliers to deliver machines that not only can produce ICs with high yield, but also with the lowest cost. While the cost per transistor is reduced in advanced IC technology, in contrast, the cost per area is increasing rapidly. Consequently, using

<sup>&</sup>lt;sup>1</sup> The BiCMOS5 process was firstly designed and developed in Dimes Technology Center in 2010 by Dr. Henk van Zeijl. The models and frameworks in this chapter are developed in cooperation with MSc student Teng Ma [3].

advanced and high cost processing for large area applications is not practical.

The CMOS and MEMS technologies provide a broad technology portfolio with many applications for solid-state lighting (SSL). However, for LED wafer level packaging (WLP), due to large nature of each LED die (mm range), high Si throughput is not possible. To reduce the fabrication cost, process should be at the lowest cost. So, to make WLP reasonable for SSL, a reliable fabrication process is required which should be simple, robust, flexible, and low cost. Moreover, it should be able to fulfil the requirements to build active electronics and sensors. In Dimes Technology Center<sup>2</sup>, a BiCMOS process with only 5 to 7 mask steps (BiCMOS5/7), comprising 1-2 metal layers, was developed which shows a possible direction towards building basic electronics by using unconventional metallization steps [2]. Nevertheless, it had never been employed for IC design. In this chapter, we introduce the concept and a framework for IC design based on BiCMOS5/7. This approach can open new areas for heterogeneous integration in broad range of applications such as smart interposers and lab on chips.

This chapter is organized as follows: in Section 2.2, we are going to present the general idea of BiCMOS5/7 process and the main process steps. In Section 2.3, layout of BiCMOS test die including its main devices is described. Section 2.4, suggests an IC design framework based on BiCMOS5/7 from device modeling to wafer level implementation and measurements. In Section 2.5, we talk about using BiCMOS for smart LED wafer level packaging. Finally, it will end by a short conclusion of the chapter.

## 2.2 Methodology

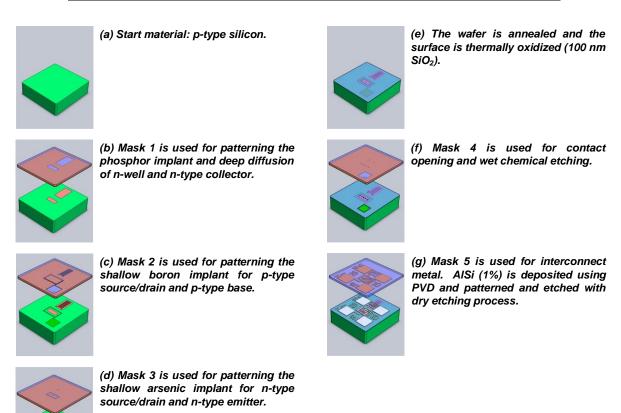

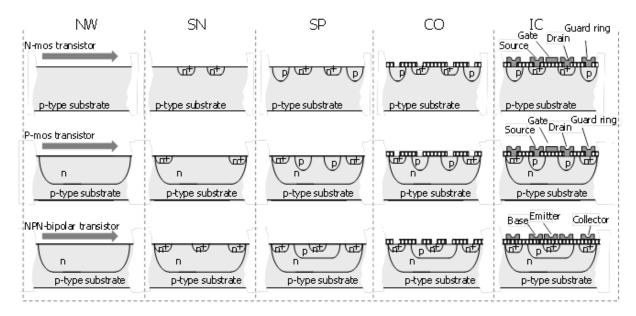

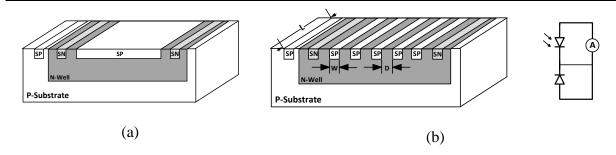

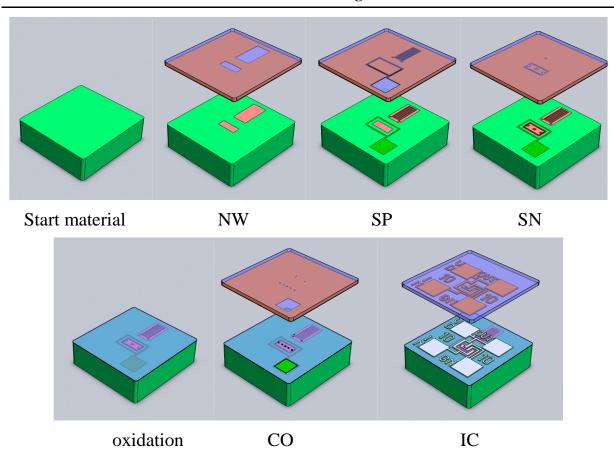

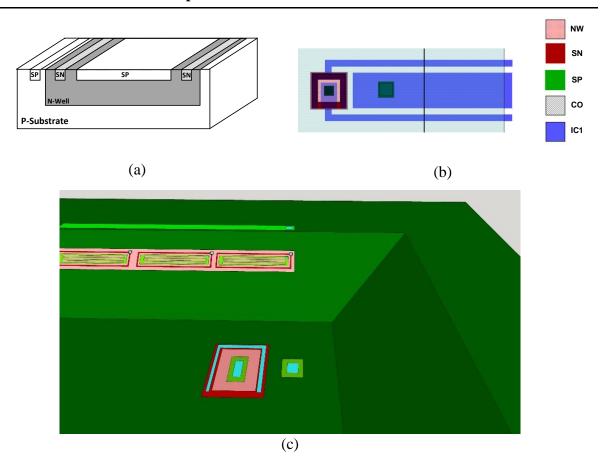

The BICMOS5 process was firstly designed by Dr. ir. Henk van Zeijl for education purposes [3]. However, its rather low cost and simple nature motivated us to use it as a base process for monolithically integration of different devices in LED WLP. The main characteristics of the process are: simple technology in terms of layout and process steps, while at the same time three main devices are being fabricated; NPN bipolar transistor, NMOS, and PMOS [2]. Table 2-1 lists core of the process consists of 5 mask steps. A brief process overview is given in Figure 2-1. More detailed outline of the process is summarized in Table 2-2. The three main devices are illustrated in Figure 2-2.

<sup>&</sup>lt;sup>2</sup> The Dimes Technology Center affiliation is changed to Else Kooi Lab, EKL, from April 2015.

Table 2-1: Core process mask steps of the BICMOS5/7 process (the grey shaded ones are added for BiCOMS7).

| Mask name | Main purpose                                                                                                         |  |

|-----------|----------------------------------------------------------------------------------------------------------------------|--|

| NW        | <ul> <li>N-type area for the PMOS transistor (N-well) and for the<br/>collector of the bipolar transistor</li> </ul> |  |

| SN        | <ul> <li>N-type source-drain for the NMOS transistor and for the<br/>emitter of the bipolar transistor.</li> </ul>   |  |

|           | <ul> <li>Low resistance collector contact</li> </ul>                                                                 |  |

|           | <ul> <li>N-type guard ring</li> </ul>                                                                                |  |

| SP        | <ul> <li>P-type source-drain for the PMOS transistor and for the base<br/>of the bipolar transistor</li> </ul>       |  |

|           | <ul> <li>P-type guard ring</li> </ul>                                                                                |  |

| СО        | <ul> <li>Contact openings</li> </ul>                                                                                 |  |

| IC        | - Interconnect and gate material                                                                                     |  |

| VIA       | <ul><li>VIA openings</li></ul>                                                                                       |  |

| IC2       | <ul> <li>Second interconnect layer</li> </ul>                                                                        |  |

Figure 2-1: Process overview of the core steps in the BICMOS5 process.

Table 2-2: Outline of BiCMOS5 Process

| Process                | Mask Name | Process Description                                                                              |

|------------------------|-----------|--------------------------------------------------------------------------------------------------|

| Substrate              |           | Silicon, 10 <sup>16</sup> cm <sup>-3</sup> boron doped                                           |

| Oxidation              |           | 20 nm thermal oxidation of silicon                                                               |

| N-well implantation    | NW        | Low dose high energy phosphorus implantation                                                     |

| N-well drive-in        |           | 1100 °C, 4 hours diffusion to form the NPN collector and the N-well for the PMOS                 |

| Shallow N implantation | SN        | High dose low energy arsenic implantation to form the NPN emitter and the NMOS source and drain  |

| Shallow P implantation | SP        | Medium dose medium energy boron implantation to form the NPN base and the PMOS source and drain. |

| Gate oxidation         |           | 1000 °C anneal and dry oxidation to activate the dopants and form the gate oxide of 100 nm.      |

| Contact opening etch   | СО        | Wet etch thermal silicon dioxide                                                                 |

| Metal deposition       |           | AlSi (1%) sputtering to deposit the gate electrode and interconnect metal                        |

| Metal pattern etch     | IC        | Wet or dry etch the metal pattern                                                                |

| Alloying               |           | Alloying by annealing at 400 °C in forming gas                                                   |

Figure 2-2: Formation of three main devices: NMOS, PMOS, and NPN bipolar transistors during 5 mask steps of BiCMOS5.

Mask name

Main purpose

BN

Buried N layer to reduce the collector resistance of the NPN transistor. This process requires an epitaxial silicon deposition process after the BN process.

PP

The dopant concentration of the P-type source drain implant is limited because this implantation is also used for the NPN-base implant. To reduce the PMOS source drain resistance, a higher dopant concentration is applied.

V<sub>T</sub> adjust

To adjust the threshold of the MOS devices, a blanket boron implantation is applied

*Table 2-3: Additional process steps of the BICMOS5 process.*

The core process requires tight tolerances on the P-type substrate doping;  $1\times10^{16}$  cm<sup>-3</sup>. The available P-type wafers at DIMES TC has much wider specifications (2-5  $\Omega$ ·cm) which corresponds  $7\text{--}3\times10^{15}$  cm<sup>-3</sup>. We can make it in two ways: epitaxy and extra implantation (to adjust the threshold voltage of the MOSFETs). As epitaxy is a complicated and expensive process, an alternative would be to add a blanket high energy/ multi-energy boron implant and anneal to obtain the required dopant concentration. Also, the threshold voltage (V<sub>T</sub>) adjust implantation, can be tuned. The dose and parameters of both methods can be tuned based on resistivity measurements of substrate wafers. However, using epitaxial layer is recommended for more reliable results.

Obviously, with only 5 masking layers; three diffusions, one contact opening and one metallization, the device performance is not ideally optimized. Additional process steps can be added to improve the PMOS and the NPN transistors. Those process steps are listed in Table 2-3.

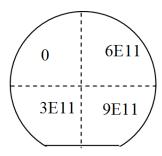

At the end, the electrical characterization is performed and the difference in the relevant transistor parameters are studied in relation to the process variations. The  $V_T$  adjust is usually implanted on 3 quadrants on the wafer with 3 different implantation dose, see Figure 2-3.

For BiCMOS7 just two more mask steps are added, for opening VIA's and patterning second interconnect layer. They are shown in grey shaded rows of Table 2-1. The corresponding additional process steps, summarized in Table 2-4, are added before final alloying.

Figure 2-3: Dose variations (in cm<sup>-2</sup>) of the boron implantation for  $V_T$  adjust. The implantation energy is 25 keV.

| Process                    | Mask Name | Process Description                                           |

|----------------------------|-----------|---------------------------------------------------------------|

| Isolation layer deposition |           | SiO <sub>2</sub> deposition @ 400°C with CVD                  |

| VIA etch                   | VIA       | Dry etch CVD silicon dioxide                                  |

| Metal deposition           |           | AlSi (1%) sputtering to deposit the second interconnect metal |

| Metal pattern etch         | IC2       | Wet or dry etch the metal pattern                             |

*Table 2-4: Additional process steps of the BICMOS7 process.*

## 2.3 Layout of BiCMOS Test Die

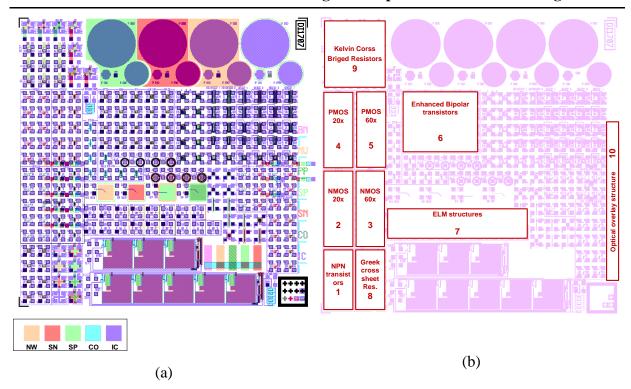

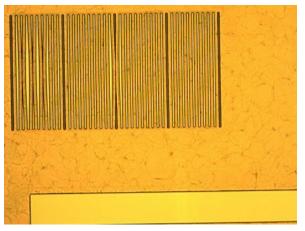

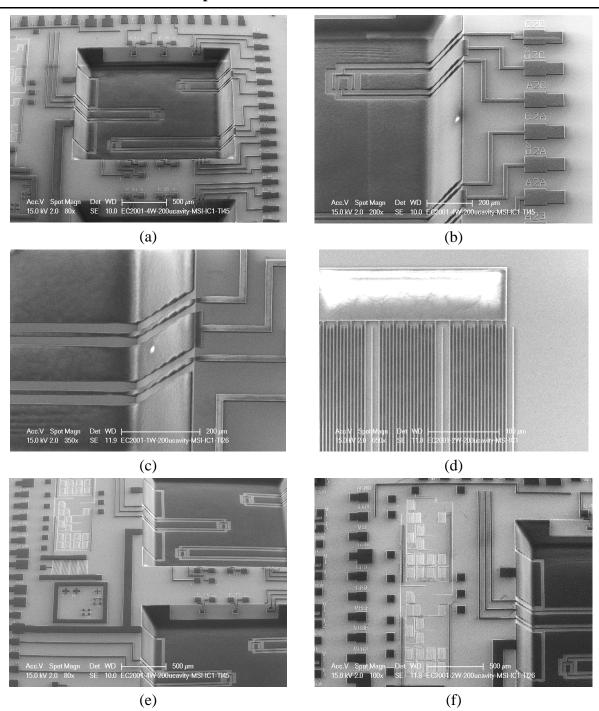

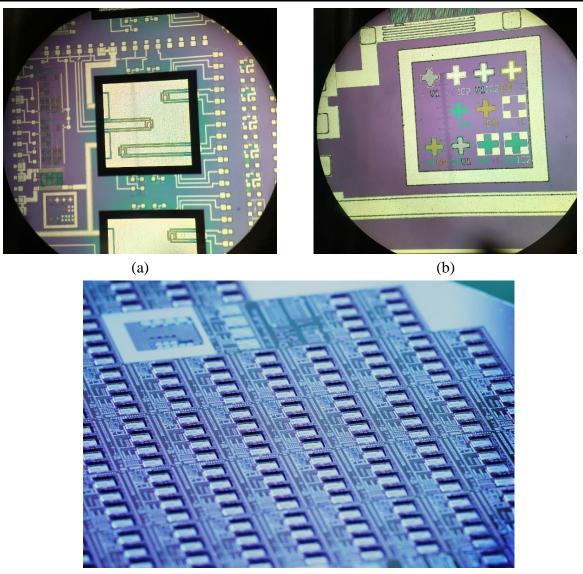

The test devices to be characterized are designed in a 6×6mm<sup>2</sup> test die. The die layout is given in Figure 2-4(a). The test chip contains different devices and test structures designed to measure the variation and parameters of process steps and characterize the transistors, resistors, etc. The devices are organized in groups called cells (see Figure 2-4(b)). Each cell is indicated with a red rectangle and a number in the die. The most relevant cells are marked and will be discussed in the following. The regular pattern of the contact pads makes it easy to do automated measurements with a probe station.

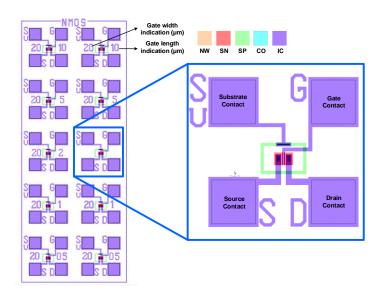

Figure 2-5 gives the layout of a set of NMOS test transistors with gate width of  $20 \,\mu m$ . They are from cell number 2 and 3 in Figure 2-4(b). The lithographically defined gate length is indicated near the transistor. Due to the out-diffusion of the source/drain dopants, the effective gate length is much smaller. There are two columns of identical sets of test transistors for redundancy purposes. For each test structure or test device, the functions of the terminals are indicated in the interconnect pattern.

Figure 2-4: BiCMOS5 test structures: (a) die layout, and (b) different cells.

Figure 2-5: Layout of a set of NMOS transistors with gate width of 20 µm for test purposes.

The same test structures are included for PMOS transistors in cell number 4 and 5 in Figure 2-4(b).

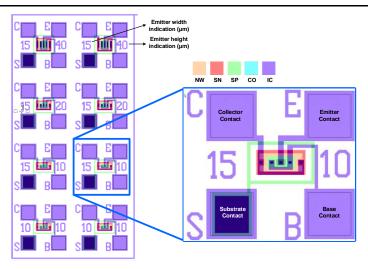

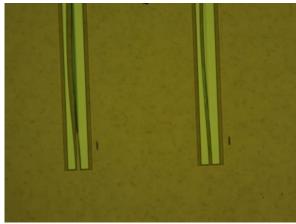

Figure 2-6 gives the layout of a set of NPN bipolar test transistors with different area from cell number 1 in Figure 2-4(b). The emitter area is indicated near the transistor.

Figure 2-6: Layout of set of NPN bipolar transistors with different emitter areas for test purposes.

There are also some process control test structures such as: electrical linewidth measurement (ELM) structures (cell number 7), Greek cross sheet resistance structures (cell number 8), cross bridge Kelvin resistors (cell number 9), and optical overlay test structures (cell number 10).

The sheet resistance is measured using the Greek cross structures. These structures make it possible to measure the sheet resistance of the different layers on the processing wafer [4]. The contact resistance is a measure for the resistance between two layers, for instance between interconnect and doped areas. A contact resistance exists due to a bandgap difference between two contacting materials. It can be measured by using a cross bridge Kelvin resistor [5].

## 2.4 Design Framework Based on BICMOS 5/7

BICMOS5 process was firstly developed in Dimes Technology Center in 2010. However, it had never been employed for IC design. The five-mask process basically meets the fabrication requirements for single components and small circuits. For the very large scale integrated circuit (VLSI) designs, more metal layers are needed. For extra metal, two additional masks are required (for patterning and etching the vias between the metals, and the second metal interconnects).

For IC design panel, making reliable device models is critical. They are later imported in circuit design tool as a reference design library. The model types are different for various simulation tools. BSIM<sub>3</sub>V<sub>3</sub>, as one of the most used MOSFET model in H-Spice simulator, is chosen for our modeling. For physical verification of the design, we should also develop design

## Device modeling (HSPICE model of MOSFETs, diodes, resistors in BSIMProPlus™) Device modeling (Hspice model of Mosfets, (Cadence) (Cadence) (Cadence/L-Edit) Layout extraction and design check (Cadence/L-Edit)

Figure 2-7: Design and fabrication framework for BiCMOS process.

rule check (DRC) and layout versus schematic (LVS) check based on our process features and limitations.

The models and design check regulations should be built up before starting the final design. In this section, a complete framework is proposed<sup>3</sup>.

Figure 2-7 shows the proposed design framework for BICMOS process. It mainly consists of four phases:

- Firstly, full characterization of the devices is done and HSPICE models for MOSFETs, diodes, and passive components are extracted using BSIMProPlus<sup>TM</sup> tool.

- Secondly, the complete model is introduced into Cadence CAD tool for circuit design and simulation.

- Thirdly, the correspond circuit layouts are sketched by applying DRC and LVS check. These checking files should be compiled based on the process criteria and design requirements. The complete layout can be transferred into L-Edit tool in order to finalize the ".tdb" mask file to produce the masks for fabrication process.

- Finally, the ICs are fabricated through BICMOS process in DIMES cleanroom 100. Then, measurement are done in both wafer/PCB-level. The feedbacks based on measurement results can be applied to the previous steps to revise/optimize the design.

The following subsections are going to describe each step in detail.

<sup>&</sup>lt;sup>3</sup> Thanks for the efforts made by Xiaochen Zhang, Jianzhao Chen and Hua Dong from UESTC. They firstly proposed a preliminary design framework based on DIMES BICMOS process in 2013.

## Device characterization in Cascade probe station

- •NMOS, PMOS, and resistors from BiCMOS test die

- •Full measurement at 25, 50, 75, and 100 °C

## Data management in MATLAB

•Import raw measurement data into MATLAB to organize and reformat them for later use by BSIMProPlus™

## Model extraction in BSIMProPlus™ modeling tool

- •Models at different temperature (25-100 °C)

- •Some process parameters can be added from process simulation to Tsuprem4-Medici

Figure 2-8: Device modeling steps.

## 2.4.1 Device Modeling

The steps are summarized in Figure 2-8. Initially, all the devices, such as NMOS, PMOS, and diodes incorporated in the BiCMOS test die are electrically characterized on the Cascade probe station. The current/voltage data are automatically recorded by a control system. For later investigation of temperature effect on our ICs, the devices are characterized at 25, 50, 75 and 100 °C. Since the BSIMProPlus<sup>TM</sup> modeling tool, can only handle certain format of data, the raw data should be organized in MATLAB. Finally, the formatted data can be loaded into BSIMProPlus<sup>TM</sup> for model extraction. With a proper extraction scheme, the output BSIM<sub>3</sub>V<sub>3</sub> models have a small average error and good consistency with the measurement results. Some process parameters like junction depth can be determined by means of process simulation. In the design phase, these models can be directly used in circuit design tool.

## 2.4.2 Circuit Design and Simulation

To setup the library of components in Cadence, the models generated in the previous step are imported into Cadence CAD environment. In Cadence design environment, first the single components and later the circuits are designed and interconnected. In next step, the designed blocks are simulated by H-spice simulator within analog design environment (ADE). In order to study the package temperature effects on circuit performance, different temperature models from 25 to 100 °C can be switched over during simulation. Based on simulation results, the design can

# Library file setup in Cadence •Importing the BSIMProPlus™ models into cadence library Circuit design in Cadence •Designing different components and circuits Simulation with HSPICE simulator •Verifying the performance of the system with setting proper test benches •Studying the effect of package temperature at different temperature (25-100 °C)

Figure 2-9: Circuit design and simulation steps.

be enhanced to optimize the performance under required conditions. The design flow is shown in Figure 2-9.

## 2.4.3 Layout Extraction and Design Check

First of all, the layers according to each mask step of BiCMOS process should be defined, each layer with its own name and functionality. Additionally, for preventing unwanted errors in the layout, we should think of some checking strategy. For layout inspection, a checking tool called "Calibre", from Mentor Graphics Inc., is available in Cadence environment. There are two main physical verifications, which are design rule check (DRC) and layout versus schematic (LVS) check. The DRC ensures all the layout geometries such as line width, clearance, area, etc. are within the acceptable range for fabrication. The LVS check is to make sure that the drawn layout is exactly corresponding to the same circuit as the schematic design is. However, it is necessary to compile two rule files for the DRC and LVS, based on BiCMOS process conditions and design requirements in advance.

Following, the layout is sketched in a hierarchy mode, from low to high level. Besides, some sub-circuit blocks can be added as process control modules for quick test on the wafer level. Then, it is necessary to perform the rule checks (DRC and LVS) on the whole layout and modify it if needed. For some applications, it is also recommended to do post layout extraction and

#### Layer defenition and compiling layout checking files

- Defining the layers for each mask step

- Compiling layout checking files based on BiCMOS process conditions

- Designing rule check (DRC)

- Layout vs. shcematic (LVS)

#### Layout design and check

- Drawing the layout for single components and circuits

- •DRC and LVS check and modifying the layout if needed

#### Finalizing the mask in L-Edit

- Exporting the GDS file from Cadence

- Importing the layout in L-Edit and put in the standard stepper mask format

Figure 2-10: Layout extraction steps.

investigate the parasites and their influences on our target performance.

As a final step, the complete circuit layout is exported as a GDS file and imported into another layout edit tool called "L-Edit", to finalize the mask layout in stepper format. These steps are depicted in Figure 2-10.

#### 2.4.4 Fabrication and Measurements

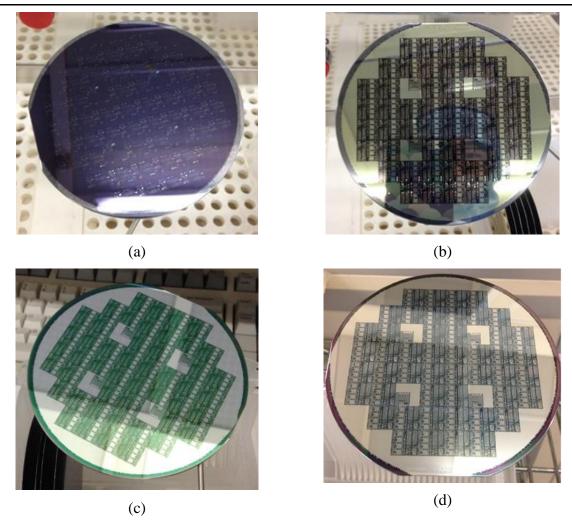

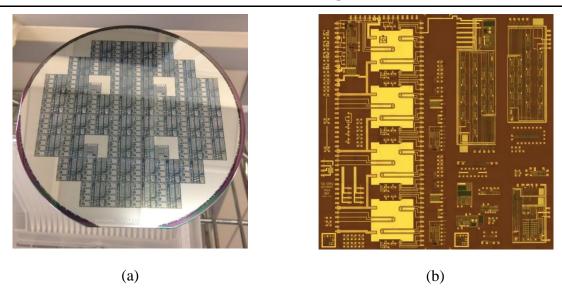

Based on the final die layout, the stepper chromic masks are printed. The process is done in EKL clean-room 100 on 4-inch wafers. For process evaluation and calibration in all the BiCMOS runs, at least 4 BiCMOS test dies are included in wafer layout (1 in each wafer quadrant). They are generally considered as process control modules (PCM). BiCMOS5 flowchart comprises almost 90 steps. For BiCMOS7, some extra steps are added for 2<sup>nd</sup> metal layer.

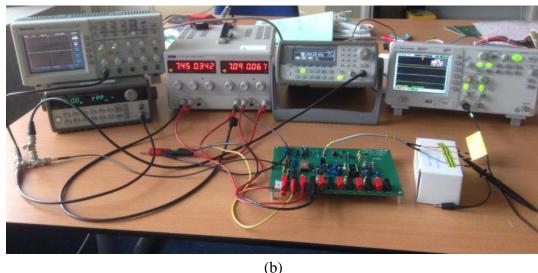

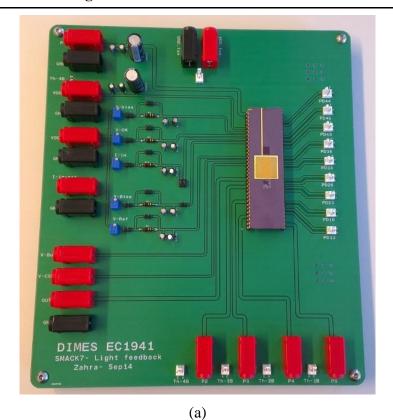

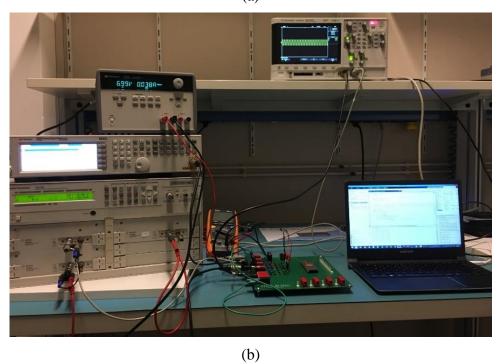

Small blocks, some sensors, and devices can be directly measured on probe station. For bigger circuits with larger number of I/O terminals and special measurements for some of the devices, tests should be done on printing circuit board (PCB). So, dies are diced and packaged. They will be later assembled on pre-designed PCBs. Figure 2-11 summarized the steps.

# Wafer processing in Dimes CR100 •BiCMOS5/7 flowchart steps with 5/7 masks Wafer-level measurement •Tests on cascade probe station PCB level measurement •Die packaging •PCB design and assembly •Measurement

Figure 2-11: Fabrication and measurements steps.

#### 2.5 Smart LED Package Runs (SMACK)

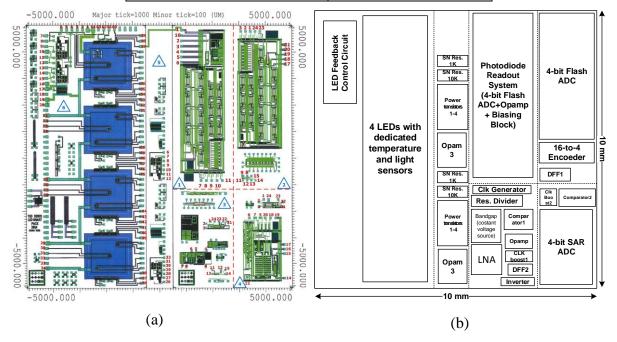

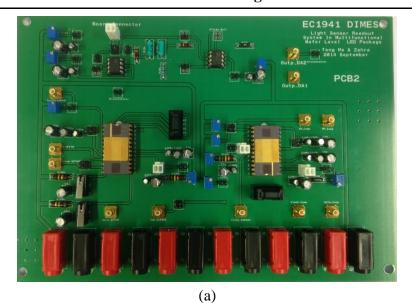

In different parts of this project, several BiCMOS runs were carried out. The optical part was designed in  $4.5\times10~\text{mm}^2$  die size, for integrating 4 LED chips with corresponding sensors and circuits. It will be discussed in next chapters. For sensor readout system, an electrical part was also added and so the full die size became  $10\times10~\text{mm}^2$ .

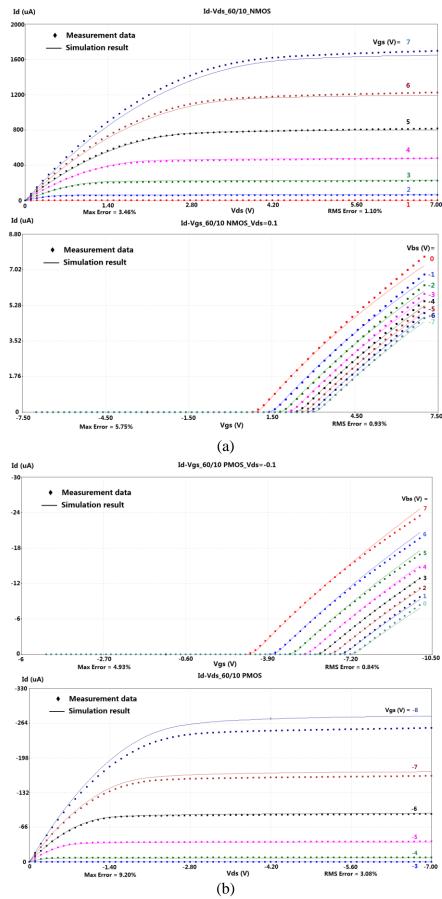

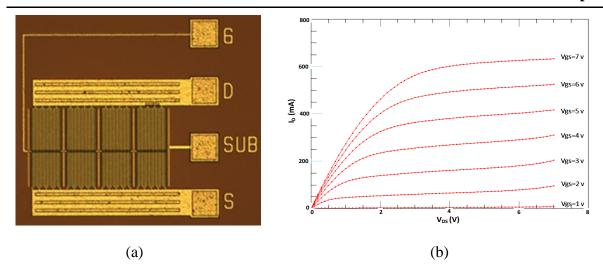

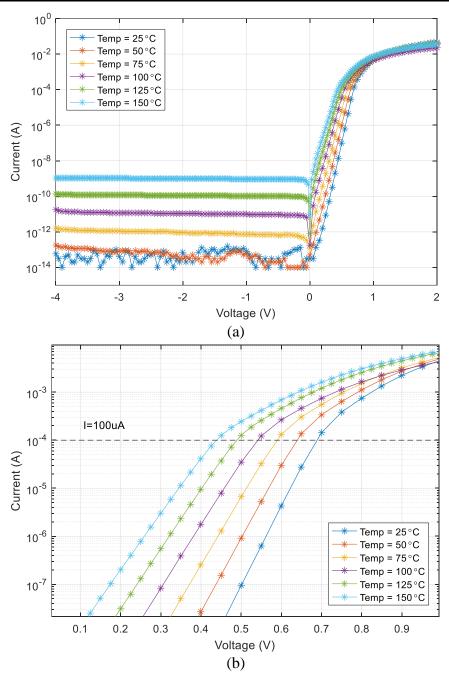

To develop the previously discussed framework, device modeling was done for MOS transistors, resistors, and diodes. The IV measurements were performed for both NMOS and PMOS transistors with 3 different channel lengths (2, 5 and 10 μm) and 2 different channel widths (20 and 60 μm) to obtain a broad overview of device characteristics. The data is then organized to be imported into BSIMProPlus<sup>TM</sup> for model extraction.

The transfer ( $I_{DS}$  – $V_{GS}$ ) and output characteristics ( $I_{DS}$  –  $V_{DS}$ ) of the transistors were measured. The source was grounded for both NMOS and PMOS. The biasing conditions for both NMOS and PMOS for IV characterizations are tabulated in Table 2-5 and Table 2-6.

| I-V data                         | V <sub>GS</sub> (V)   | V <sub>DS</sub> (V)                    | V <sub>BS</sub> (V)     |

|----------------------------------|-----------------------|----------------------------------------|-------------------------|

| I <sub>DS</sub> -V <sub>GS</sub> | $-7 \le V_{GS} \le 7$ | V <sub>DS</sub> = 0.1 V (Linear mode)  | $-7 \le V_{BS} \le 7$   |

| 1D2 A C2                         | Step= 0.2 V           | V <sub>DS</sub> =7 V (Saturation mode) | Step =1 V               |

| I <sub>DS</sub> -V <sub>DS</sub> | $1 \le V_{GS} \le 7$  | $0 \le V_{DS} \le 7$                   | $V_{BS} = 0 V$          |

| 103 V DS                         | Step= 1 V             | Step= 0.1 V                            | $V_{BS} = -7 \text{ V}$ |

Table 2-5: NMOS biasing conditions for IV characterization.

Table 2-6: PMOS biasing conditions for IV characterization.

| I-V data                         | V <sub>GS</sub> (V)    | V <sub>DS</sub> (V)                       | V <sub>BS</sub> (V)  |

|----------------------------------|------------------------|-------------------------------------------|----------------------|

| I <sub>DS</sub> -V <sub>GS</sub> | $-10 \le V_{GS} \le 5$ | V <sub>DS</sub> = - 0.1 V (Linear mode)   | $0 \le V_{BS} \le 7$ |

|                                  | Step= 0.2 V            | $V_{DS} = -7 \text{ V (Saturation mode)}$ | Step =1 V            |

| $I_{DS}-V_{DS}$                  | $-8 \le V_{GS} \le -2$ | $-7 \le V_{DS} \le 0$                     | $V_{BS} = 0 V$       |

|                                  | Step= 1 V              | Step= 0.1 V                               | $V_{BS} = 3 V$       |

Furthermore, to investigate the temperature effects on the designed blocks, four models were extracted based on the data measured at 25, 50, 75, and 100 °C. Cascade probe station, Agilent 4155B parameter analyzer, and temperature controller were utilized as the main test equipment.

Due to the out-diffusion of the source/drain dopants, the transistors with gate length smaller than 1  $\mu$ m do not work properly. The ones with gate length smaller than 2  $\mu$ m have very serious channel length modulation effect.

BSIM<sub>3</sub>V<sub>3</sub> is a scalable model that can cover a wide geometry range with one set of model parameters. To generate initial device models, the strategy here is to use global parameters as the extraction method. Based on the Tsuprem-4 and Medici simulation results and process data, some extraction parameters such as gate oxide thickness, substrate doping concentration and junction depth can be optimized. The optimized model shows a better accuracy and it can precisely reproduce the IV characteristics of actual devices. Figure 2-12(a-b) show the measurement and simulation results at 25 °C for W/L=60 $\mu$ m/10 $\mu$ m NMOS and PMOS, respectively. It shows a good agreement between the model and the actual measurement data. Also, the average error is acceptable for the target voltage range. The threshold voltage in the wafers with epi layer, using 3E11 cm<sup>-2</sup> V<sub>T</sub> adjust dose, is 1 V for NMOS and -3.5 V for PMOS.

Figure 2-12: IV characteristics for device modeling of (a) NMOS and (b) PMOS at 25 °C.

**32**

*Table 2-7: NPN biasing conditions for IV characterization of diodes.*

| I-V data       | V <sub>B</sub> (V) | V <sub>E</sub> (V)                 | V <sub>c</sub> (V) | V <sub>S</sub> (V) |

|----------------|--------------------|------------------------------------|--------------------|--------------------|

| $I_E - V_{BE}$ | 0 V                | $-1 \le V_E \le 1$ $Step = 0.01 V$ | 0 V                | 0 V                |

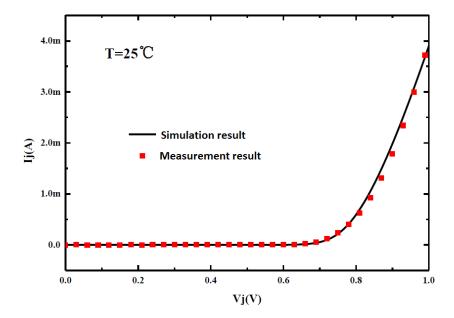

Figure 2-13: Ij vs. Vj of base-emitter junction diode at 25°C.

Base-emitter (BE) junction of a NPN bipolar junction transistor was used as a diode in our designs. The IV characterizations were performed at four different temperatures (25 - 100 °C) to obtain a wide overview of the device characteristics. The measurement data was converted into a specific format for BSIMProPlus<sup>TM</sup> and the model parameters were extracted. The biasing conditions are summarized in Table 2-7.

Figure 2-13 shows the comparison of simulation and measurement results at 25 °C for BE diode. The simulation results are well consistent with the measurement results.

As BiCMOS does not include a Poly-silicon layer, the resistors are implemented using shallow-N (SN). We mainly considered the out-diffusion effect, and voltage and temperature coefficients during resistor modeling. Due to the lateral diffusion of dopants, the effective width of resistor is bigger than layout width. This error is not related to layout width but to the process. The effective width of resistor equals W+dw. Then resistance is

$$R = R_{\blacksquare} \frac{L}{W + dW}, \tag{2.1}$$

| Length | TC1(ppm/°C) | TC2(ppm/°C) | VC1 (ppm/V) | VC2 (ppm/V) |

|--------|-------------|-------------|-------------|-------------|

| 10 μm  | 1559        | 0.464       | 646.17      | 27.82       |

*Table 2-8: Temperature and voltage coefficients of 10 μm SN Resistor.*

where R is the resistance value,  $R_{\blacksquare}$  is the sheet resistance and L is the length of SN resistor.

Linear data fitting method were used to characterize the relation of conductance with layout width. For 10 µm width, the lateral diffusion was determined as 0.62 µm.

Temperature and voltage coefficients were also extracted. The relation of resistance with temperature (T) is a complicated non-linear relationship. Quadratic polynomial data fitting method were used to describe this non-linear relationship.  $T_{Factor}$  as the temperature effect coefficient for resistance value is considered

$$T_{Factor} = 1 + TC1 \times T + TC2 \times T^2, \tag{2.2}$$

where TCI and TC2 are 1<sup>st</sup> and 2<sup>nd</sup> order coefficients that are extracted with data fitting. The change of the thickness of depletion region between N<sup>+</sup> dopant region (SN area) and P-sub with applied voltage (V) will impact the effective sectional area of resistor, i.e. the resistance will change with the applied voltage. By using quadratic polynomial data fitting method, we get the relation of resistance with applied voltage.  $\Delta V$ - Factor as the voltage coefficient for resistance value is modeled,

$$\Delta V_{Factor} = 1 + VC1 \times V + VC2 \times V^2, \tag{2.3}$$

where VC1 and VC2 are 1<sup>st</sup> and 2<sup>nd</sup> order voltage coefficients that are extracted with data fitting. In summary, the temperature coefficient and voltage coefficient of a 10  $\mu$ m SN resistor are shown in Table 2-8.

Considering the above coefficients, the sheet resistance is  $R_{\bullet} = 52.21 \Omega$ .

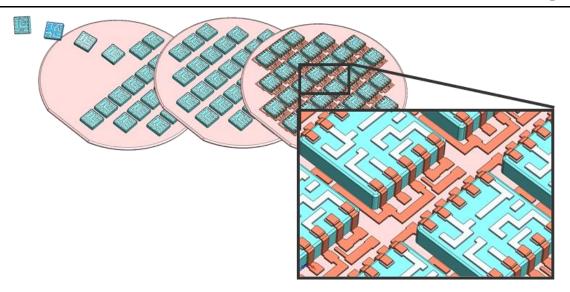

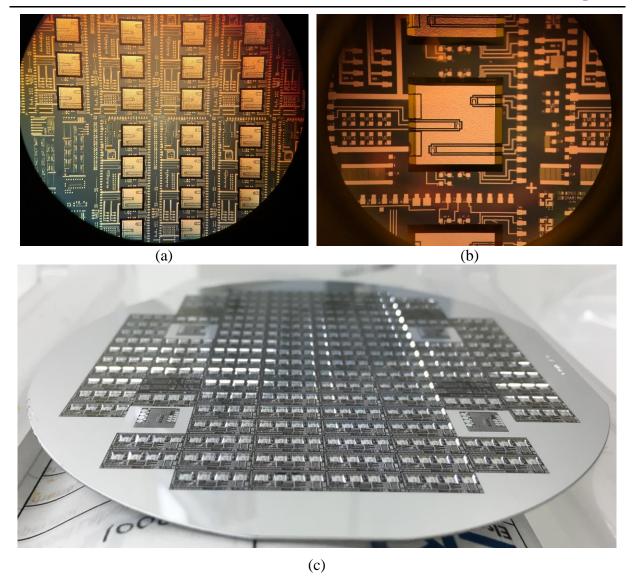

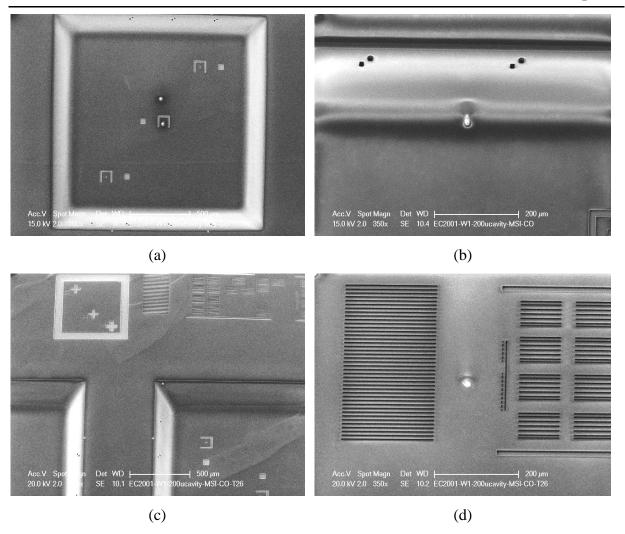

The models were later used for IC design. The wafers were split into two branches for different  $V_T$  adjust implantation parameters. Figure 2-14 shows a wafer in SMACK run through different BiCMOS7 steps. The details on achieved results will be presented in next chapters.

#### 2.6 Conclusions

In this chapter, the BICMOS5/7 process was introduced. It is a simple process that by just using 5-7 mask steps can monolithically implement different devices such as MOSFETs, BJTs,

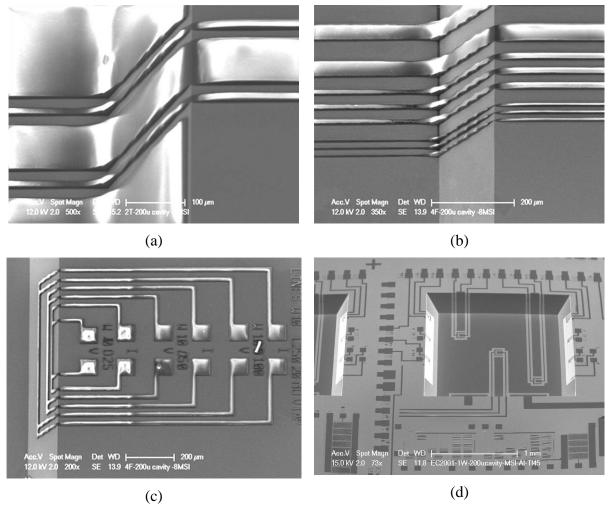

Figure 2-14: SMACK wafers through BiCMOS7 process run, (a) after NW, SN, and SP implantation, (b) with first metal pattern, (c) after VIA patterning, and (d) the complete wafer with second metal patterns.

diodes, and resistors. Due to large die size of LED chips, BiCMOS5/7 has a large potential to be utilized for WLP of smart LED systems. A design and fabrication framework based on BICMOS process was suggested. This framework covers the whole process from device modeling to system fabrication and measurements. It can be well applied for circuit design based on BiCMOS process. In addition, modeling of some of the devices used for smart LED package was discussed that will be later used in next chapters.

#### 2.7 References

- [1] "ISSCC Technology Trend," 2015.

- [2] N. S. Lawand, H. van Zeijl, P. J. French, J. J. Briaire, and J. H. M. Frijns, "Titanium nitride (TiN) as a gate material in BiCMOS devices for biomedical implants," in *IEEE Sensors*, 2013, pp. 1–4.

- [3] T. Ma, "Monolithic integration of light sensor readout system for multi-functional LED wafer-level packaging based on BICMOS process," TU Delft, 2014.

- [4] S. Enderling, C. L. Brown, S. Smith, M. H. Dicks, J. T. M. Stevenson, M. Mitkova, and M. N. Kozicki, "Sheet resistance measurement of non-standard cleanroom materials using suspended Greek cross test structures," *IEEE Trans. Semicond. Manuf.*, vol. 19, no. 1, pp. 2–9, 2006.

- [5] N. Stavitski, J. H. Klootwijk, H. W. van Zeijl, A. Y. Kovalgin, and R. A. M. Wolters, "Cross-Bridge Kelvin Resistor Structures for Reliable Measurement of Low Contact Resistances and Contact Interface Characterization," *IEEE Trans. Semicond. Manuf.*, vol. 22, no. 1, pp. 146–152, Feb. 2009.

### Silicon-Based Multi-Functional Wafer-Level-Package for LEDs<sup>4</sup>

Today, finding a low cost, efficient, functional and reliable solution for controlling smart lighting systems has become topic of many research groups and industry. In this chapter, design and fabrication of a multi-functional wafer level package (WLP) for phosphor-based white LED system using 7-mask BiCMOS process are discussed. This package integrates 4 high power blue LED dies with a temperature sensor and a blue selective light sensor for monitoring system performance. Each sensor has been designed, characterized and calibrated to be part of the smart monitoring unit. An interdigitated power transistor and a 4-bit flash analog-to-digital converter (ADC) were also monolithically integrated with sensors' readout and extra controlling functions.

#### 3.1 Introduction

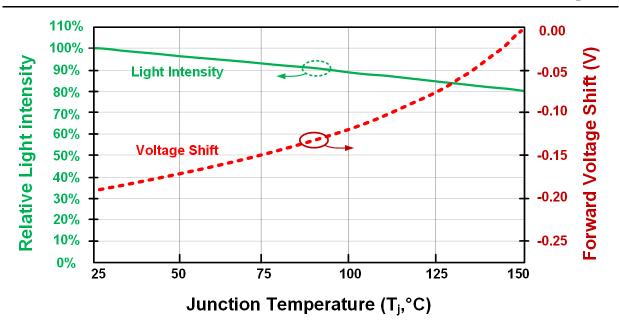

As LED technology is emerging dramatically in recent years, there are increasing demands for improving the luminous efficiency and lowering the cost for manufacturing industry. However, package reliability is still one of the main bottleneck for LED systems [1]. Specially for high power packages, high operating temperature can affect light intensity and color shifting over the time [2].

<sup>&</sup>lt;sup>4</sup> This chapter was partially presented in China SSL 2014. The more completed version is submitted as: Z. Kolahdouz, T. Ma, , H. van Zeijl, H. Abdy, M. Kolahdouz and G. Q. Zhang, "Silicon-Based Multi-Functional Wafer Level Package for LEDs in 7-Mask BiCMOS Process," to Sensors and Actuators A.

Introducing high power light emitting diodes (LEDs) was a key step for development of new application areas in lighting such as: sustainable lighting, general interior and exterior illumination, backlighting for displays, smart lighting (e.g. data transportation), indicators and signs, non-visual applications (communication), and transportation equipment lighting [3]–[6].

Among different methods of producing white light for general illumination applications, the most common approach for high power white LED source is the dichromatic method (also entitled as phosphor-based white method). It is a combination of a short wavelength LED, such as blue or UV, and phosphoric wavelength shifter. In the phosphor coating, a portion of photons are converted to yellow and the rest travel without any change. The light output is seen as a white light by human eyes [7]–[9]. This method shows good color rendering, long lifetime and acceptable reliability over the time comparing to so called trichromatic approaches [3], [7]. This concept is elaborated in more details in Chapter 4.

In addition to general illumination, blue and UV LEDs are progressively applied in medical and sensing applications [10]. Improving the system reliability in general and mainly for more sensitive areas motivates industry to develop more advanced lighting modules. Functional blocks like system monitoring units and innovative color control technology provide the ability to control and adjust the light intensity and color temperature (CT). So, integration of more functions and packaging configurations are some of the critical keys for reliable and efficient solutions for the modern lighting demands. Previously, many integrations were done in PCB level [11], [12]. However, silicon-based wafer level packaging can be one of the best promising approach considering cost, efficiency, functionality, design flexibility and uppermost reliability [13], [14].

Another concern is large heat dissipation in such a high power package. Silicon wafer-level-package (WLP) can be a good solution for thermal management and a cost effective integration [14]–[16]. Using silicon-based infrastructures, IC technologies, and MEMS toolset and processes allows us to integrate different functional sub-blocks on the same die.

Many groups formerly reported integrations of temperature and optical sensors for the most important parameters of such packages in wafer level [16]–[20]. Though, using silicon substrate gives us the opportunity to integrate more functional module such as controlling unit and the whole readout circuits.

To address such issues, a new monolithic silicon-based package is introduced which is realized in the 7-mask BiCMOS process. BiCMOS7 process can potentially implement a smart LED driver platform for the cost less than 1-2 \$/cm<sup>-2</sup> [20]. This process flow integrates monolithically the diodes, CMOS and BJT transistors all in just seven masks, which can simplify final package configuration. It is optimized for performance of different passive and active components. Final system will be a smart miniaturized LED WLP with two main functions: 1) system performance monitoring and 2) system controlling. The first function involves temperature sensors that monitor the package temperature. This data can be used for thermal management by controlling blocks or for further analysis. The monitoring function also includes blue selective photodiodes specially designed for the target LED wavelength that selectively detect the output blue light intensity. It provides very accurate brightness information of the mounted LED in the package. This photodiode is explained in depth in Chapter 4. The brightness information can be later used for a feedback control circuit to correct the intensity and color shifting of the output light [20]. The second function, system controlling, determines driving current of LEDs, which can be performed in either analog or digital ways. An analog control circuit is discussed in Chapter 5. A 4-bit flash ADC is also implemented for reading out sensor data. It can be used as a part of a digital control system. Next, a high current power switch is integrated for driving the LEDs. In this chapter the main blocks are discussed, which are the key elements for a full integrated smart silicon based LED platform.

Having different kinds of sensors in the same package with LED chips and readout circuits in a relatively low cost miniaturized module, can be an appropriate demonstrator for different applications such as biomedical diagnostic devices or other sensitive areas.

This chapter is organized as follows: in Section 3.2, design of the LED WLP is presented with explaining three main blocks: sensors, power transistor, and ADC. In Section 3.3 fabrication process is summarized with presenting the main steps of the 7-mask BiCMOS method. In Section 3.4, the implementation and measurement results are discussed. Finally, it will end by a short conclusion of this chapter.

#### 3.2 Design of LED Wafer Level Package

The package is designed as a high lumen output package integrating 4 BXCD 45 mil x 45

| Dimension           | 1143×1143×150 μm <sup>3</sup> |

|---------------------|-------------------------------|

| DC Forward current  | Max 700 mA                    |

| Reverse voltage     | 5V                            |

| Working temperature | -40 − 100 °C                  |

**Optical power (minimum)**

**Dominant wavelength**

340 mW

450-470 nm

Table 3-1: Specification of the target LED.

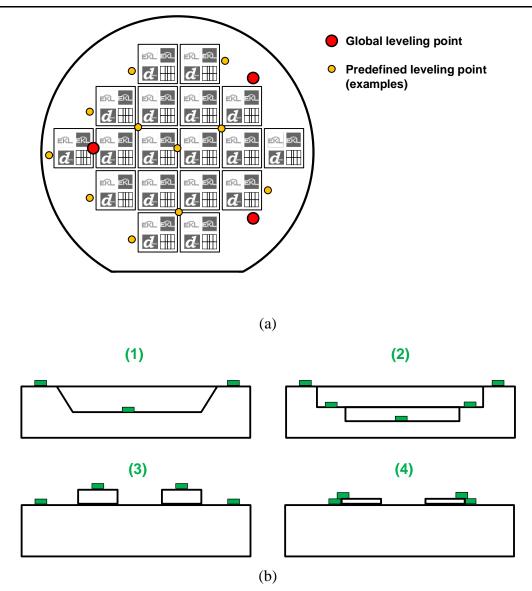

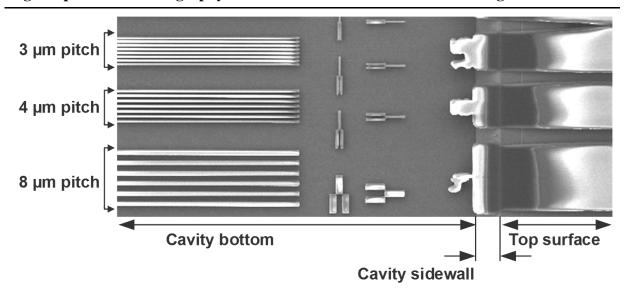

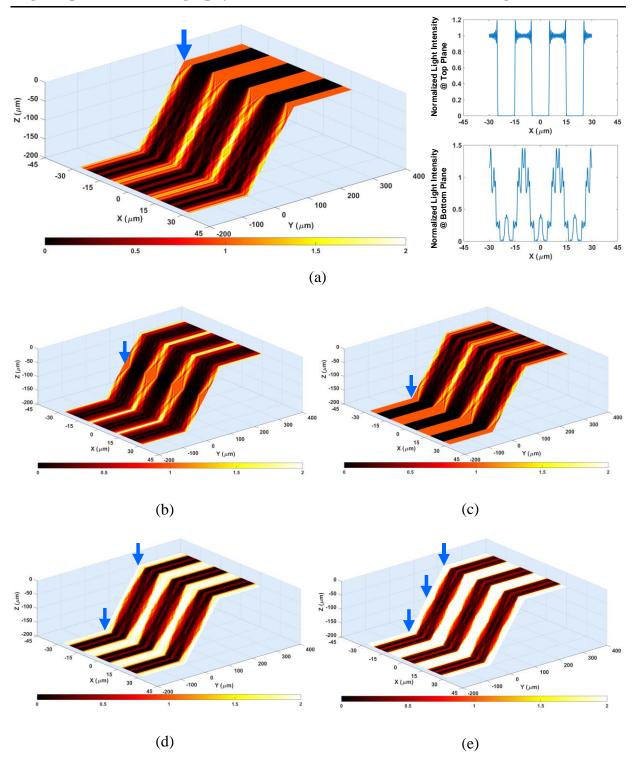

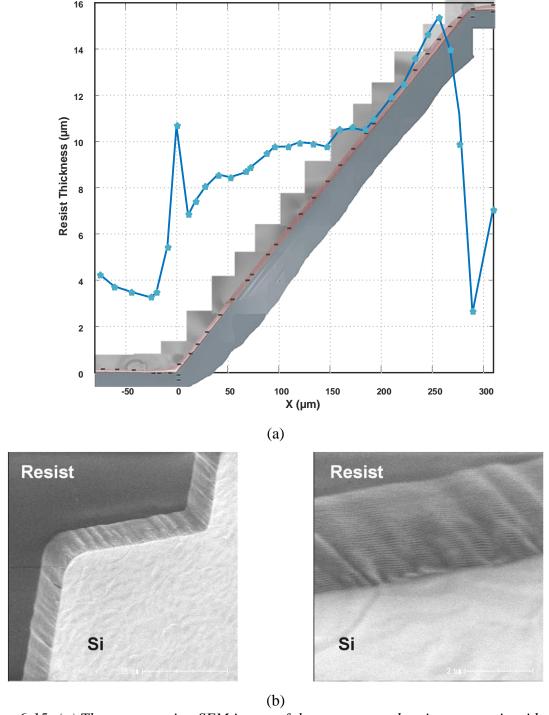

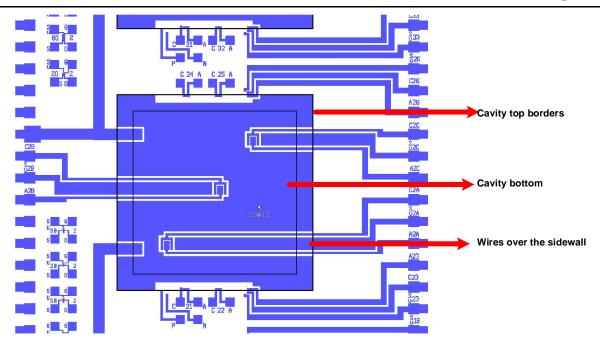

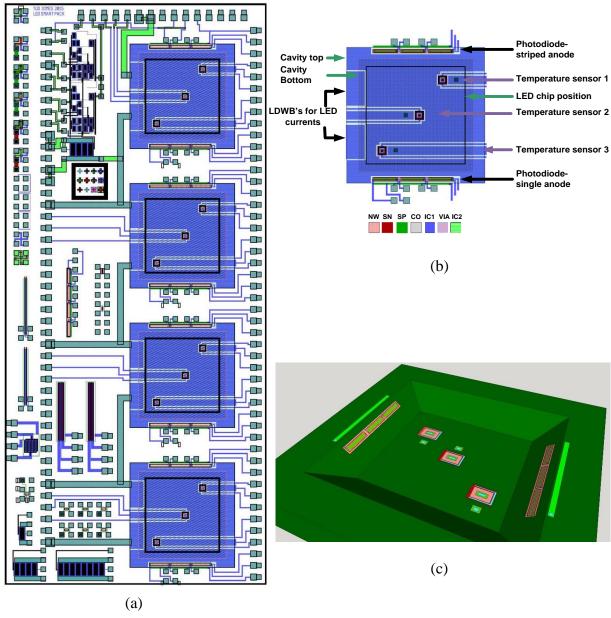

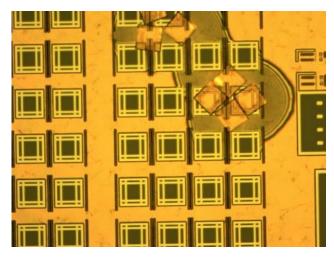

Figure 3-1: (a) Layout of the 2D LED WLP and (b) positions of different blocks.

mil Bridgelux<sup>®</sup> Blue Power Die. The complete die size is  $10\times10$  mm<sup>2</sup> including the test and main structures, but the main package is  $6\times10$ mm<sup>2</sup>. The design is such that 4 LEDs can be turned on in series with any combinations of 1 to 4. The target LED in this study is a vertical blue power die from Bridgelux<sup>®</sup>. Some of its specifications can be found in Table 3-1. These LEDs are useful in a broad range of applications such as general illumination, automotive lighting, and LCD backlighting [21].

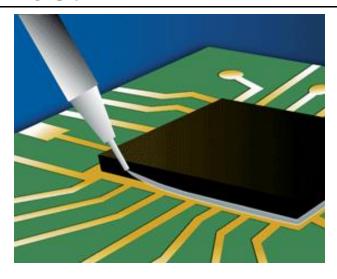

The whole design was manufactured using 2  $\mu$ m 7-mask BiCMOS process. This process was introduced in Chapter 2. Moreover, the relative low area costs for IC processing enable 2D integration of IC's with large area devices such as LED chips, in our case  $1.1\times1.1$  mm<sup>2</sup>. Figure 3-1(a) shows the complete die layout which monolithically integrated different components for the multifunctional LED system. Figure 3-1(b) demonstrates location of different blocks.

Figure 3-2: Schematic of (a) the temperature sensor and (b) the striped-shape photodiode with its equivalent circuit.

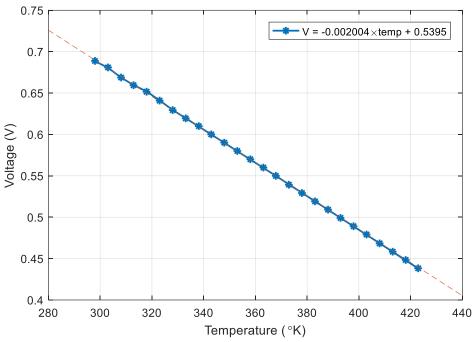

#### 3.2.1 Temperature and Light Sensors

To monitor the system performance, temperature and light sensing elements were integrated. For temperature sensing, 12 PNP dual junctions are located at different positions under the LED dies. It consists of a P<sup>+</sup> in an N-well (SP area) on a P-substrate as shown in Figure 3-2(a). The lower N-P junction is short-circuited to eliminate the effect of surrounding charges and upper P<sup>+</sup>-N junction is forward biased at constant current to evaluate the voltage as the temperature indicator.

For output light sensing, a blue selective photodiode was designed and fabricated which is schematically shown in Figure 3-2(b). These stripe-shaped dual junction photodiodes, with upper junction at 330 nm, demonstrated a very high selectivity to blue light. The maximum responsivity was achieved at 480nm which is matched with the blue LED's illumination [20].

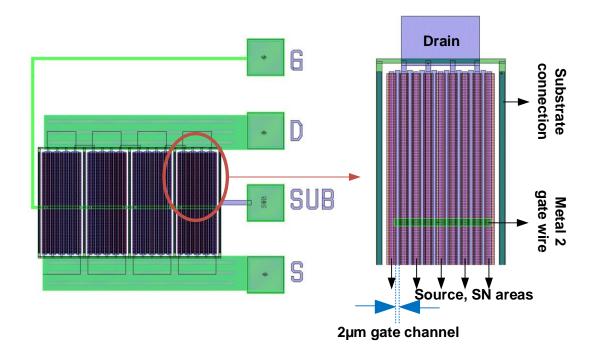

#### 3.2.2 Power Transistor

For switching LED driving current, NMOS power transistor with max 700 mA current was also integrated. For transistor, an interdigitated structure was used to improve area efficiency. As BiCMOS7 process has 2  $\mu$ m minimum feature size for implantation, the transistor channel length is set to 2  $\mu$ m. The source and drain, N<sup>+</sup> areas in the P-substrate called shallow-N (SN), were designed and manufactured as interdigitated finger-shaped structures in order to lower down the parasitic resistance in the channel and shrink the dimension. In this structure, four finger-shaped power transistors (W/L=1800 $\mu$ m/2 $\mu$ m) were connected in parallel in order to supply the required source current. It is schematically illustrated in Figure 3-3.

Figure 3-3: Layout of the power transistor comprising 4 parallel interdigitated transistors each with five source/drain fingers (360  $\mu$ m total width). The inset shows the magnified interdigit source and drain structure.

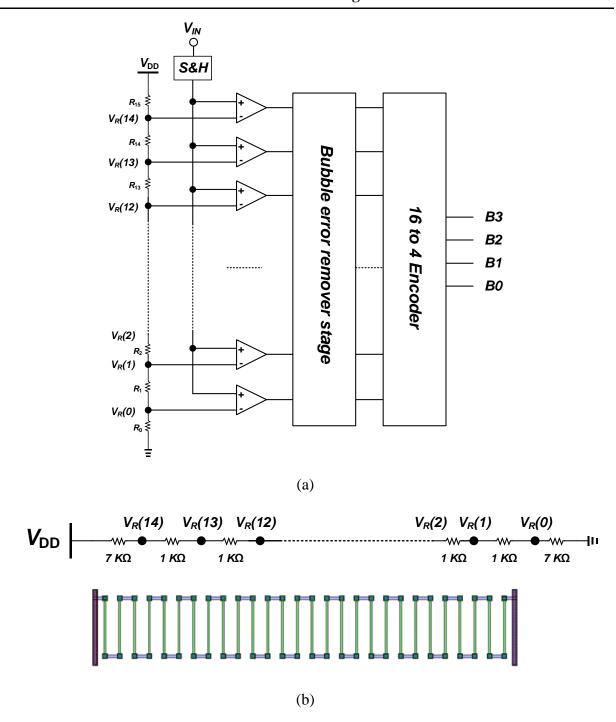

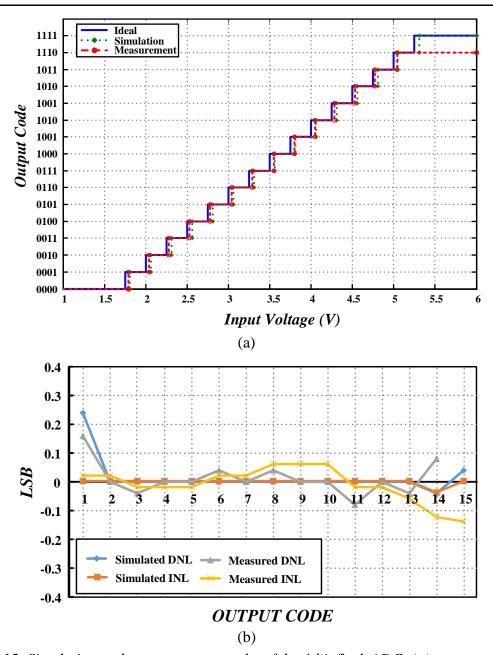

#### 3.2.3 Analog-to-Digital Converter

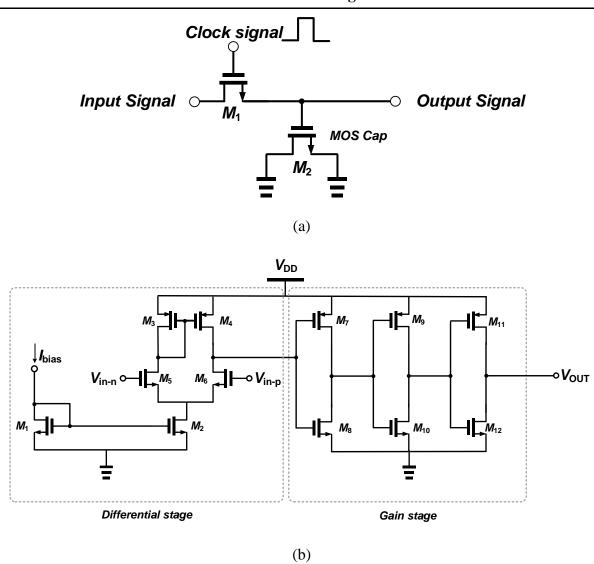

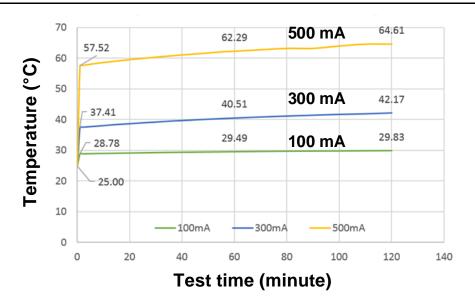

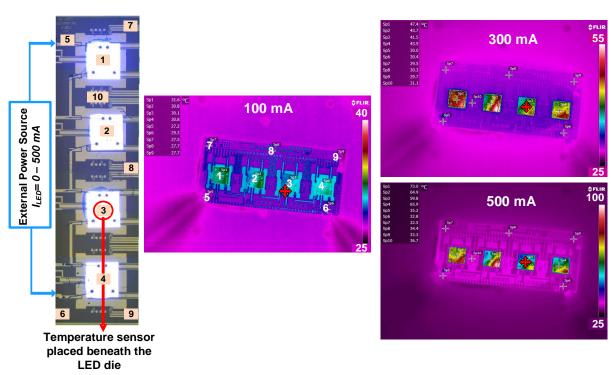

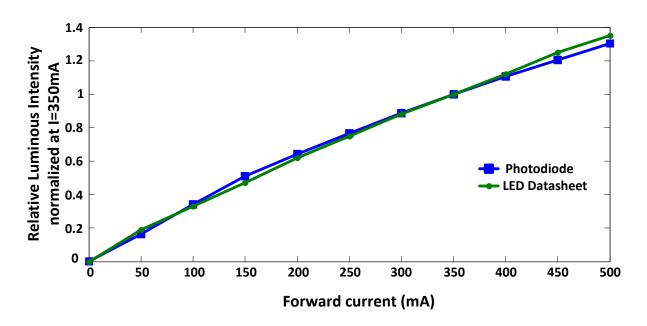

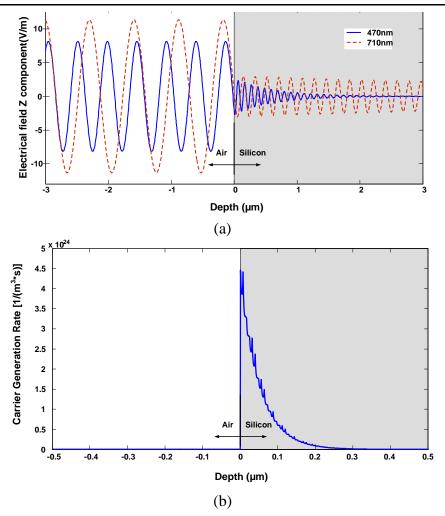

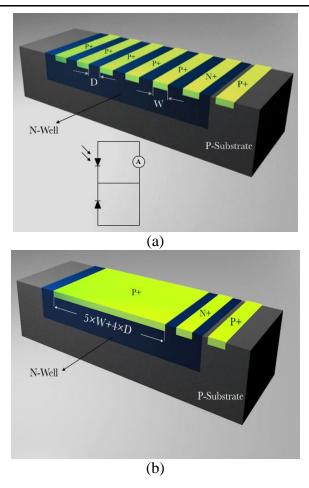

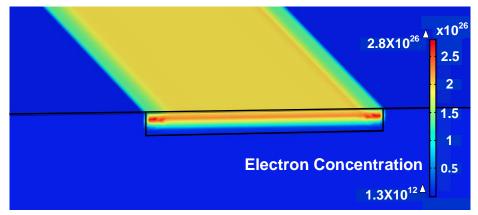

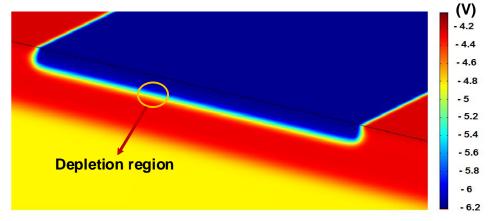

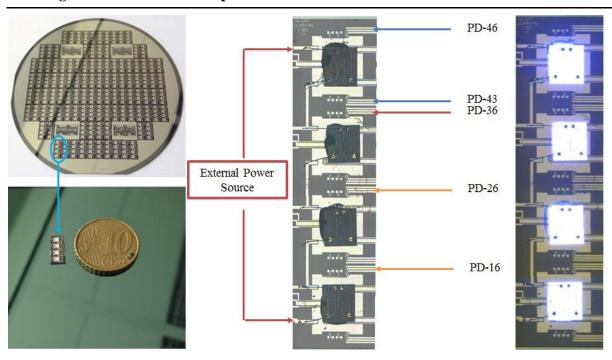

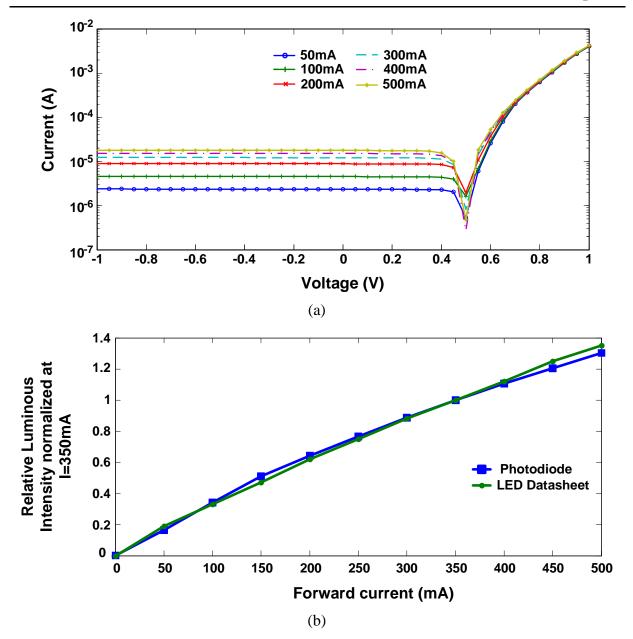

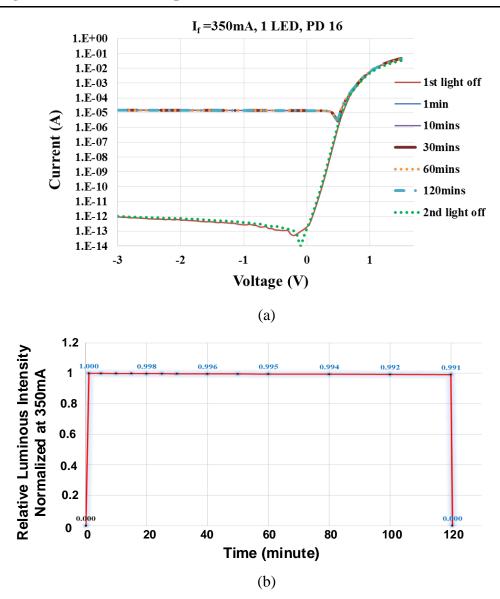

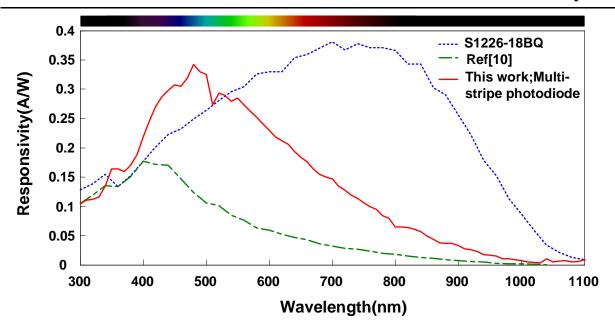

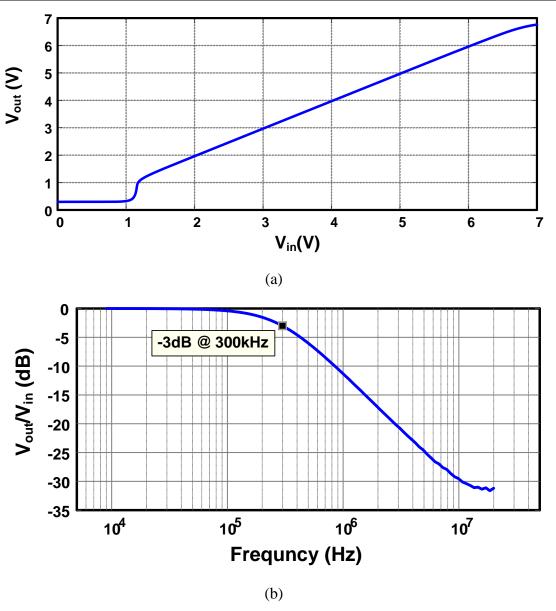

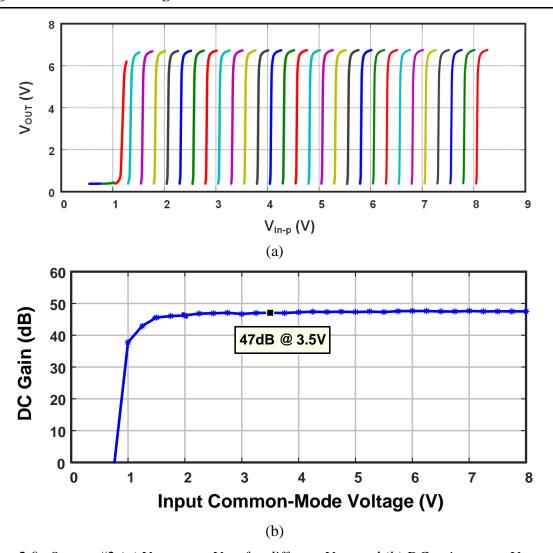

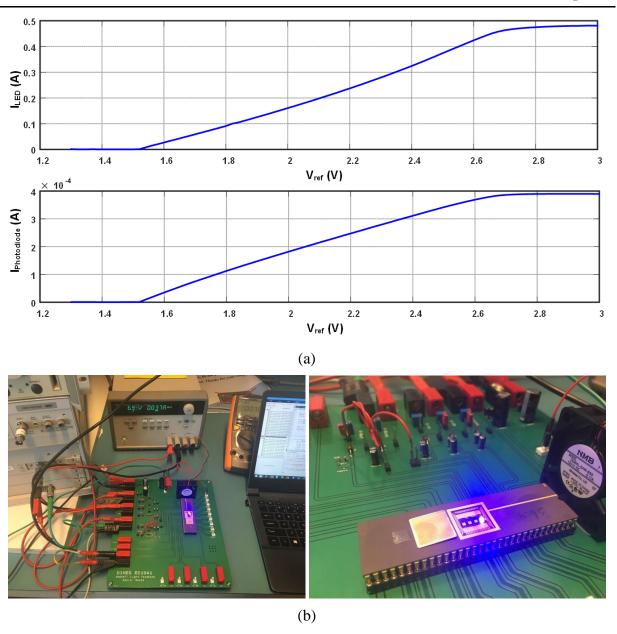

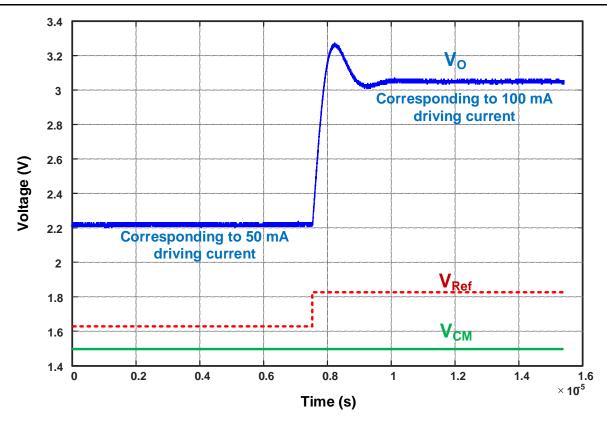

Having a complete BiCMOS run flow allows integration of some relevant logics for feedback and controlling units such as a 4-bit flash ADC combined with an operating amplifier for sensor readout circuit.