### M.Sc. Thesis

### Hardware Spiking Neural Network based Sbox AES

Hanyu Ma

#### Abstract

Hardware cryptographic algorithm implementation is easy to attack by side-channel attacks. The power-based side-channel attacks are powerful among several side-channel attacks. This attack methods use the relationship between the leakage model and power traces to reveal the secret key. Some existing countermeasures like mask and hide can protect the algorithms from attacking. However, they can not break the relationship between power traces and the leakage model. Based on the property of the neural network, the linear relationship can be easily broken. Furthermore, the spiking neural network is more hardware-friendly than a conventional neural network. The design replaces the sbox in AES with a pipeline spiking neural network-based sbox and implements it in hardware. The help of the FPGA attack platform demonstrates that the proposed design can resist DPA, CPA, Template Attacks, and Deep Learning-based attacks.

### Hardware Spiking Neural Network based Sbox AES

#### Thesis

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

MICROELECTRONIC

by

Hanyu Ma born in Wu Han, China

This work was performed in:

Circuits and Systems Group

Department of Microelectronics & Computer Engineering

Faculty of Electrical Engineering, Mathematics and Computer Science

Delft University of Technology

#### **Delft University of Technology**

Copyright  $\bigodot$  2021 Circuits and Systems Group All rights reserved.

# Delft University of Technology Department of Microelectronics & Computer Engineering

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled "Hardware Spiking Neural Network based Sbox AES" by Hanyu Ma in partial fulfillment of the requirements for the degree of Master of Science.

| Dated: My Graduation Date |                           |

|---------------------------|---------------------------|

| Chairman:                 | dr.ir. T.G.R.M van Leuker |

| Advisor:                  | dr.ir. David Aledo Ortega |

| Committee Members:        | dr.ir. Mottaqiallah Taoui |

|                           |                           |

### Abstract

Hardware cryptographic algorithm implementation is easy to attack by side-channel attacks. The power-based side-channel attacks are powerful among several side-channel attacks. This attack methods use the relationship between the leakage model and power traces to reveal the secret key. Some existing countermeasures like mask and hide can protect the algorithms from attacking. However, they can not break the relationship between power traces and the leakage model. Based on the property of the neural network, the linear relationship can be easily broken. Furthermore, the spiking neural network is more hardware-friendly than a conventional neural network. The design replaces the sbox in AES with a pipeline spiking neural network-based sbox and implements it in hardware. The help of the FPGA attack platform demonstrates that the proposed design can resist DPA, CPA, Template Attacks, and Deep Learning-based attacks.

# Acknowledgments

I would like to thank my advisor dr.ir. T.G.R.M van Leuken for his assistance during the writing of this thesis, and David who also gives many advice during project. And the Abdullah from CE group provides the experiment platform for me to do the side channel attack. Without them, this would not have been possible.

Hanyu Ma Delft, The Netherlands My Graduation Date

# Contents

| $\mathbf{A}$ | bstra | $\operatorname{\mathbf{ct}}$                                  | $\mathbf{v}$ |

|--------------|-------|---------------------------------------------------------------|--------------|

| $\mathbf{A}$ | cknov | wledgments                                                    | vii          |

| 1            | Intr  | oduction                                                      | 1            |

|              | 1.1   | Motivation                                                    | 1            |

|              | 1.2   | Goal                                                          | 2            |

|              | 1.3   | Methodology                                                   | 2            |

|              | 1.4   | Contribution                                                  | 2            |

|              | 1.5   | Thesis Outline                                                | 2            |

| 2            | Bac   | kground of Advanced Encryption Standard and Power based Side- |              |

|              | cha   | nnel Attacks                                                  | 5            |

|              | 2.1   | Advanced Encryption Standard                                  | 5            |

|              |       | 2.1.1 Round transformation                                    | 5            |

|              | 2.2   | Power Analysis Attacks                                        | 9            |

|              |       | 2.2.1 Non-Profiled Attacks                                    | 10           |

|              |       | 2.2.2 Profiled Attacks                                        | 17           |

|              |       | 2.2.3 Deep Learning-based Side Channel Attack                 | 20           |

|              | 2.3   | Countermeasures                                               | 21           |

|              |       | 2.3.1 Hide                                                    | 22           |

|              |       | 2.3.2 Mask                                                    | 23           |

| 3            | Bac   | kground of Spiking Neural Network                             | <b>25</b>    |

|              | 3.1   | Artificial Neural Network                                     | 25           |

|              | 3.2   | Spiking Neural Network                                        | 26           |

|              |       | 3.2.1 Neuron Model                                            | 26           |

|              |       | 3.2.2 Spike Encoding                                          | 28           |

|              |       | 3.2.3 SNN Learning Method                                     | 30           |

|              |       | 3.2.4 SNN Hardware Implementation                             | 30           |

| 4            | Spil  | king Neural Network Simulator Implementation                  | 33           |

|              | 4.1   | Spiking Neural Network Software Implementation                | 33           |

|              | 4.2   | Bindsnet implementation                                       | 34           |

|              |       | 4.2.1 ANN                                                     | 35           |

|              |       | 4.2.2 ANN to SNN conversion                                   | 36           |

|              | 4.3   | SpikingJelly implementation                                   | 38           |

|              |       | 4.3.1 Sbox spiking neural network                             | 38           |

|              | 4.4   | Comparison                                                    | 39           |

| <b>5</b> | Spil | ing Neural Network Hardware Implementation | 41 |

|----------|------|--------------------------------------------|----|

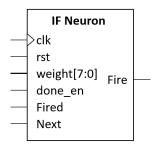

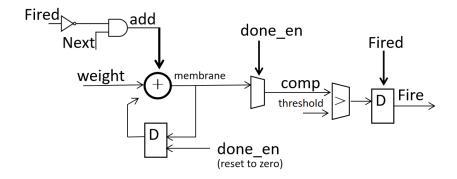

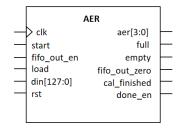

|          | 5.1  | IF Neuron model                            | 41 |

|          |      | 5.1.1 Model adaptation                     | 41 |

|          |      | 5.1.2 Architecture                         | 42 |

|          |      | 5.1.3 Simulation                           | 43 |

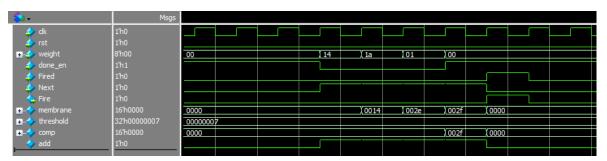

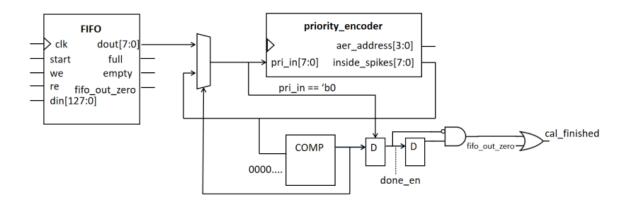

|          | 5.2  | AER protocol                               | 43 |

|          |      | 5.2.1 Design and Architecture              | 44 |

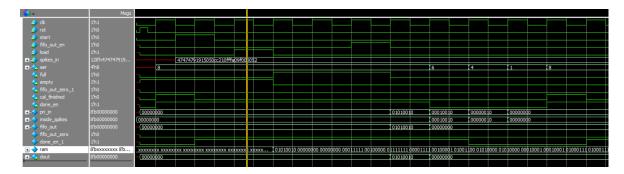

|          |      | 5.2.2 Simulations                          | 46 |

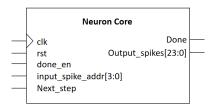

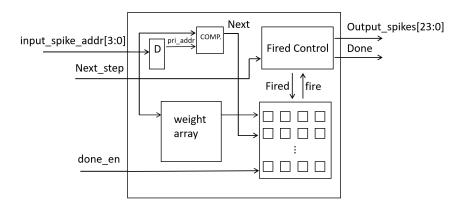

|          | 5.3  | Neuron Core                                | 47 |

|          |      | 5.3.1 Design and architecture              | 47 |

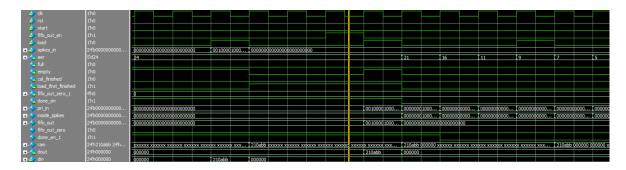

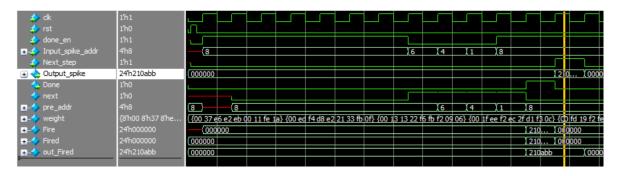

|          |      | 5.3.2 Simulation                           | 49 |

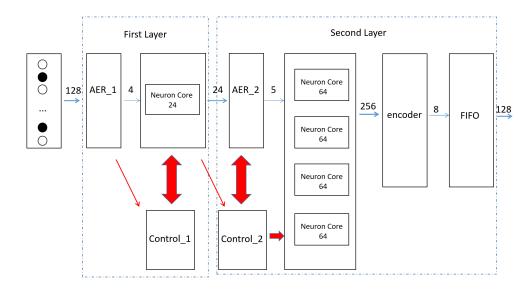

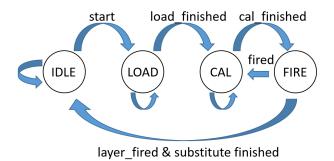

|          | 5.4  | SNN Emulation                              | 49 |

|          |      | 5.4.1 Design and Architecture              | 49 |

|          |      | 5.4.2 Simulation                           | 52 |

| 6        | Exp  | eriment                                    | 53 |

|          | 6.1  | Platform                                   | 53 |

|          | 6.2  | SNN Sbox Power Analysis                    | 55 |

|          |      | 6.2.1 Classical 1-bit DPA                  | 55 |

|          |      | 6.2.2 CPA                                  | 56 |

|          |      | 6.2.3 Template Attack                      | 57 |

|          |      | 6.2.4 DLSCA                                | 58 |

|          | 6.3  | Performance Analysis and Comparison        | 59 |

| 7        | Cor  | clusion and Future Work                    | 61 |

|          | 7.1  | Conclusion                                 | 61 |

|          | 7.2  | Future Work                                | 62 |

# List of Figures

| 2.1  | The AES workflow and the key expansion [52]                                  | 6          |

|------|------------------------------------------------------------------------------|------------|

| 2.2  | The Sbox look up table contains the 256 cases conversion [55]                | 7          |

| 2.3  | In the SubBytes step, each bytes in the array is substituted with the        |            |

|      | corresponding value in the sbox LUT [55]                                     | 7          |

| 2.4  | In the ShiftRows step, bytes in each row of the array are shifted cyclically |            |

|      | to the left [55]                                                             | 8          |

| 2.5  | In the MixColumns step, each column of the array is multiplied with a        |            |

|      | fixed polynomial [55]                                                        | 8          |

| 2.6  | The KeyExpansion involves the XOR operations and g function [18]             | 9          |

| 2.7  | Power consumption of the AES encryption[37]                                  | 11         |

| 2.8  | square-and-multiply RSA implementation[37]                                   | 11         |

| 2.9  | Difference plots for the key guesses[37]                                     | 12         |

| 2.10 | Correlation result for 7-bit subkey [38]                                     | 16         |

| 2.11 | The Gaussian Distribution indicates the possibility density distribution     |            |

|      |                                                                              | 17         |

| 2.12 | Points of Interest [50]                                                      | 19         |

| 2.13 | CNN procedure for intermediate value [29]                                    | 21         |

| 0.1  | A .: C : 1 NT                                                                | ٠-         |

| 3.1  | [ ]                                                                          | 25         |

| 3.2  |                                                                              | 26         |

| 3.3  | 0 , [ ]                                                                      | 27         |

| 3.4  | The action potential the fire period, refractory period, and the reset       | <b>3</b> 0 |

| 2.5  |                                                                              | 28         |

| 3.5  | r 1                                                                          | 28         |

| 3.6  | 0 [ ]                                                                        | 29         |

| 3.7  | Biological observation of STDP weight change [5]                             | 30         |

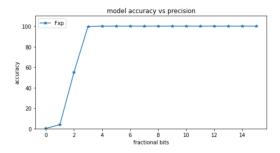

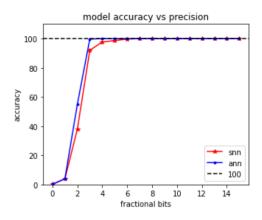

| 4.1  | Different Fractional Bits Accuracy                                           | 36         |

| 4.2  |                                                                              | 37         |

| 4.3  |                                                                              | 37         |

| 4.4  |                                                                              | 39         |

| 4.5  | ·                                                                            | 39         |

|      |                                                                              |            |

| 5.1  | 0                                                                            | 12         |

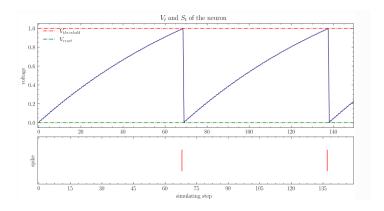

| 5.2  |                                                                              | 13         |

| 5.3  |                                                                              | 13         |

| 5.4  | 0                                                                            | 14         |

| 5.5  |                                                                              | 15         |

| 5.6  |                                                                              | 16         |

| 5.7  | v                                                                            | 17         |

| 5.8  | v                                                                            | 17         |

| 5.9  |                                                                              | 18         |

| 5.10 | Digital block of Neuron Core Schematic                                       | 18         |

| 5.11 | Neuron Core simulation                                  | 49 |

|------|---------------------------------------------------------|----|

| 5.12 | Digital block of SNN Schematic                          | 50 |

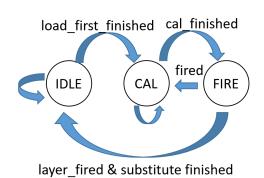

| 5.13 | First Layer Control State                               | 51 |

| 5.14 | Second Layer Control State                              | 51 |

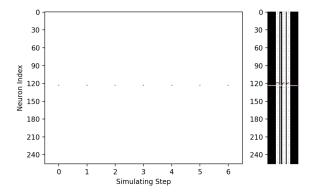

| 5.15 | First Layer Spike Simulation                            | 52 |

|      | Second Layer Spike Simulation                           | 52 |

| 5.17 | Substitute Result                                       | 52 |

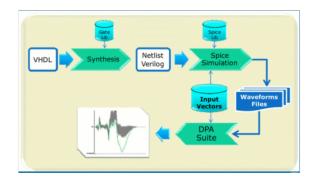

| 6.1  | The DPA work flow of Spice model [19]                   | 53 |

| 6.2  | Chipwhisperer-Lite tool                                 | 54 |

| 6.3  | CW305 FPGA Board                                        | 54 |

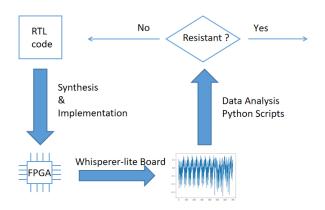

| 6.4  | Experiment Flowchart                                    | 54 |

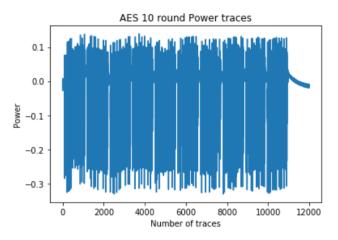

| 6.5  | AES Power Traces                                        | 55 |

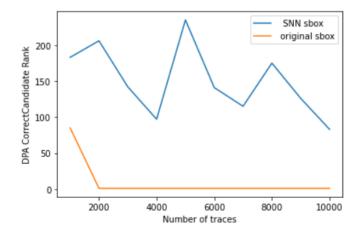

| 6.6  | DPA Rank Analysis(original vs SNN)                      | 56 |

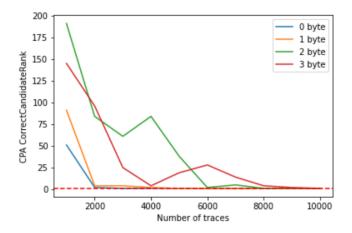

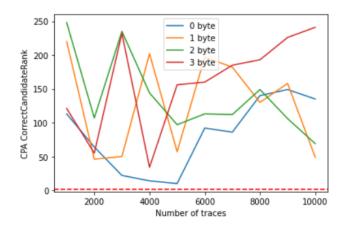

| 6.7  | Unprotected Original Sbox CPA Rank Analysis             | 56 |

| 6.8  | Protected SNN Sbox CPA Rank Analysis                    | 57 |

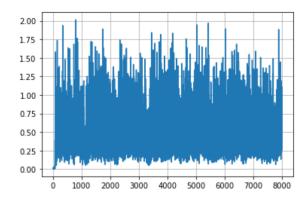

| 6.9  | Template Attack Points of Interest                      | 57 |

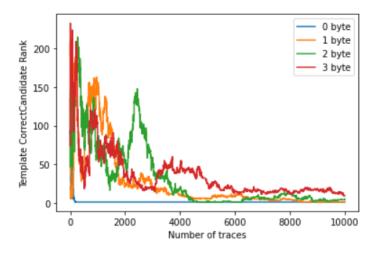

| 6.10 | Unprotected Original Sbox Template Attack Rank Analysis | 58 |

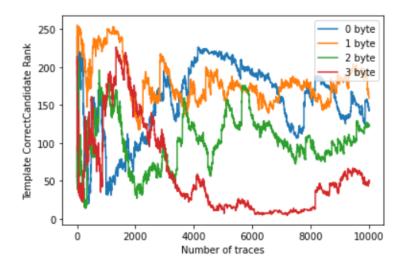

| 6.11 | Protected SNN Sbox Template Attack Rank Analysis        | 58 |

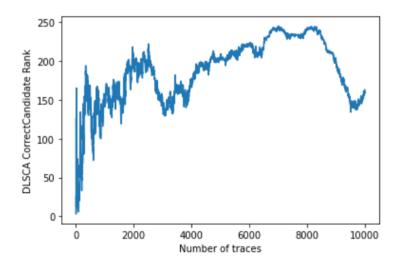

| 6.12 | SNN Sbox DLSCA Rank Analysis                            | 59 |

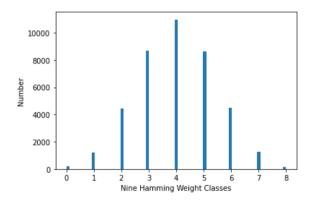

| 6.13 | The Distribution of Nine Input Classes                  | 60 |

# List of Tables

|     | Power Analysis Attacks List                 |    |

|-----|---------------------------------------------|----|

| 3.1 | State of the art digital SNN implementation | 31 |

|     | Sbox Artificial Neural Network              |    |

|     | SNN based Sbox AES Hardware Resources       |    |

### Nomenclature

#### Physics Symbol

C Capacitance R Resistance

t Time

#### Mathematical Symbol

$\sum_{a}^{b}$  mathematical sum

$\begin{array}{ccc}

\oplus & & \text{Xor function} \\

\frac{dx}{dy} & & \text{Derivation}

\end{array}$

$GF(2^n)$  The finite field of two elements

$[]_{i,j}$  Entry (i,j) of matrix

$\mu$  The mean of amount of numbers  $g_{i,j}$  The pearson's correlation function

#### Other Symbol

G The array of pearson's correlation coefficient array

S The hypothetical Sbox result array

H The hypothetical leakage model result array

The collected power traces array

P The plaintext array

f(x) The probability density distribution function

$c_i, j$  The covariance function

Introduction

#### 1.1 Motivation

The development of computers, the Internet, and communications make the world becomes a highly digital information world in today's technology. The increasing reliance on technology is also a double-edged sword, as they give a chance for the attacker to get the data by various attack methods. It is becoming more and more essential to secure every aspect of information and data. Encryption is a way of scrambling data so that only authorized parties can understand the information preventing people from economic, reputation, and privacy loss. However, encryption can not guarantee safety due to thousands of attackers in the real world. This leads to the demand for countermeasures and resistive attack methods.

There are already many encryption algorithms in the encryption field. And this research focuses on the advanced encryption standard(AES)[18], also known by its original name Rijndael. It is symmetric key encryption that is implemented in software and hardware throughout the world to encrypt sensitive data.

While some attacks can be protected by software-based security, they cannot defend from all attacks. For example, a device is used for data transmission, but if the attacker gets access to the physical device, then no amount of software routine can provide protection. Thus, this is where hardware security comes in and why it is becoming increasingly popular with SoCs, microcontrollers, and microprocessors.

However, even the system equipped with hardware security is also vulnerable to side-channel attacks(SCA)[32]. SCA takes advantage of patterns in the information exhaust that hardware constantly gives off: power[32], time[17], radiation[35], noise[4], etc. The attacks can recover the encryption key without any expensive tools. Furthermore, attackers can perform SCA even when they can not access the device. Thus, an effective countermeasure against SCA is becoming a hot topic recently.

Comparing with other SCA, power-based SCA has the advantage of less sensitivity to noise, easy implementation, and focusing on the point of attack. Power-based SCA has been proved the most powerful and attractive to many attackers. In different abstraction levels in devices, different countermeasures against power-based SCA have been implemented. And those of them are proven to be different degrees of success with the cost of the area, power, speed, etc.

Therefore, this thesis focuses on the countermeasures against power-based SCA in AES. In AES, the attackers can easily get the Hamming Weight or Distance model from substitute phases (S-box). The other phases will give out less information even uses good models. So the S-box is the weakest point because of the correlation between power consumption and the leaky model. In order to break out the correlation between those two, [54] already replaced the sbox with conventional neural network sbox in

software. We introduce the spiking neural network into AES for hardware. Exploration of hardware security while using artificial intelligence methods such as spiking neuron networks to improve the resistibility of hardware AES and power efficiency.

#### 1.2 Goal

The neural network based sbox can protect the AES from side channel attack has been demonstrated by [54]. However, not all types of neural network can achieve the task. In this thesis, we want to demonstrate the spiking neural network can protect the AES in hardware aspect and find its advantages.

#### 1.3 Methodology

- 1. Find a suitable spiking neural network simulator to train the network properly.

- 2. Building a hardware single spike neuron hardware spiking neuron network to substitute the S-box inside AES. The input information going through the S-box would be encoded by clock-driven coding to decrease the spikes amount.

- 3. The SNN architecture consists of several neuron cores which use AER communication protocol to improve performance.

- 4. In order to do the side-channel attack. To synthesize the digital implementation and use the chipwhisperer simulation tool to get the power waveforms, and perform DPA and CPA side-channel attacks on the proposed SNN with trained weight.

#### 1.4 Contribution

The contribution of this thesis work are following:

- Encoding the dataset input and then obtain the corresponding values from the simulator. Furthermore, design the digital hardware machine learning spiking neural network RTL model for S-box.

- Instead of using the Spice model to get the power traces, I choose to implement the model on FPGA. The power traces collected from the FPGA can be easily analyzed using Differential Power Analysis(DPA) and Correlation Power Analysis.

#### 1.5 Thesis Outline

- Chapter 2 introduces the background of side-channel attacks and the details of the implementation methods.

- Chapter 3 introduces the overview of spiking neural networks in spike representation, neural model, communication methods, and weight memory mapping.

- Chapter 4 presents the details of the implementation of the proposed spiking neural networks in simulator.

- Chapter 5 presents the details of the hardware design of the proposed spiking neural network.

- Chapter 6 presents the implementation of the test model and an evaluation of the results.

- Chapter 7 presents the conclusion from the above implementation and the future works needs to be done.

# Background of Advanced Encryption Standard and Power based Side-channel Attacks

In this chapter, the Advanced Encryption Standard (AES) details are described to understand the most popular encryption algorithm. Furthermore, the power-based side-channel attacks, which are very powerful to attack the AES, are introduced to prepare for the experiment. Finally, the state-of-art countermeasures to power-based side-channel attacks are listed for comparison with the thesis's countermeasure.

#### 2.1 Advanced Encryption Standard

AES (Advanced Encryption Standard) is a symmetric key block cipher based on substitution—permutation network. It comprises a series of linked operations, some involving replacing inputs with specific outputs (substitutions) and others shuffling bits around (permutations). The data packet length must be 128 bits, and the key length used is 128, 192, or 256 bits. The number of rounds is different with the key length, 10 rounds for 128 bits keys, 12 rounds for 192 bits keys, and 14 rounds for 256 bits keys. The three AES algorithms with different key lengths are called "AES-128", "AES-192", and "AES-256" respectively. The target in this thesis is "AES-128".

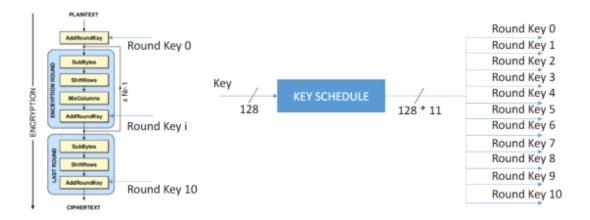

The AES encryption transformation function does not have the Feistel structure. Instead, the round transformation comprises three distinct invertible uniform transformations. The linear mixing layer, the non-linear layer, the key addition layer. With exception of the last round, each round transformation involves four operations: **Sub-Bytes**, **ShiftRows**, **MixColumns**, and **AddRoundKey**. The decryption process is the corresponding reverse operation. Since each operation is reversible, the plaintext can be recovered by decrypting in the reverse order. The key for each round of encryption and decryption is obtained by the initial **KeyExpansion**. The workflow is shown in Figure 2.1 [18].

Interestingly, the AES treats bytes level, representing the finite field GF(2<sup>8</sup>) rather than the bits level. AES ranges the 128 bits data into 4-byte words, which can form the intermediate cipher result, also called State. Each column has 32 bits. The cipher key is a rectangular matrix with four rows. Furthermore, after round transformation, the array will create a same-type array for the next round.

#### 2.1.1 Round transformation

In order to execute an available attack, it is necessary to understand the details of the AES algorithms. The central part inside the AES is the round transformation

Figure 2.1: The AES workflow and the key expansion [52].

which contains four different operations. As mentioned above, every round has four operations, but the last round does not have the MixColumns step.

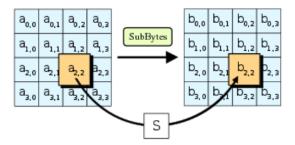

#### 2.1.1.1 SubBytes

The SubByte transformation is the unique layer that is the only non-linear byte substitution, operating on each state byte independently. The function is invertible and constructed by the following two functions [8].

- First, Implementing multiplicative inverse to state in  $GF(2^8)$  using an irreducible polynomial  $(x^8 + x^4 + x^3 + x + 1)$ .

- An affine transformation will then apply on the inverse state over GF(2).

Considered the actual memory and computation complexity, storing the result as a lookup table(LUT) in the memory like Figure 2.2 can decrease the computation complexity but bring the memory storage problem. Figure 2.3 can better explain the subbytes process.

As mentioned before, S-box has good non-linear properties and is resistant to linear and differential cryptanalysis. However, the attacker can still create a leakage model using the power traces from the device to crack the key. Instead of using the LUT, the multiplication with two can be implemented with a shift and conditional exor. In a straightforward implementation, the execution time of this operation will depend on the input value. This may allow an attacker to mount a timing attack. Insert a NOP-operations can make the execution time equal. Nevertheless, introduce the weakness of the power analysis attack. So the use of a LUT effectively counters these types of attacks.

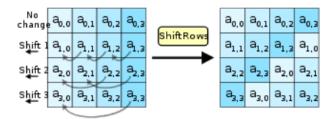

#### 2.1.1.2 ShiftRows

ShiftRows is easier to understand and more direct. The idea of shift rows is to shift the position of states to make a more diffusion array. Figure 2.4 helps to provide a visual operation.

|    | 0  | 1  | 2  | 3          | 4  | 5  | 6  | 7  | 8  | 9  | 0a | 0b | 0c | Od | 0e | Of |

|----|----|----|----|------------|----|----|----|----|----|----|----|----|----|----|----|----|

| 0  | 63 | 7c | 77 | 7b         | f2 | 6b | 6f | c5 | 30 | 1  | 67 | 2b | fe | d7 | ab | 76 |

| 10 | ca | 82 | c9 | 7d         | fa | 59 | 47 | f0 | ad | d4 | a2 | af | 9c | a4 | 72 | c0 |

| 20 | b7 | fd | 93 | 26         | 36 | 3f | f7 | СС | 34 | a5 | e5 | f1 | 71 | d8 | 31 | 15 |

| 30 | 4  | c7 | 23 | c3         | 18 | 96 | 5  | 9a | 7  | 12 | 80 | e2 | eb | 27 | b2 | 75 |

| 40 | 9  | 83 | 2c | <b>1</b> a | 1b | 6e | 5a | a0 | 52 | 3b | d6 | b3 | 29 | e3 | 2f | 84 |

| 50 | 53 | d1 | 0  | ed         | 20 | fc | b1 | 5b | 6a | cb | be | 39 | 4a | 4c | 58 | cf |

| 60 | d0 | ef | aa | fb         | 43 | 4d | 33 | 85 | 45 | f9 | 2  | 7f | 50 | 3c | 9f | a8 |

| 70 | 51 | a3 | 40 | 8f         | 92 | 9d | 38 | f5 | bc | b6 | da | 21 | 10 | ff | f3 | d2 |

| 80 | cd | 0c | 13 | ec         | 5f | 97 | 44 | 17 | c4 | a7 | 7e | 3d | 64 | 5d | 19 | 73 |

| 90 | 60 | 81 | 4f | dc         | 22 | 2a | 90 | 88 | 46 | ee | b8 | 14 | de | 5e | Ob | db |

| a0 | e0 | 32 | 3a | 0a         | 49 | 6  | 24 | 5c | c2 | d3 | ac | 62 | 91 | 95 | e4 | 79 |

| b0 | e7 | с8 | 37 | 6d         | 8d | d5 | 4e | a9 | 6c | 56 | f4 | ea | 65 | 7a | ae | 8  |

| c0 | ba | 78 | 25 | 2e         | 1c | a6 | b4 | сб | e8 | dd | 74 | 1f | 4b | bd | 8b | 8a |

| d0 | 70 | 3e | b5 | 66         | 48 | 3  | f6 | 0e | 61 | 35 | 57 | b9 | 86 | c1 | 1d | 9e |

| e0 | e1 | f8 | 98 | 11         | 69 | d9 | 8e | 94 | 9b | 1e | 87 | e9 | ce | 55 | 28 | df |

| fO | 8c | a1 | 89 | Od         | bf | е6 | 42 | 68 | 41 | 99 | 2d | Of | b0 | 54 | bb | 16 |

Figure 2.2: The Sbox look up table contains the 256 cases conversion [55].

Figure 2.3: In the SubBytes step, each bytes in the array is substituted with the corresponding value in the sbox LUT [55].

Bytes in the state matrix will shift following a standard. The first row will stay still. The second row will shift to the left by one, in the third by two, and in the fourth by three, illustrated in Figure 2.4.

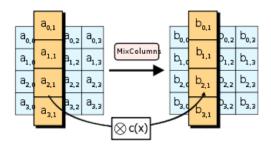

#### 2.1.1.3 MixColumns

In short, MixColumns is a linear transformation of the array. It contains matrix multiplication and bitwise XOR operation. The addition and multiplication will perform over GF(2<sup>8</sup>) like Equation 1.1. The multiplication will be performed on the result matrix of ShiftRows. It must be noted that all the columns of the matrix will perform this function. Moreover, the result matrix will have the same size as the original one. Figure 2.5 shows the MixColumns process.

$$\begin{bmatrix}

b_0 \\

b_1 \\

b_2 \\

b_3

\end{bmatrix} = \begin{bmatrix}

2 & 3 & 1 & 1 \\

1 & 2 & 3 & 1 \\

1 & 1 & 2 & 3 \\

3 & 1 & 1 & 2

\end{bmatrix} \begin{bmatrix}

a_0 \\

a_1 \\

a_2 \\

a_3

\end{bmatrix}$$

(1.1)

Figure 2.4: In the ShiftRows step, bytes in each row of the array are shifted cyclically to the left [55].

Figure 2.5: In the MixColumns step, each column of the array is multiplied with a fixed polynomial [55].

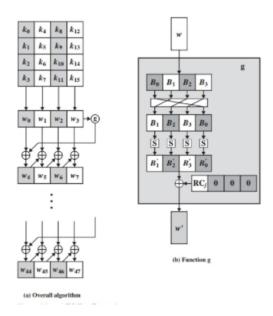

#### 2.1.1.4 KeyExpansion and AddRoundKey

The AES will perform Addroundkey at the beginning. In other words, the plaintext will do bitwise xor with the original key. In the round transformation, Addroundkey will apply a key expansion process to generate the round keys.

The AES key expansion algorithm inputs a four-word (16-byte) key and produces a linear array of 44 words (176 bytes). That key is sufficient to provide a four-word round key for the initial AddRoundKey stage. The expansion key algorithm is resistant to known cipher analytic attacks. The key will be divided into four 32bits words. Each added word w[i] depends on the immediately preceding words. The word whose position is a multiple of 4, a g function is used. The other words will perform XOR operations. Figure 2.6 describes the generation of the key and the g function. The key expansion can be done beforehand to enhance the operations, and Rijndael can be specified in terms of this expanded key.

Moreover, AES performance in software is low unless performance-optimized implementations are used like T-tables (precomputed tables and require memory). The large key size makes it hard for an attacker to use a brute force attack. However, those cryptographic devices still leak some side-channel information that the attacker can obtain to decipher the secret.

Figure 2.6: The KeyExpansion involves the XOR operations and g function [18].

#### 2.2 Power Analysis Attacks

As has been mentioned above, AES is the standard algorithm to protect the device from attack. In recent years, several attack methods have stood out. Their primary goal is to reveal the key inside the device. The implementation measures are various. Based on the different categories standard, the attack measures can have several different categories. The most straightforward criterion is the Passive and Active. As the name suggests, the Passive way reveals the secret key by measuring the physical properties of the cryptographic devices. The device usually leaks execution time information, power consumption information, and memory cache information when the device works. When the attacker performs an Active attack, they typically put some special input data and manipulate the environment to make it unusual. The abnormal information can reveal the secret key. This thesis aim at power analysis attack. Due to the easy implementation methods, the power attack analysis is prevalent and powerful to those standard security algorithms. It brings a threat to many cryptographic devices. From the reliability view and security side, it is essential to give more attention to the power consumption at the hardware register level.

The instant power consumption of a device depends on two factors which are data-dependency and operation-dependency [37]. The digital circuit consists of many CMOS inverters, which consist of transistors. The power consumption of an inverter consists of two parts which are the static power consumption  $P_{stat}$  and dynamic power consumption  $P_{dyn}.P_{stat}$  is typically very low. However, with the growth of the modern process technologies,  $P_{stat}$  increases significantly.  $P_{dyn}$  is still the dominant part of the power consumption. The  $P_{dyn}$  occurs when the output signal switches (e.g. 0 - 1, 1 - 0). The output capacitance in a circuit usually needs to be charged or discharged

| Power Analys                             | sis Attack List                     |  |  |  |  |  |

|------------------------------------------|-------------------------------------|--|--|--|--|--|

| Non-profiled Attacks                     | Profiled Attacks                    |  |  |  |  |  |

| Simple Power Analysis (SPA)              | Template Attack                     |  |  |  |  |  |

| Differential Power Analysis (DPA)        | Deep Learning based Template Attack |  |  |  |  |  |

| Correlation Power Analysis (CPA)         |                                     |  |  |  |  |  |

| Higher Order Differential Power Analysis |                                     |  |  |  |  |  |

| (HODPA)                                  |                                     |  |  |  |  |  |

Table 2.1: Power Analysis Attacks List.

according to the change of input value when the switch occurs. It has a great impact on power. The short-circuit current caused by the instant short of PMOS and NMOS also provides large power consumption. The power analysis attacks track the power during execution. After that, they perform mathematical/statistical analysis with the traces to reveal the key. The attacker usually uses the special leakage model, which correlates with the secret key bit under operation to get the key.

In addition to the passive and active classification method, the profiled and Nonprofiled criteria can also divide power analysis attacks into two parts. The profiled attacks are considered the most potent because the attacker needs to have a clone of the device and input particular plain text and secret keys to create a template. In that particular case, the attacker can reveal the secret key with the template. In comparison, the non-profiled attacks need the attackers to know the cryptographic algorithm and not the devices. The substantive difference between profiled attacks and non-profiled attacks is that the profiled attacks can have access to the device. However, the attackers can not always perform profiled attacks in reality because they can not always have control of those cryptographic devices. On the other side, the non-profiled attacks can still threaten those devices even the attacker can not get the device. It is needless to say that a good understanding of those various attack methods can help security engineers to design a resistant device. Thus, an explanation of those attack methods and summary has an outstanding contribution to this research. Table 2.1 shows the popular Power Analysis Attack methods and each one will be explained in the following subsections.

#### 2.2.1 Non-Profiled Attacks

For the non-profiled attacks, it is weaker than profiled attack from the assumption. Because attackers can not access the device and only have plaintext and ciphertext information, they need to obtain many power traces and use statistical analysis to reveal the key. As the Table 2.1 shows, non-profiled attacks has SPA, DPA, CPA, and HODPA. With the countermeasure development, traditional attacks methods like DPA and CPA can not succeed in recovering the key. So HODPA comes out, which is the method to deal with some protected devices.

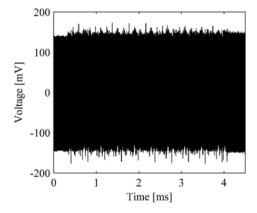

#### 2.2.1.1 Simple Power Analysis

When attackers perform SPA, the voltage drop and up showed in the power traces leak the information to the attackers. However, only using SPA can not reveal the key. It can help to locate the interesting point in the traces. From Figure 2.7, the attackers can infer that the device starts to do nine AES encryption round at 0.3ms. Furthermore, at 4.1ms, the last round is performed. Because the final round does without Mixcolumn processes, the 4ms traces becomes different from previous power traces. However, it is impossible to reveal the AES key only from one power trace.

Figure 2.7: Power consumption of the AES encryption[37].

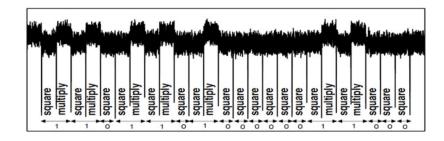

However, the SPA can still play a role in some implementations. For example, Figure 2.8 shows the unprotected RSA implementation. When multiply occurs, the power trace leak '1' information outside; meanwhile, the square operation leaks '0' information. Once the attackers get the whole power trace of RSA implementation, they can get the final key.

Figure 2.8: square-and-multiply RSA implementation[37].

The attacks which only use one or few power traces to recover the key are treated as SPA [37]. Thus, the manual effort compared to other methods is larger. Moreover, the lousy signal-to-noise ratio makes SPA challenging to use.

#### 2.2.1.2 Classical 1-bit Differential Power Analysis

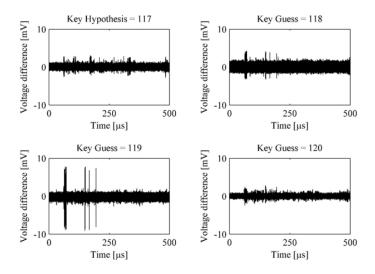

The power traces in Figure 2.9 contain the information of instruction sequence and have also been affected by the manipulated data values [32]. However, the measurement error and noise sometimes conceal the data power variations. So some attacks aimed at revealing the data power information come out. For example, DPA involves dealing with many power traces, and hypothesis key statistical analysis can recover the secret key. The DPA attacks have seven steps. At first, the attackers need to collect many power traces with varying inputs. And then select sensitive intermediate values like sbox result in AES. As sbox is commonly used and the attackers can know sbox. Then, for each possible value of K, compute the hypothesis result like  $S(p \oplus k)$ . They are choosing one bit in the hypothesis result like MSB or LSB. According to the value of that bit, partition the power traces into two groups '1' '0', compute the mean and get the difference of those two means. Because AES 8 bits key has 256 cases, the attackers can get 256 differential power traces graphs. One of them has the peak power traces is the correct key for that bit. The essential idea behind it is that if a wrong key is implemented, the intermediate data is uncorrelated to the actual power traces by the device. Moreover, in theory, the mean difference would approach zero, causing the difference in power traces graphs to flat. As showed in the Difference plots for the key guesses, the attacker can determine the 119 is one of the key. Thus, this model can use 1-bit to recover one byte key. This processes needs to be repeated several times to get the full key. To be more specific about DPA, following list explains more details about DPA.

Figure 2.9: Difference plots for the key guesses[37].

1. **Select point of interest** In AES, the first operation in each round is SubByte. As mentioned in the AES part, the first inputs of the first SubByte are plaintext and original key. The SubByte operation is a byte level and non-linear function. This makes it suitable for attacker to perform DPA.

2. Measure power traces The attacker needs to collect the random plaintexts power traces with a constant key. The amount of traces may vary from different algorithms. In Equation 2.1 and Equation 2.2, the P is the recorded plaintexts, and the T is the corresponding power traces. Moreover, the n represents the measurement point, and the d represents the number of random plaintexts.

$$P = \begin{bmatrix} p_0 & \dots & p_d \end{bmatrix} \tag{2.1}$$

$$T = \begin{bmatrix} t_{0,0} & \dots & t_{0,n} \\ \vdots & \dots & \vdots \\ t_{d,0} & \dots & t_{d,n} \end{bmatrix}$$

(2.2)

3. Compute hypothetical S-box intermediate value After collecting the power traces, the attackers can choose one byte in the plaintext and all the possible keys (e.g., AES key 256 cases) to perform SubByte  $S(p \oplus k)$ . The attackers will perform these steps many times and choose different bytes until all the 128 bits key are recovered. Equation 2.3 shows the hypothesis intermediate results.

$$S = \begin{bmatrix} S_{0,0} & \dots & S_{0,255} \\ \vdots & \dots & \vdots \\ S_{d,0} & \dots & S_{d,255} \end{bmatrix}$$

(2.3)

4. Partition traces into two groups In classical 1-bit DPA, the T power traces array can be divided into two groups based on one bit in the S intermediate value array. For example, the MSB bit of the first column in the S array(key 00 case). If MSB bit is 1, add this trace into group A in Equation 2.4. If MSB is 0, add this trace into group B in Equation 2.5.

$$A = \begin{bmatrix} t_{0,0} & \dots & t_{0,n} \\ t_{2,0} & \dots & t_{2,n} \\ t_{3,0} & \dots & t_{3,n} \\ & & \dots & & \\ t_{d,0} & \dots & t_{d,n} \end{bmatrix}$$

(2.4)

$$B = \begin{bmatrix} t_{1,0} & \dots & t_{1,n} \\ t_{4,0} & \dots & t_{4,n} \\ t_{7,0} & \dots & t_{7,n} \\ \vdots & \dots & \vdots \\ t_{d-1,0} & \dots & t_{d-1,n} \end{bmatrix}$$

$$(2.5)$$

5. Compute average and two groups means difference In this step, each group needs to average the power trace to get more robust power traces. And then do the subtraction of A and B to get the correlation of hypothetical key and real key. If the key is correct, a large peak will show in the different power traces. While

if the key is incorrect, the power traces will become flat, as the graph shows. Equation 2.6 shows the collection of each maximum value in each subkeys.

$$D = \begin{bmatrix} d_0 & d_1 & \dots & d_{255} \end{bmatrix} \tag{2.6}$$

- 6. **Identify the correct key** After comparing all the 256 different difference power traces in D, The attacker can determine which hypothesis key is the correct key byte.

- 7. **Repeat the processes** In order to get the full byte key, the attacker need to repeat step 3 6 several times. However, the power traces is still the same, which can save time for the attacker.

This attack method tells the truth that the cryptographic device depends on intermediate value is still vulnerable to the attack. If the attackers find a suitable point of interest, they can perform the corresponding DPA on this device. This method still has its limitation, the 1-bit guess is time consuming. So a different more powerful method will be introduced in the next section.

#### 2.2.1.3 Correlation Power analysis

As mentioned above, the power consumption is compromised of two part  $P_{stat}$  and  $P_{dyn}$ . Comparing to  $P_{stat}$ ,  $P_{dyn}$  takes over the dominant part. The data inside the device moves from 1 to 0 (or vice versa), the capacitance needs to be (dis)charged. Some leakage models can represent this kind of switch in the data, like the Hamming Distance and the Hamming Weight. The correlation power analysis (CPA) is the method to use those hypothetical power consumption and the measured power traces to do statistical analysis. The correlation coefficient can determine the linear relationships between data. So, the attacker can use the correlation coefficient in CPA statistical analysis to reveal the secret key [12]. In order to get full understanding of the CPA, the two generic leakage models details needs to be explained.

Hamming-Distance Model: The HD model is very suitable for data transmission and register simulation. The power consumption of the data bus is proportional to the HD model. The registers are triggered by the clock signal so that they only change in each clock cycle. However, there are many glitches inside combinational cells in combinational cells, which makes it difficult to simulate. Because the HD describes the transition of data, the calculation methods count how many transitions happen. For example, an 8-bit data "0100\_0011" transfers to "0000\_0000", three transitions are causing HD to 3. And the HD model assumes all the transmission contribute to the power consumption equally. In order to use HD model, the attacker usually needs to know the previous or following values in the algorithms. So they needs to know a little about the algorithm.

**Hamming-Weight Model**: The HW model counts the number of logic ones in the n-bit bus. It is usually used when the attacker has no idea about the algorithms. Because the HW model only describes the current state of the data and ignores the processed before and after data, it can not simulate the device's transition. However,

CMOS device's power consumption largely depends on data transitions. So this model is not very well to CMOS devices. But in some special cases, this kind model can be used. Furthermore, a easy way to calculate the HD is  $HD = HW(v_0 \oplus v_1)$ .

The following is the steps of a correlation coefficient based power analysis.

- 1. **Select point of interest** It is same that the AES sbox is still the interest point of CPA.

- 2. Measure power traces Like the DPA step 2, the CPA records the random plaintext data as a P array in Equation 2.7. For each plaintext during encryption, the same key is used to simulate actual conditions. And the collected power traces is the array T like Equation 2.8.

$$P = \begin{bmatrix} p_0 & \dots & p_d \end{bmatrix} \tag{2.7}$$

$$T = \begin{bmatrix} t_{0,0} & \dots & t_{0,n} \\ \vdots & \dots & \vdots \\ t_{d,0} & \dots & t_{d,n} \end{bmatrix}$$

(2.8)

3. Compute hypothetical sbox result In AES, the small subkeys have 256 choices. To guess the correct result of the key, all 256 keys need to do SubByte with each plaintext to get a hypothetical sbox array S like Equation 2.9.

$$S = \begin{bmatrix} S_{0,0} & \dots & S_{0,255} \\ \cdot & \dots & \cdot \\ \cdot & \dots & \cdot \\ S_{d,0} & \dots & S_{d,255} \end{bmatrix}$$

(2.9)

4. Compute hypothetical H by leakage model The CPA step 2 and step 3 are the same as the DPA step 2 and step3. Unlike DPA step 4, dividing the power traces into two groups, the CPA uses the leakage model HD or HW to calculate hypothetical traces to simulate the corresponding power consumption. Equation 2.10 shows the hypothetical traces array.

$$H = \begin{bmatrix} h_{0,0} & \dots & h_{0,255} \\ \vdots & \dots & \vdots \\ h_{d,0} & \dots & h_{d,255} \end{bmatrix}$$

(2.10)

5. Compute the Pearson's Correlation One way to evaluate the correlation between the hypothetical power traces and measured power traces can help identify the correct key. Equation 2.11 named Pearson's Correlation is a helpful tool to find the relationship. Furthermore, i is the column from the H array, and j is the column from the T array. All the g values can build a G array like Equation 2.12, which is used to choose the best guess key. For each subkey i, find the highest

value of this row. Then, comparing the 256 maximum value, the location of this column is the best key. It correlated more with the measured traces than any other guess. Note that the value is the absolute value. The linear relationship is the most interesting point. The time information can omit either.

$$g_{i,j} = \frac{\sum_{0}^{d} (h_{k,i} - \mu_{h,i})(t_{k,j} - \mu_{t,j})}{\sqrt{\sum_{0}^{d} (h_{k,i} - \mu_{h,i})^{2} \sum_{0}^{d} (t_{k,j} - \mu_{t,j})^{2}}}$$

(2.11)

$$G = \begin{bmatrix} g_{0,0} & \dots & g_{255,n} \\ & \dots & & \\ & & \dots & & \\ g_{0,0} & \dots & g_{255,n} \end{bmatrix}$$

$$(2.12)$$

6. Put together the best subkey together And after above steps, the attackers only get one byte key. So in order to get the full key, 16 times processes needs to be performed.

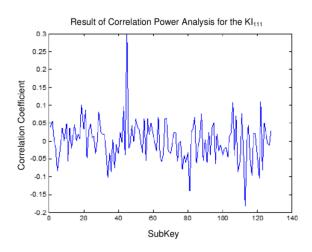

Figure 2.10 shows a 7-bit subkey correlation coefficient graph, we can infer from the graph that 42 is the most related key.

Figure 2.10: Correlation result for 7-bit subkey [38].

#### 2.2.1.4 Higher order Differential Power Analysis

With the development of attack methods, there are also countermeasures occur to prevent the device from attacking. **Masking** and **Hiding** is the main trend countermeasures. They will be introduced in later. However, like higher-order DPA and template-based DPA can succeed attacking **Masking**. The DPA and CPA which is discussed above only use one intermediate value. So these power analysis attacks are treated as *first-order* power analysis attacks. If several intermediate value is used, the this is called *high-order* power analysis attacks.

The mask conteract attacks by mask the plaintext or the key at the begining. However, even the mask is used, the operation in the algorithms will keep the mask information. If the attacker uses more intermediate value, they can recover the masked key. In practical, *second-order* attack is sufficient to exploit the leakage. And the two intermediate value can be two value masked by the same mask or a masked value and corresponding mask [40].

#### 2.2.2 Profiled Attacks

In this attack method, the attackers control the device and can build a good leakage model by using this device. Then this model, also called template, can be used to exploit the actual power traces secret information. The profiled attacks have two processes, which are profiling and extraction. The profiling step is offline and aims at capturing the behavior of the model. In the profiling step, the model may need thousands of power traces. However, the benefit is that this model can extract secret keys in the same device by a few power traces. The attacker can use the same template to attack the different user's keys in the same device. And based on the way of manipulating data, there are many different methods. For example, the template power analysis and deep learning based power analysis is now the advanced side channel attack.

#### 2.2.2.1 Template Attacks

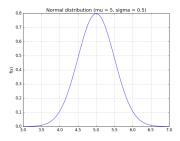

Before to describe the details of template attacks, it is necessary to understand what is a multivariate distribution and how to use it in the extraction processes. Take noise distribution as an example, the noise signal always exists to influence the measured result. It is like  $x_{result} = x_{actual} + noise$ . A Gaussian distribution can describe this random variable value. Figure 2.11 describe this more straightforward. F(x) is the probability density function and indicates the final result. The attacker can use this model in the extraction to identify the correct key. If the probability density is very small, the guessed key may be wrong. However, this only works for one measurement, the multivariate distribution can help to model several random values.

Figure 2.11: The Gaussian Distribution indicates the possibility density distribution [50].

For example, if there are two random values, X and Y. Calculating each Gaussian distribution are not helpful because they are independent. They do not have any correlation. So it is necessary to model them together (X, Y). Equation 2.13 is the

three random values model. Equation 2.14 shows the mean array of this model.

$$\sum = \begin{bmatrix} Var(x) & Cov(x,y) & Cov(x,z) \\ Cov(y,x) & Var(y) & Cov(y,z) \\ Cov(z,x) & Cov(z,y) & Var(z) \end{bmatrix}$$

(2.13)

$$\mu = \begin{bmatrix} \mu_x \\ \mu_y \\ \mu_z \end{bmatrix} \tag{2.14}$$

However, the probability density distribution will look like more complicated than just one variable value.  $f(x) = \frac{1}{\sqrt{(2\pi)^k |\Sigma|}} e^{\frac{-(x-\mu)^T \sum^{-1} (x-\mu)}{2}}$ . After the attacker gets the probability density distribution, they can put k point of one power trace into this model. If the f(x) is high, then this might be the correct key (vise versa).

#### 1. Creating the template

- (a) **Select target operation** It is the same as first-order attacks, the higher-order attack also need to find a attack operation to implement attack. In AES, the sbox is usually protected by the mask. So the related sbox operation XOR is the interested point.

- (b) Measure power traces Because the attackers need to build a good distribution to model the power traces, the tens of thoudsands of power traces are needed. The measured power traces is array T like Equation 2.15.

$$T = \begin{bmatrix} t_{0,0} & \dots & t_{0,n} \\ & \ddots & & \\ & \ddots & & \\ t_{d,0} & \dots & t_{d,n} \end{bmatrix}$$

(2.15)

(c) Compute hamming weight and divide into 9 model and calculate the mean of those model If the attacker builds a distribution model for every key, it will be considerable work. Another clever method to reduce the workload is to model the strong relation between a leakage model and target operation. The relationship between the Hamming weight and the Sbox can help the attacker reduce the model to only nine models. The H array like Equation 2.16 is the hamming weight value data. And then, divide the power traces into nine groups and calculate the according mean of each group as Equation 2.17.

$$H = \begin{bmatrix} h_0 \\ h_1 \\ h_2 \\ \dots \\ h_d \end{bmatrix} \tag{2.16}$$

$$M = \begin{bmatrix} m_0 \\ m_1 \\ m_2 \\ \dots \\ m_8 \end{bmatrix} \tag{2.17}$$

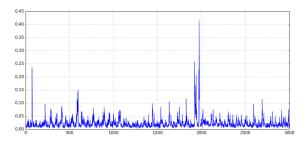

(d) **Find point of interest** In this case, the attackers do not need to create a model for every key or point of power traces. Because the key does not affect the whole power traces, and the high sample rate records some more points. In other words, the sample rate is faster than the operation rate, and some extra points can be omitted. One of the simplest method to find the point of interest(POI) is the sum of differences method like Equation 2.18.

$$D_i = \sum_{j=0}^{i} (M_i - M_j) \tag{2.18}$$

Based on Equation 2.18, a sum of differences graph can be got like Figure 2.12. As the graph shows, the attackers need to pick the highest value as the POI

Figure 2.12: Points of Interest [50].

and then ignore the near N numbers because of the extra sample point reason. Then repeat the process again to get the enough points of interest.

(e) Create the template After the attacker already find the points of interest, then they can find a mean and covariance matrix for every key (256 in AES). Take key 01 as an example, there are T traces of key 01 and  $t_{j,i}$  means the number j trace at POI i. Then the mean of POI can be calculated like  $\mu_i = \frac{1}{d} \sum_{j=0}^{d} t_{j,POI}$ . Equation 2.19 shows the array of those means.

$$\mu_i = \begin{bmatrix} \mu_0 \\ \mu_1 \\ \mu_2 \\ \dots \\ \mu_i \end{bmatrix} \tag{2.19}$$

Based on the mean, calculating the variance can use  $v_i = \frac{1}{d} \sum_{j=0}^{d} (t_{j,POI} - \mu_i)^2$ . Then the covariance can be calculated like  $c_{i,j} = \frac{1}{d} \sum_{k=0}^{d} (t_{k,i} - \mu_i)(t_{k,j} - \mu_j)$ . At last, for every group, the attacker can get an array containing variance and

covariance to indicate the possibility distribution of the input power trace. Equation 2.20 shows the multiple random model coefficient array.

$$\sum = \begin{bmatrix} v_1 & c_{1,2} & c_{1,3} & \dots \\ c_{2,1} & v_2 & c_{2,3} & \dots \\ \vdots & \vdots & \ddots & \vdots \\ \vdots & \vdots & \ddots & \vdots \end{bmatrix}$$

(2.20)

## 1. Using the template

- (a) **Identifies the target operation** Like the other methods, the Sbox is the target operation.

- (b) **Measure power traces** Comparing to the other attack methods, this method may need lesser measured power traces.

- (c) Creating POI array After getting the power traces, the attackers only needs the point of interest power traces points. D traces of n points of interest power traces array can be collected like Equation 2.21.

$$A = \begin{bmatrix} a_{0,0} & \dots & a_{0,n} \\ \vdots & \dots & \vdots \\ a_{d,0} & \dots & a_{d,n} \end{bmatrix}$$

(2.21)

- (d) Correlate the array with template Then using the f(x) function for every row in array A, the attackers can obtain the possibility distribution of the guessed key.

- (e) Combining the results One way to evaluate the f(x) is to multiply them together. However, after multiplying those values, the result may be too large or small to fit. So an alternative way is to do a log calculation and then compare the different results to determine which key is the most relative.

## 2.2.3 Deep Learning-based Side Channel Attack

As mentioned above, the template attack usually needs pre-processing and finding the point of interest to reduce the noise influence, alignment, and dimension reduction [29]. So, the pre-processing procedure is essential and based on human manipulation. Moreover, some machine-learning-based side-channel attack also needs the pre-processing and POI. However, according to some studies, the Deep learning-based side-channel attack(DLSCA) may not need to do the pre-processing and POI steps, enhancing the possibilities of success.

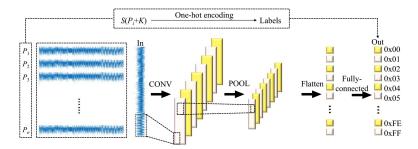

The creating template steps are different from the classical template attack. After collecting the power traces, the attacker already knows the intermediate value after the operation, like the sbox result or hamming weight. So, the attackers can use the power traces and the intermediate value as input data and the label of a neural network to create an inference model. Furthermore, the property of Convolution Neural Network(CNN) is that it is good at image classification. Although the noise and

measurement methods impact data dramatically, the CNN can still have the ability to identify the correct result by advanced input data augmentation technique. Figure 2.13 shows the training process with CNN.

Figure 2.13: CNN procedure for intermediate value [29].

After getting the trained CNN model, the attacker can use it for unknown power traces to get the relative value as array A. Array A indicates the possible result of the power traces. Then, like steps in the CPA, the 256 hypothetical subkey leakage model array can be built. The attacker needs the hypothetical array B and the template array A to identify which result has the highest value. After that, the attacker can decide which key is the correct result.

All in all, the DLSCA can avoid the pre-processing and POI steps. The steps are more straightforward than the classical template attack. However, the main factor is the trained CNN model. If the input power traces is too random and have little to train, the attack can not guarantee success. So, the amount and the regularity of the input power traces are essential for this attack method.

# 2.3 Countermeasures

The attack methods above are all interested in attacking the S-box in the AES algorithms. Because the attackers use the S-box operation can get the intermediate value for DPA, CPA, and Template attack. The intermediate value can recover the relationship between the actual power traces and the correct key. So there are many countermeasures to change the power consumption in the device. At least to reduce the dependency of those power relationships. The recent countermeasures can be divided into two major classes, hide and mask. Hide aims to hide the power relationship by adding random power or consuming equal power every clock. However, hide sill uses the same intermediate value as the unprotected algorithms use. The mask mainly replaces the intermediate value and still gets the correct result. In that way, the attackers can not use their already known intermediate value to attack this protected algorithm. Furthermore, the mask can be used either at the cell level or algorithms level. It is more popular than hiding in the scientific field and is widely discussed. Both of them are independent of the relationship between the power traces and the intermediate data. The big difference between hiding and mask is whether use the same intermediate data as the unprotected device. The following section will introduce more details of the hide and the mask countermeasures to understand resisting attacks methods better.

Table 2.2 shows the two mainstream countermeasures.

| Side-Channel Attack Countermeasure List |      |  |

|-----------------------------------------|------|--|

| Hide                                    | Mask |  |

Table 2.2: Power Analysis Attacks Countermeasures List.

# 2.3.1 Hide

The purpose of hiding is to counteract the attack method by cutting the relationship between power consumption and data operations. The designer can design the device to consume the same power every clock or random power consumption. Although those two ways are too ideal for implementation, there are still approaches to get the desired result. One method to random or equal the consumption is to change the operations power characteristic directly. Thus, those proposals belong to the amplitude dimension approaches. The other one is called the time dimension approach, which changes the operation time during one execution. So if the operations of the algorithms are randomized during the execution, the power consumption also will become random. The following subsections will describe some hiding countermeasures from the time dimension and amplitude dimension.

#### 2.3.1.1 Time dimension

The power trace needs to be pre-processed from the CPA and some machine-learning-based power analyses, and the POI is essential for the attacker to perform a successful attack. Moreover, the point of interest highly depends on the operations. If the algorithm's operation can run at a different time during each execution, the power traces will become more random [37]. Furthermore, the designer usually uses two methods inserting dummy operations and shuffling to change the composition of the power traces. The below is the details of those two approaches.

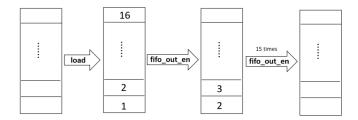

## 1. Inserting dummy operations

The motivation of inserting dummy operations is to change the operation run time. The designer can implement this either on algorithms side or on hardware side. For example, some dummy operations is inside the C code to resist attacks. And the number of hummy operations differs from each other. The more random the number of dummy operations between algorithms operations, the more random the power traces. While in the hardware side, the designer can add random delay of FIFOs in pipeline architectures [34]. The random delay FIFOs can make the data stay random when the algorithms run. Thus, the execution time will change. Moreover, the throughput will decrease as the inserting dummy operations consumes more time.

## 2. Shuffling

As some operations' sequence can be changed and the algorithms can still work correctly. In other words, the AES 16 SBOX substitution usually works in a fixed

order. If the order sequence can be shuffled every time the AES is executed, the random number of sequences is difficult to attack. Furthermore, the shuffle has less impact on throughput, like inserting dummy operations. However, the shuffle can only be used in some limited positions because some sequences in the algorithms can not be upset. So, the shuffling and inserting dummy operations are usually combined to protect the algorithms.

## 2.3.1.2 Amplitude dimension

In the time dimension, two methods to randomize the power consumption are described. In the amplitude dimension, the power characteristic can directly be modified to randomize the power and even balance the power in every operation. The noise and signal power has a significant influence on the real power. Furthermore, to increase the noise, the noise power will dominate the whole power. On another side, to decrease the operation power to a degree, the operation power will become equal and make the power trace flat.

# 1. Increasing the noise

The straightforward way to increase the noise in the device is to add the noise generator module. The generator can then add extra noise into the device to distort the power. In the hardware aspect, the more independent operations run, the more noise generated. So a wider datapath hardware architecture is more difficult to attack. Moreover, in the [45], the storage elements are distributed, and the algorithms are changed based on the logistical datapath, which can help the device resist attack.

## 2. Decreasing the signal power

The power analysis can reveal the slight differences in the power traces. So making all the operations consume equal power can enhance the security of the device. Moreover, this is not trivial. One straightforward way to make power equal is to use a filter. The filter can be used on the device to make the power constant. Because all the power is based on the CMOS cell on the device, a dedicated cell can be designed. If every cell can consume constant power, then the whole power trace will become flat.

### 2.3.2 Mask

Even if the device has a data dependency power consumption, the mask method can break the relationship because the mask does not use an intermediate value like the unprotected device. Moreover, the mask can be applied to the algorithms level and cell level. The basic idea of the mask is to use an attacker's unknown value and the original intermediate to create a new value to use in the algorithms. For example,  $v_m = v \oplus m$  use m to do xor operation with original sbox input value. And sometimes the operation can be changed according to the purpose. The mask is usually used to the plaintext and the secret key. Thus, the encryption output is the masked result too. So, the algorithms need to convert the masked data into the original one. Nevertheless, the

attack can not perform this step, and the power traces they got is not like the normal one. Furthermore, the intermediate value needs to be masked all the time. In other words, the masked intermediate value may become the original one by accident. So, it is crucial to pick the mask and mask time carefully. And several different numbers of masks will decrease the performance.

As the power analysis mentioned, the power analysis can work because of the relationship between the intermediate data and the power consumption. So the mask methods try to protect the device by a mask the intermediate value, which directly destroys the relationship. Furthermore, because the masked intermediate value's power distribution does not depend on the original intermediate value, this can only resist first-order DPA. In order to resist higher-order DPA, the secret sharing scheme needs to be used. It means several masks are used on the intermediate value. It has been proved that n masks can resist n-th order DPA [13]. However, more masks are used leads to more memory resources and more computation time. Hence, to resist the higher-order DPA, the hiding and mask methods are combined.

# Background of Spiking Neural Network

In order to understand the meaning of the spiking neural network(SNN), the background needs to be described. This chapter introduces the traditional artificial neural network and the characteristics of spiking neural networks. The different encoding methods have a significant influence on SNN. Three primary encoding methods are introduced. Furthermore, some hardware implementations of spiking neural networks are also described to guide the thesis.

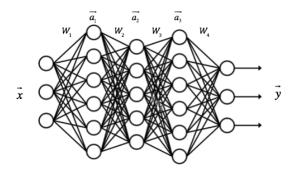

# 3.1 Artificial Neural Network

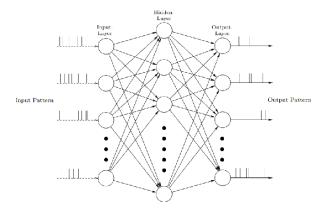

Artificial Neural Network (ANN) like Figure 3.1 is used to simulate human brain intelligence. The idea was come out firstly in 1943 by Warren McCulloch and Walter Pitts. This model contains the inputs , calculation and outputs. Those three different parts can imitate the information transmission in the brain. The input is like dendrite. The calculation function is like the cell itself. The output is like a synapse that transmits the spike to the next dendrite. At that time, the neuron can not learn by themselves. The weights are fixed numbers. Until 1949, Hebb introduced the learning rate, which lay the foundation for learning algorithms. In 1958, a simple two-layer neural network, called Perceptron, led research in neural networks. However, Minsky pointed out that the perceptron can only solve simple linear classification tasks. So until 1986, the neural network was in the winter period. Rumelhart and Hinton introduced the backpropagation (BP) algorithms which helped the neural network return to the research field. Recent research demonstrated that the ANN could be used in auto driving, computer vision, and voice recognition. Nowadays, the neural network has more layers and more neurons than before. So the calculation becomes more and more complex. A new neural network that works more like a real human brain called a spiking neural network, can solve this problem.

Figure 3.1: Artificial Neural Network Architecture[11].

# 3.2 Spiking Neural Network

The ANN has already lasted for fifty years. However, in the biological neuron model, the actual information transmission can be imitated by the voltage in the circuit. Some scientists introduced a new generation neural network, spiking neural network. It can diminish the distance between deep learning and neuroscience. The SNN uses the spikes to imitate the biological-inspired manner by discrete function. This section introduces some details of the spiking neural network. It can help the reader get a compact brief intuition of the spiking neural network [48].

#### 3.2.1 Neuron Model

The neurons in the cell throughout the nervous system transmit information. As shown in Figure 3.2, the neuron consists of three major parts. It transmits information by electricity. Before the neuron sends the information to the next motor neuron, it needs to receive a chemical message from the former neuron on its dendrites around the cell. The cell body then converts this chemical message into an electrical message through the neuron, and the electrical message is called the action potential. This neuron impulse then travels through the high-speed channel axon, which is covered with a myelin sheath. At the axon terminal, the electrical one is collected and converted to the chemical message. The axon terminal can then convert the chemical message to the next neuron. The connecting point between different neurons is called the synapse. The analog neural network imitates the function in the neuron. However, they use the fixed number rather than the electrical pulse to transmit information and do not consider the time information. Inspired by the activities of neurons, some neuron models to imitate the actual activity of neurons are invented, like Hodgkin-Huxley model, the integrate-and-fire model, and the Izhikevich model. Many of them have already been demonstrated can be used in the implementation.

Figure 3.2: The Neuron in the Brain[51].

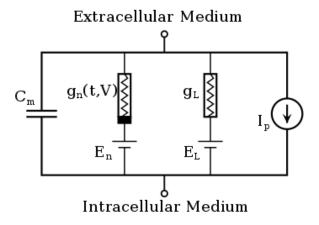

# 3.2.1.1 Hodgkin-Huxley Model

The Hodgkin-Huxley (H&H) model was firstly invented in 1952 [26]. It is a conductance-based model which describes the ionic mechanisms underlying the initiation and propagation of action potential in squid giant axon [26]. It is a mathematical function that consists of many non-linear differential functions. The basic theory can be explained by Figure 3.3. It treats every component as electrical elements. It has three different processes, voltage-gated ion channels, leak channels ,and pumps and exchangers. However, this model is hard to be implemented in the silicon compared to the other model. Its complexity constrains its usage range.

Figure 3.3: The Hodgkin-Huxley model[56].

#### 3.2.1.2 Izhikevich Model

The Izhikevich model combines the biological plausibility of Hodgskin-Huxley dynamics and the computational efficiency of integrate-and-fire neurons [28]. It can be used in large scale neuron systems. However it still has the limitation that the spike shape is always the same. There are four parameters that determine the spiking and bursting behaviour of the neurons. Various parameters can result in various firing patterns. Equation 3.1 and Equation 3.2 explain the input voltage change. With the change of a,b,c,d four different parameters, the neuron can have several different types.

$$v = 0.04v^2 + 5v + 140 - v + I \tag{3.1}$$

$$u = a(bv - u) \tag{3.2}$$

With the condition Equation 3.3:

$$ifv \ge 30mv, v \leftarrow c, u \leftarrow u + d \tag{3.3}$$

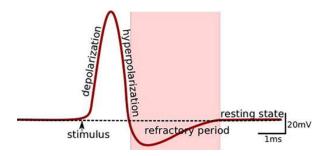

## 3.2.1.3 Integrate-and-Fire Model

The integrate-and-fire (I&F) model is the widely used model in the spiking neural network. Because it is very simple compared to the other models, it was first born

in 1907 by Lapicque. Moreover, the mechanism can be described by Equation 3.4. When the input stimulus comes, the membrane potential increases over time. After the membrane potential exceeds the threshold, a new spike is generated, and the membrane potential is set to reset value.

Figure 3.4: The action potential the fire period, refractory period, and the reset state [46].

However, this model still has its limitation. It can not describe the refractory period in the real neuron activity. The membrane potential will increase to infinite. The leaky integrate-and-fire(LIF) model can be used to solve this problem. Figure 3.4 shows the voltage change inside LIF model and Equation 3.4 explains its mechanism.

$$I(t) - \frac{V_m(t)}{R_m} = C_m \frac{dV_m(t)}{dt}$$

(3.4)

# 3.2.2 Spike Encoding

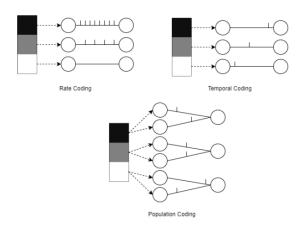

In the spiking neural network, the information can be encoded by many different ways. Different encoding methods give different impact on the neural network. There are three major popular encoding methods, rate coding, temporal coding, and population coding. The following sections give a detail description of three coding methods. And the final result judgement criterion is determined by the frequency rate or the arrive time of spikes, which is different from the criterion in the ANN. Figure 3.5 shows the firing coding general SNN structure.

Figure 3.5: General Structure of SNN[27].

## 3.2.2.1 Rate Coding

Rate coding is a widely used coding method in the spiking neural network. The principle of the rate coding is that the neurons corresponding to inputs with the highest intensities fire more frequently. In other words, the scheme treats the input pixel as a firing rate and converts it into Poisson spike train with firing rate [24]. The firing rates can be used to describe the properties of sensory or cortical neurons. There are two calculation methods for calculating firing rates. Firstly, the spike-count rate, also called temporal average, can be obtained by counting the spikes number during the trial time and divided by the trial time. The time window period needs to be set corresponding to the input stimulus. The advantage of spike-count rate is that it can be obtained by only one trial but at the cost of losing all temporal resolution in neuron response during this trial [57]. The second scheme is the time-dependent firing rate that averages the number of spikes during a short interval, divided by the interval. The same input sequence needs to be repeated several times. The time-dependent firing rate is an effective way to evaluate neuron activity. However, it can not be used to imitate the neuron in the brain because the neuron in the brain can not wait for the repeated input sequence. Nevertheless, the neuron in the experiment can use this method to get a more precise firing rate.

## 3.2.2.2 Temporal Coding

The temporal coding like time-to-first coding is that the neuron fire first with the highest intensity. In other words, the larger the input pixel is, the more information is, the earlier it fires a spike.

## 3.2.2.3 Population Coding

Population coding scheme is one way to describe method by the connection activity between neurons. For example, the spike times of several input neurons are used to represent the input data. Figure 3.6 shows the three different encoding method.

Figure 3.6: Three Different Encoding Schemes [43].

## 3.2.3 SNN Learning Method

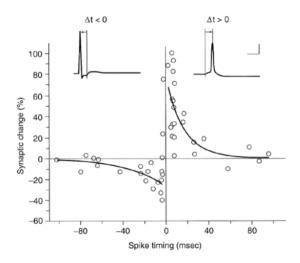

One of the most used learning algorithms is spike-time-dependency plasticity(STDP). The STDP changes the weight in proportion to the pre-synaptic firing rate and the temporal rate of the changes of the activity on the post-synaptic side [5].

Figure 3.7: Biological observation of STDP weight change [5].

In Figure 3.7, the horizontal axis represents the time differences between neurons. Moreover, the vertical axis represents the change of weight. It can be concluded from Figure 3.7 that the positive changes occur when the pre-synaptic spike before the post-synaptic spike, and the closer the time difference is, the larger the change is. The negative changes occur on the opposite when the pre-synaptic spike after the post-synaptic spike. The changes diminish to zero when the time differences become larger. And the temporal vicinity of the post-synaptic spike changes the weight significantly.

# 3.2.4 SNN Hardware Implementation

Greatly boosts deep learning spiking neural networks both in the scientific and engineering fields [49]. According to the implementation methods, the SNN hardware platforms can be categorized as multi-processor [30], FPGA [41], or analog/mixed-signal [7]. However, most of the platforms using analog circuits are mostly based on the fact that complex mechanisms can be implemented with transistors in the subthreshold regime compared to digital circuits. Analog implementation can faithfully create large-scale neuromorphic circuits and complex bio-plausible tasks. However, digital implementation can also realize bio-plausible mechanisms. Many different bio-plausible models are also created to fit hardware implementation. Machine learning may choose simple IF and LIF models to achieve high accuracy and power-efficient hardware implementation. The advantage of digital implementation of spiking neural networks is that a complex multiplier operation can be reduced to addition and compared to MAC operators in ANN. Thus, the digital SNN can only use adders to replace MAC, reducing operations complexity and improving power efficiency.