# Improving Metastability in Synchronous SAR ADCs

by

**Jorrit Hildebrand**

in partial fulfilment of the requirements for the degree of

**Master of Science in Electrical Engineering**

at the Department of Electronic Circuits and Architectures,

Faculty of Electrical Engineering, Mathematics and Computer Science

Delft University of Technology

To be defended publicly on Wednesday, 21 August 2024, at 13:30.

Supervisor: Prof. Dr. K. Bult, TU Delft / Ethernovia

Thesis Committee: Dr. F. Sebastian, TU Delft

dr. M. Babaie, TU Delft

Prof. Dr. K. Bult, TU Delft / Ethernovia

ETHERNOVIA®

**TU**Delft

# Summary

This thesis focuses on the design and optimization of Successive-approximation (SAR) Analog-to-Digital Converter (ADC), with a primary focus on enhancing the Bit Error Rate (BER). SAR ADCs are widely used in various applications due to their power-efficient characteristics. The critical point addressed in this research is improving the BER of synchronous SAR ADCs without the necessity to reduce the sampling speed.

The primary innovation presented in this work is a modified SAR loop featuring a dual Digital-to-Analog Converter (DAC) structure. This architecture aims to reduce the probability of metastable errors in the output code, which occur when the comparator fails to resolve its input within the allocated time.

An in-depth analysis of the comparator, amplifier, capture latch, and DAC elements is conducted to identify and address non-idealities affecting the performance. The research demonstrates a significant reduction in BER by incorporating a metastability detection circuit with the dual-DAC architecture. This approach allows the system to solve metastable events parallel to the SAR loop, improving the overall reliability of the output code without slowing down the SAR loop.

Theoretical models are proposed to validate the proposed solutions' effectiveness, highlighting the practicality and feasibility of the design enhancements. The simulation results demonstrate a substantial improvement in BER. This thesis's implementation strategies and techniques provide a framework for designing Dual-DAC SAR ADCs.

In conclusion, this thesis contributes to the field of high-speed digital converters by presenting innovative solutions to enhance the BER of the SAR ADC. The findings improve our understanding of managing metastability in ADCs and pave the way for future advancements in ADC technology. The methodologies and insights gained have the potential to impact the development of more robust and efficient ADC systems.

# Contents

|                                              |             |

|----------------------------------------------|-------------|

| <b>List of Figures</b>                       | <b>v</b>    |

| <b>List of Tables</b>                        | <b>viii</b> |

| <b>Acronyms</b>                              | <b>ix</b>   |

| <b>List of symbols</b>                       | <b>ix</b>   |

| <b>1 Introduction</b>                        | <b>1</b>    |

| 1.1 Synchronous SAR ADC . . . . .            | 2           |

| 1.2 Scope of the report . . . . .            | 4           |

| <b>2 Comparator</b>                          | <b>5</b>    |

| 2.1 Comparator output . . . . .              | 6           |

| 2.2 Timing . . . . .                         | 7           |

| <b>3 Metastability</b>                       | <b>9</b>    |

| 3.1 Dual capture latch . . . . .             | 12          |

| <b>4 Proposed SAR loop with improved BER</b> | <b>14</b>   |

| 4.1 Switching scheme . . . . .               | 14          |

| 4.2 Dual-DAC ADC . . . . .                   | 16          |

| 4.3 SAR cycle . . . . .                      | 17          |

| 4.4 Metastable events . . . . .              | 18          |

| <b>5 Dual-DAC limits</b>                     | <b>21</b>   |

| 5.1 Upper limit dead-zone . . . . .          | 22          |

| 5.1.1 Increased ADC resolution . . . . .     | 24          |

| 5.1.2 DAC settling artifact . . . . .        | 24          |

| 5.2 Lower limit . . . . .                    | 26          |

| <b>6 System analysis</b>                     | <b>29</b>   |

| 6.1 Clocked comparator . . . . .             | 29          |

|           |                                                 |           |

|-----------|-------------------------------------------------|-----------|

| 6.1.1     | Time response . . . . .                         | 30        |

| 6.1.2     | Non-idealities . . . . .                        | 32        |

| 6.2       | Amplifier . . . . .                             | 33        |

| 6.3       | Capture latch . . . . .                         | 34        |

| 6.4       | Comparator Chain . . . . .                      | 38        |

| 6.5       | DAC element . . . . .                           | 39        |

| 6.5.1     | Constant common-mode switching scheme . . . . . | 39        |

| 6.5.2     | DAC element . . . . .                           | 40        |

| <b>7</b>  | <b>Bit Error Rate</b>                           | <b>43</b> |

| 7.1       | System definitions . . . . .                    | 43        |

| 7.2       | Statistical model . . . . .                     | 46        |

| 7.3       | Simulation results . . . . .                    | 48        |

| 7.4       | Comparison . . . . .                            | 49        |

| <b>8</b>  | <b>Implementation of test-chip</b>              | <b>51</b> |

| 8.1       | Noise-Budget . . . . .                          | 51        |

| 8.1.1     | Sampling noise . . . . .                        | 52        |

| 8.1.2     | Quantization noise . . . . .                    | 52        |

| 8.1.3     | Thermal noise . . . . .                         | 52        |

| 8.1.4     | Other noise sources . . . . .                   | 53        |

| 8.2       | Comparator Chain . . . . .                      | 53        |

| 8.2.1     | Validation . . . . .                            | 55        |

| 8.3       | Switching scheme . . . . .                      | 56        |

| 8.4       | Capacitive DAC . . . . .                        | 56        |

| 8.4.1     | Capacitor Sizing . . . . .                      | 57        |

| 8.4.2     | Mismatch . . . . .                              | 58        |

| 8.4.3     | Switches . . . . .                              | 59        |

| 8.4.4     | DAC-logic . . . . .                             | 59        |

| 8.5       | Reference buffer . . . . .                      | 59        |

| 8.6       | Sampler . . . . .                               | 61        |

| 8.7       | Dual Single DAC Switch . . . . .                | 61        |

| <b>9</b>  | <b>Conclusion</b>                               | <b>63</b> |

| <b>10</b> | <b>Future work</b>                              | <b>64</b> |

| 10.1      | Asynchronous SAR ADC comparison . . . . .       | 64        |

|           | <b>Bibliography</b>                             | <b>66</b> |

# List of Figures

|     |                                                                                                                                                                |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | A one-way communication network between two digital systems . . . . .                                                                                          | 1  |

| 1.2 | ADCs taken from [1], power consumption versus SNDR . . . . .                                                                                                   | 2  |

| 1.3 | (a) A synchronous SAR ADC block diagram. (b) Timing diagram of the synchronous SAR ADC. . . . .                                                                | 3  |

| 2.1 | Transient of a clocked comparator with input signals varying from a $\mu$ V to 100 mV, as indicated next to the curve. . . . .                                 | 5  |

| 2.2 | Exponential gain of the comparator with ideal transconductances. . . . .                                                                                       | 6  |

| 2.3 | Differential output of a comparator. . . . .                                                                                                                   | 7  |

| 2.4 | Differential output transient and gain of a comparator, with four valid and two metastable responses. . . . .                                                  | 8  |

| 2.5 | Output transient of a comparator, with input voltage steps taken a decade apart. . . . .                                                                       | 8  |

| 3.1 | Metastable output voltages of the comparator and capture latch. . . . .                                                                                        | 9  |

| 3.2 | Input voltage sweep with the single-ended response of the comparator. . . . .                                                                                  | 10 |

| 3.3 | Transient output waveform of metastable and valid responses, with the same polarity input voltage. . . . .                                                     | 10 |

| 3.4 | Metastability detection circuit for comparators . . . . .                                                                                                      | 11 |

| 3.5 | Transient response of amplifiers A1/A2 metastability detection circuit. . . . .                                                                                | 11 |

| 3.6 | Output regions of the comparator, amplifier, and capture latch chain . . . . .                                                                                 | 12 |

| 4.1 | Metastability detection circuit of the comparator with the designated switching scheme. The capture latch connected to D1 has an additional inversion. . . . . | 15 |

| 4.2 | The different switching ranges of the complete DAC. . . . .                                                                                                    | 16 |

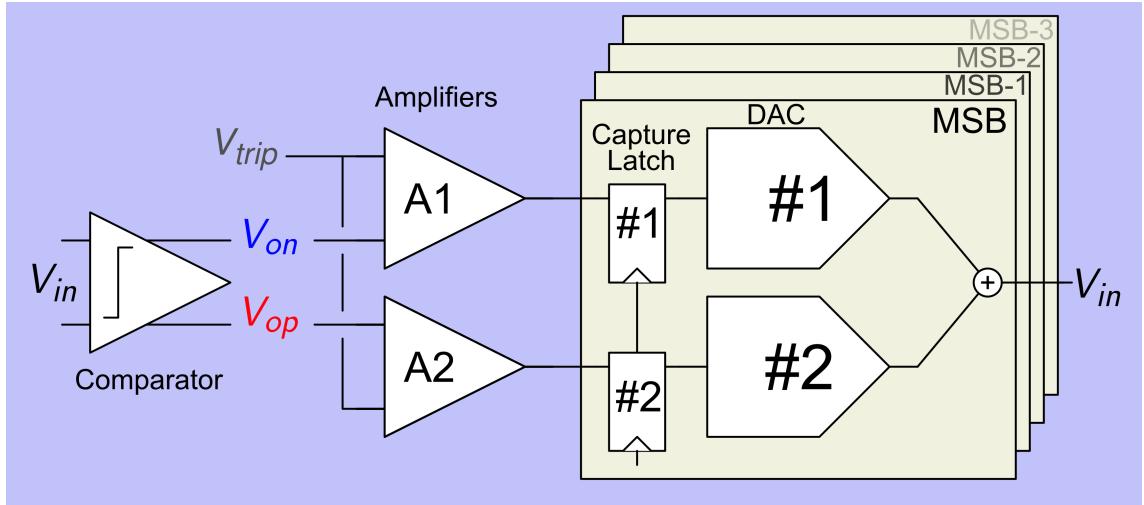

| 4.3 | System overview of a 5-bit ADC, sampling circuit excluded. . . . .                                                                                             | 16 |

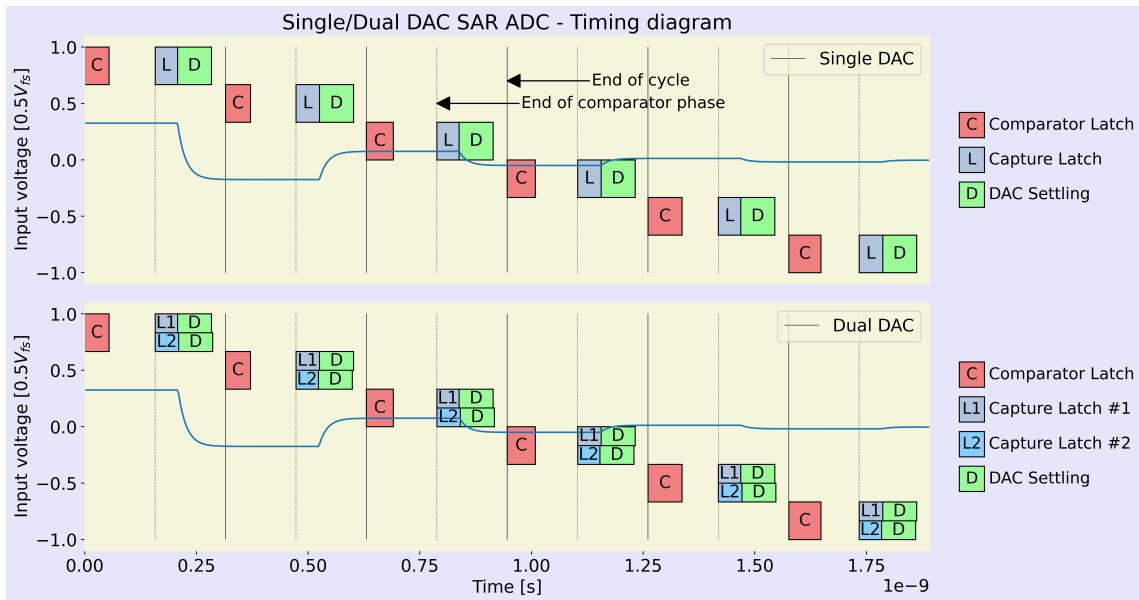

| 4.4 | A 6-bit Dual and Single DAC conversion comparison with input voltage 0.32 . . . . .                                                                            | 17 |

| 4.5 | A 4-bit Dual and Single DAC ADCs comparison with the Dual DAC showing a step artifact. . . . .                                                                 | 18 |

---

|      |                                                                                                                                                                                                                                 |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

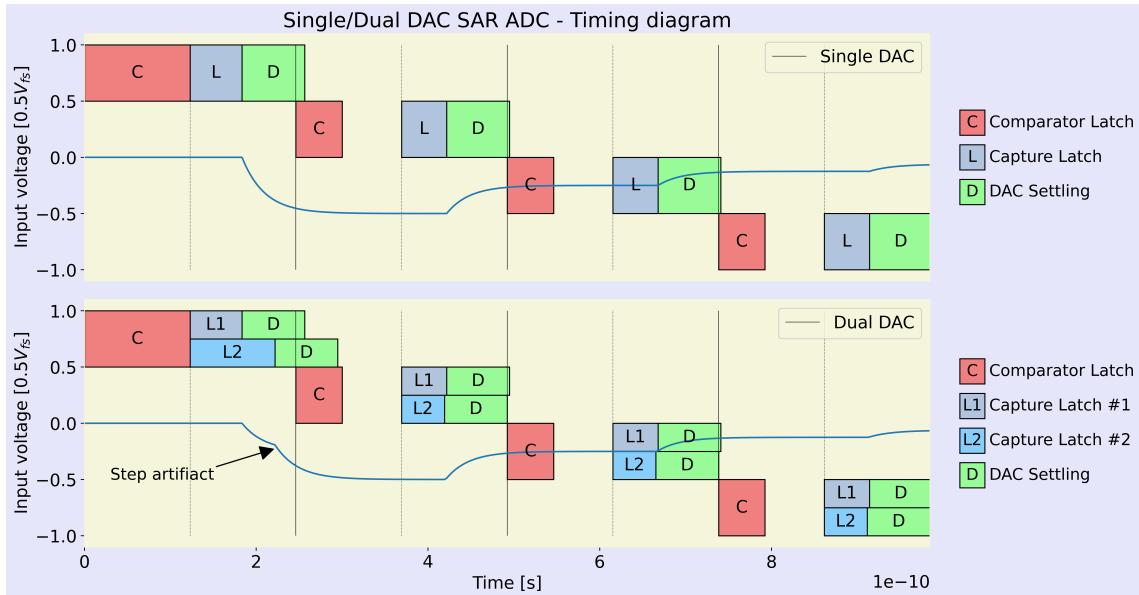

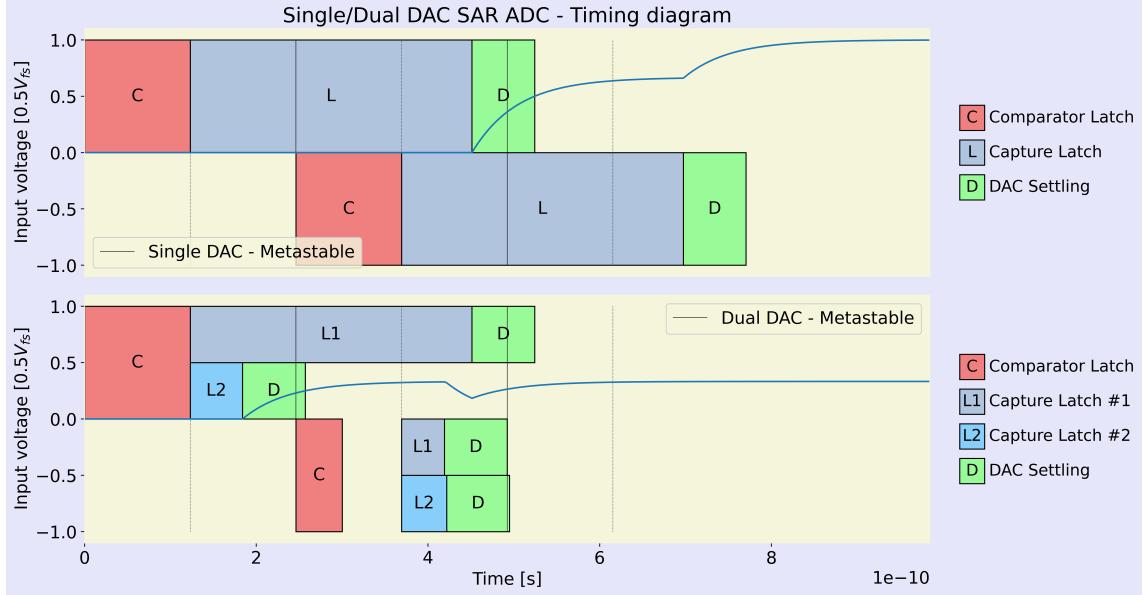

| 4.6  | The first two bits of a Dual and Single DAC ADCs in the case of a metastable event. . . . .                                                                                                                                     | 19 |

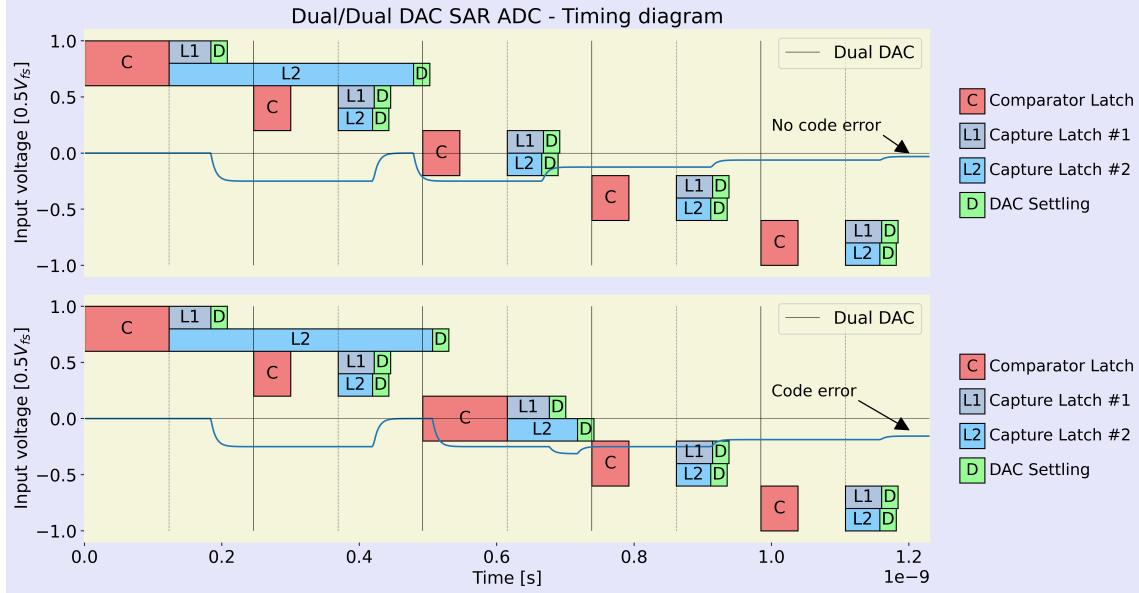

| 4.7  | Two conversions of a dual DAC ADC. The upper conversion exhibits no bit error, but the lower conversion shows a bit error. . . . .                                                                                              | 20 |

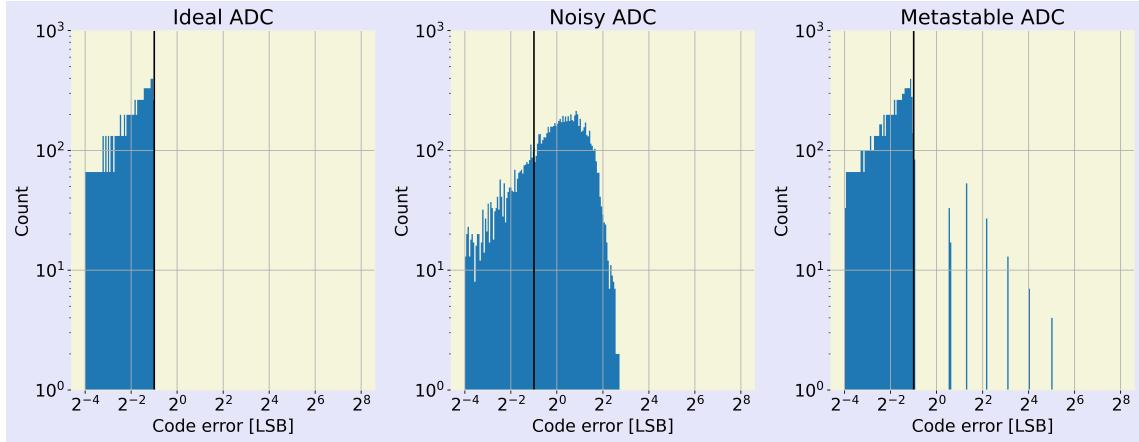

| 5.1  | Histograms of three configuration ADCs . . . . .                                                                                                                                                                                | 22 |

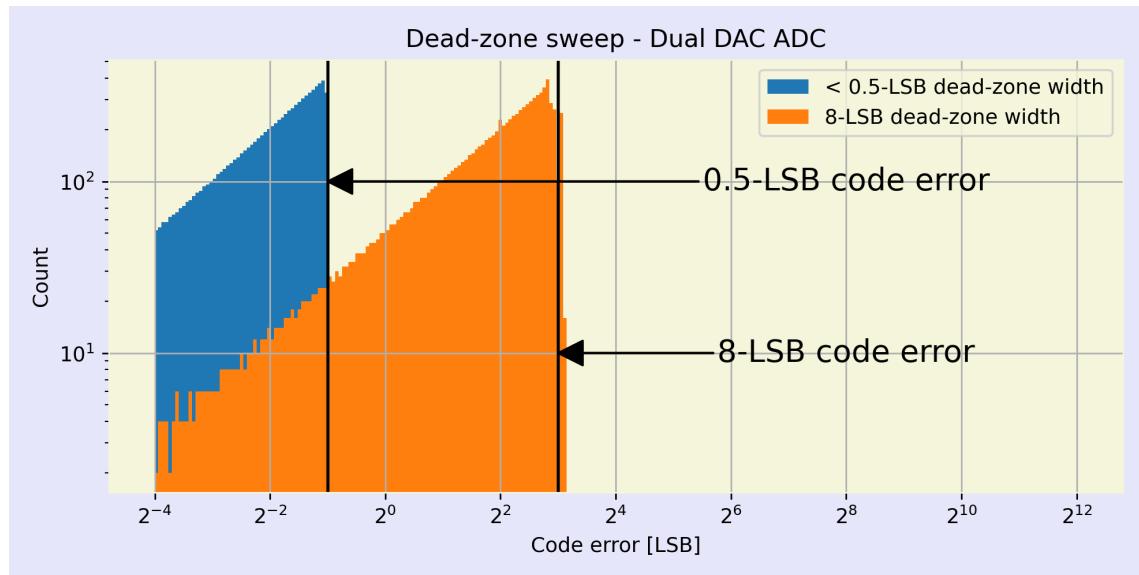

| 5.2  | Code error using two dead-zone widths . . . . .                                                                                                                                                                                 | 23 |

| 5.3  | A showcase of quantization errors due to dead-zone limits . . . . .                                                                                                                                                             | 23 |

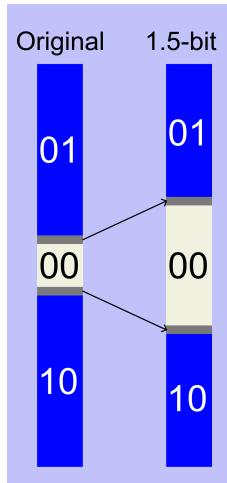

| 5.4  | Dead-zone width modification to 1.5-bit system. . . . .                                                                                                                                                                         | 24 |

| 5.5  | 6-bit Dual DAC SAR ADC with a gray area indicating the available back-end ADC range, (a) correctly operating, input voltage does not enter the gray area. (b) false trigger of the dead-zone resulting in a code error. . . . . | 25 |

| 5.6  | 6-bit dual DAC SAR ADC highlighting the false trigger of the dead-zone at the MSB-1 conversion. . . . .                                                                                                                         | 26 |

| 5.7  | Dead-zone quantization for a 10-bit ADC using 10-bit storage (for 11-bit data). . . . .                                                                                                                                         | 27 |

| 5.8  | Timing response of capture latches, output comparator referred. . . . .                                                                                                                                                         | 28 |

| 6.1  | Comparator Chain including N-bit capture latches and DAC. . . . .                                                                                                                                                               | 29 |

| 6.2  | Differential and Single-ended outputs of a clocked comparator with the three regions of operation highlighted . . . . .                                                                                                         | 30 |

| 6.3  | Comparator timing response over a large input range . . . . .                                                                                                                                                                   | 31 |

| 6.4  | (a) Offset visualization of a comparator. (b) Noise sources of a comparator. (c) kickback visualization of a comparator. . . . .                                                                                                | 32 |

| 6.5  | Inverter sizing, utilizing the internal tripping voltage. . . . .                                                                                                                                                               | 34 |

| 6.6  | Comparator chain creating an offset between both outputs, with the gray line showing the transient response of a metastable comparator .                                                                                        | 35 |

| 6.7  | Timing diagram of a 2-bit SAR ADC. . . . .                                                                                                                                                                                      | 35 |

| 6.8  | Voltage transients of an RS-latch. . . . .                                                                                                                                                                                      | 36 |

| 6.9  | Setting of an RS-latch. . . . .                                                                                                                                                                                                 | 36 |

| 6.10 | Not setting of an RS-latch. . . . .                                                                                                                                                                                             | 37 |

| 6.11 | Metastability inside an RS-latch. . . . .                                                                                                                                                                                       | 37 |

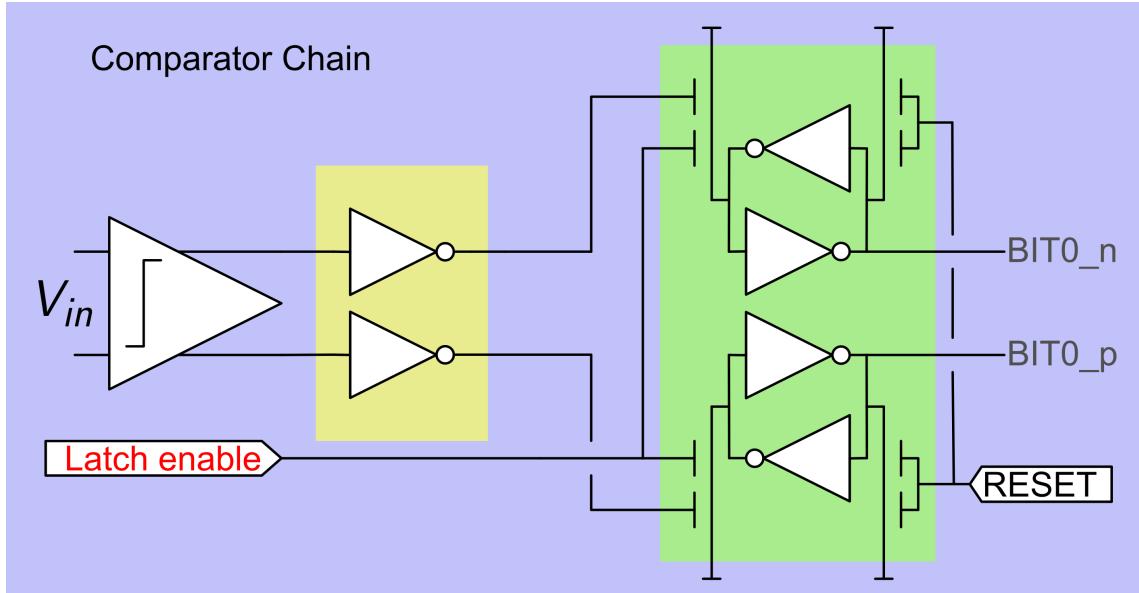

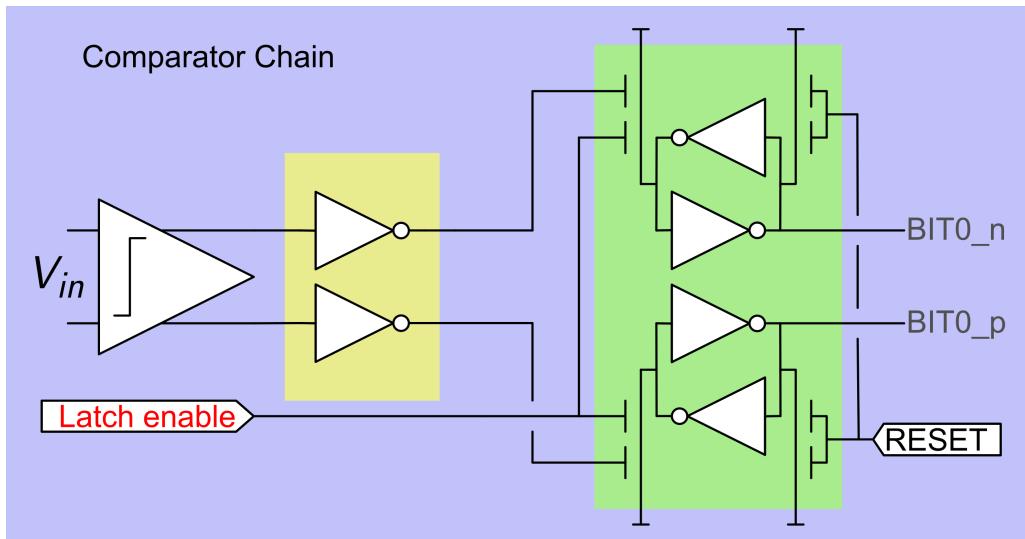

| 6.12 | comparator followed by the skewed inverters (yellow) and two the capture latches (green). . . . .                                                                                                                               | 38 |

| 6.13 | DAC switching monotonic. . . . .                                                                                                                                                                                                | 39 |

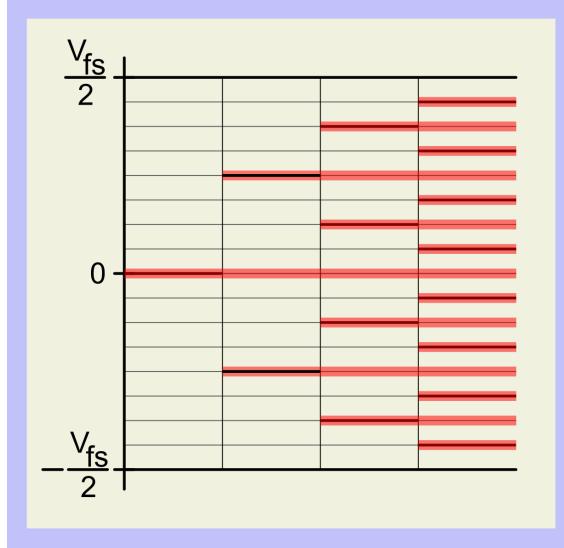

| 6.14 | a 4-bit example of constant common mode monotonic switching scheme DAC. . . . .                                                                                                                                                 | 40 |

| 6.15 | A single DAC unit with the required control signals. . . . .                                                                                                                                                                    | 41 |

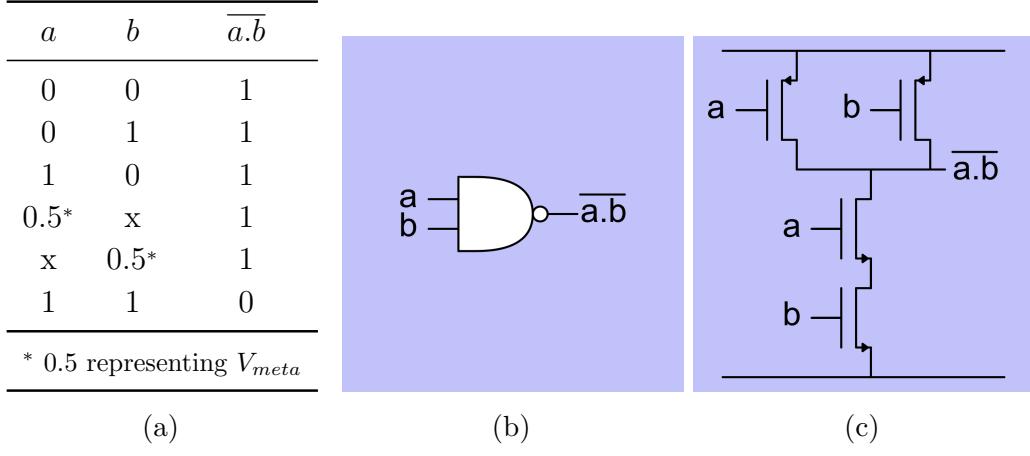

| 6.16 | (a) Truth-table of modified NAND-gate. (b) System-level NAND-gate. (c) Transistor-level NAND-gate. . . . .                                                                                                                      | 42 |

|     |                                                                                                                                         |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 7.1 | 4-bit ADC comparison regions with the metastable area highlighted in red. . . . .                                                       | 44 |

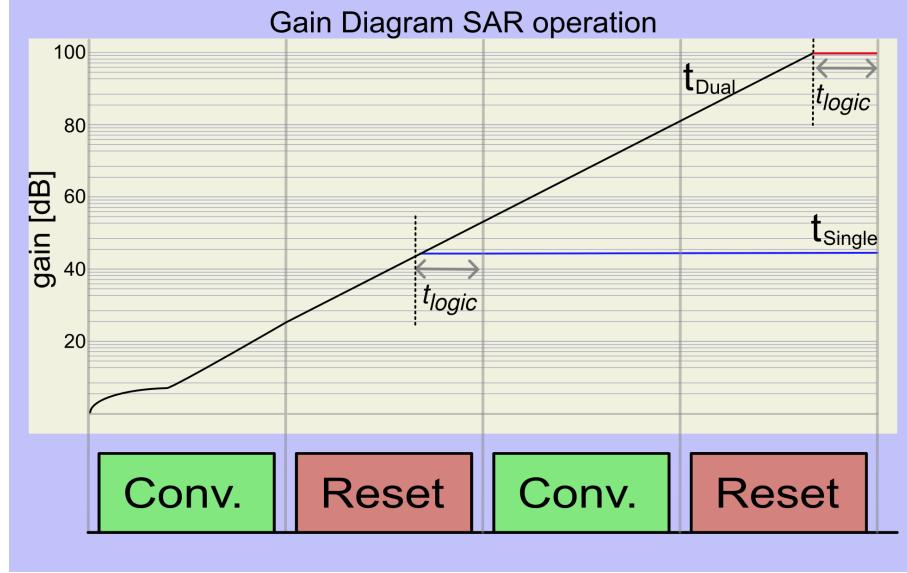

| 7.2 | Gain accumulation in the chain Single and Dual DAC ADC. . . . .                                                                         | 45 |

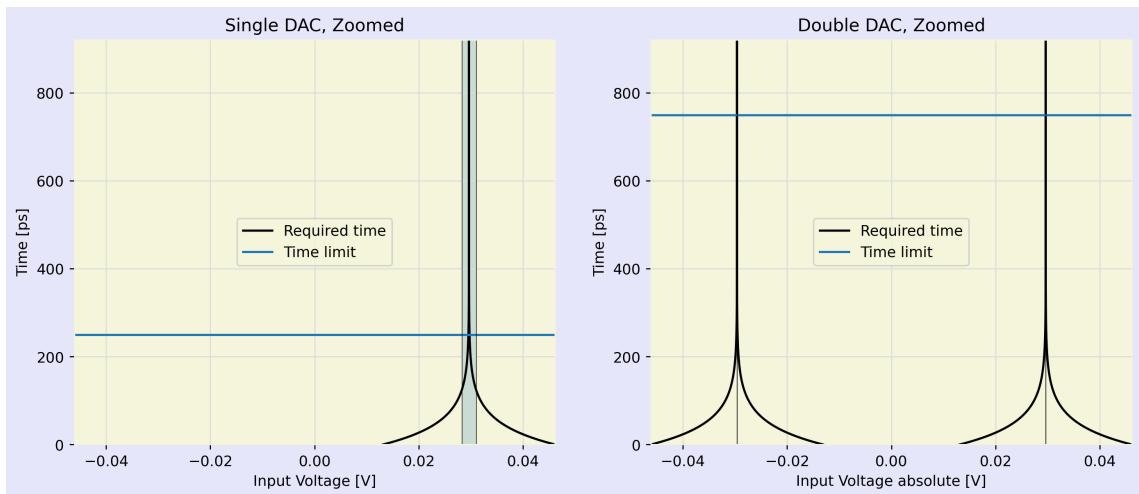

| 7.3 | Available time versus needed time for a metastable decision. . . . .                                                                    | 45 |

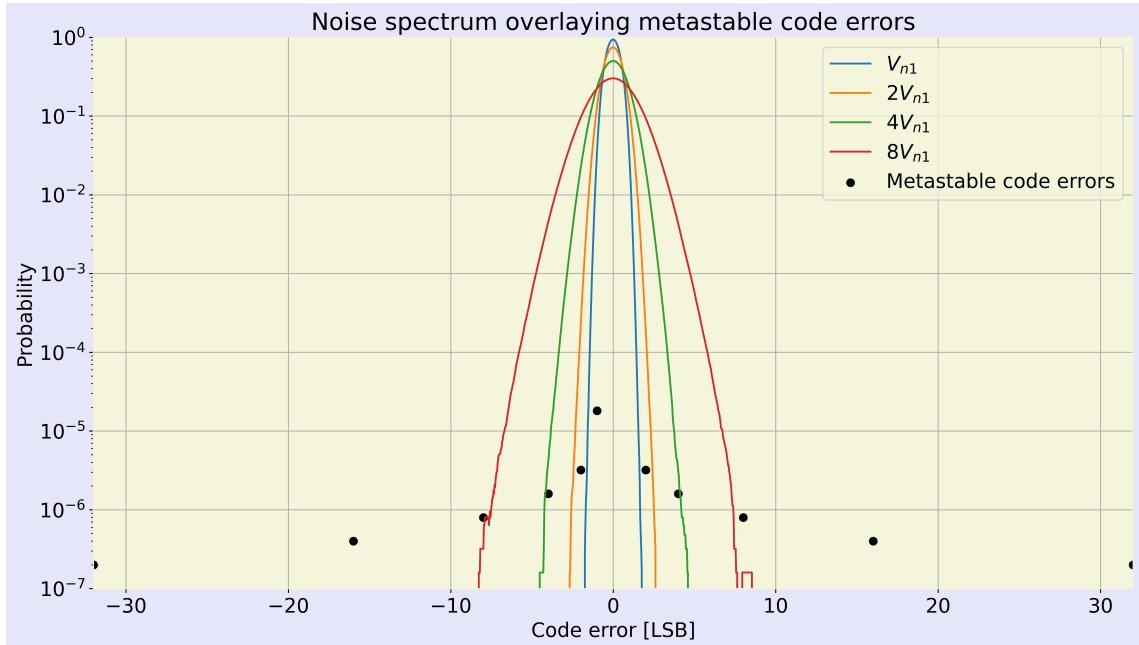

| 7.4 | Three different noise values, hiding the metastable points inside the noise floor of the system. . . . .                                | 47 |

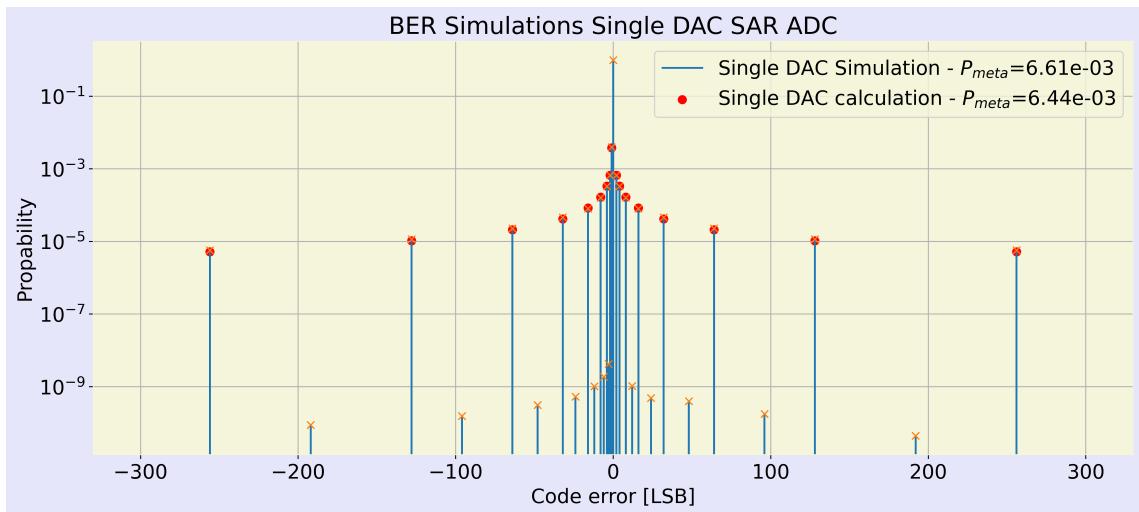

| 7.5 | Single DAC SAR ADC BER measurement results. . . . .                                                                                     | 48 |

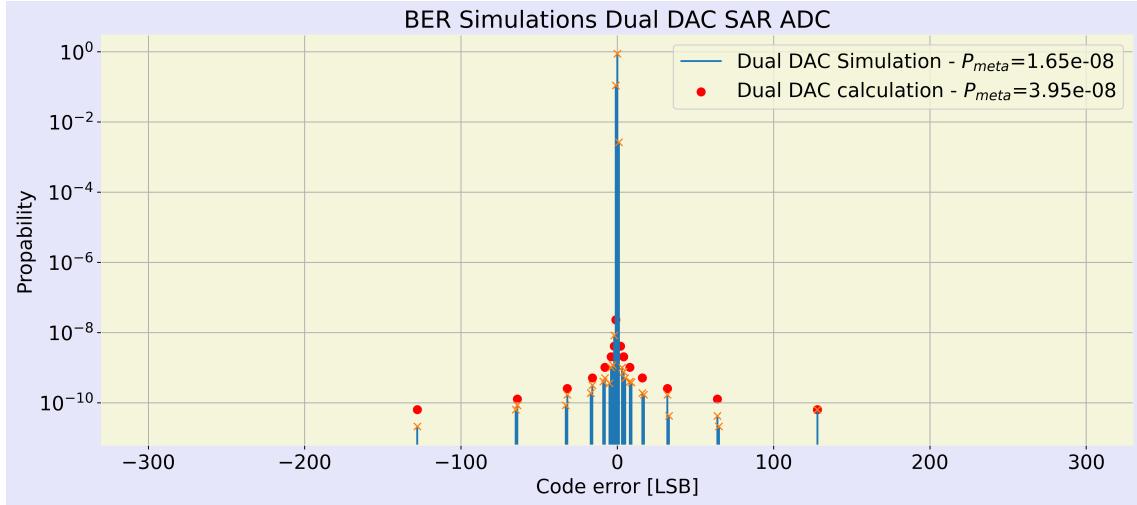

| 7.6 | Dual DAC SAR ADC BER measurement results. . . . .                                                                                       | 49 |

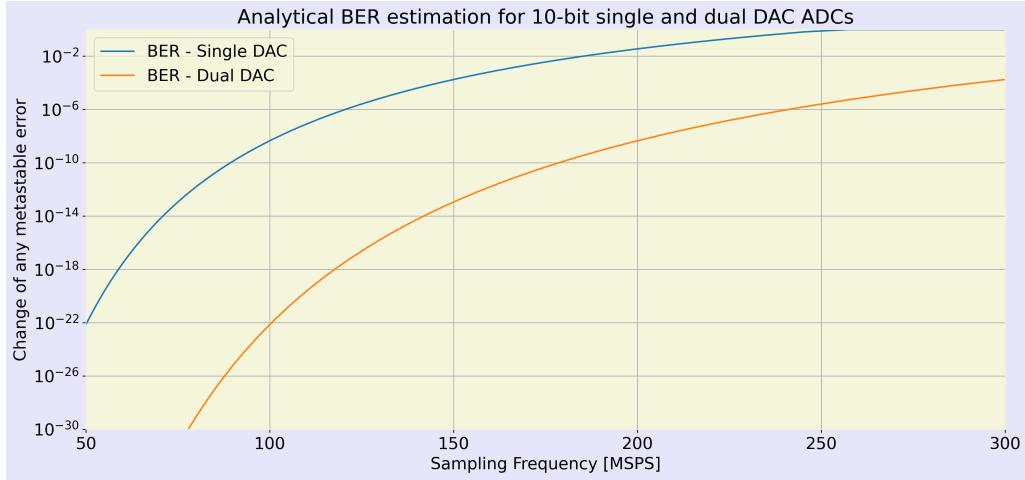

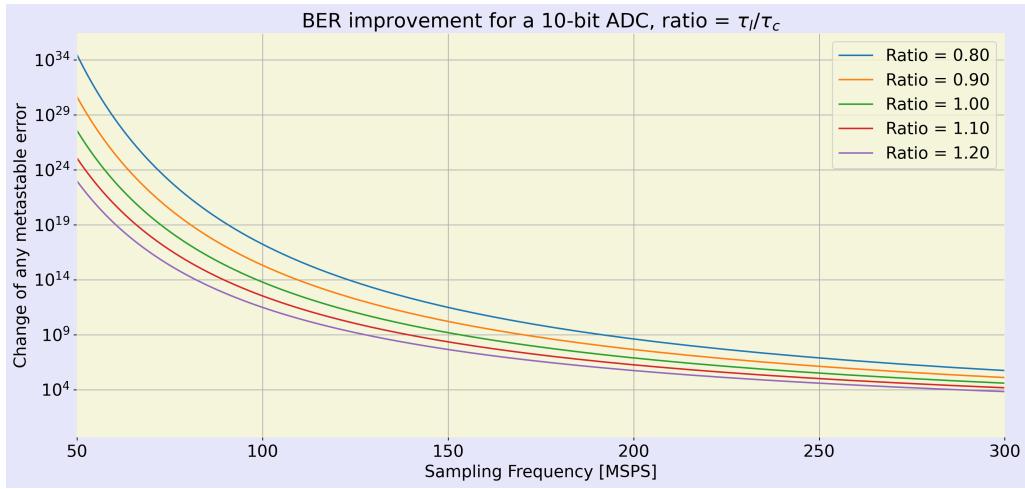

| 7.7 | Analytical calculated BER comparison between a 10-bit single and dual DAC ADC swept over a sampling frequency. . . . .                  | 50 |

| 7.8 | Normalized advantage between the single and dual DAC systems, with different timing constants between the comparator and the latch. . . | 50 |

| 8.1 | Comparator Chain . . . . .                                                                                                              | 53 |

| 8.2 | Strong arm latch comparator. . . . .                                                                                                    | 54 |

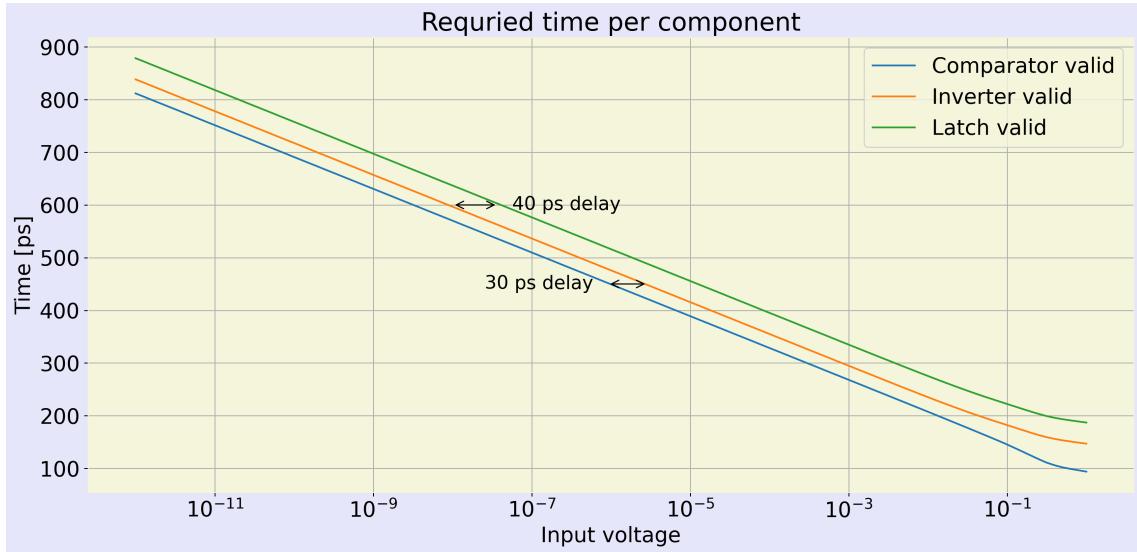

| 8.3 | Required time for a valid response per component for the final design. .                                                                | 55 |

| 8.4 | Validation chain of the system running at 100 MSPS. . . . .                                                                             | 56 |

| 8.5 | 6-bit ADC split capacitor-array network. . . . .                                                                                        | 57 |

| 8.6 | A single DAC unit with the required control signals. . . . .                                                                            | 60 |

| 8.7 | Bootstrapped switch. . . . .                                                                                                            | 61 |

# List of Tables

|     |                                                               |    |

|-----|---------------------------------------------------------------|----|

| 7.1 | $p_{meta}$ with the Least Significant Bit (LSB) error amount. | 46 |

|-----|---------------------------------------------------------------|----|

# Acronyms

- ADC** Analog-to-Digital Converter. ii, v–vii, 1–3, 19, 21, 24–27, 43, 44, 48–52, 57, 58, 64

- BER** Bit Error Rate. ii, vii, 1–4, 8, 9, 20, 29, 43, 45–51, 53, 63, 64

- CAP-DAC** Capacitor DAC. 52, 56–59

- DAC** Digital-to-Analog Converter. ii, v–vii, 2, 3, 14–22, 24–27, 29, 33, 35, 37–46, 48–52, 56–64

- DNL** Differential Nonlinearity. 58

- DR** Dynamic Range. 52

- FS** Full-Scale. 43, 52

- INL** Integral Nonlinearity. 58

- LSB** Least Significant Bit. viii, 19, 21, 46–49, 53, 57–59

- MOM-capacitor** Metal-Oxide-Metal Fringing capacitor. 59

- MSB** Most Significant Bit. 19, 25, 46, 57–59

- PDF** Probability density function. 47

- RS-latch** Reset/Set Latch. 35–38

- SAR** Successive-approximation. ii, v–vii, 2–5, 8, 9, 13, 14, 17, 21, 22, 25, 26, 31, 32, 35, 39, 43, 44, 48, 49, 51, 52, 64

- TI-SAR** time-interleaved SAR. 2

# Chapter 1

## Introduction

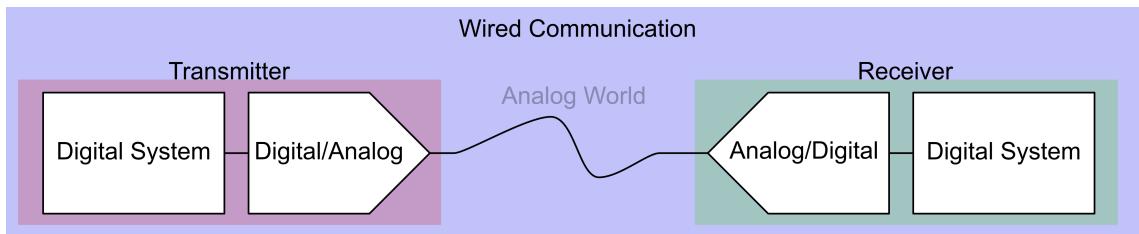

In today's modern society, communication systems are inescapable. Almost every person interacts with these systems on a daily basis, often without even realizing it. Engagements such as Internet usage, sharing digital images, and scheduling appointments are fundamental to modern life. A world without these systems seems like a distant past. These everyday communication systems face numerous challenges due to the necessity to process analog signals despite being within inherently digital frameworks. An ADC is essential to bridge this gap in various applications. High-speed and high-resolution ADCs are critical components, frequently employed in Ethernet networks within data centers and even in residential environments where Ethernet is used for tasks such as printing or accessing networked files. Fundamentally, these systems comprise a transmission and reception apparatus, as depicted in Fig. 1.1.

Figure 1.1: A one-way communication network between two digital systems

An essential requirement for all these communication systems is a good BER, which quantifies the number of bit errors relative to the total transmitted bits, indicating the integrity of the data. A system-level bit error occurs when the bit received in the digital domain at the receiver does not correspond to the digital code transmitted on the transmitter side. Maintaining a low BER is mandatory to ensure reliable communication. This necessity is particularly critical in applications

such as communication systems, where even minimal errors can significantly degrade operational performance.

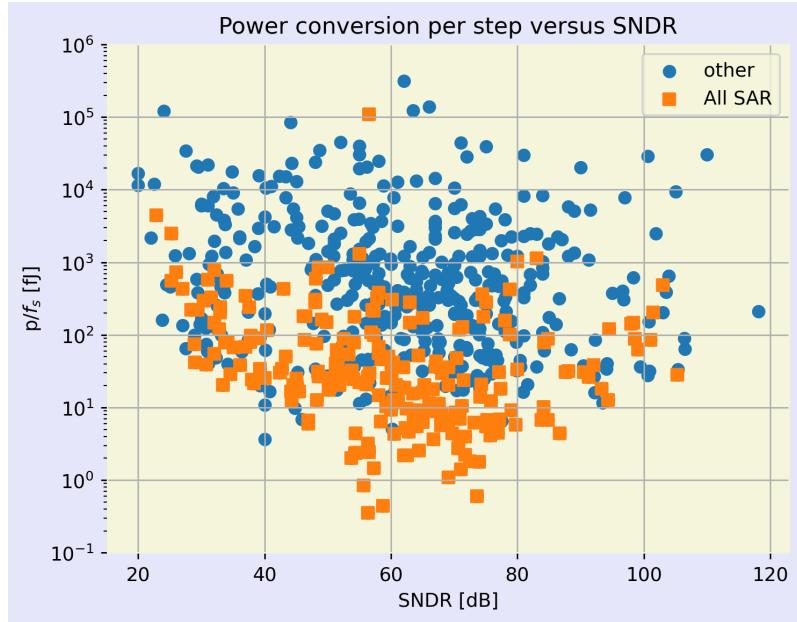

Various types of ADCs are used to transition from the analog to the digital domain, each with strengths and weaknesses. One of the most popular architectures is SAR ADC. This architecture represents a robust architecture within the ADC landscape and is used in a broad spectrum of applications. Obtaining the lowest power consumption throughout the resolution range, as illustrated in Fig. 1.2. Focusing on high-speed and high-resolution ADCs, synchronous and asynchronous SAR ADCs are used as single ADC solutions. In recent years, there has been a transition from SAR-ADCs to time-interleaved SAR (TI-SAR) and pipelined-SAR ADCs for enhanced performance compared to the SAR-only architecture [1]. These architectures employ synchronous and asynchronous SAR-ADCs as fundamental systems components. Therefore, this study will focus mainly on improving BER of synchronous SAR ADCs, thus improving SAR ADCs and laying the foundation for new and improved pipelined and TI-SAR ADCs.

Figure 1.2: ADCs taken from [1], power consumption versus SNDR

## 1.1 Synchronous SAR ADC

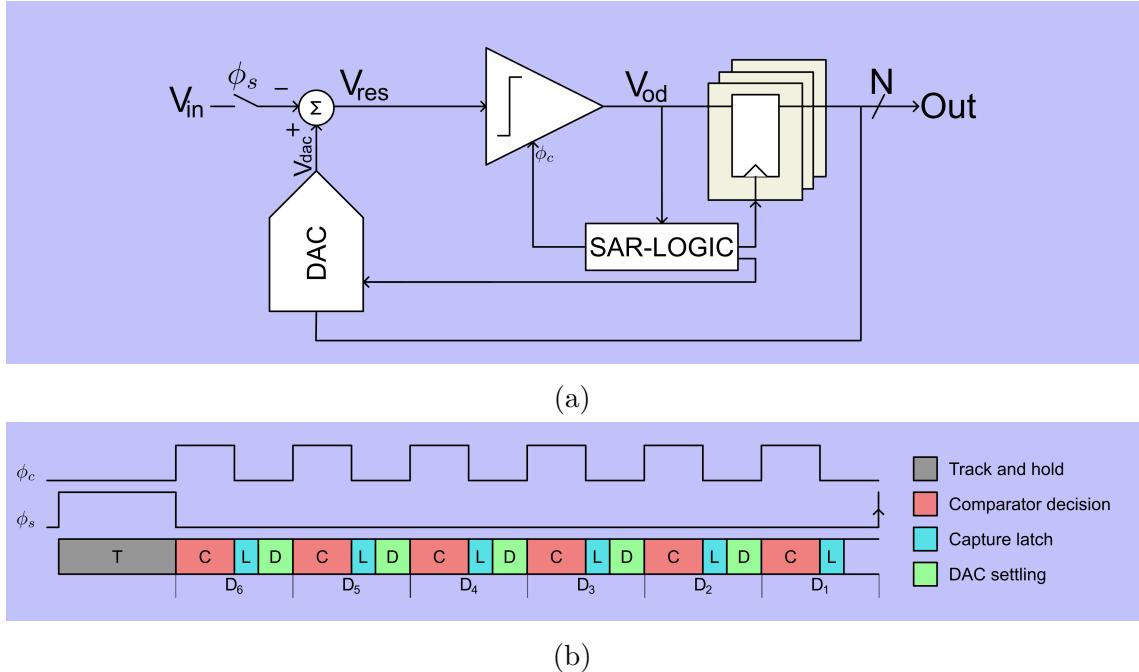

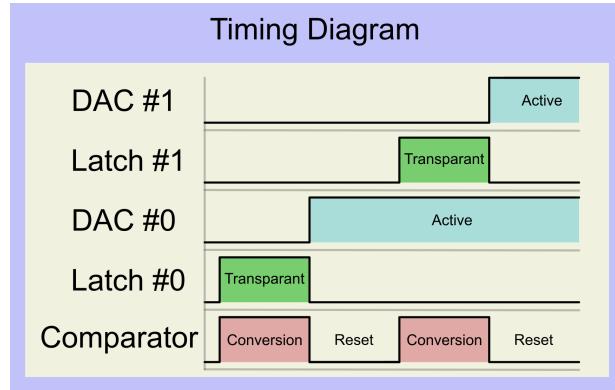

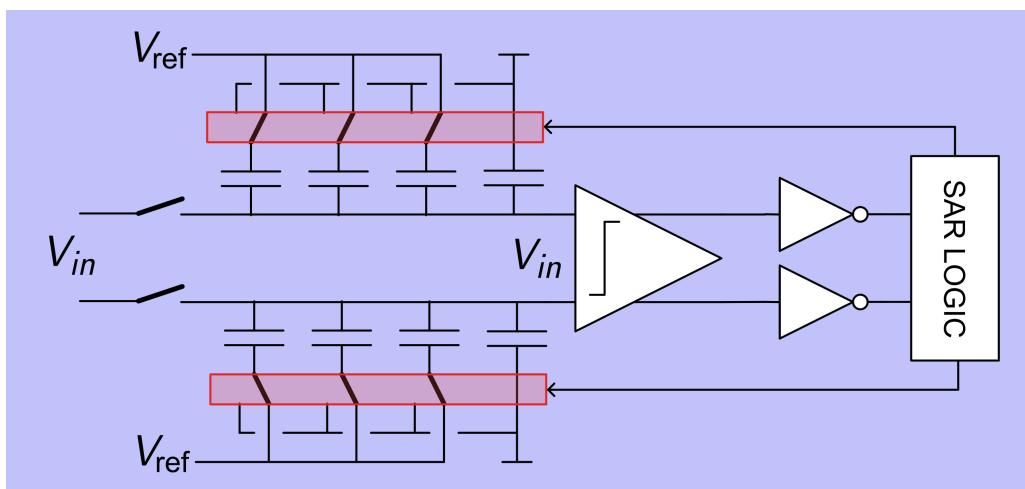

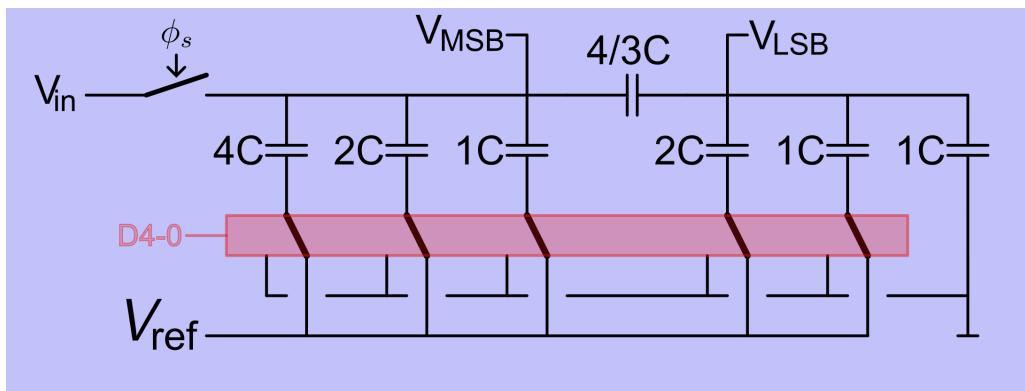

A synchronous SAR ADC consists of four main building blocks: a sample and hold, a DAC, a comparator and the SAR logic/memory, as illustrated in Fig. 1.3a. In Fig. 1.3b shows the corresponding timing response of the building blocks.

The SAR cycle starts with the sampling phase, indicated by the gray-shaded region identified as the tracking period. Once the voltage has been sampled on the

DAC, the comparator makes a comparison, indicated by the red rectangle in Fig. 1.3b. The output of the comparator is copied to the corresponding capture latch, indicated by the blue rectangle. Finally, the green rectangle shows an incremental step on the DAC. This comparison cycle is repeated  $N$  times, with  $N$  being the number of bits of the SAR-ADC, Fig. 1.3a shows a 6-bit ADC.

Figure 1.3: (a) A synchronous SAR ADC block diagram. (b) Timing diagram of the synchronous SAR ADC.

A fundamental aspect of the system is the interaction between the building blocks. The comparator has a finite time to accumulate gain, during which the capture latch remains transparent to the output of the comparator. In the subsequent phase, the comparator undergoes a reset while the capture latch stores the digital output of the comparator in the latch. The DAC proceeds with a step if the comparator output is valid.

As stated above, BER serves as an important metric for the integrity of the system's data. To estimate BER for the synchronous SAR ADC, a case where a bit error occurs must be studied. As an initial approximation, the comparator and the capture latch can be modeled as positive feedback blocks [2], exponentially building up a gain over time. When the comparator input voltage, denoted by  $V_{res}$  in Fig. 1.3a, is close to the comparator tripping voltage. More time is required to accumulate sufficient gain for a valid output. Given the SAR-loop architecture, which inherently constrains the available time, insufficient time may result in a no-decision, yielding a bit error in the output code. Essentially, a BER can be led back to a finite time in which the comparator's input signal was too close to the tripping point, resulting in

no decision from the comparator. The next chapter will provide a comprehensive analysis of metastability within the comparator.

## 1.2 Scope of the report

This thesis aims to improve the overall BER for synchronous SAR ADCs by fundamentally creating more time inside the SAR-loop for metastable events without slowing down the overall SAR loop.

The remainder of this thesis is organized as follows. Chapter 2 will focus on the comparator. Chapter 3 discusses a method for detecting metastability of a comparator. Chapter 4 incorporates the metastability detection circuit within the SAR-loop to mitigate THE BER of the system. Chapter 5 elaborates on the operational constraints imposed by dual-DAC configurations. Chapter 6 provides an in-depth analysis of all the components of the specified system. Chapter 7 validates the proposed enhancements through both analytical analysis and experimental simulations. Chapter 8 emphasizes the design considerations in the implementation of the fabricated validation chip. Chapter 9 concludes this thesis and presents future research directions.

# Chapter 2

## Comparator

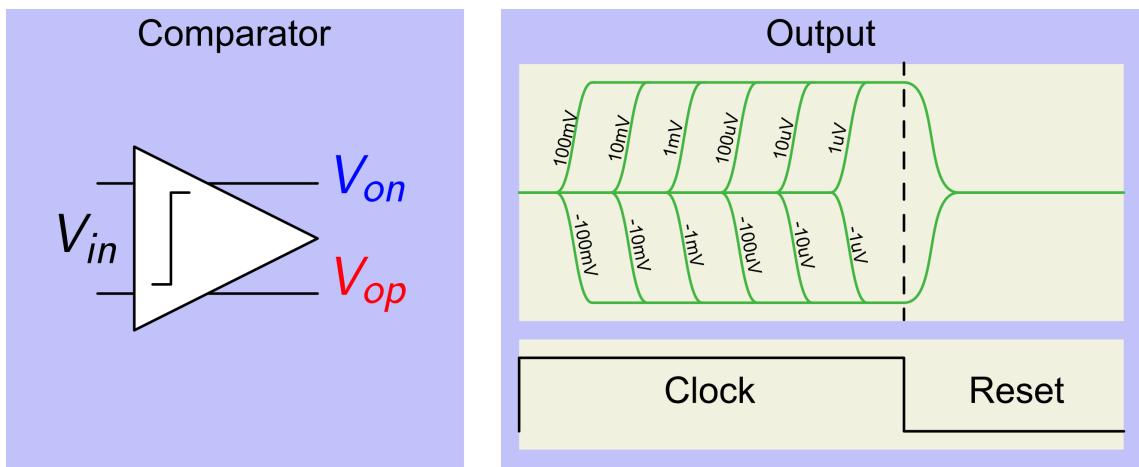

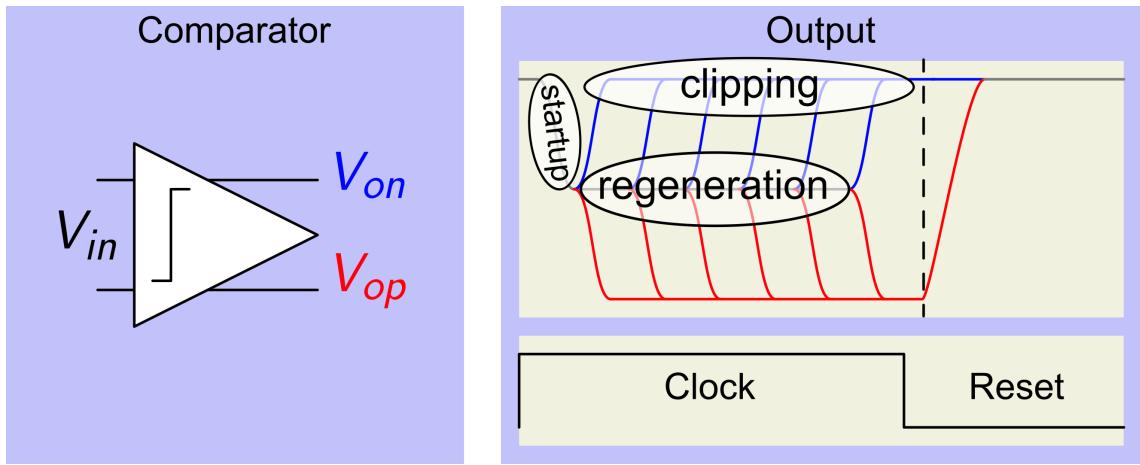

The comparator used in the SAR loop, as illustrated in Fig. 1.3a, has one main function: creating a large amount of gain in a short period of time, to achieve a complete (digital) decision. This gain is critical to accurately determine the polarity of the input signal, thereby ensuring the correct operation of the SAR loop. A clocked comparator creates the most gain in the shortest amount of time due to the use of positive feedback [2]. Given the intrinsic characteristics of a clocked comparator, the device has two distinct states: reset and active. The device is initialized to zero in the reset state, providing a consistent starting point for all conversions. In the active state, the comparator accumulates gain, determining the polarity of the input signal, as illustrated in Fig. 2.1. The comparator is active when the clock signal is high and enters the reset state with a low clock signal.

Figure 2.1: Transient of a clocked comparator with input signals varying from a  $\mu\text{V}$  to 100 mV, as indicated next to the curve.

During the time that the clock is high, the input signal is applied to the comparator. At the same time, the comparator enters the regeneration phase, accumulating

gain exponentially. Upon accumulating sufficient gain, the output voltage reaches the full digital logic voltage threshold, indicating a valid response. As illustrated in Fig. 2.1, the time required for a valid response depends on the magnitude of the input voltage, with more time required when the input voltage approaches zero.

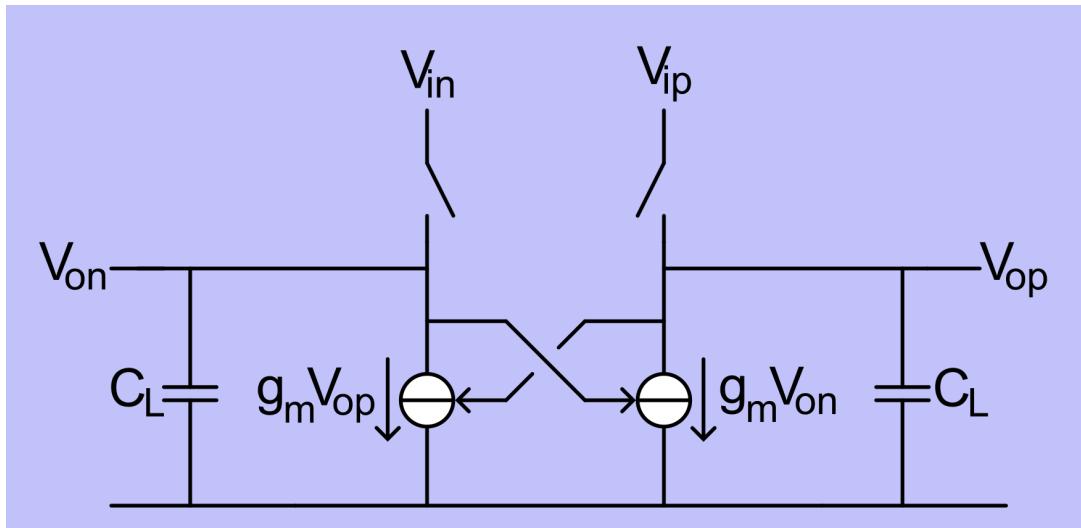

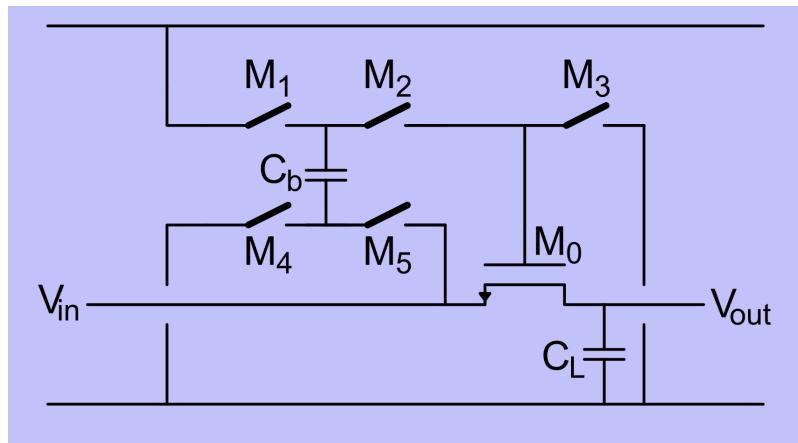

During the regeneration phase, positive feedback is implied to maximize the accumulation of gain in the system. This positive feedback is created by two transconductances ( $g_m$ ) whose outputs are cross coupled to the system's input. The comparator time constant and, thus, the device speed, are determined by the value of  $g_m$  of gm cells and the parasitic loading of the circuit ( $C_L$ ), as illustrated in Fig. 2.2

Figure 2.2: Exponential gain of the comparator with ideal transconductances.

During regeneration, the following equation holds:

$$V_{op} - V_{on} = (V_{ip} - V_{in}) \exp \frac{t}{\tau} \quad (2.1)$$

$$\tau = \frac{C}{g_m} \quad (2.2)$$

with  $\tau$  being the time-constant of the circuit defined in Eq. 2.2,  $C$  being the parasitic loading capacitance,  $g_m$  the differential transconductance of the system, and  $V_{in}, V_{ip}$  the input nodes and  $V_{on}, V_{op}$  the output nodes of the system. At  $t = 0$ , the input differential is sampled on the output differential, creating a starting voltage of  $V_{id}$  for the exponential gain.

## 2.1 Comparator output

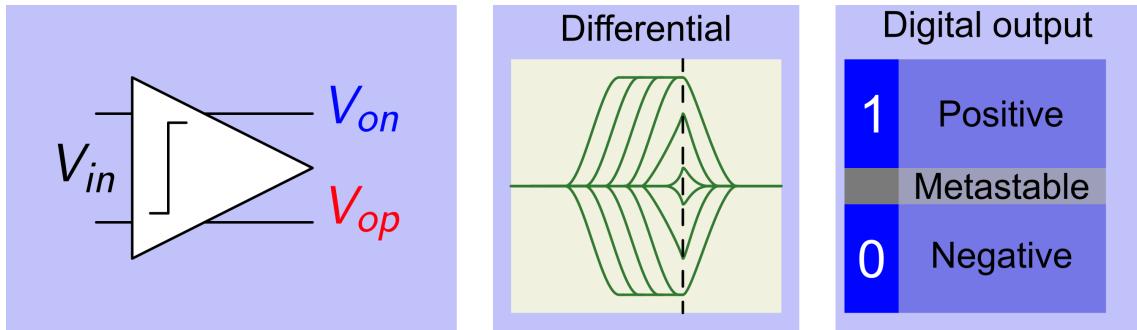

In Fig. 2.3, a comparator is shown that illustrates the differential output between the nodes  $V_{on}$  and  $V_{op}$ . Under the assumption of infinite available time for the

comparator, the differential output yields two primary digital codes, positive (1) or negative (0). However, limiting the available time of the comparator, a third region emerges. Within this region, the comparator does not accumulate enough gain; therefore, the differential output does not move significantly away from the initial starting point. With small input voltages, the gain of the comparator may be considerable, but the absolute voltage remains close to its initial value. When the output remains close to this initial value, the system cannot determine whether the output signal represents a digital 1 or a digital 0 and resides in the metastable state, as illustrated by the gray area in the output codes in Fig. 2.3.

Figure 2.3: Differential output of a comparator.

## 2.2 Timing

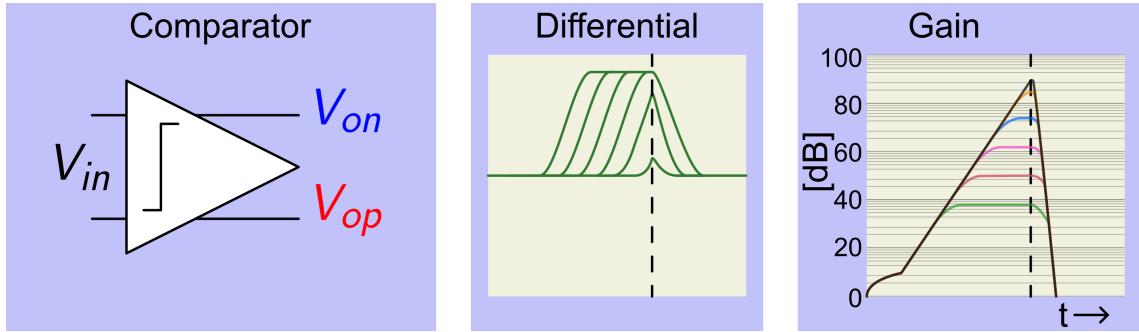

To quantify the width of the metastable region, an analysis of the system's transient response is performed. Observing the transient output shown in Fig. 2.4, it is evident that the differential output remains close to zero at the end of the conversion, indicating a metastable comparator. Using Eq. 2.1, the equation can be reformulated to calculate the time required for a valid response, leading to the following:

$$t_{valid} = \tau \ln \left( \frac{V_{od}}{V_{id}} \right) \quad (2.3)$$

with  $V_{od}$ ,  $V_{id}$  being the differential output and input voltage, respectively. From this equation, it can be shown that for small input values, more time is required to get to complete digital levels. In Fig. 2.4, the accumulated gain for various input values is illustrated. A small transitional region is present where the comparator is activated. The comparator accumulates a linear gain within this region while transitioning the output nodes into the regeneration phase. This linear gain is depicted by the asymptotic segment at the beginning of the gain plot. Once enough gain is accumulated, the clipping of the output nodes of the comparator to the supply rails results in plateauing of the gain-curve. If the input voltage is too close to zero, there is insufficient gain in the system.

Figure 2.4: Differential output transient and gain of a comparator, with four valid and two metastable responses.

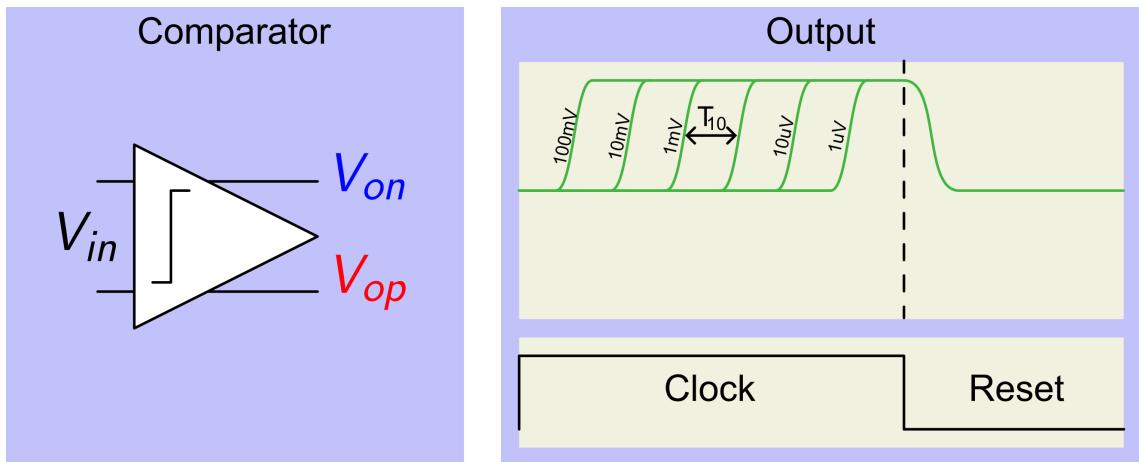

The device's time-constant is used to quantify the operational speed of the comparator. In Fig. 2.5, a comparator is depicted, demonstrating six input voltages of identical polarity, each separated by a decade. To calculate the additional time required to resolve an input signal that is an order of magnitude smaller, one can refer to Eq. 2.3, to find:

$$\Delta t = \ln(10) \cdot \tau \approx 2.3 \cdot \tau \equiv T_{10} \quad (2.4)$$

Figure 2.5: Output transient of a comparator, with input voltage steps taken a decade apart.

Due to the nature of the SAR loop, a limited time is available to the comparator. For example, if the time allotted to the regeneration phase is  $6 \cdot T_{10}$ , the maximum resolvable input signal is  $1\mu V$ . Should the input signal fall below  $1\mu V$ , the output of the comparator becomes metastable, inducing an error within the SAR loop. These types of errors will be referred to as metastable bit errors. The proportion of bit errors to error-free instances is referred to as BER. This thesis aims to reduce the BER within the SAR loop without slowing down the speed of the SAR algorithm.

# Chapter 3

## Metastability

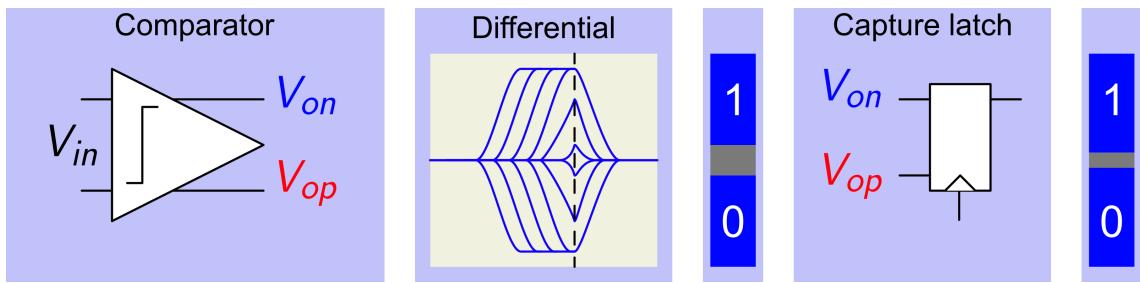

In a conventional SAR ADC, the output of the comparator is stored by the capture latch. The capture latch, implemented as an RS-latch, is also characterized by positive feedback, which enables the accumulation of additional gain during a metastable comparator decision while storing the comparator output for digital processing. At the end of the conversion, the capture latch effectively copies the output voltage of the comparator. As a result, it duplicates the metastable region of the comparator, only reducing its width by adding more gain, as illustrated in Fig. 3.1. The magnitude of this reduction is directly proportional to the additional time allocated to the capture latch.

Figure 3.1: Metastable output voltages of the comparator and capture latch.

In the classical implementation of comparator and capture latch, only a single output from the comparator is used. Thus, only one bit of information can be retrieved per comparator conversion.

Rather than observing the comparator differentiately, both output nodes can be examined independently. In the case of full decisions, both outputs are exactly opposite to each other, but in the case of metastability, their individual outputs are not the inverse of each other, and more information can be extracted from the comparator. This additional information will become a key to reducing BER, as will be described in this thesis.

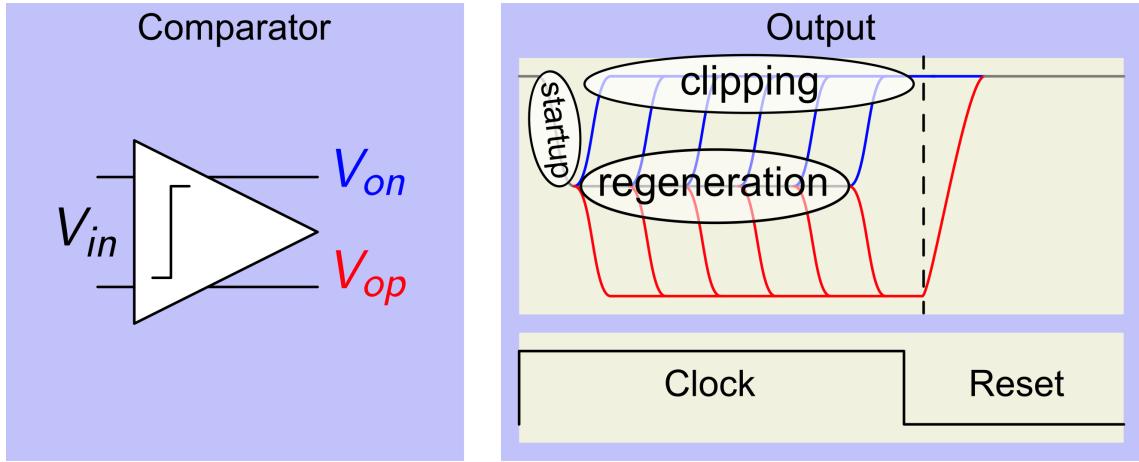

For practical reasons, in this thesis we will use a "Strong arm" latched comparator [3]. In the following, we will characterize three distinct regions: startup, regeneration, and clipping, as illustrated in Fig. 3.2. Initially, the system begins in a known state, called the reset state of the device. For the strong-arm latch, both output nodes are placed at the upper supply rail in this region. Upon activation of the system, both outputs transition from the supply rail to the natural common-mode voltage of the latch, referred to as  $V_{meta}$ . During the regeneration phase, the comparator utilizes the positive feedback element and produces exponential gain over time. The clipping region is characterized by the outputs moving progressively slower as they approach the supply rails.

Figure 3.2: Input voltage sweep with the single-ended response of the comparator.

The system exhibits a metastable conversion when the comparator remains in the regeneration phase until the end of the cycle. Consequently, both output nodes remain close to  $V_{meta}$  due to insufficient gain accumulation, as illustrated in Fig. 3.3. For correct operations, it is required that both outputs are positioned at opposite supply rails.

Figure 3.3: Transient output waveform of metastable and valid responses, with the same polarity input voltage.

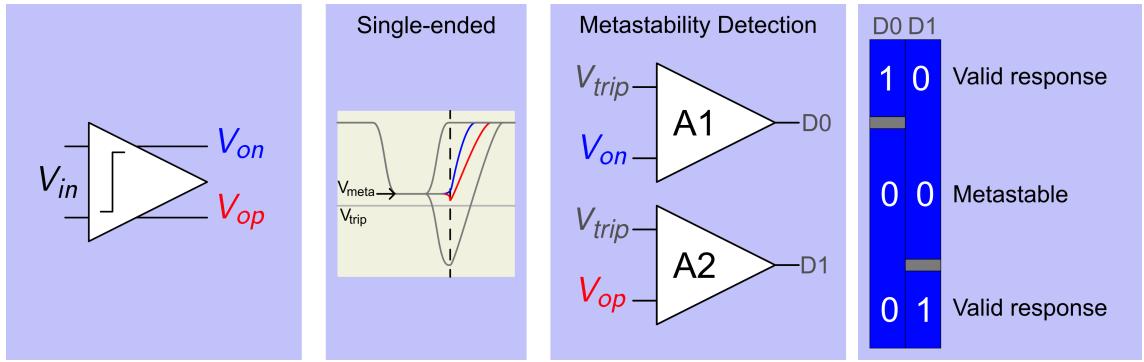

By comparing this output voltage with  $V_{meta}$ , metastable events can be detected. By implementing a gain block after the primary comparator with a specified tripping voltage, a detection scheme can be created to identify instances of metastability. Within our system, both outputs initialize from  $V_{dd}$ . Setting the tripping voltage of the gain block above  $V_{meta}$  will induce a trigger during the initialization phase. In contrast, setting the tripping voltage below  $V_{meta}$  will ensure that only valid triggers occur during the conversion phase.

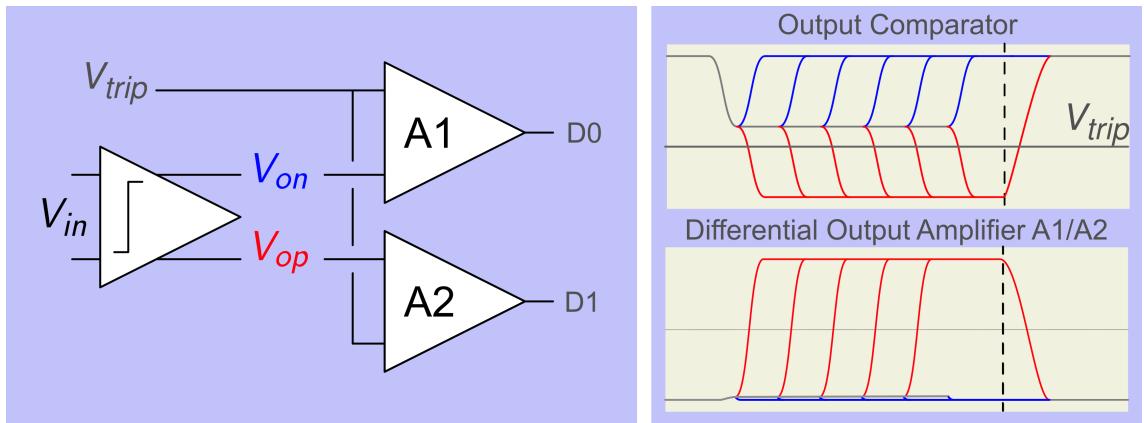

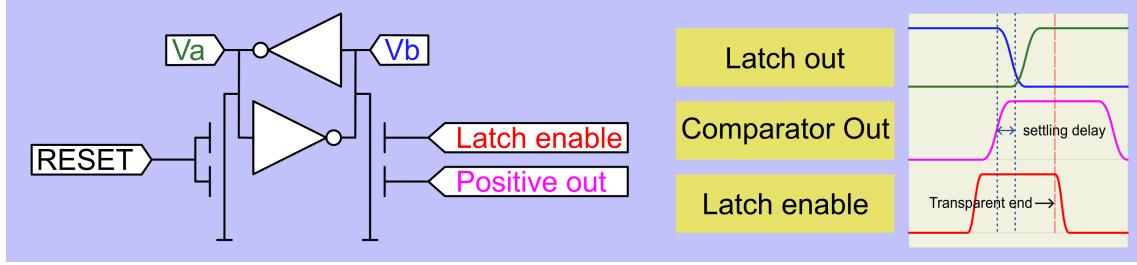

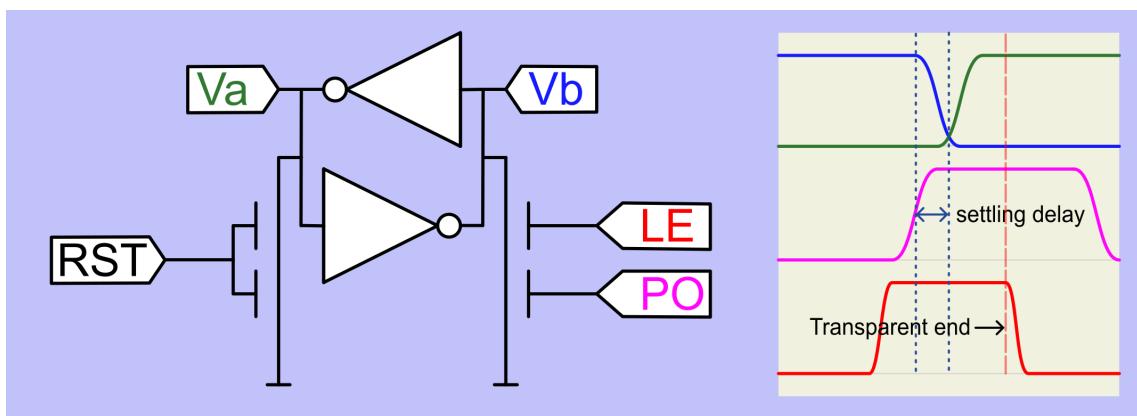

Figure 3.4: Metastability detection circuit for comparators

The various results of the metastability detection circuit are shown in Fig. 3.4. In case of an easy decisions,  $V_{on}$  or  $V_{op}$  will reside at opposite supply rails at the end of the conversion. Subsequently, the amplifiers following the comparator will saturate to the supply rails, resulting in a digital output of 1/0 or 0/1, as illustrated by the “Valid Response” in Fig. 3.5. In contrast, both output nodes remain at  $V_{meta}$  throughout the conversion in metastable scenarios. The input of the amplifier stabilizes at  $V_{meta}$  and  $V_{trip}$ , producing a differential voltage of  $V_{meta}-V_{trip}$ . Assuming the amplifier has sufficient gain, this scenario leads to an amplified output of  $V_{ss}$ , resulting in a digital combination of 0/0 at the output.

Figure 3.5: Transient response of amplifiers A1/A2 metastability detection circuit.

Although the initial comparator exhibited metastability and could not supply a full digital decision, the subsequent amplifiers do not exhibit metastability and solely provide supplementary gain to the system. This induces an offset of the metastable point of the comparator. However, when the output of the comparator comes closer to  $V_{trip}$  of the amplifier, even the output of the amplifier will not provide a full digital signal.

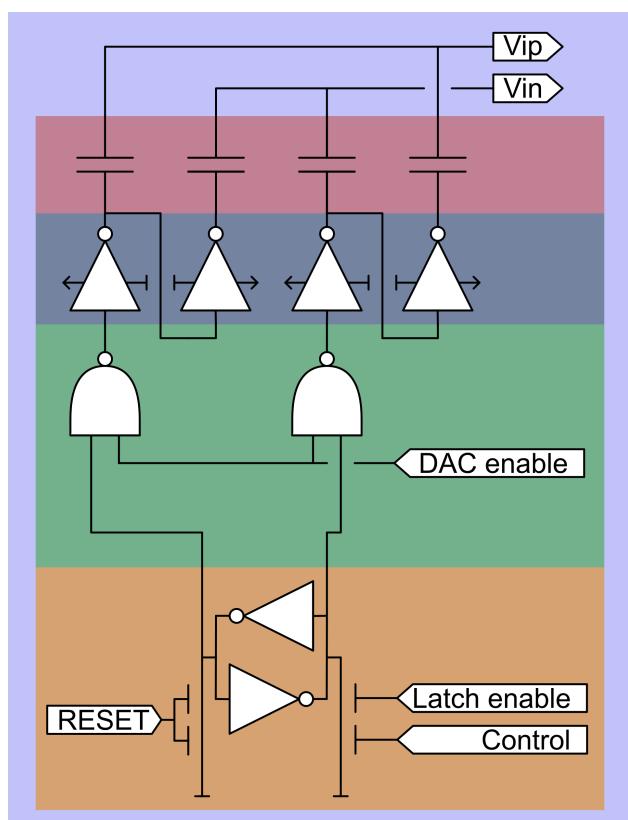

### 3.1 Dual capture latch

In the following section, we will make use of the additional information provided by the two outputs of the comparator. Two capture latches are required to store the two independent outputs of the amplifier. Both latches independently store the amplifier's digital value for digital processing. Given the symmetric nature around the voltage  $V_{meta}$  of the comparator, only one of the two amplifiers undergoes a polarity change during the conversion process. By giving each amplifier its own capture latch, as illustrated in Fig. 3.6, ensures that at any given time/voltage instance, only one of the two capture latches can be metastable.

Figure 3.6: Output regions of the comparator, amplifier, and capture latch chain

One of the capture latches can experience metastability when the amplifier's output is aligned with the tripping voltage of the capture latch at the end of the cycle. Concurrently, the other amplifier maintains its output at  $V_{ss}$ , resulting in no change in the decision and thus ensuring a consistently valid response. The former three output regions of the single comparator are now segmented into five distinct regions: two metastable points of the capture latches and three valid regions. The width of the middle region, which produces a digital output of 0/0, is controlled by the voltage differential between  $V_{trip}$  and  $V_{meta}$ .

The following chapter will show that the principal role of this detection circuit is to take advantage of both outputs of the comparator to create more time for metastable events inside the SAR loop.

## Chapter 4

# Proposed SAR loop with improved BER

As an initial thought, one might think that the detection of metastable events implies the potential for their compensation. However, the existing literature indicates that attempts to mitigate metastable events merely displace these points, failing to reduce their occurrence and instead generating new metastable errors [4]. Metastability is critically important, yet often misunderstood in the context of comparators and ADCs [5, 6]. A fundamental principle in reducing metastability within comparators is to provide the comparator with more time.

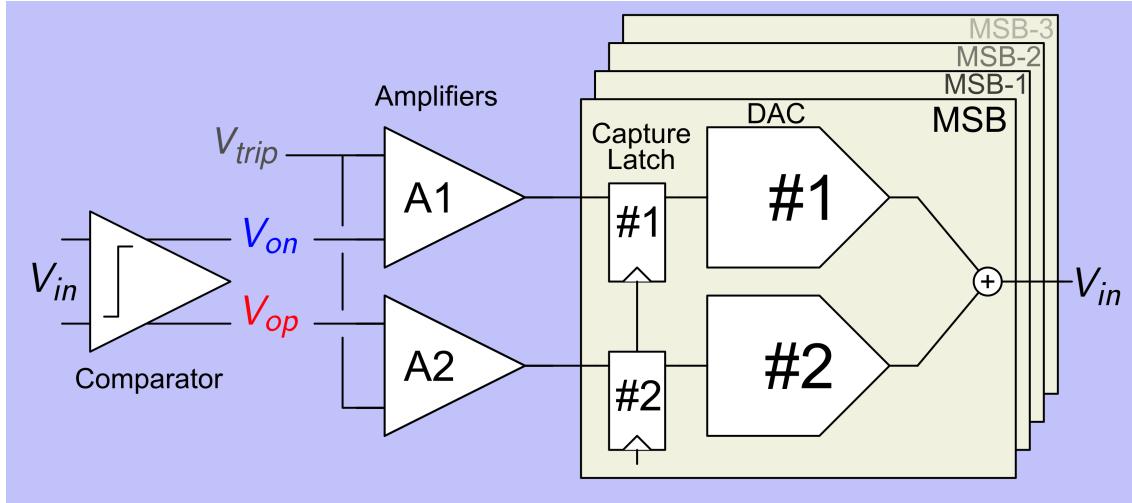

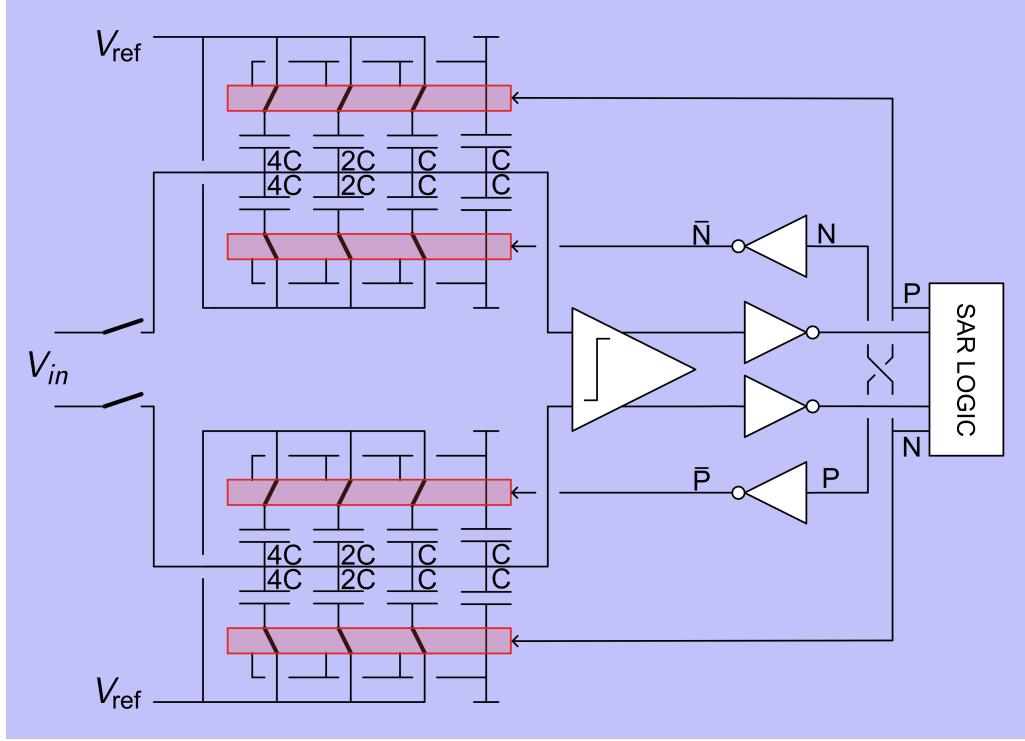

The objective of incorporating the metastability detection circuit inside the SAR loop is to extend the duration available for the capture latches to resolve metastable events parallel to the normal operation of the SAR loop. Implementing the metastability detection circuit within the SAR loop requires two capture latches, each connected to two independent DAC elements per bit, each with half the value of the original DAC element. This architecture shall be called the dual DAC system, whereas the conventional SAR-loop will be called the single DAC system.

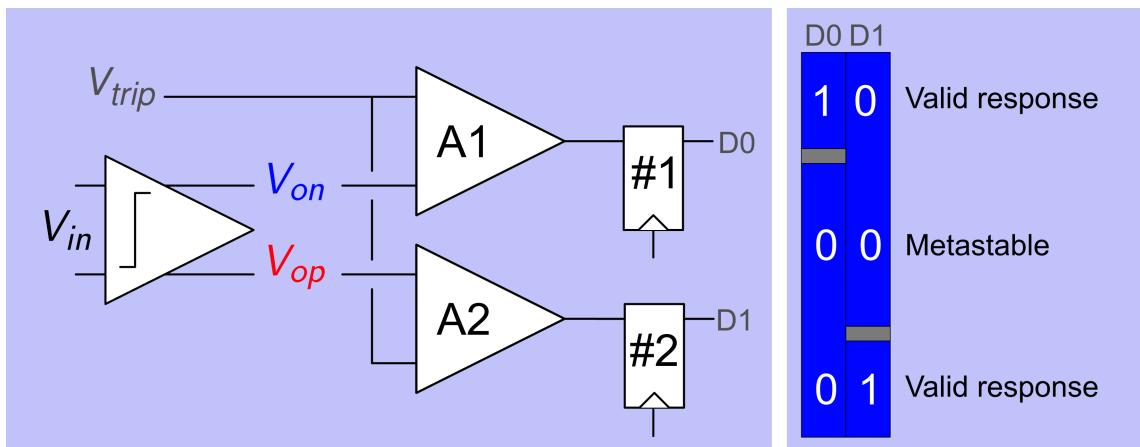

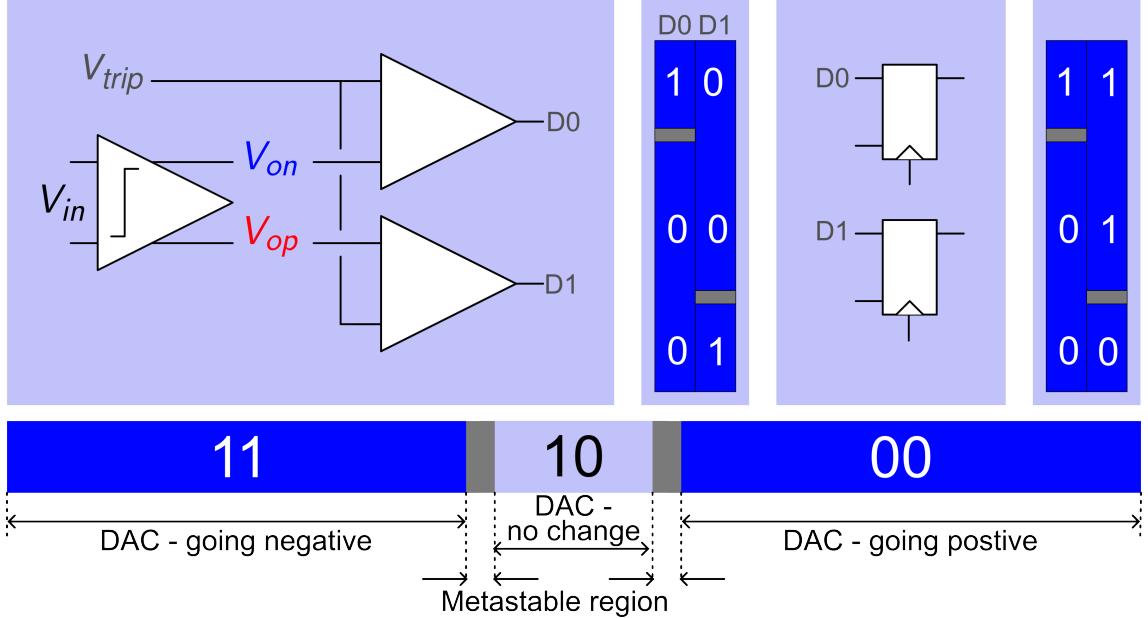

### 4.1 Switching scheme

A switching scheme is formulated based on the digital outputs, D0 and D1, of the metastability detection circuit, as illustrated in Fig. 3.4. For the valid responses 1/0 and 0/1, the DAC needs to move up or down, respectively. Upon entering the original metastable region of the first comparator, the voltage level on the DAC approaches zero, implying that no further steps are necessary. Specifically, before the end of the cycle, no voltage should have been added or subtracted from the DAC. This results in the switching scheme depicted in Fig. 4.1. The region denoted by ‘DAC - no change’ will henceforth be referred to as the dead-zone of the system.

A digital inversion has been incorporated into one of the two capture latches to facilitate system comprehension.

Figure 4.1: Metastability detection circuit of the comparator with the designated switching scheme. The capture latch connected to D1 has an additional inversion.

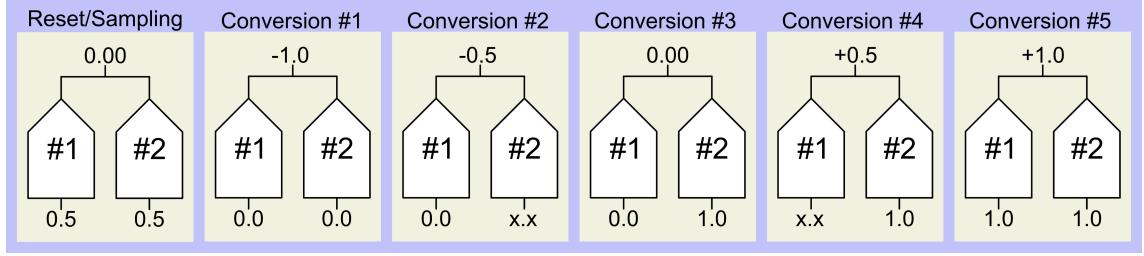

The conventional single-bit DAC structure is now replaced by a two-bit dual-DAC system, the original three distinct regions now are divided into five distinct regions comprising positive or negative DAC transitions, a dead-zone, and the two new metastable regions. These distinct regions are visualized by their respective DAC halves, as illustrated in Fig. 4.2. The digital inputs are located at the base of the DAC symbol, with the effective DAC voltage denoted at the top. The numeral inside the DAC symbol represents the differentiation between two DAC halves. The digital inputs of the DAC elements correspond to the digital outputs of the metastability detection circuit, specifically the output nodes of the capture latches. The initial state of the digital input is characterized by the reset value of 0.5. A transition of the digital input to 1 indicates a positive step on the DAC, and a transition to 0 denotes a negative step. Fig. 4.2 shows the reset and the 5 different possible situations.

The reset/sampling region serves as the starting point of a DAC element, where conversion states 1 and 5 correspond to a complete increment or decrement, respectively. Conversion state 3 represents the middle region, which does not produce an effective change in the DAC output. Both DAC units undergo complementary transitions during this state, resulting in a net zero change at the output. This phenomenon is explained through an analysis of the digital inputs; DAC 1 transitions from 0.5 to 0, taking a step down, while DAC 2 transitions from 0.5 to 1, taking a step up.

Figure 4.2: The different switching ranges of the complete DAC.

Conversion states 2 and 4 represent transient conditions in which one of the capture latches is metastable and actively resolves the metastability by building up more gain in the capture latch. Specifically, during conversion state 2, the capture latch affiliated with DAC 2 is metastable, while the capture latch linked to DAC 1 takes a decision. This puts a step onto the DAC by DAC 1, concurrently with DAC 2 actively resolving its metastability. Conversely, a similar scenario occurs in transition state 4, with the capture latch associated with DAC 1 being metastable while the other latch takes a decision. Since metastability is inherently time dependent, these transient states are temporary, with the result, given enough time, that the system always ends in one of the stable regions, namely conversion states 1, 3, or 5.

## 4.2 Dual-DAC ADC

Fig. 4.3 shows the switching scheme defined for a single bit. Every bit has two independent capture latches and two independent DAC units.

Figure 4.3: System overview of a 5-bit ADC, sampling circuit excluded.

Both amplifiers (A1 and A2) are connected directly to the two outputs of the comparator. The outputs of the amplifiers are connected to the capture latches

for the their corresponding bits. The SAR logic dictates the activation sequence of these capture latches, ensuring that the correct capture latches are transparent at the correct time intervals. The DAC unit is directly connected to the capture latch. Auxiliary logic is incorporated within the DAC element to ensure an idle state in the absence of valid signals. Consequently, both outputs of the DAC are directly connected to the input of the comparator, thus completing the SAR loop.

### 4.3 SAR cycle

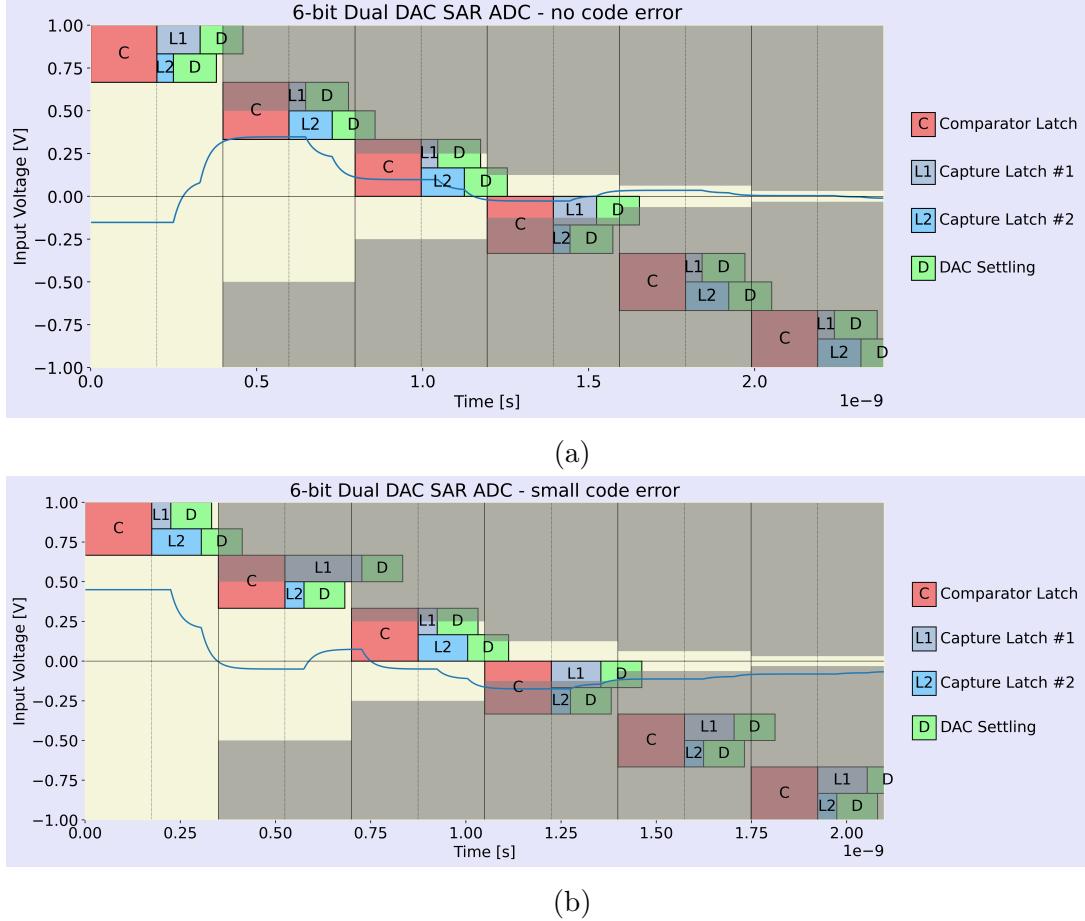

Fig. 4.4 illustrates the conversion cycles of single and dual DAC ADCs. The upper section of the illustration shows the single DAC ADC, whereas the lower section illustrates the dual DAC version. The blue line represents the effective DAC voltage, starting from the system's level input voltage. The dotted vertical lines denote the end of the comparator's comparison phase, and the gray vertical lines signify the end of the cycle. The red boxes mark the required time for the comparator; in scenarios of metastable decisions, the red box spans half the cycle, fully utilizing the available time for the comparator. In contrast, a gap is observable between the comparator and the latch for an easy decision. The single DAC is characterized by a single capture latch depicted in gray, in contrast to the dual DAC, which employs two capture latches illustrated in gray and light blue, with the DAC settling depicted in green.

Figure 4.4: A 6-bit Dual and Single DAC conversion comparison with input voltage 0.32

The width of the depicted boxes accurately reflects the required time per component, according to simulation results. The settling time (green rectangle) of the

DAC is defined such that each step remains within  $\leq 0.5$  LSB, ensuring the absence of DAC settling errors. The DAC is directly driven by the capture latch output; consequently, the DAC follows immediately after the latch.

As in the dual DAC system, the metastable zones of the two latches are always separated by the dead-zone (4.1) and hence only one latch per bit can enter a metastable state. The harder decision inherently requires a longer time to resolve, causing a delay in the DAC response compared to an easy decision. When each decision is straightforward, as shown in Fig. 4.4, no step artifacts appear. In contrast, when the input voltage is close to the amplifier's  $V_{trip}$ , the complexity of the hard decision increases, extending the time required to resolve the (short) metastability. This phenomenon manifests itself as a step artifact on the DAC output before the end of the first cycle, as illustrated in Fig. 4.5.

Figure 4.5: A 4-bit Dual and Single DAC ADCs comparison with the Dual DAC showing a step artifact.

## 4.4 Metastable events

To provoke a metastable event within the dual DAC system, the input voltage is moved closer to the tripping voltage of one of the amplifiers; see Fig. 4.6 (bottom image). The decision on capture latch 1 becomes increasingly difficult, requiring additional time to resolve the metastability. In contrast, capture latch 2 is not metastable, resulting in a discrete step on the DAC. Given that each DAC element is split into two equal halves, the magnitude of each step corresponds to the subsequent full-scale conversion step. This configuration facilitates an easy decision in the subsequent cycle in the presence of a metastable event, thereby avoiding a code error.

The Dual DAC is always capable of avoiding a code-error in this situation because the weight of the metastable half-DAC is equal to the weight of the next step in the SAR. Furthermore, the dual-DAC architecture attenuates the maximum metastable error from  $2^{N-2}$  LSB to  $2^{N-3}$  LSB.

Figure 4.6: The first two bits of a Dual and Single DAC ADCs in the case of a metastable event.

When comparing metastable events between dual and single DAC configurations, it becomes evident that the dual DAC configuration exhibits an extended period of time to resolve metastable events. For the single DAC system, a metastable Most Significant Bit (MSB) decision sustains a metastable state in the MSB-1 decision due to a delay in the MSB decision. In contrast, in the dual DAC system, the DAC element connected to capture latch 2 makes a step, while capture latch 1 remains metastable in Fig. 4.6. Consequently, the DAC voltage transitions to  $-0.250$  following the decision initiated by capture latch 2, facilitating a straightforward decision for the next conversion, while capture latch 1 remains metastable. The contribution of both MSB-1 DAC elements, each providing  $0.125$ , combines to a total step of  $0.250$ . The dual DAC system continues to function effectively, even with a metastable capture latch 1, without making a bit error.

In Fig. 4.7, two scenarios of 6-bit conversions in a dual DAC ADC are presented. In the upper section, a conversion is shown in which the metastability of capture latch 1 of the first bit is resolved before the beginning of the comparison phase of the third bit. This facilitates a straightforward decision for the third bit. Conversely, the lower section illustrated a conversion in which the metastable event at capture latch 1 resolves after the beginning of the comparison phase of the third bit. This

delayed step yields a hard decision for the third cycle, inducing an erroneous step and ultimately causing a bit error.

Figure 4.7: Two conversions of a dual DAC ADC. The upper conversion exhibits no bit error, but the lower conversion shows a bit error.

To quantify the time advantage gained by using the dual DAC system, the available time of the single DAC system needs to be known. Within an idealized and noise-free environment, a metastable initial decision implies that the capture latch has not resolved the input voltage before the next cycle, rendering the second decision inherently metastable. As a result, the single-DAC system is limited to one cycle for gain accumulation.

For the dual DAC system, if a capture latch is metastable throughout the entire cycle duration, a half step is introduced to the DAC. In the next cycle, this step is reversed, restoring the initial voltage on the DAC. Consequently, metastability is reinstated by the third cycle, perpetuating the previous loop. To disrupt this loop, the capture latch must resolve its metastability before the comparison phase of the third cycle.

A comparison of both systems reveals that, in contrast to the singular conversion cycle used for gain accumulation in the conventional design, the dual DAC system engages in two distinct cycles to accumulate gain, thus attenuating the BER of the system.

# Chapter 5

## Dual-DAC limits

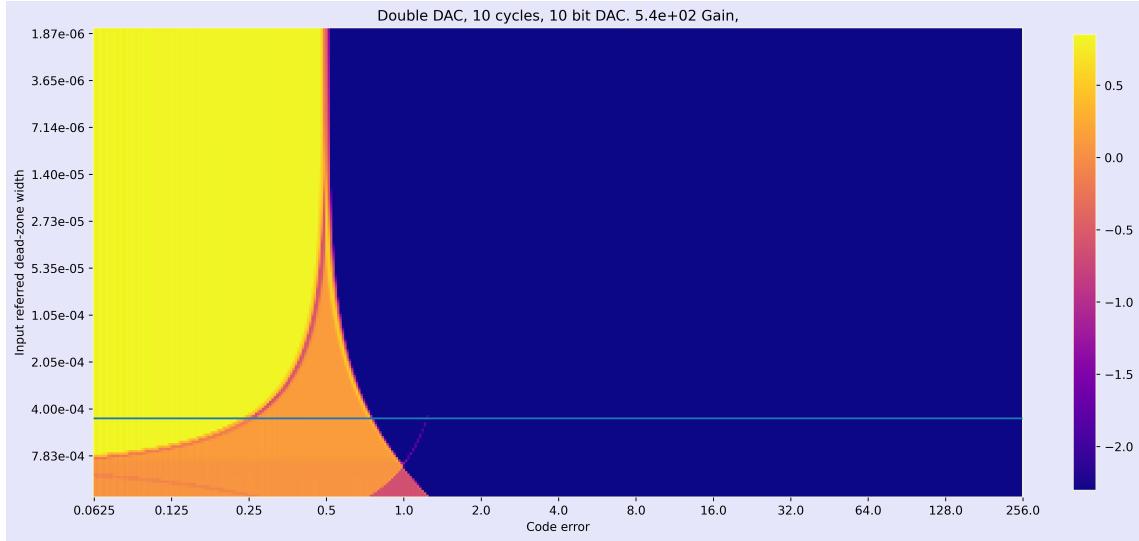

With the advantages of the dual DAC configuration shown, the boundaries of the dual DAC SAR ADC will be analyzed. A test bench configuration comprising an ideal sampler, comparator, capture latches, and DAC units has been constructed to validate and quantify these boundaries. This test bench facilitates the quantification of code errors within the system and the capability to modulate system parameters and evaluate the system's effective response. A code error is the difference between the digital output and the analog input code, representing the error between these two values. Without non-idealities in the system, the output code should be within 0.5 LSB of the input signal. The constraint of 0.5 LSB arises from the quantization noise in the system.

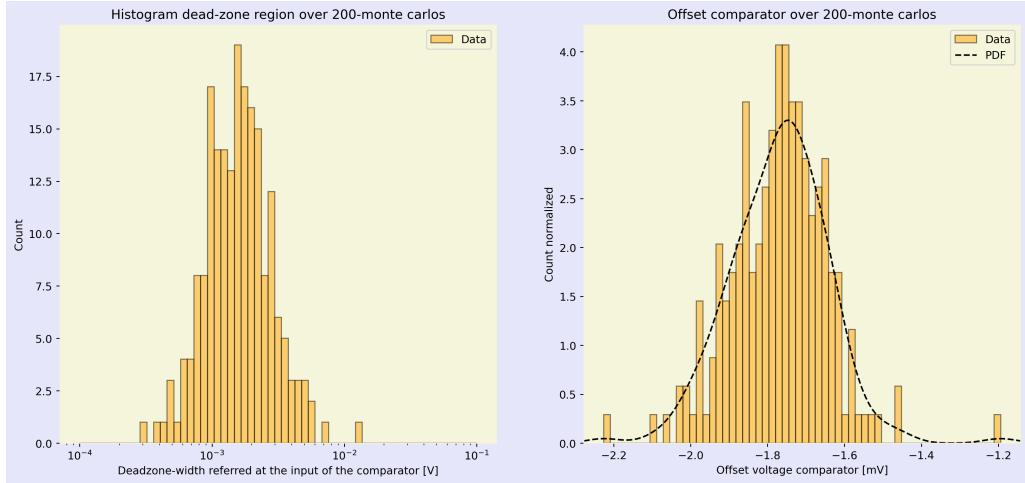

A histogram has been constructed from code errors to analyze numerous input points, as shown in Fig. 5.1. Three distinct configurations of 10-bit ADCs are present: ideal, noisy, and metastable ADCs. With the ideal ADC, all code errors are confined within 0.5 LSB, thus indicating optimal system operation. With the introduction of noise in the comparator, uncertainty is introduced about the accuracy of the system, culminating in errors extending up to 4 LSB. An increase in noise levels directly amplifies these corresponding errors. Metastable errors arise from limiting the available time of the comparator, which consequently reduces the accumulated gain in the system. This constraint induces metastable events in the comparator, leading to exponential code errors with a power of 2.

The dual DAC ADC boundaries can be systematically investigated by this created test bench. The dead-zone is characterized as the voltage range in which the single SAR ADC was defined as metastable. In contrast, the dual DAC SAR ADC stops the effective DAC stepping within this region, as illustrated in Fig. 3.4. For optimal system performance, it is essential to define two limits corresponding to the lower and upper limits of the dead-zone.

Figure 5.1: Histograms of three configuration ADCs

## 5.1 Upper limit dead-zone

Let's start with the upper limit of the dead-zone. Upon the comparator's input voltage entering the dead-zone, no steps will be made on the DAC. The system continues to operate with the remaining conversion, because in theory nothing is changed on the DAC-side the system thus will stay within the dead-zone, creating no further effective steps. Provided that the dead-zone is precisely defined below 0.5-LSBs, the resolution of the system will remain unaffected. This is because the DAC voltage resides within the system's quantization noise.

Increasing the dead-zone beyond 0.5-LSBs, for instance, to 8-LSBs, results in a corresponding loss of 8 LSBs of resolution. This is illustrated in Fig. 5.2, which depicts the code errors of two dual DAC SAR ADCs, with the distinguishing factor being the width of the dead-zone.

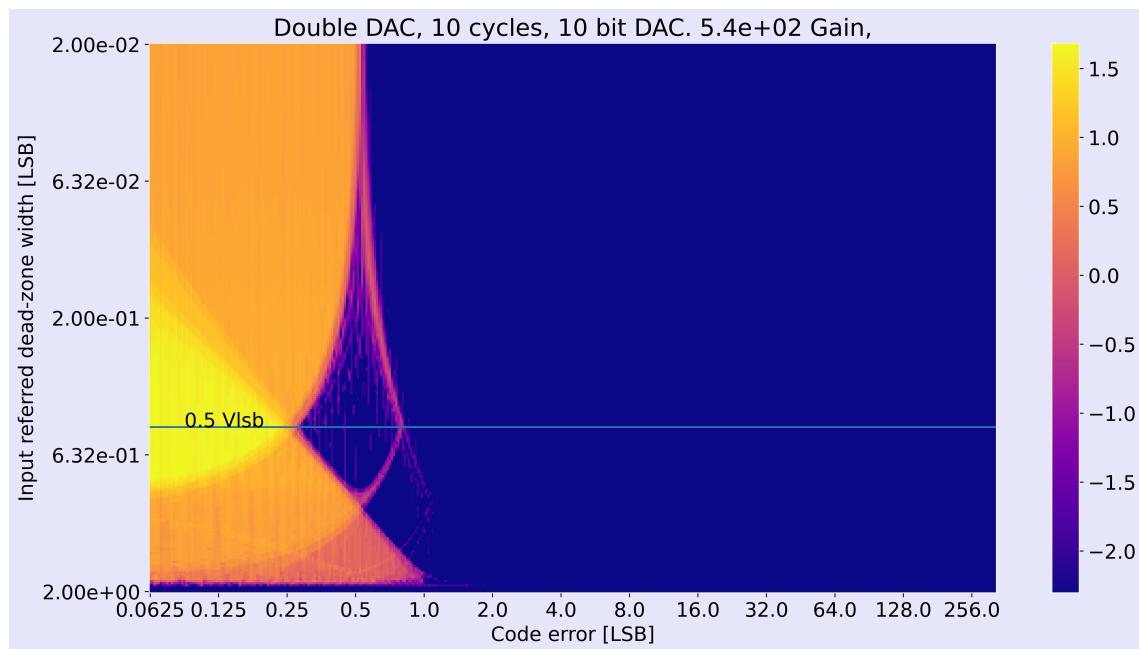

In the following, we will sweep the width of the dead-zone to fully understand the entire spectrum of the dead-zone width, enabling the comparison of multiple histograms. The histogram can be flattened and superimposed on an image for an adequate comparison, as demonstrated in Fig. 5.3. In this figure, the numerical information on the Y-axis in Fig. 5.2 is shown as a color code. Code errors are still represented on the X-axis, while the dead-zone width (input referred) is on the Y-axis.

Numerous phenomena are depicted in Fig. 5.3; the foremost is the possibility of attaining a resolution exceeding the system's quantization threshold. This assertion is proven by the majority of code errors below 0.5 LSBs for dead-zone widths. Furthermore, some code errors demonstrate an asymptotic trend that is converging toward the quantization noise threshold.

Figure 5.2: Code error using two dead-zone widths

Figure 5.3: A showcase of quantization errors due to dead-zone limits

### 5.1.1 Increased ADC resolution

Focusing on the foremost artifact, the dual DAC system, as indicated by its name, employs two DAC segments, thereby facilitating intermediate steps. During each comparator comparison, two bits of data are retained instead of the conventional single bit, thus increasing the information per conversion. Typically, these two bits are complementary and do not impart additional information. However, when the voltage is within the dead-zone, these two bits provide additional insight into the input signal. The extent of this additional information depends on the width of the dead-zone, with a larger width allowing for more information acquisition. Should we create uniform region sizes, as illustrated in Fig. 5.4, a 1.5-bit system is shown, often used in pipeline ADCs [7].

Figure 5.4: Dead-zone width modification to 1.5-bit system.

In the dual DAC system, the largest allowable dead-zone width is 0.5-LSB. At this specified width, the most additional information per conversion is stored when utilizing  $N+1$  bit storage elements. Increasing the dead-zone width above this limit reduces the system's effective resolution.

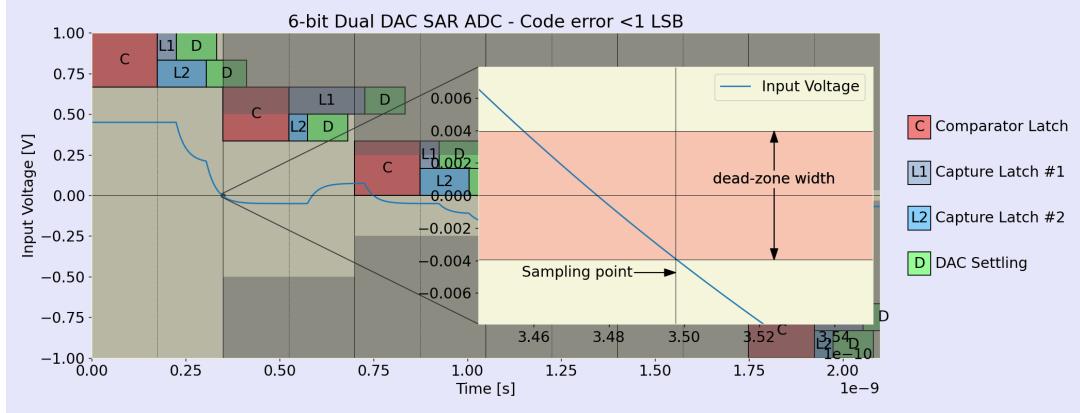

### 5.1.2 DAC settling artifact

With the improved quantization noise explained, the minor fraction of code errors will be analyzed. Simulating multiple input values, an asymptotic behavior was found in the quantization noise of the system, as illustrated in Fig. 5.3 by the thin yellow line, curving between a code error of 1.3-LSB and down to 0.5-LSB. To focus on this phenomenon, the input values that show the corresponding code error are extracted. A new simulation is performed using these input values. In this simulation a 6-bit ADC will be used, to make it easier to see the voltage steps on the DAC, as illustrated in Fig. 5.5a.

Figure 5.5: 6-bit Dual DAC SAR ADC with a gray area indicating the available back-end ADC range, (a) correctly operating, input voltage does not enter the gray area. (b) false trigger of the dead-zone resulting in a code error.

The correct operation of the SAR ADC is illustrated in Fig. 5.5a; the shaded region denotes the voltage range of which the back-end ADC cannot correct anymore. The input voltage must remain outside this shaded region for accurate operation. In Fig. 5.5b, the activation of the dead-zone is false during the initial cycle, due to the incomplete DAC-settling. Consequently, this false activation leads the system to the shaded region by the fourth conversion, resulting in a small bit error.

Examining the underlying causes of this phenomenon, it can be seen that the system operates at its edge of operation, resulting in significant delays between both capture latches. This is attributed to the relatively small gain generated by the comparator, the large dead-zone width, and the large time constants of the system. For the MSB decision, capture latch 2 induces a substantial delay, culminating in a step artifact within the system. This step artifact positions the DAC voltage within the dead-zone for the MSB-1 conversion, as depicted in Fig. 5.6. Consequently, with the MSB-1 decision residing in the dead-zone, an erroneous step, in this case a

complete lack of a step is facilitated. This forced the input voltage into the shaded region of the conversion range in the MSB-3 decision, resulting in a small code error.

Figure 5.6: 6-bit dual DAC SAR ADC highlighting the false trigger of the dead-zone at the MSB-1 conversion.

Employing an  $N$ -bit storage element to accommodate  $(N+1)$ -bit data negates the benefits conferred by the increased dead-zone width. This is depicted in Fig. 5.7 for a 10-bit ADC, producing 11-bit data, of which only ten bits are stored. The DAC settling artifact persists within the system, resulting in an effective loss of system resolution. Consequently, the upper limit must be corrected to a lower value than the initially defined limit of 0.5-LSB.

## 5.2 Lower limit

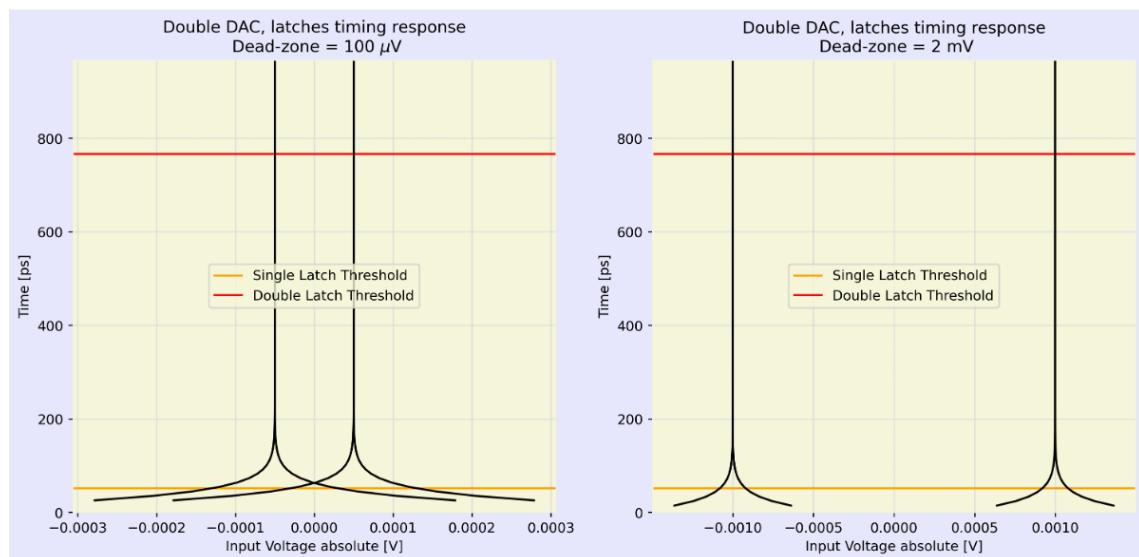

With the upper limit of the dead-zone thoroughly examined, attention can now be directed to the lower limit. It is hypothesized that should the dead-zone diminish to zero, the system reverts to a single SAR ADC configuration. In this configuration, a single DAC SAR ADC structure requires that metastability is resolved prior to subsequent conversion; failure to achieve this will result in a metastability error. Reducing the dead-zone width gradually decreases the timing difference for a valid response between both capture latches, as illustrated in Fig. 5.8. Two horizontal limits indicate the available time for the single-latch and double-latch structures. The single latch threshold represents the time limit within which an easy decision must be valid, whereas the dual latch threshold corresponds to the interval allocated for a metastable decision, from which the latch can still create a valid response in time. The black curves are the time required for a valid response within the capture latch.

Should the duration for simple decisions exceed the timing limit of a single latch, the dual-latch functionality becomes compromised, leading to a metastable error

Figure 5.7: Dead-zone quantization for a 10-bit ADC using 10-bit storage (for 11-bit data).

in the output code. On the left-hand side, for input values in between the two peaks of the black curves, there is no separation between an easy and hard decision. Conversely, the right-hand side demonstrates correct operation, where both latches are sufficiently spaced, thereby ensuring a distinct separation between the easy and the hard decision.

The minimum width required is a function of the cumulative gain within the system. For the decision to be easy, a valid response is needed before the next cycle. If the dead-zone width is defined after the comparator, one must divide it by the gain of the comparator to calculate it back to the input. This resultant value is defined as  $V_{hyst}$ . The easy decision must have sufficient gain to resolve  $V_{hyst}$  to  $V_{dd}$ . If this is not possible within the available time, the dual DAC architecture reverts back to a single DAC functionality.

Figure 5.8: Timing response of capture latches, output comparator referred.

# Chapter 6

## System analysis

With all the components of the system identified, a complete analysis of the system will be performed, with the exclusion of the sampler circuit. Referring to Fig. 6.1, the analysis will begin with the comparator, followed by an examination of the amplifiers, capture latches, and the overall interaction between these components. Finally, the DAC element will be examined, with particular emphasis on the interaction between the DAC element and the RS-latches.

Figure 6.1: Comparator Chain including N-bit capture latches and DAC.

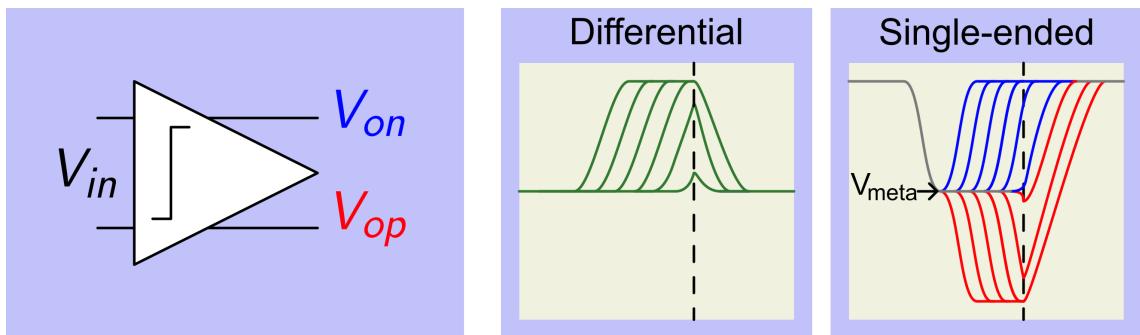

### 6.1 Clocked comparator

To define the BER of the SAR-ADC, an accurate model of the total gain built up in the chain is required. The first component in the chain is the clocked comparator, often only associated with exponential gain. The comparator has four distinct regions, consisting of the startup, regeneration phase, clipping regime, and reset, as illustrated

in Fig. 6.2. The regeneration phase is the only phase where the system builds up a gain exponentially [2].

Figure 6.2: Differential and Single-ended outputs of a clocked comparator with the three regions of operation highlighted

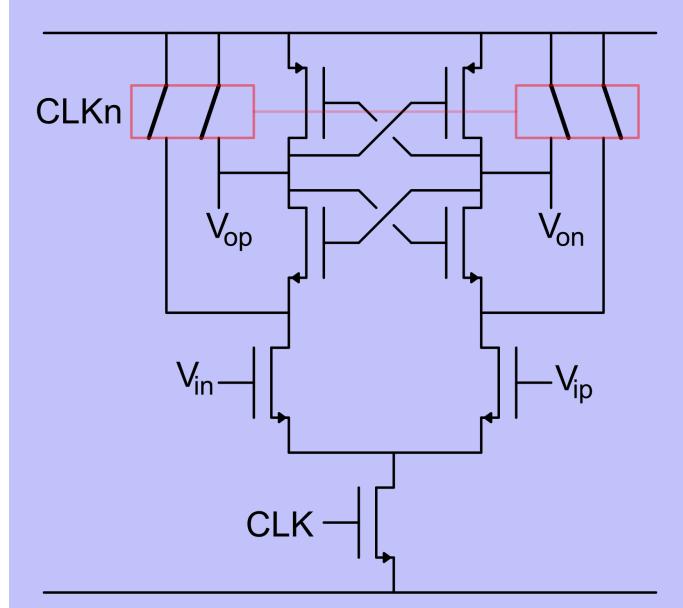

For our system, a strong-arm latched comparator has been selected, as it is a very well-known architecture. The strong-arm latch comparator features a differential pair coupled with a tail current placed below the latch, ultimately reducing the supply voltage of the latch. Creating a pre-amplification once the comparator transistors between the reset state and the regeneration phase. The initial state of the comparator is the reset state, in which both outputs are shorted to  $V_{dd}$ , thus clearing the previous conversion from the outputs. The startup phase follows the reset phase. In this phase, the comparators transition between the reset state and the regeneration phase.

### 6.1.1 Time response

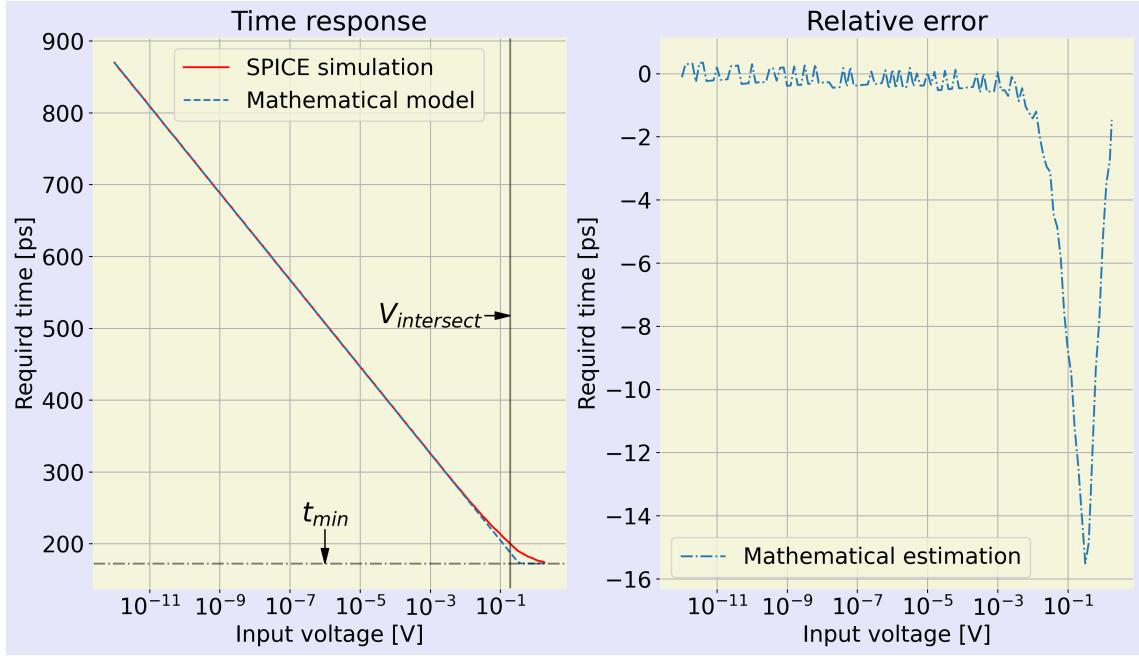

The total time required for a valid response depends on the magnitude of the input signal. When the magnitude of the input signal is close to the supply rails, a negligible gain is necessary for a valid response. However, the comparator still goes through the different regions of operation, inducing a minimal propagation delay within the system, referred to as  $t_{min}$ . Conversely, if the input signal is proximal to the tripping voltage of the comparator, more time is required to accumulate sufficient gain on the comparator side. As illustrated in Fig. 6.3, the time response of a comparator is shown.

In the following, we are going to construct a simple model for the time response of a comparator. For that, we need the time-constant  $\tau$  of the comparator and the minimum propagation delay  $t_{min}$ . To define the time-constant of the system, the derivative of the slope in the regeneration phase can be calculated. The simulation

Figure 6.3: Comparator timing response over a large input range

results of Fig. 6.3 yield a time constant of 26 ps. From the same results, the propagation delay is calculated as 175 ps. With these time constants known, a model can be constructed for the different operational regions. Using  $t_{min}$  and  $\tau$ , a linear function can be formulated:

$$t_{valid} = t_c + t_{min} \quad (6.1)$$

with:

$$t_c = \ln \left( \frac{V_{valid}}{V_{in}} \right) \cdot \tau \quad (6.2)$$

and  $V_{valid}$  denotes the full digital logic voltage. Using the above formula, an initial estimate can be made. It is observed that the mathematical model shows a deviation from the simulation results near the propagation delay of the comparator, as illustrated in Fig. 6.3 at the right-hand side where the relative error between the simulated curve and the linear model is shown. This minor deviation can be adjusted by using a fitting function. However, this deviation is inconsequential for metastable events of the comparator in synchronous SAR ADCs. In contrast, this model would prove to be inadequate if this had been an asynchronous SAR ADC, due to wrong estimations of the time required for easy decisions.

The propagation delay depends on the definition of a 'full' digital decision. If the full digital logic voltage is chosen below the clipping region, the propagation delay would be shorter. In the case of our simulation, an arbitrary valid response voltage of 0.95%  $V_{dd}$  was chosen.

A minimum-sized inverter is placed behind the comparator to reduce the loading of the comparator. This adjustment generates a trade-off between increasing the propagation delay of the system for faster  $\tau$ . Incorporating a pre-amplifier preceding the comparator reduces several inherent non-idealities, albeit with an increased propagation delay within the comparator. Due to the simplicity of the constructed model, the additional propagation delay is easily accommodated, resulting in a precise and adaptable model.

### 6.1.2 Non-idealities

A clocked comparator has multiple error sources, including offset, noise, kickback, and hysteresis, as is modeled in Figs. 6.4a-6.4c, . In the case of SAR-ADCs that employ a single comparator, the offset is inconsequential; it simply introduces a system-wide offset without contributing to distortion or noise errors. The offset becomes a critical issue when using multiple comparators, potentially inducing distortion if the offset exceeds acceptable limits. Calibration techniques are frequently used to mitigate the offset between multiple comparators, reducing the distortion of the system.

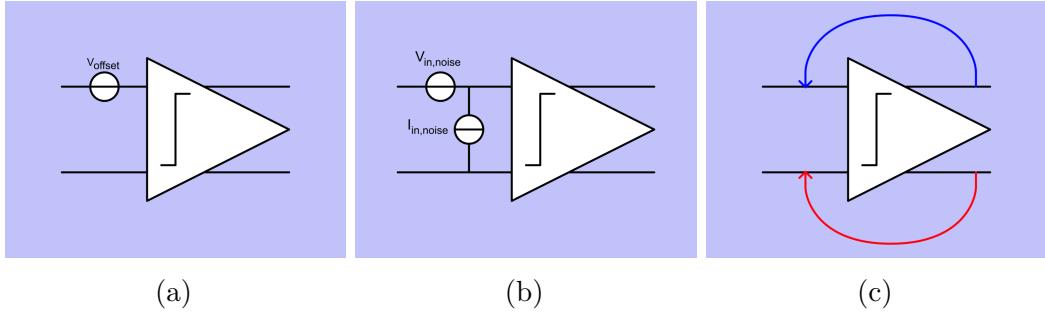

Figure 6.4: (a) Offset visualization of a comparator. (b) Noise sources of a comparator. (c) kickback visualization of a comparator.

The noise generated by the comparator represents the primary source of error in high-resolution systems. The comparator's thermal and flicker noise components can be transposed to the system's input. Both noise sources do not exhibit a direct one-to-one relationship with the system's input [8]. Due to the deterministic nature of the SAR loop, there is a specific ratio between the input-referred noise of the comparator and the equivalent noise referred to the ADC. This ratio depends on the system parameters, with the comparator's noise typically ranging between 0.7 and 1, implying that 70% of the comparator's thermal noise manifests when referred to the system's input.

Once the comparator has decided, the output nodes are positioned at opposing supply rails. However, both outputs must reset to identical voltage levels, thus establishing a uniform starting point for the subsequent conversion. Switches are

interposed between the output nodes and  $V_{dd}$  to facilitate this equilibrium. In the reset state, these switches connect the output nodes to the upper supply rail. This results in an abrupt transition at the output nodes. Because of the parasitic coupling of the comparator's output and input, a corresponding step, known as the kickback of the comparator, manifests at the device's input. The magnitude of this step depends on the impedance present at the input of the comparator. Incorporating a pre-amplifier between the DAC and the comparator attenuates the kickback phenomenon caused by the diminished coupling factor from the output to the input.

In addition, when the reset is non-ideal, it is possible that the resulting output from  $V_{ss}$  falls marginally below  $V_{dd}$ , thus inducing a slight offset attributable to the preceding decision. A small offset relative to the positive output will be present when the positive output is at  $V_{ss}$ . In contrast, should the negative output be positioned at  $V_{ss}$ , the subsequent cycle will exhibit an offset relative to the negative output, creating a code-dependent error that leads to distortion.

## 6.2 Amplifier

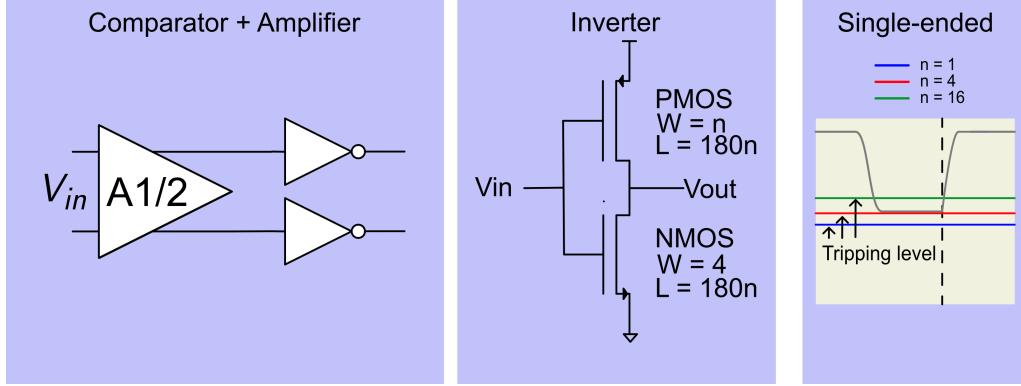

With the comparator analyzed, the next component in the chain is the amplifier, which incorporates the tripping voltage in conjunction with one of the comparator outputs. This amplifier functions as a static gain block, amplifying the difference between the tripping voltage and a particular comparator output. This introduces an offset within the comparator chain with respect to the comparator metastable point.

Inverters are typically placed between the comparator and the capture latches, to reduce the loading of the comparator, and ensuring a digital output during the whole conversion. These inverters function analogously to open-loop amplifiers, amplifying the difference between the input voltage and the inverter's tripping voltage. By modulating this tripping voltage, an inverter can serve effectively as the amplifier within the signal processing chain, without adding any overhead.

The inverter tripping voltage is characterized by the input voltage at which the current through the NMOS transistor equals the current through the PMOS transistor. With the knowledge that the inverter is operating in strong inversion at this regime, the square law model applies, resulting in the following equation for the tripping voltage:

$$V_{trip} = \frac{V_{dd} - |V_{thp}| + V_{thn} \sqrt{\frac{\beta_n}{\beta_p}}}{1 + \sqrt{\frac{\beta_n}{\beta_p}}} \quad (6.3)$$

with:

$$\beta_{n,p} = \mu_{n,p} C_{ox} \left( \frac{W}{L} \right)_{n,p} \quad (6.4)$$

and  $\mu_{n,p} C_{ox}$  the device constants,  $V_{thp,n}$  the threshold voltage of the NMOS and PMOS,  $W_{p,n}$  the channel widths, and  $L_{p,n}$  the channel lengths of the devices.

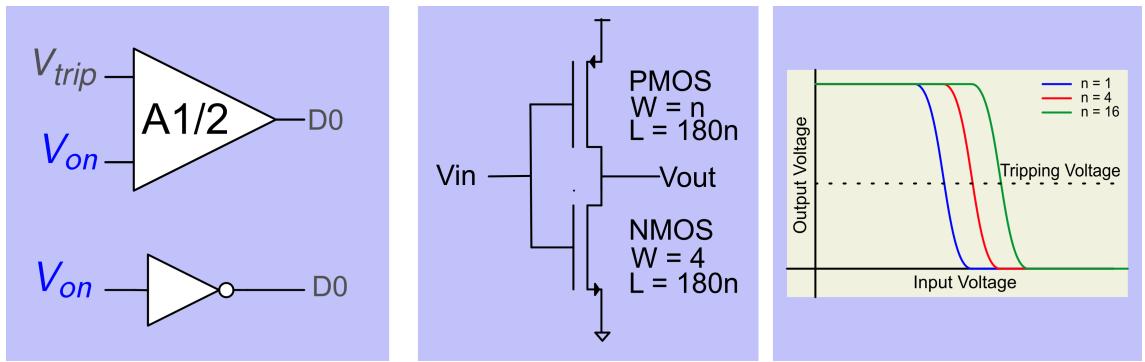

A clear correlation becomes evident between the inverter's tripping voltage and the sizing parameters of the device. By selecting a minimal channel length, the width can be modified, thereby influencing the tripping voltage with significant versatility, as illustrated in Fig. 6.5.

Figure 6.5: Inverter sizing, utilizing the internal tripping voltage.

Adjusting the inverter by altering the optimal ratio between NMOS and PMOS allows the tripping voltage to be placed below  $V_{meta}$ . The ratio of device constants, defined by  $\mu_p/\mu_n$ , is approximately 3 in the given technology. Consequently, for devices of equal strength, the PMOS must be three times larger than the NMOS. The comparator is designed to give the PMOS and NMOS devices equal strength making  $V_{meta}$  identical to the intrinsic tripping voltage of a 3/1 inverter. According to Eq. 6.3, positioning the tripping voltage below  $V_{meta}$  requires a larger NMOS than the baseline configuration.

Given that inverters are already present between the comparator and the capture latches, this approach eliminates the need for additional circuitry. Concurrently, it establishes a well-defined offset within the chain from the comparator to the capture latches, as shown in Fig. 6.6.

### 6.3 Capture latch

The primary function of the capture latch is to store the output of the comparator for subsequent digital processing. However, in cases of metastability within the comparator, the positive feedback of the capture latch increases the gain provided by the comparator, thus mitigating the likelihood of metastability-induced errors.

Figure 6.6: Comparator chain creating an offset between both outputs, with the gray line showing the transient response of a metastable comparator

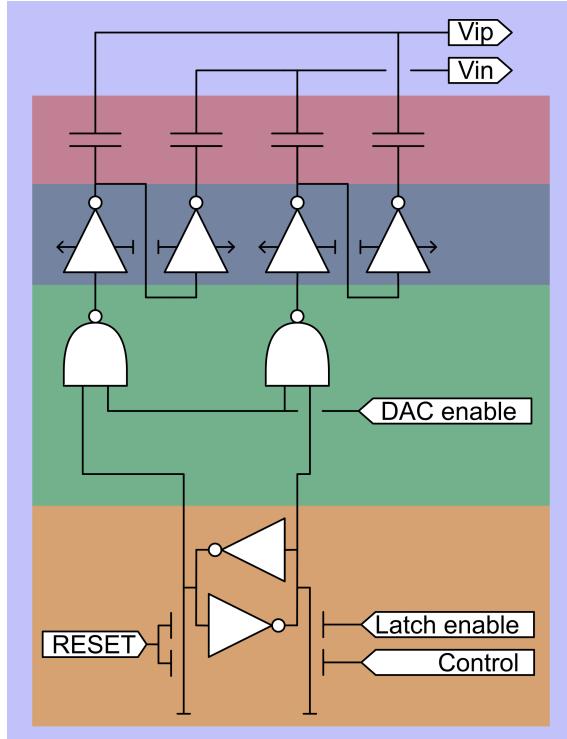

The Reset/Set Latch (RS-latch) is a standard building block in IC design and can SET and RESET the corresponding output bit. The RS-latch consists of a latch created by two back-to-back inverters, creating positive feedback, and two pull-down switches to execute the SET and RESET operations. As illustrated in Fig. 3.1, all capture latches of the system are directly connected to the output of the comparator. Consequently, the necessity arises to mask the comparator's output via an enable signal, as demonstrated in the timing diagram in Fig. 6.7.

Figure 6.7: Timing diagram of a 2-bit SAR ADC.

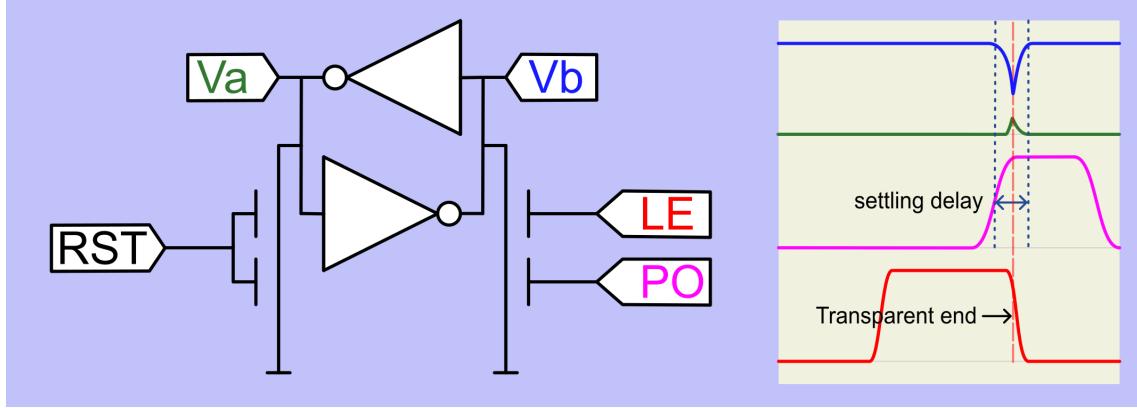

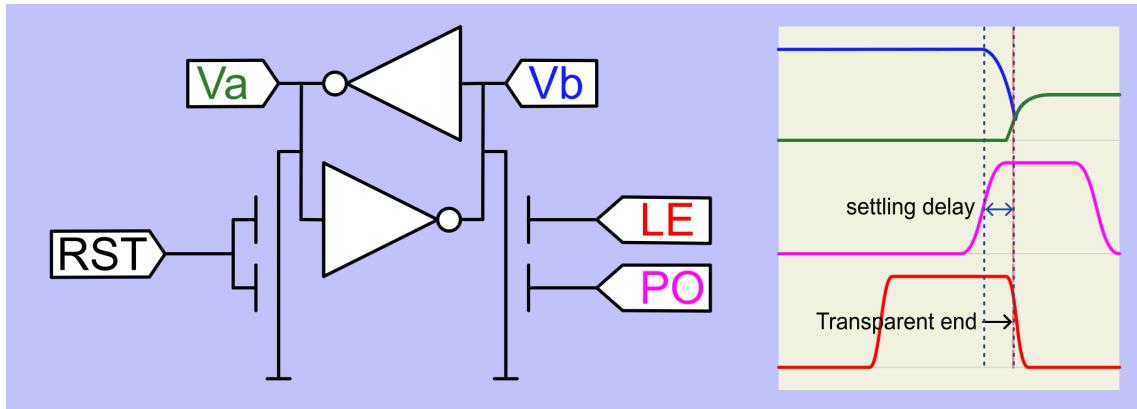

During the comparator's conversion phase, the RS-latch is transparent following the output voltage of the comparator. Once the conversion is complete, the DAC is subsequently activated. The reset operation of the RS-latch can be executed asynchronously with the help of a reset signal generated by the SAR-logic. At the system level, an AND gate is required for masking the enable signal of the RS-latch. The inputs to the AND gate consist of the latch-enable signal and one of the comparator outputs, the latch-enable signal serving as the masking signal, as illustrated in Fig. 6.8.

Figure 6.8: Voltage transients of an RS-latch.

On the left side, the RS latch is depicted. The pull-down mechanisms are used to RESET and SET the devices, where the SET operation incorporates an AND gate within the pull-down structure. The illustration on the right shows the transient response of the latch voltages, denoted by  $V_a$ ,  $V_b$ , the comparator's output, and the latch-enable signal. The latch, analogous to the comparator, has three distinct regions: SET (positive out), RESET (negative out), and a metastable region.

The RS-latch, in its initial condition, resides in the reset state. To transition the RS-latch to the SET state, it is required that both inputs to the pull-down devices (Latch Enable and Positive Out) be at a high logic level, as shown in Fig. 6.9. The comparator output remains high during the transparent phase of the RS-latch. The dashed vertical red line highlights the end of the transparent phase. The propagation delay, or settling delay, is indicated by the two dotted lines, indicating the minimum required time for simultaneous activation of the latch-enable signal and the comparator's output latch. When both signals are active longer than this settling delay, the latch will transition to the SET state.

Figure 6.9: Setting of an RS-latch.

If the comparator has a harder decision, the output of the comparator will be valid. Therefore, the available time for both inputs of the AND gate to be valid is reduced. As illustrated in Fig. 6.10, the output of the comparator took too long to

obtain a valid response, leaving insufficient time to SET the latch. This is indicated by the settling delay lines ending later than the transparent phase.

Figure 6.10: Not setting of an RS-latch.

In the case of metastability within the RS-latch, the endpoint of the settling delay coincides with the end of the transparent phase, as illustrated in Fig. 6.11. As a result of driving the RS-latch from a single side, the output node  $V_b$  is drawn below the  $V_{meta}$  threshold of the RS-latch. Once the transparent phase ends, both output nodes realign toward the device's intrinsic common mode voltage ( $V_{meta}$ ), thus entering the regeneration phase of the latch, building up the gain to overcome the metastability.

Figure 6.11: Metastability inside an RS-latch.

Minimizing settling delay will enhance the maximum accumulated gain of the comparator. To achieve a reduction in settling delay, the utilization of stronger (thus larger) pull-down devices is required. However, a downside of this approach arises as an increased time constant of the latch due to the larger pull-down devices, which results in more capacitive loading at the outputs. As indicated in Eq. 2.2, a larger capacitive load will reduce the  $\tau$  of the system. In the Dual DAC ADC, the capture

latch benefits from the longest duration to resolve metastable errors. Degrading the timing constant of the latch to curtail the settling delay will reduce the cumulative gain across the entire chain, thereby deteriorating the BER.

## 6.4 Comparator Chain

A comprehensive analysis of the comparator in combination with the RS-latch chain can be performed by detailed examination of the individual components. Fig. 6.12, shows the total chain of a one-bit system.

Figure 6.12: comparator followed by the skewed inverters (yellow) and two the capture latches (green).

Both outputs, indicated by  $BIT0_n$ ,  $BIT0_p$ , are interfaced with their respective DAC elements (not shown in the figure). For an  $N$ -bit system,  $N$  times two capture latches will be placed and arranged in parallel, each accompanied by its distinct enable signals. The timing delays within the system have been characterized, including the comparator's delay  $t_{min}$ , the propagation delay of the inverter, and the latch settling delay. Together, these delays reduce the available time of the comparator, thus diminishing the effective gain. In addition, the interaction between the components moves the initial dead-zone, defined as the difference between the tripping voltage and  $V_{meta}$ , to a higher value due to the hysteresis of the latch.

## 6.5 DAC element