### PVT Tolerant Transconductor for Low-Voltage Highly-Selective High-Frequency Filter of MRI Front-end Receiver

by

Gayatri Agarwal 4861078

A thesis submitted in partial satisfaction of the requirements for the degree of

Master of Science

in

**Electrical Engineering**

$\operatorname{at}$

The Faculty of Electrical Engineering, Mathematics and Computer Science

Delft University of Technology, Netherlands

Supervisors:

Prof.dr.ir. Wouter A. Serdijn, TU Delft, Chair Dr. Virgilio Valente, TU Delft Ir. Emil Totev, Philips Research

August 2020

The thesis titled **PVT Tolerant Transconductor for Low-Voltage Highly-Selective High-Frequency Filter of MRI Front-end Receiver**

> by Gayatri Agarwal Master of Science in Electrical Engineering Delft University of Technology, Netherlands is approved, dated on: August 5<sup>th</sup>, 2020

Chair

(Prof.dr.ir. Wouter A. Serdijn)

(Dr. Virgilio Valente)

(Dr. Fabio Sebastiano)

(Ir. Emil Totev)

#### Abstract

### PVT Tolerant Transconductor for Low-Voltage Highly-Selective High-Frequency Filter of MRI Front-end Receiver

by

### Gayatri Agarwal

### Master of Science in Electrical Engineering

MRI machine has evolved tremendously over the years from its inception in order to render high-quality 3D images, best among its companion imaging systems. Of the whole system, RF receiver is the most crucial for its noise performance, which is expected to provide high SNR at all operating conditions. At Philips, MRI's RF receiver is based on direct-digitization architecture which has replaced the bulky data-acquisition system with an integrated on-coil receiver. It allows a lot of signal processing to be done digitally which was earlier done in analog-domain, thus improving the SNR and dynamic range to more than 100 dB. However, this has increased the design restrictions of the remaining analog front-end. The high frequency bandpass filter employed to select the signal band around the receiver's resonance frequency, has not only become highly selective (Q 400,  $6^{th}$  order) to narrow down the signal bandwidth and reject the rest with a high stopband attenuation but also incorporates a high passband gain (60 dB), unlikely to see otherwise. Operating at a high frequency of 100's of MHz, with such a response, the filter can become drastically sensitive to the shift in its components with varying operating conditions. At Philips, the filter uses transconductor as one of its building blocks and filter frequency response is heavily dependent on the transconductance of unit cell as they are employed in large number in the circuit. The transconductor cell, at Philips, shows 15% deviation with process, supply and temperature variations. This leads to more than 10% variation in the passband gain of the filter. Operating at low supply voltage, such a deviation in MRI filter can deteriorate its output SNR and dynamic range by 10dB.

In this thesis, a new inverter based self-biased transconductance circuit has been proposed, which shows a deviation of  $\pm 2.5\%$  in transconductance under the process, temperature and supply variations. It limits the passband gain of the filter to 60 dB  $\pm 2\%$  and bandwidth shows a deviation of less than 0.1%. However, center frequency is matched precisely with the resonance frequency of receiver by the external components of the filter. Given, this matching is the basis for working principle of MRI receiver. With the proposed transconductance circuit, the filter shows an SNR of 112 dB, THD of -63 dB and consumes a power of 0.8 mW. The circuit has been implemented in 40 nm TSMC process and simulated for a temperature range of 0°C - 85°C at the power supply of 1.1 V  $\pm$  10%, post extraction.

### Acknowledgments

I would like to express my sincere gratitude to Ir. Emil Totev, my supervisor at Philips Research. He had always been available for an in-depth discussion, sharing his knowledge and expertise to solve the issues. Working under his guidance had continuously motivated me to improve my research and broaden my analytical skills. My association with him has triggered me to perform the research tasks independently, using the fundamental approach.

I would like to thank my university supervisor, Dr. Virgilio Valente for sharing his valuable feedback and motivating me to think critically during our continuous synchronisation meetings and reviews. He has always added value to my design proposals and supported me throughout the study. His contribution in formulating the orientation of thesis report is invaluable, it has brought an indispensable clarity to it. I would like to extend my special thanks to Prof.dr. Wouter Serdijn, for sharing his insights into my design problems and providing me new view points on it. Also, his teachings were surely beneficial in the course of this study.

I am also grateful to Dr. Sotir Ouzounov at Philips, for giving me the opportunity to work on this research study. I am equally grateful to the team members at Philips, Dr. Ketan Pol and Dr. Hugo Veenstra, for they were always ready to extend help whenever required in terms of a quick discussion on a topic or resources for a task.

I am also very grateful to my mentor, during the internship at NXP, Dr. Marco Berkhout. Under his guidance I had learnt how to structure a design methodology. He had been a continuous source of inspiration. I also want to thank Ir. Patrick Zeelen, team member during the internship at NXP. I am indebted to him for his support and help that allowed me to learn all the tools to its best use. The internship had undoubtedly provided me a good foundation which allowed me to be able to work independently as much as possible during the thesis.

Certainly, I would like to recognize the evolution of technology that allowed me to stay connected with my supervisors and be able to continue my work remotely without any delay. It's difficult to imagine how major an impact could have been if it were just five years back. Not only work, but also it allows me to stay connected with my family and friends whose support is indeed indispensable in the moment, not to mention, their love strengthened me throughout the journey, specially from my parents. I am deeply grateful to them and to Almighty God for His grace on me.

## Contents

| C        | onter | its                                                | i            |

|----------|-------|----------------------------------------------------|--------------|

| Li       | st of | Figures                                            | iii          |

| Li       | st of | Tables                                             | $\mathbf{v}$ |

| 1        | Intr  | oduction                                           | 1            |

|          | 1.1   | Magnetic Resonance Imaging                         | 1            |

|          |       | 1.1.1 Working Principle                            | 1            |

|          |       | 1.1.2 RF Receiver                                  | 3            |

|          | 1.2   | Motivation                                         | 5            |

|          | 1.3   | State of the Art constant- $g_m$ circuit           | 8            |

|          | 1.4   | Thesis Organisation                                | 9            |

| <b>2</b> | Syst  | tem Design                                         | 10           |

|          | 2.1   | Parallel RLC Resonator                             | 10           |

|          | 2.2   | Filter Circuit                                     | 13           |

|          |       | 2.2.1 Filter Programmability                       | 15           |

|          |       | 2.2.2 Architecture Overview                        | 16           |

|          |       | 2.2.3 Previous Circuit                             | 19           |

|          |       | 2.2.4 PVT Tolerance                                | 22           |

| 3        | Circ  | cuit Implementation                                | <b>27</b>    |

|          | 3.1   | Transconductor cell                                | 27           |

|          |       | 3.1.1 Constant- $g_m$ Biasing                      | 27           |

|          |       | 3.1.2 Self-biased Transconductor                   | 33           |

|          |       | 3.1.3 Complete "constant-transconductance" circuit | 36           |

|          | 3.2   | Filter                                             | 38           |

|          |       | 3.2.1 Fully-Differential Filter                    | 38           |

|          |       | 3.2.2 Parasitics in Filter                         | 40           |

|          |       | 3.2.3 Programmability                              | 43           |

|          | 3.3   | Layout                                             | 45           |

ii

| 4  | Results                                                                                                   | 48   |  |  |  |

|----|-----------------------------------------------------------------------------------------------------------|------|--|--|--|

|    | 4.1 Transconductor                                                                                        | . 48 |  |  |  |

|    | 4.1.1 Transconductance Variation                                                                          | . 48 |  |  |  |

|    | 4.2 Filter                                                                                                | . 52 |  |  |  |

|    | 4.2.1 Frequency Response                                                                                  | . 54 |  |  |  |

|    | 4.2.2 Gain at Center Frequency                                                                            | . 56 |  |  |  |

|    | 4.2.3 Bandwidth $\ldots$ | . 58 |  |  |  |

|    | 4.3 Filter Performance                                                                                    | . 60 |  |  |  |

|    | 4.3.1 Noise                                                                                               | . 60 |  |  |  |

|    | 4.3.2 Distortion $\ldots$                                                                                 | . 61 |  |  |  |

|    | 4.4 Achieved Results                                                                                      | . 62 |  |  |  |

| 5  | Discussion                                                                                                | 63   |  |  |  |

|    | 5.1 Transconductance circuit                                                                              | . 63 |  |  |  |

|    | 5.2 Filter circuit                                                                                        | . 65 |  |  |  |

| 6  | Conclusion                                                                                                | 67   |  |  |  |

| U  | 6.1 Thesis contributions                                                                                  |      |  |  |  |

|    | 6.2 Future work                                                                                           |      |  |  |  |

|    |                                                                                                           |      |  |  |  |

| Bi | Bibliography                                                                                              | 69   |  |  |  |

| Α  | Filter system modelling                                                                                   | 72   |  |  |  |

| в  | 3 More results 7                                                                                          |      |  |  |  |

# List of Figures

| 1.1<br>1.2<br>1.3 | Working principle of MRI [4, 5]                                                                                                                                           | 2<br>3<br>4 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1.4<br>2.1        | Signal at the input of RF ADC [12]                                                                                                                                        | 5<br>11     |

| 2.2               | Natural response of parallel RLC circuit [27]                                                                                                                             | 12          |

| 2.3               | LC filter                                                                                                                                                                 | 13          |

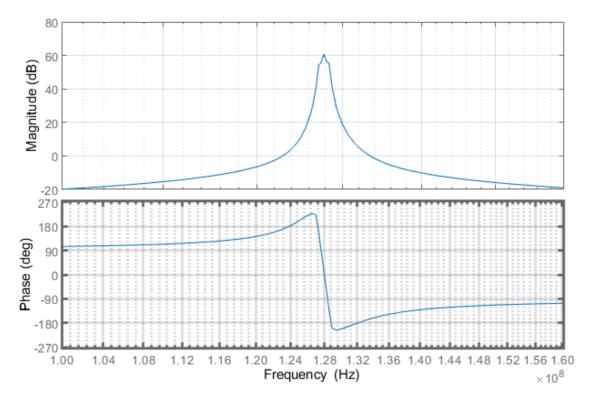

| 2.4               | Magnitude and Phase response of the desired filter                                                                                                                        | 14          |

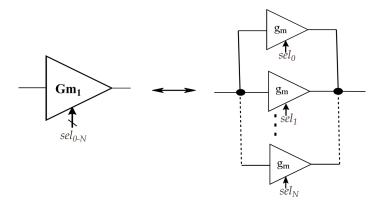

| 2.5               | Switchable transconductor for programmability                                                                                                                             | 16          |

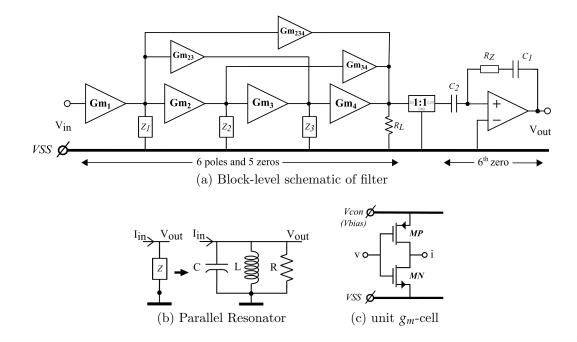

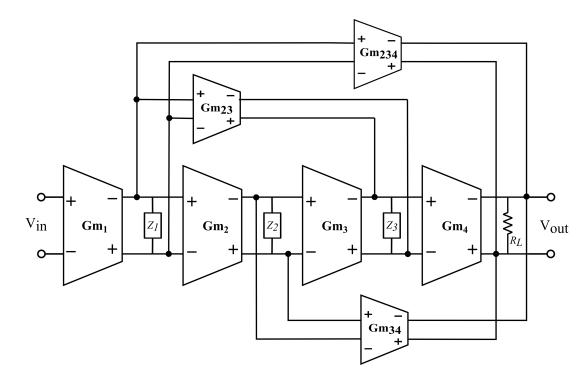

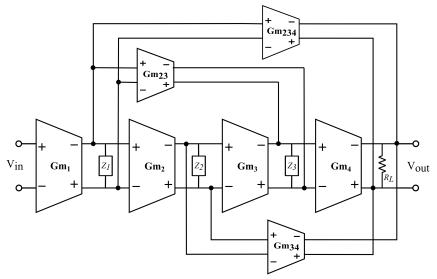

| 2.6               | Filter Architecture for MRI Receiver                                                                                                                                      | 16          |

| 2.7               | Ideal frequency response of the filter (excl. sixth zero)                                                                                                                 | 17          |

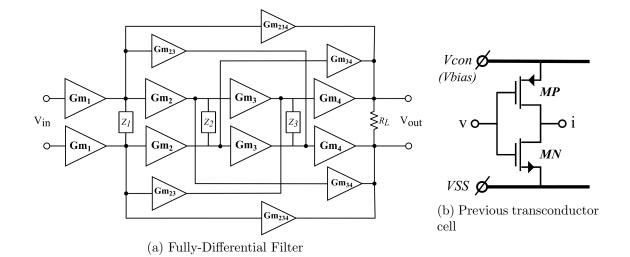

| 2.8               | Fully-differential filter schematic using previous transconductor cell                                                                                                    | 20          |

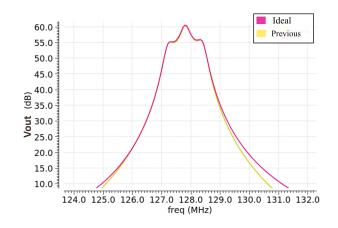

| 2.9               | Previous transconductor implemented filter response - simulation results                                                                                                  | 21          |

| 2.10              | Concept of constant- $g_m$ biasing $\ldots \ldots \ldots$ | 24          |

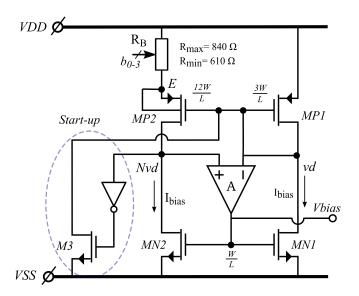

| 3.1               | Schematic of the proposed biasing circuit                                                                                                                                 | 28          |

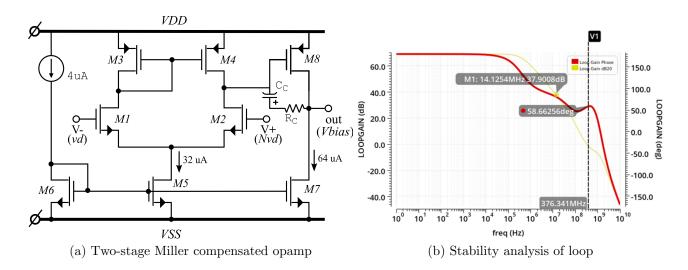

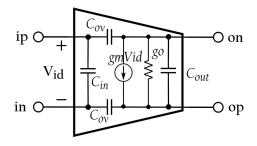

| 3.2               | Operational Amplifier used for negative feedback loop in bias block                                                                                                       | 31          |

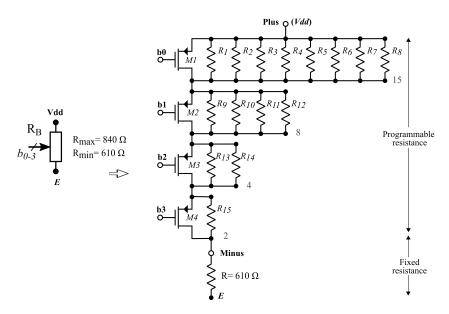

| 3.3               | Binary weighted 4-bit resistance bank.                                                                                                                                    | 32          |

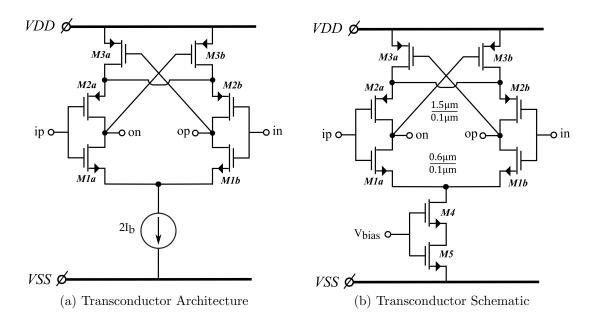

| 3.4               | Proposed Transconductor                                                                                                                                                   | 33          |

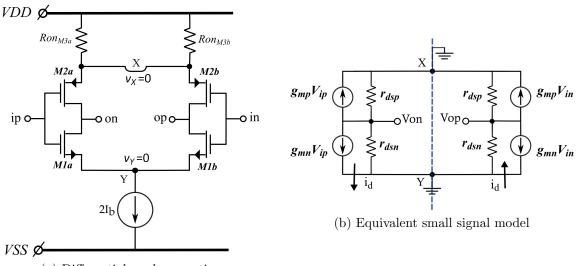

| 3.5               | Small-signal model of proposed transconductor                                                                                                                             | 35          |

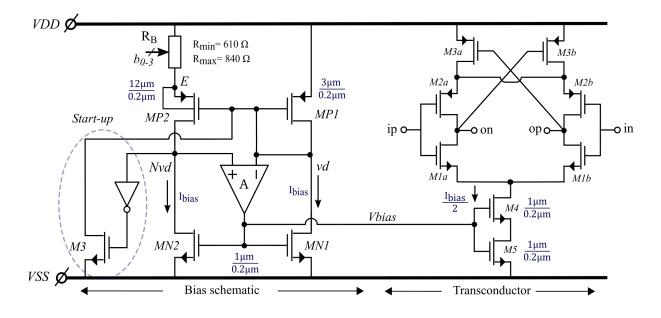

| 3.6               | Complete "constant-transconductance" circuit                                                                                                                              | 36          |

| 3.7               | Fully-differential filter using proposed transconductor                                                                                                                   | 39          |

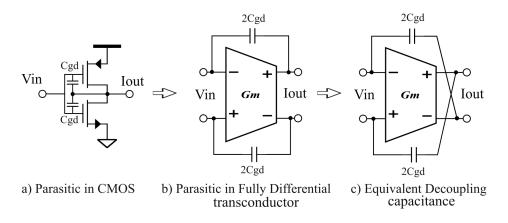

| 3.8               | Equivalent model of the transconductor with parasitics                                                                                                                    | 40          |

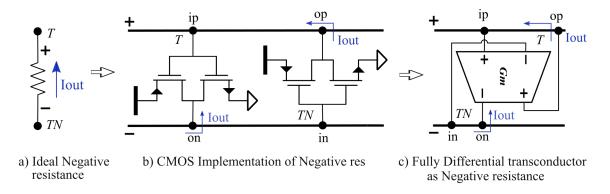

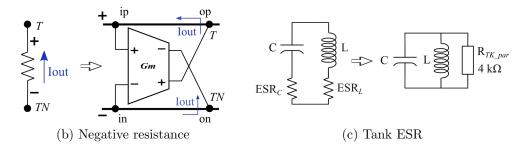

| 3.9               | Concept and implementation of negative resistance                                                                                                                         | 41          |

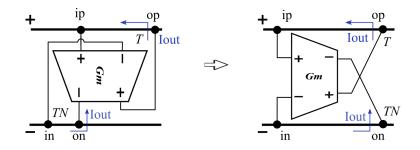

| 3.10              | Negative resistance implementation with proposed transconductor                                                                                                           | 42          |

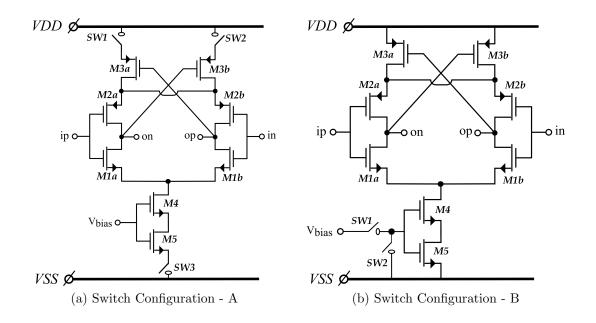

| 3.11              | 1 1 1                                                                                                                                                                     | 43          |

| 3.12              |                                                                                                                                                                           | 44          |

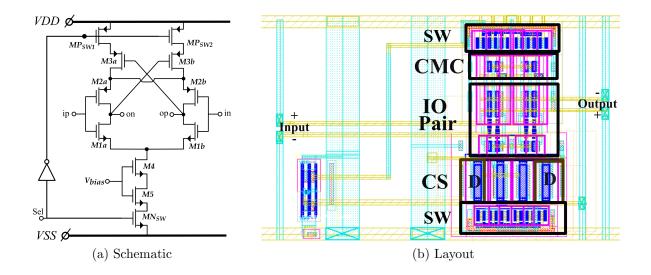

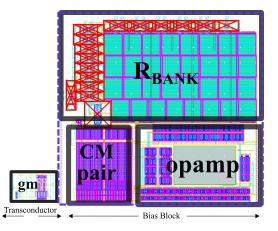

|                   | Transconductor cell Layout                                                                                                                                                | 45          |

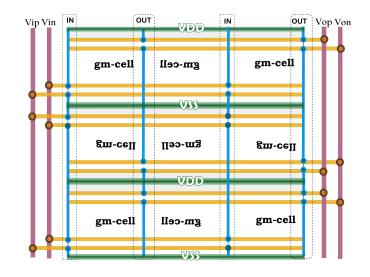

|                   | Floor plan of the $g_m$ -cells tiling to construct Gm block                                                                                                               | 46          |

| 3.15              | Bias Block Layout. Transconductor cell shown for relative area                                                                                                            | 47          |

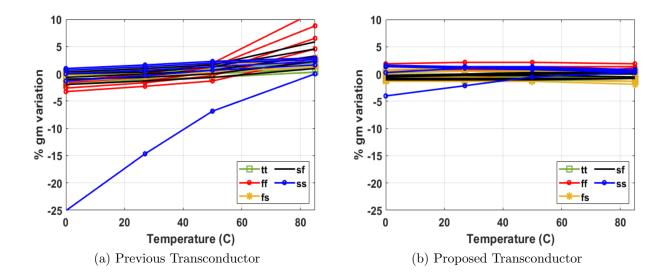

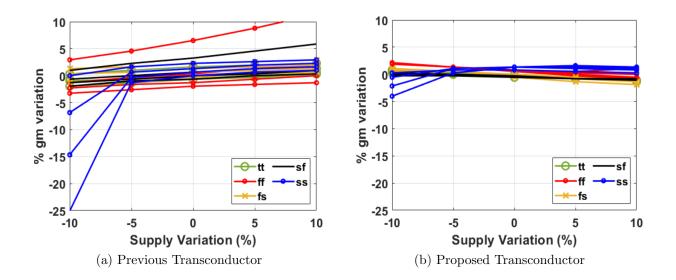

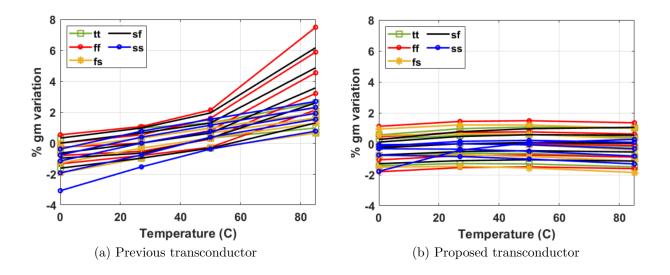

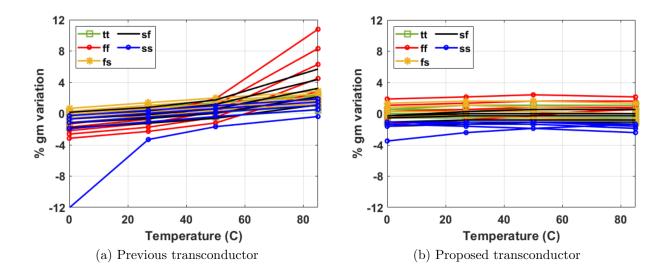

| 4.1               | $g_m$ variation with temperature (curves with same colour show supply variation)                                                                                          | 49          |

| 4.2  | $g_m$ variation with supply (curves with same colour show temperature variation)                | 49 |

|------|-------------------------------------------------------------------------------------------------|----|

| 4.3  | Proposed transconductor $g_m$ variation - Zoomed in $\ldots \ldots \ldots \ldots \ldots \ldots$ | 51 |

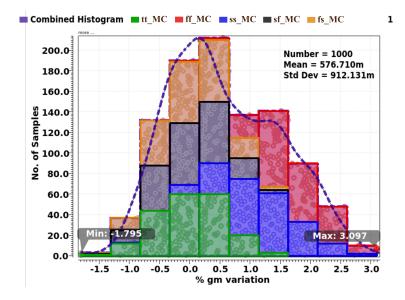

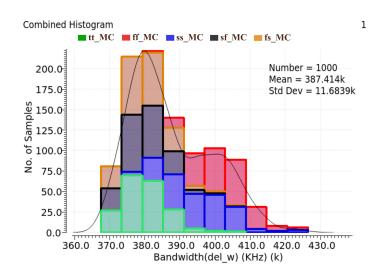

| 4.4  | Transconductance variation with device mismatch using Monte Carlo simulation                    | 52 |

| 4.5  | Fully-differential filter using proposed transconductor                                         | 53 |

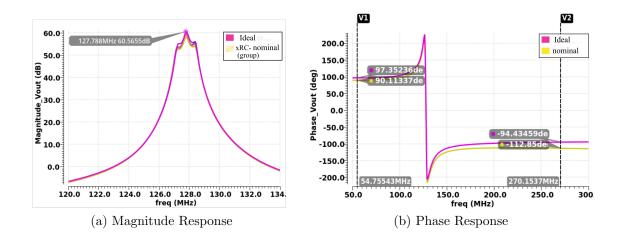

| 4.6  | Filter frequency response. Comparison with ideal response (magenta)                             | 55 |

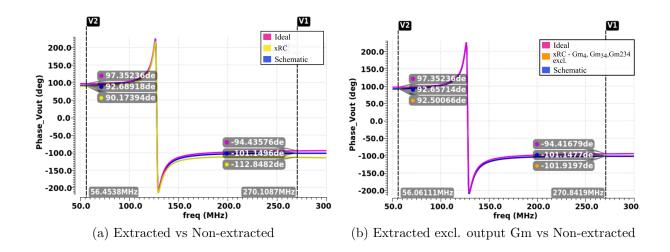

| 4.7  | Phase comparison between schematic and extraction with respect to the ideal .                   | 56 |

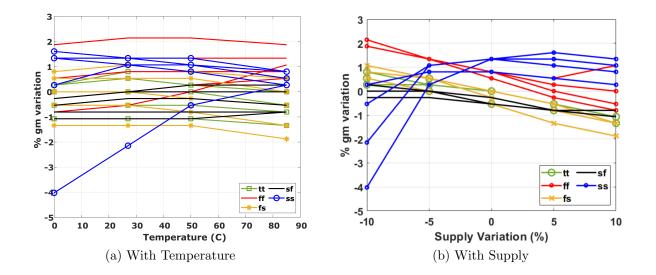

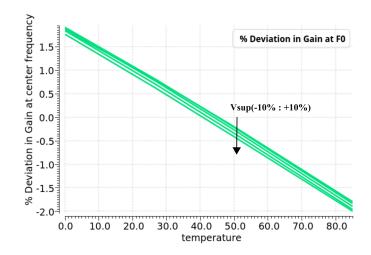

| 4.8  | Deviation in gain at $f_0$ (127.8MHz) of filter with supply and temperature                     | 57 |

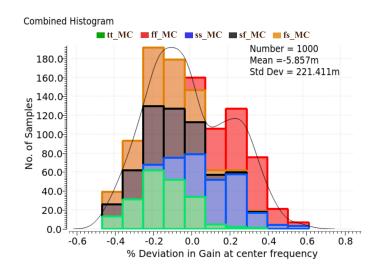

| 4.9  | Monte Carlo simulation for deviation in gain at center frequency 127.8 MHz                      | 57 |

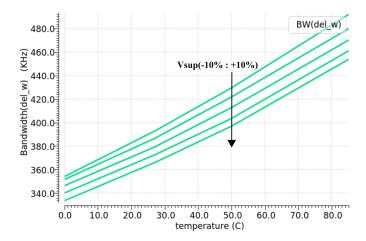

| 4.10 | Deviation in bandwidth $(\Delta f)$ of filter with supply and temperature variation             | 58 |

| 4.11 | Monte Carlo simulation for deviation in $\Delta f$                                              | 59 |

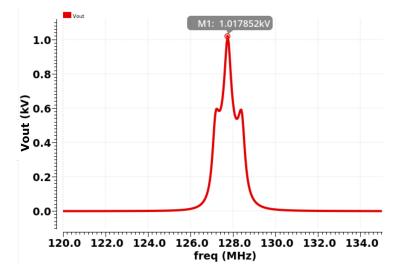

| 4.12 | Filter magnitude response on absolute scale                                                     | 60 |

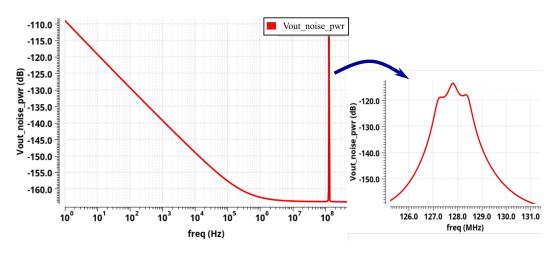

| 4.13 | Output noise power spectrum of filter                                                           | 61 |

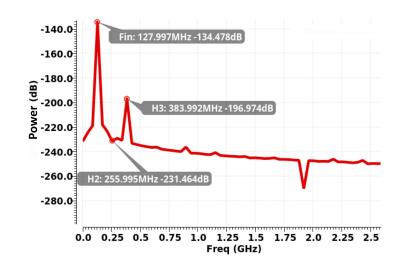

| 4.14 | Distortion spectrum of the filter                                                               | 62 |

| A.1  | Filter Architecture                                                                             | 72 |

| B.1  | Schematic simulation with normalized $R_B$ . $g_m$ variation with PVT                           | 75 |

| B.2  | Schematic simulation with $R_B$ as $R_{bank}$ . $g_m$ variation with PVT                        | 76 |

# List of Tables

| 1.1 | Target Performance for the Proposed Transconductor                                     | 7  |

|-----|----------------------------------------------------------------------------------------|----|

| 2.1 | Poles and zeros of MRI filter                                                          | 14 |

| 2.2 | Component values (RLC) of three resonators corresponding to their poles                | 18 |

| 2.3 | Transconductance per Gm block in ideal filter                                          | 18 |

| 2.4 | Number of transconductor cells per Gm block in ideal filter                            | 19 |

| 2.5 | Number of transconductor cells per Gm block in previous circuit                        | 20 |

| 2.6 | Resonator components for previous transconductor implemented filter. L=50nH            | 22 |

| 3.1 | Opamp in bias circuit. $L = 0.5 \mu m$ , except for M8                                 | 31 |

| 3.2 | Programmable 4-bit binary weighted resistance bank                                     | 32 |

| 3.3 | Transconductance per Gm block in ideal filter                                          | 38 |

| 3.4 | Number of proposed transconductor cells per Gm block in filter                         | 39 |

| 3.5 | Resonator components for proposed transconductor implemented filter. L=50nH            | 41 |

| 3.6 | Decoupling capacitance for Gm block in filter                                          | 43 |

| 4.1 | 4-bit digital code of resistance bank for process corner                               | 50 |

| 4.2 | Number of proposed transconductor cells per Gm block in filter                         | 52 |

| 4.3 | Resonator components of the filter after extraction of proposed $g_m$ -cell. L=50 nH   | 54 |

| 5.1 | Performance comparison of constant- $g_m$ circuit                                      | 65 |

| A.1 | Poles and zeros of MRI filter                                                          | 72 |

| A.2 | Component values (RLC) of three resonators $(Z_{1-3})$ corresponding to their complex- |    |

|     | conjugate poles                                                                        | 73 |

| A.3 | Transconductance per $Gm$ block in ideal filter                                        | 74 |

| A.4 | Scale factor of transconductor cells in ideal filter                                   | 74 |

## Chapter 1

## Introduction

### 1.1 Magnetic Resonance Imaging

Magnetic resonance imaging (MRI) is the most sophisticated clinical imaging system (CIS) compared to its counterparts like X-ray, CT and PET since it provides high-quality 3D images with relatively safe environment due to the absence of ionizing radiations, unlike others.

### 1.1.1 Working Principle

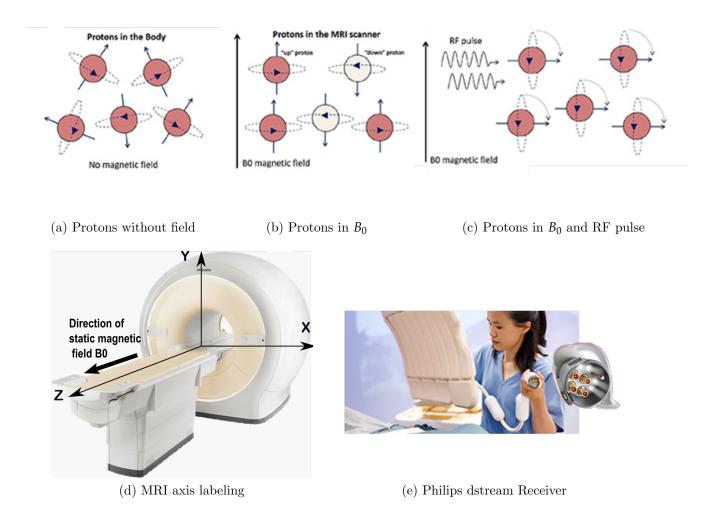

MRI is based on the principle of nuclear magnetic resonance (NMR). According to which, nuclei with an odd number of neutrons possess a nonzero nuclear spin, as a result they can be magnetized in an external field [1]. Our body carries multiple such nuclei like  $H^+$ ,  $Ca^{2+}$ ,  $Mg^{2+}$ ,  $Na^+$  etc which behave as dipole and can be scanned under MRI to determine the shape of the body tissues. MRI machine uses three fields - static magnetic field, radio frequency (RF) pulse and gradient field. The working principle is illustrated in Fig. 1.1. As soon as the static magnetic field ( $B_0$ ) is turned ON, the target nuclei, say protons ( $H^+$ ) are magnetized and begin to precess about the axis of  $B_0$  at Larmor frequency. Following which an RF pulse, transverse to the plane of  $B_0$ , is transmitted at Larmor frequency, this turns the nuclei transverse to  $B_0$ . Once the RF excitation is removed, the nuclei return back to their steady state, releasing the energy which is sensed by the RF receiver. The process of RF excitation and reception is repeated several times under the variation of gradient field to generate 3D images from 2D scans.

Here, precession is a motion of nucleus alike a "spinning top" and the Larmor frequency is defined as the rate of precession of the magnetic moment of the nucleus around the static magnetic field,  $B_0$  [2], which is given as

$$f_0 = \gamma B_0 \tag{1.1}$$

where,  $f_0$  is the Larmor frequency in MHz,  $B_0$  is the static magnetic field in tesla (T) and  $\gamma$  is gyromagnetic constant (42.6 MHz/T for H<sup>+</sup>) which depends on the target nucleus.

$B_0$  is the main field of MRI, so the machine is denoted with  $B_0$  strength only say three tesla (3 T) MRI. Using the Larmor equation, the Larmor frequency of protons for 3 T machine is 127.8 MHz. A resonance is achieved between the protons and the RF receiver at Larmor frequency such that the released energy of protons is transferred onto the receiver, which senses the change in magnetic flux in the coil and induces current [3]. Following the Faraday's law, the amount of change in flux is proportional to the induced current. Hence, the quality of the received signal depends on how exact is the matching between the receiver electronics with that of the resonance frequency to minimize any possible loss of information.

Figure 1.1: Working principle of MRI [4, 5]

### 1.1.2 RF Receiver

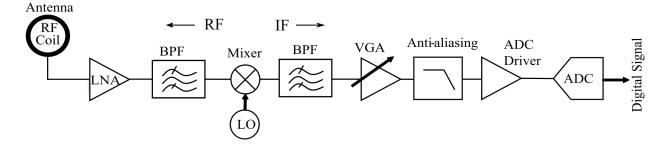

The precision of MRI system electronics is very high in order to render best quality 3D images incomparable to any other imaging system. In which the front-end of RF receiver is the most crucial, its goal is to achieve highest possible signal-to-noise ratio (SNR) for all operating conditions [1]. Being the first point of contact towards the receiving end, it is a deciding factor for SNR. Fig. 1.2 shows the classic RF receiver which aligns with the MRI RF receiver in general. It begins with antenna, here RF coil, to receive the signals reflected off the patient's body, followed by a low-noise amplifier (LNA) to suppress noise and amplify the signal, then a bandpass filter to select the desired band of interest, near Larmor frequency and then a signal processing chain from mixer till A-to-D driver to down-convert the RF signal into intermediate frequency (IF) so as to be digitized easily via analog-to-digital converter (ADC) in baseband. Following which, the signal is off for conversion into images in digital domain with the help of computer software and finally renders the output on the screen.

Figure 1.2: Block diagram of MRI receiver's analog front-end

The received signal is prone to noise from three sources. First, the stray radiations from the radio objects in the examination room. Second, the receiver electronics itself and third the thermal radiations from the patient's body. Of these the former two can be minimized by copper shielding the room and improving the receiver's electronic components respectively [6]. But the latter is inevitable and comparatively larger. Although patient's thermal noise can be modeled for a given configuration of receiver coil. It is generated from the random variation of charged particles in the patient's body tissue. Thus the signal which is of the order of few mV, available at the front-end is highly susceptible to noise. In traditional MRI receiver, the low-level RF input signal was transmitted over coaxial cable to MRI data acquisition system for signal processing, placed out of the examination room. In other words, from RF coil to LNA the signals were passed over long coax making it highly susceptible to interference<sup>[7]</sup>. Thus to ensure a high-quality image from a system view, the SNR of the receiver electronics should be higher than 90 dB [8]. The quest for higher SNR has been mostly realized with surrounding factors so far like increasing the static magnetic field  $B_{0}$ . increasing the number of channels, using parallel-imaging and averaging - taking multiple scans for the region under inspection and so on. But little had been done in the analog

### CHAPTER 1. INTRODUCTION

front-end electronics until past decade. This has lead to bulky coaxial cables and connectors, increase in cost and scan time for MRI.

Figure 1.3: Block diagram of MRI receiver's analog front-end with direct digitization

Now with the advancement in CMOS technology, a lot more improvements can be done in analog front-end leading to the invent of on-coil receiver, i.e. using an integrated broadband receiver that digitizes the signal at the MRI machine itself. It is a paradigm shift in the MRI machine with lower interference, higher image quality, faster scan, lower power and thereby reducing the cost as well [7]. This has been made possible due to the direct digitization receiver architecture. It employs the high speed ADC known as RF sampling ADC to digitize the signal in RF band only. At Philips, MRI machine uses the direct digitization and its receiver architecture is referred to as dstream, shown in Fig. 1.1e [5]. The analog front-end of the RF receiver after employing the direct digitization is shown in Fig. 1.3. In this receiver architecture, single RF sampling ADC can replace the IF sampling subsystems including mixer, local-oscillator synthesizer (LO), amplifiers (VGA, ADC driver), filters and ADC [9]. It increases the digital integration and omits the need for down-conversion in analog-domain which is now moved to digital processing units such as ASIC/FPGA or can even be done inside RF ADC with custom integrated circuit (IC) design [10]. Digital signal processing has long been preferred causing analog electronics to shrink, for its immunity to noise and capability of reusing the same hardware for multiple configurations. It allows a lot more compact hardware, low power and low noise solution to the MRI receiver. However, at the same time, the specifications for remaining analog front-end now become stringent.

### 1.2 Motivation

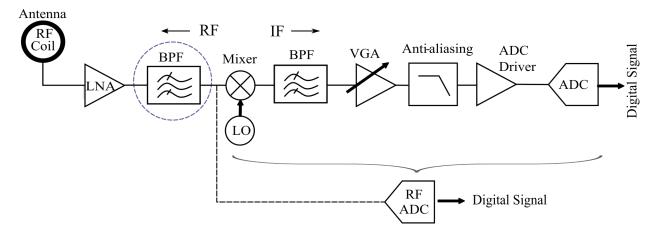

As per the working principle of MRI, in order to receive the maximum signal strength, the RF excitation and reception takes place precisely at the Larmor frequency, say 127.8 MHz(for  $H^+$  at 3 T). This implies that the signal of interest is only available around Larmor frequency. However, a wideband signal is fed into an RF sampling ADC, making it susceptible to noise. As a result, RF sampling ADC can limit the sensitivity of the receiver which refers to the minimum signal sensed efficiently. Whereas in IF receiver with the help of mixer, LO and ADC driver a sufficient gain has been added to the signal before ADC, raising the signal well above the noise-level also being at baseband the noise bandwidth was smaller [11].

Figure 1.4: Signal at the input of RF ADC [12]

One of the efficient way of reducing the noise is to reject the undesired frequency band from the received signal with high stopband attenuation as shown in Fig. 1.4. That's the role of the front-end bandpass filter placed before the RF ADC in Fig. 1.3. The MRI front-end bandpass filter is employed to select the narrow band around the Larmor frequency and reject the rest of the input signal, i.e. suppressing noise in the stopband. The MRI front-end bandpass filter hereafter is termed as filter. Due to RF sampling ADC, the filter requires to be indispensably precise ahead of it. In such an SNR-critical application, a highly selective filter (Q > 300) is required with sharp roll-off and high stopband attenuation (70 dB-80 dB). In addition, it should prevent the desensitization of receiver with its high passband gain (50 dB-60 dB) compensating the gain of the signal-chain otherwise added by mixer, LO and ADC driver. In contrast, the filter for the classic receiver would have relaxed specifications with a sufficient stopband attenuation (60 dB) at nominal selectivity (Q < 50) with low or even no passband gain (0 dB).

Such strict requirements of the filter make it highly sensitive to the deviation in its components under variable operating conditions. At a high frequency of hundreds of MHz, one can expect even a small deviation in filter response will not only pass but also amplify the noise separated with few tens of kHz that should have been suppressed otherwise in stopband. This can deteriorate the SNR of receiver. Being a medical device of high precision it is required that the filter response should remain stable with the change in operating

conditions due to temperature of the environment, voltage supply fluctuation and process artifacts. Also, there is an associated concern of power dissipation in MRI electronics, due to which the operating supply voltages are lower which makes it even more complicated to achieve high dynamic range of the filter with such a response. Choosing an appropriate architecture of the filter can limit these variations.

The desired frequency response of the filter is defined by Philips based on their receiver architecture and so does the filter architecture as well. Philips adopted a sixth-order RLC bandpass filter for this purpose. Apart from passive components (LC tanks), the filter uses active components, i.e. transconductor. Transconductor acts as a gain element of the filter as well as a current source preventing the interference between the tanks. Transconductor blocks are implemented in the form of parallel-connected discrete cells for the feature of wideband programmability of the filter IC. The filter is further detailed in Chapter 2-System Design.

Transconductance  $(g_m)$  is of our interest here, which is the key parameter for passband gain and bandwidth of the adopted filter architecture. Transconductor's  $g_m$  is susceptible to variations as it is a function of process and temperature dependent variables. The currently employed transconductor is no exception and faces a deviation in  $g_m$  of more than 15% with process, temperature and supply variations. Consequently, deviation in  $g_m$  will lead to variation in the filter's gain (>10%) and bandwidth. Operating at low voltages, this will significantly deteriorate the SNR and dynamic range of the filter, hence that of the receiver. The total number of transconductor cells in the filter are more than 200. Having such a large quantity of transconductor cells makes the situation even more vulnerable, cascading the effect of deviation in a single cell on the filter response rendering it to become highly sensitive to  $g_m$ . The goal of the study is to achieve a constant  $g_m$  of the unit transconductor cell such that the filter response remains intact. The three variations that have been considered are defined as follows, also termed as PVT variations.

- Power Supply : As it is a medical device, the power supply is well maintained during the MRI examination process. However, a variation of 10% about the operating voltage of 1.1 V is considered, i.e. voltage range is 0.99 V - 1.21 V. The origin of supply variation comes from two factors. First, the filter IC is the analog-mixed-signal chip, i.e. it has digital as well analog circuit implemented on the same chip so there is a high vulnerability of substrate noise from its digital counterparts. Moreover, 1.1 V is not an external supply, but generated on-chip with power converters this can lead to high frequency switching signals in the locally generated supply.

- 2. Temperature : Period of MRI scan can vary between 20 50 minutes [13]. The power dissipation in receiver electronics can result in thermal heating and prolonged exposure to the RF radiation can raise the temperature of the patient's body, also it may cause the electronics to heat up in RF field [8]. However, according to the safety standard IEC 60601-2-33[14], the increase in core body temperature shall be less than 1°C. This suggests that power dissipation in the receiver electronics remain the primary

source of increase in temperature. To ensure the performance of the medical device the temperature range of  $0^{\circ}$ C -  $85^{\circ}$ C is considered. Although, for safety and ambient experience of the patient  $0^{\circ}$ C and  $85^{\circ}$ C are extreme ends and less likely to occur.

3. Process corner: Process corners are the artifact of the IC fabrication. It occurs due to the non-uniformity of the doping level across the ICs on the same silicon wafer, depending on their location on the wafer. The transistors which receive lower doping are called slow(s) corner while the one with higher doping levels are called fast(f) corners. The variation in doping levels increase or decrease the threshold voltages of the respective corners. In our analysis, we have considered all five process corners – ss, ff, sf, fs and tt. The naming is conventional. The first letter denotes the type for N channel MOSFET (nMOS) and latter for the P channel MOSFET (pMOS). For example, sf implies slow nMOS and fast pMOS. While 't' refers to typical or nominal corner, that is when doping levels of the devices are same as expected.

The desired transconductor specifications are guided by the filter which is a sixth-order RLC bandpass filter with a high Q-factor of 400. It has a center frequency of 127.8 MHz (for 3 T,  $H^+$ ), passband gain of 60 dB and bandwidth of merely 350 kHz. The tolerance of passband gain variation is about 2% and that of bandwidth is less than 0.5%, while the center frequency is finely tuned to the Larmor frequency (127.8 MHz) by the LC tank. For such a filter response, the unit transconductor cell has an acceptable  $g_m$  deviation of around 2% under the PVT variations, thus filter will have the subsequent performance as listed in Table 1.1 as compared to the one with previous transconductor.

|                                                           | Previous       | Target         |

|-----------------------------------------------------------|----------------|----------------|

|                                                           | Transconductor | Transconductor |

| Center frequency (Hz)                                     | 127            | .8M            |

| Order of Filter(biquad)                                   | $6^{th}$ , Ba  | ndpass         |

| $g_m$ with voltage $(0.99 \text{V-}1.21 \text{V})$        | 15%            | $\sim 2\%$     |

| $g_m$ with temperature $(0^{\circ}-85^{\circ}\mathrm{C})$ | 10%            | $\sim 2\%$     |

| Passband Gain of filter                                   | 10%            | $\sim 2\%$     |

| -3 dB BW of filter                                        | 0.5%           | $<\!0.5\%$     |

| SNR of filter (dB)                                        | 110            | 110            |

Table 1.1: Target Performance for the Proposed Transconductor

The scope of this study is to investigate into the new transconductor cell and its respective biasing circuit to achieve the target performance as listed in Table 1.1 with respect to the previous transconductor (the one used at Philips). These specifications also implicate the constraints such as low power supply (1.1 V), wide bandwidth (> 300 MHz) and low noise requirement on transconductor cell. The study includes three stages of design - architecture, transistor-level implementation and layout of the proposed transconductance circuit. It shall be noted that the passive components constructing the LC tank are placed off the chip and the filter IC being a mixed-signal chip is out of scope to layout. Although, the performance has been analyzed at the system level of filter using post-layout simulations of proposed transconductance circuit and modeling the off-chip components.

### **1.3** State of the Art constant- $g_m$ circuit

In literature, several times the technique of constant- $g_m$  biasing has been used to achieve a stable  $g_m$  with PVT variations [15, 16, 17, 18, 19, 20, 21, 22]. The implementation of the technique is conditioned to the application. So far, none of them has implemented it for a high frequency programmable filter with very high selectivity and passband gain.

Although [15] presents a programmable wide bandwidth filter for a range of 60 - 350 MHz but it is a low pass type with no gain (0 dB), relatively smoother response, i.e. Q < 50 and acceptable cut-off frequency deviation of 2%. Whereas in this MRI specific filter, there exists a high passband gain of 60 dB which is a major function of  $g_m$  of the transconductors, while the center frequency is independent of the  $g_m$ , accurately held by LC tank to align with the Larmor frequency, so there is difference in the key parameters of the two systems. In [16, 20, 22], beta-multiplier is used based on square-law model which doesn't hold true for modern day short-channel process technology. In [15, 20, 22, 18], transconductance tracks the off-chip resistor, which is a costly solution and also suffers from parasitic pole-zero pair at lower frequency. Hence, it requires a large off-chip compensation capacitor [17]. In [17], 23, master-slave topology has been adopted to implement the on-chip resistor. [17] uses MOS operating in triode region as the resistor which is controlled by a switched capacitor network in a feedback loop. [23] uses an on-chip oscillator to tune the resistor precisely, but both are implemented for relatively lower frequency of few MHz only. In [19], author presents the transconductor biased in sub-threshold with on-chip switched-capacitor resistor but it is used for low frequency lower-order filter.

Moreover, looking at the constraints for our case, a lower power supply is available for the filter circuit. We know, the MRI front-end receiver has the requirement of high dynamic range. This implies there is a need for high input-output swing of the filter close to supply rails. In [24, 20, 23], inverter based transconductor is used for low-voltage application biased with constant- $g_m$  methodology. Of which, [20] presents the application for high order bandpass filter. But all of them have a comparatively higher acceptable variation in center frequency/cut-off frequency deviation for their respective application. 10% for [24, 20] and 4% for [23]. [25, 26], presents a self-biased common-mode control for differential pair but not used in conjunction with constant- $g_m$  bias methodology.

None of these align with all the criterion to be fulfilled for our design due to the difference in system-application, operating conditions and implementation level.

### 1.4 Thesis Organisation

The thesis is organized in four parts from chapter 2 to chapter 6 - system design, circuit implementation, results, discussion and conclusion.

- Chapter 2 provides study of the system design which includes choice of filter type, programmability feature, filter architecture and its implementation chosen by Philips. Further, it also describes the issues in the previous implementation of transconductor and looks into design challenges associated with PVT tolerance of the transconductor. Following which, constant-transconductance biasing technique is discussed as a potential solution.

- Chapter 3 presents circuit implementation of the proposed transconductor and its biasing circuit. It analyzes the chosen design with respect to the requirements. Further, this chapter presents the MRI filter using the proposed transconductor and tuning of the resonators after incorporating the parasitics. Also, switch configuration of the transconductor is presented here for the filter programmability. Lastly, the chapter presents the layout of the two blocks, the proposed transconductor and its bias.

- Chapter 4 presents the post-layout results and comparisons with the previous transconductor circuit. First, the standalone transconductor results are shown, then the impact of the proposed transconductor on the stability of the MRI filter's frequency response has been presented in terms of its passband gain and bandwidth. Lastly, it shows the performance of the filter in terms of noise and distortion.

- Chapter 5 presents the discussion on the design elements, highlighting the positives and trade-offs made. Also, a performance comparison of the proposed transconductor with respect to the state-of-the-art design has been done in this chapter.

- Chapter 6 provides an overall conclusion of the study and highlights the contributions made in this thesis. Lastly, it provides some insight into the possible improvements that can be taken up further in future.

There are two appendices provided at the end that can be referred for more details as it may require for further understanding of the reader.

# Chapter 2 System Design

As we had discussed in the previous chapter, the front-end of MRI receiver requires a highly- selective bandpass filter to select the region around the Larmor frequency only, while drastically attenuate the noise in the rest. This becomes challenging due to direct-digitization. While operating at such a high frequency of hundreds of MHz one can expect noise separated between passband and stopband with few tens of kHz, which is quite small in logarithmic scale but significant for the application of MRI. In addition, given that MRI is an SNR-critical application, feeding the RF signal directly into the ADC, because of direct digitization, makes the receiver vulnerable to be desensitized, having to digitize the input signal without sufficiently separating it above the noise floor. Hence, there is a requirement of a bandpass filter with a very sharp roll-off to limit the noise bandwidth much closer to the passband as well as high gain to amplify the signal before sending it to RF ADC. On top of this, the stability of the filter's frequency response has to be maintained for the precision of MRI.

In this chapter, first, the theory of parallel RLC circuit is discussed, which is one of the building blocks of the filter architecture. Then, the filter architecture has been detailed, the one adopted and employed by Philips to meet the requirements of the MRI front-end receiver. Following which, the implementation of the filter circuit with the previous transconductor has been discussed and analyzed. Lastly, the challenges to achieve stable transconductance circuit have been discussed and the concept of constant-transconductance biasing methodology is presented, which is adopted to fulfill the requirements.

### 2.1 Parallel RLC Resonator

A highly selective bandpass filter can be realized very accurately using parallel RLC resonator. RLC resonators are widely used as tuning circuit for their ability to select narrow band from the radio signal. They can be tuned to exact pole frequency, also termed as resonance frequency,  $\omega_0$  as well as can achieve high Q-factor by choosing appropriate value of its components as defined in Eq. (2.1). At high frequencies of hundreds of MHz the inductor and capacitor lies in the order of tens of nanohenry and picofarad range respectively, which can't be monolithic but placed off the chip. Q-factor for the system is defined as the ratio of peak energy stored in the circuit to the energy dissipated at resonance per radian. In terms of the filter it denotes the ability to pass the selected band of frequencies and reject the stop band.

$$\omega_0 = \frac{1}{\sqrt{LC}} = 2\pi \cdot f_0$$

$$Q = R \sqrt{\frac{C}{L}}$$

(2.1)

for band pass system,

$$Q = \frac{\omega_0}{\Delta\omega} \tag{2.2}$$

As per the requirements of Philips' MRI receiver, the filter needs a Q-factor of 400 at center frequency of 127.8 MHz for protons in 3 T MRI machine. In Eq. (2.2)  $\Delta \omega$  represents the bandwidth that is defined as the difference between the -3 dB frequencies about the center frequency  $\omega_0$ . For the center frequency ( $f_0$ ) of 127.8 MHz and Q of 400, the calculated bandwidth is 350 kHz, which is an extremely narrow band. To achieve high-selectivity, one can increase the Q-factor and the order of the filter. Higher order implies more number of storage elements. To realize such a filter, suitable components shall be selected. To determine the component selection, the understanding of the frequency response of the parallel RLC circuit is illustrated. Fig. 2.1 represents the the parallel RLC circuit for natural response analysis [27].

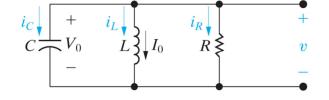

Figure 2.1: Circuit for illustrating the natural response of the parallel RLC circuit [27].

From Fig. 2.1, the equation for the differential voltage across the circuit can be given by

$$\frac{v}{R} + \frac{1}{L} \int_0^t v d\tau + I_0 + C \frac{dv}{dt} = 0$$

$$\frac{1}{R} \frac{dv}{dt} + \frac{v}{L} + C \frac{d^2v}{dt^2} = 0$$

(2.3)

If we take the Laplace transform of the Eq. (2.3) we get the characteristic equation of the parallel RLC circuit.

$$s^2 + \frac{s}{RC} + \frac{1}{LC} = 0 (2.4)$$

From this the roots of the quadratic equation can be calculated that is the poles of parallel RLC circuit's frequency response.

$$s_1, s_2 = \frac{-1}{2RC} \pm j \sqrt{\left(\frac{1}{2RC}\right)^2 - \frac{1}{LC}}$$

(2.5)

Neper frequency,

$$\alpha = \frac{1}{2RC}$$

Resonant frequency,  $\omega_0 = \frac{1}{\sqrt{LC}}$

In time-domain, the solution of the characteristic equation Eq. 2.4 can be denoted as in Eq. 2.6, where  $A_1$  and  $A_2$  are the coefficients.

$$v = A_1 e^{s_1 t} + A_2 e^{s_2 t} \tag{2.6}$$

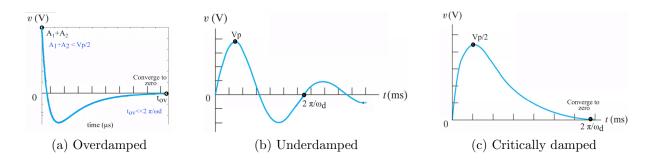

There are three possible behaviours of the natural response guided by the  $\omega_0$  and  $\alpha$ , independent of  $A_1$  and  $A_2$ . If  $\omega_0^2 < \alpha^2$ , the response is overdamped, if  $\omega_0^2 > \alpha^2$ , the response is underdamped and if  $\omega_0^2 = \alpha^2$ , the response is critically damped. In time-domain, the damping represents the way the response reaches its final value, i.e. steady state value which is governed by the damping frequency,  $\omega_d = \sqrt{\omega_0^2 - \alpha^2}$  [27]. Hence, for a characteristic equation of a particular parallel RLC circuit, the three different natural response are possible depending on the value of the resistance as shown in Fig. 2.2.

Figure 2.2: Natural response of parallel RLC circuit [27]

For the implementation of MRI front-end filter, there is a requirement of 60 dB gain (otherwise, 0 dB - 20 dB) in the passband with infinitesimally small loss of energy. One can visualize a response along the similar lines of underdamped case above but with increased peak-to-peak amplitude and very slow decay over time. Parallel RLC is a passive circuit, so to add gain there is a need of an active element to be included in the configuration that sources energy. The chosen active element is the transconductor which acts as a current source without disturbing the construct of LC tank, i.e. prevent any interference between the tanks [28]. For such a filter, it can be said that the component values are strongly guided by the desired poles and passband gain where R, L, C depend on poles and transconductance  $(g_m)$  depends on gain.

### 2.2 Filter Circuit

As per the requirements of the MRI receiver at Philips, the filter needs a Q-factor of 400 and three complex-conjugate pairs of pole, i.e. sixth order to achieve the desired high selectivity. To implement an analog filter, the four commonly used configurations are active-RC,  $g_m$ -C, switched capacitor (SC) and LC. SC filters are resilient to PVT variations. However, they are prone to noise due to the clock feedthru as well as preferable for relatively low-order low frequency operation. In active-RC and  $g_m$ -C, the pole/zero locations are defined by the R (or  $1/g_m$ ) and C, so their stability depends on the matching achieved. Active-RC filters suffer from poor matching of R and C, thus time constants vary upto 30% with PVT variation [29]. However,  $g_m$ -C filters can achieve a good matching to provide stable filter response with high-order high frequency operation, but Q is limited to less than 100. This is because Q in  $g_m$ -C is based on the transconductance division. Also, active filters are prone to noise and non-linearity.

On the other hand, LC filters can implement Q as high as 1000 with high-order and high frequency of operation that too with low noise and good linearity [30]. In addition, the locations of time constants are accurately determined by the discrete components (L and C) providing stable response with PVT variations. Given the priority of noise, selectivity and accuracy of the filter in MRI front-end receiver, the LC implementation is best suited.

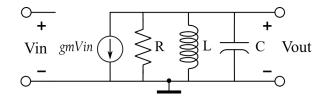

The filter IC is designed to be programmable for a range of 64 MHz -128 MHz, i.e. using same IC for a range of Larmor frequencies. In addition, there is a need of high gain (60 dB) in the passband. Hence effectively, the filter is a tunable amplifier [28]. For gain, an active element can be placed in parallel to the LC tank. An LC filter is as shown in Fig. 2.3. At resonance, the effective impedance, Z(s) of the RLC filter is only resistance, R so the voltage at the output, *Vout* is directly proportional to current,  $g_m V_{in}$ , i.e.  $Vout = -g_m V_{in} * R$ . Thus, it can be said that the gain of the LC filter is  $g_m R$ , where R is constant decided by Q-factor of the filter.

Figure 2.3: LC filter

The transfer function of the filter in Fig 2.3 can be written as

$$\frac{V_{out}}{V_{in}} = -g_m Z(s) = \frac{-g_m}{C} \left(\frac{s}{s^2 + \frac{s}{RC} + \frac{1}{LC}}\right)$$

(2.7)

| Pole (MHz)               | Zero (MHz)               | Q <sub>pole</sub> |

|--------------------------|--------------------------|-------------------|

| $-0.160 \pm j \ 127.800$ | $-5.578 \pm j \ 129.656$ | 400               |

| $-0.159 \pm j \ 127.200$ | $-3.003 \pm j \ 125.816$ | 400               |

| $-0.160 \pm j \ 128.400$ | -150.900 & 0(origin)     | 400               |

Table 2.1: Poles and zeros of MRI filter

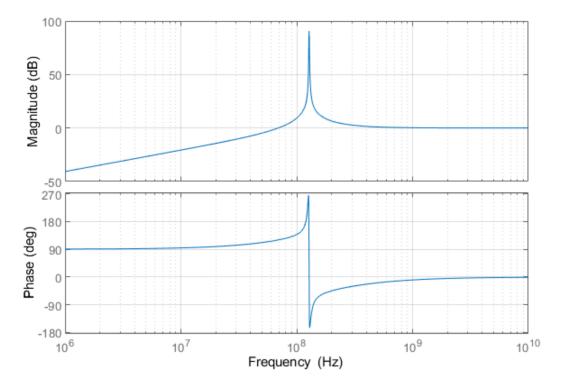

Figure 2.4: Magnitude and Phase response of the desired filter

The desired poles and zeros of the filter are defined in Table 2.1 and the corresponding frequency response is shown in Fig 2.4. From the frequency response of the filter, the poles and zeros can be identified as follows. There exists a zero at the origin, providing  $+90^{\circ}$  phase shift. It is followed by two pairs of complex-conjugate zeros at 125.8 MHz and 129.7 MHz that surrounds the three pairs of complex-conjugate poles at 127.2 MHz, 127.8 MHz and 128.4 MHz. This marks the passband of the filter with Larmor frequency (127.8 MHz) at the center. This band brings a phase shift of  $-180^{\circ}$ . Until here, we have our five zeros and six poles. Further, at 151 MHz there occurs the sixth zero shifting the phase by  $+90^{\circ}$  bringing the resultant phase to  $0^{\circ}$ , for it is a biquad filter.

Three resonators can be placed in a cascaded fashion to implement the poles. Each resonator represents a second order section, adding up to sixth order of the filter. Resonator frequencies are chosen close to each other, such that the Larmor frequency is in the middle of the three. Such a configuration prevents any major deviation in the filter response at the Larmor frequency, which can otherwise be impacted by the variation in field strength or MRI system electronics, thereby slightly shifting the resonance frequency of the receiver. To limit the phase shift across the filter to less than 180° as well as achieve flat passband six zeros are realized making it a biquad filter.

### 2.2.1 Filter Programmability

MRI filter IC incorporates the capability of tuning to a range of center frequencies from 64 MHz - 128 MHz. This means same filter IC can be employed in multiple scan machines as well as for varied nucleus targets. Center frequency of the filter is the resonance frequency of the receiver that is equal to the Larmor frequency, which depends upon the target nucleus and strength of MRI machine given by Eq. (2.8) (reiterating here for continuity), where  $f_0$  is the Larmor frequency in MHz,  $\gamma$  is the gyromagnetic constant (for H<sup>+</sup>, 42.6 MHz/T) and  $B_0$  is the strength of static magnetic field in tesla (T).

$$f_0 = \gamma B_0 \tag{2.8}$$

In LC filter inductor and capacitor, being off-chip components, can be chosen as per the requirements of new resonance frequency of the receiver guided by the Larmor frequency. The off-chip capacitance is employed in conjunction with an on-chip variable capacitance, which is primarily used to incorporate parasitics in filter, will be discussed later. Given, high frequency operation, a change of few hundred's of fF can change the resonance frequency of filter in the order of MHz. Hence, new resonance frequency differed by few MHz can be realized without any variation in off-chip components but only using the integrated capacitance bank, upto a range of 2pF. However, in case of larger changes in resonance frequency, inductor and capacitor both should scale proportionally to keep the Q-factor constant.

For example, in case of scanning flouride ions  $(F^-)$  instead of proton  $(H^+, 128 \text{ MHz})$  in 3 T machine whose Larmor frequency is 120 MHz [31] which can be achieved by the on-chip capacitance bank without much deviation in Q-factor. Whereas, in case of protons under 1.5 T MRI machine, the Larmor frequency is reduced to half, 64 MHz. To achieve resonance at this frequency off-chip capacitance and inductance both are doubled maintaining the same Q-factor.

While programming the filter to a different resonance frequency, shape of the filter response should remain intact. This is achievable if we make the components on IC, i.e. transconductor, switchable. This will enable a complete freedom of varying the filter components as per the requirement of chosen filter configuration. Fig. 2.5 shows the transconductor Gm block as a group of parallel connected N transconductor cells whose switches are controlled by a digital selection signal "sel". Array of signal "sel" can be controlled by a binary decoder at the top level.

Figure 2.5: Switchable transconductor for programmability

### 2.2.2 Architecture Overview

Figure 2.6: Filter Architecture for MRI Receiver

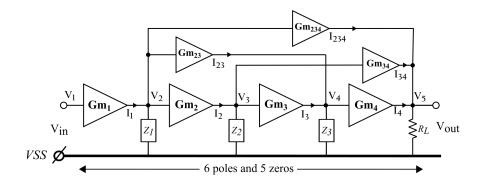

Filter architecture implements passive LC tanks tuned to the desired pole frequencies and corresponding active elements contributing gain in the passband, as shown in Fig. 2.6. It is a sixth order biquad filter with six poles and six zeros. Poles and zeros can be noticed in the filter as follows. Resonators,  $Z_{1-3}$  realize three pairs of complex-conjugate poles, making six poles in total. Feed-forward paths realize the two pairs of complex-conjugate zeros. Rest of the two zeros are real zeros, one is located at the origin as there exists a direct path from input to output through  $Gm_{1-4}$  and second, the sixth zero has been implemented after buffer with an integrator. Here, Z denotes the parallel RLC resonator block while Gm denotes the transconductor block, i.e. transconductor cells connected in parallel.

Since, we are only concerned with improving the performance of filter by redesigning the transconductor, for that purpose only the filter stage from  $V_{in}$  until  $R_L$  is of our interest. The integrator doesn't play any role in the transconductor analysis, so it can be excluded. Fig. 2.6a shows the portion of the filter with six poles and five zeros, excluding the integrator. Fig. 2.7 shows its corresponding frequency response. Since, sixth zero (151 MHz) is well separated from the passband (125 MHz-130 MHz) of the filter, shape of the magnitude response in passband remains same, only the gain is reduced from 90 dB to 60 dB. While, the phase response shows an additional shift of -90° at 151 MHz as compared to the full filter circuit due to the exclusion of zero (at 151 MHz). For further references and reading, only the part from  $V_{in}$  until load resistance  $R_L$  is denoted as the filter. The total phase shift across the filter is 180° with the peak gain of 60 dB at 127.8 MHz.

Figure 2.7: Ideal frequency response of the filter (excl. sixth zero)

| Pole (MHz)               | Resonator      | Capacitance (pF) | Resistance $(k\Omega)$ | Inductor (nH) |

|--------------------------|----------------|------------------|------------------------|---------------|

| $-0.160 \pm j \ 127.800$ | Z <sub>1</sub> | 31.02            | 16                     | 50            |

| -0.159 ± j 127.200       | Z <sub>2</sub> | 31.31            | 16                     | 50            |

| $-0.160 \pm j \ 128.400$ | Z <sub>3</sub> | 30.73            | 16                     | 50            |

Table 2.2: Component values (RLC) of three resonators corresponding to their poles

Once the architecture is decided, component selection can be done as follows. For a resonance frequency of the order of hundreds of MHz, the capacitor and inductor lies in the order of tens of pF and nH respectively. Since they are large to accommodate for monolithic implementation, they are placed off-chip. An inductor of 50 nH is chosen suited to the pole frequencies. Once the inductor is decided, the capacitor and resistance can be calculated for the respective poles frequencies with Q of 400 using the Eq. (2.1). The resistance comes out to be 16 k $\Omega$  while the capacitance is around 31 pF. The values are given in Table 2.2. Thus we know resonator components from desired pole frequencies, now we need to determine the transconductance of Gm block. This can be calculated by equating the transfer function derived from pole-zero information to that of the nodal analysis of filter architecture. The transconductances of the Gm blocks are decided by the passband gain of 60 dB, i.e. 1000x. With nodal analysis, transfer function of the filter architecture can be written in terms of transconductance  $Gm_{1-234}$  and resonator impedance  $Z_{1-4}(s)$ ,

$$\frac{V_{out}}{V_{in}}(s) = R_L \{ (Gm_1 Z_1(s) Gm_2 Z_2(s) Gm_3 Z_3(s) Gm_4 + Gm_1 Z_1(s) Gm_4 Z_3(s) Gm_{23} + Gm_1 Z_1(s) Gm_2 Z_2(s) Gm_{34} + Gm_1 Z_1(s) Gm_{234} \}$$

(2.9)

$$Z(s) = \frac{1}{C} \left( \frac{s}{s^2 + \frac{s}{RC} + \frac{1}{LC}} \right)$$

(2.10)

| Gm block | mA/V (mS) | Gm block                 | mA/V (mS) |

|----------|-----------|--------------------------|-----------|

| $Gm_1$   | 2.5       | <i>Gm</i> <sub>23</sub>  | -1.7      |

| $Gm_2$   | 1.25      | $Gm_{34}$                | -0.02     |

| $Gm_3$   | 1.25      | <i>Gm</i> <sub>234</sub> | 0.34      |

| $Gm_4$   | 0.625     |                          |           |

Table 2.3: Transconductance per Gm block in ideal filter

Table 2.3 shows the transconductances of the respective Gm blocks calculated after comparison of the two equivalent transfer functions. Note that the values in table only denote the result of mathematical calculation, which indicates there is a need of inversion in transconductance  $Gm_{23}$  and  $Gm_{34}$ . Every Gm block is composed of a group of discrete transconductor cells connected in parallel, where unit transconductor cell is shown in Fig. 2.6c. If unit  $g_m$ -cell transconductance is  $g_m$  and the number of  $g_m$ -cells in a block is N(Gm), then transconductance of that block, Gm equals to  $N(Gm) * g_m$ . The  $g_m$  of the unit transconductor cell can be chosen depending on the desired programming resolution. Lower the value, higher is the resolution. It has been found that the unit transconductance if aligns with the multiple of inverse of load resistance that is 62.5  $\mu$ S (1/R), a good linearity of the filter is achieved. In the previous circuit, the unit transconductance ( $g_m$ ) of 31.25  $\mu$ S is realized. Thus, the number of transconductor cells per Gm block can be calculated by dividing the transconductance of the block, given in Table 2.3, by the unit cell  $g_m$ , 31.25  $\mu$ S. Table 2.4 shows the number of unit transconductors in each block  $Gm_{1-234}$  denoted as  $N(Gm_{1-234})$ . For further understanding on calculating the scale factors of Gm block the reader is referred to Appendix A.

| Gm block  | No. of $g_m$ -cell | Gm block      | No. of $g_m$ -cell |

|-----------|--------------------|---------------|--------------------|

| $N(Gm_1)$ | 80                 | $N(Gm_{23})$  | 54                 |

| $N(Gm_2)$ | 40                 | $N(Gm_{34})$  | 1                  |

| $N(Gm_3)$ | 40                 | $N(Gm_{234})$ | 11                 |

| $N(Gm_4)$ | 20                 |               |                    |

Table 2.4: Number of transconductor cells per Gm block in ideal filter

### 2.2.3 Previous Circuit

Previous circuit primarily, refers to the previous transconductor cell and the filter constructed after plugging those  $g_m$ -cells in the architecture mentioned above. It is the one which is employed at Philips, whose performance improvement is the goal of the thesis as mentioned earlier.

### A. Previous Filter

As we noticed in Table 2.3, mathematically there is a requirement of negative transconductance for  $Gm_{23}$  and  $Gm_{34}$ , which means a polarity inversion in practice. It is because each of them provide an auxiliary feed forward path over two Gm blocks which reverses their polarity. Hence, a differential topology is adopted so as to make use of the opposite phase available on either side of the resonator.

Fig. 2.8 shows the filter circuit in differential form. Here  $Gm_{23}$  and  $Gm_{34}$  have their output and input cross connected respectively to other half of the schematic for the purpose mentioned above. To realize same transfer function with differential topology it can be understood that for each half circuit, resonator impedance will go half while current will go

Figure 2.8: Fully-differential filter schematic using previous transconductor cell

| Gm block  | No. of $g_m$ -cell | Gm block      | No. of $g_m$ -cell |

|-----------|--------------------|---------------|--------------------|

| $N(Gm_1)$ | 160                | $N(Gm_{23})$  | 109                |

| $N(Gm_2)$ | 80                 | $N(Gm_{34})$  | 1                  |

| $N(Gm_3)$ | 80                 | $N(Gm_{234})$ | 22                 |

| $N(Gm_4)$ | 40                 |               |                    |

Table 2.5: Number of transconductor cells per Gm block in previous circuit

double. In simple words, for half circuit  $\mathbb{R} \to \frac{R}{2}$ ,  $\mathbb{L} \to \frac{L}{2}$ ,  $\mathbb{C} \to 2\mathbb{C}$ , while the scale factor for transconductors goes 2x on each side of the differential filter configuration. The total resonator impedance of the full circuit remains same, hence component values of R, L and C in the fully-differential circuit are same as that of the single-ended, previously shown in Table 2.2. Whereas, transconductor cells per *Gm* block as well as the number of *Gm* blocks become double in fully-differential filter. This employs 4x the total number of unit transconductor cells as compared to the single ended filter, shown in Table 2.5. The circuit in Fig. 2.8 has been employed in the Philips MRI machine. This is our reference for benchmarking. The transconductor cell used here is referred to as the previous transconductor.

### **B.** Previous Transconductor

The previous transconductor is a single-ended CMOS transconductor as shown in Fig. 2.8b. It provides high input-output swing with its complementary MOS input-output pair, suitable for high dynamic range (>90 dB) at low voltage supply (1.1 V) operation. It is biased with a fixed voltage bias Vcon, which is set at 860 mV providing a fixed transconductance

of 31.25  $\mu$ S to the transconductor cell. Frequency response of the filter using the previous transconductor is shown in Fig. 2.9. With real implementation of the filter circuit, frequency response matches fairly well to the desired response (ideal). This confirms that this adopted architecture meets the requirements of the filter, given that circuit elements are stable and not subject to variations.

Figure 2.9: Previous transconductor implemented filter response - simulation results

Although, Table 2.2 depicts the component values of resonators in ideal case, in practical the transconductor cell's output capacitance and resistance will act as parasitic to the filter, which shall be incorporated to keep the frequency response intact. As mentioned before, for three resonators, the inductor is fixed at 50 nH due to the standard off-chip component, resistance is monolithic integrated component while capacitance has been divided into two parts, one being integrated capacitance bank and other, an off-chip standard capacitance. This implies that during the IC implementation, it is possible to incorporate the shift in filter poles arising due to the parasitics of the  $g_m$ -cells, with the help of resonator capacitance and resistance as required. It is further detailed with respect to the proposed transconductor in *Parasitics in Filter* (Section 3.2.2). Resonator capacitance and resistance after including the parasitics from the transconductors is given in Table 2.6. However, it shall be noted that the net resistance and capacitance at resonator remains same as that of the ideal which is the requirement of the system, the values "with Gm" only indicates the residual component values required to achieve the ideal value after parasitics are considered. The table shows that there is a requirement of negative resistance in resonators. This can be implemented using the transconductor itself. Principally, a transconductor is a voltage-to-current converter and if the polarity of voltage across a device is in reverse with the polarity of the flow of current through it, it can be treated as a negative resistance. This is also detailed with respect to the proposed transconductor in *Parasitics in Filter* (Section 3.2.2).

| Pole (MHz)             | Capac | itance (pF) | Resistance $(k\Omega)$ |         | Q-factor  |

|------------------------|-------|-------------|------------------------|---------|-----------|

| Pole (MIIIZ)           | Ideal | with Gm     | Ideal                  | with Gm | (with Gm) |

| $-0.160 \pm j \ 127.8$ | 31.02 | 30.97       | 16                     | -20     | 398       |

| -0.159 ± j 127.2       | 31.31 | 31.27       | 16                     | 144     | 387       |

| $-0.160 \pm j \ 128.4$ | 30.73 | 30.7        | 16                     | -87     | 410       |

Table 2.6: Resonator components for previous transconductor implemented filter. L=50nH

### 2.2.4 PVT Tolerance

There are four circuit elements in the filter - inductor, capacitor, resistor and transconductor. The inductor and capacitor being off-chip can be chosen to have high precision, while integrated resistor is a negative resistance implemented with transconductor and lastly transconductor itself. This implies, predominantly it is transconductor which is responsible for the performance of the filter IC. For filter to accurately select the channel with the desired passband gain under the process, voltage and temperature variations, the  $g_m$  of the transconductor shall be constant.

### A. Challenges

Transconductance is subjected to variation due to its dependency on temperature and process variable parameters such as threshold voltage  $V_{th}$ , mobility  $\mu$ . Previous transconductor also suffers from  $g_m$  deviation due to several factors. First, it uses a fixed-voltage bias (*Vcon*). Although, *Vcon* is a stable biasing voltage, but there are more than 200 x 4 transconductor cells on the chip which are biased with same voltage supply, *Vcon*. Any coupling with other signals on chip or voltage drop across *Vcon* path can disturb the biasing point of transconductor cell. Second, it lacks any self-stabilizing capability being a single-ended structure. It has no power supply or common-mode rejection ability, thereby highly sensitive to any variation in its operating conditions say temperature or voltage. This makes the stability of the transconductor be solely dependent on its bias, which in itself is vulnerable to variations as mentioned formerly.

In post-layout simulations, it is observed that previous transconductor cell suffers from more than 15%  $g_m$  deviation under the impact of PVT variations. This leads to up to 10% degradation in filter passband gain, which is highly undesirable for it degrades the noise performance and dynamic range, having placed at the forefront of MRI receiver. Since, transconductor cells are present in large quantity, filter frequency response depends heavily on its performance and it is very sensitive to the change in its unit cell.

To address the issue of transconductor having no common-mode rejection which degrades its performance due to coupling of control signal, fully-differential topology has been adopted in literature. Further to add stability, cascoding technique can be an option which increases the effective impedance, thus reduce the impact of variations. However, while designing for high dynamic range at low voltage supply, which is a necessity in the application of MRI and has to be atleast 90 dB, transistor stacking should be avoided. This is because cascoding topology can make it difficult for the devices to avail a sufficient overdrive voltage to stay in saturation region, thus lowering the possible signal swing.

On the other hand, one can look into improving the biasing technique to add stability to the  $g_m$  of transconductor. Previous transconductor uses constant-voltage biasing, but it is highly susceptible to variation due to coupling and also it is difficult to maintain exact biasing point with fixed-voltage bias due to the voltage drop along the bias path, which is why it is not a recommended technique. Among traditional biasing methods - constant-current biasing has been used very often because of the ease of generating a fixed current bias and distributing it by creating multiple copies of the current-mirror. This is convenient from layout perspective as well, being resilient to parasitic coupling. With constant-current bias, it was observed that the variation in transconductance across process corner is 9% while across temperature is upto 30% at typical process corner. We know, for a constant-current biasing, the output current is expressed by the square-law

$$I_{ds} = \mu Cox \frac{W}{L} (V_{gs} - V_{th})^2$$

(2.11)

This shows that the current has direct dependency on temperature dependent parameters that is mobility and square of threshold voltage, which is steered directly to the transconductance as well. Hence, such a huge variation is seen because the current copy is imbalanced due to the mobility degradation with temperature and also temperature dependency of threshold voltage. Thus, constant-current biasing is not suitable for our requirements. We know that  $g_m$  is defined as change in output current per unit change in input voltage, so if we need a constant  $g_m$  with temperature, there needs to be a biasing scheme which cancels out the effect of temperature variation on  $g_m$  with that on current.

### **B.** Potential Solution - Constant- $g_m$ Bias

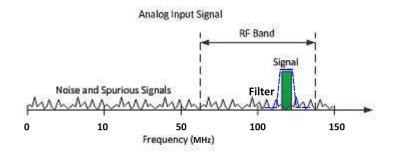

The methodology of constant- $g_m$  biasing has been adopted in literature to avail stable transconductance circuit with PVT variations.

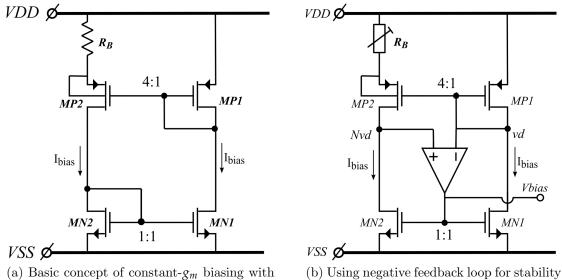

Constant- $g_m$  biasing is based on the principle of PTAT current generator used in BJT. It uses two current-mirror pairs, one each of nMOS and pMOS connected back to back as shown in Fig. 2.10a. The transistors are sized such that one of the pair is at equal size while the other is skewed in the ratio of 4:1. This ensures a constant current in both the branches and the difference in the overdrive voltages of the skewed pair appears across the resistor, where resistor shall be ideally independent of the temperature variation. This way the transconductance  $(g_m)$  becomes proportional to the inverse of resistance and independent of process and temperature variations. It can be said that constant- $g_m$  biasing ensures the transconductance tracks the precise resistance.

Here, a current has been generated which adjusts itself with temperature variations such that the transconductance remains constant. This is further illustrated with the help of the

Temperature

(b) Using negative feedback loop for stability against supply variations

Figure 2.10: Concept of constant- $g_m$  biasing

Eq. (2.12)-(2.17). where,  $V_{thP}$  is threshold voltage of pMOS,  $V_{gs}$  is the gate-source voltage,  $I_{ds}$  is the drain-source current,  $V_{gt}$  is the overdrive voltage  $(V_{gs} - V_{th})$  and K is the process variable  $(0.5\mu C_{ox})$ .

$$V_{gsMN1} = V_{gsMN2}$$

hence,  $I_{dsMN1} = I_{dsMN2} = I_{bias}$

$$I_{dsMP1} = I_{dsMP2} = I_{bias}$$

where,  $I_{dsMP1} = K \frac{W}{L} (V_{gsMP1} - V_{thP})^2$

$$I_{dsMP2} = K \frac{4W}{L} (V_{gsMP2} - V_{thP})^2$$

(2.12)

(2.13)

from

$$(2.13)$$

,

$$(V_{gsMP1} - V_{thP}) = 2(V_{gsMP2} - V_{thP})$$

(2.14)

because of same current in each branch,  $I_{bias}$ ,

$$V_{gsMP1} - V_{gsMP2} = I_{bias} R_B \tag{2.15}$$

from (2.14) and (2.15),

$$\frac{2I_{bias}}{V_{gsMP1} - V_{thP}} = \frac{1}{R_B}$$

(2.16)

we know  $g_m = \frac{\partial I_{ds}}{\partial V_{gs}}, g_m = \frac{2Ids}{V_{gs} - V_{th}}$   $g_{mMP1} = \frac{1}{R_B}$ (2.17)

Using the pMOS pair over nMOS, to skew in the ratio of 4:1 prevents the body effect due to the feasibility of connecting the bulk with the source of pMOS in the CMOS technology. Under body effect, the threshold voltage of MOS varies with change in source-bulk voltage,  $V_{SB}$ . Whereas with the adopted technique, while generating difference in gate-source voltage  $V_{gs}$  of pMOS pair available across resistor, voltage  $V_{SB}$  is maintained at zero for both MP1 and MP2 and so matching of all four transistors is retained. The circuit in Fig. 2.10a produces current  $I_{bias}$  such that the transconductance tracks the resistance  $R_B$  with temperature variation.