EXCIMER LASER ANNEALING FOR

ULTRASHALLOW JUNCTIONS AND

CONTACTS

VIKTOR GONDA

# **EXCIMER LASER ANNEALING FOR ULTRASHALLOW JUNCTIONS AND CONTACTS**

## **PROEFSCHRIFT**

TER VERKRIJGING VAN DE GRAAD VAN DOCTOR

AAN DE TECHNISCHE UNIVERSITEIT DELFT,

OP GEZAG VAN DE RECTOR MAGNIFICUS PROF. DR. IR. J. T. FOKKEMA,

VOORZITTER VAN HET COLLEGE VAN PROMOTIES,

IN HET OPENBAAR TE VERDEDIGEN OP

MAANDAG 1 DECEMBER 2008 OM 10:00 UUR

DOOR

**VIKTOR GONDA**

GÉPÉSZMÉRNÖK, TECHNISCHE UNIVERSITEIT BUDAPEST, HONGARIJE

GEBOREN TE BUDAPEST, HONGARIJE

Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. L. K. Nanver

Samenstelling promotiecommissie:

|                                |            |                               |

|--------------------------------|------------|-------------------------------|

| Rector Magnificus              | voorzitter | Technische Universiteit Delft |

| Prof. dr. L. K. Nanver         | promotor   | Technische Universiteit Delft |

| Prof. dr. ir. J. W. Slotboom   |            | Technische Universiteit Delft |

| Prof. dr. ir. R. A. M. Wolters |            | Universiteit Twente           |

| Prof. dr. ir. R. Dekker        |            | Technische Universiteit Delft |

| Dr. V. Privitera               |            | CNR-IMM, Italy                |

| Dr. R. Ishihara                |            | Technische Universiteit Delft |

| Dr. T. Suligoj                 |            | University of Zagreb, Croatia |

Gonda, V.

Excimer laser annealing for ultrashallow junctions and contacts

Ph.D. thesis Delft University of Technology, with summary in Dutch.

Keywords: excimer laser annealing, laser doping, residual implantation defects, ultrashallow junctions, silicon diodes, low-ohmic contacts

ISBN 978-90-8559-475-8

Copyright © 2008 by Viktor Gonda

All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the prior written permission of the copyright owner.

# Contents

|          |                                                                        |           |

|----------|------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                                    | <b>1</b>  |

| 1.1      | Overview of annealing methods . . . . .                                | 3         |

| 1.1.1    | Evolution of annealing for implanted dopants . . . . .                 | 4         |

| 1.1.2    | Laser doping . . . . .                                                 | 5         |

| 1.2      | Ultrashallow junctions by laser-anneal-only . . . . .                  | 6         |

| 1.3      | Laser annealing in silicon-on-glass technology . . . . .               | 6         |

| 1.4      | Outline of the thesis . . . . .                                        | 11        |

| <b>2</b> | <b>Laser annealing methods and evaluation techniques</b>               | <b>13</b> |

| 2.1      | Excimer laser annealing . . . . .                                      | 13        |

| 2.1.1    | Excimer laser systems . . . . .                                        | 13        |

| 2.1.2    | Laser annealing mechanism . . . . .                                    | 16        |

| 2.2      | Process and device modelling . . . . .                                 | 20        |

| 2.2.1    | Thermal simulations . . . . .                                          | 20        |

| 2.2.2    | Process and device simulation . . . . .                                | 23        |

| 2.3      | Test structures and characterization methods . . . . .                 | 23        |

| 2.3.1    | Material analysis . . . . .                                            | 23        |

| 2.3.2    | Electrical device characterization . . . . .                           | 25        |

| <b>3</b> | <b>Process optimization for laser annealing of implanted junctions</b> | <b>31</b> |

| 3.1      | Experimental considerations . . . . .                                  | 31        |

| 3.2      | Results . . . . .                                                      | 33        |

| 3.2.1    | Laser masking . . . . .                                                | 33        |

| 3.2.2    | Contact window etching . . . . .                                       | 38        |

| 3.2.3    | Low-energy implantation . . . . .                                      | 40        |

| 3.2.4    | Laser anneal . . . . .                                                 | 42        |

| 3.2.5    | Metallization . . . . .                                                | 44        |

---

## CONTENTS

|          |                                                                                          |           |

|----------|------------------------------------------------------------------------------------------|-----------|

| 3.3      | Optimal process results . . . . .                                                        | 44        |

| 3.4      | Conclusions . . . . .                                                                    | 50        |

| <b>4</b> | <b>Deactivation and junction leakage in the vicinity of laser annealed implantations</b> | <b>51</b> |

| 4.1      | Introduction . . . . .                                                                   | 51        |

| 4.2      | Experimental procedures . . . . .                                                        | 52        |

| 4.3      | Results . . . . .                                                                        | 53        |

| 4.3.1    | Ideality of the junctions . . . . .                                                      | 53        |

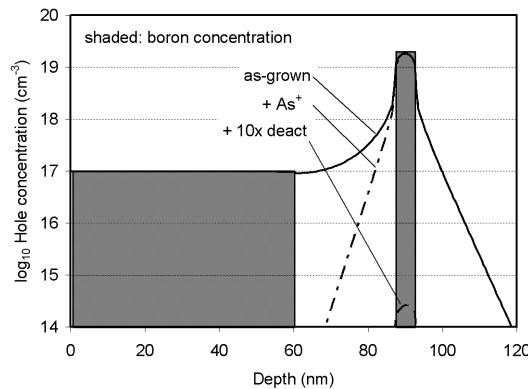

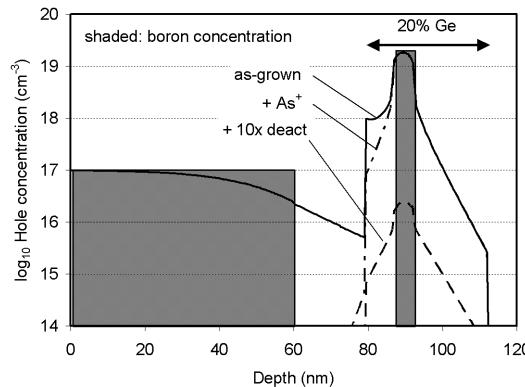

| 4.3.2    | Base properties . . . . .                                                                | 56        |

| 4.4      | Discussion . . . . .                                                                     | 61        |

| 4.4.1    | Diffusion and activation effects . . . . .                                               | 61        |

| 4.4.2    | Effect of the ELA implant on an ideal BJT . . . . .                                      | 65        |

| 4.4.3    | Methods of suppressing defects . . . . .                                                 | 67        |

| 4.5      | Conclusions . . . . .                                                                    | 68        |

| <b>5</b> | <b>Laser annealing and Si/Ge/C strained layers</b>                                       | <b>69</b> |

| 5.1      | Experimental procedures . . . . .                                                        | 69        |

| 5.2      | Results . . . . .                                                                        | 71        |

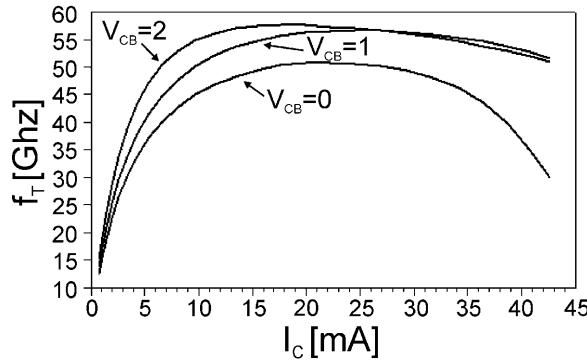

| 5.2.1    | Transistor operation . . . . .                                                           | 71        |

| 5.2.2    | Simulated hole profiles . . . . .                                                        | 72        |

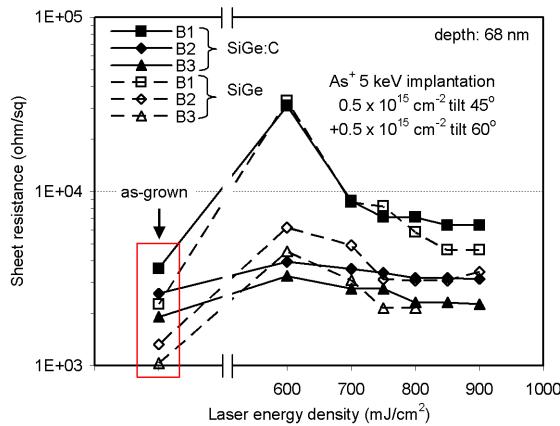

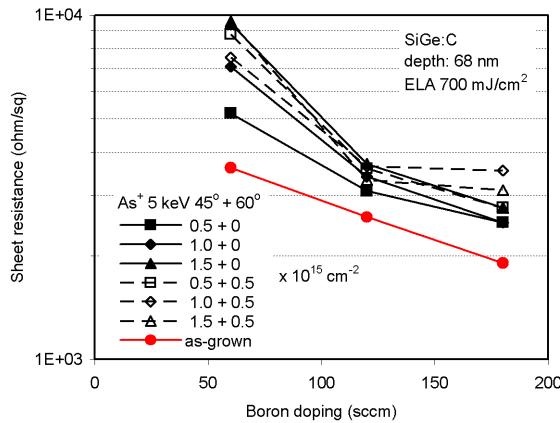

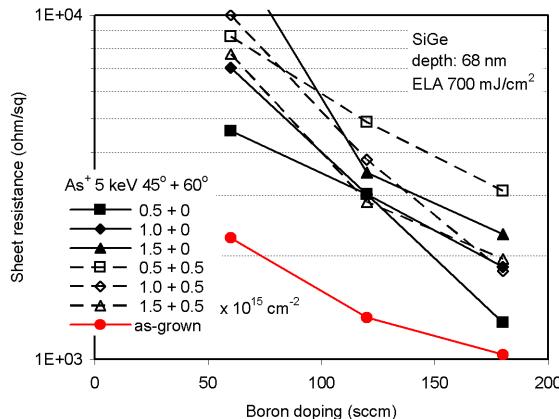

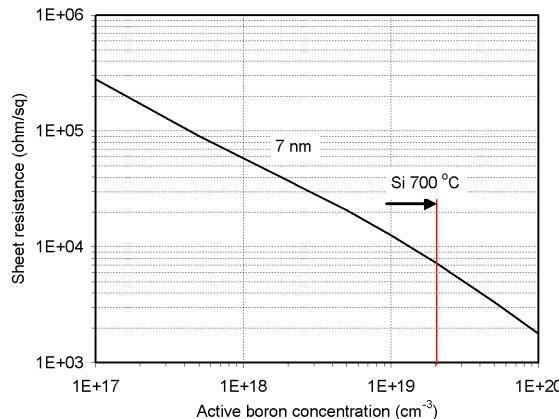

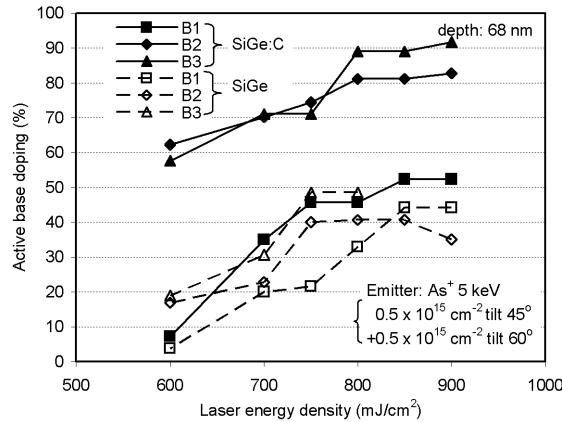

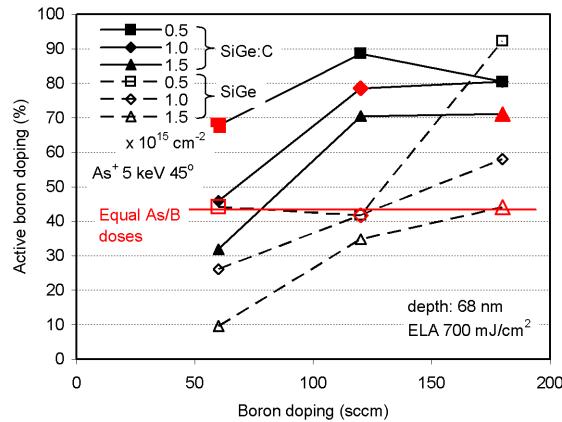

| 5.2.3    | Sheet resistance in the intrinsic base . . . . .                                         | 74        |

| 5.3      | Discussion . . . . .                                                                     | 80        |

| 5.3.1    | Active doping in the base . . . . .                                                      | 80        |

| 5.4      | Conclusions . . . . .                                                                    | 82        |

| <b>6</b> | <b>Laser doping from CVD deposited As source</b>                                         | <b>85</b> |

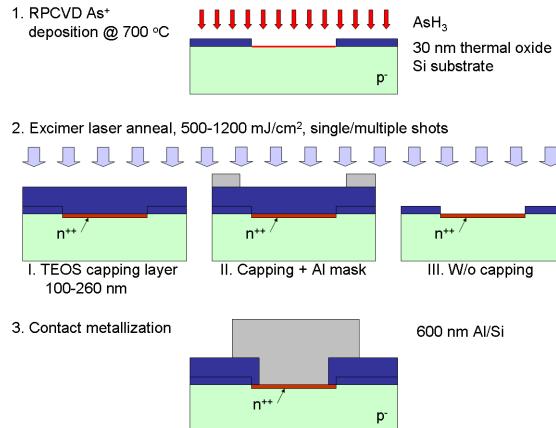

| 6.1      | Experimental procedures . . . . .                                                        | 85        |

| 6.2      | Results . . . . .                                                                        | 87        |

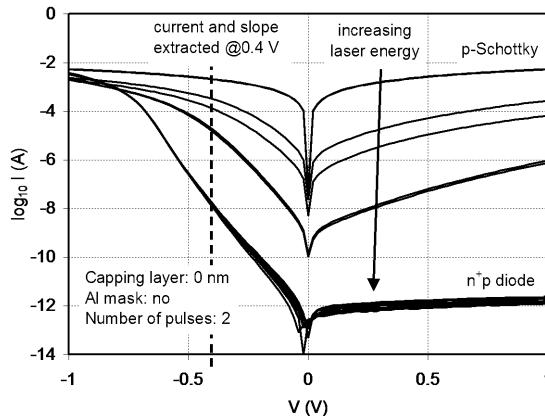

| 6.2.1    | Diodes . . . . .                                                                         | 87        |

| 6.2.2    | Contacts . . . . .                                                                       | 91        |

| 6.2.3    | Laser induced surface patterns . . . . .                                                 | 93        |

| 6.3      | Conclusions . . . . .                                                                    | 95        |

| <b>7</b> | <b>Double laser annealing</b>                                                            | <b>97</b> |

| 7.1      | Introduction . . . . .                                                                   | 97        |

| 7.2      | Experimental procedures . . . . .                                                        | 98        |

| 7.3      | Results . . . . .                                                                        | 98        |

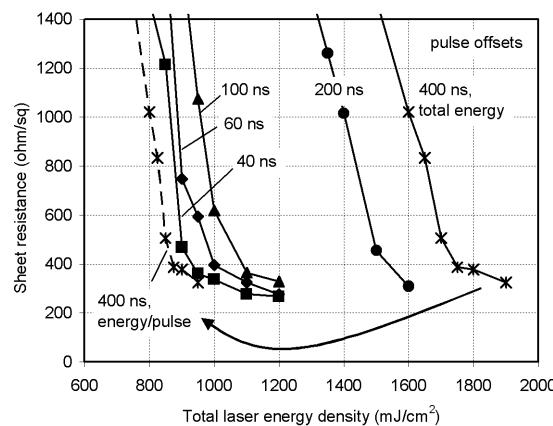

| 7.3.1    | Equal energy ratio . . . . .                                                             | 98        |

## CONTENTS

---

|                                                               |            |

|---------------------------------------------------------------|------------|

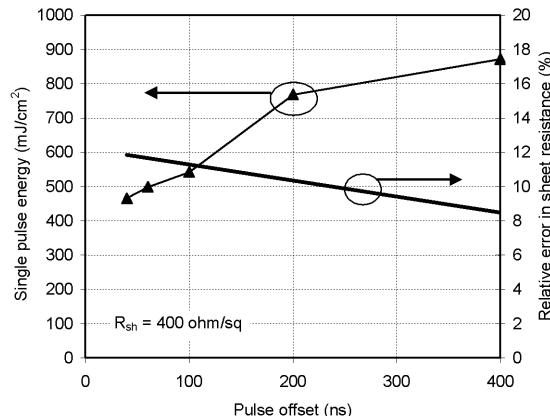

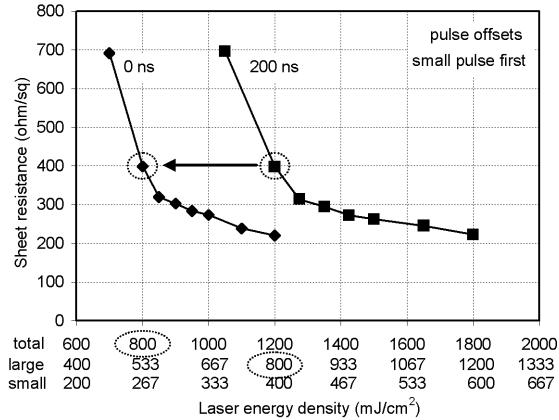

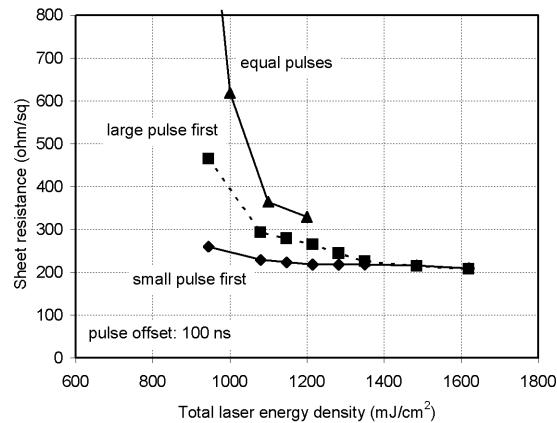

| 7.3.2 Non-equal pulse ratios: pre- and post-heating . . . . . | 102        |

| 7.4 Conclusions . . . . .                                     | 105        |

| <b>8 Conclusions and recommendations</b>                      | <b>107</b> |

| <b>References</b>                                             | <b>111</b> |

| <b>Summary</b>                                                | <b>121</b> |

| <b>Samenvatting</b>                                           | <b>125</b> |

| <b>List of Publications</b>                                   | <b>129</b> |

| <b>Acknowledgements</b>                                       | <b>133</b> |

| <b>About the author</b>                                       | <b>135</b> |

# Chapter 1

## Introduction

Miniaturization has driven electronic devices from micro to nano scale in order to increase speed and functionality of the circuits. In planar technologies, lateral downscaling is required to be able to place more electronic components on the silicon surface. This leads, on one hand, to a reduction of the size of contacts to the silicon and, if no special measures are taken, the contact resistances will increase accordingly. One option for decreasing the contact resistivity is to increase the doping of the contact surface. On the other hand, due to the increased proximity of doped regions, such as for the source and drain of a metal-oxide-semiconductor field-effect transistor (MOSFET) where short channel effects become detrimental, there is also a drive towards vertical downscaling. For this, aggressively scaled highly-doped, ultrashallow junctions are needed. According to the international technology roadmap for semiconductors (ITRS) [itr, 2007], beyond 2009, ultrashallow source-drain extensions should scale below 10 nm, with lateral abruptness below 2 nm/decade. Full-melt laser annealing in combination with low energy implants, which is the topic of this thesis, is one of the few techniques that can fulfil these requirements.

The straightforward route that the industry took to downscale junctions was to decrease the implantation energies and the thermal budget for the annealing. This route was eventually complicated by fast diffusion effects related to non-equilibrium diffusion phenomena, and this has led to the development of high-temperature short-time annealing in combination with innovative defect engineering techniques.

Laser annealing for the doping of silicon was first studied in the 1970's [Lojek, 1999]. However, due to issues such as junction leakage, reproducibility and IC-processing compatibility, that were related to the high implantation energies and laser equipment limitations of that time, this technique was all but forgotten by the mid 1980's. A

revival of the research was launched in 1999 when the technique appeared on the ITRS roadmap and was recognized as being naturally capable of fabricating the ultrashallow junctions necessary for future CMOS generations. Nevertheless, integration proved to be difficult and unlike most other processing techniques, the optical properties of the wafer became a vital parameter. There were two other techniques that at that time had just reached some degree of maturity and also needed to take the optical properties of the wafers into consideration: rapid thermal annealing (RTA) methods such as flash lamp annealing [Lerch et al., 2007] and UV lasering for (re-)crystallisation had found its ways into the fabrication of thin-film displays [Kagan and Andry, 2003]. This latter application demonstrated another useful property of laser annealing: it is a surface annealing technique, i.e., only the surface layer is affected by the heat, due to the low thermal budget, the small absorption depth and the short timescales, the temperature quickly drops towards the bulk of the wafer. This makes the technique attractive for applications where thermal limitations apply such as for the thin-film panels where silicon is deposited and recrystallized on glass that must be processed at temperatures below about 500 °C.

The recent work in the literature on the laser-annealing of implanted junctions has to a great extent been devoted to engineering the junction depth and sheet resistance values that make the method attractive for source/drain fabrication in future CMOS generations [Surdeanu et al., 2002, Whelan et al., 2003]. Yet other studies have focused on the actual integration in CMOS [Yu et al., 1999, Wong et al., 2005], which still remains very challenging. In any case, the integration of the laser annealing is complicated by the optical nature of the method, which results in a strong pattern sensitivity, by the localized nature of the anneal, which gives high thermal gradients, and by the low thermal budget available for annealing the implanted dopants. The latter means that not all defects are annealed and non-annealed defects must either be eliminated by additional processing or be tolerated in the specific device structure being fabricated, which may entail customized device optimization.

Rather than having a flat panel or CMOS focus, the work in this thesis has been performed in the context of the non-MOS high-frequency silicon device integration research being performed at DIMES. In general, in high-frequency devices the demand for thin, abrupt and accurately tailored doping profiles has also put focus on low-temperature processing techniques. Moreover, the demand for low parasitic resistance and capacitance in both devices and circuits has lead to the development of aggressive isolation schemes. At DIMES the search for solutions answering to these demands has crystallized in the development of an in-house silicon-on-glass technology in which special bipolar junction transistors, heterojunction SiGe bipolar transistors and high-linearity varactor circuits have been successfully realized. In all these implementations, the use of laser annealing to integrate ultrashallow junctions or low-

Table 1.1: Typical annealing times, temperatures, and heating rates for different types of thermal annealing techniques.

| Anneal type           | Furnace         | Soak           | Spike          | Flash           | Laser                |

|-----------------------|-----------------|----------------|----------------|-----------------|----------------------|

| Timescale             | $\times 10$ min | $\times 1$ min | $\times 1$ sec | $\times 1$ msec | $\times 1$ $\mu$ sec |

| Temperature (°C)      | 900             | 1000           | 1100           | 1200            | >1300                |

| Heating rate (°C/sec) | <0.1            | 1              | 10             | 100             | $10^6$               |

ohmic contacts has played a crucial role. In particular, the thermal restrictions after silicon substrate transfer by gluing to glass are severe: no thermal treatments above 300 °C can be tolerated. In the SiGe devices for the preservation of the doping profiles, it is attractive to keep temperatures below 700 °C after SiGe epitaxy and below 500 °C after implanting dopants.

In this thesis, the integration of high-power excimer laser annealing to activate low-energy implanted regions is investigated with the goal of fabricating ideal junctions and low-ohmic contacts in high-frequency silicon-on-glass devices. The results of the investigation include several generally applicable rules for optimizing the fabrication and integration sequence to accommodate the laser anneal step. In particular, the integration of a suitable reflective laser masking layer to protect regions that should not be annealed is challenging since the desire for minimum device dimensions dictates the use of self-aligned techniques. Moreover, obtaining an ideal annealing of the perimeter of a junction that is self-aligned to the contact window becomes the most critical issue.

## 1.1 Overview of annealing methods

For the different types of thermal annealing techniques, the processing times can range from hours to microseconds as is shown in Table 1.1. A high-temperature thermal step will induce diffusion and activation of the dopants as well as movement and repair of defects. With respect to shallow junctions, where the requirements are shallowness and abruptness, high activation, and low leakage, the preference is to have low diffusion, high levels of activation and a high amount of defect repair.

### 1.1.1 Evolution of annealing for implanted dopants

#### Early laser annealing

In the late 1960's laser–semiconductor interaction was first studied in Russian groups. They demonstrated a laser-annealed diode and the re-crystallization of a deposited amorphous silicon layer [Kutolin and Kompanec, 1969]. In the mid 1970's the use of laser annealing of implanted damage was researched [Pilipovic, 1975]. In the early 1980's the high research interest resulted in extensive understanding and modelling of the fundamental mechanisms governing the laser annealing process: the melt and solidification processes including the associated impurity diffusion and segregation [Poate and Mayer, 1982, Thompson et al., 1984]. Excimer lasers were applied for the first time for device fabrication, and laser doping in the gas phase was also investigated [Lojek, 1999]. Despite a quite significant and valuable research effort, device integration proved to be too complicated: in the laser–Si interaction the optical properties of Si become important and the process is very different from the commonly applied furnace annealing. Therefore, focus was shifted to extending the well-known thermal annealing techniques that used tens-of-minute anneal times into the time-frame of what was then called rapid thermal annealing (RTA) and aimed at minute long anneals.

#### Rapid thermal annealing and TED

If only thermal equilibrium diffusion effects are assumed, deep diffusion of dopants can be avoided for shallow-junction formation either by using high temperatures with short anneal times or by using low temperatures with longer anneal times to nevertheless eliminate the influence of defects. However, in the latter, much deeper diffusion than expected was observed especially in the case of implanted boron [Eaglesham et al., 1994]. This was found to be due to the long defect dissolution times at low temperatures and a non-equilibrium diffusion induced by dopant interaction with mobile defects. This effect, which is called transient enhanced diffusion (TED) [Stolk et al., 1997] has driven research towards RTA with short times at high temperatures. In the development of the annealing equipment the major effort was also put into tools for realizing shorter annealing times.

#### Millisecond anneal and co-implants

At present the state of the art in manufacturing is millisecond annealing [Timans et al., 2006]. In order to slow down the demands for decreasing the thermal budget, defect engineering methods have also been developed. These include methods where in addition to the dopant an additional non-active species such as F or C is co-implanted

to retard diffusion, and methods using vacancy engineering to retard enhanced diffusion [Claverie et al., 2008]. As the thermal budget decreases and anneal times are shortened, flash lamps are often used as the heating elements. This has meant that the optical properties of the substrates to be annealed have also started to play a role in this case and pattern sensitivity is also an issue. To decrease the junction depth beyond what has been possible with thermal methods and shallow implants, alternative methods for doping are being researched.

### 1.1.2 Laser doping

In ultrashallow junction technology, techniques to substitute low-energy ion-implantation with something less damaging have received an increasing amount of interest. All in all, low-energy implantations together with low thermal budget anneals suffer from reduced activation efficiency, channelling, transient enhanced diffusion and tradeoffs between residual damage and thermal budget.

Since a thermal step is unavoidable in the doping process, a laser thermal processing step is attractive due to the fact that the very high temperatures can be achieved with an extremely low thermal budget while only affecting the surface of the wafers. In laser doping, dopants can be introduced by a spin-on technique [Lo et al., 1996b], or, with a much better dose control, by gas-immersion laser doping [Carey et al., 1985].

Dose control is also excellent in the atomic-layer-doping technique, where an adsorbed dopant monolayer can be deposited by using CVD. These layers can then be capped by oxides so that dose loss during a subsequent thermal drive-in thermal step can be avoided. [Song et al., 1999] demonstrated arsenic and phosphorous drive-in, while [Kim et al., 2000a] demonstrated it for boron. Such junctions have been integrated in MOS transistors on SOI [Koh et al., 2002], and in devices with SiGe source/drain regions [Jung et al., 2002]. [Popadic et al., 2007] analyzed diffusion from a monolayer for arsenic and phosphorous as a function of the annealing temperature.

Nevertheless, these alternative doping techniques do not have the versatility with respect to integration that implantation has. This is the main reason that most of the work in this thesis is focused on the laser annealing of implantations. While the device structures fabricated in the silicon-on-glass technology have allowed the use of full-melt annealing, considerable research has been reported by others on non-melt and partial-melt techniques that aim to enhance the compatibility of the laser anneal step with CMOS process flows.

## 1.2 Ultrashallow junctions by laser-anneal-only

In most of the work reported in the literature on the formation of ultrashallow junctions with laser annealing, thermal processing steps after the laser anneal have been included in the total process flow [Chong et al., 2002]. This has mainly been because the laser anneal alone did not remove enough implantation damage at the junction to be able to achieve low-leakage diode characteristics. It has been attempted to remove this damage by thermal processing at temperatures as low as 600 °C. Moreover, the post-laser process flow often demands that the laser-annealed doping profile should tolerate some degree of thermal processing. The results of the laser-annealing are in the most of these cases far from optimal in part due to TED effects.

In contrast to this work, at DICES the research focus has been on the laser-anneal-only approach. At the time when this thesis work started, it had just been demonstrated that near-ideal diodes with excellent ideality factors of  $n \approx 1.1$  could be fabricated by activating implanted dopants purely by excimer laser annealing [Nanver et al., 2003, Gonda et al., 2005a]. To completely avoid post-laser thermal processing steps, a straightforward process flow was implemented where dopants were implanted directly in a contact window that was etched through a reflective layer stack of aluminium on a thermal oxide surface isolation. The laser annealing is then performed just before the contact metallization. This basic scheme proved very attractive for the silicon-on-glass applications that were under development at DICES and these are described in the next section.

The laser-anneal-only approach is not easily made compatible with conventional CMOS. However, it may be very attractive for advanced CMOS that aims at high-k-dielectric metal-gate stacks. A first demonstration of this was given by [Baek et al., 2004] who integrated laser-annealed source/drain regions in metal-gate transistors. In this case the gate metal functions as the reflective mask. A similar device is now under development at DICES in the framework of the FP6 project *High-frequency disposable SiGe dot FET*. The device has an  $\text{SiO}_2\text{-Al}_2\text{O}_3\text{-Al}$  gate stack that masks the laser annealing of arsenic implanted source/drain regions.

## 1.3 Laser annealing in silicon-on-glass technology

Since 1999 high-frequency silicon-on-glass IC-processes have been under development at DICES. In the original SOG substrate-transfer technology that was pioneered by Philips [Dekker et al., 1997] the processing after transfer to glass was limited to non-critical large-area patterning and contacting of the back-wafer (backside of the wafer). The DICES version of SOG processing is specifically referred to as back-

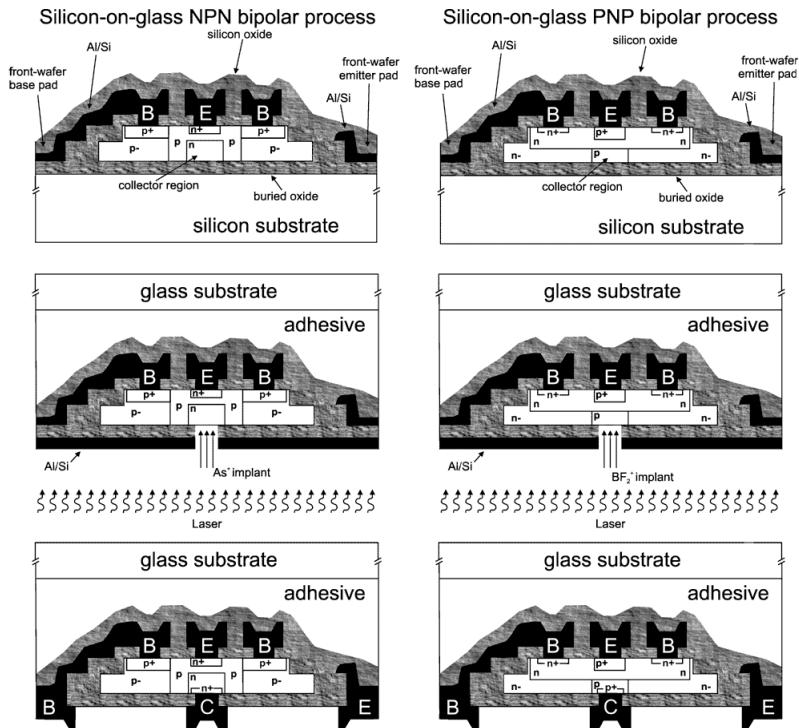

Figure 1.1: Schematic process flow of the DIMES silicon-on-glass implanted and laser annealed back-wafer-contacted complementary bipolar technology [Lorito et al., 2006].

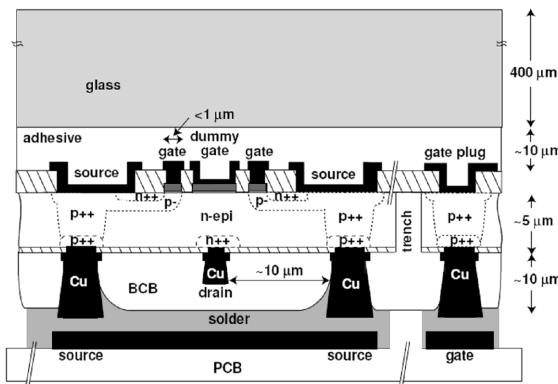

Figure 1.2: Schematic cross section of the surface mounted silicon-on-glass VDMOS-FET with  $p^{++}$  and  $n^{++}$  implanted and laser annealed regions [Nenadovic et al., 2004].

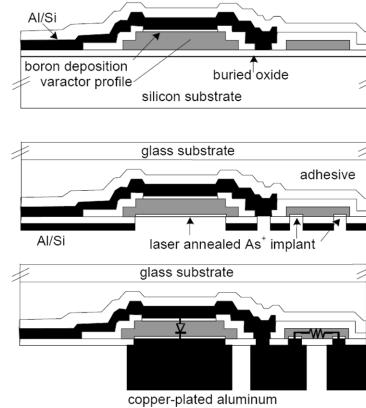

Figure 1.3: Schematic process flow for the integration of SOG varactor diodes and high-ohmic resistors with a laser annealed  $As^{+}$  implant [Buisman et al., 2005].

wafer-contacted SOG technology [Nanver et al., 2008c] because it distinguishes itself from earlier versions by the implementation of minimum dimension waferstepper patterning on both the front-wafer (front side of the wafer) and back-wafer and the use of laser annealing to produce junctions and low-ohmic contacts on the back-wafer. The transfer to glass is performed by gluing with an acrylic adhesive that does not tolerate temperatures above 300 °C. Therefore laser annealing is one of the techniques that can be used to activate implanted dopants on the back-wafer. A successful implementation of this technique was already demonstrated in 1999 for collector-contacting of SOG NPNs [Nanver et al., 1999] and later a complementary bipolar process with similar vertical PNPs was also demonstrated [Lorito et al., 2006]. A schematic of the basic process flow is shown in Fig. 1.1. In the course of the work it became clear that under certain circumstances the implants in the back-wafer could have a detrimental effect on the parts of the device regions already processed during the front-wafer processing. An investigation of these effects and their dependence on the implant and laser-anneal conditions has been performed in the context of this thesis [Gonda et al., 2006b, Gonda et al., 2006a] and are treated in Chapters 4 and 5. For the bipolar SOG devices a new type of collector contacting was developed that avoids the use of implantations in the back-wafer: the ohmic collector contact was replaced by a Schottky contact [Lorito et al., 2006] and this has proven to have advantages for the performance of the transistors for many analog applications.

In another SOG device, the vertically diffused MOS (VDMOS), low-ohmic contacts on the back-wafer to the p-type source and n-type drain are made with laser annealed implants. This solution could be implemented without any compromises because the other device regions containing junctions are more than 3  $\mu\text{m}$  away [Nenadovic et al., 2004]. This can be seen in Fig. 1.2.

However, in yet another application, the high-linearity SOG varactor [Buisman et al., 2005], back-wafer contacting with very low series resistance is vital for the device performance. This is easily achieved with implantation and laser annealing as shown in Fig. 1.3. However, in this application the residual implantation damage is positioned so that it can reduce the varactor diode breakdown voltage, which is a crucial parameter for the overall performance. Therefore it becomes important to find ways of minimizing the amount of the defects created around the contact.

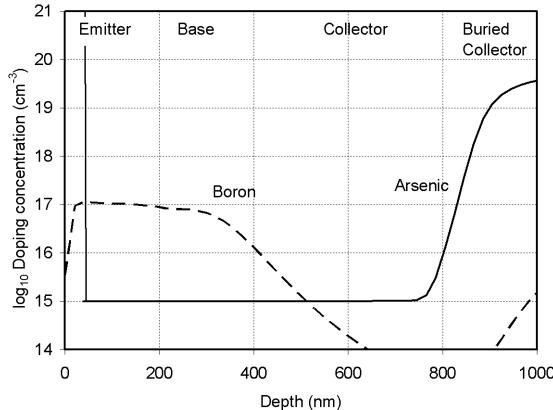

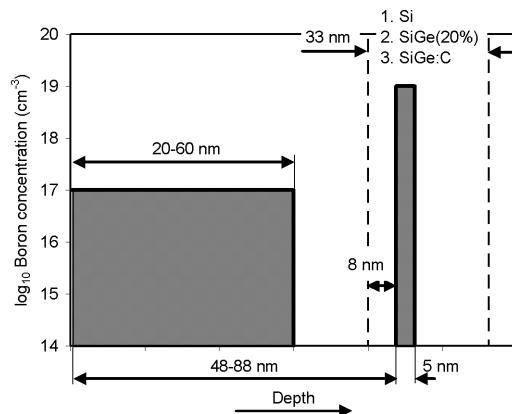

The ultimate goal of the bipolar SOG work has been to integrate a SiGe HBT with no TED effects after formation of the epitaxially-grown boron-doped strained-SiGe base. To achieve this, the emitter and base contact should be fabricated without combining implantations with thermal anneals. Although this would appear to be quite doable by replacing the thermal anneal by laser annealing in a process as in [Nanver et al., 2003], a straightforward implementation, even for micron size contacts, is complicated by the fact that the limited thermal budget after SiGe epitaxy also does

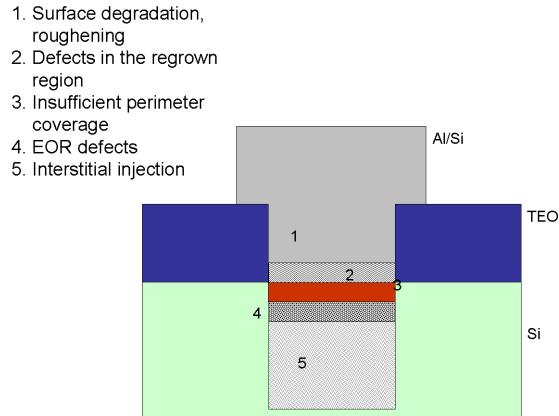

Figure 1.4: Main issues related to laser annealing of implanted junctions.

not allow the growth of thick thermal oxides like those used in that publication. On the contrary, the isolation layer is effectively composed of less ideal materials deposited by chemical-vapor-deposition (CVD) methods. With respect to these materials the thermal oxide has the advantage of a very uniform composition that guarantees a uniform etching and in addition the etch rate in HF that is used to remove native oxide is low. The latter has consequences for the dip etching of the contact window before metallization. Excessive etching of the contact perimeter during this step can lead to diode perimeter leakage because the laser annealed diodes are very critically aligned to the original contact window.

Despite the isolation issues, experimental bulk devices with laser-anneal-only emitter and base contact fabrication that give a first proof-of-concept were realized [Lorito et al., 2008]. These devices have an aggressively downscaled emitter-base doping profile with an emitter depth of about 10 nm but the current gain and high-frequency performance are shown to be good. In Chapter 5 these devices are analyzed with respect to the influence of residual damage in the base region as a result of implantation and laser annealing.

## 1.4 Outline of the thesis

To summarize, as shown in Fig. 1.4, the main issues related to laser annealing of implanted junctions are residual implantation induced damage, non-ideality of diodes related to bulk and perimeter imperfections, pattern dependence and non-uniformities. All of these issues are treated in this thesis, with the main focus placed on establishing process flows that enable high-frequency device fabrication in the back-wafer-contacted SOG technology.

The following chapter introduces the tools with which the work in the thesis has been performed. In first instance the high-power excimer laser annealing systems are described followed by the methods used to model the basic thermal behavior during laser annealing. A short overview of the applied material analysis techniques is given, while the electrical characterizations techniques, which have been the most important means of evaluating the quality of the laser anneal junctions and contacts, are treated in detail. These include the measurement of test structures for determining contact resistance and the I–V and C–V characteristics of diodes, bipolar junction transistors and junction field-effect transistors.

In Chapter 3, the basic process flow is described for integrating the laser annealing of an implanted region with the goal of obtaining a near-ideal ultrashallow junction. The results of a series of systematic experiments where the influence of individual process steps is evaluated make it possible to optimize the process flow in different device integration situations.

Both the implantation and the subsequent laser anneal can have an effect on the doping in regions in the vicinity of the implant. Chapter 4 concentrates on the effects of residual defects injected into the substrate and not annealed by the laser, which can result in increased junction leakage and deactivation of dopants. It is shown that the severity of these effects can be reduced by modifying the implantation parameters. In the region just below the implant, the heat pulse sent into the substrate from the laser melt region can be instrumental in reactivating dopants that were deactivated by the implantation. This is experimentally demonstrated in Chapter 5 where the laser annealed junction functions as emitter in SiGe HBT transistors. In these devices the SiGe base is as close as 50 nm to the emitter.

In Chapter 6 some initial experiments are described for replacing arsenic implants with CVD deposited monolayer of arsenic. The high deposition temperature complicates the fabrication of the laser reflective masking layer but nevertheless encouraging results were achieved.

In the last year of this thesis work, double laser annealing with short pulse offsets became available [Gonda et al., 2007a, Gonda et al., 2007b]. This new technique offers a novel method of extending the effective laser heating time and it is shown in Chapter

7 to be a useful extra parameter for optimizing the thermal budget of the overall anneal. In Chapter 8 the conclusions of this thesis work are given along with recommendations for future work.

# Chapter 2

## Laser annealing methods and evaluation techniques

In this chapter the infrastructure for the laser annealing experiments is described. First the laser systems are introduced, followed by the description of the laser annealing mechanism and the thermal modelling for laser annealing. Finally, the test structures for material analysis and the electrical device structures are described together with the electrical characterization methods.

### 2.1 Excimer laser annealing

#### 2.1.1 Excimer laser systems

There were two laser systems used in this work: a single laser system by XMR was used at DICES until the end of 2005, and a custom built double excimer laser setup by Exitech that replaced the XMR in early 2006.

##### Single laser system

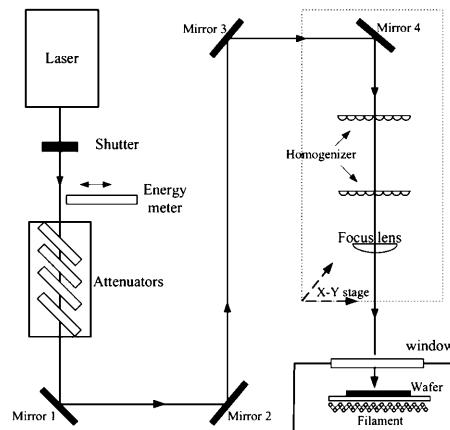

A schematic of the XMR laser setup is shown in Fig. 2.1. The XMR 5100 laser source uses Xe and Cl<sub>2</sub> active gases and emits at a wavelength of 308 nm, with a pulse duration of 60 ns full width at half maximum (FWHM). The output energy is measured by a removable energy meter. The fluence is set roughly by reducing the transmittance with beam splitters in the attenuator box, after which the fine tuning is achieved by

Figure 2.1: Schematic of the XMR7100 system.

adjusting the position of the upper cylindrical lens array of the homogenizer, therefore varying the actual spot size. Typical spot sizes are  $0.3\text{--}1 \times 1 \text{ cm}^2$ . The homogenizer also provides a uniform spatial profile of the pulse. Scanning is performed by moving the optical components shown enclosed with the dotted line in Fig. 2.1, while the wafer is fixed in a vacuum chamber. The sample can be preheated up to  $450^\circ\text{C}$  by a tungsten filament.

### Double laser system

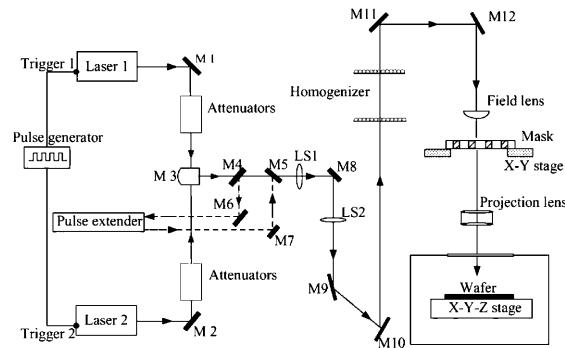

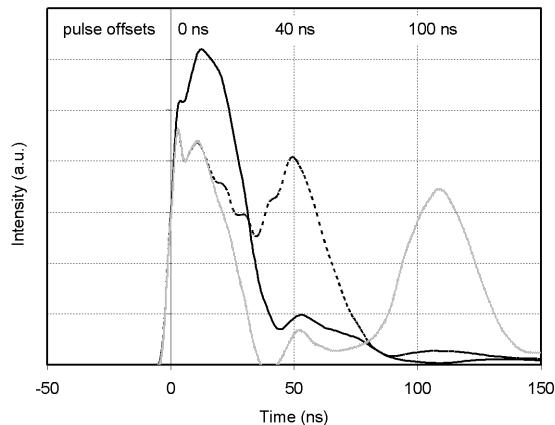

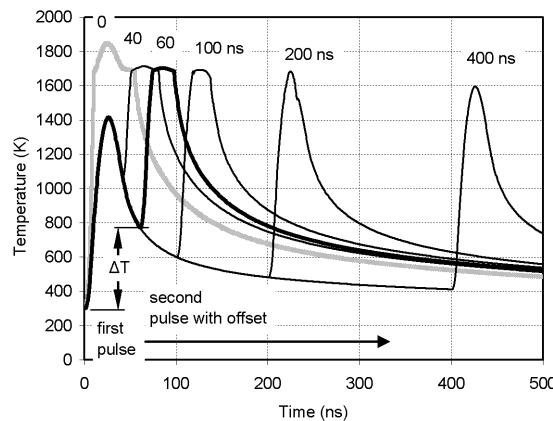

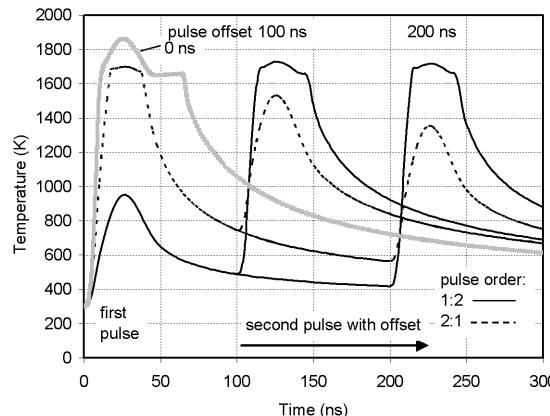

A schematic of the Exitech double laser crystallization setup is shown in Fig. 2.2. It consists of two Lambda Physik LPX 210 XeCl excimer laser sources with a wavelength of 308 nm, and a pulse duration of 25 ns FWHM, which are triggered by the pulse generator. Different pulse offsets can be realized by the pulse generator settings, and the jitter between the laser pulses at  $1\sigma$  is 4 ns. Examples of the temporal profiles are shown in Fig. 2.3. The energy densities are set with the attenuators after which the laser beams are combined. There is an optional path for the pulse extender, which was not used in this work. A homogenizer was used to produce a flat-top intensity profile with a 7% energy variation across a  $10 \text{ mm}^2$  area. Spot sizes of either  $3 \times 5 \text{ mm}^2$  or  $1.5 \times 2.5 \text{ mm}^2$  are determined by the magnification of the projection lens in use, which therefore determines the energy density range too. If both lasers are used simultaneously, then respectively 1200 and  $4800 \text{ mJ/cm}^2$  can be achieved. The wafer

Figure 2.2: Schematic of the Exitech M8000V double laser system. The M1–M12 are mirrors.

Figure 2.3: Pulse shapes as a result of combining two equal laser pulses with offsets of 0, 40 and 100 ns.

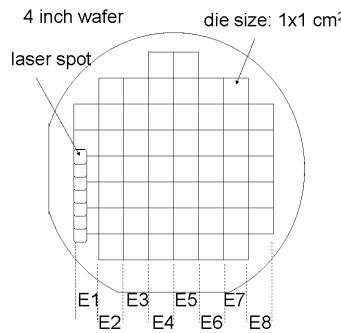

Figure 2.4: Laser annealing makes it possible to vary the annealing parameters over the wafer. A columnar layout for applying the annealing parameters E1–E8 is shown as an example.

is held in the vacuum chamber on a moving stage, which can be positioned with  $\mu\text{m}$  accuracy. The chuck can be heated up to 450 °C.

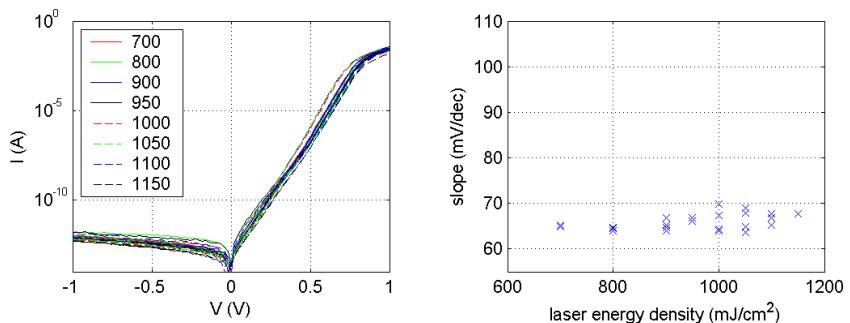

Laser annealing parameters (e.g. energy density, pulse offset or number of shots) can be varied over the wafer. Throughout this work variations were frequently made in a columnar fashion, an example of which is shown in Fig. 2.4. Due to the localized manner of the laser annealing, the resulting anneal is subjected to spot-to-spot non-uniformities [Vandervorst et al., 2008].

### 2.1.2 Laser annealing mechanism

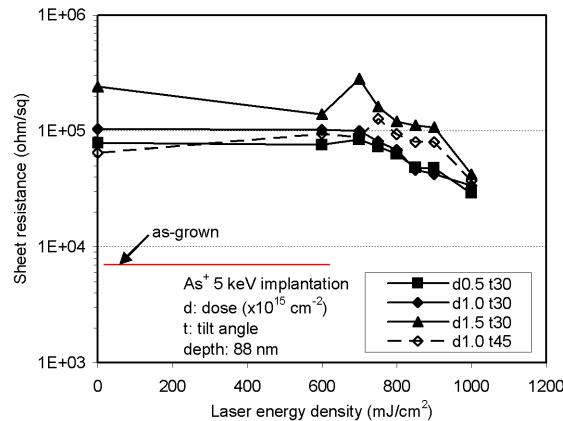

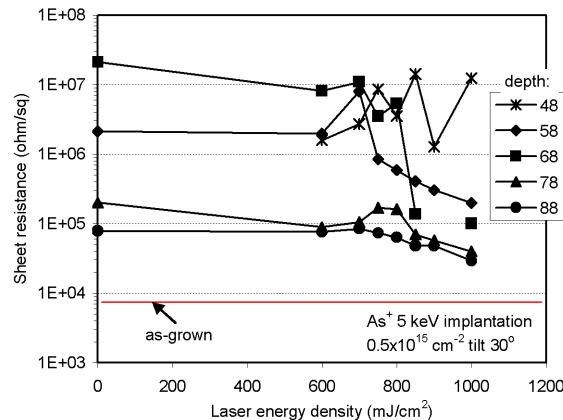

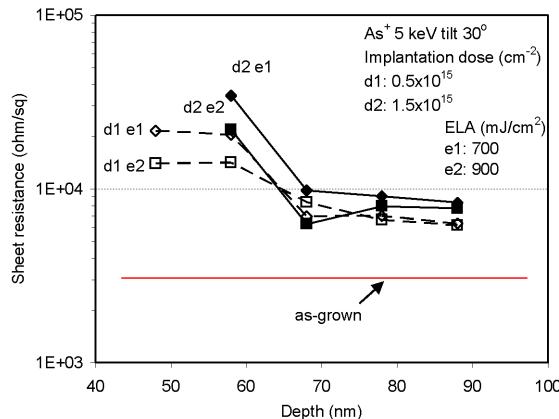

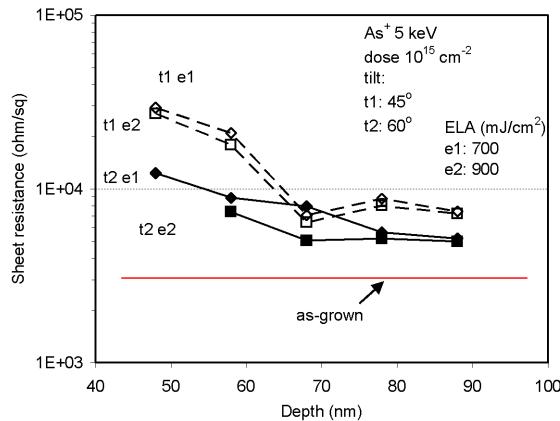

The laser annealing mechanism is described here by considering the variations of the sheet resistance of a laser annealed arsenic implant. P-type bulk or SOI wafers were used, with an SOI thicknesses of 110, 220, 450, 750 or 1500 nm and a buried oxide thickness of 1000 nm. After a 4 min 0.55% HF dip,  $\text{As}^+$  was implanted with 15 keV to a dose of  $5 \times 10^{14} \text{ cm}^{-2}$ . The laser annealing was carried out with the Exitech setup in vacuum, using laser energy densities from 200–1200 mJ/cm<sup>2</sup> with 66% pulse overlap at room temperature or chuck heating of 250, 300 or 350°C. Sheet resistances were measured by a CDE Resmap 4 point probe system.

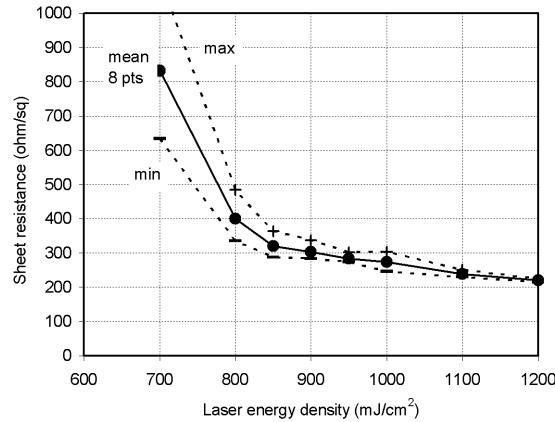

Figure 2.5: Sheet resistance of a laser annealed  $\text{As}^+$  15 keV,  $5 \times 10^{14} \text{ cm}^{-2}$  implant versus the laser energy density. From 6 to 8 measurement points taken across the wafer are averaged and shown with the solid line. Minimum and maximum values are shown with dotted lines.

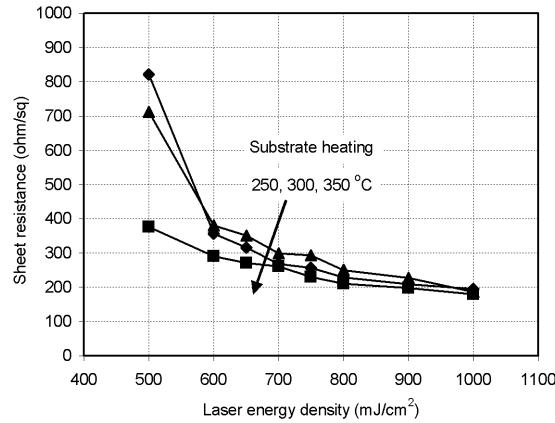

Figure 2.6: Sheet resistance of a laser annealed  $\text{As}^+$  15 keV,  $5 \times 10^{14} \text{ cm}^{-2}$  implant while the substrate is heated to 250, 300 or 350 °C.

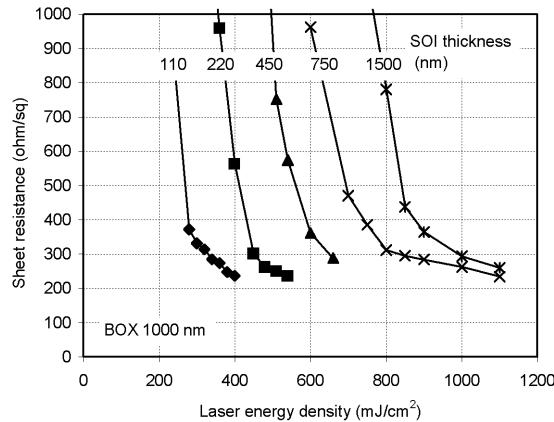

Figure 2.7: Sheet resistance of a laser annealed  $\text{As}^+$  15 keV,  $5 \times 10^{14} \text{ cm}^{-2}$  implant in SOI with silicon thicknesses of 110–1500 nm. The buried oxide was 1000 nm thick.

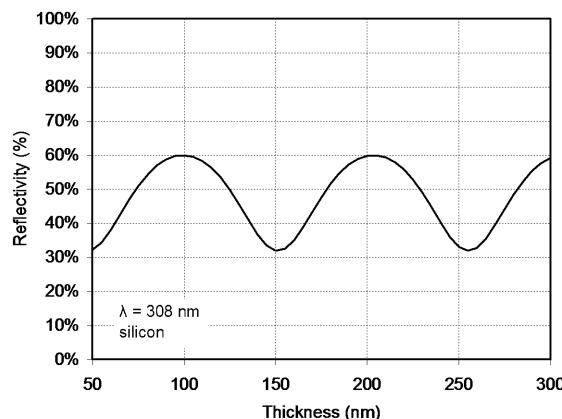

Figure 2.8: Calculated reflectivity of the oxide–silicon stack at a wavelength of 308 nm as a function of the oxide capping layer.

### Implanted dopant activation

The UV lasing wavelength of 308 nm is absorbed within 6 nm of the amorphous or crystalline silicon surface. While the total thermal budget is very low, it is concentrated in a very small volume at the surface for a very short time. Increasing laser energies result in increasing surface temperatures. The temporal thermal balance is determined by the thermal properties of the substrate, towards which the temperature rapidly decays. Above certain laser energies, surface temperatures exceed the melting temperature of Si. The melt depth extends deeper with the increasing laser energies. In c-Si, ablation will limit the achievable melt depth. In a thin a-Si surface layer above c-Si, such as in implanted Si, melting occurs earlier than in c-Si, because of the lower thermal conductivity and melting temperature of a-Si. As melting temperature is 200–300 °C lower than that of c-Si, the molten part is severely supercooled and explosive crystallization occurs before the full melt [Thompson et al., 1984]. If the melt depth reaches the crystalline interface, it can only propagate further if the melt temperature of c-Si is reached. If this interface is reached, then the c-Si layer will act as a seed layer for resolidification, and therefore an epitaxial layer will solidify. If this interface is not reached, then polycrystalline Si will regrow, and the crystalline quality can be correlated to the laser energy density.

Any dopants residing in the melt, diffuse orders of magnitude faster than in the solid, and will distribute uniformly. During the quick solidification, they are trapped at substitutional sites in the lattice. Due to trapping, concentrations can extend the solid solubility limits.

The sheet resistance,  $R_{sh}$  of the layer is strongly dependent on the melt depth, which determines the junction depth,  $x_j$

$$R_{sh} = \frac{1}{q\mu(x_j)N(x_j)x_j} \quad (2.1)$$

where  $q$  is the electron charge,  $\mu$  is the charge carrier mobility, and  $N$  is the active doping density. The mobility slightly changes with the doping at high concentrations, further it is also dependent on the number of inactive dopants [Rousseau et al., 1996] and on the crystalline quality of the regrown layer. A typical plot of the measured sheet resistance versus the laser energy is shown in Fig. 2.5. The scatter decreases as the sheet resistance decreases, presumably due to the improvement in the crystalline quality and defect anneal.

### Thermal balance

The thermal balance is strongly dependent on the substrate conditions and boundary conditions. Substrate heating increases the total thermal budget and for the same  $R_{sh}$  the laser energy range shifts to lower energies as shown in Fig. 2.6. At elevated wafer temperatures, the resulting temperature profile has low thermal gradients and therefore solidification velocities are smaller. As an extra advantage, this effect can be beneficial for defect annealing [Venturini, 2005]. A strong thermal confinement occurs in the case where SOI wafers are used since oxide has a heat conduction coefficient two orders of magnitude lower than Si. The shift to the lower laser energies is dependent on the thickness of the top silicon layer (Fig. 2.7). A trench will also have some effect due to the lateral confinement. An oxide capping layer, as used in Chapter 6, creates a complex situation because the laser light reflectivity of the oxide changes periodically with its thickness as shown in Fig. 2.8. Moreover, as it will draw some heat, it can act as a heat storage or a heat sink, dependent on the thickness [He et al., 2006].

## 2.2 Process and device modelling

### 2.2.1 Thermal simulations

To estimate temperature profiles heat conduction is considered and the transient heat transfer equation in 1-D is formulated as

$$\rho c_p(T) \frac{\partial T}{\partial t} + Q_f = \frac{\partial}{\partial x} \left( k(T) \frac{\partial T}{\partial x} \right) + Q(x, t) \quad (2.2)$$

where  $\rho$  is the mass density,  $c_p$  the specific heat capacity,  $Q_f$  the heat of fusion,  $k$  the heat conductivity,  $T$  the absolute temperature, and  $t$  the time.

The heat,  $Q$ , generated in the silicon by the laser irradiation is given by

$$Q(x, t) = \alpha(1 - R)I(t) \exp(-\alpha x) \quad (2.3)$$

where  $\alpha$  is the absorption coefficient,  $R$  is the reflectivity of the surface, and  $I$  the intensity of the laser pulse. The boundary conditions that are applied in the numerical simulations are given by assuming that the surface is insulated so that

$$\frac{\partial T}{\partial x} \bigg|_{x=0} = 0 \quad (2.4)$$

and in the substrate beyond the zone affected by the laser heating the temperature,  $T_{x_{max}}$ , is set at a constant temperature

$$T_{x_{max}} = T_0 \quad (2.5)$$

The phase transition during melting or solidification causes a moving boundary at the solid–liquid interface, and its velocity depends on the heat rate difference at the interface, which is formulated in a Stefan problem. Different implicit solutions exist such as the enthalpy based method, the moving grid, the level set, and the phase field method. An excellent comparison of the numerical models for the Stefan problems can be found in [Javierre et al., 2006]. In this work, the enthalpy based method and the phase field method were used.

### Enthalpy based method

Melting is most conveniently formalized by using the enthalpy [Taler and Duda, 2006]. The enthalpy,  $h$ , has a jump discontinuity at the liquid-solid interface determined by the latent heat,  $L_H$  given by

$$h(T) = \int c_p(T)dt + L_H \cdot H(T - T_m) \quad (2.6)$$

where  $H$  is the Heaviside step function,  $T_m$  is the melt temperature. By differentiating this relationship it follows that

$$c'(T) = \frac{dh}{dT} = c_p(T) + L_H \cdot \delta(T - T_m). \quad (2.7)$$

The latter form can be very easily implemented in the simulators. As in Eq. 2.2,  $Q_f$  is embedded in a modified specific heat capacity function.

### Phase field method

A physically more valid formalization of the moving interface problem is possible with the phase field method as the driving forces acting on the interface are related to the phase field parameters. The sharp liquid-solid interface is replaced with a smooth, diffused interface. A phase function,  $\Phi$ , that is changing continuously between 0 (liquid) and 1 (solid) can be introduced. The implementation of the phase field method for laser annealing is used hereafter [La Magna et al., 2004]. In Eq. 2.2,  $Q_f$  is written as

$$Q_f = 6\Phi(1 - \Phi)\rho L_H \frac{\partial\Phi}{\partial t}. \quad (2.8)$$

The kinetic equation is written as

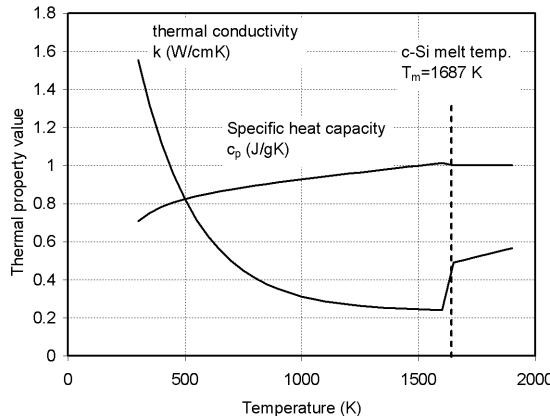

Figure 2.9: Temperature dependent thermal conductivity and specific heat capacity for c-Si and l-Si used in the numerical simulations [Fogarassy et al., 1989, Unamuno and Fogarassy, 1989].

$$\frac{\partial \Phi}{\partial t} = M \frac{\delta F}{\delta \Phi} \quad (2.9)$$

where  $M$  is related to the interface mobility, and  $F$  is the thermodynamic driving force. The Helmholtz free energy of the system is

$$F = \int_V \left( f(\Phi, T) + \frac{\epsilon}{2} |\nabla \Phi|^2 \right) dV \quad (2.10)$$

where  $V$  is the system volume,  $f(\Phi, T)$  is the Caginalp-type potential function,  $\epsilon$  is the interface width. Parameters of this model and a more detailed description can be found in [La Magna et al., 2004].

Equations 2.2 and 2.9 form a system of two coupled partial differential equations describing the system and should be solved simultaneously.

### Simulation parameters

In all the simulations performed in this thesis, a 1-D portion of silicon to a depth of 10  $\mu\text{m}$  was simulated with a dense mesh being used close to the surface. The laser pulse shape was approximated as a smooth trapezoidal-like shape with a 10 ns rise time, 10

ns hold time and 30 ns fall time, where the pulse full width at half maximum was 25 ns. Double pulses can be applied with defined offsets.

The absorption coefficient was  $\alpha = 10^6 \text{ cm}^{-1}$ , the reflectivity was  $R_c = 0.65$  and  $R_l = 0.7$  in the solid and in the liquid state, respectively. The melting temperature was  $T_m = 1687 \text{ K}$ , the latent heat was  $L_H = 1780 \text{ J/g}$ . The material density was  $\rho = 2.33 \text{ g/cm}^3$ . Temperature dependent thermal properties, as shown in Fig. 2.9, were obtained from literature [Fogarassy et al., 1989, Unamuno and Fogarassy, 1989]. For the solid phase the relationship becomes

$$k(T) = 0.235 + 4.45 \exp(-T/247) \quad (2.11)$$

$$c_p(T) = 0.81 + 1.3 \cdot 10^{-4}T - 1.26 \cdot 10^4 T^{-2} \quad (2.12)$$

while in the liquid state

$$k(T) = 0.502 + 2.99 \times 10^{-4}(T - T_m) \quad (2.13)$$

and  $c_p = 1 \text{ J/gK}$ .

### 2.2.2 Process and device simulation

Modelling of implantations and furnace anneals was performed with *TSUPREME4*. Low energy implants were modelled by *TRIM/SRIM*. Simple carrier concentrations were calculated with *MEDICI*.

## 2.3 Test structures and characterization methods

### 2.3.1 Material analysis

Laser annealed layers were analyzed by measuring the sheet resistance with a four point probe. Chemical and electrical dopant profiling were made with SIMS and SRP, respectively. TEM was used for the analysis of the crystallinity, and AFM was used to analyze the surface morphology.

#### Four-point resistance measurements

The CDE Resmap sheet resistance meter was used to measure the sheet resistance of laser annealed implants with energies down to 5 keV. The arsenic implants were performed in p-type wafers with a resistivity of 2-5 ohm-cm.

A critical issue with respect to shallow junction measurement is the probe penetration and its influence on the measured results. An excellent treatment of this subject can be found in [Clarissee et al., 2006]. Measurement heads with 100 and 500  $\mu\text{m}$  probe radii were used. The latter provides lower contact forces so it was used to measure shallow layers.

Normally the CDE meter is used to measure uniformly implanted and annealed wafers. If the surface is patterned the value measured within one uniform region will depend on the distance to the neighbouring regions and the doping profile depth of the individual junctions. These parameters will determine the current spreading into the neighbouring regions. Since the laser annealed regions are very shallow, it was possible to pattern the surface in regions of  $1 \times 1 \text{ cm}^2$  by trench isolation and still measure sheet resistance values to an accuracy within 1%.

Probes were placed at least  $2 \times$  the probe spacing distance from the perimeter of these areas so that edge effects were negligible. Accuracy can be an issue where partially annealed areas are measured since these can contain grains that give a non-uniform current distribution. In the formulas homogenous sheets are assumed.

## SIMS

Chemical doping profiles have been determined with secondary ion mass spectroscopy (SIMS). It requires a relatively large square area of about  $300 \times 300 \mu\text{m}^2$ , and the detection limit is about  $10^{16} \text{ cm}^{-3}$ , depending on the element. The resolution is about 0.5-1 nm/decade, which limits the accuracy of the measurement in conjunction with very abrupt and ultrashallow profiles.

## SRP

Electrically active dopant profiles can be determined by spreading resistance profiling (SRP). In this method, the surface is bevelled under a low angle, and the probes measure the spreading resistance along the bevelled path. This is then translated to a depth profile. The spreading resistance is calibrated with doped etalons so that the carrier concentration can be measured. A Poisson-solver can be used to accurately determine the active doping concentrations [Dickey, 1992]. Steep profiles are difficult to measure due to carrier spilling and space-charge effects [Clarissee et al., 1996].

## TEM

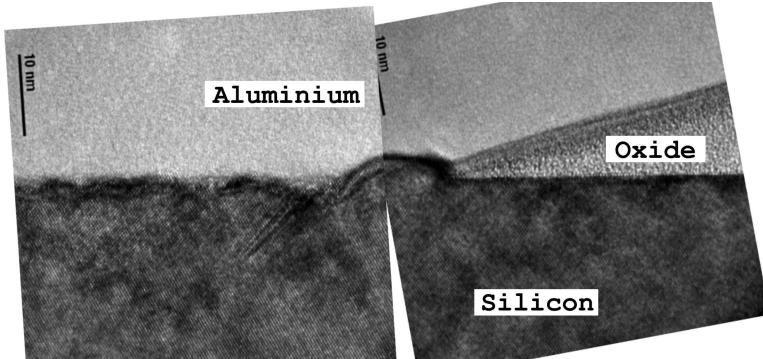

Imaging with transmission electron microscopy (TEM) is used to inspect cross sections and it is capable of atomic resolution. The TEM images shown in the following section

in Fig. 3.2 and Fig. 3.12 were prepared from of a fully processed and electrically characterized transistor test structure with a laser annealed emitter. The emitter size was  $40 \times 40 \mu\text{m}^2$ , and the cutting plane was approximately across the midplane of the active region at an edge of a contact window. The sample dimensions were  $5 \times 3 \mu\text{m}^2$  for the cross sectional area, and the thickness was about 100 nm. Magnifications up to 100.000 $\times$  were used.

## AFM

The surface roughness for etched, implanted or laser annealed surfaces was measured by atomic force microscopy (AFM). The scanned base area was  $5 \times 5 \mu\text{m}^2$  for all the measurements. The pre-processing of the data consists of compensating for waviness or any background envelope or skewness. Then the surface roughness was determined over the whole field, and extreme peaks were excluded in this case.

The root mean square is a common statistical parameter describing the scatter, and it is formulated for the surface roughness measurements by

$$R_q = \sqrt{\frac{1}{A} \int_A (x - \bar{x})^2 dA}. \quad (2.14)$$

where  $A$  is the surface area,  $x$  is the height parameter, the overscore denotes the mean value.

### 2.3.2 Electrical device characterization

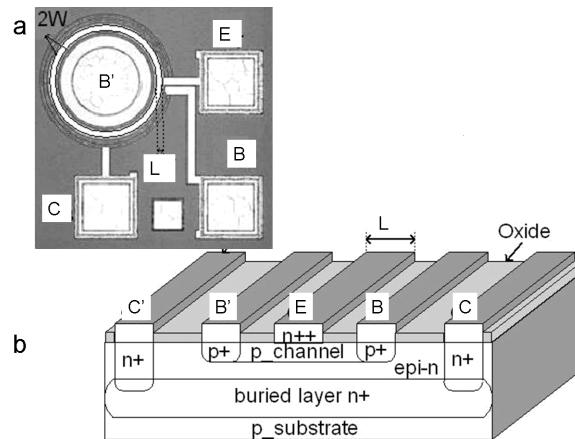

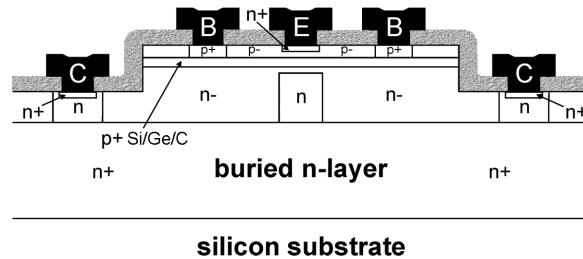

A set of rectangular and ring-shaped circular bipolar transistor structures are available with different emitter sizes [Liu et al., 2006]. The basic cross-section is shown for an NPN transistor in Fig. 2.10. The buried  $n^+$ -layer forms the collector contact on which an undoped epitaxy layer is grown. A 30 nm thermal oxide is grown through which the  $p^+$  contacts, the  $n^+$ -plug to the buried layer and the lightly-doped p-type base are implanted and annealed.

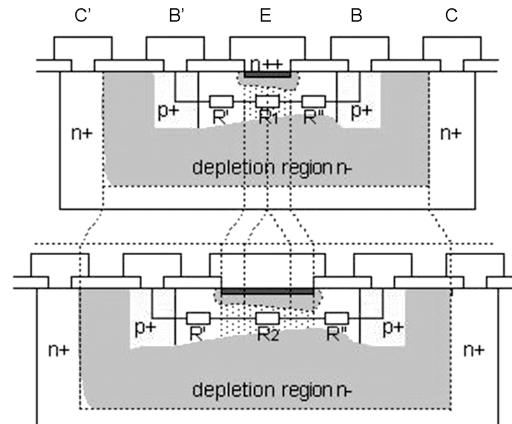

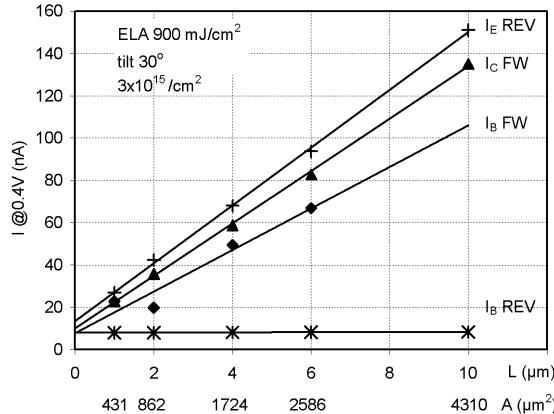

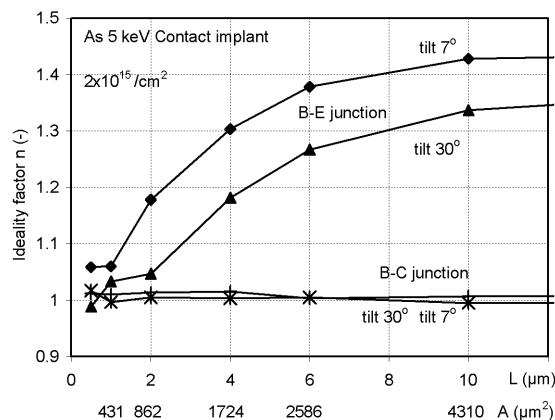

The circular bipolar transistors with double base contacts were designed with different emitter lengths, which allows to extract transistor parameters in the intrinsic transistor region by subtracting the peripheral regions as shown in Fig. 2.11. The central radius of the emitter is constant (emitter width,  $W = 431 \mu\text{m}$ ) for all the devices, while the emitter length,  $L$ , varies from 1, 2, 4, 6, and 10  $\mu\text{m}$ . Therefore emitter area,  $A$ , varies ( $A = 431, 862, 1724, 2586$  or  $4310 \mu\text{m}^2$ ) while the perimeter lengths are practically the same ( $P = 2W = 862 \mu\text{m}$ ).

Figure 2.10: (a) Photo of a ring-shaped NPN test structure. (b) Cross section through the ring from inner to outer edge. [Liu et al., 2006]

Figure 2.11: Cross section showing that the B-B' contact regions are the same for both small and large  $L$ . The emitter and collector depletion regions for  $V_{B-B'} < 0$  and  $V_B = V_E = V_C$  are indicated. [Liu et al., 2006]

Sheet and contact resistance structures are also available on patterned wafers. Sheet resistances can be determined by using van der Pauw crosses through a four point measurement. The measurement limit is about 40 kohm/sq. Contact resistance can be measured by specially designed Kelvin structures with contact sizes from  $10 \times 10$  down to  $2 \times 2 \mu\text{m}^2$  [Nanver et al., 1996].

The electrical characteristics were measured using an Agilent 4156C parameter analyzer, a HP 4278A capacitance meter, and a Cascade Microtech probe station equipped with DCM200 probes that have negligible probing series resistance.

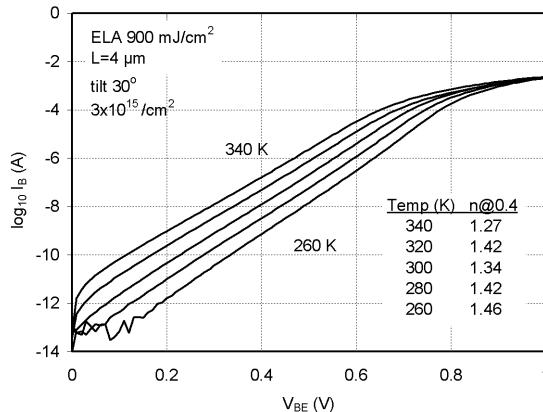

The following electrical measurements were carried out on the ring shaped structures: junction characterization, Gummel plots, determination of pinch-off and base sheet resistance, capacitance-voltage characteristics, and mobility in the base.

### Diode characteristics

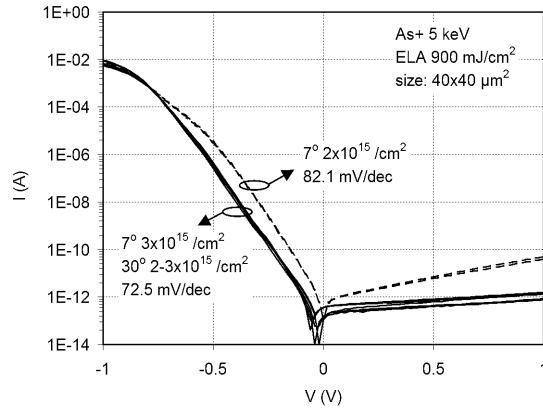

The emitter masks designed for transistors have also been used to fabricate diodes to the substrate, which then is contacted either on the front or by metallizing the back of the wafer. The junctions have been characterized by diode I-V measurements, an example of which is shown in Fig. 6.2, where the emitter contact has been biased from  $-1$  to  $1\text{V}$  and the substrate is the grounded. The forward diode current in the small to medium current range follows the relationship

$$I = I_0 \exp \left( \frac{V}{n(V)V_T} \right) \quad (2.15)$$

where  $I$  is the measured current,  $I_0$  is the saturation current,  $V$  is the applied bias,  $n(V)$  is the ideality factor,  $V_T = kT/q$  is the thermal voltage, in which  $k$  is Boltzmann's constant,  $T$  the absolute temperature.

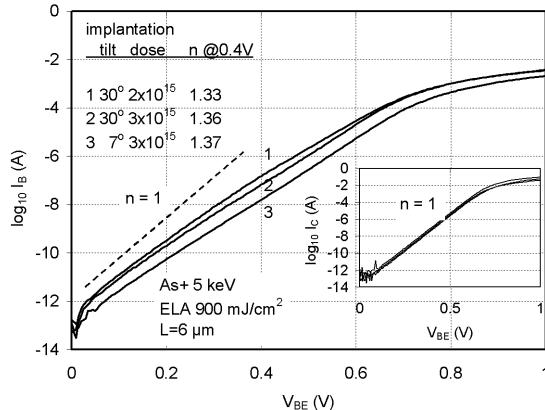

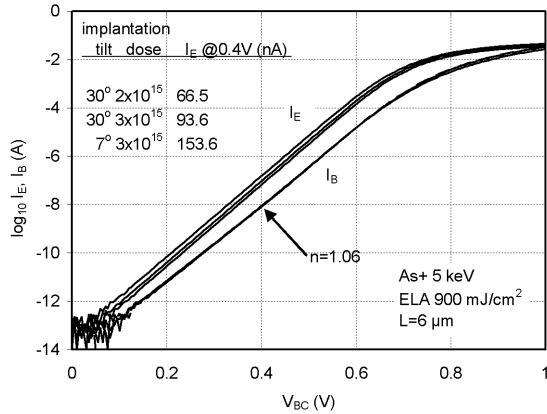

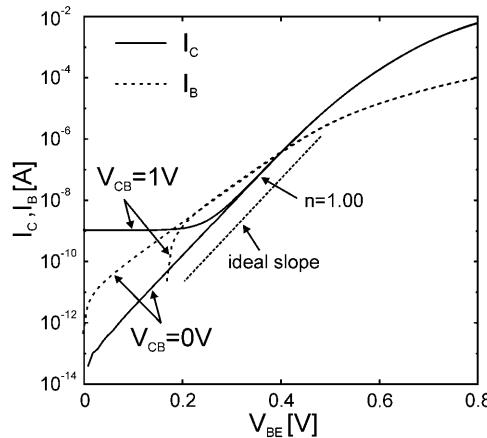

### Gummel plots

Both the B-E and the B-C diode quality can be evaluated in the forward and reverse Gummel plots. In the forward Gummel plots, the base current is determined by the emitter Gummel number,  $G_E$ , the base-emitter junction area,  $A_{BE}$ . The collector current is determined by the base Gummel number,  $G_B$ . The magnitude of the currents in the small to medium current range can be written in the form of eq. 2.15 where the parameters for  $I_0$  and  $V$  can be chosen for the particular setup and measured current  $I$  from Table 2.1. These formulas are only valid for the laterally uniform case, i.e. when perimeter components are excluded. The intrinsic carrier concentration is  $n_i$ . The Gummel number is the total majority carrier charge in the concerning transistor region.  $D_n$  and  $D_p$  are the electron and hole diffusion coefficients, respectively.

Table 2.1: Parameters for Eq. 2.15 for the determination of the transistor currents of forward or reverse Gummel plots in low to medium current range.

| Gummel plot | $I$   | $I_0$                           | $V$      |

|-------------|-------|---------------------------------|----------|

| forward     | $I_B$ | $qn_i^2 A_{BE} \frac{D_p}{G_E}$ | $V_{BE}$ |

|             | $I_C$ | $qn_i^2 A_{BE} \frac{D_n}{G_B}$ |          |

| reverse     | $I_B$ | $qn_i^2 A_{BC} \frac{D_p}{G_C}$ | $V_{BC}$ |

|             | $I_E$ | $qn_i^2 A_{BC} \frac{D_n}{G_B}$ |          |

By measuring the reverse Gummel plot, The base current is determined by the collector Gummel number,  $G_C$ , for the base-collector junction area,  $A_{BC}$ . The emitter current is determined by the base Gummel number,  $G_B$ .

For any of the measured currents,  $I$ , the current per unit area,  $J$ , in the laterally uniform region under the emitter can be isolated by plotting  $I$  as a function of  $L$ . The perimeter component  $I_P$ , which includes all currents that do not scale linearly with  $L$  may be extracted by identifying the emitter lengths that are large enough to give a linear relationship. From the extracted forward Gummel plots the  $J$  characteristic corresponding to the base current can be isolated as well as the ideality of this current. If the gain of the transistor is much higher than 1, the base current will be lower than the corresponding total diode current and is therefore a much more sensitive monitor of any non-ideal leakage currents. From the measurements, the ideality factor  $n$  of the diode region localized under the emitter can also be extracted by Eq. 2.15. In general a large emitter length is advantageous for accurate determination of parameters that scale linearly with  $L$ , while the access to several small gate lengths gives a better means of evaluating of perimeter components.

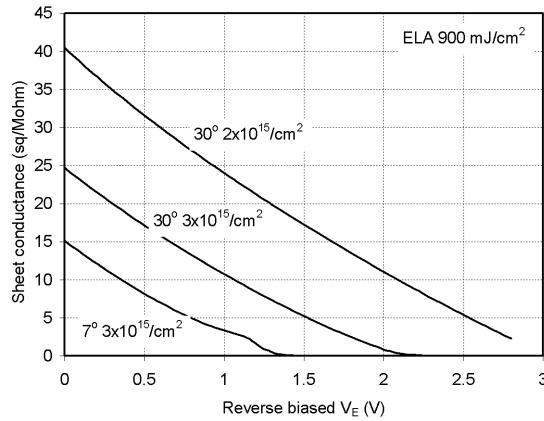

### Pinch-off

In a junction FET (JFET) like operation, the two base contacts act as source and drain and the base becomes the channel. In such a setup the pinch-off can be measured by measuring the channel current while narrowing the channel by reverse biasing the top or bottom gate. The pinch-off is corresponding to the closing of the channel.

### Sheet resistance

The sheet resistance in the intrinsic base can be extracted by measuring the base resistance by I–V measurements across the  $B - B'$  contacts of the ring structures for  $V_{B-B'} = 0$  while keeping the emitter and the collector reverse biased. The sheet resistance,  $R_{sh}$  can be extracted by plotting the measured resistance as a function of the emitter length,  $L$ , and identifying the linear region

$$R_B = \frac{dV_{B-B'}}{dI_B} \Big|_{V_{B-B'}=0} = R_p + R_{sh} \frac{L}{W} \quad (2.16)$$

where  $R_B$  is the base resistance between the two base contacts,  $V_{B-B'}$  is the voltage applied between the two base contacts,  $I_B$  is the measured base current,  $R_p$  is the perimeter component,  $L$  and  $W$  are the emitter length and width, respectively. The sheet resistance or the sheet conductance,  $G_{sh}$  at a certain emitter or collector reverse bias, is dependent on the base active dopant concentration,  $N_A$ , the base width,  $w_B$ , and the hole mobility in the base,  $\mu_p$

$$R_{sh}(V_C, V_E) = \frac{1}{G_{sh}(V_C, V_E)} = \frac{1}{q \int_{w_B(V_C, V_E)} \mu_p(x) N_A(x) dx} \quad (2.17)$$

### Capacitance-voltage characteristics

The laterally uniform capacitance in the intrinsic region can be isolated by means of differential measurements similar manner as in eq. 2.16. This way the parasitic effects are also excluded. As the laser annealed emitter-base junction is abrupt and high-doped, capacitances measured here can be used for extracting the active doping profile in the base

$$N_A(x = x_j + w(V_E)) = \frac{-2}{q \varepsilon_s \left( \frac{d(1/C^2(V_E))}{dV_E} \right)} \quad (2.18)$$

where  $\varepsilon_s$  is the permittivity of silicon,  $C$  is the specific capacitance,  $V_E$  is the applied reverse bias,  $x_j$  is the emitter's junction depth, and the depletion depth,  $w$ , is

$$w(V_E) = \frac{\varepsilon_s}{C(V_E)} \quad (2.19)$$

**Mobility in the base**

The mobility in the base is determined in a differential manner by combining the sheet conductance and the active doping profile data. The mobility in a p-doped base as a function of the depth can be extracted by rearranging eq. 2.17 as

$$\mu_p(x) = \frac{dG_{sh}}{-qN_A(x)dx}. \quad (2.20)$$

## Chapter 3

# Process optimization for laser annealing of implanted junctions

In this chapter, the integration of laser annealing with the use of LPCVD TEOS as surface isolation and an Al reflective masking layer is examined and generally valid conclusions on the procedures needed to achieve good ideality of the laser annealed diodes are extracted.

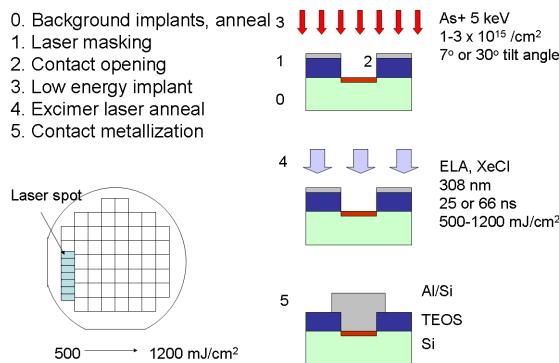

### 3.1 Experimental considerations

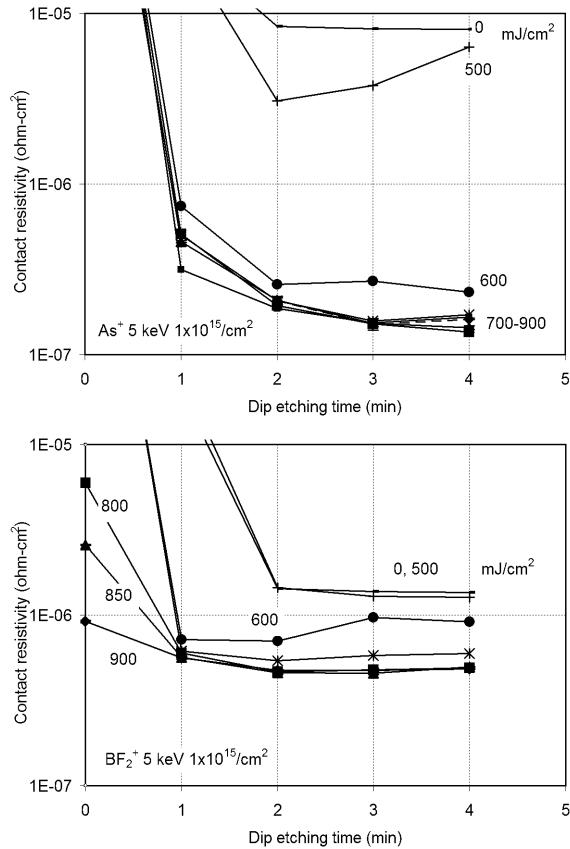

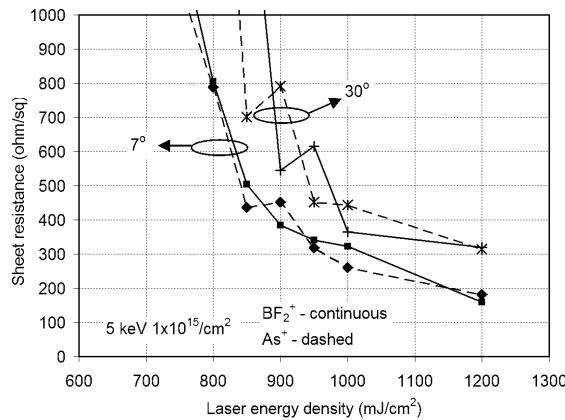

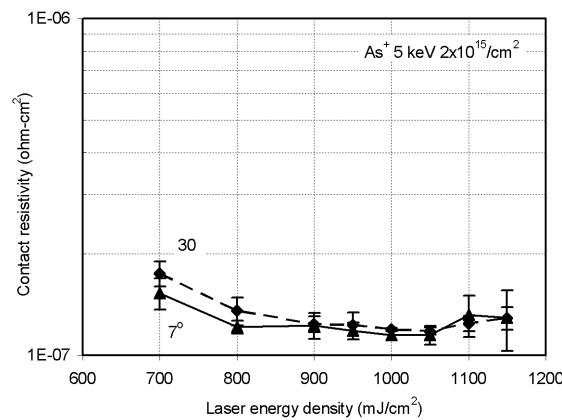

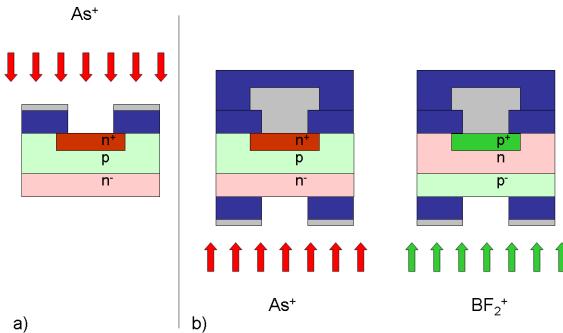

The basic process flow for the fabrication of laser annealed diodes is shown in Fig. 3.1 for  $n^+p$  diodes. Both  $p^+n$  and  $n^+p$  diodes are fabricated on (100) p-type silicon wafers that are patterned with both n- and p-type regions with a surface doping of  $10^{17} \text{ cm}^{-3}$ . In all the results presented in this chapter, the  $p^+$  and  $n^+$  regions to be laser annealed are formed by a 5 keV,  $1-3 \times 10^{15} \text{ cm}^{-2}$   $\text{BF}_2^+$  and  $\text{As}^+$  implantations, respectively with tilt angles of 7 and 30 degrees. Buried layers and deep implants are employed in some structures to allow contacting via the surface rather than from the back of the wafer and to achieve low diode series resistance. Rectangular diodes are measured in a size range from  $2 \times 1$  to  $40 \times 40 \mu\text{m}^2$ . Moreover, on some wafers Kelvin contact resistance test structures and van der Pauw sheet resistance structures are fabricated with the extra implants.

Figure 3.1: Schematic of basic process flow for fabrication of  $n^+p$  laser annealed diodes.

The ELA implants are performed directly in the contact windows, which has the advantage that no high temperature thermal processing is necessary after the laser anneal to complete the devices and the characteristics achieved by pure laser activation can be studied. The individual processing steps have been varied in several respects:

- The 330 nm thick surface isolation layer is either thermal oxide, LPCVD TEOS oxide deposited at 700 °C or a stack of 30 nm thermal oxide covered with LPCVD TEOS.

- The ELA reflecting masking layer is either a Al/Si(1%) or a pure Al layer deposited with different thickness by PVD at either 50 °C or 350 °C,

- the contact windows are defined by different combinations of plasma and wet etching through the Al and oxide to the silicon. The bulk of the plasma etch is performed by high rate, high power plasma etching where the Al is etched with a chlorine plasma until the underlying oxide layer that then is etched in a fluorine plasma. The actual landing on the silicon is performed with either a hard landing, where the oxide is etched with the high power plasma down to the silicon surface, or a soft landing where the power is reduced by 66%. Moreover a wet landing using different HF solutions is investigated,

- just before implanting the contacts, a short dip etch step is performed to remove the native oxide. A 3 min 0.55% HF dip is compared to dipping in 1:7 diluted buffered hydrofluoric (BHF) acid,

- the implantation was performed with either a standard 7° tilt with 22° twist or high tilt angles of 30° or 45° with 8 equal rotations to minimize shadowing with doses from  $1\text{--}3 \times 10^{15} \text{ cm}^{-2}$ .

- The laser annealing after the implantation was performed in a vacuum, using a XeCl excimer laser system with a wavelength of 308 nm, pulse duration of 66 ns (full width at half maximum), unless otherwise specified. On each wafer the laser energy densities are varied in the range of 500 to 1200 mJ/cm<sup>2</sup>. A single shot anneal is used because the masking layer deteriorates after each shot [Nanver et al., 2003].

- Before the standard metallization process, a HF dip etch step is performed to remove the native oxide before the metallization. The dip etch times are varied from 0–4 min.

- A new layer of 600 nm Al/Si(1%) is sputtered, patterned and the created contacts are measured before and after alloying at 400 °C for 30 min in forming gas.

## 3.2 Results

Processing steps shown in Fig. 3.1 from 1–5 are evaluated.

### 3.2.1 Laser masking

#### Isolation layer

The ideal isolation layer is also a good Si interface passivation layer. Moreover, it has low deposition temperature, good dielectric properties, good interface properties, is reflective to laser light and has low etch rates in HF. CVD nitrides that has extremely low etch-rates in HF are not directly an option because these materials have a high absorption of laser light and readily ablate for the energies applied here. For this reason only oxides are considered. Process parameters for the available oxides are summarized in Table 3.1. PECVD oxides are deposited at low temperatures (~400 °C) but they are not directly applicable to Si due to the interface properties and the low material density. High etch rates during the pre-metallization dip etch step result in enlargement of the contact windows, therefore insufficient oxide overlap at the diode edges, which leads to

Table 3.1: Process parameters for the isolation layers.

| layer         | dep. temp. (°C) | etch rate in 0.55% HF (nm/min) |

|---------------|-----------------|--------------------------------|

| thermal oxide | >1000           | 2.5                            |

| LPCVD TEOS    | 700             | 10                             |

| PECVD TEOS    | 400             | 15                             |

perimeter leakage of the diodes. The available LPCVD TEOS deposited at 700 °C has better properties, but is still not suitable as sole isolation layer because of its interface properties, and the relatively high etch rate. Thermal oxides give the best isolation properties, and low etch rates but at high temperature processes. For this reason a combination of 30 nm thermal oxide and 300 nm LPCVD TEOS is needed. The thin thermal oxide layer is sufficiently dip etch resistant to preserve the isolation of the diode edges due to the low etch rate of 2.5 nm/min in 0.55% HF. All oxide layers are partially transparent at the laser wavelength. Therefore, an additional reflective masking layer is needed.

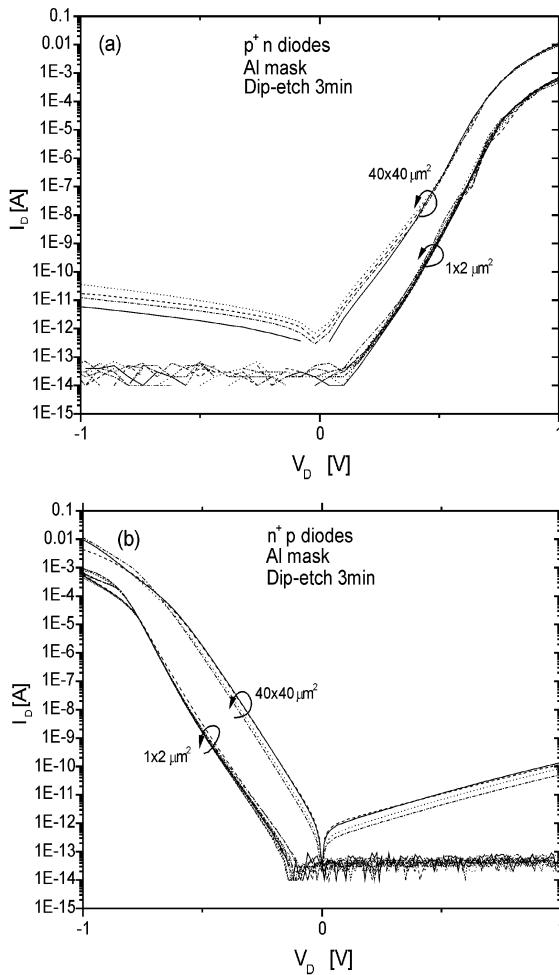

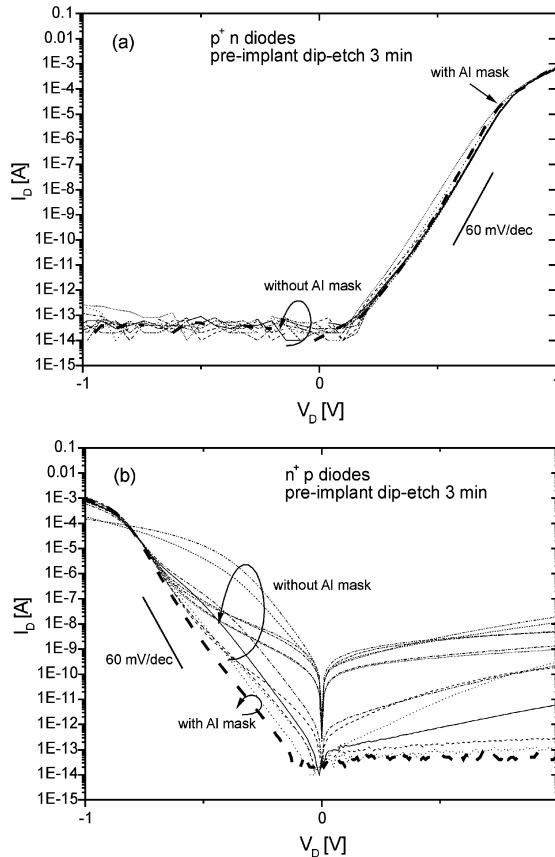

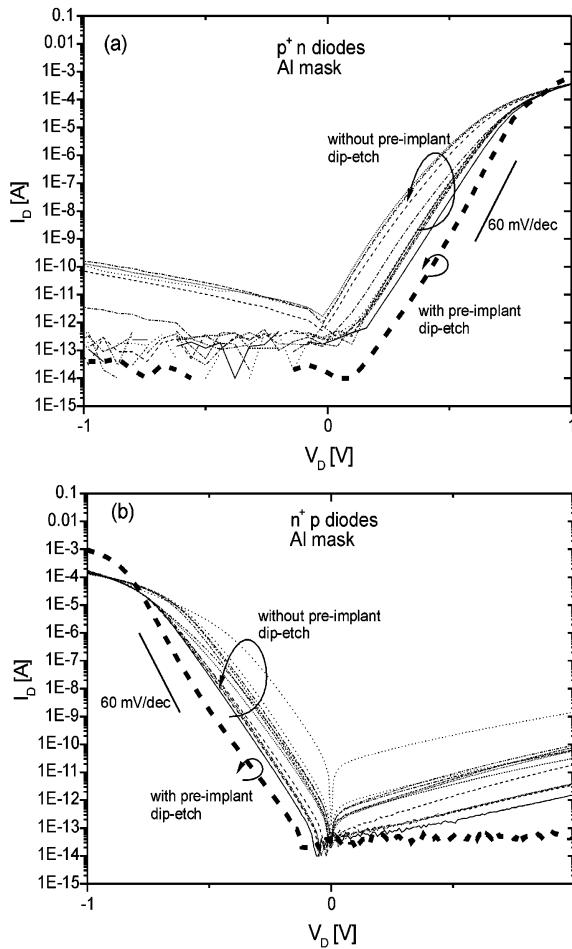

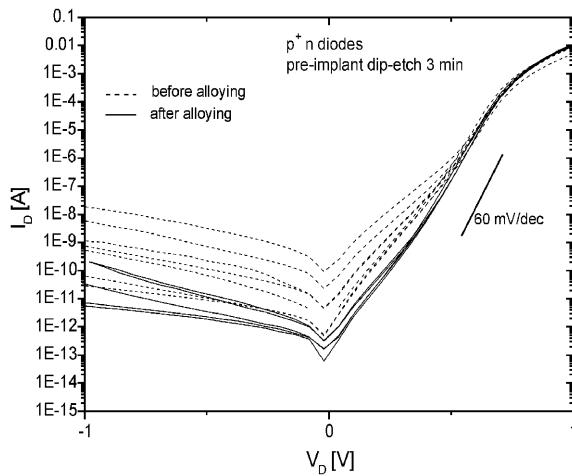

The ideality of diodes fabricated using the different combinations of isolation layer is summarized in Table 3.2. Very low ideality factors of 1.1 are achieved with pure thermal oxide isolation when hard landing and HF dip is used (Fig. 3.3). The same etch conditions give very high values, about 1.66–2.3, when replacing the bulk of the thermal oxide with TEOS. A combination of 30 nm thermal oxide and 300 nm LPCVD TEOS with soft landing and BHF dip gives a very significant improvement with values from 1.1–1.3 being reached (Fig. 3.13). This is comparable to the pure thermal oxide

Table 3.2: Comparison of n<sup>+</sup>p diodes with different isolations. Al/Si layer thickness: 100 nm, implant tilt: 30°, pre-metallization dip etch in 0.55% HF: 4 min.

| isolation                         | ideality |

|-----------------------------------|----------|

| 330 nm thermal oxide              | 1.1      |

| 330 nm TEOS                       | 1.66–2.3 |

| 30 nm thermal oxide + 300 nm TEOS | 1.1–1.3  |

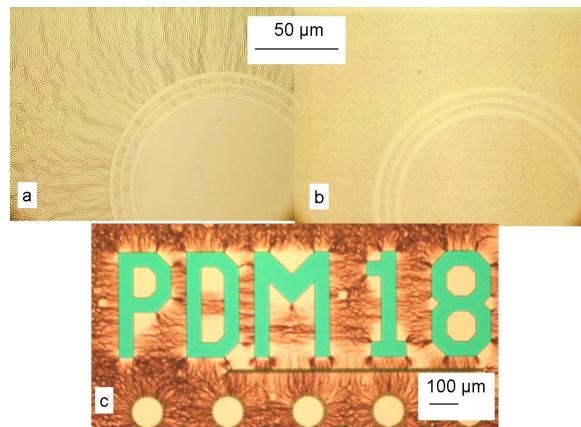

Figure 3.2: TEM image of the contact window edge. Laser masking: 30 nm thermal oxide, 300 nm TEOS, 100 nm Al/Si. Pre-implantation dip etch: 15 sec in 1:7 BHF, pre-metallization dip etch: 4 min in 0.55% HF.

situation. Figure 3.2 shows a TEM image of a diode edge in a fully processed device. Due to the lower etch rate of thermal oxide compared to PECVD TEOS, a smaller enlargement of the contact window at the interface is apparent, and therefore the diode edges are protected. The thermal oxide ensures sufficient isolation and prevents leakage. Pre-metallization etching time was 4 min in 0.55% HF for all cases.

### Reflective mask

Laser annealing can be masked by a reflective layer. The reflectivity of the oxides for the lasing wavelength is periodically changing with its thickness between 30-60% (Fig. 2.8). A more controllable situation can be created by adding a high reflectivity layer. In our case sputtered Al layers are used as reflective coating. The more than 300 nm thick Al/Si(1%) layers normally used for metallization were found to have several drawbacks. Normally a sputtering temperature of 350 °C is used to achieve good step coverage but this also entails large grain formation. The laser annealing of these large grain layers results in a non-uniform composition of the Al/Si that is difficult to plasma etch uniformly during subsequent contact window etching. Using 100 nm thin layers deposited at 50 °C results in a fine grain structure. An improvement in the diode

Figure 3.3: Over the wafer measurements of I-V diode characteristics for (a)  $p^+ n$  and (b)  $n^+ p$  diodes, with diode areas of  $1 \times 2 \mu\text{m}^2$  and  $40 \times 40 \mu\text{m}^2$ . Laser masking: 300 nm thermal oxide, 600 nm Al/Si [Nanver et al., 2003].

Figure 3.4: Over the wafer measurements of I-V diode characteristics for (a)  $p^+n$  and (b)  $n^+p$  diodes with a diode area of  $1 \times 2 \mu\text{m}^2$ , with and without an Al masking layer. Laser masking: 300 nm thermal oxide, 600 nm Al/Si [Nanver et al., 2003].

Table 3.3: Pre-implant RMS surface roughness (angstrom) as a function of the type of Al masking layer and the etch process used for landing on the silicon. Laser masking: 300 nm thermal oxide, 100 nm Al(/Si).

| landing | Al | Al/Si |

|---------|----|-------|

| hard    | 17 | 27    |

| soft    | 12 | 12    |

| wet     | 11 | 35    |

characteristics is shown in Fig. 3.4 with an Al/Si reflective layers for  $\text{As}^+$  and  $\text{BF}_2^+$  ELA implants.

### 3.2.2 Contact window etching

The laser annealed junctions are self-aligned to the contact windows, in which they are implanted. Opening the contact window requires etching through the Al(Si)/ TEOS/ (thermal oxide) layer stack, which is performed by plasma etching with chlorine chemistry for the metal and fluorine chemistry for the oxide layers. The landing on the silicon has to be tuned in order to prevent large overetching and consequent surface degradation.

The effect of the landing is studied by determining the surface roughness of the silicon surface after etching by AFM [Gonda et al., 2004]. The measurement procedure is described in Section 2.3.1. Results are shown in Table 3.3. The soft landing procedure, where plasma power was decreased when reaching the Si surface, in general resulted in the smoothest surface in the close to 10 angstrom RMS roughness. However, excessive soft etching (overetching) can damage the silicon surface so in practice it can become a critical step. The wet landing in combination with pure Al results in an equally smooth surface. For both hard and wet landing the results indicate an increased surface roughness when Al/Si is used as reflective layer. For wet landing, this can be attributed to Si precipitates from the Al/Si and to avoid this issue it can be more attractive to use a pure Al reflective coating.

However, when most of the thermal oxide is replaced by TEOS, the resulting diode characteristics also become sensitive to the total contact window etch procedure, especially to the pre-implantation dip etching.

Figure 3.5: Over the wafer measurements of I-V diode characteristics for (a)  $p^+n$  and (b)  $n^+p$  diodes with a diode area of  $1 \times 2 \mu\text{m}^2$ , with and without a 3 min dip etch in 0.55% HF prior to the implantation. Note that in case of p-diodes at uncovered edges a Schottky diode forms. Laser masking: 300 nm thermal oxide, 600 nm Al/Si [Nanver et al., 2003].

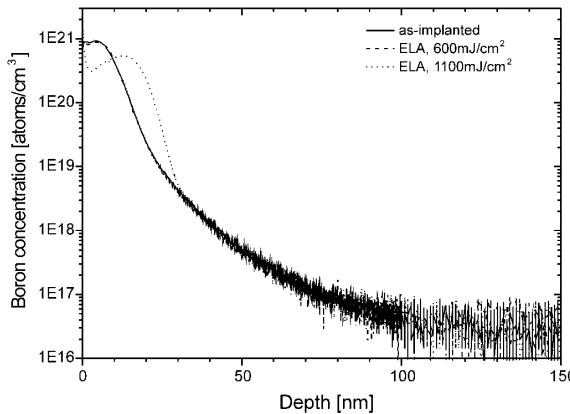

Figure 3.6: SIMS profiles of the boron chemical concentration after a 5 keV  $10^{15} \text{ cm}^{-2}$   $\text{BF}_2^+$   $7^\circ$  implant and laser annealing at 600 or 1100  $\text{mJ/cm}^2$  [Burtsev et al., 2004].

### 3.2.3 Low-energy implantation

#### Pre-implant dip etch

The results in Fig. 3.5 show that the surface of the contact window should be dip etched in HF to remove native oxide before the low-energy implant in order to guarantee good diode characteristics. This is correlated to the fact that due to the very short range of the ions, a large number are captured in the non-uniform native oxide layer.

However, with the conventionally applied 0.55% HF acid the etch rate of Al is high (75 nm/min) and this prohibits its use in combination with thin reflective coatings. An alternative, short time etching in BHF, was found to give attractive results for an etch time of 15 s. In this process about 50 nm Al/Si and 60 nm of TEOS oxide are etched. In BHF the etching of the Al is a self-terminating process with a maximum of 50 nm being etched so that a reliably thin masking layer remains.

#### Implantation parameters

A shallow implantation can be achieved by using low implantation energies. The lowest achievable energy depends on the implanter machinery. A SIMS profile of the 5 keV  $\text{BF}_2^+$  implant with a tilt angle of  $7^\circ$  is shown in Fig. 3.6, the as-implanted  $\text{B}^+$  projected range is about 7 nm. The advantage of the compound is that 49/11 times higher energies

Figure 3.7: SIMS profiles of the arsenic chemical concentration after a 5 keV  $10^{15} \text{ cm}^{-2}$   $\text{As}^+$  implant with tilt angles of 7, 30, and 45 degrees and laser annealing at  $1000 \text{ mJ/cm}^2$  with a 25 ns pulse.

can be used to achieve the same implant depth compared to  $\text{B}^+$  ion implantation due to the large total mass.

All the doses used for the shallow implants are well above the amorphizing limit. Increase of the dose from 1 to  $3 \times 10^{15} \text{ cm}^{-2}$  will not give a significant increase in the implantation depth, but the amorphous zone will be deeper. This is valid for the implant energies in the low energy range [Jones et al., 1998]. The generated amount of implantation damage scales with the implant dose as well [Hobler and Otto, 2003].

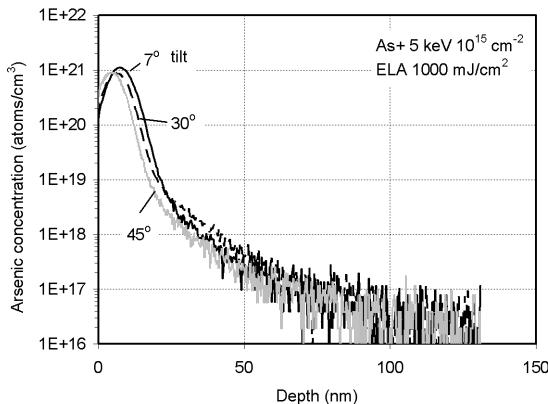

Tilted implants are beneficial to increase the overlap with the window or gate edges, and these implants also result in shallower profiles. Trim simulations results for 5 keV  $\text{As}^+$  implantation into silicon show that increasing tilt angles of 7°, 30° and 60° results in projected ranges of 85, 74 and 46 angstroms with straggle of 30, 29 and 25 angstroms, respectively. Sputtering of silicon also increases with the increasing tilt angles as 1, 1.58 and 6 atoms/ion, respectively. SIMS results for a  $10^{15} \text{ cm}^{-2}$   $\text{As}^+$  implant with tilt angles of 7, 30, and 45 degrees, laser annealing at  $1000 \text{ mJ/cm}^2$  are compared in Fig. 3.7. Increasing tilt angles result in shallower profiles. The dose loss is apparent in the measured doses:  $1.05 \times 10^{15} \text{ cm}^{-2}$ ,  $7.98 \times 10^{14} \text{ cm}^{-2}$ , and  $7.43 \times 10^{14} \text{ cm}^{-2}$  with the increasing tilt angles. Slightly more channelling is seen at 30° tilt. The abruptness of the tail of the profiles are about 5 nm/decade.

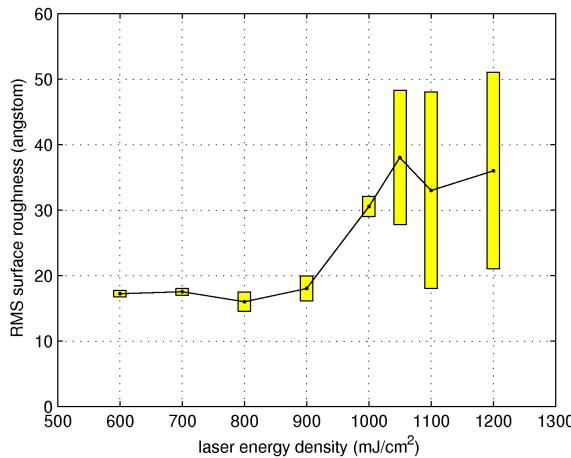

Figure 3.8: AFM measured surface roughness of an  $\text{As}^+$   $10^{15} \text{ cm}^{-2}$  5 keV implanted and laser annealed surface as a function of laser anneal energy [Burtsev et al., 2004].

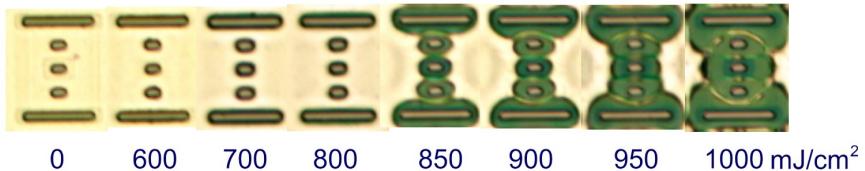

Electrical diode characteristics show a dependence on the tilt for the  $n^+p$  but it is less obvious for the  $p^+n$  diodes. Typical measurements of the I-V characteristics of p-type diodes that were fabricated with  $30^\circ$  tilt during the implant are shown in Fig. 3.14. The spread in ideality factor increases as the laser energy density increases, which can be attributed to laser induced surface roughening. Leakage currents are reduced in the case of  $\text{As}^+$  implants, when the implantation tilt is changed from  $7^\circ$  to  $30^\circ$  as can be seen from the improvement in I-V characteristics of  $n^+p$  diodes in Fig. 3.13.

### 3.2.4 Laser anneal

During the laser illumination the surface layer is melted to a depth that depends on the laser energy. The redistribution of dopants seen in Fig. 3.6 indicates that for an ELA of  $600 \text{ mJ/cm}^2$  is necessary for the melt onset while  $1100 \text{ mJ/cm}^2$  causes full melt with a depth 20 nm. The junction depth at a doping of  $10^{18} \text{ cm}^{-3}$  has also been measured by a special CV-profiling technique [Nanver et al., 2003] to be in this range. The activation is very high in the melted region and for an optimal recrystallization of this region the melt zone should extend past the original amorphous/ crystalline interface. Beneath the recrystallized region the implantation induced end-of-range defects are not necessarily annealed. The defect distribution has been studied by positron annihilation

Figure 3.9: Enlargement of the aluminium mask windows due to the high temperatures experienced around the laser annealed silicon. The size of the small opening is  $2 \times 1 \mu\text{m}^2$ . Laser masking layer: 30 nm thermal oxide, 300 nm LPCVD TEOS, 100 nm Al/Si.

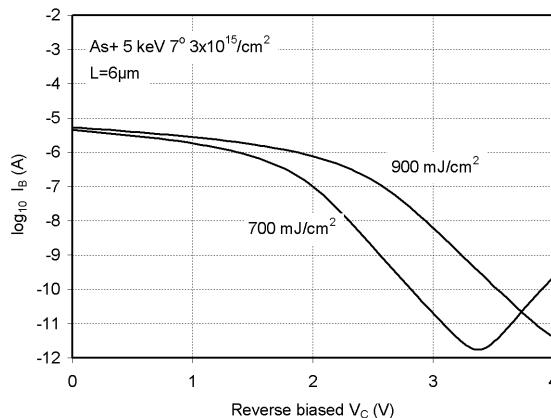

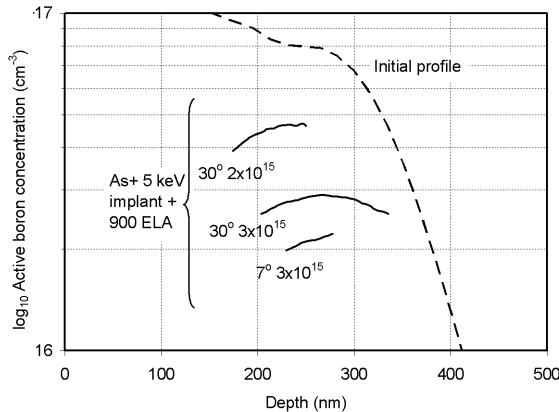

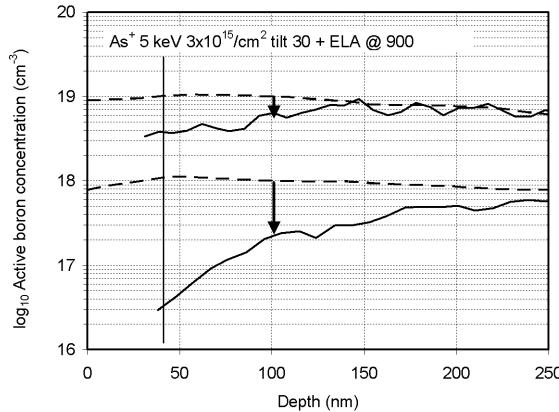

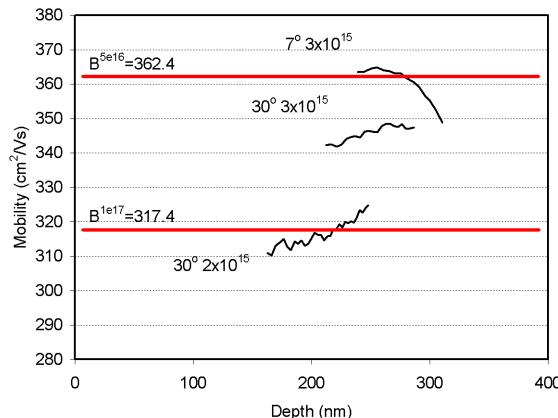

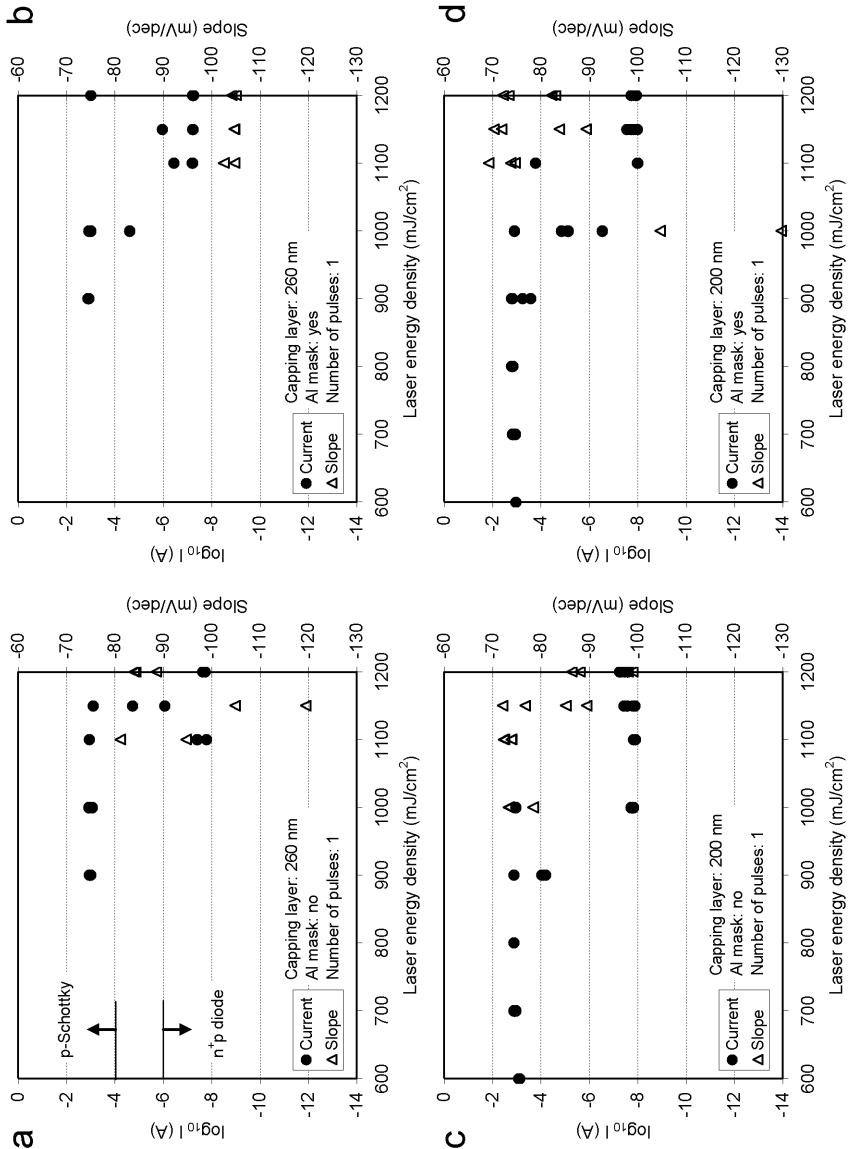

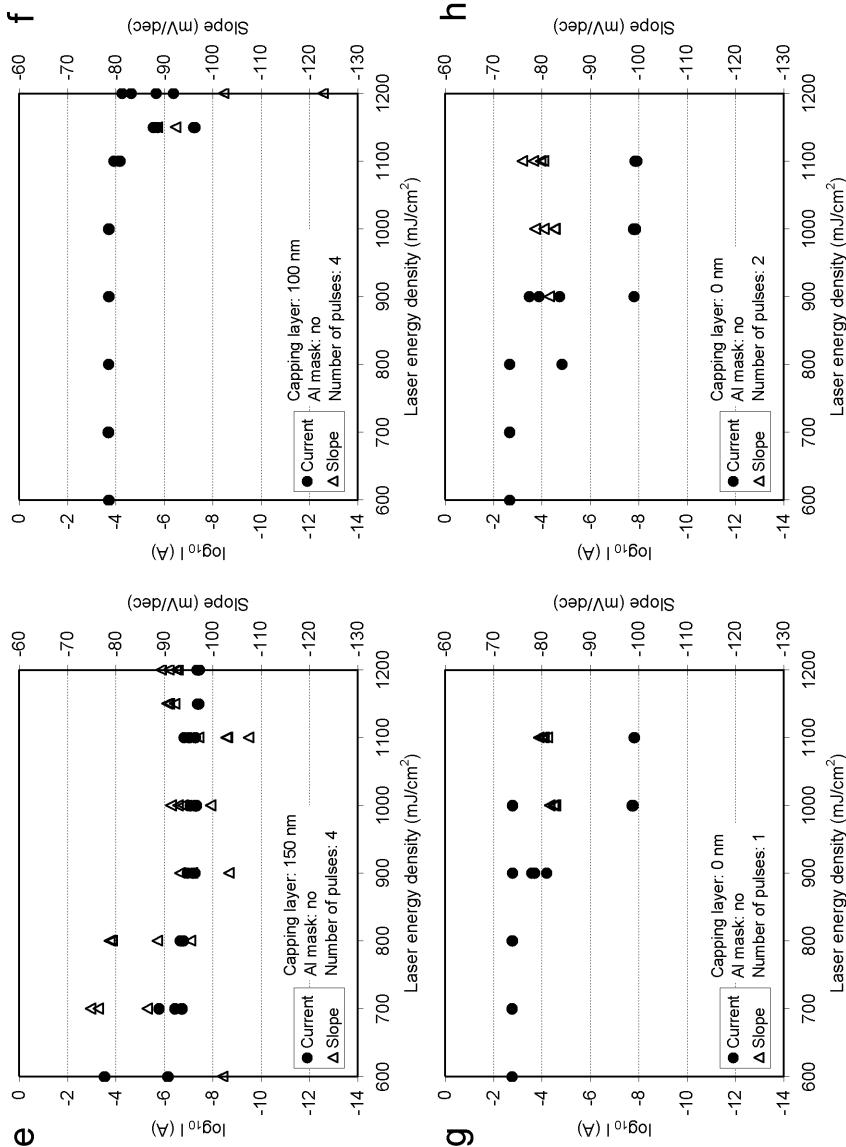

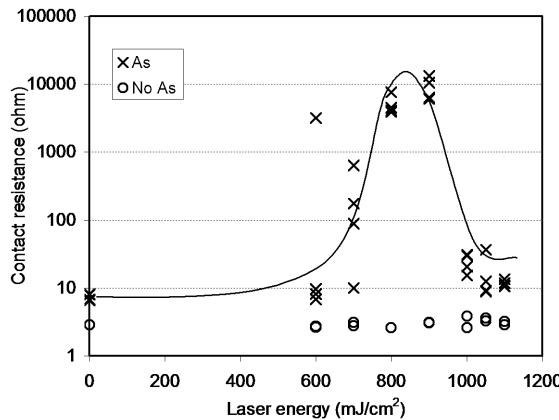

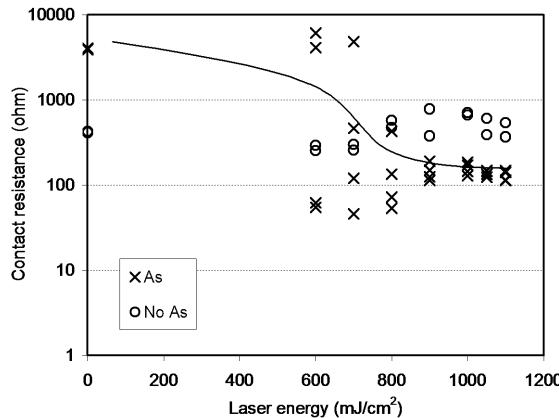

doppler broadening technique [Burtsev et al., 2004], and it was shown that defects also accumulate at a depth of 150-200 nm.