### M.Sc. Thesis

# Data Acquisition System Design for a 160x128 Single-photon Image Sensor with On-pixel 55 ps Time-to-digital Converter

Chockalingam Veerappan

#### Abstract

Time-resolved image sensors enabling picosecond resolutions over large formats are needed in many advanced imaging fields, from fluorescence lifetime imaging microscopy (FLIM) to positron emission tomography (PET). Integrated single-photon avalanche diode (SPAD) technology embodies the new frontiers of time-resolved imaging, namely better instrument response function, increased throughput and lower costs. SPADs have recently developed onto large arrays with increasing on-chip functionality. With larger array sizes however, the data generation rate has become a throughput bottleneck and thus necessitating an efficient data acquisition system.

In this thesis a data acquisition system was developed, for one of the largest single-photon imager ever devised with 160x128 pixels capable of detecting the time-of-arrival of single photons with picosecond resolution. To handle the gigabytes of data generated every second, techniques such as a column based event-driven system for photonstarved applications was implemented.

The thesis presents a test strategy and characterization methodology. Using the developed data acquisition system, the imager was tested and characterized successfully. To conclude, an example of a biological sample imaged with FLIM is shown as a demonstration of the potentialities of our system.

# Data Acquisition System Design for a 160x128 Single-photon Image Sensor with On-pixel 55 ps Time-to-digital Converter

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

MICROELECTRONICS

by

Chockalingam Veerappan born in Coimbatore, India

#### This work was performed in:

Circuits and Systems Group

Department of Microelectronics & Computer Engineering

Faculty of Electrical Engineering, Mathematics and Computer Science

Delft University of Technology

#### **Delft University of Technology**

Copyright  $\odot$  2010 Circuits and Systems Group All rights reserved.

# DELFT UNIVERSITY OF TECHNOLOGY DEPARTMENT OF MICROELECTRONICS & COMPUTER ENGINEERING

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled "Data Acquisition System Design for a 160x128 Single-photon Image Sensor with On-pixel 55 ps Time-to-digital Converter" by Chockalingam Veerappan in partial fulfillment of the requirements for the degree of Master of Science.

| Dated: 26 November 2010 |                               |

|-------------------------|-------------------------------|

| Chairman:               | prof. dr. ir. Edoardo Charbon |

| Advisor:                | prof. dr. ir. Edoardo Charbon |

| Committee Members:      | dr.ir. Stephan Wong           |

|                         | dr.ir. Dennis Schaart         |

### Abstract

Time-resolved image sensors enabling picosecond resolutions over large formats are needed in many advanced imaging fields, from fluorescence lifetime imaging microscopy (FLIM) to positron emission tomography (PET). Integrated single-photon avalanche diode (SPAD) technology embodies the new frontiers of time-resolved imaging, namely better instrument response function, increased throughput and lower costs. SPADs have recently developed onto large arrays with increasing on-chip functionality. With larger array sizes however, the data generation rate has become a throughput bottleneck and thus necessitating an efficient data acquisition system.

In this thesis a data acquisition system was developed, for one of the largest single-photon imager ever devised with 160x128 pixels capable of detecting the time-of-arrival of single photons with picosecond resolution. To handle the gigabytes of data generated every second, techniques such as a column based event-driven system for photon-starved applications was implemented.

The thesis presents a test strategy and characterization methodology. Using the developed data acquisition system, the imager was tested and characterized successfully. To conclude, an example of a biological sample imaged with FLIM is shown as a demonstration of the potentialities of our system.

## Acknowledgments

I wish to express my gratitude to my professor, Edoardo Charbon for offering me an opportunity to work on this interesting project. His continued support, encouragement and guidance have motivated me ever since I joined his group for my graduation thesis. I would also like to thank Matthew Fishburn and Yuki Maruyama for their help, support and the time they spent with me in the lab during the testing and characterizing phase. I attribute a level of my master thesis to them without whom, this thesis would not have been successful. I would like to thank Hyung June Yoon, Mohammad A. Karami and Matteo Tonina for their support.

I would also like to thank D.U.Li, Justin Richardson and Richard Walker with whom I collaborated during the initial phase of this thesis. I would like to thank Antoon Frehe for providing the computing facilities and support in solving the computer related issues.

I would like to use this opportunity to thank my friends Ashish Nigam, Saket Sakunia, Madhavan Manivannan, Karthick Chandrasekar, Vinoth Elangovan, Maxim Volvo, Vashishth Chaudhri, Raj Thilak, Sumeet Kumar, Shilesh, Rajat Bharadwaj, Sriram and Akansh Goyal for their help and support during the course of this thesis.

Finally I would like to thank my parents, brothers and my friends back in India for their support and encouragement, throughout my course of study at TU Delft.

Chockalingam Veerappan Delft, The Netherlands 26 November 2010

# Contents

| $\mathbf{A}$ | bstra        | nct                                                                        |   |  |  |  |

|--------------|--------------|----------------------------------------------------------------------------|---|--|--|--|

| A            | ckno         | wledgments                                                                 | 1 |  |  |  |

| 1            | Introduction |                                                                            |   |  |  |  |

|              | 1.1          | Motivation                                                                 |   |  |  |  |

|              | 1.2          | Contribution                                                               |   |  |  |  |

|              | 1.3          | Overview                                                                   |   |  |  |  |

| 2            | MF           | 128 Architecture                                                           |   |  |  |  |

|              | 2.1          | Megaframe chip architecture overview                                       |   |  |  |  |

|              | 2.2          | Categorization of internal modules                                         |   |  |  |  |

|              | 2.3          | Pixel array                                                                |   |  |  |  |

|              |              | 2.3.1 The Photon detector                                                  |   |  |  |  |

|              |              | 2.3.2 Measurement unit                                                     |   |  |  |  |

|              |              | 2.3.3 Buffer                                                               |   |  |  |  |

|              |              | 2.3.4 Pixel enable / disable logic                                         |   |  |  |  |

|              |              | 2.3.5 Design for testability                                               |   |  |  |  |

|              | 2.4          | Readout system                                                             |   |  |  |  |

|              | 2.1          | 2.4.1 Data compression technique                                           |   |  |  |  |

|              | 2.5          | System configuration module                                                |   |  |  |  |

|              | 2.0          | 2.5.1 I2C                                                                  |   |  |  |  |

|              |              | 2.5.2 ROWEN/COLEN                                                          |   |  |  |  |

|              | 2.6          | Summary                                                                    |   |  |  |  |

| _            |              | ·                                                                          |   |  |  |  |

| 3            |              | ta acquisition system                                                      |   |  |  |  |

|              | 3.1          | Specification                                                              |   |  |  |  |

|              |              | 3.1.1 Light source insensitivity                                           |   |  |  |  |

|              |              | 3.1.2 Requirements to communicate with the MF128 imager                    |   |  |  |  |

|              | 3.2          | Analysis on the earlier version of the imager                              |   |  |  |  |

|              | 3.3          | Hardware setup                                                             |   |  |  |  |

|              | 3.4          | Data acquisition system top-level design                                   |   |  |  |  |

|              |              | 3.4.1 Firmware Architecture                                                |   |  |  |  |

|              |              | 3.4.2 Established communication protocol between the firmware and software |   |  |  |  |

|              | 3.5          | Firmware design                                                            |   |  |  |  |

|              |              | 3.5.1 USB communication                                                    |   |  |  |  |

|              |              | 3.5.2 Line timing                                                          |   |  |  |  |

|              |              | 3.5.3 I2C                                                                  |   |  |  |  |

|              |              | 3.5.4 ROWEN/COLEN                                                          |   |  |  |  |

|              |              | 3.5.5 Data pipeline path                                                   |   |  |  |  |

|              | 3.6          | Software                                                                   |   |  |  |  |

|   | 3.7                  | Application specific data-throughput optimization techniques          | 28         |

|---|----------------------|-----------------------------------------------------------------------|------------|

|   |                      | 3.7.1 Data accumulators for TUPC mode                                 | 28         |

|   |                      | 3.7.2 Column based event driven system                                | 28         |

|   |                      | 3.7.3 Time interleaved sampling on high DCR pixels for code-density   |            |

|   |                      | test                                                                  | 30         |

|   | 3.8                  | Summary                                                               | 34         |

| 4 | $\operatorname{Tin}$ | ne-Uncorrelated Photon Counting                                       | 35         |

|   | 4.1                  | TUPC overview                                                         | 35         |

|   | 4.2                  | Test strategy                                                         | 36         |

|   |                      | 4.2.1 Inter-module dependency                                         | 36         |

|   | 4.3                  | Module test                                                           | 37         |

|   |                      | 4.3.1 I2C                                                             | 37         |

|   |                      | 4.3.2 Serializer and Y-decoder                                        | 38         |

|   |                      | 4.3.3 Ripple counter                                                  | 39         |

|   |                      | 4.3.4 ROWEN/COLEN                                                     | 40         |

|   |                      | 4.3.5 Photon detector                                                 | 41         |

|   | 4.4                  | TUPC test                                                             | 44         |

|   |                      | 4.4.1 Test methodology                                                | 44         |

|   |                      | 4.4.2 Results and discussion                                          | 44         |

|   | 4.5                  | Dark noise characterization                                           | 44         |

|   |                      | 4.5.1 Dark noise overview                                             | 44         |

|   |                      | 4.5.2 Experimental Setup                                              | 45         |

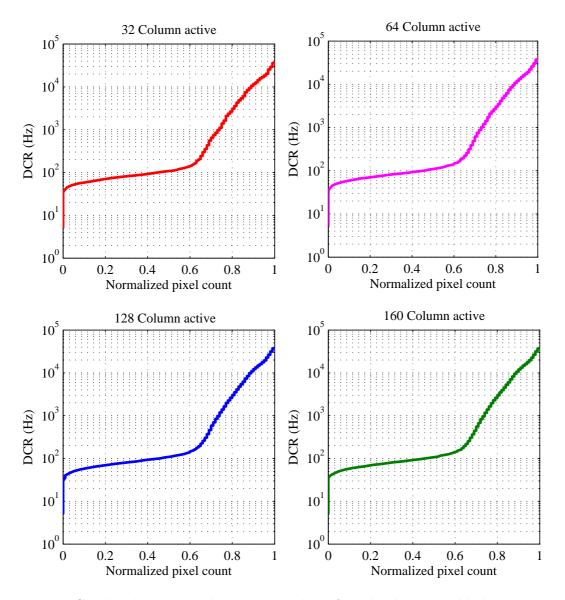

|   |                      | 4.5.3 Dark count rate uniformity                                      | 45         |

|   |                      | 4.5.4 Effect of DCR on electrical noise (Supply or substrate induced) | 45         |

|   |                      | 4.5.5 Effect of DCR on temperature and excess bias voltage            | 47         |

|   |                      | 4.5.6 SPAD breakdown voltage extraction                               | 47         |

|   | 4.6                  | Impact of digital noise                                               | 51         |

|   | 4.7                  | 2-D picture                                                           | 51         |

|   | 4.8                  | Summary                                                               | 52         |

| 5 | Tim                  | as Cannalated Single Dhaten Counting Made                             | 55         |

| Э |                      | ne-Correlated Single Photon Counting Mode  Time to digital conventor  | <b>5</b> 5 |

|   | 5.1                  | <u> </u>                                                              | 55<br>55   |

|   |                      | 5.1.1 Test methodology                                                | 56         |

|   | 5.2                  | Study on scaling active TDCs: Using TEST start-stop signal            | 50<br>57   |

|   | ٥.∠                  | 5.2.1 Experiment                                                      | 57<br>57   |

|   |                      | 5.2.2 Analysis                                                        | 58         |

|   |                      | 5.2.3 Inference                                                       | 59         |

|   | 5.3                  | TDC jitter measurement using electrical impulse                       | 60         |

|   | 5.4                  | Code density test                                                     | 62         |

|   | J.T                  | 5.4.1 TDC output range test                                           | 62         |

|   |                      | 5.4.2 Unexpected spike                                                | 64         |

|   |                      | 5.4.3 TDC resolution measurement                                      | 70         |

|   |                      | 5.4.4 TDC non-linearity measurement                                   | 71         |

|   | 5 5                  | TCSPC tost                                                            | 73         |

|    |                      | 5.5.1  | Test methodology                          | 74 |

|----|----------------------|--------|-------------------------------------------|----|

|    |                      | 5.5.2  | Results and discussion                    | 74 |

|    | 5.6                  | Timing | g resolution                              | 75 |

|    | 5.7                  | Study  | on scaling active TDCs: Under light       | 75 |

|    | 5.8                  | Fluore | scence Life Time Imaging Microscopy(FLIM) | 82 |

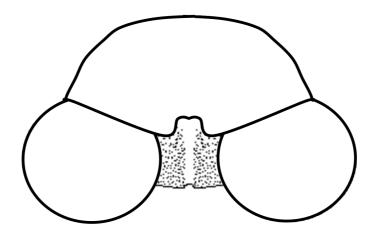

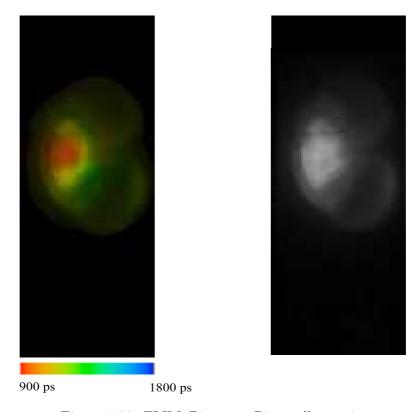

|    |                      | 5.8.1  | Biological sample                         | 83 |

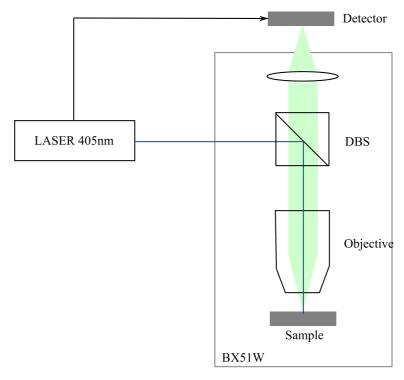

|    |                      | 5.8.2  | Optical setup                             | 83 |

|    |                      | 5.8.3  | MF128 configuration                       | 84 |

|    |                      | 5.8.4  | Data analysis                             | 84 |

|    |                      | 5.8.5  | Experimental results                      | 85 |

|    | 5.9                  | Summ   | ary                                       | 86 |

| 6  | Con                  | clusio | 1                                         | 89 |

|    | 6.1                  | Summ   | ary                                       | 89 |

|    | 6.2                  |        | e work                                    | 90 |

| A  | I2C                  | Regist | ter map                                   | 91 |

| Bi | Bibliography         |        |                                           | 95 |

| Li | List of Publications |        |                                           | 97 |

# List of Figures

| 2.1  | MF128 Block Diagram                                                                                               | 6               |

|------|-------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.2  | Categorization of internal modules                                                                                | 6               |

| 2.3  | Pixel contents                                                                                                    | 7               |

| 2.4  | Photon detector or SPAD ensemble                                                                                  | 8               |

| 2.5  | Ring oscillator schematic                                                                                         | 10              |

| 2.6  | TDC schematic                                                                                                     | 10              |

| 2.7  | Process Voltage Temperature (PVT) variation control loop                                                          | 10              |

| 2.8  | Pixel enable logic                                                                                                | 11              |

| 2.9  | Pixel Architecture                                                                                                | 12              |

| 2.10 | Simplified readout system                                                                                         | 13              |

| 2.11 | MF128 architecture summary                                                                                        | 15              |

| 3.1  | Light source control: Master/Slave mode                                                                           | 18              |

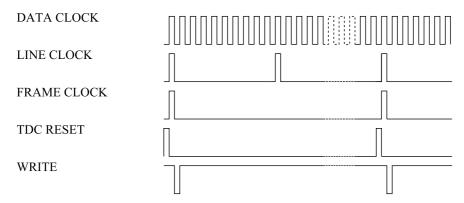

| 3.2  | Data acquisition system: Timing diagram                                                                           | 20              |

| 3.3  | Hardware setup                                                                                                    | 21              |

| 3.4  | Data acquisition system overview                                                                                  | 22              |

| 3.5  | Firmware Architecture                                                                                             | 23              |

| 3.6  | Software: Abstraction layer                                                                                       | $\frac{25}{27}$ |

| 3.7  | Accumulator based design                                                                                          | 29              |

| 3.8  | Column based event driven system                                                                                  | 31              |

| 3.9  | DCR distribution: With various number of pixel columns enabled at                                                 | 01              |

| 0.0  | room temperature and 0.96 V excess bias voltage                                                                   | 32              |

| 3.10 | Time interleaved sampling system                                                                                  | 33              |

| 4 1  |                                                                                                                   | 0.7             |

| 4.1  | Test strategy                                                                                                     | 37              |

| 4.2  | Ripple counter test results                                                                                       | 40              |

| 4.3  | Photon detection probability (PDP)                                                                                | 42              |

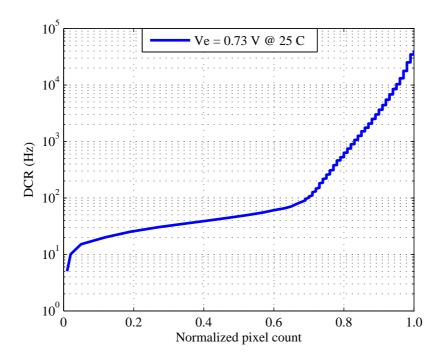

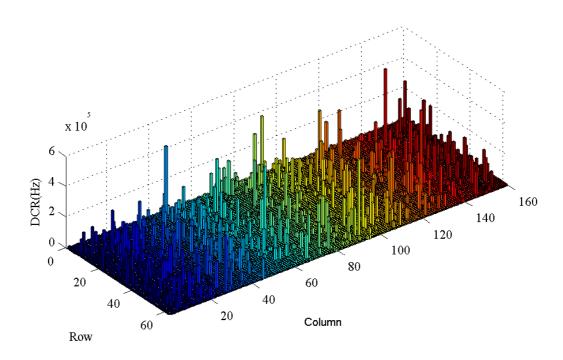

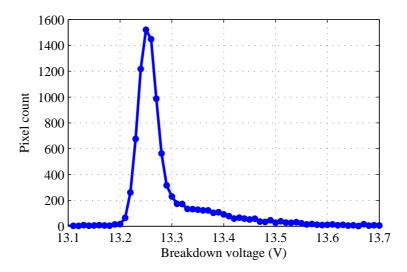

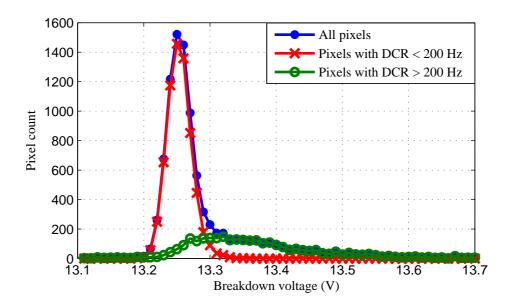

| 4.4  | DCR histogram at 25°C and 0.73V excess bias voltage                                                               | 46              |

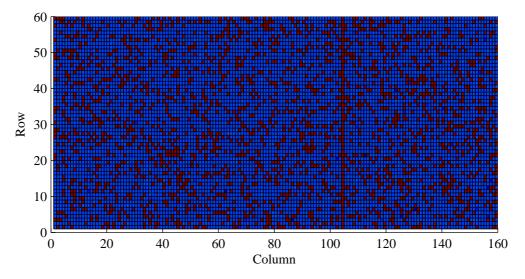

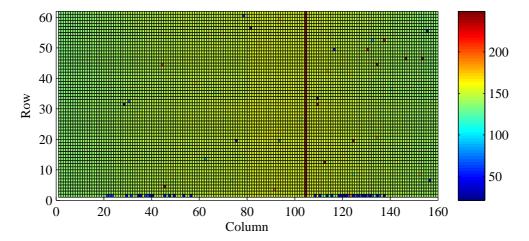

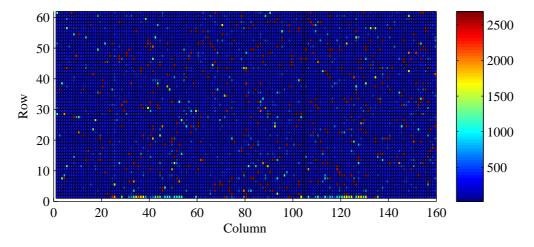

| 4.5  | DCR spatial distribution at 25°C and 0.73V excess bias voltage                                                    | 46              |

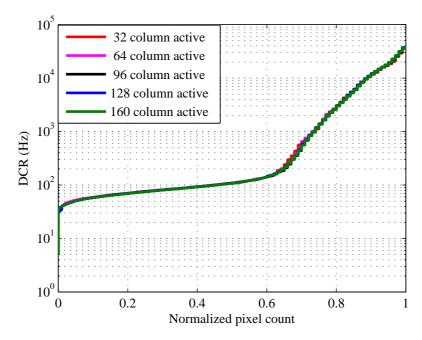

| 4.6  | Impact on DCR of active columns at room temperature and 0.96V excess                                              |                 |

|      | bias voltage                                                                                                      | 47              |

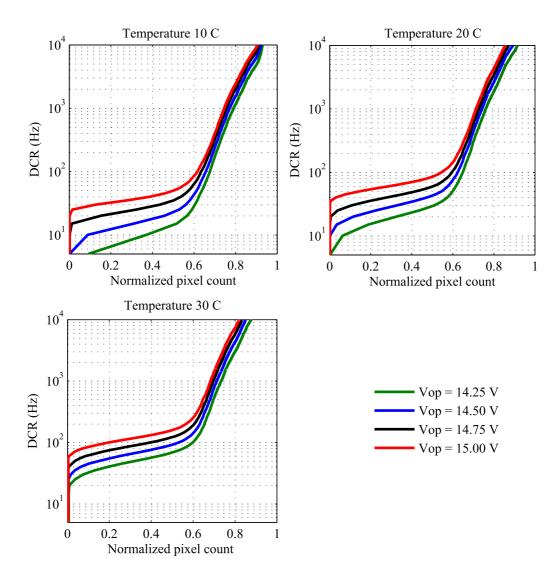

| 4.7  | DCR distribution varying temperature and excess bias voltage                                                      | 48              |

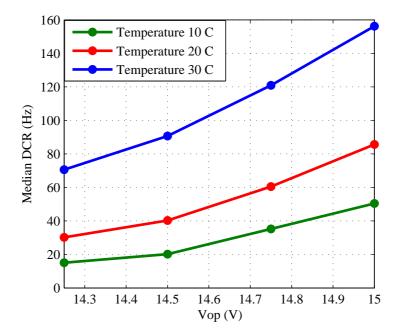

| 4.8  | Median DCR vs $V_{op}$ at various temperatures                                                                    | 49              |

| 4.9  | SPAD breakdown voltage distribution                                                                               | 50              |

| 4.10 | Spatial distribution of high threshold voltage (>13.3V) pixels                                                    | 50              |

| 4.11 |                                                                                                                   | 51              |

|      | Impact of digital noise on TUPC mode                                                                              | 52              |

| 4.13 | Mannequin image                                                                                                   | 52              |

| 5.1  | Experimental results to test the TDC functionality                                                                | 56              |

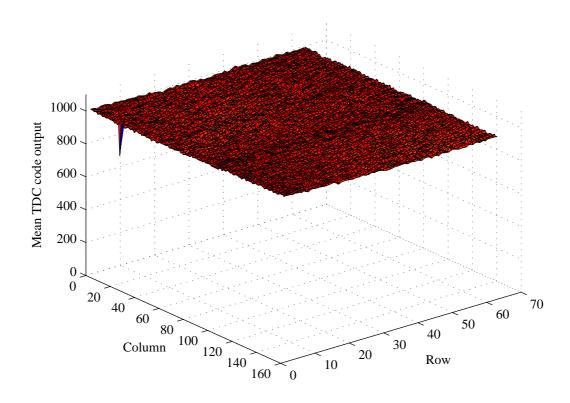

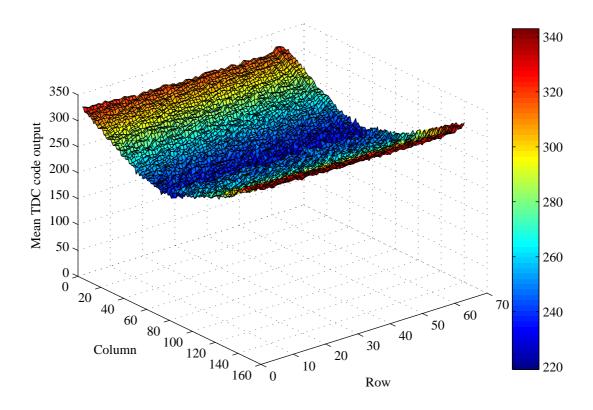

| 5.2  | Mean TDC code output distribution across the pixel array with 160x64 pixels active using TEST start - STOP signal | 57              |

| 5.3           | Effect on mean TDC code output on column 1, with increasing active                |

|---------------|-----------------------------------------------------------------------------------|

| - 1           | column                                                                            |

| 5.4           | Mean TDC code output observed with one column active at a time                    |

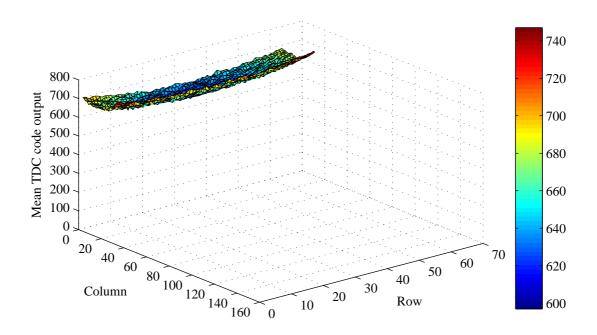

| 5.5           | Mean TDC output code distribution across the pixel array, with 32x64              |

| - 0           | pixels acive at one extreme of the array                                          |

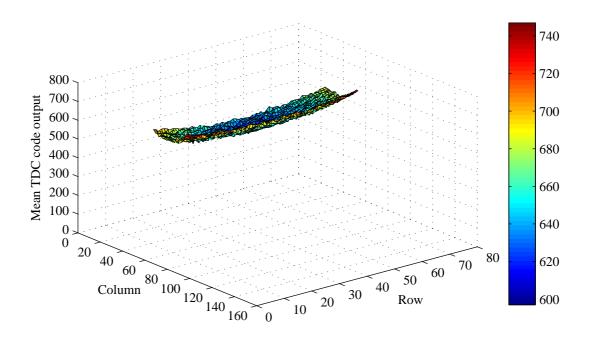

| 5.6           | Mean TDC output code distribution across the pixel array, with 32x64              |

|               | pixels acive in the center of the pixel array                                     |

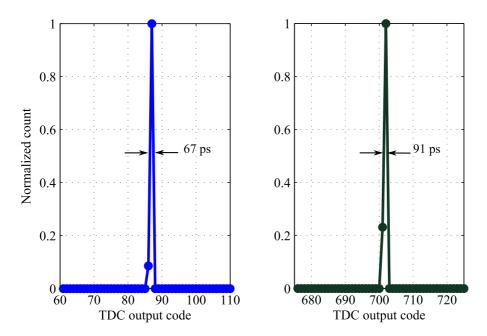

| 5.7           | TDC jitter measurement                                                            |

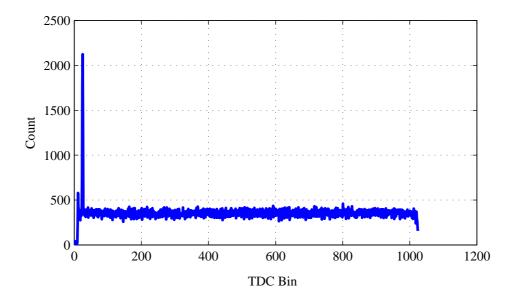

| 5.8           | Code density test output                                                          |

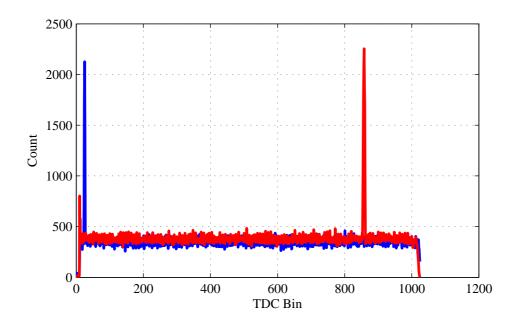

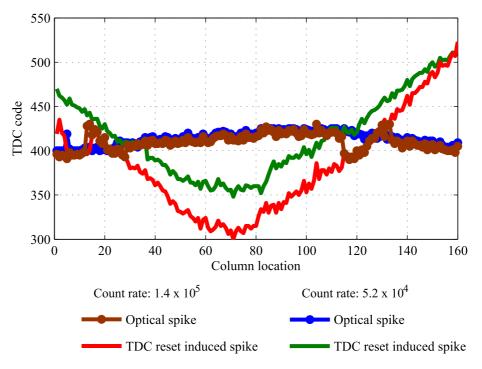

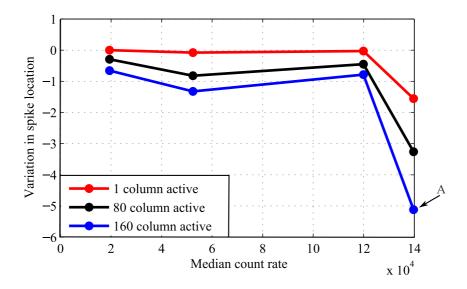

| 5.9           | Code density test: variation in the location of the spike                         |

| 5.10          | 1                                                                                 |

| 5.11          |                                                                                   |

|               | reset and stop clock, used to study the spike cause                               |

| 5.12          | Experimental results of two different experiments with different delay            |

|               | between the TDC reset and stop clock, with SPAD off                               |

|               | Pixel architecture analysis to understand the spike cause                         |

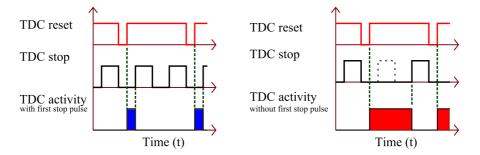

| 5.14          | Timing diagram: showing the spike cause with and without first stop               |

|               | pulse after TDC reset                                                             |

| 5.15          | Experimental results with SPAD on: Before and after removing first stop           |

|               | pulse after TDC reset                                                             |

|               | TDC reset instability                                                             |

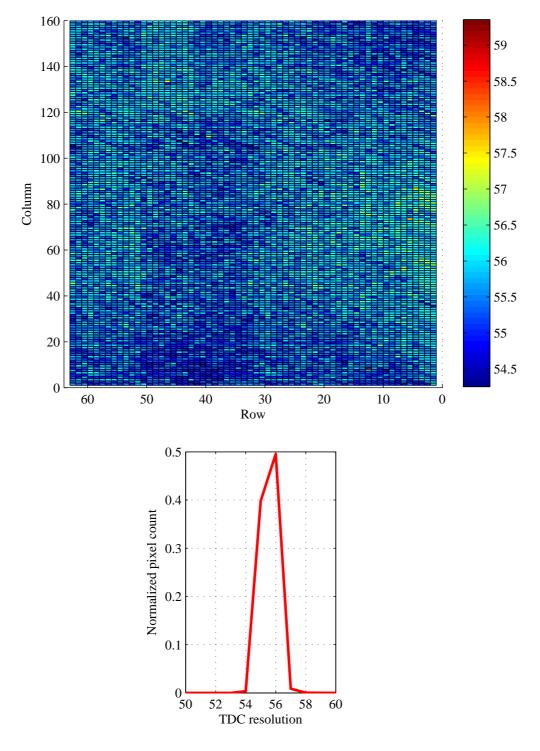

|               | Resolution distribution                                                           |

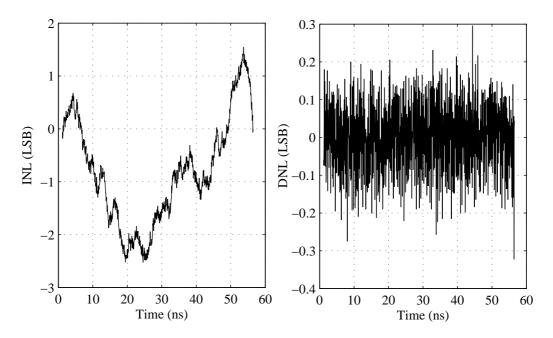

|               | INL and DNL                                                                       |

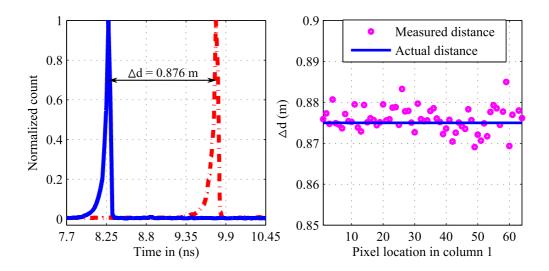

|               | TCSPC testing: Using distance meaurement                                          |

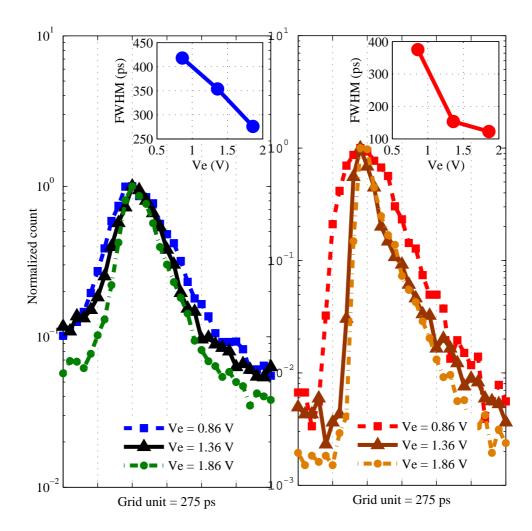

|               | Jitter measurement varying excess bias voltage $(V_e)$                            |

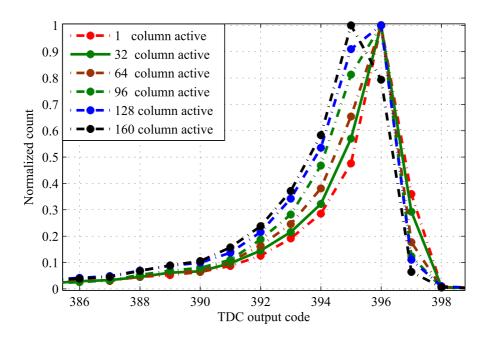

|               | Effect on optical spike with increasing number of active pixels                   |

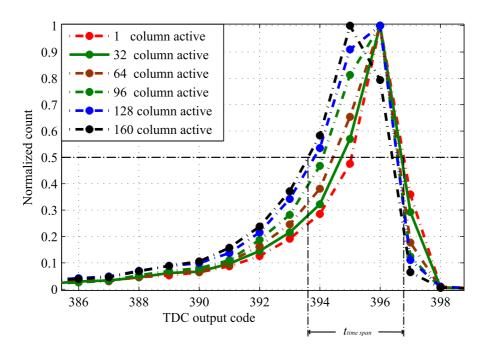

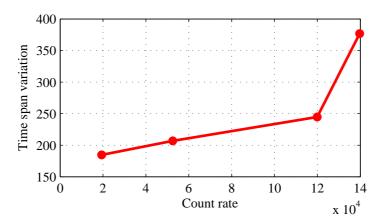

|               | TDC scaling time-span measurement technique                                       |

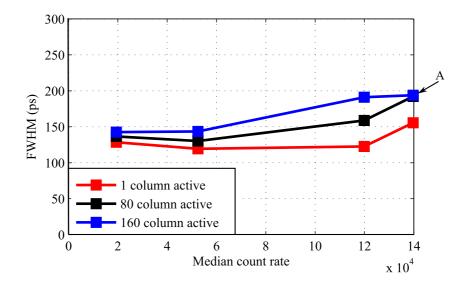

| 5.23          | TDC scaling jitter-optical spike location measurement technique: Jitter variation |

| 5 24          | TDC scaling jitter-optical spike location measurement technique: Opti-            |

| J. <u>2</u> 1 | cal spike location variation                                                      |

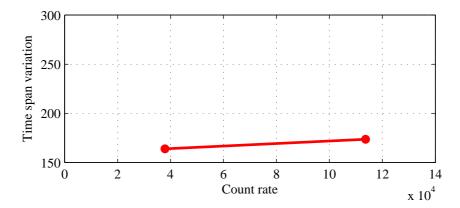

| 5 25          | Without PLL: Using TDC scaling time-span measurement technique                    |

|               | With PLL: Measurement result of one pixel with photon count rate being            |

| J. <u>2</u> U | 17 kHz                                                                            |

| 5 27          | With PLL: Using TDC scaling time-span measurement technique                       |

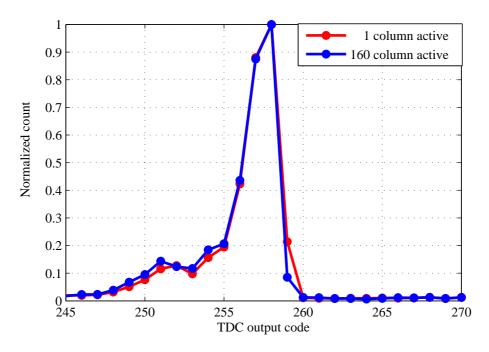

|               | Temporal position of the optical spike in terms of TDC output code                |

| J. <u>2</u> U | when the TDC resolution is about 90 ps                                            |

| 5.29          | FWHM distribution                                                                 |

|               | Pollen grain structure                                                            |

|               | Optical setup                                                                     |

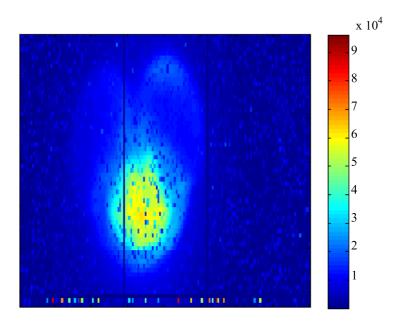

|               | Count rate                                                                        |

|               | FLIM: Bisaccate Pine pollen grain                                                 |

|               |                                                                                   |

# List of Tables

| 6.1 | MF128 Imager performance summary | 90 |

|-----|----------------------------------|----|

| A.1 | MF128: I2C Register Map          | 92 |

Introduction

#### 1.1 Motivation

Image sensors capable of resolving the time-of-arrival (TOA) of individual photons with high resolution are needed in several applications, such as Fluorescence lifetime imaging microscopy (FLIM), Forster resonance energy transfer (FRET), optical range finding, Positron emission tomography (PET) and Fluorescence correlation spectroscopy (FCS). For instance in fluorescence lifetime imaging microscopy application the lifetime of the fluorescent marker used to study a biological specimen is generally in the order of a few nanoseconds. However, due to fluorescence quenching, the observed lifetime in the fluorescence lifetime imaging application can drop down to less than 100 ps [1]. In FRET the observed fluorescence lifetime is generally in the range of 100 to 300 ps [1]. Hence, to resolve the fluorescence lifetime in these applications prompts the need for deep sub-nanosecond resolution in the instrument response function (IRF) of the overall optical system. This inturn requires new time-resolved image sensors with higher time resolution, increased throughput, and lower costs.

The general trend is to reach a picosecond time resolution with millions of measurements per second and an increasing image resolution. Photomultiplier tubes are capable of high time resolution over relatively large sensitive areas but lack imaging capability that is usually achieved via optical scanning. Multi-channel plates provide such capability but are still relatively bulky and costly. Solid-state avalanche photodiodes operated in Geiger mode, or single-photon avalanche diodes (SPADs), have existed for decades [2] and are increasingly adopted as a good compromise between cost and performance, especially after multi-pixel CMOS SPAD imagers have appeared [3, 4, 5].

As SPAD array sizes have grown, the on-chip readout bottle neck has also become evident leading to hybrid designs involving complex technological solutions [6] or more integration and more parallelism on-chip [7]. This trend has accelerated with the introduction of SPAD devices in deep-submicron CMOS [8] that have enabled the design of massively parallel arrays where the entire photon detection and TOA circuitry, is integrated on pixel [9, 10, 11]. This thesis revolves around one such imager also known as the *Megaframe 128* or *MF128*. The MF128 was developed in a project called as *Megaframe*, supported by the European Union within the Sixth Framework Program IST FET open.

The MF128 is one of the largest single-photon imager with 160x128 pixels capable of detecting the time-of-arrival of single photons with picosecond resolution; the chip was implemented in a 130nm CMOS technology. The pixel count in this imager is about twenty times larger than the state of the art in-pixel time-resolved imagers, proposed in [9, 10, 11]. Advantages in increasing pixel count come along with its own challenges. The major challenge that we anticipate in using the MF128 is the data generation rate.

For example the MF128 can generate about 1.28 GB/sec, while operating the imager at 50 kilo frames per second.

Further, since the MF128 being one of its kind ever realized to date with around 20,480 SPAD-TDC pixels, puts forth various interesting questions such as

- 1. What is the effect on the performance of the SPAD-TDC array on scaling?

- 2. What methodology can be used to analyze and study scaling?

- 3. And on what parameters does the scaling effect depend?

#### 1.2 Contribution

This thesis concentrates on developing a data acquisition system for the MF128 imager that can be used for various applications such as wide field fluorescence lifetime imaging, positron emission tomography etc. However, in this thesis the developed data acquisition system is utilized mainly to study and characterize the MF128 imager. Furthermore, based on the knowledge gathered on the chip architecture, various methodologies to test the imager were proposed, implemented and tested using the data acquisition system. Hence, the test functions developed during the course of this thesis can be scripted later to automate the testing process of the imager. Finally the developed data acquisition system is used to perform wide field fluorescence lifetime imaging, where a pine pollen grain is observed.

The main contributions of this thesis are:

- 1. Development of a flexible data acquisition system for the MF128 imager.

- Design and implementation of a column based event driven system to reduce the data rate for photon-starved applications.

- Development of a fast data acquisition technique to perform code intensity test on all the pixels simultaneously. By implementing time interleaved sampling on the data generated by noisy pixels.

- 2. Development of various test methodologies to test various basic modules of the imager, with the aim of automating the test process later.

- 3. Study on the performance degradation of the SPAD-TDC array with scaling was carried out, after formulating a study methodology.

- 4. Backend tool to generate FLIM images based on the raw data collected from the MF128 imager was also developed.

#### 1.3 Overview

The thesis is split in two parts. The first part describes the data acquisition system developed for the MF128 imager. The second part of the thesis presents the proposed test methodologies along with the testing and characterization results of the imager. Finally the results of the fluorescence lifetime imaging technique realized using the MF128 are presented.

The organization of the thesis is as follows: Chapter 2 elucidates the architecture of the MF128 imager. Where the internal design of the imager is analyzed using the top-down approach. Chapter 3 presents the architecture of the developed data acquisition system, explaining the various strategies used to optimize the data transfer rate.

Chapter 4 and Chapter 5 focus on the testing and characterization of the MF128 imager. Where Chapter 4 concentrates on the time-uncorrelated single photon counting (TUPC) mode and Chapter 5 focuses on the time-correlated single photon counting (TCSPC) mode. The test methodologies used to test and characterize the basic modules required for the TUPC mode is presented in Chapter 4. Further the characterization results of the imager in the TUPC mode are also presented. Chapter 5 discusses the test strategy used to test the TCSPC mode. Then it presents and explains the experimental results of the imager in TCSPC mode. Further, the fluorescence lifetime imaging technique realized using the developed data acquisition system is also presented in this chapter. Finally, Chapter 6 concludes the thesis, providing the summary of the results, along with the possible future directions.

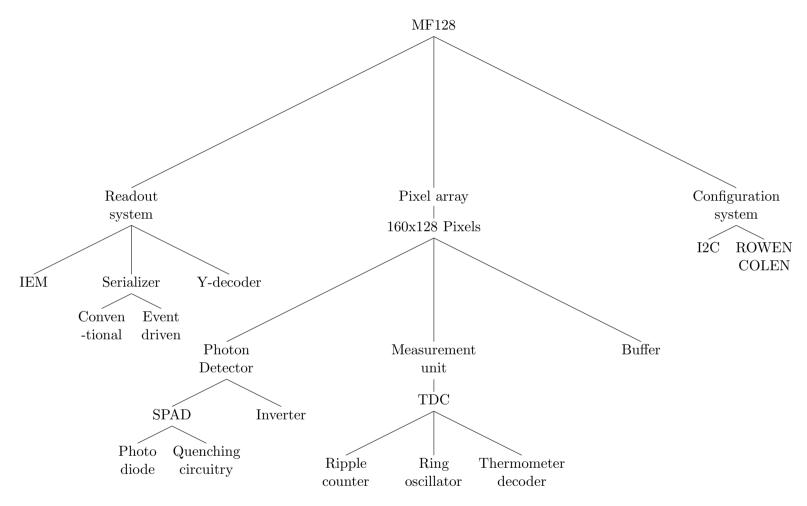

MF128 Architecture

The aim of this chapter is to elucidate the study made on the internal design of the MF128 chip. In this study, the chip is analyzed by breaking it down into smaller modules. Conventionally, the method of analyzing a big design by breaking it into smaller modules is known as the top-down approach. This method of analysis will provide the insight into the internal architecture of the chip.

The organization of the chapter is the following: first the overview of the MF128 chip architecture is briefed in Section 2.1. Followed by this, the MF128 chip is studied by categorizing the internal modules of the chip, based on their functionality in Section 2.2. Further, each category is analyzed by breaking it into various basic functional units as discussed in Section 2.3, Section 2.4 and Section 2.5. The summary of the chapter is presented in Section 2.6.

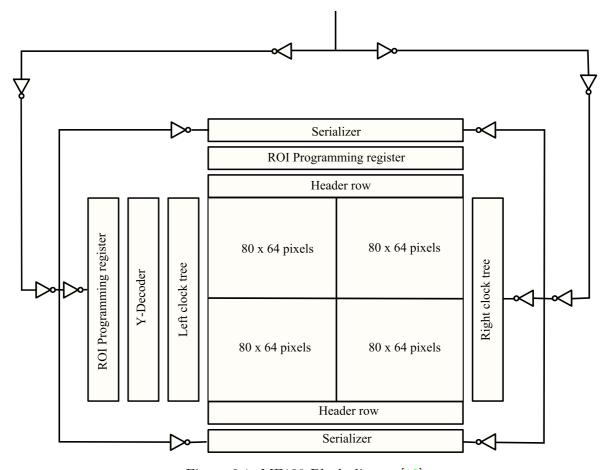

#### 2.1 Megaframe chip architecture overview

The MF128 chip is an image sensor with 160x128 pixels capable of measuring the time-of-arrival of single photons. To realize this functionality every pixel contains a single photon detector along with a time-of-arrival measurement unit. The block diagram of the imager is shown in Figure 2.1. The sensor is partitioned in four identical quadrants that are served by a balanced clock tree so as to minimize skews and ensure the fastest possible readout process. The ten bit data generated by every pixel is sent out serially using two independent serializers for every column. The region of interest (ROI) is programmable via vertical and horizontal registers that select a section of the pixel array that needs to be active. In addition to 128 rows of pixels, the MF128 has two additional header rows near the serializer. These header pixels were introduced to increase the readability of the generated data. The pixels in the header row are capable of generating ten bit data, with seven bits representing the frame count. The frame count is monitored in every header pixel using a seven bit counter.

The MF128 image sensor is designed to work in two different modes of operation, one the Time Uncorrelated Photon Counting (TUPC) mode or the intensity mode and second the Time-Correlated Single Photon Counting (TCSPC) mode. In the time-uncorrelated mode the sensor counts the number of photons arrived in a period of time. Whereas in the time-correlated mode the time-of-arrival of every detected photon is measured, with respect to a time reference. All configurations and control of the state of the chip are carried out using an I2C module.

Figure 2.1: MF128 Block digram [12]

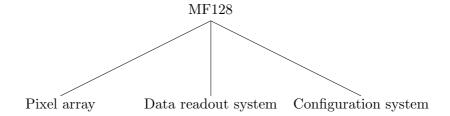

#### 2.2 Categorization of internal modules

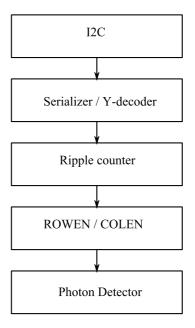

To realize an imager as defined in Section 2.1, the chip contains various modules. These modules can be classified into three categories based on their functionality, namely: a pixel array, a data readout system and the configuration system.

Figure 2.2: Categorization of internal modules

The functionality of each of the category is identified as follows:

1. Pixel array: The functionality of the pixel array is to detect and measure the time of arrival/intensity of the detected photon(s).

- 2. Data readout system: The readout system is used to read and communicate the measured data, from the pixel array to the interface circuitry located outside the chip.

- 3. Configuration system: The configuration system facilitates the user to configure and control the operating mode/conditions of the pixel array/readout system.

The three categories introduced in this section are elaborated in Section 2.3, Section 2.4 and Section 2.5 respectively.

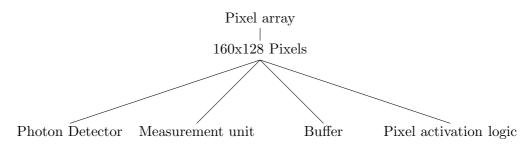

#### 2.3 Pixel array

The MF128 chip contains an array of 160x128 pixels (160 columns and 128 rows). Where, every pixel in the array is designed to detect and measure the photon arrival time/photon intensity, irrespective of other pixels. Since the functionality of every pixel is identical and independent of the other pixels, it is possible to define the architecture of one pixel and then extend it to the whole array. Therefore in this section the internal design of a single pixel is explained in detail.

#### Pixel Architecture

In the MF128 chip every pixel is designed to have its own photon detector, measurement unit and a 10 bit buffer. In addition to the detector and a measurement unit, every pixel incorporates circuitry that can facilitate the testability and the pixel activation/deactivation.

Figure 2.3: Pixel contents

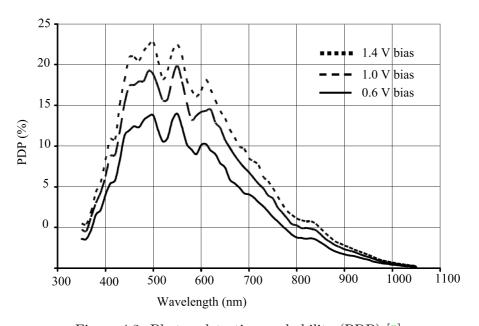

#### 2.3.1 The Photon detector

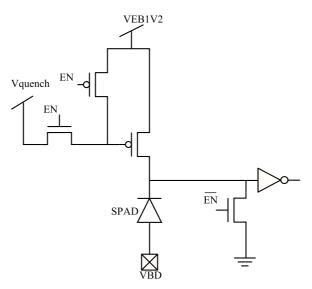

The detector implemented in the Megaframe chip is a single-photon detector called as Single Photon Avalanche Diode (SPAD). The design and implementation of the SPAD proposed by C. Niclass et al [13], M. Gersbach et al [14] and J.Richardson et al [8] for 130 nm CMOS technology is used in the megaframe MF128 chip.

#### SPAD

The SPAD is a PN junction photo diode, reverse biased above the breakdown voltage. In this mode of operation called as the geiger mode, a photo electron created in the depletion region might create an avalanche by impact ionization [15]. The high current resulting from the avalanche signifies the arrival of a photon. However, the avalanche current needs to be quenched, to avoid a thermal breakdown in the diode. To quench the avalanche two types of techniques [16] viz. active quenching and passive quenching are discussed in the literature. Of these two techniques the passive quenching technique [8] is used in the MF128 chip.

#### Quenching circuitry

In the MF128 chip a transistor, biased to act as a current source, is added in series to the SPAD. In this configuration, the current resulting from the avalanche increases the voltage drop across the transistor. This in turn reduces the voltage across the SPAD. As the bias voltage across the SPAD reduces to near breakdown voltage, the avalanche gets quenched [15]. After the avalanche gets quenched, the associated junction capacitance of the SPAD recharges to its original working condition through the quenching resistor. The total time required to quench and recharge the SPAD back to its working condition is called as the dead time of the SPAD.

During the avalanche and in the process of quenching and recharge, a voltage pulse is developed across the quenching resistor. This voltage pulse is used in the MF128 to detect the arrival of a photon. To map this voltage pulse to the conventional CMOS domain for further processing, an inverter is added.

Figure 2.4: Photon detector or SPAD ensemble [12]

Figure 2.4 shows the passive quenching circuitry implemented in MF128 along with the SPAD. The pixel implemented in the MF128 chip offers the flexibility to vary the bias conditions of the SPAD.

The options available to the user to vary the SPADs bias conditions are:

- 1. Voltage across the SPAD  $(V_{op})$  can be varied by changing  $V_{bd}$ .

- 2. Quenching current value can be adjusted by varying Vquench.

- 3. SPAD can be activated/deactivated by toggling the enable (EN) signal.

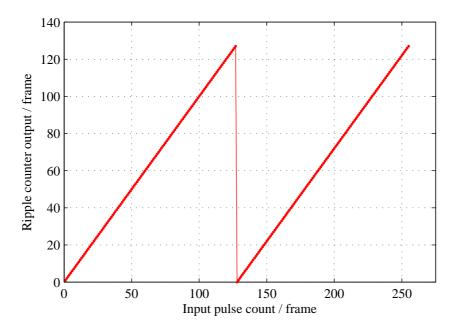

#### 2.3.2 Measurement unit

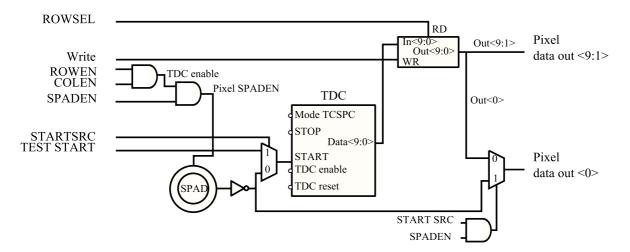

The SPAD along with its quenching circuitry detects the arrival of a photon. For every detected photon, the detector generates a voltage pulse. This voltage pulse is used by the measurement unit, to measure the photon arrival time/ photon count. In the MF128 chip, the photon counting feature is incorporated into the time of arrival measurement module. The time-of-arrival measurement module is a time-to-digital converter (TDC). Because this module generates a digital code, that is proportional to the time difference between two signals viz., the START and the STOP signal. Where the START signal comes from the photon detector and the STOP signal comes from a reference clock. The researchers involved in designing the Megaframe chip designed three different TDC designs [10, 11, 9]. Of these three designs, in the MF128 chip the design proposed by Justin Richardson et al [10] is implemented. This design is briefed in the next paragraph.

#### Ring oscillator based TDC

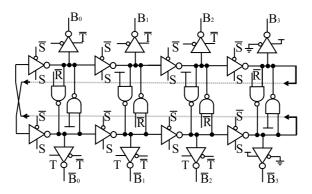

The TDC used in the MF128 chip is based on a ring oscillator with fast start-up as shown in Figure 2.5. The ring oscillator gets activated whenever the START signal transits to a high state. And remains activated till the STOP signal goes high. The activated oscillator generates clock cycles via B3,  $\overline{B3}$ , which is then counted using a seven bit ripple-counter. The output of the seven bit ripple counter serves as a seven most-significant-bits of the measurement. The three least-significant-bits of the measurement are provided by the eight intermediate state of the ring oscillator. The intermediate states of the ring oscillator are latched using the control signal T and converted to a three bit binary code (D0:D2) using a thermometer decoder as shown in Figure 2.6. The stop signal  $S, \overline{S}$  is used to freeze the ring oscillator, while the rising edge of R resets the TDC. In TUPC mode the seven bit ripple counter is also used to count the detected photons.

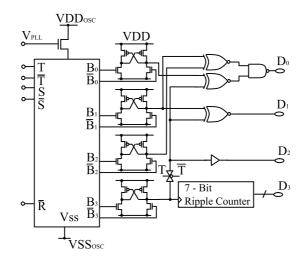

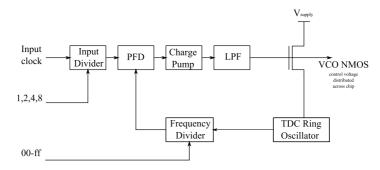

#### Process Voltage and Temperature (PVT) compensation [10]

To reduce the jitter introduced by the supply voltage variations, a differential inverter with a NMOS based supply regulation is used as a delay element in the ring oscillator. The NMOS based supply regulation forms a part of the Process Voltage and Temperature (PVT) variations control loop. The PVT variations control loop is a closed loop calibration system implemented outside the pixel array, using the PLL architecture as shown in Figure 2.7. This calibration system is designed to lock the ring oscillator's output to a stable input clock, using a PLL. It is to be noted that the ring oscillator used in the PLL is identical to the ring oscillator implemented inside the TDC. The VCO voltage generated by the locked-in PLL loop is used to control the supply voltage of the ring oscillators in the TDC.

Figure 2.5: Ring oscillator schematic

Figure 2.6: TDC schematic

Figure 2.7: Process Voltage Temperature (PVT) variation control loop [10]

#### **2.3.3** Buffer

Every pixel in the chip has a ten bit memory to store the measured data. The stored data is then communicated to the readout system.

#### 2.3.4 Pixel enable / disable logic

The pixel activation logic in MF128 is designed to act in two levels. In the first level it is possible to activate the measurement unit alone. In the second level the whole pixel including the detector and the measurement unit can be activated.

The activation/deactivation logic depends on three signals viz., the ROW enable, the COLUMN enable and the global SPAD enable signal. Where the ROW enable and COLUMN enable signal comes from an on chip register that can be programmed by the user. And the global SPAD enable signal is provided by the user from outside the chip.

In the first level, the measurement unit is activated using the ROW enable and the COLUMN enable signal. Then in the second level, the entire pixel is activated using the global SPAD enable signal along with the ROW enable and COLUMN enable signal.

Figure 2.8: Pixel enable logic [12]

The implemented pixel activation/deactivation logic is shown in Figure 2.8.

#### 2.3.5 Design for testability

To facilitate testability, every pixel contains two MUXs. One MUX is used to select an input to the TDC, while the other MUX is used to select a source for the pixel's output. The input to the TDC can either be from a photon detector or the TEST start signal that can be controlled externally by the user. The least significant bit in the pixels output can be controlled either directly by the photon detector output or by the LSB of the TDC. The select signals for the two MUXs are controlled using a user programmable register. Using the TEST start signal it is plausible to test the TDC by providing a known start signal. Whereas by monitoring the photon detector output it is possible to test the photon detector. Hence by using these two MUXs the photon detector and the TDC can be tested separately.

The overall pixel architecture with the entire set of control signals is shown in Figure 2.9

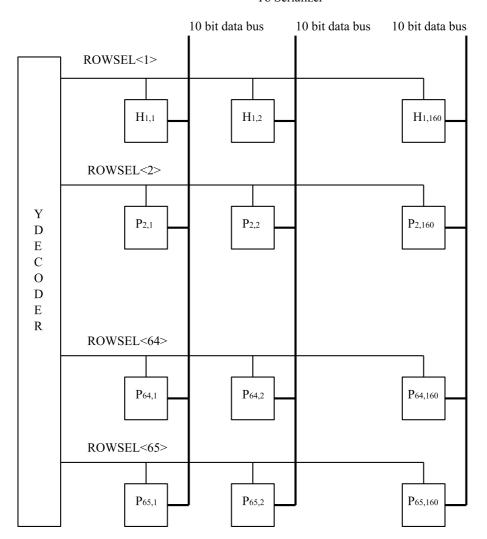

#### 2.4 Readout system

The readout system in the megaframe chip is designed to collect and transfer the data, from the pixel to the circuitry located outside the chip. It is worth mentioning here, that every pixel in the MF128 chip generates 10 bits at a frame rate of one megahertz. The megaframe chip which contains 160x128 pixels including the header pixels will then generate 160x128x10 bits for every micro second. To handle this large amount of data, a robust readout system is required.

Figure 2.9: Pixel Architecture [12]

The readout system of the Megaframe chip is split into two identical halves, where each half of the readout system is responsible for the readout of one half of the pixels i.e. 160x64 pixels. These 160x64 pixels are organized into 160 columns and 64 rows. The output of every pixel in a column is connected to a common data bus. The serializer also connected to the data bus reads the 10 bit data from the data bus and converts it into a serial data. This serial data is finally transferred to the circuitry located outside the chip.

To facilitate the sharing of the data bus between the pixels in a column, a Y-decoder is implemented. The Y-decoder time multiplex's the data bus between the various pixels of a column. The time multiplexing is implemented, such that the row readout happens sequentially in a rolling shutter mode. The ROWSEL signal generated by the Y-decoder is used to read a particular pixel row as shown in Figure 2.10.

To synchronize the data readout, the Y decoder and the serializer uses three different clocks namely the data clock, the line clock and the frame clock. The data clock is used by the serializer to transfer the data serially. The line clock instructs the Y-decoder and serializer to read the next row. The frame clock instructs the Y-decoder that the frame readout is over. Since the data generated by every pixel is 10 bits, line clock is 10 times the data clock and the frame clock needs to be 65 times the line clock when all the rows are active.

#### 2.4.1 Data compression technique

As mentioned earlier, the data generation rate in MF128 is very high. So to reduce the data transfer rate from MF128, two compression techniques are implemented on chip. The first technique is based on the IEM algorithm [17] and the second is an event-driven serializer that exploits the scarcity of the data in a frame. Since the on chip data compression techniques are not explored in this thesis, it is not explained in detail here. However, the detailed explanation of the same can be found in [12].

#### To Serializer

Figure 2.10: Simplified readout system

#### 2.5 System configuration module

The pixel array and the readout system are designed such that it can be configured to work in various modes of operations. The configuration and control feasibilities available on chip are made visible to the user through a set of configuration registers. The configuration registers available on chip are designed to be programmed either using the inter integrated circuits (I2C) protocol or the serial interface.

#### 2.5.1 I2C

The Megaframe chip contains a group of registers that can be configured using the I2C protocol [18]. To facilitate the communication a I2C slave module is implemented in the megaframe chip. In general the registers that are visible through the I2C communication are responsible to configure various modules. A tabulation listing various registers

along with its address and functionality is re-produced from [12] in Appendix A.

#### 2.5.2 ROWEN/COLEN

In MF128, pixels in the region of interest can be activated using two registers viz. ROWEN and COLEN. The ROWEN and COLEN are two shift registers, each of width 130 and 160 bits respectively, where every bit in the ROWEN and COLEN register corresponds to a row and a column in the pixel array. Hence a specific pixel can be activated by configuring its corresponding row and column bit in the ROWEN and COLEN register. The ROWEN and COLEN registers are designed to be configured serially by the user.

#### 2.6 Summary

- MF128 is designed to work in two modes of operation viz. time-uncorrelated and time-correlated single photon counting.

- Internal modules of the MF128 are categorized into three categories viz. pixel array, readout system and a configuration system.

- Pixel array contains 160x128 pixels. Where every pixel contains a photon detector and a TDC.

- Readout system is made up of two serializers and a Y-decoder.

- Configuration system contains a set of registers programmable either using a I2C protocol or serial communication.

- Additionally data compression techniques such as IEM and event driven serializer are implemented in MF128.

The top down approach followed in this chapter to analyze the MF128 imager is summarized pictorially in Figure 2.11.

Figure 2.11: MF128 architecture summary

Data acquisition system

The goal of this chapter is to present the design of the data acquisition system developed for the MF128 imager. The MF128 is a time resolved imager, with 160x128 pixels capable of working in two different operating modes, namely the Time Un-correlated Photon Counting (TUPC) mode and Time Correlated Single Photon Counting (TCSPC) mode. Chapter 2 categorized the internal module of the imager into three categories namely the pixel array, readout system and the configuration system. Even though the pixel array forms the core of the imager, the configuration system and the readout system provide the user with the access to operate the chip. Hence in this chapter the configuration and readout system are analyzed to derive the specifications for the data acquisition system to control, configure and acquire data from the imager. Later the derived specifications are used to design a data acquisition system.

Organization of the chapter is as follows: In Section 3.1 the MF128 architecture is analyzed to obtain the specification for the data acquisition system. The derived specification where then used to analyze the available data acquisition system in Section 3.2. In Section 3.3 the hardware set-up realized for the MF128 is presented. Extending the discussion on the hardware setup, an overview of the developed data acquisition system is presented in Section 3.4. Following the overview a detailed design of the system is explained in Section 3.5 and Section 3.6. Further, three application specific data compression techniques are presented in Section 3.7. Finally, the chapter is summarized in Section 3.8.

#### 3.1 Specification

#### 3.1.1 Light source insensitivity

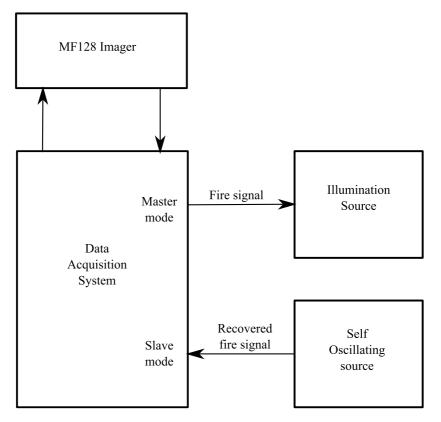

The MF128 imager can be operated with a variety of light sources, including high performance lasers (such as femtosecond lasers of the type Mira and MaiTai) and cheaper laser diodes. To accommodate the differing properties of these devices, a number of clocking options must be provided. Specifically, it should be possible to operate in a master mode, where the data acquisition system drives a pulse train into the illumination source, and a slave mode, where the output of a self-oscillating source is optically captured and used as the reference for the various system clocks. Figure 3.1 provides a simplified illustration of this configuration.

#### 3.1.2 Requirements to communicate with the MF128 imager

As stated earlier, the data acquisition system is required to control, configure and acquire the data from the imager. Hence to design such a system, first it is important to understand the communication protocol the MF128 imager uses to communicate

Figure 3.1: Light source control: Master/Slave mode

with the outside world. This information can be extracted from the Chapter 2 on the MF128 architecture.

The signal lines required to communicate with the MF128 imager can be classified into three categories, namely:

- 1. Control signals

- 2. Chip configuration signals

- 3. Data readout signals

#### The control signals

In MF128 five signals can be classified in this category, viz. the SPAD enable, TDC reset, write signal, TEST start and the external STOP. All these five signals are global signals routed to all the pixels in the array.

- SPAD enable: The SPAD enable signal is used to enable or disable the SPAD.

- *TDC reset:* The TDC reset signal is used to reset the measurement unit. Hence, this signal needs to be activated at the start of every frame, to reset the data measured in the previous frame.

- Write: This signal is used to write the measurement unit output on to a 10-bit buffer present inside every pixel, which is then used by the readout system. Therefore, this signal needs to be activated just before the end of every frame. Hence, the light exposure duration for every frame in MF128 imagers is defined as the time interval between the TDC reset and write signal.

- TEST start: As mentioned in Chapter 2, the TEST start can be used to test the measurement unit. Since this signal can be controlled directly from outside, it does not need to follow any specific protocol. Therefore, depending on the test vector this signal can be modified accordingly.

- External STOP: External STOP signal can be used either to provide the STOP signal for the measurement unit during its testing phase or when it is required to excite a light source i.e. while operating the light source as a slave to the data acquisition system.

#### Chip configuration signals:

As stated in Chapter 2, the MF128 imager contains two modules to facilitate the chip configuration. These two modules are I2C and ROWEN/COLEN.

- I2C: The I2C slave module in MF128 uses the I2C protocol for communication. Hence an I2C master module is required to establish the communication with the I2C slave implemented on-chip. In general I2C protocol requires two signals namely the SDA and SCL. Where the SDA is the data line and SCL is the clock line signifying the data communication. It should be noted that this module is designed to operate at 400 kHz. The detailed description of the I2C protocol can be found in [18].

- ROWEN/COLEN: The configuration register present in this module uses a serial communication. Hence each of these registers requires two signal lines namely, the data and the clock.

#### Data readout signals:

The data readout system implemented in the MF128 imager requires three signals, namely the data clock, line clock and the frame clock.

- Data clock: Data clock is used by the serializers on-chip to communicate the data. Hence the frequency of the data-clock determines the data rate from the imager.

- Line clock: Line clock is used to request the imager to send the next row of data. Therefore to ensure reliable data transfer the time period of the line clock needs to be at-least n times the data clock time period. Where n is the number of data bits per pixel. In MF128 while using the conventional serializer n is equal to 10 bits.

- Frame clock: Frame clock is used to signify the end of frame readout. Hence the time period of this clock needs to be at-least active row times the line clock time period.

Hence to ensure reliable data transfer from the imager, the signals presented in this section should follow the timing requirements presented in Figure 3.2.

Figure 3.2: Data acquisition system: Timing diagram

However by generating signals as specified in Figure 3.2 will ensure a reliable data transfer from the imager, but it is equally important to ensure that the data is collected in the data acquisition system reliably as well. Hence to ensure a reliable communication, the data generated by the serializer needs to be sampled in the data acquisition system, at the same frequency as the data clock. Since the propagation delay introduced by the PCB is not known beforehand, it is required to have flexibility to vary the phase relation between the data clock and data sampling clock during the testing phase.

Since the MF128 can operate in various modes of operation and also depending on the configuration, the readout data rate can vary in wide range. Hence to control, configure and read data from the MF128 imager in real time, it is required to have a flexible data acquisition system.

## 3.2 Analysis on the earlier version of the imager

Before designing a data acquisition system for the MF128 imager, a study was carried out on the earlier version of the MF128 imager also called as the MF32. From the study it was found that the MF32 is a 32x32 on-pixel time resolved imager, following a similar architecture as MF128. The study revealed that the MF32 imager also has an I2C module, similar but a scaled down version of the MF128 readout system and a same set of control signals. However the difference between the two imagers is that the MF128 has 160x128 pixels, whereas the MF32 has 32x32 pixels. Further, the functionality of the I2C configuration register of MF32 is different from MF128. For example, in MF32 pixels in the region-of-interest (ROI) were enabled using the register available in I2C, on the other hand the MF128 uses a separate module also called ROWEN/COLEN to activate the pixels in ROI. Furthermore, the MF128 has on-chip compression techniques such as IEM and event-driven serializer, in contrast to MF32.

Since the I2C communication, control signals and the data readout signals are identical in MF128 and MF32, and also because the MF32 data acquisition system is designed to provide the required flexibilities to control, configure and read data from the imager,

it was decided that upgrading the MF32s data acquisition system to the MF128 would be the right choice. Rather than developing the whole new system for the MF128.

## 3.3 Hardware setup

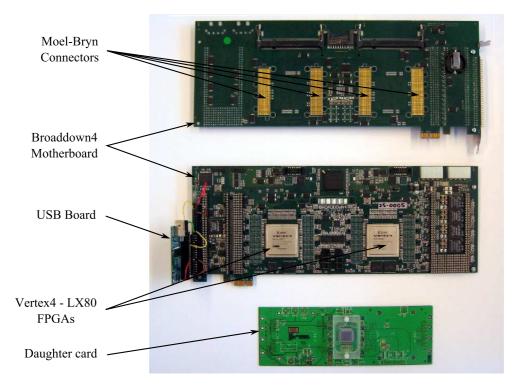

The hardware platform used to develop the data acquisition system is shown in Figure 3.3. It is based on a Broaddown4 board [19] from Enterpoint featuring a dual Virtex-4 FPGA and fast communication modules.

Figure 3.3: Hardware setup

The MF128 sensor is mounted on a daughter card in chip-on-board style, while a USB link is implemented as an add-on module, is also visible in Figure 3.3. The dual Virtex-4 FPGA acts as a mother board controlling the daughter card with MF128 sensor.

Four Moel-Bryn connectors have been used to connect the motherboard with the daughterboard. Considering the number of available pins in the motherboard, daughterboard is designed such that control signals and one half of the columns are connected to one FPGA and the other half is connected to the other FPGA.

## 3.4 Data acquisition system top-level design

The data acquisition system developed for the MF128 is divided in two parts viz. the firmware and the software. The firmware is used to control the MF128 and the software is used to control the firmware based on the user commands. Hence, the firmware is

realized in the field programmable gate array (FPGA) and the software is realized using the Visual C++ programming language. The communication between computer and FPGA is established using a USB interface. The top-level architecture of the developed data acquisition system for the MF128 imager using the MF32 design as it backbone, is briefed in this section.

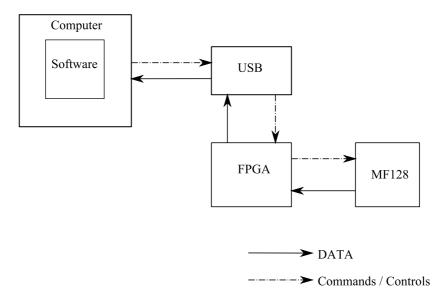

#### Data acquisition system overview

To satisfy the requirements stated in Section 3.1, the data flow between the software, firmware and the MF128 chip is established as shown in Figure 3.4. The software receives the commands from the user, on how to control the chip. These commands are then carried over to FPGA through the USB interface. The firmware loaded in the FPGA decodes these commands to generate the control/configuration signals. Further the data collected from the MF128 in the FPGA, is transferred to the computer on-request through the USB interface.

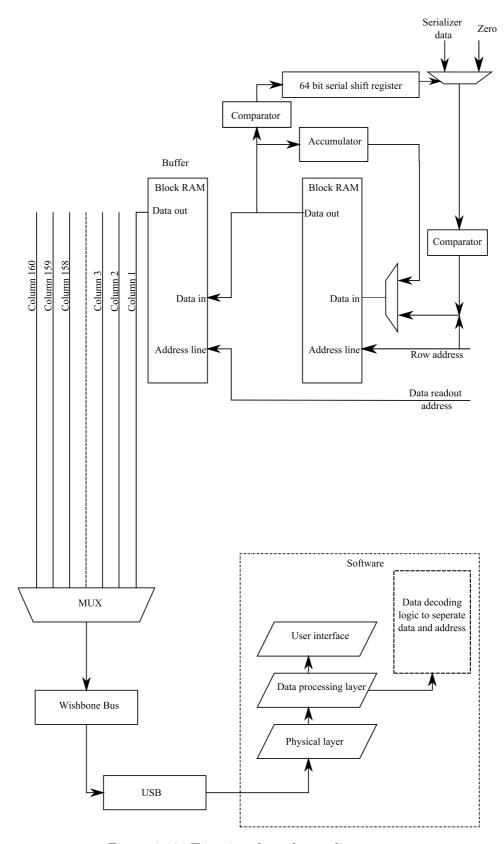

Figure 3.4: Data acquisition system overview

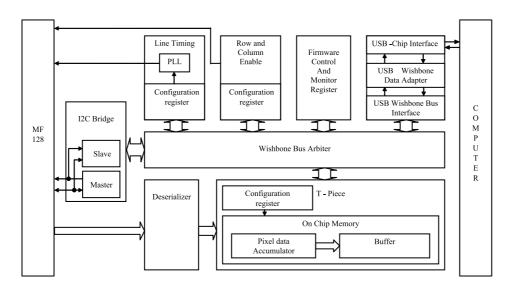

#### 3.4.1 Firmware Architecture

The MF128 chip communicates with different interfaces and standards. Various modules with different functionalities were designed on FPGA to communicate and monitor the MF128 chip. These modules are connected using the Wishbone Bus interface [20] as shown in Figure 3.5. As all of these module need to be controlled by the user through software. The USB interface that comes under the direct control of the user acts as a master.

To facilitate the flexibility in controlling the MF128s functionality from the software, the design of every slave module connected to the wishbone bus is partitioned into two parts viz. the wishbone bus interface and the functional unit. The wishbone bus interface contains a set of programmable registers that can be configured from

the software. These registers are in-turn designed to generate control signals to the functional unit. Hence, by controlling the functionality of the functional unit it is possible to control the MF128 imager as required by the user through the software.

#### The main modules are the following:

- Deservative: It is the module used to treat the data flowing from the MF128 chip and to reorganize them in a fashion that is compatible to display and further processing.

- *T-Piece*: It is the module that collects data from the serializer and packetizes it to transfer the data to the computer. This module also implements data compression techniques to reduce the data transfer rate from the FPGA to computer.

- *I2C bridge:* It is the module that programs the on-chip I2C so as to configure the chip.

- Control generator module: It is the module that generates the control signals used to control other modules and also to monitor for errors in other modules.

- *USB communication module* It is the module that enables the communication between the FPGA and the PC workstation.

Figure 3.5: Firmware Architecture

The Block diagram representing of the firmware design for the data acquisition system is shown in Figure 3.5. The detailed explanation for each of these modules is presented in Section 3.5.

# 3.4.2 Established communication protocol between the firmware and software

The main functionality of the software is to receive commands from the user and send it across to the firmware loaded in the FPGA. In addition it is also designed to collect

the data from the MF128 through the FPGA. Hence, the communication between the firmware and software can be divided into two parts, namely the upstream communication and the downstream communication. Since the data acquisition system is designed such that the software acts as a master to the firmware, the upstream communication is always preceded by the downstream communication. Hence, to initiate a data transfer from FPGA to computer, a command needs to be sent from the software to the firmware.

#### Downstream communication

The software initiates the data transfer either upstream or downstream, by sending three words of width 32 bit length each. These three words represent the command, address and data. The command represents whether the software wants to read, write, abort or acknowledge. Address represents the address of the slave and the register, where the data needs to written in the slave. Hence by transferring three words it is possible to write data into the FPGA, provided the instruction in the command word corresponds to a write operation.

#### Upstream communication

As stated earlier the upstream communication is initiated by a downstream communication of sending three words as described earlier. On receiving a read command from the software, the firmware sends a header packet, along with the packet size it wishes to send. The software responds to the header packet with an acknowledgement. Then the firmware starts streaming the data.

## 3.5 Firmware design

A brief overview of the firmware design was presented in Section 3.4. This section will explain in detail the functionalities of the various modules.

#### 3.5.1 USB communication

USB communication plays a vital role in creating a high-speed communication from the software to the FPGA and vice-versa. Since the motherboard is not provided with an on-board USB communication module. An ad-hoc USB communication board is required, which can convert the data coming from FPGA to the USB standards. From the market study, it was found that USB interface board offered by ELRASOFT [21] matched all the requirements and also more importantly it uses the same USB communication chip from Cypress [22] as used in MF32 mother board. This particular feature of the board will allow us to use most of the USB interface modules designed for the MF32. One major change required when compared to MF32 is that, in MF32 the USB communication is used by the PC to program the FPGA, as well as to control the loaded firmware. Whereas in the MF128 motherboard board, there is a separate JTAG connector specially meant for the FPGA configuration. Hence, the USB communication is required only to control the loaded firmware. To satisfy the above stated requirements a new configuration file for USB chip was designed.

#### USB interface module

The USB interface module in the firmware is designed to provide the physical interface between FPGA and USB chip. To match the timing requirements put forth by the USB chip. It was decided to use the 48 MHz clock generated by USB chip rather than using the clock generated by FPGA itself, this module is also responsible for generating the required control signals and presenting the data to the USB chip.

The USB communication chip from Cypress used in the data acquisition system require the data to be transferred in packets of 16 bits. Since the implemented wishbone bus architecture is 32 bit wide. The USB interface takes up the responsibility of combining the two 16 bit word into one 32 bit word during the downstream communication i.e. from PC to FPGA, and also it is responsible to de-packetize the 32 bit data coming from the wishbone bus into two 16 bit word during the upstream communication i.e. from the FPGA to PC.

#### USB Wishbone adapter module

The USB Wishbone adapter module monitors for the incoming data. As stated earlier the software initiates the data transfer with a packet containing three words representing command, address and data. The USB wishbone bus adapter decodes this packet and uses the command information to either block the upstream or downstream USB communication depending upon the command. Further this module is responsible to transfer the data reliably from the USB clock domain (48 MHz) to FPGA clock domain (32 MHz).

#### USB Wishbone BUS interface module

The USB Wishbone BUS interface module acts as a master on the BUS. Further, it is responsible for communicating the data to other module as per the Wishbone Bus standards. This module receives the configuration data stream from the software through the USB Wishbone adapter. The configuration data received from the software can be a data that needs to be written to a specific module connected to the bus or a request to read data from a module. Depending upon whether it is write or read, request the state machine designed inside the module will request the arbiter for an access to communicate with the required module.

Every slave module connected to the wishbone bus is designed such that it has a wishbone bus interface and a set of register that can be configured from the software using the wishbone bus.

#### 3.5.2 Line timing

The Line timing module acts as a slave in the wishbone bus. This module is designed to generate signals such as line clock, data clock, frame clock, TDC reset, write, SPADEN, TEST start and the external stop signal.

This module uses the PLL available in FPGA to generate data clock. Then the generated data clock is used as a base clock to generate other signals. Further, this module not only generates clock and control signal to control the MF128, but also it

generates clocks for other modules in the firmware, such as DATA sample clock used in deserializer unit.

#### 3.5.3 I2C

The I2C module acts as a slave in the Wishbone Bus. The main purpose of this module is to act as a master in I2C bus to communicate with I2C slave module that is on MF128 chip. As shown in Figure 3.5, the FPGA firmware is designed to contain both, I2C bus master and slave. This replication is made for two purposes, one to ease the testing process for I2C communication between firmware and software. Two, at runtime data that is sent to I2C slave in MF128 is also send to the on chip I2C slave module. This allows us to monitor the configuration file loaded into the chip, and also to use the configuration data for other modules in the firmware.

#### 3.5.4 ROWEN/COLEN

The ROWEN/COLEN module is used to transfer ROW enable and COLUMN enable data serially to the MF128 chip. This module receives the data from the software through the wishbone bus and then uses serial shift register to transfer the data to the MF128 imager. The design is made such that the ROWEN and COLEN registers can be programmed in parallel.

#### 3.5.5 Data pipeline path

The Data pipeline path is used to read the data generated by the MF128. It consists of two units, de-serializer and a T-Piece.

#### De-serializer

The De-serializer is designed to convert the serial data generated by the MF128 into a data word of 10 bits. This module also tags the 10 bit data with the ROW number, frame count and the operational mode of the MF128 chip. These tags are used by the downstream blocks to collect and align the data for a particular pixel. Each serializer in the MF128 is assigned with a separate describing in the FPGA.

## T-piece

The main purpose of the T-piece is to collect the data from the deserializer and send it across to the computer. Hence this module contains a buffer that is be used to collect the data from the deserializer. Design is made such that the every pixel in the MF128 has its own 16-bit buffer. In FPGA these buffers were mapped to the block RAM available inside the FPGA. However it should be noted that the design presented in this section, is a very basic design that be adapted to all mode of operation. The problem with this approach is that the data generated by the MF128 is about 1.28 GB/sec, but the achieved USB communication speed with the current hardware setup is about 20 MB/sec. Hence due to the communication bottleneck most of the data generated by the MF128 is lost. However to reduce the impact of the communication bottleneck, three different techniques implemented in this thesis is presented in Section 3.7.

#### 3.6 Software

#### Various abstraction levels

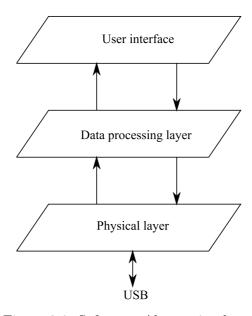

The main objective of the software is to communicate the users instructions to the firmware. Hence, it is designed to establish a two way communication between the software and the firmware. To realize these functionalities, the software is designed in three levels of abstraction namely:

- 1. Physical layer

- 2. Data processing layer

- 3. User interface

Figure 3.6: Software: Abstraction layer

- Physical layer: The physical layer uses the LibUSB library and creates a physical communication between the software and the USB interface chip. Hence this layer hides the USB communication interface from the other layers.

- Data processing layer: The data processing layer is designed to generate packets based on the instructions received from the user interface. In this layer the packets are generated to satisfy the requirements presented in Section 3.4. Further, the generated packet is transmitted to the firmware through the physical layer. Additionally, this layer is responsible to decode the data packet received from the firmware to be displayed in the user interface.

- User Interface: A graphical user interface (GUI) was created to receive commands and display the information received from the data processing layer. The command received from the GUI is communicated to the data processing layer to generate data packets for the firmware.

# 3.7 Application specific data-throughput optimization techniques

In Section 3.5 a generalized design for the T-Piece module is presented. The drawback with this design is that it is requires every collected frame to be transferred to the computer. As stated in Section 3.5, the difference in data generation rate (1.28 GB/sec at 50 kcps) and data transfer rate (20 MB/sec) prohibits the transfer of every generated frame of data to the computer. Hence, in this technique around 64 frames of data is lost for every frame of data collected. This corresponds to around 98.43% of the generated data is lost due to the communication bottleneck. Hence a better technique is required to reduce the data loss. This section explains three techniques implemented in this thesis to reduce the impact of the data communication protocol. However it is critical to understand that these three techniques are application specific.

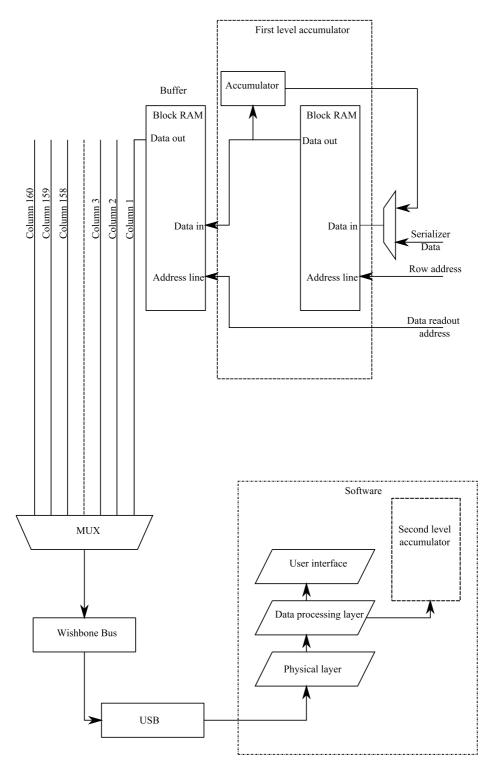

#### 3.7.1 Data accumulators for TUPC mode

In time un-correlated single photon counting mode, during the characterization phase for example to measure the dark count rate [23] (DCR), it is important to accumulate numerous frames of data to obtain a statistically reasonable result. Also in photon starved applications for example in fluorescence life time imaging microscopy (FLIM) to obtain an intensity image, it is required to accumulate frames of data.

To accommodate such applications, in the developed data acquisition system two levels of accumulators are incorporated for every pixel. In the first level an accumulator is realized in the firmware and in the second level another accumulator is realized in the software. The first level accumulator realized in the firmware is designed using a 16 bit memory mapped to a block RAM available in the FPGA. This 16 bit memory is used to store the accumulated value. Since the MF128 generates 7-bits of valid data in TUPC mode, using 16 bit memory will allow us to accumulate 512 frames of data. To obtain a statistically reasonable result, for most of the applications it is required to accumulate thousands of data frame. To accommodate this requirement a second level of accumulator is incorporated in the software. Hence by using this technique any number of frame data can be accumulated. However it is important to accept that the accumulator in the software can also overflow.

In this design a 16 bit accumulator used inside the FPGA has effectively reduced the data transfer rate by a factor of 320 times. Hence the required data transfer rate using this method is about 4 MB/sec, which is far below the available USB communication bandwidth i.e. 20 MB/sec. Hence this method can be effectively used to accumulate data in the TUPC mode.

The implemented architecture for the accumulator based design is shown in Figure 3.7.

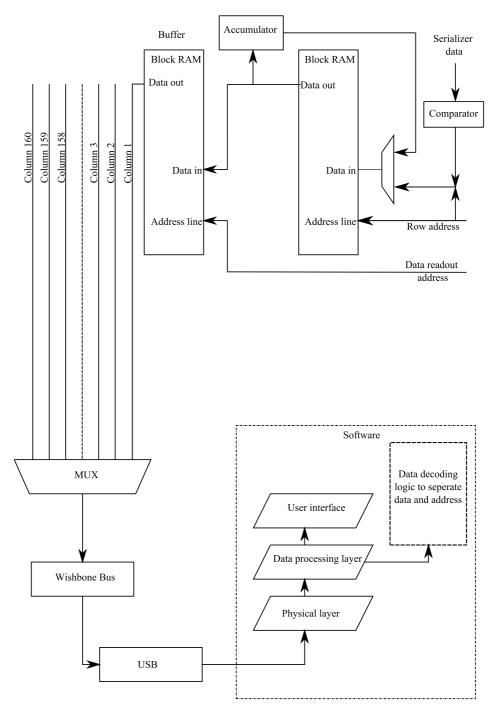

### 3.7.2 Column based event driven system

The MF128 imager is designed for photon starved applications. In photon starved applications the number of photon detected per second is about 40-60 k counts/sec. Hence, in the photon starved applications the number of photon detected in the pixel

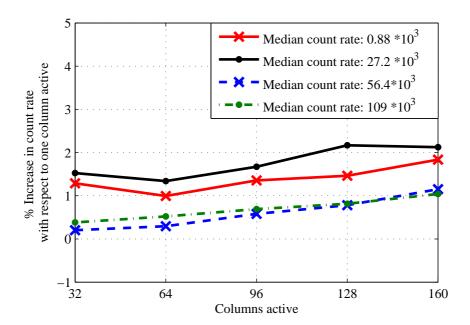

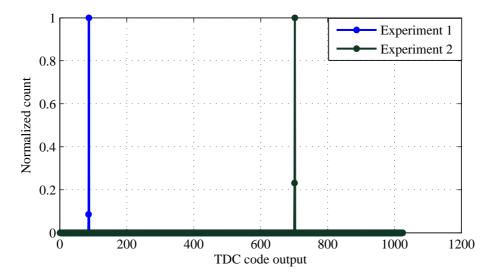

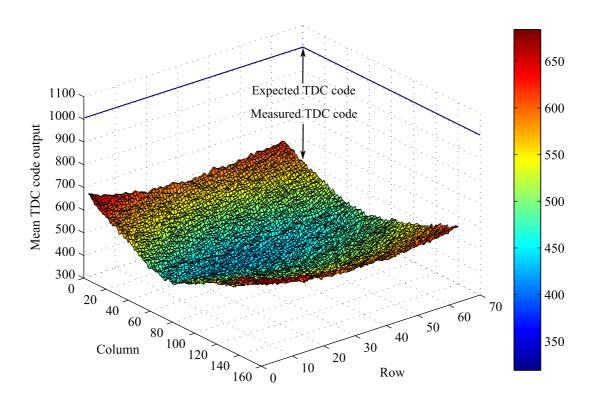

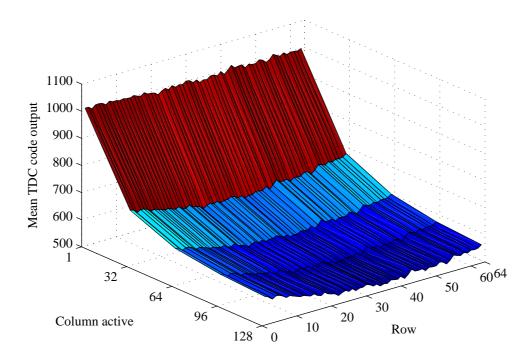

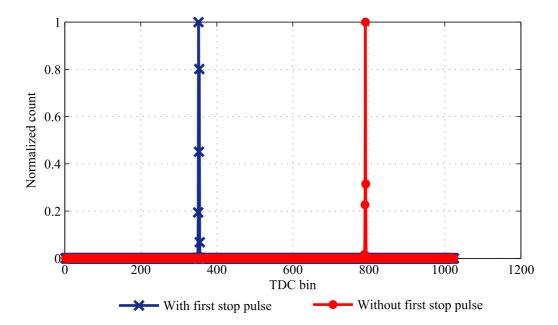

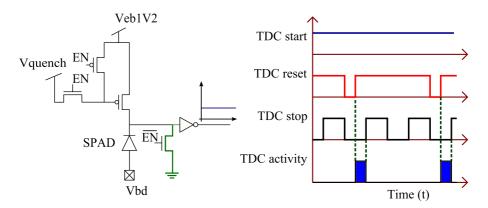

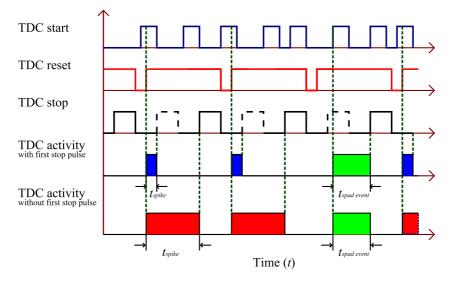

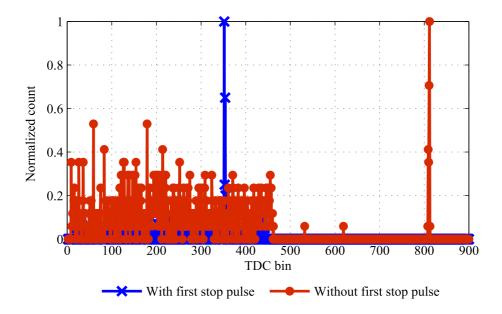

Figure 3.7: Accumulator based design