# Energy-efficient integrated circuits for piezoelectric energy harvesting

Yue. X.

10.4233/uuid:c0921ca3-8aed-4fe0-8433-b2b15db2e867

**Publication date**

**Document Version** Final published version

Citation (APA)

Yue, X. (2025). Energy-efficient integrated circuits for piezoelectric energy harvesting. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:c0921ca3-8aed-4fe0-8433b2b15db2e867

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# ENERGY-EFFICIENT INTEGRATED CIRCUITS FOR PIEZOELECTRIC ENERGY HARVESTING

**Xinling YUE**

# **Propositions**

accompanying the dissertation

# **Energy-Efficient Integrated Circuits for Piezoelectric Energy Harvesting**

by

# **Xinling YUE**

- 1. Rather than being a free lunch, energy harvesting is often a very expensive one (*This proposition pertains to this dissertation*).

- 2. The duty-cycle-based MPPT technique proposed in this thesis greatly simplifies the design of piezoelectric energy harvesters (*This proposition pertains to this dissertation*).

- 3. The output power of an energy harvesting system is mainly limited by its transducers and not by its interface electronics (*This proposition pertains to this dissertation*).

- 4. Messaging apps like WhatsApp and WeChat improve communication efficiency but distance people from one another.

- 5. By amplifying misinformation and polarization, social media has done public discourse more harm than good.

- 6. Reviewers of journals and conferences should be paid for the time and expertise they invest in the review process.

- 7. Free will is fast becoming an illusion as social media algorithms increasingly determine human behaviour.

- 8. Artificial intelligence will exacerbate social inequality.

- 9. Collaboration with industry is essential for doing an impactful PhD in engineering.

- 10. Technology makes people's lives more convenient, but not always happier.

These propositions are regarded as opposable and defendable and have been approved as such by the promotor, prof. dr. K.A.A. Makinwa and copromotor dr. S. Du.

# ENERGY-EFFICIENT INTEGRATED CIRCUITS FOR PIEZOELECTRIC ENERGY HARVESTING

#### Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology

by the authority of the Rector Magnificus prof.dr.ir. T.H.J.J. van der Hagen

Chair of the Board for Doctorates

to be defended publicly on

Thursday 4 September 2025 at 17:30 o'clock

by

Xinling YUE

Master of Engineering in Control Engineering, University of Electronic Science and Technology of China, China

Born in Shandong, China

This dissertation has been approved by the promotors.

Composition of the doctoral committee:

Rector Magnificus, chairperson

Prof. dr. K.A.A. Makinwa, Delft University of Technology, promotor

Dr. S. Du, Delft University of Technology, copromotor

# Independent members:

Prof.dr.ir. W.A. Serdijn, Delft University of Technology

Prof.dr. A.A. Seshia, University of Cambridge

Dr. F. Tavernier, KU Leuven

Dr. A. Cathelin, STMicroelectronics

Prof.dr. G.Q. Zhang, Delft University of Technology, reserve member

# Copyright © by Xinling Yue

All rights reserved. No part of this publication may be reproduced or distributed in any form or by any other means or stored in a database or retrieval system without the prior written permission of the author.

| Chapter 1 Introduction                                           | 1  |

|------------------------------------------------------------------|----|

| 1.1 Motivation                                                   | 1  |

| 1.2 Energy Harvesters                                            | 2  |

| 1.3 Vibrational Energy Harvesters                                | 4  |

| 1.4 Interface Circuits for Piezoelectric Energy Harvesting       | 6  |

| 1.4.1 A Basic PT Interface Circuit                               | 6  |

| 1.4.2 Rectifier Efficiency                                       | 6  |

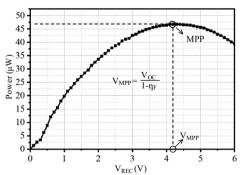

| 1.4.3 The Maximum Power Point Tracking Technique                 | 7  |

| 1.4.4 Challenges of PT Interface Circuits                        | 9  |

| 1.5 Thesis Organization                                          | 13 |

| References                                                       | 15 |

| Chapter 2 Literature Review                                      | 22 |

| 2.1 Introduction                                                 | 22 |

| 2.2 Equivalent Circuit of a Piezoelectric Transducer             | 22 |

| 2.3 Rectifiers                                                   | 24 |

| 2.3.1 Diode Rectifiers                                           | 24 |

| 2.3.2 Active Rectifiers                                          | 25 |

| 2.4 Maximum Power Point Tracking Techniques                      | 28 |

| 2.4.1 Fractional Open Circuit Voltage MPPT                       | 28 |

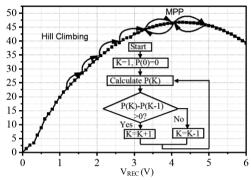

| 2.4.2 Perturb & Observe MPPT                                     | 31 |

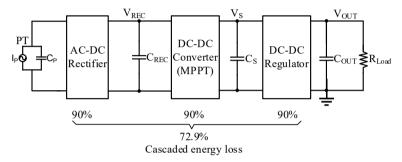

| 2.5 Cascaded System Architecture                                 | 32 |

| 2.6 Conclusion                                                   | 33 |

| References                                                       | 34 |

| Chapter 3 A Synchronized Switch Harvesting Rectifier with Reusal |    |

| 3.1 Introduction                                                 |    |

| 3.2 Theoretical Analysis of the Proposed Rectifier               | 40 |

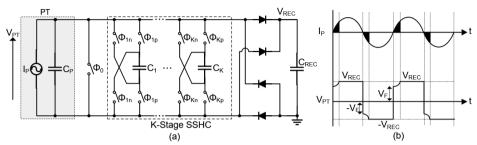

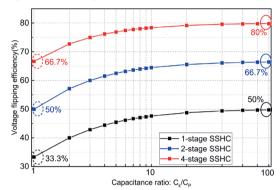

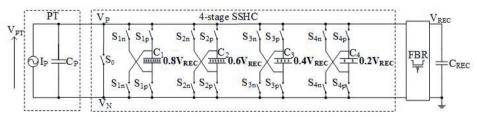

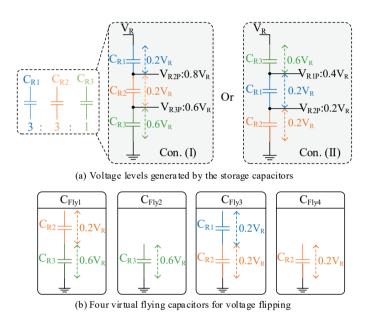

| 3.2.1 Flying Capacitors Used in a Typical SSHC Rectifier         |    |

| 3.2.2 Storage Canacitor Sharing in the Proposed SSHSC Rectifier  | 42 |

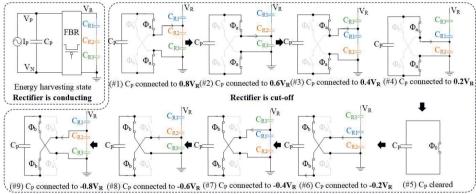

|   | 3.3 Proposed Synchronized Switch Harvesting Rectifier                                                         | . 46                 |

|---|---------------------------------------------------------------------------------------------------------------|----------------------|

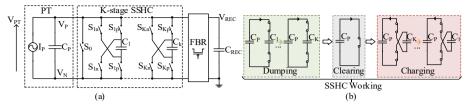

|   | 3.3.1 Topology and System Operations                                                                          | . 46                 |

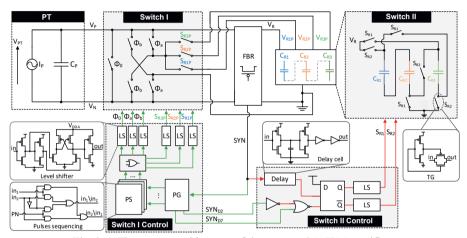

|   | 3.3.2 System Architecture                                                                                     | . 47                 |

|   | 3.4 Circuit Implementation                                                                                    | . 49                 |

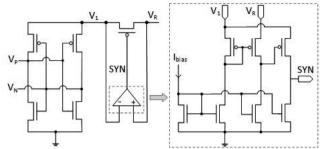

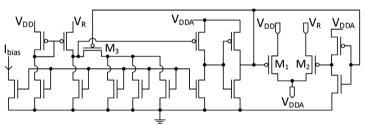

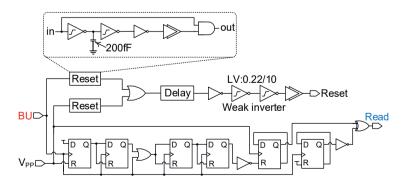

|   | 3.4.1 FBR implementation                                                                                      | . 49                 |

|   | 3.4.2 Pulse Generation Block                                                                                  | . 50                 |

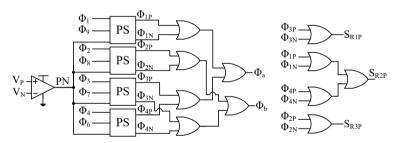

|   | 3.4.3 Supply Voltage Selector for Switches                                                                    | . 51                 |

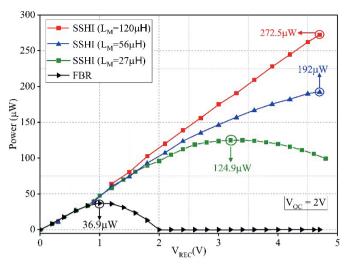

|   | 3.5 Measurement Results                                                                                       | . 51                 |

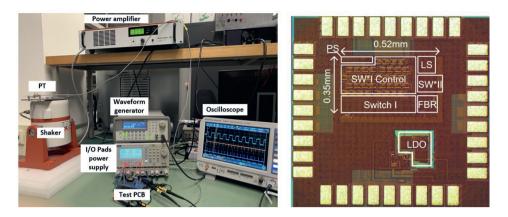

|   | 3.5.1 Measurement Setup                                                                                       | . 51                 |

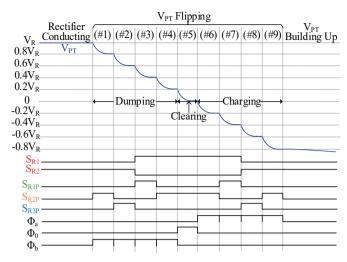

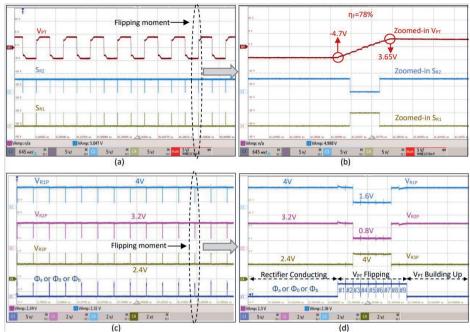

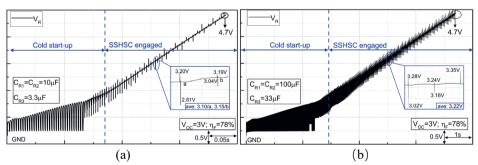

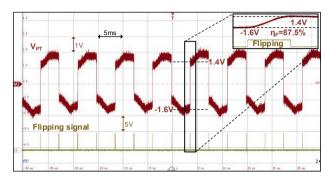

|   | 3.5.2 Measured Voltage Waveforms and Related Control Signals                                                  | . 52                 |

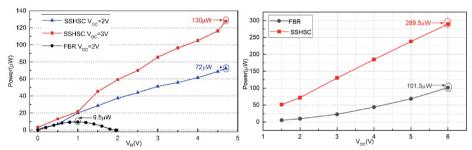

|   | 3.5.3 Output Performance Analysis                                                                             | . 55                 |

|   | 3.6 Conclusion                                                                                                | . 57                 |

|   | References                                                                                                    | . 58                 |

| C | Chapter 4 A Bias-Flip Rectifier with Duty-Cycle-Based MPPT                                                    | . 60                 |

|   | 4.1 Introduction                                                                                              | . 60                 |

|   | 4.2 Analysis of the Proposed DCB MPPT Algorithm                                                               | . 60                 |

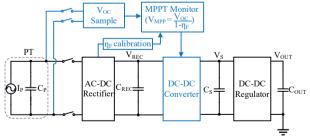

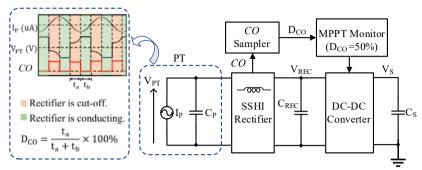

|   | 4.2.1 System Topology of the Proposed DCB MPPT                                                                | . 60                 |

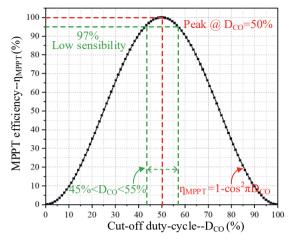

|   | 4.2.2 Theoretical Analysis of the Proposed DCB MPPT Algorithm                                                 | . 61                 |

|   | 4.3 Proposed DCB MPPT Technique                                                                               | . 65                 |

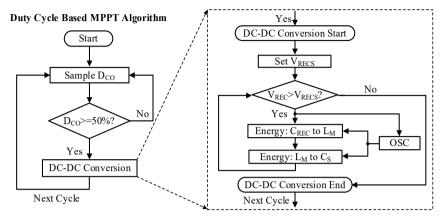

|   | 4.3.1 System Flowchart                                                                                        | . 65                 |

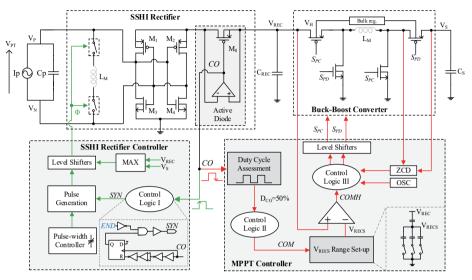

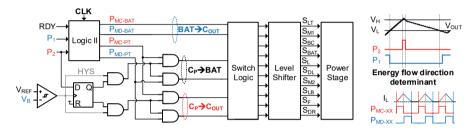

|   | 4.3.2 System Architecture                                                                                     | . 66                 |

|   | 4.4 Circuit Implementations                                                                                   | . 68                 |

|   |                                                                                                               |                      |

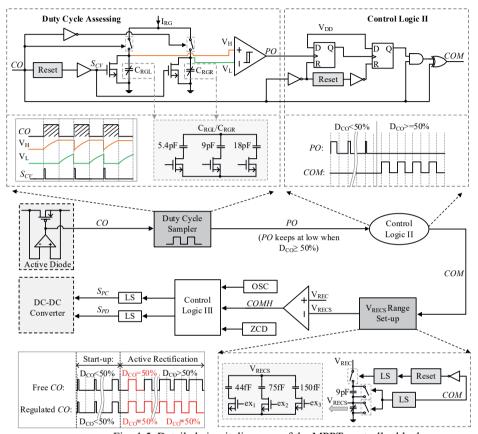

|   | 4.4.1 Circuit Diagram of the MPPT Controller Block                                                            | . 68                 |

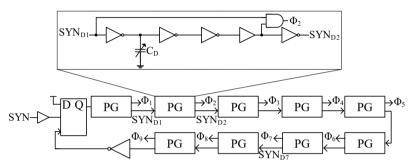

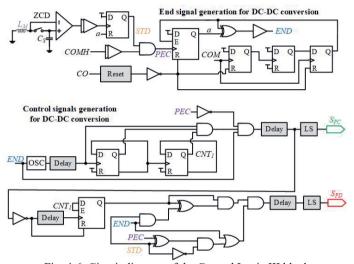

|   | 4.4.1 Circuit Diagram of the MPPT Controller Block  4.4.2 Circuit Details of the Control Logic III Block      |                      |

|   |                                                                                                               | . 69                 |

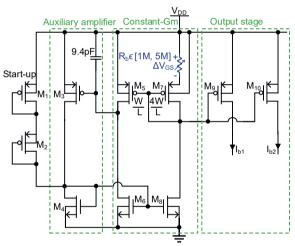

|   | 4.4.2 Circuit Details of the Control Logic III Block                                                          | . 69<br>. 71         |

|   | 4.4.2 Circuit Details of the Control Logic III Block                                                          | . 69<br>. 71<br>. 71 |

|   | 4.4.2 Circuit Details of the Control Logic III Block 4.4.3 Biasing Current Generation 4.5 Measurement Results | . 69<br>. 71<br>. 71 |

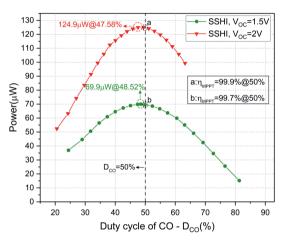

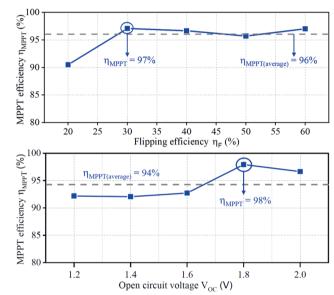

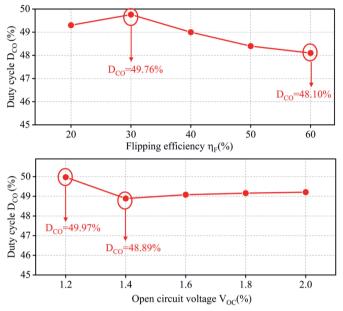

| 4.5.4 Performance Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.6 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.5.4 Performance Analysis       6         4.6 Conclusion       82         References       83         apter 5 A Single-Stage Bias-Flip Rectifier with Highly-Digital Duty-Cycled-sed MPPT       85         5.1 Introduction       85         5.2 Topology and Operations of the Proposed Single-Stage Rectifier       86         5.3 Comparisons with Conventional 3-Stage Systems       87         5.3.1 Operation Comparison       87         5.3.2 Power Analysis of a Conventional 3-Stage System       89         5.3.3 Power Analysis of the Proposed Single-Stage BMRR       91         5.4 Proposed System Architecture and Flowchart       92         5.5 Circuit Implementation       94         5.5.1 Highly-Digital MPPT Circuit Implementation       94         5.5.2 Output Voltage Regulation Block       96         5.6 Measurement Results       97         5.6.1 Measurement Waveform of PT Voltage       98         5.6.3 Measured PT Voltage Waveform During MPPT       100         5.6.4 Measured Waveform During Output Regulation       100         5.7 Performance Analysis       101         5.8 Conclusion       105         6.1 Main Findings       108         6.2 Comparisons with the State-of-the-Art       109         6.3 Future Work       111 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

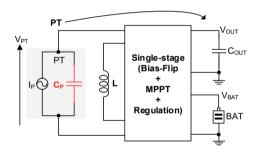

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

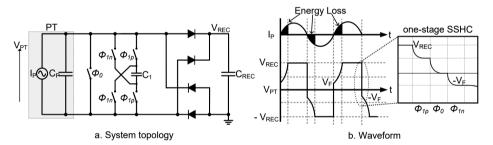

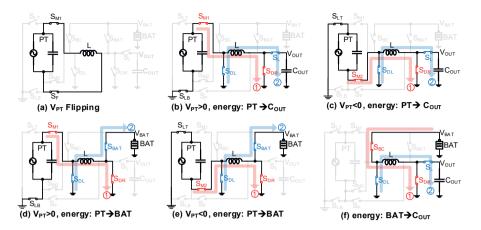

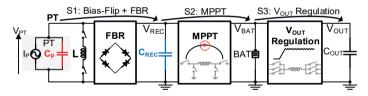

| 5.2 Topology and Operations of the Proposed Single-Stage Rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.3 Comparisons with Conventional 3-Stage Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82         83         as-Flip Rectifier with Highly-Digital Duty-Cycled-85         85         85         6 of the Proposed Single-Stage Rectifier       86         86 attional 3-Stage Systems       87         87 conventional 3-Stage System       89         8 Proposed Single-Stage BMRR       91         9 cture and Flowchart       92         9 Circuit Implementation       94         2 attion Block       96         97       97         98       Waveform During MPPT       100         During Output Regulation       101         105       107         106       108         107 ce-of-the-Art       109         111 differ With Output Regulation       111         1al Sinusoidal Excitation       112 |

| 5.3.1 Operation Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.3.2 Power Analysis of a Conventional 3-Stage System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.3.3 Power Analysis of the Proposed Single-Stage BMRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

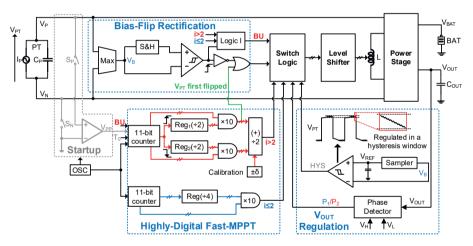

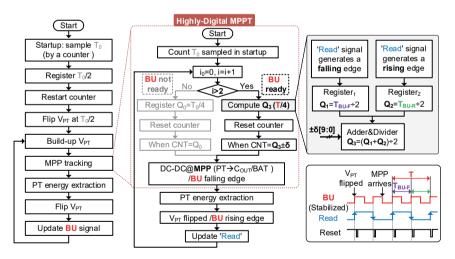

| 5.4 Proposed System Architecture and Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.5 Circuit Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

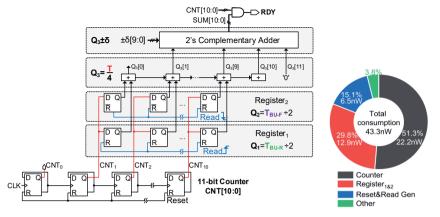

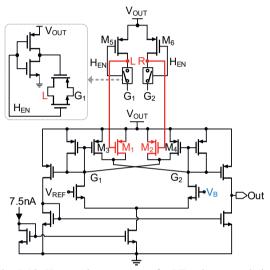

| 5.5.1 Highly-Digital MPPT Circuit Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.5.2 Output Voltage Regulation Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.6 Measurement Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.6.1 Measurement Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

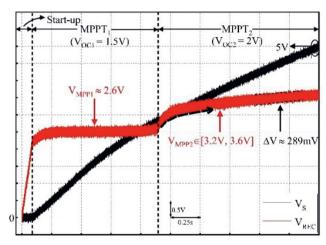

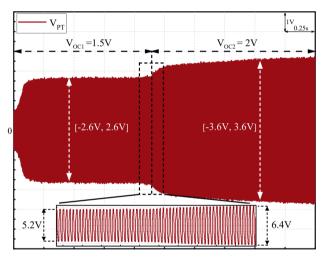

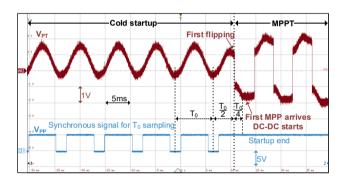

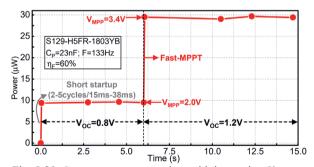

| 5.6.2 Measurement Waveform of PT Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

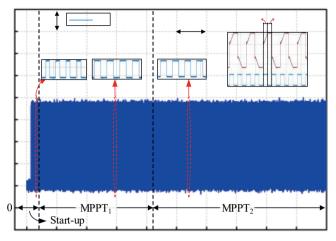

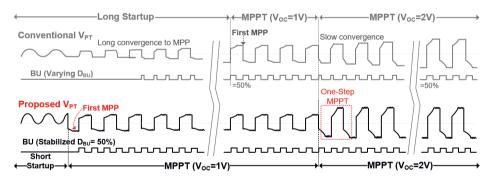

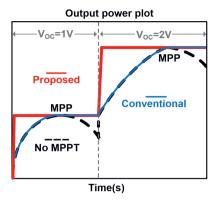

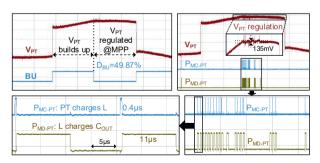

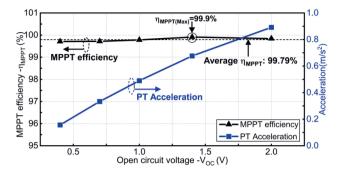

| 5.6.3 Measured PT Voltage Waveform During MPPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

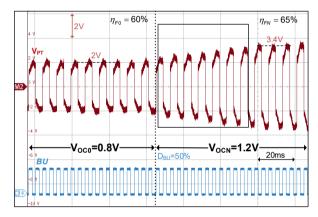

| 5.6.4 Measured Waveform During Output Regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

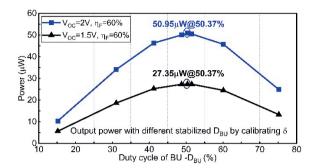

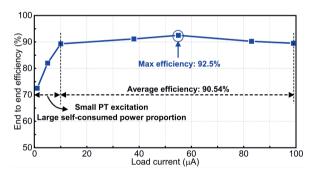

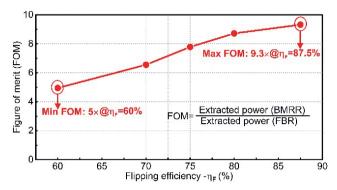

| 5.7 Performance Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.8 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Chapter 6 Conclusions and Outlook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.1 Main Findings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

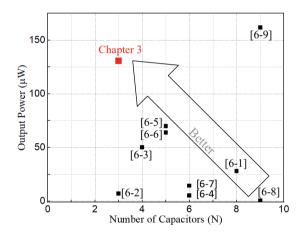

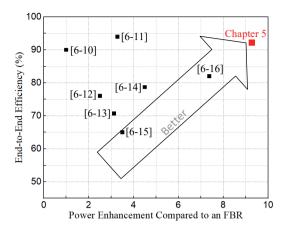

| 6.2 Comparisons with the State-of-the-Art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.3 Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.3.1 Fully Capacitive Rectifier With Output Regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.3.2 MPPT under Non-Ideal Sinusoidal Excitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6 3 3 Power Limit Analysis and Possible Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| References           |     |

|----------------------|-----|

| Summary              | 118 |

| Samenvatting         |     |

| Acknowledgments      |     |

| List of Publications | 126 |

| About the Author     |     |

# 1.1 Motivation

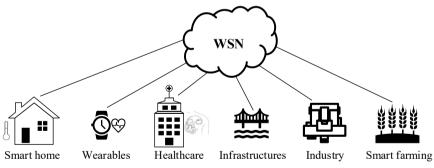

The Internet of Things (IoT) has permeated almost every part of our daily lives, fundamentally altering human society. One of its main drivers has been the development of wireless sensors, which can be used in wireless networks, thus providing real-time information about the physical world to distributed and increasingly intelligent systems. As shown in Fig. 1-1, wireless sensor networks have become ubiquitous and are used in smart homes, wearables, healthcare, infrastructures, industrial applications, and smart farming. In smart homes, for instance, wireless sensors monitor parameters such as temperature, humidity, air quality, sound, and light intensity, ensuring optimal living conditions. In the healthcare sector, wireless sensors have revolutionized patient care by facilitating continuous monitoring, delivering real-time health data to doctors and nurses, and enabling timely and informed medical interventions. In industrial automation, wireless sensors are used to monitor the condition of vital equipment and environmental parameters, such as pressure, liquid level, flow rate, and vibration, thus enhancing operational efficiency and safety.

Fig. 1-1. Wireless sensor node (WSN) applications.

Wireless sensors are often powered by electrochemical batteries, whose reliability and storage capacity then determine the sensor's operational life. For example, the LIS3DH, a low-power 3-axis accelerometer intended for IoT applications, dissipates 28µW during normal operation [1-1]. This results in an operational life of about 4

months when it is powered by a 35mAh CR1220 coin-cell battery. This can obviously be increased by using a larger battery or by replacing/recharging it more frequently. However, a large battery is undesirable in portable wireless sensors, while battery replacement is impractical or costly in applications such as implantable medical devices or autonomous sensors in remote areas. As a result, there is a need for low-cost, sustainable, and environmentally friendly alternatives to traditional batteries.

# 1.2 Energy Harvesters

Energy harvesters extract energy from their environment and convert it into electrical energy for use in other electronic devices. As such, they are a promising alternative to the use of batteries in wireless sensors. Table 1-1 lists common environmental energy sources, such as heat, light, electromagnetic waves, and vibration, which are suitable for powering electronic devices.

Thermoelectric generators (TEGs) are based on the Seebeck effect, which refers to the ability of thermocouples to generate a voltage from a temperature difference [1-2][1-3][1-4]. As shown in Table 1-1, TEGs are particularly effective at harvesting industrial waste heat, which can have power densities as large as  $3\mu W/K^2/cm^2$ . In contrast, the power densities associated with harvesting human body heat are much lower, in the order of  $0.03\mu W/K^2/cm^2$ . TEGs do not have moving parts, ensuring high reliability and minimal maintenance requirements. However, they require large and continuously available temperature gradients to operate effectively and are thus not well-suited for use in infrastructure monitoring or smart agriculture.

Table 1-1. Different types of energy harvesting systems.

| Harvester  |             | Power Density                              | Scenario             | Ref.   |

|------------|-------------|--------------------------------------------|----------------------|--------|

|            | Thermal     | Conventional: 3 µW/K²/cm²                  | Industrial heat      | F1 101 |

|            | Inermai     | CMOS Compatible: $0.026 \mu W/ K^2/cm^2$   | Human body           | [1-19] |

| \ <u>\</u> | S-1         | Outdoor: 15 mW/cm <sup>2</sup>             | Rooftop (sunny days) | [1-20] |

| *          | Solar       | Solar Indoor: <10 μW/cm <sup>2</sup> Light | Light                |        |

|            | <b>≈</b> RF | GSM Network: 0.1 µW/cm <sup>2</sup>        | Mobile phone         | [1 21] |

| Ş          | KΓ          | Wi-Fi Network: 0.01 μW/cm <sup>2</sup>     | Wi-Fi, radar, RFID   | [1-21] |

| <b>~</b>   | Vibration   | Electromagnetic: 4 μW/cm <sup>2</sup>      | Motor, transformer   | [1-22] |

|            | vioration   | Piezoelectric: 500 μW/cm <sup>2</sup>      | Road, human motion   | [1-23] |

Photovoltaic (PV) harvesters use sunlight or artificial lighting to create electricity via the photovoltaic effect [1-5] [1-6]. Thanks to their high energy efficiency, mature fabrication process, and reliability without employing any moving parts, they have been dominantly employed worldwide in the past decade for renewable energy generation. As shown in Table 1-1, they can achieve power densities as high as  $15 \text{mW/cm}^2$  in direct sunlight, making them well-suited for use in autonomous systems. However, their power density drops dramatically (to less than  $10 \mu \text{W/cm}^2$ ) under indoor lighting conditions.

Radio frequency (RF) energy harvesters convert electromagnetic waves into electrical power [1-7] [1-8] [1-9] [1-10]. Since RF signals are ubiquitous in urban environments due to the presence of radio, television, and cellular networks, RF energy harvesters are well-suited for use in smart homes. Unfortunately, the low energy density of RF signals (typically less than  $0.1 \mu W/cm^2$ ) limits their use in industrial and healthcare applications, as well as in remote rural or mountainous settings.

Last, but not least, vibrational energy harvesting (VEH) involves the conversion of kinetic energy, in the form of mechanical motion or vibration, into electrical energy. Compared to other energy sources, kinetic energy, can be readily harvested: from door handles and light switches, from human body motion, from building/bridge/tunnel vibrations, from rotating machines, and from wind or wave motion. Furthermore, vibra-

tion energy harvesting offers advantages such as low maintenance costs, simple construction, and often, continuous output power. Therefore, the main focus of this thesis will be on the design of vibration energy harvesters.

# 1.3 Vibrational Energy Harvesters

Vibrational energy can be harvested by electromagnetic, electrostatic, triboelectric, or piezoelectric harvesters. Electromagnetic generators are based on the principle of electromagnetic induction [1-11][1-12]. Their main components are a moving magnet and/or coil. Mechanical force changes the position of the magnet or coil, changing the magnetic flux through the coil and generating an induced current. Electromagnetic generators are widely used in large-scale power generation scenarios, such as motors and transformers in industries, which are not suitable for powering wireless sensors.

Electrostatic energy harvesters are devices that convert mechanical energy into electrical energy using variable capacitors. The basic principle is that, under either the charge-constrained or voltage-constrained condition, mechanical motion (e.g., vibration or displacement) changes the capacitance of the device, thereby altering the stored electrostatic energy and inducing current flow in the external circuit [1-13][1-14]. However, this approach typically requires an external bias to enable energy conversion. A special form of electrostatic energy harvesting is electret-based electrostatic energy harvesting, in which a variable-capacitance structure incorporates an electret material with an intrinsic electric field, thus eliminating the need for an external bias and enabling self-startup [1-15]. Nevertheless, electret-based devices still face limitations in powering wireless sensors, including low power density, high output impedance, strong dependence on precise mechanical gaps and packaging integrity, and possible charge decay of the electret under high-humidity or high-temperature conditions [1-13][1-15][1-16].

Triboelectric nanogenerators (TENGs) are an energy harvesting technology based on the triboelectric effect and electrostatic induction, in which two materials with dif-

ferent electronegativities undergo periodic contact—separation or relative sliding, leading to electron transfer and charge separation, and subsequently generating electrical output through an external circuit [1-17][1-18]. TENGs feature high output voltage, mechanical flexibility, and versatile material/structural design, and in recent years have been widely explored in areas such as wearable electronics, environmental monitoring, and infrastructure health monitoring [1-17]. However, issues such as surface wear and lifetime degradation caused by contact—sliding interfaces, as well as charge leakage under humid environmental conditions, remain significant challenges [1-19][1-20][1-21]. Moreover, the commercialization of TENG front-end devices is still limited, with no large-scale or standardized products available [1-17]. These factors make current TENG technology unsuitable for providing stable and reliable power to most wireless sensor systems.

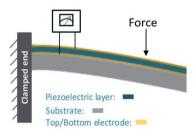

Piezoelectric transducers (PTs) are based on the piezoelectric effect [1-22][1-23][1-24][1-25], which refers to the ability of certain crystals or ceramics to generate an electric field when subjected to mechanical pressure [1-34][1-35] or stress [1-35][1-36]. They usually contain a piezoelectric layer sandwiched by two metal layers as electrodes, which offer significant advantages in size, weight, power density (500μW/cm²), and cost over other vibrational generators. Moreover, PTs can be made in various shapes, for instance, cantilever beams [1-37] [1-38], flat circular discs [1-39] [1-40], stacked structures [1-41], etc., making them easy to integrate into different devices with simple structures. Piezoelectric devices can also be fabricated in micromechanical systems (MEMS) technology to achieve high-integration levels with CMOS power-conditioning circuits for miniaturization [1-48]. Hence, PTs are well-suited for use in miniature low-power vibrational energy harvesting systems. However, integrating them into wireless sensors requires efficient interface circuits, as will be discussed in the next section.

# 1.4 Interface Circuits for Piezoelectric Energy Harvesting

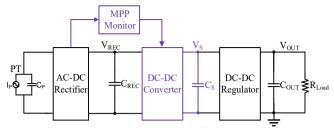

# 1.4.1 A Basic PT Interface Circuit

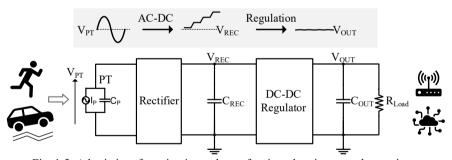

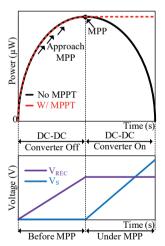

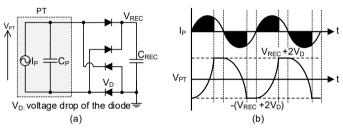

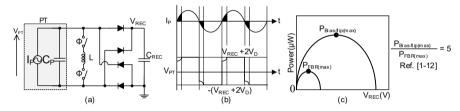

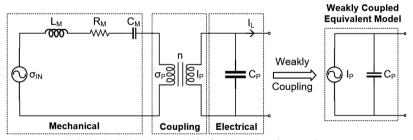

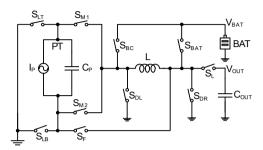

Piezoelectric transducers (PTs) produce AC current in response to mechanical changes and thus can be modelled by an AC current source ( $I_P$ ) connected in parallel with a capacitor ( $C_P$ ). An interface circuit is then required to convert this AC signal into the stable DC supply voltage required by most electronic systems.