# Meta-learning for few-shot on-chip sequence classification

by

Douwe M. J. den Blanken

to obtain the degree of Master of Science

at the Delft University of Technology,

to be defended publicly on Thursday September 28, 2023 at 13:00.

Student number: 4843940

Project duration: November 14, 2022 – September 23, 2023

Thesis committee: Dr. C. Frenkel, TU Delft, daily supervisor

Prof. dr. K.A.A. Makinwa, TU Delft, department head

Prof. M. Verhelst, KU Leuven, external jury

*This thesis is confidential and cannot be made public until September 28, 2025.*

An electronic version of this thesis is available at <http://repository.tudelft.nl/>.

## **Disclaimer on open-source contributions**

As part of the effort to increase and promote reuse in the hardware design space, the following items are published as open-source:

- hardware design: <https://github.com/VOXNIHILI/chameleon>,

- meta-learning benchmarking suite: <https://github.com/VOXNIHILI/meta-learning-arena>,

- all experimental machine learning data: <https://wandb.ai/douwe/meta-learning-arena>,

- all vector-graphics figures: [https://drive.google.com/file/d/1447Nd-1guDoKupiJSHBD\\_PKoScaEVtCt/view?usp=sharing](https://drive.google.com/file/d/1447Nd-1guDoKupiJSHBD_PKoScaEVtCt/view?usp=sharing).

Furthermore, throughout the course of this thesis, contributions were made to the following open-source repositories:

- PyTorch (machine learning framework): <https://github.com/pytorch/pytorch>,

- QPyTorch (reduced bitwidth simulation): <https://github.com/Tiiiger/QPyTorch>,

- Harvard Multilingual keyword spotting project: [https://github.com/harvard-edge/multilingual\\_kws](https://github.com/harvard-edge/multilingual_kws),

- AudioLoader (collection of PyTorch speech datasets): <https://github.com/KinWaiCheuk/AudioLoader>.

*"I didn't have time to write a short letter,

so I wrote a long one instead." – Mark Twain*

## Acknowledgements

Here, I would like to make use of the opportunity to express my heartfelt gratitude to all those who have contributed to the successful completion of this master's thesis. This journey would not have been possible without their support, guidance, and encouragement.

First and foremost, I want to send out my deepest appreciation to my thesis advisor, Charlotte Frenkel; for her support and mentorship, for her all-in commitment to my work and for the many opportunities I was offered throughout the entire research process. From enabling me to do a tape-out to giving me the chance to visit conferences and training courses. Without you, none of these things would have been possible. Your expertise and 24/7-dedication played a pivotal role in shaping all aspects of my thesis. Thank you for everything.

For the silicon design specifically, I want to thank Nandor, Nicolas and Martin: without you, I would not have been able to navigate so quickly through many of the issues I encountered. Also, I want to express my gratitude to Atef for, even after your retirement, helping us until the very end of the tape-out. Furthermore, I would like to send out a huge thank-you to Yihan, with whom I led our subtape-out group. You have been instrumental in making sure all the hardware came together! I would also like to thank my brother Tim for designing an amazing top mask for the final hardware design.

Moreover, I'm really thankful for all the help and support from my friends and family. First, I want to thank my parents and brother for being there for me throughout my life and especially during this busy time of mine. I also want to thank my girlfriend for consistently offering her love, support, and a sense of calm during this journey.

And last but not least, thanks to Artemis and Charis, Froso and Kyriakos for taking care of everything over the summer, which allowed me to focus on my thesis during the holidays.

Douwe

# Abstract

The growing interest in edge computing is driving the demand for more efficient deep learning models that fit into resource-constrained edge devices like Internet-of-Things (IoT) sensors. The challenging limitations of these devices in terms of size and power has given rise to the field of tinyML, focusing on enabling low-cost machine learning on edge devices. Up until recently, the work in this space was primarily focused on static inference scenarios. However, a prominent issue with this is that models cannot adapt post-deployment, leading to robustness issues with shifting data distributions or the introduction of new features in the data. However, at the edge, full on-device retraining, or communicating all new data to a central server, is infeasible: this necessitates the development of data-efficient learning algorithms to adapt locally and autonomously from streaming data. This challenge at the intersection of edge computing and data-efficient learning is currently an open challenge.

In this thesis, we propose to solve this challenge with *meta-learning*. To clarify in which way the application of meta-learning is the most suitable for edge hardware, for the first time, a principled approach for meta-learning at the edge is outlined and investigated in three parts.

The first part of this thesis details the selection of a suitable neural network architecture for few-shot learning over *sequential* data. By not being fixated on one architecture from the start, it is possible to explore different approaches to learning over sequences of temporal data, leading to the identification of the most effective architecture for generalizing from limited temporal examples. The quantitatively evaluated architectures are a recurrent neural network (RNN), a gated recurrent unit (GRU), a long-short-term memory (LSTM) and a temporal convolutional network (TCN). We show that TCNs outperform all architectures, while GRUs and LSTMs have a lower activation memory requirement. However, the latter require a linearly increasing number of multiplications with input sequence length, while it scales logarithmically for TCNs. Our results show that TCNs therefore provide the most favorable trade-off for low-cost temporal feature extraction at the edge.

The second part of the thesis focuses on the algorithmic developments of the few-shot learning setup. Building on recent results from machine learning research, we highlight how meta-learning techniques primarily rely on learning high-quality features that generalize well. Taking into account hardware-driven considerations such as memory and compute overheads and through detailed quantitative analyses, we demonstrate that the best performance-cost trade-off is reached with a simple supervised pre-training scheme, where on-chip learning is performed by comparing the outputs of a TCN-based feature extractor with Manhattan distance. We also analyze the impact of quantization on this trade-off and, accordingly, we select a scheme with 4-bit logarithmic weights and 4-bit unsigned activations.

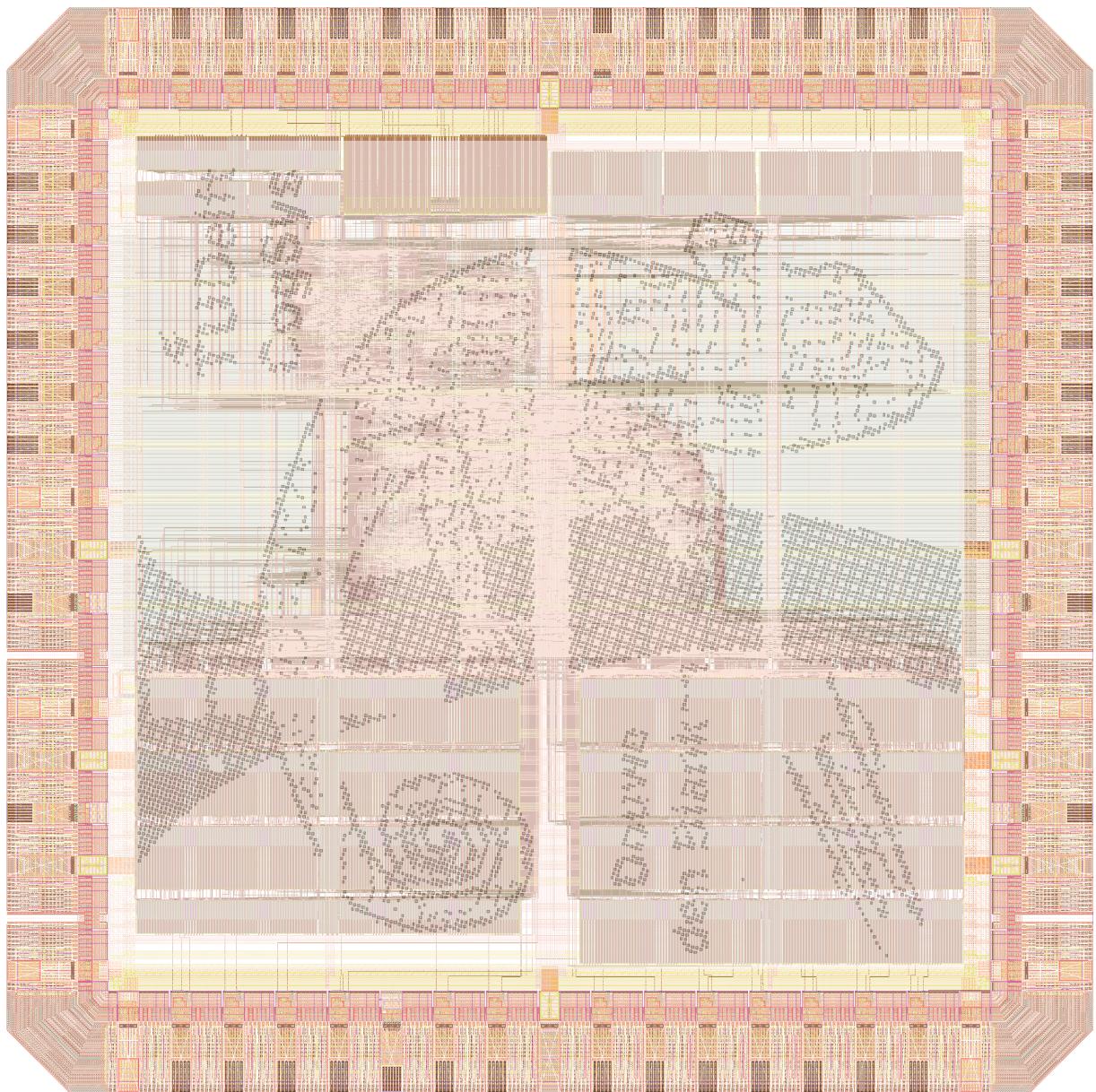

Building on these results, the third and final part of the thesis covers the design and implementation of an application-specific integrated circuit (ASIC) for few-shot learning from temporal data at the edge, taped out in a TSMC 40-nm technology node with a sub-mm<sup>2</sup> core area, which we codename *Chameleon*. The design follows a typical accelerator-style architecture and supports per-layer variable kernel sizes for up to 16 TCN layers. Processing such networks takes place in a 16 × 16 processing-element (PE) array performing bit shifts instead of multiplications thanks to the use of logarithmic weights. To benchmark Chameleon, we select two tasks consisting in 5- and 20-class, single-shot classification of never-seen-before handwritten characters from the Omniglot dataset, for which we obtain accuracies of 97.9% and 93.6%, respectively. Furthermore, we show that these on-chip learning capabilities do not degrade the efficiency of regular classification tasks. Indeed, streaming inference for real-time 16-ms-latency keyword spotting can be done at a clock speed of only 4.38 kHz, yielding a 93.5-% classification accuracy on the Google Speech Commands (GSC) dataset.

Our results pave the way for low-cost few-shot learning over temporal data, at the edge. By enabling edge devices to perform this local and data-efficient learning, these devices will be able to adapt autonomously to shifting data distribution or new features altogether, while maintaining user privacy.

# Nomenclature

AI Artifical Intelligence

ANIL Almost No Inner Loop

ASIC Application-Specific Integrated Circuit

CL Continual Learning

DL Deep Learning

FOMAML First-Order MAML

GSC Google Speech Commands

KD Knowledge Distillation

KWS KeyWord Spotting

LLMs Large Language Models

LR Logistic regression

LSTM Long Short-Term Memory

MAML Model-Agnostic Meta-Learning

ML Machine Learning

MSE Mean-squared error

MSWC Multilingual Spoken Words Corpus

NIL No Inner Loop

PN Prototypical Networks

PTQ Post-Training Quantization

QAT Quantization-Aware Training

RNN Recurrent Neural Network

STE Straight-through estimator

TCN Temporal Convolutional Network

# Contents

|                                                           |           |

|-----------------------------------------------------------|-----------|

| <b>Acknowledgements</b>                                   | <b>iv</b> |

| <b>Abstract</b>                                           | <b>v</b>  |

| <b>1 Introduction</b>                                     | <b>1</b>  |

| <b>2 Background</b>                                       | <b>3</b>  |

| 2.1 Meta-learning . . . . .                               | 3         |

| 2.1.1 The need for data-efficient learning . . . . .      | 3         |

| 2.1.2 Formalizing meta-learning . . . . .                 | 4         |

| 2.1.3 Taxonomy . . . . .                                  | 7         |

| 2.1.4 Meta-learning algorithms . . . . .                  | 9         |

| 2.1.4.1 Learning an initialization . . . . .              | 9         |

| 2.1.4.2 Feed-forward models . . . . .                     | 11        |

| 2.1.4.3 Metric learning . . . . .                         | 13        |

| 2.1.5 Qualitative algorithm comparison . . . . .          | 14        |

| 2.1.6 Benchmarks . . . . .                                | 15        |

| 2.1.6.1 Omniglot . . . . .                                | 17        |

| 2.1.6.2 Few-shot keyword spotting . . . . .               | 18        |

| 2.1.7 Continual learning . . . . .                        | 21        |

| 2.2 Classifying time-series data . . . . .                | 22        |

| 2.2.1 Recurrent Neural Networks . . . . .                 | 23        |

| 2.2.2 Temporal Convolutional Networks . . . . .           | 25        |

| 2.3 Neural network quantization . . . . .                 | 27        |

| 2.3.1 The need for quantization . . . . .                 | 27        |

| 2.3.2 Quantization fundamentals . . . . .                 | 28        |

| 2.3.2.1 Multiply-accumulate operation . . . . .           | 28        |

| 2.3.2.2 Quantization . . . . .                            | 30        |

| 2.3.2.3 Dequantization . . . . .                          | 31        |

| 2.3.2.4 Symmetric vs. asymmetric quantization . . . . .   | 32        |

| 2.3.2.5 Per-tensor and per-channel quantization . . . . . | 33        |

| 2.3.3 Quantized training . . . . .                        | 33        |

| 2.3.3.1 Quantization-Aware Training . . . . .             | 33        |

| 2.3.3.2 Residual layer handling . . . . .                 | 34        |

| 2.3.3.3 Batch normalization folding . . . . .             | 35        |

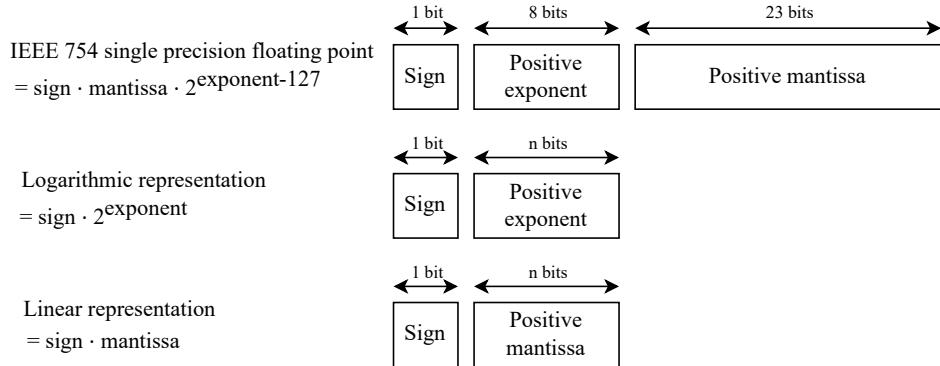

| 2.3.4 Number representations . . . . .                    | 35        |

| <b>3 Network design</b>                                   | <b>39</b> |

| 3.1 Architecture type choice . . . . .                    | 39        |

| 3.1.1 Performance . . . . .                               | 39        |

| 3.1.1.1 Sequential & permuted MNIST . . . . .             | 39        |

| 3.1.1.2 Adding problem . . . . .                          | 39        |

| 3.1.1.3 Copy memory . . . . .                             | 40        |

| 3.1.1.4 Results . . . . .                                 | 40        |

| 3.1.2 Training properties . . . . .                       | 41        |

| 3.1.3 Hardware considerations . . . . .                   | 43        |

|          |                                                                        |           |

|----------|------------------------------------------------------------------------|-----------|

| 3.1.3.1  | Activation memory size . . . . .                                       | 43        |

| 3.1.3.2  | Required multiplications . . . . .                                     | 45        |

| 3.1.4    | Final choice . . . . .                                                 | 45        |

| 3.2      | Network designs per benchmark . . . . .                                | 46        |

| 3.2.1    | Receptive field size considerations . . . . .                          | 46        |

| 3.2.2    | Final designs . . . . .                                                | 47        |

| 3.2.2.1  | 12-class KWS . . . . .                                                 | 47        |

| 3.2.2.2  | Few-shot KWS . . . . .                                                 | 48        |

| 3.2.2.3  | Sequential Omniglot . . . . .                                          | 49        |

| <b>4</b> | <b>Algorithmic development</b>                                         | <b>50</b> |

| 4.1      | Hardware-driven considerations . . . . .                               | 50        |

| 4.2      | From model-agnostic meta-learning to supervised pre-training . . . . . | 51        |

| 4.2.1    | Features or adaptation? . . . . .                                      | 51        |

| 4.2.2    | Simple baselines . . . . .                                             | 53        |

| 4.2.3    | Pre-training an embedder . . . . .                                     | 54        |

| 4.2.4    | Key takeaways . . . . .                                                | 56        |

| 4.3      | Meta-learning algorithm choice . . . . .                               | 57        |

| 4.3.1    | Quantitative meta-learning method comparison . . . . .                 | 57        |

| 4.3.1.1  | Sequential Omniglot . . . . .                                          | 57        |

| 4.3.1.2  | Few-shot keyword spotting . . . . .                                    | 58        |

| 4.3.2    | Embedding distance metric comparison . . . . .                         | 59        |

| 4.3.3    | Final choice . . . . .                                                 | 62        |

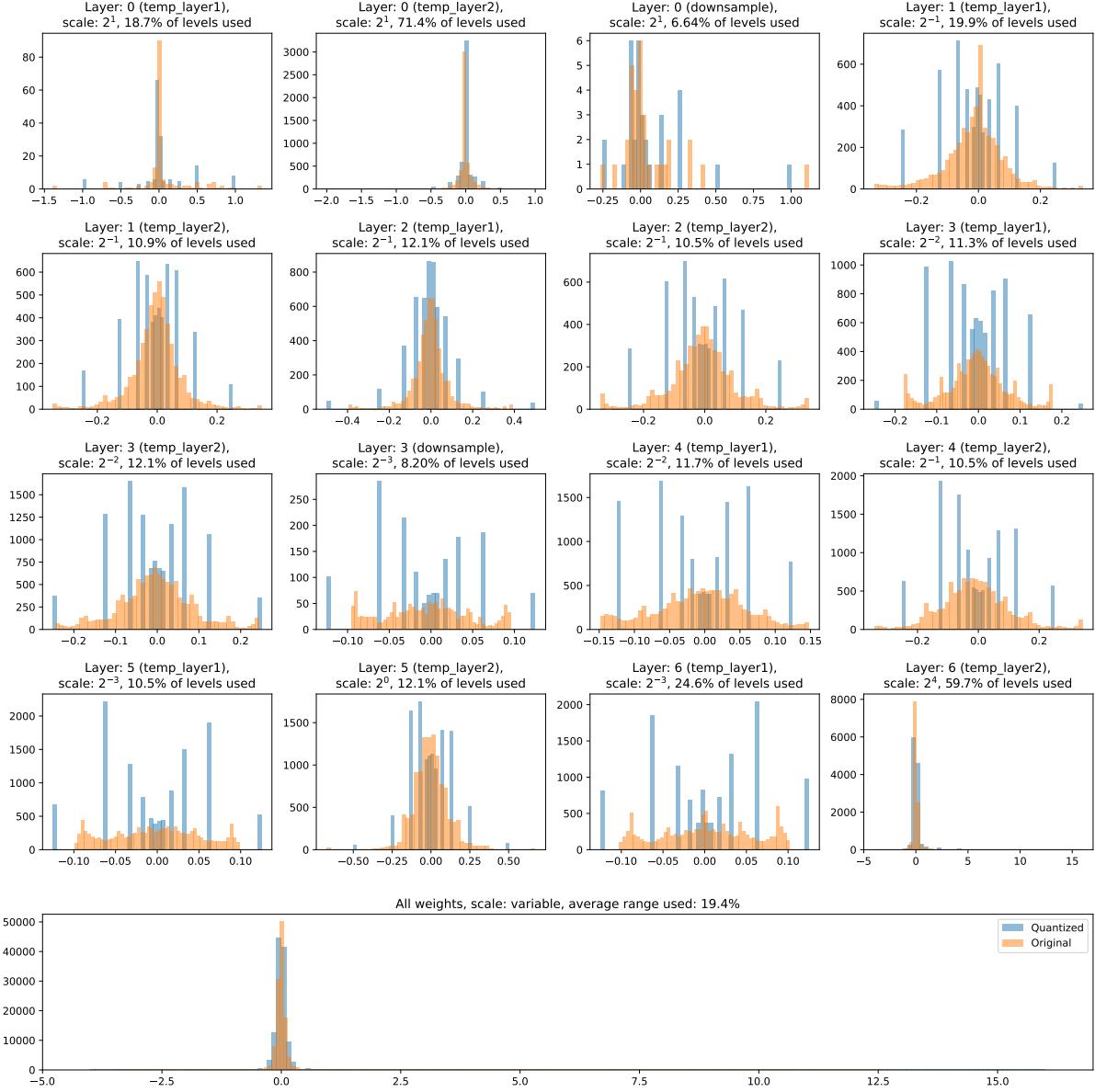

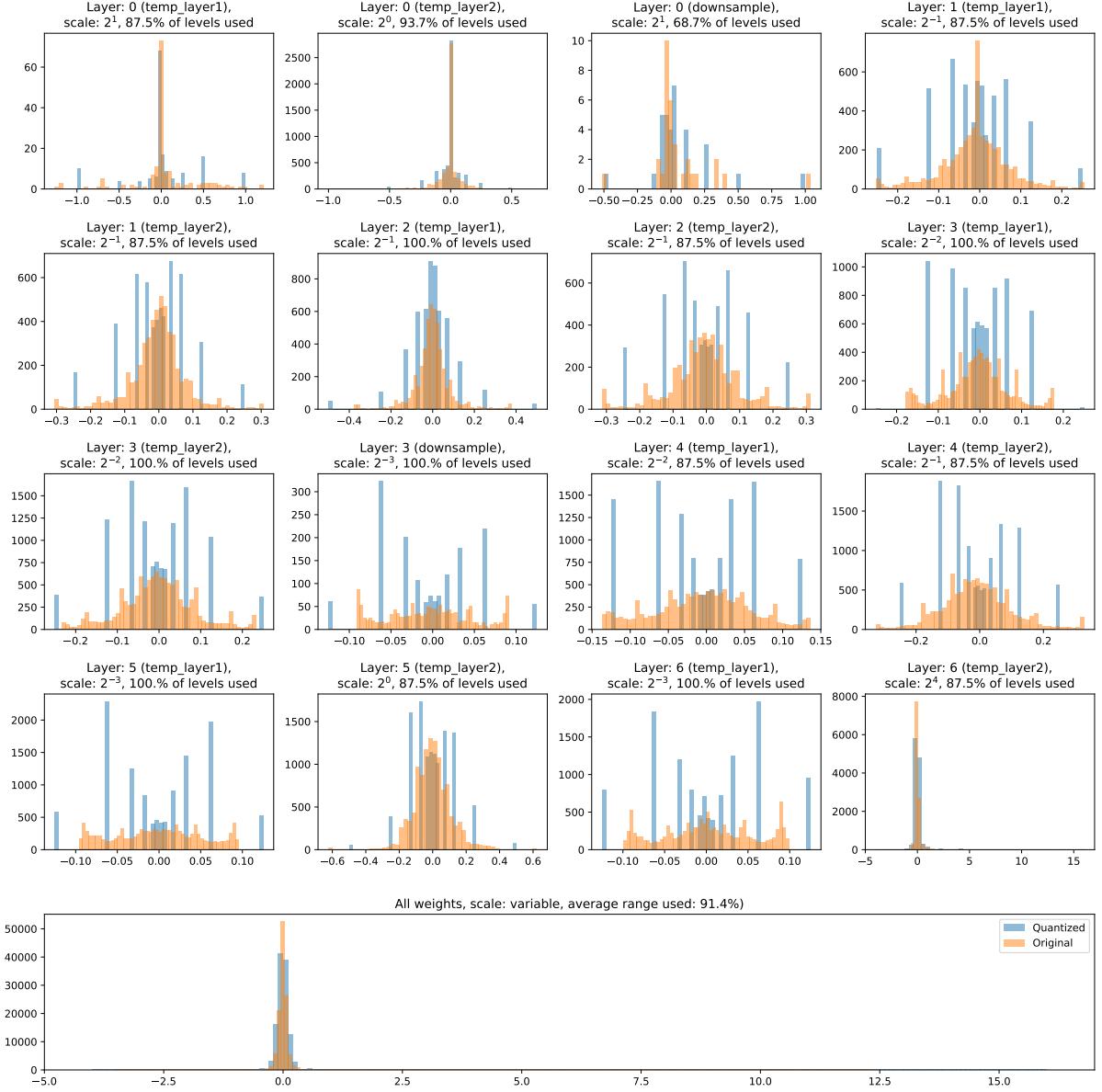

| 4.4      | Quantitative quantization scheme comparison . . . . .                  | 63        |

| 4.4.1    | Sequential Omniglot . . . . .                                          | 64        |

| 4.4.2    | 12-class KWS . . . . .                                                 | 67        |

| 4.4.3    | Quantization scheme choice . . . . .                                   | 68        |

| 4.5      | Final performance . . . . .                                            | 68        |

| <b>5</b> | <b>Hardware implementation</b>                                         | <b>69</b> |

| 5.1      | Requirements . . . . .                                                 | 70        |

| 5.2      | Related work . . . . .                                                 | 71        |

| 5.2.1    | TCN acceleration . . . . .                                             | 71        |

| 5.2.2    | Keyword-spotting acceleration . . . . .                                | 72        |

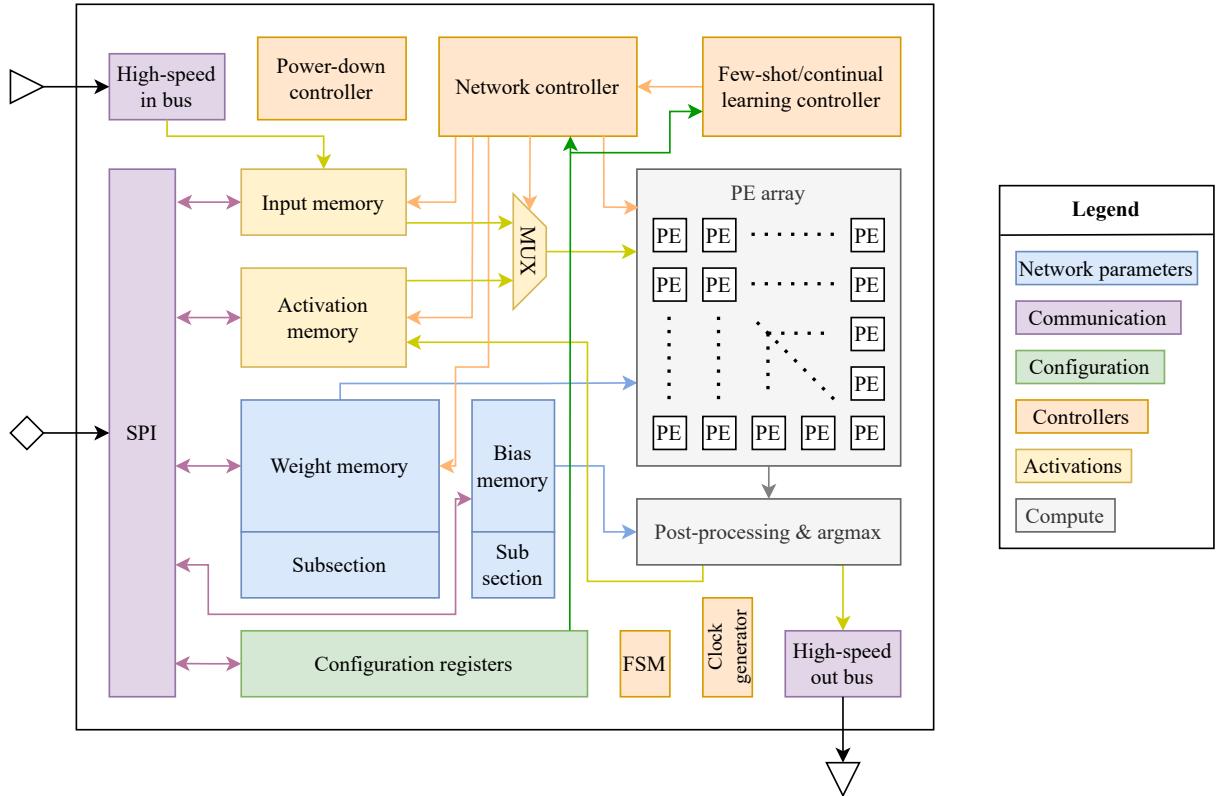

| 5.3      | High-level architecture . . . . .                                      | 73        |

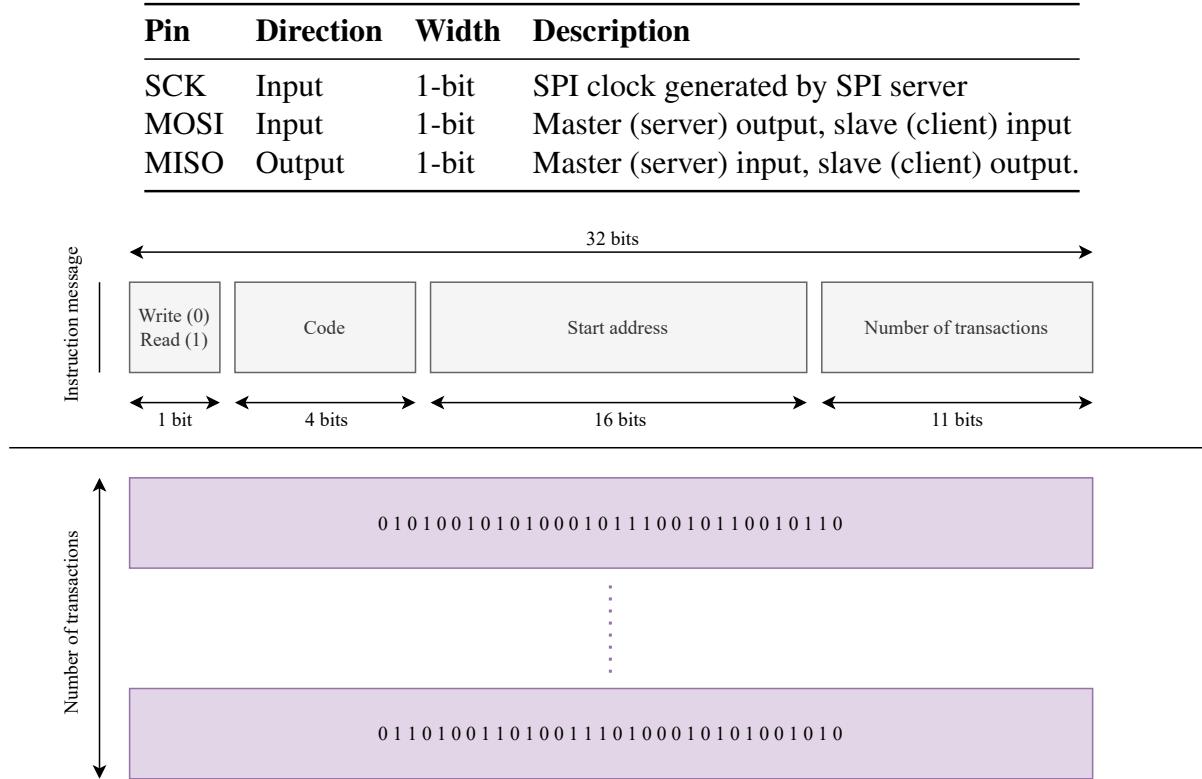

| 5.4      | Connectivity . . . . .                                                 | 74        |

| 5.4.1    | SPI bus . . . . .                                                      | 74        |

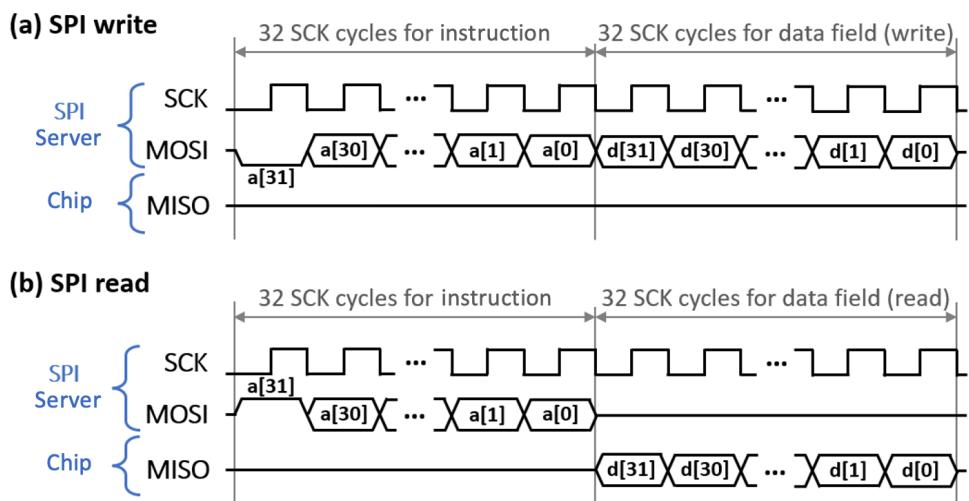

| 5.4.2    | High-speed in and out buses . . . . .                                  | 76        |

| 5.5      | Network controller . . . . .                                           | 77        |

| 5.5.1    | Survey of process and control alternatives . . . . .                   | 78        |

| 5.5.2    | Controller choice . . . . .                                            | 79        |

| 5.5.3    | Implementation . . . . .                                               | 80        |

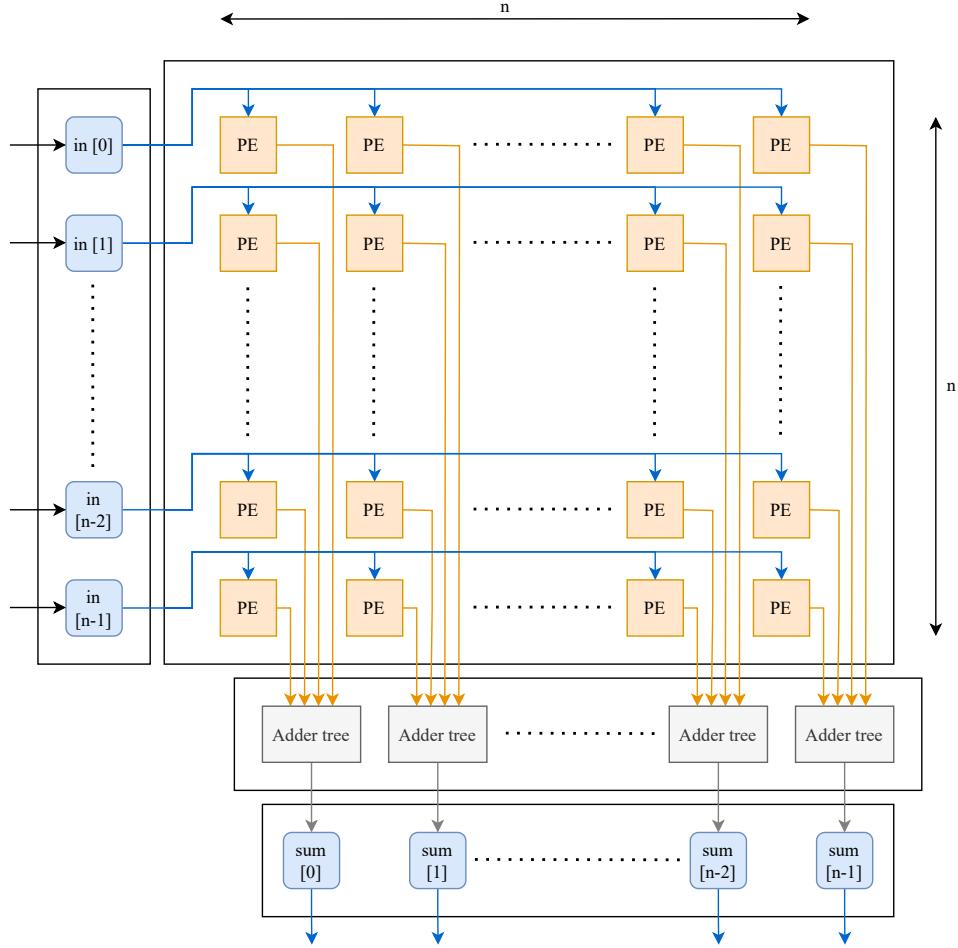

| 5.6      | Processing element array . . . . .                                     | 81        |

| 5.6.1    | Processing element design . . . . .                                    | 81        |

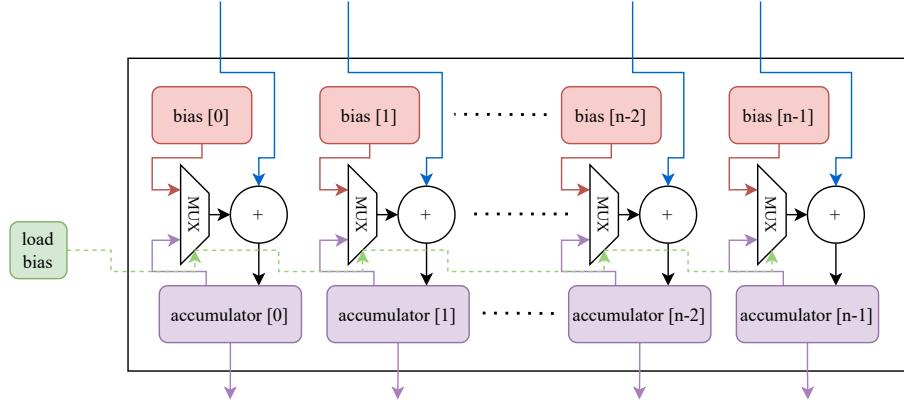

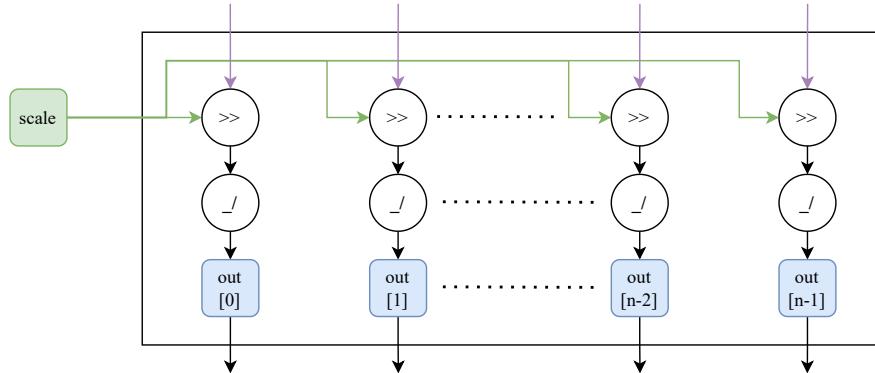

| 5.6.2    | Array design . . . . .                                                 | 82        |

| 5.6.3    | Post-processing . . . . .                                              | 83        |

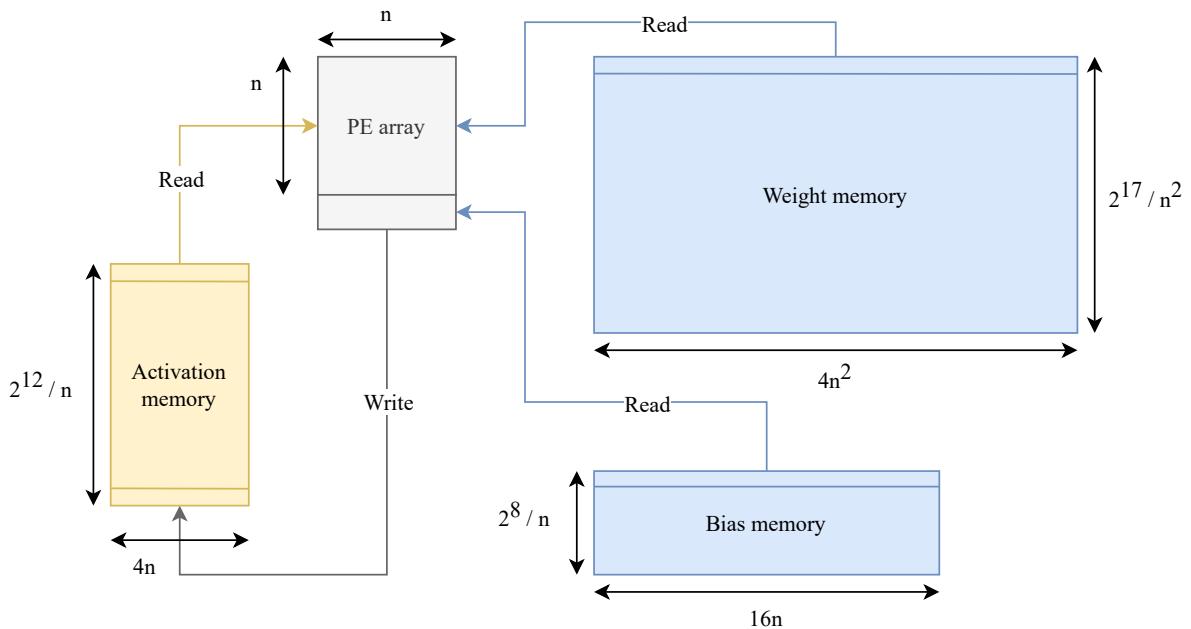

| 5.7      | Storage . . . . .                                                      | 84        |

| 5.7.1    | Generic storage setup . . . . .                                        | 85        |

|          |                                                                   |            |

|----------|-------------------------------------------------------------------|------------|

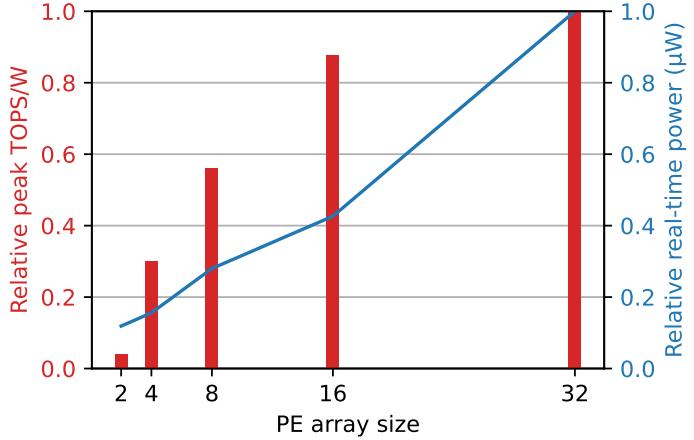

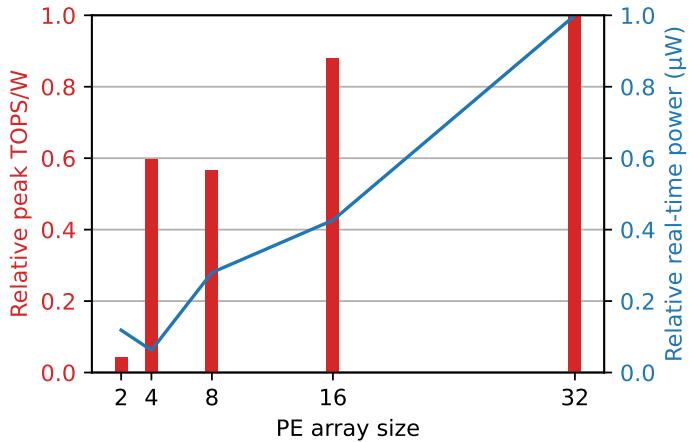

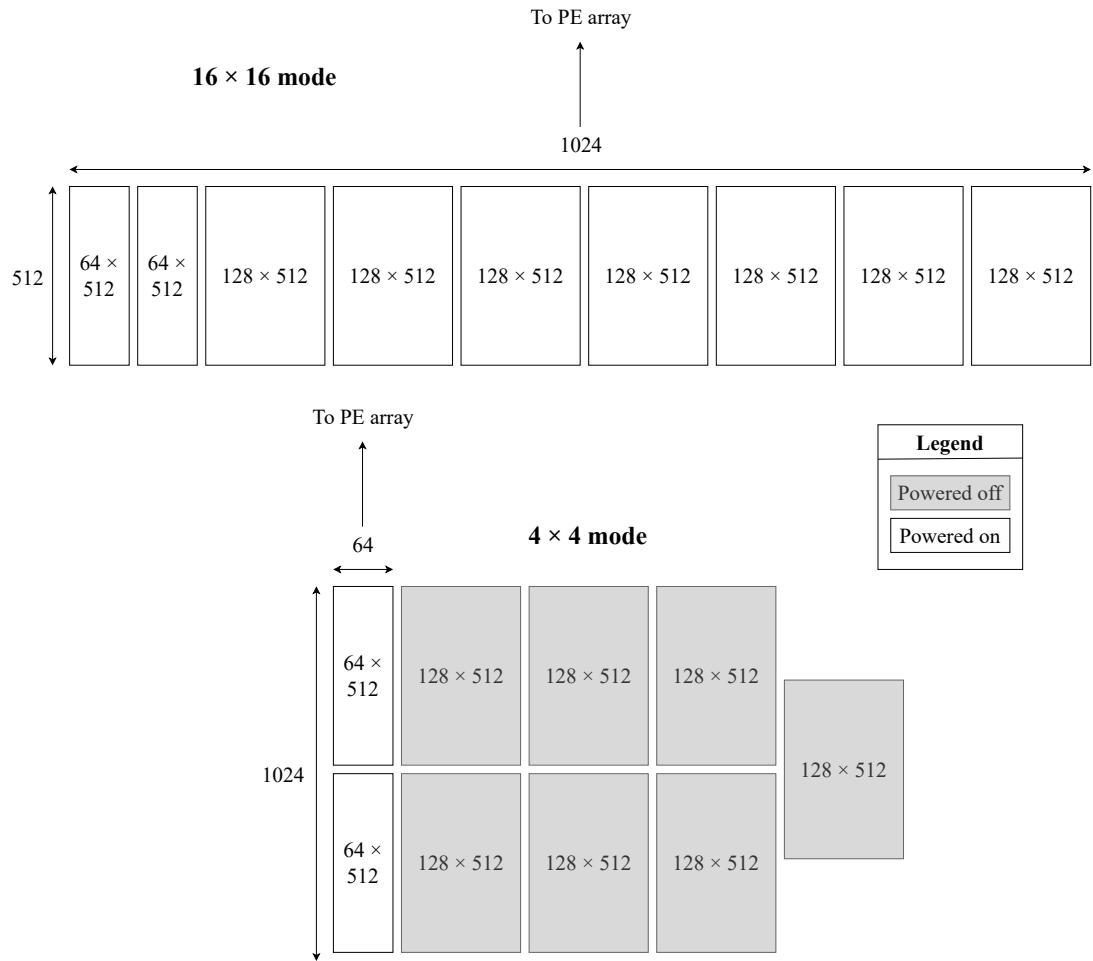

| 5.7.2    | PE array size determination . . . . .                             | 86         |

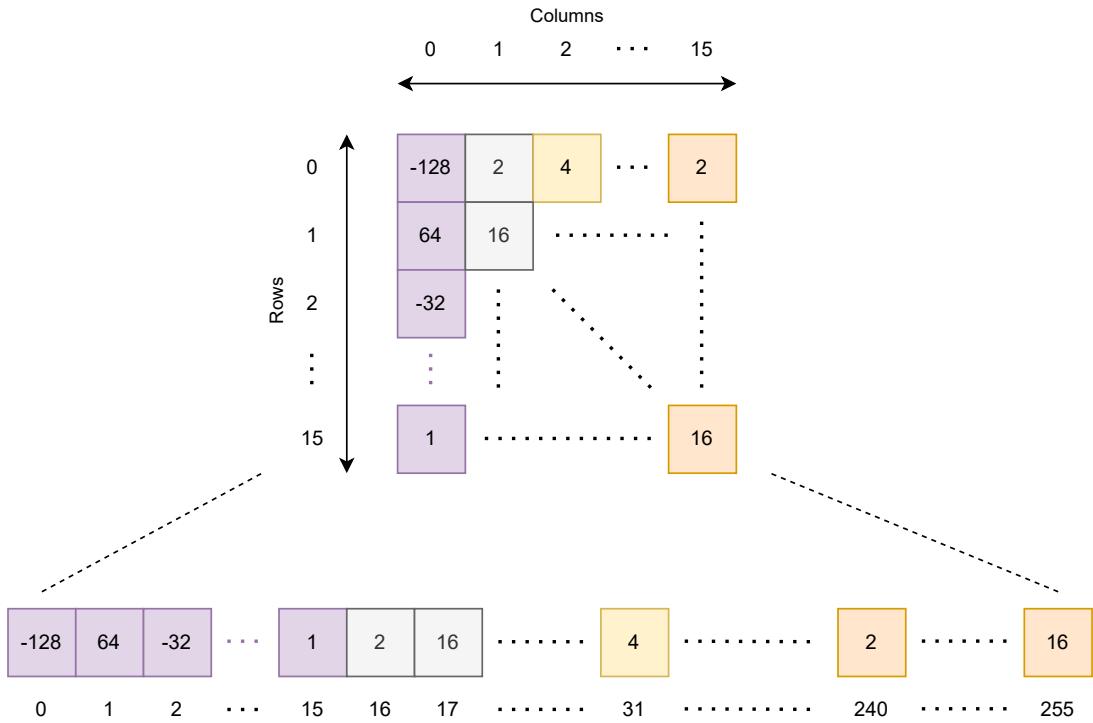

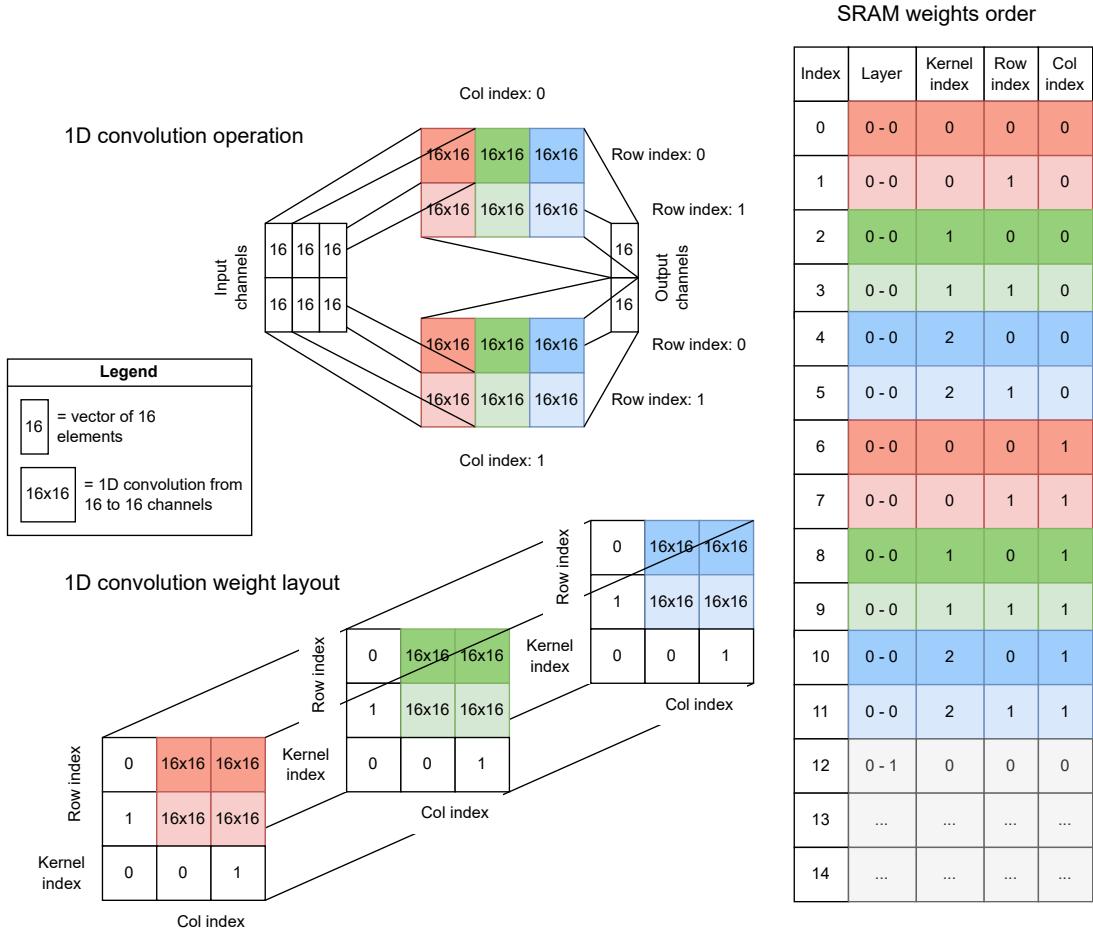

| 5.7.3    | Weight storage . . . . .                                          | 88         |

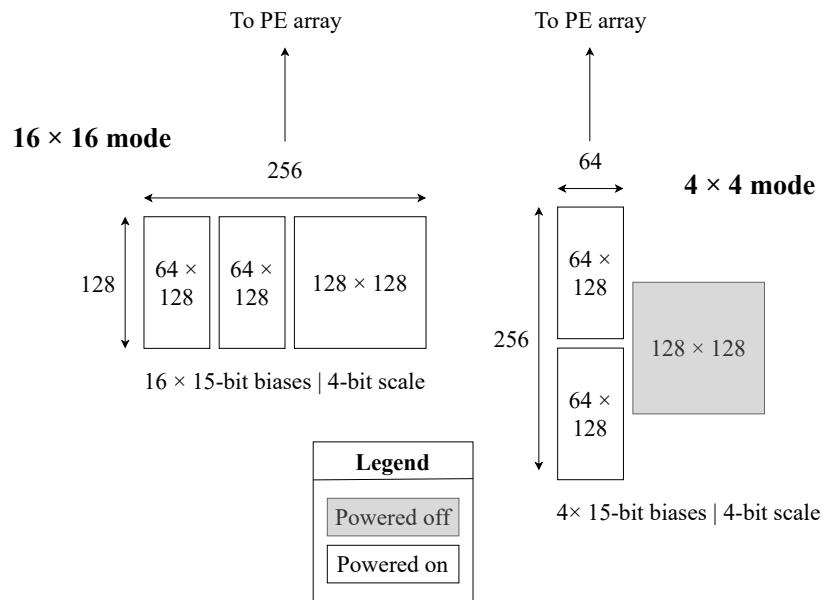

| 5.7.4    | Bias storage . . . . .                                            | 89         |

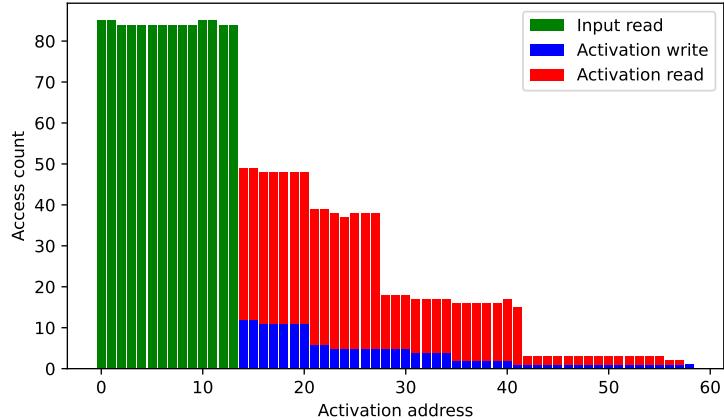

| 5.7.5    | Activation storage . . . . .                                      | 90         |

| 5.8      | Few-shot learning . . . . .                                       | 92         |

| 5.9      | Comparison with the state of the art . . . . .                    | 93         |

| <b>6</b> | <b>Conclusion and outlook</b>                                     | <b>98</b>  |

| 6.1      | Latest trends . . . . .                                           | 98         |

| 6.2      | Future work . . . . .                                             | 98         |

| <b>A</b> | <b>Metric learning formalization</b>                              | <b>111</b> |

| <b>B</b> | <b><i>miniImageNet</i></b>                                        | <b>111</b> |

| <b>C</b> | <b>MFCC with and without discrete cosine transform comparison</b> | <b>111</b> |

# 1 Introduction

Along with the increasing interest in edge computing [1], there is a growing need for deploying deep learning (DL) models on edge devices [2], enabling networked smart end-nodes and sensors that form the backbone of the Internet-of-Things (IOT) ecosystem [2]. However, the size and power limitations of these devices contrast with the processing requirements for traditional neural networks [2]. This challenge led to the creation of a new machine learning branch called tiny machine learning (tinyML). [3].

However, most modern tinyML devices are currently focusing on inference [2], exhibiting mostly *static* edge intelligence. This means that the machine learning model has to be trained before deployment [4] and is not able to adapt post-deployment, resulting in a system that cannot accommodate for data distribution shifts over time [2] or new features in data altogether. While the former can cause smart sensors to become unreliable after deployment [5], the latter can cause models to fail in situations that were not predicted before deployment [6].

One possible way to combat this problem is to upload locally sourced data to a centralized server, where it is used to extend the original training dataset [2]. The model then has to be retrained from scratch in order to emulate an independent and identically distributed (*i.i.d.*) dataset, which is necessary to ensure that the new data is taken into account during learning, without forgetting the original information [7]. After this, the new model has to be downloaded to the edge device, which is then able to perform accurate inference on the new data. However, this approach not only costs time, meaning that real-time data changes cannot be dealt with on-the-fly [4], it also requires the device to record, store, upload and download data throughout its life cycle. Furthermore, while the majority of developments linked to edge computing and low-cost machine learning models has historically focused on static image recognition, streaming data (e.g., temporal information such as sound or video) is actually much more representative of real-world edge scenarios, which implies the use of neural network architectures that are able to maintain a state over time.

As conventional retraining is therefore not an option for edge devices, on-device-learning emerges as a key requirement. However, a new challenge arises at the intersection of edge computing and data-efficient learning, which requires a minimal amount of data to acquire knowledge and adapt to new tasks. This challenge necessitates the development of learning algorithms that excel in scenarios where the use of conventional training methods is not feasible. Overall, endowing edge devices with the ability to learn new tasks and features from their environment with little data will directly contribute to:

- data privacy, which is increased by keeping the user data on-chip [1], [8],

- long-term robustness, which is improved as changes in tasks over time can be dealt with locally and in real time,

- electronic waste reduction, thanks to a longer device life cycle,

- maintenance costs reduction, thanks to a reduced reliance on over-the-air updates,

- a reduced dependence on communication network reliability in non-urban areas, as the cloud is removed from the learning process.

These advantages underscore the importance of advancing algorithms that have this ability. *Meta-learning*, a machine learning framework where models learn to learn efficiently, is among the most promising candidates to enable data-efficient learning at the edge. Therefore, the main

research question of this thesis is as follows:

*"How can meta-learning unlock low-cost adaptation to temporal data for deep neural network accelerator hardware at the edge?"*

To address this question, we highlight how meta-learning primarily relies on performing efficient feature extraction, allowing for the use of simple training and evaluation methods. We also show that temporal convolutional networks (TCNs) can be used as excellent feature extractors for temporal data. Building on this, we propose a TCN accelerator that fully removes the need for on-device gradient computation for few-shot learning, keeping the cost of learning good features where resources are abundant, i.e. in servers and cloud environments. The proposed approach also generalizes to continual learning for shifting data distributions, closing the loop back to robust edge intelligence. The main contributions of this work are:

- a first *in-silico* TCN<sup>1</sup> accelerator implementation,

- a first accelerator for few-shot learning, which performs on-chip temporal data classification via meta-learning and continual learning.

Guiding the reader towards these points, the thesis is structured as follows. First, Section 2 introduces relevant background information for understanding the developments at the core of this work. Section 3 then compares multiple architectures for sequence classification tasks, among which one is selected for hardware implementation. Next, Section 4 performs an initially a qualitative, then quantitative, analysis on meta-learning algorithms, from which the meta-learning algorithm and quantization approach for hardware implementation are chosen. The silicon implementation, which is based on these three design decisions, is then covered in Section 5. Finally, Section 6 presents the conclusion of the thesis by looking back and answering the main research question. An outlook for key applications and future work is also provided.

---

<sup>1</sup>A TCN as defined by Bai *et al.*, using exponentially increasing dilation and residual layers. 1D residual networks, also a type of TCNs, are excluded as they cannot be processed in a streaming fashion.

## 2 Background

In this section, the required background information for the claims made in this thesis will be presented. First, in Section 2.1, meta-learning and its suitability for edge computing will be discussed, after which in Section 2.2 the neural networks used in this work will be introduced. Finally, Section 2.3 covers the fundamentals of network quantization, which is necessary for deploying deep neural networks on edge devices.

### 2.1 Meta-learning

Meta-learning forms the core of the developments in this thesis. Therefore, a broad overview of the matter will be provided in this section. First, in Section 2.1.1 the need and applicability of meta-learning will be discussed. After that, in Section 2.1.2 a mathematical formalization of meta-learning is provided to aid the understanding of various meta-learning methods. Following this, Section 2.1.3 presents an overview of the meta-learning landscape, from which a subset of the methods will be covered in Section 2.1.4. This subset will then be qualitatively compared in Section 2.1.5. Three meta-learning benchmarks will then be discussed in Section 2.1.6. Finally, in Section 2.1.7, continual learning and its synergies with meta-learning will be explored.

#### 2.1.1 The need for data-efficient learning

The potency of modern machine learning models, as exemplified by the likes of AlphaGo [9], GPT-4 [10] and Llama 2 [11], emanates from the processing of vast volumes of (simulated) data. For example, the training set for Llama2 consisted of two trillion ( $10^{12}$ ) tokens [11]. Yet, environments where data quantity and computational resources are constrained are excluded from the successes achieved by such models: a challenge therefore emerges at the intersection of edge computing and data-efficient learning. In the space where conventional training paradigms find themselves tested, this challenge gives rise to the need for data-efficient and low-compute learning algorithms, which have the following advantages:

- data privacy is increased through keeping the user data on-chip [8],

- long-term robustness is improved as changes in tasks over time can be dealt with locally and in real-time,

- electronic waste is reduced due to a longer device life cycle,

- maintenance costs will be lower by reducing reliance on over-the-air updates.

One possible pathway to such ideal algorithms is through the application of *meta-learning*, which is a machine learning approach where models learn how to learn, enabling them to adapt quickly to new tasks with limited data. Using meta-learning avoids the need for large-scale data collection at the edge before a model can be extended with new capabilities: instead of requesting a user to repeat a set of gestures over several epochs before they can be classified, only a few examples are required for each new gesture.

Overall, meta-learning provides a promising pathway toward true edge intelligence, enabling more privacy-friendly systems and allowing for deployment in more unpredictable scenarios.

### 2.1.2 Formalizing meta-learning

In this section, a formal definition of meta-learning will be established, in order to have a standardized framework for the later evaluation of various meta-learning methods. Note that for the entirety of this section, the mathematical formalization from Hospedales *et al.* [12] is followed.

Starting off, first, conventional machine learning is formally introduced. For this, the following symbols are defined:

- $\theta$ : the parameters of the model.  $\theta^*$  are the optimal (inducing the lowest loss) model parameters,

- $f_\theta$ : the predictive model with parameters  $\theta$ ,

- $\omega$ : the information about how to perform learning, also referred to as "meta-knowledge". This can be a network architecture, initial network parameters, an optimization algorithm such as gradient descent or parameters that guide the learning, such as the learning rate: meta-knowledge can therefore be seen as a set of hyperparameters,

- $D = \{(x_1, y_1), \dots, (x_N, y_N)\}$ : an N-sample dataset containing samples  $(x_i)$  with corresponding labels  $(y_i)$ .  $D^{\text{train}}$  is a subset of  $D$  and represents the training dataset,

- $L$ : the loss function, measuring the error between the ground-truth labels  $(y_i)$  and predicted  $(\hat{y}_i)$  outputs.

Using these symbols, supervised learning can be formalized as

$$\hat{y}_i = f_\theta(x_i), \quad (1)$$

$$D^{\text{train}} \subset D, \quad (2)$$

$$\theta^* = \arg \min_{\theta} L(D^{\text{train}}; \theta, \omega). \quad (3)$$

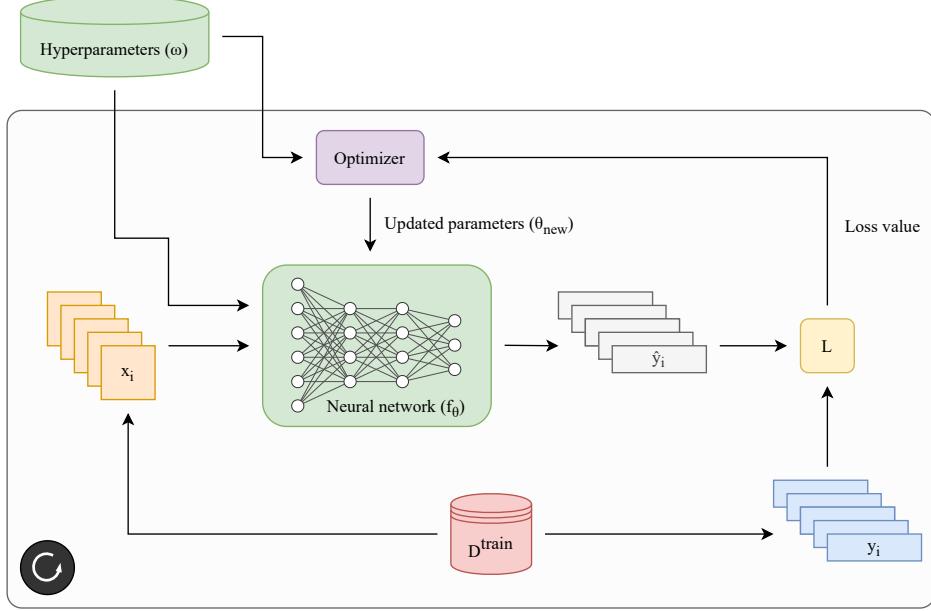

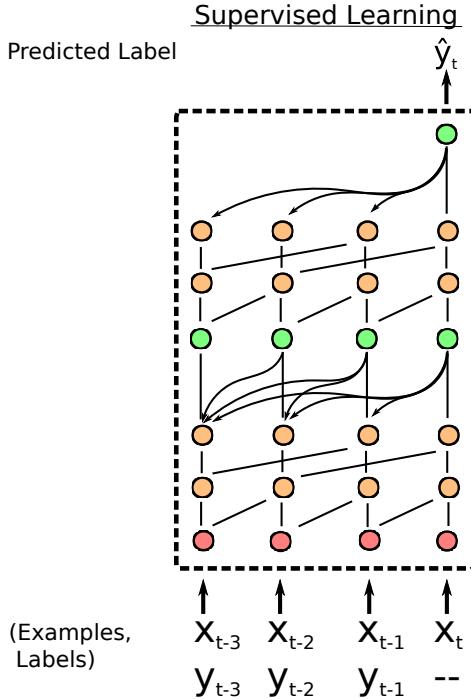

Note that Eqs. (1) to (3) can be represented by an optimization loop as shown in Fig. 1, since Eq. (3) cannot always be solved for explicitly and therefore requires an approximation by iteration. There are two important assumptions in this case [12]:

- $\omega$  is fixed or chosen by the user before training,

- $f_\theta$  is trained from scratch for every new task/dataset.

Consequently, specifying different values for  $\omega$  can have a drastic impact on the performance of the final learned model. However, when the search space is very large, manually finding the optimal  $\omega$  can be impractical. For example, when  $\omega$  represents all possible optimization hyperparameter values, it is not feasible to find the optimal set of values by hand, which is a well-known issue for large machine learning workloads [13].

The key idea of meta-learning is to view conventional machine learning as a process that can itself be optimized. Indeed, meta-learning is often referred to as "learning to learn" (a term first coined by Thrun *et al.* in [14]), indicating that unlike conventional machine learning methods, where a model is learned, it is learned how to optimally learn a model.

**Figure 1:** Overview of the conventional supervised learning pipeline. Hyperparameters  $\omega$  can influence both the optimization and the neural network as per the definition. The left-bottom circular arrow indicates that the steps in this figure, starting from the training dataset  $D^{\text{train}}$  and ending with the updated parameters,  $\theta$ , are repeated multiple times until  $\theta \approx \theta^*$ .

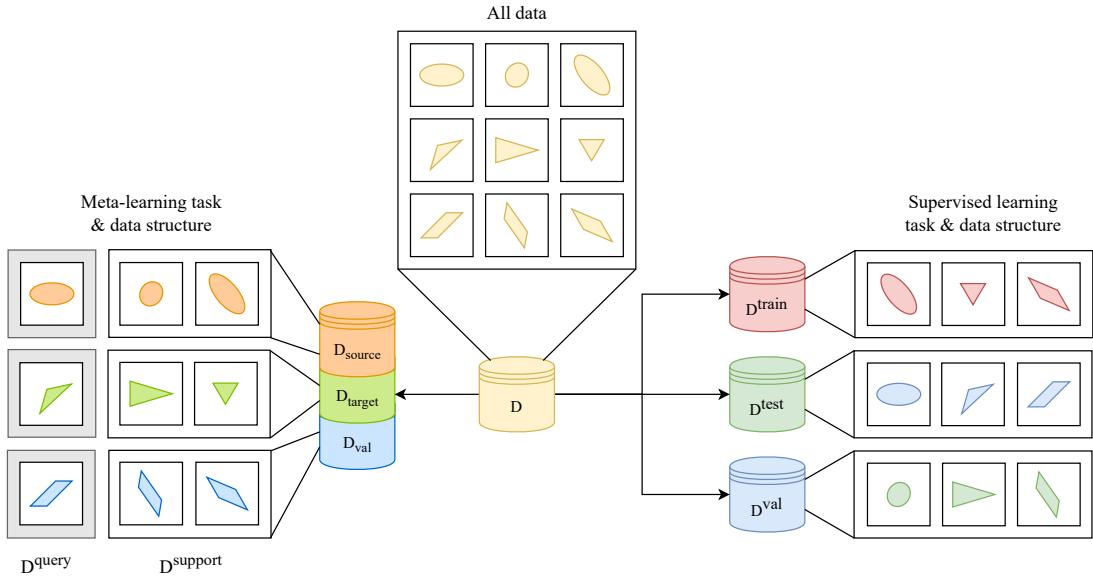

**Figure 2:** Splitting of dataset  $D$  for meta-learning (on the left) into  $D_{\text{source}}$ ,  $D_{\text{target}}$ ,  $D_{\text{val}}$  and for conventional supervised learning (on the right) into  $D^{\text{train}}$ ,  $D^{\text{test}}$  and  $D^{\text{val}}$ . Note how in the supervised setting, every split has the same classes, while in the meta-learning scenario, every split has unique classes.

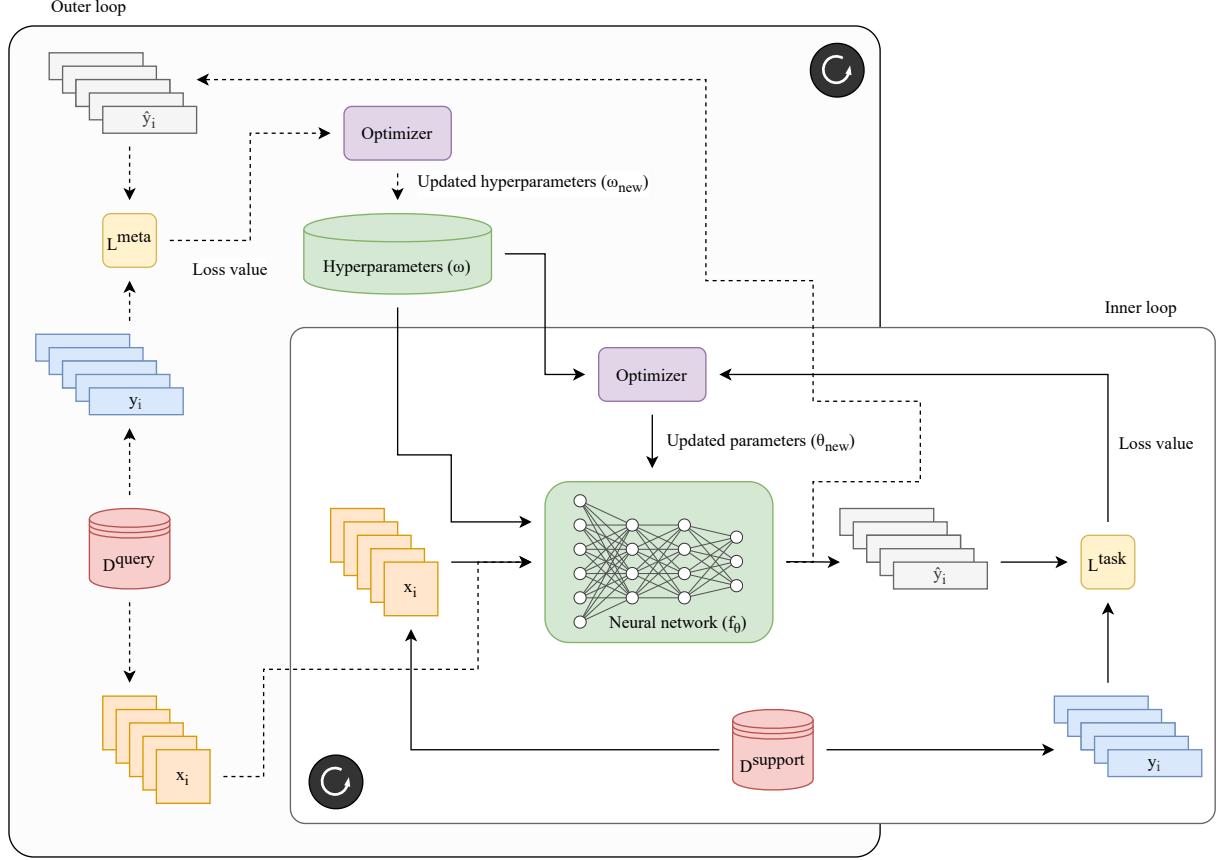

This formalization indicates that meta-learning can be viewed as a bilevel optimization problem [12]: there is an *inner loop*, where a model is learned (equivalent to supervised learning) and an *outer loop*, where this learning process is itself learned.

Therefore, in contrast to supervised learning, with meta-learning,  $\omega$  is **learned** and not assumed fixed. This means that an optimal value is found by a learning algorithm, just like this is the case for  $\theta$ . Furthermore, instead of being trained from scratch for every new task,  $f_\theta$  is

now meta-trained through a set of  $M$  tasks, with a *source* dataset  $D_{\text{source}}$  defined as

$$D_{\text{source}} = \left\{ \left( D_{\text{source}}^{\text{support}}, D_{\text{source}}^{\text{query}} \right)^{(i)} \right\}_{i=1}^M, \quad (4)$$

$$D_{\text{source}} \subset D.$$

This source dataset represents all the data that is available for meta-training before deployment. It consists of a *support* set and a *query* set, which can be assimilated to the training ( $D^{\text{train}}$ ) and test ( $D^{\text{test}}$ ) sets in conventional machine learning, respectively. This structure is displayed in Fig. 2, where also the validation sets ( $D^{\text{val}}$ ) are shown for both meta-learning and supervised learning.

Formalizing the extra level of optimization/learning for  $\omega$  [12] through this set of tasks, which is referred to as "meta-training", gives

$$\omega^* = \arg \min_{\omega} \sum_{i=1}^M L^{\text{meta}} \left( D_{\text{source}}^{\text{query}(i)}; \theta^{*(i)}(\omega), \omega \right), \quad (5)$$

$$\text{s.t. } \theta^{*(i)}(\omega) = \arg \min_{\theta} L^{\text{task}} \left( D_{\text{source}}^{\text{support}(i)}; \theta, \omega \right), \quad (6)$$

where  $L^{\text{meta}}$  and  $L^{\text{task}}$  represent the objectives in the outer and inner loops, respectively and  $\omega^*$  is the set of optimal hyperparameters. They can differ but do not have to: for example, when dealing with a set of regression tasks, both objectives are equal to the Euclidean distance function.

Graphically, the full nested optimization is shown in Fig. 3. Note that the inner loop of this figure is exactly the same as in Fig. 1, where  $D^{\text{support}} = D^{\text{train}}$  and  $L^{\text{task}} = L$ . Putting Eq. (3) and Eq. (6) side by side, it can indeed be seen that regular machine learning reduces to purely the inner loop. Also, similar to the assumptions for conventional machine learning, parameters  $\omega$  are fixed in the inner loop during meta-training.

After completing the meta-training phase, the learned meta-knowledge  $\omega$  is used for training the base model for a new target task  $i$ , taken from a set of  $Q$  tasks in a target dataset  $D_{\text{target}}$  (also see Fig. 2):

$$D_{\text{target}} = \left\{ \left( D_{\text{target}}^{\text{support}}, D_{\text{target}}^{\text{query}} \right)^{(i)} \right\}_{i=1}^Q, \quad (7)$$

$$D_{\text{target}} \subset D,$$

$$D_{\text{source}} \cap D_{\text{target}} = \emptyset.$$

The target support set  $D_{\text{target}}^{\text{support}}$  represents the example data that the user provides to the model for learning a new task, while the target query set  $D_{\text{target}}^{\text{query}}$  is the data used for inference after the examples have been shown. Training with each of the  $Q$  target tasks is called "meta-testing":

$$\theta^{*(i)} = \arg \min_{\theta} L^{\text{task}} \left( D_{\text{target}}^{\text{support}(i)}; \theta; \omega^* \right), \quad (8)$$

$$\hat{y}_i = f_{\theta^{*(i)}} \left( x_{\text{source}}^{\text{query}(i)} \right). \quad (9)$$

Meta-testing is exactly the same as the inner loop of meta-training and consequently the same as supervised learning (see Fig. 1). However, comparing Eq. (8) to Eq. (3), it can be seen

**Figure 3:** Graphical depiction of the bilevel optimization scheme of meta-learning. Dashed arrows represent information flow in the outer loop, whereas continuous lines represent information flow in the inner loop.

that the learning on the support set now benefits, after meta-learning, from the learned meta-knowledge about the algorithm to use, which is handpicked in the conventional case rather than part of an optimization problem.

Considering the full formalization, it can now be put into the context of learning at the edge. Firstly, the process of meta-training always occurs off-chip, typically carried out in environments such as the cloud or a local GPU cluster. Conversely, the phase of meta-testing is exclusively executed on-chip. This means that the design or complexity of the outer loop (Eq. (5)) does not influence the design or operation of the edge device that should perform learning. Consequently, an edge device that supports a certain inner loop for meta-testing automatically supports the deployment of any meta-learning method using that inner loop.

### 2.1.3 Taxonomy

With the formalization of meta-learning outlined, the different types of meta-learning methods can now be considered. However, due to the large variety in approaches [12], first, a meta-learning taxonomy is defined, from which a subset is selected for further study in this thesis.

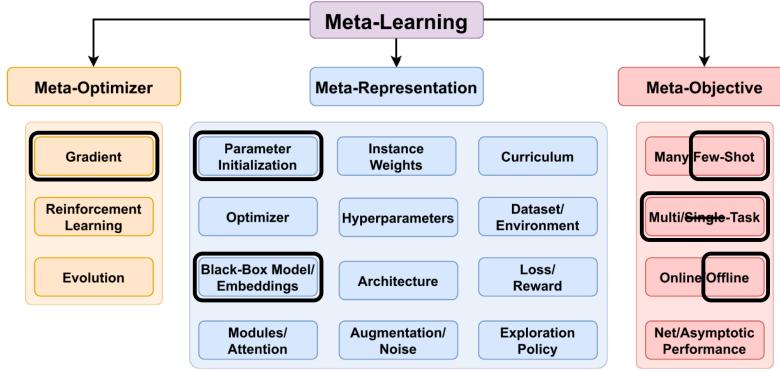

In this section, the taxonomy as introduced by Hospedales *et al.* [12] is used. This taxonomy contains the following three axes (see Fig. 4):

- **Meta-Optimizer:** defining **how** to learn. This indicates the choice of optimizer/learning algorithm for outer-loop optimization in meta-training (see Eq. (5)),

**Figure 4:** The meta-learning landscape, following the taxonomy proposed by [12]. Highlighted boxes indicate what is investigated in the thesis. Image adapted from [12].

- **Meta-Representation:** defining **what** to learn. This relates to the contents of  $\omega$ ,

- **Meta-Objective:** defining **why** to learn. This relates to the goal of the meta-learning setup, which is set by choosing  $L_{meta}$  (see Eq. (5)), the task distribution and the interactions between both optimization levels [12].

Considering the meta-training formalization of Eqs. (5) to (6), the mentioned axes can be color-coded as follows:

$$\omega^* = \arg \min_{\omega} \sum_{i=1}^M L^{\text{meta}} \left( D_{\text{source}}^{\text{query}(i)}; \theta^{*(i)}(\omega), \omega \right), \quad (10)$$

$$\text{s.t. } \theta^{*(i)}(\omega) = \arg \min_{\theta} L^{\text{task}} \left( D_{\text{source}}^{\text{support}(i)}; \theta, \omega \right). \quad (11)$$

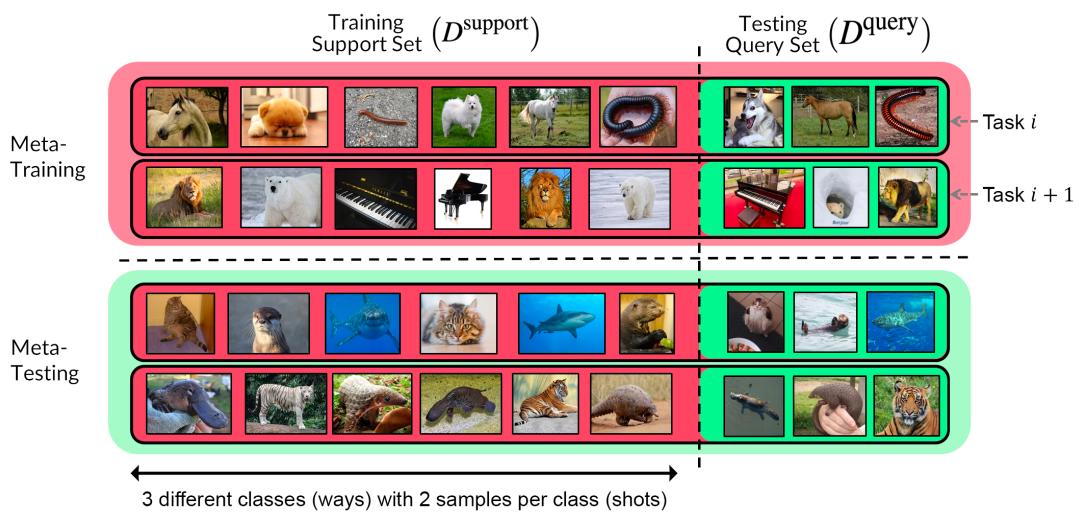

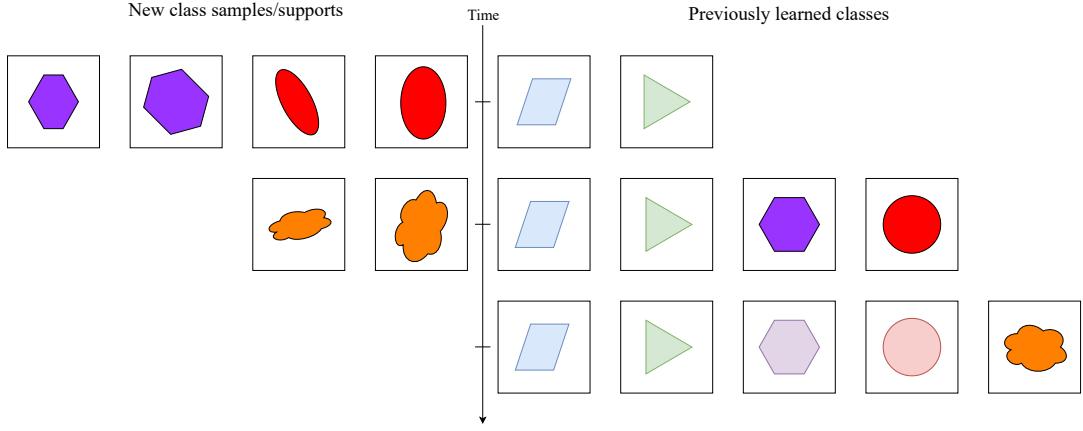

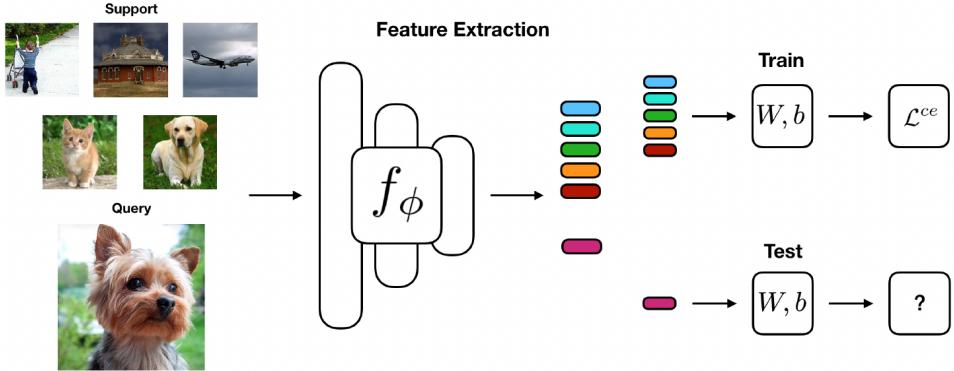

For each axis, highlighted boxes in Fig. 4 indicate the selection of the meta-learning landscape for this thesis. This subset is chosen to fit the use case of this work: few-shot sequential data classification at the edge. *Few-shot* indicates here that only a low number of samples is available for training, which is often the case at the edge. Meta-training is then used to train a model for such few-shot classification tasks. Generally, few-shot learning can be seen as a subset of meta-learning: a model learns to classify previously unseen inputs using  $k$  labeled examples (*shots*). The number of classes that the model learns for a new task is referred to as *ways*. A visual overview of this can be found in Fig. 5. Based on this use case, the following explanation outlines the selected subset for each axis and the rationale behind these choices.

- Starting with the meta-optimizer axis, only methods that use *gradient descent* for optimization are considered. Reinforcement learning is often used when  $f_\theta$  or  $L_{meta}$  is non-differentiable [12], while evolutionary algorithms only work well for smaller models [12]. Since, in this thesis, fully differentiable neural networks for classification will be used, containing a minimum of 10k parameters, gradient-based methods are best suited for this situation.

- For the meta-representation axis, only *parameter initialization* and *black-box model/ embeddings* are considered. This choice is made as the other meta-representations do not have a straightforward hardware implementation (see Section 4.1).

- Finally, in this work, there is only a single meta-objective as per the use case. The three marked options together form this objective: few-shot multi-task offline learning. A *few-shot* learning setup is chosen, as it is assumed that a low number of examples/shots (1-20) will be available at the edge. The reason for the objective being *multi-task*, is that after meta-training, the learner is expected to solve any task taken from the  $D_{\text{target}}$  set instead of simply solving one specific task. More specifically, the model is trained to learn different classes for every task as shown in Fig. 5, where for task  $i$ , the classes *horse*, *dog* and *worm* are learned, while in task  $i + 1$  the classes *piano*, *polar bear* and *lion* are learned. Lastly, *offline* indicates that during meta-testing, only inner-loop updates are performed, while in the *online* case, outer-loop updates can be performed during meta-testing, which does not correspond to the selected edge scenario.

Since only the meta-representation axis is not yet fixed by the research question of this thesis, this axis will be the main focus of the next section.

**Figure 5:** Example of meta-training and meta-testing with a 3-way 2-shot task.<sup>2</sup>

## 2.1.4 Meta-learning algorithms

Using the formalization and categorization described, this section will cover different meta-learning algorithms, grouped by meta-representation ( $\omega$ ).

Note that while the black-box model and embeddings are combined to form one category in the taxonomy of Fig. 4, in this work, they are treated separately as they vary significantly at a high level. However, it is possible to formulate all embedding methods as special forms of black-box models [12], hence why they are shown combined.

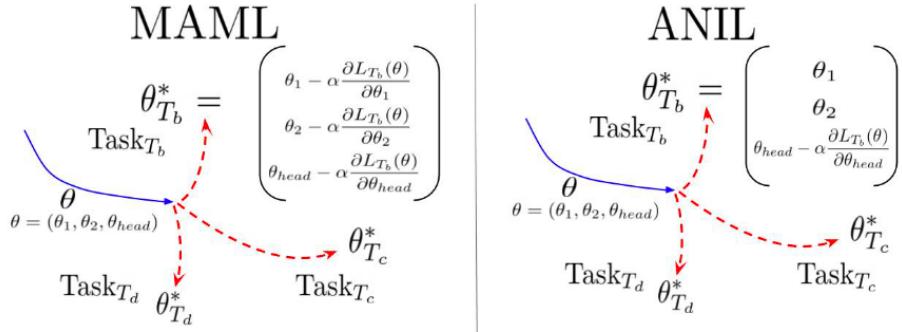

**2.1.4.1 Learning an initialization** In the first category,  $\omega$  represents the initial values of the neural network parameters for the inner optimization step (see Eq. (6) and Eq. (8)). Model-agnostic meta-learning (MAML) [15] is one of the most popular algorithms in this space [12]. The goal of MAML is to learn a good network initialization so that only a few steps of gradient descent are required to update the network for a new task, instead of requiring many iterations.

<sup>2</sup>Image adapted from [https://iclr-blog-track.github.io/2022/03/25/understanding\\_mtr\\_meta/](https://iclr-blog-track.github.io/2022/03/25/understanding_mtr_meta/).

Within the context of edge computing, this translates to the inner-loop edge device adapting with only a few iterations. In Algorithm 1, the steps of MAML are displayed. The **foreach** loop represents the inner optimization loop as per Eq. (6), while line 12 represents the outer optimization loop as per Eq. (5). Note that performance can be improved by performing multiple gradient descent steps in the inner loop (i.e.  $k > 1$ ). This inner-outer optimization is repeated until convergence or after a fixed number of repetitions. After convergence, meta-testing is performed to calculate the final performance.

---

**Algorithm 1:** Pseudocode for meta-training via model-agnostic meta-learning (MAML) where  $g$  indicates the gradient. Based on [16].

---

**Data:** step size hyperparameters  $\alpha, \beta$ ; number of inner loop gradient descent steps  $k$

- 1 initialize  $\omega$  with any strategy;

- 2 **repeat**

- 3     **foreach**  $D_{\text{source}}^{(i)} \in D_{\text{source}}$  **do**

- 4         initialize  $\theta_i$  with  $\omega$ ;

- 5         take  $\{D_{\text{source}}^{\text{support}(i)}, D_{\text{source}}^{\text{query}(i)}\} = D_{\text{source}}^{(i)}$ ;

- 6         **for**  $i \leftarrow 0$  **to**  $k$  **do**

- 7             evaluate  $g = \nabla_{\theta_i} L^{\text{task}}(D_{\text{source}}^{\text{support}(i)}, \theta_i)$ ;

- 8             update  $\theta_i \leftarrow \theta_i + \alpha g$ ;

- 9         **end**

- 10         evaluate test loss  $L_i = L^{\text{task}}(D_{\text{source}}^{\text{query}(i)}, \theta_i)$ ;

- 11     **end**

- 12     update  $\omega \leftarrow \omega - \beta \sum_{D_{\text{source}}^{(i)} \in D_{\text{source}}} \nabla_{\omega} L_i$ ;

- 13 **until** convergence;

---

One of the downsides of MAML is that it requires computing second-order gradients for all parameters in the network. This can be seen by substituting lines 6-10 (assuming  $k = 1$ ) into line 12 in Algorithm 1, after which the  $\nabla$  operator appears twice (see Eq. (12)). This makes training, especially for larger networks, rather slow. To resolve this, the authors propose a first-order approximation of MAML (FOMAML) [15], where the red part in Eq. (12) is treated as a constant [17]. This results in almost equivalent performance compared to regular MAML.

$$\omega \leftarrow \omega - \beta \sum_{D_{\text{source}}^{(i)} \in D_{\text{source}}} \nabla_{\omega} L^{\text{task}} \left( D_{\text{source}}^{\text{query}(i)}, \theta_i + \alpha \nabla_{\theta_i} L^{\text{task}} \left( D_{\text{source}}^{\text{support}(i)}, \theta_i \right) \right) \quad (12)$$

Due to its flexibility, MAML has inspired many derivative works. MAML++ [18] extends MAML with a set of changes to the meta-training procedure to stabilize training. Reptile [17] builds on top of the first-order MAML approximation by repeatedly sampling tasks and updating  $\omega$  with a gradient equal to the difference in weights before and after each task (see Algorithm 2).

Sign-MAML [19] also uses the first-order approximation method, but only considers the sign of the gradient. Orthogonally, MetaSGD [20] uses a vector  $\mathbf{a}$  instead of a scalar for  $\alpha$  in Algorithm 1 and makes it learnable by updating it after line 12 via  $\mathbf{a} \leftarrow \mathbf{a} - \beta \sum_{D_{\text{source}}^{(i)} \in D_{\text{source}}} \nabla_{\mathbf{a}} L_i$ . MetaCurvature [21] is similar to MetaSGD, but uses a matrix  $M$  instead of a vector  $\mathbf{a}$ . Overall, while all of these methods improve the baseline in data efficiency or generalization performance, MAML remains a simple yet elegant initialization baseline for meta-learning [18].

---

**Algorithm 2:** Pseudocode for Reptile. Based on [17].

---

**Data:** step size hyperparameter  $\alpha$ ; number of inner loop gradient descent steps  $k$

- 1 initialize  $\omega$  with any strategy;

- 2 **foreach**  $D_{\text{source}}^{(i)} \in D_{\text{source}}$  **do**

- 3     initialize  $\theta_i$  with  $\omega$ ;

- 4     take  $\{D_{\text{source}}^{\text{support}(i)}, D_{\text{source}}^{\text{query}(i)}\} = D_{\text{source}}^{(i)}$ ;

- 5     **for**  $i \leftarrow 0$  **to**  $k$  **do**

- 6         evaluate  $g = \nabla_{\theta_i} L^{\text{task}}(D_{\text{source}}^{\text{support}(i)}, \theta_i)$ ;

- 7         update  $\theta_i \leftarrow \theta_i + \alpha g$ ;

- 8     **end**

- 9     update  $\omega \leftarrow \omega + \alpha(\theta_i - \omega)$ ;

- 10 **end**

---

**2.1.4.2 Feed-forward models** In feed-forward or black-box meta-learning approaches,  $\omega$  represents the parameters of a model that provides a direct feed-forward mapping from the support samples ( $D^{\text{support}}$ ) to parameters required to perform predictions on query samples ( $D^{\text{query}}$ ) [12]. Therefore, in contrast to initialization-based methods, feed-forward meta-learning methods do not require gradient updates to solve Eq. (8).

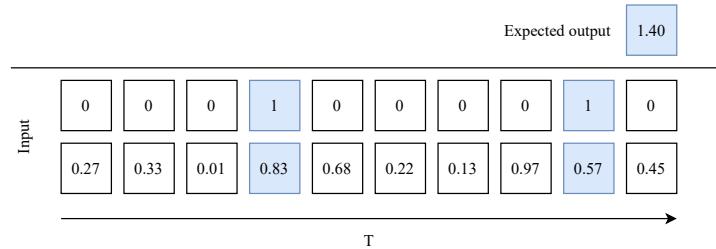

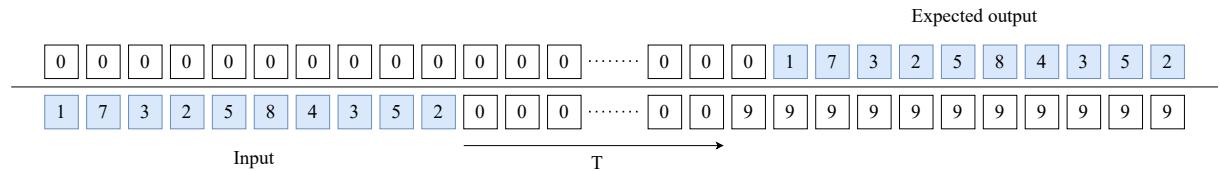

One well-known feed-forward method is the simple neural attentive meta-learner (SNAIL) proposed by Mishra *et al.* [22]. SNAIL effectively converts meta-learning to a sequence-to-sequence task, as shown in Fig. 6. In written language, a prompt for such a task would be: "5 times 3 is 15; 6 times 3 is 18; 4 times 3 is 12; 8 times 3 is \_\_\_\_". The model then, in an autoregressive fashion, predicts after three labeled examples (supports) the outcome of the last (queried) sample.

**Figure 6:** Overview of SNAIL.  $(x_{t-3}, y_{t-3})$  to  $(x_{t-1}, y_{t-1})$  represent the support samples  $D^{\text{support}}$  while  $(x_t, y_t)$  represents a single query sample from  $D^{\text{query}}$ . Figure taken from [22].

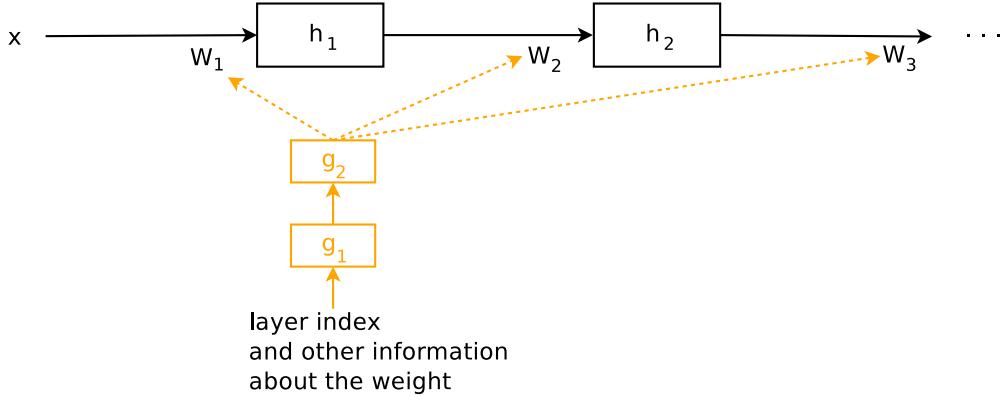

Another idea in feed-forward approaches is a concept called *hypernetworks* [23], where a network generates the parameters of another network. In terms of formalization, a hypernetwork with parameters  $\omega$  generates parameters  $\theta$  for a main network based on  $D^{\text{support}}$ .

The main network operates similarly to a typical neural network, as it is responsible for mapping raw inputs to their intended targets. Conversely, the hypernetwork receives inputs that encapsulate weight structure information and produces the corresponding weights for a given layer.

**Figure 7:** Visualization of a hypernetwork. Black connections and parameters are part of the main network, whereas orange connections and parameters are part of the hypernetwork;  $g_1, g_2$  and  $h_1, h_2$  are the activations from the hidden layers of the hypernetwork and the main network, respectively. The main network weights  $W_1, W_2$ , etc. are subsequently generated from the hypernetwork. Taken from [23].

Recently, Zhao *et al.* applied this technique to few-shot learning [24], achieving similar performance to Meta-SGD [20]. A similar approach is proposed by Qiao *et al.* in [25], where the final-layer parameters of the model are predicted from the activations of the support data ( $D^{\text{support}}$ ).

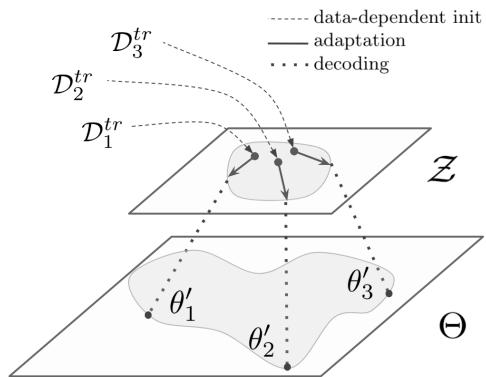

Orthogonally, Rusu *et al.* propose *latent embedding optimization* (LEO) in [26], which effectively combines MAML with a feed-forward model in the inner loop. In this approach, a latent code  $z$  that has lower dimensionality than  $\theta$  is conditioned on  $D^{\text{support}}$  through parameters  $\omega$ . This vector  $z$  is then mapped to parameters  $\theta$  which perform the classification. This process is visualized in Fig. 8. The main advantage of this approach is that MAML now does not optimize in the high-dimensional space of  $\theta$ , but in the low-dimensional space of  $z$  [26].

**Figure 8:** Visualization of the key idea from LEO, where optimization now takes place in the lower dimensional space  $Z$  instead of  $\Theta$ . Taken from [26].

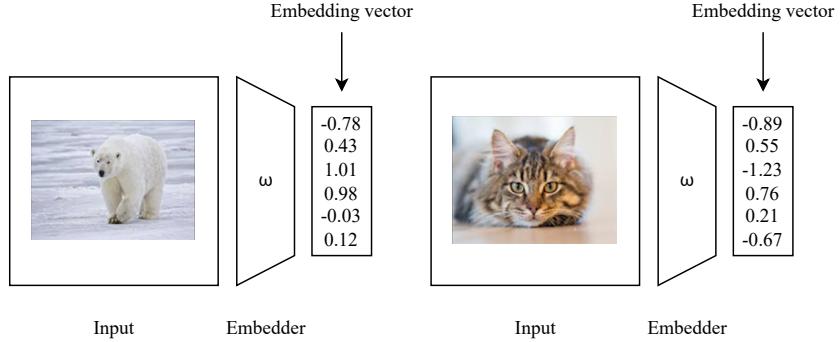

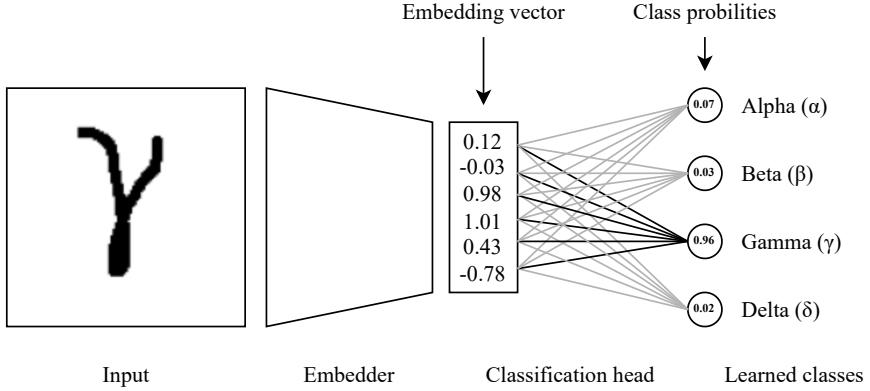

**2.1.4.3 Metric learning** In embedding methods or metric learning,  $\omega$  represents the parameters of an embedding network, generating  $M$ -dimensional vector representations from input samples (see Fig. 9). Using these embeddings, the classification of unseen samples can be performed without any gradient updates, similar to feed-forward methods. As the exact way classification is performed varies per algorithm, a detailed workout of metric learning following the formalization of meta-learning is provided in Appendix A.

**Figure 9:** Example of generating an  $M = 6$ -dimensional embedding from an input image. Notice how the dimensionality of the input is severely reduced, going from a full-color image to only six scalars.

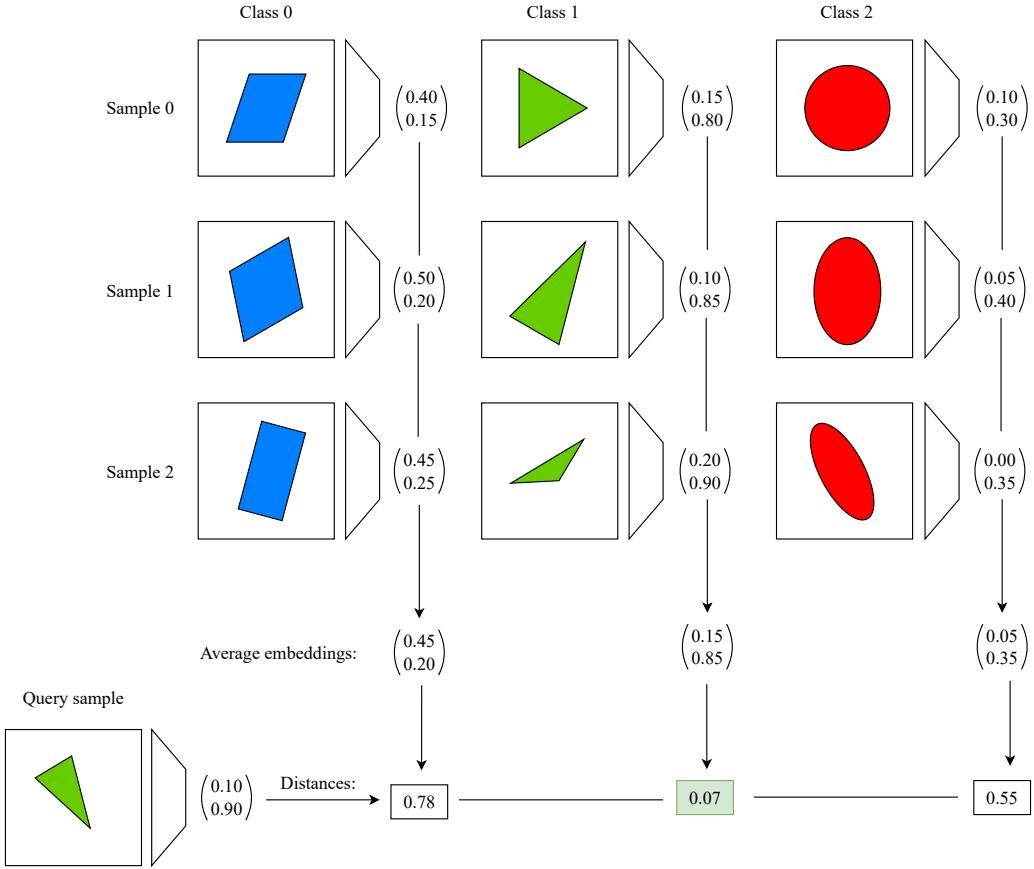

Prototypical networks are one of the most popular metric learning algorithms, proposed by Snell *et al.* in [27]. In this method, the  $M$ -dimensional embeddings for each sample  $x_i$  of class  $k$  in a set of labeled examples  $S_k$  are averaged into a "prototype"  $c_k$  [27]:

$$c_k = \frac{1}{|S_k|} \sum_{(x_i, y_i) \in S_k} f_{\omega}(x_i). \quad (13)$$

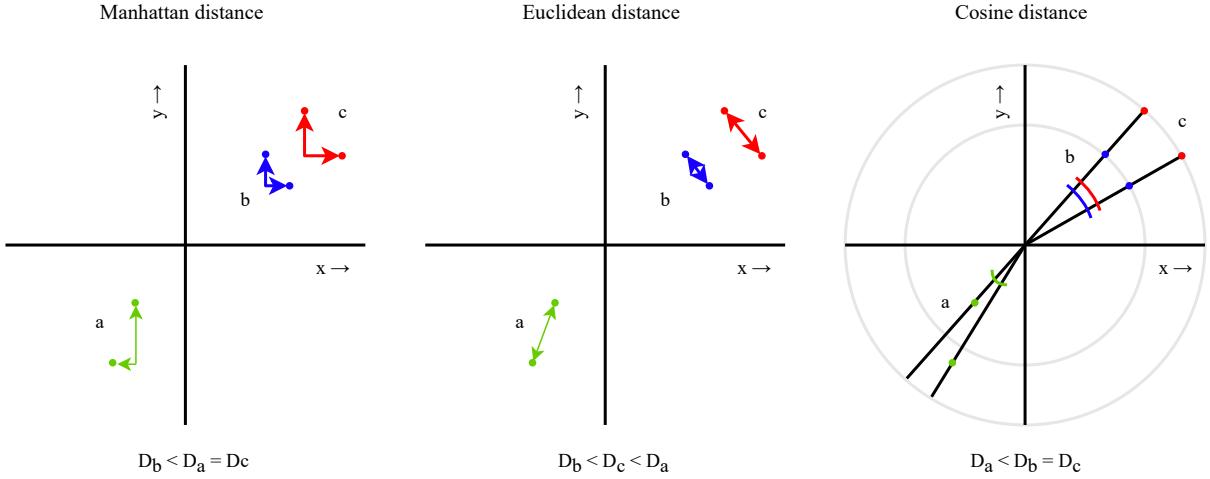

Illustrated in Fig. 10, is that classification then takes place by comparing the embedding from the query sample with the prototypes of all support classes through a distance function  $d: \mathbb{R}^M \times \mathbb{R}^M \rightarrow [0, +\infty)$  [27]. The class of the prototype with the lowest distance to the query embedding is assigned to the query. Since any distance metric  $d$  works in this setting, two popular distance metrics are compared: squared Euclidean distance and cosine distance. The authors then empirically find that squared Euclidean distance gives better few-shot classification accuracy.

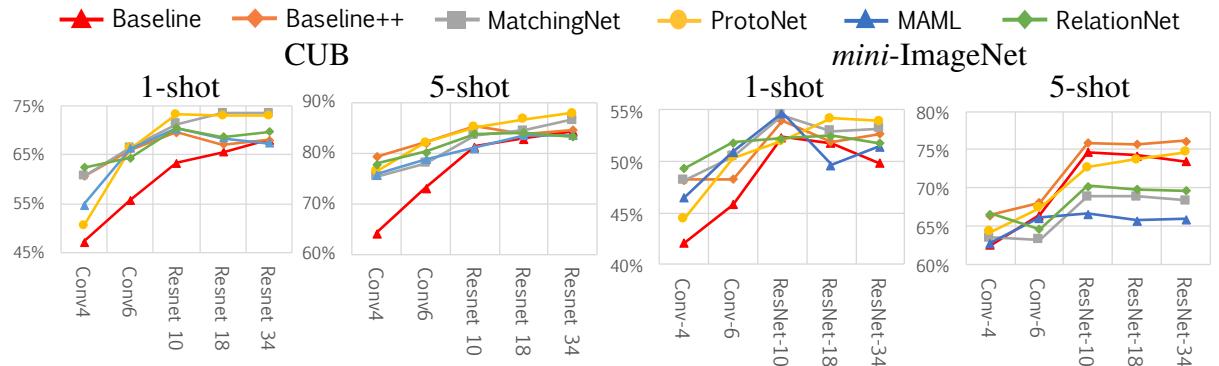

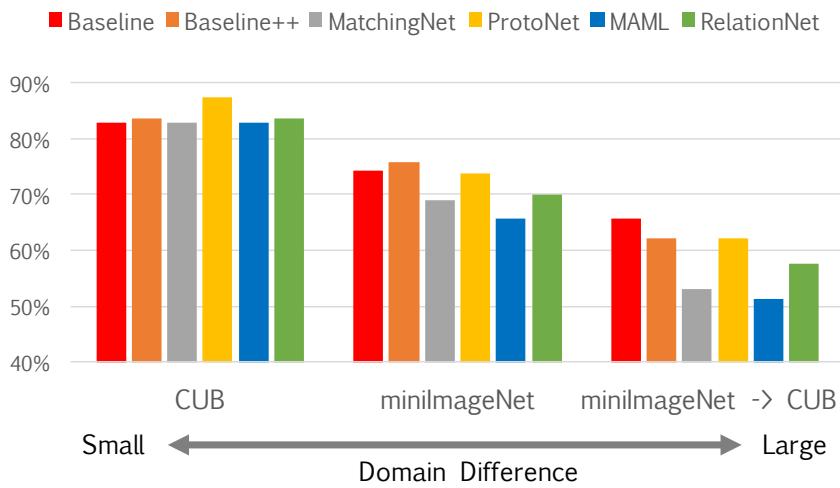

As opposed to prototypical networks, which are trained with a set of tasks using the bi-level meta-learning structure, the *Baseline++* method from Chen *et al.* [28] simply pre-trains an embedder using normal supervised learning on all data in  $D_{\text{source}}$ . Evaluation is then performed using cosine distance between support and query embeddings, similar to prototypical networks.

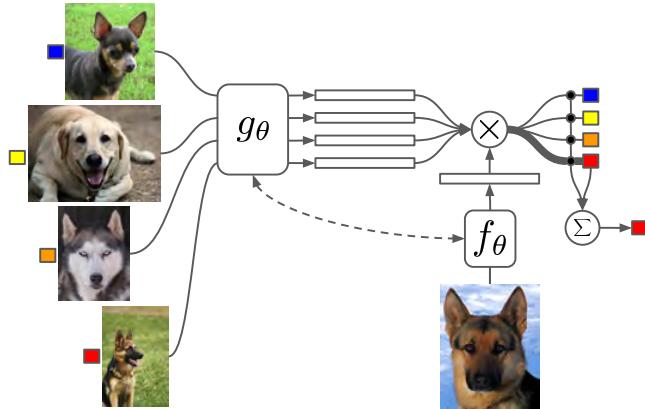

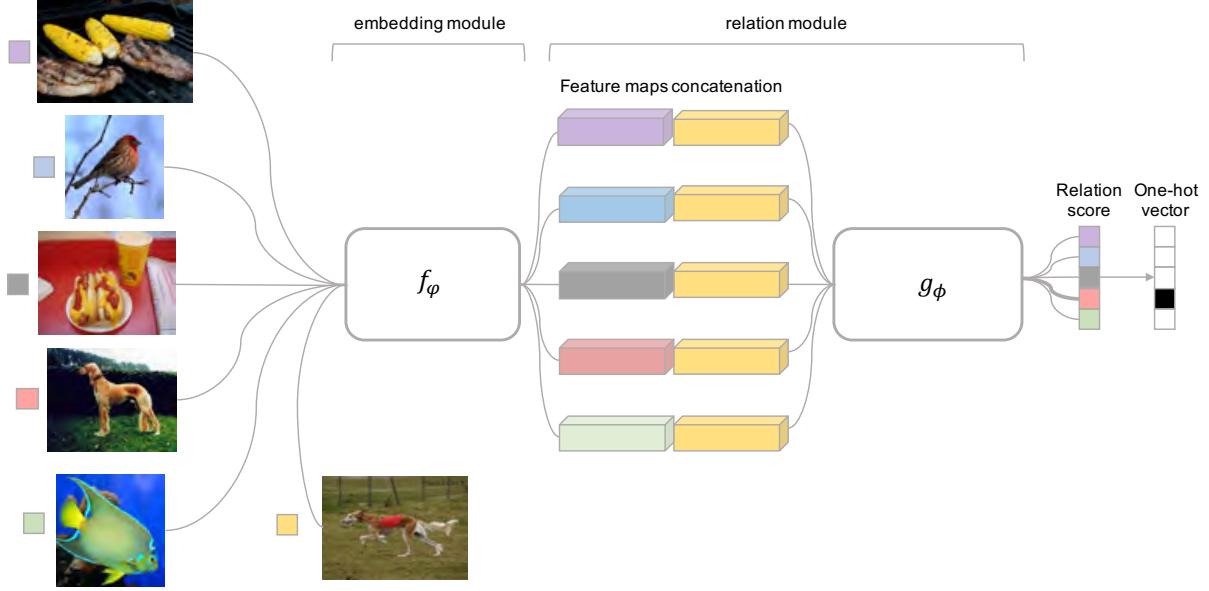

Note that metric learning methods do not have to rely on a distance algorithm by definition. For example, *matching networks* [29] use an attention mechanism over the support embeddings combined with the query embeddings to predict the class of the query sample (see Fig. 11) while, in *relation networks* [30], a "relation module" that produces a similarity score between support and query samples is employed (see Fig. 12). However, even with such constructions, metric learning methods suffer from one downside compared to initialization-based and feed-forward-based methods: they only work for classification problems [1]. For example, during classification, the output embedding is used to compare with other embeddings. This is due to the fact that embeddings do not mean anything for the continuous input and output space of regression tasks.

**Figure 10:** Example evaluation of a prototypical network in a 3-way 3-shot scenario with Euclidean distance as a loss function. The class of the prototype with the lowest distance is assigned to the incoming query sample. The trapezia represent the embedder.

**Figure 11:** Matching network architecture for a 4-way 1-shot problem with one query sample, where  $g_\theta$  and  $f_\theta$  are two (potentially identical) embedders and  $\times$  is an attention mechanism. Taken from [29].

## 2.1.5 Qualitative algorithm comparison

Having covered a variety of meta-learning methods, a qualitative comparison is displayed in Table 1. It lists all the discussed methods, ordered by appearance in the text and line-separated by meta-representation. Per method, the key idea(s), the on-chip friendliness, as well as the key advantages and disadvantages are listed.

**Figure 12:** Relation network architecture for a 5-way 1-shot problem with one query sample, where  $f_\phi$  is any embedder and  $g_\phi$  is the relation network. Taken from [30].

For brevity reasons, on-chip friendliness is a visual score based loosely on three criteria: meta-testing complexity (or the control complexity thereof), total required computation steps and memory usage. The first aspect mainly affects design complexity and testability, while the second impacts the real-time constraints as well as power usage. The third aspect not only concerns power usage but also the total silicon area and thus the overall cost.

Among the surveyed methods, the need for gradient descent during meta-testing is considered one of the largest disadvantages as it negatively affects all three aspects: it significantly increases complexity, requires more computation steps than pure inference and needs larger memories to store the intermediate activations for gradient calculation. Next to this, extra modules besides the main network during meta-testing are also considered a disadvantage as they directly imply extra hardware overhead.

The two highest-scoring methods in this on-chip friendliness score are prototypical networks [27] and the Baseline++ method from [28]. Both of them then do not require on-chip gradient descent and only compare embeddings during meta-testing. This means that, on top of the network, extra on-chip storage is only required for the averaged embeddings. However, neither of them is state-of-art in terms of few-shot classification accuracy compared to some of the more complex methods such as MAML++ [18] or LEO [26].

Hence, in order to accelerate the adoption of meta-learning for edge devices, novel yet simple methods (i.e. gradient-free) are required that offer similar or better few-shot classification accuracy than the more complex methods.

### 2.1.6 Benchmarks

Beyond qualitative comparisons, in order to quantitatively compare the performance of different meta-learning methods, standardized benchmarks are required. This section covers two such benchmarks: Section 2.1.6.1 reviews the Omniglot dataset [31] while Section 2.1.6.2 discusses (few-shot) keyword spotting. Both of these will be used as guiding tasks throughout this work,

**Table 1:** Qualitative comparison between the introduced meta-learning methods. In the on-chip friendly?-column, indicates very low, while indicates very high.

| Name                                   | Key idea(s)                                                                                             | On-chip friendly? | Advantages                                                  | Disadvantages                                                         |

|----------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------|-----------------------------------------------------------------------|

| MAML [15]<br>MAML++ [18]               | Model-agnostic meta-learning<br>= MAML + improved training procedure<br>= gradient descent on each task |                   | Simple performance<br>Better performance than baseline MAML | Requires gradient descent<br>Complex setup for training and inference |

| Reptile [17]                           | <i>approx</i> first-order MAML<br>= first-order MAML but only using the sign of the gradient            |                   | Very simple, fast training                                  | Requires gradient descent                                             |

| Sign-MAML [19]                         | = MAML but inner loop learning rate is a vector                                                         |                   | Better performance than first-order MAML                    | Requires gradient descent                                             |

| MetaSGD [20]                           | = MAML but inner loop learning rate is a matrix                                                         |                   | Better all-round performance than MAML                      | Parameter count doubles                                               |

| MetaCurvature [21]                     | = MAML but inner loop learning rate is a matrix                                                         |                   | Better few-shot performance than MetaSGD                    | Parameter count increases, complex inner loop                         |

| SNAIL [22]                             | Attention over convolved support sequence for few-shot tasks                                            |                   | Gradient-free                                               | Contains multiple attention layers                                    |

| Meta-learning via Hypernetworks [24]   | Generating task-specific network weights                                                                |                   | Better performance than baseline MAML                       | More parameters, gradient calculation + hypernetwork forward-pass     |

| Predict parameters by activations [25] | = hypernetwork to generate classification layer                                                         |                   | Only one matrix multiplication to compute weights           | Increased parameter count through hypernetwork                        |

| LEO [26]                               | = MAML + $\omega$ is a hypernetwork                                                                     |                   | Very high few-shot performance                              | Gradient calculation + decoder forward-pass, more parameters          |

| Prototypical Networks [27]             | Computing class prototypes for few-shot tasks                                                           |                   | Simple, gradient-free, fast training                        | Harder to deal with out-of-domain tasks, not state-of-art accuracy    |

| Baseline++ [28]                        | Supervised embedder pre-training for few-shot tasks                                                     |                   | Extremely simple, gradient-free extremely fast training     | Difficulty with out-of-domain tasks, more training samples required   |

| Matching Networks [29]                 | Attention layer over support embeddings for few-shot tasks                                              |                   | Gradient-free                                               | Requires attention calculation                                        |

| Relation Networks [30]                 | Learning relationships for few-shot learning                                                            |                   | Gradient-free                                               | Increased parameter count through relation module                     |

not only for the software but also for the hardware design.

This means that the most widely adopted dataset for comparing meta-learning methods, *miniImageNet* [29] (discussed in Appendix B), is not used in this thesis. The reason for this is that this work focuses on few-shot **sequence** classification: while converting a color image to a sequence is definitely possible, much semantic information is lost when doing so.

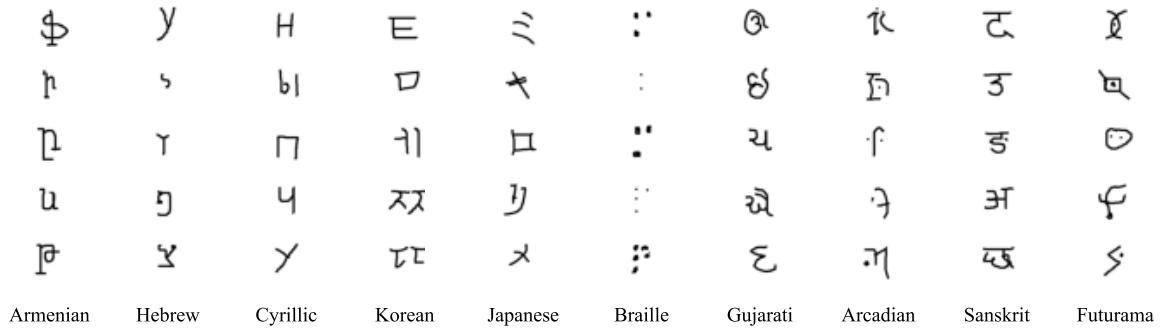

**2.1.6.1 Omniglot** The Omniglot dataset [31] consists of handwritten characters from a diverse range of writing systems and was introduced in 2015 by Lake *et al.* to address the challenge of one-shot learning.

The dataset contains characters from 50 alphabets, including but not limited to, Armenian, Hebrew, Cyrillic, Korean, Japanese and Braille. It comprises a collection of 1,623 different characters, each handwritten by 20 different people, resulting in a total of 32,460 distinct character images. Fig. 13 displays a subset of alphabets and characters contained in the dataset.

**Figure 13:** A selection of characters for various alphabets in the training split of the Omniglot dataset.

Each character image is grayscale and 105 by 105 pixels in size. The images can be resized to, e.g. to  $28 \times 28$  pixels as in the MNIST dataset [29] [27], so that smaller neural networks can be used. However, unlike the MNIST dataset of handwritten digits [32], the Omniglot dataset also contains the stroke data for all characters, which was released in 2019 [33].

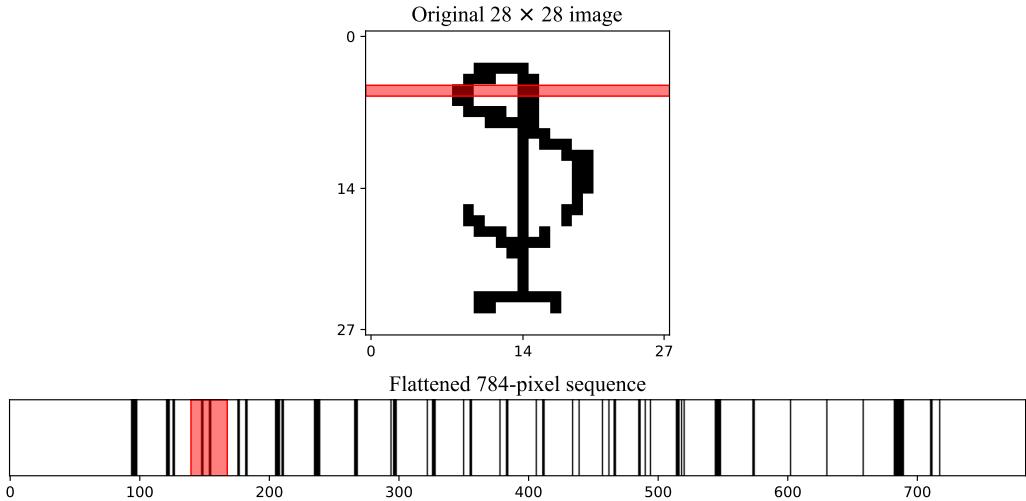

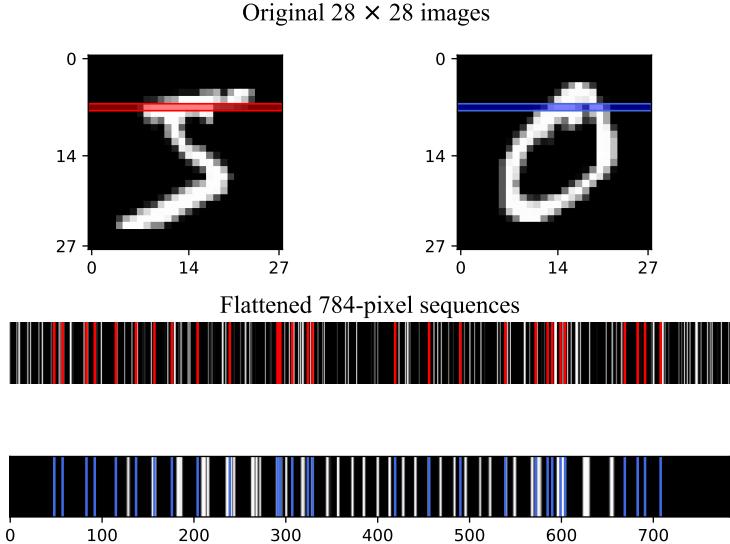

As this work focuses on streaming applications at the edge, inputting static images of characters into a model is not immediately representative of the desired application. However, due to its widespread adoption and low compute requirements, using Omniglot eases comparison between previous meta-learning approaches, hence it will be used in this work. Nevertheless, to emulate a streaming setting, the pixel rows of a single image can be concatenated from top to bottom to form a sequence (see Fig. 14). This procedure is taken from Le *et al.* [34], where it was used to convert the MNIST digit images [32] to sequences for temporal classification by a recurrent neural network (RNN).

The Omniglot dataset has two splits: a background and an evaluation split, containing 964 and 659 characters, respectively. Originally, the background set was meant for meta-training and the evaluation set for meta-testing [33]. However, Vinyals *et al.* created a new split with 1200 characters for meta-training in 2016 [29], which was subsequently used by key papers in the meta-learning domain [15] [27]. Another extension from the same authors was to create three new classes from each character by rotating it in multiples of 90 degrees, yielding 4800 classes in total.

Increasing the number of classes in the meta-training set makes the task at hand easier since more data is available for training while less data is available to test on. However, to provide a fair comparison to other methods that mainly use this split, the 1200-class rotation-extended split from Vinyals *et al.* is also employed in this work.

**Figure 14:** Sample conversion from an Omniglot image to a sequence, where the highlighted row in the 2D image is mapped to the highlighted slice in the flattened 1D sequence.

**2.1.6.2 Few-shot keyword spotting** While Omniglot and *miniImageNet* are well-recognized datasets for few-shot learning, both are static image-only datasets at their core. As this work focuses on streaming applications, a keyword-spotting (KWS) benchmark is chosen that deals with real-world sequential data, which is a supervised learning task where a model tries to detect when one or two words are spoken [35]. A real-world application of keyword spotting is to trigger the voice assistant of a smartphone or tablet to launch. For example, at any point, while the assistant is switched off, a user can say *"Hey [name of company]"*, after which the assistant program is launched and starts listening for the next voice input query. This query, usually multiple words or a sentence, can then be processed in a cloud environment with more computing power to perform the voice-to-text operation. The initial keyword spotting task needs to take place in an always-on fashion directly on the device, as it otherwise would require a continuous streaming of device audio to the cloud, which is not scalable to many clients, increases privacy risks and would require a significant energy footprint for communication [35].

As a popular real-world streaming application, there are many software implementations [36] [37] [38] and edge hardware implementations [39] [40] [41] [42] that target keyword spotting. Also, various public datasets are available [35] [43] in this domain.

**Feature extraction** Keyword spotting is rarely performed on the raw audio of the keywords. Instead, it is common to extract mel-frequency cepstral coefficients (MFCCs) features from the audio and feed these features into a neural network [44]. These features are extracted from windows of the digital audio signal, where each window has a typical length of 25–32 ms with an overlap of 10–16 ms [44]. This means that every 10–16ms, a new feature vector for processing in the neural network becomes available. Each feature vector contains between 10 and 40 MFCCs [45].

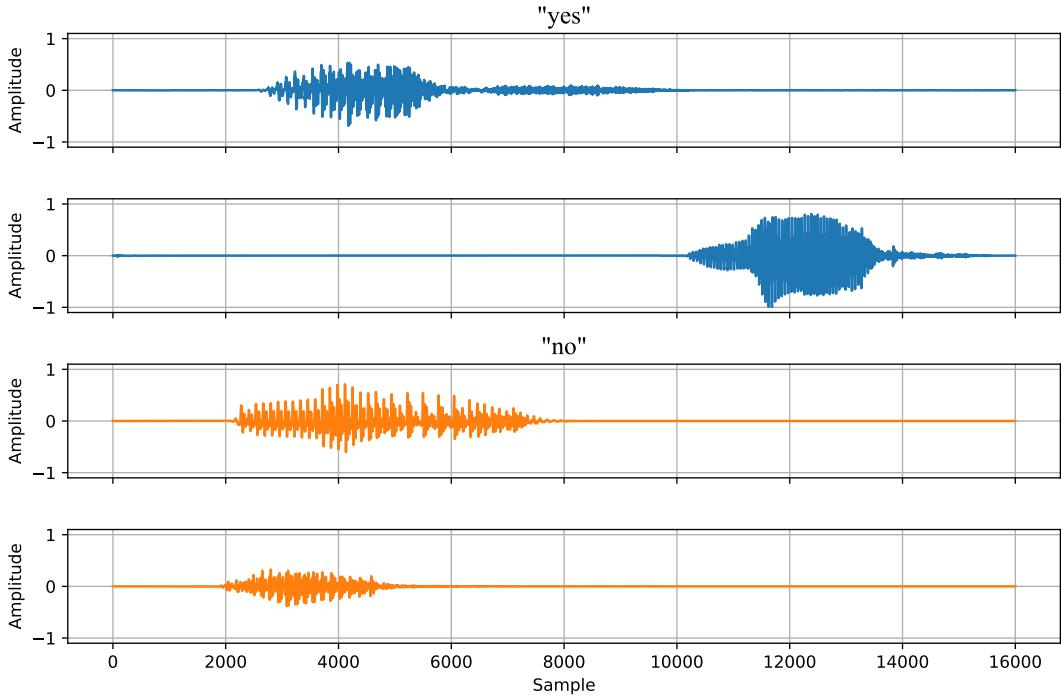

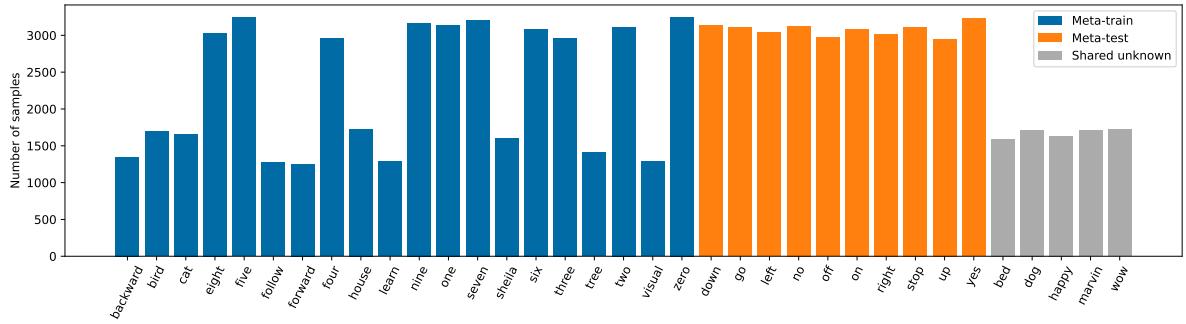

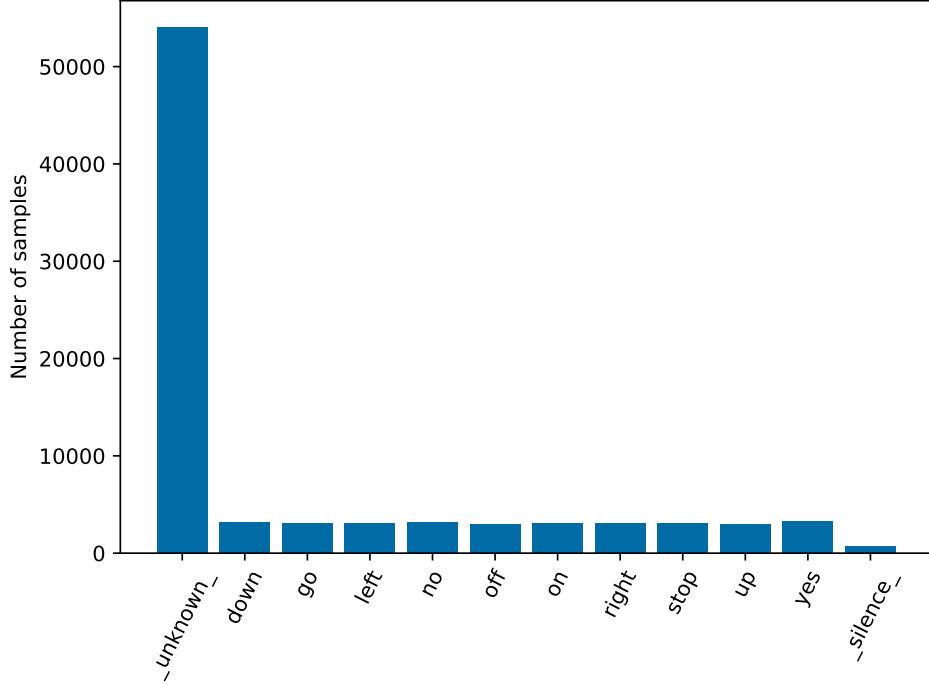

**Datasets** The most frequently used dataset for benchmarking keyword spotters is the Google speech commands (GSC) dataset [35]. It contains 35 classes / unique keywords with a total of 105,289 1-second utterances<sup>3</sup> sampled at 16 kHz (see Fig. 15 for the visualization of a data

<sup>3</sup>This sample count is for version 2 of the dataset; version 1 contained 64,727 samples [35]. Unless specified otherwise, the V2 variant is used by default in this work.

sample). Also included is a set of minute-long clips that contain background noise, such as a recording of someone doing the dishes and a clip of generated white noise.

**Figure 15:** Sample audio waveforms for the "Yes" and "No" keywords from the V2 Google speech commands dataset [35].

The standard evaluation procedure is to *spot* ten words: "Yes", "No", "Up", "Down", "Left", "Right", "On", "Off", "Stop" and "Go". Randomly sampled clips from the remaining 25 words form an 11th class "Unknown word", while a 12th class "Silence" contains randomly selected 1-second clips from the background recordings. The goal is to correctly classify the keywords while minimizing false positives for the non-keyword words and background sounds, accurately representing the expected input from a real-world deployment [35].

Another dataset for keyword spotting is the Multilingual Spoken Words Corpus (MSWC) [43]. This dataset contains 340,000 unique keywords from 50 languages with a total of 23.4 million 1-second clips. The benchmark setup for MSWC is a 761-class supervised learning classification task: 760 keywords and one silence class (1.4 million samples, taken from nine languages).

**Baseline task definition** Before going into the few-shot KWS task definition, a baseline supervised learning task is defined. This is done as there is very little literature in on-chip learning via meta-learning, meaning that it might prove hard to compare this thesis' hardware design with other designs purely based on meta-learning performance.

Therefore, the 12-class GSC variant will be used as a supervised keyword spotting task. This variant is chosen as it is the most popular benchmark for edge hardware and will therefore allow for a fair comparison with many hardware designs.

**Few-shot task definition** GSC and MSWC do not directly present a true few-shot benchmark scenario. To adapt keyword spotting to a realistic few-shot scenario, it is assumed that the user can train the model at the edge to spot new keywords with only a few user-generated examples.

For example, instead of "Hey [name of company]", a user can enable their virtual assistant with the words "Wake up [any name]". However, compared to few-shot image classification, few-shot keyword spotting is not as popular in the literature. Because of this, there is not yet one commonly agreed-on method to benchmark this task. Therefore, a few possibilities are outlined, after which a single format is selected.

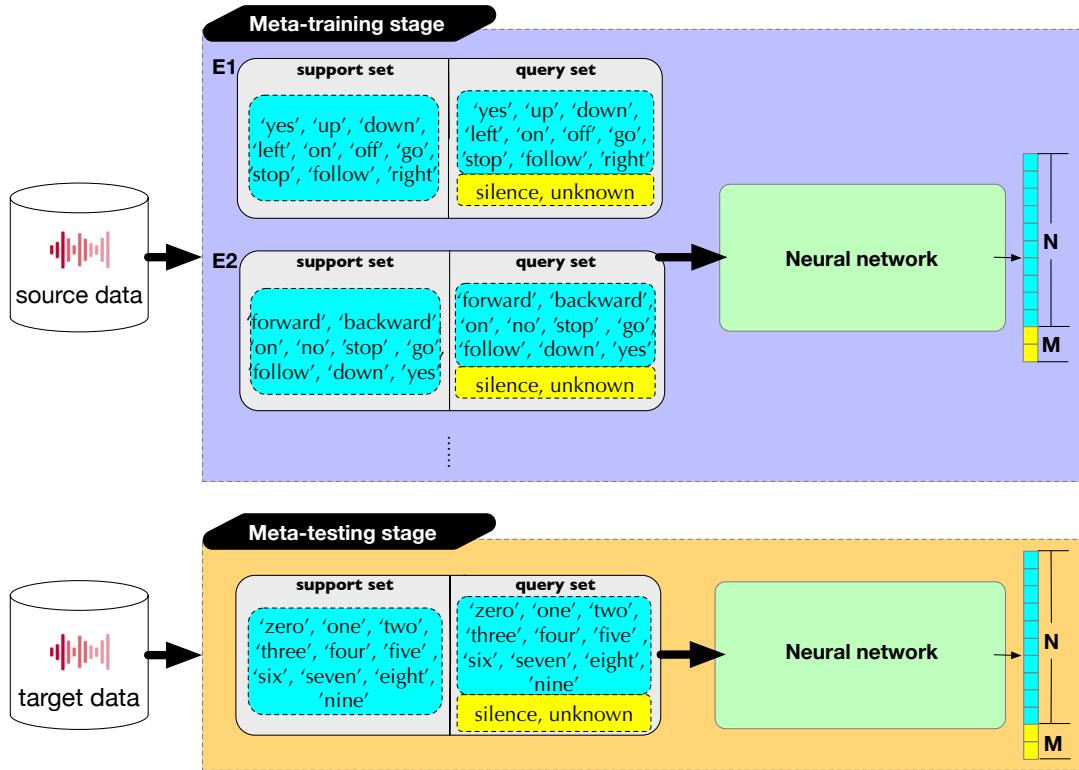

In [46], Chen *et al.*, formulate an  $N+M$  way few-shot learning scenario, where  $N$  and  $M$  are the number of new classes and fixed classes, respectively. The dataset used in this setup is the GSC dataset. Fixed classes are classes that are known a priori, in this case, "Unknown word" and "Silence" ( $M = 2$ ). Two tasks were created to fit this scenario: digit classification using digits zero to nine (see Fig. 16) and command classification using the commands from the standard evaluation procedure of GSC. Next to these ten ( $N = 10$ ) user-defined keywords, five keywords form the "Unknown word" set, while the remaining twenty keywords form the meta-training ( $D_{\text{source}}$ ) set from which tasks can be sampled [46].

**Figure 16:** Digit classification task as presented in [46]. Figure adapted from [46].

For the MSWC dataset, next to the supervised learning setup, Mazumber *et al.* also define a 1+2-way<sup>4</sup> 5-shot learning task in [47]. The 1-way is a new keyword from any of the fifty languages, while the +2-way again represents the "Unknown word" and "Silence" categories. For the "Unknown word" category, 128 samples from a set of 5000 utterances are sampled for each few-shot task.

Alternatively, in [48], Jung *et al.* create a large-scale keyword dataset called LibriSpeech Keywords (LSK), consisting of 1,000 keyword classes extracted from the LibriSpeech corpus [49]. This dataset acts as the pre-training set, after which fine-tuning is performed on GSC. For this, the same ten-digit keywords as in [46] are selected as the user-defined set; 15 keywords then form the "Unknown word" set and the remaining ten command keywords (the same key-

<sup>4</sup>Originally described as 3-way, but using the notation from [46] here.

words as in the standard evaluation procedure of the GSC dataset), form the meta-training set. Overall, this setup corresponds to a 10+1-way task.

While these are not the only approaches for few-shot keyword spotting [50] [51], each of them provides a slightly different setup on a different dataset, as summarized in Table 2. To select a final benchmark in this work, in order to keep development time under control, the primary criterion will be the ease of use. Firstly, the LSK → GSC approach can be discarded, as Jung *et al.* did not open source their dataset. Also, since the benchmark does not contain a silence class, it is not entirely realistic for deployment in an edge device, where most of the input audio will be silent. Between the MSWC few-shot approach and the GSC-based approach, it is clear that the GSC-based approach is favorable to ensure a low iteration time, as training will be 14× faster with 14× fewer data. Therefore, the 10+2-way command classification task from Chen *et al.* [46] is chosen as the few-shot keyword spotting benchmark task for this thesis.

**Table 2:** Comparison of the three discussed few-shot keyword-spotting benchmarks. **Bold** means best.

| Approach name              | N+M-way problem [46]        | MSWC few-shot [47] | LSK → GSC few-shot [49]           |

|----------------------------|-----------------------------|--------------------|-----------------------------------|

| Used dataset(s)            | Google Speech-Commands [35] | MSWC [43]          | LibriSpeech Corpus [49], GSC [35] |

| Total sample count         | 105,289                     | <b>1,455,300</b>   | 1,000,000 <sup>5</sup>            |

| # of meta-training classes | 20+2                        | 760+1              | <b>1000+10+1</b>                  |

| # of meta-testing classes  | 10+2                        | 256+2              | 10+1                              |

| Ways benchmarked           | 10+2                        | 1+2                | 9+1                               |

| Shots benchmarked          | <b>1, 5, 10</b>             | 5                  | <b>1, 5, 10</b>                   |

| Public data release        | <b>Yes</b>                  | No                 | <b>Yes</b>                        |

| Public split release       | <b>Yes</b>                  | No <sup>6</sup>    | No                                |

### 2.1.7 Continual learning

Complementary to the concept of meta-learning is *continual learning* (CL), which refers to the fact that neural networks should not only be able to learn from little data, but also to keep learning new tasks sequentially without forgetting previous knowledge, similar to animals. For this reason, CL is sometimes also referred to as *incremental learning* or *lifelong learning* [8].

In continual learning, there are two tracks [2]: learning from new/unseen data belonging to known classes, called *domain-incremental* CL and learning from new/unseen data containing entirely new classes, called *class-incremental* CL. While both tracks relate to meta-learning, class-incremental CL is closest to few-shot classification as new classes are learned and hence links to the contents of this thesis.

While CL does not mandate the use of little data for learning new tasks by definition, this is still a very desirable property at the edge. Such a few-shot continual-learning ability brings the same advantages as those obtained through meta-learning (e.g., privacy-friendly, low maintenance costs), with the ability to keep learning, a key benefit since the outside world evolves continuously [52]. Compared to regular few-shot learning, where the gained knowledge from the previous task is progressively erased when learning on a new task, in CL, knowledge can accumulate. This is visualized in Fig. 17.

<sup>5</sup>This value is estimated from Table 3 in the paper

<sup>6</sup>[https://github.com/harvard-edge/multilingual\\_kws/issues/41](https://github.com/harvard-edge/multilingual_kws/issues/41)

**Figure 17:** Illustration of class-incremental continual learning versus few-shot learning. The faded classes are learned during continual learning but progressively forgotten in few-shot learning.

The main challenge in continual learning is tackling *catastrophic forgetting/inference* [53], which refers to the phenomenon where, as the neural network gains new knowledge, it starts to forget previously learned knowledge. A few of the key approaches that aim to tackle this problem are discussed next.

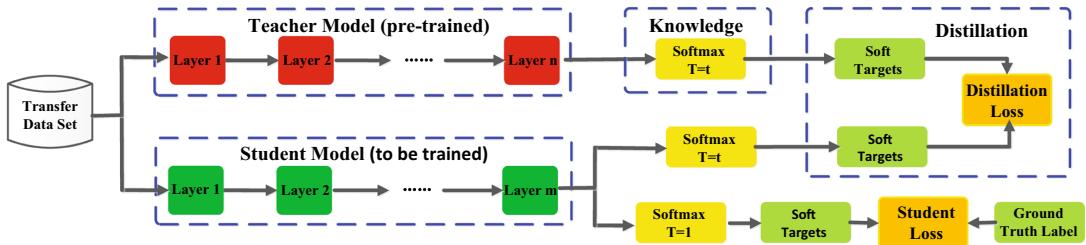

In [52], Aljundi *et al.* propose to penalize weight changes of important networks weight while learning a new task, allowing at the same time to overwrite less important weights. Alternatively, Pellegrini *et al.* present a technique called *latent replay* [4]. This builds on top of the rehearsal strategy for continual learning, where some of the input samples from previously learned tasks are stored and added to the training set of a new task [54]. With latent replay, instead of storing the data in the input space, activations at some intermediate layer are stored and used for rehearsal, significantly reducing compute and memory requirements with respect to the naive baseline. Notably, meta-learning can also be used to tackle catastrophic forgetting: the goal is then to learn how to "not forget". MAML [15] is often used as the baseline algorithm for this [55] [56].

Currently however, none of these approaches is completely able to alleviate the *catastrophic forgetting* phenomenon: therefore, an open challenge remains in learning quickly for little data.

## 2.2 Classifying time-series data

In this section, two neural network architectures for classifying and processing time-series data will be covered. Note that any network designed to perform sequential data classification can also perform few-shot sequential data classification when part of a meta-learning framework (see Section 2.1.4).

The reason for focusing on classifying time-series or sequential data is that at the edge, streaming data is much more common than static data such as images. Examples of such streaming data at the edge are biological signals such as heart rate or blood oxygen over time [57], environmental data such as temperature, humidity or air quality metrics [58], communication data such as human speech [35] or animal behavior [59] and surveillance video for traffic monitoring [60] or anomaly detection [61].

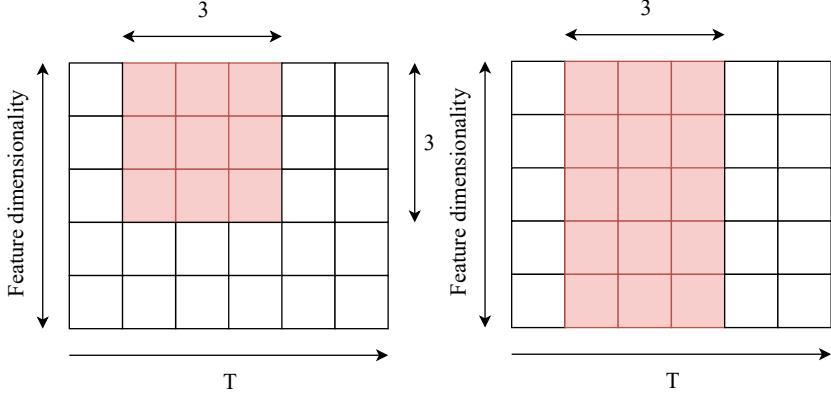

For classifying sequential data, different architectures are available. Excluding hybrid architectures or ensemble approaches, key base architectures are: transformers [62], recurrent neural networks (RNNs), temporal convolutional residual networks (TC-ResNets) [63] and temporal convolutional networks (TCNs) [64].

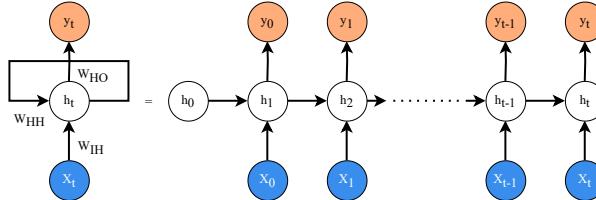

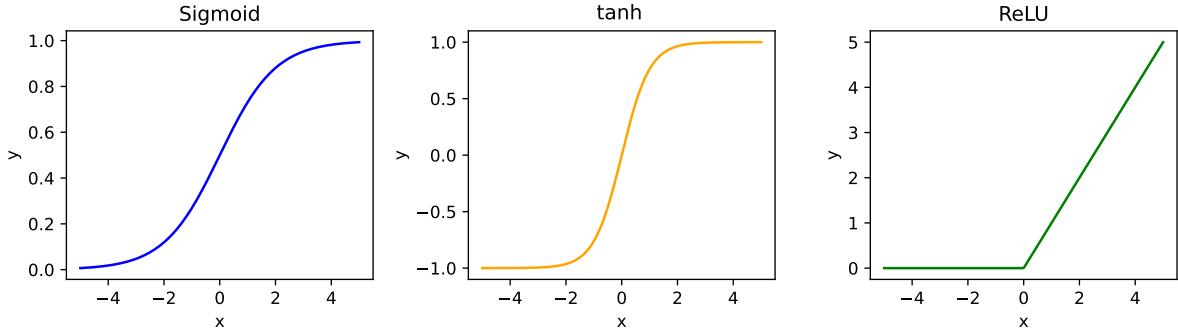

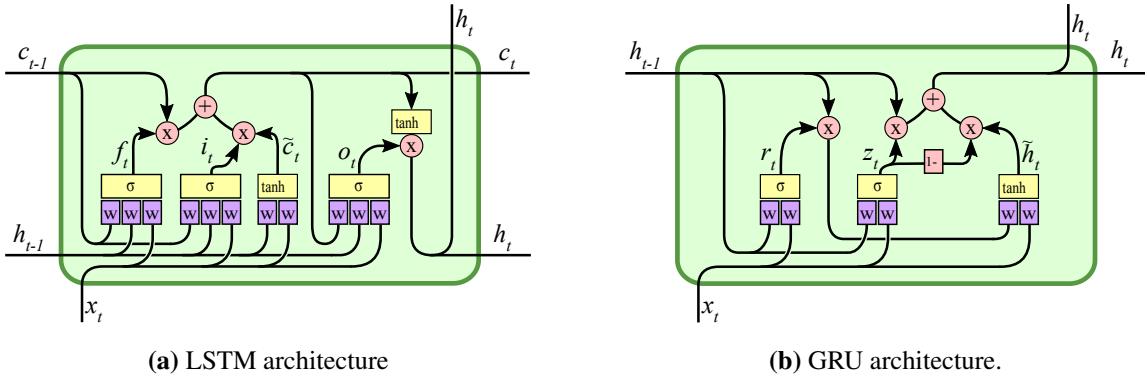

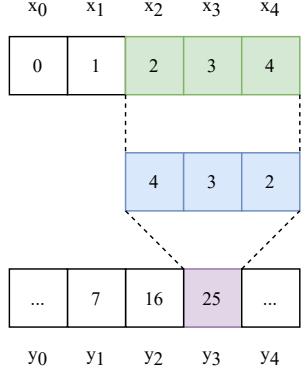

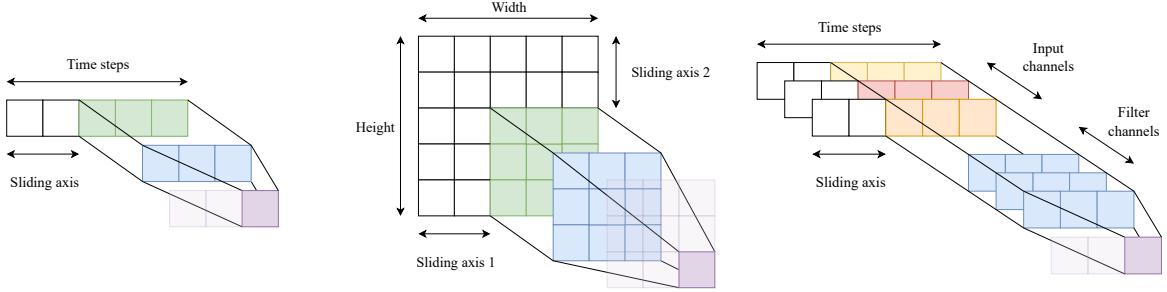

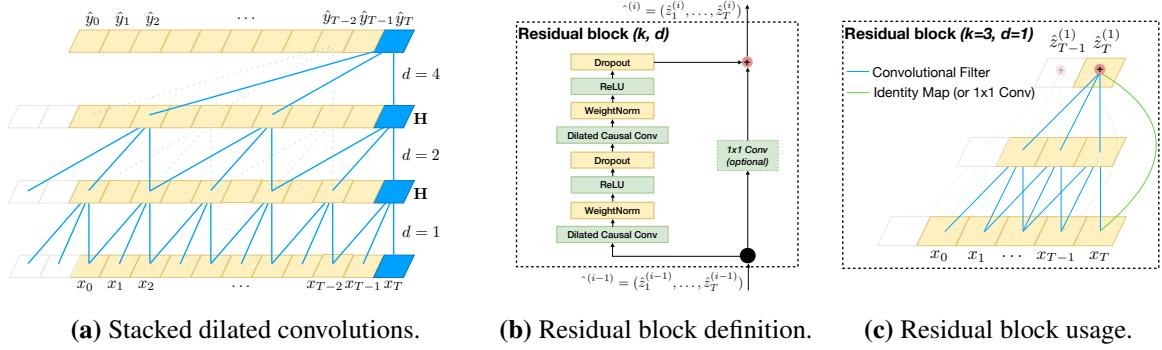

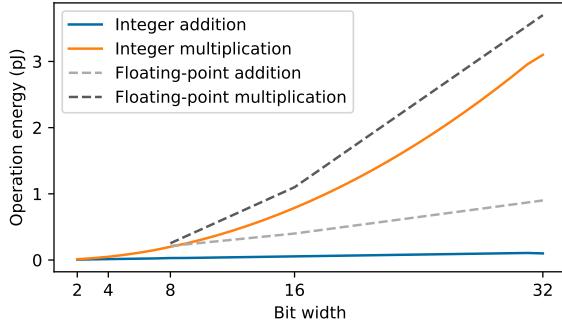

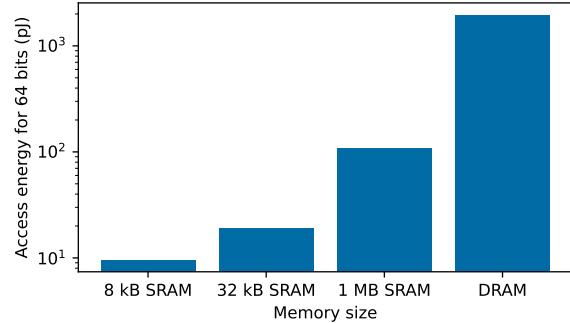

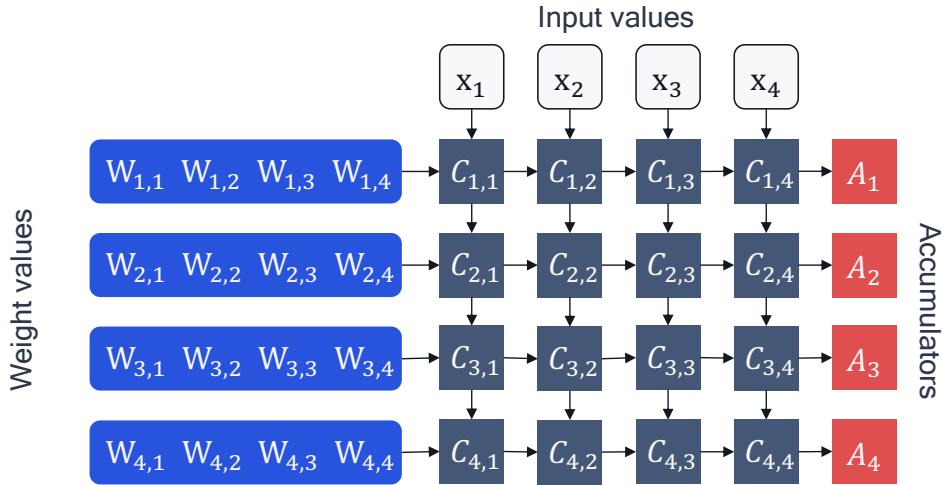

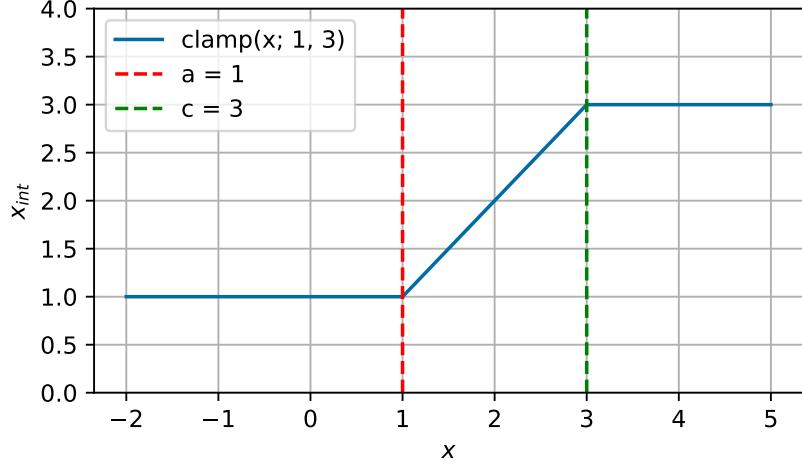

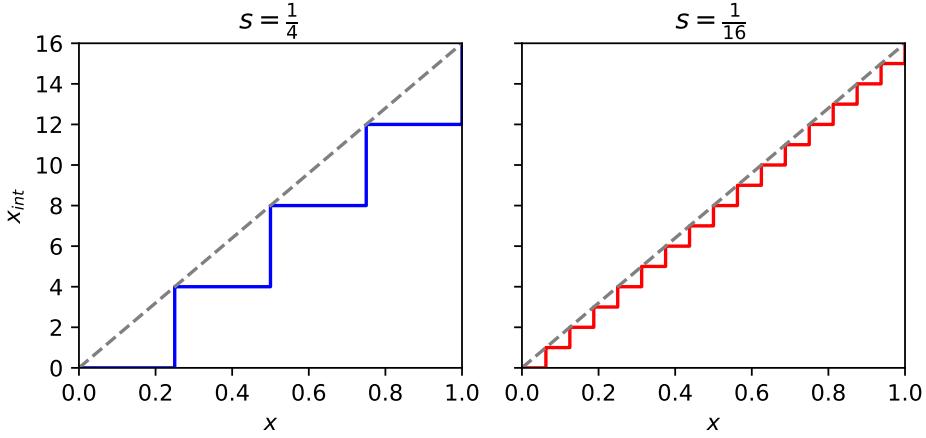

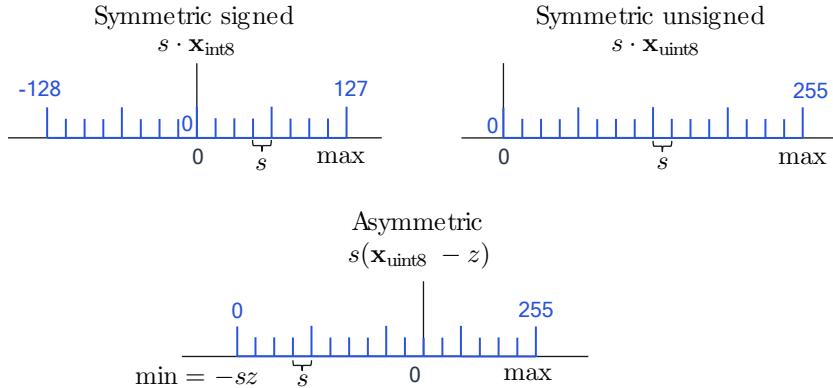

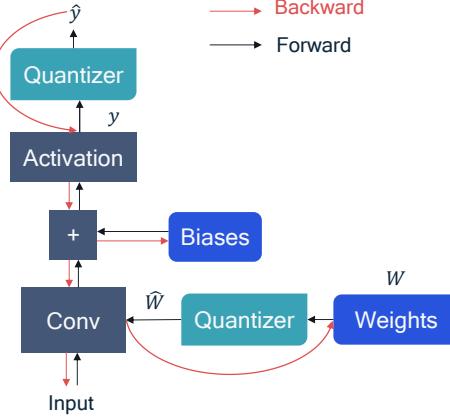

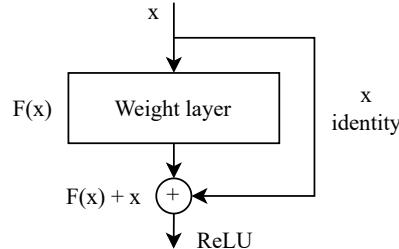

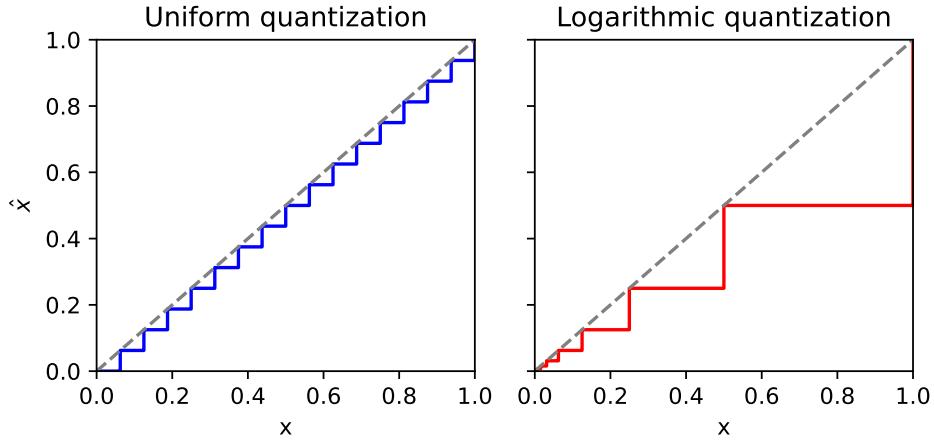

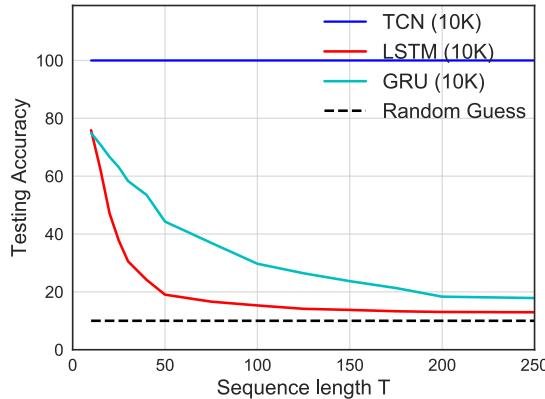

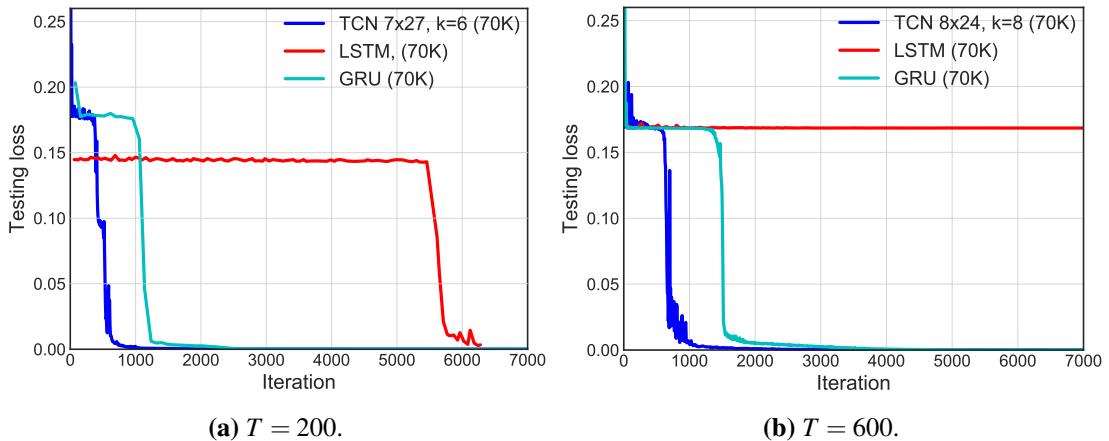

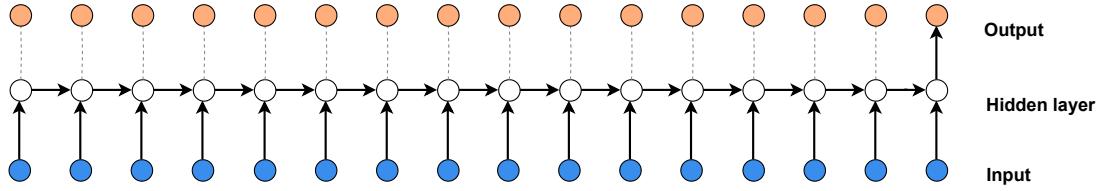

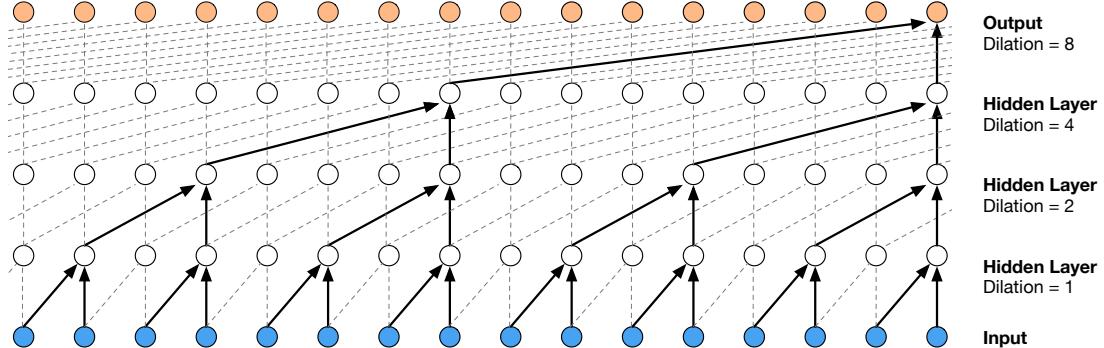

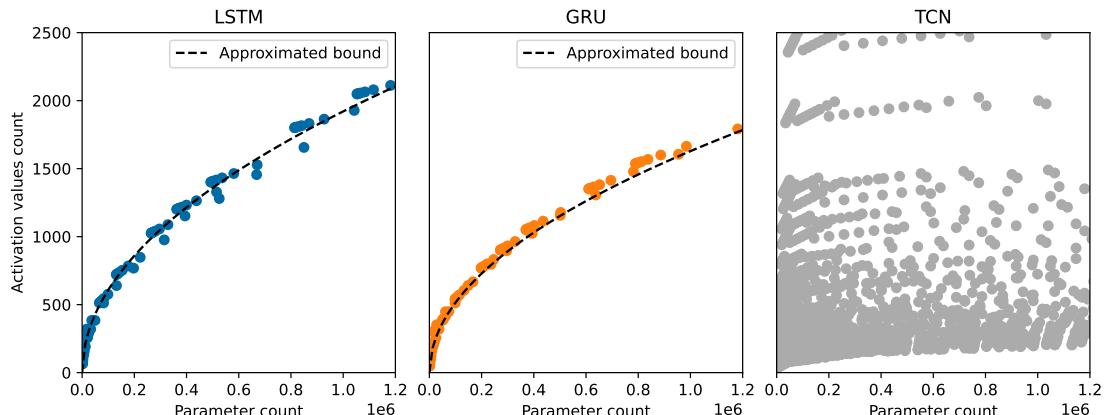

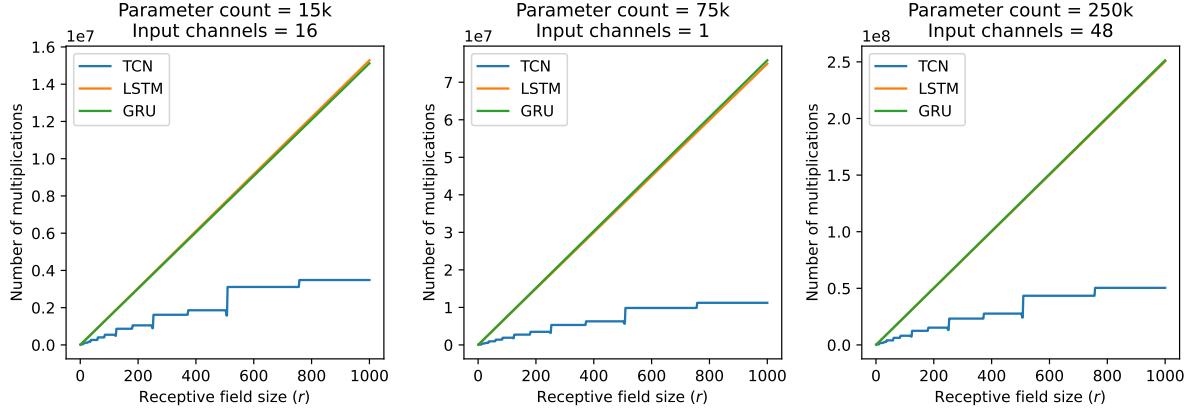

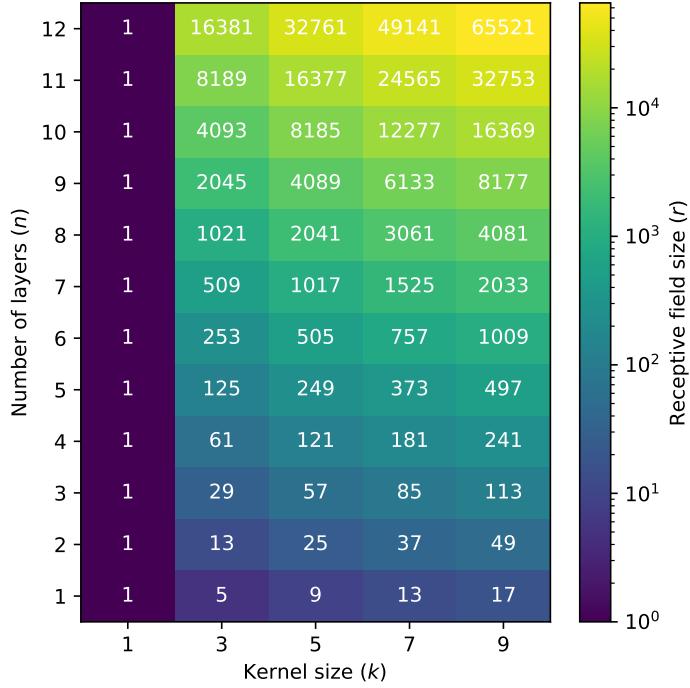

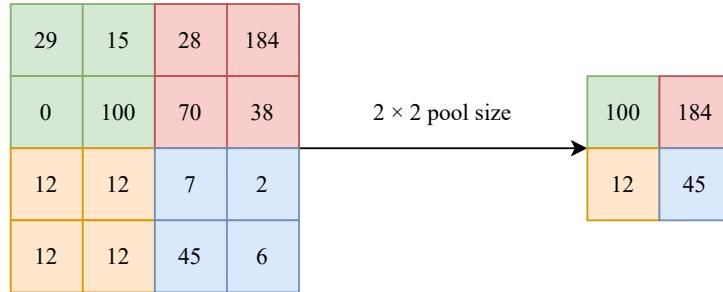

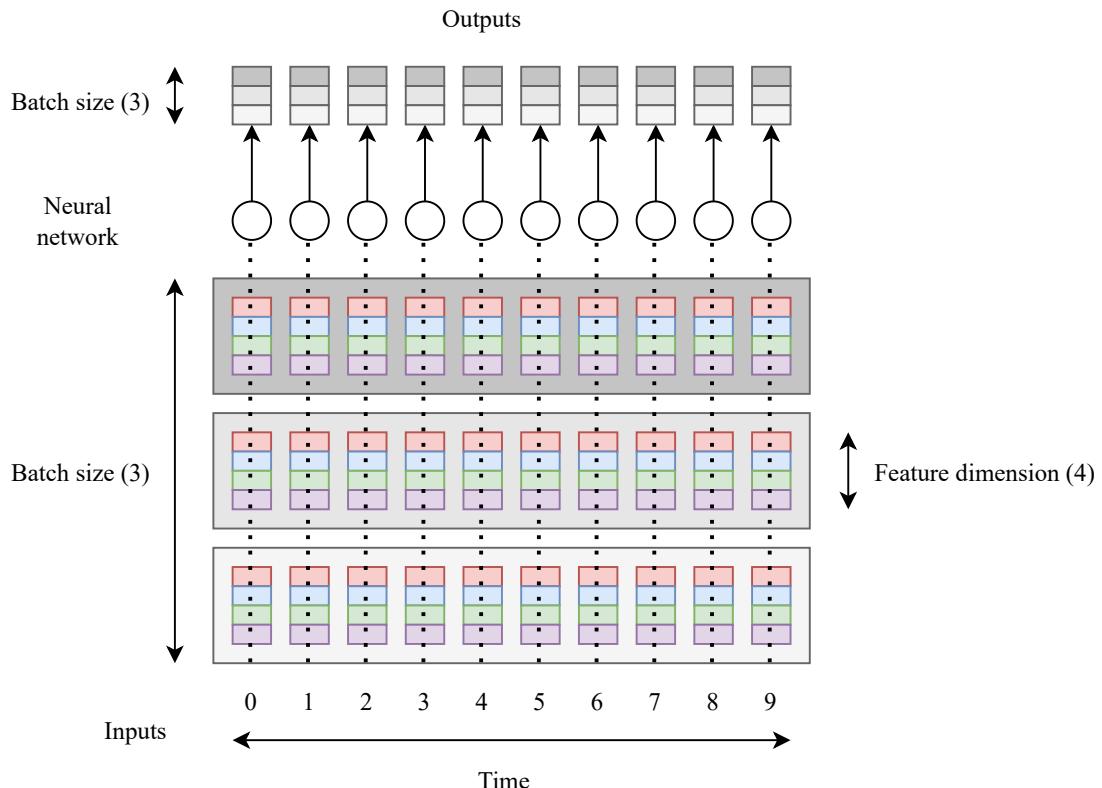

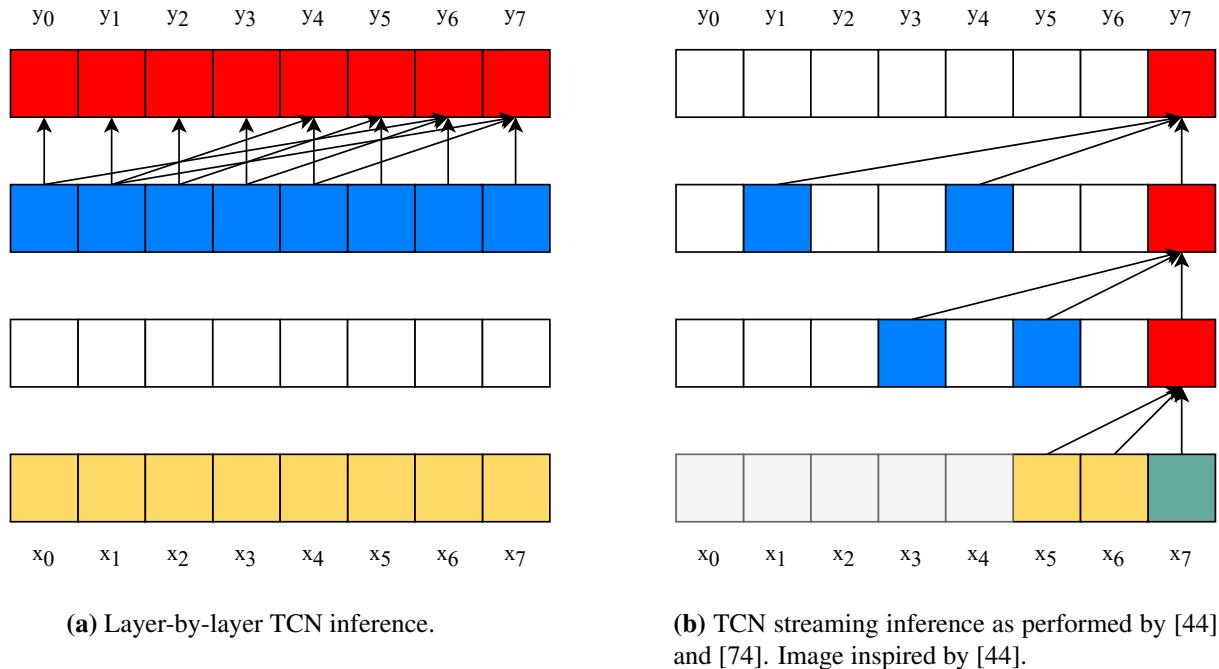

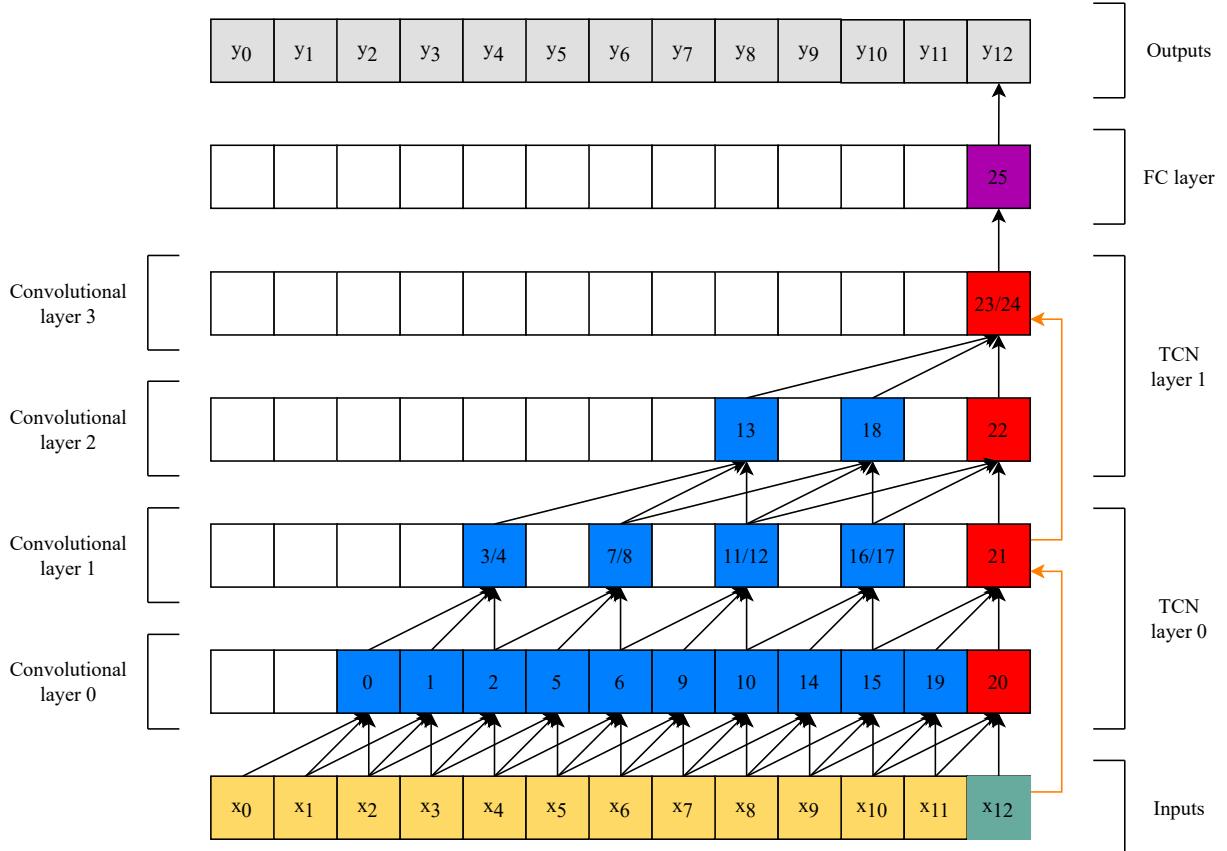

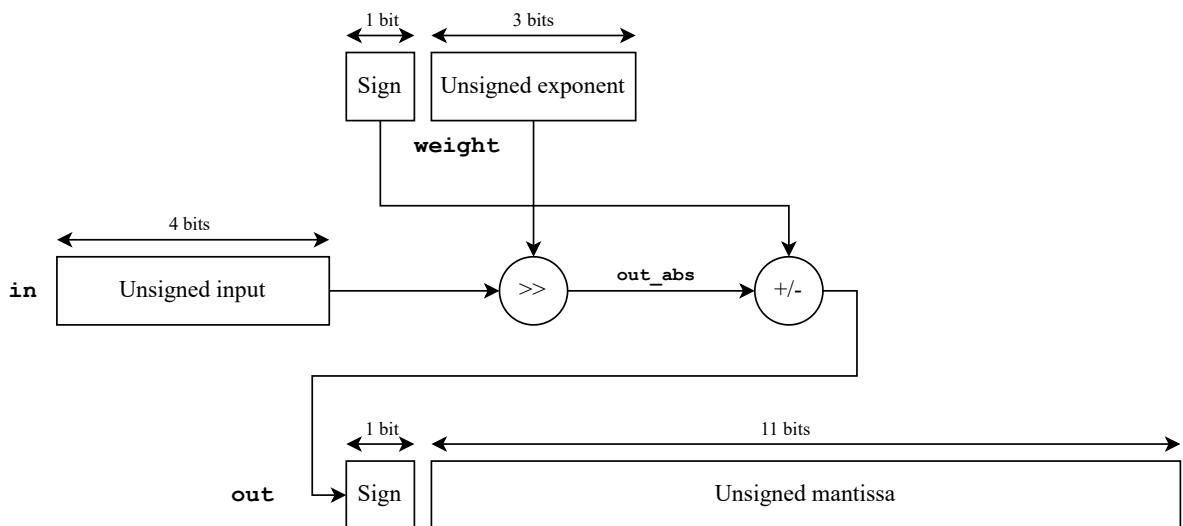

Transformers demonstrated state-of-art performance on tasks with large amounts of data (4.5 and 36 million sentence pairs [62] for two translation tasks) [62], however, they perform on par or worse compared to TCN and RNN architectures for a variety of tasks that have one or two orders of magnitude less training data (1 million words for a language modeling task) [65]. Furthermore, popular transformer architectures such as BERT [66] only support input sequences of up to 512 tokens, which is limiting even for the Omniglot task having 784 tokens per timestep. Similarly, TC-ResNets [63] have not been demonstrated on sequences beyond 150 timesteps. In addition, traditional transformers have memory requirements that scale quadratically with input sequence length [67].