## A 24GHz Radar Receiver in CMOS

#### **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft,

op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben; voorzitter van het College voor Promoties,

in het openbaar te verdedigen op donderdag 2 juli 2015 om 12:30 uur

Door

#### Ka Chun KWOK

Master of Philosophy in Electrical and Electronic Engineering, Hong Kong University of Science and Technology, Hong Kong, China

geboren te Hong Kong, China

This dissertation has been approved by the

promotor: Prof. dr. J.R. Long

#### Composition of the doctoral committee:

Rector Magnificus

Prof. dr. J.R. Long promotor

#### Independent members:

Prof. dr. R.B. Staszewski EWI, TU Delft

Prof. dr. ir. B. Nauta University of Twente

Prof. dr. ir. G. Dolmans Eindhoven University of Technology

Mr. K. Kianush Catena Holding B.V. Dr. ir. L.C.N. de Vreede EWI, TU Delft

Prof. dr. ing. A. Neto EWI, TU Delft, reservelid

This work was financially supported by Dutch Technology Foundation (STW) contract DCS-6422e. Technology access was facilitated by Jack Pekarik and David Harame of IBM Microelectronics, in Burlington, VT., USA. Fabrication was facilitated by the MOSIS IC fabrication service.

### Copyright © 2015 by Ka Chun KWOK

All rights reserved. No part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without any prior permission of the copyright owner.

Printed by CPI-Wöhrmann Print Service – Zutphen, The Netherlands

# **Table of Contents**

| -            |                                                     |    |

|--------------|-----------------------------------------------------|----|

| Samenvatting |                                                     |    |

| Chapter 1    | Introduction                                        |    |

| 1.1.         | Motivation                                          |    |

|              | 1.1.1 Advantages of Radio Ranging                   | 4  |

|              | 1.1.2 Potential Markets                             |    |

|              | 1.1.3 Advantages of CMOS Implementation             | 6  |

| 1.2.         | Design Challenges                                   |    |

|              | 1.2.1 Radar Hardware Implementation                 | 7  |

|              | 1.2.2 Disadvantages of CMOS Implementation          | 8  |

|              | 1.2.3 Low-Voltage, Low-Power Implementation         | 9  |

|              | 1.2.4 Millimeter-Wave Wideband Frequency Generation | 9  |

|              | 1.2.5 On-Chip Magnetic Components                   | 10 |

| 1.3.         | Thesis Organization                                 | 11 |

| 1.4.         | References                                          | 12 |

| Chapter 2    | Background Information                              | 19 |

| 2.1.         | Analog Impairments in a Receiver                    | 19 |

|              | 2.1.1 Noise                                         |    |

|              | 2.1.2 Non-Linear Distortion                         | 22 |

| 2.2.         | Gain Parameters                                     |    |

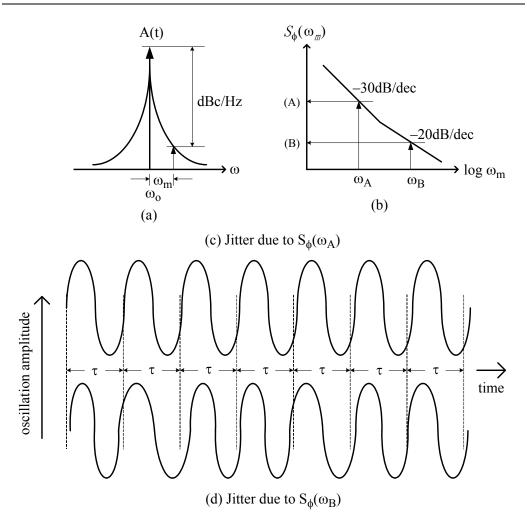

| 2.3.         | Phase Noise.                                        |    |

| 2.4.         | Summary                                             |    |

| 2.5.         | References                                          |    |

| Chapter 3    | Short-Range Radar System Implementation             |    |

| 3.1.         | Radar Configurations.                               |    |

|              | 3.1.1 FMCW Radar                                    |    |

|              | 3.1.2 Requirements for Short-Range Application      |    |

| 3.2.         | Link Budget                                         |    |

|              | 3.2.1 Emission Limits.                              |    |

|              | 3.2.2 Signal-to-Noise Ratio                         |    |

|              | 3.2.3 Third-Order Non-Linearity                     |    |

|              | 3.2.4 Phase Noise                                   | 45 |

| 3.3.         | SRR Receiver Architectures                          | 47 |

|              | 3.3.1 Homodyne Receiver                             | 47 |

|              | 3.3.2 Heterodyne Receiver                           |    |

| 3.4.         | Design Example                                      |    |

|              | 3.4.1 Functional Requirements                       |    |

|              | 3.4.2 FMCW Radar System Parameters                  |    |

|              | 3.4.3 Transceiver Specifications                    |    |

|              | 3.4.4 Building Block Specifications                 |    |

|              | <b>U</b> 1                                          |    |

| 3.5.      | Summary                                                    | 58  |

|-----------|------------------------------------------------------------|-----|

| 3.6.      | References                                                 | 58  |

| Chapter 4 | Voltage-Controlled Oscillator                              | 63  |

| 4.1.      | Motivations                                                | 63  |

| 4.2.      | Varactor-Tuned VCOs                                        | 64  |

| 4.3.      | Transconductor-Tuned VCO                                   | 69  |

| 4.4.      | First Testchip: 23.2-to-29.4GHz VCO                        | 74  |

|           | 4.4.1 Circuit Design                                       | 74  |

|           | 4.4.2 Experimental Results                                 |     |

| 4.5.      | Second Testchip: 18.6-to-21.2GHz VCO                       | 82  |

|           | 4.5.1 Circuit Design                                       |     |

|           | 4.5.2 Experimental Results                                 | 84  |

| 4.6.      | Discussions                                                | 87  |

| 4.7.      | Summary                                                    | 90  |

| 4.8.      | References                                                 |     |

| Chapter 5 | LNA Design and Optimization                                | 95  |

| 5.1.      | Introduction                                               | 95  |

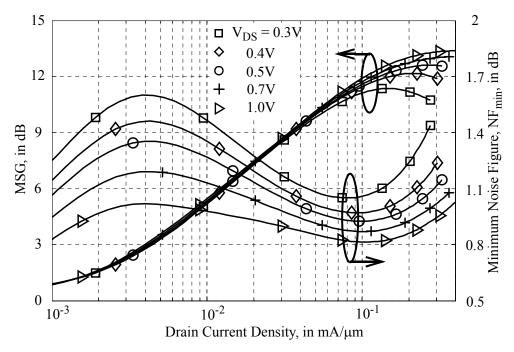

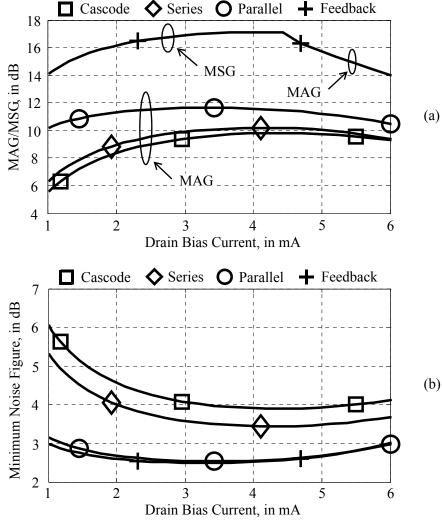

| 5.2.      | Optimization at the Device Level                           | 97  |

|           | 5.2.1 Device Sizing for Power Gain                         | 97  |

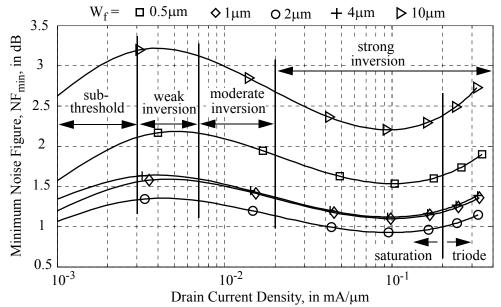

|           | 5.2.2 Device Sizing for Noise Figure                       | 101 |

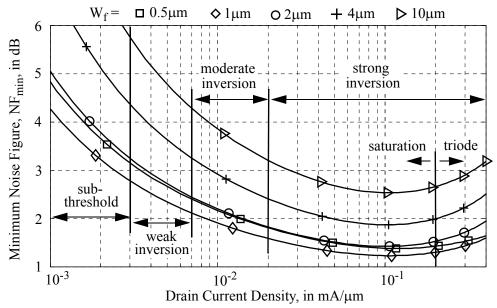

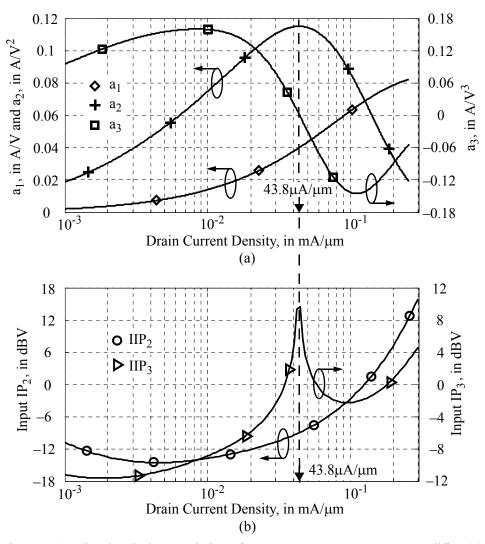

|           | 5.2.3 Device Sizing for Linearity                          | 103 |

|           | 5.2.4 Device Sizing for Bandwidth                          | 105 |

|           | 5.2.5 Device Sizing for Passive Matching Network Loss      | 106 |

| 5.3.      | Optimization at the Circuit Level                          | 111 |

|           | 5.3.1 Current and Voltage Budget Partitioning              | 111 |

|           | 5.3.2 Impedance Matching Conditions for Cascaded Stages    | 113 |

|           | 5.3.3 Feedback Based Impedance Matching                    | 114 |

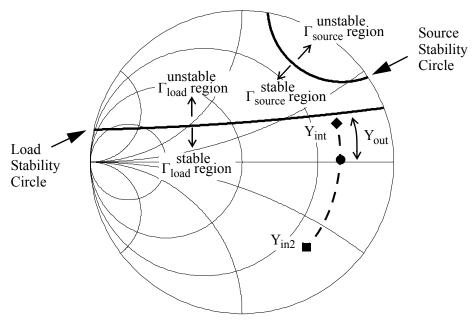

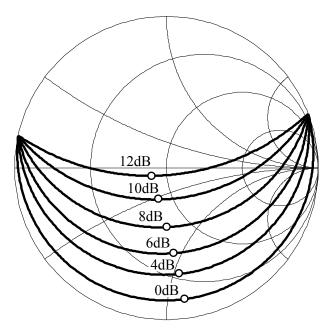

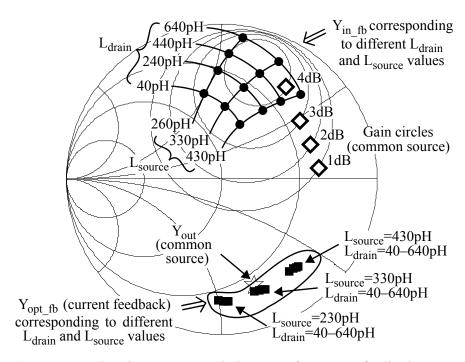

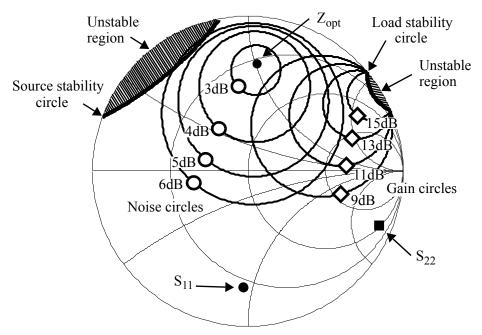

|           | 5.3.4 Smith Chart Based Bilateral Optimization Methodology | 116 |

| 5.4.      | Design Examples                                            | 119 |

| 5.5.      | Summary                                                    | 121 |

| 5.6.      | References                                                 | 121 |

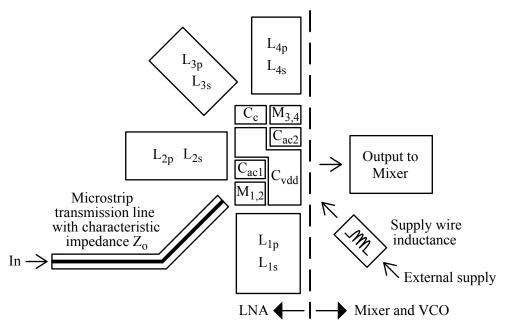

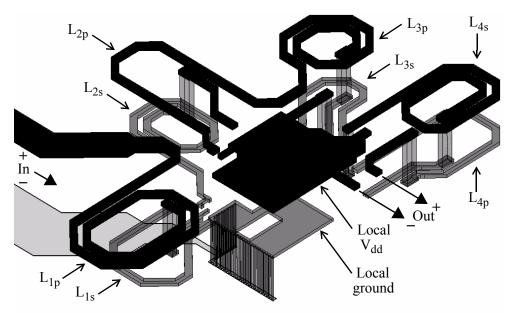

| Chapter 6 | LNA and 24GHz Frequency Downconverter                      | 123 |

| 6.1.      | Low Noise Amplifier                                        | 123 |

|           | 6.1.1 Limitations of Cascode LNAs                          | 123 |

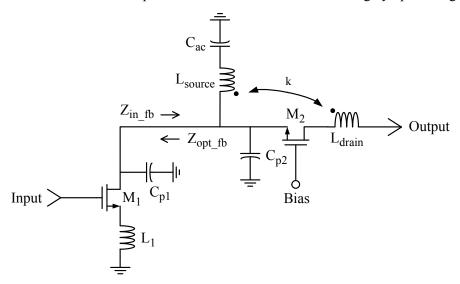

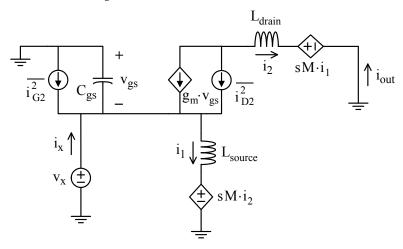

|           | 6.1.2 Current Feedback with a 3-Port Transformer           | 126 |

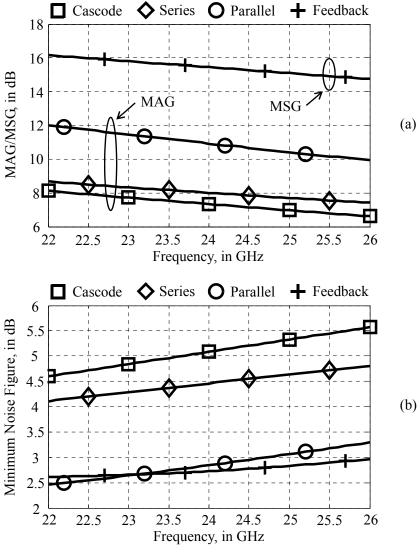

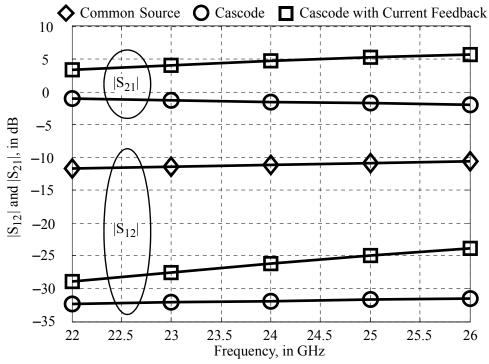

|           | 6.1.3 Simulated Performance Comparison                     | 130 |

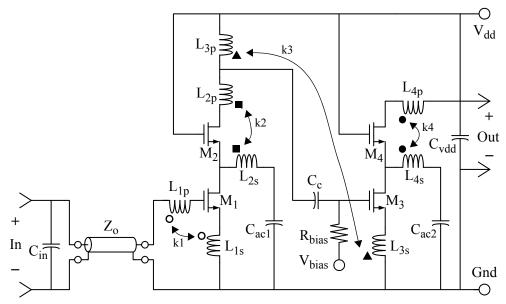

|           | 6.1.4 LNA Design and Implementation                        | 135 |

| 6.2.      | Frequency Downconverter                                    |     |

|           | 6.2.1 Mixer Design and Implementation                      | 141 |

|           | 6.2.2 Simulation Results                                   |     |

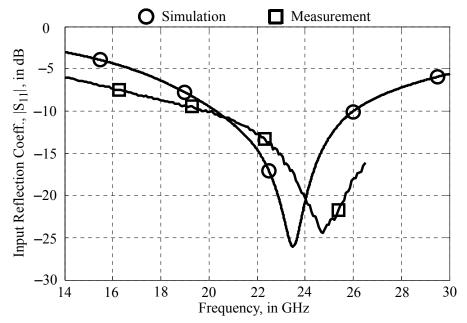

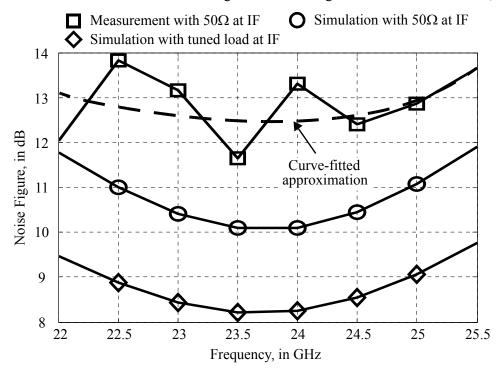

| 6.3.      | Experimental Results                                       | 146 |

| 6.4.      | Summary                                                    |     |

| 6.5.      | References                                                 | 158 |

| Chapter 7                         | Conclusion and Recommendations | 161 |

|-----------------------------------|--------------------------------|-----|

| 7.1.                              | Findings                       | 161 |

| 7.2.                              | Contributions                  | 163 |

| 7.3.                              | Future Work                    | 165 |

| 7.4.                              | References                     | 167 |

| List of Abbreviations and Symbols |                                | 169 |

| Acknowledgements                  |                                | 175 |

| List of Publications.             |                                |     |

| Biography                         |                                | 179 |

## Summary

This thesis investigates the system design and circuit implementation of a 24GHz-band short-range radar receiver in CMOS technology. The propagation and penetration properties of EM wave offer the possibility of non-contact based remote sensing and through-the-wall imaging of distance stationary or moving objects. The feasibility of realizing these concepts in hardware with a small form factor could accelerate commercialization and initiate new product opportunities. Minimizing the receiver power consumption to the 15mW range enables 4 hours of continuous operation from a 1.2 gram button sized lithium battery. CMOS technology has the potential for realization of both the RF transceiver and baseband processor in a single chip.

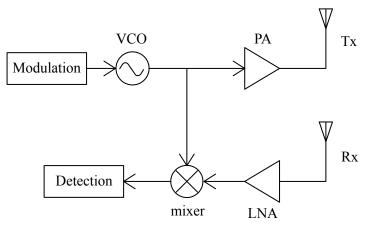

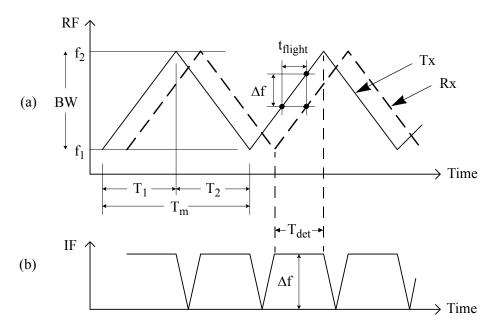

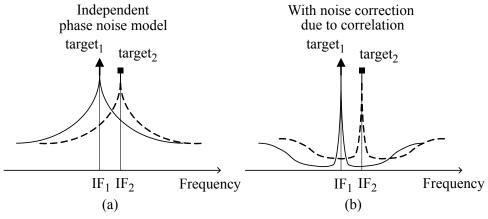

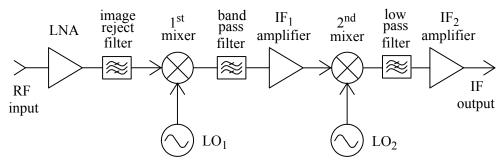

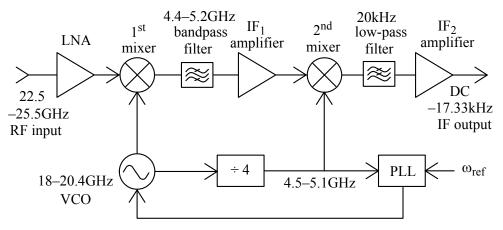

An understanding of the functional requirements is a prerequisite for system optimization. The 15mW power budget necessitates the continuous nature of FMCW radar configuration, which obviates the requirement for a power-hungry transmitting amplifier. FMCW radar in short-range applications benefits from the phase noise correlation between transmitted and received waveforms, which may be exploited to lower the power consumption of the LO generation circuits. A choice for the heterodyne receiver architecture mitigates erroneous detection due to second-order intermodulation distortions caused by interfering radar transmitters nearby, accuracy degradation due to frequency pulling of the ultra-wideband VCO, and signal quality degradation due to flicker noise generated by CMOS transistors. The power dissipation and hardware overhead of a heterodyne receiver are relaxed by proper frequency planning and elimination of the image-reject filter due to frequency chirping property of the FMCW signal.

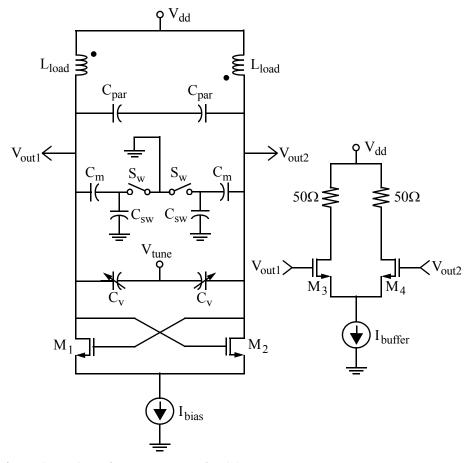

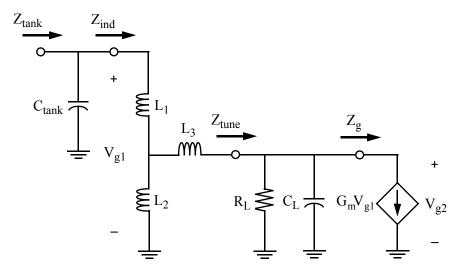

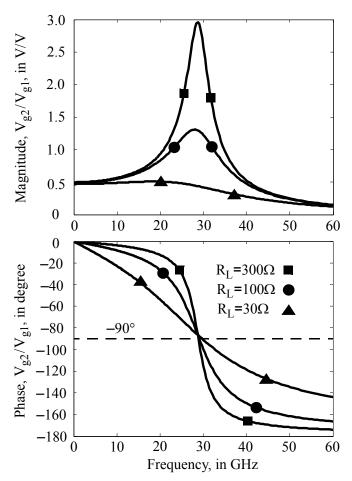

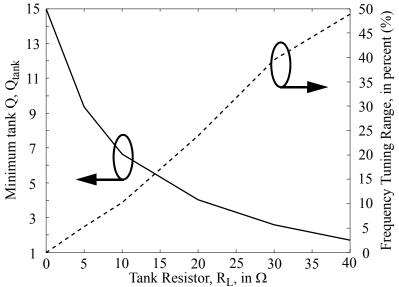

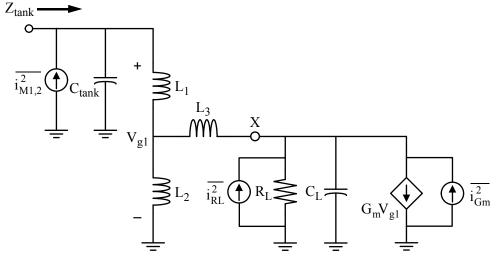

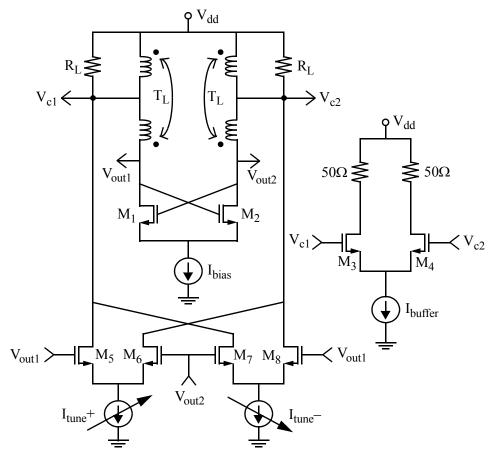

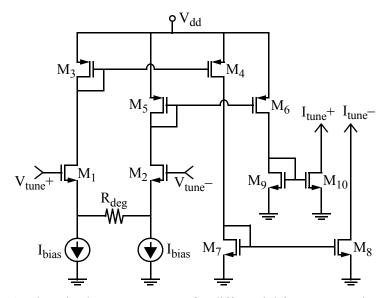

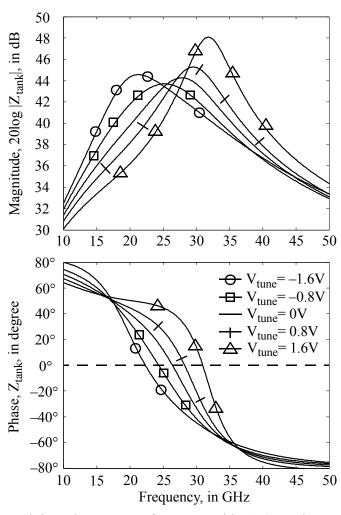

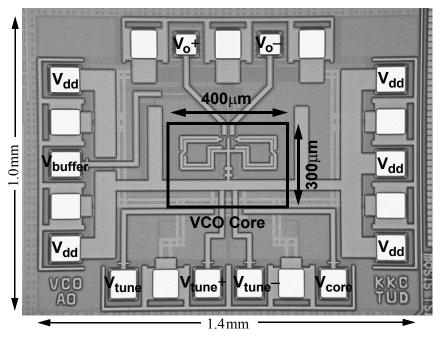

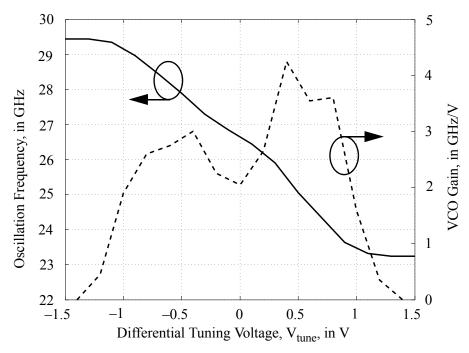

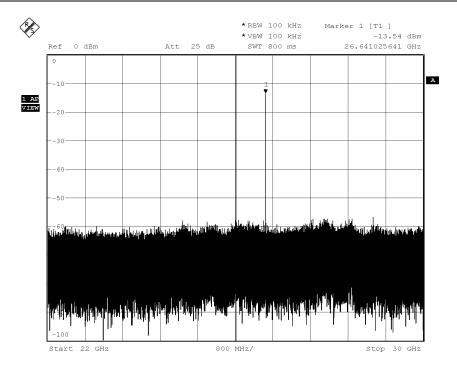

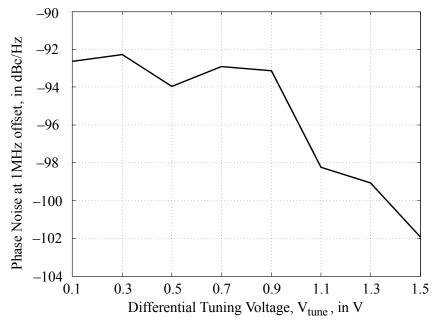

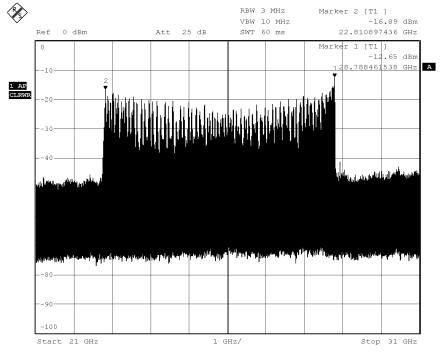

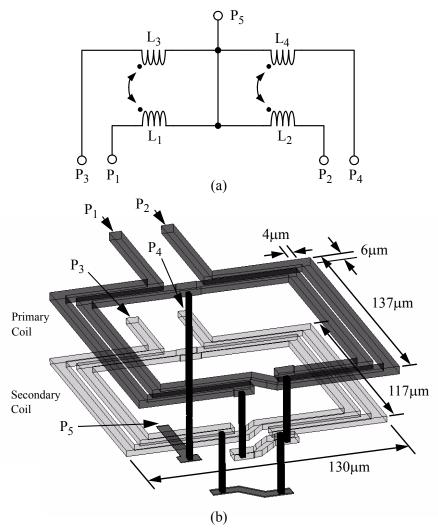

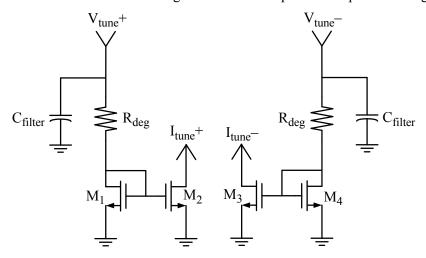

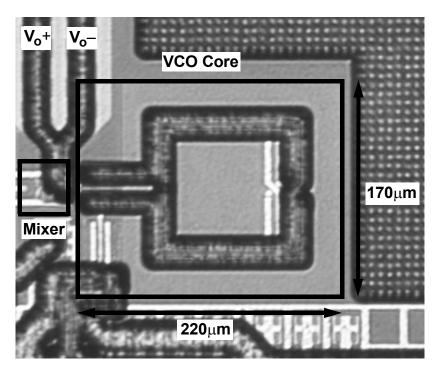

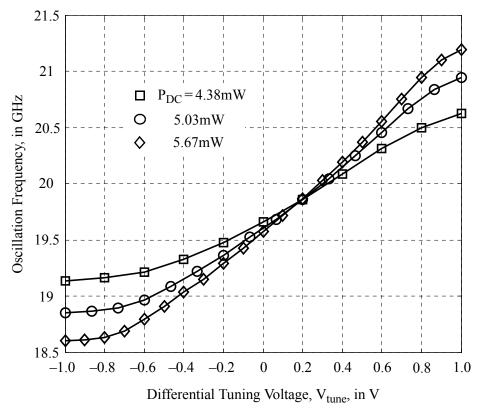

A frequency downconverter for the radar receiver is realized by integrating a LNA, a Gilbert-type mixer, and a VCO running at the carrier frequency. A varactorless frequency tuning scheme is proposed for the VCO which breaks through the conventional trade-offs seen in continuous and wideband mm-wave frequency generation between capacitance tuning ratio, quality factor, and operating frequency in CMOS design. Inductive frequency tuning is enabled by a transformer resonant tank which exploits the gyration (90°) across the input/output terminal voltages of a transconductor. The parallel resonant frequency is controlled by sweeping the sign and magnitude of the transconductance. The VCO is frequency-agile, and is continuously tunable by altering the DC bias current of the transconductance cell. Adaptability between frequency tuning and power consumption is possible. Two VCO test circuits are reported in this thesis. (1) A proof of concept in 0.13µm RF-CMOS consumes 43mW from a 1.2V supply. The frequency coverage is from 23.2GHz to 29.4GHz (23.6% tunable range) and the phase noise is -92.6dBc/Hz at 1MHz frequency offset. (2) A miniaturized prototype is implemented in 90nm CMOS for the radar receiver. It consumes 5.7mW from a 1.0V supply. Its maximum frequency range is from 18.6GHz to 21.2GHz (13.1% tunable range) and phase noise is -82.0dBc/Hz at 1MHz frequency offset.

Operation of a CMOS LNA in the moderate inversion region and at a frequency approaching the transistor's operational limit deteriorates its power gain and noise figure. A two-step LNA optimization algorithm is proposed in this thesis which addresses both the device and circuit levels. Transistor dimensions and biasing are set for optimal power gain, noise figure, linearity, bandwidth, and matching network loss. Partitioning the limited power budget across multiple gain stages maximizes the overall power gain. Optimizing the transistor's interaction with bilateral power flows in a multi-stage amplifier is facilitated by Smith chart based visualization and a computer-aided design methodology. The advantages of this methodology are demonstrated by design examples.

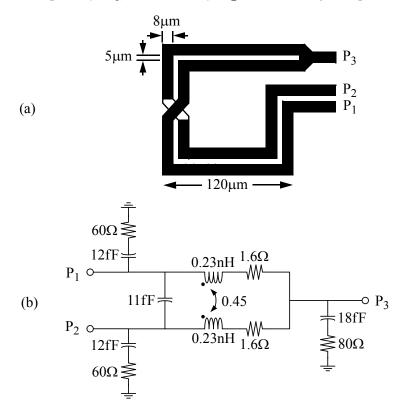

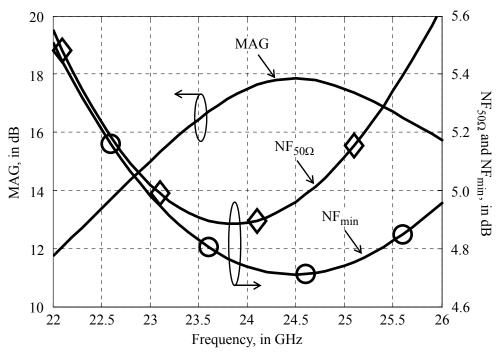

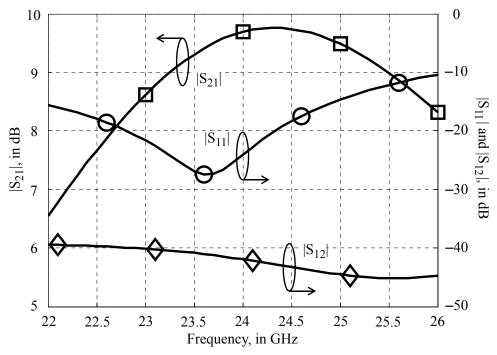

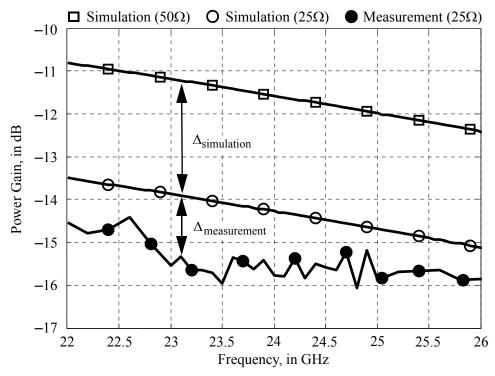

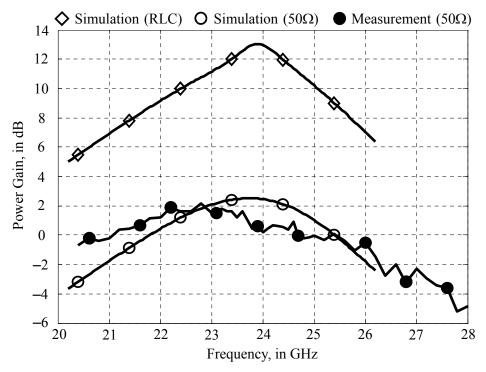

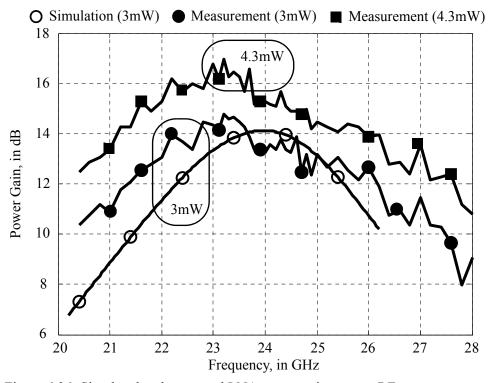

Current-feedback by a 3-port transformer in a cascode LNA is proposed in this thesis in order to increase the power gain and lower the noise figure performance under low-power conditions. The feedback modifies the relationship between the input referred voltage and current noise sources of a common-gate MOS transistor, and thereby fulfills the internal interface impedance conditions in the cascode LNA for optimal power gain and noise figure matching. A two-stage, single-ended, current-feedback cascode LNA prototype is realized in 90nm CMOS. Physical implementation with multiple magnetic components, signal integrity associated with current return path, and circuit simulations employing an S-parameter model are addressed and emphasized in the LNA development. Consuming just 3mW from a 1V supply, the LNA achieves 14.5dB peak power gain, a –3dB gain bandwidth of 5.0GHz. The noise figure varies from 4.9dB to 5.6dB across a 22GHz and 26GHz RF bandwidth, and the IIP3 is –6.0dBm.

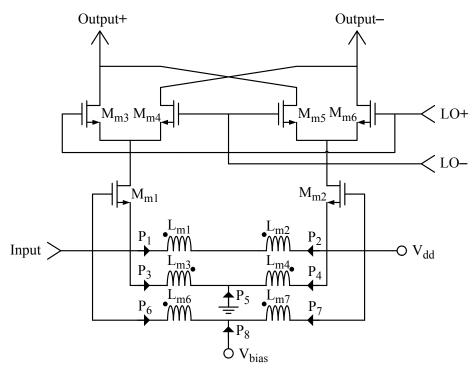

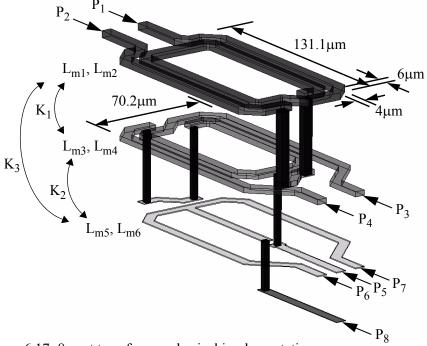

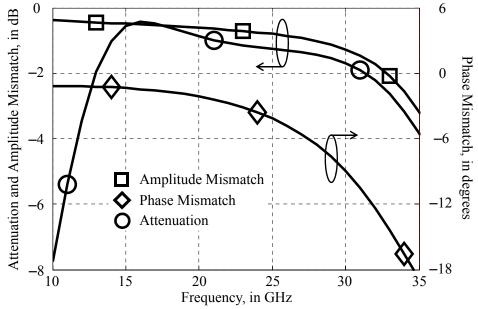

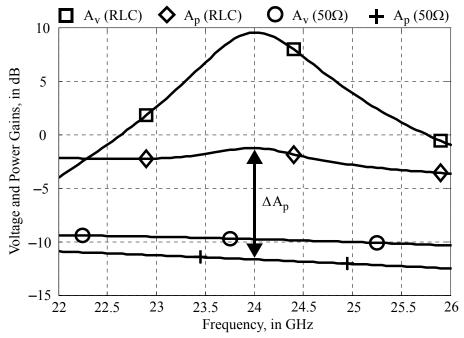

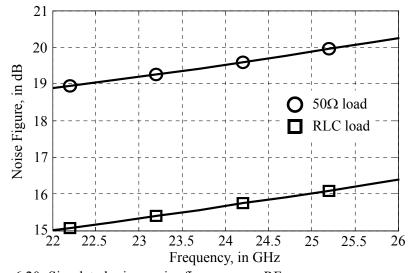

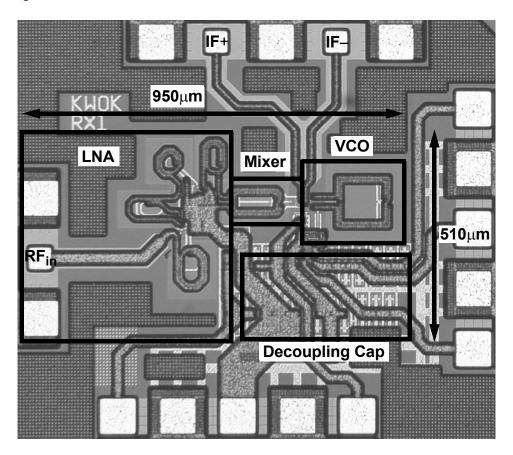

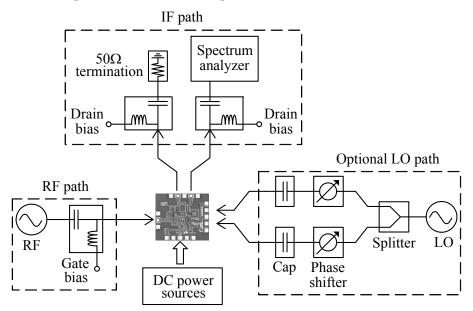

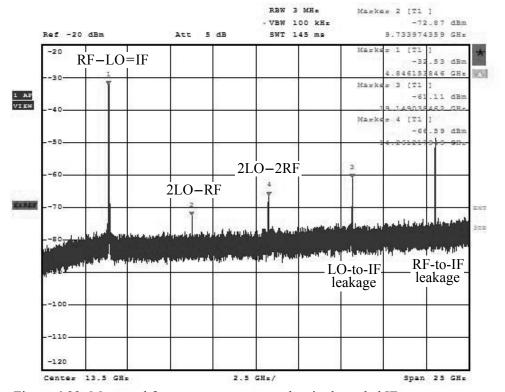

The frequency downconverter is realized by integrating the inductive-tuned VCO and current-feedback LNA with a differential Gilbert-type mixer. Isolation of the LNA single-ended current return path from the rest of the receiver is maintained by a 8-port transformer balun preceding the mixer. This receiver RF front-end draws 10.7mW from a 1.0V supply, and delivers 12.6dB peak power gain, –3dB bandwidth of 1.25GHz. The noise figure varies from 10.6dB to 11.5dB across the RF bandwidth, and the IIP<sub>3</sub> of the downconverter is –12.1dBm.

## Samenvatting

Dit proefschrift onderzoekt het systeemontwerp en de circuitimplementatie van een 24GHz-band radarontvanger voor korte afstand detectie in CMOS technologie. Door gebruik te maken van de propagatie- en penetratie eigenschappen van EM golven is het namelijk mogelijk om stilstaande of bewegende objecten (zelfs achter een muur) op afstand te detecteren of te visualiseren. De mogelijkheid om deze radar systemen te kunnen realiseren in zeer compacte afmetingen, kan hun commercialisatie versnellen en nieuwe product mogelijkheden introduceren. Door het stroomverbruik te minimaliseren tot 15mW, kan een ontvanger 4 uur lang continue operationeel zijn met slechts een 1,2 gram lithium knoopcel batterij als energiebron. Het gebruik van CMOS technologie maakt het mogelijk om zowel de RF zendontvanger als basisbandprocessor in een enkele chip te implementeren.

Om zo'n radar systeem te optimaliseren, is het essentieel om de functionele eisen te begrijpen. Om bijvoorbeeld het energieverbruik tot 15mW te beperken kan gebruik worden gemaakt van het continue karakter van het FMCW radar concept. Hiermee kan de eis voor een energie verslindende hoogvermogen zendversterker worden ondervangen. Verder heeft een FMCW radar voor de korte afstand ook het voordeel dat men gebruik kan maken van de faseruiscorrelatie tussen de zend- en ontvangstgolf; hierdoor kunnen de eisen en dus ook het energieverbruik van de LO signaal generatie worden verlaagd. De keuze voor een heterodyne ontvanger architectuur vermindert ook detectiefouten die t.g.v. tweede-orde intermodulatie effecten veroorzaakt kunnen worden door interfererende radarzenders in de omgeving. Ook frequentie "pulling" van de zeer breedbandige oscillator kan beter worden tegengegaan waardoor de nauwkeurigheid verbeterd. Verder wordt in een heterodyne systeem de invloed van flikkerruis van de CMOS transistors beperkt wat de signaalkwaliteit ten goede komt. Het iets hogere energieverbruik en de compliciteit van een heterodyne ontvanger kunnen worden ondervangen door een optimale frequentieplanning en de eliminatie van het "image-reject" filter, dit is mogelijk door gebruik te maken van de frequentie "chirp" eigenschappen van het FMCW signaal.

De frequentieomzetting in de radarontvanger is gerealiseerd door het integreren van de LNA, een Gilbert-mixer en een VCO die opereert op de werkfrequentie. Een varactor-vrije frequentieverstemming is toegepast in de VCO om de traditionele compromissen tussen verstembaarheid, kwaliteitsfactor en werkfrequentie te ondervangen in CMOS gebaseerde ontwerpen. De toegepaste "inductieve" frequentieverstemming wordt mogelijk door gebruik te maken van een resonerende transformator tank die de 90° fasedraaiing tussen de ingang/uitgang spanning van de "transconductor-cell" aansluitingen benut. In deze configuratie kan de resonantiefrequentie worden geregeld d.m.v. het teken en de grootte van de transconductantie. M.b.v. deze configuratie kan de VCO continue worden veranderd door het aanpassen van de DC-stroom van de "transconductor-cell". Aanpassingen in frequentie verstemmingsbereik en stroomverbruik zijn mogelijk. Twee VCO testcircuits

worden beschreven in dit proefschrift, namelijk: (1) Een demonstratie circuit t.b.v. het aantonen van het concept in 0,13µm RF-CMOS, welke 43mW verbruikt van een 1,2V voeding. Het frequentiebereik van dit circuit is 23,2GHz tot 29,4GHz (23,6% relatieve bandbreedte) met een faseruis van –92,6dBc/Hz bij 1MHz frequentie-offset. (2) Een geminiaturiseerd prototype van de radarontvanger geïmplementeerd in 90nm CMOS. Dit circuit verbruikt 5,7mW van een 1,0V voeding. Het maximale frequentiebereik is 18,6GHz tot 21,2GHz (13,1% relatieve bandbreedte) met een faseruis van –82,0dBc/Hz bij 1MHz frequentie-offset.

Het gebruik van een CMOS LNA in het inversiegebied, in combinatie met een werkfrequentie die de limiet van de transistor benadert, verslechtert de haalbare vermogensversterking en ruis. Een twee-stap LNA optimalisatie-algoritme is voorgesteld in dit proefschrift waarin rekening wordt gehouden met zowel de transistors als de feitelijke circuitimplementatie. In deze aanpak worden transistor afmetingen en stoom ingesteld voor een optimale vermogensversterking, ruisgetal, lineariteit en bandbreedte, terwijl de benodigde matchingnetwerken worden beperkt voor hun verliezen. Het verdelen van het beperkte vermogensbudget over meerdere versterkingstrappen helpt om de totale vermogensversterking te verhogen. Het optimaliseren van de interactie van de transistor met de bilaterale energiestromen in een meertrapsversterker wordt vergemakkelijkt door een Smith chart gebaseerd visualisatie en computer-aided ontwerpmethode. De voordelen van deze techniek worden aangetoond door ontwerpvoorbeelden.

Stroomterugkoppeling d.m.v. een 3-poort transformator in een cascode LNA is in dit proefschrift geïntroduceerd om de vermogensversterking te verhogen en het ruisgetal te verbeteren onder klein-signaal condities. Deze terugkoppeling wijzigt de interne relatie tussen de ingangsspanning en -stroom ruisbronnen van een "common-gate" MOS transistor. Hiermee kan aan de impedantie condities in de cascode LNA worden voldaan voor optimale vermogen en ruis matching. Een twee-traps stroomgekoppeld cascode LNA prototype is gerealiseerd in 90nm CMOS. De fysieke implementatie van de LNA met meerdere magnetische componenten, de bijbehorende signaalintegriteit ten aanzien van het stroomretourpad en circuit simulaties welke gebruik maken van een S-parameter modellen worden belicht en bediscussieerd. Met een energieverbruik van slechts 3mW in combinatie met 1V voeding behaalt deze LNA 14,5dB vermogensversterking bij een –3dB bandbreedte van 5,0GHz. Het ruisgetal varieert van 4,9dB tot 5,6dB over de 22GHz tot 26GHz RF-band en de bijbehorende IIP3 is –6,0dBm.

De frequentieomzetting is gerealiseerd door integratie van de verstelbare-inductie VCO en stroom-teruggekoppelde LNA in combinatie met een differentiële Gilbert-cel mixer. De isolatie van de (single-ended) LNA retourstroom met de rest van de ontvanger wordt gehandhaafd door het plaatsen van een 8-poort transformator balun voor de mixer. Deze RF ontvanger verbruikt 10,7mW uit een 1,0V voeding, en levert 12,6dB vermogensversterking bij een –3dB bandbreedte van

$1,25 \mathrm{GHz}$ . Het ruisgetal varieert van  $10,6 \mathrm{dB}$  tot  $11,5 \mathrm{dB}$  over de RF bandbreedte, met een IIP3 van  $-12,1 \mathrm{dBm}$ .

## Chapter 1

## Introduction

The discovery of electromagnetic waves and their properties in the late 19<sup>th</sup> century led to the development of radio detection and ranging (RADAR) technology. The first radar-like apparatus was demonstrated in the Rotterdam harbour of the Netherlands in 1904 [1.1]. It was designed to detect the presence of distant objects on ships for collision avoidance using a spark-gap transmitter, however, it was incapable of providing range information. The first radar for aircraft detection was made practical in Britain in 1935 [1.2] after the invention of the cavity magnetron source [1.3]. Global development of military radar systems evolved rapidly during the Second World War [1.4]. These high-power, pulse-type radars were used to track aircraft and ballistic missiles. Commercialization of the radar technique happened in the post-war era, where it found widespread application in air traffic control [1.5], marine navigation [1.6], weather forecasting [1.7], geological research [1.8], and ground vehicle speed monitoring [1.9]. Advances in integrated circuit and semiconductor device technologies are now enabling the development of low-cost radar products for the automotive [1.10], industrial [1.11] and consumer electronics [1.12] markets, CMOS technologies feature superior mixed-signal integration capability [1.13] and low implementation cost in high volume production due to the planar manufacturing processes [1.14]. This has stimulated miniaturization of commercial radar devices into a small form factor suitable for use in an automobile or for handheld applications using silicon IC technology, and the opportunity to reduce the bill of materials (BoM) cost of the radar products simultaneously through the use of silicon CMOS.

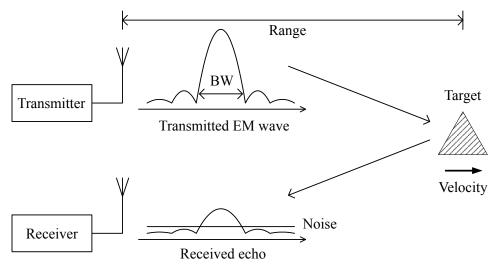

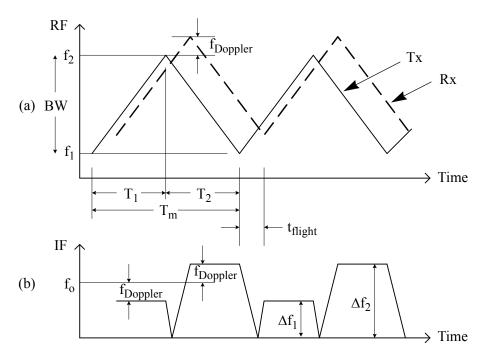

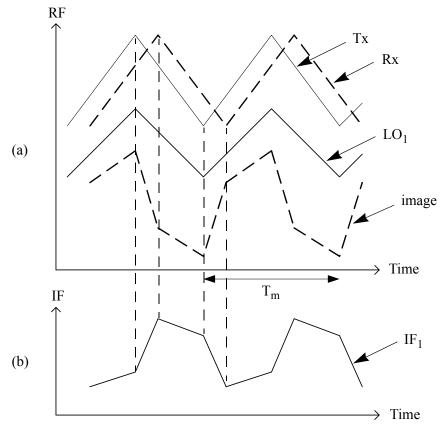

Radar detects remote object by transmitting an electromagnetic (EM) wave towards the target and sensing the reflected waveform, or the "echo" signal. Figure 1.1 illustrates the radar operation with transmitted and received frequency spectra. The time of flight is calculated by recognizing the delay time and frequency difference between the transmitted and echo signals, and the range and relative velocity of distant objects can be detected subsequently.

The purpose of this thesis is to investigate the feasibility of implementing a 24GHz-band short-range radar (SRR) receiver in CMOS technology for the automotive, industrial and consumer electronics market with power consumption in the 15mW range. This enables 4 hours of continuous operation from a button sized lithium battery with a weight of 1.2 grams and energy capacity of 60mAh [1.15].

Factors that determine detection accuracy include the transmit frequency

Figure 1.1 Radar operation with transmitted and received frequency spectra

bandwidth and receiver sensitivity. The minimum resolvable range, or range resolution ( $\Delta R$ ) in radar terminology, is inversely proportional to the bandwidth of the transmitted wave (BW) [1.16]. It is expressed as

$$\Delta R = \frac{c}{(2 \cdot BW)},\tag{1.1}$$

where c is the speed of light. From Eqt. (1.1), the occupied bandwidth requirement on the transmitter and receiver is as wide as 3GHz for a SRR resolution of 5cm.

Selection of the radar frequency band is a trade-off between the fractional bandwidth occupied by the Tx signal and the limits of the technology used. Most commercial usage of the radio spectrum at present is concentrated at frequencies below 10GHz [1.17]. For example, the global system for mobile communication (GSM) occupies frequency bands at 850MHz, 900MHz, 1.8GHz, and 1.9GHz [1.18], and the IEEE-802.11 wireless LAN protocols operate in the 2.4GHz and 5GHz bands [1.19]. Operating in a higher frequency range avoids overcrowding the valuable bands used for mobile and wireless data communications, and relaxes the circuit requirements [1.20] by minimizing the fractional bandwidth as defined by [1.21]

fractional bandwidth =

$$\frac{3 \text{dB bandwidth}}{\text{center frequency}}$$

. (1.2)

On the other hand, the upper frequency range is limited by the availability of suitable electronic technology for hardware implementation, because performance from active and passive devices always declines with increasing frequency. The 5GHz spectrum at the 24GHz band available from North America and Europe for SRR applications is a good compromise between these factors [1.22].

The choice of this center frequency also favours a smaller antenna because the physical dimensions of an antenna are inversely proportional to the operating frequency. The wideband circular disc monopole antenna in [1.23] realizes >10dB return loss from 2.5GHz to 55GHz with a disc diameter about one-quarter of the signal wavelength of the first resonant frequency at 3GHz. For the 24GHz SRR, the antenna dimension is further reduced because the lower-end of the frequency range is much greater, at around 22.5GHz.

Regulatory authorities across North America [1.24] and Europe [1.25] allocate certain frequency bands for radar sensing and regulate the maximum radiated power level. The transmitted power experiences two times the free space path loss as it travels from the antenna to the target and back again, as illustrated in Figure 1.1. From Friis' equation [1.26], this loss is given by

radar path loss =

$$\frac{\text{received power}}{\text{transmitted power}} = \frac{1}{(4\pi)^3} \cdot \frac{c^2}{f^2 R^4} \cdot (\sigma \cdot G_r \cdot G_t), \quad (1.3)$$

where c is the speed of light, f is the signal frequency, R is the target range,  $\sigma$  is the radar cross section of the target, and  $G_r$  and  $G_t$  are the receiver and transmitter antenna gains, respectively. Assuming that  $\sigma = 1 \text{m}^2$  and  $G_r = G_t = 10 \text{dB}$ , the radar path loss equals 91dB for a 10m range at 24GHz.

The received echo is accompanied by the thermal noise due to the receiving antenna radiation resistance [1.26]. This noise power has a constant power spectral density over frequency as depicted in Figure 1.1, and its integrated power  $(P_n)$  across the signal bandwidth (BW) is given by

$$P_n = k \cdot T \cdot BW , \qquad (1.4)$$

where k and T are Boltzmann's constant and absolute temperature, respectively.  $P_n$  equals -79.0dBm for the 3GHz occupied bandwidth at 300K (room temperature). With 0dBm transmit power, the signal-to-noise ratio (SNR) of the echo signal at the receiver input is as low as (0dBm - 91dB) - (-79dBm) = -12dB.

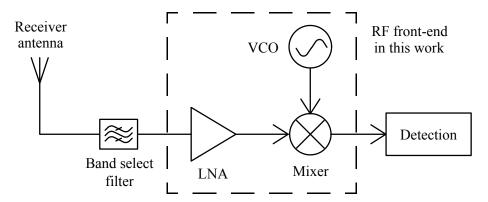

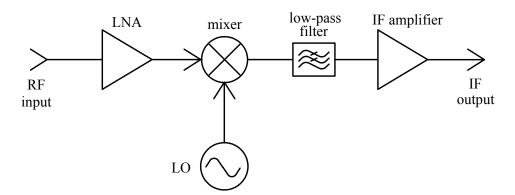

Figure 1.2 illustrates the proposed block diagram for the SRR receiver. The echo signal is first picked up by a receiver antenna and is passed through a band

Figure 1.2 Block diagram of a SRR receiver

select filter. Its power level is then scaled up by a low-noise amplifier (LNA) and is subsequently frequency downconverted by the mixer and voltage-controlled oscillator (VCO) prior to a detection circuit block at IF. The designs reported in this thesis cover the implementation and optimization of the wideband signal generation, low-noise amplification and subsequent frequency downconversion, which are integrated into a low-power radar receiver RF front-end.

The LNA is necessary at the receiver to scale up the tiny echo power while adding as little noise as possible in order to maintain the fidelity of the target information. The detection circuit could be implemented in the digital domain [1.27]. The downconversion mixer together with the wideband VCO translates the frequency of the received echo power to an IF prior to digitization by an analog-to-digital converter (ADC). This relaxes the sampling bandwidth requirement on the ADC [1.28].

The designs proposed in this thesis exploit the high frequency capability of advanced nanometer-scaled CMOS technology together with the utilization of onchip magnetic components to lower power consumption and realize wideband performance specifications. The processing yield and system integration capability of CMOS technology has the potential for realization of both the RF transceiver and baseband processor in a single chip. The LNA gain and noise performance are optimized at low-power dissipation by power gain and noise matching among cascaded amplifying stages. A wideband VCO implemented without any extra-cost technology options is realized by a transconductance frequency tuning scheme that does not use a varactor. Adaptive performance tuning is possible by trading-off power consumption and the frequency tuning range. The mixer is implemented with the Gilbert double-balanced mixer configuration, and an integrated balun couples the differential mixer input to the single-ended LNA output. The measured silicon prototype verifies that these components satisfy the SRR receiver specifications proposed in the system study of this thesis.

#### 1.1 Motivation

The propagation and penetration properties of EM waves offer the possibility of non-contact based remote sensing [1.29] and through-the-wall imaging [1.30] of stationary or moving objects at a distance. The feasibility of realizing these concepts in hardware with a small form factor could accelerate their commercialization with widespread acceptance.

### 1.1.1 Advantages of Radio Ranging

Alternative technologies exist for the remote detection of objects, including passive-type video-based imaging, and infrared [1.31] or ultrasonic sensing [1.32]. Passive sensors are inherently safe and pose no risk in industrial applications because there is no signal emission in the detection process. They are not subject to government

1.1 Motivation 5

regulations regarding interference, coexistence or compliance. Ultrasonic sensors are similar to radar in that distance to a target is calculated from interpretation of an echo signal, but at a lower transmitted frequency (e.g., around 18kHz) [1.32]. The signal processing requirements are thus much less demanding with lower BoM cost and power consumption. However, various performance aspects make radio ranging superior to other techniques.

The penetration of millimeter wavelength radio waves [1.33] compared to visible light or ultrasonic waves enables the radar to be mounted behind the vehicle body in automotive applications, or inside the case for most non-metallic handheld products. This is an important factor that promotes the widespread acceptance and market value of a radar sensor for consumers by offering a stylistic advantage in product appearance. This penetration property also gives radar immunity to inclement weather conditions such as rain, fog, high humidity, and heavy dust [1.34].

Signal attenuation due to atmospheric absorption is also the lowest for microwave propagation compared to non-radio frequency bands. During fog condition with visibility of about 1km, [1.35] compares the attenuation of visible light and a 94GHz carrier and they are measured 16dB/km and 2dB/km, respectively. At sea level, lowering the carrier frequency from 94GHz to 24GHz further reduces the atmospheric absorption by about 0.25dB/km [1.36]. Radar sensors therefore have excellent performance for the maximum detectable range among different sensing techniques. Compared to a video-based imaging sensor, their functionality is also not influenced by the time of day or night, or by poor lighting in an indoor environment.

Radar range resolution is inversely proportional to the signal bandwidth [1.16], and millimeter range resolution can be easily achieved by an ultra-wide transmit bandwidth (UWB). The Doppler shift [1.37] introduced by the velocity of both fast and slow moving targets are more resolvable in radar sensing because EM waves travels with the speed of light rather than at the speed of sound.

#### 1.1.2 Potential Markets

The cost reduction of radar implementation could initiate emerging opportunities in different markets. One potential mass-market application is automotive collision avoidance radar, which is intended to increase road traffic safety and lower the number of road accidents. Studies estimate that 95% of road accidents result from human errors [1.38], and that most collisions could be prevented if an additional 2.3 seconds of reaction time were available to the driver [1.39]. One vision for the future is to develop an array of technologies to warn the driver prior before a possible collision, and exercise pre-crash preparations such as airbag launch, pre-tensioning seat belts, etc., if a collision is unavoidable. Short-range radar in an automotive application favors a hybrid array of radar units installed around the vehicle for different functions [1.38]. Potential applications include rear and front collision warning, to pre-crash airbag launch, parking aids, and blind spot detection [1.40]. These

sensors could reduce the number of fatalities, injuries, damage to property, and economic losses to the society. The European Union permits the use of 24-GHz band sensors for the automotive SRR until January 1<sup>st</sup> 2022 [1.41]. Nevertheless, the technologies developed in this thesis are applicable to other frequency bands as well.

Radar sensors currently available in the industrial sector offer a broad range of measurement capabilities [1.42], but in a bulky form factor with an approximate weight of 6.1kg and starting at a cost of US\$3,381 (quoted in April 2015) per unit [1.43]. Industrial automation could be developed further with the penetration of low-cost microwave radar. Non-contact measurements of the existence, distance or velocity of solid or liquid materials is beneficial to the optimization of the cost of production and increased throughput, robustness and quality. This is applicable to either food or pharmaceutical plants in controlled conditions, or chemical or construction sites with high temperature, high pressure, or extremely dusty environments.

Tools exist that estimate the range of objects with known dimensions using video-based cameras, but their accuracy is poor [1.44]. Radar distance measurement of a stationary target demands less signal processing power for the calculation algorithms with simple hardware while maintaining accuracy. This opens-up an opportunity for handheld wireless ranging for length measurements (e.g., an electronic tape measure) or something similar if the RF circuitry for the radar could also be implemented at minimal cost. Embedding radar devices in smartphones or wearable electronic watches or glasses may make the "X-ray glasses" advertised widely in 20<sup>th</sup> century comic books a potential reality.

### 1.1.3 Advantages of CMOS Implementation

The continuous scaling of CMOS transistor feature sizes according to Moore's law has strengthened digital computing power and increased data throughput. The technological advantages of digital signal processing are further solidified by the advancement of automated CAD tools for logic synthesis, place-and-route, and functional verification. With the ever decreasing power consumption of digital processors, the advantage of using digitally assisted analog techniques [1.45] to enhance performance of analog and RF circuitry becomes attractive because of its potential for reconfigurability [1.46], scalability across technology nodes, and shortened design time with automated CAD tools.

A 24GHz SRR transceiver can benefit from the evolution of digital computation capability. For example, carrier leakage in the RF transmitter can be suppressed by applying digital compensation algorithms, similar to the off-chip FPGA platform implemented in [1.47]. Linearization of the transmitted modulated carrier by dithering the VCO tuning port via a digital-to-analog converter is demonstrated in [1.48]. Automatic gain control in the RF receiver can be accomplished by adapt-

ing the bias current via digital switches [1.49], with the analog gain steps being compensated in the digital baseband [1.50]. Correction of the analog impairments in the digital backend after the A/D conversion is also possible, such as improvements to the amplitude and phase errors of a radar receiver's IF quadrature signal path [1.51], or the linearity of a pipelined ADC [1.52].

The projection of an increase in silicon wafer diameters from the current state-of-the-art of 300mm to the 450mm, which is expected for mass production in 2017 [1.53] will continuously lower the cost per unit silicon die area for a given technology node.

## 1.2 Design Challenges

The quality and accuracy of a radar sensor does not only depend on the electrical performance of each building block, but also on the interaction of almost everything involved within the transceiver link [1.54]. This covers the fields of communication theory, wireless standardization, microwave and analog/RF circuit design, and digital signal processing. This thesis investigates the system and circuit design of a low-power, low-cost 24GHz UWB SRR radio receiver, and the challenges of designing and implementing the analog/RF front-end in CMOS technology. Implementation-level considerations are emphasized with respect to passive components integration, performance, and power dissipation. The outcomes of this study could enable other new opportunities radar systems.

#### 1.2.1 Radar Hardware Implementation

Radar used to be an expensive technology with applications limited to air defense, air traffic control or weather forecasting due to the hardware implementation cost. The RF transceiver in a radar usually consists of discrete microwave components such as waveguides, power dividers, isolators, circulators, directional and hybrid couplers, etc. [1.55]. Signal generation, amplification, and frequency translation are feasible with planar monolithic microwave integrated circuit (MMIC) implemented in compound semiconductor technologies [1.56]. Production yield and reliability problems for these circuits limit them to only small-scale integration [1.57], and precision analog and low-power digital are not feasible in these MMICs. Furthermore, monolithic integration of digital switches, power control, voltage regulators, etc., is not possible. The state-of-the-art maximum wafer diameter available in the industry is 150 mm [1.58] which is one-half to one-third the current silicon wafer size used in CMOS production. The computational demands at baseband frequency for either time-gating for pulse-type radar or fast Fourier transform (FFT) signal processor for continuous-type radar could only be satisfied with the employment of a hybrid implementation approach with different semiconductor technologies for the RF and baseband circuitries. Additional regulations and licensing requirements exist for radar applications which govern the frequency band and power emission levels [1.24,1.25]. These factors contribute to the high cost of the radar equipment

realization in the past.

Consumers favor low-cost, low-power products, but also sophisticated functionality. They also demand high performance. The widespread acceptance of radio ranging in the automotive, industrial and consumer electronics markets can be gained only after economical devices become available satisfying the required performance for a particular application. System-on-chip (SoC) integration of the RF radar front-end with data converter, power management, and digital baseband processor in low-cost CMOS technology could offer a possible solution for high-volume applications.

#### 1.2.2 Disadvantages of CMOS Implementation

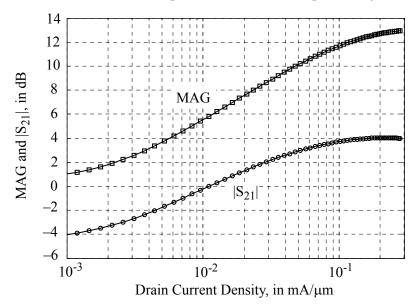

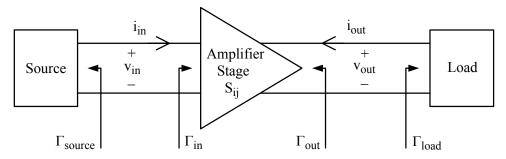

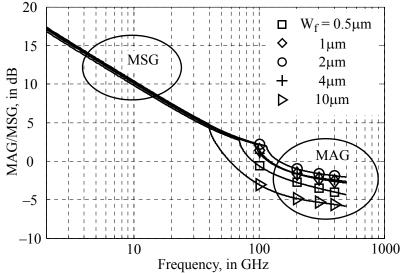

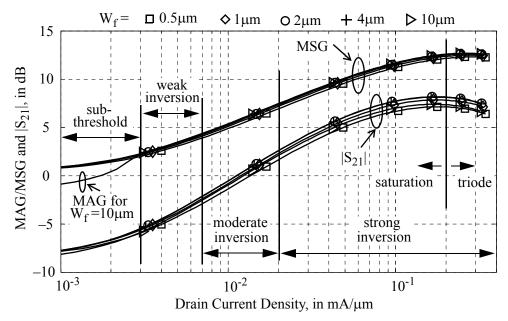

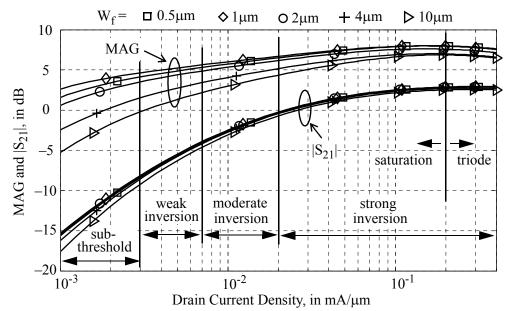

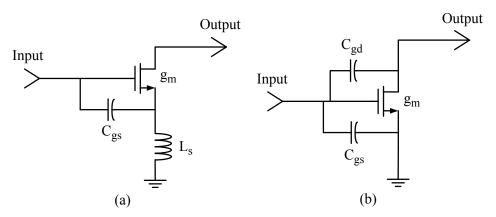

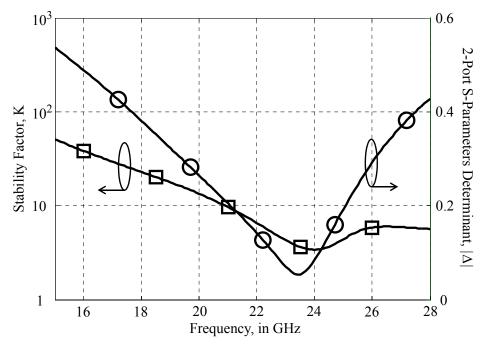

The performance of CMOS transistors can be quantified by the maximum available gain (MAG). It is plotted in Figure 1.3 together with the forward transmission coefficient ( $|S_{21}|$ ) for an NMOS transistor in 90nm technology having a 1µm finger width, for varying drain current density at a fixed 0.6V drain-source voltage. Both of these gain parameters increase with the bias current in the saturation region but there is a significant gap between the MAG and  $|S_{21}|$ . This difference arises from the need for passive matching networks which transform the  $50\Omega$  source/load resistances to a higher impedance level. These networks resonate out the transistor's parasitic capacitance to realize higher gain. For a constant gain-bandwidth product available from the transistor, adding a narrowband matching network with high quality factor (Q) reduces the circuit bandwidth. This bandwidth narrowing is accentuated in a cascade of independent narrowband amplifier stages.

Figure 1.3 Simulated maximum available gain and forward transmission coefficient of an NMOS transistor at 24GHz

The overall RF bandwidth and gain flatness are sensitive to temperature drift and parameter variations of the matching networks. Therefore, careful and precise modelling of the passive networks becomes essential to prevent the measured data deviating from the simulated predictions.

#### 1.2.3 Low-Voltage, Low-Power Implementation

Lowering the circuit supply voltage has the benefit of minimizing the power dissipation for a given bias current. This could maximize battery lifetime, or allow the usage of a coin cell battery with minimal size and weight. This is a critical factor for the realization of portable devices, and in particular integrating the SRR into wearable consumer electronics products such as watches or glasses.

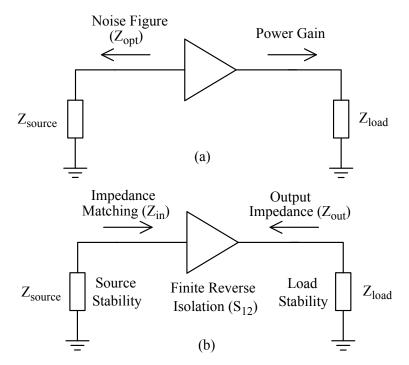

The low-voltage requirement excludes the optimum operation of certain high performance circuit topologies for signal amplification and signal generation, such as the cascode amplifier or Colpitts oscillator. The 90nm CMOS technology utilized in this work concurrently set the nominal operating supply at 1.0V [1.59]. Minimizing the bias current in active devices without compromising performance is another important design objective to be satisfied.

CMOS transistor noise figure and gain parameters are proportional to the drain bias current density. Biasing a transistor at low current constrains the performance available from a single amplifier stage. The cascade of multiple gain stages is therefore usually necessary in order to fulfill system requirements. With each amplifier loaded by a single LC resonant tank, the number of on-chip coils grows with the number of stages. Hence, the layout floorplan with multiple passive components that consumes minimal chip area becomes a critical part of the design process.

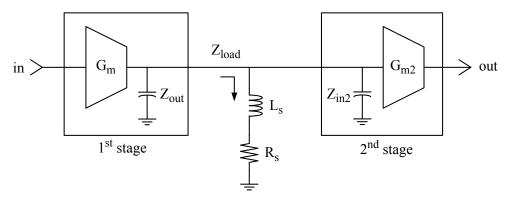

The finite reverse isolation of an amplifier without the voltage headroom for a cascode stage must also be addressed in the optimization routine. The selections of amplifier input and output resonant networks for impedance and gain matching are dependent on each other, and the co-design of both active and passive components becomes critical in the optimization process.

### 1.2.4 Millimeter-Wave Wideband Frequency Generation

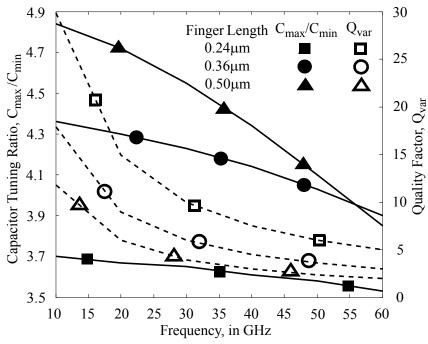

VCOs have typically used a voltage-controlled capacitor (i.e., varactor) to electrically control the resonant frequency of an LC tank, thereby allowing electronic tuning of the oscillation frequency. In contrast to operation below 10GHz, where inductor Q dominates losses in the on-chip tank, a varactor implemented in production VLSI technologies (silicon CMOS or SiGe BiCMOS) tends to dominate resonant tank losses at millimeter-wave (mm-wave) frequencies (i.e., above 12.5GHz on a silicon chip). Since the equivalent tank loss is proportional to the inductance to capacitance (L/C) ratio, only a relatively small capacitance can be used if high spectral purity is required from the VCO. In addition, there is a trade-off between the varactor Q and capacitance tunability as its bias voltage varies from maximum to

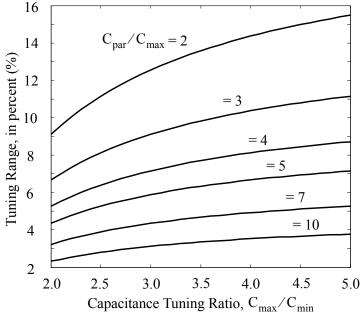

minimum (i.e.,  $C_{max}/C_{min}$ ). The  $C_{max}/C_{min}$  ratio is typically less than three at mm-wave frequencies. Also, parasitic capacitances of the transistors and the tank inductor limit the portion of the total tank capacitance that can be tuned electrically. These three factors: limited total capacitance, available capacitance ratio, and circuit parasitics, restrict the tuning range of a conventional LC VCO to less than 10% at approximately 20GHz [1.60,1.61] and less than 5% at 60GHz [1.62-1.64].

VCOs with 25% tuning range have been implemented using supply and tuning voltage magnitudes at, or above 3V in SiGe BiCMOS (–5.6V and 4.5V in [1.65], –5.5V and 3.0V in [1.66]) when a collector-base junction is used as a varactor diode [1.65], or in technologies featuring processing options for the varactor devices [1.66]. Also, VCOs implemented in silicon-on-insulator (SOI) CMOS technologies, where the parasitic capacitance for both active and passive devices is lower than in bulk CMOS, have demonstrated tunability over a wide frequency range [1.67-1.69]. However, non-standard and/or dual supply voltages increase system and component costs. Extra-cost processing options for the varactor, or implementation in SOI-CMOS adds to the BoM of an integrated circuit, and are not a favorable choice for a low-cost radar implementation.

As to be explained in Chapter 3 of this thesis, a wideband, frequency-agile, and continuously-tunable VCO is an essential element of frequency-chirping continuous-type radar with low power consumption. The techniques of multi-band VCO by switchable capacitor arrays [1.70] or a multi-mode resonant tank [1.71] in order to achieve high frequency tuning range are inapplicable to the low-power radar implementation because of their discrete and discontinuous frequency tuning curves across the radar bandwidth.

### 1.2.5 On-Chip Magnetic Components

In CMOS technology, magnetic components such as inductors and transformers are implemented by the interconnection of planar coils separated from the substrate by oxide layers. The quality factor of these components is limited by the substrate loss due to electric coupling to the semiconducting silicon substrate and the ohmic losses from metal strips and via interconnections [1.72]. Newer CMOS technology nodes come with an increased number of metal layers in order to cope with the routing congestion in modern ULSI system [1.73]. This increases the oxide thickness underneath the magnetic components and lowers the substrate loss due to electric coupling. On the other hand, the metal thickness scales down together with the active device minimum feature size to favour digital circuit performance by increasing the logic gates layout density and lowering power dissipation caused by the dynamic switching of current. This increases the ohmic loss and the degradation is further magnified by the finite skin depth at the mm-wave frequencies. Stacking multiple metal layers [1.74] lowers the ohmic loss at the cost of higher substrate coupling between metal layers in the stack close to the silicon substrate. Iterative EM simulations are unavoidable when optimizing the coil dimensions for a desired inductance value and operating frequency range.

The use of multiple magnetic coils is necessary for the implementation of matching networks, a multi-stage LNA, mixer, and LO generation circuits targeting low power dissipation at mm-wave frequencies. EM coupling between these coils must be captured in simulation to prevent shifting of the resonant frequency in an individual LC tank, or potential stability problems caused by parasitic positive feedback loops. Traditional lumped RLC or S-parameter models for individual coils are inadequate to characterize a complex multiple-coil structure, and a new modelling and simulation strategy is necessary for accurate prediction of performance.

## 1.3 Thesis Organization

This thesis is organized as follows. Chapter 2 lays out the theoretical framework for the design and optimization of a CMOS wireless receiver. It presents the analog impairments in receiver design with physical parameters such as noise, non-linear distortion, and phase noise, as well as definitions and comparisons of different gain parameters in a design of cascaded stages.

The principle of operation for FMCW radar is presented in Chapter 3, along with radar receiver design and link budget considerations. A proposed architecture for a prototype 24GHz-band SRR receiver, as well as a design example with emphasis on the demonstration of a SRR in CMOS technology is also described.

Chapter 4 presents a review of different frequency tuning techniques in CMOS technology, and proposes a new continuous-tuned differential VCO that does not require an on-chip varactor for frequency tuning. The operation principle and adaptability between frequency tuning and power consumption are discussed along with simulation and measurement data for two silicon prototypes.

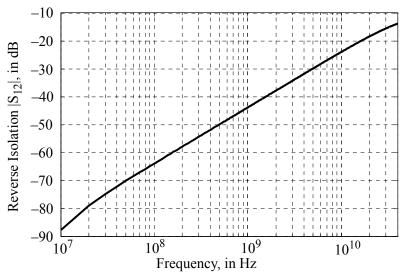

Chapter 5 discusses the fundamental aspects of LNA design and optimization, and presents a new and efficient Smith chart based bilateral methodology for the design and optimization of a low-voltage, low-power CMOS LNA. Design examples are given to demonstrate the advantages of the proposed optimization algorithm on cascade of (non-cascode) stages with finite reverse isolation.

Chapter 6 continues with a 24GHz LNA prototype operating from a 1.0V supply which consumes 3mW. It conquers the supply voltage limitation and non-optimal power gain and noise matching among the amplifier stages of a cascode amplifier by biasing the transistors in moderate inversion region and applying transformer feedback in the common-gate gain block, respectively. The single-ended-to-balanced interfacing between the LNA and mixer, and design of the downconversion mixer are also detailed. Design and layout techniques for the circuits considering operation at mm-wave frequencies are immediately followed by simulation and measurement data of a frequency downconverter, which implements the front-end of a 24GHz SRR receiver.

This thesis is concluded in Chapter 7 with a brief summary, a list of research contributions, and suggestions for future work.

#### 1.4 References

- [1.1] O. Bauer. (2005, Jan.). *Christian Hülsmeyer and about the early days of radar inventions: a survey.* Foundation Centre for German Communication and related Technology. Diemen, The Netherlands [Online]. Available: http://www.cdvandt.org/Huelspart1def.pdf

- [1.2] B.A. Austin, "Precursors to radar the Watson-Watt memorandum and the Daventry experiment," *International Journal of Electrical Engineering Education*, vol. 36, no. 4, pp. 365–372, Oct. 1999.

- [1.3] W. Kaiser, "The development of electron tubes and of radar technology: the relationship of science and technology," in *Tracking the history of radar*. New Jersey: IEEE Inc., 1994, pp. 217–236.

- [1.4] L. Brown, "Preliminaries," in *A radar history of World War II: technical and military imperatives*. New York: Taylor & Francis Group, 1999, pp. 1–32.

- [1.5] M.S. Nolan, "Navigation systems," in *Fundamentals of air traffic control*, 5<sup>th</sup> ed. New York: International Code Council, 2011, pp. 44–137.

- [1.6] D. Burch, "Radar piloting," in *Radar for mariners*, revised ed. Blacklick, OH: McGraw-Hill Education, 2013, pp. 58–66.

- [1.7] P. Meischner, "The state of weather radar operations, networks and products," in *Weather radar: principles and advanced applications*. Berlin: Springer, 2004, pp. 1–51.

- [1.8] R.P. Gupta, "SAR interferometry," in *Remote sensing geology*, 2<sup>nd</sup> ed. Berlin: Springer, 2003, pp. 367–392.

- [1.9] J.M.M. Ferreras, J.C. Gallego, and F.P. Martinez, "Monitoring road traffic with a high resolution LFMCW radar," *IEEE Radar Conference*, 2008, pp. 1–5.

- [1.10] M. Camiade, D. Domnesque, Z. Ouarch, and A. Sion, "Fully MMIC-based front end for FMCW automotive radar at 77GHz," *European Microwave Week*, 2000, pp. 280–283.

- [1.11] R. Agethen, M. PourMousavi, H.P. Forstner, M. Wojnowski, K. Pressel, R. Weigel, and D. Kissinger, "60 GHz industrial radar systems in silicon-germanium technology," *IEEE International Microwave Symposium*, 2013, pp. 1–3.

- [1.12] R.J. Evans, P.M. Farrell, G. Felic, H.T. Duong, V.L. Hoang, J. Li, M. Li, W. Moran, M. Morelande, and E. Skafidas, "Consumer radar: Technology and limitations," *International Conference on Radar*, 2013, pp. 21–26.

- [1.13] M. He, R. Winoto, X. Gao, W. Loeb, D. Signoff, W. Lau, Y. Lu, D. Cui, K.S. Lee, S.W. Tam, P. Godoy, Y. Chen, S. Joo, C. Hu, A.A. Paramanandam, X. Wang, C.H. Lin, L. Lin, "A 40nm dual-band 3-stream 802.11a/b/g/n/ac MIMO WLAN SoC with 1.1Gb/s over-the-air throughput," *IEEE International Solid-State Circuits Conference*, 2014, pp. 350–351.

1.4 References

[1.14] N.H.E. Weste and D.M. Harris, "CMOS processing technology," in *CMOS VLSI design: a circuits and systems perspective*, 4<sup>th</sup> ed. Boston: Pearson Education, 2011, pp. 99–140.

- [1.15] J.O. Besenhard, "Practical batteries," in *Handbook of battery materials*. Weinheim: Wiley-VCH, 1999, pp. 19–62.

- [1.16] M.I. Skolnik, "CW and frequency-modulated radar," in *Introduction to radar systems*, International student edition. Tokyo: McGraw-Hill, 1962, pp. 72–112.

- [1.17] G. Staple and K. Werbach, "The end of spectrum scarcity [spectrum allocation and utilization]," *IEEE Spectrum*, vol. 41, no. 3, pp. 48–52, Mar. 2004.

- [1.18] E. Song, Y. Koo, Y.J. Jung, D.H. Lee, S. Chu, and S.I. Chae, "A 0.25-µm CMOS quad-band GSM RF transceiver using an efficient LO frequency plan," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 5, pp. 1094–1106, May 2005.

- [1.19] M.S. Gast, "Introduction to wireless networking," in 802.11 wireless networks: the definitive guide. Sebastopol, CA: O'Reilly Media Inc., 2005, pp. 1–12.

- [1.20] G.R. Aiello, "Challenges for ultra-wideband (UWB) CMOS integration," *IEEE Radio Frequency Integrated Circuits Symposium*, 2003, pp. 497–500.

- [1.21] S. Emami, "UWB preliminaries," in *UWB communication systems: conventional and 60GHz: principles, design and standards*. New York: Springer, 2013, pp. 1–20.

- [1.22] M. Schneider, "Automotive radar status and trends," *German Microwave Conference*, 2005, pp. 144–147.

- [1.23] L. Zhong, J. Qiu, N. Zhang, and X. Xing, "Novel ultrawide-band miniature antennas," *International Conference on Microwave and Millimeter Wave Technology*, 2007, pp. 1–4.

- [1.24] Federal Communications Commission. (2002, Apr.). Revision of part 15 of the commission's rules regarding ultra-wideband transmission systems [Online]. Available: http://transition.fcc.gov/Bureaus/Engineering\_Technology/Orders/2002/fcc02048.pdf

- [1.25] European Telecommunications Standards Institute. (2008, Feb.). ETSI EN 302 288-1 V1.3.1, Electromagnetic compatibility and Radio spectrum Matters (ERM); short range devices; Road Transport and Traffic Telematics (RTTT); short range radar equipment operating in the 24 GHz range; Part 1: technical requirements and methods of measurement [Online]. Available: http://www.etsi.org/deliver/etsi\_en/302200\_302299/30228801/01.03.01\_60/en\_30228801v010301p.pdf

- [1.26] B. Sklar, "Communication link analysis," in *Digital communications, fundamentals and applications*, 2<sup>nd</sup> ed. New Jersey: Prentice-Hall, 2001, pp. 242–303.

- [1.27] L. Bai, B. Wen, J. Yang, and W. Shen, "Design of reconfigurable receiver for HF surface wave radar," *International Conference on Ionospheric Radio Systems and Techniques*, 2006, pp. 226–229.

- [1.28] M.J.M. Pelgrom, "Sampling," in *Analog-to-digital conversion*, 2<sup>nd</sup> ed. New York: Springer, 2013, pp. 163–196.

- [1.29] J.B. Campbell and R.H. Wynne, "History and scope of remote sensing," in *Introduction to remote sensing*, 5<sup>th</sup> ed. New York: The Guilford Press, 2011, pp. 3–30.

- [1.30] F. Ahmad, M.G. Amin, and G. Mandapati, "Autofocusing of through-the-wall radar imagery under unknown wall characteristics," *IEEE Transactions on Image Processing*, vol. 16, no. 7, pp. 1785–1795, Jul. 2007.

- [1.31] J.S. Wilson, "Optical and radiation sensors," in *Sensor Technology hand-book*. Burlington, MA: Elsevier, 2005, pp. 307–320.

- [1.32] D. Ensminger and L.J. Bond, "Ultrasonics: a broad field," in *Ultrasonics, fundamentals, technologies, and applications*, 3<sup>rd</sup> ed. Boca Raton, FL: CRC Press, 2012, pp. 1–26.

- [1.33] X. Liu, H.J. Chen, Y. Alfadhl, X. Chen, C. Parini, and D. Wen, "Conductivity and frequency dependent specific absorption rate," *Journal of Applied Physics*, vol. 113, no. 7, pp. 074902–074902-10, Feb. 2013.

- [1.34] E. Jose and M.D. Adams, "Millimeter wave RADAR spectra simulation and interpretation for outdoor SLAM," *IEEE International Conference on Robotics and Automation*, 2004, pp. 1321–1326.

- [1.35] J.H. Buys and L.H. Janssen, "Comparison of simultaneous atmospheric attenuation measurements at visible light, mid-infra-red (3–5µm) and millimeter waves (94GHz)," *IEE Proceedings Part H: Microwaves, Optics and Antennas*, vol. 128, no. 3, pp. 131–136, Jun. 1981.

- [1.36] Federal Communications Commission. (1997, Jul.). *Millimeter Wave Propagation: Spectrum Management Implications* [Online]. Available: http://transition.fcc.gov/Bureaus/Engineering\_Technology/Documents/bulletins/oet70/oet70a.pdf

- [1.37] R.J. Doviak and D.S. Zrnic, "Principles of radar," in *Doppler radar and weather observations*. Orlando: Academic Press, 1984, pp. 21–46.

- [1.38] I. Gresham, A. Jenkins, R. Egri, C. Eswarappa, N. Kinayman, N. Jain, R. Anderson, F. Kolak, R. Wohlert, S.P. Bawell, J. Bennett, and J.P. Lanteri, "Ultra-wideband radar sensors for short-range vehicular applications," *IEEE Transactions on Microwave Theory and Techniques*, vol. 52, no. 9, pp. 2105–2122, Sep. 2004.

- [1.39] D.V. McGehee, E.N. Mazzae, and G.H.S. Baldwin, "Driver reaction time in crash avoidance research: validation of a driving simulator study on a test track," *Proceedings of the 14th Triennial Congress of the International Ergonomics Association and the 44th Annual Meeting of the Human Factors and Ergonomics Society*, 2000, pp. 320–323.

- [1.40] European Telecommunications Standards Institute. (2002, Jul.). ETSI TR 101 982 V1.2.1, Electromagnetic compatibility and Radio spectrum Matters (ERM); radio equipment to be used in the 24 GHz band; system reference document for automotive collision warning short range radar [Online]. Available:

- http://www.etsi.org/deliver/etsi\_tr/101900\_101999/101982/01.02.01\_60/tr\_101982v010201p.pdf

1.4 References 15

[1.41] N. Kroes, "Commission implementing decision of 29 July 2011 amending Decision 2005/50/EC on the harmonisation of the 24 GHz range radio spectrum band for the time-limited use by automotive short-range radar equipment in the community," *Official Journal of the European Union*, vol. 54, pp. 71–72, Jul. 2011.

- [1.42] Siemens AG. (2012). *Continuous level measurement radar transmitters: SITRANS LR460* [Online]. Available: http://www.automation.siemens.com/mcms/infocenter/dokumentencenter/sc/pi/Documentsu20Catalogs/sitransl lr460 fi01en.pdf

- [1.43] Lesman Instrument Company. (2014). Siemens SITRANS LR460 Radar Level [Online]. Available: http://www.lesman.com/acatalog/Siemens\_SITRANS\_LR460.html

- [1.44] Vtprojects. (2012). LaserDistanceMeter camera distance measure tool [Online]. Available: http://forums.androidcentral.com/android-applications/219319-paid-apppost-developer-laserdistancemeter-camera-distance-measure-tool.html

- [1.45] B. Murmann, "Digitally assisted analog circuits," *IEEE Micro Magazine*, vol. 26, no. 2, pp. 38–47, Mar.–Apr. 2006.

- [1.46] D.C. Daly and A.P Chandrakasan, "A 6-bit, 0.2V to 0.9V highly digital flash ADC with comparator redundancy," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 11, pp. 3030–3038, Nov. 2009.

- [1.47] H.Y. Shih and C.W. Wang, "A highly-integrated 3–8GHz ultra-wideband RF transmitter with digital-assisted carrier leakage calibration and automatic transmit power control," *IEEE Transactions on Very Large Scale Integration Systems*, vol. 20, no. 8, pp. 1357–1367, Aug. 2012.

- [1.48] V. Winkler, "Ramp linearization for FMCW radar using digital down-conversion of a sampled VCO signal," U.S. Patent Application: US20090033538 A1, Publication date Feb. 5, 2009.

- [1.49] H. Xu, Y. Shi, and F.F. Dai, "A 5.2GHz variable gain low noise amplifier RFIC with adaptive biasing for improved linearity," *IEEE Bipolar/BiCMOS Circuits and Technology Meeting*, 2010, pp. 224–227.

- [1.50] A.F. Shalash, "An automatic gain control topology for CMOS digital radio receiver," *IEEE International Symposium on Circuits and Systems*, 2009, pp. 2033–2036.

- [1.51] M. Mailand and R. Richter, "Blind IQ-regeneration for six-port-based direct conversion receiver with low analog complexity," *European Wireless Conference 2005 Next Generation Wireless and Mobile Communications and Services*, 2005, pp. 1–7.

- [1.52] Y. Chiu, C.W. Tsang, B. Nikolic, and P.R. Gray, "Least mean square adaptive digital background calibration of pipelined analog-to-digital converters," *IEEE Transactions on Circuits and Systems I*, vol. 51, no. 1, pp. 38–46, Jan. 2004.

- [1.53] T. Sonderman. (2011). Reaping the benefits of the 450mm transition. Presented at SEMICON West [Online]. Available: http://semiconwest.org/sites/semiconwest.org/files/Thomas%20Sonderman GLOBALFOUNDRIES.pdf

- [1.54] B. Razavi, "Basic concepts in RF design," in *RF microelectronics*. New Jersey: Prentice-Hall, 1998, pp. 11–53.

- [1.55] R.E. Collin, "Passive microwave devices," in *Foundations for microwave engineering*, 2<sup>nd</sup> ed. New Jersey: John Wiley & Sons, 2001, pp. 394–480.

- [1.56] S.F. Paik, "MMIC radar transceivers for industrial sensors," *IEEE International Microwave Symposium*, 1995, pp. 1063–1065.

- [1.57] N.H.E. Weste and D.M. Harris, "Introduction," in *CMOS VLSI design: a circuits and systems perspective*, 4<sup>th</sup> ed. Boston: Addison-Wesley, 2011, pp. 1–60.

- [1.58] Masimo Semiconductor. (2012). Advanced compound semiconductor, epitaxial MOCVD wafers III-V [Online]. Available: http://www.masimosemiconductor.com/masimo-semiconductor/downloadable\_documents/

LAB7287A\_Sales\_Tool\_Masimo\_Semi\_03%20Epitaxial\_MOCVD\_Wafers III-V.pdf

- [1.59] IBM Corp. (2008). CMOS 9SF (CMOS9SF) technology design manual.

- [1.60] N. Tzartzanis and W.W. Walker, "A reversible poly-phase distributed VCO," *IEEE International Solid-State Circuits Conference*, 2006, pp. 2452–2453.

- [1.61] C.R.C. de Ranter and M.S.J. Steyaert, "A 0.25µm CMOS 17GHz VCO," *IEEE International Solid-State Circuits Conference*, 2001, pp. 370–371.

- [1.62] H. Wang, "A 50GHz VCO in 0.25µm CMOS," *IEEE International Solid-State Circuits Conference*, 2001, pp. 372–373.

- [1.63] M. Tiebout, H.D. Wohlmuth, and W. Simbürger, "A 1V 51GHz fully-integrated VCO in 0.12µm CMOS," *IEEE International Solid-State Circuits Conference*, 2002, pp. 300–301.

- [1.64] P.C. Huang, M.D. Tsai, H. Wang, C.H. Chen, C.S. Chang, "A 114GHz VCO in 0.13 µm CMOS technology," *IEEE International Solid-State Circuits Conference*, 2005, pp. 404–405.

- [1.65] B. Jung and R. Harjani, "High frequency LC VCO design using capacitive degeneration," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 12, pp. 2359–2370, Dec. 2004.

- [1.66] H. Li, and H.M. Rein, "Millimeter-wave VCOs with wide tuning range and low phase noise, fully integrated in a SiGe bipolar production technology," *IEEE Journal of Solid-State Circuits*, vol. 38, no. 2, pp. 184–191, Feb. 2003.

- [1.67] N. Fong, J. Kim, J.O. Plouchart, N. Zamdmer, D. Liu, L. Wagner, C. Plett, and G. Tarr, "A low voltage 40-GHz complementary VCO with 15% frequency tuning range in SOI CMOS," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 5, pp. 841–846, May 2004.

- [1.68] F. Ellinger, T. Morf, G. von Büren, C. Kromer, G. Sialm, L. Rodoni, M. Schmatz, and H.Jäckel, "60GHz VCO with wideband tuning range fabricated on VLSI SOI CMOS technology," *IEEE International Microwave Symposium*, 2004, pp. 1329–1332.

1.4 References

[1.69] J. Kim, J.O. Plouchart, N. Zamdmer, R. Trzcinski, K. Wu, B.J. Gross, and M. Kim, "A 44GHz differentially tuned VCO with 4GHz tuning range in 0.12µm SOI CMOS," *IEEE International Solid-State Circuits Conference*, 2005, pp. 416–417.

- [1.70] S. Li, I. Kipnis, and M. Ismail, "A 10-GHz CMOS quadrature LC-VCO for multirate optical applications," *IEEE Journal of Solid-State Circuits*, vol. 38, no. 10, pp. 1626–1634, Oct. 2003.

- [1.71] Z. Safarian and H. Hashemi, "Wideband multi-mode CMOS VCO design using coupled inductors," *IEEE Transactions on Circuits and Systems I*, vol. 56, no. 8, pp. 1830–1843, Aug. 2009.

- [1.72] A.M. Niknejad and R.G. Meyer, "Analysis, design, and optimization of spiral inductors and transformers for Si RF ICs," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 10, pp. 1470–1481, Oct. 1998.

- [1.73] N.H.E. Weste and D.M. Harris, "Interconnect," in *CMOS VLSI design: a circuits and systems perspective*, 4<sup>th</sup> ed. Boston: Addison-Wesley, 2011, pp. 211–240.

- [1.74] R. Singh, D.L. Harame, and M.M. Oprysko, "Technology development," in *Silicon germanium: technology, modeling, and design*. New Jersey: IEEE, 2004, pp. 47–102.

## Chapter 2

# **Background Information**

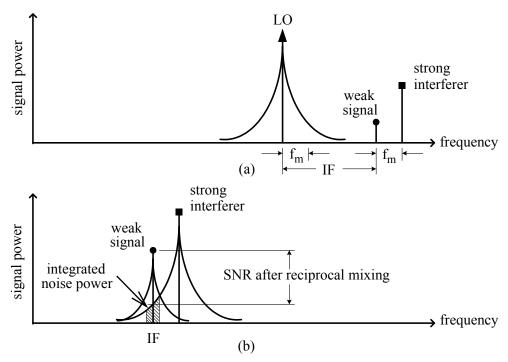

This chapter lays out the theoretical framework for the radar receiver architecture, wide-band VCO and LNA developments in this thesis. Quantitative descriptions of the analog impairments in receiver design by noise and non-linear distortion for a single-stage amplifier are first presented. These are followed by definitions and comparisons of gain parameters, and a review of the design equations for cascaded stages. Finally, the concept of phase noise, and its detrimental effect on the down-converted receive signal quality are examined.

## 2.1 Analog Impairments in a Receiver

Electrical implementation of a practical radar suffers from imperfections which deteriorate the detection accuracy. In this section, the concepts of noise and non-linear distortion, and their implications for the received signal quality are described.

#### **2.1.1** Noise

Noise limits the sensitivity of a radio receiver. The most common form of noise is thermal noise, which is a consequence of the Brownian (random) motion of electrons [2.1]. Conductor metals, resistors, the (inverted) channel and gate contacts to a MOS transistor, and the antenna radiation resistance are all sources of thermal noise. This noise is proportional to absolute temperature and the bandwidth of interested, and has a flat power spectral density (PSD), that is, it is independent of frequency. The power available from the noisy element is

$$P_{\text{available}} = k \cdot T \cdot BW , \qquad (2.1)$$

where k is Boltzmann's constant, T is absolute temperature, and BW is the measured bandwidth.

The second type of noise arises from the random fluctuation of electron flow [2.2]. This includes the shot noise observable in a bipolar transistor when an electron travels through the potential barrier across a PN junction, and flicker noise, where electron flow is disturbed by the trapping and releasing of charge. The MOS transistor is a surface-controlled device where current flows immediately below the gate oxide. Interface states and defects in the oxide introduce plenty of opportunities for charge trapping, and therefore MOS transistors suffer more from flicker noise than bipolars. The PSD of flicker noise is given as [2.3]

$$PSD = \frac{K_f}{Area \times f} , \qquad (2.2)$$

where  $K_f$  is a device-specific flicker noise constant, Area is the surface area covered by the interface states (the channel area for a MOS transistor), and f is the spot frequency of interest. Because the PSD of flicker noise is inversely proportional to frequency, it is also called 1/f noise.

With each circuit element contributing noise to a circuit block, the noise power affecting a radio receiver may be represented by equivalent voltage and current noise sources at its input [2.4]. These equivalent noise sources represent all of the noise generated in the receiver, and the circuit is then considered as noiseless.

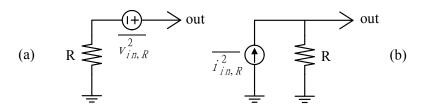

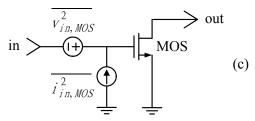

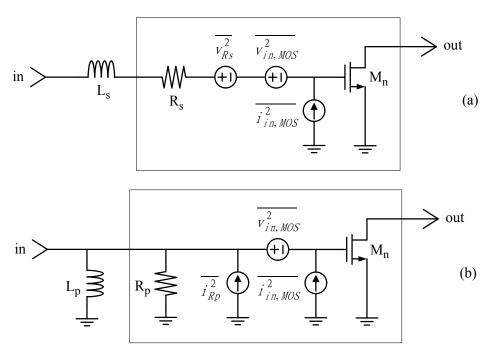

Figure 2.1 illustrates examples of a resistor and a MOS transistor. The resistor noise can be represented as a voltage source in series [see Figure 2.1(a)] or as a current noise source in parallel [see Figure 2.1(b)]. Their mean-square powers are

$$\overline{V_{in,R}^2} = 4kT \cdot R \cdot BW \tag{2.3}$$

and

$$\overline{i_{in,R}^2} = 4kT \cdot \frac{1}{R} \cdot BW , \qquad (2.4)$$

respectively. Eqts. (2.3) and (2.4) are Thévenin and Norton equivalents, respectively, of the thermal noise power.

The equivalent voltage and current noise powers at the input of the common-source NMOS transistor amplifier are given by [2.4]

$$\overline{V_{in,MOS}^2} = \left(4kT \cdot \frac{\gamma}{g_m} + \frac{K_f}{C_{OX}WL \cdot f}\right) \cdot BW$$

(2.5)

and

$$\overline{i_{in,MOS}^2} = \left(\frac{4\pi/3C_{ox}WL \cdot f}{g_m}\right)^2 \left(4kT\gamma \cdot g_m + K_f \frac{I_D^a}{f}\right) \cdot BW , \qquad (2.6)$$

where  $g_m$ ,  $K_f$ ,  $C_{ox}$ , W, L,  $I_D$ ,  $\gamma$ , and a are: transconductance, flicker noise constant,

Figure 2.1 Equivalent input noise sources for a resistor [in (a) and (b)] and MOS transistor (c)

gate oxide capacitance per unit area, gate width, gate length, drain bias current, thermal noise coefficient, and constant 0.5 < a < 2, respectively. The coefficient  $\gamma$  equals 2/3 for long-channel devices, and increases to a value between 2 and 3 for submicron MOS transistors [2.5]. The contribution from the MOS transistor drain current thermal noise  $4kT\gamma \cdot g_m$  appears in both Eqts. (2.5) and (2.6). Therefore, these input-referred noise sources are correlated.

While the input-referred voltage and current sources generate noise power, radio receiver performance is parameterized by ratios such as signal-to-noise ratio (SNR), noise factor (F), and noise figure (NF) [2.6]. The SNR is a ratio of the signal and noise powers taken within the same bandwidth, such as the band-select filter in the front-end module, or the channel-select filter in the IF circuitry.

The received signal being processed by the radio receiver is subsequently demodulated to retrieve the desired information. Processes such as amplification, frequency translation, digitization, or digital signal processing always degrade SNR. Noise factor and noise figure are defined as

$$F = SNR_{in} / SNR_{out}$$

(2.7)

and

$$NF = 10 \cdot \log_{10} F$$

. (2.8)

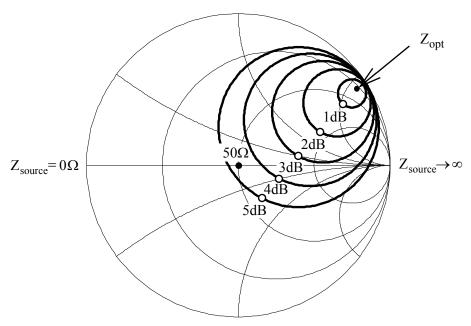

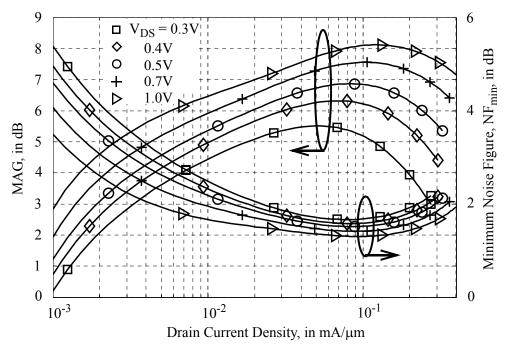

The noise factor is a relative measure because it depends not only on how noisy the circuit element itself is, but also the impedance of the input source. Consider the equivalent input-referred noise model of the common-source MOS amplifier in Figure 2.1(c), with the input port connected to a source impedance ( $Z_{source}$ ). If  $Z_{source}$  is zero, the noise current source at the input makes no contribution to the total output noise power. A similar observation can be made for  $Z_{source}$  approaching infinity and the input noise voltage source. An optimum source impedance ( $Z_{opt}$ ) which lies between these two extremes (i.e.  $0 \le Z_{opt} < \infty$ ) exists where the noise factor is minimized (i.e.,  $F_{min}$ ) [2.2].

Effects of the input-referred noise sources and source impedance on the noise factor of a two-port amplifier was analyzed in [2.7]. The noise factor is

$$F = F_{min} + \frac{4r_n |\Gamma_{source} - \Gamma_{opt}|^2}{(1 - |\Gamma_{source}|^2) \cdot |1 + \Gamma_{opt}|^2},$$

(2.9)

where  $r_n$  is the normalized equivalent resistance of the input-referred voltage noise source, and  $\Gamma_i$  is the reflection coefficient of impedance  $Z_i$ .  $F_{min}$  and  $\Gamma_{opt}$  are functions of the input-referred voltage and current noises, and their correlation. On the complex plane of  $\Gamma_{\text{source}}$ , contours of different constant noise factor values are visualized as a family of circles. This is known as the noise circles of the amplifier.

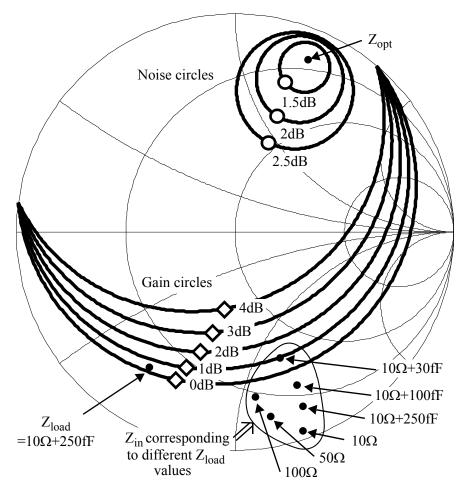

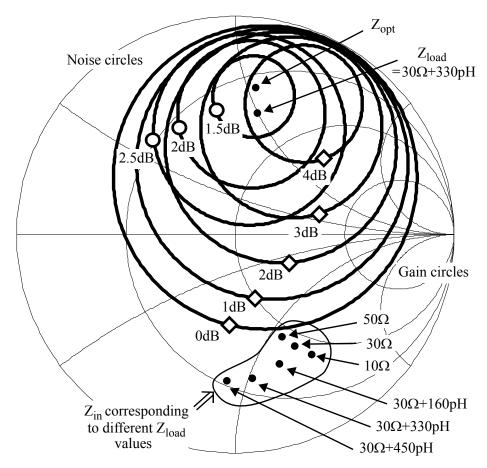

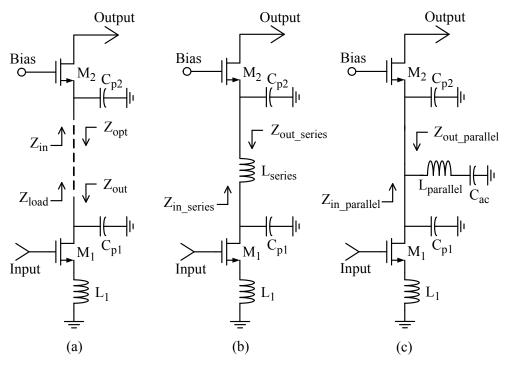

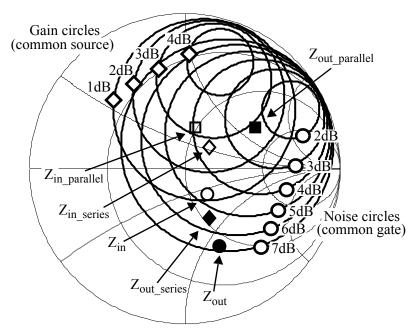

The simulated noise circles of a  $40 \times 1 \mu m/90 nm$  NMOS common-source amplifier is illustrated in Figure 2.2. The transistor is biased at a current density of 25  $\mu$ A per micron of gate width by a constant drain-source voltage of 0.6V. At

Figure 2.2 Noise figure circles plotted in the  $\Gamma_{source}$  plane for a  $40\times1\mu m/90nm$  NMOS common-source amplifier at 24GHz

24 GHz, the optimum source impedance  $Z_{opt}$  is  $25.5 + j170 \Omega$ , and the minimum noise figure is 0.612 dB. On the other hand, the simulated noise figure for a  $50 \Omega$  source impedance is 4.67 dB, which can be observed from the origin of the  $\Gamma_{source}$  plane in Figure 2.2 being bounded by the 4dB and 5dB noise figure circles.

Transformation of the actual source impedance to  $Z_{opt}$  minimizes the amplifier noise figure for a given power dissipation. However, the gain, bandwidth, and input return loss of the amplifier are not optimized simultaneously, in general. The degradation of noise figure by any change in the source impedance selection is visualized easily from the Smith chart. This simplifies the process of making design trade-offs involved in the optimization of a multi-stage, power-constrained LNA.

#### 2.1.2 Non-Linear Distortion

Design of linear amplifiers using active devices is based on the assumption of a small-signal model [2.8]. For example, a MOS transistor is biased at a certain quiescent value and linear model is derived. Practical active devices have non-linear transfers, and therefore this assumption of linearity for the transistor is invalid when the input signal grows too large or is accompanied by strong interference. For example, assume that the transfer characteristic of a system can be approximated by

$$y(t) = a_1 x(t) + a_2 x^2(t) + a_3 x^3(t),$$

(2.10)

where y(t) is the output and x(t) is the input signal.

With a single sinusoid  $x(t) = A_0 \cos \omega t$  applied to the input, the output is

$$y(t) = \left(a_1 A_0 + \frac{3 a_3 A_0^3}{4}\right) \cos \omega t + \frac{a_2 A_0^2}{2} \cos 2\omega t + \frac{a_3 A_0^3}{4} \cos 3\omega t + \dots , \quad (2.11)$$

which reveals that second, third, and higher harmonics of the input frequency are generated at the outputs. These tones are harmonic distortion generated by the transistor. Amplification of the input signal is characterized by the fundamental term

$a_1A_0 + 3a_3A_0^3/4$  in Eqt. (2.11). The input –1dB compression point is defined as the input signal magnitude at which the output power drops by 1dB from the ideal linear transfer value (i.e., compression). It is given by [2.9]

$$A_{0,-1\,dB} = \sqrt{0.145 \cdot |a_1/a_3|} \ . \tag{2.12}$$

A weak desired signal along with a large interferer lowers the gain available from the radio receiver by driving it into gain compression. The reduction in the output signal magnitude is significant compared to the drop of the total output noise level, and the system SNR is degraded.

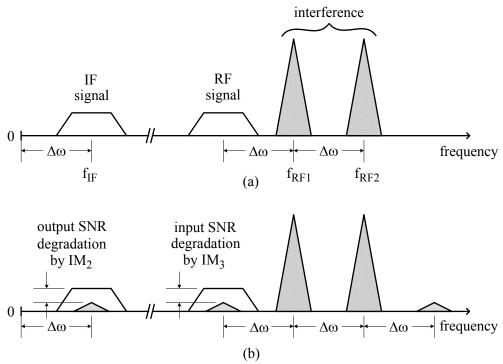

With two sinusoidal interference tones  $x(t) = A_0 \cos \omega_1 t + A_0 \cos \omega_2 t$  injected into the input, the non-linear distortion components at the system output relevant to RF receiver design are dominated by the quadratic and cubic terms specified in Eqt. (2.11). They are

$$y(t) = (3/4) \cdot a_3 A_0^3 \cdot [\cos(2\omega_1 - \omega_2) t + \cos(2\omega_2 - \omega_1) t]$$

$$+ a_2 A_0^2 \cos(\omega_1 - \omega_2) t + \dots$$

(2.13)

The first two components in Eqt. (2.13) appear in the vicinity of interferer frequencies at  $\omega_1$  and  $\omega_2$ . They are proportional to the third-order non-linearity (a<sub>3</sub>) and are commonly known as third-order intermodulation (IM<sub>3</sub>) distortion. The input third-order intercept point is an extrapolation of the input signal level to the point where the output IM<sub>3</sub> equals the linear gain component at the fundamental frequency. It is given by [2.9]

$$A_{0, IP3} = \sqrt{(4/3) \cdot |a_1/a_3|}$$

(2.14)

The last term in Eqt. (2.13) is a low-frequency beat signal at the difference between the two interferer frequencies. It is the second-order intermodulation (IM<sub>2</sub>) distortion since it is originated from the second-order non-linearity (a<sub>2</sub>) component. The input signal level at which the output signal levels at  $\omega_1$  (or  $\omega_2$ ) and  $\omega_1-\omega_2$  equal each other (from an extrapolation) is defined as the input second-order intercept point. It is given by [2.9]

$$A_{0, IP2} = \sqrt{|a_1/a_2|} . {(2.15)}$$

The implications of IM<sub>2</sub> and IM<sub>3</sub> in a receiver system are illustrated in Figure 2.3. Two interferers with the frequency difference  $\Delta \omega = \omega_1 - \omega_2$  are separated

Figure 2.3 Receiver frequency diagram with two-tone interference, showing signal-to-noise ratio deterioration due to second and third-order intermodulations