# On the Effective Parallel Programming of Multi-core Processors

PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op dinsdag 7 december 2010 om 10.00 uur

$\operatorname{door}$

Ana Lucia VÂRBĂNESCU

Master of Science in Architecturi Avansate de Calcul, Universitatea POLITEHNICA București, România geboren te Boekarest, Roemenië. Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. ir. H.J. Sips

Samenstelling promotiecommissie:

**Rector Magnificus** Prof.dr.ir. H.J. Sips Prof.dr.ir. A.J.C. van Gemund Prof.dr.ir. H.E. Bal Prof.dr.ir. P.H.J. Kelly Prof.dr.ing. N. Ţãpuş Dr. R.M. Badia Dr. M. Perrone Prof.dr. K.G. Langendoen

voorzitter Technische Universiteit Delft, promotor Technische Universiteit Delft Vrije Universiteit Amsterdam, The Netherlands Imperial College of London, United Kingdom Universitatea Politehnicã București, Romania Barcelona Supercomputing Center, Spain IBM TJ Watson Research Center, USA Technische Universiteit Delft, reservelid

ASCI dissertation series number 223.

The work in this dissertation was performed in the context of the Scalp project, funded by STW-PROGRESS.

This work was carried out in the ASCI graduate school.

Parts of this work have been done in collaboration and with the material support of the IBM T.J. Watson Research Center, USA.

Part of this work has been done in collaboration with the Barcelona Supercomputing Center, and supported by a HPC Europa mobility grant.

Copyright © 2010 by Ana Lucia Varbanescu. All rights reserved.

No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without the prior permission from the author. The author can be contacted at analucia@gmail.com.

ISBN/EAN: 978-90-8570-708-0

Printed in the Netherlands by Wöhrmann Print Service (www.wps.nl).

# Acknowledgments

There have been many moments in which my PhD felt a lonely fight against the world. But now, when writing the very last pages of my thesis - the acknowledgements - I realize I've been lucky to have a lot of people by my side, all the way. I try to thank all of them here - in a vague chronological order. As the list can only be limited and therefore prone to omissions - I will probably fail. For those of you that I might have omitted: please accept my apologies, my thanks, and a glass of wine from me, to wash away the sorrow.

I want to thank Prof. Nicolae Tapus, for his guidance during my academic years in Romania, and for accepting to be part of my committee. I am grateful to late Prof. Irina Athanasiu, for her continuous encouragement, and for her role in my first collaboration with TUDelft. And I want to thank Prof. Sorin Cotofana, for making my first encounters with TUDelft, The Netherlands, and the Dutch interesting and comfortable.

Special thanks go to Prof. Henk Sips, my supervisor, for his help and support, for putting up with all my last minute ideas and panic moments (starting from that CPC'06 paper). I owe him thanks for his patience in waiting for my thesis, who was "almost ready" for many months, but also for our enlighting discussions about non-scientific topics such as sailing, traveling, wine, or earrings.

I'd like to thank Prof. Arjan van Gemund for his help on PAM-SoC and the SCALP project, and for the valuable insight in performance analysis, modeling, and prediction. Further thanks go to the other SCALP members: Dr. Maik Nijhuis, Dr. Herbert Bos, and Prof. Henri Bal (from Vrije Universiteit Amsterdam) - for our collaboration in building SP@CE. One extra "thank you" to Prof. Henri Bal for his useful comments on the draft of my thesis. Thanks to Paul Stravers and Jos van Eindhoven (currently at VectorFabrics) for their help with the SpaceCAKE architecture itself, and for the valuable insights in the pragmatic thinking of "the industry".

I would like to thank Dr. Michael Perrone, my two-time manager at IBM TJ Watson Research Center - his enthusiasm for the Cell/B.E., and his ability to quickly detect good solutions from bad ones and extract the essence from any (vague) idea played an important role in my work so far. Thank you, Michael, for your help and support, for the subtle ways you found to motivate me, and for the continuous interest you showed in my career. Last, but not least, thank you for the suggestions made for improving this thesis. Additional thanks go to the other members of the Cell Solutions team with whom I worked at TJ Watson - Gordon Braudaway, Daniele Scarpazza, Fabrizio Petrini, and Virat Agarwal - for sharing with me some of the secrets of Cell/B.E. programming.

I owe thanks to Rosa Badia and Xavier Martorell, with whom I worked for six weeks at the Barcelona Supercomputing Center (and continued to collaborate afterwards). Our work on classifying, comparing, and evaluating a large variety of programming models, has helped me understand more of the subtle effects that programmability and productivity have on platform adoption and performance.

Thanks to Ian Buck and Stephen Jones for my nice summer internship in the CUDA team from NVIDIA, where I had to opportunity to see how difficult it is to build the right software tools and models in a hardware-dominated environment.

I'd like to thank Prof. Paul Kelly for accepting to be part of my committee, for his comments on the draft of my thesis, as well as for our occassional, yet very interesting discussions on parallelism and performance. And thank you, Prof. Joerg Keller, for our fruitful collaboration, which I hope to maintain and improve.

I would like to end my "professional" acknowledgements by thanking two of my most stable scientific partners, and friends: Dr. Rob van Nieuwpoort and Alexander van Amesfoort. Thanks, guys, for the smooth collaboration in our various projects together, and for our entertaining discussions. I surely hope we will keep working together for a while longer.

I am grateful for all the help and support I got from my friends and my family. Thanks, Monel and Mihaitza for always finding the energy to spend some time with me. Thanks, Robert, for keeping me up to date with the pubs in Bucharest. Thanks Nicoleta, Ervin and Anca Vitos, and Michou for your good thoughts from far away. Thank you, Ana Maria O. and Corina for the fun in Amsterdam, and for geek girls nights out. Thank you, Karan, for being so close to me from the other side of the world. Thank you, Ivo, for the wine and cheese evenings, and for being such a great officemate - no wonder I never wanted to work from home! Thanks, Otto, for your help with the Dutch in all its/their forms, and for your visits on the dark side of the corridor. Thanks, Pawel and Alex F., for making weekends at the TUDelft bearable.

These years, basketball has been an important part of my life. I am grateful to my teammates, trainers, and coaches from Punch, for the many fun memories on and off court. Special thanks to Tessa, Marije, Marta, Charlotte, Siri, Bridgit, and Jill for their kind friendship outside the club. Thanks to "my" Heren3 team, for accepting such a shouting coach, and for teaching me the inner beauty of pink. Thank you, Remus, Coco, Patricia, and Rita for the many crazy tournaments we have played together - I enjoyed them a lot. And thank you very much, Maider, for extending our friendship so far beyond basketball.

I would not remember my time in the US with that much pleasure if it wouldn't have been for the friends I made there. Thank you, Janet, for your kindness and your care during the months I spent in your house. Thank you, Nicolas, for the biking trips and for your restless efforts to make me understand the beauty of american football (sorry, I still don't get it). Thank you, Marcio, for the afternoon coffees. Thank you, Virat and Leo, for the tennis matches and the movie evenings in the conference rooms. Thank you, Mesut, for the wine and cheese parties at Janet's. Thank you, Vlad, for showing me some of the beautiful places of California.

Finally, there are four more special people in my life, to whom I am most grateful - without them, all these years would have been a lot tougher. Thank you, Ancutza, for being my best friend all these years, for being there in the cloudiest of days (and those are plenty in The Netherlands!), for listening and for talking, for always being honest, direct, and fair. Thank you, Alexandru, for your love, for putting up with my mood swings and pre-deadline panic, for standing by my side when I needed it, for believing in me and for encouraging me; thank you for your patience and your calm support. And thank you, Mom and Dad, for teaching me to work hard and to never give up, and for inspiring me to be the best in what I do. Thank you for being so proud of me. Thank you, Mom, for teaching me the magic powers of good food. Thank you, Dad, for these last 25 years of basketball and computing machineries. Thank you for everything. I love you very very much.

Ana Lucia.

# Contents

| 1        | Intr                 | roduction                                                                 | 1  |  |  |  |  |

|----------|----------------------|---------------------------------------------------------------------------|----|--|--|--|--|

|          | 1.1                  | 1 The Hardware Push                                                       |    |  |  |  |  |

|          | 1.2                  | The Programmability Gap                                                   | 4  |  |  |  |  |

|          | 1.3                  | Problem Statement                                                         | 6  |  |  |  |  |

|          |                      | 1.3.1 Approach                                                            | 6  |  |  |  |  |

|          | 1.4                  | Thesis Main Contributions and Outline                                     | 6  |  |  |  |  |

|          |                      | 1.4.1 Thesis Outline                                                      | 7  |  |  |  |  |

| <b>2</b> | Mu                   | lti-Core Architectures                                                    | 9  |  |  |  |  |

|          | 2.1                  | Wasabi/SpaceCAKE: An Embedded Multi-core Processor                        | 10 |  |  |  |  |

|          | 2.2                  | General-purpose multi-core processors                                     | 11 |  |  |  |  |

|          |                      | 2.2.1 Intel Nehalem                                                       | 11 |  |  |  |  |

|          |                      | 2.2.2 AMD Barcelona, Istanbul, and Magny-Cours: N-Core Opteron Processors | 12 |  |  |  |  |

|          |                      | 2.2.3 Sun UltraSPARC T2 and T2+                                           | 14 |  |  |  |  |

|          |                      | 2.2.4 A Summary of GPMCs                                                  | 15 |  |  |  |  |

|          | 2.3                  | General Processing on GPUs (GPGPU) Computing                              | 16 |  |  |  |  |

|          |                      | 2.3.1 NVIDIA G80/GT200                                                    | 16 |  |  |  |  |

|          |                      | 2.3.2 Intel's Larrabee                                                    | 20 |  |  |  |  |

|          | 2.4                  |                                                                           |    |  |  |  |  |

|          |                      | 2.4.1 The Cell/B.E                                                        | 22 |  |  |  |  |

|          |                      | 2.4.2 Intel's Single-Chip Cloud Computer (SCC)                            | 24 |  |  |  |  |

|          | 2.5                  | Comparing Multi-Core Processors                                           | 26 |  |  |  |  |

|          |                      | 2.5.1 Architectural characteristics                                       | 26 |  |  |  |  |

|          |                      | 2.5.2 A quantitative comparison                                           | 27 |  |  |  |  |

|          |                      | 2.5.3 Compatibility                                                       | 30 |  |  |  |  |

|          | 2.6                  | Summary                                                                   | 32 |  |  |  |  |

|          |                      | 2.6.1 Future Trends for Multi-core Architectures                          | 33 |  |  |  |  |

| 3        | $\operatorname{Cas}$ | e-Study 1: A Traditional Scientific Application                           | 35 |  |  |  |  |

|          | 3.1                  | Application Analysis                                                      | 36 |  |  |  |  |

### vi CONTENTS

|          | 3.2                        | Parallelization Strategies                                            | 8 |  |  |  |

|----------|----------------------------|-----------------------------------------------------------------------|---|--|--|--|

|          | 3.3                        | Experiments and Results                                               | 1 |  |  |  |

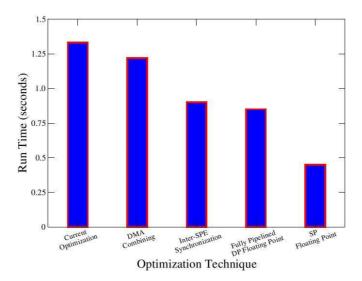

|          |                            | 3.3.1 SPE Optimizations                                               | 1 |  |  |  |

|          |                            | 3.3.2 Loop Vectorization                                              | 2 |  |  |  |

|          |                            | 3.3.3 Peak and Actual Floating Point Performance                      | 3 |  |  |  |

|          |                            | 3.3.4 Scalability                                                     | 3 |  |  |  |

|          |                            | 3.3.5 Performance Comparison and Future Optimizations                 | 5 |  |  |  |

|          | 3.4                        | Lessons Learned and Guidelines                                        | 6 |  |  |  |

|          | 3.5                        | Related Work                                                          | 7 |  |  |  |

|          | 3.6                        | Summary and Discussion                                                | 8 |  |  |  |

| 4        | Cas                        | e-Study 2: A Multi-Kernel Application 5                               | 1 |  |  |  |

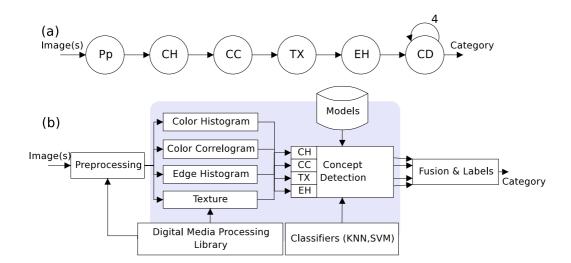

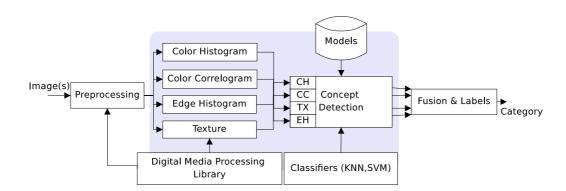

|          | 4.1                        | Application Analysis                                                  | 2 |  |  |  |

|          |                            | 4.1.1 From MARVEL to MarCell                                          | 3 |  |  |  |

|          |                            | 4.1.2 MarCell: First Performance Measurements                         | 6 |  |  |  |

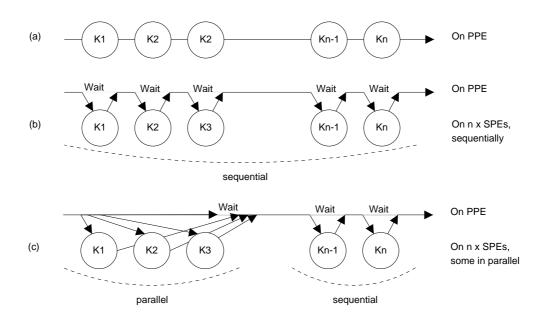

|          | 4.2                        | Task parallelism                                                      | 8 |  |  |  |

|          | 4.3                        | Data parallelism                                                      | 0 |  |  |  |

|          | 4.4                        | Combining data and task parallelism                                   | 2 |  |  |  |

|          | 4.5                        | Lessons Learned and Guidelines                                        |   |  |  |  |

|          | 1.0                        | 4.5.1 MarCell Relevance                                               |   |  |  |  |

|          |                            | 4.5.2 Cell/B.E. Relevance                                             |   |  |  |  |

|          |                            | 4.5.3 Cell/B.E. Parallelization Guidelines                            |   |  |  |  |

|          | 4.6                        | Related Work                                                          | 5 |  |  |  |

|          | 4.7                        | Summary and Discussion                                                | 6 |  |  |  |

| <b>5</b> | Cas                        | e-Study 3: A Data-intensive Application 69                            | 9 |  |  |  |

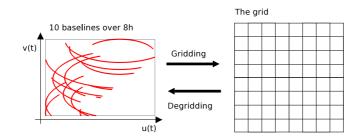

|          | 5.1 Radioastronomy Imaging |                                                                       |   |  |  |  |

|          | 0.1                        | Radioastronomy Imaging    70      5.1.1    Radio Interferometry    70 |   |  |  |  |

|          |                            | 5.1.2 Building the Images                                             |   |  |  |  |

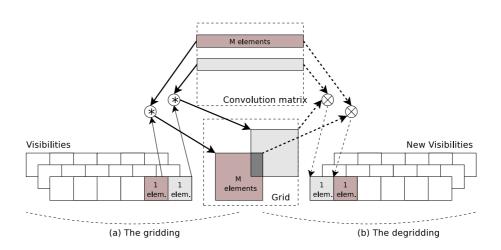

|          | 5.2                        | Gridding and Degridding                                               |   |  |  |  |

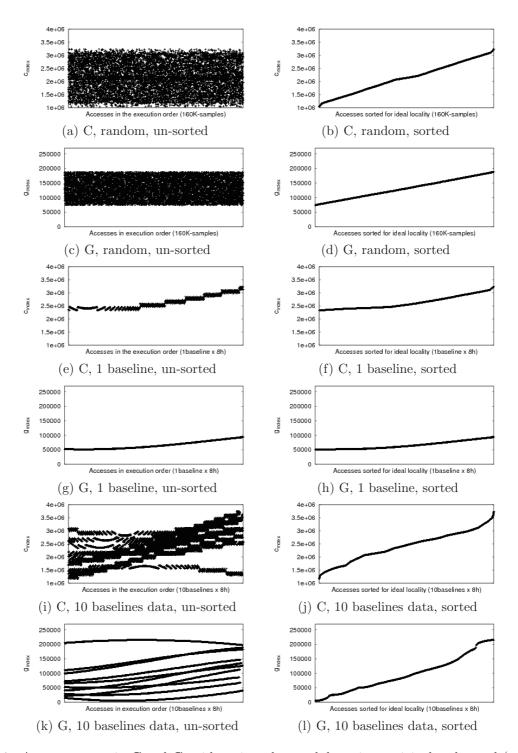

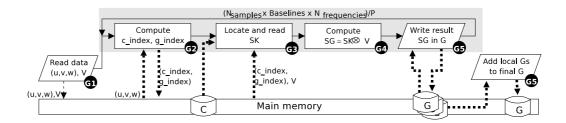

|          | 0.2                        | 5.2.1 Application Analysis                                            |   |  |  |  |

|          |                            | 5.2.2 Application Modeling                                            |   |  |  |  |

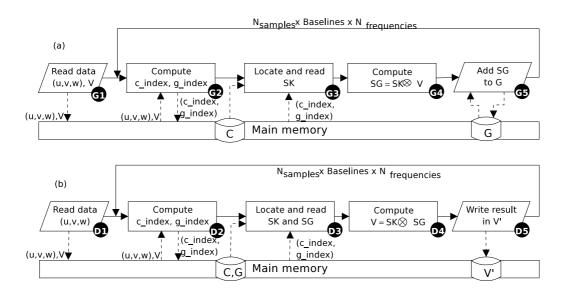

|          | 5.3                        | Parallelization on the Cell/B.E.                                      |   |  |  |  |

|          | 0.0                        | 5.3.1 A Model-driven Application Parallelization                      |   |  |  |  |

|          |                            | 5.3.2 Mapping on the Cell/B.E.                                        |   |  |  |  |

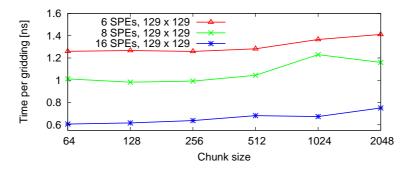

|          |                            | 5.3.3 Application Specific Optimizations                              |   |  |  |  |

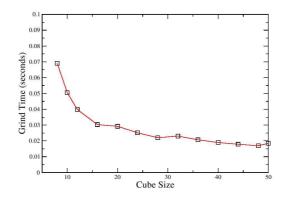

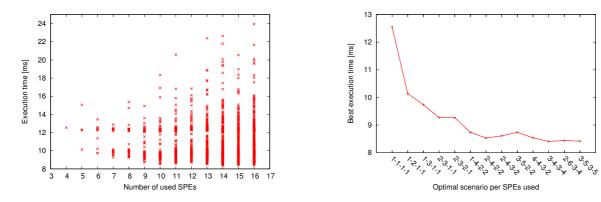

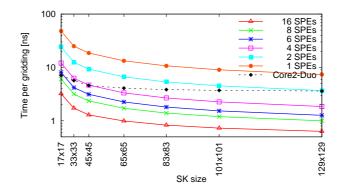

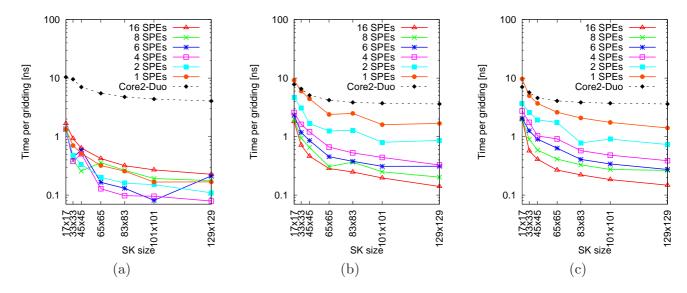

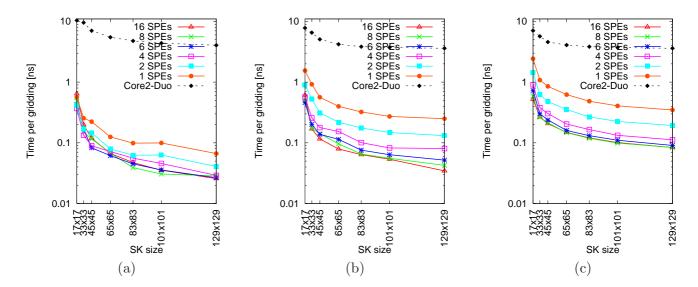

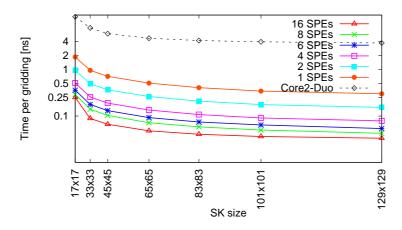

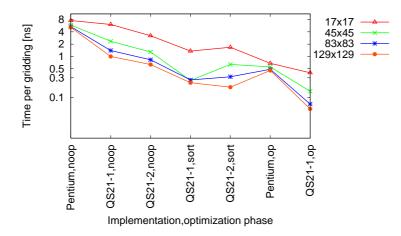

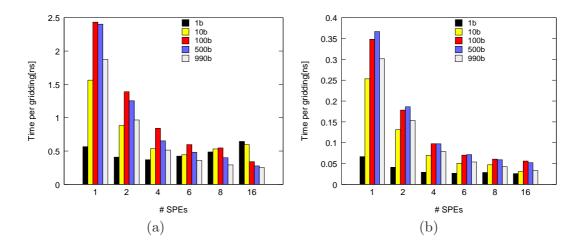

|          | 5.4                        | Experiments and Results on the Cell/B.E.                              |   |  |  |  |

|          | 0.1                        | 5.4.1 The Experimental Set-up                                         |   |  |  |  |

|          |                            | 5.4.2 A First Cell/B.E. Implementation                                |   |  |  |  |

|          |                            | 5.4.3 Improving the Data Locality                                     |   |  |  |  |

|          |                            | 5.4.4 PPE Multithreading                                              |   |  |  |  |

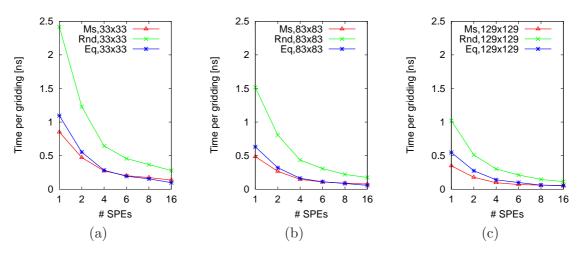

|          |                            | 5.4.5 Data-dependent Optimizations                                    |   |  |  |  |

|          |                            | 5.4.6 Summary                                                         |   |  |  |  |

|          | 5.5                        | Lessons Learned and Guidelines                                        |   |  |  |  |

|          |                            |                                                                       | 1 |  |  |  |

|   | 5.6                                            | Related Work                                                                                                                                                   |  |  |  |  |  |

|---|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|   | 5.7                                            | Summary                                                                                                                                                        |  |  |  |  |  |

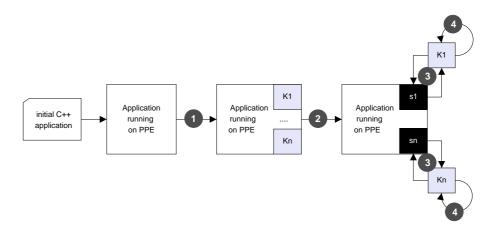

| 6 | Porting C++ Applications onto the Cell/B.E. 97 |                                                                                                                                                                |  |  |  |  |  |

|   | 6.1                                            | The Porting Strategy                                                                                                                                           |  |  |  |  |  |

|   |                                                | 6.1.1 The PPE Version                                                                                                                                          |  |  |  |  |  |

|   |                                                | 6.1.2 Kernels Identification                                                                                                                                   |  |  |  |  |  |

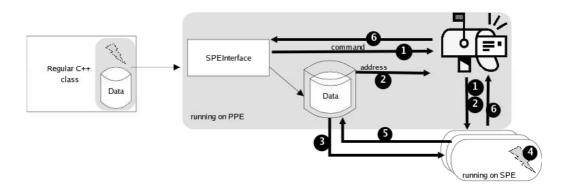

|   |                                                | 6.1.3 The SPEInterface stub                                                                                                                                    |  |  |  |  |  |

|   |                                                | 6.1.4 Kernel migration                                                                                                                                         |  |  |  |  |  |

|   |                                                | 6.1.5 The PPE-SPE Communication                                                                                                                                |  |  |  |  |  |

|   | 6.2                                            | The Code Templates                                                                                                                                             |  |  |  |  |  |

|   |                                                | 6.2.1 The SPE Controller                                                                                                                                       |  |  |  |  |  |

|   |                                                | 6.2.2 The SPEInterface class 103                                                                                                                               |  |  |  |  |  |

|   |                                                | 6.2.3 The PPE-SPE communication                                                                                                                                |  |  |  |  |  |

|   |                                                | 6.2.4 Changes in the main application                                                                                                                          |  |  |  |  |  |

|   | 6.3                                            | Overall Application Performance                                                                                                                                |  |  |  |  |  |

|   | 0.0                                            | 6.3.1 The Kernel Optimizations                                                                                                                                 |  |  |  |  |  |

|   |                                                | 6.3.2 Evaluate application performance                                                                                                                         |  |  |  |  |  |

|   | 6.4                                            | MarCell: A Case-Study                                                                                                                                          |  |  |  |  |  |

|   | 0.1                                            | 6.4.1 Porting MARVEL on Cell                                                                                                                                   |  |  |  |  |  |

|   |                                                | 6.4.2 Building MarCell                                                                                                                                         |  |  |  |  |  |

|   |                                                | 6.4.3 Experiments and results                                                                                                                                  |  |  |  |  |  |

|   | 65                                             | Related Work                                                                                                                                                   |  |  |  |  |  |

|   | 6.5                                            |                                                                                                                                                                |  |  |  |  |  |

|   | 6.6                                            | Summary and Discussion                                                                                                                                         |  |  |  |  |  |

| 7 | $\mathbf{M}\mathbf{u}$                         | lti-core Applications Analysis and Design 115                                                                                                                  |  |  |  |  |  |

|   | 7.1                                            | Generic Findings and Empirical Guidelines 118                                                                                                                  |  |  |  |  |  |

|   |                                                | 7.1.1 Case Studies Overview                                                                                                                                    |  |  |  |  |  |

|   |                                                | 7.1.2 Problems and empirical solutions                                                                                                                         |  |  |  |  |  |

|   | 7.2                                            | The Programmability Gap                                                                                                                                        |  |  |  |  |  |

|   |                                                | 7.2.1 Platform Programmability                                                                                                                                 |  |  |  |  |  |

|   |                                                | 7.2.2 Performance, productivity, and portability                                                                                                               |  |  |  |  |  |

|   |                                                | 7.2.3 Required features $\ldots \ldots \ldots$ |  |  |  |  |  |

|   | 7.3                                            | Are we there yet? A Survey of Programming Tools                                                                                                                |  |  |  |  |  |

|   |                                                | 7.3.1 Cell/B.E. Programming Models                                                                                                                             |  |  |  |  |  |

|   |                                                | 7.3.2 GPMC Programming Models                                                                                                                                  |  |  |  |  |  |

|   |                                                | 7.3.3 GPU Programming Models                                                                                                                                   |  |  |  |  |  |

|   |                                                | 7.3.4 Generic Programming Models                                                                                                                               |  |  |  |  |  |

|   |                                                | 7.3.5 A Comparison of Multi-Core Programming Models                                                                                                            |  |  |  |  |  |

|   | 7.4                                            | Summary and discussion                                                                                                                                         |  |  |  |  |  |

|   |                                                |                                                                                                                                                                |  |  |  |  |  |

| 8 | AG                                             | Generic Framework for Multi-Core Applications 141                                                                                                              |  |  |  |  |  |

| 8 |                                                | * *                                                                                                                                                            |  |  |  |  |  |

| 8 | <b>A</b> G<br>8.1                              | A Strategy for Multi-core Application Development       141         8.1.1       An application-centric approach       141                                      |  |  |  |  |  |

|   | 8.2  | MAP: A Framework for Platform-Centric Application development | 145 |

|---|------|---------------------------------------------------------------|-----|

|   |      | 8.2.1 User input                                              | 145 |

|   |      | 8.2.2 Analysis                                                | 147 |

|   |      | 8.2.3 Design                                                  | 147 |

|   |      | 8.2.4 Prototype                                               | 148 |

|   |      | 8.2.5 Implementation                                          | 149 |

|   |      | 8.2.6 Tuning                                                  | 150 |

|   | 8.3  | A MAP Example: MARVEL                                         | 151 |

|   |      | 8.3.1 User input and the analysis stage                       | 151 |

|   |      | 8.3.2 The Design Stage                                        | 152 |

|   |      | 8.3.3 The Prototype Stage                                     | 155 |

|   |      | 8.3.4 The Roll-back                                           | 159 |

|   | 8.4  | Current status                                                | 160 |

|   | 8.5  | Summary and discussion                                        | 161 |

| 9 | Com  | clusions and Future Work                                      | 169 |

| 9 |      |                                                               | 163 |

|   | 9.1  | Conclusions                                                   | 163 |

|   | 9.2  | Future Work Directions                                        | 165 |

| A | Dat  | a-Intensive Kernels on Multi-Core Architectures               | 167 |

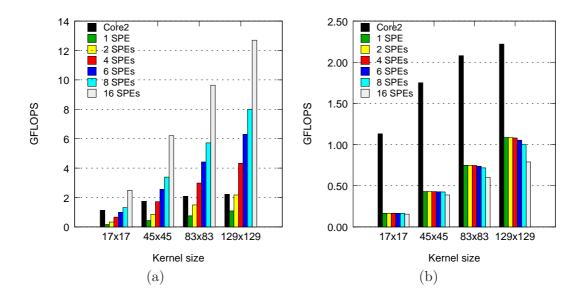

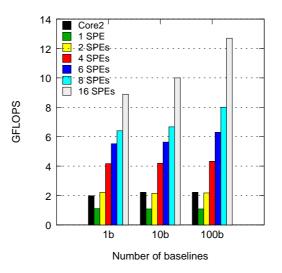

|   | A.1  | General-purpose multi-cores (GPMCs)                           | 167 |

|   |      | A.1.1 Gridding on the GPMCs                                   | 167 |

|   | A.2  | Graphical Processing Units (GPUs)                             | 168 |

|   |      | A.2.1 Gridding on GPUs                                        | 168 |

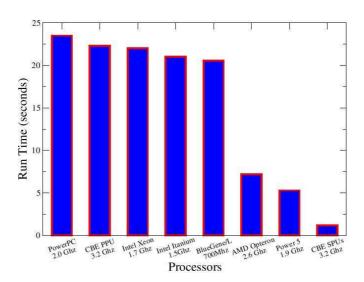

|   |      | A.2.2 Platform comparison                                     | 169 |

|   | A.3  | Experiments and Results on multiple platforms                 | 170 |

|   | 11.0 | A.3.1 Experimental Set-up                                     | 170 |

|   |      | A.3.2 Experiments with the GPMCs                              | 170 |

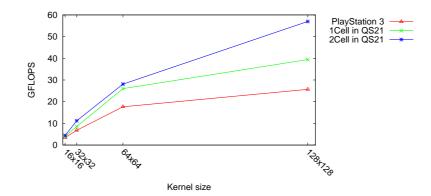

|   |      | A.3.3 Experiments with the Cell/B.E.                          | 171 |

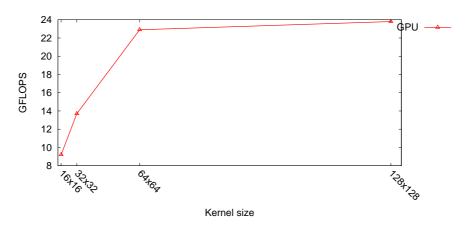

|   |      | A.3.4 Experiments with the GPU                                | 172 |

|   |      | A.3.5 A Brief Comparison                                      | 173 |

|   | A.4  | Discussion                                                    | 173 |

|   | A.5  | Related Work                                                  | 175 |

|   |      | Summary                                                       | 176 |

|   |      |                                                               | 110 |

| Β | PAI  |                                                               | 177 |

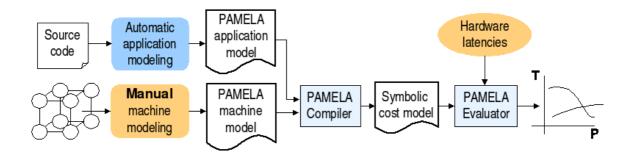

|   | B.1  | The PAMELA Methodology                                        | 177 |

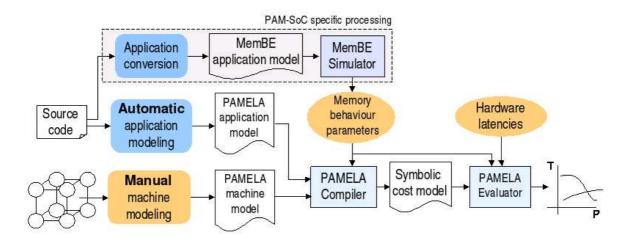

|   | B.2  | PAM-SoC: Pamela for MPSoCs                                    | 179 |

|   |      | B.2.1 MPSoC Machine Modeling                                  | 179 |

|   |      | B.2.2 Application modeling                                    | 181 |

|   |      | B.2.3 The memory statistics                                   | 181 |

|   |      | B.2.4 Validation experiments                                  | 181 |

|   |      | B.2.5 Design space exploration                                | 183 |

|   | B.3  | PAMELA for Multi-Cores                                        | 185 |

### CONTENTS ix

|         |        | Examples of Multi-Core Machine Models |            |

|---------|--------|---------------------------------------|------------|

| B.4     | Summ   | nary                                  | . 189      |

| List of | Acron  | nyms                                  | 191        |

| Bibliog | raphy  |                                       | 195        |

| Summa   | ary    |                                       | 207        |

| About   | the Au | uthor                                 | <b>215</b> |

#### l Chapter

# Introduction

The pace of the entire (computational) world is increasing. We all push the limits of (conventional) processors when we require more accurate, more detailed, and quicker results from the multitude of devices we use every day. In fact, we all demand *better performance* from these devices.

Over the last 40 years, the responsibility for increasing application performance (or the blame for the lack there of) has oscillated between hardware and software. Originally, processors had very limited resources (e.g., a few hundreds of kilobytes of main memory, one simple arithmetic-logical unit, and one slow floating point processing unit), so programmers had to invent ingenious solutions to efficiently use them. That was the time when major optimization techniques, in both compilers and programming models, have emerged.

As technology advanced, larger and faster memories, combined with faster and more complex processing units, have significantly increased the hardware performance. When the hardware constraints reduced, application development became easier, with many designers/developers paying less attention to detailed optimizations in favor of shorter time-to-delivery. This trend has generated a very large collection of algorithms and implementations in a multitude of computational fields. For these applications, speed-up came almost for free, as every new processor generation increased clock frequency, allowing for more operations to be solved per time unit. Although parallelism and concurrency were already recognized as potential performance boosters, they remained the "fancy" tool of High Performance Computing (HPC), despite impressive performance gains for compute-intensive scientific applications running on large-scale parallel machines.

In the early 2000s, the frequency increasing trend slowed down, mainly due to power consumption and overheating concerns. Even more, it became obvious that this technique can no longer sustain, by itself, significant performance improvements. Multi-core processors have emerged as an alternative approach: instead of a single, large, very complex, power hungry core per processor, multiple "simplified" cores are tightly coupled in a single chip and, by running concurrently, they yield better overall performance than the equivalent single-cores<sup>1</sup>.

In terms of applications, this shift from single-core processors to multi-cores made parallelism ubiquitous. Quite suddenly, most existing applications, as well as applications emerging from new computational fields, have to be parallelized, optimized, tuned, and deployed on multi-core processors. This process is non-trivial: finding the right architecture for a given application, choosing the right parallelization and data distribution strategies, and tuning the code for the specifics of the chosen architecture are all difficult tasks. Also, the variety of available architectures decreases portability, leading to significant differences in algorithm design. The increased number of parallelism layers and the finer granularity imposed by the tightly-coupled cores make "inherited" parallelization techniques (i.e., solutions available for large-scale parallel machines) hard to (re)use. Finally, performance analysis methodologies and prediction tools are practically nonexistent.

<sup>&</sup>lt;sup>1</sup>It is worth mentioning that, before becoming **the** viable alternative to traditional processors, multi-cores have had other names, such as *multi-processor system-on-chips* (MPSoCs), or *chip multi-processors* (CMPs)

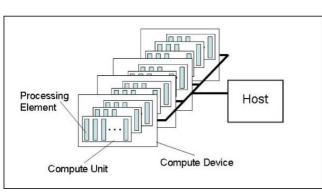

# 1.1 The Hardware Push

Multi-cores are now designed and developed by all the important players on the processors market. In only five years, this inherent competition has generated a broad range of multi-core architectures. Major differences include the types and numbers of cores, the memory hierarchy, the communication infrastructure, and the parallelism models. For example, a Cell Broadband Engine (Cell/B.E.) offers eight dedicated RISC accelerator cores managed by a ninth light PowerPC core, in a Direct Memory Access (DMA)-controlled distributed memory model. The latest Intel© Core i7 has eight x86 cores, all hypethreaded [Int09]. A typical NVIDIA Graphical Processing Unit (GPU) has 16 to 30 processing units, each comprising of 16 or 32 "individual" computing units; various shared and distributed memory modules are "scattered" in the chip.

However, the history of parallel computers has already seen so many architectures that it is hard not to wonder what is new with multi-cores. The differences are both fundamental and subtle, and they refer to three main issues: (1) fine granularity, (2) multiple parallelism layers, and (3) very complex memory infrastructure. In the following paragraphs we discuss these key differences in more detail, proving that the complexity level of multi-cores is significantly higher than that of traditional parallel architectures.

#### Parallelism Layers

Multi-core processors offer multiple layers of parallelism: Core-Level Parallelism (CLP), multithreading, Single Instruction Multiple Data (SIMD), Instruction Level Parallelism (ILP), and communicationcomputation overlapping.

Core-Level Parallelism (equivalent to Multiple Instruction Multiple Data (MIMD)) is present in processors where cores can run (pseudo-)independent tasks. It is typical for General Purpose Processor (GPP) multi-cores and for heterogeneous platforms. Further, cores may offer multithreading, a technique that allows multiple (hardware) threads to run in parallel. SIMD is a technique that allows multiple threads to run the same operations on different data elements; note that for different architectures, SIMD can be exploited at different levels (core level, thread level, or instruction level). Below multithreading and SIMD, cores use Instruction Level Parallelism to overlap instruction execution. Finally, several architectures can overlap off-chip communication and computation (using techniques similar to prefetching or context switch in case of memory stalls), resulting in parallelism between some memory and compute instructions.

Of course, multiple parallelism layers can also be found in larger scale parallel architectures, like clusters or Massively Parallel Processors (MPPs). However, the impact of successive layers on the overall performance is usually orders of magnitude apart, and quite independent. In the case of multicores, each of these layers is critical to overall performance. Note that the theoretical performance of a multi-core is quoted with full parallelism, i.e., benchmarked with a set of applications that fully exploit each of these layers. Unfortunately, as experience shows, very few real-life applications can be "divided" to expose enough parallelism to fill the entire stack. Further, because the layers are not independent and the relative impact on performance is comparable, the performance effects when choosing one layer over another are hard to predict.

#### Large Scale, Fine Granularity

We define the (computational) granularity of a parallel architecture as the largest "computational unit" that should run sequentially on a node. Note that granularity is directly connected with the parallelism

layers of a platform: a platform that offers low-level parallelism will implicitly have fine granularity. Additionally, the coarser the platform granularity is, the least intrusive application parallelization will be: fine granularity requires more synchronization points and complex data distribution.

Finally, the simplest accepted paradigm for programming parallel machines is for the programmer to define application computational units and their communication patterns, and let the system-level tools deal with concurrent execution (via mapping) and lower-level parallelization (via compiler and hardware optimizations).

When comparing multi-core with conventional parallel machines, the difference in granularity is significant. For most traditional parallel machines, the granularity is logically uniform, and the computational units are, in both the SPMD and MPMD models, fairly coarse. In the case of multi-core processors, one should investigate multiple granularity levels, starting from tasks, but also investigating at thread-level and loop-level parallelism, in search for appropriately sized computational units (i.e., a unit that fits the resources of a node and allows for concurrent execution with other units). Thus, we typically deal with non-uniform, nested granularity layers.

The lower granularity of multi-cores has clear implications for (1) performance, (2) mapping/scheduling, and (3) low-level parallelization tools. A poor choice of the parallelization granularity decreases platform utilization and limits the achievable performance to only a fraction of the theoretical peak. As the computational units become smaller, we deal with a large-scale mapping and scheduling problem. Finally, low-level parallelization tools have to act as very fine tuners/optimizers, a cumbersome task as the number of techniques with performance gain potential is unpredictable (i.e., it depends on the application, on the platform, and most of the time also on the mapping/scheduling decisions).

#### Memory and Data Locality

For multi-core based systems, we consider a typical memory hierarchy to include both on-chip and off-chip memories, and the I/O subsystem. As expected, on-chip memories are small (and offer low-latency), while off-chip memories typically large (but they also exhibit high-latency). Most architectures opt for a layered on-chip memory hierarchy, with per-core ("local") memories and shared memories per groups of cores. Some architectures, like Intel's Core i7 or the newest NVIDIA GPUs use some of the local memories as caches, while others, such as the Cell/B.E., give the programmer full control over the transfers.

Most on-chip memories have strict restrictions on access alignments, patterns, and sizes in order to minimize the latency and fully utilize the memory bandwidth. Low-latency is essential for decreasing communication overheads (especially for fine-grain parallelism), while increased bandwidth allows the hardware to overlap memory accesses and computation efficiently.

Data locality plays an essential role in the performance of multi-cores, similar to traditional parallel machines: fetching data from a close-by memory is always faster than fetching data from remote memories. Consequently, the communication cost of an application is increased by the number and the latencies of the memory layers, as well as by the frequency of memory operations. A compact memory hierarchy, typical for traditional parallel machines, allows for larger memories per layer, and minimizes the need for inter-layer memory traffic. A "taller" memory hierarchy, typical for multi-cores, has less memory per layer, increasing memory traffic between layers; ultimately, this translates into severe performance penalties for poor data locality.

These considerations can be easily extended to the I/O subsystems, i.e., the connection of the processor with "the outside world". Multi-core systems have two types of I/O traffic: to/from the off-chip memory and to/from the on-chip memory. The bandwidth of both these connections is a

crucial factor in the overall performance of the system. In fact, in many cases, the first estimate of a maximum achievable performance of an application is not given by the platform's computational throughput, but rather by the platform's I/O bandwidth.

# 1.2 The Programmability Gap

Once multi-core processors have become state-of-the-art in computing systems, applications have to use parallelism and/or concurrency to achieve the performance these chips can offer. The failure to do so will make multi-cores highly inefficient and, ultimately, application performance will stall or even decrease.

Despite the very large collection of (traditional) parallel programming models, languages, compilers, the software community is still lagging behind: the applications, the operating systems, and the programming tools/environments are not yet coping with the parallelism requirements posed by this new generation of hardware. With new platforms being advertised every month, the widening "multi-core programmability gap" has become a major concern shared by both communities.

Attempts to bridge the programmability gap have been quite abundant in the last few years. Application case studies, dedicated programming models, and a few compilers and code generators have enabled, to some extent, a systematic approach to multi-core programming. But most of these initiatives lack generality, infer performance penalties, and/or pose severe usability limitations.

In reality, multi-core programmers still base their application design and implementation on previous experience, hacking, patching, and improvisation. Furthermore, when considering the entire pile of applications that have to be implemented for multi-cores, these solutions can be generically called "needle-in-the-haystack methods".

Nevertheless, even when these methods eventually succeed, they raise three fundamental issues: (1) there is no measure of success (except the functional correctness), (2) productivity and efficiency are unpredictable, and (3) the path to the found solution is in most cases non-reconstructible and non-repeatable for new problems (even for slight variation of the originally solved problem). Any approach towards systematic parallel programming has to tackle the three key issues that are ignored by the needle-in-the-haystack methods: (1) performance, (2) productivity, and (3) portability.

#### Performance

The ultimate goal of using new hardware platforms is the search for increased *performance*. However, performance in itself is a complex function of multiple parameters: the application, the chosen algorithm and its implementation, the input data set, and the hardware platform. When compared with single-core applications, multi-core processors increase the complexity of this performance function to a new level, both in terms of numbers of parameters and in terms of their interdependence.

Also note that performance metrics are different for various computing fields. For example, HPC applications aim to minimize execution time. In turn, typical embedded systems applications focus on real-time constraints. Streaming applications (think of on-line multimedia streaming, for example) focus on data throughput. Mobile applications target low power consumption.

Not all these performance metrics are easy to measure. Furthermore, their way to relate to hardware complexity and/or application modules/phases is non-trivial. Therefore, performance analysis becomes complicated, while traditional performance estimation loses accuracy.

Nevertheless, application development must be performance-driven. Remember that the increased complexity of multi-core processors effectively means that the number of ways to solve a problem (i.e., the variations of algorithms, implementations, and optimizations) increases significantly. Consequently, the choices programmers are facing increase and testing all solutions becomes unfeasible. In many cases, implementation and optimization decisions are taken either based on programmer experience or even arbitrarily. We strongly believe that including simple performance estimation (for the application-specific metrics) early in the development process leads to a bounded solution search space and its systematic exploration.

### Productivity

Currently, the hardware players lead the effort, releasing new processors with increased theoretical performance every few months. Still, this trend will end very soon, as the critical mass of applications unable to get a decent fraction of the theoretical peak performance is reached. We argue that only productivity and efficiency can significantly alleviate this problem, by enabling a shorter and more effective application development process.

For multi-core application, we loosely define productivity as the achieved performance per time unit spent on programming. One can see this as an efficiency metric, i.e., a ratio between the achieved performance and the invested effort. Either way, to increase productivity, one has to balance the application performance with the time spent in the development process.

Speeding up the development process is only possible by using high-level programming models and performance analyzers, as they offer an increased level of standardized programming, decreasing development time and, more importantly, decreasing maintenance and update costs. Further, we acknowledge that programmers fiddling around with applications might get (slightly) better performance, but this is usually a result of using platform-specific optimizations and tricks, hard to reproduce and estimate for a general system. Therefore, we belive that hand-tuning and platform-specific optimizations should come only as the final parts of the development process.

### Portability

The increased variety of multi-core processors brings along a new question: given a company that has to improve the performance of a large application, what platform should be used for achieving best results?

The answer is non-trivial. First, these "best results" have to be qualified and quantified, by defining the metrics and their acceptable values. Next, application and data set characteristics have to be taken into account for establishing the platform components and scale.

When the options for platform components (i.e., one or more types of multi-cores, in our case) are very different, the choice is made by some sort of estimation, be it driven by experimental or analytical evidence, or by programmer expertise. However, once this choice is made, the result is a platformspecific implementation. And if the original platform choice does not meet the set performance goals, the development process is restarted.

In a context where most platforms are not compatible, this is yet another reason for low productivity/efficiency. Therefore, portability must be achieved by the software layers. Of course, such a model is unable to deliver stable good performance for entirely different platforms. However, a high-level programming model that enables portability among various hardware platforms is much more likely to be adopted than a platform-specific one. Such a model can also become an incentive for eliminating "hardware glitches" (i.e., features that are cluttering the hardware while only delivering very little performance) because a (semi-)universal software model will force hardware designers to think if the model can express and use the novel features they plan to include, thus being forced to evaluate the impact these changes have on software.

### **1.3** Problem Statement

Both the lack of structure in the field of multi-core programming, as well as the low effectiveness of available parallel programming tools are direct consequences of the high complexity and fine granularity that multi-core architectures exhibit. The multiple parallelism layers, the complicated memory hierarchies, and the delicate performance balance between arithmetic, memory, and I/O operations generate a large variety of solutions to a single problem. Searching for the right solution, especially when using a non-systematic approach, makes multi-core programming difficult, as it usually comes down to an iterative process with an unclear stop-condition.

We believe that the current state-of-the-art in programming multi-cores is no more than a "needle-in-the-haystack" search, being driven by programmer experience and ad-hoc empirical choices. This approach hinders performance, productivity, and portability. In this thesis, we investigate whether a structured approach to parallel programming for multi-cores is possible and useful, as well as what conditions, actions, and tools are necessary to transform this approach into a complete framework that can improve the design and development of parallel applications for multi-core processors.

#### 1.3.1 Approach

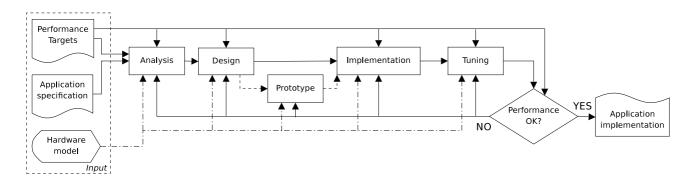

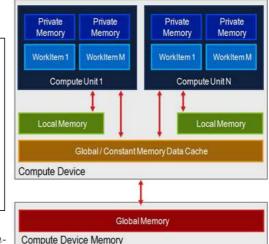

To structure multi-core application development, we propose  $MAP^2$ , a complete framework that guides the user through the phases of application development, from analysis to implementation and optimizations. Essentially, the framework, sketched in Figure 1.1, takes as input an *application specification* and a *set of performance targets*, and allows the programmer to use a step-by-step approach to analyze, design, prototype, implement, and optimize a multi-core application. Furthermore, the framework enables hybrid design, allowing a switch from application-driven to hardware-driven development in any stage, by taking platform specific decisions, at the expense of portability (i.e., the sooner this decision is taken, the lower the application portability will be). Finally, the framework also includes a performance feedback loop, which enables an essential roll-back mechanism, based on performance checkpoints, which allows the user to come back at previous design stages and take a different path without sacrificing the entire design flow.

By the end of this thesis, we show an application development strategy for multi-core applications, we discuss the MAP framework prototype, and we investigate the tools to support our framework.

# 1.4 Thesis Main Contributions and Outline

The main goal of this thesis is to propose a framework for efficient programming of parallel applications on multi-core processors. To build this framework, we first investigate the state-of-the-art multi-cores and predict a future trend in their development (Chapter 2). Further, we analyze three case-studies (Chapters 3, 4, 5), aiming to determine the major challenges that arise in application development, from design to implementation and optimization. We also give an example of the practical challenges

$<sup>^{2}</sup>$ MAP stands for "Multi-cores Application Performance", the three major elements of our framework

**Figure 1.1:** The MAP framework. Application specification and performance targets are user-specified inputs. Platform and application modeling, as well prototyping and programming tools are parts of the framework tool-chain.

of porting legacy code on multi-cores (Chapter 6). We summarize these challenges and we verify if any of the modern programming tools, mostly designed to support multi-cores, offer the right mix of features to support the user in the whole development process (Chapter 7). We find that the programming models are separated into two disjoint classes: application-centric and hardware-centric. This split mimics, and unfortunately widens, the programmability gap. To bridge this gap, we devise a complete analysis-to-implementation strategy to deal with multi-core applications. Next, we design the framework prototype (Chapter 8) to enable this strategy, and we investigate the availability/effort of building a potential tool-chain. We conclude that despite the elegance and completeness of the solution, the state-of-the-art tool support is by no means sufficient. Among other interesting future research directions (Chapter 9), we recommend more effort to be invested in developing these support tools (eventually at the expense of hardware-centric programming models).

#### 1.4.1 Thesis Outline

Chapter 2 presents the state-of-the-art in multi-core architectures, including the Cell/B.E., graphical processing units, and homogeneous multi-cores (for desktops, servers, and HPC clusters). We summarize by discussing architectural trends and their impact on the application world.

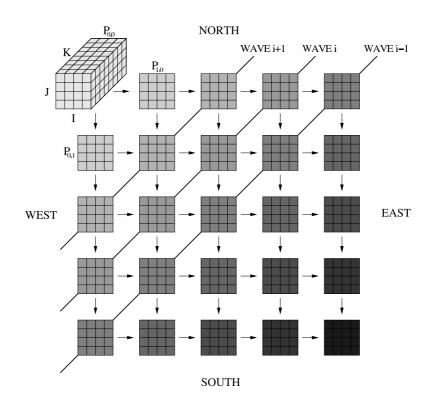

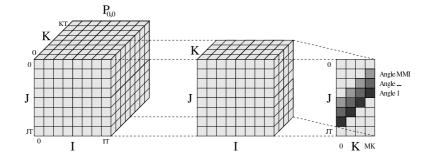

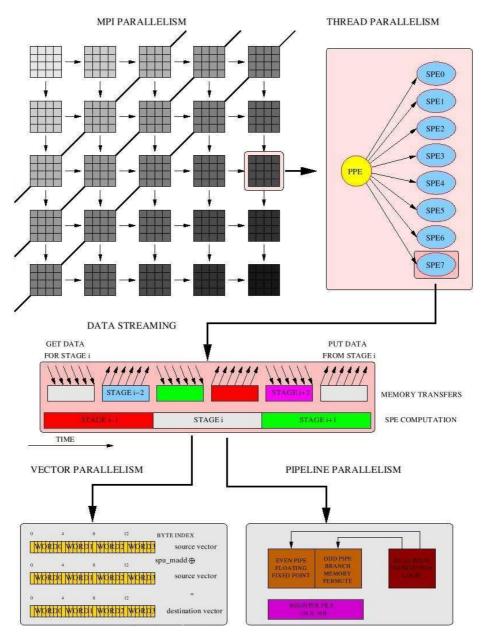

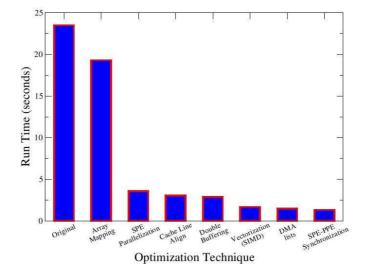

Chapter 3 describes a multi-core specific implementation of a traditional HPC application, and the lessons to be learned from this exercise. This implementation focuses on the compute-intensive kernel, and investigates Cell-specific low-level optimizations that enable the overall execution time to drop more than a factor of 20. This chapter is based on joint work with IBM Research, previously published in IPDPS'07 ([Pet07]).

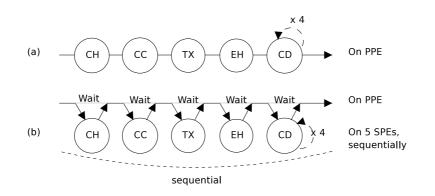

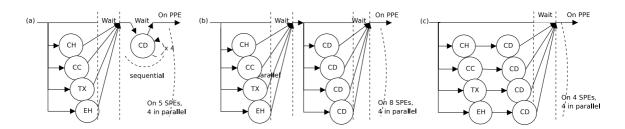

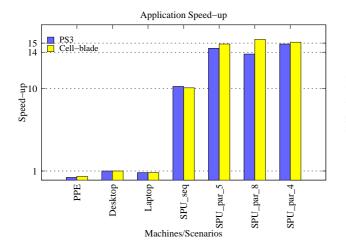

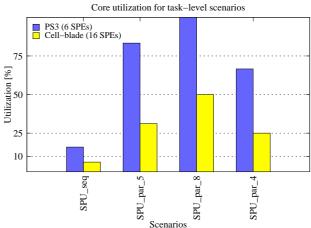

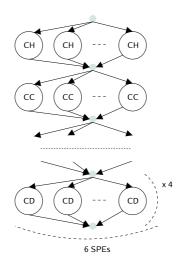

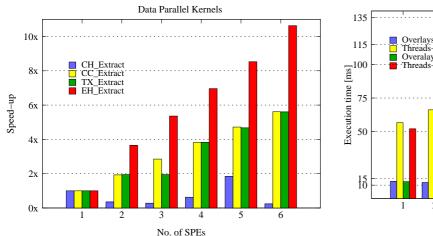

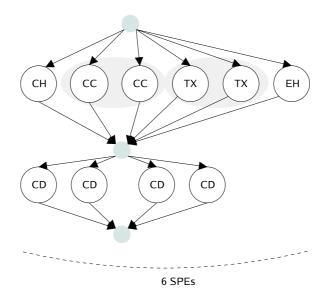

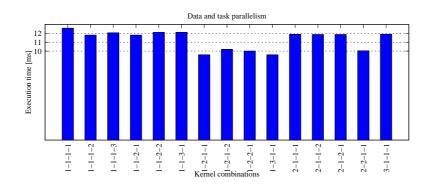

Chapter 4 describes a multi-core specific implementation of a large, multi-kernel image contentanalysis application. Specifically, we investigate both low-level optimizations and the influence of high-level mapping and scheduling of kernels on a heterogeneous multi-core. Finally, we compare the application behavior for task, data, and hybrid parallelization, and we show unintuitive performance results. This chapter is based on joint work with IBM Research, previously published in ICME'07 ([Liu07]) and Concurrency and Computation: Practice and Experience 21(1) ( [Var09b]).

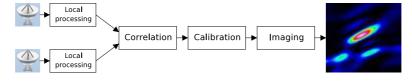

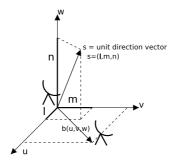

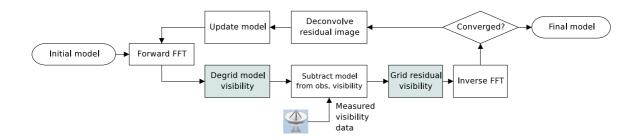

Chapter 5 focuses on the implementation of a data-intensive application. The application is part of a radio-astronomy imaging chain, and requires very large, unordered collections of data to be processed. We investigate the challenges it poses for a multi-core processor - data intensive behavior,

#### 8 INTRODUCTION

random memory access patterns, very large data structures - and we propose potential solutions to address them. This chapter is based on work previously published in Euro-Par 2008 ([Var08b]) and in Scientific Programming 17(1-2), 2009 ([Var09a]).

Chapter 6 presents some of the challenges that one can encounter when porting legacy, objectoriented applications on multi-core processors. Specifically, we discuss a generic, template-based strategy for porting large C++ applications on an accelerator-based multi-core processor. We validate the strategy by showing how MarCell [Liu07] was ported onto the Cell/B.E.. Although not fully aligned with the thesis story-line, our reasons to include this chapter are twofold: we give one more example of the difficulties of multi-core programming, and we provide more technical details for the discussion in Chapter 4.

Chapter 7 summarizes the lessons we have learned from all these case studies. We extract two sets of best-practice guidelines: a platform-agnostic set, mainly addressing parallel application design for multi-core processors, and a platform-specific set, combining guidelines for all three multi-core processor families used for HPC applications. Finally, based on these best practices, we investigate the available multi-core programming models for a best match. The work in this chapter is partially based on work presented at CPC'09 ([A.L09]).

Chapter 8 presents a strategy for systematic multi-core application development. We propose the MAP framework as the right way to support this strategy, and we show how a MAP prototype should look like. We further investigate the available tool support for all its components. Finally, we also include an example to show how the framework works for designing, implementing, and optimizing a real application.

Chapter 9 concludes the thesis and discusses future work directions.

Appendix A presents additional work and results on the data intensive case-study presented in Chapter 5. Specifically, we discuss the design and implementation of the same application on two more hardware platforms, comparing all these with the original Cell/B.E. implementation. We compare the three platforms in terms of performance and programmability, and we recommend a few empirical guidelines for choosing the right platform for a data-intensive application.

Appendix B is a brief discussion on performance prediction for multi-cores. We briefly present the PAMELA methodology [van93], which uses application and machine models to "reason" about the potential performance of parallel applications. Further, we present PAM-SoC, a PAMELA-based tool for Multi-processor System-on-Chip (MPSoC) application performance prediction, focused on predicting application behavior *before* the application and/or the architecture are (fully) available. Finally, we discuss why such a tool is difficult enough to implement for multi-core processors that its feasibility is questionable.

# **Multi-Core Architectures**

This chapter presents an overview of the available multi-core processors, focusing on their architectural features.

Multi-core processors come in various shapes and sizes. As they are difficult to compare, there is little consensus on a potential best architecture. Rather, a few types of architectures tend to polarize the applications in just a few hot-spots. General purpose multi-cores cover the consumer market - for both workstations and servers. Typically, these processors have few identical powerful cores, shared memory, and a hierarchy of caches. They mainly focus on increasing the performance of workloads composed of multiple generic consumer applications.

Instead, embedded systems multi-processors (we include here network processors, digital signal processors, and other similar, application-specific processors) have a few different cores (typically, only some of them are programmable), little memory (either shared or distributed), and small caches. They focus on specific application fields (by design), and they are usually unsuitable for large, generic workloads.

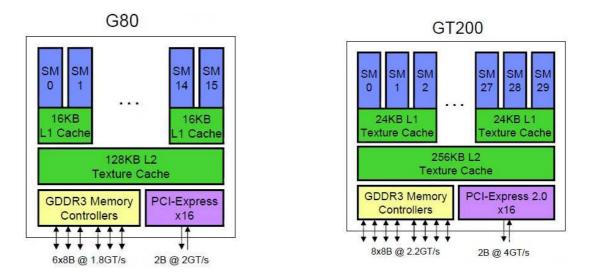

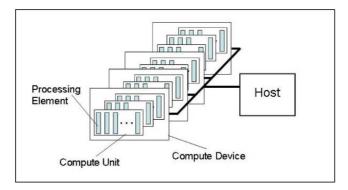

With the development of General Processing on GPUs (GPGPU), GPUs claim a category for themselves. With special, massively parallel architectures (i.e., collections of hundreds of simple cores), state-of-the-art GPUs have passed the TFLOP barrier - for the applications that are able to use it.

High-performance computing (HPC) processors are platforms that offer hundreds to thousands of GFLOPS, and are used primarily for number crunching. Traditionally, experimental platforms that use non-traditional architectures to obtain high computational peaks become experimental HPC processors. Therefore, we hardly see any common architectural trends for HPC multi-cores - except for the continuous search for the highest absolute peak performance (counted in GFLOPS).

However, the borders between these categories are quite blurred: architectures like the STI Cell/B.E. [Kah05], NVIDIA's Fermi [NVI10], or IBM's POWER7 [IBM09] are hard to place in a single bin. However, as there is no clear, universally accepted taxonomy of multi-cores (nor a clear terminology, either), our classification is sufficient to structure our processor survey.

To provide a broad overview of the multi-core platforms, we discuss several examples of *representative* multi-core processors from each of these four categories. Our presentation targets mostly the architectures of these platforms, discussing similarities and differences as seen by both the hardware and the software designers. Hence our emphasis on the specific hardware characteristics, the performance potential, and the programming approach for each of these processors. For simplicity, we present the platforms in the chronological order of their appearance, and we only discuss platforms introduced after the year 2000.

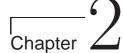

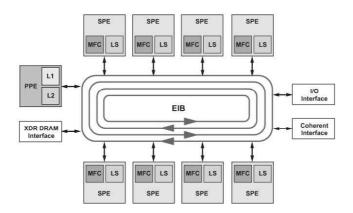

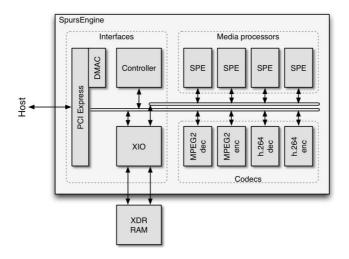

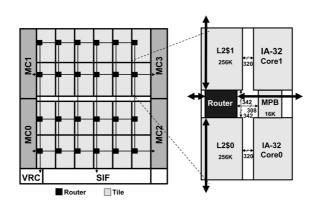

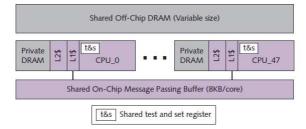

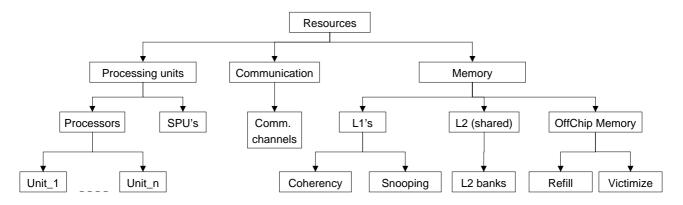

Figure 2.1: The Wasabi architecture - one tile of the SpaceCAKE architecture.

# 2.1 Wasabi/SpaceCAKE: An Embedded Multi-core Processor

Embedded systems have featured multiple cores per chip since microcontrollers have emerged, but those cores were hardly programmable, very rudimentary, and geared towards accelerating very simple operations directly in hardware. As the complexity of embedded-systems increased, the performance requirements for application-specific processors has also increased, and *multi-processor system-on-chips* (MPSoCs) or *chip multi-processors* (CMPs) have emerged as programmable multi-cores for embedded systems. Today, most embedded systems use such processors for a wide range of embedded applications (e.g., automotive systems, multimedia and digital signal processing, and medical devices).

Typical MPSoCs are heterogeneous platforms with multiple types of cores: one master core able to execute an operating system and I/O operations, a set of programmable cores dedicated to generic computations, and a set of non-programmable specialized functional units. In most cases, they are shared-memory machines, with simple memory hierarchies, used as stand-alone processors.

An example is the Wasabi/SpaceCAKE architecture, a tile-based embedded processor [Str01] designed in 2001 by Philips for its high-end multimedia systems. SpaceCAKE is a collection of homogeneous tiles, communicating via a high-speed interconnect. A SpaceCAKE tile, presented in Figure 2.1, is a typical MPSoC: it has one main core (an ARM or a MIPS), eight programmable multimedia processors (Philips Trimedia) [Bor05; Phi04], and several special functional units (non-programmable hardware accelerators). The memory hierarchy has three levels: (1) private L1's for each processor, (2) one shared on-chip L2 cache, available to all processors, and (3) one off-chip memory module. Hardware cache consistency between all L1's and L2 is enforced.

#### Wasabi/SpaceCAKE Programming<sup>1</sup>

For software support, Wasabi runs eCos [eCo], a modular open-source Real-Time Operating System (RTOS), which has embedded support for multithreading. Programming is done in C/C++, using eCos synchronization system calls and the eCos thread scheduler.

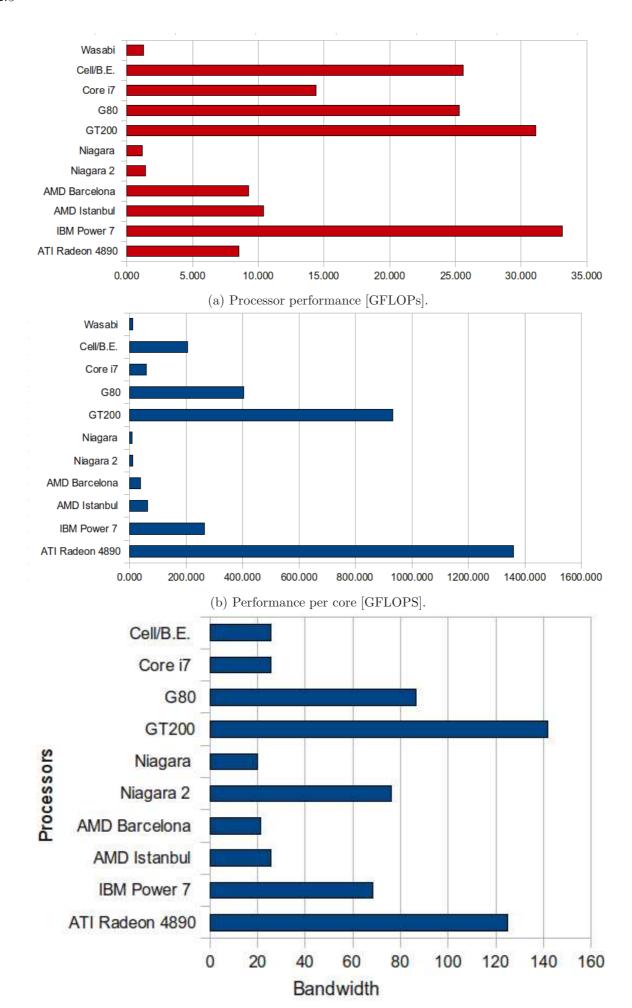

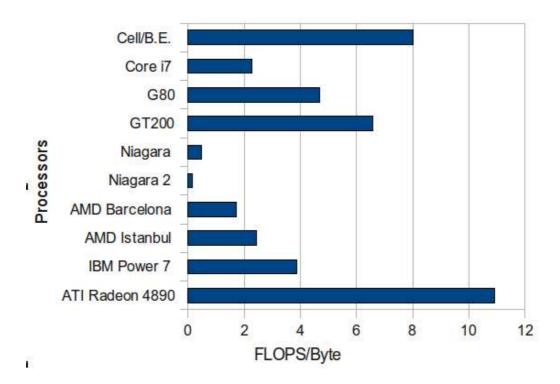

Despite the promising architecture, the processor has never been fully built. In our experiments (see more details in Appendix B) we have only used a cycle-accurate software simulator. However, the estimated performance of a single Wasabi chip, based on the specification of its cores, was around 10 GFLOPs (for all 9 cores combined).

Despite the platform being canceled in 2006, Wasabi/SpaceCAKE was a good experiment. Many of Wasabi's design ideas have been reproduced in later, more successful architectures. Also, the ambitious fully-coherent memory system generated a lot of interesting research on caches, cache partitioning [Mol09], and coherency.

# 2.2 General-purpose multi-core processors

Starting from 2004, General purpose Multi-cores (GPMCs) are replacing traditional CPUs in both personal computers and servers. Generically called "multi-cores", they are already offered by most of the big players - Intel, Sun, AMD, and IBM. GPMCs are homogeneous platforms with complex cores, based on traditional processor architectures; they are typically shared-memory architectures, with multiple layers of caches, and they are used as stand-alone processors.

In the following paragraphs, we discuss a few very common examples of general-purpose multicores, and we propose a brief comparison between their features and peak performance potential. Note that the time-frame in which these processors have emerged and developed is quite similar, so we just group them under the GPMCs label.

#### 2.2.1 Intel Nehalem

#### Nehalem EE: Quad-core Intel Core i7

Nehalem EE, introduced in 2008, is a four-core processor based on the Intel Core i7 architecture; with Intel's hyperthreading technology [Int09], the processor can use eight hardware threads. Base clock speeds range between 2.66 GHz and 3.2 GHz, while turbo clock speeds range between 2.80 GHz and 3.46 GHz. Note that the turbo mode is supposed to be turned on automatically when more computation power is needed.

The peak performance of Nehalem EE is achieved by the Intel Core i7-975 Extreme Edition: in normal mode, it runs at 3.33 GHz, delivering 53.28 GFLOPS; in turbo mode, the same processor runs at 3.6GHz and it delivers 57.6 GFLOPS.

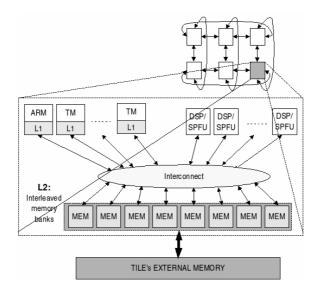

The on-chip memory hierarchy has three levels of caches: the L1, per core, separated for data and instructions (32 KB each), a low-latency L2, per core, 256 KB for both data and instructions, and a fully shared fully inclusive L3 cache, up to 8 MB. The chip supports 3 channels of external DDR3 memory, with interleaved access, and at most 8 GB per channel. The bandwidth per channel is 8.5 GB/s. The system bus, using Intel<sup>®</sup>Quick Path Interconnect (QPI), offers a peak bandwidth of 25.6 GB/s. A diagram of a system based on a Core i7-975 is presented in Figure 2.2.

$<sup>^{1}</sup>$ As Wasabi is the processor that has started this work, we decided to include it here as an interesting and original embedded multi-core platform.

Figure 2.2: Intel Core i7 (figure courtesy of RealWorld Technologies [Kan08]).

#### Nehalem EX: Eight-core Intel Core i7 (Xeon 7500 series)

The Intel Nehalem EX is an eight-core processor (introduced in early 2010), using hyperthreading to raise the number of available hardware threads to sixteen. The chip supports the SSE instruction set, allowing operations on SIMD vectors of 4 single-precision floating point numbers. The cache hierarchy has the same three as Nehalem EE, but the fully shared fully inclusive L3 cache can be increased up to 24 MB. The chip supports 4 channels of external DDR3 memory.

#### Intel Nehalem Programming

For programming its multi-cores, Intel provides a set of highly optimized function libraries, like Intel<sup>®</sup>Integrated Performance Primitives (IPP) and Intel<sup>®</sup>Math Kernel Library (MKL), the Intel<sup>®</sup>Threading Building Blocks (TBB) C++ template library, and a generalized data parallel programming solution with the Ct programming model. Besides these home-brewed solutions, programmers may use traditional, low-level multi-threading primitives, or opt for higher-level generic solutions such as OpenMP and MPI.

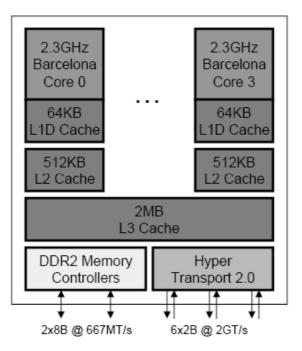

### 2.2.2 AMD Barcelona, Istanbul, and Magny-Cours: N-Core Opteron Processors

The architecture of AMD multi-cores is similar to the one of Intel Core i7: homogeneous cores, per-core L1 and L2 caches, shared L3 cache and off-chip memory, and separated memory and I/O buses/channels.

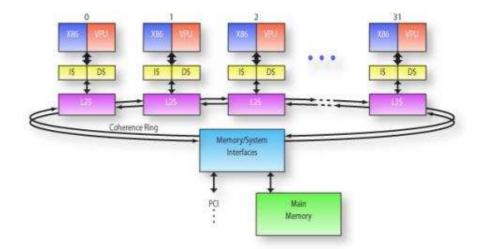

Figure 2.3: A Multi-Core AMD Opteron Processor(figure courtesy of RealWorld Technologies [Kan08]).

The first in the series, AMD Barcelona (late 2007), is a four-core processor able to reach a theoretical peak performance of 41.6 GFLOPS. The six-core version, code-named Istanbul (and launched in mid-2009), is clocked at 2.6GHz, delivering a theoretical peak performance of 62.4 GFLOPS. The latest generation, code-named Magny-Cours (launched in early 2010) has 12 cores (although on two separate dies, with very fast inter-die interconnect).

Each core has an L1 cache of 128 KB, half for data and half for instructions, and an L2 cache of 512 KB; all cores share a 6 MB L3 cache. The dual-channel main memory controller is clocked at 2.2GHz. The main memory (off-chip) supports up to DDR2-800 RAM, and can go up to 16 GB. The maximum bandwidth for main memory transfers is 19.2 GB/s. The system bus, using AMD<sup>®</sup>Hyper Transport 3 (HT3), runs at a maximum bandwidth of 19.2 GB/s (4.8 GT/s). A diagram of the AMD Barcelona is presented in Figure 2.3.

#### AMD Multi-core Programming

Just like Intel, AMD provides a highly optimized math library, the AMD<sup>®</sup> Core Math Library (ACML). To compete with Intel<sup>®</sup>IPP, AMD has invested in the open-source Frame wave project [AMD08], which offers code-level access to a vast array of signal and image processing functions and routines. The Framewave library is API compatible with IPP. Currently, for application development, programmers use low-level multi-threading primitives or higher-level generic solutions such as OpenMP and MPI. AMD is said to be in discussions with Microsoft for developing/supporting additional multi-core programming tools.

Figure 2.4: Sun UltraSPARC T2 Plus (figure courtesy of RealWorld Technologies [Kan06]).

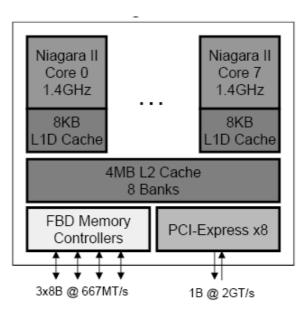

#### 2.2.3 Sun UltraSPARC T2 and T2+

Sun's top multi-core processors are visible in the servers product line. The Sun multi-core family is based on the UltraSPARC Tx processors, and it has three members: Niagara (Sun UltraSPARC T1, launched in 2006), Niagara II (Sun UltraSPARC T2, launched in 2008), and Victoria Falls (Sun UltraSPARC T2+, launched in early 2009). The architectural differences between these chips are not significant. Rather, most differences come from the "numbers", as later platforms have faster clocks, more threads, more memory, and increased numbers of multi-chip configurations.

Victoria Falls [Ora08], the top of the line, is an Symmetrical Multiprocessor (SMP) architecture with 8 SPARC cores, each core handling 8 concurrent threads. Cores are clocked at 1.4 GHz (T2+) (compared to 1.2 GHz for T2). Consequently, the achieved performance is 11.2 GFLOPS (for T2, we have 9.33 GFLOPS).

The memory system has two levels of cache - an L1 (separated for data and instructions) per core, and a shared L2. The L1 instruction cache is 16 KB large (32 B lines, 8-way set associative), while the The L1 data cache is 8 KB large (16 B lines, 4-way set associative). The L2 is a 4MB, 8 banks, 16-way associative cache. Each core is bidirectionally connected to each L2 bank by a custom, full  $8 \times 9$  cache crossbar switch. Thus, the interconnect supports 8 Byte writes from any core to any bank, and 16 Byte reads from any bank to any core. An additional port in the crossbar switch allows cores to perform I/O operations. All I/O operations are handled by a System Interface Unit (SIU), which connects networking and I/O to the memory. The crossbar bandwidth (i.e., the aggregated L2 memory bandwidth) reaches 90 GB/s for writes and 180 GB/s for reads per channel. To access the (off-chip) main memory, Victoria Falls uses two Fully Buffered DIMM (FB-DIMM) controllers per socket, with four DIMMs each. The aggregated memory bandwidth (for both sockets) is about GB/s. A diagram of the Sun UltraSPARC T2+ is presented in Figure 2.4. **Sun Niagara II Programming** We note that the Sun Niagara II differs significantly from the other GPMC processors, because it is a scalar, in-order processor (with hardware threads) instead of a super-scalar out-of-order processor (with - Intel Nehalem - or without -AMD N-Core Opteron - hardware threads). The Niagara II focuses on high throughput instead of fast completion of tasks. The very high bandwidth, both internal and external, clearly indicates very good support for data intensive workloads, as the processor is dedicated to a large variety of servers (the "Cool Threads" family, by Sun).

In terms of programming, besides the classical OpenMP and MPI solutions, Sun offers the largest variety of tools, including application evaluation/analysis, porting, debugging, optimizing, and testing tools. Sun Studio 12 provides an integrated environment for compilers and tools that cover the application development phases [Sun08].

#### **IBM POWER7**

The latest IBM processor, the POWER7, announced in the summer of 2009, is also a large multi-core that focuses on the servers market. Clocked at 3.0 GHz to 4.14 GHz, a POWER7 chip has 4, 6, or 8 cores; each core is 4-ways SMT. Thus, a dual-chip module (available already for server machines) can offer up to 64 concurrent threads. The theoretical peak performance per core is estimated at 33.12 GFLOPS per core, allowing for a maximum of 264.96 GFLOPS per chip. For its memory system, POWER7 relies on 2 layers of private caches - 32 KB L1 instruction and data cache (per core) and 256 KB L2 Cache (per core), and 1 layer of shared cache - 32 MB on-die <sup>2</sup>, shared by all cores (at most 32/die). The chip also features two DDR3 memory controllers, reaching 100GB/s sustained memory bandwidth. In SMP mode, the POWER7 delivers 360GB/s bandwidth/chip.

#### **IBM POWER7 Programming**

Overall, POWER7 is a HPC processor aimed at supercomputers and/or high-end application servers. Being yet another symmetric multi-core architecture, POWER7 also allows programmers to use generic parallel programming models such as OpenMP or MPI. While IBM is not spending a lot of effort in the high-level design tool chains (it does, however, provide specially optimized compilers and profilers), there are "imported" solutions to be considered. For example, Partitioned Global Address Space (PGAS) languages like UPC [Car99; Zhe10] and Co-Array FORTRAN [Coa05; MC09], together with Charm++ [Kal96; Kal95b; Kal95a], are currently used for programming Blue Waters, the largest POWER7 supercomputer to date.

#### 2.2.4 A Summary of GPMCs

A summary of the important features of the three general purpose multi-core processors we have discussed is presented in Table 2.2.4. Note that from the computer architecture point of view, the platforms are very similar. A more significant variety appears in the architectural parameters - number of cores and/or threads, clock frequency, memory bandwidth, etc.

In terms of programming, it is safe to say that all GPMC processors target similar applications, namely coarse grain MPMD and/or SPMD workloads. The parallelism model is symmetrical multi-threading (i.e., all the available hardware threads are similar). The mapping/scheduling of processes

$<sup>^{2}</sup>$ The cache is implemented in eDRAM, which does not require as many transistors per cell as a standard SRAM so it allows for a larger cache while using the same area as SRAM.

| Platform     | Intel Nehalem EE        | AMD Istanbul             | Sun Niagara                | IBM POWER7           |

|--------------|-------------------------|--------------------------|----------------------------|----------------------|

| Cores        |                         |                          |                            |                      |