# All-Digital I/Q RF-DAC

Seyed Morteza Alavi

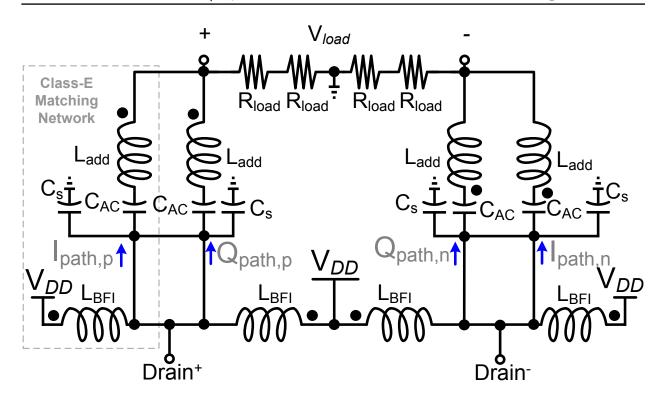

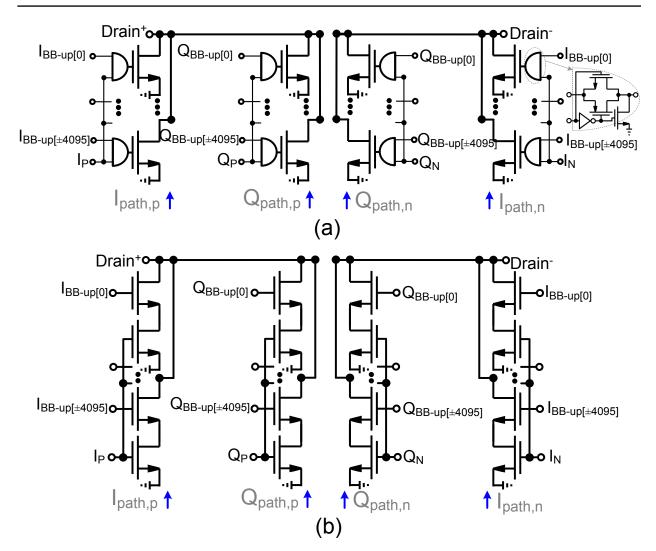

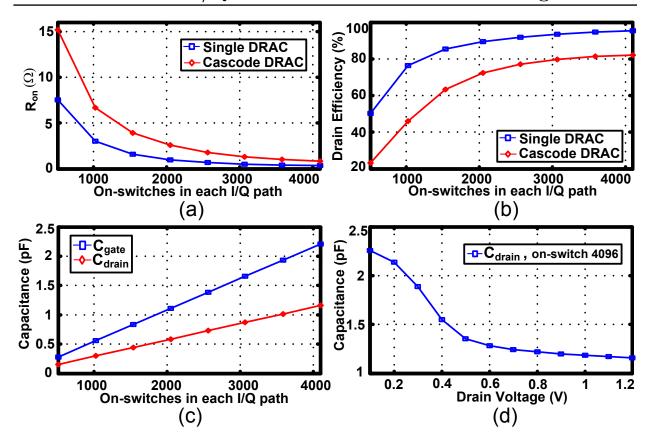

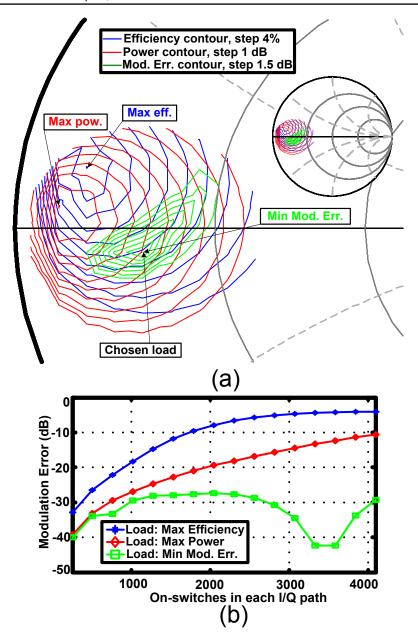

# All-Digital I/Q RF-DAC

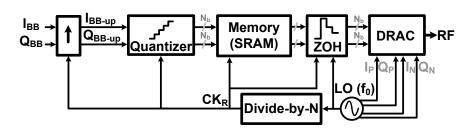

Proefschrift

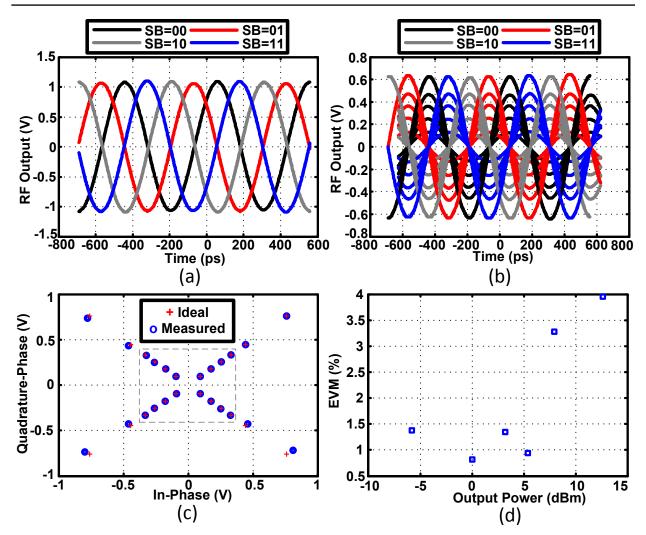

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op donderdag 19 juni 2014 om 12.30 uur

door

Seyed Morteza ALAVI

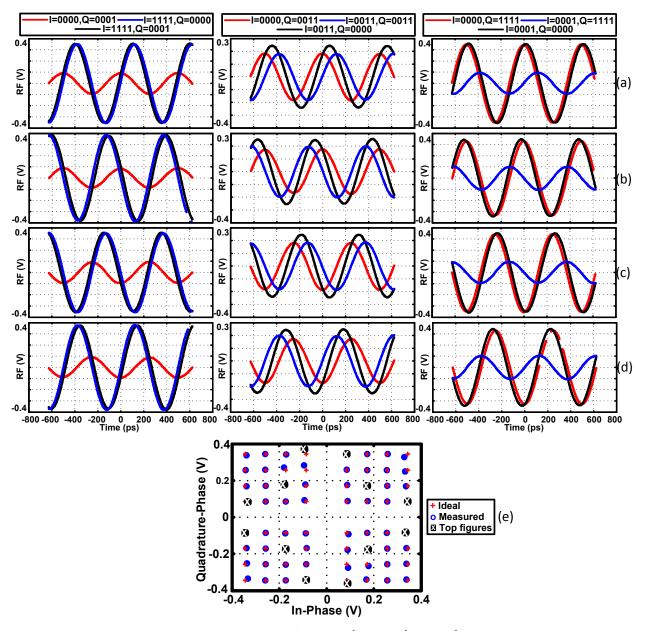

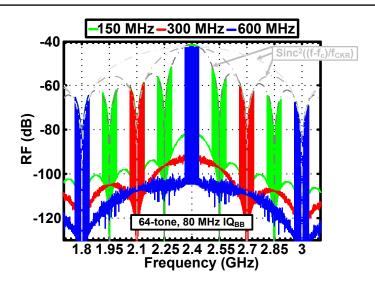

Master of Science in Electrical Engineering, University of Tehran, Iran geboren te Teheran, Iran.

Dit proefschrift is goedgekeurd door de promotor: Prof. dr. R. B. Staszewski Copromotor: Dr. ing. L. C. N. de Vreede

Samenstelling promotiecommissie:

| Rector Magnificus,             | voorzitter                                |

|--------------------------------|-------------------------------------------|

| Prof. dr. R. B. Staszewski,    | Technische Universiteit Delft, promotor   |

| Dr. ing. L. C. N. de Vreede,   | Technische Universiteit Delft, copromotor |

| Prof. dr. J. R. Long,          | Technische Universiteit Delft, adviseur   |

| Prof. dr. ir. P. G. M. Baltus, | Technische Universiteit Eindhoven,        |

| Prof. dr. ir. F. E. van Vliet  | Universiteit Twente,                      |

| Prof. dr. P. Wambacq,          | Vrije Universiteit Brussel, Belgie        |

| Prof. dr. ing. S. Heinen,      | RWTH Aachen University, Duitsland         |

| Prof. dr. K. A. A. Makinwa,    | Technische Universiteit Delft, reservelid |

Seyed Morteza Alavi, All-Digital I/Q RF-DAC, Ph.D. Thesis Delft University of Technology, with summary in Dutch.

Keywords: balun, digital power amplifier (DPA), digital predistortion (DPD), digital-to-RFamplitude converter (DRAC), in-phase/quadrature-phase (I/Q) modulator, MOS switch, RF digital-to-analog converter (RF-DAC), transformer, transmitter (TX).

ISBN 978-94-6259-218-6

Copyright © 2014 by Seyed Morteza Alavi

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the prior written permission of the copyright owner.

Printed in the Netherlands.

To my lovely parents (Mehdi and Noushin) To my lovely sister (Sara) and her respected family To my lovely grand parents and my late grand parents To my lovely uncles, aunts, and my late uncles To my lovely cousins and their respected families To all my family members in Iran and around the world To all my friends in Iran and around the world To all my teachers in Iran and around the world And last, but not least, to my lovely wife (Haleh) and her respected family "Now it is established in the sciences that no knowledge is acquired save through the study of its causes and beginnings, if it has had causes and beginnings; nor completed except by knowledge of its accidents and accompanying essentials."

Avicenna, 980-1037

# Contents

| C        | Contents i |                                                                                                                             |           |  |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------|-----------|--|

| 1        | Intr       | oduction                                                                                                                    | 1         |  |

|          | 1.1        | The Conventional RF Radio                                                                                                   | 1         |  |

|          | 1.2        | Motivation                                                                                                                  | 4         |  |

|          | 1.3        | The Thesis Objectives                                                                                                       | 6         |  |

|          |            | 1.3.1 System Simulation of WCDMA Baseband Data                                                                              | 6         |  |

|          |            | 1.3.2 Some Important Figures-of-Merit in RF Transmitters                                                                    | 7         |  |

|          | 1.4        | Thesis Outline                                                                                                              | 9         |  |

| <b>2</b> | An         | alog Versus Digital RF Transmitters                                                                                         | 11        |  |

|          | 2.1        | Analog-Intensive RF Transmitters                                                                                            | 11        |  |

|          | 2.2        | Digitally-Intensive RF Transmitters                                                                                         | 14        |  |

|          | 2.3        | New Paradigm of RF Design in Nanometer-Scale CMOS                                                                           | 15        |  |

|          | 2.4        | All-Digital Polar Transmitter                                                                                               | 16        |  |

|          | 2.5        | All-Digital I/Q Transmitter                                                                                                 | 18        |  |

|          | 2.6        | Conclusion                                                                                                                  | 20        |  |

| 3        | Idea       | a of All-Digital I/Q Modulator                                                                                              | <b>21</b> |  |

|          | 3.1        | Concept of Digital I/Q Transmitter                                                                                          | 21        |  |

|          | 3.2        | Orthogonal Summing Operation of RF-DAC                                                                                      | 23        |  |

|          | 3.3        | Conclusion                                                                                                                  | 34        |  |

| 4        | Or         | thogonal Summation: A 2×3-bit All-Digital I/Q RF-DAC                                                                        | 35        |  |

|          | 4.1        | Circuit Building Blocks of Digital I/Q Modulator                                                                            | 36        |  |

|          |            | 4.1.1 Digitally Controlled Oscillator                                                                                       | 37        |  |

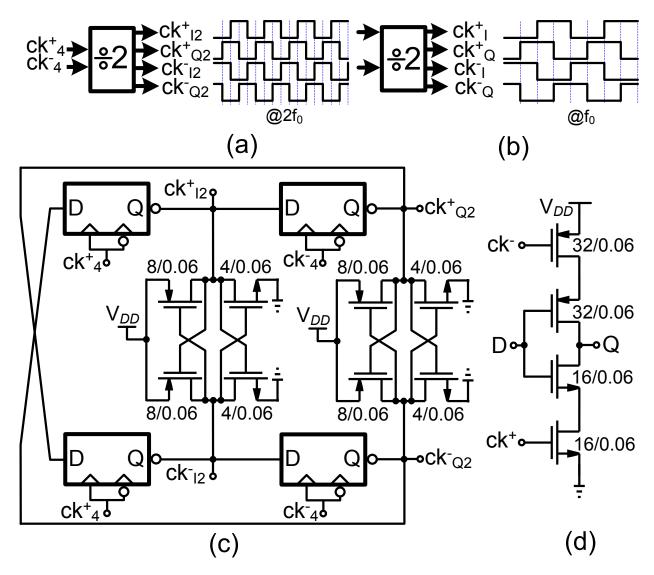

|          |            | 4.1.2 Divide-By-Two Circuit                                                                                                 | 38        |  |

|          |            | 4.1.3 25% Duty Cycle generator $\ldots \ldots \ldots$ | 39        |  |

|          |            | 4.1.4 Sign Bit Circuit                                                                                                      | 40        |  |

|          |            | 4.1.5 Implicit Mixer Circuit                                                                                                | 40        |  |

|          |      | 4.1.6 $2 \times 3$ -bit I/Q Switch Array Circuits $\ldots \ldots \ldots$ | 41  |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

|          | 4.2  | Measurement Results                                                                                                                     | 46  |

|          | 4.3  | Conclusion                                                                                                                              | 52  |

| <b>5</b> | To   | wards High-Resolution RF-DAC: The System Design Perspective                                                                             | 53  |

|          | 5.1  | System Design Considerations                                                                                                            | 54  |

|          | 5.2  | Conclusion                                                                                                                              | 62  |

| 6        | Dif  | fferential I/Q DPAs and The Power Combining Network                                                                                     | 63  |

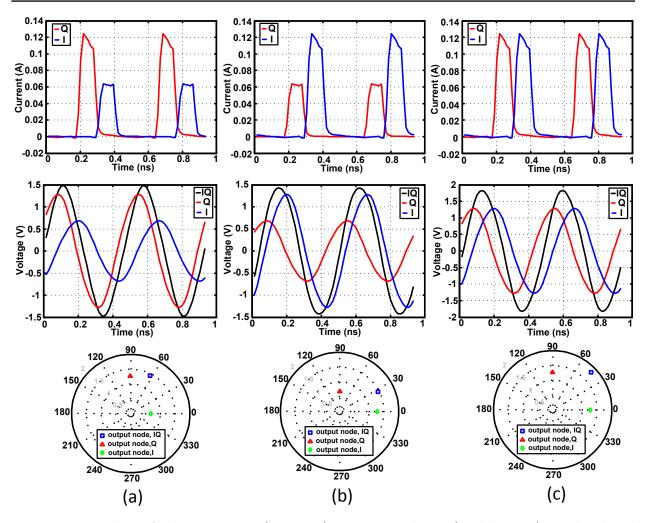

|          | 6.1  | Idealized Power Combiner With Different DRACs                                                                                           | 64  |

|          | 6.2  | A Differential I/Q Class-E Based Power Combiner                                                                                         | 69  |

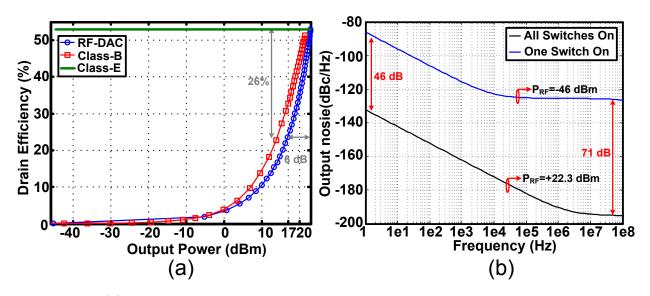

|          | 6.3  | Efficiency of I/Q RF-DAC                                                                                                                | 77  |

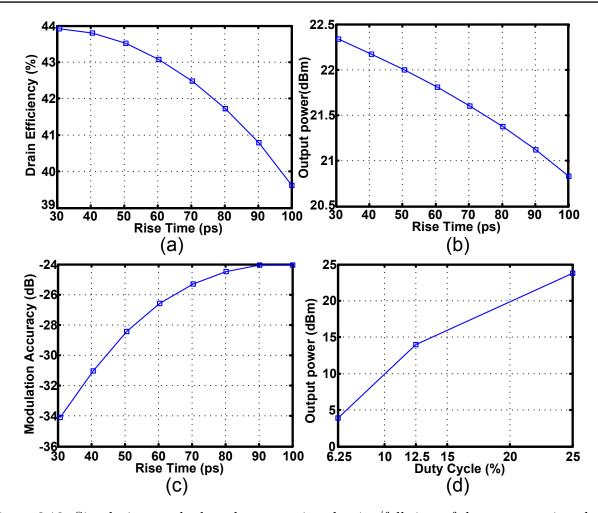

|          | 6.4  | Effect of Rise/Fall Time and Duty Cycle                                                                                                 | 81  |

|          | 6.5  | Efficiency and Noise at Back-Off Levels                                                                                                 | 82  |

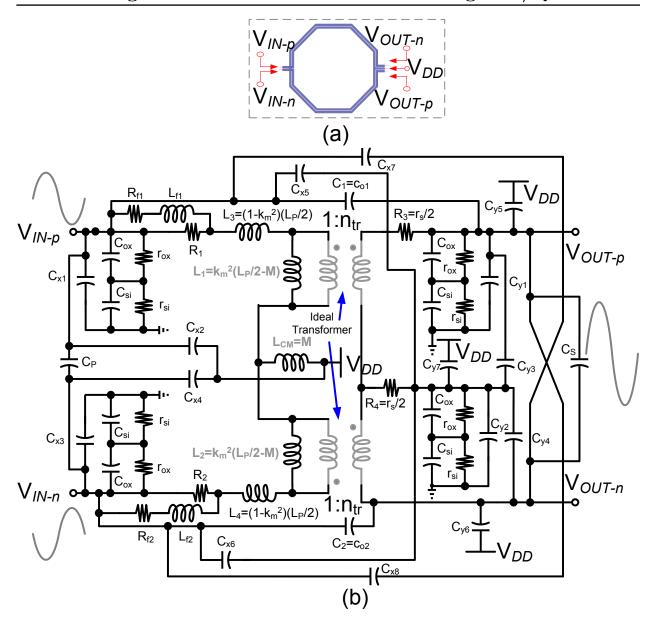

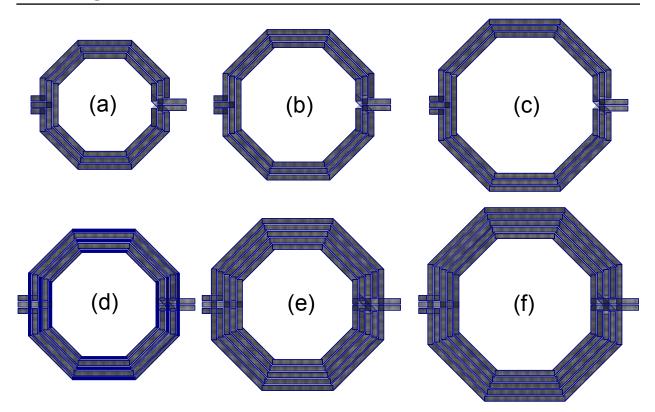

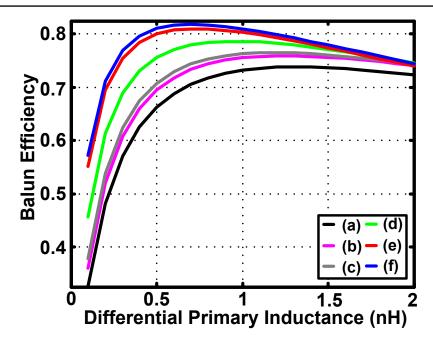

|          | 6.6  | Design an Efficient Balun For Power Combiner                                                                                            | 84  |

|          | 6.7  | Conclusion                                                                                                                              | 91  |

| 7        | ΑV   | Wideband $2 \times 13$ -Bit All-Digital I/Q RF-DAC                                                                                      | 93  |

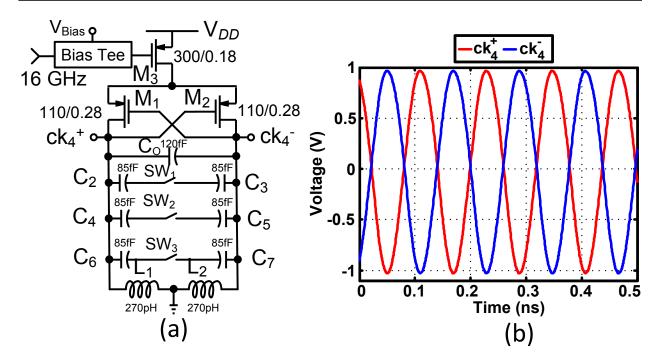

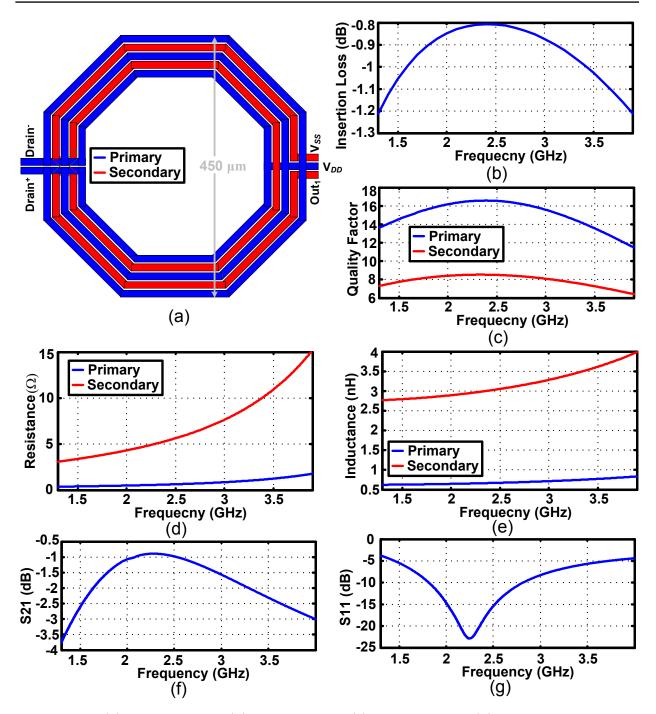

| •        | 7.1  | Clock Input Transformer                                                                                                                 | 93  |

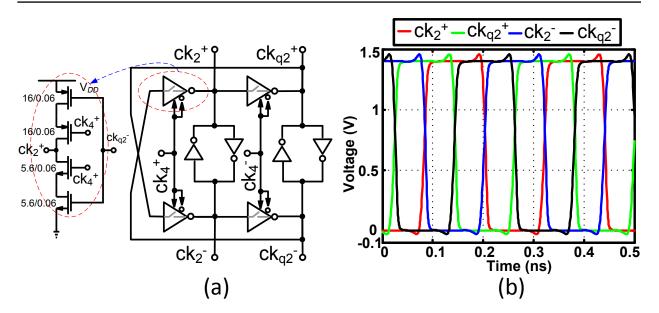

|          | 7.2  | High-Speed Rail-to-Rail Differential Dividers                                                                                           | 94  |

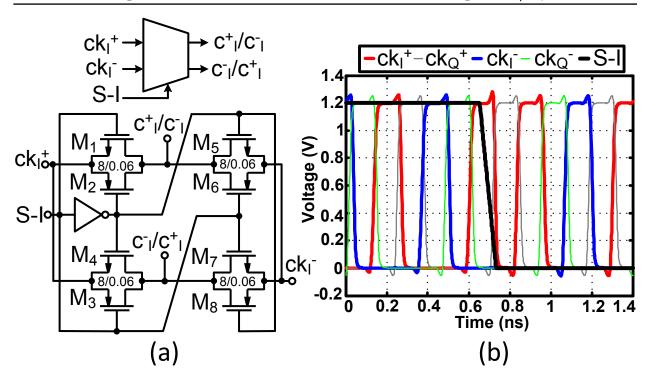

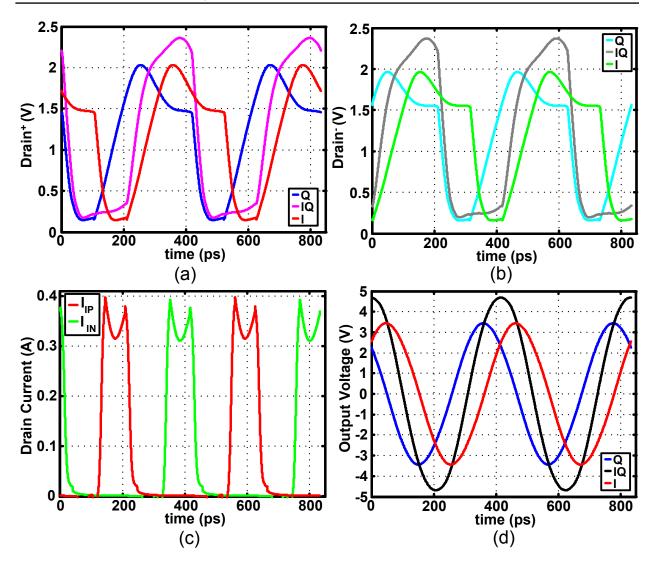

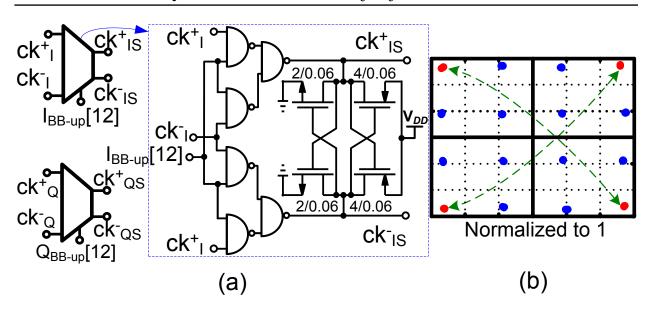

|          | 7.3  | Complementary Quadrature Sign Bit                                                                                                       | 96  |

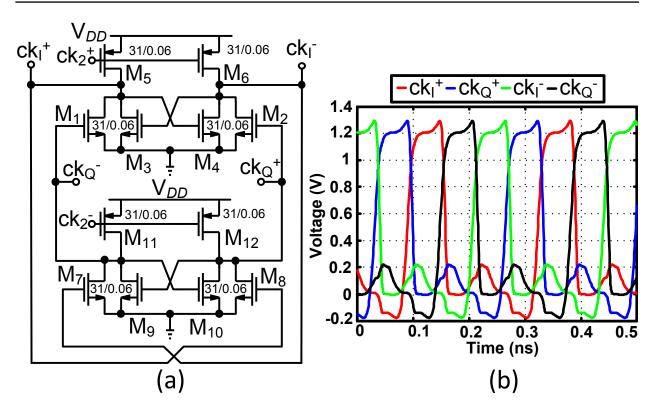

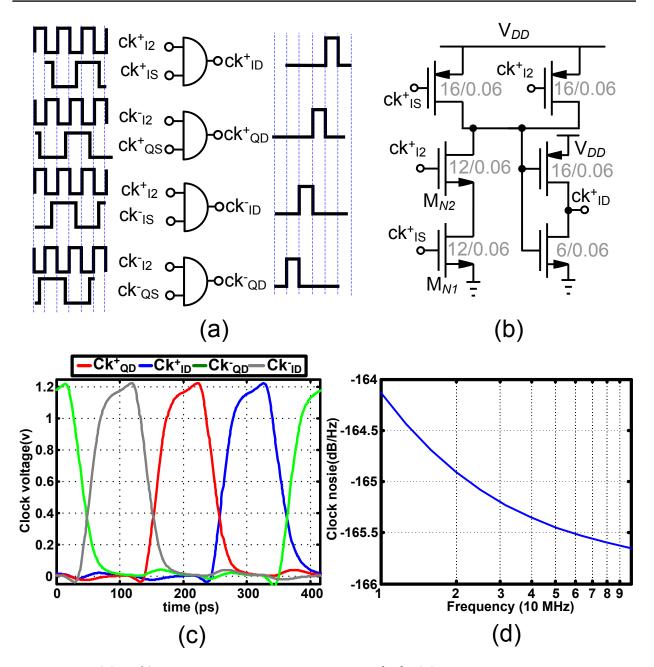

|          | 7.4  | Differential Quadrature 25% Duty cycle Generator                                                                                        | 97  |

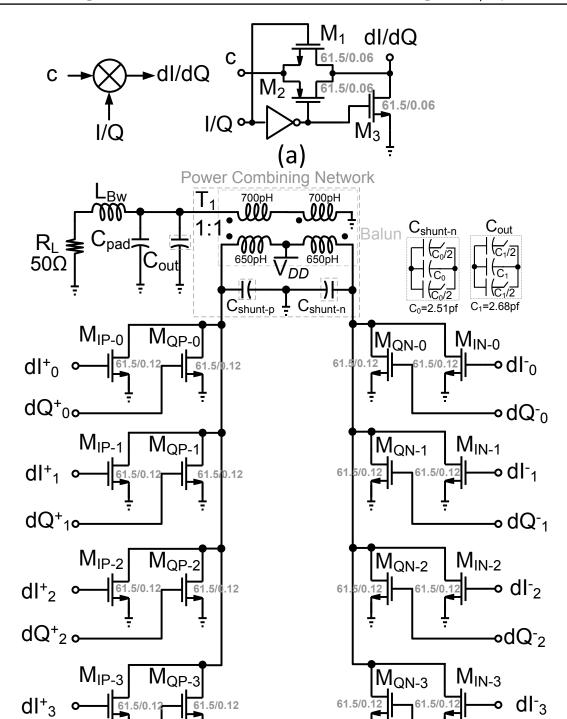

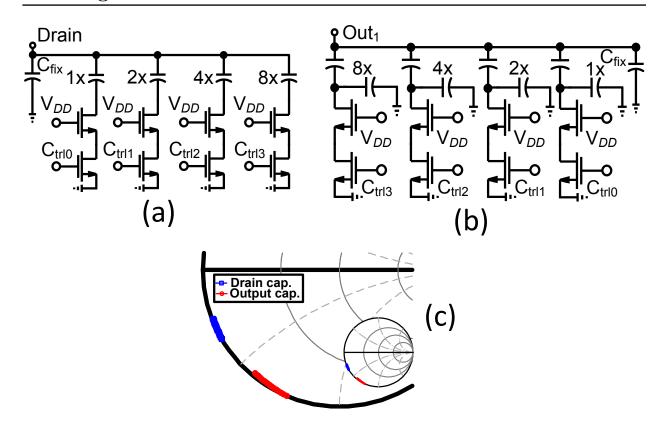

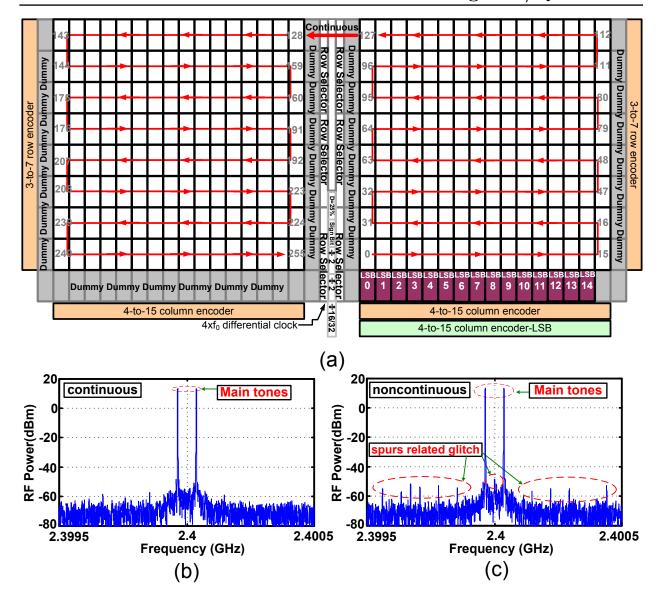

|          | 7.5  | Floorplanning of $2 \times 13$ -bit DRAC                                                                                                | 99  |

|          | 7.6  |                                                                                                                                         | 101 |

|          | 7.7  |                                                                                                                                         | 101 |

|          | 7.8  |                                                                                                                                         | 106 |

|          | 7.9  |                                                                                                                                         | 108 |

|          |      |                                                                                                                                         | 109 |

|          |      |                                                                                                                                         | 111 |

|          |      |                                                                                                                                         | 113 |

|          |      |                                                                                                                                         | 116 |

|          |      |                                                                                                                                         | 118 |

|          |      |                                                                                                                                         | 119 |

|          | 7.10 |                                                                                                                                         | 120 |

| 8        | Me   | asurement Results of the $2 \times 13$ -bit I/Q RF-DAC                                                                                  | 121 |

| -        | 8.1  |                                                                                                                                         | 121 |

|          | 8.2  | -                                                                                                                                       | 123 |

|          | 8.3  |                                                                                                                                         | 126 |

|          | 2.3  | ·                                                                                                                                       | 127 |

|          |      |                                                                                                                                         | 128 |

|          |      |                                                                                                                                         |     |

\_\_\_\_\_

### CONTENTS

|    | 8.4               | 8.3.3 The RF-DAC's Linearity Using Constellation Mapping                                                                                                                                | 130<br>136                                                                  |  |

|----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| 9  | 9.1<br>9.2<br>9.3 | The Thesis Outcome                                                                                                                                                                      | <ul> <li><b>137</b></li> <li>137</li> <li>139</li> <li>142</li> </ul>       |  |

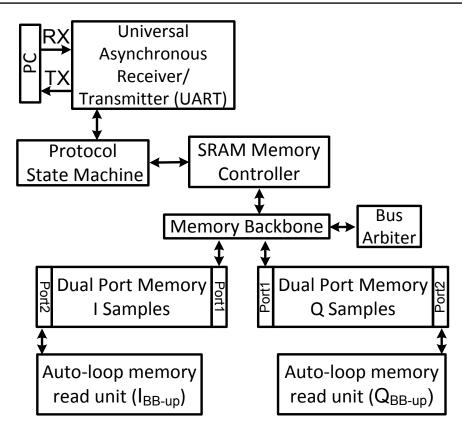

| A  | A.1<br>A.2<br>A.3 | <b>litional Elaboration</b> Universal Asynchronous Receiver/TransmitterMatching Network Equations (Chapter 6)AM-AM/AM-PM Relationship (Chapter 7)DPD Bandwidth Expansion (Chapters 7–8) | <ul> <li>143</li> <li>143</li> <li>143</li> <li>146</li> <li>147</li> </ul> |  |

| Bi | bliog             | graphy                                                                                                                                                                                  | 149                                                                         |  |

| Su | mma               | ary                                                                                                                                                                                     | 161                                                                         |  |

| Sa | menv              | vatting                                                                                                                                                                                 | 165                                                                         |  |

|    |                   | ·                                                                                                                                                                                       | 169                                                                         |  |

|    |                   | 5                                                                                                                                                                                       | 172                                                                         |  |

|    |                   |                                                                                                                                                                                         | 177<br>178                                                                  |  |

|    | 0                 |                                                                                                                                                                                         |                                                                             |  |

| At | out               | the Author                                                                                                                                                                              | 183                                                                         |  |

# Chapter 1 Introduction

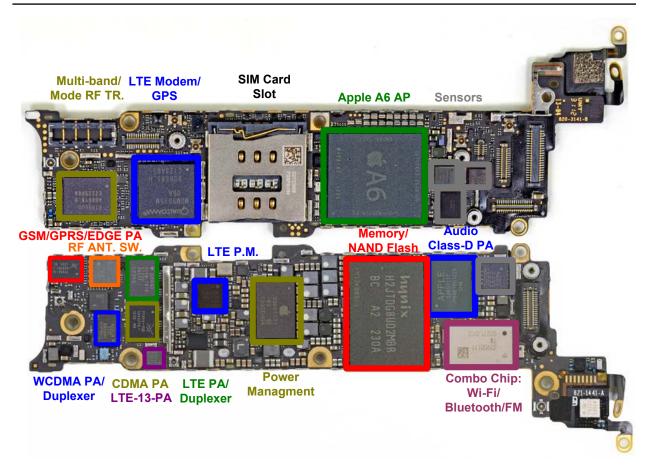

Consumer electronic devices such as smartphones, tablets, and laptops, are constantly evaluated against three key criteria: low-cost, high power efficiency, and support of multimode/multi-band communication standards such as Wi-Fi including wireless LAN (IEEE 802.11) [1], Bluetooth [2], GNSS<sup>1</sup>, second generation (2G) cellular using Global System for Mobile Communications (GSM), third generation (3G) cellular using Wideband Code Division Multiple Access (WCDMA) [3], and fourth generation (4G) cellular using either of WiMAX or 3GPP Long-Term Evolution (LTE) [4,5]. These gadget devices comprise a myriad of integrated circuit (IC) chips to perform an extensive number of distinct functions such as multimedia streaming and gaming as well as supporting the aforementioned communication standards. As an example of contemporary gadget devices, Fig. 1.1 illustrates the mainboard of a smartphone, e.g., the iPhone 5. It consists of an application processor (AP) unit, subscriber identification module (SIM) card slot, NAND flash memory, power management unit, Class-D audio amplifier and, most significantly, a number of radio frequency (RF) transceiver modules that support today's universal communication standards such as GSM, CDMA, Wi-Fi/Bluetooth/FM, GPS, and LTE in combination with its power management unit. Over the past two decades, there have been tremendous efforts to design RF radios that will afford an opportunity to address the low-power, low-cost, and extremely power efficient demands and, yet, they have also employed inventive transceiver architectures.

# 1.1 The Conventional RF Radio

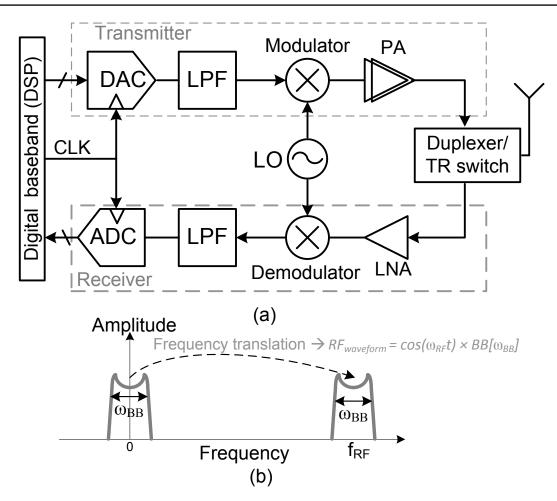

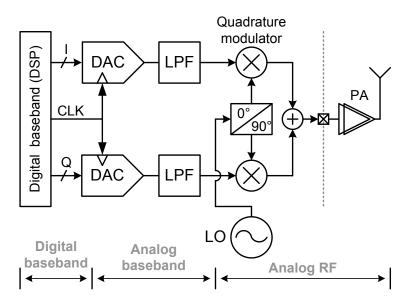

As depicted in Fig. 1.2(a), a conventional RF transceiver consists of a baseband digital signal processing (DSP) unit, transmitter (TX), and receiver (RX) [6,7]. The transmitter performs

<sup>&</sup>lt;sup>1</sup>GNSS is the abbreviation of global navigation satellite system. It includes American's GPS, Russian's GLONASS, European Union's Galileo, and China's Beidou navigation system.

Figure 1.1: The front and rear mainboard of iPhone-5 (Courtesy of Apple Inc.).

in the following manner: The anticipated transmitted information such as voice, video, or digital data like text/images are initially digitally processed, then encoded, and subsequently applied to a digital-to-analog converter (DAC) in order to convert the digital data to their corresponding analog counterparts. Due to the fact that these analog signals comprise unwelcome noise and spectral replicas, the transmitter utilizes low-pass filter (LPF) to reduce those undesirable artifacts. The filtered analog signals are subsequently mixed with an RF local oscillator (LO) utilizing an upconverting mixer and, consequently, upconverted to their designated RF transmit frequency band. Otherwise stated, as illustrated in Fig. 1.2(b), the LO signal translates the low-frequency Baseband analog signals with the bandwidth of  $\omega_{BB}$  into their equivalent high-frequency RF representation. In fact, the LO clock modulates the baseband signal. Thus, the upconverting RF mixer is referred to as an RF modulator. A power amplifier (PA) is succeedingly employed to efficiently boost the RF signal. The subsequent RF amplified signal is then applied to either a duplexer or transmit/receive (TR) switch<sup>2</sup> in order to be delivered to the transmitting antenna.

$<sup>^{2}</sup>$ If the radio uses frequency-division duplexing (FDD), it employs a duplexer. Otherwise, in the timedivision duplexing (TDD) communication system, it requires a TR switch.

Figure 1.2: (a) A conventional RF transceiver, (b) frequency-domain illustration of modulating the baseband signal.

In the receiver, however, its sensitivity is ameliorated utilizing a low noise amplifier (LNA). The subsequent signal is then down converted to baseband frequency utilizing a down-converter mixer, which is also referred to as a demodulator. By employing a few LPF circuits and then an analog-to-digital converter (ADC), the received signal is digitized for further digital baseband processing operation.

Among transceiver blocks, the RF transmitter is considered to be the most power consuming block of the entire radio, thus being a hindrance for extending the battery lifetime of portable wireless devices. This is due to the fact that it comprises power hungry building blocks such as DAC, the upconverting mixer and, most importantly, the RF PA. For example, in the aforementioned smartphone, as indicated in Fig. 1.1, there are at least 6 different RF-PA modules<sup>3</sup> to support multi-band/ multi mode communication standards.

Consequently, the power amplifiers are the most "power-hungry" building blocks of any portable device due to the high-power RF signal generation that is required by the corre-

<sup>&</sup>lt;sup>3</sup>1-GSM/GPRS/EDGE; 2-WCDMA; 3-CDMA; 4-LTE; 5-LTE band 13; 6-Wi-Fi/Bluetooth/FM.

| Company | 4Q13      | 4Q13 Market  | 4Q12      | 4Q12 Market  |

|---------|-----------|--------------|-----------|--------------|

|         | Units     | Share $(\%)$ | Units     | Share $(\%)$ |

| Samsung | 83,317.2  | 29.5         | 64,496.3  | 31.1         |

| Apple   | 50,224.4  | 17.8         | 43,457.4  | 20.9         |

| Huawei  | 16,057.1  | 5.7          | 8,666.4   | 4.2          |

| Lenovo  | 12,892.2  | 4.6          | 7,904.2   | 3.8          |

| LG      | 12,822.9  | 4.5          | 8,038.8   | 3.9          |

| Others  | 106,937.9 | 37.9         | 75,099.3  | 36.2         |

| Total   | 282,251.7 | 100          | 207,662.4 | 100          |

Table 1.1: Worldwide Smartphone Sales in 4Q13 (kUnits)

Source: Gartner (February 2014)

sponding communication standard to continuously ensure an impeccable transmitting operation. For example, the corresponding PA in the GSM standard should provide 2 W RF power. Considering a power efficiency as high as 40%, the battery must drain 5 W to generate such RF power which reduces the battery life of the portable device [8–10].

It is worth mentioning that, currently, there are over 6 billion cellular phone users and, in particular, the number of smartphone users is increasing exponentially. Table 1.1 depicts the third quarter of 2012-2013 global smartphone market. As is indicated, smartphone production increases approximately 45% every year. With the progressive number of wireless devices and the relative shortage of bandwidth availability, it will become increasingly difficult to transmit power efficient, undistorted RF signals that do not interfere with other users.

### 1.2 Motivation

Considering the aforementioned design challenges of the conventional RF transmitter in Section 1.1, intensive research has recently been directed towards the realization of digitally intensive and all-digital RF transmitters that provide high output power with high efficiency while concurrently being highly reconfigurable [11–21]. This was also in response to the incredible advancements of the mainstream Complementary metal-oxide-semiconductor (CMOS) technology in both processing speed and circuit density as well as the relentless coercion to reduce total solution costs through integration of RF, analog, and digital circuitry. Since the digital baseband part of a wireless communication channel has traditionally been implemented in the most advanced CMOS technology available at a given time for mass

#### 1.2 Motivation

production, the need for single-chip CMOS integration has forced immutable changes to the way RF circuits are fundamentally designed. In this low-voltage nanometer-scale CMOS environment, the high-performance RF circuits must exploit the time-domain design paradigm and rely significantly on digital assisted techniques. In other words, contemporary designers are analog thinkers; they tend to cogitate in terms of continuous voltages and currents. On the contrary, digital designers think in terms of discrete-time, discrete-value and, most recently, time-domain operations.

Scientist researchers believe that the development of the concepts behind direct digital or all-digital RF transmitters are in their infancy and innumerable untapped applications and standards are still available. In the current Information Era where more and more data is wirelessly transmitted, it is essential that this information is transmitted in a clear and distortion-free manner while exploiting as little energy as possible. The innovative concept should involve a method and system for digitally generating wideband radio frequency (RF) signals that can be transmitted without the requirement of the current state-of-the-art polar topology which has only been successfully applied to narrowband modulation schemes  $[14]^4$ . Otherwise stated, the wireless LAN (WLAN) as well as the currently running wideband modulation standards such as the 3G cellular employing WCDMA and the 4G cellular using 3GPP LTE cannot exploit the current state-of-the-art digital polar RF technology [14] due to the wide bandwidth requirements. Solving the wide bandwidth modulation issues will afford an opportunity to introduce a universal all-digital RF transmitter. It will decrease the cost of production for new and existing IC customers and also will benefit the end users. Concurrently, it will reduce the IC area which signifies increased space for other applications. It will also lower power consumption, thereby resulting in a longer battery lifetime. To summarize, the main advantages of utilizing the new direct digital transmitter architecture are:

- 1. The circuit integration level will be higher, thus the wireless portable devices can be smaller, lighter, and have nicer designs through smaller form factors. From a technical perspective, employing a direct digital transmitter eliminates the bulky DAC, analog LPFs, and analog mixers;

- 2. Due to the elimination of several power-hungry analog components, the power efficiency of the RF transmitter will be higher, therefore, it subsequently increases battery life or leads to smaller battery size.

- 3. The new topology can afford more sophisticated reconfigurability in order to handle various standards and even modulation methods that have yet to be invented.

$<sup>^{4}</sup>$ As will be explained in the following chapters, although recent publications have indicated that polar architecture can manage up to 20 MHz [18–21], the utilized polar structure is still very complicated. Moreover, it could not handle wider band signals such as 802.11n/ac with the modulation bandwidth of 40/160 MHz.

# **1.3** The Thesis Objectives

Based on the previous explanations in Sections 1.1 and 1.2, the underlying objective of this dissertation is, therefore, to implement an innovative, fully-integrated<sup>5</sup>, all-digital RF transmitter which should be power-efficient and, yet, must manage a wideband complex-modulated signal in order to support multi-mode/multi-band communication standards. Moreover, it should generate adequate RF power, minimal out-of-band spectra while the generated far-out noise of the all-digital RF transmitter must be low enough that is does not desensitize the companion receiver circuit blocks. Due to the zero-order-hold operation in the digital-to-RF interface, the direct digital RF transmitter, however, inherently creates spectral replicas at multiples of the baseband upsampling frequency away from the carrier frequency. In contrast, in the conventional analog RF transmitter, the spectral replicas have been eliminated due to utilizing the analog continuous-time filters directly following the DAC (see Fig. 1.2(a)). Moreover, the quantization noise induced by the limited effective baseband code resolution of the digital transmitter, worsens out-of-band spectra. This anomaly also does not exist in the analog counterparts. To gain more insight into these phenomena, the following subsection will be conducive.

#### 1.3.1 System Simulation of WCDMA Baseband Data

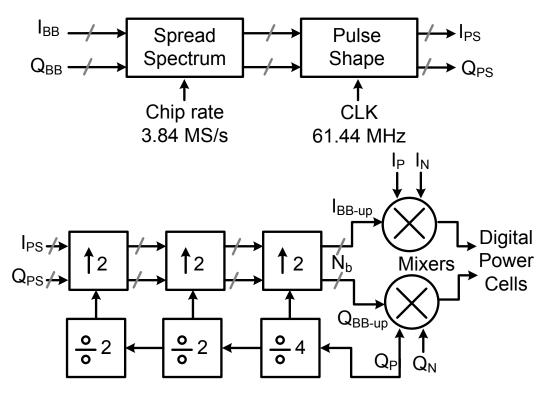

As discussed previously, although the direct digital transmitter does not necessitate the bulky analog LPF, it requires another type of filtering based on a discrete-time digital approach. Consider a WCDMA baseband signal in which its data rate varies between 7.5 kb/s to 960 kb/s. Fig. 1.3 illustrates the filtering process whereby the spread spectrum filter is first applied to an in-phase digital baseband  $(I_{BB})$  and a quadrature-phase digital baseband  $(Q_{BB})$  samples at a chip rate of 3.84 MHz. Subsequently, in order to constrain the occupied RF band, the resulting signals get pulse-shaped. The pulse-shaped oversampling rate is usually 16; therefore, the baseband data rate will increase to  $61.44 \,\mathrm{Mb/s}$ . If these samples ( $I_{PS}$  and  $Q_{PS}$  shown in Fig. 1.3) are applied directly to the mixer of an all-digital transmitter, then the resulting signal will produce spectral images at every 61.44 MHz from the up-converted spectrum which are very difficult to filter out. Therefore, it necessitates interpolation of these signals to higher data rates. Moreover, with the use of upsampling, the quantization noise spreads over a wider operational frequency range which also improves the dynamic range or resolution. With the employment of three cascaded finite impulse response (FIR) filter-based interpolators, each with an upsampling factor of L = 2, the resulting signal sampling rate is 535 MHz. Consequently, the images repeat every 535 MHz from the desired spectrum, which are now easier to filter out. It should be mentioned that,

<sup>&</sup>lt;sup>5</sup>As will be demonstrated in Chapter 4, the first prototype is exploited an on-chip, digitally-controlled oscillator (DCO) while the second chip in Chapter 7 just utilizes an external local oscillator (LO).

Figure 1.3: Upsampling and interpolation process of WCDMA baseband signals.

as depicted in Fig. 1.3, the FIR clocks are synchronized to the carrier clocks using clock frequency dividers which are a divide-by-4, and consecutive divide-by-2.

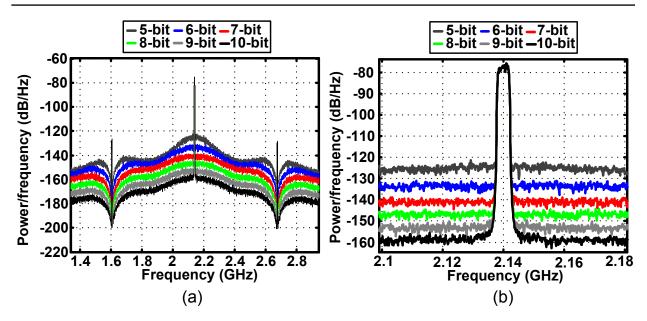

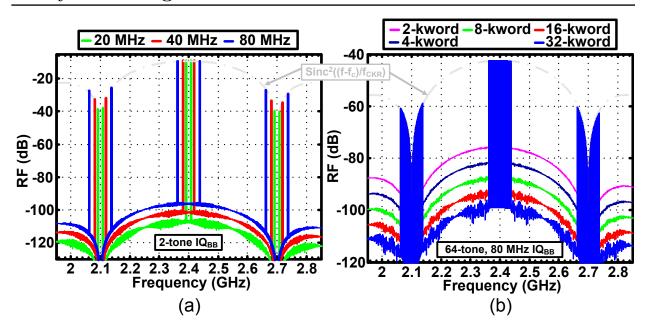

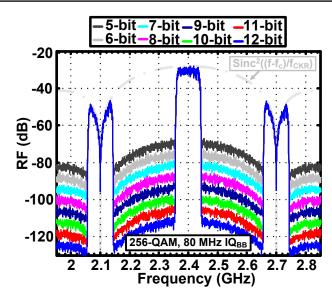

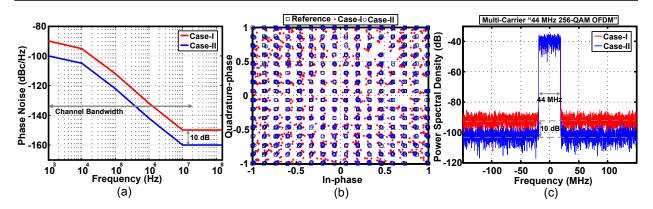

The simulation results of Fig. 1.3 are depicted in Fig. 1.4, which also indicates that, by increasing the resolution  $(N_b)$  of the all-digital transmitter, the quantization noise is decreased and, thus, the dynamic range of the WCDMA signal improves. Each additional bit corresponds to a 6 dB improvement in the dynamic range. The far-out spectrum of Fig. 1.4 demonstrates the sampling image replica of the original signal which is located 535 MHz away. This reveals that the baseband signals<sup>6</sup> are ultimately upsampled by a factor of 128  $(16 \times 8)$  to spread the quantization noise, thus lowering its spectral density.

In conclusion, an all-digital RF transmitter at the equal RF output power level compared to its analog counterpart, creates more noisy out-of-band spectrum.

#### **1.3.2** Some Important Figures-of-Merit in RF Transmitters

The RF transmitter can be evaluated by employing a number of figures-of-merit and they will be discussed as follows. First, the drain efficiency of the transmitter is defined as:

$$\eta_{drain} = \frac{P_{RFout}}{P_{DC-PA}} = \frac{V_{RFout} \times I_{RFout}}{V_{DC-PA} \times I_{DC-PA}}$$

(1.1)

$<sup>^6\</sup>mathrm{Note}$  that the WCDMA chip rate is  $3.84\,\mathrm{MS/s}.$

Figure 1.4: Simulated WCDMA RF output spectrum for different resolutions of all-digital transmitter: (a) far-out; (b) close-in range.

where  $P_{RFout}$  is the generated RF output power at the 50  $\Omega$  load, and  $P_{DC-PA}$  is the corresponding direct current (DC) power consumption of the PA. Moreover,  $V_{RFout}$  and  $I_{RFout}$  are root mean square (RMS) output voltage and current, respectively. Second, the system efficiency of the transmitter is defined as:

$$\eta_{system} = \frac{P_{RFout}}{P_{DC-Total}} = \frac{P_{RFout}}{P_{DC-PA} + P_{DC-Driver}}$$

(1.2)

where  $P_{DC-Total}$  is the related DC power consumption of the entire RF transmitter which includes the DC power consumption of PA and the upconverting clock driver circuit. The RF transmitter dynamic performance is subsequently divided into in-band performance and out-of-band spectral purity. The error vector magnitude (EVM) is conventionally utilized for the evaluation of the in-band performance and calculates the difference between the symbol sampling points of the measured and reference waveforms. The EVM result is defined as the square root of the ratio of the mean error vector power to the mean reference power and is expressed as a percentage [3]:

$$EVM_{RMS} = \frac{\sqrt{\sum_{i=1}^{N_{pt}} \frac{1}{N_{itr}} \times (IQ_{ideal}(i) - IQ_{real}(i))^2}}{\sqrt{\sum_{i=1}^{N_{pt}} \frac{1}{N_{itr}} \times (IQ_{ideal}(i))^2}}$$

(1.3)

where  $N_{itr}$  is the number of iterations for each point, and  $N_{pt}$  is the number of constellation points. Moreover,  $IQ_{ideal}(i)$  and  $IQ_{real}(i)$  are " $i_{th}$ " ideal (reference) and real (measured) constellation points, respectively. Additionally, the out-of-band spectral purity can be evaluated as an adjacent channel power ratio (ACPR)<sup>7</sup> and far-out noise performance at the corresponding receiver frequency band of interest. ACPR is utilized to measure the nonlinear distortion in the transmitted signal. Moreover, ACPR in combination with the modulation scheme determines the maximum allowable nonlinearity of the related RF transmitter. ACPR is defined as follows [22, 23]:

$$ACPR_{adj} = \frac{P_{adj}}{P_{main}} \tag{1.4}$$

where  $P_{adj}$  is the total adjacent right/left channel and  $P_{main}$  is the total RF power within the main transmit channel. Note that, instead of ACPR, the third order intermodulation product (IM<sub>3</sub>) can also be employed [22, 24]. Furthermore, as discussed previously, the farout noise performance of the RF transmitter strongly depends on quantization noise and baseband up-sampling rate. It is noteworthy that the far-out noise at the receiver frequency band of interest<sup>8</sup> must be less than its related thermal noise of -173.83 dBm/Hz<sup>9</sup>. Thus, as will be explained in more detail in Chapter 5, the baseband code resolution as well as the baseband upsampling rate should be suitably selected so as not to deteriorate the out-ofchannel spectrum as well as the far-out noise performance.

### 1.4 Thesis Outline

This dissertation is organized as follows:

In Chapter 2, four types of RF transmitter architectures are briefly described. The analog Cartesian modulators are the most simple and most widely exploited RF transmitters. They have subsequently been replaced by analog polar counterparts to address their poor power efficiency and noise performance. However, in the analog polar RF transmitters, their related amplitude and phase signals must be aligned, or spectral regrowth is inevitable. Utilizing digitally intensive polar RF transmitters mitigates the latter alignment issue. Nonetheless, polar transmitters suffer from an additional issue related to its nonlinear conversion of inphase and quadrature signals into the amplitude and phase representation. Consequently, the polar RF transmitters are unable to manage the substantial baseband bandwidth of the most stringent communication standards. However, reusing Cartesian modulators based on

<sup>&</sup>lt;sup>7</sup>Sometimes ACPR is expressed as adjacent channel leakage ratio (ACLR).

<sup>&</sup>lt;sup>8</sup>This condition is applicable in full-duplex systems.

<sup>&</sup>lt;sup>9</sup>This noise power level is obtained assuming conjugate matching at the input of the receiver,  $50 \Omega$  input load and temperature at  $27^{\circ}C$  [24, 25]. Note that, the noise figure (NF) and signal-to-noise ratio (SNR) of the receiver should also be considered which will be discussed in more detail in Chapter 5.

digitally intensive implementation appears to be a reasonable approach for managing this issue.

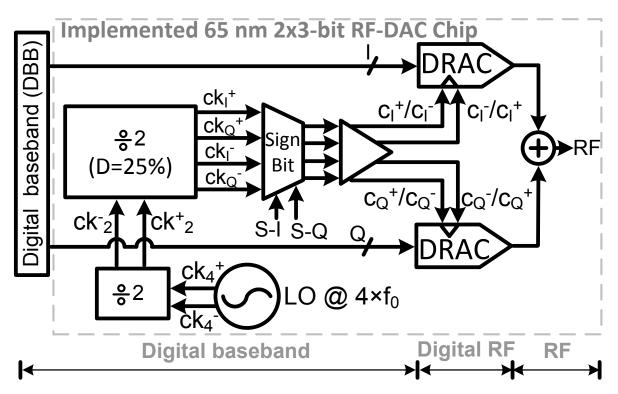

In Chapter 3, the novel all-digital I/Q RF modulator is described. This concept suggests that utilizing an upconverting RF clock with a 25% duty cycle ensures the orthogonal summation of  $I_{path}$  and  $Q_{path}$ . It is clarified that electric summing of I and Q digital unit array switches are the most appropriate I/Q orthogonal summation approach. Moreover, in order to cover all four quadrants of the constellation diagram, differential quadrature upconverting RF clocks should be used.

In Chapter 4, a novel  $2\times3$ -bit all-digital I/Q (i.e., Cartesian) RF transmit modulator is implemented. The radio-frequency digital-to-analog converter (RF-DAC) functions according to the concept of orthogonal summing and it is based on a time-division duplexing (TDD) manner of an orthogonal I/Q addition whereby a simple and compact design featuring high-output power, power-efficient and low-EVM is realized.

In Chapter 5, the system design considerations of the proposed high-resolution, wideband all-digital I/Q RF-DAC are discussed.

In Chapter 6, the design procedure of a 12-bit digital power amplifier together with a class-E-based power combining network are discussed.

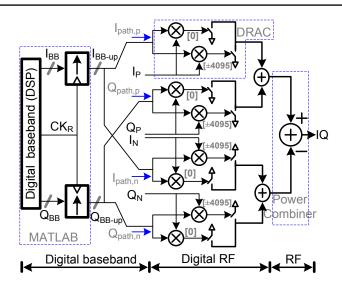

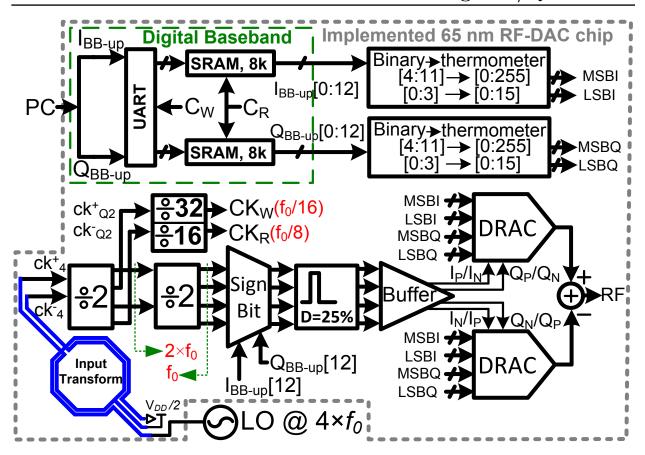

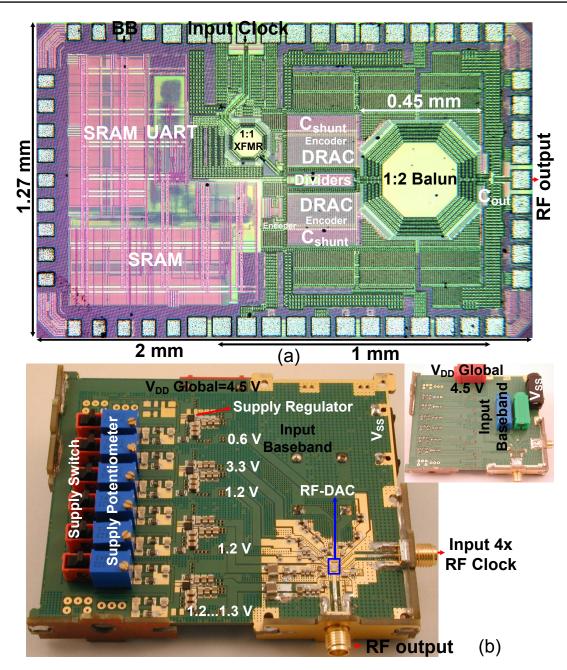

In Chapter 7, the implemented wideband,  $2 \times 13$ -bit I/Q RF-DAC-based all-digital modulator realized in 65-nm CMOS is presented. The 12-bit DRAC is implemented by employing the segmentation approach which consists of 256 MSB bits and 16 LSB thermometer unit cells. The layout arrangement of the DRAC unit cell proves to be very crucial. The LO leakage and I/Q image rejection technique as well as two DPD memoryless techniques of AM-AM/AM-PM and constellation mapping are introduced which will be employed extensively during the measurement process.

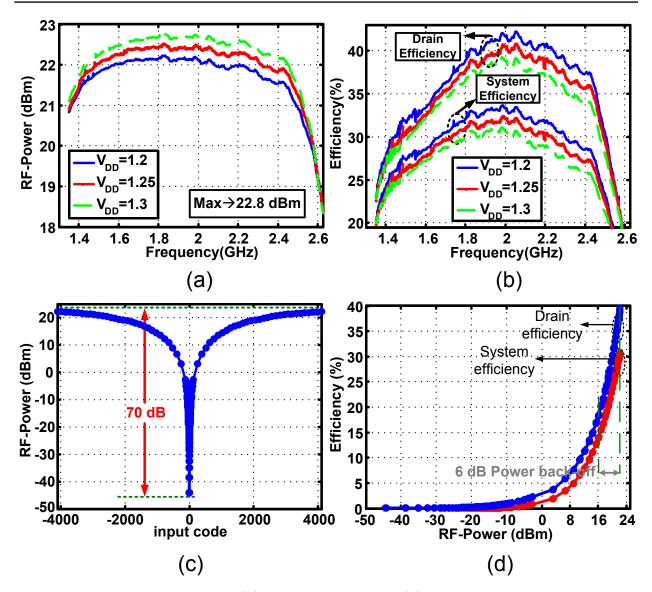

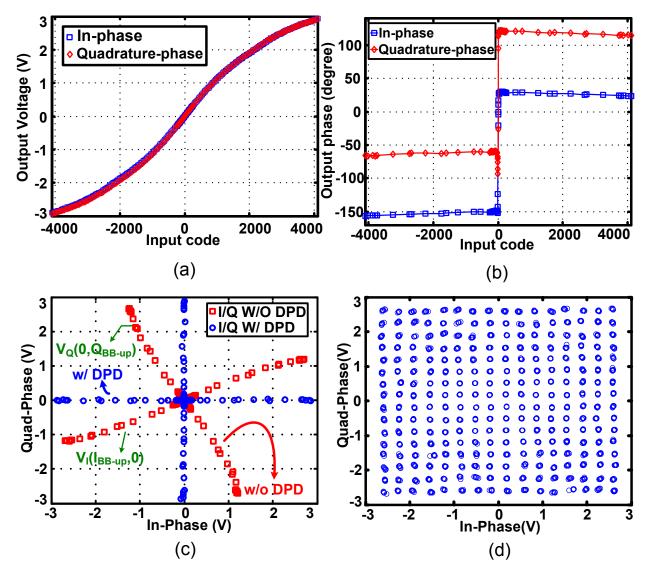

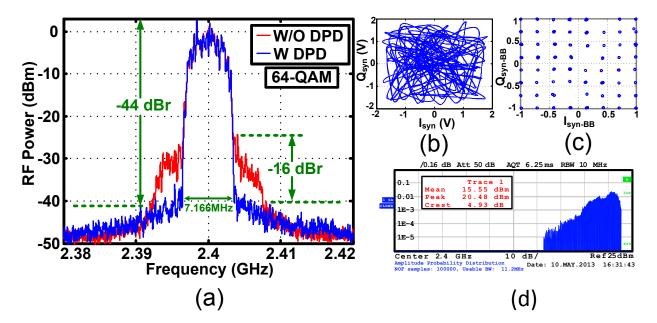

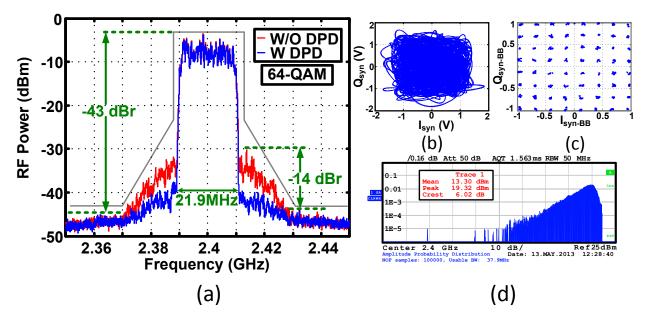

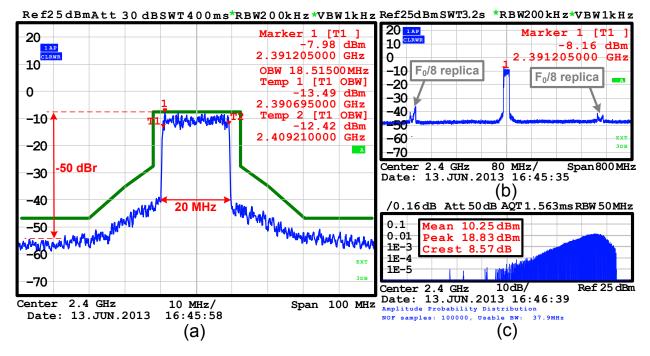

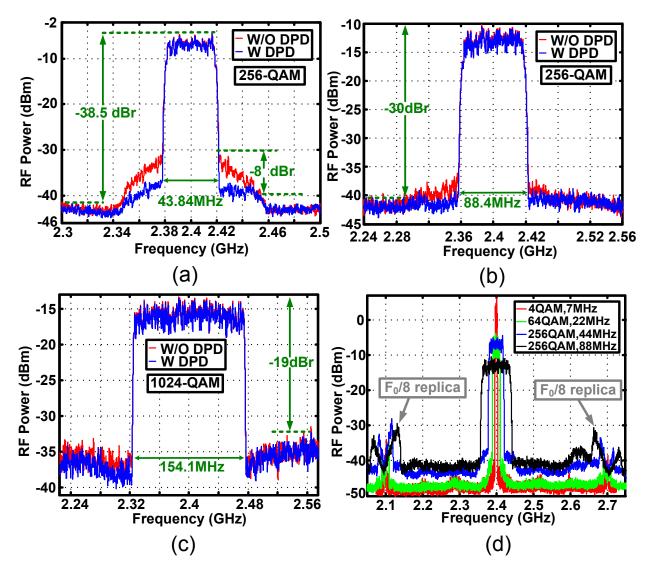

In Chapter 8, the high-resolution wideband  $2 \times 13$ -bit all-digital I/Q transmitter will be measured. First, the chip is tested in continuous-wave mode operation. The RF-DAC chip generates more than 21 dBm RF output power within a frequency range of 1.36 to 2.51 GHz. The peak RF output power, overall system, and drain energy efficiencies of the modulator are 22.8 dBm, 34%, and 42%, respectively. The RF-DAC could be linearized using the DPD lookup table. Its linearity is examined using single-carrier 4/16/64/256/1024-QAM as well as multi-carrier 256-QAM OFDM baseband signals while their related modulation bandwidth is as high as 154 MHz. Moreover, the constellation-mapping DPD is applied to the RF-DAC thereby improving linearity by more than 19 dB.

In Chapter 9, the dissertation is concluded, and sensible suggestions are presented for future developments.

# Chapter 2

# Analog Versus Digital RF Transmitters

This chapter gives an overview of the various existing types of radio frequency integrated circuit transmitter (RFIC-TX) architectures that are required to determine their advantages and disadvantages in order to develop an innovative approach to devise a fully integrated all-digital RF transmitter. Though this has already been explained in many ways in existing literature [24–26], it is still beneficial to reiterate their distinctions. Section 2.1 discusses analog-intensive Cartesian as well as polar RF transmitters. In Section 2.2, the need for digital-intensive RF transmitters is examined. Section 2.3 explains the new paradigm of RF transmitter design utilizing the nano-scale CMOS process technology. In Section 2.4, an all-digital polar transmitter is explored while Section 2.5 unveils all-digital Cartesian transmitters. Finally, the conclusion of the chapter is drawn in Section 2.6.

# 2.1 Analog-Intensive RF Transmitters

Beginning around the 1990s, virtually all RFIC-TXs have been analog intensive and based on an architecture similar to that depicted in Fig. 2.1. At the transmitter back-end, the baseband user information symbols become pulse-shaped to obtain two orthogonal components of complex-number digital samples, i.e., in-phase (I) and quadrature-phase (Q) that are constrained to the allocated frequency channel.

They are then converted into an analog continuous-time domain through a DAC with a typical zero-order-hold (ZOH) function. The LPF following the DAC subsequently filters out the switching harmonics. Thus obtained analog baseband signal is then upconverted (frequency translated) into RF through a quadrature modulator. The resulting (typically external) PA increases the RF power level at the antenna to that of what is required by

Figure 2.1: Traditional analog-intensive Cartesian (I/Q) RF transmitter.

the wireless standard, which could be as high as 2W for a GSM handset. The frequency synthesizer-based LO performs the frequency translation. It is typically realized as a chargepump phase-locked loop (PLL) with  $\Sigma\Delta$  dithering of the divider modulus to realize the fractional-N frequency division ratio. The complete architecture and monolithic circuit design techniques of the conventional transmitter exhibited in Fig. 2.1 have been described extensively in an innumerable amount of literature, particularly in the latest editions of text books [24, 25]. These architectures have been successfully employed in integrated CMOS transmitters [27–34] for over a decade (since the late 1990s). Unfortunately, their beneficial lifetime is gradually coming to an end [35] to make room for analog polar and more digitallyintensive architectures. In summary, due to linear summation of I and Q signal paths, this architecture can manage large modulation bandwidth. On the other hand, it comprises power-hungry as well as bulky components which make this transmitter deficient.

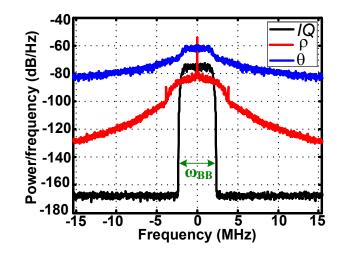

An alternative to the I/Q topology of Fig. 2.1 is the polar realization exhibited in Fig. 2.2 in which the two uncorrelated, i.e., orthogonal, components (alternative to the I and Q components) are amplitude  $\rho$  and phase  $\theta$ :

$$\rho = \sqrt{I^2 + Q^2}

\theta = \tan^{-1}\left(\frac{Q}{I}\right)$$

(2.1)

The complex-envelope signal is  $S = \rho \exp(j\theta)$ . The phase modulation could be performed by a direct or indirect frequency modulation of a PLL. The amplitude modulation could be performed by a low drop-out (LDO) voltage regulator modulating the  $V_{DD}$  supply of a highefficiency switched-mode PA, such as a class-E PA. The analog polar TX architecture is a more recent development that addresses the inherent poor power efficiency and noise issues

Figure 2.2: Traditional analog-intensive polar RF transmitter.

Figure 2.3: Polar modulator bandwidth expansion of the WCDMA signal.

of the I/Q architecture. Notwithstanding these benefits, polar topologies exhibit certain serious disadvantages:

- 1. Their phase and amplitude paths exploit heterogeneous circuits whose delays must be accurately aligned to avoid spectral distortion at the final recombining stage, yielding spectral re-growth;

- 2. The required instantaneous bandwidth is significantly larger than in the I/Q approach. Otherwise stated, the composite modulator bandwidth is typically limited due to the bandwidth constrains in the practical DC-to-DC switchers or linear converters.

The latter aspect can be understood by examining the nonlinear operations that the amplitude  $\rho$  and phase  $\theta$  experience during conversion from the I/Q representation (2.1). The resulting signal bandwidth expansion can be observed in Fig. 2.3. This figure compares the baseband bandwidth ( $\omega_{BB}$ ) expansion of an example WCDMA I/Q modulator with its polar

counterpart. Note that the bandwidth expansion is due to the fact that  $\rho$  and  $\theta$  enhance the even  $(2\omega_{BB}, 4\omega_{BB}, 6\omega_{BB}, \ldots)$  and odd  $(3\omega_{BB}, 5\omega_{BB}, 7\omega_{BB}, \ldots)$  harmonics of baseband signal, respectively<sup>1</sup>.

Over the past several years, such analog-intensive polar transmitters (both small-signal, i.e., at the transceiver IC level, and large signal, i.e., encompassing PA) have been touted for their reconfigurability, implementational, and performance benefits more so than their traditional Cartesian counterparts that are based on an I/Q upconversion mixer. A number of recent publications have demonstrated their superiority with highly-integrated silicon realizations [36–42] but only for the *narrowband* (200 kHz allocated bandwidth) modulation standard, Enhanced Data rates for GSM Evolution (EDGE), of the 2G cellular. The polar architecture migration to *wideband* modulation standards, such as 3G (WCDMA – allocated bandwidth of 5 MHz), 4G (3GPP LTE, WiMAX – allocated bandwidth of up to 20 MHz), and other evolving wideband wireless standards (e.g., 802.11n/ac) continues to be a daunting task and, thus far, there has only been one very recent silicon demonstrator that produces low efficiency and low RF output power (3 dBm) discussed in the open literature [43]. The effort, however, appears to continue with another theoretical proposal of the polar topology for WCDMA [44] and one 90-nm CMOS demonstration of the RF front-end block components of the WCDMA digital polar transmitter [45].

# 2.2 Digitally-Intensive RF Transmitters

As mentioned above, the digital approach to design RF circuits and architectures is taking over in industry. The primary contributors to this sea-like transformation are the everimproving cost advantages and processing capabilities of the CMOS technology that have been occurring at regular intervals at the pace according to the so-called Moore's law. Basically, with every CMOS process technology advancement node (i.e., from 90-nm to 65-nm, then to 40-nm, and then to 28-nm, and so on) occurring every 18–24 months, the digital gate density, being a measure of the digital processing capability, doubles (i.e., gate area scaling factor of  $0.5\times$ ). Simultaneously, the basic gate delay, being a measure of the digital processing speed, improves linearly (i.e., gate delay scaling factor of  $0.7\times$ ). Likewise, the cost of fabricated silicon per unit area remains approximately the same at its high-volume production maturity stage. Indeed, over the last decade, the cost of silicon charged by IC fabs has remained constant. The main implication of this is that a cost of a given digital function, such as a GSM detector or a digital audio decoder, can be cut in half every 18-24 months when transitioned to an upgraded CMOS technology. At the same time, the circuits consume proportionately less power and are faster [26].

<sup>&</sup>lt;sup>1</sup>Note that according to eq. (2.1) the envelope signal is an even function (square function) which entails the bandwidth expansion due to even harmonics. On the other hand, the phase signal is an odd function (arctangent function) which causes the bandwidth expansion because of odd harmonics.

#### 2.3 New Paradigm of RF Design in Nanometer-Scale CMOS 15

Unfortunately, these astonishing benefits of digital scaling are not shared by traditional RF circuits. Additionally, the strict application of the Fig. 2.1 and Fig. 2.2 architectures to the advanced CMOS process node might actually result in a larger silicon area, inadequate RF performance, and higher consumed power. The constant scaling of the CMOS technology has had an unfortunate effect on the linear capabilities of analog transistors. To maintain reliability of scaled-down MOS devices, the  $V_{DD}$  supply voltage continues to decrease, while the threshold voltage  $V_t$  remains almost constant (to maintain the low level of leakage current). This negatively affects the available voltage margin when the transistors are intended to operate as current sources. Moreover, the implant pockets that were added for the benefit of digital operation have drastically degraded the MOS channel dynamic resistance  $r_{ds}$ , thus severely reducing the quality of MOS current sources and the maximum available voltage self-gain

$$A_{v-intrinsic} = g_m \cdot r_{ds} \tag{2.2}$$

where  $g_m$  is the transconductance gain of a transistor. Furthermore, due to the thin gate dielectric becoming increasingly thinner, large high-density capacitors realized as MOS switches are becoming unacceptably leaky. This prevents an efficient implementation of low-frequency baseband filters and charge pump PLL loop filters.

# 2.3 New Paradigm of RF Design in Nanometer-Scale CMOS

An early attempt at designing RF circuits in advanced CMOS has revealed a new paradigm:

In a deep-submicron CMOS process, time-domain resolution of a digital signal edge transition is superior to voltage resolution of analog signals [11].

On a pragmatic level, this indicates that a successful design approach in this environment would exploit this paradigm by emphasizing the following:

- 1. Fast switching characteristics or high  $f_T$  (20 ps and 250 GHz in 40-nm CMOS process, respectively) of MOS transistors: high-speed clocks and/or fine control of timing transitions;

- 2. High density of digital logic (1 Mgates/mm<sup>2</sup>) and also static random access memory (4 Mb/mm<sup>2</sup>) results in extremely inexpensive digital functions and assistant software;

- 3. Ultra-low equivalent power-dissipation capacitance  $C_{pd}$  of digital gates leading to both low switching power consumption

$$P_T = f \cdot C_{pd} \cdot V_{DD}^2 \tag{2.3}$$

as well as potentially low coupling power into sensitive analog blocks;

4. Small device geometries and precise device matching made possible by the fine lithography to create high-quality analog and RF data converters;

while avoiding the following:

- 1. Biasing currents that are commonly exploited in analog designs;

- 2. Reliance on voltage resolution with continuously decreasing supply voltages and increasing noise and interferer levels;

- 3. nonstandard devices that are not required for memory and digital circuits, which constitute the majority of the silicon die area.

Despite the early misconceptions that the digitalization of RF would somehow produce more phase noise, spurs, and distortion, the resulting digitally-intensive architecture is inclined to be, overall, more robust by actually producing lower phase noise and spurious degradation of the transmitter chain and a lower noise figure of the receiver chain in face of millions of active logic gates on the same silicon die, as repeatedly substantiated in subsequent publications [13,14,17,19,46–49]. Additionally, the new digital TX architecture would be highly reconfigurable with analog blocks that are controlled by software to guarantee the best achievable performance and parametric yield. An additional benefit would be an effortless migration from one process node to the next without significant modifications.

### 2.4 All-Digital Polar Transmitter

A transmitter architecture that is amenable to the digital nanoscale CMOS technology is depicted in Fig. 2.4 [13,14]. This digital polar transmitter has found its way into commercial products. Note that, this digital-to-RF architectural transformation is influenced by the ever-improving cost advantages and process capabilities of CMOS technology, and various successful implementations have been brought to fruition, e.g., [14]. The work of Chowdhury *et al.* [19] and, most recently, Lu *et al.* [21, 49] proposed wideband polar modulators, which achieve high output power and high efficiency.

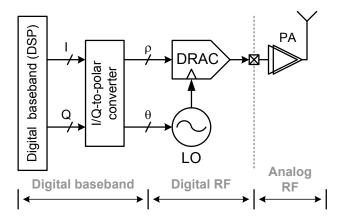

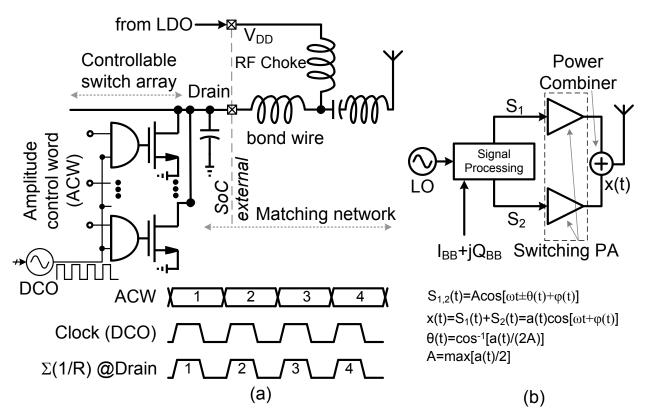

The LO in Fig. 2.4 is realized as an all-digital PLL (ADPLL) that produces a phase or frequency modulated digital clock carrier employing the two-point digital modulation scheme. The clock is fed into a digital-to-RF-amplitude converter (DRAC) that produces an RF output of which the envelope is substantially proportional to the amplitude control word (ACW) or  $\rho$ . Hence, the architecture is termed as a digital polar TX.

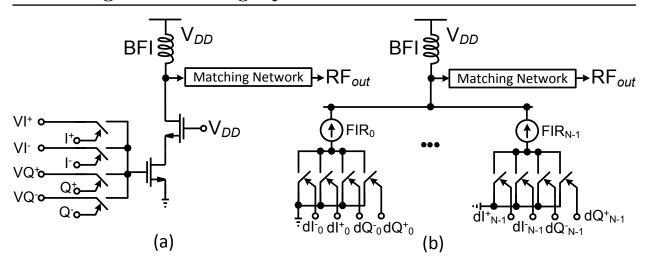

The DRAC is realized as an all-digital RF power generation circuit as illustrated in Fig. 2.5(a) [50]. It is also referred to as a digitally controlled power amplifier (DPA). Note that compared to the traditional power amplifier which amplifies the analog/RF input signal,

Figure 2.4: All-digital polar transmitter.

in this context, the input signal of the DPA is an internal digital clock, therefore, measuring the *amplification* gain of the DPA seems a bit problematic. The DRAC has proven its exploitation by the amplitude modulation in more advanced modulation schemes, such as the extended data rate (EDR) mode of Bluetooth, EDGE and WCDMA.

The DRAC operates as a near-class-E RF PA and is driven by the square wave output of a digitally-controlled oscillator (DCO) in the ADPLL. The rise-/fall-time of digital signals, including clocks, is typically 40–60 ps in 65 nm low-power CMOS process, which makes the trapezoidal shape almost square for cellular band signals. A large number of core NMOS transistors are employed as on/off switches, each with a certain conductance 1/R, and are followed by a matching network that interfaces with an antenna or an external PA. The number of active switches, and thus the total conductance  $\sum(1/R)$ , is digitally controlled and establishes the instantaneous amplitude of the output RF envelope. The RF output power is incited by coherently moving the resonating energy through the LC tank between the load and the switches. The supply  $V_{DD}$  replenishes the energy lost to the load and internally. The RF amplitude is contingent upon the relationship between the total switch conductance and the conductance of the matching network.

The class-E PA operation is attempted in order to achieve the maximum output power (all the switches are active), where the highest achievable efficiency is of the utmost importance. Note that there could be different methods of conversions from digital to RF amplitude as well as classes of operation. For example, class-D PA [18,52] would utilize two switching devices operating complementary and connected to the supply/ground and the matching network. Fine amplitude resolution is achieved through high-speed  $\Sigma\Delta$  transistor switch dithering. The timing diagram of Fig. 2.5(a) [50] assumes that the data changes with every RF clock cycle, which is reasonable considering the high-speed dithering. In practice, the integer ACW signals would change every certain number of DCO cycles. Despite the high speed of digital logic operation, the overall power consumption of the transmitter architecture is reasonably low.

As previously indicated, the significant advantage of the polar architecture is its high

Figure 2.5: (a) DRAC in digital polar TX [50]. (b) Digital outphasing TX [51].

power efficiency. However, due to the nonlinear signal processing, there is a significant bandwidth expansion that makes it unusable for very wideband signals. This has prompted researchers to consider alternative architectures. The outphasing architecture [53], which avoids the amplitude modulation at the component level, is not only highly efficient at maximum RF output power, but also efficiently operates at back-off power levels. Moreover, a few research groups have recently demonstrated various digital implementations [51,54–56]. Depicted in Fig. 2.5(b), the digital transmitter in [51] produces 26 dBm peak RF power while its drain efficiency is 35 %. However, the outphasing architecture still experiences bandwidth expansion issues due to the nonlinear signal transformation which might limit its usefulness for very wideband signals.

# 2.5 All-Digital I/Q Transmitter

As mentioned in 2.1, due to the bandwidth expansion of  $\rho$  and  $\theta$ , which could be as much as  $10 \times$  the original I/Q signal bandwidth, it might be problematic to apply the digital polar TX architecture to the wideband modulation, especially the most recent 3GPP LTE cellular and 802.11.n/ac wireless connectivity standards. The required bandwidths would exploit approximately hundreds of MHz. Even though [17] introduced a wideband digital polar PA,

Figure 2.6: Digital I/Q TX.

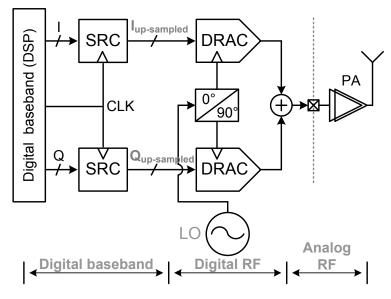

the efficiency was inadequate. In addition, [19, 48, 49] proposed wideband polar modulators, which achieve high output power and high efficiency. Nonetheless, they require a complicated baseband processing of  $\rho$  and  $\theta$  signals. Consequently, the digitally intensive I/Q architecture has been introduced [16, 57–66] to maintain the digital RF approach while addressing the bandwidth expansion issue of the polar topology. A typical architecture is illustrated in Fig. 2.6. Compared to Fig. 2.1, a new optional circuit, sample-rate converter (SRC), is included to convert the lower-rate baseband I/Q signal (processed at integer multiple of the symbol rate) into a much higher rate that is necessary to spread the quantization noise, thus lowering its spectral density. Note that this optional SRC circuit could also be incorporated in the digital polar TX of Fig. 2.4 as a component of the I/Q-to-polar converter.

The operation of the digital I/Q modulator is as follows. The I and Q digital samples drive their respected DRAC converters that produce two RF signal components in which their amplitudes are ideally proportional to the respective I/Q digital inputs. The two amplitude-modulated RF components are subsequently combined to produce the desired composite RF output. The output is then either directly transmitted to the antenna or through a high-performance power amplifier. Note that, the phase of the subsequent RF signal is implicitly the result of the arctangent function of "DRAC Q RF output voltage" to "DRAC I RF output voltage". This is due to the fact that the phase of the DRAC Q output is 90° delayed with respect to that of the I output.

This digital I/Q architecture does not appear to compare favorably with the polar topology of Fig. 2.4. The digital I/Q architecture seems increasingly complex with extra circuitry contributing noise and creating signal distortion. The frequency modulation of the LO in Fig. 2.6 could be satisfactorily accomplished through the familiar two-point modulation scheme of the ADPLL. The phase component is thus under the closed-loop feedback, which reduces the noise and distortion content falling within the ADPLL loop bandwidth. Closing the loop around the I/Q modulator RF output is typically much more difficult. The traditional issues of the timing misalignment in the analog polar architecture is no longer an issue with the digital approach. The digital discrete-time operation is, by construct, clock-cycle accurate while the modern technology can clearly support sampling rates even at the GHz range, as well as ultra-fast settling of the DPA conversion circuits (with the speed governed by  $f_T$ ). Consequently, the circuits of digital architectures can ensure fine time accuracy which is constant and not subject to processes and environmental changes. The DRAC could be implemented as a digitally-controlled RF-modulated current source [16, 58]. In this manner, the addition of the two DRAC output components could be as uncomplicated as connecting them electrically. For the I/Q signal orthogonality to maintain, these two current sources must be ideal such that one signal path output does not influence the operation of the other. This indicates the need to resort to current source impedance boost techniques, such as cascoding. Unfortunately, stacking of the MOS transistors in a cascode structure as a current source is difficult in the modern low-voltage technologies and further produces an excessive amount of leakage and noise. In order to mitigate the aforementioned issues, consequently, there is a need for a digital TX architecture that is capable of supporting advanced wideband wireless modulation standards but which also avoids the intrinsic bandwidth expansion issues of the polar topology and the severe noise issues of the conventional digital I/Q architectures.

#### 2.6 Conclusion

Four types of RF transmitter architectures are briefly described. The analog I/Q modulators are the most straightforward and widely employed RF transmitters. They are later replaced by analog polar counterparts to address their poor power efficiency and noise performance. On the other hand, in the analog polar RF transmitters, their related amplitude and phase signals must be aligned or spectral regrowth is inevitable. Utilizing digital intensive polar RF transmitters mitigates the latter alignment issue. Nonetheless, polar transmitters suffer from an additional issue that is related to their nonlinear conversion of in-phase and quadrature-phase signals into the amplitude and phase representation. Therefore, the polar RF transmitters are not able to manage very large baseband bandwidth of the most stringent communication standards, therefore, reusing I/Q modulators based on digitally intensive implementation appears to be a reasonable approach to resolve this issue. The digital I/Q RF transmitters, however, suffer again from inadequate power efficiency. Moreover, the combination of in-phase and quadrature-phase paths must be orthogonal to produce an undistorted-upconverted-modulated RF signal. In Chapter 3, a novel digital I/Q modulator that alleviates those extreme issues will be uncovered.

# Chapter 3

# Idea of All-Digital I/Q Modulator

As discussed in the preceding chapters, for wide modulation bandwidths, due to their direct linear summation of the I and Q signals and thus the avoidance of the bandwidth expansion, Cartesian [16,57–66] modulators are prove to be a better choice than their polar [13,14,17,19, 46–49] or outphasing [51,54–56] counterparts. Reference [16] proposed a digitally controlled I/Q modulator that utilizes current sources to isolate the orthogonal I and Q paths. The exploitation of the current sources, however, worsens the far-out noise. Additionally, in order to produce the required RF output power, that approach employs an external power amplifier. Later, an I/Q direct digital RF modulator is introduced in [63] in which an FIRbased quantization noise filter is embedded in order to filter the quantization noise in the receiver frequency band. Implemented in 130 nm CMOS, it also employed numerous current sources to isolate the orthogonal paths as well as to establish the proper coefficient value for the FIR filtering operation. However, its drain efficiency, at 15.4 dBm output power, does not exceed 13%. Moreover, the related noise floor is not better than -152 dBc/Hz at 20 MHz offset. To alleviate the foregoing concerns, a novel digital I/Q modulator concept is introduced. Section 3.1 explains the principal concept behind the proposed digital I/Qmodulator. Section 3.2 discusses the various types of orthogonal summing in digital intensive or all-digital I/Q transmitters. Finally, Section 3.3 summarizes this chapter.

## 3.1 Concept of Digital I/Q Transmitter

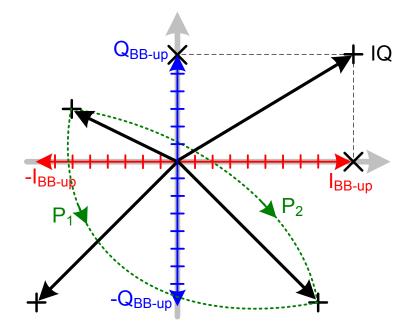

Fig. 3.1 illustrates the concept of the digital I/Q modulator. The desired I/Q vector (IQ) is constructed by vectorial summing of their composite I and Q digital vectors. Their code resolution  $(N_b)$  must be high enough to cover all I/Q points of the corresponding trajectory

Figure 3.1: Digital I/Q modulation concept; Its related IQ constellation vectors.

connecting the symbols [22].

This indicates that, for supporting only an m-symbol constellation diagram, the resolution of the digital I/Q modulator should be at least<sup>1</sup>

$$N_b \ge \log_2(\sqrt{\frac{m}{4}}) \tag{3.1}$$

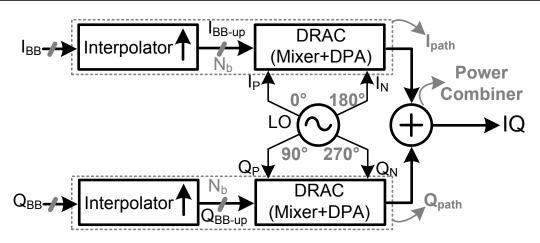

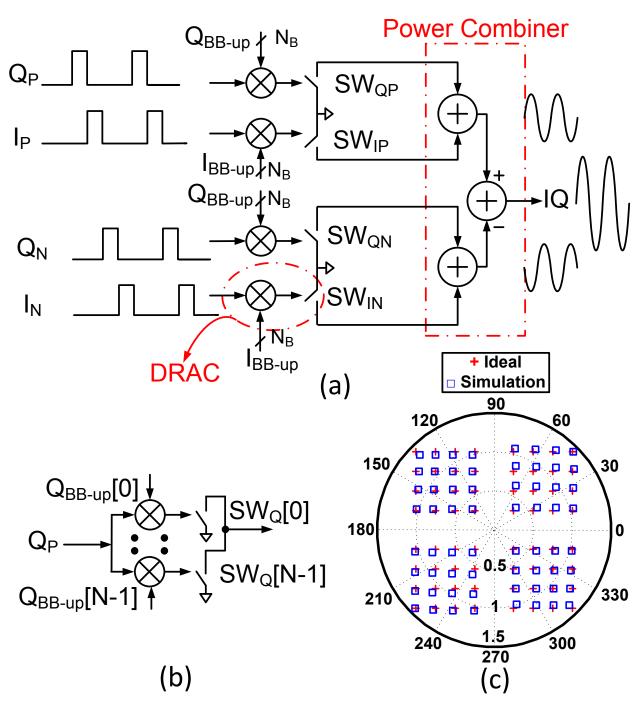

In addition,  $N_b$  also affects the subsequent quantization noise, which is discussed in more detail in the following chapters. A significant issue related to any transmit modulator is its agility to traverse from one I/Q point to another. As graphically depicted in Fig. 3.1 by  $P_1$  and  $P_2$  paths, traversing along  $P_2$  trajectory instead of  $P_1$  makes the complex baseband modulation faster and, consequently, the modulator must manage a wider bandwidth as well as a higher sampling rate. To do so, based on the idealized block diagram in Fig. 3.2, the  $I_{BB}$  and  $Q_{BB}$  digital baseband signals are upsampled as interpolated  $I_{BB}$  ( $I_{BB-up}$ ) and interpolated  $Q_{BB}$  ( $Q_{BB-up}$ ). This process ensures that the spectral images will be attenuated and located far away from the carrier and thus can easily be filtered out. The  $I_{BB-up}$  and  $Q_{BB-up}$  are  $2 \times N_b$ -bit ( $N_b$  for in-phase as well as  $N_b$  for quadrature component) upsampled digital signals, which should be directly upconverted to their continuous-time reconstructed RF output signal. As a result, these signals are applied to a pair of DRACs, comprising an array of 1-bit unit cell mixers and 1-bit unit cell DPAs.

The DRACs are clocked in tact of differential quadrature upconverting clocks  $I_P$ ,  $I_N$ ,  $Q_P$ , and  $Q_N^2$ . According to Fig. 3.1, the four quadrants of the constellation diagram must be

<sup>&</sup>lt;sup>1</sup>Of course, the resolution based on eq. (3.1) is not enough to support corresponding IQ trajectories.

Figure 3.2: Digital I/Q modulation concept; Its related idealized block diagram.

addressed by the modulator. The switching between quadrants can be achieved by swapping between  $I_P/I_N$  or/and between  $Q_P/Q_N$  according to the sign bits of  $I_{BB-up}$  and  $Q_{BB-up}$ . The DRAC outputs are connected to a power combiner that facilitates the conversion of the upconverted digital signals into the reconstructed RF output. In fact, the digital I/Q modulator represents an RF digital-to-analog converter (RF-DAC). In this approach, however, the primary challenge is related to the orthogonal summing of the I and Q DRAC outputs in order to reliably reconstruct the modulated RF signal [26, 67–69].

#### 3.2 Orthogonal Summing Operation of RF-DAC

From the digital communications theory, in order to maintain high bandwidth efficiency, the baseband information is generally represented by two orthogonal streams, i.e., I and Q signals, each modulated by the corresponding orthogonal carrier signal (i.e., basis function), and they are subsequently summed. Based on that, the I/Q RF-DAC of Fig. 3.2 has two signal paths, namely, the in-phase path  $(I_{path})$  and the quadrature-phase path  $(Q_{path})$ performing the following operations:

$$I_{path}(t) = (I_P(t) - I_N(t)) \times I_{BB-up}(t) = 2 \times I_P(t) \times I_{BB-up}(t)$$

(3.2)

$$Q_{path}(t) = (Q_P(t) - Q_N(t)) \times Q_{BB-up}(t) = 2 \times Q_P(t) \times Q_{BB-up}(t)$$

(3.3)

The final modulated IQ signal is generated by vectorial summation of (3.2) and (3.3) and mathematically expressed as:

<sup>&</sup>lt;sup>2</sup>These clocks comprise four phases separated by  $90^{\circ}$

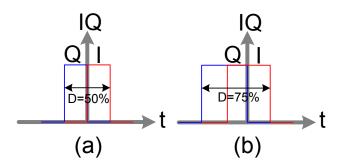

Figure 3.3: Conceptual diagram of I/Q signals: (a) D = 50%; (b) D = 25%.

$$IQ(t) = I_{path}(t) + Q_{path}(t)$$

= 2 × {I<sub>P</sub>(t) × I<sub>BB-up</sub>(t) + Q<sub>P</sub>(t) × Q<sub>BB-up</sub>(t)} (3.4)

The transmitted RF signal is a band-pass filtered version of IQ(t).

$$RF_{out}(t) = \text{filter}\left[IQ(t)\right] \tag{3.5}$$

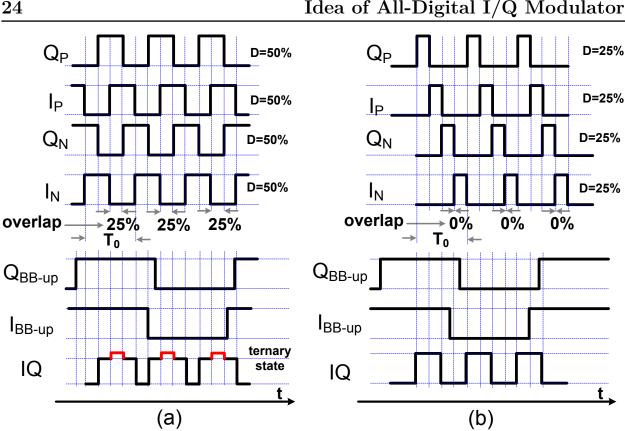

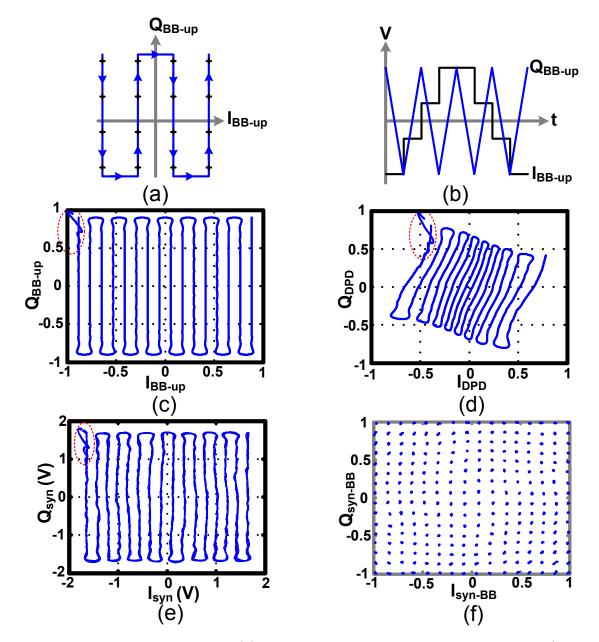

Equation (3.4) reveals two aspects of the quadrature modulation: orthogonality and summation. The summing operation must be orthogonal, and there should be no interaction or correlation between  $I_{path}$  and  $Q_{path}$ , or the EVM, bit error rate (BER) and spectral regrowth will arise. The digital carrier signals are typically rectangular pulses with a 50%duty cycle (D) that toggle between ground and supply. If duty cycle of the upconverted clock is 50% [66], there invariably exists an overlap between  $I_P/I_N$  and  $Q_P/Q_N$ . Mathematically, their orthogonality can be verified by employing a dot product operation. Fig. 3.3(a) is a conceptual illustration of the carrier signals. Based on mathematical principles, two signals are orthogonal with respect to each other if an integral of their inner product over the interval of one period is zero. The orthogonality of the carrier signals (D=50%) is examined

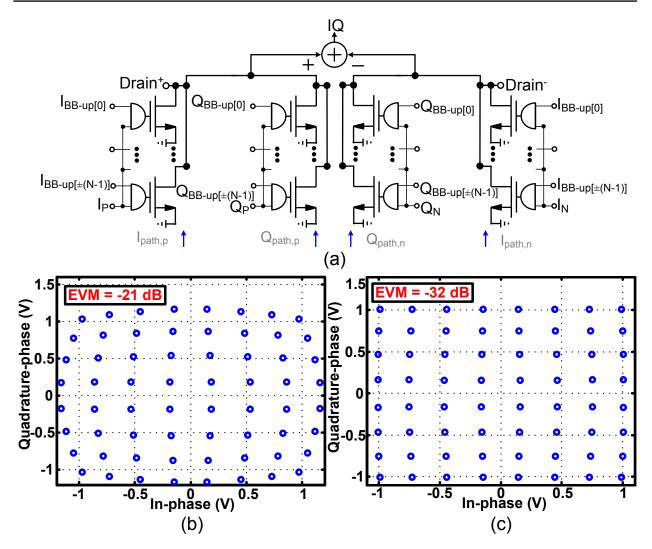

Figure 3.4: (a) Idealized schematic of digital I/Q modulator; Its related SPICE simulated constellation diagrams for (d) D=50%; (c) D=25%.

as follows:

$$\frac{1}{T_0} \int_0^{T_0} \left[ (I_P - I_N) \cdot (Q_P - Q_N) \right] = 0.25 \tag{3.6}$$

where  $T_0$  is the clock period, and the clocks are assumed of unity amplitude. Based on (3.6) the carrier signals,  $I_P/I_N$  and  $Q_P/Q_N$ , are not orthogonal. Fig. 3.3(a) intuitively confirms (3.6) and clearly demonstrates that, when  $I_P$  and  $Q_P$  are both simultaneously one, provided that  $I_{BB-up}$  and  $Q_{BB-up}$  are also one, then the resulting IQ signal of a practical circuit implementation exhibits a third state. This signifies that the  $I_{path}$  and  $Q_{path}$  are correlated, and the receiver cannot determine the component to which this unsolicited state belongs. Let's consider an idealized digital I/Q modulator depicted in Fig. 3.4. Employing the D=50% clocks, the foregoing circuit is simulated. According to its SPICE simulated

Figure 3.5: Illustration of full power combining of  $I_{path}$  and  $Q_{path}$  employing upconverting clock for (a) D=25%; (b) D=50%.

Table 3.1: Comparison between  $1^{st}$ ,  $2^{nd}$ , and  $3^{rd}$  harmonic components: D=50%; D=75%.

| IQ Duty Cycle | Fundamental (dB) | Second (dB) | Third (dB) |

|---------------|------------------|-------------|------------|

| 50%           | -2.34            | -327        | -11.88     |

| 75%           | -5.35            | -8.36       | -14.89     |

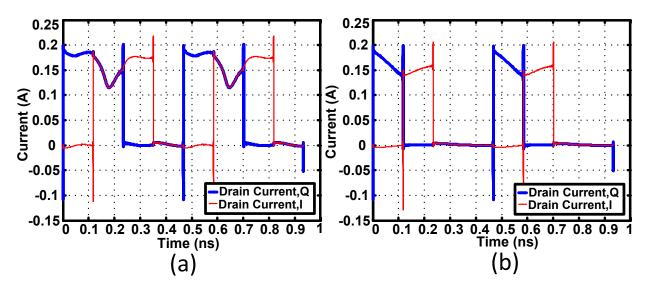

constellation diagram of Fig. 3.4(b), its related EVM at 16 dBm RF output power is -21 dB. Hence, to improve linearity, a sophisticated digital predistortion (DPD) algorithm would be required [66]. In addition, the drain efficiency of its composite DPA is deficient due to the fact that the maximum conduction angle is 75% of the RF clock cycle.

To make the carrier signals orthogonal, their overlapping part should be eliminated. As a result, to perform orthogonal summation, the duty cycle of upconverting clocks is selected at 25% to deter any interaction between the  $I_{path}$  and  $Q_{path}$ . Based on Fig. 3.3(b), the overlap between  $I_P/I_N$  and  $Q_P/Q_N$  is now zero and the resultant IQ signal comprises only two states. The orthogonality of the new carrier signals can be expressed as:

$$\frac{1}{T_0} \int_0^{T_0} \left[ (I_P - I_N) \cdot (Q_P - Q_N) \right] = 0 \tag{3.7}$$

Thus, this also mathematically confirms the orthogonality of the component carriers. The solution could be considered as a TDD in which the linear addition of the time-shifted I and Q paths is accomplished by allocating individual time slots to enter the I/Q information into the system. Employing the aforementioned D=25% upconverting clocks of the digital I/Q modulator of Fig. 3.4(a), the circuit level simulated constellation diagram of Fig. 3.4(c) is achieved. Its corresponding EVM at 16 dBm RF output power is -32 dB. As a result, this system only needs a very simple DPD [70,71] and, more significantly, the related drain efficiency of its composite DPA is higher due to the 50% maximum conduction angle. Note that, according to Fig. 3.4, the I/Q RF-DAC can cover the entire 4-quadrant constellation diagram.

It should be pointed out that, at the maximum power of operation, since both  $I_{path}$

Figure 3.6: Analog current source arrays summing.

and  $Q_{path}$  are activated, the subsequent drain voltage waveform is a square-shaped signal with D=50% providing that the duty cycle of their related upconverting clocks is 25% (see Fig. 3.5(a)). In contrast, if the duty cycle of the upconverting clock is chosen at 50%, which is depicted in Fig. 3.5(b), their subsequent IQ signal is a square-shaped waveform with the duty cycle of 75%. Table 3.1 summarizes their corresponding fundamental, second, and third harmonic frequency components. According to it, the fundamental component of the 50% IQ waveform is  $\sqrt{2} \times$  higher than with the 75% one. Moreover, the 50% IQ waveform, ideally, creates a zero second harmonic frequency component which facilitates the design of the following transformer balun in the power combiner. On the other hand, the preceding clock generator circuits of the 50% duty cycle differential quadrature signals are less complicated than their 25% counterparts.

As stated earlier in (3.4), an additional aspect of the quadrature modulation is the summation. There would be at least four different ways of adding the orthogonal base function signals.

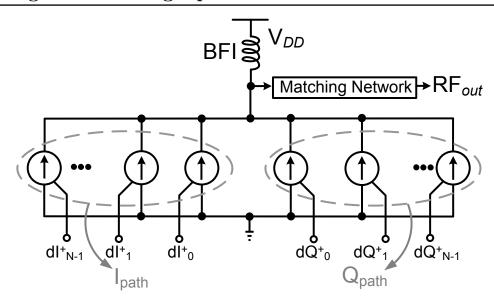

In the first approach [16, 58], as depicted in Fig. 3.6, the summation is performed by electrically connecting unit-weighted ideal current sources and adding them according to the input data. The controlling signals of the current sources are  $dI_{0,1,\dots,N-1}^+$  and  $dQ_{0,1,\dots,N-1}^+$  and are expressed as:

$$dI_{0,1,\dots,N-1}^{+} = I_P \times I_{0,1,\dots,N-1} \tag{3.8}$$

$$dQ_{0,1,\dots,N-1}^+ = Q_P \times Q_{0,1,\dots,N-1} \tag{3.9}$$

which indicates the implicit mixer operation. For maintaining the orthogonality of the I/Q

Figure 3.7: Two separate digital switch arrays using transformer summing.

signal, the  $I_{path}$  and  $Q_{path}$  must be uncorrelated such that one signal path output does not affect the operation of the other. This might require resorting to a current source impedance boost technique, such as cascoding. Unfortunately, stacking of the MOS transistors in a cascode structure is difficult in the modern low-voltage CMOS technologies and further produces an excessive amount of leakage and noise. In summary, numerous disadvantages exist related to this approach. First, this structure comprises MOS current sources which continuously work in the saturation region, therefore, create more noise than when operated in other regions. This structure is primarily implemented employing the Gilbert mixer topology. The thermal output spot noise of a Gilbert cell mixer can be approximated as [60]:

$$\overline{V_{out-n}^2} = 4KT\gamma \frac{G^2}{g_m} + KT\pi \frac{G}{g_m}$$

(3.10)

where  $K=1.38\times10^{-23}$  J/K denotes the Boltzmann constant, T is the absolute temperature, the parameter  $\gamma$  has a value of 2/3 in saturation region for long channel devices,  $g_m$  is the device transconductance, and  $G \propto g_m R_{out}$  is the voltage gain of the Gilbert mixer ( $R_{out}$ is the equivalent mixer output resistance). Since the gain of the mixer is constant due to linearity constrain, in order to reduce the noise,  $g_m$  should be increased. Thus, as a second disadvantage, the power efficiency of this approach is minimal, as is apparent in [16, 58]. Third, the linearity of this structure is not promising due to the voltage to current conversion in the Gilbert cell.

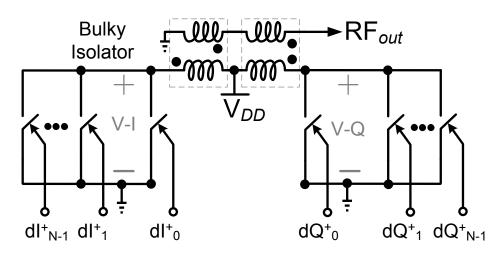

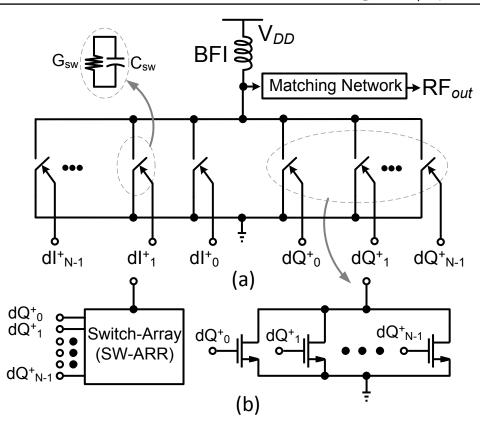

The second approach illustrated in Fig. 3.7 might also be realized as a pair of digitallycontrolled RF-modulated resistor structures. This approach could benefit from a less complicated circuit, the lack of stacked devices, and the elimination of noisy current sources. Since the MOS switch operates either in the off or in triode state, less noise is introduced. In addition, because of the switched-mode behavior, it has a potential to produce higher power efficiency [50]. Unfortunately, the final I/Q signal summation is difficult to accomplish in

Figure 3.8: (a) Quadrature passive upconverting mixer using 25% duty cycle upconverting clock. (b) Analog current source FIR arrays summing.

this method since the individual I and Q outputs are not currents but, instead, voltages. Due to the fact that the individual voltages of the RF outputs of the matching networks must be included, bulky microwave-type isolator/combiner would be required, otherwise, the RF voltage level of the  $I_{path}$  will affect the impedance of the  $Q_{path}$ , and vice versa. Hence, the I/Q orthogonality of this structure will not be preserved.

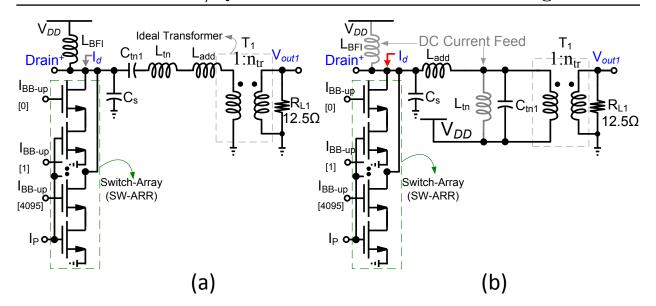

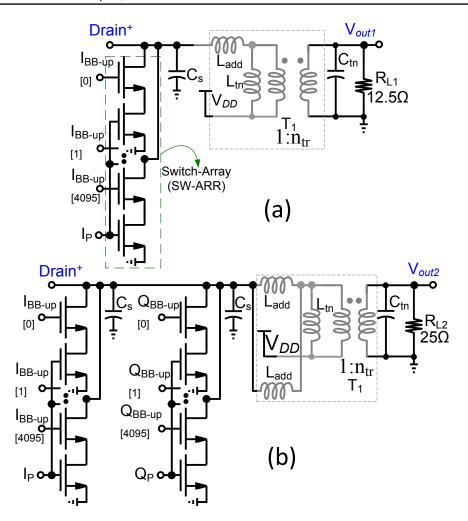

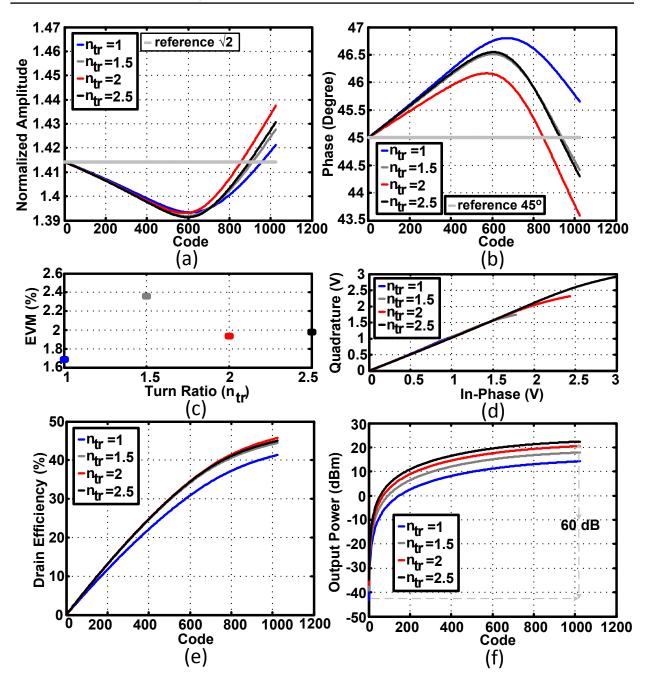

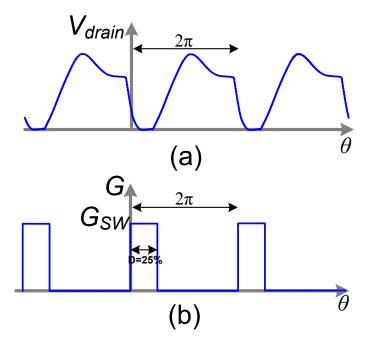

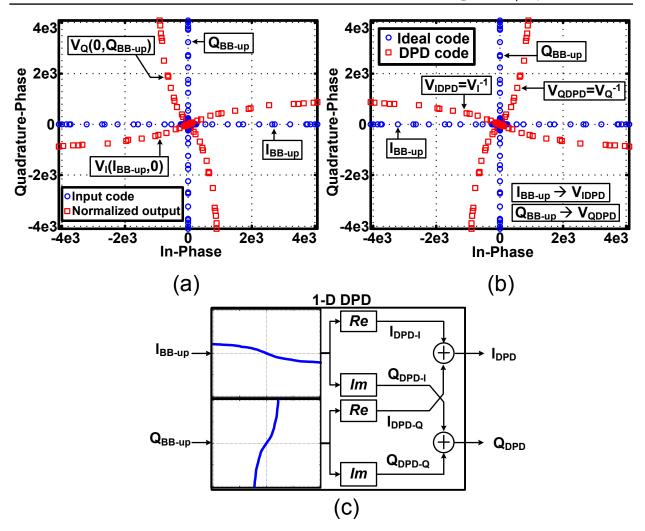

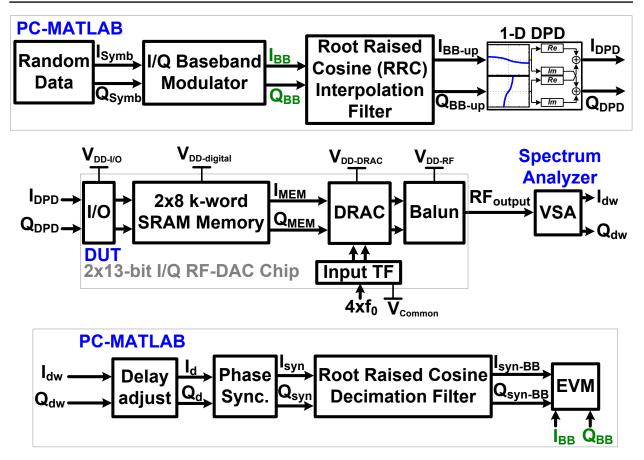

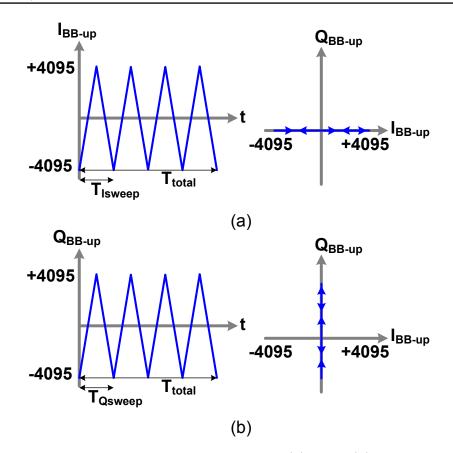

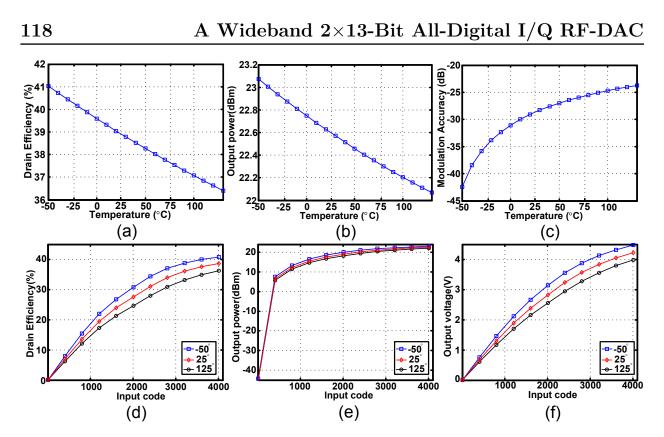

The third approach is based on employing the quadrature passive mixer which utilizes 25% duty cycle upconverting clock which is depicted in Fig. 3.8(a) [60, 61]. Note that, in this approach, the baseband input signals are converted to analog continuous-time waveforms exploiting two separate DACs and their following LPFs (see [60,61]). To boost the subsequent upconverted signals, however, this approach requires stand alone on-chip as well as off-chip power amplifiers. Thus, its power efficiency is deficient. Moreover, this approach is a digitally intensive approach rather than a fully digital approach. In order to transform it into a fully digital structure, the upsampled baseband signals are directly applied to passive mixer arrays [63]. In this approach, the in-phase and quadrature-phase signals are orthogonally summed employing analog current source cells which are depicted in Fig. 3.8(b). Note that the aforementioned current sources also provide the required FIR filter coefficient in order to notch the generated noise of the transmitter at the receiver frequency band. Implemented in a 130 nm CMOS process, this approach requires large voltage headroom due to adopting current sources. Moreover, this structure necessitates an additional power amplifier to increase the transmitted RF power thus its power efficiency is deficient.