## Energy Reduction Techniques for Caches and Multiprocessors

### Energy Reduction Techniques for Caches and Multiprocessors

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.dr.ir. J.T. Fokkema, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op 16 oktober 2009 om 12:30

door

Pepijn Jacob DE LANGEN

elektrotechisch ingenieur geboren te Groningen, Nederland Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. K.G.W. Goossens

#### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof. dr. K.G.W. Goossens, promotor

Dr. B.H.H. Juurlink, copromotor

Prof. dr. N.J. Dimopoulos

Prof. dr. K.G. Langendoen

Prof. dr. S.K. Nandy

Prof. dr. ir. H.J. Sips

Prof. dr. H.A.G. Wijshoff

Technische Universiteit Delft Technische Universiteit Delft

Technische Universiteit Delft

University of Victoria

Technische Universiteit Delft

Indian Institute of Science

Technische Universiteit Delft

Universiteit Leiden

ISBN: 978-90-72298-03-4

Keywords: Energy reduction, Caches, Multi processor scheduling

Cover design: Floris de Langen

Copyright © 2009 P.J. de Langen

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

Printed in the Netherlands

The research presented in this dissertation was partially funded by the Netherlands Organization for Scientific Research (NWO, The Hague, project no. 612-064-308).

Dedicated to Nicole and Tijmen, for all their love and support over the years.

## Energy Reduction Techniques for Caches and Multiprocessors

Pepijn de Langen

#### **Abstract**

Parchitecture. Not only for the handheld embedded market, but also for desktop machines and high-end server facilities, there is a demand for ever increasing processing power while maintaining or even decreasing energy consumption. For processors embedded in battery-powered devices, consumers both demand an increasing number of features and an increase of battery lifetime. For commodity desktop and high-end server systems, the demand to reduce energy consumption is mostly fueled by cost, environmental issues, and the wish to have systems without noisy cooling systems. This dissertation studies several techniques that aim at reducing energy consumption in processors.

Part of the techniques presented in this dissertation focusses at reducing energy consumption by decreasing the amount of data transferred between a processor and external memory. Since memory is one of the known bottlenecks in computer systems, manufacturers had to employ increasingly aggressive techniques in the past decades to increase performance. The techniques proposed in this dissertation target at improving or at least maintaining performance, while reducing the amount of energy dissipated in the memory subsystem.

Another part of this dissertation focusses on reducing energy by lowering the speed of nodes in multiprocessor systems in combination with turning off some of these nodes. Multiprocessor systems have gained significant interest in the past years, mostly because power constraints have prevented further increasing clock frequencies and because instruction level parallelism has suffered from diminishing returns. Due to the way how energy is dissipated in semiconductor fabric, using multiple cores on a reduced frequency is an effective way to reduce energy consumption. Due to decreasing sizes of the components from which processors are built, it is expected that this energy model will change significantly in future years. Some of the techniques presented in this dissertation aim at reducing energy consumption in such contemporary and near-future multiprocessor systems.

#### Acknowledgments

This dissertation is the result of over 4 years of work in the Computer Engineering laboratory of the Technical University in Delft. This work would not have been possible without the help and support of several people.

First of all, I would like to thank my adviser and copromotor Ben Juurlink, for providing the opportunity to perform my Ph.D. research and for the guidance throughout the years. His insightful comments have significantly contributed to this work.

I am very grateful for having known Professor Stamatis Vassiliadis, both in a professional and in a personal setting. Like for most people in the Computer Engineering group, Professor Vassiliadis was a huge source of inspiration. It was a great loss to everyone when he passed away on April 7<sup>th</sup> 2007. He was a passionate researcher and a great person. He will always remain in my heart and mind as 'my professor'.

I thank Professor Kees Goossens, who suddenly had to take up the role of promotor for me and many other Ph.D. candidates.

I would like to thank my first office mates, Dan and Gabi, who have helped me significantly getting started in the first months of my Ph.D. They both were valuable sources for getting quick answers to technical questions, but also great people for having endless discussions about non-technical issues.

I want to thank all my friendly colleagues in the Computer Engineering group. I have really enjoyed working with such a wide variety of inspiring people. I am especially thankful to my good friends Carlo and Lotfi, for all the lovely dinners, the interesting discussions, and especially for their support in the last years.

I also owe my thanks to Georgi Gaydadjev, for being both a good neighbor and a good friend. I thank Bert and Lidwina, for all their technical and administrative support.

I would like to thank my parents for all the love they have brought to my life,

and for always supporting my academic endeavors. I am grateful to Gillis, Floris, and Roderik, for the fact that we are not only brothers but also very good friends. In addition, I want to thank Floris for designing the cover of this dissertation.

Last but not least, I am in great debt to Nicole and Tijmen, the two most important people in my life. This work would not even have been remotely possible if it weren't for their love, support, and understanding throughout the years. Numerous evenings, weekends, and holidays were given up or reorganized to support my Ph.D.

Pepijn de Langen

Delft, the Netherlands, 2009

#### Contents

| Al | bstrac  | et            |             |           |        |  |  |  |  |  |  | i    |

|----|---------|---------------|-------------|-----------|--------|--|--|--|--|--|--|------|

| A  | cknov   | vledgme       | nts         |           |        |  |  |  |  |  |  | iii  |

| Li | st of l | Figures       |             |           |        |  |  |  |  |  |  | xii  |

| Li | st of ' | <b>Tables</b> |             |           |        |  |  |  |  |  |  | xiii |

| Li | st of   | Acronyı       | ıs          |           |        |  |  |  |  |  |  | xiv  |

| 1  | Intr    | oductio       | 1           |           |        |  |  |  |  |  |  | 1    |

|    | 1.1     | Motiva        | tion        |           |        |  |  |  |  |  |  | 1    |

|    | 1.2     | Power         | and Energy  | ·         |        |  |  |  |  |  |  | 3    |

|    | 1.3     | Challe        | nges        |           |        |  |  |  |  |  |  | 4    |

|    | 1.4     | Organ         | zation and  | Contribu  | itions |  |  |  |  |  |  | 6    |

| 2  | Red     | ucing C       | ache Confl  | ict Miss  | ses    |  |  |  |  |  |  | 9    |

|    | 2.1     | Introd        | ction       |           |        |  |  |  |  |  |  | 10   |

|    | 2.2     | Relate        | l Work      |           |        |  |  |  |  |  |  | 11   |

|    | 2.3     | Detect        | ng Conflict | Misses    |        |  |  |  |  |  |  | 13   |

|    | 2.4     | BCC a         | nd SCC Ca   | ches .    |        |  |  |  |  |  |  | 14   |

|    | 2.5     | Experi        | mental Resi | ults      |        |  |  |  |  |  |  | 16   |

|    |         | 2.5.1         | Experimen   | ıtal Setu | ıp     |  |  |  |  |  |  | 16   |

|    |         | 2.5.2         | Impact of   | the CDT   | ΓSize  |  |  |  |  |  |  | 17   |

|    |         | 2.5.3         | Traffic     |           |        |  |  |  |  |  |  | 18   |

|   |     | 2.5.4    | Energy Reduction                                 | 22 |

|---|-----|----------|--------------------------------------------------|----|

|   |     | 2.5.5    | Impact on Execution Time                         | 25 |

|   | 2.6 | Conclu   | asions                                           | 27 |

| 3 | Men | nory Co  | opies in Multi-Level Memory Systems              | 29 |

|   | 3.1 | Introd   | uction                                           | 29 |

|   | 3.2 | Relate   | d Work                                           | 31 |

|   | 3.3 | Memo     | ry Copies in Multi-Level Memory Systems          | 32 |

|   |     | 3.3.1    | Copying Using Copy Engines                       | 33 |

|   |     | 3.3.2    | Limitations of On-Chip Copy Engines              | 35 |

|   |     | 3.3.3    | Dynamic Copy Engines                             | 37 |

|   |     | 3.3.4    | Dynamic Copy Engine with Non-Temporal Fetching . | 42 |

|   | 3.4 | Experi   | mental Results                                   | 43 |

|   |     | 3.4.1    | Experimental Setup                               | 43 |

|   |     | 3.4.2    | Experiments with a Memcopy Micro-Benchmark       | 46 |

|   |     | 3.4.3    | Experiments with a TCP/IP Processing Benchmark   | 50 |

|   |     | 3.4.4    | Energy Reduction                                 | 53 |

|   | 3.5 | Conclu   | asions                                           | 53 |

| 4 | Lim | iting th | e Number of Dirty Cache Lines                    | 55 |

|   | 4.1 | Introd   | uction                                           | 56 |

|   | 4.2 | Relate   | d Work                                           | 59 |

|   | 4.3 | Clean/   | Dirty Cache                                      | 61 |

|   | 4.4 | Experi   | mental Results                                   | 63 |

|   |     | 4.4.1    | Experimental Setup                               | 63 |

|   |     | 4.4.2    | Experimental Results                             | 65 |

|   | 4.5 | Case S   | Study with Cache Decay                           | 69 |

|   |     | 4.5.1    | Cache Decay                                      | 69 |

|   |     | 4.5.2    | Cache Decay using the Clean/Dirty Cache          | 70 |

|   | 4.6 | Conclu   | asions                                           | 77 |

| 5 | Ene | rgy Effi | cient Multiprocessor Scheduling using DVS          | <b>79</b> |

|---|-----|----------|----------------------------------------------------|-----------|

|   | 5.1 | Introd   | uction                                             | 80        |

|   | 5.2 | Relate   | d Work                                             | 81        |

|   | 5.3 | Energ    | y Reduction using DVS                              | 83        |

|   |     | 5.3.1    | Dynamic Voltage Scaling                            | 83        |

|   |     | 5.3.2    | Voltage Scaling Requirements                       | 84        |

|   |     | 5.3.3    | Voltage Scaling in a Multiprocessor Environment    | 87        |

|   | 5.4 | Syster   | n and Application Model                            | 88        |

|   | 5.5 | Energ    | y Efficient Scheduling Algorithms                  | 90        |

|   |     | 5.5.1    | Schedule & Stretch                                 | 90        |

|   |     | 5.5.2    | Leakage Aware MultiProcessor Scheduling            | 92        |

|   | 5.6 | Exper    | imental Results                                    | 95        |

|   |     | 5.6.1    | Experimental Setup                                 | 95        |

|   |     | 5.6.2    | Experimental Results                               | 96        |

|   | 5.7 | Concl    | usions                                             | 101       |

| 6 | Ene | røv Effi | icient Multiprocessor Scheduling using DVS and DPM | 103       |

|   | 6.1 |          | uction                                             | 104       |

|   | 6.2 |          | d Work                                             | 105       |

|   | 6.3 |          | ninaries                                           | 106       |

|   |     | 6.3.1    | Power Model                                        | 106       |

|   |     | 6.3.2    | Effect of DVS for the Power Model                  | 109       |

|   |     | 6.3.3    | Processor Shutdown / DPM                           | 109       |

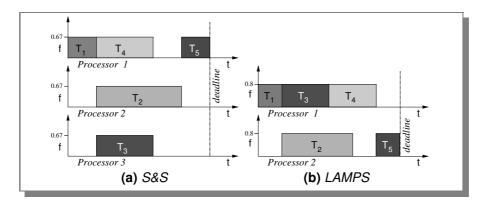

|   | 6.4 |          | processor Scheduling with DVS and DPM              |           |

|   |     | 6.4.1    | S&S+DPM and LAMPS+DPM                              |           |

|   |     | 6.4.2    |                                                    | 114       |

|   | 6.5 | Experi   | imental Results                                    | 115       |

|   |     | 6.5.1    | Experimental Setup                                 |           |

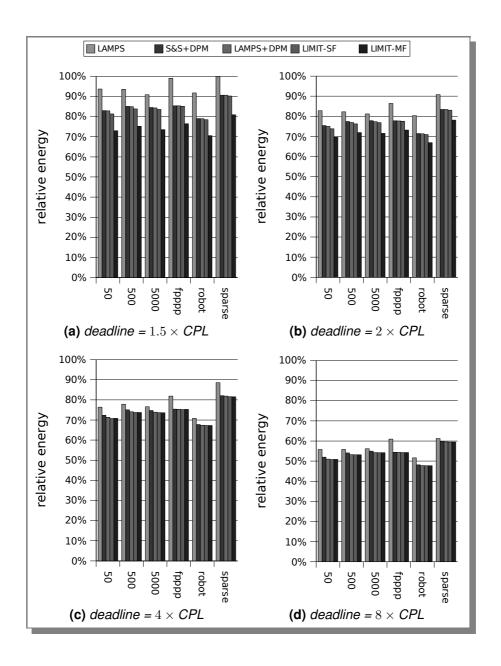

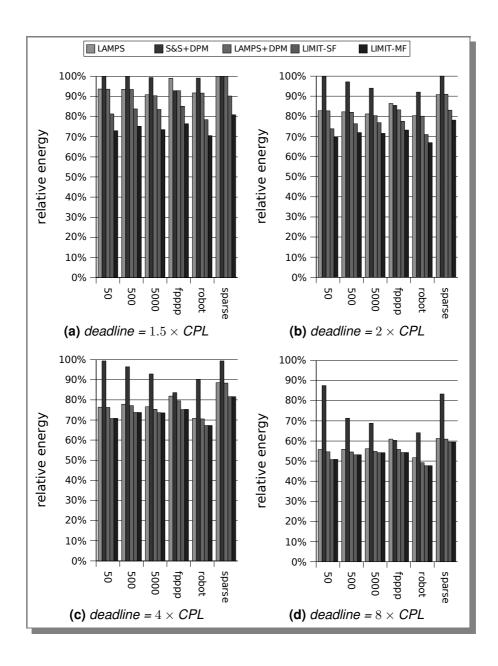

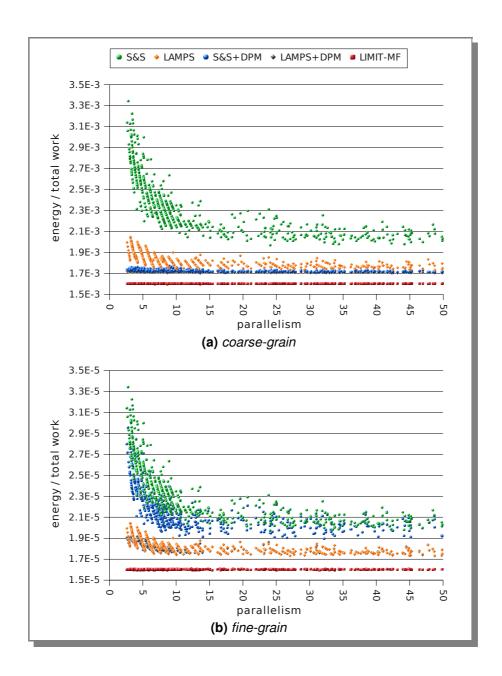

|   |     | 6.5.2    | Results for the Standard Task Graph Set            | 117       |

|   |     | 6.5.3    | Results for MPEG-1                                 |           |

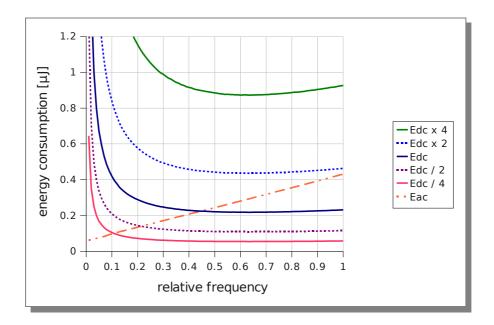

|   |     |          | Results for Different Levels of Static Power       |           |

|                      | 6.6           | Conclusions                         | 126 |  |  |

|----------------------|---------------|-------------------------------------|-----|--|--|

| 7                    | 7 Conclusions |                                     |     |  |  |

|                      | 7.1           | Summary and Contributions           | 132 |  |  |

|                      | 7.2           | Possible Directions for Future Work | 136 |  |  |

| Bi                   | Bibliography  |                                     |     |  |  |

| List of Publications |               |                                     |     |  |  |

| Samenvatting         |               |                                     |     |  |  |

| Cı                   | ırricu        | lum Vitae                           | 155 |  |  |

#### List of Figures

| 1.1  | ies versus the number of transistors in Intel microprocessors                                              | 2  |

|------|------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Total electricity use for servers in the world in 2000 and 2005, including cooling and auxiliary equipment | 3  |

| 2.1  | Conflict Detection Table (CDT)                                                                             | 14 |

| 2.2  | Relative amount of traffic produced by a 4kB BCC cache                                                     | 19 |

| 2.3  | Relative amount of traffic produced by a 4kB SCC cache                                                     | 19 |

| 2.4  | Relative amount of traffic produced by a 16kB BCC cache                                                    | 20 |

| 2.5  | Relative amount of traffic produced by a 16kB SCC cache                                                    | 20 |

| 2.6  | Relative amount of traffic saved by the BCC cache, when compared to a conventional cache                   | 21 |

| 2.7  | Relative amount of traffic saved by the SCC cache, when compared to a conventional cache                   | 22 |

| 2.8  | Energy per reference in the off-chip memory bus and CDT for conventional, BCC, and SCC caches of 1kB       | 24 |

| 2.9  | Energy per reference in the off-chip memory bus and CDT for conventional, BCC, and SCC caches of 4kB       | 24 |

| 2.10 | Miss rates for conventional, BCC, and SCC caches of 1kB                                                    | 26 |

| 2.11 | Miss rates for conventional, BCC, and SCC caches of 4kB                                                    | 26 |

| 3.1  | Schematic description of how a copy is performed by a copy engine                                          | 34 |

| 3.2  | Schematic design of how the copy engines are implemented in several levels of the memory hierarchy         | 38 |

| 3.3  | Pseudo-code for the dynamic copy engines                                                                   | 40 |

| 3.4  | Maximum speedups for copying non-resident data using an on-chip copy engine and the DCE                                                 | 42 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5  | Example of how one missing block may cause all consecutive memory blocks to be copied in the same cache                                 | 44 |

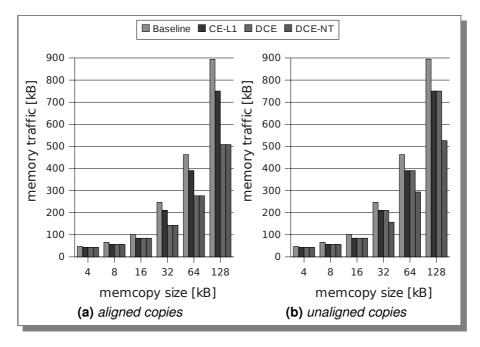

| 3.6  | Data traffic produced by the memcopy kernel using a 16kB L1 data cache                                                                  | 47 |

| 3.7  | Data traffic produced by the memcopy kernel using a 32kB L1 data cache                                                                  | 48 |

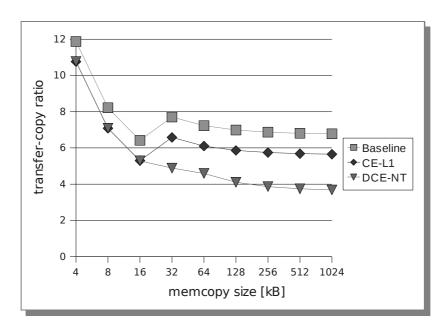

| 3.8  | Ratio of transferred bytes to copied bytes in the memcopy micro-benchmark                                                               | 49 |

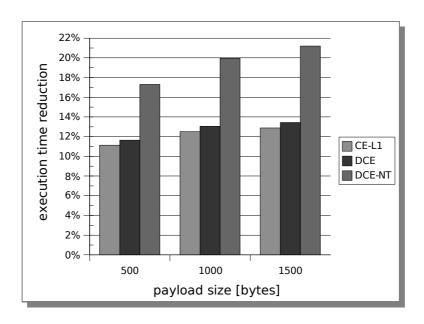

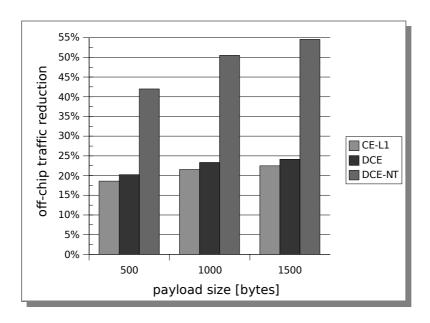

| 3.9  | Execution time reduction                                                                                                                | 51 |

| 3.10 | Off-chip traffic reduction                                                                                                              | 52 |

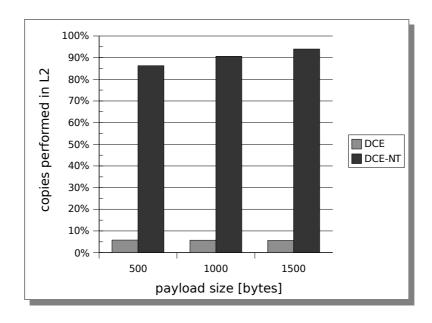

| 3.11 | Percentage of memory copies performed in L2                                                                                             | 52 |

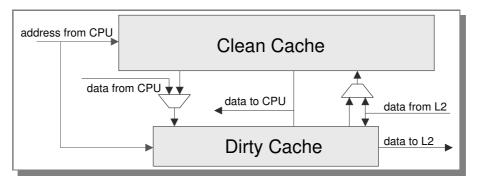

| 4.1  | Schematic representation of the Clean/Dirty-cache                                                                                       | 61 |

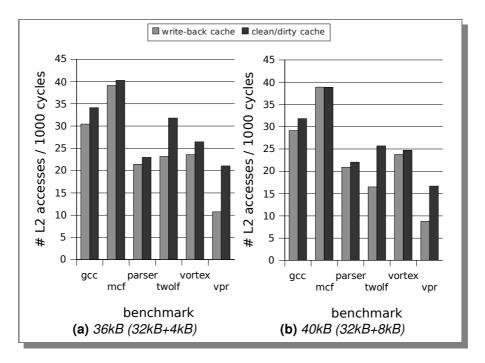

| 4.2  | L2 accesses per 1000 cycles for baseline write-back and CD-caches with capacities of 36kB and 40kB                                      | 66 |

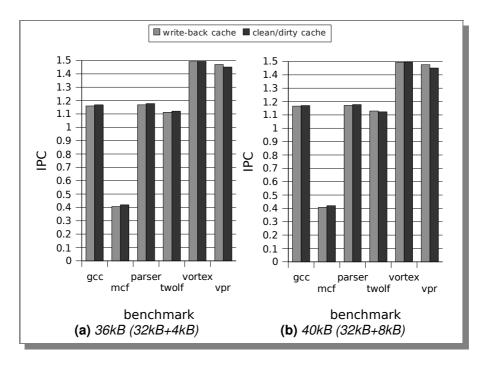

| 4.3  | IPC for write-back and CD-caches of 36kB and 40kB                                                                                       | 67 |

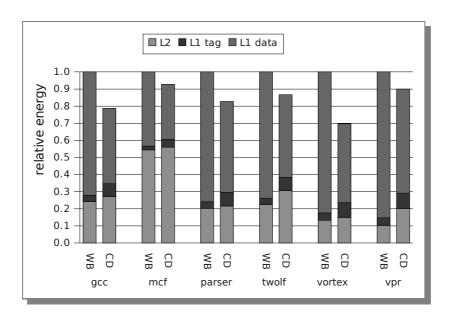

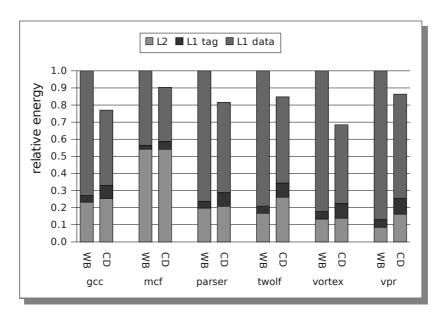

| 4.4  | Dynamic energy consumed in L1 and L2 for baseline write-back and CD-caches of 36kB                                                      | 68 |

| 4.5  | Dynamic energy consumed in L1 and L2 for baseline write-back and CD-caches of 40kB                                                      | 68 |

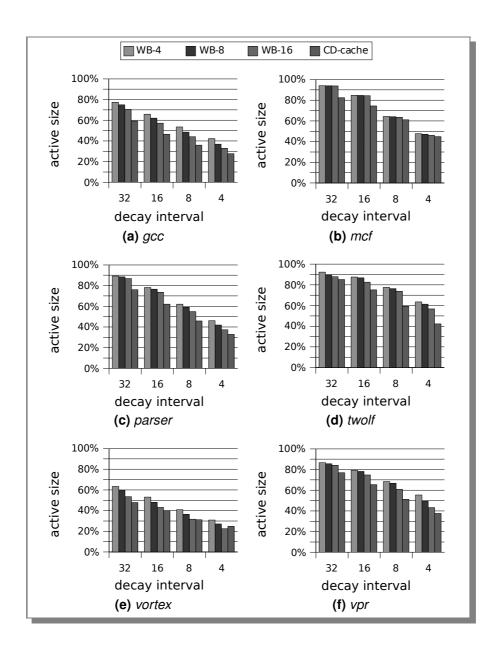

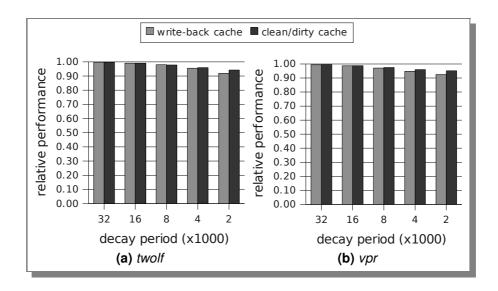

| 4.6  | Average active size for normal write-back and CD-caches using cache decay                                                               | 72 |

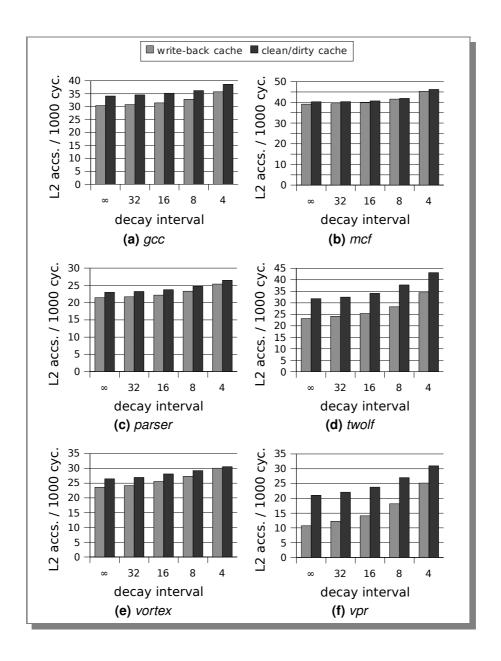

| 4.7  | L2 accesses per 1000 cycles for write-back and CD-caches using cache decay                                                              | 74 |

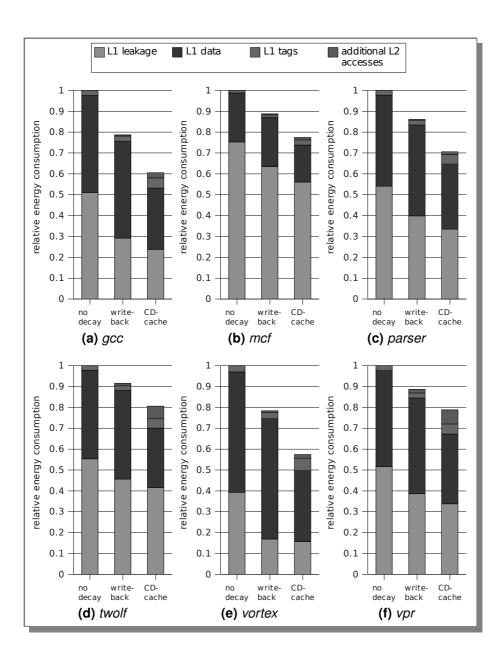

| 4.8  | Relative energy consumption in the L1 data cache and by the additional L2 accesses when using cache decay with a period of 16000 guales | 76 |

| 4.9  | of 16000 cycles                                                                                                                         | 70 |

|      | back cache without decay                                                                                                                | 77 |

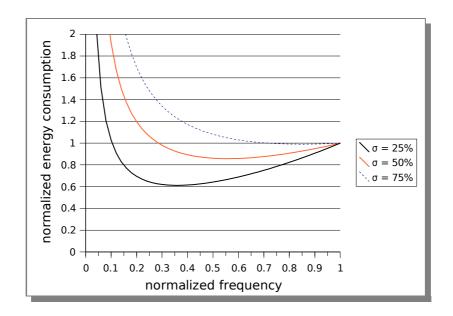

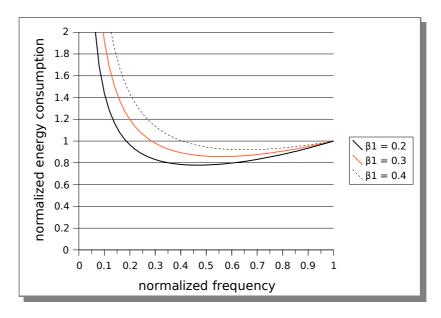

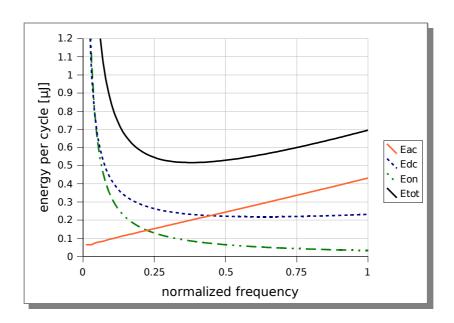

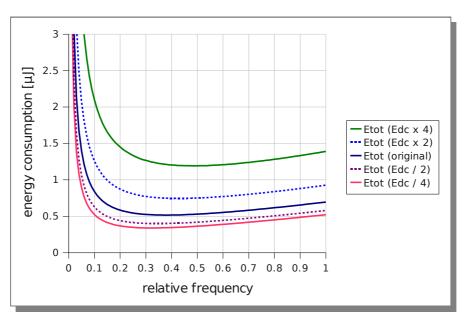

| 5.1  | Normalized energy consumption as a function of the normalized frequency for varying combinations of the dynamic and static components                                              | 86  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2  | Normalized energy consumption as a function of the normalized frequency for varying threshold voltages                                                                             | 86  |

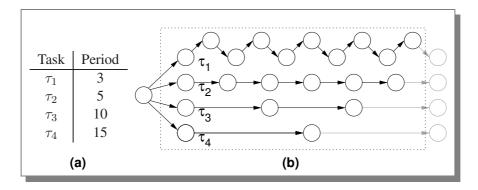

| 5.3  | Example of translating periodic tasks into a DAG                                                                                                                                   | 89  |

| 5.4  | Example for translating KPNs into DAGs                                                                                                                                             | 90  |

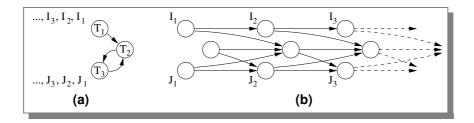

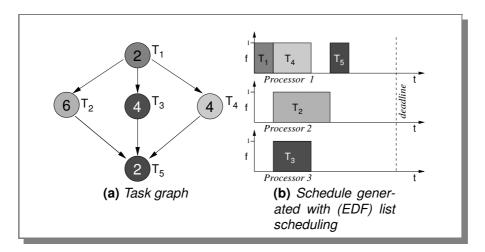

| 5.5  | Example graph and schedule                                                                                                                                                         | 91  |

| 5.6  | Pseudo-code for the list scheduling algorithm                                                                                                                                      | 92  |

| 5.7  | Schedules produced by S&S and LAMPS                                                                                                                                                | 93  |

| 5.8  | Pseudo-code for the LAMPS heuristic                                                                                                                                                | 94  |

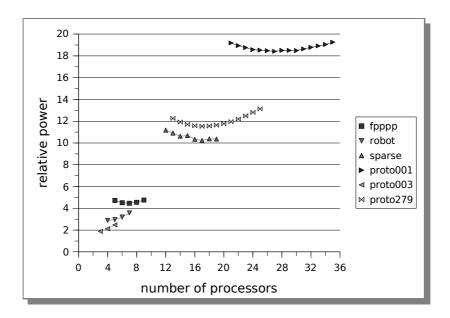

| 5.9  | Average power consumption of various schedules, normalized to a single fully active processor, for different benchmarks with the deadline at $1.5 \times$ the critical path length | 97  |

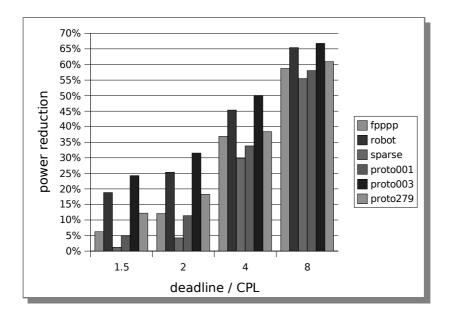

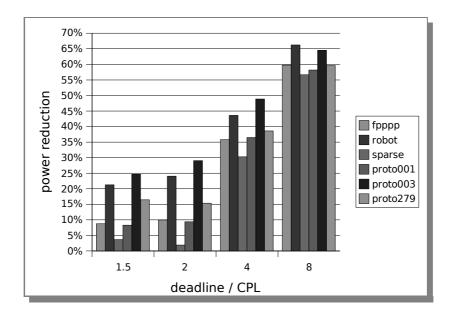

| 5.10 | Power reduction achieved by the LAMPS scheduling heuristic over S&S                                                                                                                | 100 |

| 5.11 | Power reduction achieved by the LAMPS scheduling heuristic over S&S, when scaling the voltage in discrete steps                                                                    | 101 |

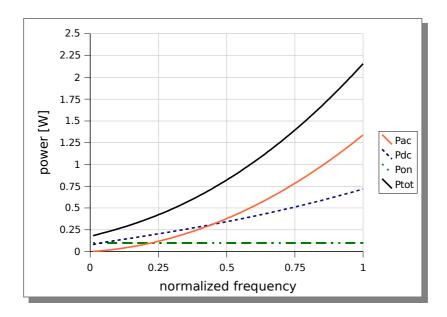

| 6.1  | Power consumption as a function of the normalized frequency                                                                                                                        | 108 |

| 6.2  | Energy consumption as a function of the normalized frequency                                                                                                                       | 108 |

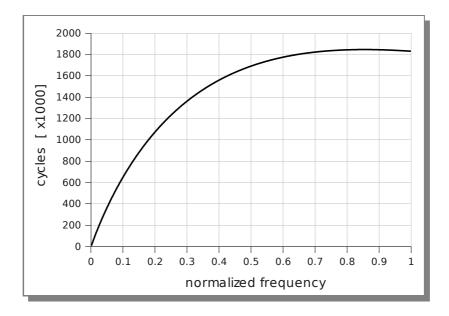

| 6.3  | Minimum number of idle cycles required for processor shut-<br>down to be beneficial, as a function of the normalized proces-                                                       |     |

|      | sor frequency                                                                                                                                                                      | 110 |

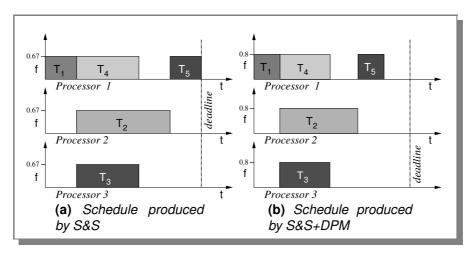

| 6.4  | Illustration of S&S and S&S+DPM                                                                                                                                                    | 111 |

| 6.5  | Pseudo-code for the SS+DPM heuristic                                                                                                                                               | 112 |

| 6.6  | Pseudo-code for the LAMPS+DPM heuristic                                                                                                                                            | 113 |

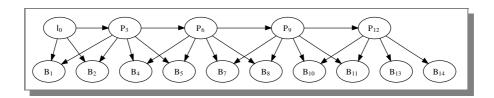

| 6.7  | Dependence graph for processing 15 MPEG-1 frames                                                                                                                                   | 116 |

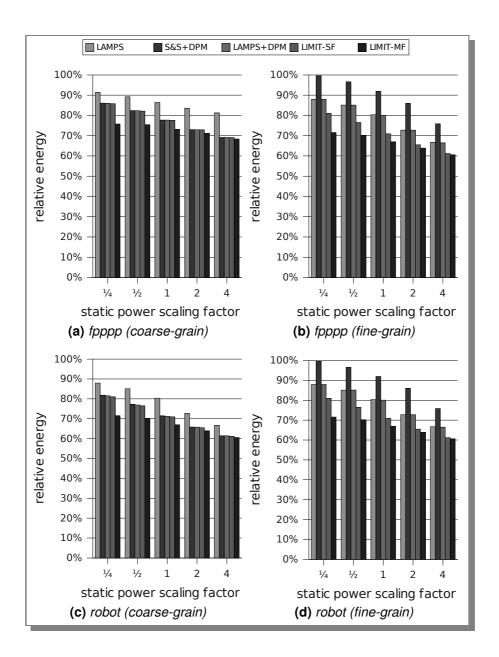

| 6.8  | Energy consumption relative to $S\&S$ for coarse-grain tasks                                                                                                                       | 118 |

| 6.9  | Energy consumption relative to S&S for fine-grain tasks. $\ . \ . \ .$                                                                                                             | 119 |

| 6.10 | Energy/total work as a function of the average amount of parallelism                                                                                                               | 122 |

| 6.11 | Energy consumption as a function of the relative frequency for different levels of static energy consumption       | 125 |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

| 6.12 | Total energy consumption as a function of the relative frequency for different levels of static energy consumption | 125 |

| 6.13 | Energy consumption relative to S&S for fpppp and robot, using different levels of static power consumption         | 127 |

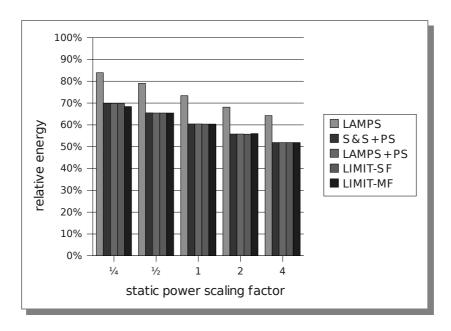

| 6.14 | Energy consumption relative to S&S for MPEG-1, using dif-<br>ferent levels of static power consumption             | 128 |

#### List of Tables

| 2.1 | Benchmarks and inputs from the MediaBench suite                                                            | 16  |

|-----|------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Main properties of the simulated system                                                                    | 45  |

| 4.1 | Average percentage of dirty cache lines in a 32kB 2-way set-associative cache with a line size of 32 bytes | 56  |

| 4.2 | Write miss alternatives                                                                                    | 58  |

| 4.3 | Baseline processor configuration                                                                           | 64  |

| 4.4 | Energy consumption of 32kB 2-way set-associative caches with cache lines of 32 bytes                       | 64  |

| 4.5 | Relative energy costs of caches in experimental model                                                      | 65  |

| 5.1 | Six benchmarks from the Standard Task Graph set and their main characteristics.                            | 96  |

| 5.2 | Results for deadlines of $1.5\times$ the critical path length                                              | 98  |

| 5.3 | Results for deadlines of $2\times$ the critical path length                                                | 98  |

| 5.4 | Results for deadlines of $4\times$ the critical path length                                                | 99  |

| 5.5 | Results for deadlines of $8\times$ the critical path length                                                | 99  |

| 6.1 | Constants for 70nm technology                                                                              | 107 |

| 6.2 | Employed benchmarks from the Standard Task Graph set and their main characteristics                        | 116 |

| 6.3 | Energy consumption relative to S&S for the MPEG-1 benchmark using various approaches                       | 123 |

#### List of Acronyms

**Notation** Description

ABB Adaptive Body Biasing ABC Allocation By Conflict

BCC Bypass in Case of Conflict

CD-Cache Clean/Dirty cache

CDT Conflict Detection Table

CE Copy Engine

CMOS Complementary Metal-Oxide Semiconductor

CPL Critical Path Length

DAG Directed Acyclic Graph DCE Dynamic Copy Engine

DCE-NT Dynamic Copy Engine with Non-Temporal

Fetching

DMA Direct Memory Access

DPM Dynamic Power Management

DTSE Data Transfer and Storage Exploration

DVFS Dynamic Voltage and Frequency Scaling

DVS Dynamic Voltage Scaling

EDF Earliest Deadline First

GOP Group Of Pictures

IPC Instructions Per Second

**Notation** Description

KPN Kahn Process Network

LAMPS Leakage Aware MultiProcessor Scheduling

LAMPS+DPM Leakage Aware MultiProcessor Scheduling with

DPM

LCM Least Common Multiple

LS-EDF List Scheduling with Earliest Deadline First

MAT Memory Address Table

PIM Processing-In-Memory

SCC Sub-block in Case of Conflict SMT Simultanious Multi-Threading

S&S Schedule and Stretch

S&S+DPM Schedule and Stretch with DPM STTD Shortest Time To Deadline

# Introduction

his dissertation covers several different energy reduction techniques for contemporary and future processors. While background and motivation for each distinct technique is provided with each corresponding chapter, this introductory chapter provides the background and motivation that is common among the different chapters. Finally, the organization of this dissertation is outlined.

#### 1.1 Motivation

Energy and power consumption are becoming increasingly important in the design of processors. Not only for processors embedded in battery powered devices, also for processors targeted at high-end server clusters energy consumption gains a growing interest. In this dissertation we propose several techniques targeted at reducing energy consumption in single- and multiprocessor systems, applicable to the embedded as well as to the high-end market.

Although computer architecture research was historically mostly targeted at enhancing performance, energy and power consumption have become increasingly important in recent years for several reasons.

The first reason is that processors are increasingly deployed in battery-powered

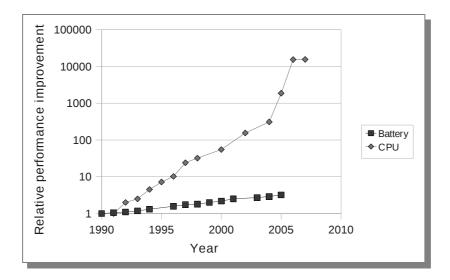

**FIGURE 1.1** Relative improvement in energy density of lithium ion batteries versus the number of transistors in Intel microprocessors [14].

embedded systems. The physical size of batteries as well as their limited capacity demand that these systems use power as sparingly as possible. This demand is even more fueled by an increasing demand for more processing power without a comparable improvement of battery capacities. The disparity between the growth of processors and the growth of battery capacities is depicted in Figure 1.1, which shows a graph redrawn from work by Chalamala [14].

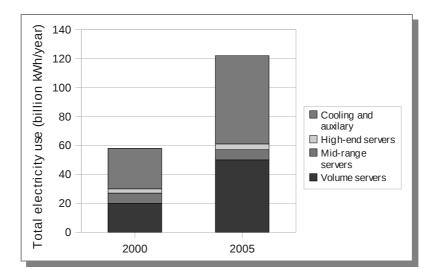

Another reason for increased attention for energy reduction relates to the increase in the total number of servers deployed around the world, and the growing importance of the electricity cost of these servers. Figure 1.2 depicts the total amount of electricity used by servers in world in 2000 and 2005, as estimated by Koomey [63]. The data in this figure is separated in electricity used for three different server classes and electricity used for cooling and auxiliary equipment. From this figure, it is clear that in 5 years the total amount of electricity used by servers around the world has more than doubled. Moreover, approximately half the electricity is used for cooling and auxiliary equipment. As a result of an increase in power consumption and a decrease in the cost of computing hardware, for many companies the electricity bills are becoming an increasingly large fraction of the total expenditure.

**FIGURE 1.2** *Total electricity use for servers in the world in 2000 and 2005, including cooling and auxiliary equipment [63].*

#### 1.2 Power and Energy

In many works in literature, power and energy are used interchangeably. Although there is a clear relation between these two quantities, they are only proportional if power refers to *average* power. In many cases, however, power reduction techniques aim to reduce the peak power consumption or the power density [80], in order to keep processors functional without requiring exorbitant cooling.

This dissertation presents techniques to reduce the energy or average power consumption of processors. Although there are strong relations between techniques aimed at reducing average power and techniques aimed at reducing peak power or power density, the first is the primary focus of this dissertation.

Power in CMOS circuits is generally classified in a dynamic and a static part. The dynamic part refers to the power dissipated due to switching between low and high logic levels. The static part refers to the power dissipated through leakage currents in non-ideal transistors. Dynamic power has dominated static power in the past decades, and has increased significantly due to its quadratic relation on the clock frequency. Due to increasing transistor counts and decreasing feature sizes, however, static power consumption has increased significantly and is expected to increase further in the next decades [41]. More

specifically, Borkar [8] predicted leakage current to increase by a factor of five with each technology generation, and Duarte et al. [25] predicted that static power consumption will eventually surpass the dynamic power consumption.

#### 1.3 Challenges

In order to develop energy efficient techniques for future processors, one should know the key challenges for such processors, both from an energy and a performance perspective. To this end, two key observations were made.

The first observation is that limited memory bandwidth is and will remain a fundamental impediment to attain higher performance, rendering the memory hierarchy as one of most important considerations in the design of contemporary and future processors. To hide the long latency of off-chip memories, most processors employ several levels of caches, on-chip and/or off-chip. This is beneficial due to the inherent temporal and spatial locality of data. While memories get faster over time, processors become faster as well. In fact, processors speeds have grown at a faster rate than memory speeds have, which has led to a growing disparity between the speeds of processors and memories. Due to the limited number of processor pins and the intrinsic delay due to the physical distance between processors and off-chip memories, this disparity is even more significant for memories located off-chip. This problem is often referred to as the *memory wall* [71, 95]. To improve performance of systems with limited bandwidth and long memory latency, chip manufacturers have used increasingly larger on-chip caches, boosted the transfers speed between processors and off-chip memories, and employed aggressive prefetching techniques. While these choices provide one-time improvements, they do not fundamentally solve the problem. And while these techniques improve performance for memory-bound programs, they generally also increase the total energy consumption.

Accesses to off-chip memory are not only posing an impediment to higher performance, they also contribute significantly to the power budget [69, 86]. For example, Basu et al. [6] show that an off-chip data bus in an embedded processor consumes between 9.8% and 23.2% of the total power.

In many contemporary processors, large on-chip caches often already take up the majority of the die area. This not only drives the cost of these processors, larger caches also consume a significant amount of power.

These observations have led to the following questions:

1.3 CHALLENGES 5

• Especially for low-power embedded processors, memory transfers are responsible for a significant amount of energy consumption. Moreover, the memory bandwidth is a fundamental impediment to attain higher performance on memory-bound programs. How can we decrease the used memory bandwidth in processors while maintaining or possibly improving performance, without employing large caches?

- Are there situations in which caches and multi-level memories perform particularly bad? If so, can these problems be resolved efficiently?

- Since larger on-chip caches are more costly in terms of energy and manufacturing cost than smaller caches, can we attain comparable performance with processors employing significantly smaller caches?

The second observation is that industry no longer tries to improve performance by boosting the clock frequency. While this has been popular and effective in past decades, this trend cannot simply be continued for the following reasons. First, the key to increasing clock frequency has been the shrinking size of transistors. With decreasing feature size, however, it becomes increasingly hard to make reliable circuits, both due to an increase in transient errors and due to process variations. Furthermore, decreasing transistor sizes inherently lead to an increases in leakage current, which in term may lead to higher energy consumption. Secondly, power consumption in CMOS circuits grows quadratically with the clock frequency. Increasing this frequency therefore leads to fundamental cooling problems, required to guarantee proper operation. As a result, the trend of increasing clock frequencies has shifted to maintaining the same frequency but increasing the number of processor cores. Yet, this has been an energy efficient solution mostly due to the current state of technology. In current technology, dynamic power consumption (due to switching between logic levels) dominates static power consumption (due to leakage currents in non-ideal transistors). With decreasing feature sizes and with reduced clock frequencies, however, this balance may be different. When static power becomes more significant, the most energy efficient solution is no longer to use as many processors as possible on a low clock frequency. Instead, it will be more efficient to find a proper balance between the clock frequency and the number of used processor cores.

From these observations, the following questions were derived:

• While in many cases increasing the number of processor cores and decreasing the clock frequency leads to a reduction in energy, this is mostly

due to the importance of dynamic energy. In the case of increased leakage power, to what extend will increasing parallelism lead to a reduction in energy?

- In CMOS, both dynamic and static power consumption decrease with decreasing voltage and clock frequency. Lowering the clock frequency, however, also increases the time to complete computational tasks. Since energy equals power multiplied by time, the static energy consumption will actually increase when reducing the clock frequency. As a result, the total energy consumption may also start to increase below a certain speed. To what extend should the clock frequency be lowered in order to minimize energy consumption?

- When static power consumption is more significant, it becomes worthwhile to temporarily power-off processor cores. Switching cores off and on, however, requires a certain amount of time and will therefore also consume energy. Under which circumstances is switching of processor cores an interesting option?

- How do these options (number of processor cores, reduced frequency, and temporarily turning off processors) relate, and how can we find the optimal operating point that minimizes energy?

#### 1.4 Organization and Contributions

As was already indicated in the previous section, the techniques presented in this dissertation can be classified into two areas. The first area, covered by the first three chapters, targets energy reduction in the multi-level memory system. The second area, covered by the last two chapters, proposes energy efficient scheduling techniques for near-future multiprocessor systems.

Small direct-mapped caches consume less energy than large set-associative caches. However, small direct-mapped caches incur many conflict misses. In Chapter 2, we target energy reduction by reducing the amount of (off-chip) memory traffic caused by recurring conflict misses in caches. The proposed technique is based on a structure called the *Conflict Detection Table* (CDT). The CDT is used to detect conflict misses in direct-mapped caches. Using this information, memory traffic is reduced by transferring only the requested word instead of the whole cache line from the next memory level. Two cache organizations that employ the CDT are proposed: the *Bypass in Case of Conflict* (BCC) cache and the *Subblock in Case of Conflict* (SCC). While the BCC

bypasses the cache when a conflict miss is detected, the SCC only stores the requested subblock on the same event. Experimental results show that these organizations can reduce the amount of memory traffic by up to 65% for the BCC, and up to 47% for the SCC.

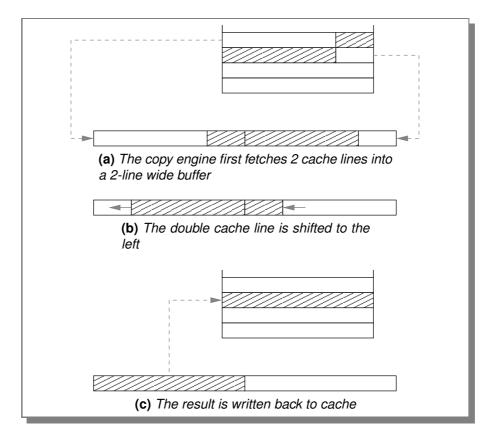

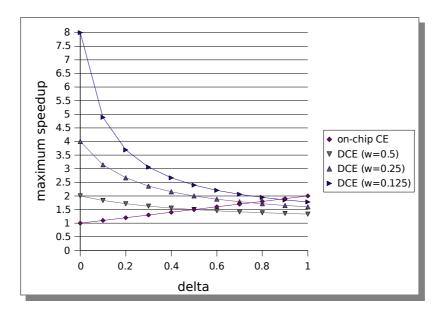

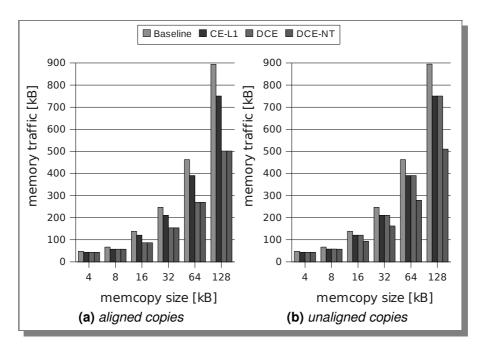

Memory copies require virtually no computational power, but produce a significant amount of memory traffic. Furthermore, large memory copies can completely replace the contents of the data cache, while the newly allocated data may not be used directly after. In Chapter 3, we develop a technique to efficiently handle memory copies in multi-level memory systems, using an organization where memory copies are performed using *Copy Engines* (CEs). A technique is proposed that can dynamically decide in which level the copy should be performed in order to minimize memory traffic. By avoiding transfers back and forth between the main memory and the CPU, a significant amount of traffic and energy can be saved. Furthermore, by reducing the amount of used memory bandwidth and by performing the memory copies asynchronously in dedicated hardware, the proposed organization also improves performance. In an experimental setup with a TCP/IP processing benchmark and a 2-level cache hierarchy, the proposed technique shows to reduce memory traffic by up to 94% and improve execution time by up to 21%.

Write-back caches are usually preferred over write-through caches since they attain significantly higher performance. Furthermore, write-through caches produce significantly more write traffic, wasting precious memory bandwidth and energy. Write-back caches, on the other hand, maintain a significant number of dirty cache lines, which can be problematic for several reasons. Many techniques to reduce energy consumption in caches resize, reconfigure, or shut down (parts of) a cache dynamically. With these techniques, dirty cache lines have to be written back to the next memory level first. Not only can this lead to an increased number of bandwidth stalls due to bursts of write-back traffic, it can also bring additional complexity to the design of the energy reduction logic. Furthermore, with error detection clean cache lines are tolerant to transient errors, whereas dirty cache lines need error correction. In Chapter 4, we propose a cache organization called the Clean/Dirty (CD) cache. The CDcache is a cache organization using two separate cache structures. The first structure is only used to store clean data. The second structure is much smaller, and is used to store all dirty data. By splitting the cache in clean and dirty data, cache energy reduction techniques can be applied efficiently to the clean data, while maintaining an acceptable amount of write traffic. The proposed organization results in a similar or higher performance than a write-back cache, while reducing the number of dirty cache lines significantly. In a case study it is shown how the proposed organization can be applied efficiently to a energy reduction technique called *Cache Decay*. Compared to a conventional writeback cache that uses cache decay, the CD-cache with cache decay improves the energy reduction by more than twice on average.

An effective technique to reduce power consumption in modern CPUs is Dynamic Voltage Scaling (DVS), in which both the frequency and the supply voltage are scaled down when less performance is demanded. For multiprocessors, an effective technique is to use as many processors as possible to reduce the makespan of the schedule, and to use the remainder of time until the deadline (slack) to reduce the frequency and supply voltage. This technique is effective because in current technologies dynamic power consumptions dominates static power consumption. As static power consumption due to leakage currents is expected to increase dramatically in the near future, this technique may no longer suffice. Instead, it becomes more effective to balance between reducing the makespan and limiting the number of employed processors. In Chapter 5, we propose a technique called Leakage Aware MultiProcessor Scheduling (LAMPS). LAMPS is a scheduling heuristic that finds an optimal balance between DVS and using the correct number of processors. This is achieved by using a non-optimal but fast scheduling algorithm, which allows our heuristic to dedicate more time to finding the optimal number of processors. Results show that this heuristic improves energy consumption by up to 67%, compared to a technique that employs as many processors as possible.

In Chapter 6, we extend LAMPS by also allowing a processor to shut down temporarily. The proposed heuristic finds an optimal balance between DVS, using the correct number of processors, and shutting down these processors temporarily. Results show that this approach reduces the energy consumption by up to 14%, compared to the LAMPS heuristic presented in Chapter 5. Furthermore, two lower bounds are presented. One for the case where all processors run at the same frequency and where this frequency is fixed throughout the schedule, and one where each processor is assigned its own frequency and this frequency may change over time. Using these lower bounds, it is shown that after applying the proposed scheduling heuristic, there is little room left for improvement.

Chapter 7 concludes this dissertation by summarizing the most important contributions and directions for future research.

## 2

#### Reducing Cache Conflict Misses

ff-chip memory accesses are a major source of power consumption in embedded processors [6, 13, 93, 94]. In order to reduce the amount of traffic between the processor and the off-chip memory as well as to hide the memory latency, nearly all processors have one or more levels of cache on the same die as the processor core. However, because small caches dissipate less power and are cheaper than large caches, a small cache is preferable to a large cache in embedded processors. Furthermore, because setassociative caches consume more power than direct-mapped caches, a directmapped cache is preferable to a set-associative one. Small, direct-mapped caches, however, generally incur many conflict misses. To reduce the amount of traffic generated by small direct-mapped caches, in this chapter we propose and evaluate a structure called the Conflict Detection Table (CDT). This table can be used to determine if a memory access is expected to hit the cache. If a hit is expected and a miss occurs, then a conflict is detected and appropriate action can be taken. In addition, we propose two cache structures that use this information to apply a better caching strategy: the Bypass in Case of Conflict (BCC) cache and the Sub-block in Case of Conflict (SCC) cache. The BCC cache bypasses the cache when a conflict is detected, whereas the SCC cache fetches a sub-block of the missing cache line in such a case. Both the BCC and the SCC cache try to minimize the amount of data traffic, by only fetching the requested word instead of a whole cache line when a conflict is detected.

While bypassing the cache disallows exploiting temporal or spatial locality, the benefit is that it avoids the need to discard the previous contents of the cache line. With sub-block caching, the previous contents are discarded. In this case, however, it may be possible to exploit temporal locality if the requested sub-block is referenced again in the near future. Whether bypassing or sub-block caching is more efficient, therefore, depends on how data is referenced afterwards. Experimental results using several embedded workloads show that the BCC and SCC cache reduce the amount of traffic significantly in many cases. Furthermore, overall they incur the same number of cache misses as the direct-mapped cache. This shows that the BCC and SCC cache reduce the amount of energy consumption with a negligible reduction in performance.

Most of the material presented in this chapter has been previously published in [19].

#### 2.1 Introduction

In order to limit the amount of off-chip memory traffic, it is essential that embedded processors make effective use of the on-chip cache. Embedded processors often exploit a small cache with limited associativity, because they are cheaper and more power efficient than large caches, and because increased associativity increases the power consumption and cycle time [84]. Small, direct-mapped caches, however, generally produce many conflict misses and, as a result, generate a significant amount of processor-memory traffic [18].

In this chapter, we present a novel technique to detect and eliminate conflict misses in caches. This technique is based on a structure called the *Conflict Detection Table* (CDT). The CDT contains the tag part of the addresses referenced by recently executed load/store instructions and is indexed by the lower-order bits of the program counter. The idea behind the CDT is that if an entry corresponding to a load/store instruction is found in the CDT and the data tag stored in this entry matches the tag of the current data address, a (spatial) hit is expected because the referenced word was loaded in the cache the previous time this instruction was executed. Furthermore, if a hit is expected but the cache access yields a miss, then a conflict is detected because the word must have been replaced by another instruction.

We propose two cache structures that employ the CDT. The first, called the *Bypass in Case of Conflict* (BCC) cache, bypasses the cache when a conflict is detected. The second, called the *Sub-block in Case of Conflict* (SCC) cache, is a sector cache that fetches only the missing sector (or sub-block) when a

conflict is detected. Both the BCC as well as the SCC cache are direct-mapped.

This chapter is organized as follows. Section 2.2 briefly discusses related work. In Section 2.3 we explain how recurring conflict misses can be detected and appropriate action can be taken. Section 2.4 presents cache organizations that use the CDT to reduce the negative effect of recurring conflict misses. The effectiveness of these caches are experimentally verified in Section 2.5. Conclusions are given in Section 2.6.

#### 2.2 Related Work

Jouppi [47] proposed employing a small (consisting of four to eight entries), fully associative *victim cache* in order to reduce conflict misses in direct-mapped caches. Blocks evicted from the L1 cache are not immediately placed in the L2 cache but are given a second chance in the victim cache. The victim cache is fully associative, however, and fully associative caches consume more energy than direct-mapped caches [84]. Memik et al. [73] showed how the victim cache can be used to reduce energy consumption by avoiding more expensive accesses to the next memory level. They furthermore showed that this resulted in better energy-delay and energy-delay-area products than would be obtained by increasing the size or associativity.

Kin et al. [60] stated that designers should be willing to trade performance for low power, and proposed to use an unusually small *filter cache* in-between the L1 cache and the load store unit. Energy is reduced by servicing memory access from the much smaller filter cache instead of the normal L1 cache. However, due to the limited size of this filter cache, many requests are serviced from the bigger L1 cache with an increased latency, thereby causing a decrease in performance.

The Dual Data Cache proposed by González et al. [29] includes a mechanism that detects if a load instruction interferes with itself. This happens, for example, when a vector is accessed repeatedly and the vector is larger than the cache. In such a case, the vector displaces itself from the cache. This situation is even worse when the vector is accessed with a stride unequal to one and the stride and the cache size are not co-prime, because in this case not all blocks are used to cache the vector. This mechanism, however, does not detect cross-interference, i.e., it does not discover situations in which data is replaced by data referenced by a different load instruction. Juurlink proposed to apply this technique using a sector cache instead of two separate cache structures, which was called the Unified Dual Data Cache [49].

Johnson et al. [45] try not to evict a block if it is more heavily used than the arriving block that generated a miss. To do so they divide the memory into regions called *macroblocks* and employ a table called the *Memory Address Table* (MAT) that contains information about how often each macroblock is used. If the MAT indicates that the block to be replaced is more heavily used than the arriving block, the arriving block is not stored in the cache. The MAT behaves like a cache, and according to results in [45] it appears that it must be rather large in order to be effective. Furthermore, this technique is targeted at improving performance rather than reducing energy consumption.

Tam [89] proposed the *Allocation By Conflict* (ABC) replacement policy. In this organization a 1-bit counter is associated with each cache block, which is increased (decreased) each time an access to this block yields a miss (hit). A block is evicted from the cache only when two consecutive accesses produce a miss.

There are also static (compiler) approaches aimed at reducing conflict misses. The Data Transfer and Storage Exploration (DTSE) methodology [10, 11] developed at IMEC, for example, focuses on compile-time techniques. One of the steps in this methodology aims at improving locality by applying loop transformations such as loop interchange and loop splitting and merging. In another step the restricted lifetimes of (parts of) array variables are exploited to overlap them in the address space. The leads to better cache performance and also reduces the total size of the required memories. While very good results have been achieved using the DTSE methodology (speedups of up to a factor of 3 and reductions in bus load by an order of magnitude have been reported), the approach has two limitations. First, the methodology is only partially supported by tools and, hence, requires manual intervention which increases the design complexity. Second, it is unclear if it can be applied to dynamic, pointer-based applications.

Another static approach to reduce conflicts in caches is proposed by Petrov and Orailoglu [78]. Their method is aimed at application-specific customization of the data cache of embedded processors. They present an algorithm that partitions memory access instructions into groups of instructions that exhibit data reuse amongst them. Each group is mapped to a certain partition of the cache, which allows to isolate them from possibly interfering groups. Furthermore, the tag comparison can be avoided if it can be determined that a reference will invariably hit the cache.

#### 2.3 Detecting Conflict Misses

A conflict miss occurs when a memory word is referenced twice but is inbetween replaced by other data. Conflict misses occur more frequently in direct-mapped caches than in set-associative caches, because each memory word is mapped to only one cache location. Consider, for example, the following simple loop:

```

for (i=0; i< n; i++)

a[i] = b[i]+c[i];

```

If the differences between the base addresses of the arrays a, b, and c are a multiple of the cache size, each a[i], b[i], and c[i] all map to the same cache line and each will replace the other in the cache so that there is no chance to exploit the spatial locality exhibited by this code. Such 'ping-pong' effects will degrade the cache performance severely. Although, in this simple example, these conflicts can be avoided by loop transformations, this may not always be possible for more complex code.

To detect conflict misses in direct-mapped caches, we propose a small structure called the CDT. The principle idea behind the CDT is that when consecutive executions of a load/store instruction access the same cache line, a cache hit is expected for all but the first access. If a hit is expected but a cache miss occurs, a different instruction must have accessed a word that is mapped to the same cache line.

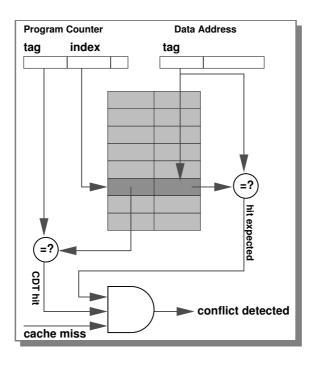

As illustrated in Figure 2.1, the CDT is a cache-like structure that is indexed by the lower-order bits of the program counter. While the CDT could be designed as a set-associative cache, in this work it is assumed to be direct-mapped. Every entry contains the higher-order bits of the instruction address and the tag of the address referenced the previous time the corresponding load/store instruction was executed. Each time a load/store instruction is executed, the CDT is accessed and the higher-order bits of the instruction address are used to determine if there is an entry for the current instruction. If no entry is found, one is allocated and the data tag field is set to the tag of the current address. If the higher order bits of the instruction address match, an entry is found, and the data tag stored in this entry is compared to the tag of the current address. If these data tags also match, the requested data is expected to be already present in the cache, because it was fetched the last time this instruction was executed. From this it follows that if a cache miss is encountered, the requested data must have been replaced by a different instruction and a conflict is detected.

**FIGURE 2.1** *Conflict Detection Table (CDT).*

A conflict can only be detected when a cache miss occurs. The information about possible conflicts, therefore, does not need to be available until after the tag comparison. This implies that the CDT will not increase the time to hit the cache. Furthermore, since the amount of required logic to implement the CDT is fairly low, it will not consume much energy. A detailed evaluation relating the energy consumed by the CDT to the energy saved by reducing memory traffic is presented in Section 2.5.

#### 2.4 BCC and SCC Caches

When a conflict is detected, it is not known in advance which instruction will be the first to re-use this cache line. Therefore, for reducing the miss rate, it is not certain what will be most efficient: replacing the current line or bypassing the cache. The same is true for reducing the amount of traffic. If a cache line is not reused in the near future, it may be beneficial to only fetch the requested data and/or to bypass the cache. If the same cache line is accessed several times in the near future, however, this will increase the amount of traffic since

each request also requires transferring the address. The techniques presented in this chapter target memory traffic reduction by fetching only the requested word instead of the whole cache line, but only if a conflict is detected.

We propose two cache structures that employ the CDT to detect and eliminate conflict misses. Both caches are direct-mapped but have the additional possibility to bypass the cache or to store only part of the requested cache line.

- Bypass in Case of Conflict The first cache organization using the CDT uses cache bypassing and is called the BCC cache. When a conflict is detected in the BCC cache, the requested word is fetched from the next memory level, but it is not stored in cache. In other words, when the CDT detects that the cache line has been replaced by another instruction, this cache will no longer store the words referenced by this instruction, as long as the instruction references the same cache line.

- **Sub-block in Case of Conflict** The second cache organization using the CDT employs *sub-block* caching [33] and is called the SCC cache. When a conflict is detected by the CDT, only the requested sub-block is fetched instead of the whole cache line. This sub-block is then stored in the corresponding location in cache, and the rest of the sub-blocks on the same cache line are invalidated. When afterwards an invalidated sub-block is referenced, it is treated as a normal miss and the whole cache line is fetched from the next memory level.

When a miss occurs in either the BCC or the SCC cache, this data is fetched from the next memory level, similar to a conventional cache. However, when a conflict is detected in the BCC and SCC caches, only the requested word of the cache line is transferred from the next memory level, whereas in a conventional cache the whole cache line is transferred. This potentially saves a significant amount of data traffic, especially if a significant number of conflict misses occur. However, not fetching the remainder of the cache line may degrade performance if the CDT incorrectly predicts conflicts for instructions that exhibit a certain amount of spatial locality.

Both the BCC and the SCC cache avoid transferring data speculatively when a conflict is detected. The fundamental difference between the BCC and the SCC caches is that when a conflict is detected, the SCC assumes there is no benefit from spatial locality, but still tries to benefit from temporal locality by storing the requested sub-block. The BCC cache, on the other hand, tries to benefit from not replacing a previously referenced cache line.

| Benchmark  | Input                 | # of mem. refs.     |  |

|------------|-----------------------|---------------------|--|

| adpcm-dec  | clinton.adpcm         | $4.59 \cdot 10^5$   |  |

| adpcm-enc  | clinton.pcm           | $4.59 \cdot 10^5$   |  |

| g721-dec   | clinton.g721          | $4.90 \cdot 10^{7}$ |  |

| g721-enc   | clinton.pcm           | $4.78 \cdot 10^7$   |  |

| gsm-dec    | clinton.pcm.gsm       | $8.39 \cdot 10^6$   |  |

| gsm-enc    | clinton.pcm           | $5.19 \cdot 10^7$   |  |

| jpeg-dec   | testimg.jpg           | $1.18 \cdot 10^{6}$ |  |

| jpeg-enc   | testimg.ppm           | $6.55 \cdot 10^4$   |  |

| mpeg2-dec  | mei16v2.m2v           | $3.28 \cdot 10^{7}$ |  |

| pegwit-dec | my.sec & pegwit.enc   | $5.31 \cdot 10^6$   |  |

| pegwit-enc | my.pub & pegwit.plain | $8.52 \cdot 10^6$   |  |

| epic       | test_image.pgm        | $7.47 \cdot 10^6$   |  |

| unepic     | test_image.pgm.E      | $1.64 \cdot 10^6$   |  |

**TABLE 2.1** Benchmarks and inputs from the MediaBench [64] suite.

#### 2.5 Experimental Results

In this section, it is shown by experiments that the BCC and SCC cache reduce the amount of off-chip memory traffic without causing a significant performance degradation. It is furthermore shown how these reductions in off-chip traffic can be translated to energy improvements.

#### 2.5.1 Experimental Setup

As benchmarks, we employed the *MediaBench* [64] benchmarking suite, which consists of a number of audio and video codecs as well as encryption and decryption routines. These benchmarks are representative of embedded multimedia applications. The *MiBench* [32] benchmarking suite, which is specifically aimed at embedded systems and also contains workloads from other application domains, was not available at the time this project was started. Moreover, MediaBench and MiBench suites have several benchmarks in common. The employed benchmarks are listed in Table 2.1.

The *sim-safe* simulator from the SimpleScalar tool set [4] was modified to generate traces containing instruction and data addresses of all executed load and store instructions. These traces were fed to our trace-driven cache simulator,

which generates several statistics, such as to the number of hits and misses and how often a replaced cache line is dirty. From these statistics, the number of transferred bytes can be computed, as well as the miss rate. We also use these statistics to compute the average energy per reference.

The simulated cache size ranges from 256 bytes to 16 kilobytes. All caches have a line size of 32 bytes, are direct-mapped, and employ the write-back policy. The sub-block size of the SCC cache is equal to the word size (32 bits). For the CDT, we have used a direct-mapped structure with 8 to 128 entries. We measured the total amount of traffic between the cache and main memory, including request (address) traffic.

Some benchmarks issue significantly more data references and therefore produce more memory traffic than others. In order to be able to compare the attained traffic savings for different benchmarks, we therefore show the relative changes between the proposed cache organizations and the conventional direct-mapped cache. For miss rates, however, relative differences do not provide proper information. If, for example, in one case the miss rate increases from 1% to 2%, and in another case it increases from 40% to 80%, the performance penalty is far more severe with the latter than with the former. Therefore, one should consider absolute differences between the miss rates of two caches rather than relative differences.

This section also quantifies the possible energy reductions by using BCC or SCC caches compared to conventional caches. While existing tools tools such as *sim-wattch* can be used to determine the energy consumption of experiments performed using SimpleScalar, we have chosen not to use these tools for several reasons. First, these tools are well suited to determine the energy consumption of existing architectures, while we employ a more custom cache architecture. Second, we are mostly interested in the savings obtained by reducing memory traffic, offset against the energy used by the CDT.

#### 2.5.2 Impact of the CDT Size

One of the most influential design parameters for both the BCC and SCC caches is the size of the CDT. The CDT can only detect conflicts if an entry is not replaced in-between two consecutive invocations of the same load/store instruction. Furthermore, the CDT will predict subsequent conflicts as long as the entry remains available. For a very small CDT, both the BCC and the SCC will behave exactly like normal caches. For a very large CDT, on the other hand, these caches may keep predicting conflicts indefinitely, even if

these conflicts only occurred for a small period of time. Naturally, it would be preferable to keep the CDT as small as possible, in order to limit the required area and the energy consumption.

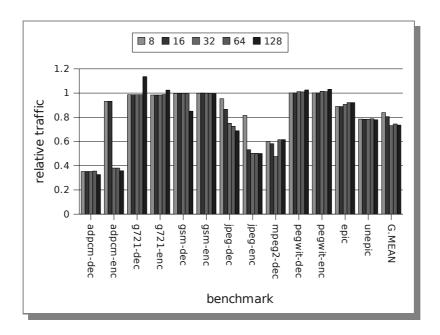

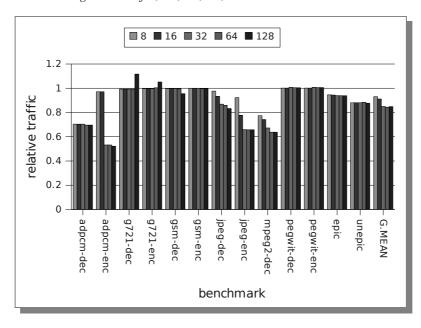

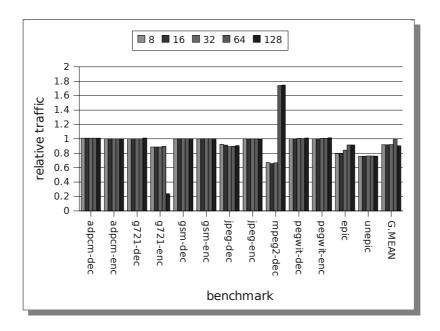

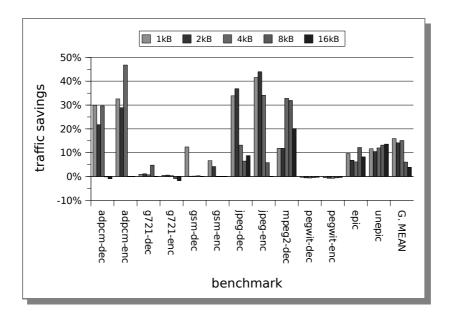

To determine the proper size of the CDT, experiments were conducted using CDT sizes ranging from 8 to 128 entries. Figures 2.2 and 2.3 depict the amount of traffic relative to a normal direct-mapped cache for the BCC and SCC caches, respectively. In both cases, a cache size of 4kB was used. Figures 2.4 and 2.5 depict results from the same experiments with caches of 16kB.

Clearly, when the CDT has too few entries, the opportunities to detect and predict conflict misses become limited, as can be seen from Figures 2.2 and 2.3 for the *adpcm-enc* and *jpeg-dec* benchmarks. A CDT with too many entries, on the other hand, can also be detrimental to traffic reduction, as can be seen for the *mpeg-dec* benchmark in Figure 2.4. In this case, the CDT incorrectly keeps predicting conflicts, leading to a significant increase in traffic in case of the BCC cache. A similar unwanted behavior can be seen for the *g721-dec* and the *g721-enc* benchmarks in Figure 2.2 and 2.3. Overall, a CDT of 32 entries shows to be a good balance, leading to no significant increase in traffic for any benchmark and to proper traffic savings for most benchmarks. Therefore, we will use a CDT of 32 entries in the remainder of this chapter.

Another notable results is that for some benchmarks, such as *adpcm-dec* and *unepic*, the savings appear to be almost independent of the CDT size. In these cases, a CDT of only 4 entries is sufficient to detect most conflicts, leading to a traffic reduction of up to 65% with *adpcm-dec* and over 20% for the *unepic* benchmark when using caches of 4kB.

As the benchmarks used in this chapter have relatively small working sets, they do not stress larger data caches significantly. In fact, from Figures 2.4 and 2.5 it can be seen that both the BCC and the SCC are only able to reduce traffic for less than half of the employed benchmarks. Because of this, and because the number of conflict misses decreases significantly with an increase in cache size, the experiments presented in this chapter are performed using relatively small caches of 1 to 16kB. The fact that these benchmarks perform relatively well on small caches can be verified by looking at the corresponding miss rates, presented in Section 2.5.5.

#### 2.5.3 Traffic

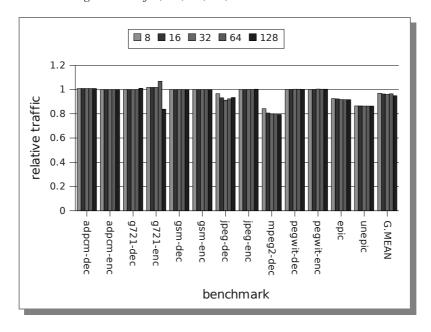

Figure 2.6 and Figure 2.7 depict, for various benchmarks and cache sizes, the relative traffic savings upon a normal direct-mapped cache of the same size, for

**FIGURE 2.2** Relative amount of traffic produced by a 4kB BCC cache using a CDT of 8, 16, 32, 64, and 128 entries.

**FIGURE 2.3** Relative amount of traffic produced by a 4kB SCC cache using a CDT of 8, 16, 32, 64, and 128 entries.

**FIGURE 2.4** Relative amount of traffic produced by a 16kB BCC cache using a CDT of 8, 16, 32, 64, and 128 entries.

**FIGURE 2.5** Relative amount of traffic produced by a 16kB SCC cache using a CDT of 8, 16, 32, 64, and 128 entries.

**FIGURE 2.6** Relative amount of traffic saved by the BCC cache, when compared to a conventional cache.

respectively the BCC cache and the SCC cache. The bars labelled G.MEAN denote geometric means measured over all benchmarks. Geometric means are used instead of averages, since we are comparing relative quantities.

It can be seen that in most cases both the BCC cache and the SCC cache produce significantly less traffic than the normal direct-mapped cache. Specifically, in 55% of all benchmark/cache size combinations, the BCC cache produces at least 5% less traffic than the direct-mapped cache. The SCC cache improves upon the direct-mapped cache by at least 5% in 50% of all cases. Especially when the cache size is small (1, 2, or 4 kB), a traffic reduction of more than 50% can be achieved by the BCC as well as the SCC cache. Averaged over all benchmarks and cache sizes (using a geometric mean), the amount of traffic produced by the BCC cache is 20% smaller than the amount of traffic generated by the direct-mapped cache. For the SCC cache, the average reduction is 11%. For larger cache capacities, fewer benchmarks benefit from the proposed conflict detection technique.

The efficacy of the BCC and SCC cache depend significantly on the type and amount of locality that is exhibited by an application. In a small number of cases, the BCC and the SCC cache actually produce more traffic than the direct-mapped cache. This is particularly the case with the *pegwit-dec* and

**FIGURE 2.7** Relative amount of traffic saved by the SCC cache, when compared to a conventional cache.

*pegwit-enc* benchmarks. In these cases, the benchmarks suffer from decreased performance due to the fact that available spatial locality is not fully exploited. In most cases, however, both cache organizations reduce the amount of off-chip traffic considerably and, hence, the amount of energy consumed by an application. We further observe that although the BCC cache produces the least amount of traffic for most benchmarks and cache sizes, it will also increase traffic more than the SCC cache when incorrectly predicting conflicts.

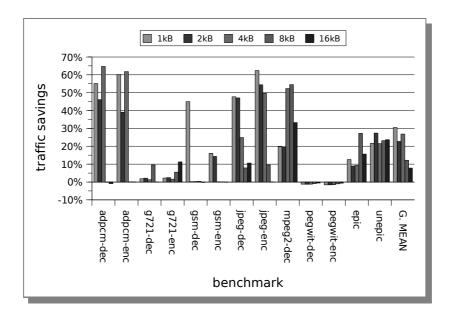

#### 2.5.4 Energy Reduction

By reducing the amount of data that is transferred between on-chip and offchip memories, a significant amount of energy can be saved. However, this has to be offset against the energy consumed by the CDT, which is accessed on every load or store instruction. The difference in energy consumption between the conventional direct-mapped cache and the BCC and SCC can be estimated by comparing the energy saved by the traffic reduction to the energy consumed by the accesses to the CDT. In both cases, these numbers have to be multiplied by the appropriate energy cost. Since the CDT closely resembles a cache, the energy consumption of accessing the CDT can be estimated using CACTI [90]. Using CACTI 4.1, a 128-entry direct-mapped cache with a line size of 8 bytes was modelled, using the 180 nm technology node. According to CACTI, this results in a cost of approximately 2.14pJ per access. It should be noted that we use a CDT of 32 entries in these experiments and that the CDT actually employs a line size of 4 bytes. However, the minimum line size in CACTI is 8 bytes, and the energy cost of accessing the CDT is therefore over-estimated.

To model the cost of transferring data between on- and off-chip memories, we use a lower bound by only calculating the energy involved in bit switches on the bus. The dynamic energy consumed by a single bit switch can be expressed as:

$$E = C \cdot V^2$$

where C denotes the bus capacitance and V denotes the employed voltage. This voltage is assumed to be 1.8V, which is the minimum voltage used in commodity memories available on the market today [38]. The capacitance of a single metal wire between on- and off-chip is estimated at 20pF for 180 nm technology. This is the same value as is used by Basu et al. [6], which in turn is based on data provided in [12].

We assume that, when transferring data, on average half the bits on the memory bus switch. As a result, the energy involved with these transfers can be estimated by:

$$E_{bus} = 4 \cdot traffic \cdot C \cdot V^2$$

,

where traffic denotes the total number of bytes transferred across the bus. For example, a transfer of one 4-byte word across the bus will consume  $4 \cdot 4 \cdot 20 \cdot 10^{-12} \cdot (1.8)^2 = 1.036nJ$ , whereas transferring a 32-byte cache line will cost 8.29nJ.

The dynamic energy consumption of both the CDT and the memory bus will be lower when a smaller technology is used. However, we expect that this will benefit the CDT at least as much as the memory bus, and that the presented results are a lower bound for smaller technologies as well.

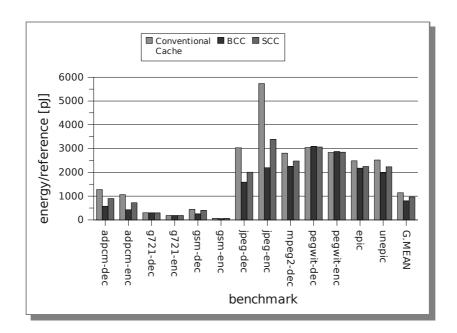

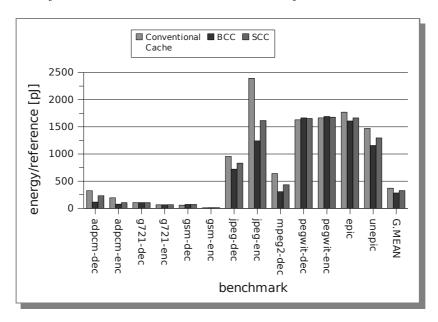

The energy consumed by the CDT is found by multiplying the number of memory accesses by 2.14pJ. This results in the graphs depicted in Figures 2.8 and 2.9, which depict the energy *per reference* consumed in the memory bus and CDT for cache sizes of 1kB and 4kB, respectively. These results include data for a conventional cache, the BCC, and the SCC.

As expected, the energy reduction of the proposed cache organizations de-

**FIGURE 2.8** Energy per reference in the off-chip memory bus and CDT for conventional, BCC, and SCC caches of 1kB.

**FIGURE 2.9** Energy per reference in the off-chip memory bus and CDT for conventional, BCC, and SCC caches of 4kB.

creases with increasing cache size. Although accessing the CDT on every memory reference adds to the total energy consumption, the reduction in traffic on the off-chip memory bus outweighs this. In fact, for the cases in Figures 2.6 and 2.7 where either the BCC or the SCC show a significant reduction in traffic, a similar energy reduction per reference can be found in Figures 2.8 and 2.9. However, where these caches in Figures 2.6 and 2.7 show an increase in traffic, the increase in energy in Figures 2.8 and 2.9 is far less significant. The reason for this difference is that while the relative amount of traffic is increased significantly, this increase is still not very significant in absolute terms. Due to a low cache miss-rate in the baseline cache, the energy consumption per reference will increase, but it will not be very significant when compared to the total number of memory references.

In general, Figures 2.8 and 2.9 show that the BCC is able to reduce energy consumption by approximately a factor of two for benchmarks like the *adpcm* and *jpeg* applications. The SCC cache also reduces energy consumption in these cases, but generally to a lesser extend. Only for the *pegwit* benchmarks there is a slight increase in energy, in which case the increase is less than 2.1%.

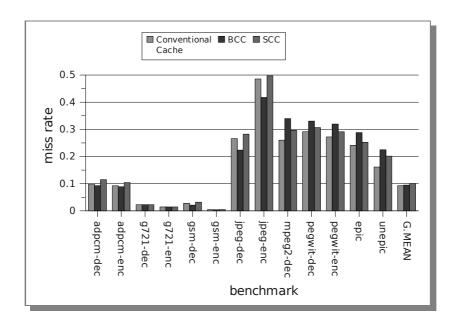

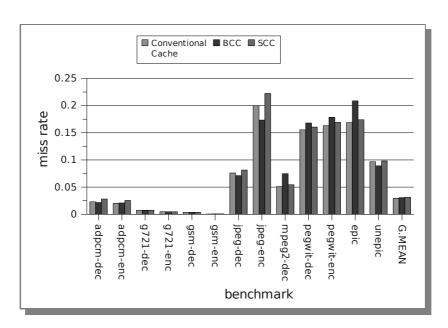

#### 2.5.5 Impact on Execution Time

The results discussed above show that the BCC and the SCC cache reduce the amount of off-chip memory traffic. However, if they would increase the miss rate (and therefore execution time) significantly, no energy reduction would be achieved. To validate this, Figure 2.10 and Figure 2.11 depict the miss rates generated by the direct-mapped cache, the BCC cache, and the SCC cache, for cache capacities of 1kB and 4kB, respectively. In most cases the miss rates of the BCC cache and the SCC cache are comparable to the miss rate of the direct-mapped cache. In some cases, however, the miss rate of the BCC cache is significantly larger than the miss rate of the direct-mapped cache. In one case, for *mpeg2-dec* using a cache size of 1kB, the miss rate increases from 26% to 34% when using the BCC cache. The largest increase in miss rate for the SCC cache, from 16% to 20%, is found with the *epic* benchmark. Furthermore, in several cases the BCC cache performs better than the direct-mapped cache. On average, they perform equally.

We conclude that the BCC cache is the most efficacious cache structure. It generates significantly less off-chip traffic than a direct-mapped cache, while performing equally as well. However, for some applications the SCC cache may be preferable, especially when performance is critical.

**FIGURE 2.10** *Miss rates for conventional, BCC, and SCC caches of 1kB.*

**FIGURE 2.11** *Miss rates for conventional, BCC, and SCC caches of* 4kB.

2.6 CONCLUSIONS 27

#### 2.6 Conclusions

We have proposed a technique which can detect and is often able to reduce the negative effects of recurring conflict misses. The proposed technique employs a small structure called the *Conflict Detection Table* (CDT). This conflict detection mechanism does not require much logic and as as result does not significantly add to the total energy consumption. Furthermore, since the CDT only needs to be consulted on a cache miss, it will not increase the cycle time. Consequently, it can easily be applied to on-chip caches that lack associativity. We have proposed two cache organizations that employ the CDT: the *Bypass in Case of Conflict* (BCC) cache and the *Sub-block in Case of Conflict* (SCC) cache.