# On Leveraging Vertical Proximity in 3D Memory Hierarchies

Lefter, Mihai

10.4233/uuid:f744c1af-505e-440c-bc49-2a1d95d0591d

**Publication date**

**Document Version** Final published version

Citation (APA)

Lefter, M. (2018). On Leveraging Vertical Proximity in 3D Memory Hierarchies. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:f744c1af-505e-440c-bc49-2a1d95d0591d

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# On Leveraging Vertical Proximity in 3D Memory Hierarchies

# On Leveraging Vertical Proximity in 3D Memory Hierarchies

# Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus Prof. dr. ir. T.H.J.J. van der Hagen chair of the Board for Doctorates to be defended publicly on

Wednesday 14 November 2018 at 10:00 o'clock

by

# Mihai LEFTER

Master of Science in Computer Engineering Delft University of Technology, The Netherlands born in Braşov, Romania This dissertation has been approved by the promotors.

# Composition of the doctoral committee:

Rector Magnificus, voorzitter Delft University of Technology

Dr. S.D. Cotofană Delft University of Technology, promotor Dr. J.S.S.M. Wong Delft University of Technology, copromotor

#### Independent members:

Prof. dr. P.J. French Delft University of Technology

Prof. dr. J. Pineda de Gyvez Eindhoven University of Technology, The Netherlands

Prof. dr. A. Rubio Solá

Polytechnic University of Catalonia, Spain

Prof. dr. L. Vințan

Lucian Blaga University of Sibiu, Romania

Prof. dr. L. Anghel University Grenoble-Alpes, France

Prof. dr. W. A. Serdijn Delft University of Technology, reserve member

#### ISBN 978-94-6186-983-8

Keywords: 3D stacked integrated circuits, nems, nemfet, zero-energy, memory hierarchy, reliability.

# Copyright © 2018 Mihai Lefter

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

Printed in The Netherlands.

# **Abstract**

ithin the past half century, Integrated Circuits (ICs) experienced an aggressive, performance driven, technology feature size scaling. As the technology scaled into the deep nanometer range, physical and quantum mechanical effects that were previously irrelevant become influential, or even dominant, resulting in, e.g., not any longer negligible leakage currents. When attempting to pattern such small-geometry dimensions, the variability of technological parameters considerably gained importance. Furthermore, it became more difficult to reliably handle and integrate such a huge number of tiny transistors into large scale ICs, considering also that a substantial increase in power density needed to be taken into account. Scaling induced performance was no longer sufficient for delivering the expected improvements, which lead to a paradigm switch from uniprocessors to multiprocessor micro-architectures. At the same time, since for certain application domains, such as big data and Internet of things, the to be processed data amount increases substantially, computing system designers become more concerned with ensuring data availability than with reducing functional units latency. As a result, state of the art computing systems employ complex memory hierarchies, consisting of up to four cache levels with multiple shared scenarios, making memory a dominant design element that considerably influences the overall system performance and correct behavior. In this context, 3D Stacked Integrated Circuit (3D SIC) technology emerges as a promising avenue in enabling new design opportunities since it provides the means to interconnect devices with short vertical wires. In this thesis we address the above mentioned memory challenges by investigating the 3D SIC technology utilization in memory designs, as follows. First, we propose a novel banked multi-port polyhedral memory that provides an enriched access mechanism set with a very low bank conflict rate and we evaluate its potential in shared caches. Second, we propose a low power hybrid memory in which 3D technology allows for the smooth co-integration of: (i) short circuit current free Nano-Electro-Mechanical Field Effect Transistor (NEMFET) based inverters for data storage, and, (ii) CMOS-based logic for read/write operations and data preservation. Third, we propose a memory repair framework that exploits the 3D vertical proximity for inter-die redundant resources sharing. Finally, we propose novel schemes for performing user transparent multi-error correction and detection, with the same or even lower redundancy than the one required by state of the art extended Hamming single error correction schemes.

# Acknowledgments

I would like to express my gratitude to Dr. Sorin Cotofană, my promotor and daily supervisor. Sorin did not only grant me the opportunity to pursue a PhD, but he also guided and challenged me during this almost everlasting journey. He sacrificed many late evenings, weekends, and holidays to help me with my research. He always encouraged me to develop myself, and his deep insights were very valuable to my work. Over the years, his friendly attitude, inspiring ideas, and unbounded optimism gave me the strength to not lose focus and to always move forward. In addition, thank you Sorin for the delicious dinner events that sparkled a lot of fruitful debates and open discussions that shaped my views on many issues.

Thank you George, Saleh, and Marius, my project and office colleagues, for creating the greenest faculty environment in our office, which enhanced such a wonderful working atmosphere. In addition to the productive work discussions, I deeply enjoyed your friendship and our countless debates on world matters. Mottaqiallah, thank you for the interesting talks we had during and outside the 3DIM<sup>3</sup> project, for your motivation, and for translating the thesis abstract into Dutch. I would also like to thank the co-authors of the publications related to this thesis: Prof. Dr. Said Hamdioui, Dr. Demid Borodin, Dr. Thomas Marconi, and Dr. Valentin Savin. Also, thank you Demid for stirring the photography passion in me, and thank you Thomas for your great introduction into the LDPC world.

Special thanks to Lidwina for her assistance in smoothing all the bureaucratic matters and for the fun discussions that we had, as well as to Erik and Eef, who always did their best to ensure that all of our computer-related problems were solved as quickly as possible. I would also like to thank all colleagues from the CE department for providing an excellent and inspiring working atmosphere.

My staying in The Netherlands would have not been so enjoyable if not for the great Romanian community. I wish to use this opportunity to thank Bogdan, Adriana, Madalina, Marina, Ana Andreea, Alex Catalin, Razvan, Roxana, Alex, Sorina, Dragos, Remus, Alin, Radu, Elena, Vlad, Razvan, Tina, Ozana, Anca, Nicoleta, Andrei, Nicolae Emanuel, Raluca, Cristi, Iulia, Bogdan, Ruxandra, Mihai, and all the others I may have missed. In addition, in Delft I made many great international friends. Thank you Changlin, Yao, Chunyang, Asha, Peter, Olga, Mafalda, Imran, Laiq, Faisal, Seyab, Innocent, Andre, and all the other people in the CE group.

I do not want to miss the occasion to thank Bogdan, Catalin, and Prof. Dr. Georgi Gaydadjiev who ensured that I had to opportunity to study at TU Delft.

I am especially grateful to Jeroen Laros for the confidence boost and support required to continue and finish this PhD.

Last but not least, I wish to thank my family. Mom and dad, thanks for always encouraging me, for your love and continuously warm support. My sister Elena and my brother-in-law Ciprian, I am grateful for your emboldening and affection. My parents in law, Cristina and Iustin, thank you for your encouragements. In addition, I am very fortunate to have a son as Matei - thank you for making my days so happy through your sparkling laughter and joy. And most of all I want to thank Iulia for always being there for me.

Mihai Lefter

Delft, The Netherlands, October 2018

# Table of Contents

| Tit | le      |         |                                                           |

|-----|---------|---------|-----------------------------------------------------------|

| Αb  | stract  | t       |                                                           |

| Ac  | know    | ledgmen | its ix                                                    |

| Lis | st of T | ables . |                                                           |

| Lis | st of F | igures  |                                                           |

| 1   | Intro   | duction |                                                           |

|     | 1.1     | Moderi  | n Processor Design Challenges                             |

|     |         | 1.1.1   | Technology Scaling                                        |

|     |         | 1.1.2   | Ensuring Data Availability in Multi-core Processors 14    |

|     |         | 1.1.3   | Processor Design Within a Restricted Power Envelope 15    |

|     |         | 1.1.4   | Memory Dependability in the Nano Scale Era                |

|     | 1.2     | Techno  | ology Enablers                                            |

|     |         | 1.2.1   | 3D Integration Technology                                 |

|     |         | 1.2.2   | Emerging Technologies                                     |

|     | 1.3     | Resear  | ch Questions                                              |

|     | 1.4     |         | ation Contributions                                       |

|     | 1.5     | Dissert | ation Organization                                        |

|     | Bibli   | ography |                                                           |

| 2   |         |         | lyhedral Cache for 3D Wide-I/O Multi-core Computing Plat- |

|   | 2.1   | 2.1 Introduction                                              |    |  |

|---|-------|---------------------------------------------------------------|----|--|

|   | 2.2   | Wide-I/O Shared Polyhedral Cache                              | 54 |  |

|   |       | 2.2.1 Traditional Cache Design                                | 54 |  |

|   |       | 2.2.2 Polyhedral Cache Design                                 | 55 |  |

|   | 2.3   | Experimental Evaluation                                       | 57 |  |

|   | 2.4   | Conclusion                                                    | 61 |  |

|   | Bibli | iography                                                      | 63 |  |

| 3 | Enei  | gy Effective 3D Stacked Hybrid NEMFET-CMOS Caches             | 65 |  |

|   | 3.1   | Introduction                                                  | 66 |  |

|   | 3.2   | Low Power Short Circuit Current Free  NEMFET Inverter         | 67 |  |

|   | 3.3   | Low Leakage 3D-Stacked Hybrid NEMFET-CMOS Caches              | 69 |  |

|   |       | 3.3.1 3D-Stacked Hybrid NEMFET-CMOS Memory                    | 69 |  |

|   |       | 3.3.2 3D-Stacked Hybrid NEMFET-CMOS Caches                    | 72 |  |

|   | 3.4   | System Level Evaluation                                       | 74 |  |

|   |       | 3.4.1 Evaluation Methodology and Metrics                      | 75 |  |

|   |       | 3.4.2 Analysis                                                | 77 |  |

|   | 3.5   | Conclusion                                                    | 78 |  |

|   | Bibli | iography                                                      | 81 |  |

| 4 | ls TS | SV-based 3D Integration Suitable for Inter-die Memory Repair? | 83 |  |

|   | 4.1   | Introduction                                                  | 84 |  |

|   | 4.2   | Redundancy Based Memory Repair                                | 85 |  |

|   |       | 4.2.1 Previous Work in 3D Memory Repair                       | 87 |  |

|   | 4.3   | 3D Inter-die Memory Repair Architecture                       | 88 |  |

|   | 4.4   | 3D Inter-die Memory Repair Infrastructure                     | 90 |  |

|   |       | 4.4.1 Inter-die Row Replacement                               | 90 |  |

|   |       | 4.4.2 Inter-die Column Replacement                            | 93 |  |

|   | 4.5   | Discussion                                                    | 94 |  |

|   | 4.6   | Conclusion                                                    | 97 |  |

|   | Ribli | lography                                                      | 00 |  |

| 5   | Low     | Cost Multi-Error Correction for 3D Polyhedral Memories 101 |

|-----|---------|------------------------------------------------------------|

|     | 5.1     | Introduction                                               |

|     | 5.2     | ECC for Polyhedral Memories                                |

|     |         | 5.2.1 On Die Internal ECC                                  |

|     |         | 5.2.2 Dedicated Die ECC                                    |

|     | 5.3     | Performance Evaluation                                     |

|     |         | 5.3.1 Error Correction Capability                          |

|     |         | 5.3.2 On Die Internal ECC Overhead                         |

|     |         | 5.3.3 Dedicated Die External ECC Analysis                  |

|     | 5.4     | Conclusion                                                 |

|     | Biblio  | ography                                                    |

| 6   | ו חפר   | C-Based Adaptive                                           |

| •   |         | Error Correction for 3D Memories                           |

|     | 6.1     | Introduction                                               |

|     | 6.2     | LDPC-based Error Correction Proposal                       |

|     | 6.3     | LDPC Decoder Design Space                                  |

|     | 6.4     | Evaluation                                                 |

|     | 6.5     | Conclusion                                                 |

|     | Biblio  | ography                                                    |

| 7   | Conc    | lusions and Future Work                                    |

|     | 7.1     | Summary                                                    |

|     | 7.2     | Future Research Directions                                 |

| Lis | t of Pu | ublications                                                |

| Saı | menva   | tting                                                      |

| Pro | positi  | ons                                                        |

| Cu  | rriculu | ım Vitae                                                   |

# List of Tables

| 2.1 | TSV Access Control Signals                          | 57  |

|-----|-----------------------------------------------------|-----|

| 3.1 | CMOS vs. hybrid NEMFET-CMOS Caches Comparison       | 73  |

| 3.2 | Processor Configuration                             | 75  |

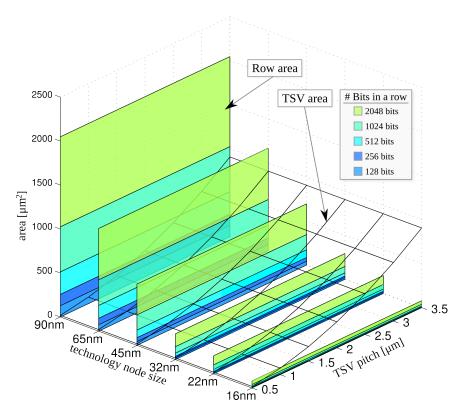

| 4.1 | TSV requirements for proposed schemes               | 95  |

| 4.2 | Required TSV pitch [ $\mu$ m] for 16nm 6T-SRAM cell | 97  |

| 6.1 | LDPC Encoders and Decoders in ASIC Implementations  | 130 |

# List of Figures

| 1.1 | Brief memory technology and computing system evolution road map.                                                                                                                                                | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | The processor - memory performance gap [8]. The memory baseline is 64 KB DRAM from 1980. In the last decades processor manufacturers gradually introduced several cache levels in an attempt to reduce the gap. | 9  |

| 1.3 | Technology process generations (adapted from [57])                                                                                                                                                              | 10 |

| 1.4 | Microprocessors trend data (adapted from [64])                                                                                                                                                                  | 12 |

| 1.5 | State of the art memory hierarchy overview                                                                                                                                                                      | 13 |

| 1.6 | 3D technology classification                                                                                                                                                                                    | 20 |

| 1.7 | TSV based 3D integration                                                                                                                                                                                        | 22 |

| 2.1 | Memory hierarchy                                                                                                                                                                                                | 53 |

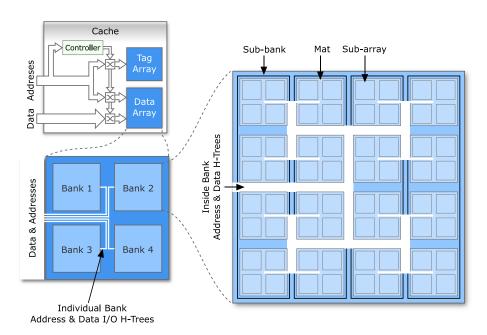

| 2.2 | Traditional cache and memory array layout                                                                                                                                                                       | 54 |

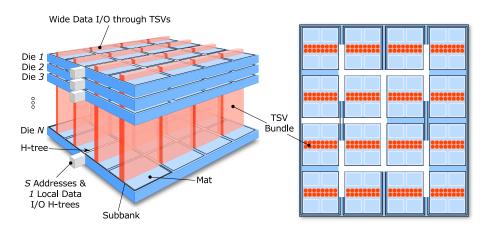

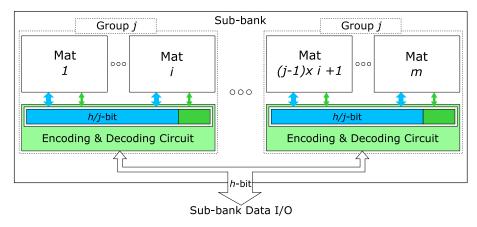

| 2.3 | Polyhedral memory array                                                                                                                                                                                         | 55 |

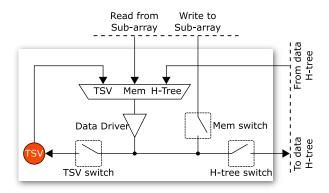

| 2.4 | Required TSV access logic                                                                                                                                                                                       | 56 |

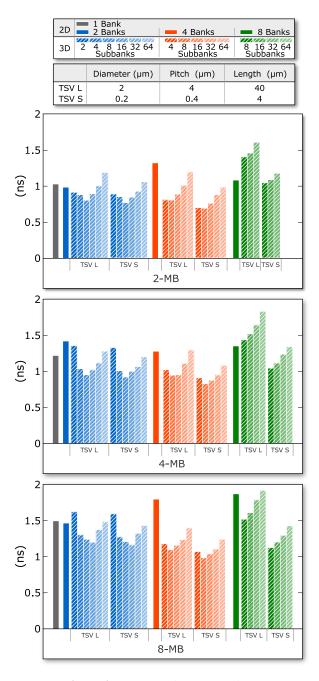

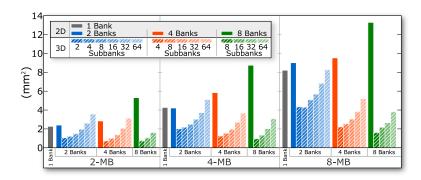

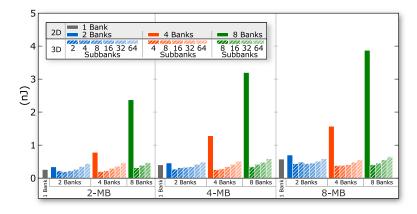

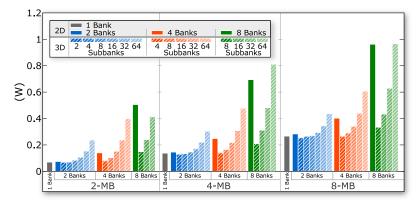

| 2.5 | Access time comparison                                                                                                                                                                                          | 59 |

| 2.6 | Footprint comparison                                                                                                                                                                                            | 60 |

| 2.7 | Read energy comparison.                                                                                                                                                                                         | 60 |

| 2.8 | Leakage comparison                                                                                                                                                                                              | 60 |

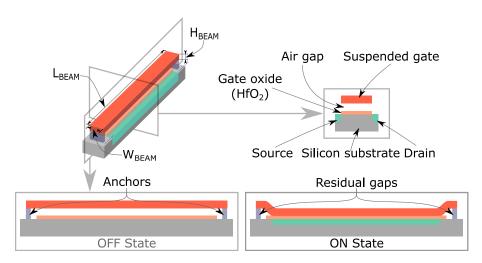

| 3.1 | NEMFET's geometry [8]                                                                                                                                                                                           | 68 |

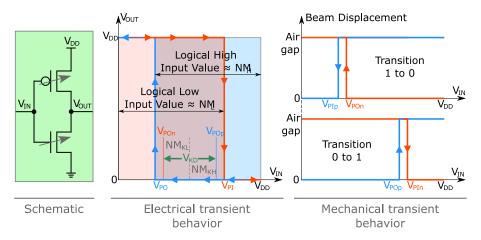

| 3.2 | NEMEET's inverter schematic and transient behavior                                                                                                                                                              | 69 |

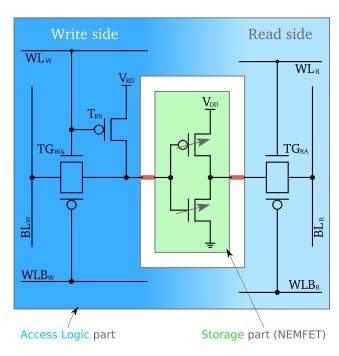

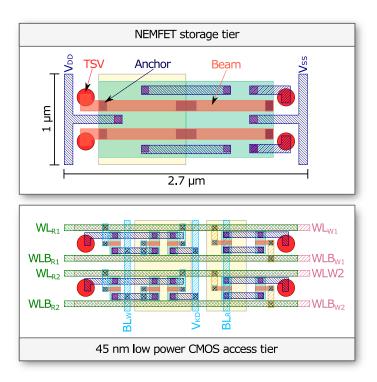

| 3.3 | Hybrid NEMFET-CMOS memory cell                                                                            | 70  |

|-----|-----------------------------------------------------------------------------------------------------------|-----|

| 3.4 | Two adjacent hybrid NEMFET-CMOS memory cells layout                                                       | 71  |

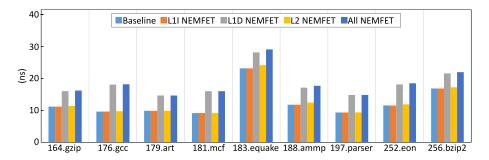

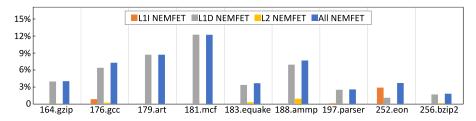

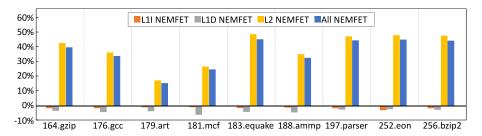

| 3.5 | L1 instruction cache average miss latencies                                                               | 76  |

| 3.6 | L1 data cache average miss latencies                                                                      | 76  |

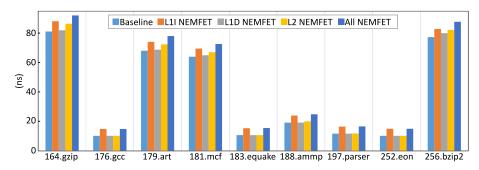

| 3.7 | IPC reduction relative to <b>baseline</b> (lower is better)                                               | 78  |

| 3.8 | Energy difference relative to <b>baseline</b> (higher is better)                                          | 78  |

| 4.1 | Memory redundancy with external (a) and internal (b) spares                                               | 86  |

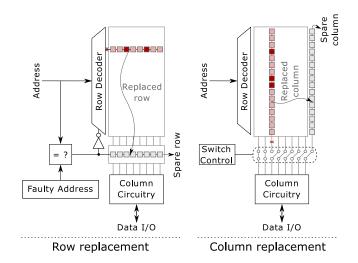

| 4.2 | General 2D internal redundancy                                                                            | 87  |

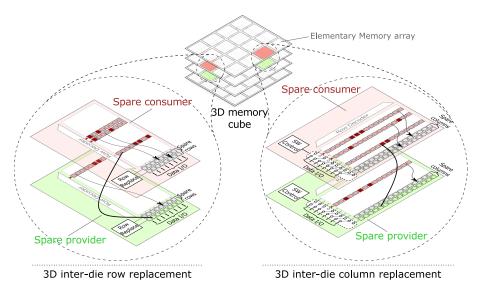

| 4.3 | 3D inter-die memory repair - general idea                                                                 | 88  |

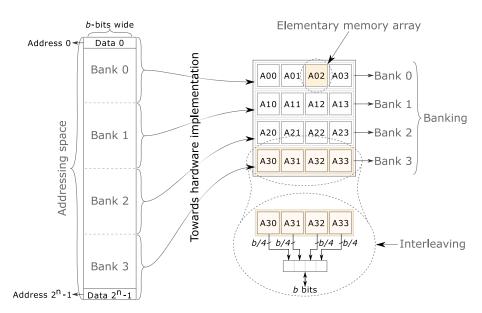

| 4.4 | Memory partitioning.                                                                                      | 89  |

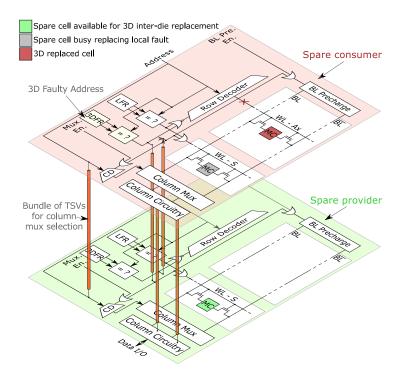

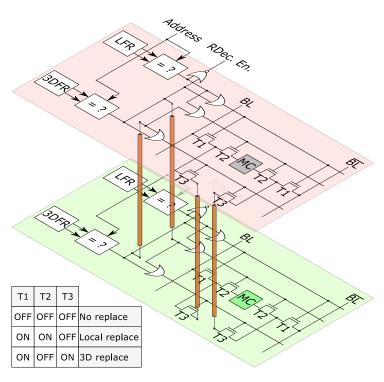

| 4.5 | Inter-die row replacement infrastructure with idle provider                                               | 91  |

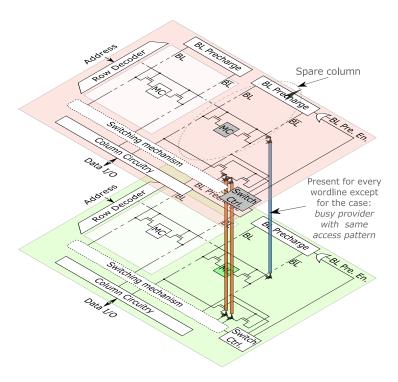

| 4.6 | Inter-die row replacement infrastructure parallel <i>consumer</i> and <i>provider</i> access              | 92  |

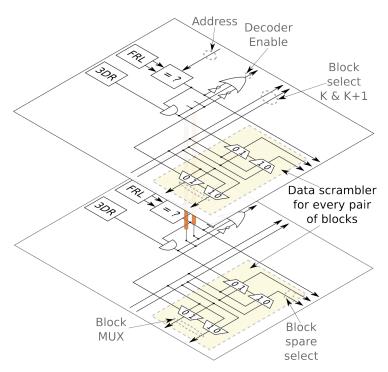

| 4.7 | Inter-die row replacement with "busy <i>provider</i> identical access pattern", divided wordlines, detail | 93  |

| 4.8 | Inter-die row column replacement infrastructure                                                           | 94  |

| 4.9 | TSV area overhead vs. row area for 32-bit data I/O                                                        | 96  |

| 5.1 | On die internal ECC for polyhedral memories                                                               | 04  |

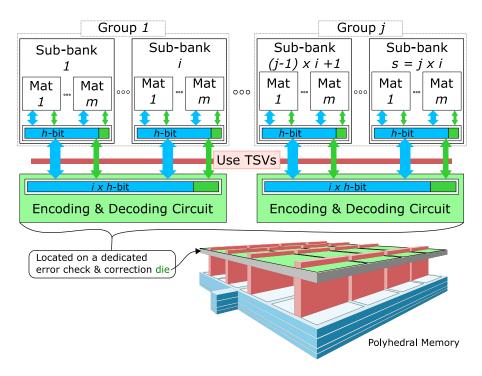

| 5.2 | MEC-based ECC for polyhedral memories                                                                     | 105 |

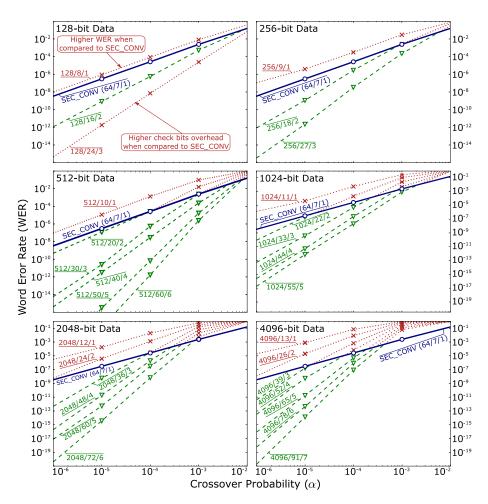

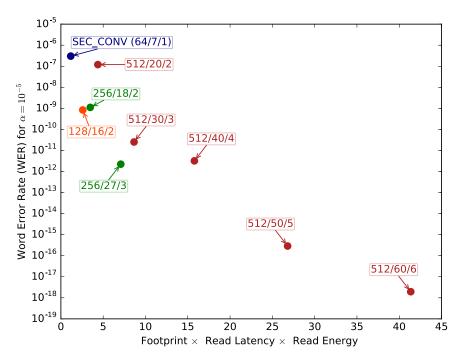

| 5.3 | Word error rate vs bit flip probability                                                                   | 109 |

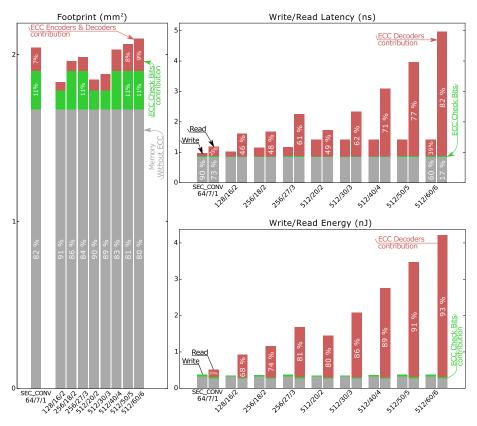

| 5.4 | On die internal ECC evaluation                                                                            | 10  |

| 5.5 | On die internal trade offs                                                                                | 11  |

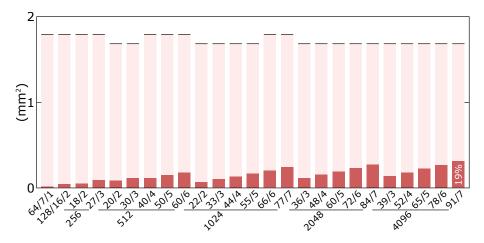

| 5.6 | Dedicated die ECC - footprint comparison                                                                  | 12  |

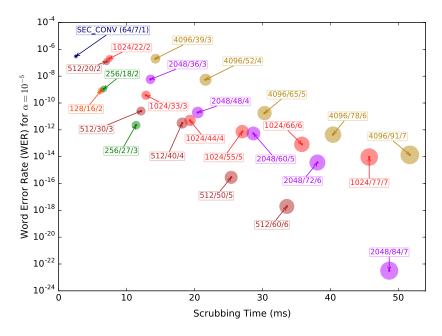

| 5.7 | WER vs. ideal scrubbing time                                                                              | 14  |

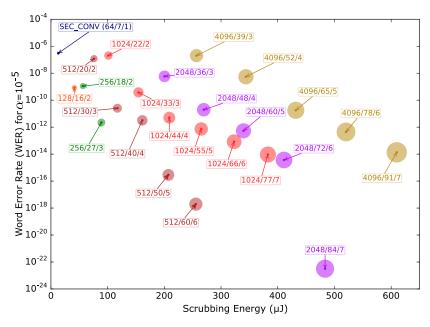

| 5.8 | WER vs. ideal scrubbing energy                                                                            | 15  |

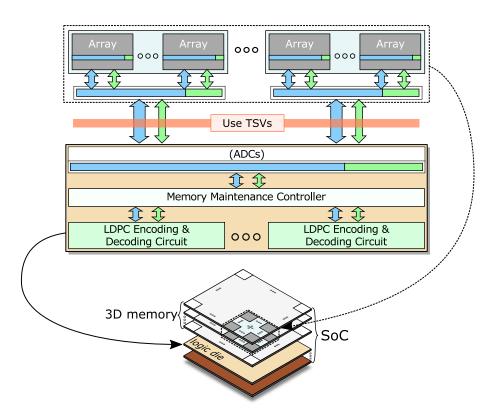

| 6.1 | LDPC-based error correction for 3D memories                                                               | 122 |

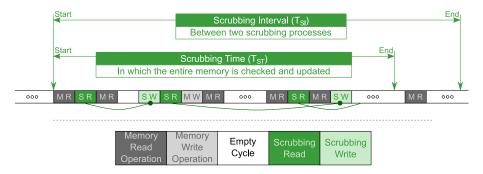

| 6.2 | Memory scrubbing timeline                                                                      |

|-----|------------------------------------------------------------------------------------------------|

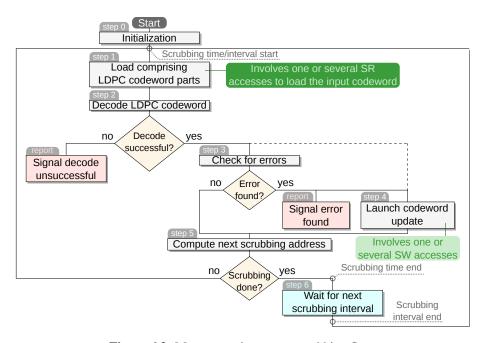

| 6.3 | Memory maintenance scrubbing flow                                                              |

| 6.4 | LDPC decoders summary                                                                          |

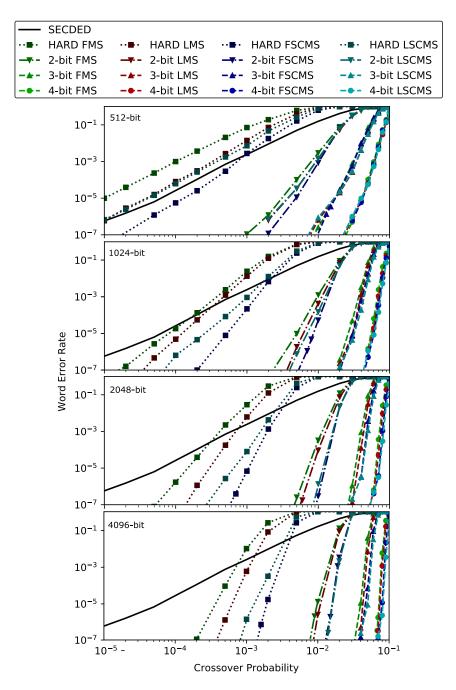

| 6.5 | LDPC vs extended Hamming                                                                       |

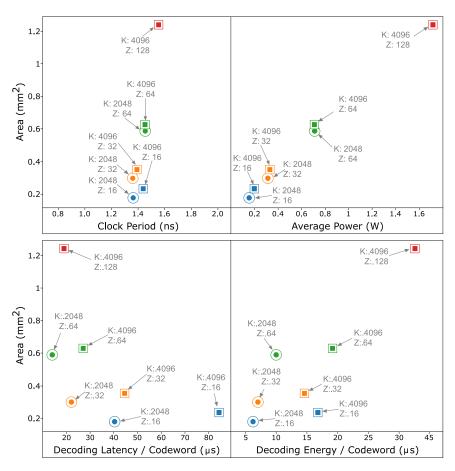

| 6.6 | Area vs. clock period, area vs. power, area vs. decoding latency, and area vs. decoding energy |

| 6.7 | LDPC error correction die real estate utilization                                              |

| 6.8 | L2 correction canability 13'                                                                   |

# Introduction

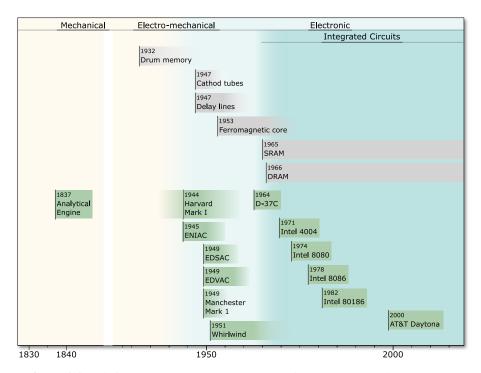

emory represents an essential constituent of any computing machine, along with data processing cores and transport infrastructure. It is utilized to store both the to-be-executed program instructions as well as the input/output information data and any other intermediate values. Memory capacity and behavior represent a key factor for the overall system performance and in the following we briefly describe its metamorphosis tightly coupled with the one of computing technology since its infancy up to state of the art, by following the time line depicted in Figure 1.1.

#### **Early Days**

In the 1830s Charles Babbage originated the programmable computer concept while conceiving a machine capable of automatically perform a large variety of mathematical calculations. He named it the *analytical engine* and his intentions were to revolutionize computation by mechanizing it. He saw this as highly necessary since the computer term in his time was referring to actual humans that were performing mathematical calculations in a very time inefficient and error prone manner, relying on mathematical tables printed on thousands of pages [1]. When Babbage was designing the analytical engine Faraday's work on electromagnetism was just about getting under way, while electrical circuits were only mathematically analyzed by Ohm. Hence, Babbage had to rely on existing technology, which at that time could provide mechanical components [1], with the steam engine being the only valid option to drive the entire assembly.

If built, the analytical engine would have weighted several tones, with the store unit, i.e., the today modern computer main memory equivalent, measuring 7 m in length and 3 m in height and width. It would have operated on 50 decimal

Figure 1.1: Brief memory technology and computing system evolution road map.

digit numbers, with the store unit consisting of about 1000 such entries. For each digit, i.e., a basic memory element, a 10-toothed metal wheel would have been utilized. An elaborate mechanical transportation way based on racks and pinions would fetch the decimal stored numbers to the processing unit, entitled by Babbage as the mill, since, once the numbers arrived at the input, they were milled around to get the results. Reliable Jacquard punched card loom technology would have been used for program input [2]. Even though Babbage was unable to construct the analytical engine, it is considered one of the first general purpose computer, since it was designed to contain all the modern computer core components [2]. A key element in the analytical engine design was the ability to perform conditional branching. This, together with a potentially theoretical limitless memory store unit, makes the analytical engine a Turing complete machine, a concept unheard of at that time.

Inspired by Charles Babbage's work, Howard Aiken designed in the 1930s a general purpose computer, named Mark I [3]. In contrast to his predecessor, Aiken was living in an era in which electronic components developed substantially to allow for their utilisation in computers. Mark I was an electromechan-

ical computer and was constructed during the 1940s by IBM in collaboration with Harvard University. Its memory consisted of 72 adding storage and 60 constant registers, each 23 decimal digits long, implemented as electromechanical counter wheels. Punched paper tapes together with switch positions were employed for program input [4].

Shortly after Mark I's development, which was to remain operational until 1959, electromechanical computers became obsolete as they were too slow paced for the highly dynamic post WWII world. The first fully operational electronic computer, called ENIAC (Electronic Numerical Integrator and Calculator), was built in the mid 1940s [5]. Even though it was designed for a specific military goal, i.e., to compute artillery firing tables, it was assembled too late to be used in the Second World War effort. Its first task still had a military purpose, being utilized to perform a series of complex calculations related to hydrogen bomb development. However, it was later utilized as a general purpose computer solving a steady stream of problems in a variety of fields ranging from number theory to meteorology, that demonstrated its versatility and power [2] and it remained operational until 1959 when it was disassembled. ENIAC was also a decimal machine, as its (electro)-mechanical predecessors. Its memory consisted of 20 accumulator registers, each capable of holding a 10-digit decimal number, with a ring, the electronic counterpart to the mechanical calculator's decimal wheel [2], of 10 vacuum tubes used for each digit [6; 7].

ENIAC's major drawback was that programming was manually executed by plugging up cables and setting switches, with input data being provided on punched paper cards. Reprogramming required from a half an hour to a whole day [7; 8]. The team behind the ENIAC, including John von Neumann, was aware of its time pressure induced limitations which resulted in a difficult machine programming manner, and wanted to improve this aspect. Already in 1945, when ENIAC was not yet entirely finalized, they were discussing about storing programs as numbers and published a first report draft [9] proposing a stored-program computer called EDVAC (Electronic Discrete Variable Automatic Computer), the successor of ENIAC. This was an inspiring memo that originated the stored-program concept, which was right away adopted by computer researchers worldwide. The stored-program concept is still the basis for nearly all digital computers today [7; 8]. Maurice Wilkes and his team from Cambridge University employed it during the construction of what is considered the world's first full scale operational stored-program computer [8], the EDSAC (Electronic Delay Storage Automatic Calculator), which became operational in 1949. The EDSAC logic was implemented by vacuum tubes and its

memory by ultrasonic mercury delay lines, a technology with origins in radar. The total memory consisted of 1024 storage locations, each being capable of holding a number with 16 binary digits plus a sign digit [10; 11]. In delay line memories, trains of electronic pulses are converted by means of quartz crystal into ultrasonic pulses, which are inserted into a special medium path that slows them down [12; 13]. From the delay element end they are fed back to the beginning through amplifying and timing circuits. Thus, delay line memories required periodic refresh in order to maintain their stored values, and provided variable latency sequential access only, for which complex extra access logic was required. However, they were much more reliable and cheaper then vacuum tubes flip-flops memory instances utilized, e.g., in ENIAC.

For sequential access memories data are always accessed one after the other, which allows for quick retrieval times when program execution does not encounter any branches, or when the operands reside one after the other. However, if an arbitrary address is encountered, the requested location needs to be sought first, an operation that can be extremely time inefficient. This was the case for delay line memories for which the seeking operation incurred unexpected delays and by implication program behavior. Thus, there was a stringent need in those times for the processor to be able to access a memory location in almost the same time interval, irrespective of the data physical location inside the memory, in order to ensure reliable execution times estimation. One of the first such Random Access Memory (RAM) implementations was the Williams-Kilburn tube, which stored data as electrically charged spots on the face of a cathode ray tube [14]. It was firstly utilized in the Manchester Small-Scale Experimental Machine (SSEM), which was not designed to be a practical computer, but to act as a proof of concept for the Manchester Mark 1 machine [15; 16]. The Manchester Mark 1 had two Williams-Kilburn CRTs as main memory holding a total of 128 words each 40 bit long. The today's equivalent of disk storage consisted in about 3000 words and was implemented by means of drum memory, a type of memory that stores information on the outside of a rotating cylinder coated with ferromagnetic material, which is circled by read/write heads in fixed positions [17]. Manchester Mark 1 developed into Ferranti Mark 1, which became the world's first commercially available general-purpose electronic computer in 1951 [18].

The Massachusetts Institute of Technology Servomechanisms Laboratory developed for the U.S. Navy between 1948-1951 the Whirlwind I computer [19]. Williams-Kilburn tube RAMs were among the considered options for the Whirlwind I memory implementation. However, to avoid the Williams-Kilburn tube required refresh times, a special kind of CRT electrostatic storage

tubes were chosen instead [20; 21], a decision that soon proved to be costly. The team behind the Whirlwind project quickly renounced the unreliable electrostatic storage tubes in favor of the newly proposed ferromagnetic core memories [22] for Whirlwind II [23], which was the first computer to make use of such a technology for its 2048 16-bit word memory. This proved a wise decision since magnetic core memories, which consisted of an array of multiple ferrite rings that exhibit a hysteresis curve, were by far more reliable than CRTs (or mercury delay lines), much cheaper, and required considerable less real estate. They soon became the element of choice for main memory implementations during the 1950s and were heavily utilized until the 1970s [24; 25].

By the beginning of 1950s computing systems were employing a hierarchical memory system: core memories were backed up by magnetic drums which were, in their turn, backed up by magnetic tapes. Starting from late 1950s a fast but small magnetic core memory was added as a slave for a slow, but much larger one, in such a way that the effective access time is nearer to that of the fast memory than to that of the slower memory. This marked the beginning of caches, which were formalized as a concept by Wilkes in 1965 [26]. The programmers dream of having almost unlimited amounts of fast memory at their disposal seemed somewhat possible due to the incipient memory hierarchies that ferromagnetic memories facilitated. This was however more achievable with the next significant technological discovery, i.e., the transistor, that became the fundamental building block of modern electronic systems. The field effect transistor was proposed as a concept in Canada by Julius Edgar Lilienfeld in 1926 [27] and in Europe by Oskar Heil in 1934 [28] in a time when it was not possible to actually construct a working device, and no one was able to do anything with it [29]. The breakthrough came in 1947 when John Bardeen, Walter Brattain, and William Shockley from Bell Telephone Laboratories implemented the first working bipolar transistor device [30]. Transistors quickly replaced electronic vacuum tubes in similar circuit configurations since they offered tremendous power reductions and smaller form factor, which resulted in considerable speed improvements and, as a side note, reduced for the moment the need for air conditioning [24]. Transistor logic, together with core memories brought significant improvement in reliability and there were no longer talks about "mean time to failure" [24], and remained essential computer building blocks for several years. The Manchester University experimental transistor computer, to become operational in 1953, is considered to be the first transistor based computer implementation.

# **Integrated Circuits Revolution**

Transistors contributed in a substantial manner to computer development, but very soon manufacturers were confronted with a problem that seemed insurmountable: the huge component number involved in projects was almost unmanageable in terms of design complexity and necessitated an excruciating and error prone effort in terms of hand wiring. For several years researchers went through what Bell Labs vice president Jack Morton entitled as "the tyranny of numbers" [31]. The solution came in 1959 when Jean Hoerni and Robert Noyce, both from Fairchild Semiconductor, introduced the planar manufacturing process [32] and the monolithic approach [33], respectively. These proposals completely revolutionized the semiconductor manufacturing technology and the Integrated Circuits (ICs) era started. The first working monolithic ICs were produced in 1960, credited to Jack Kilby from Texas Instruments [34] and Robert Noyce from Fairchild Semiconductor [33]. ICs from the early 1960s were manufactured with a low density fabrication process, known as Small Scale Integration (SSI), consisting of only a few transistors and provided limited computation functionality. Military and aerospace computer systems were among the first to benefit from the ICs applications in the mid 1960s, e.g., the D-37C computer used in the LGM-30 Minuteman intercontinental ballistic missile project in 1964 and the Apollo Guidance Computer developed by NASA in 1966 [35]. The integration scale rapidly rose though, approximately doubling every year, and by the end of 1960s Medium Scale Integration (MSI) emerged, with a chip transistor count of 100 or more. As ICs complexity increased, practically all computers switched to IC-based designs since more functionally complex logic devices such as adders and shifters could be easily implemented on a chip [36].

While processors were already benefiting from IC emergence, memories were still implemented based on ferromagnetic core technology, but this was about to change soon. In 1961 Bob Norman from Fairchild Semiconductor thought that it was practical to begin considering semiconductor devices implementing a flip-flop array for memory storage [37] and four years later the first Static RAM (SRAM) was proposed by Scientific Data Systems and Signetics. Implemented using bipolar technology it had 256 72-bit word capacity and an access time of 120 ns [38; 39]. Two years later the single transistor Dynamic RAM (DRAM) was invented by Robert Dennard from IBM [40; 41; 42], and in 1970, Intel, at the time a small start-up company specialized in memories [43], produced the first commercially available DRAM. The Intel 1103 MOS DRAM had a capacity of 1-Kb, an access time of 300 ns, and was nicknamed

"The Core Killer" [39]. This was the beginning of the end for ferromagnetic memories, which by the mid-to-late 1970s were completely replaced by semi-conductor memories as the primary computing systems storage devices.

Intel was part of another important evolutionary step in 1971 with the introduction of the first single-chip microprocessor, the Intel 4004 [44; 45]. Produced in the beginning of the Large Scale Integration (LSI) period, Intel 4004 processor was fabricated with a 10  $\mu$ m silicon-gate enhancement load pMOS technology, consisted of 2300 transistors, and was able to operate at a maximum clock frequency of 740 KHz [45; 46]. Implemented on a 12 mm<sup>2</sup> die, this revolutionary microprocessor could execute a total of 0.092 Million Instructions Per Second (MIPS), which was almost twice as much as the first electronic computer, the ENIAC, which filled an entire room [47]. The 4004 microprocessor was part of the Micro Computer System 4 (MCS-4) chip-set that included three other chips, namely 4001 Read Only Memory (ROM), 4002 Random Access Memory (RAM), and 4003 Shift Register [46], and allowed for the easy realization of small computers with varying memory amounts and I/O facilities. Subsequently, in 1974 Intel introduced the 8080 microprocessor that operated at a maximum clock frequency of 3 MHz [48]. This is considered the first true general-purpose microprocessor [49], since it did not require the presence of additional chips as it was the case for 4004, and it was the core of Altair - the first personal computer.

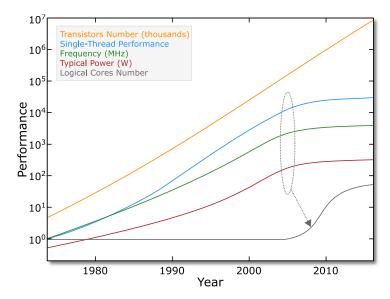

Since 1970s ICs density underwent a staggering revolution following quite rigorously the insightful prediction initially stated in 1965 [50] and further formalized in 1975 [50] by Gordon Moore, that per die transistors count will grow exponentially. Moore's initial projection was for at least a decade, but being adopted as a target guideline by the semiconductor companies in order to maintain their market position, it prevailed for the past 5 decades. From 2300 transistors, for Intel 4004 in 1971, using the 10  $\mu$ m process technology, to 7200000000 transistors, for Intel Xeon Broadwell-E5 in 2016, using 14 nm process technology, is a six order of magnitude increase. This technology development allowed for different capabilities to be gradually included for processor performance improvements. For example, in the beginning of 1970s the transistor high rate count increase was used to advance the architecture from 4-bit, to 8-bit, to 16-bit, and to 32-bit microprocessors in the early 1980s, when between 25000 and 50000 transistors could fit on a single chip [8]. 32-bit processors remained the norm until the early 1990s when they were slowly replaced by their 64-bit successors, which are still manufactured today, while 128-bit instances not being expected too soon.

The above presented technology evolution enabled for a  $10^8 \times$  MIPS increase over the last six decades [51], while the computing power cost has decreased exponentially [52]. Many challenges were overcame in order to maintain a sustained miniaturization trend that allowed for today's pocket-sized devices to be more powerful than 1960s-1980s supercomputers that took up entire rooms. Subsequently, computing systems were uniquely adopted and spread virtually to all economy sectors, from defense industry, aerospace, telecommunications, to automotive, health, and food industries. However, in order to keep up with the continuously developing market requirements, many challenges are still to be faced by computer designers, with the most important ones being present in the next section while keeping the main focus on memory hierarchy technology and architecture.

# 1.1 Modern Processor Design Challenges

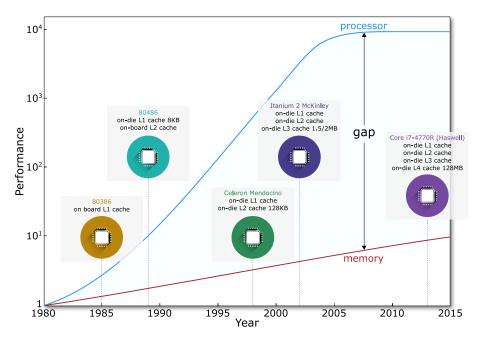

Initially, microprocessor chips were operating at smaller frequencies than main memory DRAM chips, together with which they were teamed up to form computing systems since 1970s, while by the beginning of the 1980s, microprocessors and memories reached somewhat similar operating frequency levels. The Intel 8086 processor, launched in 1978, which would give rise to Intel's most successful line of processors, the x86 architecture family, operated at 5 MHz frequency, i.e., 200 ns clock period, while its successor, Intel 80186, launched in 1982, operated at 6 MHz, i.e., 166 ns clock period. At the same time, in 1980, a 64 Kbit DRAM had a row access time between 150-180 ns and a (read/write) access time of about 250 ns[8]. This balance abruptly changed by the end of the 1980s when logic performance started to substantially surpass memory performance and the well known processor-memory bottleneck [53] (also known as the memory wall [54]) emerged. As detailed in Figure 1.2, microprocessor performance increased 1.52× per year between 1986 and 2000, and 1.2× per year between 2000 and 2005, while DRAMs experienced only a 1.07× yearly performance increase over the 1980-2005 period [8].

While logic operations once represented the processor bottleneck, the 1980s fabrication technology revolution (scaling) allowed for, e.g., faster clock rates, extensive instruction level parallelism with about 20 stages deep pipelines, out-of-order execution, and sophisticated instruction fetch units. These developments, combined with the aforementioned gently DRAM performance increase, led to a data availability crisis. Considering a hypothetical and greatly simplified scenario with a processor operating at 800 MHz and a memory run-

**Figure 1.2:** The processor - memory performance gap [8]. The memory baseline is 64 KB DRAM from 1980. In the last decades processor manufacturers gradually introduced several cache levels in an attempt to reduce the gap.

ning at 100 MHz, for each single memory access, 8 processor clock cycles are elapsed. This could lead to the processor being forced to wait 7 cycles until the data that reside in the memory are retrieved, an inefficient situation since those 7 cycles are practically waisted.

In an attempt to bridge the processor - memory gap, i.e., to be able to feed the processor with enough data to diminish the number of memory waiting generated stall cycles, different solutions were employed. Wilkes' idea of caching, proposed for core memories in the 1960s, was among the considered approaches and it proved to be somewhat successful. To benefit the most from this solution a faster memory than DRAM was required. SRAM proved to be the best cache implementation choice, since, even though much more expensive than DRAM, it was much faster. Initially, caches were introduced on-board, e.g., for Intel 80386 launched in 1985 [55; 56], and then on-chip, when the semiconductor technology reached a certain point and was able to eliminate the chip crossings between processor and cache memories by their co-integration. The first processor with an integrated on-chip cache was Intel 80486 introduced in 1989. To further mitigate memory speed and capacity re-

**Figure 1.3:** Technology process generations (adapted from [57]).

quirements, after almost a decade a second cache level was added in 1998 for the budget oriented Celeron Mendocino processor. Very soon after, in 2002, the third cache level was introduced for the Itanium 2 McKinley processor, that was targeted towards enterprise servers and high-performance computing systems. Other manufactures followed the same scenario and at present times a three level SRAM cache hierarchy is the norm. Quite recently, in 2013, Intel included a fourth cache level implemented with embedded DRAM (eDRAM) technology. The complex multi-level cache hierarchy present in modern processors was enhanced by the aggressive technology scaling which allowed for increased integration density, a topic that is further detailed in the next section.

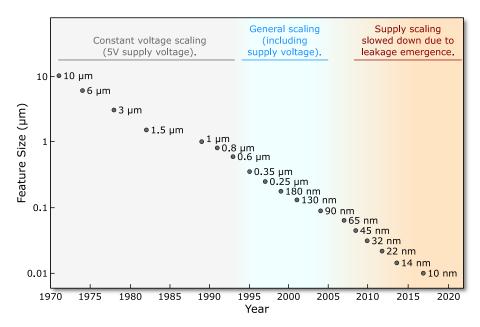

# 1.1.1 Technology Scaling

The feature size of a CMOS process refers to the minimum transistor length with which devices can be reliable manufactured [57]. Continuous technology scaling consisting in a feature size reduction by 30% every two to three years, as depicted in Figure 1.3, was a major driving force behind constant improvements in ICs performance, area and power reduction. At the core of this process was Robert Dennard's observation from 1970s that the basic transistor operational characteristics can be preserved and its performance improved

when some critical parameters are scaled by a dimensionless factor [58]. These parameters include device dimensions (i.e., gate length, width, and oxide thickness) and voltage, that are downscaled, and doping concentration densities, that are upscaled by the inverse of the same factor.

The reduction of the power supply voltage was considered by the industry undesirable from a system level perspective since it would have break the plug-in compatibility with every new generation [59]. Hence, a 5 V constant supply voltage scaling was performed up to through the early 1990s, an approach that offered quadratic delay improvement and maintained continuity in I/O voltage standards, but it increased device breakdown risk and power consumption become unacceptable [57]. Therefore, since the half-micron node downward general Dennard scaling became the norm, even though the supply voltage did not follow exactly the scaling factor applied to device dimensions [57], and was very successfully employed by the industry up until the 130 nm generation node in the early 2000s. At that technology node the gate oxide thickness reached about 1.2 nm and electron tunneling through such a thin dielectric lead to an abrupt increase of the leakage current. This posed significant challenges to technology scaling that were further addressed by introducing innovations in transistor materials and structure [60]. Examples in this direction include: strained silicon transistors introduced by Intel for the 90 nm technology [61], high-k metal gate transistors utilized in Intel's 45 nm technology [62], and the more notorious FinFET (tri-gate) transistors employed in Intel's 22 nm technology [63].

Technology feature size shrinking was a major driving force behind ICs transistor count exponential growth and, since with scaling transistors generally improve in performance, behind the continuous clock frequency increase, which, e.g., for Intel's microprocessors, doubled approximately every 3 years from their introduction until 2005. This contributed to a sustained overall processor performance improvement, as summarized in Figure 1.4, that, even though transistor scaling continued, began to saturate by mid 2000s. The main reason behind was that, in contrast to transistors, IC wire delays do not diminish with decreased feature size. This may not seem to be a problem for local wires, that run within functional units and which are short enough for their resistance to not matter, or for semi-global wires, that run between functional units and for which an appropriate number of repeaters could result in enough speeding up [57]. For global wires however, that run across an entire chip, even with multiple repeaters their delays are getting bigger as technology scales. Thus, the time to cross a chip in a nanometer process increases substantially, making wire delays becoming the dominant issue for each clock cycle

**Figure 1.4:** Microprocessors trend data (adapted from [64]).

and a major design limitation for large integrated circuits [8; 57]. In addition to wire delays, power developed also into a real concern for circuit designers and the combination of the two led to a stall in uniprocessor frequency increase and has limited the instruction level parallelism exploitation. Aware of this concerns and since it was easy to envision that the integration level was about to soon allow for a billion transistors per chip, in 1990s several studies suggested that both software and technology trends have reached the point when one should start favoring chip multiprocessor microarchitectures [65].

One of the first manufactured multiprocessor chip was AT&T Daytona [66], a four core digital signal-processor, introduced in 2000 [67]. However, the real paradigm switch occurred only after 2005 when multiple general purpose multi-core processors reached the market [8; 67]. Since then Intel has been adding about two more cores per generation and performance increase became more of a programmers burden in that it requires a switch to a parallel software design paradigm [8].

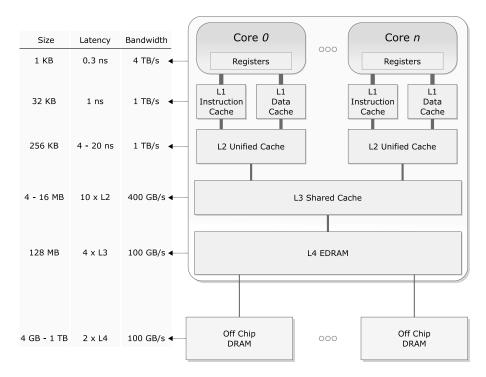

After the 2005 shift towards multi-core chip processors there has been no substantial improvement noticed for frequency and single-thread performance. The focus moved on memory hierarchy, to improve data availability, and other architectural concepts related to parallel computing. To get some insight into those developments we depict in Figure 1.5 a state of the art multi-core processor memory hierarchy. At the top the register files are the smallest but fastest

Figure 1.5: State of the art memory hierarchy overview.

memories that operate at the core frequency, in the order of a few GHz, and which are supported by separate instruction and data L1 caches, each of about 32 KB and operating at about 1 GHz frequency. A unified L2 cache level follows, which is about  $8\times$  larger than an L1 instance, 4 to  $20\times$  slower, and feeds both L1 caches. The next cache level is shared by all the cores, being slightly larger than the L2, and about  $10\times$  slower. This shared L3 can be optionally followed by an 128 MB  $4\times$  slower fourth level cache implemented with eDRAM technology, which constitutes the last on-chip memory element. Further down the hierarchy, on the motherboard, several memory channels ensure communication with external DRAM chips, which are  $2\times$  slower than the L4, but offer several times more storage capacity.

Having presented the modern processors' state-of-the-art in terms of technology and architecture, we next focus on detailing the challenges currently faced by computing system designers.

# 1.1.2 Ensuring Data Availability in Multi-core Processors

It can be noticed from Figure 1.5 that multi-core processors put more pressure on the memory hierarchy since they significantly increase the bandwidth requirements. This is easily observable for the shared L3 cache, since in the multi-core context it has to supply data for multiple L2 caches instead of only for one, as it used to be the case for single-core processors. As a result, L3 generates more requests further down the memory hierarchy leading to a natural off-chip DRAM traffic escalation when the cores number increase. With a memory bandwidth increase limited by the pin count growth, which is about 10% per year, and considering that the an on-chip core number is doubling every 18 months, today's processor designers are facing a bandwidth wall [68]. The provided off-chip memory bandwidth should sustain the rate at which memory requests are generated, otherwise adding more cores to the chip will not yield any additional performance. Thus, it is futile to expect overall performance gains from multi-core systems proportional to the increase in the cores number without substantial memory and its afferent interconnection redesign.

Several methods to increase the off-chip bandwidth have been proposed. A shared DRAM controller design that provides a fair thread DRAM access policy to boost system throughput is introduced in [69]. A self-optimizing memory controller design that operates using the principles of reinforcement learning is presented in [70]. In [71] the authors propose to exploit processor inactivity periods due to memory stalls, i.e., when the processor is waiting for data to be fetched from the off-chip memories, in order to improve off-chip bandwidth. Based on the fact that in those pausing intervals the processor requires much less power, since the frequency is usually scaled down some power delivery pins become available and can be used for data transport to ensure extra bandwidth. Unfortunately, while being able to bring certain benefits, the presented methods off-chip bandwidth increase is limited, since in the best case it can only reach a theoretical maximum, which considering the current pin number constraints, is not sufficient to feed the multi-processor cores with enough data.

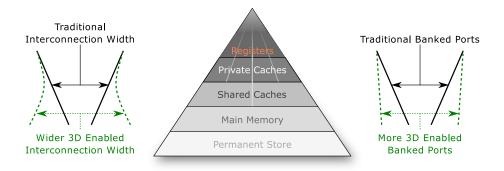

A step forward from the technology perspective is represented by the emergence of three dimensional stacked ICs, which seem to provide a promising solution to this DRAM bandwidth problem, since they allow for an amount of interconnection unconceivable in current 2D off-chip designs [72]. While we detail this approach later in this chapter (see Section 1.2), it is important to note here that it puts additional pressure on the last level shared cache, which is expected to become the data traffic bottleneck at the processor to DRAM

frontier. Thus, it is of high interest to investigate novel multi-port memory designs to be employed as shared caches, such that a sustained high amount of parallel accesses can be served and processor data availability is ensured, a topic that is addressed in Chapter 2 of this thesis.

In the next subsection we focus on static power dissipation, which reduction represents another modern processor design challenge that emerged due to technology scaling.

# 1.1.3 Processor Design Within a Restricted Power Envelope

CMOS technology was renowned for its manufacturing process simplicity and its almost "zero" static power consumption characteristic, aspects which contributed substantially to its dominance. However, already since reaching the Very-Large-Scale Integration (VLSI) level, that enabled ICs to hold hundreds of thousands of transistors, power consumption developed as the most important constraint in circuit design, overcoming traditional area and delay metrics [73]. Generally speaking, CMOS circuit power dissipation can be broken up into three main categories: dynamic, short circuit, and static power. In the past, its dynamic constituent represented the main dissipation source and performance-driven technology scaling allowed for substantial dynamic power consumption reductions. However, since the MOSFET threshold voltage scalability frontier limits the power supply voltage reduction, technology scaling is no longer able to sustain the same amount of power reduction [74]. In addition, static power, which is dissipated by leakage currents that flow even when the device is inactive, increases abruptly with technology scaling and becomes a significant component of the overall power consumption [75; 76]. There are several leakage sources for MOS transistors [77], with the most significant being considered the subthreshold leakage, the gate leakage, and the junction leakage [57]. According to ITRS [78] subthreshold and gate leakage are projected to exponentially increase with MOSFET feature size scaling. The gate leakage current is relatively smaller then the subthreshold leakage for older technologies, but it is expected to be comparable to the subthreshold leakage current in the deep nanometer nodes [77].

Since in modern chip multiprocessor systems a significant real estate is dedicated for storage, in some cases considerably larger than 50%, memory represents a major contributor to the overall system power consumption [8; 79; 80; 81; 82; 83; 84]. Experimental results from [80] indicate that the leakage power consumption of L2 caches becomes almost 40% of the total power of cores, interconnect, and L2 caches. Simulations from [84] suggest

that the total static energy ranges from 80%, for a two-core two-issue 8 MB L2 processor, down to 30%, for an eight-core eight-issue 1 MB L2 processor. For mobile targeted devices, in which the processors are designed in a less aggressive manner in order to fit within a tight power budget, the caches can account for 25% to 50% of the total power consumption [8]. Thus, reducing the memory power consumption directly implies an important overall energy benefit for chip multiprocessor systems and there has been a large body of work in this direction.

Several circuit level memory power reduction techniques were proposed, e.g., forced transistor stacking [85] or PMOS-based pull-up networks with domino logic [86]. Alternatives that combine circuit with architectural techniques were also introduced. One of the first such approach [87; 88], which is also mostly employed, consists in gating (shutting off) the SRAM cells comprising inactive cache blocks. The decision upon which cache blocks are turned off is crucial since it is highly desirable to obtain significant power benefits with little penalties in terms of performance. For single threaded single processor systems the decision can be taken by considering the characteristics of the only executing program, thus cache blocks are turned off if they are not accessed for a predefined, or dynamically adapted, threshold time-out cycles [89; 90; 91; 92]. For chip multiprocessor systems many challenges are present since multiple threads are simultaneously executed on multiple processors and their cache blocks might interact with each other. Several methods were proposed, including virtual exclusion [93], an architectural technique that saves L2 caches leakage by keeping the data portion of repetitive but infrequently accessed cache lines off, given that locality allows for such entries to be already present in L1. Other approaches consist in turning off cache lines by using the coherence protocol invalidations, utilizing cache decay techniques specific for coherent caches [94], employing a dynamical way adaptation mechanism [95; 96], or by exploiting replicated cache blocks [80]. It is important to mention that for all the above techniques performance penalties are incurred.

Despite of all the above efforts, a static power increase with threshold voltage reduction is always expected for future CMOS devices. This represents a serious technology scaling limitation that generates a stringent need to investigate alternative memory designs based on the utilization of emerging devices with "zero" leakage currents. Before completely moving to novel emerging devices, considering the CMOS technology maturity, hybrid approaches seem to be the next natural step forward, a direction which is further explored in more detail in Chapter 3 of this thesis.

In the next subsection we focus on the last modern processor design challenge addressed in this dissertation, the ensuring of dependable memory operation in the context of increased technology scaling induced device variability.

#### 1.1.4 Memory Dependability in the Nano Scale Era

In addition to the above presented static power wall emergence, with technology feature size reduction increasingly smaller geometries should be handled. This leads to a less precise manufacturing process, with more defects being induced, which make transistors more prone to various in-field failures. Maintaining ICs reliability at the desired market demanded level became a critical challenge which is to be addressed both at design-time and at runtime [97].

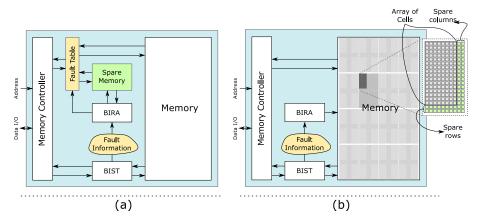

Memories are susceptible to both hard failures, related to the physical breakdown of a device or an interconnect, and soft errors, usually triggered by radiation striking a chip that corrupts the stored information. Considering that memory cells are typically designed with a minimum silicon area and occupy most chip real estate, memories are most sensitive to process variations and device mismatch than other semiconductor-based electronic devices. Fortunately, their regular structure makes it easy to enhance their design such that repair mechanism are incorporated to improve reliability. Such a method consists in the addition of redundant spare rows and columns for hard error correction. This dates back many decades, being firstly proposed and utilized for 64 Kb DRAMs in 1979 [98]. The employed spare types as well as their number depend on the anticipated defect density, with the important mention that even a small amount of redundant elements can make a big difference in yield. Originally, testing and repair, i.e., bad rows/columns disabling and spares allocation, were performed in factory, with special equipment being required for that. With device miniaturization, it became possible to incorporate built-in self test and repair mechanisms in memory chips and allow for on-field test and repair.

Since scaling trends have considerably reduced memory cell size, an increasing soft error rate has been observed. This is due to the smaller charge stored on the memory cells and the considerable increase in chip storage capacity [57]. Memories became extremely sensitive to soft errors and Error Correction Codes (ECCs) have been utilized to cope with this issue. Extended Hamming ECCs [99], which are still the norm in this respect, use additional 8 check bits to any 64-bit memory word to correct one error and detect any pair of errors in the word. The additional check bits and the corresponding mechanism increase memory area and add delay penalties, but Single Error Correction

Double Error Detection (SECDED) ECCs able to make use of information redundancy to improve reliability have been utilised for decades. However, once entering the 100 nm era, Multi-Bit Upsets (MBU) become much more frequent since a particle hitting a memory array creates disturbances in multiple physically adjacent cells [100; 101; 102; 103]. Column interleaving methods [104; 105; 106] were proposed as a solution but this seems not to suffice any longer as according to [107] an MBU multiplicity of over 100 bits is predicted for 32 nm and 22 nm SRAM generations. This clearly suggests that state of the art schemes are not effective any longer and research effort is required towards improved ECC techniques capable to cope with the increasing error amount.

In view of the above, it is crucial to investigate alternative avenues that enhance memory dependability. More specifically, designs that allow for increased spare access could provide improved possibilities for memory repair. In addition, Multi-Error Correction (MEC) codes might provide the means to mitigate the detrimental effects of high MBU multiplicity. We follow in this thesis both directions in Chapters 4, 5, and 6. The context of the emerging technology enablers is detailed in the following section.

#### 1.2 Technology Enablers

With CMOS technology reaching its scaling limits [108; 109] and the stringent need to maintain the same computing systems performance rate gains, a multitude of alternatives are being investigated. In the following we provide a brief overview of emerging technologies that could continue the same miniaturization and performance trends established in the Moore's law context, while providing means to overcome the processor design challenges detailed in Section 1.1.

#### 1.2.1 3D Integration Technology

Conventional ICs are sandwich-like structures created by superimposing several layers of conducting and insulating materials. The base surface for the manufacturing process comes in the form of a silicon wafer that serves as both mechanical support and electrical common point. Utilizing a fabrication sequence that involves a series of deposition, lithography, etching, and implant steps, a transistors layer is firstly built on the silicon substrate, after which several metal interconnect layers are constructed [57]. By harnessing the third vertical dimension, the technology to manufacture 3D integrated circuits can

vertically stack multiple such traditional IC layers. 3D integration technology is emerging as a promising avenue to overcome some physical, technological, and economical limits encountered in conventional ICs. In the following we detail the motivations behind the 3D technology development, afterwards continue with a brief 3D technology manufacturing classification, and end this subsection by presenting state of the art 3D technology utilization proposals for memory hierarchies.

#### **Motivation**

The development of the 3D integrated circuit technology has been driven by the need to provide viable solutions to issues that cannot be any longer properly addressed only within the framework of planar IC designs as follows:

#### • Interconnect latency

The continuous transistor feature size down-scaling has shifted the dominant latency factor from devices to interconnection wires [110]. Contemporary TSVs are copper pillars with electrical properties comparable with normal metal wires. By placing adjacent blocks on top of each other, millimeter long wires can now be shortened to the micrometer lengths of the vertical interconnections. In [111] it is theoretically proven that by 3D stacking global interconnect wire length scale with the square root of the stacked layer number.

#### • Power consumption

Shortening of wires also has a direct effect on power usage as less heat is dissipated in the wires. Although a vertical interconnection is expected to dissipate more heat than a normal horizontal metal wire, the significant reduction in total wire length plus the fact that wire repeaters are no longer required, compensate so that the global power consumption is lower for a 3D stack. Even more, larger power savings are obtained through the removal of now obsolete power-hungry transceivers for inter-die communications links, i.e., high speed parallel and/or serial links between processing cores or between cores and memory, in 2D system in package realizations.

#### • Heterogeneous integration

The ability to integrate heterogeneous technologies onto the same chip has been one of the first and main drivers as there are a large number of applications which can benefit greatly from this, ranging from micro-

**Figure 1.6:** 3D technology classification.

and nano-sensors with Micro-/Nano-Electro-Mechanical-Systems and CMOS logic layers to high-performance computing cluster nodes with optical, memory and logic layers. Furthermore, various emerging technologies proposed to replace CMOS-based computing can use 3D technology as an enabler for hybrid transitional circuits.

#### • Form factor

Apart from system architecture related aspects and performance, the form factor of the complete system can be a key factor precluding the utilization of 2D circuits in space confined applications. By allowing for vertical chip grows 3D stacking opens more miniaturization opportunities of which many applications could benefit from and in this way enable new applications introduction [112].

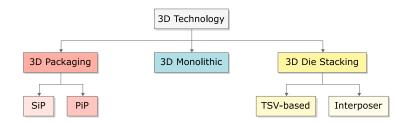

#### 3D Technology Classification

In the last few years, 3D technology has garnered a lot of interest and significant progress towards commercial availability has been made. Several manufacturing approaches are currently prototyped consisting of three main classes, as depicted in Figure 1.6: 3D packaging, 3D monolithic, and 3D die stacking.

In 3D packaging, multiple dies are stacked vertically at the packaging level. Interconnects between the dies I/Os are typically formed by wire-bonding, flip-chip, or Ball-Grid-Array (BGA) stacking, approaches that provide the lowest interconnect density from all the mentioned 3D classes. A subclass of the 3D packaging approach is the System-in-Package (SiP), in which the system comprises severals stacked ICs internally connected by fine wires bonded to the substrate and packaged in a single chip. Being the most mature approach, SiPs are widely employed in mobile devices, digital cameras, and portable audio players [113; 114]. Another 3D packaging subclass is Package-On-Package

(PoP) technology where multiple packaged chips are stacked vertically [113]. This can include several SiPs packages.

In the *3D monolithic* approach [115] the first circuit layer is constructed in a similar fashion to traditional 2D CMOS ICs. Next, a dielectric is added on what would have been the last metal layer for the 2D only approach, on which a new circuit layer consisting of transistors and several metal layers is built. This procedure is repeated until the desired number of 3D circuit layers is achieved, which are interconnected using nano-scale inter layer vias, with no bonding materials being required between the circuit layers. While the monolithic approach provides the highest vertical interconnect density between the stacked layers, it is very challenging to ensure a low-temperature process for the upper devices in order to not destroy the metallization and devices in the bottom layers [116].

An alternative approach is 3D die stacking, which consists in manufacturing each circuit layer on a separate silicon wafer and then bond either wafers, sliced dies, or sliced dies to unsliced wafers to create 3D Stacked Integrated Circuits (3D-SIC). The inter-die interconnection link can be either physically implemented by micro-bumps and/or with Through-Silicon-Vias (TSVs) [112; 117; 118], or by employing a contactless communication method based on capacitive [119; 120] or inductive coupling [121; 122]. Contactless interconnection schemes face several challenges, the most prominent consisting in ensuring power supply, that slow down their adoption [123]. On the contrary, utilizing TSVs as interconnects between stacked planar dies is perceived as being the most promising approach for the current technology status [124], which is also sustained by the fact that semiconductors industry players have already announced TSV based stacked chip products [125; 126].

A special class of die stacking, known as "2.5D", consists in "stacking" multiple dies side-by-side on a silicon interposer carrier, a technology that is already supported by certain design tools [127]. The interposer is only used to connect the active dies by means of TSVs and wires, which makes 2.5D-SICs easier to manufacture, however they are typically less effective than 3D-SICs in terms of power dissipation in interconnects, bandwidth, and off-chip I/O density [128]. In this dissertation we focus on TSV-based 3D-SICs, which are detailed next.

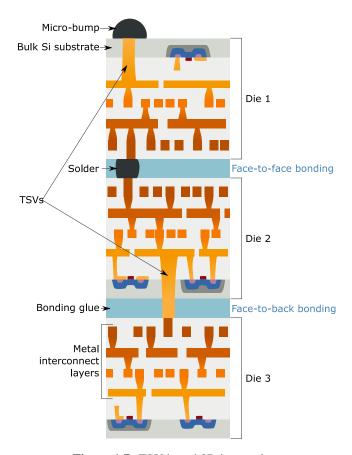

#### **TSV Based 3D-SICs**

The idea of vertically integrating multiple layers of active electronic components into a single circuit through TSVs was envisioned more than 50

Figure 1.7: TSV based 3D integration.

years ago [129]. It was revisited multiple times since then, when semi-conductor engineers thought Moore's law could be stalled by technology issues [129; 130; 131]. In Figure 1.7 is depicted a conceptual 3 layer TSV based 3D integrated circuit that employs the two main stacking techniques, i.e., Face-to-Face (F2F) and Face-to-Back (F2B). In F2F bonding two tiers are stacked such that the very top metal layers are connected. Note that since wafer bonding does not go through a thick buried silicon layer, micro-bumps can be employed as tier interconnects. In F2B bonding device layers are stacked with the top metal layer of one bonded together with the substrate of the other one, requiring in this case TSVs utilization [132]. TSVs are actually holes that traverse the entire silicon substrate and are filled with a conducting material, e.g., copper or tungsten, in order to allow for inter tier communication. TSVs formation can occur at several IC manufacturing stages: via-first, via-middle, via-

last, and via-after-stacking [133]. Via-first TSVs are manufactured prior to the front-end of line, i.e., before transistors are fabricated, and must be filled with doped poly-silicon which has a relatively high resistance. Via-middle TSVs are manufactured between the front-end of line and back-end of line, i.e., before the metal layers are fabricated and typically copper or tungsten is utilized as filling material. Via-last TSVs are manufactured after back-end of line, either prior or post thinning. Compared to via-first and via-middle TSVs, via-last TSVs have the advantage that foundries without TSV processing equipment already may manufacture the whole IC. Finally, in the via-after-stacking approach TSVs are manufactured as the last 3D processing step.

With respect to bonding, there are three methods: Die-to-Die (D2D), Die-to-Wafer (D2W), and Wafer-to-Wafer (W2W) [133]. Although complex, a high alignment accuracy is feasible in D2D and D2W bonding at the cost of a low production throughput. On the other hand, handling very small dies becomes impractical for both D2D and D2W methods, which is simpler for W2W bonding. However, W2W bonding requires stacking dies with same sizes, which makes this approach only suitable for applications with a high degree of regularity, e.g., memories and FPGAs. In addition, W2W stacking negatively impacts the compound yield as it is impossible to prevent good dies stacking over bad dies. This is not the case in D2D and D2W bonding methods, which make use of pre-bond testing prior to the actual stacking to prevent faulty dies from entering the 3D mounting process, which results in an improved compound yield [133].

Having detailed the 3D-SIC technology, next we focus on state of the art research that attempts to exploit its benefits in today's complex memory hierarchy subsystems.

#### **3D Memory Hierarchies**

Harvesting 3D technology advantages is possible at different circuit and architectural levels. First, memories as independent circuits can directly benefit from, e.g., the 3D wire length reduction, since their internal regular structure facilitates for easy storage element distribution across multiple layers. Various 3D caches and DRAMs have been proposed in this direction, and even commercial products, such as [125], are available. Additionally, new avenues are also opened at the circuit level in terms of facilitating reliability improvements [134; 135]. Next, the entire multiprocessor memory hierarchy can benefit from 3D technology, since memories themselves can be distributed in the chip 3D space. Thus, technology can ease again the introduction of new archi-

tectural concepts. In the following we review some key strategies applicable at both circuit and architecture levels.

The process of partitioning memories across multiple device layers can take place at different granularities as follows:

#### • Array stacking

The coarsest 3D memory granularity partitioning takes place at the array level and consists in stacking multiple arrays on the top of each other. We include in here also entire bank stacking, i.e., multiple cell arrays with their afferent address decoders, write drivers, etc. An important overall reduction in wire length is obtained (about 50% for certain configurations), which is translated into significant power and delay gains [136; 137; 138]. The 3D 2 Gb DRAM manufactured by Samsung reported in [125] is based on this bank stacking approach.

#### • Intra-array stacking

This approach, considered to lead to a true 3D memory [136], breaks the array boundaries and consists in splitting the cells connected to the same bit-line or word-line in groups and placing each group on a different tier [136; 137; 138]. The first approach is also known as *divided-columns* while the latter as *divided-rows*. The peripheral logic, i.e., row decoders, sense amplifiers, column select logic, etc., can be separated from cell arrays and placed on one dedicated layer. This allows for an independent optimization of the peripheral logic for speed, while the cell arrays can be arranged to meet other criteria, e.g., density, footprint, thermal, etc. Research in this area has been performed for both SRAMs [136; 137] and DRAMs [139; 140]. Examples of 3D manufactured SRAMs and DRAMs based on cells stacked on logic are presented in [141]and [142; 143], respectively.

#### • Intra-cell (bit) partitioning

At this finest granularity level memory cell components are split among one or more layers. The relative small cell size makes the actual implementation of this splitting approach rather impossible for DRAMs. Nevertheless, this option can be feasible for multi-port SRAM arrays, used for example in register file implementations, since they have a larger area than the single port ones, and the cell access transistors could be split among multiple layers [136].