# Modeling and Analysis of System-on-Chip Address Maps

Master of Science Thesis Delft University of Technology

Niels Mook

# Modeling and Analysis of System-on-Chip Address Maps

July 17<sup>th</sup>, 2024

## THESIS

# submitted in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

in

#### EMBEDDED SYSTEMS

by

Niels Mook born in Leiden, the Netherlands

under supervision of

Arie van Deursen Soham Chakraborty Erwin de Kock Bas Arts

Programming Languages Group Department of Software Technology Faculty EEMCS Delft University of Technology Delft, the Netherlands www.ewi.tudelft.nl

System Design & Verification Group Department of Design Enablement Chief Technology Office NXP Semiconductors Eindhoven, the Netherlands www.nxp.com

© 2024 NXP Semiconductors, Delft University of Technology, Niels Mook.

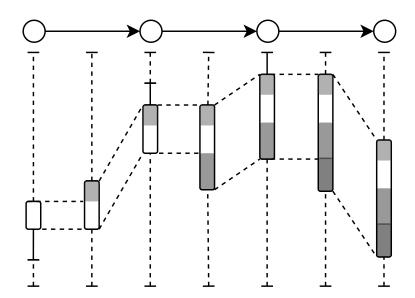

Cover picture: Simplified address-axis diagram example with three shifts and clips.

# Modeling and Analysis of System-on-Chip Address Maps

Author:Niels MookStudent id:4607279Email:n.l.c.mook@student.tudelft.nl

#### Abstract

This thesis presents a methodology for the formal verification of memory organizations in System-on-Chip (SoC) designs described in IP-XACT. The approach involves modeling the address map structures of the design's IP-XACT description and its spreadsheet-based global address map specification into a unified graph model we developed, called an Address Map Graph (AMG). Additionally, it introduces an analysis of AMGs to determine the equivalence of their mapped addresses, called Graph Bitmapping Equivalence (GBE). The methodology was implemented through a series of modular programs integrated into a solution flow. These programs process the spreadsheet memory specifications and IP-XACT design representations into AMGs and perform efficient GBE calculation and detailed reporting. The solution was evaluated using a state-ofthe-art mid-size SoC design as a case study. Verification of results was performed using commercially available design analysis tools. The results demonstrated the developed solution was effective to analyze and verify the memory organization of complex SoC designs and to assist in identifying the causes of discrepancies.

Thesis Committee:

| Responsible Professor: | A. van Deursen, Faculty EEMCS, TU Delft                 |

|------------------------|---------------------------------------------------------|

| Company Supervisor:    | E. de Kock, Chief Technology Office, NXP Semiconductors |

| Company Supervisor:    | B. Arts, Chief Technology Office, NXP Semiconductors    |

| University Supervisor: | S. S. Chakraborty, Faculty EEMCS, TU Delft              |

|                        |                                                         |

# Preface

This thesis not only marks an end to a nine-month research and internship, but also to my master's degree and education at TU Delft, as to my formal education at large starting in Gouda. At each step, I have strived to reach the maximum of my potential, which made the road challenging but also exciting and rewarding.

I want to thank my daily supervisors from NXP, Erwin de Kock and Bas Arts, for your fantastic onboarding, patience, and support for the entire duration of the internship. You have been my mentors but also closest colleagues for the past nine months. I want to thank you for your critical feedback, which I feel has refined both the thesis as well as myself into something better.

I want to thank my daily supervisor from TU Delft, Soham Chakraborty, for your support, valuable advice and feedback throughout the thesis. I also want to thank Arie van Deursen from TU Delft for your feedback and enablement of this opportunity.

My time at NXP Semiconductors in Eindhoven has been inspirational, educational, and I am grateful for the warm welcome and support I received from Bram Kruseman and the rest of the team. Thank you for your good company in and outside the office.

Finally, I want to express my deepest gratitude to my parents and my brothers, who have encouraged and supported me throughout my studies. Last but not least, I am thankful for the love and presence of my dogs through this period. With fulfillment and this gratitude, I close this chapter of my life with this work and look forward to grow and apply my knowledge further in the coming years.

> Niels Mook Delft, the Netherlands July 12, 2024

# Contents

| Pr | eface          | i                                     | ii |

|----|----------------|---------------------------------------|----|

|    |                | Preface                               | ii |

| Co | ontent         | te                                    | v  |

| CU | /iterit        |                                       | v  |

| Li | st of <b>F</b> | Figures                               | x  |

| 1  | Intro          | oduction                              | 1  |

|    | 1.1            | System-on-Chips                       | 1  |

|    | 1.2            | Motivation                            | 1  |

|    | 1.3            | Objectives                            | 2  |

|    | 1.4            | Contributions                         | 2  |

|    | 1.5            | Related Work                          | 3  |

|    |                | 1.5.1 UVM                             | 3  |

|    |                | 1.5.2 Kactus2                         | 3  |

|    |                | 1.5.3 SystemRDL                       | 4  |

|    |                | 1.5.4 CMSIS-SVD                       | 4  |

|    | 1.6            | Overview                              | 4  |

| •  | n 1            |                                       | _  |

| 2  |                |                                       | 7  |

|    | 2.1            |                                       | 7  |

|    |                |                                       | 7  |

|    |                | , , , , , , , , , , , , , , , , , , , | 9  |

|    |                |                                       | 2  |

|    | 2.2            | 0                                     | 3  |

|    |                | 0 1                                   | 3  |

|    |                |                                       | 4  |

|    |                | 0                                     | 4  |

|    | 2.3            | 1 1                                   | 5  |

|    | 2.4            | 1                                     | 6  |

|    |                |                                       | 6  |

|    |                |                                       | 8  |

|    |                | 0                                     | 9  |

|    |                |                                       | 0  |

|    | 2.5            | Bitmapping Calculation                |    |

|    |                | 0 11 0                                | 1  |

|    |                | 11 0                                  | 3  |

|    | 2.6            | Graph Bitmapping Equivalence (GBE)    | 5  |

|   |      | 2.6.1 Bitmapping Address Function                               |

|---|------|-----------------------------------------------------------------|

|   |      | 2.6.2 Bitmapping Set Address Function                           |

|   |      | 2.6.3 Bitmapping Set Equivalence                                |

|   |      | 2.6.4 Node Mapping                                              |

|   |      | 2.6.5 Graph Bitmapping Equivalence                              |

|   | 2.7  | Formal Problem Statement                                        |

| 3 | Solu | ation 27                                                        |

|   | 3.1  | Overview                                                        |

|   |      | 3.1.1 Tools                                                     |

|   |      | 3.1.2 AMG Model Representation and Serialization                |

|   |      | 3.1.3 Test Cases During Development                             |

|   | 3.2  | AMG Construction from Global Address Map Specification          |

|   |      | 3.2.1 Program Arguments                                         |

|   |      | 3.2.2 Configurable Spreadsheet Layout 29                        |

|   |      | 3.2.3 Construction Procedure                                    |

|   | 3.3  | AMG Construction from IP-XACT Description    31                 |

|   |      | 3.3.1 Program Arguments                                         |

|   |      | 3.3.2 Extension of Node Fields with IP-XACT Identifiers         |

|   |      | 3.3.3 Construction Procedure                                    |

|   | 3.4  | Node Mapping   36                                               |

|   | 0.1  | 3.4.1 Program Arguments                                         |

|   |      | 3.4.2         CSV File Layout         37                        |

|   |      | 3.4.3 Node Mapping Procedure                                    |

|   | 3.5  | Graph Bitmapping Equivalence Assessment                         |

|   | 0.0  | 3.5.1 Program Arguments                                         |

|   |      | 3.5.2 GBE Assessment Procedure                                  |

|   | 3.6  | Solution TCL Scripting Flow       47                            |

|   | 5.0  |                                                                 |

| 4 | Eval | uation 49                                                       |

|   | 4.1  | Report Structure         49                                     |

|   | 4.2  | Bitmapping Comparison Scenarios and Report Results 50           |

|   | 4.3  | Analysis and Interpretation of Non-Equivalences                 |

|   |      | 4.3.1 Analysis Methodology                                      |

|   | 4.4  | Solution Application                                            |

|   |      | 4.4.1 Causes of Non-Equivalence                                 |

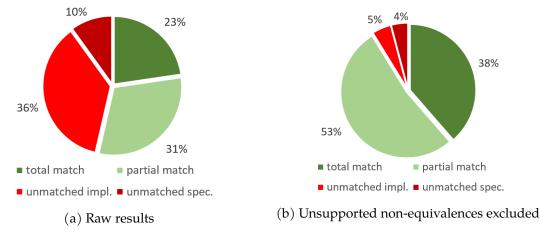

|   | 4.5  | Results                                                         |

| 5 | Con  | clusion 57                                                      |

|   | 5.1  | Summary                                                         |

|   | 5.2  | Discussion                                                      |

|   |      | 5.2.1 Definition of the AMG model and GBE                       |

|   |      | 5.2.2 Processing of Memory Specification XLS Files into AMGs 58 |

|   |      | 5.2.3 Processing IP-XACT Designs into AMGs                      |

|   |      | 5.2.4 Checking AMGs for GBE                                     |

|   |      | 5.2.5 Key Observations                                          |

|   | 5.3  | Future Work         59           59         59                  |

|   | 2.0  | 5.3.1 GBE Analysis for AMGs of Equal Type                       |

|   |      | 5.3.2 Dynamic IP-XACT Address Maps                              |

|   |      |                                                                 |

63

# Bibliography

| Ac | Acronyms |                                                |    |  |

|----|----------|------------------------------------------------|----|--|

| A  | Α        |                                                | 67 |  |

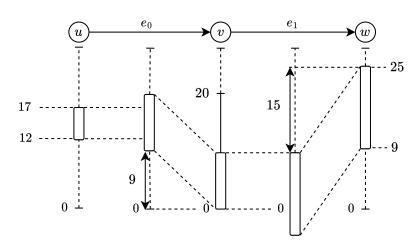

|    | A.1      | Bitmapping Example Calculation                 | 67 |  |

|    | A.2      | Bitmapping Maximization Correctness Test Cases | 69 |  |

# List of Figures

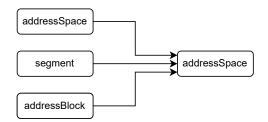

| 2.1  | IP-XACT object references                                                | 8  |

|------|--------------------------------------------------------------------------|----|

| 2.2  | Diagram of a local memory map in IP-XACT                                 | 9  |

| 2.3  | Diagram of a memory map in IP-XACT                                       | 9  |

| 2.4  | Diagram of an IP-XACT construct using a transparent bridge               | 10 |

| 2.5  | Simplified diagram of an IP-XACT construct using an opaque bridge        | 11 |

| 2.6  | Detailed diagram of an IP-XACT construct using an opaque bridge          | 11 |

| 2.7  | Diagram of an IP-XACT construct using a channel                          | 12 |

| 2.8  | Simple address map structure with two hierarchical interconnects         | 12 |

| 2.9  | Example contents of (a) an addressBlock and (b) an addressSpace $\ldots$ | 13 |

|      | Example contents of a segment defined in $AS_0$ of Figure 2.9b           | 14 |

|      | Example specification spreadsheet in default layout                      | 16 |

|      | Identified memory element mapping streams                                | 17 |

|      | Memory element mapping stream processed into the model                   | 18 |

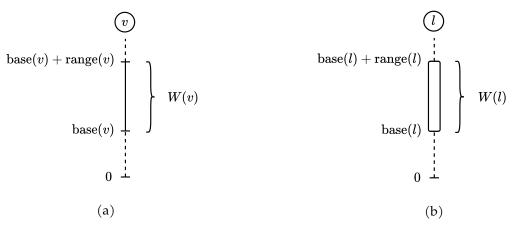

|      | AAD of (a) a non-leaf node and (b) a leaf node                           | 21 |

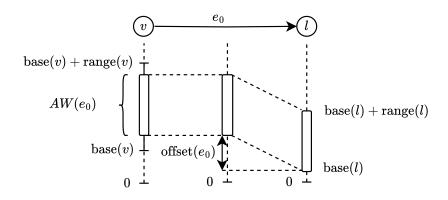

|      | AAD of the address mapping of a leaf node                                | 22 |

|      | AAD of the address map of a non-leaf node                                | 23 |

|      | AAD a final edge that clips top and bottom addresses                     | 24 |

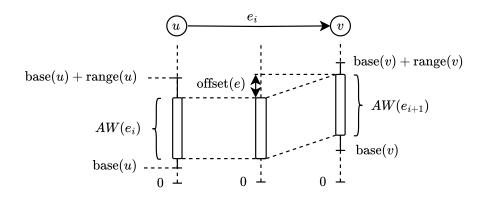

| 2.18 | AAD of a bitmapping along two edges                                      | 25 |

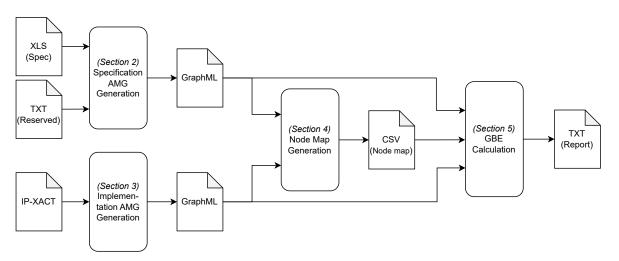

| 3.1  | Overview of the implemented solution flow                                | 27 |

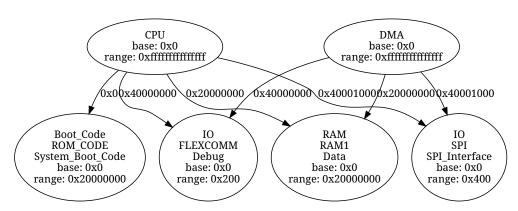

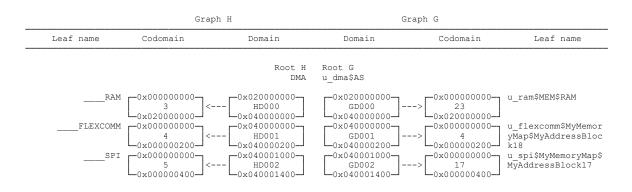

| 3.2  | AMG graph visualization of an example specification                      | 30 |

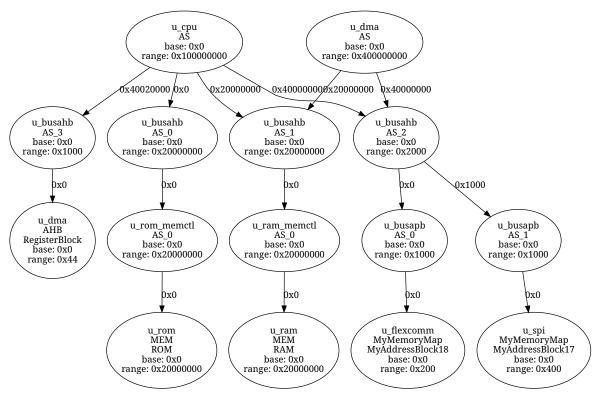

| 3.3  | AMG graph visualization of an example implementation                     | 33 |

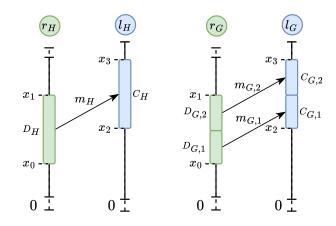

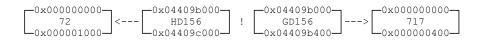

| 3.5  | Bitmappings from two graphs that implement the same address function     | 39 |

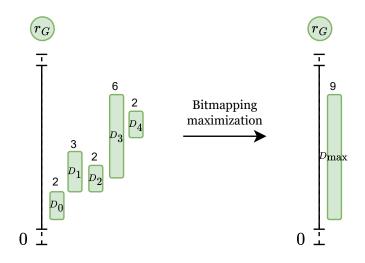

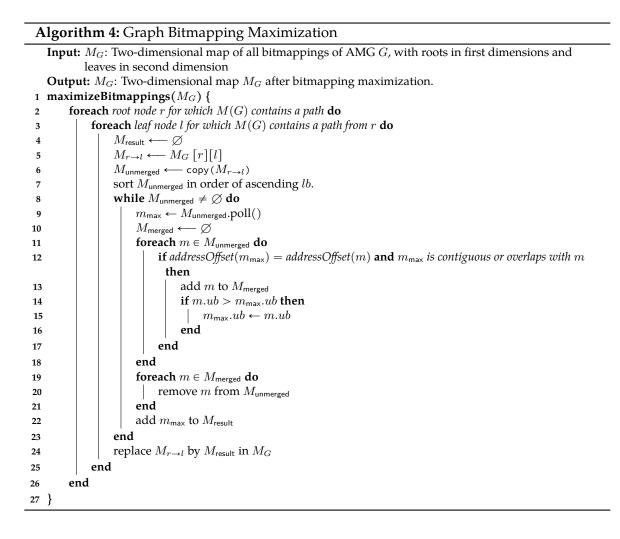

| 3.6  | Example bitmapping maximization problem                                  | 40 |

|      |                                                                          |    |

| 4.1  | Header and first entries of a GBE report example                         | 50 |

| 4.2  | Example of a path trace                                                  | 50 |

| 4.3  | Two bitmappings with total equivalence                                   | 51 |

| 4.4  | Two bitmappings with partial equivalence                                 | 51 |

| 4.5  | An implementation bitmapping without equivalent specification bitmapping | 51 |

| 4.7  | The distribution of evaluation bitmapping equivalence scenarios          | 54 |

| A.1  | Example path with two edges                                              | 68 |

|      | 1 1 0                                                                    |    |

# Chapter 1

# Introduction

## 1.1 System-on-Chips

At the heart of system-on-chip (SoC) design lies the process of integrating diverse intellectual property (IP) blocks – ranging from processors and peripheral interfaces to memory controllers and connectivity modules – into one system. SoC integration enables the creation of highly specialized and optimized systems to meet the high demands of modern embedded applications. Central to the integration of an SoC is its global address map, which specifies the address space allocated to peripheral IP blocks within the system. The implementation of the global address map through mappings of IP memory facilitates the routing of data and control signals across the SoC. Initiator IP blocks initiate data transactions in the SoC. The implemented address maps enable initiator IP blocks in the SoC to access and control peripheral IP blocks by reading from or writing to its designated addresses. Address maps thereby connect individual IPs into a cohesive system.

The timeline of SoC development has strict deadlines to minimize its time-to-market, enforcing software to be developed in parallel with hardware. This requires architects to define the SoC global address map at an early stage in the design process. The process of defining an global address map specification is often ad-hoc in nature. In consequence, the use of unconstrained, non-standardized text documents and spreadsheets for describing the global address map is prevalent among companies [1]. Consequently, the address map must be redefined in standardized formats at a later points in the design flow, in order to realize, verify, and document the address map. While designers and developers try to adhere to the prescribed global address map, its implementation in other formats is currently prone to human error.

## 1.2 Motivation

During SoC integration, the description of address map implementations plays a critical role. To formalize these descriptions, a standardized format is used, such as IP-XACT (IEEE Standard 1685) [2]. IP-XACT is an eXtensible Markup Language (XML) standard that is widely used to describe the aforementioned SoC integration. Once expressed in IP-XACT, the address maps implemented by the IP-XACT description together form its memory structure, which represents a possible implementation of the global address map specification. A specification describes how peripheral memory should be addressable by the SoC, typically as a single address map. However, the memory structures that implement the specification can be complex. One address map in the specification may be realized by multiple address maps in the implementation, allowing for intermediate address maps to take any form and paths through the design, as long as the addresses are mapped according to specification. To avoid bugs in SoC products, it is essential to thoroughly verify the IP-XACT descriptions for SoC designs, especially given the complexity and often manual construction. Typical verification methodologies today construct complex testbenches and run elaborate simulations to perform the functional verification of an integrated SoC design. Such methodologies take a significant amount of time, while not verifying the correctness of implemented address maps directly. Instead, the correctness of the design is verified based on its correct functioning. A direct and formal verification method of address maps implemented by IP-XACT descriptions against their global address map specification could improve efficiency in this context by providing immediate verification of implemented address maps before functional verification or even during IP-XACT development.

# 1.3 Objectives

This thesis aims to find a methodology for the formal verification of address map implementations in IP-XACT descriptions (implementations) against their global address map spreadsheet (specification) in order to improve the efficiency of the current verification methodologies. To do this, this thesis addresses the following four research questions:

- **RQ0**: What unified data model represents both a memory implementation and specification, and enables the comparison of their address maps?

- **RQ1**: What algorithms process a memory specification XLS file into the unified data model?

- RQ2: What algorithms process the IP-XACT files of an SoC into the unified data model?

- **RQ3**: What algorithms check any two unified data model instantiations for equivalence in address maps?

# 1.4 Contributions

The main contributions of this thesis are:

- Definition of a unified data model, called the *Address Map Graph* (AMG) to represent address maps of both memory implementations described by IP-XACT and memory specifications outlined in XLS files. This includes the definition of the *Address-Axis Diagram* (AAD) format to illustrate the path of an AMG; a *bitmapping* representing the mapping of contiguous bit addresses between two nodes in the AMG; and the equivalence in mapped addresses between two AMGs, called *Graph Bitmapping Equivalence* (GBE).

- Implementation of a parser to process memory specification XLS files into the AMG data model.

- Development and implementation of an algorithm to transform hierarchical IP-XACT descriptions into the AMG data model.

- Development and implementation of an algorithm to determine GBE between an implementation and specification AMG and to generate a text-based report of found bitmappings equivalences and non-equivalences for debugging purposes.

- Integration of all algorithm implementations into a solution flow that is modular for extension purposes to other specification and implementation standards.

# 1.5 Related Work

Only a few studies have been conducted on the topic of formal memory map description, including its modeling and visualization. Besides these, we will discuss the standards that have been established for functional SoC verification and formal memory description.

# 1.5.1 UVM

The Universal Verification Methodology (UVM) [3], [4] is currently the most popular [5] methodology for the functional verification of SoC designs [6], [7]. However, UVM suffers from two drawbacks regarding address map verification:

Firstly, the verification of address map implementations against their specifications using UVM takes significant time, involving the construction of complex testbenches and elaborate simulations. Furthermore, the verification consists of development-simulation-debugging-coverage cycles [5], which can take substantial time in the SoC design process. Reducing the duration of these verification cycles is crucial to achieve efficiency in this methodology.

Secondly, the debugging process is slowed down due to the ambiguity of the origin of the bugs it finds. To perform the verification, UVM generates a register model from the design's IP-XACT description that models the memory state of the SoC under test. This model is then used as reference to perform tests and verify its state under different circumstances. However, a found bug may be caused by an error in the design behavior, but it may also be caused by an error in the generated register model. An incorrectly generated register model may be caused by discrepancies between the global address map specification and the implementation by the IP-XACT description.

Our proposed formal verification could shorten the verification cycles, by indicating inconsistencies between specified and implemented address maps instantly compared to UVM. As such, bugs could be found before testbench construction or even during IP-XACT development. This could result in less bugs found in the verification cycles, and thus shorter debugging steps and shorter cycles.

Additionally, our proposed formal verification provides assurance of the correctness of the generated UVM register model. This is achieved by the verification of the memory organization implemented by the IP-XACT description from which the register model is generated. When the implemented memory organization conforms to the specified global address map, then there is a higher assurance that the register model generate from it contains less bugs, and thus that any bugs found by UVM are not due to errors in the register model, but errors in the IP-XACT functionality.

# 1.5.2 Kactus2

Pekkarinen, Teuho, and Hämäläinen have developed a method that is most relevant and comparable to the modeling aspect of this research; they have developed a graph-based method for analyzing the memory layout in IP XACT design hierarchies. They have built upon the foundations laid by Kamppi et al., who have developed a graphical electronic design automation (EDA) tool for intuitive use of the IP-XACT standard, called Kactus2 [8], [9]. Pekkarinen et al. [1] have developed a method of interpretation, representation, and visualization of the memory map information of an IP-XACT design into a graph model to analyze and edit the memory organization. This included an algorithm to traverse the entire design and generate the corresponding graph elements and properties. In the developed graph model, nodes represent interfaces of the IP block, while edges represent their connections through various IP-XACT constructs. Our graph model developed in this work differs fundamentally in that nodes represent the memory elements of the IP blocks rather than their interfaces. Furthermore, our research focuses on the automated and formal verification of IP-XACT design memory organization, rather than on visualization and editing. Finally, we hope to provide our solution as a verification tool that can be integrated in various workflows beside Kactus2.

The visualization of the resulting model has been improved further by their continued effort of creating a method of visual data compression [10]. This has resulted in a compressed version of the original visualization, to improve the clarity and ease of viewing and editing the memory structures in Kactus2. In contrast, our research visualizes memory structures in the form of directed graphs using the DOT format with GraphViz.

#### 1.5.3 SystemRDL

For the purpose of formally describing an SoC global memory map, SystemRDL has emerged as a capable framework and language [11]. It is able to describe and manage the top-level IP global memory map, including a comprehensive register hierarchy, specifying details from individual bitfields to larger constructs like contiguous memory blocks. Additionally, SystemRDL allows the definition of access policies and constraints. As such, the capabilities of SystemRDL to describe the global memory map is more powerful than that of IP-XACT<sup>1</sup>.

It is possible to specify an HDL path for a memory description in order for the SystemRDL environment to access and potentially verify it. No public implementation of this verification process is known. Furthermore, the verification is performed against the HDL, while the focus of this research lies on IP-XACT.

For further integration into the SoC design flow, SystemRDL compilers and parsers are introduced. PeakRDL [12], [13] is an open-source implementation of such a SystemRDL transpiler to and from SystemVerilog, C header files, and IP-XACT. The PeakRDL implementation shows, however, that this translation to and from IP-XACT only deals with a single IP-XACT component comprising of multiple addressBlock elements. This level of implementation is insufficient for complex or hierarchical IP-XACT designs involving multiple IP instantiations.

#### 1.5.4 CMSIS-SVD

Another relevant standard to describe SoC memory maps, particularly for ARM Cortex microcontrollers, is CMSIS-SVD [14]. It is an XML standard that provides a standardized way to describe the system and peripheral registers of a microcontroller design, akin to System-RDL and IP-XACT for general SoC designs. Similar to SystemRDL, it is able to define the global memory map from course grained device or peripheral regions down to bitfield level. Regarding its integration into the SoC design flow, it is able to generate C header files to aid in software development and could be used to perform verification. However, similar to UVM, this involves a dynamic functional verification which requires significant effort to setup. Instead, our approach aims for an automated and formal verification.

### 1.6 Overview

In the following Chapter 2 we give an introduction to the aspects of IP-XACT relevant to this research, after which we explain the data model and its properties we created. Finally, we use this data model to describe the formal problem statement at the end of the chapter.

Chapter 3 will provide the solution that we found to the formal problem. We explain how this solution was implemented, including its algorithms, structure, and general workflow.

Chapter 4 will then provide the methodology and results of evaluation of the solution against a complex SoC design. Alongside this evaluation, we explain the structure of the solution's generated report, and causes to the types of results we identified in this evaluation.

<sup>&</sup>lt;sup>1</sup>https://peakrdl-ipxact.readthedocs.io/en/latest/exporter.html#limitations

Finally, Chapter 5 will summarize the thesis project and provide a detailed discussion of our found results. It will evaluate the effectiveness and shortcomings of the model, the solution, and its implementation to realize the asserted objectives. Furthermore, it will discuss research directions for future work.

# Chapter 2

# **Problem Statement**

Verification can be defined as checking whether an implementation adheres to a specification. In the context of this research, a *memory specification* is defined as the layout of a component's memory that is predefined at the early stages of IP design flow. Its source file is a spreadsheet that maps address blocks and peripheral memory to an address offset and range for one or more root components. After the IP-XACT description of an IP design is completed, it has its own memory layout dispersed through its components, called the *memory implementation*. With these two address map descriptions, we define verification as the matching of a memory implementation against the corresponding memory specification.

The comparison of a memory implementation with its specification is simplified when both are represented in the same data structure. A network of address maps lends itself well to be represented in a directed graph G = (V, E) named a address map graph (AMG). When the AMG represents a memory specification, it is called a *specification graph*. When it represents a memory implementation, it is called an *implementation graph*. The definition and construction of both AMG types will be elaborated first. Then the general operations and methodology of comparison and verification will be explained. Finally, code of the generators that implement these operations are discussed.

# 2.1 IP-XACT (IEEE Std 1685)

This section provides an overview of the general organization of the IP-XACT standard [15] which enables designers to describe reusable IP blocks and system designs in a format that is agnostic to vendor, implementation language, and used tooling. To realize these system designs, IP-XACT facilitates the description address maps between IP instantiations. In turn, these designs can be assembled into new IP blocks, or complete products if forwarded further along the design flow.

Given that IP-XACT is an extensive standard, this section focuses specifically on aspects related to address mapping. We begin with the general structure and objects of an IP-XACT design implementation, then explain the memory structures that can be created using IP-XACT, and finally, we explain the addressing details of these memory structures.

#### 2.1.1 General Design Structure

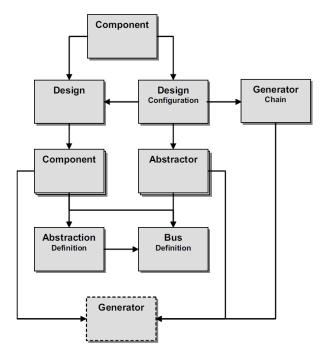

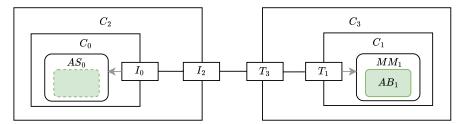

The IP-XACT standard abstracts the integration of SoC design into a structure of interacting objects. This section outlines the general structure of IP-XACT and how the objects and their elements realize a hierarchical design description. Some of the discussed objects are shown in Figure 2.1 [15, p. 4], which indicates the reference of one object to another with an arrow. We will focus on objects that are relevant to creating IP-XACT designs and to the research conducted in this work.

Figure 2.1: IP-XACT object references

# 2.1.1.1 Component Objects and Views

An IP block is abstracted into a component object, also called "component" in this work. It describes the metadata of an IP block such that it can be integrated into larger designs. A component contains view elements that define the implementation of the component. For a behavioral component, its register-transfer level (RTL) view elements contain the HDL files that implement its IP. For a structural component, its hierarchical view contains the instantiation of a design and designConfiguration object.

### 2.1.1.2 Bus Interface Objects and Interaction

Components may define bus interfaces, also called "interfaces" in this work. Interfaces are used to interact with other components. These interactions can involve communication protocols (e.g.  $I^2S$ ), interrupt signals, hierarchical implementations, and address maps. As such, the interfaces have properties and attributes that adhere to their communication requirements. These properties and attributes are defined in their referenced *bus definition* and *abstraction definition* elements. Furthermore, the *interface modes* determines the role each interface has in the interaction, such as initiator or the target of communication.

### 2.1.1.3 Design Objects

A design object defines the internal structure of a structural component; it defines the configuration of and interconnection between component instances, later to be packaged into a new component. Essentially, they describes component instances and the interconnections between their bus interfaces.

### 2.1.1.4 Design Configuration Objects

A designConfiguration object defines the active views for each component instance within the design. This object defines the active view for each component instance in a design. Note that the design and designConfiguration are referenced by a view of the enclosing component,

Figure 2.2: Diagram of a local memory map in IP-XACT

Figure 2.3: Diagram of a memory map in IP-XACT

such that different designs are possible per component. This flexibility enables the creation of various configurations and hierarchical structures of the same component within a single design.

# 2.1.1.5 Integration

The hierarchical integration of component instantiations is realized through the combined use of design and designConfiguration object instantiations. A top-level component references a design that describes how multiple lower-level component instantiations are interconnected through their bus interfaces. In turn, each lower-level structural component may also reference a design and designConfiguration, creating a multi-level hierarchy, and enabling the creation of complex SoC designs.

# 2.1.2 Memory Structures

In the following section, we identify and explain the memory structures that can be defined in IP-XACT in order to realize an address map. All the memory that is addressable by a component must be mapped to its address space, defined by an addressSpace element. A component may use zero, one, or multiple addressSpace elements, describing an address range with addresses starting at 0. Physical memory blocks of components are defined by addressBlock elements, which possibly start at a base address offset. A component cannot reference the contents of an addressBlock directly. Instead, it must be mapped to one of its addressSpaces. IP-XACT offers several memory structures to realize this address mapping: local address maps, (regular) address maps, bridges, and channels. Each will be elaborated in detail.

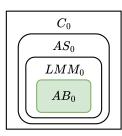

# 2.1.2.1 Local address map

By mapping a locally defined addressBlock to one of the component's addressSpaces, the component may address memory in the addressBlock. In this case, the addressBlock must be contained in a localMemoryMap element, which in turn is contained in one of its addressSpaces. This will create a local address map to the addressSpace, as illustrated in Figure 2.2, where component  $C_0$  contains an addressSpace  $AS_0$ . This addressSpace contains a localMemoryMap  $LMM_0$ , with  $LMM_0$  containing one addressBlock  $AB_0$ . Note that the  $AB_0$  is mapped to its own base address inside  $AS_0$ .

Figure 2.4: Diagram of an IP-XACT construct using a transparent bridge

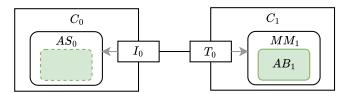

## 2.1.2.2 Address map

A component may address memory in the addressBlock of another component, such that the addressBlock is mapped to one of its addressSpaces. In this case, the addressBlock must be contained in a memoryMap element of an external component. An address map is established implicitly via the connection of bus interfaces. The initiator and target interface modes are most important to create address maps. An initiator interface initiates transactions, while a target interface receives transactions. The establishment of an address map will now be explained according to the example showed in Figure 2.3. An element reference is denoted as a gray arrow. In order to realize the address map, firstly, an initiator interface must reference a memoryMap. When the initiator interface and target interface are connected by an IP-XACT interconnect element, indicated by the black line, then the addressBlocks of the memoryMap become addressable from the addressSpace, again under their own base address like for local-MemoryMaps. This results in the mapping of addressBlock  $AB_1$  to addressSpace  $AS_0$ . The green box with the dashed outline in  $AS_0$  denotes the mapped  $AB_1$  that is now accessible from  $AS_0$ .

### 2.1.2.3 Bridges

It is possible to combine and reorder multiple address mappings into one address map through the use of a bridge. A bridge component contains an element configuration that (implicitly) map multiple addressSpaces to a single memoryMap. IP-XACT defines two types of bridges – transparent and opaque – which will be explained in further detail.

Unlike a memoryMap in an address map, a mapped addressSpace defines no base address offset. Instead, this offset is provided by the bridge component for each mapped addressSpace individually. This offset causes inbound address accesses to the corresponding addressSpace to shift positively or negatively. As a result, the contents of the addressSpace are mapped with an offset. This process is called the *shifting* of an address mapping.

### 2.1.2.3.1 Transparent Bridge

A transparent bridge describes the mapping of (the contents of) multiple addressSpaces to one memoryMap. Each addressSpace is mapped with a unique offset defined in its referencing initiator interfaces. In the element configuration of a transparent bridge partake one target interface and one or more initiator interfaces. The target interface references each of the partaking initiator interfaces in the bridge component. For each of the initiator interfaces, if it references an addressSpace then it will be mapped to the memoryMap. Note that the transparent bridge does not actually contain a memoryMap element. Instead, its memoryMap is only *implied* at the target interface. In other words, when this target interface is connected to a component's initiator interface referencing an addressSpace then this implied memoryMap is mapped to the addressSpace.

Figure 2.5: Simplified diagram of an IP-XACT construct using an opaque bridge

Figure 2.6: Detailed diagram of an IP-XACT construct using an opaque bridge

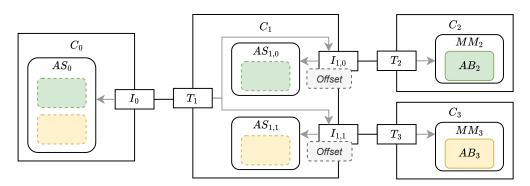

Figure 2.4 shows an example configuration that implements a transparent bridge  $C_1$ , where each initiator interface references an addressSpace  $AS_{1,i}$ , and the implied memoryMap at  $T_1$  is mapped to addressSpace  $AS_0$  in  $C_0$ . As a result, incoming transactions will be able to access their address spaces directly. This direct access implicitly maps shifted contents of the bridge component's addressSpaces  $AS_{1,i}$  to the destination addressSpace  $AS_0$ .

Note that when multiple initiator interfaces reference the same addressSpace, then each interface maps to its own instantiation of this addressSpace, instead of mapping to the same addressSpace.

#### 2.1.2.3.2 Opaque Bridge

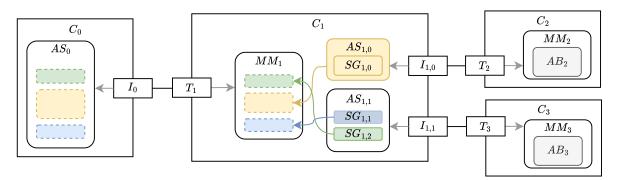

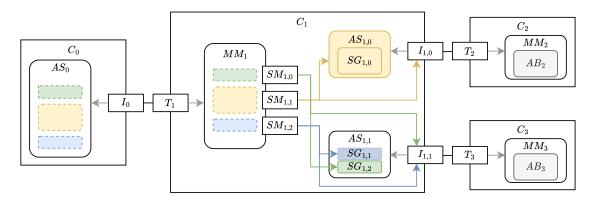

An opaque bridge can reorganize a set of address mappings even further than its transparent counterpart. This is possible, because an addressSpace can define segment elements. These are segments of the addressSpace that are to be mapped separately from the containing addressSpace. They define their own base address offset and address range. See Section 2.2 for more information on their addressing. Figure 2.5 is a simplified illustration of the mapping structure. Via regular address maps, the addressBlocks  $AB_2$  and  $AB_3$  are mapped to  $AS_{1,0}$  and  $AS_{1,1}$  respectively. In component  $C_1$ , it shows the mapping of addressSpace  $AS_{1,0}$  and segments  $SG_{1,1}$  and  $SG_{1,2}$  to memoryMap  $MM_1$  by the colored arrows. Finally, the memoryMap is mapped to the addressSpace  $AS_0$  in component  $C_0$  via an address map.

Contrary to the transparent bridge, the offset at which a segment is mapped is not defined in the initiator interface, but in a subspaceMap element defined and contained in the memory-Map to which it must be mapped. A subspaceMap defines a reference to an initiator interface, a reference to a segment or addressSpace, and a base address offset. This is illustrated in the more detailed diagram of Figure 2.6 which denotes subspaceMaps as  $SM_{1,i}$ . To establish the mapping, the subspaceMap must first reference an initiator interface. For a segment mapping, the subspaceMap must also reference the segment contained in the addressSpace referenced

Figure 2.7: Diagram of an IP-XACT construct using a channel

Figure 2.8: Simple address map structure with two hierarchical interconnects

by the initiator interface, as is done by  $SM_{1,0}$  and  $SM_{1,2}$ . For an addressSpace mapping, the subspaceMap must reference the addressSpace referenced by the initiator interface, as is done by  $SM_{1,1}$ .

Via the opaque bridge, an address map's memoryMap can contain addressBlocks, but also subspaceMaps that map a segment or addressSpace. In all cases, the memoryMap's contents are mapped to the addressSpace referenced by the initiator interface. Therefore, an address map can map addressBlocks, segments, and addressSpaces.

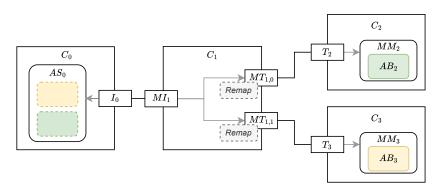

### 2.1.2.4 Channel

In the context of previous constructs, a *channel* component is essentially a transparent bridge, but without any addressSpaces associated with its initiator interface(s). Instead of regular initiator and target interfaceModes, they use the *mirroredInitiator* and *mirroredTarget*. Interfaces in these modes may only be connected to non-mirrored initiator and target interfaces respectively. An example configuration that implements a channel is illustrated in Figure 2.7. Inside the component, the mirroredInitiators reference the mirroredTargets, for example  $MT_{1,0}$  referenced by  $MI_1$ . Incoming memory operations are forwarded from the mirroredInterface to the mirroredTargets. This causes addressSpaces and addressBlocks accessible through the connected target interface to be mapped to the addressSpace referenced by the connected initiator interface.

The mirroredTarget interfaces can provide a remap address. This remap address offsets the address of the incoming memory accesses. Consequently, the addressSpaces and addressBlocks that are accessible through the mirroredTarget are mapped with the offset defined by its remap address.

# 2.1.3 Hierarchical Interconnects

An IP-XACT design is a hierarchical description of an IP-block. This means that it consists of IP-blocks, which in turn may also be hierarchical. For each instantiation of a hierarchical component, its child components are also instantiated. The hierarchy is implemented by *hierarchical interconnects*, which connect an interface of a child component to an interface of

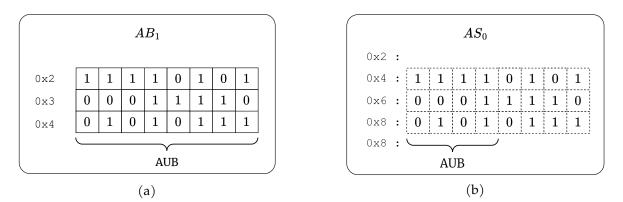

Figure 2.9: Example contents of (a) an addressBlock and (b) an addressSpace

the parent component of the same type. For example, a hierarchical connection may connect the initiator interface of a child component to the initiator interface of the parent component.

Any interconnection used in previously explained constructs may be followed or lead by any number of hierarchical interconnects. This is illustrated in Figure 2.8. The source and destination memory elements of a mapping construct may reside in components at different hierarchical levels.

# 2.2 Addressing

The addressing of addressSpaces and memory in addressBlocks depends on their properties and their context. Memory addressing is understood as the way (groups of) bits are accessed by an address in an addressBlock, addressSpace, or segment; how many bits per address; under what address offset; starting from which address; for how many addresses. The context of an IP-XACT element is defined by the properties of its parent element and (in)directly referenced elements. The addressing may be further delimited by a semantic consistency rule (SCR) as defined by the IP-XACT standard [2, Annex B]. This section explores the fundamentals of this addressing for the memory structures provided by Section 2.1.2.

#### 2.2.1 Addressing Properties

The addressing of addressBlocks and addressSpaces in address mappings depends on several of their properties and of their parent element.

Each addressBlock defines a row width, base address offset, and address range. It makes use of an address unit bits (AUB) value, which defines the number of bits which are addressed by one bit increments of the address. The AUB may be defined by its containing memoryMap for an address map, or by its containing addressSpace for a local address map. If it is not defined, it is presumed to be 8 [2, p. 222]. The width is a multiple of the AUB in accordance with SCR 8.1 [2]. The range is defined in AUBs. An example addressBlock is illustrated in Figure 2.9a, where the AUB is 8, the width is 8, base address is 0x2, and the range is 3. In accordance with SCR 8.4 [2], addressBlocks in the same memoryMap may not overlap.

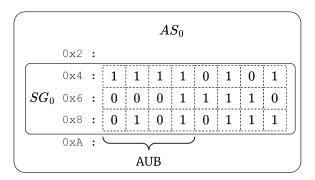

Each addressSpace defines a row width and an address range. It may also define an AUB value, else it is presumed to be 8. Again, its width is a multiple of its AUB, and its range is defined in AUBs. An example addressSpace is illustrated by Figure 2.9b, where the AUB is 4, the width is 8, and the range is 10. Let us assume that the addressBlock  $AB_1$  of Figure 2.9a is mapped to addressSpace  $AS_0$ , via the memory map of Figure 2.3. The mapped memory bits of  $AB_1$  are shown in  $AS_0$  with a dashed outline. Any defined segments must fall within the range of the containing addressSpace in accordance with SCR 9.8 [15].

Figure 2.10: Example contents of a segment defined in  $AS_0$  of Figure 2.9b

Each segment defines a base address offset and an address range, while it inherits the address width and AUB from its containing addressSpace. An example segment is illustrated by Figure 2.10. Note that the boundaries of a segment are irrespective of the boundaries of mapped addressBlocks. Therefore, (parts of) multiple addressBlocks may be mapped to one segment.

#### 2.2.2 Address Resolution

The contents of memory may not remain at the same address when they are mapped to an addressSpace. Beside offsets introduced by bridges and channels, the AUB of a mapped addressBlock, addressSpace, or segment may differ from that of the destination addressSpace. The resolution of an address to its mapped address therefore possibly involves a translation of addresses. In this translation, the range and width of the destination addressSpace will always take precedence over those of the addressBlock addressSpace or segment being mapped. Each scenario of altered addressing will now be explained.

Firstly, the width may become smaller or larger. In both cases, it causes the bits to be wrapped to the new width and the content of addresses to shift. This happens because an addressBlock is an array of contiguous memory bits that can be addressed in any addressing width. This, however, only affects the number of bits transferred per transaction. A width change does not affect the addressing of mapped memory, for this is solely determined by the AUB and any induced offsets.

Secondly, the AUB may become smaller or larger. With exception of address  $0 \times 0$ , a smaller AUB increases all memory addresses, while a larger AUB decreases them. For example, in the mapping of  $AB_1$  to  $AS_0$  in Figure 2.9, their widths remain the same, but the AUB is halved in  $AS_0$ . Consequently, the base address offset doubles from  $0 \times 2$  to  $0 \times 4$ , and the bits originally at address  $0 \times 3$  are now mapped to address  $0 \times 6$  and  $0 \times 7$ .

After memory has been mapped to its new address, it is possible for it to fall outside the accessible addresses of the destination addressSpace. Alternatively, it may fall outside the boundaries of a mapped segment. One example is the situation where the range of an addressSpace is smaller than the range of the mapped addressBlock. The addresses mapped to such out-of-range addresses remains inaccessible, which is called the clipping of memory. Note that neither memoryMaps nor their subspaceMaps define a range. Therefore, they cannot clip memory that is mapped to them. Clipping will be further elaborated in the following chapter.

#### 2.2.3 Bit Addressing

The following chapters use bit addressing to simplify the aforementioned situations of differing AUBs. A bit address in an addressBlock or addressSpace is calculated by multiplying an address by the appropriate AUB value. The starting address of an addressBlockand subspaceMapin bit-addressing is given by Equation (2.1) and Equation (2.2) respectively [2, p. 223]. In a similar fashion, the bit addressed range of memory elements is obtained by multiplying its range with the appropriate AUB.

$$addressBlock\_bit\_address\_offset = addressBlock.baseAddress \\ \times addressUnitBits$$

(2.1)

subspaceMap\_bit\_address\_offset = subspaceMap.baseAddress (2.2)

× memoryMap.addressUnitBits (2.2)

The address at the target interface for a transparent bridge is given by Equation (2.3) [2, p. 225]. The address at the target interface for an opaque bridge mapping an addressSpace and a segment is given by Equation (2.4) and Equation (2.5) respectively [2, p. 225]. Note that the term "initiator" in the equations refers to the initiator interface.

The address at the mirrored target interface of a channel can be derived from Equation (2.6) [2, p. 225]. The bitsInLau is an AUB value defined specifically by a mirroredTarget interface. The interface's remap address is defined in this bitsInLau.

```

\label{eq:mirrored_initiator_bit_address_offset = mirrored_target_bus_bit_address_offset \\ + mirroredTarget.baseAddress.remapAddress \\ \times mirroredTarget.bitsInLau \\ (2.6)

```

(2.6)

# 2.3 Global Address Map Specification

The memory organization of an SoC design is specified in a global address map, which defines the address space and layout of memory elements within the system. The global address map ensures that all memory elements are correctly addressed and accessible by the initiator IP blocks within the SoC design. In the rest of this research, the organization specified by a global address map is referred to as a "specification".

This research focuses on specifications defined in spreadsheets, which are commonly used because they are intuitive to read and edit during the design process. To integrate this tool into such workflows and utilize existing designs with spreadsheet specifications as study cases for verification, XLS files are used as specification format in this research.

A spreadsheet specification file defines how peripherals are mapped to the address space of initiator IP blocks, such as the CPU, DMA controller, and others. An example spreadsheet

| Address    | Identifier | Attached Unit | Purpose          | Spec Size<br>[kB] | Implemented<br>[kB] | CPU      | DMA      |

|------------|------------|---------------|------------------|-------------------|---------------------|----------|----------|

| 0x00000000 | Boot Code  | ROM           | System Boot Code | 524288            | 524288              | ROM CODE |          |

|            |            | RAM1          | Data             | 524288            | 524288              | RAM      | RAM      |

| 0x4000000  | IO         | FLEXCOMM      | Debug            | 4                 | 0.5                 | FLEXCOMM | FLEXCOMM |

| 0x40001000 |            | SPI           | SPI Interface    | 1                 | 1                   | SPI      | SPI      |

Figure 2.11: Example specification spreadsheet in default layout

layout is illustrated in Figure 2.11. This layout defines peripherals row-wise on the left and initiator IP blocks column-wise on the right, specifying the mapped starting address, the mapped range, and to which initiator IP blocks each peripheral should be mapped.

The default layout, as defined by the configuration parameters, is shown in Figure 2.11. On the left side, the layout specifies all peripherals and their potential mappings to the address space of initiator IP blocks. The first column displays the hexadecimal byte-address, while the sixth column indicates the kilobyte-addressed range mapped for each peripheral. The right side columns define the initiator IP blocks, where each is specified by a name in the header, followed by a cell for each peripheral row. A non-empty cell signifies that the peripheral in that row should be mapped to the address space of the initiator IP block. For example, in Figure 2.11, all peripherals are mapped to both initiator IP blocks, except for the first ROM peripheral, which is not mapped to the "DMA".

# 2.4 Graph Definition

In this section, we present the unified graph model to describe the memory organization defined by both the IP-XACT implementation and the spreadsheet specification of the SoC design. This allows us to compare the models of implementations and specifications with each other.

This section starts by identifying the the different mapping types to be modeled, as well as how the specification memory specification is handled. Then we explain the properties of the nodes and edges in our model, as well as properties of the graph as a whole.

# 2.4.1 Address Mapping Types

To help in further defining the graph data structure, we identify the mapping types of both the IP-XACT implementation and spreadsheet specification of the memory organization.

### 2.4.1.1 Implementation Mapping Types

The following five types of address mappings to addressSpaces are identified for the memory structures introduced in Section 2.1.2:

- 1. A local address map that maps addressBlocks from a localMemoryMap to an addressSpace without any shifting.

- 2. An address map that maps the contents of a memoryMap to an addressSpace without any shifting. The contents can be addressBlocks, but also segments and addressSpaces from bridges.

- 3. An address map with a transparent bridge, that maps one or more addressSpaces to an addressSpace, possibly with an address offset defined by the channel's initiator interfaces under the AUB of the mapped addressSpace.

Figure 2.12: Identified memory element mapping streams

- 4. An address map with an opaque bridge, that maps one or more addressSpaces or segments to a memoryMap, possibly with an address offset defined by the subspaceMap under the AUB of the containing memoryMap.

- 5. Mapping type 2, 3, or 4, interjected by a channel. It may map the contents of one or more memoryMaps to an addressSpace in the case of type 2 and 4. Or, it may map addressSpaces to an addressSpace in the case of type 3.

It is important to observe that a memory element that is explicitly mapped to an address-Space may end up in one of its segments. Whenever any memory element is mapped to an addressSpace, then is it also mapped to the segment within which it falls, if such a segment is defined. Furthermore, whenever an addressSpace is mapped, we must assume that all its segments are mapped as well. In short, any mappings to or from an AS are also performed to and from its segments. In the latter case, note that the segment base offset is not considered, thus not subtracted, so Equation (2.4) applies instead of Equation (2.5).

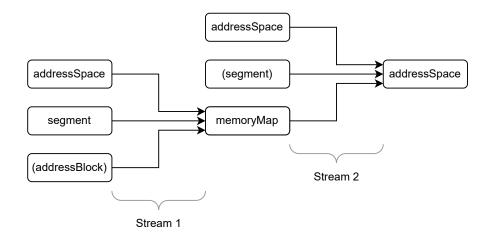

At first glance, these mapping types show that there are two streams of address mappings shown in Figure 2.12; firstly, from addressSpaces, their segments and contained address-Blocks to memoryMaps and secondly, from memoryMaps addressSpaces, and contained segments to addressSpaces. Note that child items are in parentheses, as their mapping to the parent memory element is implicit by their child-parent relation. It is observed, however, that memoryMaps have significantly different behavior from addressSpaces and segments as mapping destinations. To elaborate, a memoryMap has no clipping behavior like addressSpaces and segments have, for memoryMaps have neither a defined base nor range. The clipping of a memory-Map's contents only happens once it is mapped to an addressSpace or segment and clipped by its boundaries. It is part of the mapping process, in which addressBlocks, addressSpaces, and segments are aggregated by the memoryMap as an implied addressSpace before finally being mapped to an actual addressSpace or segment. In other words, a memoryMap can be regarded as a transitory mapping element. Therefore, only addressSpaces, their segments, or addressBlocks are modeled as nodes in the graph, while memoryMaps are not. This results in one stream remaining, where addresses in addressSpaces can resolve to addresses in either other addressSpaces, their segments, or addressBlocks, shown in Figure 2.13.

#### 2.4.1.2 Specification Mapping Types

As explained in Section 2.3, the spreadsheet specifies how the addressBlocks of peripheral IP blocks should be mapped to the addressSpaces of initiator IP blocks. This specification

Figure 2.13: Memory element mapping stream processed into the model

includes both the address range and the destination address within the initiator IP blocks. As such, the spreadsheet defines regular address maps analogous to implementation mapping types 1 and 2. Therefore, our model can represent both the implementation and the specification effectively.

#### 2.4.2 Node Attributes

A node  $v \in V$  is defined to represent a memory element, which is either an addressSpace, segment, or addressBlock. Therefore, For each memory element, there exists a node and vice versa. As explained in Section 2.1, every memory element has several IP-XACT properties related to their addressing: a base address and an address range, both of which under a certain AUB. This results in a window of addresses that are accessibly by the memory element. Its base address is the first address in its window. Its address range is the number of addresses in its window. Given an IP-XACT element m, assume that its defined base address, range, and AUB – if they exist – can be retrieved through  $pBase(m) \in \mathbb{N}$ ,  $pRange(m) \in \mathbb{Z}^+$ ,  $aub(m) \in \mathbb{N}$ , respectively.

The graph model must also handle the situation where the two memory elements of an address mapping have different AUBs. Given a mapped memory element, this translation may increase or decrease, and thereby shift, the addresses to which this memory is mapped. Meanwhile, the mapping offsets must be applied while dealing with different AUBs, as explained in mapping types. For the purpose of uniformity and simplicity of calculation, all addressing in the graph will therefore be using bit addressing.

$$bBase(m_0, m_1) = ipBase(m_0) \cdot aub(m_1)$$

(2.7)

$$bRange(m_0, m_1) = ipRange(m_0) \cdot aub(m_1)$$

(2.8)

The processing of a memory element into a node  $v \in V$  then involves the calculation of two bit-addressed attributes  $base(v) \in \mathbb{N}$  and  $range(v) \in \mathbb{Z}^+$ . Their calculation involves the multiplication of their non-bit-addressed properties with their corresponding AUB, according to functions  $bBase(m_0, m_1)$  and  $bRange(m_0, m_1)$  defined by Equation (2.7) and Equation (2.8) respectively. The IP-XACT element arguments  $m_0$  and  $m_1$  depend on the memory element type – addressSpace, segment, or addressBlock:

- Any addressBlock  $AB_0$  in memoryMap  $MM_0$  is processed into a node  $v \in V$  with  $base(v) = bBase(AB_0, MM_0)$  and  $range(v) = bRange(AB_0, MM_0)$ .

- Any segment  $SG_0$  contained in addressSpace  $AS_0$  is processed into a node  $v \in V$  with  $base(v) = bBase(SG_0, AS_0)$  and  $range(v) = bRange(SG_0, AS_0)$ .

- Any addressSpace  $AS_1$  is processed into a node v with  $base(v) = bBase(AS_1, AS_1)$  and  $range(v) = bRange(AS_1, AS_1)$ .

Together, base(v) and range(v) define the window W(v), which is a range of bit addresses available to the node. As defined in Equation (2.9), the base is the first bit address in the window, and the range is the number of bit addresses in the window.

$$W(v) = [base(v), base(v) + range(v))$$

(2.9)

#### 2.4.3 Edge Attributes

With the memory elements processed into nodes, the address mappings between them can be processed into edges. Any address mapping between two nodes  $u, v \in V$  is processed into an edge  $e \in E$ . Such an edge is an ordered pair e = (u, v), also shortly denoted as uv. We define the edge source u = s(e) as the addressing memory element, and the edge target v = t(e) as the mapped memory element. Each edge has the attribute offset $(v) \in \mathbb{Z}$ , which is the address offset it may induce.

The graph edge direction has been chosen to follow address evaluation, instead of the direction of address mapping. Although the direction should not matter in the final verification, this direction was chosen because the mappings in the memory implementation should resolve to the same addresses as in the specification, while the opposite does not hold. In other words, address resolution is a central aspect of the verification process.

The interpretation of IP-XACT address mappings into graph edges depends on the mapping type. As is examined in Section 2.1.2, the mapping type is determined by the constellation of IP-XACT components, their interface interconnections, their interface references, and their contained IP-XACT elements, configurations and types. Given an IP-XACT element m, assume that its defined offset – if it has one – can be retrieved through ipOffset(m). For transparent bridges and channels, this means that the remap address defined in their initiator interface I is retrievable via ipOffset(I). For opaque bridges, this means that the base address defined in their subspaceMap SM is retrievable via ipOffset(SM).

$$bOffset(m_0, m_1) = ipOffset(m_0) \cdot aub(m_1)$$

(2.10)

Then, the bit-addressed offset(e) property is calculated for each edge  $e \in E$  according to Equation (2.10). Mappings of type 5 that involve channels are ignored for now, because channels are rarely used in practice. From the four remaining types of address mappings identified in Section 2.4, we look at how combinations of the first three types are processed into edges. This results in the following scenarios:

- Consider a local address map (type 1), an example of which is shown in Figure 2.2. Assume that the addressSpace of a component  $C_0$  contains a localMemoryMap, which in turn contains an addressBlock. Then, the addressSpace and addressBlock are processed into nodes u and v respectively. Consequently, edge uv is created with offset(uv) = 0.

- Consider simple address map (type 2) where the memoryMap contains only address-Blocks, an example of which is shown in Figure 2.3. Then, the addressSpace is processed into node u, and the addressBlock in the memoryMap is processed into node v. Then, edge uv is created with offset(uv) = 0.

- Consider an address map with a transparent bridge (type 3), an example of which is shown in Figure 2.4. Assume that an addressSpace  $AS_{1,0}$  – referenced by initiator interface  $I_{1,0}$  in component  $C_1$  – is mapped to addressSpace  $AS_0$  in component  $C_0$ .  $AS_0$ and  $AS_{1,0}$  are processed into nodes u and v respectively. Then, edge uv is created with offset(uv) = bOffset( $I_{1,0}, AS_{1,0}$ ).

- Consider an address map with an opaque bridge (type 2 & 4), an example of which is shown in Figure 2.6. Assume that it maps a segment  $SG_{1,1}$  to a subspaceMap  $SM_{1,0}$

contained in a memoryMap  $MM_1$ , all in component  $C_1$ . Then, assume that  $MM_1$  in turn is mapped to addressSpace  $AS_0$  in component  $C_0$ . Then,  $AS_0$  is processed into node u, and  $SG_{1,0}$  or  $AS_{1,0}$  is processed into node v. Consequently, edge uv is created with offset $(uv) = bOffset(SM_{1,1}, MM_1) - bBase(SG_{1,0}, AS_0)$ . The segment base must be subtracted because the opaque bridge will map the segment directly to the subspace map's offset, disregarding the segment base. Meanwhile, the node that represents the segment does contain the base. As such, the base must be subtracted from the edge offset.

• Consider an address map with an opaque bridge (type 2 & 4), an example of which is shown in Figure 2.6. Assume that it maps addressSpace  $AS_{1,0}$  to subspaceMap  $SM_{1,1}$ contained in memoryMap  $MM_1$ , all in component  $C_1$ . Then, assume that  $MM_1$  in turn is mapped to addressSpace  $AS_0$  in component  $C_0$ . Then,  $AS_0$  is processed into node u, and  $SG_{1,0}$  or  $AS_{1,0}$  is processed into node v. Consequently, edge uv is created with offset(uv) = bOffset( $SM_{1,1}, MM_1$ ).

#### 2.4.4 Graph Properties

The set of nodes V and edges E, that result from processing all address mappings in an IP-XACT design, together form its graph G = (V, E), called the Address Mapping Graph (AMG). An AMG is directed, possibly a non-tree, and possibly disconnected. When the AMG represents the memory organization of an IP-XACT implementation, it is called an implementation AMG. When it represents the memory organization of a spreadsheet specification, it is called a specification AMG. An implementation AMG may contain cycles, the base case of which is a bridge initiator interface connected to its own target interface. In practice, cycles rarely occur. For this reason, we exclude cyclic AMGs from the scope of this research. Specification AMGs cannot contain cycles in this research. This means that an IP block cannot be specified as both a initiator IP block as well as a mapped peripheral in the spreadsheet. As such, specification AMGs have a height of 1.

AMGs have a set of roots  $R \subset V$  without incoming edges, and a set of leaves  $L \subset V$  without outgoing edges, as defined by Equation (2.11) and Equation (2.12). A root node always represents an addressSpace or segment, because an addressBlock cannot address itself. On the other hand, a leaf node always represents an addressBlock, because addressSpaces and segments have nothing to address as leaves. As such, R and L are disjunct, such that  $R \cap L = \emptyset$ . Components may contain multiple addressSpaces that are processed into root nodes. Such a component is typically a initiator component, such as a CPU.

$$R = \{r \in V \mid \delta^+(r) = 0\}$$

(2.11)

$$L = \{l \in V \mid \delta^{-}(l) = 0\}$$

(2.12)

A path  $p = (e_0, e_1, ..., e_{n-1})$  is a sequence of n consecutive edges, where  $p(i) = e_i$ , such that for each  $0 \le i < n-1$ ,  $t(e_i) = s(e_{i+1})$ . The set of all possible paths in G, that start in R and end in L, is denoted P, as defined by Equation (2.13). When we take a specific root  $r \in R$  and leaf  $l \in L$ , then we define a root-to-leaf path  $p_{r \to l}$  as a path that starts in r and ends in l. Multiple paths may exist from the same root to leaf. As such, the set of all root-to-leaf paths from r to l is denoted  $P_{r \to l}$ , as defined by Equation (2.14).

$$P = \{ p \in \mathscr{P} \mid \mathbf{s}(e_0) \in R \land \mathbf{t}(e_{n-1}) \in L \}$$

$$(2.13)$$

$$P_{r \to l} = \{ p \in P \mid \mathbf{s}(e_0) = r \land \mathbf{t}(e_{n-1}) = l \}$$

(2.14)

Figure 2.14: AAD of (a) a non-leaf node and (b) a leaf node

# 2.5 Bitmapping Calculation

With the definition of implementation and specification AMGs completed, we can now move forward to defining their equivalence in terms of address mappings. To achieve this, we first need to analyze and define the concepts of shifting and clipping of a path, as introduced in Section 2.1, in more detail. Next, we will explain the concept of the addressable window of a path. This will allow us to formalize the cumulative clippings along a path. Finally, we will use this formalization to define the concept of a bitmapping, on which we will base the equivalence definition.

### 2.5.1 Shifting and Clipping

An address mapping can have a clipping effect, shifting effect, or both effects on the mapped addresses of a memory element. A shift occurs when the edge  $uv \in E$  of the address mapping has a non-zero offset(uv). Without channels, shifting is only possible between non-leaf nodes, however, shifting of leaf node memory will still be considered in the graph model and the following analysis. This is done for completeness of the model, and possible future inclusion of channels. Mapped addresses are clipped after shifting when they fall outside the window of addressing node u.

### 2.5.1.1 Address-Axis Diagrams

To aid more detailed explanation of address mappings, and their the shifting and clipping phenomena, they will be visualized using an address-axis diagram (AAD). Figure 2.14a shows the address axis of a non-leaf node v. The dashed line indicates the address axis. A solid line indicates its address window W(v). Figure 2.14b shows the address axis of a leaf node l. Addresses that resolve to an addressBlock are visualized as a block. Because l is a leaf node and represents an addressBlock, its entire window W(l) visualized as a block.

Figure 2.15 shows an AAD where the window of leaf node l is mapped to node v by an edge  $e_0$ . At this point, the AAD must be read from right-to-left, in the direction of address mapping. Later on, we will read the AADs from left-to-right, in the direction of address resolution. The address axis of leaf l is shown on the right. The middle axis is a transitory address axis, unto which the shifted memory of l is projected under offset $(e_0)$ . Finally, the shifted memory is mapped to the address axis of v on the left. Only addresses that fall inside the window W(v) are kept, while addresses that fall outside of it are clipped. In this case. In this case, all addresses in W(l) remain addressable.

Figure 2.15: AAD of the address mapping of a leaf node

#### 2.5.1.2 Addressable Windows

The concept of addressable windows is first introduced using Figure 2.15, after which the format definition is explained.

An address in an addressSpace or segments is only addressable when an addressBlock address is mapped to it; addresses that do not resolve to an addressBlock address are non-addressable. Therefore, v's window in Figure 2.15 has an addressable (sub-)window, denoted  $AW(e_0)$ .

Leaf nodes represent the addressBlock. addressable, however, as leaf nodes cannot address their own memory. Instead, the leaf window must be mapped to the window a non-leaf node u. All addresses in W(v) to which it directly maps will become addressable. This results in a range within window W(v) that is addressable, called the addressable window  $AW(e_i)$ . Because any addressable window  $AW(e_i)$  resolves to addressBlock addresses, it is also visualized as a block in AADs.

For any edge e along a path p, the unclipped portion of an addressBlock that is mapped to the window of node s(e) is the addressable window AW(e) of that node. For any path pstarting in r and ending in leaf l, take edge  $e_i$  with  $v = s(e_i) \in V$ . Then, the addressable window  $AW(e_i)$  is the range of addresses of the leaf window W(l) that are mapped to window W(v). This is illustrated by Figure 2.15 for a single edge path.

#### 2.5.1.3 Final Edge Clipping Conditions

To form an intuition in the clipping conditions, consider of the final edge  $e_{n-1} = (v, l)$  of a path p, such that  $t(e_{n-1}) = l$  and  $l \in L$ . Then, the bottom mapped addresses are clipped when the condition in Equation (2.15) holds, while the top mapped addresses are clipped when the condition in Equation (2.16) holds.

$$base(v) > base(l) + offset(e_{n-1})$$

where  $e_i = p(i)$  (2.15)

$$base(v) + range(v) < base(l) + range(l) + offset(e_{n-1})$$

(2.16)

An example of such a final edge is illustrated in Figure 2.15. For this example, no clipping occurs because both equations do not hold.

#### 2.5.1.4 Addressable window boundaries

Once an address has been clipped, it will no longer be mapped to further nodes up along the path. Figure 2.16 shows an AAD where the memory of previously used non-leaf node v maps to a node u by an edge  $e_i$ . Note how only the addressable window AW(e) is mapped to the window W(u). This is done, because we do not care about the mapping of non-addressable

Figure 2.16: AAD of the address map of a non-leaf node

addresses. As such, for any leaf  $l \in V$ , the size of the addressable portion of W(l) along a path is only able to be clipped or remain equal. The bounds of an addressable window of an edge depend on the bounds of the addressable window of all edges towards the leaf node. Therefore, the definition of the bounds of the addressable window is recursive.

Given any  $e_i \in p$ , the boundaries of  $AW(e_i)$  can be resolved with respect to the remainder of the path down the to the root. In other words, the lower bound and upper bound of the addressable window  $AW(e_i)$  must be calculated recursively down to  $e_0$ . Given a  $p = (e_0, e_1, ..., e_{n-1})$  with edge index  $i \in \mathbb{Z}^+$  such that  $p(i) = e_i$ , the lower bound  $lb(e_i)$  and upper bound  $ub(e_i)$  of  $AW(e_i)$  can be calculated recursively according to Equation (2.17) and Equation (2.18) respectively. For each function, the first line shows the base case where i = n and the second line gives the recursive case where i < n. Note that no shifting can occur in the base case, for it must be a address map, such that  $offset(e_n) = 0$ . Then an addressable window can be defined as in Equation (2.19).

$$lb(e_{n-1}) = max (base(s(e_{n-1})), base(t(e_{n-1})) + offset(e_{n-1}))$$

$$lb(e_i) = max (base(s(e_i)), lb(e_{i+1}) + offset(e_i))$$

$$where e_i = p(i)$$

$$(2.17)$$

$$ub(e_{n-1}) = \min(base(s(e_{n-1})) + range(s(e_{n-1})), base(t(e_{n-1})) + range(t(e_{n-1})) + offset(e_{n-1})) ub(e_i) = \min(base(s(e_i)) + range(s(e_i)), ub(e_{i+1}) + offset(e_i)) where  $e_i = p(i)$

$$AW(e_i) = [lb(e_i), ub(e_i)) \text{ where } e_i = p(i)$$

(2.19)$$

## $AW(e_i) = |lb(e_i), ub(e_i)|$ where $e_i = p(i)$

#### 2.5.2 Bitmappings

#### 2.5.2.1 Cumulative Path Clipping

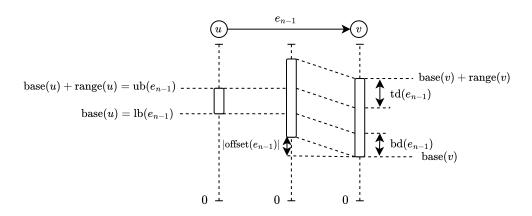

Any  $AW(e_i)$  addresses an equal sized region in the leaf node window W(l). It is necessary to calculate the offset this region has from the base address offset of the leaf. The offset can be viewed from the bottom boundary of W(l) called the bottom delta  $bd(e_i)$ , or from the top boundary of W(l) called the top delta  $td(e_i)$ . The bottom and top deltas are equal to the cumulative clippings of the bottom and top addresses, respectively. For any path  $p = (e_0, e_1, \dots, e_{n-1})$ , they are calculated recursively according to Equation (2.20) and Equation (2.21) respectively. Both deltas are visualized in Figure 2.17 for the final edge  $e_{n-1}$  of a path.

Figure 2.17: AAD a final edge that clips top and bottom addresses

$$bd(e_{n-1}) = max(0, lb(e_{n-1}) - base(t(e_{n-1})) - offset(e_{n-1}))$$

$$bd(e_i) = bd(e_{i+1}) + max(0, lb(e_i) - lb(e_{i+1}) - offset(e_i))$$

where  $e_i = p(i)$

(2.20)

$$td(e_{n-1}) = max(0, base(t(e_{n-1})) + range(t(e_{n-1})) + offset(e_{n-1}) - ub(e_{n-1}))$$

$$td(e_i) = td(e_{i+1}) + max(0, ub(e_{i+1}) + offset(e_i) - ub(e_i)$$

(2.21)

where  $e_i = p(i)$

Symbolic definition of lb in terms of bd and vice versa is difficult, due to the max and min functions. These require further information, or assumption on their resolution (e.g. they always resolve to their second term). Instead, to demonstrate their correctness, we express the codomain upper bound in terms of td and bd, resulting in Equation (2.22). All formulas and this equations are applied an example path in Appendix A.1, which demonstrates their correct representation of the cumulative clippings of top and bottom address.

$$base(t(e_{n-1})) + range(t(e_{n-1})) - td(e_0) = base(t(e_{n-1})) + bd(e_0) + ub(e_0) - lb(e_0)$$

where  $e_i = p(i)$

(2.22)

#### 2.5.2.2 Domains and Codomains

For any root-to-leaf path  $p_{r \rightarrow l} = (e_0, e_1, ..., e_{n-1})$ , the recursive calculations of  $lb(e_0)$  and  $ub(e_0)$  together define the addressable window  $AW(e_0)$ , called the *domain* of path  $p_{r \rightarrow l}$ . This domain maps to an equally sized range of contiguous bit addresses of the leaf window, called the *codomain* of path  $p_{r \rightarrow l}$ . The codomain is defined by the recursive calculation of  $bd(e_0)$ , the leaf node  $e_{n-1}$  base  $base(e_{n-1})$ , and the range of the domain  $ub(e_0) - lb(e_0)$ . The lower bound of the codomain is defined as  $base(e_{n-1}) + bd(e_0) + ub(e_0) - lb(e_0)$ . Thus, the domain and codomain represent a contiguous range of bit addresses in the root and leaf node, respectively.

#### 2.5.2.3 Bitmapping Definition

A bitmapping, denoted as m(p), is formed by the domain and codomain of a path within an AMG. As defined in Equation (2.23) with  $e_i = p(i)$ , it is a tuple of four values. The first two values  $lb(e_0)$  and  $ub(e_0)$  are the lower and upper bounds of the path recursively calculated for the path root, which together define the domain of the path. The second two values  $bd(e_0)$  and  $base(e_{n-1})$  are the bottom delta recursively calculated for the path root, and the base

Figure 2.18: AAD of a bitmapping along two edges

address offset of the path leaf, which together with the domain range define the codomain of the path. A bitmapping describes the address map from the domain in the root to the codomain in the leaf of a path. This way, a bitmapping describes the mapping of equally sized contiguous memory regions realized by the path within the AMG. The bitmapping  $m(p_{r \rightarrow l})$  defines the range of bits in the window of the path root W(r) map, and the range of bits in the window of the path leaf W(l) that map to each other. The domain of a bitmapping is denoted D(m(p)).

$$m(p) = (lb(e_0), ub(e_0), bd(e_0), base(t(e_{n-1})))$$

where  $e_i = p(i)$  (2.23)

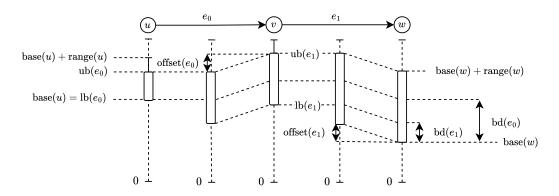

An example two-edge path  $p = (e_0, e_1)$  is visualized by Figure 2.18. Both edges introduce only bottom address clippings, and no top address clippings. The resulting bitmapping is  $m(p) = (lb(e_0), ub(e_0), bd(e_0), base(w))$ , with its domain  $D(m(p)) = [lb(e_0), ub(e_0))$  and its codomain equal to  $C(m(p)) = [base(w) + bd(e_0), base(w) + range(w))$ .

#### 2.5.2.4 Bitmapping Sets