### A 15-nW per Sensor Interference-Immune Readout IC for Capacitive Touch Sensors

Hussaini, Said; Jiang, Hui; Walsh, Paul; MacSweeney, Dermot; Makinwa, Kofi

10.1109/JSSC.2019.2907041

**Publication date**

**Document Version** Final published version

Published in IEEE Journal of Solid-State Circuits

Citation (APA)

Hussaini, S., Jiang, H., Walsh, P., MacSweeney, D., & Makinwa, K. (2019). A 15-nW per Sensor Interference-Immune Readout IC for Capacitive Touch Sensors. *IEEE Journal of Solid-State Circuits*, *54*(7), 1874-1882. Article 8691537. https://doi.org/10.1109/JSSC.2019.2907041

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A 15-nW per Sensor Interference-Immune Readout IC for Capacitive Touch Sensors

Said Hussaini, Hui Jiang<sup>®</sup>, Paul Walsh, Dermot MacSweeney, *Member, IEEE*, and Kofi A. A. Makinwa<sup>®</sup>, *Fellow, IEEE*

Abstract—This paper presents a readout IC that uses an asynchronous capacitance-to-digital-converter (CDC) to digitize the capacitance of a touch sensor. A power-efficient tracking algorithm ensures that the CDC consumes negligible power consumption in the absence of touch events. To facilitate its use in wake-on-touch applications, the CDC can be periodically triggered by a co-integrated ultra-low-power relaxation oscillator. At a 38-Hz scan rate, the readout IC consumes 15 nW per touch sensor, which is the lowest reported to date.

*Index Terms*—Asynchronous tracking logic, capacitance-to-digital-converter (CDC), self-capacitance sensor, stand-alone touch sensor, ultra-low-power oscillator.

#### I. INTRODUCTION

N BATTERY-POWERED devices such as smart meters and wearable and mobile devices, sleep modes are often used to extend battery life [1]–[3]. In such modes, most of the device's electronic systems will be disabled, with the exception of a watchdog circuit that wakes up the full system when necessary [1]–[3]. Since its power dissipation will then define an upper limit on battery life, a typical watchdog circuit will consist of an event-detecting sensor, together with an ultra-low-power timer and readout circuit.

Due to their low cost, low power, and robustness, capacitive touch sensors are often used to realize user interface functions such as buttons, sliders, and wheels [4]. Since capacitive sensors do not consume static power, the power consumption of a capacitive-sensing system will be limited by that of the readout circuitry, typically a capacitance-to-digital-converter (CDC) [5]–[19]. For use in watchdog circuits, ultra-low-power readout circuits are required, which must also be robust to external interference in order to limit the occurrence of power-wasting detection errors [5].

Energy-efficient CDCs based on sigma-delta modulation [6]-[12], period modulation [13], and slope integration [14], [15] have been reported. Although they can achieve high resolution, this is not required in watchdog circuits, and

Manuscript received November 20, 2018; revised January 21, 2019 and March 2, 2019; accepted March 11, 2019. Date of publication April 15, 2019; date of current version June 26, 2019. This paper was approved by Guest Editor Ángel Rodríguez Vázquez. (Corresponding author: Hui Jiang.)

- S. Hussaini, H. Jiang, and K. A. A. Makinwa are with the Electronic Instrumentation Laboratory, Department of Microelectronics, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: jianghuithu@gmail.com).

- P. Walsh and D. MacSweeney are with Cypress Semiconductor, Cork, T12 F76C Ireland.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2019.2907041

their power consumption is also too high. Much lower power with moderate resolution can be achieved by CDCs based on the successive approximation algorithm (SAR) [16]-[19]. State-of-the art designs only require a few nW to perform an 8-bit conversion [16]–[18]. However, touch sensors typically have a large baseline capacitance compared to the capacitance changes induced by touch events. A conventional CDC will then use most of its dynamic range and, thus, most of its power consumption, to digitize this baseline capacitance. To address a similar problem, an LSB-first SAR algorithm was proposed in [20], whose activity, and hence power dissipation, is dependent on the change in its analog input between successive readout cycles. When signal activity is low, only 3.7  $\mu$ W was required to perform a 10-b conversion. However, compared to the conventional SAR algorithm, the required logic is significantly more complex.

This paper presents a stand-alone readout IC [21] that consists of an asynchronous tracking CDC, whose power consumption depends on touch activity, which is periodically triggered by a nano-power timer. The CDC employs a differential architecture, which confers considerable robustness to common-mode interference and human finger noise, i.e., external interference coupled into the sensor by a touch event. At a 38-Hz scan rate, the readout IC consumes only 15 nW per sensor pad, which is about 46× better than the state of the art [2].

In the following, Section II describes the operating principle of the proposed readout IC. Sections III and IV discuss its circuit implementation, detailed design, measurement results, and comparison with the state of the art. Finally, conclusions are drawn.

#### II. OPERATING PRINCIPLE

#### A. Touch-Sensing System

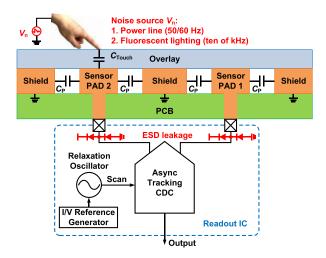

As described in [4], capacitive touch sensors can be divided into two types: 1) mutual-capacitance sensors and 2) self-capacitance sensors. A mutual-capacitance sensor typically consists of an array of conductive rows and columns separated by a dielectric. A dielectric overlay provides mechanical protection. When touched, part of the array's projected electric field will be diverted to ground, which, in turn, decreases the mutual capacitance between the nearest row and column intersection. In self-capacitance sensors, the capacitance between individual electrodes and ground is detected (Fig. 1). In this case, a touch event will increase the sensor's capacitance to ground. The readout IC senses the total capacitive load of a

Fig. 1. Schematic of the stand-alone touch readout IC connected to two sensor pads on a PCB.

finger on a row or column, which is typically much larger than their mutual capacitance. In addition, self-capacitance sensors typically cost less than mutual-capacitance sensors, mainly because they can be fabricated from a single metal layer, and only one connection per sensor is required. As a result, self-capacitance sensors are often the preferred choice due to their lower cost, higher touch signal, and thus simpler readout circuitry.

A block diagram of the proposed touch-sensing system is shown in Fig. 1. It consists of a readout IC and a PCB-based touch sensor. The latter consists of a conductive pad that is shielded electrically by a surrounding ground plane, and mechanically by a dielectric overlay (typically glass, or plastic). When touched, the capacitance of the sensor pad to ground will increase slightly. It can be modeled as a relatively large fixed (or baseline) capacitance ( $C_p$ ), together with a small variable capacitance ( $C_{touch}$ ) that represents the touch signal.

The readout IC consists of a CDC and an ultra-low-power relaxation oscillator that periodically triggers the CDC. Since the sensor pad is exposed to the environment, it will pick up external interference from the mains and from fluorescent lighting, which may contaminate the touch signal. To minimize detection errors, the readout IC should be designed to be robust to such interference.

#### B. Tracking Algorithm

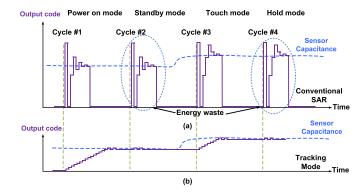

As shown in Fig. 2(a), where the sensor is readout by a conventional SAR CDC, the full SAR algorithm will be executed during every conversion cycle; even when the sensor's capacitance has not changed, e.g., during cycles #2 and #4 [16]–[19]. The corresponding SAR cycles are, thus, unnecessary and waste energy.

A more efficient algorithm is shown in Fig. 2(b), in which the CDC uses the stored digital output of the previous conversion cycle as a starting point and only updates its digital output if the capacitance changes. In effect, the CDC just tracks changes in sensor capacitance. Conversion time refers to the time interval between the beginning and end of a conversion.

Fig. 2. (a) SAR algorithm. (b) Tracking algorithm.

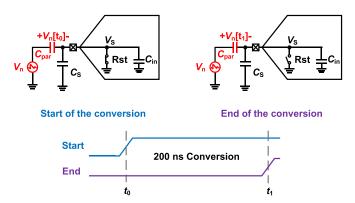

Fig. 3. Input CDS function of the CDC.

Like the LSB-first algorithm, the result is higher energy efficiency compared with the conventional SAR CDCs [20]. Moreover, the proposed tracking technique can be simply implemented with power-efficient asynchronous control logic.

#### C. Interference Immunity

The proposed tracking CDC is designed to operate in a differential manner, by digitizing the difference in capacitance between two neighboring touch sensing pads. Environmental interference that couples to both inputs of the CDC will then appear as a common-mode voltage and be rejected. Due to the mismatch between the two sense-pad capacitances, a small fraction of this interference will still appear as a differential voltage, but in practice, this residual interference is quite negligible. In applications where it is not feasible to sense neighboring pads, a dummy pad can be realized to facilitate the pseudodifferential operation.

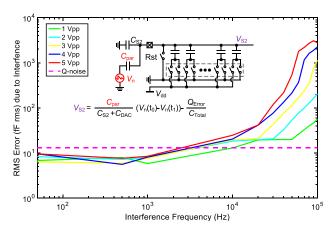

Another source of error is human finger noise, which is caused by capacitively coupled interference from the mains (50/60 Hz) and fluorescent lighting (tens of kHz) pickup [5]. This interference appears only at the touched pad, and so will not be rejected by the CDC's differential architecture. As will be explained next, however, the effect of such interference is mitigated by the fact that the CDC is only sensitive to changes in  $V_n$  that occur over a short period of time.

As shown in Fig. 3, human finger noise can be modeled as an interference source  $V_n$  that is coupled to the touched pad by a parasitic capacitance  $C_{\text{par}}$ . During the reset phase, while  $V_S$  is grounded,  $C_{\text{par}}$  is charged to  $V_n$  and stored at time  $t_0$ .

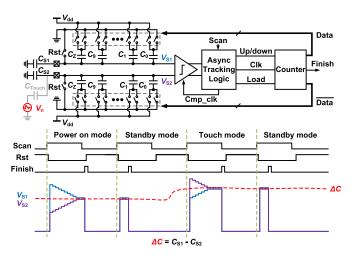

Fig. 4. Asynchronous tracking CDC and simplified timing diagram.

Thus,  $V_S$  sees only the change in  $V_n$  during conversion time. At the end of the conversion,  $t_1$ ,  $V_S$  is given by

$$V_S[t_1] = (V_n[t_1] - V_n[t_0]) \cdot \alpha$$

(1)

where  $\alpha$  is the ratio of  $C_{par}$  to the total capacitance present on the pad, which is due to the sensor, the capacitive digital-to-analog converter (CDAC), and any parasitic capacitances. Equation (1) corresponds to a correlated-double sampling (CDS) transfer function, which suppresses interference at low frequencies ( $<1/T_{conv}$ ). Thanks to the short conversion time of the CDC ( $\sim$ 200 ns for touch events), human finger noise will be significantly reduced. Moreover, the residual interference will be further attenuated by a factor of  $\alpha$ .

#### III. CIRCUIT IMPLEMENTATION

#### A. Asynchronous Tracking CDC

Fig. 4 shows the schematic and timing diagram of the proposed asynchronous tracking CDC. It consists of a differential CDAC, an asynchronous logic unit, a coarse-fine binary counter, and a dynamic comparator. The CDC digitizes the difference in capacitance  $\Delta C$  between two external capacitors  $C_{s1}$  and  $C_{s2}$ . At the start of each conversion, their voltages,  $V_{s1}$  and  $V_{s2}$ , respectively, are first reset to zero and then pulled up toward  $V_{\rm dd}$  by fixed baseline-compensating capacitors  $C_z$  (=9.2 pF). This is necessary because the lower limit of the comparator's common-mode input range is defined by the threshold voltage of an NMOS device. The pull-up function implemented by capacitors  $C_7$  ensures that  $V_{s1,2}$  are always within the comparator's common-mode range even with large sensor capacitances (up to 50 pF). The asynchronous logic unit and the binary counter then force  $V_{s1}$  =  $V_{\rm s2}$  by ramping the two CDACs up and down, respectively, starting from their mid-code. The final counter code data are then proportional to  $\Delta C$ . During the next conversion, the counter is loaded with the previous code and is either incremented or decremented to force  $V_{s1} = V_{s2}$  again. The CDC's activity is, thus, proportional to the change in  $\Delta C$ between readout cycles.

An analysis of the power consumption of CDACs used in data converters concludes that for the minimum power

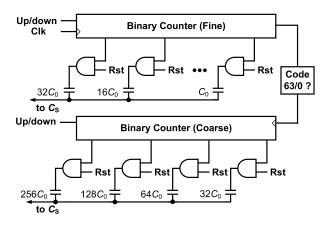

Fig. 5. Coarse-fine binary counter.

consumption, a CDAC should be implemented with unary weighted capacitors and uses a thermometer code to ramp its output voltage up/down toward the value of the input voltage [22]. However, a unary implementation will require a large number of switches and logic gates. Although the logic can be implemented with dynamic circuitry, its leakage current will be a dominant source of power consumption, especially at the low scan rates required for touch sensing. For this reason, a binary-weighted CDAC will be used in this design.

As discussed before, significant energy will be wasted if the full SAR algorithm is always executed, especially during the mid-code transitions of a binary CDAC. But even with the proposed tracking algorithm, small changes in sensor capacitance may still cause mid-code transitions, leading to increased power consumption. To reduce this, the CDAC is implemented as a combination of a 4-bit coarse CDAC and a 6-bit fine CDAC whose range is equivalent to two coarse LSBs. Each time the coarse CDAC toggles, the fine CDAC is reset to its mid-code, thus ensuring that the coarse CDAC only toggles when  $\Delta C$  changes by more than one coarse LSB. For such fine-only conversions, this technique reduces the maximum CDAC switching losses by  $\sim 16 \times$ .

The two CDACs are driven by 6- and 4-b binary counters, respectively. To save power, the fine counter is reset to its mid-code every time the coarse counter toggles. As shown in Fig. 5, this is implemented by setting the fine counter's MSB bit to 1 and its other bits to 0, whenever the coarse counter transitions to states 63 or 0. As discussed before, the range of the fine CDAC is equal to 2 LSBs of the coarse CDAC, so the output of the CDC can be decoded simply by adding the state of the fine counter to half the state of the coarse counter.

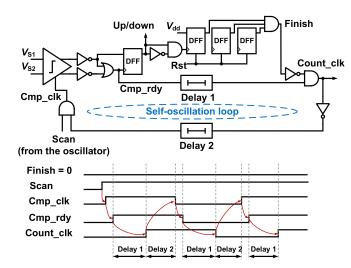

The CDC employs asynchronous logic based on a self-oscillating loop formed by the delay ( $\sim$ 30 ns) between the comparator's clock signal and its ready signal. As shown in Fig. 6, the self-oscillation loop starts and, while the Finish signal is low, provides a clock signal for the comparator and the counter. To minimize false decisions, the Finish signal stops the conversion only after the comparator's output changes sign three times. Two delay blocks, Delay 1 and Delay 2, implemented as inverter chains, are inserted into the oscillation loop to prevent errors due to incomplete settling. Delay 1 is designed to provide a delay of  $\sim$ 3 ns, as required for the logic that generates the Finish signal. Delay 2, on the other

Fig. 6. Asynchronous logic unit.

Fig. 7. Dynamic comparator.

hand, provides the  $\sim$ 12-ns delay required to ensure CDAC settling.

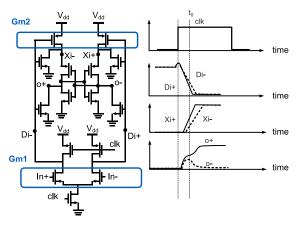

In order to make the CDC's operation fully dynamic, a low-noise single-phase comparator has been implemented. The schematics and timing of the comparator are shown in Fig. 7 [23]. When the clock signal is low, Di nodes are precharged to  $V_{\rm dd}$ , while Xi nodes and outputs of the comparator are reset to ground. After the rising edge of clock, Di node voltages drop at a rate that depends on the input voltages. At  $t = t_0$ , Gm1 amplifies the differential inputs. The outputs of Gm1 (Di+ and Di-) are connected to Gm2 pair and amplified even further. The Gm2 outputs (Xi nodes) will then drive the core latch. Thus, the differential input will be amplified by two gain stages before it drives the core latch, which reduces the total input-referred noise and offset of the core latch.

The comparator is designed to ensure that the CDC is quantization-noise limited. This reduces spurious activity due to thermal noise and thus reduces the CDC's average power consumption. The CDAC elements were sized for matching, and as such their thermal noise contribution is negligible. According to simulations, the total input-referred noise of the comparator is about 200  $\mu$ Vrms, which is  $\sim$ 6× smaller than the input signal swing ( $\sim$ 1.2 mV) corresponding to a 1-LSB step. Its simulated offset is less than 12 mV,

Fig. 8. Low-power oscillator and its timing diagram.

Fig. 9. Schematic of the reference generation circuits for the oscillator.

which results in a 10-LSB offset error at the output of the CDC. Being a static error, however, this does not generate false touch events. Over temperature, the worst-case variation of the offset was simulated to be only 1 mV, i.e., less than an LSB.

Since the CDC is designed for low power rather than speed, input leakage currents, e.g., due to electrostatic discharge (ESD) devices, may discharge the CDAC leading to decision errors. However, simulations show that the CDC's conversion time  $T_{\rm conv}$  (~90 ns-~1  $\mu$ s for fine-only conversions) is short enough to prevent such errors.

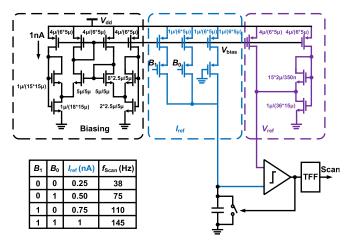

#### B. Oscillator

In order to trigger the CDC, a timer is required to provide the clock signal. For wake-up timer applications, the frequency stability specifications are very relaxed. However, if the frequency is too high, it will unnecessarily increase the scan rate of the CDC and thus its dynamic power consumption, while if it is too low, touch events may be missed. A frequency stability of 5% over temperature (25 °C–85 °C), which results in an acceptable 5% variation in power consumption, is a proper choice.

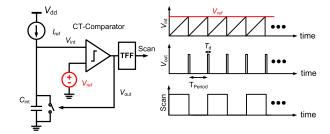

The schematic of the proposed relaxation oscillator is shown in Fig. 8. A current source ( $I_{\rm ref}$ ) charges an integration capacitor ( $C_{\rm int}$ ), causing a voltage ramp-up rate of  $I_{\rm ref}/C_{\rm int}$  on  $C_{\rm int}$ . A continuous-time comparator periodically resets the integration capacitor when its voltage  $V_{\rm int}$  exceeds  $V_{\rm ref}$ . The oscillator's schematic and the corresponding waveforms are shown in Fig. 9.

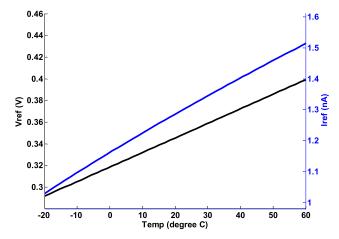

Fig. 10. Simulated temperature dependencies of the voltage and current reference generators.

Fig. 11. Continuous-time comparator.

The period of the relaxation oscillator ( $T_{period}$ ) can be expressed as

$$T_{\rm period} \approx \frac{V_{\rm ref}}{I_{\rm ref}} C_{\rm int}, \quad T_{\rm period} \gg T_d$$

(2)

where  $T_d$  is the comparator delay. Its output  $V_{\text{out}}$  is a short pulse with a low duty cycle  $T_d/T_{\text{period}}$ , which may be too short to reliably trigger the CDC. To increase the duty cycle, the output of the comparator is used to drive a T flip-flop (TFF). The resulting scan clock will then have a robust 50% duty cycle.

For stand-alone operation, references ( $V_{\rm ref}$  and  $I_{\rm ref}$ ) should be implemented on-chip. However, on-chip current and voltage references are often quite temperature dependent when biased at nano-ampere levels. According to (2), the oscillator's output frequency is determined by the ratio between  $I_{\rm ref}$  and  $V_{\rm ref}$ . If these two references have similar temperature dependencies, then the oscillation frequency will be temperature independent. This suggests a low-complexity ratio-metric method of building the circuit references.

In this design, both the charging current and the threshold voltage are derived from a constant inversion current source shown in Fig. 9. The biasing block is similar to a constant Gm circuit, with the usual resistor being replaced by self-cascoded nMOS transistors [24]. To compensate for process spread, the biasing circuit can be trimmed by adjusting the charging current with the help of a 2-bit current DAC controlled by B1 and B0. The Monte Carlo simulation shows that the spread in the oscillator's output frequency due to process variation and mismatch is only about  $10 \text{ Hz} (1\sigma)$ .

Fig. 12. Die micrograph of the readout IC

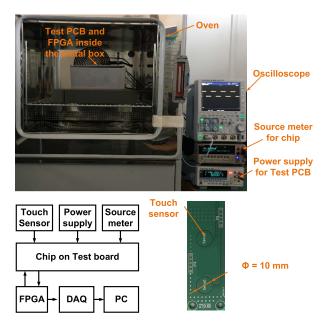

Fig. 13. Measurement setup.

Fig. 10 shows the results of simulating the behavior of the reference generators over temperature. The temperature coefficients of the voltage reference and current reference are 1.35 mV/°C and 6 pA/°C, respectively. The resulting oscillation frequency then has a temperature stability of  $\pm 2\%$  from 25 °C to 85 °C. To achieve a low operating current and low leakage, all transistors in the reference circuit are implemented with high-threshold devices.

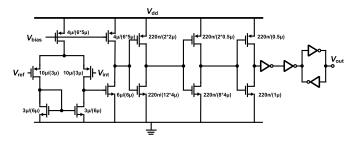

The proposed relaxation oscillator uses a low-power continuous-time comparator to periodically reset the integration capacitor when its voltage exceeds a certain threshold. As shown in Fig. 11, this consists of a preamp followed by a chain of inverters. The preamp consists of a two-stage operational amplifier that is biased by the current reference circuit, consuming 2 nA of static current. PMOS transistors are used as the input pair to allow the comparator work under a low-input common-mode voltage (Fig. 11). The amplifier then is followed by an inverter chain to provide enough comparator delay  $T_d$ . The first three inverters are sized to have low short-circuit currents when driven by signals with long rise/fall time. A regenerative back-to-back inverter latch at the end of the chain provides a reset signal with steep edges. Simulation shows the supply sensitivity of the oscillator is only 3.7 Hz/V.

Fig. 14. Transient response of the readout IC.

Fig. 15. Measured current consumption of the proposed tracking CDC.

#### IV. MEASUREMENT RESULTS AND COMPARISON

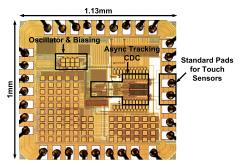

The readout IC is implemented in a standard TSMC 0.18- $\mu$ m CMOS process and occupies an active area of 0.1 mm² (Fig. 12). The CDC and oscillator occupy 80% and 20% of the total area, respectively. For good matching, the unit capacitors of the 6-bit fine CDAC are realized with fringe capacitors (~11 fF/LSB), while the 4-bit coarse CDAC is realized with MIM capacitors (~320 fF/LSB), to save area. The CDC has a  $\pm 10.8$ -pF differential input range when connected to 9.2-pF baseline capacitors.

The measurement setup for characterizing the proposed readout IC is shown in Fig. 13. A Keithley 2400 source meter is used as the supply voltage and also for current measurements. The field-programmable gate array (FPGA) is only used to program the IC's trim registers and to define various scan rates used to evaluate CDC performance. Measurements with the CDC connected to the touch sensor were made with the help of the on-chip clock. A climate chamber was used to characterize the frequency variation of the oscillator and the power consumption of the readout IC over temperature. The PCB touch panel is fabricated in an FR4 two-layer PCB technology, with a sensor diameter of 10- and 0.7-mm spacing to the ground plane (Fig. 13). The sensors are connected to the readout IC using standard pads.

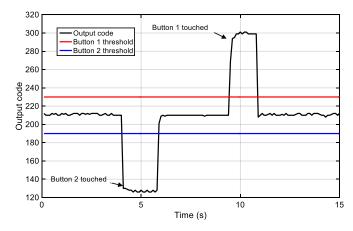

Fig. 14 shows the readout IC's response to an actual touch when sampled at a 38-Hz scan rate. For this measurement,

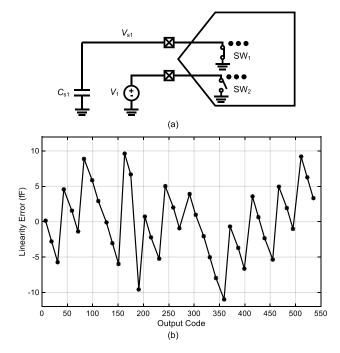

Fig. 16. (a) CDC's linearity measurement test bench and (b) results.

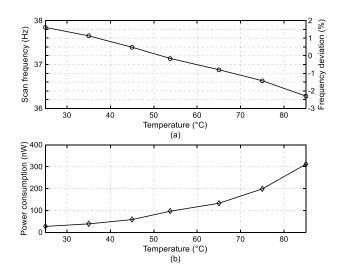

Fig. 17. Temperature sensitivity of the proposed readout IC. (a) Frequency deviation and (b) power consumption over temperature.

the two buttons have baseline capacitances of  $\sim$ 9 and  $\sim$ 11 pF, respectively, where the 2-pF difference in capacitance is due to PCB parasitics. (One button is closer to the chip than the other.) The typical range of button capacitance is from about 5 to 15 pF. Together, the CDC and the relaxation oscillator then consume 30 nW (CDC: 13.8 nW and oscillator: 16.2 nW) from a 1.35-V supply.

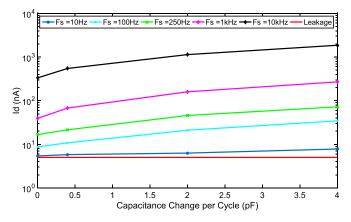

Fig. 15 shows the CDC's measured current consumption at different scan rates when the sensor's capacitance changes by a given amount  $\Delta C$  per readout cycle. This is emulated by using an external voltage source to drive its ground node, thus preloading it with a well-defined differential charge. As shown in Fig. 15, the CDC's current consumption is roughly proportional to the amount of  $\Delta C$  per readout cycle. This is measured when the CDC is supplied at 1 V.

|                           | This work             |       |       | [13]  | [14]   | [16] | [17]  | [18]            | [15]   | [19]    |    |

|---------------------------|-----------------------|-------|-------|-------|--------|------|-------|-----------------|--------|---------|----|

| Technique                 | Asynchronous Tracking |       |       | PM    | $ID^1$ | SAR  | SAR   | SAR             | DS     | SAR+VCO |    |

| Support Self-capacitance  | Yes                   |       |       | No    | Yes    | No   | No    | No              | Yes    | No      |    |

| Differential              | Yes                   |       |       | No    | No     | No   | Yes   | Yes             | No     | No      |    |

| Technology (nm)           | 0.18                  |       |       | 160   | 40     | 180  | 180   | 180             | 180    | 40      |    |

| $F_{\rm s}({ m kHz})$     | 102                   |       |       | 4.8   | 52.6   | 0.25 | 62.5  | 200             | 156.25 | 1000    |    |

| Cap-range (pF)            | ±10.8 <sup>2</sup>    |       |       | 8     | 11.3   | 75.3 | 12.66 | 6               | 30.7   | 5       |    |

| Resolution (fFrms)        | 11.462                |       | 1.4   | 12.3  | 6      | 1.1  | 5.2   | 8.7             | 1.1    |         |    |

| Cap-change (LSB/Cycle)    | 0                     | 10    | 50    | 100   |        |      |       |                 |        |         |    |

| Power (µW)                | 0.333                 | 0.553 | 1.143 | 1.863 | 14     | 1.84 | 0.16  | 7.25            | 9.4    | 0.11    | 75 |

| FoM <sup>5</sup> (fJ/c-s) | 61                    | 100   | 208   | 342   | 1870   | 141  | 181   | 35 <sup>4</sup> | 45     | 5300    | 55 |

TABLE I

COMPARISON WITH STATE-OF-THE-ART CDCs

- 1. Iterative delay-chain discharge.

- 2. Measured at a scan rate,  $F_s$ , of 10 kHz and a baseline capacitance of 9.2pF.

- 3. Excluding the on-chip oscillator.

- 4. Excluding the high frequency clock generator used for power gating amplifier, and SAR logic.

- 5. FoM = Power/ $(F_s \cdot 2^{\text{ENOB}})$ , ENOB =  $(20\log((\text{Cap-range/2}\sqrt{2})/(\text{LSB/}\sqrt{12}) 1.76) / 6.02$

Fig. 18. CDS transfer function for interference and the measured rms error  $(C_{par} = 1 \text{ pF})$ .

The test bench used to measure sensor linearity is shown in Fig. 16(a). The CDC is configured to operate in the single input mode, i.e., while one input is connected to an external capacitor, the other input is biased with an external reference voltage  $(V_1)$ . In order to avoid short circuits, the on-chip switch, SW<sub>2</sub>, is programed to be always open. During each conversion, the tracking algorithm adjusts the CDAC such that  $V_{s1} = V_1$ . Therefore, sweeping  $V_1$  can emulate capacitance changes. Since only one CDAC is active in this mode, each LSB corresponds to a  $2\times$  unit capacitance change. As the CDC employs a coarse-fine charge redistribution scheme, calibration is required to find the conversion step and the ratio of the coarse and fine capacitor banks. Fig. 16(b) shows the nonlinearity of the proposed CDC, which is less than 0.1% over the full (10.8-pF) range.

The proposed oscillator achieves a temperature sensitivity of 0.7%/°C, as shown in Fig. 17(a). Moreover, the power consumption of the readout IC versus temperature is shown in Fig. 17(b). At low temperature, the power consumption is

$\label{thm:table} TABLE\ II$   $Comparison\ With\ State-of-the-Art\ Stand-Alone\ Touch\ Sensors$

| Product          | Year | Scan-rate | Power/Button (uW) |  |  |

|------------------|------|-----------|-------------------|--|--|

| MSP430FR2633 [1] | 2015 | 8 Hz      | 0.690             |  |  |

| EFM32 [2]        | 2016 | 10 Hz     | 1.561             |  |  |

| PSOC4 [3]        | 2016 | 8 Hz      | 3.961             |  |  |

| This work        | 2017 | 38 Hz     | 0.015             |  |  |

mostly dominated by the dynamic power consumption of the system. At higher temperatures, however, the leakage current of the chip increases exponentially, dominating the total power consumption.

The CDC's immunity to interference was characterized by coupling a voltage source to one of its inputs via a 1-pF capacitor and measuring the resulting rms error (2<sup>15</sup> samples).

Fig. 18 shows that low-frequency interference, e.g., 50/60 Hz, is indeed strongly attenuated. At higher frequencies, this attenuation becomes amplitude dependent, since large signals increase  $T_{\rm conv}$  and, thus, reduce the cutoff frequency of the CDC's CDS function.

At a 10 kHz scan rate, the CDC draws 333 nA from a 1-V supply. It achieves a quantization-noise-limited resolution of 11.46 fF $_{\rm rms}$  (39.7 fF · LSB) and a figure-of-merit (FoM) $_{\rm Walden}$  of 61 fJ/c · s. In Tables I and II, the performance of the tracking CDC is summarized and compared with the state-of-the-art and to commercial products. Compared to prior CDCs [6]–[9], it achieves competitive energy efficiency, while offering self-capacitance-sensing capability with the excellent interference immunity. Compared to the state-of-the-art standalone readout systems for touch sensors, it consumes 15 nW per button, which is  $46\times$  better than the state of the art [2]. These characteristics make the presented readout IC, a promising candidate for self-capacitance touch sensors with a limited power budget.

#### V. CONCLUSION

This paper presents an ultra-low-power stand-alone readout IC for self-capacitance touch sensors. Low-power operation is achieved by utilizing the charge redistribution technique. An asynchronous tracking algorithm is proposed to realize data-dependent power consumption. This is especially efficient in wake-on-touch applications where the touch sensor spends most of its time in the idle mode. Employing a differential architecture together with an intrinsic CDS function heavily attenuates the effect of environmental interference and human finger noise. Including the on-chip relaxation oscillator, the readout IC achieves competitive energy efficiency, while offering self-capacitance sensing capability with the excellent interference immunity. The readout IC consumes only 15 nW per button from a 1.35-V supply (coin cell).

#### REFERENCES

- [1] Texas Instrument. MSP430FR2633, Datasheet. Accessed: 2015. [Online]. Available: http://www.ti.com/lit/ds/symlink/msp430fr2633.pdf

- [2] Silicon Lab. EFM32. Accessed: 2016. [Online]. Available: https://www.silabs.com/documents/public/application-notes/an0028efm32-lesense-capacitive-sense.pdf

- [3] Cypress Semiconductor. PSOC4. Accessed: 2016. [Online]. Available: http://www. cypress.com/file/231251/download

- [4] H. Klein et al., "Advanced capacitive sensing for mobile devices," in Low-Power Analog Techniques, Sensors for Mobile Devices, and Energy Efficient Amplifiers: Advances in Analog Circuit Design. Cham, Switzerland: Springer, 2018.

- [5] J.-H. Yang et al., "A highly noise-immune touch controller using filtered-delta-integration and a charge-interpolation technique for 10.1-inch capacitive touch-screen panels," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2013, pp. 390-391.

- [6] Z. Tan, R. Daamen, A. Humbert, Y. V. Ponomarev, Y. Chae, and M. A. P. Pertijs, "A 1.2-V 8.3-nJ CMOS humidity sensor for RFID applications," *IEEE J. Solid-State Circuits*, vol. 48, no. 10, pp. 2469-2477, Oct. 2013.

- [7] H. Jiang, S. Amani, J. G. Vogel, S. H. Shalmany, and S. Nihtianov, "A 117DB in-band CMRR 98.5DB SNR capacitance-to-digital converter for sub-nm displacement sensing with an electrically floating target," in Proc. IEEE Symp. VLSI Circuits, Jun. 2018, pp. 159-160.

- [8] S. Park, G.-H. Lee, and S. Cho, "A 2.69 uW dual quantization-based capacitance-to-digital converter for pressure, humidity, and acceleration sensing in 0.18 um CMOS," in Proc. IEEE Symp. VLSI Circuits, 2018, pp. 163-164.

- [9] S. Oh, W. Jung, K. Yang, D. Blaauw, and D. Sylvester, "15.4b incremental sigma-delta capacitance-to-digital converter with zoom-in 9b asynchronous SAR," in Symp. VLSI Circuits Dig. Tech. Papers, Honolulu, HI, USA, 2014, pp. 1-2.

- [10] S. Xia, K. Makinwa, and S. Nihtianov, "A capacitance-to-digital converter for displacement sensing with 17b resolution and 20µs conversion time," in Proc. IEEE Int. Solid-State Circuits Conf., San Francisco, CA, Feb. 2012, pp. 198-200.

- [11] R. Yang, M. A. P. Pertijs, and S. Nihtianov, "A precision capacitanceto-digital converter with 16.7-bit ENOB and 7.5-ppm/°C thermal drift," IEEE J. Solid-State Circuits, vol. 52, no. 11, pp. 3018–3031, Nov. 2017.

- [12] B. Yousefzadeh, W. Wu, B. Buter, K. Makinwa, and M. Pertijs, "A compact sensor readout circuit with combined temperature, capacitance and voltage sensing functionality," in Proc. Symp. VLSI Circuits, Kyoto, Japan, Jun. 2017, pp. C78-C79.

- [13] Y. He, Z.-Y. Chang, L. Pakula, S. H. Shalmany, and M. Pertijs, "27.7 A 0.05 mm<sup>2</sup> 1V capacitance-to-digital converter based on period modulation," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, San Francisco, CA, USA, Feb. 2015, pp. 1-3.

- [14] W. Jung, S. Jeong, S. Oh, D. Sylvester, and D. Blaauw, "27.6 A 0.7pF-to-10nF fully digital capacitance-to-digital converter using iterative delaychain discharge," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, San Francisco, CA, USA, Feb. 2015, pp. 1-3.

- [15] S. Oh et al., "A dual-slope capacitance-to-digital converter integrated in an implantable pressure-sensing system," IEEE J. Solid-State Circuits, vol. 50, no. 7, pp. 1581-1591, Jul. 2015.

- [16] H. Ha, D. Sylvester, D. Blaauw, and J.-Y. Sim, "12.6 A 160nW 63.9fJ/conversion-step capacitance-to-digital converter for ultra-lowpower wireless sensor nodes," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, San Francisco, CA, USA, Feb. 2014, pp. 220-221.

- [17] H. Omran, A. Alhoshany, H. Alahmadi, and K. N. Salama, "A 35fJ/step differential successive approximation capacitive sensor readout circuit with quasi-dynamic operation," in Proc. IEEE Symp. VLSI Circuits, Jun. 2016, pp. 24-25.

- [18] H. Jiang, Z. Wang, C. Zhang, H. Jiang, and Z. Wang, "A combined low power SAR capacitance-to-digital analog-to-digital converter for multisensory system," Analog Integr. Circuits Signal Process., vol. 75, no. 2, pp. 311-322, May 2013.

- [19] A. Sanyal and N. Sun, "An energy-efficient hybrid SAR-VCO  $\Delta\Sigma$ capacitance-to-digital converter in 40-nm CMOS," in Proc. IEEE J. Solid-State Circuits, vol. 52, no. 7, pp. 1966-1976, Jul. 2017.

- [20] F. M. Yaul and A. P. Chandrakasan, "A 10 bit SAR ADC with datadependent energy reduction using LSB-first successive approximation,' in Proc. IEEE J. Solid-State Circuits, vol. 49, no. 12, pp. 2825-2834, Dec. 2014.

- [21] S. Hussaini, H. Jiang, P. Walsh, D. MacSweeney, and K. A. A. Makinwa, "A 15nW per button noise-immune readout ic for capacitive touch sensor," in Proc. IEEE 44th Eur. Solid State Circuits Conf., Sep. 2018, pp. 190-193.

- [22] M. Saberi, R. Lotfi, K. Mafinezhad, and W. A. Serdijn, "Analysis of power consumption and linearity in capacitive digital-to-analog converters used in successive approximation ADCs," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 58, no. 8, pp. 1736-1748, Aug. 2011.

- [23] M. Miyahara, Y. Asada, D. Paik, and A. Matsuzawa, "A low-noise selfcalibrating dynamic comparator for high-speed ADCs," in Proc. IEEE Asian Solid-State Circuits Conf., Nov. 2008, pp. 269-272.

- [24] E. M. Camacho-Galeano, C. Galup-Montoro, and M. C. Schneider, "A 2-nW 1.1-V self-biased current reference in CMOS technology," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 52, no. 2, pp. 61-65, Feb. 2005.

Said Hussaini received the B.Sc. degree in electrical engineering from the Ferdowsi University of Mashhad, Mashhad, Iran, in 2014, and the M.Sc. degree (cum laude) from the Electronic Instrumentation Laboratory, Delft University of Technology (TU Delft), Delft, The Netherlands, in 2017.

Since 2017, he has been an Analog/Mixed-Signal Designer with SiTime Corporation, Delft. His current research interests include nano-powered analog/mixed-signal ICs and precision sensor interface ICs.

Hui Jiang received the master's degree in integrated circuit engineering from Tsinghua University, Beijing, China, in 2013.

He is currently a Ph.D. Researcher with the Electronic Instrumentation Laboratory, Delft University of Technology, Delft, The Netherlands. His doctoral work involves the design of energy-efficient readout ICs for piezo-based sensors and capacitive displacement sensors. His research has resulted in several patents and publications in JSSC, ISSCC, and VLSI.

Mr. Jiang is a Committee Member of the SSCS

Young Professionals. He was a recipient of the ISSCC Student Travel Grant in 2015, the Third Prize of the Benelux Student Chip Design Competition in 2016, and the IEEE Solid-State Circuits Society Predoctoral Achievement Award in 2018. He serves as a reviewer for IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II, IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, IEEE Sensors Journal, IEEE Transactions on Instrumentation AND MEASUREMENT, and SENSORS AND ACTUATORS A: PHYSICAL.

**Paul Walsh** was born in Limerick, Ireland. He received the B.E. degree in electronic engineering from the University of Limerick (UL), Limerick, in 1999, and the M.Eng. degree from the University of Michigan, Ann Arbor, MI, USA in 2004.

He is currently a Senior MTS Architect with the Microcontroller and Connectivity Division, Cypress Semiconductor, Cork, Ireland, where he is responsible for both capacitive and inductive sensing at the Cypress' Capacitive Sensing Centre of Excellence (COE). At Cypress, he has led the development

of capacitive-sensing IP for touch and fingerprint controllers. He currently manages the Systems Research and Development Team, COE, with a focus on the next-generation sensing.

**Dermot MacSweeney** (M'02) was born in Cork, Ireland. He received the B.E. and M.Eng.Sc. degrees in electrical engineering from University College Cork (UCC), Cork.

He was with UCC where he worked on compact modeling and parameter extraction. He is currently a Design Engineering Director with the Microcontroller and Connectivity Division, Cypress Semiconductor, Cork, where he is worked on high-speed systems for applications in broadband communication, specifically for SONET and Ethernet applica-

tions, and in addition, he worked on the modeling of SiGe bipolar devices at very high speeds. He manages the Analog Team, Cypress' Centre of Excellence for Capacitive Sensors, Cork. His main interests are in the design of human interface devices where his team has developed several generations of touchscreen controllers, fingerprint readers, and capsense controllers. His research involved the development of subcircuit models, the analysis of high-frequency effects, efficient parameter extraction techniques, and statistical analysis of bipolar devices which he published in several IEEE JOURNALS and IEEE conferences.

Kofi A. A. Makinwa (M'97–SM'05–F'11) received the B.Sc. and M.Sc. degrees from Obafemi Awolowo University, Ife, Nigeria, in 1985 and 1988, respectively, the M.E.E. degree from the Philips International Institute, Eindhoven, The Netherlands, in 1989, and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2004.

From 1989 to 1999, he was a Research Scientist with Philips Research Laboratories, Eindhoven, where he worked on interactive displays and digital recording systems. In 1999, he joined the Delft

University of Technology, where he is currently an Antoni van Leeuwenhoek Professor and the Head of the Microelectronics Department. He has coauthored or edited more than 15 books and more than 250 technical papers, and holds more than 30 patents. His research interests include the design of mixed-signal circuits, sensor interfaces, and smart sensors.

Dr. Makinwa is a member of the Royal Netherlands Academy of Arts and the Sciences and the Editorial Board of the *Proceedings of the IEEE*. For his doctoral research, he received the 2005 Simon Stevin Gezel Award from the Dutch Technology Foundation. At the 60th anniversary of ISSCC, he was recognized as a Top-10 Contributor. He was a co-recipient of 15 best paper awards from JSSC, ISSCC, VLSI, ESSCIRC, and Transducers, among others. He is the Analog Subcommittee Chair of the International Solid-State Circuits Conference (ISSCC). He is also on the program committees of the VLSI Symposium, the European Solid-State Circuits Conference (ESSCIRC), and the Advances in Analog Circuit Design (AACD) Workshop. He has been a Guest Editor of the *Journal of Solid-State Circuits*(JSSC). He has served as a Distinguished Lecturer and an Elected AdCom member for the IEEE Solid-State Circuits Society.