# Wafer scale fabrication of Josephson junctions

by

# **Pim Duivestein**

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on ......at ....

| Student number:   | 4568249                     |                      |

|-------------------|-----------------------------|----------------------|

| Project duration: | September 1, 2020 – June 4, | 2021                 |

| Thesis committee: | Prof. dr. ir. L. DiCarlo,   | TU Delft, supervisor |

|                   |                             | TU Delft             |

|                   |                             | TU Delft             |

| Daily supervisor: | ir. N. Muthusubramanian,    | TU Delft             |

# Abstract

In this thesis variations in the Josephson junction conductance across a 100 mm wafer are studied. For this study junctions fabricated with a Dolan bridge and with the Manhattan layout are used. These junctions are fabricated on a planar and a non-planar NbTiN base layer to characterise the uniformity. On a planar base junctions fabricated with a Dolan bridge showed higher uniformity and yield than junctions with the Manhattan layout. On a non-planer base junctions fabricated with a Manhattan layout showed a higher uniformity than the Dolan bridge junctions. This can be attributed to the through silicon vias, which affect the resist spinning required for the Dolan bridge.

Manhattan style junctions are fabricated on a Si base layer in an attempt to improve the uniformity across a 100 mm wafer. By fabricating junctions on Si overall fabrication complexity is reduced, while also reducing the fabrication time. These junctions are used to investigate the role of oxygen ashing prior to the junction deposition. We find that the ashing increase the uniformity of the junctions, however, further attempts to improve the uniformity using different ashing steps did not how any additional improvements.

Finally, to explain the variations in Manhattan style junctions a geometric model is introduced. This model is based on the thickness of the top resist stack, which could potentially affect the width of the junction electrodes. The model is compared with SEM images and with the coefficient of variation. The model shows correspondence with the SEM data, but overestimates the variations when compared with the coefficient of variation.

# Acknowledgements

During the time I worked on my thesis I got to know a lot of new people and learn new things. I would like to thank all of them for making this an enjoyable and educational experience. However, there are a few people that I would like to thank in particular.

First of all I would like to thank Leo for the opportunity to join his lab during these difficult times. His expertise and feedback helped me throughout my thesis, especially his help on the geometric model was invaluable.

Thijs your help with the geometric model and your insights on the different aspects that could play a role helped a lot.

The members of the fabrication team, Matvey, Christos and Alessandro helped me in and around the cleanroom. Matvey, your work on the automatic probe station saved me from measuring a lot of junctions. Christos, your upbeat attitude and expertise was great to have around in the cleanroom. Alessandro, your critical feedback and experience prevented me from pursuing dead ends.

Hiresh and Santiago, you were great company during to have around in the lab and also outside of the university. I hope we can have some more dinners together in the future.

Sean even though we worked together for a short time I enjoyed our time together and I'm gratefully for your help towards my thesis.

Lastly, I would like to thank my daily supervisor Nandini for training me in the cleanroom and her interest in my project. You always made time for me if I had any questions and gave a detailed explanation. The indian food you made helped brighten up my day.

Of course, I also want to thank my friends, family and girlfriend, for supporting me during this period and for being patient with me during my long work days.

Pim Duivestein Delft, June 4, 2021

# Contents

| Ał           | stract                                                                                                                                                                                                                                                                  | iii                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Lis          | t of Figures                                                                                                                                                                                                                                                            | ix                        |

| Lis          | t of Tables                                                                                                                                                                                                                                                             | xiii                      |

| 1            | Introduction         1.1       Motivation         1.2       Objective         1.3       Outline                                                                                                                                                                         |                           |

| 2            | Theory         2.1       Superconductivity         2.2       Josephson Junction         2.3       Harmonic Oscillator         2.4       Superconducting Qubits         2.5       Surface Code         2.6       Nanofabrication Processes         2.7       Fabrication | 5<br>10<br>11<br>13<br>16 |

| 3            | Junction Characterisation         3.1 Surface-17 Test Pads         3.2 NbTiN Base Comparison                                                                                                                                                                            |                           |

| 4            | All Aluminum Junctions         4.1 Design         4.2 Ashing                                                                                                                                                                                                            |                           |

| 5            | Geometric Model         5.1       Resist Shadowing                                                                                                                                                                                                                      | 49<br>51                  |

| 6            | Conclusion and Outlook         6.1 Conclusion                                                                                                                                                                                                                           |                           |

| Α            | Filtering of data                                                                                                                                                                                                                                                       | 57                        |

| В            | Fabrication Recipe: Junctions on NbTiNB.1 Substrate preparation.B.2 Base Patterning.B.3 Josephson Junction.                                                                                                                                                             | 61                        |

| $\mathbf{C}$ | Fabrication Recipe: All Aluminum Junctions                                                                                                                                                                                                                              | 65                        |

# List of Figures

| 2.1  | Schematic representation of a Josephson junction connected to a bias voltage V. Two super-<br>conducting materials with phase $\phi_L$ and $\phi_R$ respectively are separated by an insulating barrier.<br>Figure taken from [27].                                                                                                                                                                                                                                              | 5  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

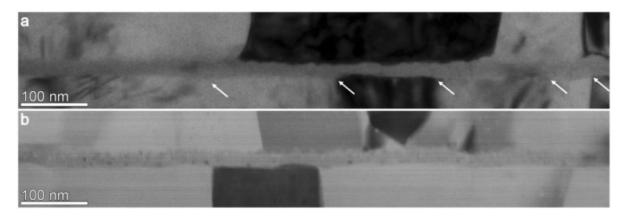

| 2.2  | TEM images of a Al/AlO <sub>x</sub> /Al junction fabricated. In figure a the AlO <sub>x</sub> barrier is formed with dynamic oxidation using pure $O_2$ . The white arrow points to grain boundaries. In figure b the AlO <sub>x</sub> barrier is formed with dynamic oxidation using pure $O_2$ in the presence of UV-illumination to enhance dynamic oxidation. Figure taken from [33]                                                                                         | 7  |

| 2.3  | Schematic representation of the resist stack used for the fabrication of Dolan bridge junctions. The top resist layer is used to create a Dolan bridge. The color correspond to: Red - first metal deposition, Blue - second metal deposition, Grey - Si, Light Blue - PMGI, Light Red - PMMA                                                                                                                                                                                    | 8  |

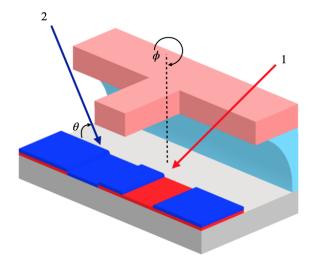

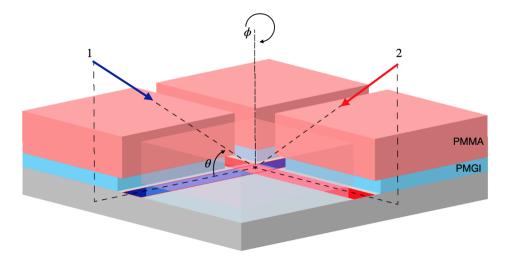

| 2.4  | Schematic representation of the resist stack used for the fabrication of Manhattan junctions.<br>The color correspond to: Red - first metal deposition, Blue - second metal deposition, Grey - Si,<br>Light Blue - PMGI, Light Red - PMMA.                                                                                                                                                                                                                                       | 9  |

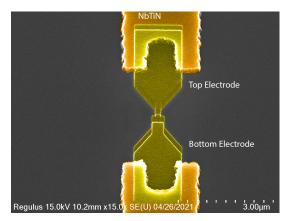

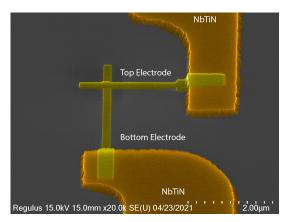

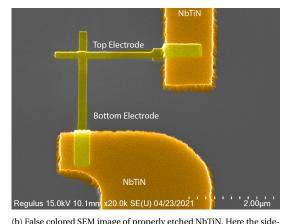

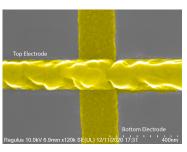

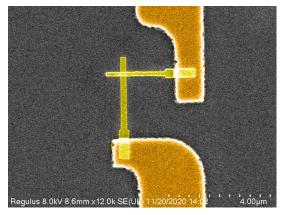

| 2.5  | False colored SEM images of both Josephson junctions types at a 45° tilt. The aluminum elec-<br>trodes are yellow and the NbTiN base layer is orange                                                                                                                                                                                                                                                                                                                             | 10 |

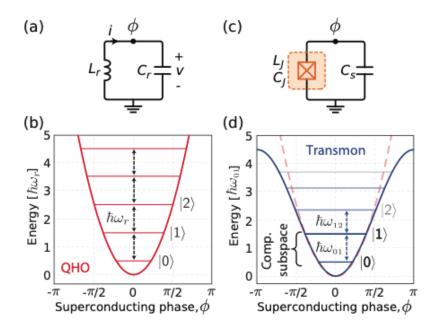

| 2.6  | Comparison between a harmonic oscillator and an anharmonic oscillator. The harmonic oscillator is constructed by using a LC-circuit, whereas the anharmonic oscillator uses a Josephson junction instead of an inductor in the LC-circuit, to create an anharmonicity. In the anharmonic oscillator the energy spacing's between each level is different, which allows for the confinement of the computational subspace to the lowest two energy levels. Figure taken from [42] | 10 |

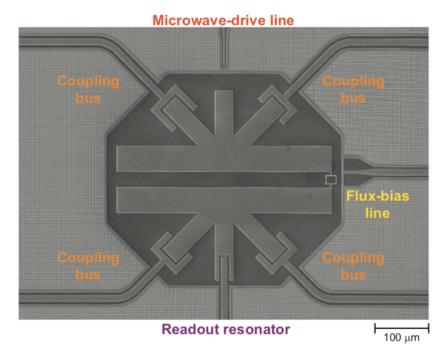

| 2.7  | SEM image of the starmon design. Figure taken from [50]                                                                                                                                                                                                                                                                                                                                                                                                                          | 12 |

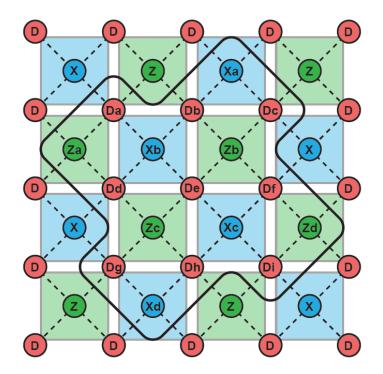

| 2.8  | Layout of the surface-code fabric. The black line encloses the Surface-17 layout, which consists of 8 data qubits and 9 ancilla qubits. The red circles represent the data qubits and the blue (green) circles represent the ancilla qubits used for performing X-type (Z-type) parity checks on the nearest-neighbor data qubits. Figure taken from [50].                                                                                                                       | 13 |

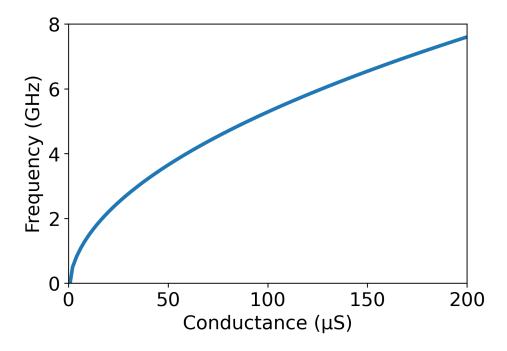

| 2.9  | The transmon qubit frequency as a function of the Josephson junction conductance. These two parameters are related to each other by the Ambegaokar-Baratoff relation. For this figure the following values are used for the $E_c = 0.3$ GHz and $M_{\#} = 130$ GHzk $\Omega$ .                                                                                                                                                                                                   | 15 |

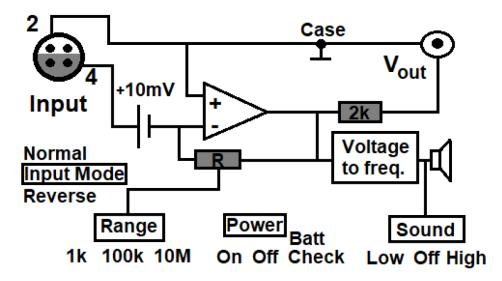

| 2.10 | Electrical circuit of the junction measurement box.                                                                                                                                                                                                                                                                                                                                                                                                                              | 16 |

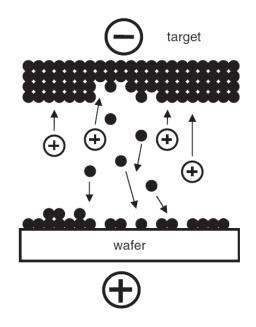

| 2.11 | Schematic representation of a sputtering process. The Ar ions are attracted to the target material and will dislocate atoms from it. These atoms fly through the chamber, before being deposited on the wafer.                                                                                                                                                                                                                                                                   | 16 |

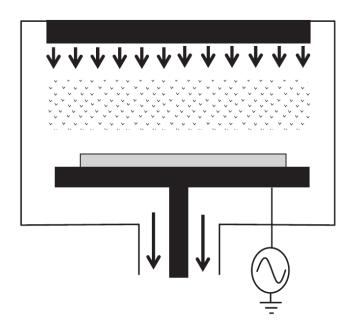

| 2.12 | Schematic representation of the chamber of a RIE system. The gas is injected at the top of the chamber. The RF voltage ignites a plasma which splits the gas into ions and excited neutrals. The ions are accelerated towards the bottom electrode and etch the substrate by physically bombarding it, while the excited neutrals chemically react with the substrate to form a volatile product that is removed from the substrate.                                             | 17 |

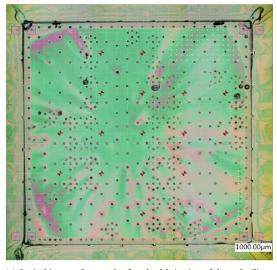

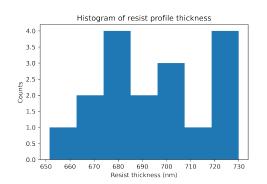

| 2.13 | Optical image of a $13 \times 13$ mm chips with through silicon vias on in. The image shows color alterations, which correspond to height variations in the resist as seen in figure 2.13b. This figure shows the resist height off 17 points corresponding to the positions of the qubits on a Surface-17 device.                                                                                                                                                               | 21 |

| 2.14 | False colored SEM images of an over etched and 2.14a and a properly etched 2.14b etched NbTiN base. These SEM images are taken after the deposition of the Josephson junctions                                                                                                                                                                                                                                                                                                   | 22 |

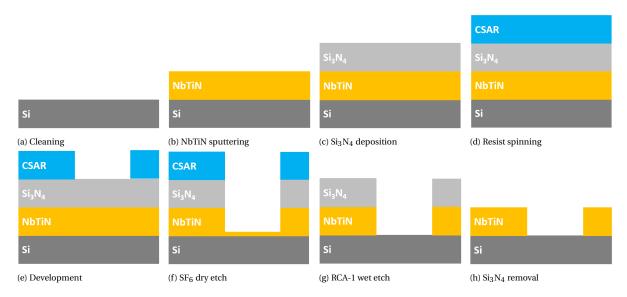

| 2.15       | 5 Graphical representation of the fabrication procedure to obtain NbTiN with the desired patterns<br>on the wafer. First the wafer is cleaned with BOE to remove $SiO_x$ present on the wafer 2.15a,<br>followed by the sputtering of NbTiN 2.15b and PECVD of $Si_3N_4$ 2.15c. The electron beam resist<br>ARP.6200-18 (CSAR) is spun on top 2.15d and exposed using a EBPG. The resist is developed<br>using pentyl acetate 2.15e. The $Si_3N_4$ and NbTiN are etched using RIE with SF <sub>6</sub> while keeping a<br>thin layer of NbTiN on the substrate 2.15e. The CSAR is removed using NMP followed by a wet<br>etch using the constituents of RCA-1 at 33 °C to remove the thin layer of NbTiN 2.15g. Finally<br>the $Si_3N_4$ is removed using HF 2.15h. | 22             |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

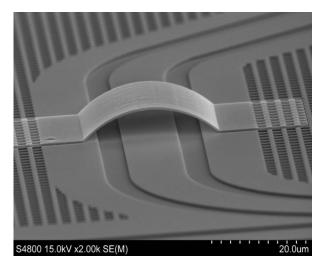

| 2.16       | 6 SEM image of an airbridge over a co-planer waveguide. The airbridge is used to connect the ground plane on both sides of the co-planer waveguide.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24             |

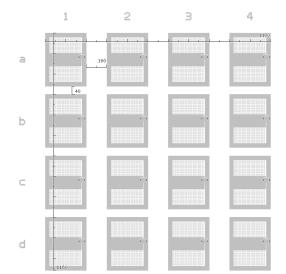

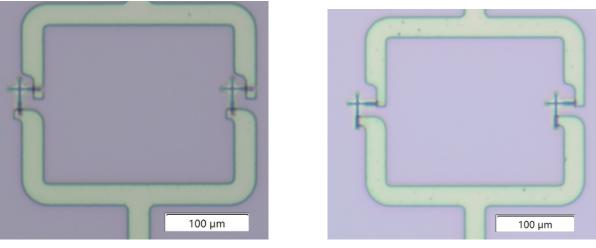

| 3.1        | Schematic representation of the design used for the test pads and test array. The grey area corresponds to Si, the white area to NbTiN and the black are corresponds to the position of the Josephson junctions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25             |

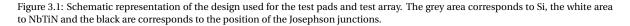

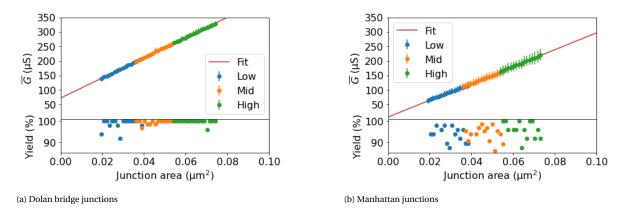

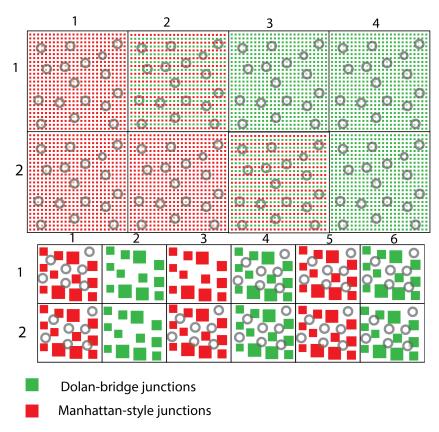

| 3.2<br>3.3 | Schematic representation of the Surface-17 test design and the layout of the wafer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26<br>26<br>27 |

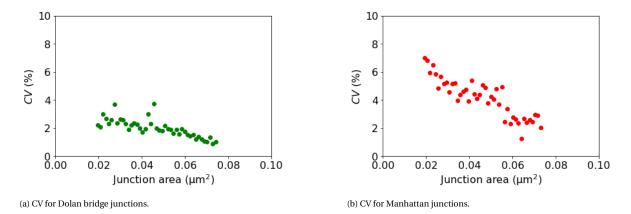

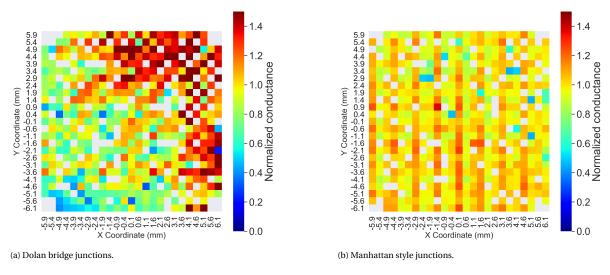

| 3.4        | CV of the Josephson junction conductance as a function of the designed junction area of the SQUID loop. The CV for Dolan bridge junctions is lower than for the Manhattan junctions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27             |

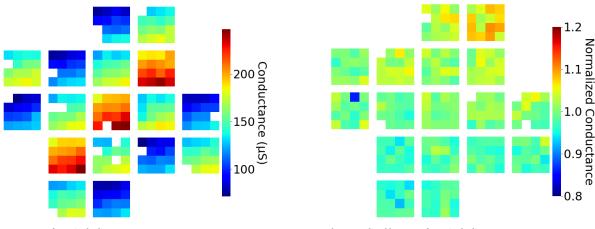

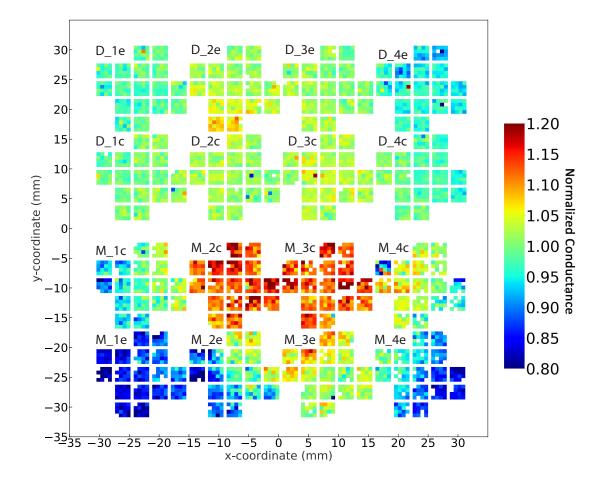

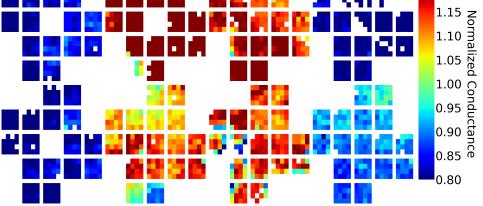

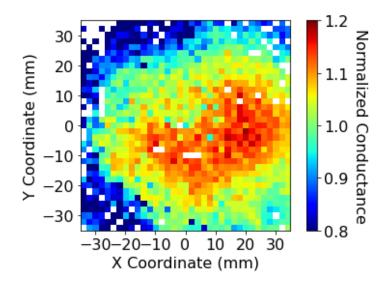

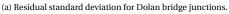

| 3.5<br>3.6 | Heatmap for a single die. The white spaces correspond to shorted, open or half-open junctions.<br>Normalized heatmap of the wafer used to study the variations in Josephson junction conduc-<br>tance. The normalization for Dolan bridge junctions and Manhattan junctions is done sep-<br>arately. Dolan bridge junctions seem to show some variations from center to edge, whereas                                                                                                                                                                                                                                                                                                                                                                               | 28             |

| 3.7        | Manhattan junctions show much larger variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29             |

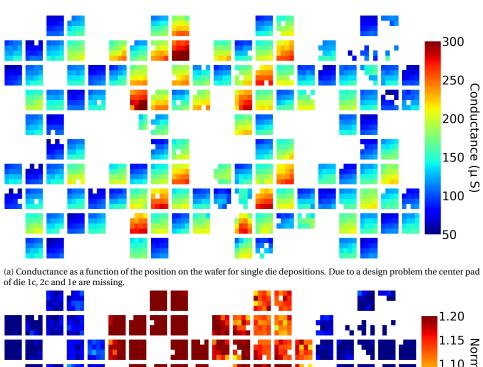

| 3.8        | tance for the four samples in the middle of the figure. However the normalized heatmap shows that there are large variations in the conductance per die deposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30             |

| 3.9        | wafer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31             |

| 3.10       | nification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32             |

| 3.11       | smaller spread than the single die depositions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32             |

| 3.12       | junctions after development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34             |

| 3.13       | Josephson junctions fabricated on a planar NbTiN base layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35             |

|            | device. The bottom chips have the same size as a Surface-7 device, which arrays of Dolan bridge<br>and Manhattan junctions fabricated on it.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36             |

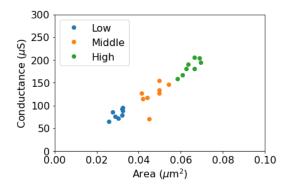

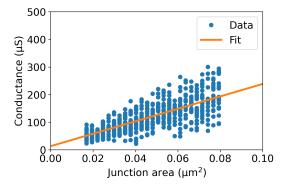

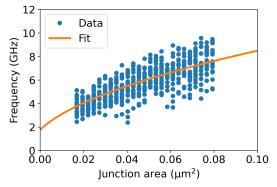

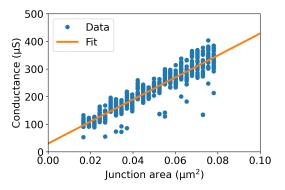

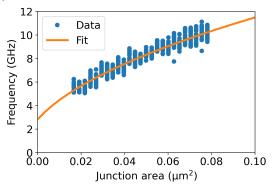

| 3.14       | <sup>4</sup> Conductance and predicted qubit frequency as a function of the overlap area for both Josephson junction types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37             |

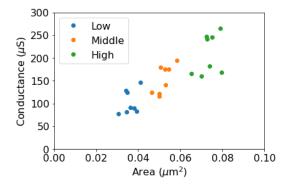

| 3.15       | 5 Conductance and predicted qubit frequency as a function of the overlap area for both Josephson junction types.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37             |

|            | 6 Normalized conductance as a function of the X and Y coordinate for both junction types 7 Coefficient of variation as a function of the overlap area for a non-planar base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38<br>38       |

| 4.1   | Schematic representation of the design used to study the variations in the conductance on a bare Si wafer.                                                                                  | 39         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

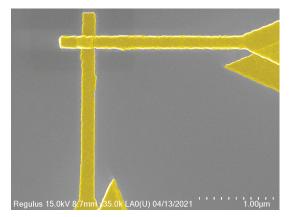

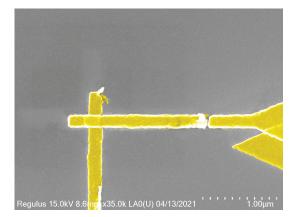

| 4.2   | False colored SEM images of all aluminum junctions at a magnification of 35k. The right figure shows a gap in the aluminum resulting in an open junction. The blue corresponds to aluminum. | 41         |

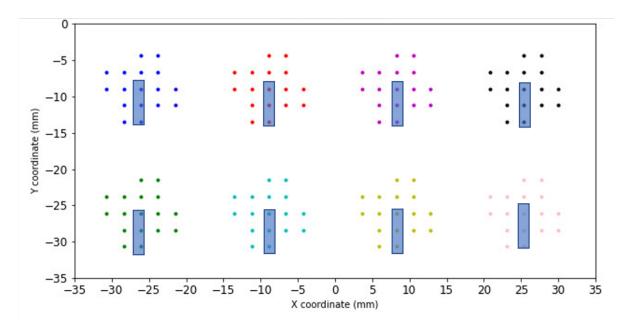

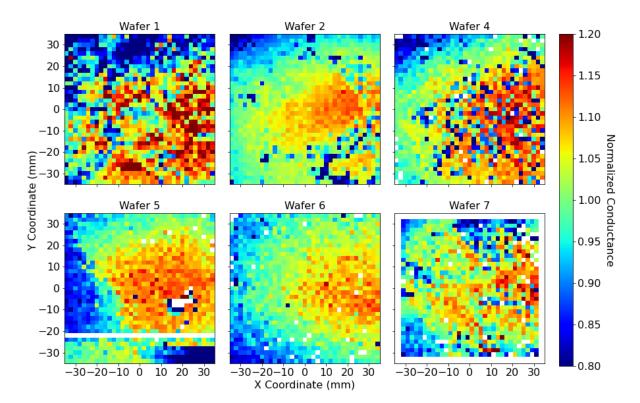

| 4.3   | Mean normalized conductance as a function of X and Y coordinate of the wafers used to test the                                                                                              | 41         |

| 4.5   | influence of ashing on the uniformity of Josephson junctions across a 100 mm wafer. Wafer 1                                                                                                 |            |

|       | is fabricated without an ashing step. Wafer 2 is fabricated with the standard ashing procedure.                                                                                             |            |

|       | Wafer 4 is fabricated on a <111> substrate while ashed with 180° rotation compared to the other                                                                                             |            |

|       | samples. For wafer 5 the ashing step is divided into 4 steps, which combined have a similar ash                                                                                             |            |

|       | time as the normal recipe. The wafer is rotated 90° between each ashing step. Wafer 6 is fabri-                                                                                             |            |

|       | cated by dividing the ashing step into 16 separate steps while rotating the wafer 90° four times                                                                                            |            |

|       | in four corners of the system chamber. Wafer 7 is fabricated using an ashing step in another                                                                                                |            |

|       | system.                                                                                                                                                                                     | 42         |

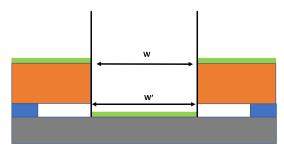

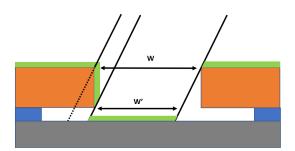

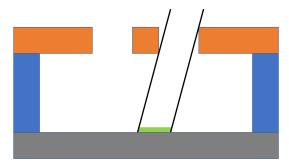

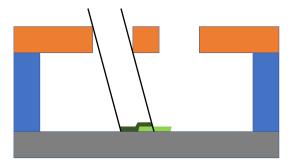

| 5.1   | Schematic representation of the one dimensional view of the model. The black lines represent                                                                                                |            |

|       | the direction of the deposited metal. The colors corresponds to: Green - Al, Orange - PMMA,                                                                                                 |            |

|       | Blue - PMGI, Grey - Si.                                                                                                                                                                     | 45         |

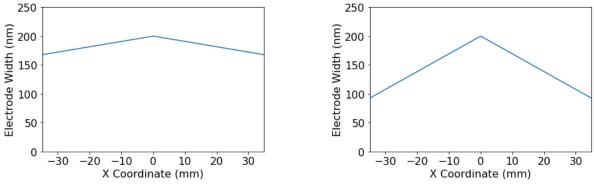

| 5.2   | Electrode width as a function of the X coordinate according to equation 5.1. The designed width,                                                                                            |            |

|       | <i>W</i> , is 200 nm and the distance from the wafer to crucible, <i>D</i> is 650 mm. The height of the top                                                                                 |            |

|       | resist is changed, to show the dependence on this parameter. In figure 5.2a the top resist has a                                                                                            |            |

|       | height of 600 nm and in figure 5.2b a height of 2000 nm. These figures show that the width is                                                                                               |            |

|       | the largest at the center and linearly decreases towards the edges, where an increase in the top                                                                                            |            |

|       | resist height results in a larger change as a function of the X coordinate                                                                                                                  | 46         |

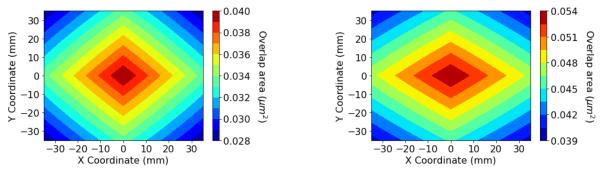

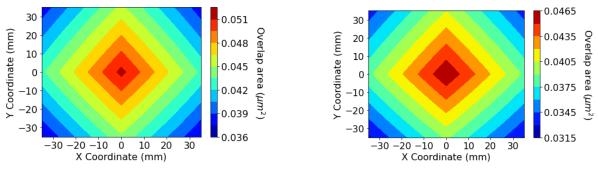

| 5.3   | Schematic representation of the two dimensional model. Figure 5.3a is based on the overlap of                                                                                               |            |

|       | the top and bottom electrode, according to equation 5.2. Figure 5.3b is based on the overlap                                                                                                |            |

|       | area of the top and bottom electrode and adds an extra contributions due to the overlap area,                                                                                               |            |

|       | according to equation 5.3. The contributions of the sidewalls result in an elongated effect along the X axis. The designed width for the top and bottom electrode is 200 nm                 | 46         |

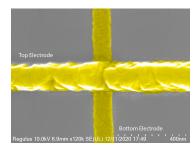

| 5.4   | False colored SEM image of a Josephson junction at a 45° tilt. The yellow corresponds to the Al                                                                                             | 40         |

| 5.1   | junction and the blue corresponds to the surrounding Si.                                                                                                                                    | 47         |

| 5.5   | Schematic representation of the two dimensional view of the model.                                                                                                                          | 48         |

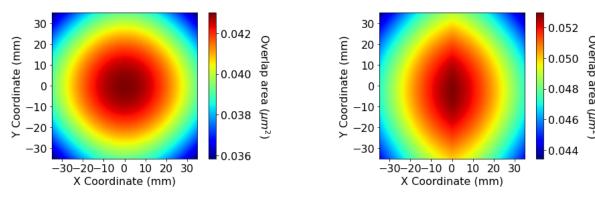

| 5.6   | Overlap area as a function of the X and Y coordinate applied on a 100 mm wafer for the produc-                                                                                              |            |

|       | tion of superconducting quantum processors.                                                                                                                                                 | 48         |

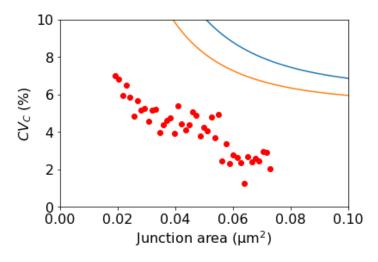

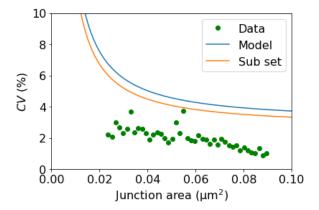

| 5.7   | Coefficient of variation of Manhattan style junctions as a function of junction overlap area                                                                                                | 49         |

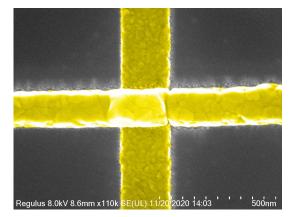

| 5.8   | Scanning electron micrographs of a Manhattan style Josephson junction around the NbTiN bay                                                                                                  |            |

|       | (5.8a) and a close up on the overlap area of which the width of the top and bottom electrode can                                                                                            |            |

|       | be extracted (5.8b)                                                                                                                                                                         | 49         |

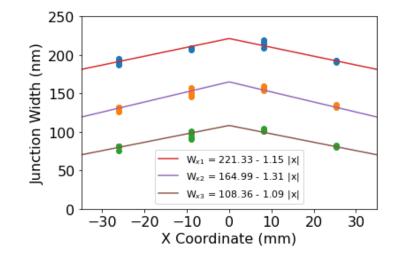

| 5.9   | Measured junction width of the bottom electrode of the center dies as a function of the X-                                                                                                  |            |

|       | coordinate                                                                                                                                                                                  | 50         |

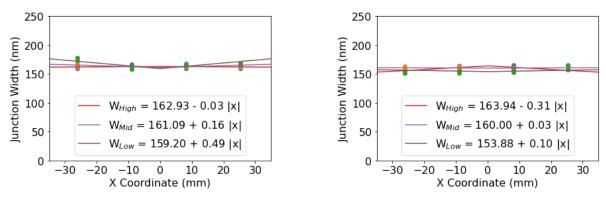

| 5.10  | Comparison of the variations in center and edge dies. The data is fitted according to equation                                                                                              |            |

|       | (5.1). $W_{High}$ shows the data for the junction corresponding to a high frequency, $W_{Middle}$ shows                                                                                     |            |

|       | the data for the junction corresponding to a middle frequency and $W_{Low}$ shows the data for the junction corresponding to a low frequency.                                               | 50         |

| 5 1 1 | Overview of the method used to extract the thickness of the junction electrodes using an AFM                                                                                                | 50         |

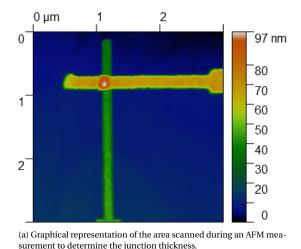

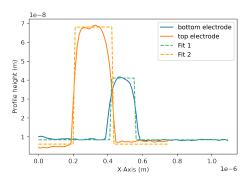

| 5.11  | measurement.                                                                                                                                                                                | 51         |

| 5.12  | Schematic representation of the deposition for Dolan bridge junctions. The black lines repre-                                                                                               | 01         |

| 0.12  | sent the direction of the deposited metal. The colors corresponds to: (dark)Green - Al, Orange                                                                                              |            |

|       | - PMMA, Blue - PMGI, Grey - Si. The light green corresponds to the first Al deposition and the                                                                                              |            |

|       | dark green to the second Al deposition.                                                                                                                                                     | 52         |

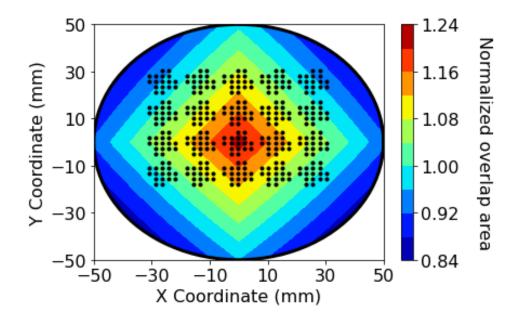

| 5.13  | Graphical representation of the model used to determine to overlap area between the top and                                                                                                 |            |

|       | bottom electrode for the Dolan bridge Josephson junction. Figure 5.13a shows that if only the                                                                                               |            |

|       | variation in resist height are taken into account the overlap area becomes radial dependent.                                                                                                |            |

|       | If other contributions are taken into account such as the tilt, thickness variations and width                                                                                              | _          |

|       | variations a elliptic pattern appears.                                                                                                                                                      | 53         |

| 5.14  | Coefficient of variation as a function of the overlap area for the Dolan bridge Josephson junc-                                                                                             | <b>F</b> 0 |

|       | tions. The experimental data is plotted                                                                                                                                                     | 53         |

58

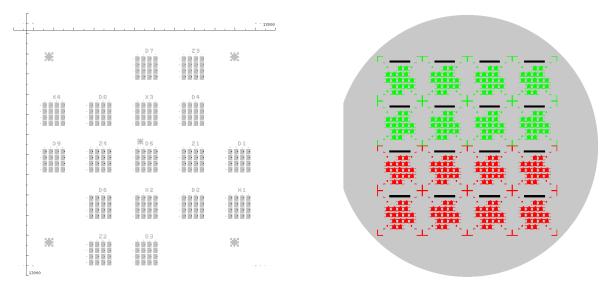

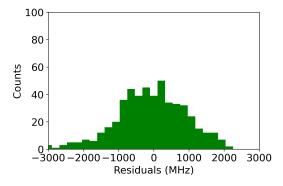

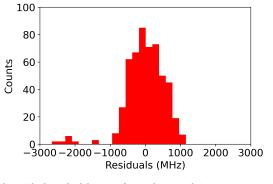

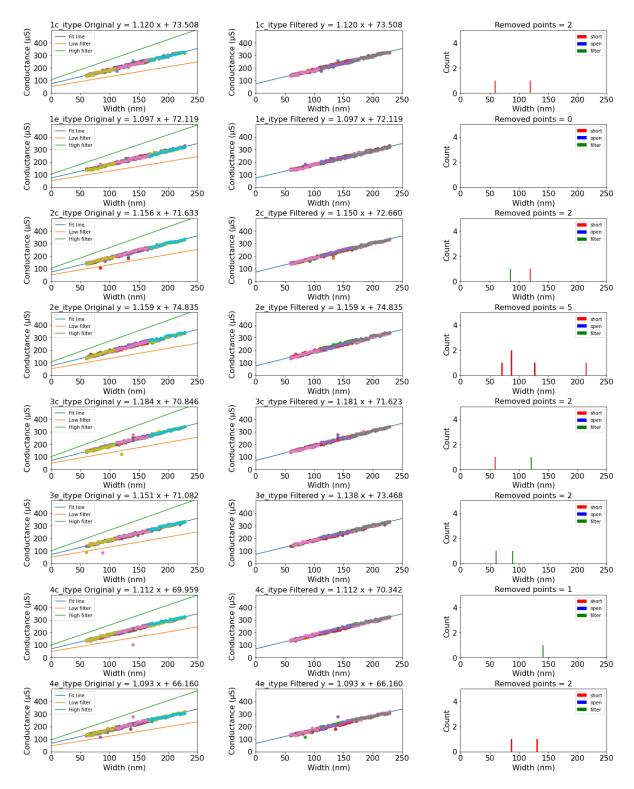

- A.1 Filtering of the data from Blackbird 2 Dolan bridge Style. The left column corresponds to the original data, with a fit through this data. The fit line is used to filter outliers, the middle columns shows the images after filtering. The right column shows the number of points filtered for a certain junction width, it also shows if the filtered points where open, short or half-open. . . . .

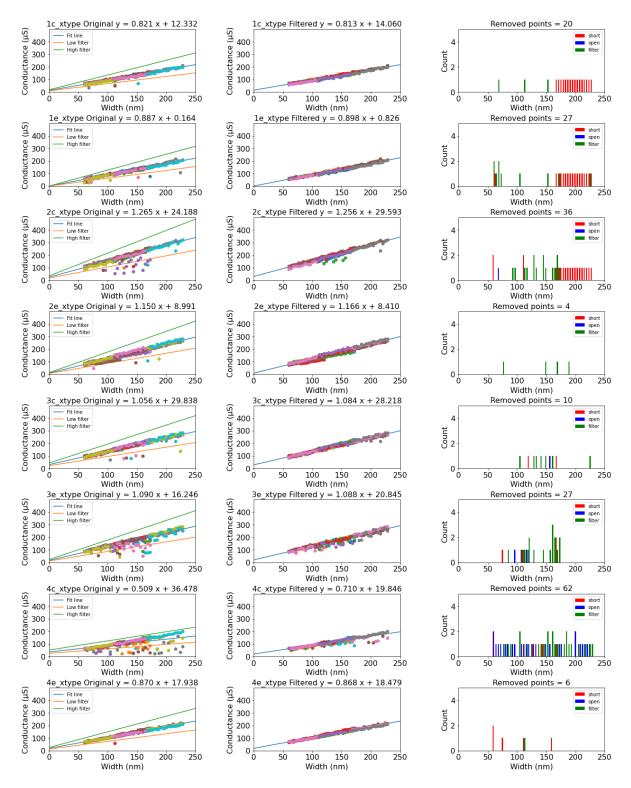

- A.2 Filtering of the data from Blackbird 2 Manhattan Style. The left column corresponds to the original data, with a fit through this data. The fit line is used to filter outliers, the middle columns shows the images after filtering. The right column shows the number of points filtered for a certain junction width, it also shows if the filtered points where open, short or half-open.

- A.3 Filtering of the data from Blackbird 1 Manhattan Style. The left column corresponds to the original data, with a fit through this data. The fit line is used to filter outliers, the middle columns shows the images after filtering. The right column shows the number of points filtered for a certain junction width, it also shows if the filtered points where open, short or half-open.

# List of Tables

| Pearson coefficient of the overlap area and conductance measurements of Josephson junctions for three frequency groups                                                                                                                                                                                                                                                                                       |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Overview of the wafers used to determine the influence of the ashing on the Josephson junction<br>uniformity. The table list the system used for the ashing step, the number of rotations used dur-<br>ing each ashing step, the Josephson junctions yield, the coefficient of variation, the coefficient<br>of variation for a smaller area, the average conductance, the standard deviation and the number |    |

| of Josephson junctions on each sample.                                                                                                                                                                                                                                                                                                                                                                       | 43 |

| Parameters used for the model                                                                                                                                                                                                                                                                                                                                                                                |    |

# 1

# Introduction

This chapter gives an introduction on why there is an interest in the field of quantum mechanics followed by the objective of this thesis. Finally an overview of the chapters in this work is given.

## 1.1. Motivation

In the last few decades the field of quantum mechanics has received a lot of attention. Governments and companies such as Google, Amazon, IBM and Microsoft are investing heavily in the field in order to speed up the progress. But why is this field of such interest and why are companies investing in the field as well?

It turns out that quantum mechanics can be used to create a quantum computer. Where a classical computer uses bits that can either be a 0 or a 1, a quantum computer uses quantum bits, also known as qubits. These qubits obey the laws of quantum mechanics and can therefore be in a superposition of 0 and 1 at the same time. Due to this unique property a quantum computer is able to solve certain problems faster than a classical computer. A textbook example of this is Shor's algorithm [1], which uses prime factorization to break the RSA encryption which is used for secure data transmission.

The problem with quantum computers is that it is still unknown how to build a large quantum computer that is able to solve non-trivial problems. This is also the reason that governments and companies are investing in the field, every party wants to be the first to build a quantum computer. While there are multiple platforms to build a quantum computer, such as nitrogen-vacancies in diamond, trapped ions, quantum dots and Majorana zero modes, most companies focus on the same platform, superconducting qubits. This platform has the advantage that it is compatible with current CMOS and microwave control technology.

In this thesis the emphasis lies on the *transmission line shunted plasma oscillation qubit* [2], also known as the transmon qubit. The transmon is a form of a superconducting qubit, which uses a capacitor in parallel with a Josephson junction to create an an-harmonic oscillator. By confining the computational subspace to the lowest two energy levels of the oscillator it is possible to create a qubit. This qubit operates at a certain frequency, which is determined by the capacitance and the inductance of the electrical circuit. This frequency is an important parameter for the performance of a chip with multiple qubits, also known as a superconducting quantum processor. In such a processor the qubits are divided into three frequency groups, in which ideally all qubits of the same group have the same frequency. If the qubit frequencies within a certain group differ too much from each other the processor will not function properly.

As the number of physical qubits on a superconducting quantum processor increases, it becomes more difficult to connect all the wires required for the control of the qubits. In order to overcome this problem through silicon vias are introduced, these vias can be used as 3D interconnects to allow for the control of all the qubits on a chip. The downside of these vias is that they affect the resist spinning, which results in a non-uniform thickness. Currently a critical piece of the superconducting qubit, called the Josephson junction, requires a uniform resist thickness, which poses a problem for the fabrication of superconducting qubits. In order to solve this problem a different type of Josephson junction that is less sensitive to resist thickness variations is currently investigated in the field.

# 1.2. Objective

This thesis focuses on characterising and improving the frequency targeting of superconducting qubits during wafer-scale fabrication. This goal is investigated by studying a critical feature of the qubit, the Josephson junction. The Josephson junction conductance obtained from room temperature measurements is directly related to the qubit frequency according to the Ambegaokar-Baratoff relation [3]. Therefore, the objective of this thesis is to quantify and improve the uniformity of the Josephson junction conductance across a 100 mm wafer.

# 1.3. Outline

This thesis is structures into five different chapters.

Chapter 2 (Theory) provides a brief introduction on Josephson junctions and the physics behind the transmon qubit that is of interest for this thesis. Such as the relation between the frequency targeting of a qubit and the room temperature resistance measurements.

Chapter 3 (Junction Characterisation) determines the variations in the Josephson junction conductance using the current fabrication recipe on a NbTiN base layer.

Chapter 4 (All Aluminum Junctions) describes the experiments performed to study the junction uniformity using a simplified fabrication process. This process reduces the number of fabrication steps and thus variables.

Chapter 5 (Model) discusses a geometric model that could explain the variations in the Josephson junction conductance.

Chapter 6 (Conclusions and Outlook) summarizes the results of this thesis and gives an outlook on further research that is relevant for the fabrication of transmon qubits.

# 2

# Theory

This chapter gives a brief introduction on the concept of superconductivity and how this phenomena can be used to create a Josephson junction. This junction is used to create a superconducting qubit. Building on this the surface code and its importance is introduced and discussed. Lastly, the fabrication steps required to create Josephson junctions on a wafer are discussed.

## 2.1. Superconductivity

A concept that is important for the fabrication of superconducting qubits is superconductivity itself. In 1911 H. Kamerlingh Onnes discovered that the resistance of a solid mercury vanishes if the wire is cooled below 4.2 K [4]. Later he discovered that the resistance of other materials such as lead and tin also vanishes below a certain critical temperature  $T_c$ . This is the first hallmark of a superconductor, perfect conductivity. Later in 1933 Meissner and Ochsenfeld discovered another hallmark, perfect diamagnetism [5], in which a magnetic field is excluded from entering a superconductor up to some critical magnetic field known as the Meissner effect. Applying a magnetic field stronger than the critical magnetic field will break superconductivity. Similarly, applying a current above the critical current will break this superconductivity as well. The cause of these properties of a superconductor were unclear for quite some time, until 1950 when Ginzburg and Landau proposed the macroscopic theory of superconductivity [6]. While this theory gives a description of superconductivity, the microscopic behaviour of superconductivity remained elusive, until 1957 when John Bardeen, Leon Cooper and John Robert Schrieffer proposed a microscopic theory of superconductivity [7–10], now known as BCS-theory.

### 2.1.1. BCS Theory

The Bardeen-Cooper-Schrieffer theory explains superconductivity based on the formation of Cooper pairs by an attractive interaction between two electrons. Under normal circumstances electrons repel each other due to the Coulomb interaction. However, it is possible to overcome the Coulomb interaction, which allows the electrons to bond and form a Cooper pair. An example of this pairing can be given using a simple lattice of a metal. In this case the electron moves through the metal, where it is repelled by other electrons due to their negative charge and it is attracted to ions in the lattice that have a positive charge. This attractive force is able to create a small displacement in the lattice in the form of a phonon. In this case the charge density will be locally increased, which attracts another electron. The force at which both electrons are attracted is large enough to overcome the Coulomb interaction, thus allowing the electrons to bond and form a Cooper pair. The bonding of the electrons is quite weak and is therefore easily broken if the thermal energy is too high. If the thermal energy decreases it becomes more difficult to split the Cooper pairs into electrons, at some point the thermal energy is too low and the Cooper pairs are not split into electrons anymore. The temperature corresponding to this thermal energy is called the critical temperature. Below this temperature the fermionic electrons in the metal will form bosonic Cooper pairs. The Cooper pairs obey Bose-Einstein statistics and are therefore able to occupy only the ground state of the system. If all the electrons in the material form Cooper pairs and occupy the ground state the resistance of the material vanishes. This can be explained by the fact that the electrons normally cause the resistivity in a material, but when all the electrons form Cooper pairs, there are no electrons left to create the resistivity.

#### 2.1.2. Superconducting Materials

There is a wide array of materials that become superconducting below a certain temperature,  $T_c$ , also known as the critical temperature. However, only a small number of these materials are used in circuit quantum electrodynamics (cQED). In cQED, the superconducting materials are used for the coherent transport of signals throughout the superconducting circuit. The choice of the superconducting material depends on various factors, such as material properties and compatibility with fabrication processes. For the material properties such as the critical current, dielectric losses and the magnetic field tolerance are important. In this section, a number of materials and compounds explored in cQED are discussed, in general elemental materials are more popular because film depositions are relatively simple and stable [11]. The downside of pure materials is that these often form a thin oxide layer at the surface, which can house two-level systems (TLS), which are identified to be a dominant source of losses. For each material, the critical temperature is given, whereas for the compounds a range is given, as the critical temperature depends on the composition of each element in the compound.

• Aluminum (Al):  $T_c \approx 1.2 \text{ K}$

The material of choice for the fabrication of Josephson junctions, however it can also be used as the superconducting base layer. Al has a small superconducting band gap of 0.3 meV, a low critical temperature of  $T_c = 1.2$  K and a relative long quasi particle life time [12], which can affect the performance of the transmon qubits. Al oxidises when exposed to air, which allows for TLS to form on top of the base. Even though that Al has some disadvantage properties it has been used in high performance superconducting quantum processors, such as Google's Sycamore processor, used to demonstrate quantum supremacy [13].

• Niobium (Nb):  $T_c \approx 9.3 \text{ K}$

At first glance pure Nb appears to be a suitable choice of superconducting material, it has a high  $T_c$  and a large superconducting band gap. However, it turns out that Nb has a few downsides. The first is the complex stoichiometry of Nb forms with O<sub>2</sub> (NbO, NbO<sub>2</sub>, Nb<sub>2</sub>O<sub>5</sub>), which are able to house TLS and thus losses. Secondly, Nb is observed to have a larger density of sub-gap states than materials with a lower  $T_c$ , such as Al, which corresponds to more thermally excited quasi-particles and shorter coherence times [14, 15]. In order to overcome these problems, compounds of Nb and other materials are explored for superconducting base layers, such as NbN and NbTiN. In another study, deposited Nb was exposed with nitrogen in order to replace the formation of surface oxides with nitrides, however measurements showed that there were still oxides present on the film, indicating that this is not a feasible solution [16].

• Niobium Nitride (NbN):  $T_c \approx 8 - 16 \text{ K}$

Adding N to Nb allows for a high  $T_c$  and high critical magnetic field, while potentially reducing losses due to TLS by removing surface oxides. The downside of NbN is the short superconducting coherence length, which causes problems for the fabrication of high-quality tunnel junctions, and the long magnetic penetration depth which limits its application in high frequency superconducting circuits [17].

• Titanium Nitride (TiN):  $T_c \approx 0 - 6 \text{ K}$

TiN is used in superconducting microwave kinetic inductance detectors [18] and has also been used in superconducting qubits [19]. This compound is very hard and robust and has been used to create high quality resonators ( $Q_i > 10^7$ ) while having a long quasi-particle lifetime ranging from 10-200 µs [18]. The nitrogen is added to increase the  $T_c$  of the compound, where the highest  $T_c$  and lowest film resistivity is measured for films where the stoichiometry was correct i.e. 1:1 Ti:N. It is hypothesized that the N at the surface would prevent the oxidation of the film and would thus reduce the TLS population. However, it is found that TiN also form a thin oxidation layer on top of the film, thus still allowing for the presence of TLS. [15, 20–22].

• Niobium Titanium Nitride (NbTiN):  $T_c \approx 15 - 18 \text{ K}$

NbTiN is a compound with a high critical temperature, large superconducting band gap, little microwave phase noise and microwave loss. NbTiN is heavily used in the field of astronomy due to its ability to operate in a large frequency range. It has similar applications and properties as NbN, but the addition of Ti to the compound allows for the metallic and structural benefits of TiN. In this compound, the N allows for a high  $T_c$  and stability in air. The addition of N should also prevent the formation of surface oxides and thus reduce losses due to TLS. [23, 24].

• Tantalum (Ta):  $T_c \approx 4.5 \text{ K}$

Ta is a relatively new material in the field of cQED, but one that attracts a lot of attention. Using a Ta base layer on a sapphire substrate transmon qubits with a relaxation time  $(T_1)$  exceeding 0.3 ms [25] and 0.5 ms [11] have been fabricated. The current hypothesis is that the insulating oxide layer that forms on the Ta allows for a better metal air interface and it thus allows for lower losses when compared to Nb, that has a more complicated stoichiometry [11, 25].

## 2.2. Josephson Junction

In 1962 B.D. Josephson predicted the mathematical relation between the current and the voltage between two superconductors separated by an insulator [26], also known as a weak link. This type of junction is known as a superconductor-insulator-superconductor (SIS) junction. It is also possible to fabricate a junction using a normal metal between the two superconductors, which is known as a superconductor-normal metal-superconductor (SNS) junction. The requirement on the insulator separating the two superconductors is that it should be thin enough, such that Cooper pairs can quantum mechanically tunnel through the barrier. A schematic representation of a Josephson junction can be seen in figure 2.1. Here two superconducting materials with phase  $\phi_L$  and  $\phi_R$  are separated by an inductive layer with a current  $I_J$  going through the junction. In a Josephson junction, the current and voltage are described by the Josephson equations

Figure 2.1: Schematic representation of a Josephson junction connected to a bias voltage V. Two superconducting materials with phase  $\phi_L$  and  $\phi_R$  respectively are separated by an insulating barrier. Figure taken from [27].

$$I_J = I_C \sin\left(\varphi\right) \tag{2.1}$$

$$V = \frac{\Phi_0}{2\pi} \frac{d\varphi}{dt}$$

(2.2)

where  $I_J$  is the current through the Josephson junction,  $I_C$  is the critical current,  $\varphi = \phi_L - \phi_R$  is the superconducting phase difference, V is the current over the junction and  $\Phi_0 = h/2e$  is the superconducting flux quantum, with h Planck's constant and e the electron charge. The critical current  $I_C$  can be determined according to

$$I_C = \frac{\Delta_1(T)}{R_N} K \left( \left( 1 - \frac{\Delta_1^2(T)}{\Delta_1^2(T)} \right)^{1/2} \right)$$

(2.3)

where  $\Delta_1(T)$  is the smallest of the two temperature dependent superconducting band gaps and  $\Delta_2(T)$  is the larger one, K() is the complete elliptical integral of the first kind and  $R_N$  is the normal junction resistance [3]. In case that the same material is used for both electrodes of the Josephson junction i.e.  $\Delta_1(T) = \Delta_2(T)$  and thus  $K(0) = \frac{1}{2}\pi$  equation (2.3) reduces to

$$I_C = \frac{\pi \Delta(T)}{2R_N} \tag{2.4}$$

This simplified equation can be used to determine the critical current of a Josephson junction from room temperature resistance measurements, which will be discussed in further detail later on.

Another important property of the Josephson junction is the inductance. Using equations (2.1) and (2.2) the inductance,  $L_J$ , can be calculated

$$L_{J} = \frac{V}{dI_{J}/dt} = \frac{\Phi_{0}}{2\pi I_{0}\cos(\varphi)}$$

(2.5)

here we used the fact equation (2.1) can be rewritten as  $\frac{\partial I_J}{\partial \varphi} = I_0 \cos \varphi$  and the property  $\frac{dI}{dt} = \frac{\partial I}{\partial \phi} \frac{\partial \phi}{\partial t}$ . From equation (2.5) it becomes clear that the inductance is non-linear due to the  $\cos(\varphi)$  dependence. The inductance has an oscillating behaviour and reaches a maximum at  $\varphi \to \pi/2$  and becomes negative for  $\pi/2 < \varphi < 3\pi/2$ .

This non-linear behaviour of the Josephson junction is important for the fabrication of a superconducting qubit, which is discussed later on [28].

#### 2.2.1. SQUID

Superconducting qubits often use two Josephson junctions in parallel to form a superconducting quantum interference device (SQUID). SQUID's are used as they allow for the tuning of the Josephson coupling energy [2]. In a SQUID the superconducting phase  $\varphi$  becomes important as the phase can be different for both Josephson junctions. The Josephson current through the SQUID is simply the sum of the individual Josephson junctions

$$I_{J,SQUID} = I_{C,1}\sin(\varphi_1) + I_{C,2}\sin(\varphi_2)$$

(2.6)

where  $I_{C,n}$  is the critical current and  $\varphi_n$  is the superconducting phase for each Josephson junction respectively [28]. These parameters  $I_{C,n}$  and  $\varphi_n$  depend on the physical properties of the Josephson junction such as the size and materials. In case that a symmetric SQUID is used equation (2.6) can be written as

$$I_{J,SQUID} = 2I_C \cos\left(\frac{\varphi_1 - \varphi_2}{2}\right) \sin\left(\frac{\varphi_1 + \varphi_2}{2}\right)$$

(2.7)

in the case that an asymmetric SQUID is used the critical current through each junction in the SQUID becomes different and the equation becomes more complicated. In this work only symmetric SQUID's are used and therefore the asymmetric case is not considered. When a magnetic field is applied perpendicular to the plane of the SQUID, the superconducting phase is shifted. The phase shift in the SQUID obeys the relation  $\varphi_1 - \varphi_2 = -2\pi \frac{\Phi}{\Phi_0}$ , where  $\Phi$  is the magnetic flux through the SQUID [29]. In this case the Josephson current can be written as

$$I_J = 2I_C \cos\left(\pi \frac{\Phi}{\Phi_0}\right) \sin\left(\varphi_2 + \pi \frac{\Phi}{\Phi_0}\right)$$

(2.8)

From which we find that the Josephson current depends on the magnetic flux through the SQUID. It is important to note that this equation only holds when the Josephson current does not exceed the critical current. For the SQUID the critical current can be expressed as

$$I_{C,SQUID} = 2I_C \left| \cos\left(\pi \frac{\Phi}{\Phi_0}\right) \right|$$

(2.9)

Finally the inductance of the SQUID can be determined using  $L_J = \frac{V}{dI_J/dt}$ , the way as for the single Josephson junction. From this we find

$$L_{SQUID} = \frac{\Phi_0}{2I_C \cos\left(\pi \frac{\Phi}{\Phi_0}\right) \cos\left(\varphi_2 + \frac{\Phi}{\Phi_0}\right)}$$

(2.10)

From which we find that similar to the Josephson current through the SQUID the inductance also depends on the magnetic flux through the SQUID. This allows for the flux tunability of the qubit frequency, which is discussed later on.

#### 2.2.2. Al/AlO<sub>x</sub> Properties

The most common material used for the fabrication of Josephson junctions in superconducting qubits is aluminum. Al has the advantage that it oxidizes when exposed to  $O_2$ , resulting in the formation of a thin layer ( $\approx 2 - 3$  nm) of AlO<sub>x</sub> on top of the Al. This property allows for the fabrication of a Josephson junction in a single electron beam step by using a double angle evaporator and thus Al is compatible with methods such as a Dolan-bridge and the Manhattan layout. Al has a superconducting band gap of 0.3 meV, which allows for small junctions. The problem with this material is that two-level defects in the amorphous AlO<sub>x</sub> tunnel barrier are identified to limit the performance of the superconducting qubit [30, 31]. A study by Zeng et al. [32] showed that due to non-uniformities in the bottom electrode and the formation of the substrate on which the electrodes are deposited directly affects the roughness of the electrode and thus the tunnel-barrier. In order to reduce this effect it is important to create a smooth surface for the deposition of the electrodes.

A study on the influence of the deposition method used on the  $AlO_x$  barrier is conducted by Fritz et al. [33]. This study involved three different deposition machines with different operating settings. One of these machines is a Plassys-MEB550, which is the same machine used at the DiCarlo lab to fabricate Josephson

Figure 2.2: TEM images of a Al/AlO<sub>x</sub>/Al junction fabricated. In figure a the AlO<sub>x</sub> barrier is formed with dynamic oxidation using pure  $O_2$ . The white arrow points to grain boundaries. In figure b the AlO<sub>x</sub> barrier is formed with dynamic oxidation using pure  $O_2$  in the presence of UV-illumination to enhance dynamic oxidation. Figure taken from [33].

junctions. This study used transmission electron microscopy (TEM) to study the transition between the  $Al/AlO_x/Al$  layers. Two TEM images of a  $Al/AlO_x/Al$  barrier fabricated using the Plassys can be seen in figure 2.2. The Al layers are present at the top and bottom of the image and are separated by a 20-30 nm  $AlO_x$  layer and are obtained by multiple deposition and oxidation steps. The top figure corresponds to  $Al/AlO_x/Al$  junction formed using dynamic oxidation in pure oxygen and the bottom figure corresponds to  $Al/AlO_x/Al$  junction formed using dynamic oxidation in pure oxygen in the presence of UV-illumination to enhance dynamic oxidation. When the top and bottom are compared we find that the  $Al/AlO_x/Al$  formed in the presence of UV shows a smoother interface with less grain boundaries.

It is important to note that  $AlO_x$  tunnel barriers suffer from a process called aging. Aging refers to the instability of the  $AlO_x$  tunnel barrier over time. This instability is attributed to the diffusion of oxygen atoms from the oxide barrier to the electrode and the change of the chemical composition of the barrier [34, 35]. This aging is able to increase or decrease the conductance of the Josephson junction. This can be exploited to change the conductance post fabrication in order to obtain the desired frequency value [36, 37]. Aging of the junctions can be suppressed by nitridation of the electrodes, nitrides are chemically more stable therefore show less signs of aging. It has been shown that aging is affected by contaminations around the area where the electrodes are deposited. By cleaning the substrate with ethanol and isopropylalcohol (IPA) or isotropic reactive ion etching (RIE) the effect of aging can be reduced, where junction fabricated on the RIE cleaned surface showed no aging. Isotopic etching is required since areas with a large undercut need to be cleaned [34].

Koppinen et al. [38] showed that junctions annealed at 200 °C and 400 °C showed an increase in the resistance of 50% and 300% respectively. During this process the junction area was not cleaned. Pop et al. [34] showed that junction fabricated on an area cleaned with RIE are stable when annealed at 200 °C. In this same study, junctions are annealed at 200 °C with a layer of polymethyl methacrylate (PMMA) resist on top of it. In this case, a decrease in the junction resistance is observed. This change is attributed to hydrates (-OH) from the resist, which combine with the oxides on the aluminum. The resistance was measured a week later, which showed an increase in the junction resistance. When the junctions are again annealed at 200 °C with PMMA resist on it, the resistance decreased again. A measurement four weeks later again showed an increase in the resistance. The increase/relaxation behaviour can be explained by the hydrates that are absorbed during the annealing process and are desorbed during the storage of the junctions.

#### 2.2.3. Josephson Junction Types

In this work two methods to fabricate Josephson junctions are used, the first method utilizes a Dolan bridge [39, 40] and the second method is based on the Manhattan design [41]. Here Josephson junctions fabricated using one of these techniques will be referred to as Dolan bridge junctions and Manhattan junctions.

A Dolan bridge is a connection between two parts of a resist layer between two exposed parts on top of another over exposed resist layer. A schematic representation of the cross section of a Dolan bridge can be seen in figure 2.3. In this design, metal is deposited from direction 1 under a tilt  $\theta$ , followed by an oxidation step to create the oxide layer. The second layer of metal is deposited from direction 2 under the same tilt  $\theta$ , thus by rotating the sample 180°. The overlap area between the top and bottom electrode can be defined by determining the amount of material deposited under the bridge, which can be calculated for the bottom electrode as

$$L_{Bottom} = R_H / \tan\left(\theta\right) \tag{2.11}$$

where  $L_{Bottom}$  is the length of the bottom electrode under the Dolan bridge,  $R_H$  is the height of the bottom resist and  $\theta$  is the angle of the incident material. The same calculation can be used for the top electrode, but with the thickness of the bottom electrode being subtracted from the height.

$$L_{Top} = (R_H - T_{Bottom}) / \tan(\theta)$$

(2.12)

where  $L_{Top}$  is the length of the bottom electrode under the Dolan bridge and  $T_{Bottom}$  is the thickness of the bottom electrode. In this case the overlap area can be determined by the length of the top and bottom electrode overlap multiplied by the width of the top electrode

$$A_{Dolan,top} = (L_{Top} + L_{Bottom} - L_{Bridge})W_{Top}$$

(2.13)

where  $A_{Dolan,top}$  is the overlap area of the Dolan bridge junction,  $L_{Bridge}$  is the length of the Dolan bridge and  $W_{Top}$  is the width of the top electrode. In a typical Dolan bridge junction the top electrode has a smaller width than the bottom electrode, therefore only the width of the top electrode is relevant. In the Dolan bridge junction, the contribution of the sidewall between the top and bottom electrode can also be taken into account, which would add a contribution of

$$A_{Dolan,side} = T_{Bottom} W_{Top} \tag{2.14}$$

where  $A_{Dolan,side}$  is the contributions of the sidewall to the overlap area. In this case the total overlap is defined as

$$A_{Dolan} = A_{Dolan,top} + A_{Dolan,side}$$

(2.15)

Figure 2.3: Schematic representation of the resist stack used for the fabrication of Dolan bridge junctions. The top resist layer is used to create a Dolan bridge. The color correspond to: Red - first metal deposition, Blue - second metal deposition, Grey - Si, Light Blue - PMGI, Light Red - PMMA.

The advantage of Dolan bridge junctions is that spinning resist allows for an uniform layer, thus allowing uniform fabrication of junctions across a sample. The downside of Dolan bridge junctions is that the resist spinning requires a relatively flat substrate in order to spin an uniform layer. In the case of through silicon vias (TSV) this requirement is not met, which results in variations in the Dolan bridge junction fabrication process.

The Manhattan junction is a bridgeless junction that is less sensitive to resist height variations than the Dolan bridge. A schematic representation of the layout used to fabricated Manhattan style junctions can be seen in figure 2.4. Here a thick top resist layer is used to create the pattern for the deposited material, while a thin bottom resist layer is used to promote lift-off. The metal is deposited from direction 1 under a tilt  $\theta$ , followed by an oxidation step to create the oxide layer. Then the substrate is rotated around the  $\varphi$  axis by 90° followed by another deposition under a tilt  $\theta$ . For this process it is important that the resist stack thickness  $T_{resist}$ , junction width W and the tilt  $\theta$  obey the following relation.

$$T_{resist} > W/\tan\left(\theta\right) \tag{2.16}$$

If this relation is not satisfied, material of the first deposition is deposited in the opening for the second deposition, resulting in problems in the Josephson junction. In case that there is a misalignment  $\alpha$  between the axis of rotation and the width of the junction, the relation becomes:

$$T_{resist} > W/(\tan(\theta)\cos(\alpha))$$

(2.17)

The overlap area of the Manhattan style junctions can be calculated by multiplying the width to the top and bottom electrode

$$A_{Top} = W_{Bottom} W_{Top} \tag{2.18}$$

Where  $A_{Top}$  is the overlap area,  $W_{bottom}$  is the width of the bottom electrode and  $W_{Top}$  is the width of the top electrode. For the Manhattan junctions the area on the side of the bottom electrode can also be taken into account, these add a contribution of

$$A_{Side} = 2W_{Top}T_{Bottom} \tag{2.19}$$

here the factor of 2 is added, since there is a sidewall on both sides of the junction. The advantage of the Manhattan style junction is that it is less sensitive to resist height variations. This advantage becomes important as the number of physical qubits on a processor increases. In order to connect all the wires to the processor 3D interconnects are necessary, which will affect the uniformity of resist spinning. Figure 2.5 shows scanning electron microscope (SEM) images of both type of Josephson junction fabricated on a NbTiN base.

Figure 2.4: Schematic representation of the resist stack used for the fabrication of Manhattan junctions. The color correspond to: Red - first metal deposition, Blue - second metal deposition, Grey - Si, Light Blue - PMGI, Light Red - PMMA.

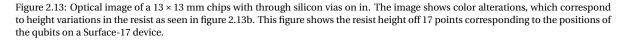

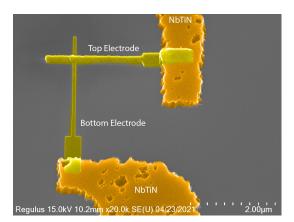

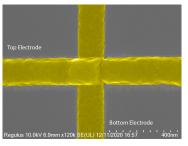

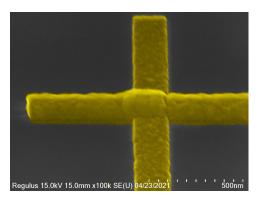

(a) False colored SEM image of a Dolan bridge junction at 15k magnification.

(b) False colored SEM image of a Manhattan junction at 20k magnification.

Figure 2.5: False colored SEM images of both Josephson junctions types at a 45° tilt. The aluminum electrodes are yellow and the NbTiN base layer is orange.

## 2.3. Harmonic Oscillator

This non-linear inductance of the Josephson junction can be used in a LC-circuit to form an anharmonic quantum oscillator, opposed to the normally used harmonic quantum oscillator, which uses a normal inductor. Figure 2.6 shows both of these oscillators. Note that in the case of the harmonic oscillator the energy levels are degenerate and thus it is not possible to confine the lowest two energy levels. In the case of the anharmonic oscillator this degeneracy is broken by the Josephson junction, in this case the lowest two energy levels can be used as the computational subspace of the qubit. We also note that in the anharmonic oscillator it becomes apparent that the energy spacing between each consecutive level decreases. This is an important consideration as the higher energy levels become a source of leakage for the transmon qubits, thus the transition to these levels should be suppressed sufficiently.

Figure 2.6: Comparison between a harmonic oscillator and an anharmonic oscillator. The harmonic oscillator is constructed by using a LC-circuit, whereas the anharmonic oscillator uses a Josephson junction instead of an inductor in the LC-circuit, to create an anharmonicity. In the anharmonic oscillator the energy spacing's between each level is different, which allows for the confinement of the computational subspace to the lowest two energy levels. Figure taken from [42].

## 2.4. Superconducting Qubits

Superconducting qubits are a promising platform to build a quantum computer in the future. Superconducting qubits have the advantage that they are highly designable, scalable, easy to couple to each other and relatively easy to control in comparison to other platforms [43]. The downside of these qubits is that they are not true 2-level systems, they are quite large and they require dilution refrigerators for operation.

In general, superconducting qubits use a Josephson junction to obtain an anharmonic oscillator. There are two main categories of superconducting qubits, namely the charge qubit and the flux qubit. These categories can be distinguished from each other by looking at the ratio of  $E_J/E_C$  in which they operate. The charge qubit operates in the regime of  $E_J \ll E_C$ . The flux qubit operates at around  $1 \ll E_J/E_C \ll 100$ . During the evolution of superconducting qubits new categories have arised, such as fluxonium [44] and the transmon [2] which is used in our lab.

#### 2.4.1. Charge Qubit

The first superconducting qubit was proposed in 1998 by Bouchiat et al. [45], which was called the Cooperpair box. This design consists of a single superconducting island connected to a superconducting electron reservoir by a Josephson junction. By designing the qubit such that it operates in the  $E_J \ll E_C$  regime it is possible to determine the qubit state by the presence or absence of an extra Cooper pair on the superconducting island. The Hamiltonian of this system is given by

$$\hat{H} = 4E_{\rm C} \left(\hat{n} - n_{\rm g}\right)^2 - E_{\rm J} \cos(\hat{\phi})$$

(2.20)

where  $\hat{n}$  is the Cooper pair number operator,  $n_g$  is the offset,  $\hat{\phi}$  is the phase difference operator  $E_J$  is the Josephson energy and  $E_C$  is the charging energy, which is defined as  $E_C = \frac{e^2}{C}$ , where *C* is the junction capacitance. Charge qubits have a large anharmonicity (> 10 GHz), but suffer from short dephasing times due to environmental charge noise. An adaptation of the charge qubit is the transmon, which uses a shunted capacitor in order to reduce the sensitivity to noise and improve the performance [46].

#### 2.4.2. Flux Qubit