# SIMPLIFIED PROCESSING OF INTERDIGITATED-BACK-CONTACTED SILICON HETEROJUNCTION SOLAR CELLS

Featuring novel  $MOO_x$ -based selective passivating contact stacks

KATARINA KOVAČEVIĆ

# Simplified processing of interdigitated-back-contacted silicon heterojunction solar cells

Featuring novel  $MoO_x$ -based selective passivating contact stacks

by

# Katarina Kovačević

A thesis submitted for Master of Science degree in Sustainable Energy Technology at Delft University of Technology.

Student number: 4709934

Project duration: November, 2021 - August, 2022 Supervisors: Prof. dr. Olindo Isabella

Ir. Yifeng Zhao Dr. Guangtao Yang

# Graduate

Katarina Kovačević

MSc Sustainable Energy Technology

Faculty of Electrical Engineering, Mathematics and Computer Science, Delft University of Technology

# Thesis committee

Prof. dr. Olindo Isabella, Professor, PVMD, Department of Electrical Sustainable Energy

Dr. René A.C.M.M. van Swaaij, Associate Professor, PVMD, Department of Electrical Sustainable Energy

Dr. ir. Sten Vollebregt, Assistant Professor, Electronic Components, Technology and Materials, Department of Microelectronics

Ir. Yifeng Zhao, PhD candidate, PVMD, Department of Electrical Sustainable Energy

# **Delft University of Technology**

Department of Electrical Sustainable Energy

Photovoltaic Materials and Devices (PVMD)

# Abstract

Silicon heterojunction (SHJ) solar cells are one of the most promising PV technologies nowadays due to high photoconversion efficiencies and low manufacturing costs. However, standard front/back-contacted (FBC) solar cells feature a front metal grid that brings shading to the front side of the devices, which limits the conversion efficiency of solar cells. One solution is to move metal contacts fully to the back by introducing interdigitated-back-contacted (IBC) architecture. In 2018, IBC-SHJ solar cells achieved a photoconversion efficiency of 26.7% holding a record for single-junction c-Si cells. However, the standard fabrication process of IBC solar cells comes with increased complexity and manufacturing costs. The focus of this research is on developing and optimizing a simple and industry-appealing fabrication process for high-efficiency IBC-SHJ solar cells.

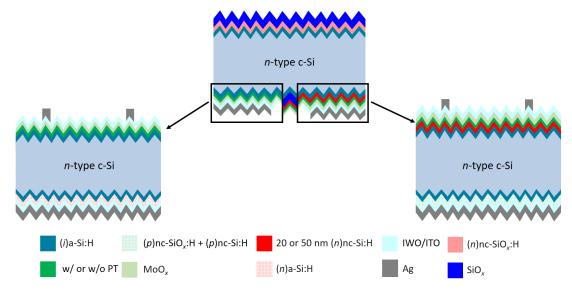

The first part of the project investigates the simple processing of IBC-SHJ solar cells featuring tunneling recombination junction (TRJ). The first tunneling IBC devices are fabricated successfully with an efficiency of 13.90%. However, shunting is observed from the J-V curves of fabricated devices, which can be related to the internal shunting of tunneling IBC architecture and high lateral conductivity of p-type nc-Si:H-based blanket layer. Hence, alternative contact stacks are designed for application in the previously developed flowchart with the aim to minimize the lateral conductivity of the blanket layer and keep the fabrication process simple.  $MoO_x$  with low lateral conductivity is proposed as an alternative to p-type nc-Si:H-based blanket layer. Thus, in the proposed device architecture, hole transport takes place through  $MoO_x$  layer, whereas electron transport is achieved through a novel contact stack consisting of (n)nc-Si:H and  $MoO_x$ .

The proposed hole collection contact stack is firstly implemented in the front junction (FJ) FBC solar cells. The FJ FBC devices reach  $V_{OC}$  of 704 mV and FF of 79.29% with hole collector consisting of (*i*)a-Si:H and  $MoO_x$  with an intermediate plasma treatment (PT). On the other hand, rear junction (RJ) FBC solar cells are fabricated featuring a novel electron collection contact stack that is developed within this thesis.  $V_{OC}$  of 715 mV and FF of 82.24% are obtained in RJ devices with 50 nm (*n*)nc-Si:H and  $MoO_x$  without PT. The results of RJ FBC solar cells with newly developed contact stack show excellent results in terms of FF, making it a promising candidate for further application in IBC devices.

The introduction of the optimized device design enabled the successful fabrication of IBC solar cells with the simple process developed for tunneling IBC devices while ensuring no shunting occurs. The initial IBC-SHJ solar cells featuring novel  $MoO_x$ -based selective passivating contact stacks reach an efficiency of 12.88%. Further optimization of the thickness of  $MoO_x$  and PT conditions is executed to investigate the effect of these parameters on  $V_{OC}$  and FF. According to the results of the experiments, the optimal thickness of  $MoO_x$  is below 5 nm with the current process conditions, whereas the incorporation of PT appears necessary for an improved hole collection, thus also enabling higher FF in the devices.

# Contents

| A۱ | bstra           | net                                                           | iii      |

|----|-----------------|---------------------------------------------------------------|----------|

| N  | omen            | nclature                                                      | vi       |

| Li | st of           | Figures                                                       | viii     |

| Li | st of           | Tables                                                        | хi       |

| 1  | $\mathbf{Intr}$ | $\operatorname{roduction}$                                    | 1        |

|    | 1.1             | Status and perspectives of solar energy                       |          |

|    | 1.2             | Silicon heterojunction solar cells                            |          |

|    | 1.3             | Interdigitated-back-contacted solar cells                     |          |

|    | 1.4             | Transition metal oxides                                       |          |

|    | 1.5             | Research goals                                                |          |

|    | 1.6             | Thesis outline                                                | 5        |

| 2  |                 | adamentals                                                    | 7        |

|    | 2.1             | Photovoltaic fundamentals                                     |          |

|    |                 | 2.1.1 Semiconductor materials                                 |          |

|    |                 | 2.1.2 Working principle of a solar cell                       |          |

|    | 0.0             | 2.1.3 Fundamental limitations and recombination mechanisms    |          |

|    | 2.2             | Working principle of silicon heterojunction solar cells       |          |

|    |                 | 2.2.1 Hydrogenated amorphous sincon                           |          |

|    |                 | 2.2.3 Optical and electrical properties of a-Si:H and nc-Si:H |          |

|    | 2.3             | Interdigitated-back-contacted solar cell                      |          |

|    | 2.0             | 2.3.1 Introduction to tunneling recombination junction        |          |

|    | 2.4             | Working principle of TMO-SHJ solar cells                      |          |

| 3  | Met             | thods for SHJ Solar Cell Fabrication and Characterization     | 19       |

|    | 3.1             | Wafer preparation techniques                                  | 19       |

|    |                 | 3.1.1 Wafer texturing                                         | 19       |

|    |                 | 3.1.2 Wafer cleaning                                          | 19       |

|    | 3.2             | Deposition techniques                                         |          |

|    |                 | 3.2.1 Plasma-enhanced chemical vapor deposition               |          |

|    |                 | 3.2.2 Radio frequency magnetron sputtering                    |          |

|    |                 | 3.2.3 Screen printing                                         |          |

|    | 0.0             | 3.2.4 Evaporation                                             |          |

|    | 3.3             | Patterning techniques - Photolithography                      |          |

|    | 3.4             | Characterization techniques                                   |          |

|    |                 | 3.4.1 Spectroscopic ellipsometry                              | 25<br>26 |

|    |                 | 3.4.3 Current-Voltage measurement                             |          |

|    |                 | 3.4.4 SunsV <sub>OC</sub> measurement                         |          |

|    |                 | 3.4.5 External quantum efficiency                             |          |

|    |                 | 3.4.6 UV-Vis-NIR spectroscopy                                 |          |

| 4  | IBC             | C-SHJ solar cells with Si-based doped layers                  | 33       |

| •  | 4.1             | FBC solar cells as a proof-of-concept                         |          |

|    | 4.2             | Fabrication of tunneling IBC-SHJ solar cells                  |          |

|    | 1.4             | 4.2.1 Process challenges                                      |          |

|    |                 | 4.2.2 Results and analysis                                    |          |

Contents

|              | 4.3    | Fabrication of standard IBC-SHJ solar cells                                                                                               | 41<br>43<br>44 |

|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 5            | IBC    | C-SHJ solar cells with $MoO_x$                                                                                                            | 47             |

|              | 5.1    | Introduction to IBC-SHJ solar cells with $MoO_x$ blanket layer                                                                            | 47             |

|              | 5.2    | FBC solar cells as proof-of concept $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$                                      |                |

|              |        | 5.2.1 Fabrication of FBC-SHJ solar cells                                                                                                  |                |

|              |        | 5.2.2 Results and analysis                                                                                                                |                |

|              | 5.3    | Fabrication of IBC-SHJ solar cells with $MoO_x$                                                                                           |                |

|              |        | 5.3.1 Process challenges                                                                                                                  |                |

|              |        | 5.3.2 Results and analysis                                                                                                                |                |

|              | 5.4    | 5.3.3 Conclusions and outlook on the IBC-SHJ architecture with $MoO_x$ Optimization of contact stacks of IBC-SHJ solar cells with $MoO_x$ |                |

|              | 5.4    | 5.4.1 MoO <sub>x</sub> thickness series with PT                                                                                           |                |

|              |        | 5.4.2 MoO <sub>x</sub> thickness series without PT                                                                                        |                |

|              | 5.5    | Conclusions and outlook                                                                                                                   |                |

| 6            | Con    | aclusions and outlooks                                                                                                                    | 69             |

| U            | 6.1    | Conclusions                                                                                                                               | 69             |

|              | 0.1    | 6.1.1 Development and optimization of process flowchart for fabrication of high-efficiency                                                | 0.5            |

|              |        |                                                                                                                                           | 69             |

|              |        | 6.1.2 Optimization of electron and hole collection layers of IBC-SHJ solar cells                                                          | 69             |

|              | 6.2    | Outlooks                                                                                                                                  | 70             |

|              |        | 6.2.1 Improvements of the fabrication process of IBC-SHJ solar cells                                                                      | 70             |

|              |        | 6.2.2 Optimization of materials and layers implemented in devices                                                                         | 70             |

| $\mathbf{A}$ | Opt    | imization of contact stacks of IBC-SHJ solar cells with $MoO_x$                                                                           | <b>73</b>      |

| Ac           | knov   | wledgments                                                                                                                                | 77             |

| D.           | efere  | neos                                                                                                                                      | 84             |

| Tre          | rer er | IICES                                                                                                                                     | 34             |

# Nomenclature

| Abbreviations             |                                                                | Unit                     |

|---------------------------|----------------------------------------------------------------|--------------------------|

| ARC                       | Anti-reflection coating                                        |                          |

| BSF                       | Back surface field                                             |                          |

| DST                       | Double-side-textured                                           |                          |

| $\mathrm{ETL}$            | Electron transport layer                                       |                          |

| EQE                       | External quantum efficiency                                    | [-]                      |

| IQE                       | Internal quantum efficiency                                    | [-]                      |

| FBC                       | Front/back-contacted                                           |                          |

| FJ                        | Front junction                                                 |                          |

| FSF                       | Front surface field                                            |                          |

| FZ                        | Float zone                                                     |                          |

| HPT                       | Hydrogen plasma treatment                                      |                          |

| HTL                       | Hole transport layer                                           |                          |

| IBC                       | Interdigitated-back-contacted                                  |                          |

| ITO                       | Indium tin oxide                                               |                          |

| IWO                       | Indium tungsten oxide                                          | r -31                    |

| MCD                       | Minority carrier density                                       | $[\mathrm{cm}^{-3}]$     |

| PECVD                     | Plasma enhanced chemical vapor deposition                      |                          |

| PVD<br>PT                 | Physical vapor deposition<br>Plasma treatment                  |                          |

| RF                        | Radio frequency                                                |                          |

| RJ                        | Rear junction                                                  |                          |

| SHJ                       | Silicon heterojunction                                         |                          |

| SRH                       | Shockley-Read-Hall                                             |                          |

| SST                       | Single-side-textured                                           |                          |

| TCO                       | Transparent conductive oxide                                   |                          |

| TMO                       | Transition metal oxide                                         |                          |

| TRJ                       | Tunneling recombination junction                               |                          |

| VHF                       | Very high frequency                                            |                          |

| WF                        | Work function                                                  | [eV]                     |

| Letters                   |                                                                |                          |

| $E_{\mathbf{a}}$          | Activation enegy                                               | [meV]                    |

| $\mathrm{E_{F}}$          | Fermi energy                                                   | [eV]                     |

| $\mathrm{E}_{\mathrm{G}}$ | Band gap                                                       | [eV]                     |

| $\operatorname{FF}$       | Fill factor                                                    | [%]                      |

| $ m I_{ph}$               | Photocurrent                                                   | [A]                      |

| $iV_{OC}$                 | Implied open-circuit voltage                                   | [mV]                     |

| $J_0$                     | Saturation current density                                     | $[mA/cm^2]$              |

| $ m J_{SC}$               | Short-circuit current density                                  | $[mA/cm^2]$              |

| $J_{SC, EQE}$             | Short-circuit current density calculated from EQE measurements | $[\mathrm{mA/cm^2}]$     |

| pFF                       | Pseudo fill factor                                             | [%]                      |

| R                         | Reflectance                                                    | [-]                      |

| $R_{S}$                   | Series resistance                                              | $[\Omega \text{cm}^2]$   |

| $R_{S, SunsVoc}$          | Series resistance calculated from $SunsV_{OC}$ measurements    | $[\Omega \mathrm{cm}^2]$ |

| $ m R_{SH}$        | Shunt resistance                           | $[\Omega { m cm}^2]$ |

|--------------------|--------------------------------------------|----------------------|

| $V_{OC}$           | Open-circuit voltage                       | [mV]                 |

| η                  | Photoconversion efficiency                 | [%]                  |

| λ                  | Wavelength                                 | [nm]                 |

| $	au_{	ext{eff}}$  | Effective minority charge carrier lifetime | $[\mu s]$            |

| $\sigma_{ m dark}$ | Dark conductivity                          | [S/cm]               |

# List of Figures

| 1.1<br>1.2<br>1.3<br>1.4 | Global PV installation estimate (blue) and forecast (light blue) as of January 2022 [5] The best efficiency developments of c-Si solar cells [14]                                                                                           | 1<br>2<br>3<br>3 |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2.1                      | Schematic illustration of the photon absorption in a semiconductor with bandgap $E_G$ . $E_{\rm ph}$ represents photon energy, CB represents conduction band and VB represents valence                                                      |                  |

| 2.2                      | band [3]                                                                                                                                                                                                                                    | 8                |

| 2.3                      | circuit [3]                                                                                                                                                                                                                                 | 9                |

| 2.4                      | Band diagram of a (a) homojunction and (b) SHJ based on $n$ -type c-Si absorber. $E_C$ denotes the conduction band edge, $E_V$ the valence band edge, $E_F$ the Fermi level, $e^-$                                                          | 11               |

| 2.5                      | Schematic representation of crystalline silicon (left) and amorphous silicon (right) crystal lattice                                                                                                                                        | 12               |

| 2.6                      | Schematic representation of a-Si:H growth on hydrogen-terminated Si surface. Adapted from [45]                                                                                                                                              | 12               |

| 2.7                      | Schematic representation of nanocrystalline silicon                                                                                                                                                                                         | 13               |

| 2.8                      | Schematic cross-sectional representation of nc-Si:H growth on c-Si substrate coated with                                                                                                                                                    |                  |

|                          | -                                                                                                                                                                                                                                           | 14               |

| 2.9                      | Schematic representation of (a) TRJ consisting of intrinsic and doped Si-based layers,                                                                                                                                                      |                  |

|                          | TCO and metal and (b) sketch of band diagram of TRJ. Adapted from [20] Cross-section of the doped nc-Si:H bilayer microstructure on the rear side of tunneling                                                                              | 15               |

| 2.10                     | IBC device. Adapted from [20]                                                                                                                                                                                                               | 16               |

| 2.11                     | The structure of FBC-SHJ solar cell with $MoO_x$                                                                                                                                                                                            | 17               |

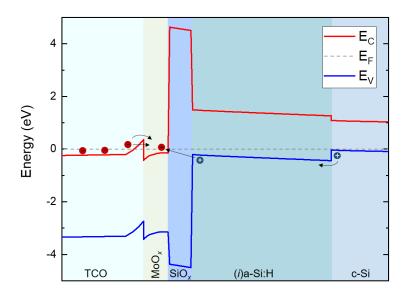

|                          | Band diagram of hole transport layer featuring $MoO_x$ . Conduction and valence bands are shown in red and blue, respectively. Transport of electrons (red circles) and holes                                                               |                  |

|                          | (blue circles) is sketched                                                                                                                                                                                                                  | 17               |

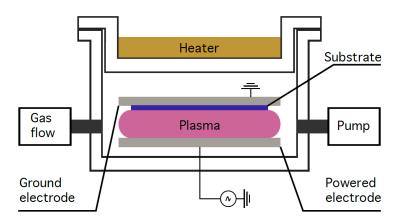

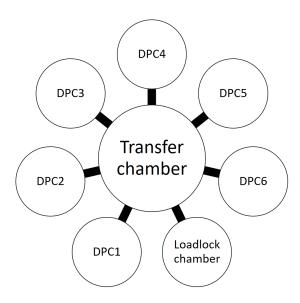

| 3.1<br>3.2               | Schematic representation of a typical PECVD chamber. Adapted from [39] Schematic top-view of AMIGO PECVD (Elettrorava, S.p.A.) with six deposition chambers, loadlock chamber, and transfer chamber. All chambers are connected to pumps to | 20               |

|                          | allow high vacuum transfer and deposition                                                                                                                                                                                                   | 21               |

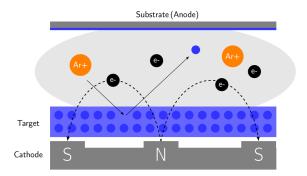

| 3.3                      | Schematic representation of magnetron sputtering process. Adapted from [71]                                                                                                                                                                 | 22               |

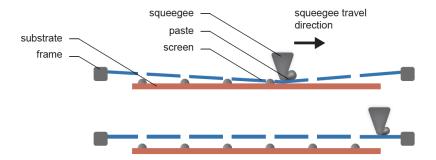

| 3.4                      | Schematic representation of screen printing during the process (top) and at the end of                                                                                                                                                      |                  |

|                          | the process (bottom). Adapted from [74]                                                                                                                                                                                                     | 23               |

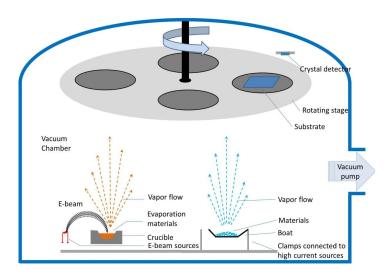

| 3.5                      | Schematic representation of metal evaporation system used in this project. Electron                                                                                                                                                         |                  |

|                          | beam evaporation is shown on the left, while thermal evaporation is on the right side of                                                                                                                                                    |                  |

|                          | the sketch. Adapted from [77]                                                                                                                                                                                                               | 23               |

| 3.6                      | Schematic representation of the simplified working principle of photolithography using a                                                                                                                                                    |                  |

|                          | positive photoresist. Adapted from [74]                                                                                                                                                                                                     | 24               |

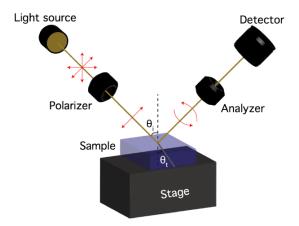

| 3.7                      | Schematic representation of the SE measurement setup. Adapted from [39]                                                                                                                                                                     | 25               |

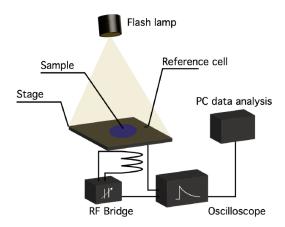

| 3.8                      | Schematic representation of Sinton WCT-120. Adapted from [39]                                                                                                                                                                               | 26               |

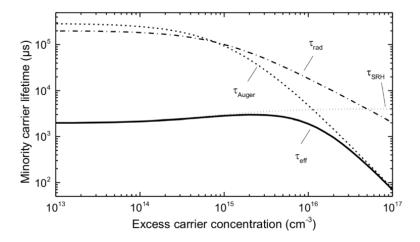

| 3.9                      | Simulated minority carrier lifetime curve as function of the excess carrier concentration.                                                                                                                                                  |                  |

|                          | Adapted from [44]                                                                                                                                                                                                                           | 27               |

List of Figures ix

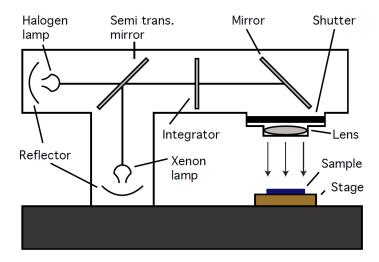

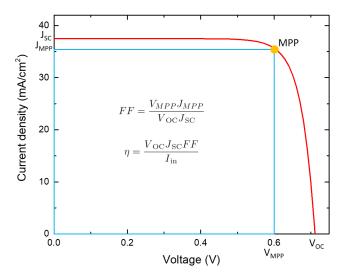

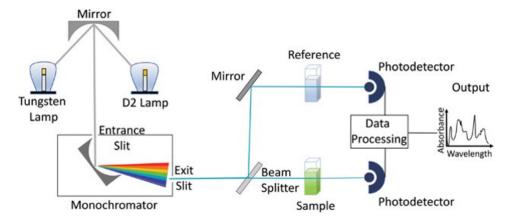

|              | Schematic representation of current-voltage measurement setup. Adapted from [39] An example of a J-V curve with external parameters and definition of fill factor and photoconversion efficiency                                                         | 28<br>28 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

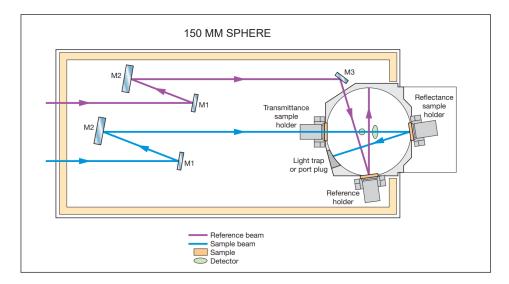

|              | Schematic representation of UV-Vis-NIR spectrophotometer. Adapted from [83] Schematic representation of the optical design of 150 mm integrating sphere including the position of sample holders for transmittance and reflectance measurements. Adapted | 30       |

|              | from [84]                                                                                                                                                                                                                                                | 30       |

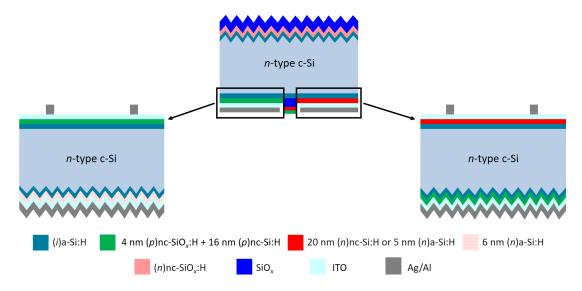

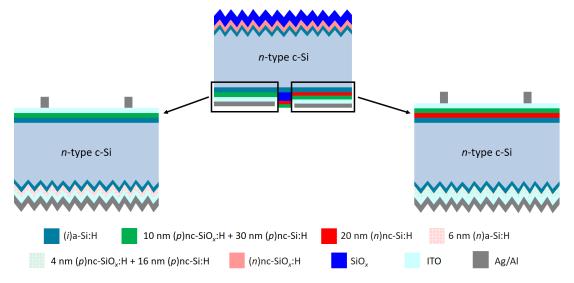

| 4.1          | The structure of standard IBC-SHJ and corresponding FBC-SHJ solar cells with Si-based doped layers. FBC-SHJ devices are fabricated by [85]                                                                                                               | 33       |

| 4.2          | The structure of tunneling IBC-SHJ and corresponding FBC-SHJ solar cells with Si-based doped layers. FBC-SHJ devices are fabricated by [85]                                                                                                              | 34       |

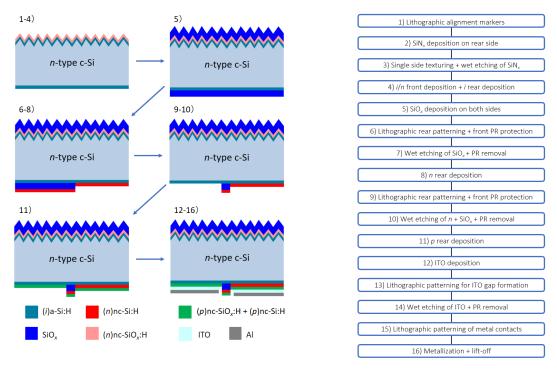

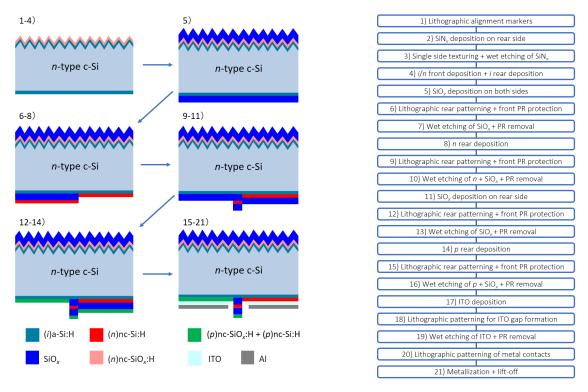

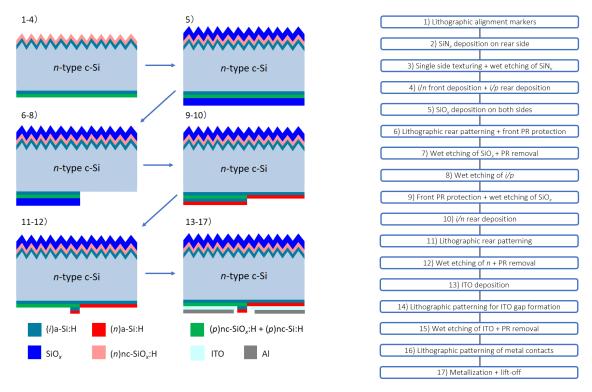

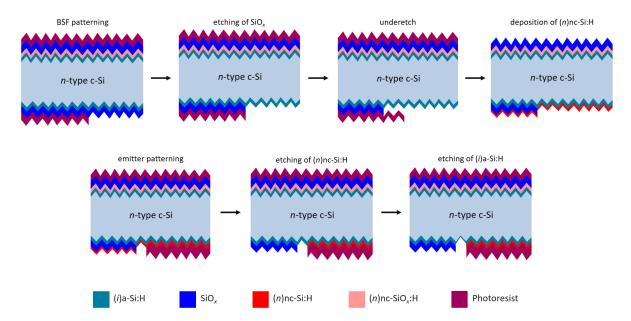

| 4.3          | Flowchart of tunneling IBC-SHJ solar cell manufacturing process using wet etching steps.                                                                                                                                                                 | 35       |

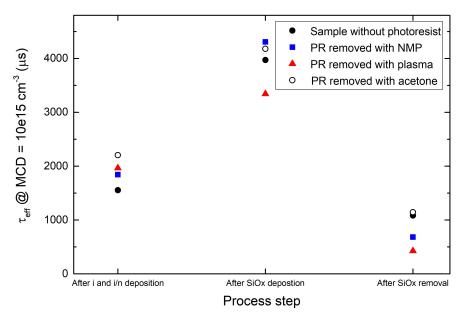

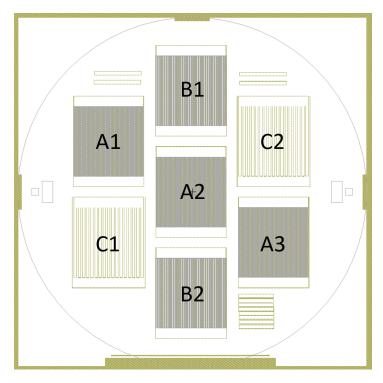

| $4.4 \\ 4.5$ | Effective carrier lifetime depending on the photoresist removal method                                                                                                                                                                                   | 37<br>38 |

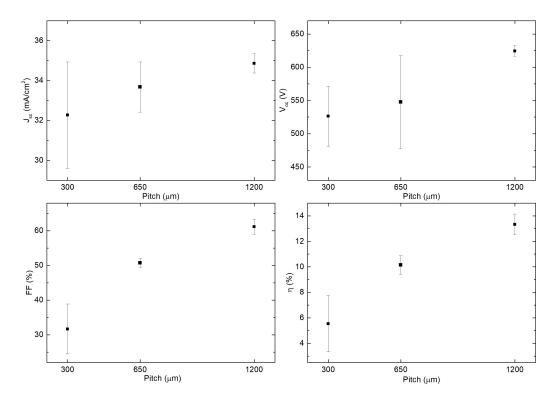

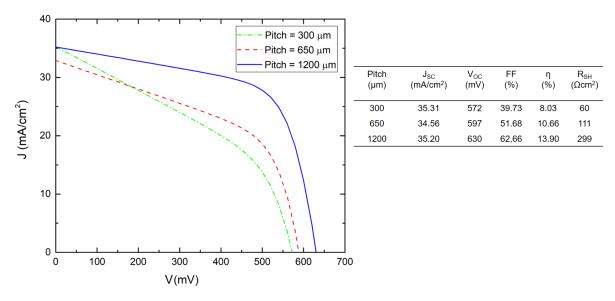

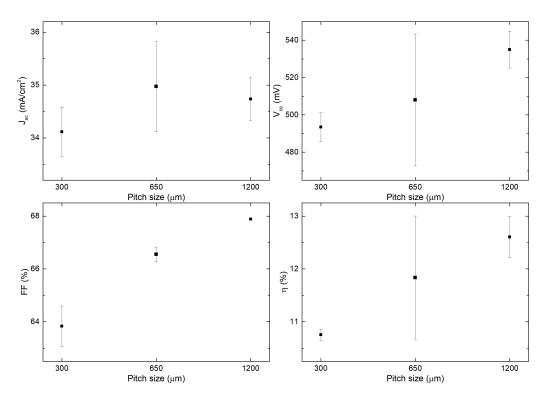

| 4.6          | External parameters of single-side textured tunneling IBC cells with different pitch sizes.                                                                                                                                                              | 39       |

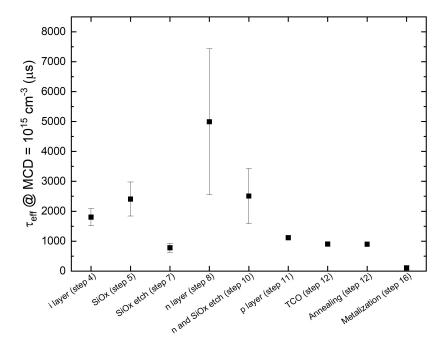

| 4.7          | $\tau_{\rm eff}$ of cell precursors during fabrication process                                                                                                                                                                                           | 40       |

| 4.8          | J-V curves, external parameters and R <sub>SH</sub> values of best single-side textured tunneling IBC-SHJ solar cells with different pitch sizes                                                                                                         | 40       |

| 4.9          | Flowchart of standard IBC-SHJ solar cell manufacturing process using wet etching steps.                                                                                                                                                                  | 41       |

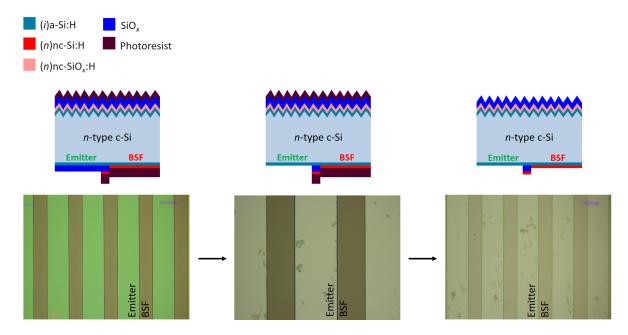

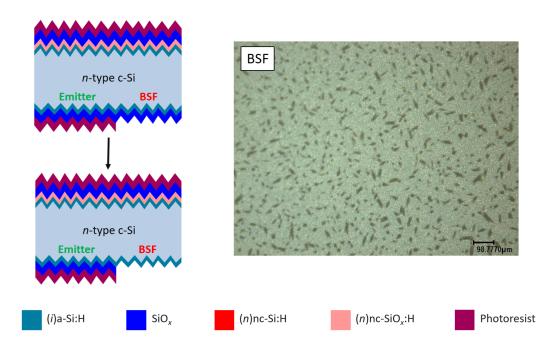

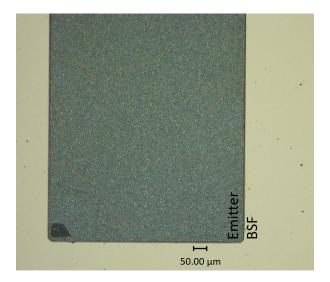

| 4.10         | Cell precursor sketches in the case of ideal etching and optical microscope images of etching residues resulting from consequent removal of $(n)$ nc-Si:H and SiO <sub>x</sub> (step 10 in                                                               |          |

|              | Figure 4.9)                                                                                                                                                                                                                                              | 42       |

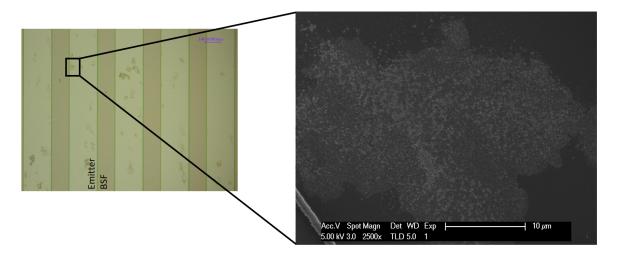

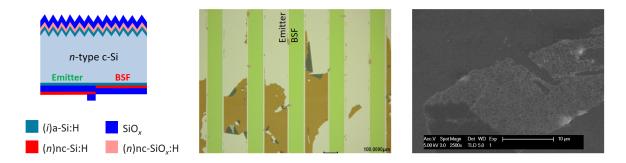

|              | Optical microscope (left) and SEM (right) image of etching residues resulting from consequent removal of $(n)$ nc-Si:H and SiO <sub>x</sub>                                                                                                              | 42       |

| 4.12         | Simplified flowchart of standard IBC-SHJ solar cell manufacturing process using wet etching steps                                                                                                                                                        | 43       |

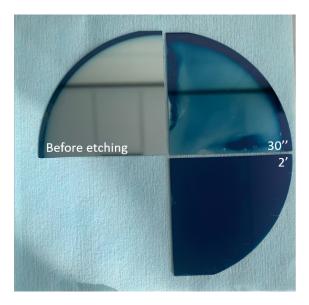

| 4.13         | Samples showing nonuniform etching of (i)a-Si:H/(n)a-Si:H layer stack in 1% KOH solution after 30 seconds (top right) and 2 minutes (bottom right)                                                                                                       | 44       |

|              | Flowchart of standard IBC-SHJ solar cell manufacturing process using dry etching steps.                                                                                                                                                                  | 45       |

| 4.15         | Sketch of the process step (left), optical microscope (middle) and SEM (right) image of etching residues resulting from removal of $SiO_x$                                                                                                               | 46       |

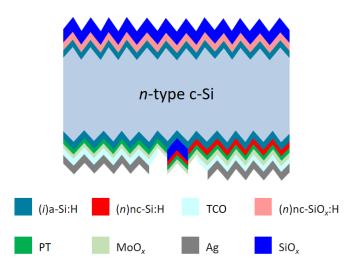

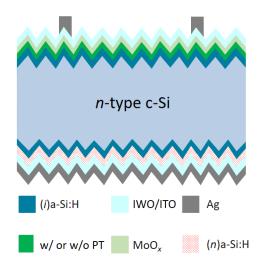

| 5.1          | The structure of IBC-SHJ solar cell with $MoO_x$                                                                                                                                                                                                         | 47       |

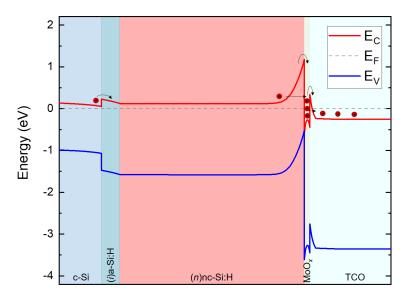

| 5.2          | Band diagram of electron transport layer featuring $(n)$ nc-Si:H/MoO <sub>x</sub> contact. Conduction and valence bands are shown in red and blue, respectively. The transport of electrons                                                              |          |

|              | (red circles) is sketched                                                                                                                                                                                                                                | 48       |

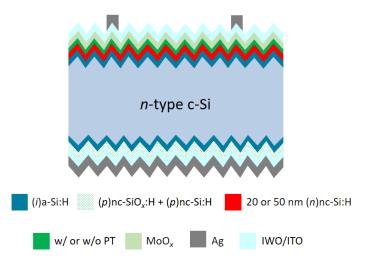

| 5.3          | The structure of IBC-SHJ solar cell with $MoO_x$ and corresponding FBC-SHJ solar cells.                                                                                                                                                                  | 49       |

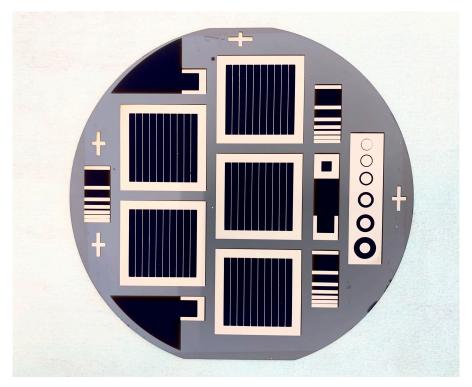

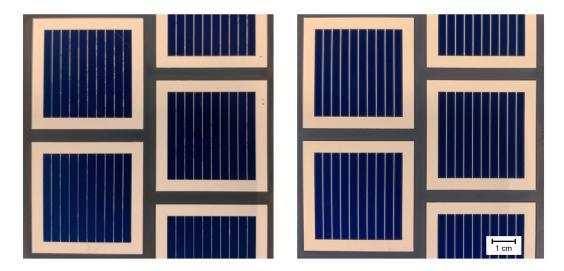

| 5.4          | The front side of manufactured FBC-SHJ solar cells                                                                                                                                                                                                       | 50       |

| 5.5<br>5.6   | The structure of FJ FBC-SHJ solar cell                                                                                                                                                                                                                   | 51       |

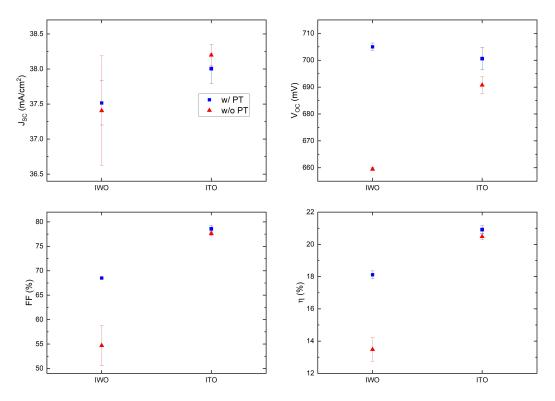

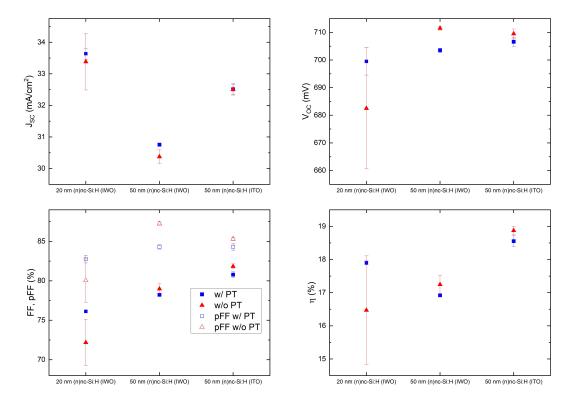

| 5.0          | function of selected TCO                                                                                                                                                                                                                                 | 52       |

| 5.7          | Devices with poorly printed metal fingers (left) and devices with successful screen printing.                                                                                                                                                            | 52       |

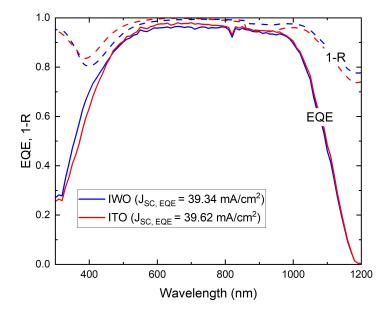

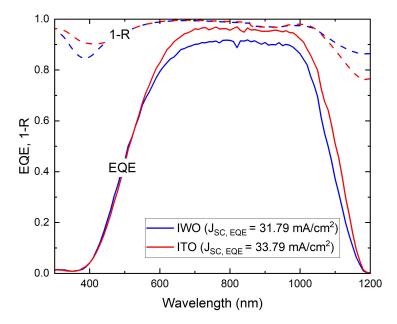

| 5.8          | External quantum efficiency (EQE) and 1-R curves of FJ solar cells with PT. J <sub>SC, EQE</sub> values are indicated in the legend.                                                                                                                     | 53       |

| 5.9          | The structure of RJ FBC-SHJ solar cell                                                                                                                                                                                                                   | 54       |

| 5.10         | External parameters of double-side textured RJ FBC-SHJ solar cells with $\mathrm{MoO}_x$ as a                                                                                                                                                            |          |

| 5.11         | function of $(n)$ nc-Si:H thickness and selected TCO                                                                                                                                                                                                     | 55       |

|              | Si:H and without PT. $J_{SC, EQE}$ values are indicated in the legend                                                                                                                                                                                    | 56       |

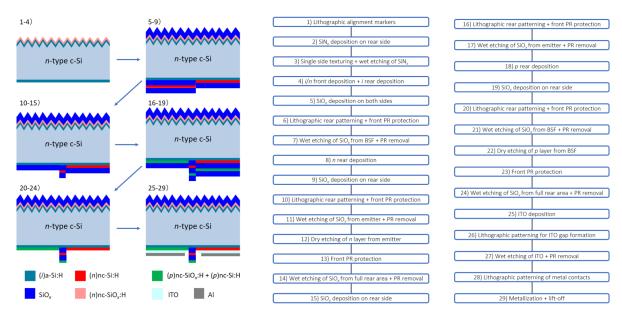

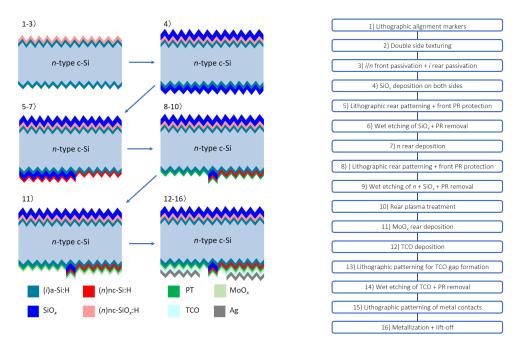

|              | Flowchart of IBC-SHJ solar cell with $MoO_x$ manufacturing process                                                                                                                                                                                       | 57       |

| 5.13         | A sketch of the etching step (left) and optical microscope image (right) of a sample                                                                                                                                                                     |          |

|              | showing nonuniform etching of $SiO_x$ in BHF 1:7 solution in step 6. Darker areas represent $SiO_x$ , while lighter areas are underlying (i)a-Si:H                                                                                                       | 58       |

| 5 14         | Optical microscope image of a sample showing $SiO_x$ residue after etching in BHF 1:7                                                                                                                                                                    | 90       |

| J.17         | solution in step 9. The darkest area in the bottom left corner represents $SiO_x$                                                                                                                                                                        | 59       |

List of Figures x

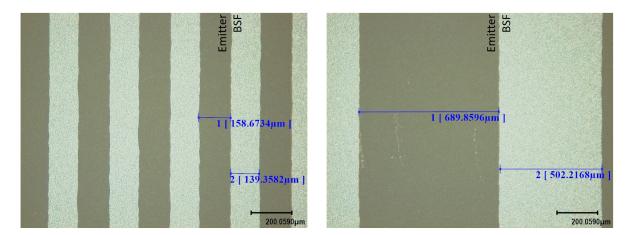

| 5.15 | Optical microscope image of samples showing a result of isotropic of $SiO_x$ after etching            |    |

|------|-------------------------------------------------------------------------------------------------------|----|

|      | in BHF 1:7 solution in step 6. On the left, a device with the smallest pitch is shown (cell           |    |

|      | type A). On the right, a device with the largest pitch is shown (cell type C)                         | 60 |

| 5.16 | Sketch of processing steps including the underetch of $SiO_x$ caused by isotropic etching             |    |

|      | and the influence of the underetch on further processing. The steps shown in this sketch              |    |

|      | correspond to steps 5 to 9 of the flowchart.                                                          | 60 |

| 5.17 | External parameters of double-side textured IBC-SHJ solar cells with $MoO_x$ related to               |    |

|      | different pitch sizes.                                                                                | 61 |

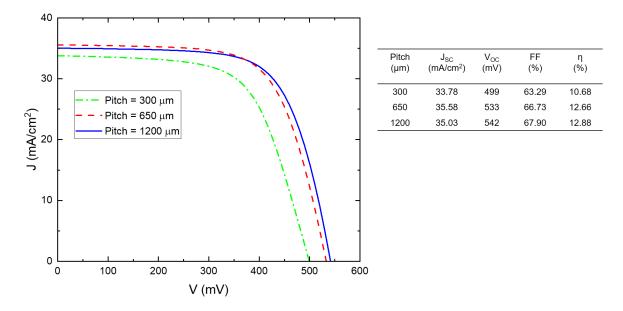

| 5.18 | J-V curves and external parameters of best double-side textured IBC-SHJ solar cells with              |    |

|      | $MoO_x$ with different pitch sizes                                                                    | 62 |

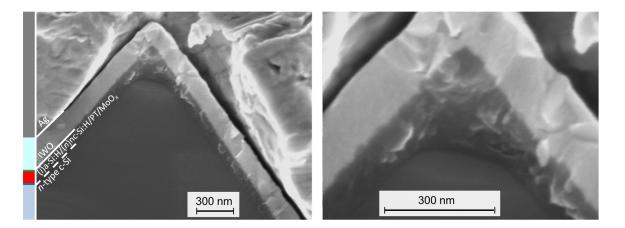

| 5.19 | SEM cross-section of election collection stack. Images show the same contact stack with               |    |

|      | lower (left) and higher (right) magnification                                                         | 63 |

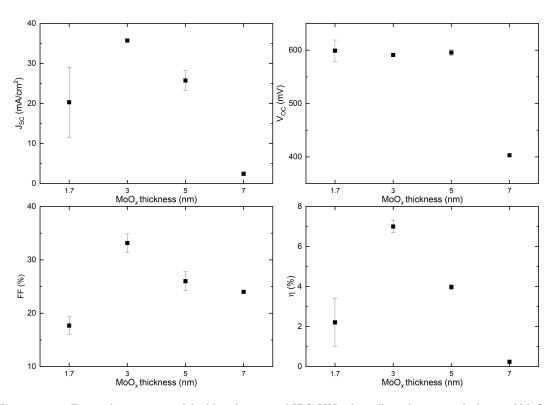

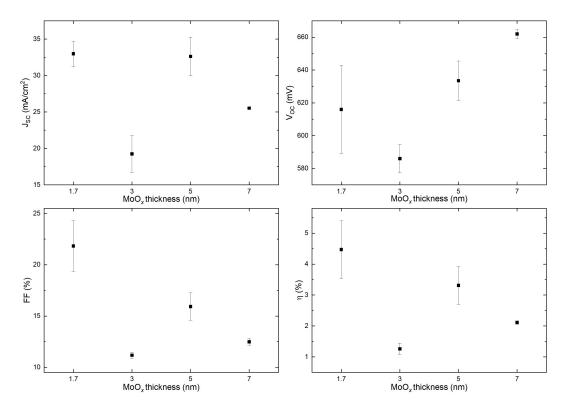

| 5.20 | External parameters of double-side textured IBC-SHJ solar cells with varying thickness                |    |

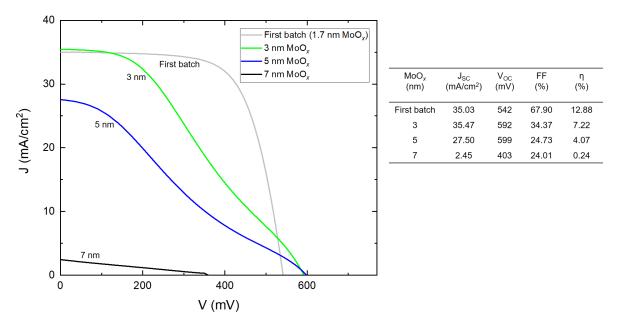

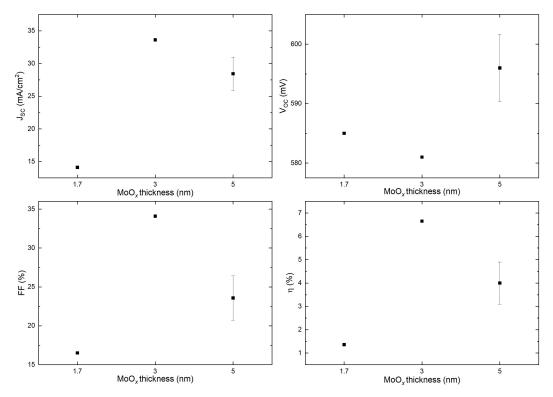

|      | of $\mathrm{MoO}_x$ .                                                                                 | 64 |

| 5.21 | J-V curves and external parameters of double-side textured IBC-SHJ solar cells with                   |    |

|      | varying thickness of $MoO_x$                                                                          | 65 |

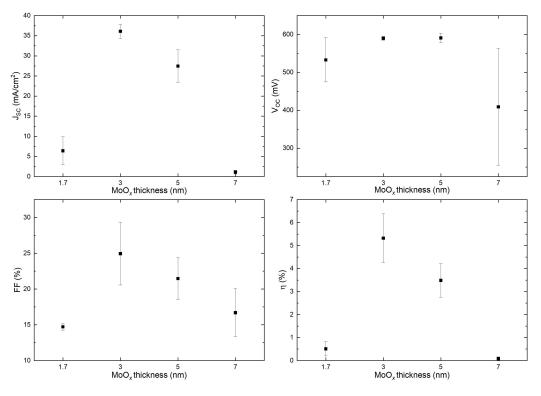

| 5.22 | External parameters of double-side textured IBC-SHJ solar cells with varying thickness                |    |

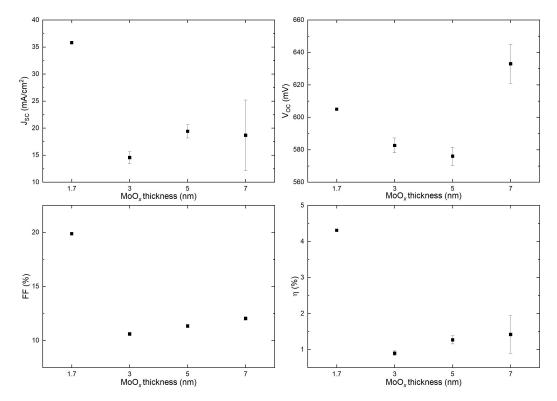

|      | of $MoO_x$ without PT                                                                                 | 66 |

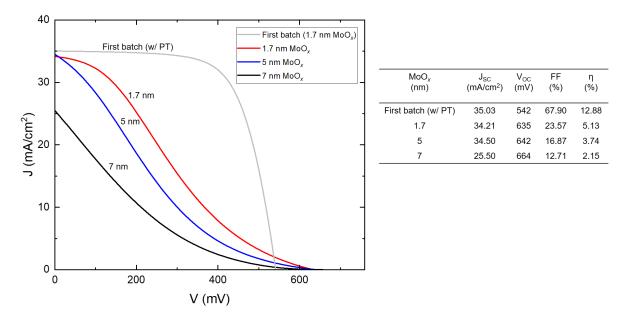

| 5.23 | J-V curves and external parameters of double-side textured IBC-SHJ solar cells with                   |    |

|      | varying thickness of $MoO_x$ without PT                                                               | 67 |

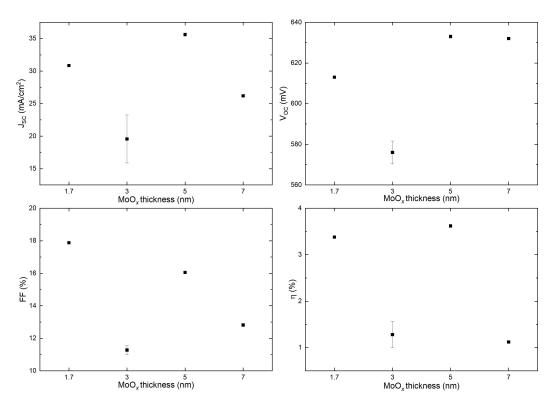

| A.1  | External parameters of double-side textured IBC-SHJ solar cells with varying thickness                |    |

| л.1  | of $MoO_x$ with PT. Parameters of devices with 300 $\mu$ m pitch (cell type A) are shown              | 73 |

| A.2  | External parameters of double-side textured IBC-SHJ solar cells with varying thickness                | 10 |

| Λ.Δ  | of $MoO_x$ with PT. Parameters of devices with 650 µm pitch (cell type B) are shown                   | 74 |

| A.3  | External parameters of double-side textured IBC-SHJ solar cells with varying thickness                | 14 |

| 11.0 | of $MoO_x$ without PT. Parameters of devices with 300 µm pitch (cell type A) are shown.               | 75 |

| A.4  | External parameters of double-side textured IBC-SHJ solar cells with varying thickness                | 10 |

| 11.7 | of $MoO_x$ without PT. Parameters of devices with 650 µm pitch (cell type B) are shown.               | 75 |

|      | of 1400 $x$ without 1.1.1 drameters of devices with 000 $\mu$ m pitch (cen type <b>b</b> ) are shown. | 10 |

# List of Tables

|     | Deposition parameters of layers deposited with AMIGO PECVD (Eletrrorava, S.p.A.). Deposition parameters of $SiO_x$ deposited with Plasmalab 80 Plus PECVD (Oxford In- | 21 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | struments plc)                                                                                                                                                        | 22 |

| 4.1 | The results of proof-of-concept FBC-SHJ solar cells fabricated by [85]                                                                                                | 35 |

| 4.2 | The geometry of three types of manufactured solar cells                                                                                                               | 38 |

| 4.3 | Dry etching conditions and approximate etching rate for materials used in this thesis.  .                                                                             | 45 |

| 5.1 | Four types of fabricated FJ FBC-SHJ solar cells                                                                                                                       | 51 |

| 5.2 | The results of best proof-of-concept FJ FBC-SHJ solar cells with MoOx                                                                                                 | 53 |

| 5.3 | Six types of fabricated RJ FBC-SHJ solar cells                                                                                                                        | 54 |

| 5.4 | The results of best proof-of-concept RJ FBC-SHJ solar cells with MoOx                                                                                                 | 56 |

# Introduction

# 1.1. Status and perspectives of solar energy

The increase in energy demand is one of the main challenges of the 21<sup>st</sup> century leading to a number of social and environmental concerns such as resource depletion, energy shortages, and climate change [1]. Predictions of global population growth of 2 billion by 2050 indicate a further increase in energy demand and related problems. Such problems are considered the most important drivers for the sustainable energy transition [2]. With the sun being an abundant energy source, solar energy plays a significant part in the energy transition as a possible alternative to traditional energy sources [3]. Photovoltaic (PV) technology, which converts solar energy to electricity, is currently considered a crucial renewable energy technology with a sharp increase in capacity installations over the past decade [4]. In 2021, newly installed PV capacity reached 183 GW, which is an increase of almost 40 GW compared to 2020 (Figure 1.1).

Figure 1.1: Global PV installation estimate (blue) and forecast (light blue) as of January 2022 [5].

Moreover, in March 2022 global installed PV capacity reached 1 TW, marking the start of the terawatt age for photovoltaics [6]. As shown in Figure 1.1, yearly installations are expected to further increase in the coming years as a result of a decrease in energy production costs [5]. Crystalline silicon (c-Si) modules represent the majority of PV modules produced and installed up to date, which can be ascribed to the abundance of silicon in nature and fast increase in volume manufacturing [7]. The trends of cost decrease and efficiency improvements of c-Si photovoltaics are expected to continue, ensuring that this

PV technology prospers as a global energy source playing a vital role in the decarbonization of energy systems and climate change mitigation [7].

# 1.2. Silicon heterojunction solar cells

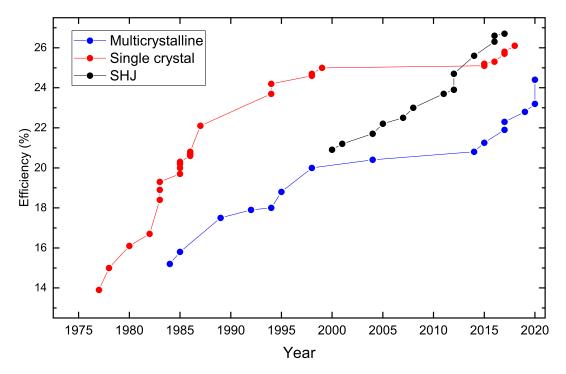

Silicon heterojunction (SHJ) solar cells are one of the most promising PV technologies nowadays due to low manufacturing costs and high photoconversion efficiencies. In June 2022, LONGi reported the new record efficiency for front/back-contacted (FBC) SHJ device of 26.5% [8]. Previous record efficiency of 26.3%, also held by LONGi, was achieved as a result of improved passivation quality, decrease in contact resistance and use of a (n)µc-Si:H window layer [9]. Optimization of these parameters enabled enhancement of  $V_{OC}$ , FF and  $J_{SC}$ , respectively. Moreover, the highest certified photoconversion efficiency of single-junction c-Si cells was achieved by Japanese Kaneka Corporation in 2018, reaching an efficiency of 26.7% with interdigitated-back-contacted (IBC) SHJ device [10], [11]. In Figure 1.2, recent progress of SHJ devices is shown. Despite the later development of SHJ technology compared to other c-Si solar cells, SHJ devices have shown world record efficiencies in the past decade due to the use of passivating contacts. Namely, upon generation of charge carriers, it is important to efficiently collect them with minimal recombination losses. SHJ cells achieve excellent results due to the use of passivating contacts that allow the reduction of recombination at the surface of the silicon absorber. Typically, an intrinsic hydrogenated amorphous silicon layer ((i)a-Si:H) is deposited on both sides of the silicon absorber to reduce defect density, followed by the deposition of (n)a-Si:H and (p)a-Si:H layers. Doped layers induce band offset at c-Si/a-Si:H interface enabling selective carrier collection. Together, intrinsic and doped layers serve as selective passivating contacts allowing high V<sub>OC</sub> (730mV - 750mV) [12], [13].

Figure 1.2: The best efficiency developments of c-Si solar cells [14].

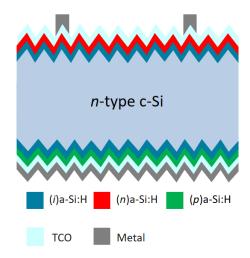

In Figure 1.3 typical architecture of double-side-textured (DST) FBC-SHJ device is presented. As mentioned above, (i)a-Si:H layers are deposited on both sides of c-Si absorber. On top of the intrinsic layer, n- and p-type silicon layers are deposited serving as semipermeable membranes for electron and hole collection, respectively. On the front side, transparent conductive oxide (TCO) is deposited to improve lateral transport of charge carriers, while also serving as an anti-reflection coating (ARC). On the rear side, the TCO layer is deposited with the main purpose of preventing spiking during contact formation and maximizing the internal reflectance [15], [16]. The last step of SHJ device manufacturing involves the formation of metal contacts that allow the connection of the device to the external circuit.

Unlike the traditional solar cells that use p-type wafers, SHJ devices are typically made on n-type c-Si absorber due to lower price, lower light degradation and its better tolerance for impurities [3]. Moreover, results of SHJ cells based on p-type c-Si absorber show lower performance than their n-type counterparts [16], [17].

Figure 1.3: The structure of a typical FBC-SHJ solar cell with a-Si:H layers.

However, one of the limitations of FBC solar cells in general is lower  $J_{SC}$  due to the shading by the front metal contacts. Lower light absorption due to shading and resulting limitation in  $J_{SC}$  directly influence photoconversion efficiency of the devices. In the case of FBC-SHJ solar cells, additional losses are caused by the parasitic absorption of front TCO and front Si layers.

# 1.3. Interdigitated-back-contacted solar cells

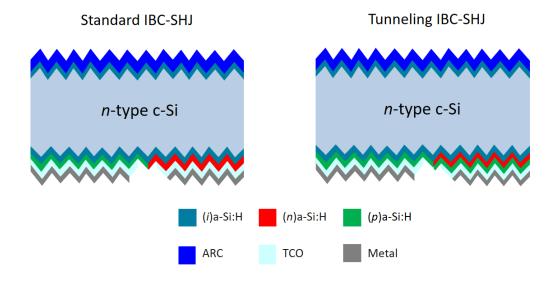

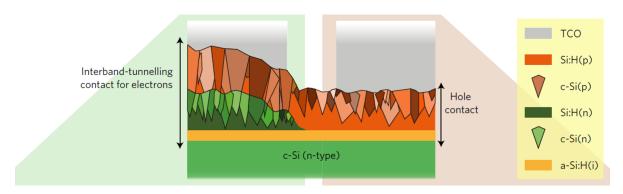

By placing both electron and hole collection contact stacks on the rear side of the device and allowing the removal of the front metal grid and TCO, IBC cells offer a solution for above mentioned  $J_{SC}$  limitations and provide an improved cell performance. Moreover, front Si layers in IBC devices are only used for passivation purposes and, therefore, they can be optimized to decrease parasitic absorption and to serve as an ARC. Figure 1.4 shows a schematic representation of standard and tunneling IBC-SHJ.

Figure 1.4: The structure of standard (left) and tunneling (right) IBC-SHJ solar cell with a-Si:H layers.

In the case of the standard IBC device, (p)a-Si:H layer is used as an emitter, whereas the (n)a-Si:H forms a back surface field (BSF). In order to ensure high  $V_{OC}$ , good passivation of both front and rear surfaces is obtained by deposition of high quality (i)a-Si:H. To secure high FF, it is important to ensure the good interface quality between intrinsic and (p)a-Si:H during the processing [18]. Moreover, low FF can be caused by the reduced area for electron and hole collection [19]. Therefore, it is important to carefully select the area and ratio of electron and hole collection regions. Lastly, High  $J_{SC}$  can be achieved by optimizing the front side of the device by introducing a transparent, dielectric layer (e.g.  $SiO_x$ ) that acts as an ARC.

On the other hand, for a tunneling device (see Figure 1.4 (right)), the layer stack including (n)a-Si:H and (p)a-Si:H serves as BSF, while other aspects of the device are kept the same as in the standard IBC structure. This architecture is introduced as the standard fabrication process of IBC solar cells comes with high complexity and manufacturing costs [20]. The fabrication of tunneling IBC cells typically involves fewer patterning steps compared to the standard architecture, leading to lower manufacturing costs and a fabrication process that is more industry appealing and scalable.

Due to manufacturing defects such as imprecise patterning, significant power losses can occur in solar cells as a result of shunting. Namely, low shunt resistance provides an alternative path for the photogenerated current leading to power losses. In order to ensure high shunt resistance, in both standard and tunneling IBC devices proposed in this project, BSF and emitter are separated by 7  $\mu$  wide SiO<sub>x</sub> gap. Even though this gap is expected to isolate electron and hole collection regions, due to relatively high lateral conductivity of p-type layer that is covering the full rear area of the cell, shunting can potentially be observed in tunneling devices. To overcome this problem, a layer with lower lateral conductivity can be introduced in place of p-type layers. As an alternative, so-called transition metal oxides (TMO) that act as carrier selective contacts can be implemented [21].

# 1.4. Transition metal oxides

Transition metal oxides (TMO) are an example of dopant-free materials that are characterized by low dark conductivity ( $\sigma_{\rm dark} = 2 \times 10^{-5}$  S/cm of MoO<sub>x</sub> [22] compared to  $\sigma_{\rm dark} = 10^{-1}$  S/cm of (p)nc-Si:H [23]) [21], [24]. TMOs have lately gained a lot of attention in photovoltaic research, firstly in combination with organic semiconductors followed by applications combined with SHJ technology [25]. TMOs are characterized by a large span of work function (WF) values allowing them to act as carrier selective contacts in SHJ devices [22], [26], [27]. This is because the difference in WF values at TMO/Si interface induces band banding leading to enhanced transport of one type of charge carrier and acting as a barrier for the other. Low WF TMOs can be used as electron transport layers (ETL) replacing n-type silicon-based layers, while high WF materials can act as hole transport layers (HTL) in SHJ cells [25].

Owing to their high WF, the common TMOs used as hole transport layers (HTL) are molybdenum trioxide (MoO<sub>3</sub> with WF = 6.9 eV), vanadium pentoxide (V<sub>2</sub>O<sub>5</sub> with WF = 7 eV) and tungsten trioxide (WO<sub>3</sub> with WF = 6.7 eV) [28]. Even though V<sub>2</sub>O<sub>5</sub> is characterized by the highest WF among the three materials, MoO<sub>3</sub> with slightly lower WF is most commonly used as HTL in SHJ solar cells due to lower melting temperature allowing for simple deposition via thermal evaporation [28]. An important feature of MoO<sub>3</sub> is the high oxygen reactivity leading to the reaction of oxygen atoms from MoO<sub>3</sub> with the surrounding materials. Due to oxygen reactivity, sub-stoichiometric molybdenum oxide (MoO<sub>x</sub> where x is in the range between 2 and 3) is deposited on the substrate [29]. Moreover, MoO<sub>x</sub> FBC-SHJ devices have shown excellent results in the past. Solar cells with MoO<sub>x</sub> as HTL on the front side and (n)a-Si:H as ETL on the rear side developed at PVMD group at the Delft University of Technology achieved conversion efficiency of 23.83%. During this project, contact stacks based on MoO<sub>x</sub> have been further developed and implemented in an IBC device.

# 1.5. Research goals

Even though research on IBC-SHJ solar cells has yielded excellent results [10], [11], the manufacturing process is very complex, requiring extensive efforts for optimizing the process to minimize losses and ensure high device quality. Therefore, the development of a working process flowchart for obtaining high-efficiency devices can be particularly challenging.

To minimize the losses along the fabrication process of IBC-SHJ solar cells, two main research goals are

1.6. Thesis outline 5

proposed. For each of the main research goals, sub-goals are defined to assist in efficiently achieving the research goals.

As the complex manufacturing of IBC devices involves potentially damaging steps leading to a decrease in device performance, the first main research goal of the project is:

- Development and optimization of process flowchart for fabrication of high-efficiency IBC-SHJ solar cells.

- (a) Recognizing and resolving the main obstacles in the process flowchart hindering the successful fabrication of IBC-SHJ solar cells.

- (b) Identifying processing steps that lead to degradation in passivation quality of cell precursors and optimizing the damaging steps to preserve passivation quality.

Once the flowchart is developed and the working IBC device is fabricated, the focus will shift towards improving the performance of the devices. To achieve better performance, the second main research goal is proposed as:

- 2. Optimization of electron and hole collection layers of IBC-SHJ solar cells to fabricate high-efficiency solar cells.

- (a) Identifying the main physical properties of electron and hole collection layers required for cells to achieve high  $V_{\rm OC}$  and FF.

- (b) Determining the main processing parameters that can be adjusted to fulfill the physical requirements.

### 1.6. Thesis outline

The key motivation for research on high-efficiency solar cells and specifically research on SHJ-IBC devices has been presented in Chapter 1. Subsequently, the main research goals of this thesis have been given.

Chapter 2 starts with an overview of the working principle of photovoltaic devices in general and introduces the fundamentals of SHJ technology, as well as the background on IBC architecture and the theory behind tunneling IBC devices. Moreover, in Chapter 2, the characteristics of materials used in fabricated devices and recombination and passivation mechanisms are covered. Chapter 3 introduces fabrication and characterization tools used during the work on this thesis. The results of FBC-SHJ devices used as proof-of-concept and the explanation and results of four main manufacturing approaches for IBC-SHJ devices with Si-doped layers are explained in Chapter 4. The main limitations of the attempted processes are highlighted, and the executed improvements and suggestions for future developments are described. In Chapter 5, alternative contact stacks are introduced in a simplified flowchart for the fabrication of IBC devices. The optimization of the IBC device structure and involved layers is covered in this Chapter. In Chapter 6, concluding notes and outlooks for future research are presented.

# **Fundamentals**

This Chapter provides a theoretical foundation for the experimental study conducted in this thesis, as well as for the main assumptions and methods used in this work. Firstly, the basic principles of photovoltaic energy conversion are presented in Section 2.1. This Section focuses on the basis of semiconductor physics for solar cell applications with an emphasis on the fundamental limitations and recombination mechanisms. The concept and working principle of silicon heterojunction solar cells are described in detail in Section 2.2. Moreover, the properties of materials implemented in manufactured devices are addressed in this Section. Furthermore, IBC architecture is introduced in Section 2.3, focusing on its main advantages and limitations. Lastly, the working principle of TMO-SHJ devices is explained in Section 2.4.

# 2.1. Photovoltaic fundamentals

In this Section, the fundamental theory of photovoltaic energy conversion is presented. Section 2.1.1 briefly introduces the main characteristics of semiconductor materials, while Section 2.1.2 focuses on the working principle of a solar cell. Lastly, Section 2.1.3 covers the principal limitations of solar cells.

### 2.1.1. Semiconductor materials

Semiconductors are a group of materials with conductivity values falling between conductors and insulators [30]. The conduction in semiconductors occurs at energy states that are separated by a gap (band gap) where no electrons are allowed [30]. In order to participate in conduction, electrons must absorb enough energy to bridge the band gap between the valence (VB) and conduction band (CB). The absorbed energy can be taken from thermal energy of the surroundings or be a result of illumination. When an electron is excited from the valence to conduction band, it leaves a positively charged hole in the valence band. If the bottom energy of CB is defined as  $E_C$  and the top energy of VB as  $E_V$ , then the width of the band gap can be defined as  $E_G$ = $E_C$ - $E_V$  [3].

# 2.1.2. Working principle of a solar cell

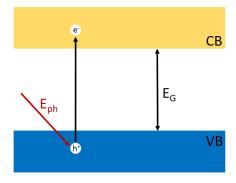

The formation of a potential difference at the junction of two materials due to exposure to light, called photovoltaic effect, is the basis for solar cells' operation [3]. Photovoltaic effect starts with photon absorption in a material (absorber) that leads to excitement of an electron to a higher energy level as shown in Figure 2.1.

Figure 2.1: Schematic illustration of the photon absorption in a semiconductor with bandgap  $E_G$ .  $E_{ph}$  represents photon energy, CB represents conduction band and VB represents valence band [3].

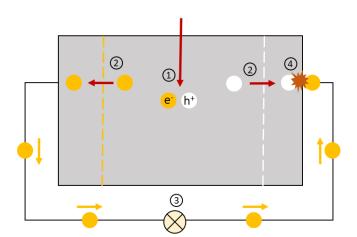

The photon with energy  $(E_{ph})$  larger than  $E_G$  of the absorber will excite an electron from VB to CB while leaving a positively charged hole in the valence band. In order to avoid recombination of the electron-hole pair, so-called semipermeable membranes formed by n- and p-type materials are placed on both sides of the absorber to selectively collect electrons and holes, respectively [3]. This is followed by the flow of charge carriers into an external circuit and their utilization in form of electricity. A simplified sketch of this process is shown in Figure 2.2.

Figure 2.2: A simplified model of a solar cell showing (1) absorption of a photo leading to the generation of electron-hole pair, (2) separation of electrons and holes, (3) formation of an external circuit and (4) electron-hole recombination as the electrons pass through the circuit [3].

# 2.1.3. Fundamental limitations and recombination mechanisms

The fundamental losses of solar cells are highly dependent on  $E_G$  of the absorber [3]. Namely, the photons with energy lower than the  $E_G$  cannot be absorbed, while part of the absorbed photon energy, in the case of photons with energy above  $E_G$ , cannot be utilized and is released as heat. In the case of low  $E_G$  material, high current can be achieved, but high thermalization losses limit voltage values. On the other hand, high  $E_G$  absorber can generate high voltage, but current losses are high. An optimum  $E_G$  for the highest conversion efficiency can be found as a trade-off between current and voltage losses.  $E_G$  of c-Si is equal to 1.12 eV, which is slightly below the optimal value of 1.34 eV [3].

As explained in Section 2.1.2, electron-hole pairs are generated in the absorber as a result of illumination. The excitation of electrons to conduction band due to illumination induces a non-equilibrium state and the system will attempt to reestablish the equilibrium condition. This occurs through so-called recombination mechanisms. As a result, charge carrier collection is suppressed, lowering solar cell

performance. The recombination process has an effect on both the current and voltage of the solar cell, however the limitation it poses on the solar cell voltage is more restricting.

Depending on where the recombination takes place, two main sets of recombination mechanisms can be distinguished - bulk and surface recombination. Moreover, the characteristics of the material define the dominant recombination mechanism. Main recombination mechanisms in solar cells are radiative, Auger and Shockley-Read-Hall recombination.

### Recombination mechanisms

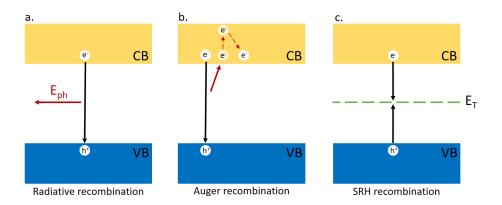

The radiative recombination process, illustrated in Figure 2.3a, involves a band-to-band electron-hole recombination where an electron directly moves back to valance band and recombines with a hole [31], [30]. During this process, a photon with an energy close to  $E_G$  is released. The radiative recombination is a dominant mechanism in direct bandgap materials. As c-Si is an indirect bandgap material, a more significant recombination mechanism is Auger recombination.

The Auger recombination is a recombination mechanism that involves three particles (Figure 2.3b) [32]. In the Auger recombination process, the energy released during electron-hole recombination is transferred to the third carrier that can be either an electron or a hole. The third particle is then excited to higher energy levels, before returning to the edge of a conduction (or valence) band and releasing thermal energy. Recombination rate of the Auger recombination is dependant on doping concentration and at high doping levels it becomes more significant.

In the Shockley-Read-Hall (SRH) recombination process, recombination of electrons and holes is supported by an impurity atom or lattice defect [33], [34]. Impurities and defects introduce allowed energy level ( $E_T$ ) within the band gap. An electron and a hole can be trapped at the same defect state where they recombine as shown in Figure 2.3c. Recombination rate is dependent on the location of the defects. In case the defect is located close to the valence or conduction band edge, the probability of recombination is lower. Namely, in case of the defect state close to the conduction band, the electron has a higher probability to move to the conduction band than to recombine with the hole that has to move from the valence band to the defect state. On the other hand, in case of the midgap defect state the recombination is more likely to happen making the SRH recombination more effective.

Figure 2.3: Schematic representation of (a) radiative, (b) Auger and (c) SRH recombination mechanisms [3].

The recombination mechanisms described above belong to bulk recombination mechanisms taking place in the bulk of a semiconductor. However, apart from the bulk recombination, the surface recombination can occur in semiconductor devices and, in low-defect semiconductors, it can be the dominant recombination mechanism [3]. Due to abrupt end of silicon crystal lattice and the breaking of covalent bonds, unpaired electrons are present at the silicon surface. The unpaired electrons are referred to as dangling bonds and they represent a surface defect which induces surface SRH recombination at high rate.

### Effective minority carrier lifetime

Effective minority carrier lifetime ( $\tau_{\rm eff}$ ) is described as the average time before minority carriers recombine with the corresponding majority carriers in a material [3].  $\tau_{\rm eff}$  is commonly used to make an

estimate of the upper limit of  $V_{\rm OC}$  of solar cells. The above mentioned recombination mechanisms influence the  $\tau_{\rm eff}$  as shown in Equation 2.1.

$$\frac{1}{\tau_{eff}} = \frac{1}{\tau_{rad}} + \frac{1}{\tau_{Auger}} + \frac{1}{\tau_{SRH}} + \frac{1}{\tau_{surf}}$$

(2.1)

In the Equation 2.1,  $\tau_{\rm rad}$  is the lifetime due to the radiative recombination,  $\tau_{\rm Auger}$  is that due to the Auger recombination,  $\tau_{\rm SRH}$  is the lifetime due to the SRH recombination and  $\tau_{\rm surf}$  is the lifetime due to the surface recombination.

In the case of the high-quality Float Zone c-Si wafers that are used in this project, the recombination occurs mainly at the wafer surface and Equation 2.1 can be simplified to Equation 2.2.

$$\tau_{eff} \approx \tau_{surf}$$

(2.2)

The surface recombination can be reduced by saturating dangling bonds on the wafer surface [35]. This process is referred to as chemical passivation. As surface recombination plays a crucial role in determining the effective lifetime of solar cells and, therefore, the final performance of the fabricated devices, it is important to ensure good quality of surface passivation. During the work on this project and in order to ensure good performance of the final devices, the effective lifetime was followed throughout the process using photoconducance decay measurements as explained in Section 3.4.2.

### Passivation mechanisms

The passivation quality is essential in the production of high-performance solar cells. Typically, two types of passivation mechanisms can be employed in solar cells - chemical and field-effect passivation [36], [37].

As mentioned above, chemical passivation mechanisms are introduced on the surface of the silicon wafer in order to saturate dangling bonds and consequently reduce the defect density at the interface. Wet chemical treatments are commonly used to minimize the defect density at the c-Si surface by removing the native oxide with an HF dip and forming bonds between the surface Si atoms and hydrogen [38]. The complete wafer cleaning and wet etching procedure used to minimize dangling bonds at c-Si surface as suggested by [39] are presented in Section 3.1.2. On the other hand, intrinsic hydrogenated amorphous silicon ((i)a-Si:H) can be deposited on the c-Si surface allowing excellent surface passivation as the dangling bonds are saturated [40], [41]. By deposition of (i)a-Si:H, high  $V_{OC}$  values can be achieved.

The field-effect passivation is a passivation mechanism that reduces the surface recombination by inducing a band bending at c-Si surface. As a consequence, the built-in electric field repels one type of charge carrier from the surface reducing the probability of recombination and improving the effective carrier lifetime. Dielectric materials such as SiO<sub>2</sub> can be introduced on the silicon surface to induce the field effect [42] but introducing non-conductive layers increases the design complexity. The field effect can also be achieved by introducing an optimized doped Si-based layer, that is introduced as front or back surface field or emitter in heterojunction devices [43].

In this research, both chemical and field-effect passivation methods are used in order to achieve low defect density at the absorber surface and improve selective collection of charge carriers. Wet chemical processing steps and deposition methods used for this purpose are explained in Chapter 3.

# 2.2. Working principle of silicon heterojunction solar cells

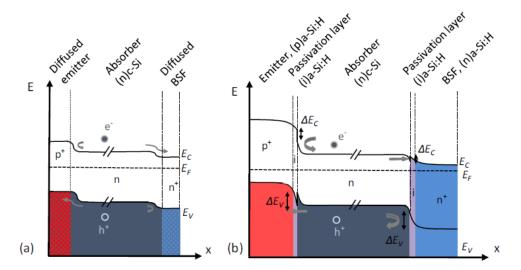

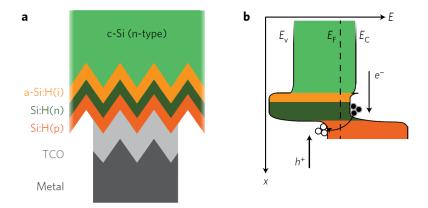

A heterojunction is a junction of two different semiconductors [30]. As the materials forming a heterojunction are characterized by different band gaps, work functions, and electron affinities, the band diagrams are more complex compared to that of a homojunction that features the same semiconductor material with different doping types (Figure 2.4a [44]). In the case of heterojunctions, as the Fermi level has to remain constant and the vacuum level continuous throughout the sample in the dark at thermal equilibrium, discontinuities at valence and conduction band are formed [30]. These discontinuities can represent a barrier for electrons and holes. In the case of SHJ solar cells, the heterojunction is formed between two different silicon-based materials [3]. SHJ is formed by depositing a-Si:H film on both sides

of the c-Si absorber. In Figure 2.4b [44] a schematic band diagram of SHJ solar cell with n-type c-Si absorber up to TCO layer is shown. The band bending at c-Si/a-Si:H interfaces represents barriers for electrons and holes and it is induced by different band gaps of c-Si ( $E_G = 1.12 \text{ eV}$ ) and a-Si:H ( $E_G = 1.6 - 1.8 \text{ eV}$ ).

Figure 2.4: Band diagram of a (a) homojunction and (b) SHJ based on n-type c-Si absorber.  $E_C$  denotes the conduction band edge,  $E_V$  the valence band edge,  $E_F$  the Fermi level,  $e^-$  electrons, and  $h^+$  holes. Adapted from [44].

While (i)a-Si:H layer ensures low defect density on the absorber surface, band bending induced by doped a-Si:H layers has a beneficial influence on charge carrier transport across the c-Si/a-Si:H interface. Together, good quality of chemical and field-effect passivation leads to a significant reduction in recombination losses compared to homojunction devices and high  $V_{\rm OC}$  values can be reached [13].

In the case of SHJ solar cells, transparent conductive oxide (TCO) is deposited over doped Si layers on the front and rear side of the device prior to the deposition of metal contacts. As the doped a-Si:H layers have insufficient lateral conductivity, TCO is deposited to ensure lateral transport of charge carriers to the metal contacts at the front side of FBC devices where metal contacts are separated. In that case, TCO can be additionally optically optimized to serve as an anti-reflection coating (ARC). In the case of rear side TCO, it can prevent spiking during metal contact formation and maximize internal reflectance [16].

# 2.2.1. Hydrogenated amorphous silicon

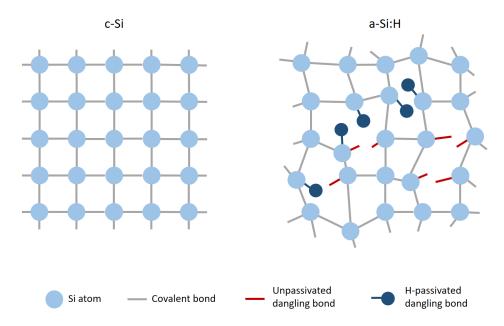

As mentioned above, typical SHJ solar cells consist of c-Si absorber on which intrinsic and doped a-Si:H or nc-Si:H layers are deposited. In c-Si, every Si atom is tetrahedrally bonded to four other Si atoms [3]. As such structure is repeated throughout the material in long-range order, a homogeneous, highly structured crystal lattice with low number of defects is formed as shown in Figure 2.5 on the left. On the other hand, in the case of a-Si, the tetrahedral structure is only present in the short-range order as the bond between Si atoms is slightly distorted (Figure 2.5 right). In this distorted structure, some of the electrons cannot form bonds with surrounding Si atoms. The unbound electrons are known as dangling bonds [3]. Dangling bonds represent recombination centers allowing high rate of SRH recombination both in the bulk material, as well as at the a-Si/c-Si interface. In order to decrease the recombination rate caused by dangling bonds, hydrogen is incorporated during the deposition of a-Si as a way of passivating the dangling bonds. This way hydrogenated amorphous silicon (a-Si:H) is formed, as shown in Figure 2.5 on the right.

Figure 2.5: Schematic representation of crystalline silicon (left) and amorphous silicon (right) crystal lattice.

### Growth mechanism of a-Si:H

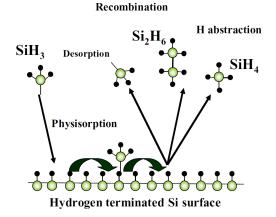

a-Si:H is deposited using plasma enhanced chemical vapor deposition (PECVD) [45], which will be explained in detail in Section 3.2.1. For deposition of a-Si:H, silane (SiH<sub>4</sub>) and H<sub>2</sub> precursor gases are used. As the SiH<sub>4</sub> collide with energized electrons in plasma, a series of reactions occurs producing different neutral radicals (SiH<sub>3</sub>, SiH<sub>2</sub>, SiH, Si, H). In the case of low power density ( $< 10 \text{ W/cm}^2$ ) and low pressure (< 10 Pa) conditions, SiH<sub>3</sub> radical, the main precursor for formation of low defect density a-Si:H, is the most abundant species within the mixture of products generated in plasma [46], [47], [48], [49]. Following the generation of radicals, transport and diffusion of radicals to the substrate occur. Lastly, the radicals react at the surface of the substrate forming a-Si:H layer.

A schematic representation of interaction of  $SiH_3$  with hydrogen-terminated Si surface is presented in Figure 2.6 [45]. As the  $SiH_3$  diffuses through plasma sheath towards the substrate surface, it can be weakly absorbed (physisorbed) at Si:H surface due to the low deposition temperature (< 200°C) where thermal energy is insufficient to break Si-H bonds. Once physisorbed,  $SiH_3$  diffuses along the substrate surface and different processes occur during the diffusion. Processes such as desorption as  $SiH_3$ , recombination with another  $SiH_3$ , abstraction of H atom or formation chemical bonds with dangling bonds at Si surface can occur, where the last leads to a-Si:H layer growth on the surface of the substrate.

Figure 2.6: Schematic representation of a-Si:H growth on hydrogen-terminated Si surface. Adapted from [45].

As passivation of dangling bonds is not entirely accomplished by the above-explained mechanism,  $H_2$  is included as a precursor gas during a-Si:H deposition. To avoid epitaxial growth of a-Si:H and ensure high quality of deposited layer, the ratio between  $H_2$  and Si $H_4$  (hydrogen dilution ratio) [50] and deposition temperature [51] have to be carefully selected. Post-deposition hydrogenation step [41] or deposition of multiple layers [40] can be included to secure sufficient hydrogen content and avoid epitaxial growth, achieving better surface passivation. During this research, (i)a-Si:H layer is deposited in two steps, both at substrate temperature of 160°C. Firstly, (i)a-Si:H from pure Si $H_4$  with no additional  $H_2$  is deposited in order to prevent epitaxial growth, followed by the deposition of the second (i)a-Si:H layer with Si $H_4$  and  $H_2$ . In the case of <111> textured surface, an additional hydrogen plasma treatment step is introduced following the deposition of (i)a-Si:H bilayer to include additional hydrogen in the layer.

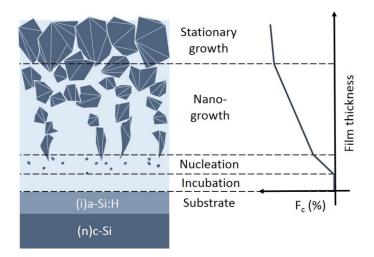

# 2.2.2. Hydrogenated nanocrystalline silicon

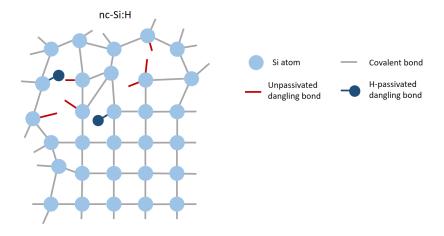

As an alternative to a-Si:H doped layers, doped hydrogenated nanocrystalline silicon (nc-Si:H) layers can be deposited over (i)a-Si:H [3]. As shown in Figure 2.7, nc-Si:H is a material consisting of a crystalline phase embedded in the amorphous material. Just like for a-Si:H, hydrogen is used to passivate dangling bonds within the nc-Si:H bulk and ensure a lower SRH recombination rate. Moreover, hydrogen content plays an important part in the growth and quality of nc-Si:H material [52], as higher hydrogen content leads to a higher fraction of the crystalline phase. The growth of nc-Si:H is also highly dependent on the substrate, total thickness of the deposited layer, and inclusion of doping precursor gases for formation (p)nc-Si:H or (n)nc-Si:H [52].

${\bf Figure~2.7:~Schematic~representation~of~nanocrystalline~silicon.}$