#### Xinyu Yang

# Ultrasound Transmitter for Non-invasive Vagus Nerve Stimulation

# Ultrasound Transmitter for Non-invasive Vagus Nerve Stimulation

Ву

#### Xinyu Yang

in fulfilment of the requirements for the degree of

#### **Master of Science**

in Electrical Engineering at the Delft University of Technology

Student ID: 4873092

Supervisor: Dr. Tiago Costa, Prof. dr. ir. Wouter Serdijn

Thesis committee: Prof. dr. ir. Wouter Serdijn, Bioelectronics, TU Delft

Prof. dr. ir. Ronald Dekker, ECTM, TU Delft

Dr. Tiago Costa, Bioelectronics, TU Delft

An electronic version of this thesis is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

## Content

| List of Figures                                     | iii  |

|-----------------------------------------------------|------|

| List of Tables                                      | vi   |

| Abstract                                            | vii  |

| Acknowledgements                                    | viii |

| Chapter 1 Introduction                              | 1    |

| 1.1 Vagus nerve                                     | 1    |

| 1.2 Vagus nerve stimulation                         | 2    |

| 1.2.1 Electrical VNS                                | 2    |

| 1.2.2 Ultrasound VNS                                | 3    |

| 1.3 Transmitter and beamforming                     | 6    |

| 1.4 Prior art and Thesis objective                  | 8    |

| 1.5 Thesis organization                             | 9    |

| Chapter 2 Stimulation model and Matlab simulation   | 11   |

| 2.1 Stimulation model                               | 11   |

| 2.1.1 Variables under simulation                    | 12   |

| 2.1.2 Simulation setup                              | 15   |

| 2.2 Simulation results                              | 16   |

| 2.2.1 Output figures on the sensing plane (f, A, N) | 16   |

| 2.2.2 Detailed analysis of focusing performance     | 18   |

| 2.2.3 Time delay extraction                         | 21   |

| 2.3 Sparsity                                        | 22   |

| Chapter 3 Coarse delay generation                   | 25   |

| 3.1 Delay/phase map arrangement                     | 25   |

| 3.2 Fundamentals of DLL                             | 26   |

| 3.2.1 Architecture and operating principle          | 26   |

| 3.2.2 Non-idealities of DLL                         | 28   |

| 3.3 Phase detector                                  | 30   |

| 3.3.1 Start-controlled phase detector               | 32   |

| 3.4 Charge pump                                     | 36   |

| 3.4.1 Non-idealities in the Charge pump             | 36   |

| 3.4.2 Design of Charge pump circuit                 | 38   |

| 3.5 Voltage-controlled delay line                   | 42   |

| 3.6 DLL performance                              | 45 |

|--------------------------------------------------|----|

| Chapter 4 Fine delay generation                  | 49 |

| 4.1 Fine delay generation for the VNS            | 49 |

| 4.2 Phase interpolator                           | 50 |

| 4.3 Thermometer Decoder                          | 52 |

| 4.4 Performance                                  | 53 |

| Chapter 5 Pulse wave mode function Design        | 56 |

| 5.1 TX pulse wave mode using digital circuit     | 56 |

| 5.2 Continuous wave triggered output             | 57 |

| 5.2.1 Direct approach                            | 57 |

| 5.2.2 Double DFF approach                        | 59 |

| 5.3 Counter design                               | 60 |

| 5.4 Comparator design                            | 61 |

| 5.5 MUX design                                   | 65 |

| 5.6 Register design                              | 66 |

| 5.7 Performance                                  | 67 |

| Chapter 6 Transducer interface                   | 69 |

| 6.1 Devices required in the transducer interface | 69 |

| 6.2 Level shifter design                         | 71 |

| 6.3 High voltage driver                          | 72 |

| 6.4 Performance                                  | 74 |

| Chapter 7 Conclusions                            | 77 |

| 7.1 The whole design of the transmitter          | 77 |

| 7.2 Thesis contribution                          | 77 |

| 7.3 Future work                                  | 78 |

| Bibliography                                     | 79 |

# List of Figures

| Figure 1.1 Vagus Nerve in Parasympathetic Nerve System [1] and related function[2    | ]1                     |

|--------------------------------------------------------------------------------------|------------------------|

| Figure 1.2 Electrical VNS[9]                                                         | 2                      |

| Figure 1.3 non-thermal modulation of neural activity by LIFU[15]                     | 4                      |

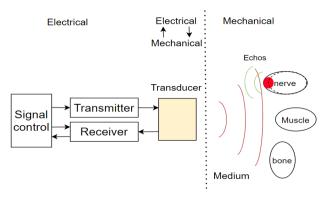

| Figure 1.4 structure of an ultrasound system                                         | 4                      |

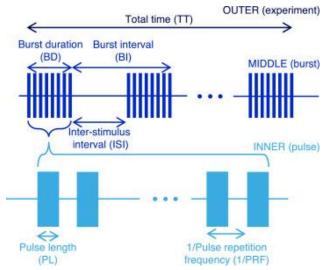

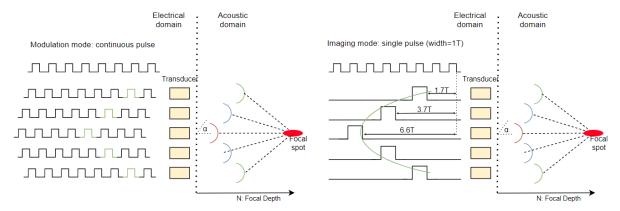

| Figure 1.5 signal timing properties related to exposure time[16]                     | 5                      |

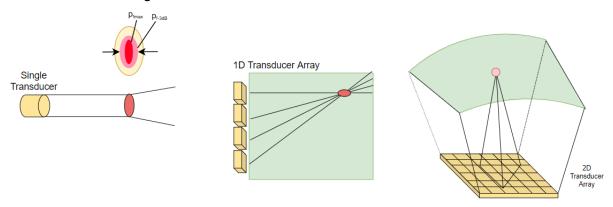

| Figure 1.6 Focusing and tuning area for different transducer structure: single, 1D a | array, 2D              |

| array (each element in the 2D array is separated like in 1D array)                   | 6                      |

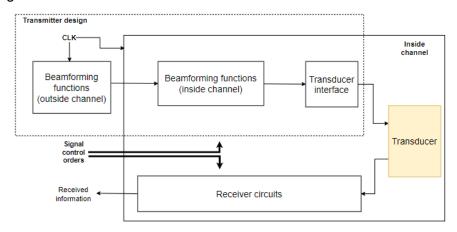

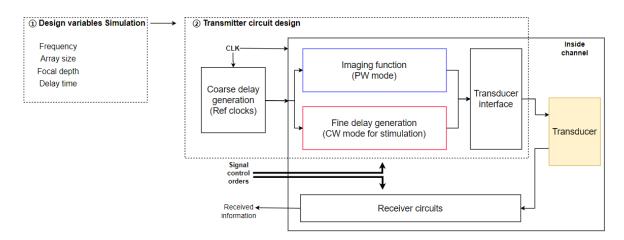

| Figure 1.7 circuits implementation in the ultrasound VNS system                      | 7                      |

| Figure 1.8 beamforming of the transmitter in a 2D array                              | 7                      |

| Figure 1.9 proposed device and the general specifications                            | 9                      |

| Figure 1.10 Transmitter design blocks                                                | 9                      |

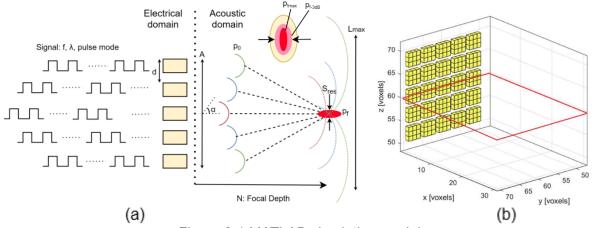

| Figure 2.1 MATLAB simulation model                                                   | 11                     |

| Figure 2.2 Focal shift model [20]                                                    | 14                     |

| Figure 2.3 Quantization (a)before quantization (b)after quaantization                | 15                     |

| Figure 2.4 Output figures of the sensing plane                                       | 18                     |

| Figure 2.5 Performance variations                                                    | 19                     |

| Figure 2.6 delay time before and after quantization (a)before quantization           | (b)after               |

| quantization (c)zoomed-in before quantization (d) zoomed-in after quantization       | 21                     |

| Figure 2.7 Output figures of the sparsity simulation                                 | 23                     |

| Figure 2.8 Deviation of the performance factors due to sparsity                      | 24                     |

| Figure 2.9 Modulation of sparsity on focal pressure                                  | 24                     |

| Figure 3.1 Phase map of delay generation                                             | 25                     |

| Figure 3.2 The block diagram of DLL                                                  | 26                     |

| Figure 3.3 Loop dynamics of analog DLL[23]                                           | 27                     |

| Figure 3.4 Edge-to-edge jitter                                                       | 28                     |

| Figure 3.5 Output of PD under different phase difference                             | 29                     |

| Figure 3.6 Current sources mismatch of CP                                            | 30                     |

| Figure 3.7 Characteristic curve of PD                                                | 31                     |

| Figure 3.8 Phase locking diagram                                                     | 31                     |

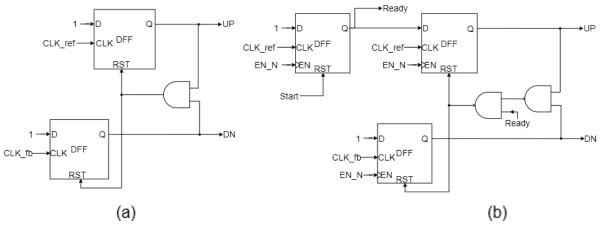

| Figure 3.9 Phase detector architecture                                               | (a)                    |

| Conventional edge-triggered PD (b) Start-controlled PD[24]                           | 32                     |

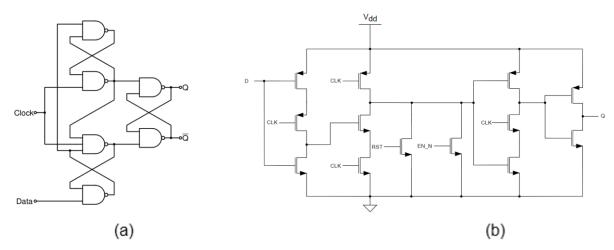

| Figure 3.10 DFF topologies (a) Conventional digital DFF (b) TSPC DFF[24]             | 32                     |

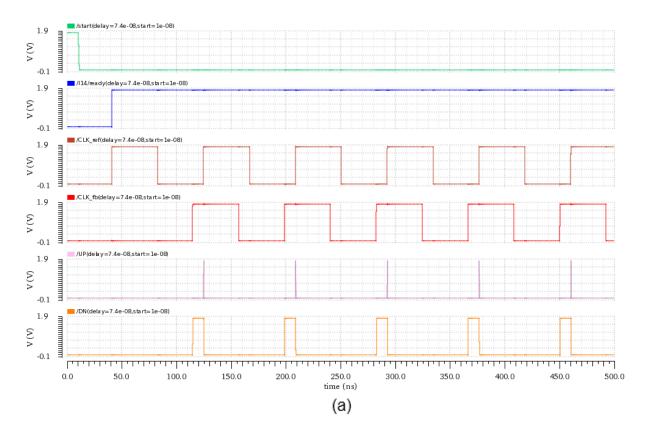

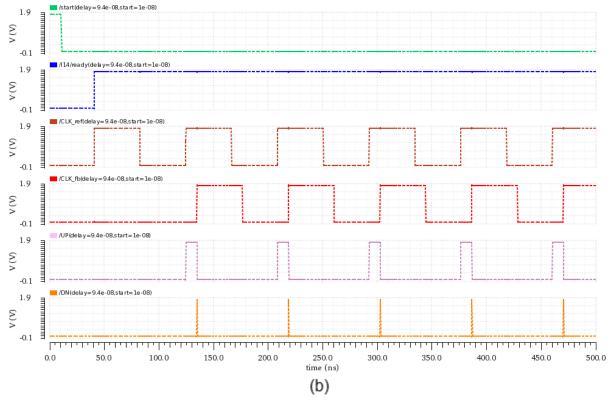

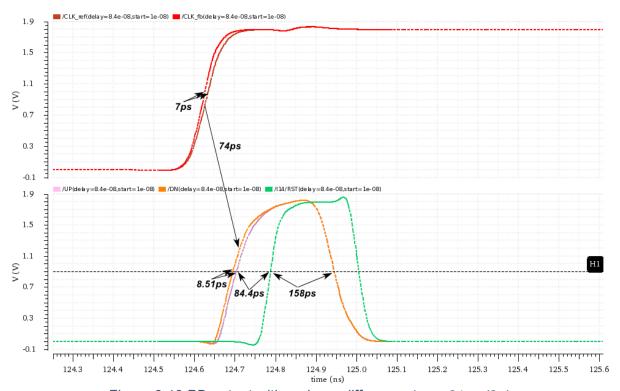

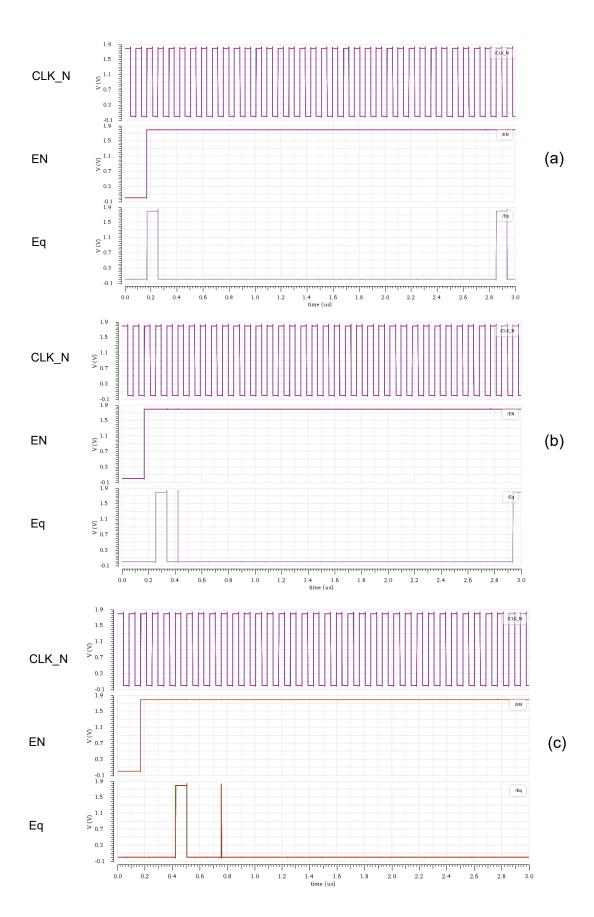

| Figure 3.11 PD output simulation                                                     | (a) $\Delta \varphi =$ |

| $74ns~(1.76\pi)~\text{CLK\_fb}$ ahead of the expected position                       | (b)                    |

| $\Delta \varphi = 94 ns~(2.24\pi)$ CLK_fb later than the expected position           | 34                     |

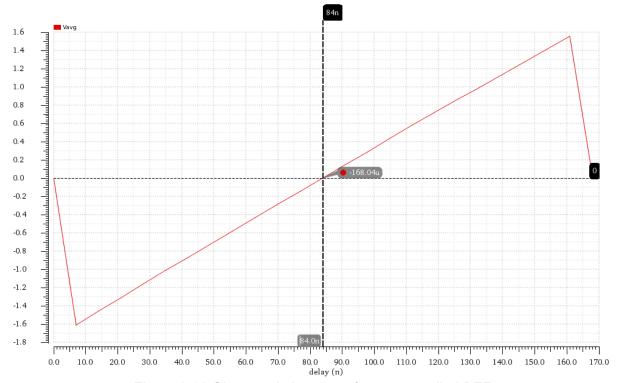

| Figure 3.12 Characteristic curve of start-controlled DFF                             | 34                     |

| Figure 3.13 PD output with a phase difference $\Delta \varphi = 84 ns~(2\pi)$        | 35                     |

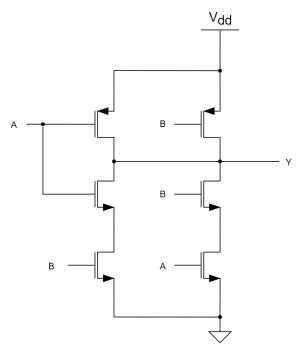

| Figure 3.14 Balanced-delay NAND gate                                                 | 36                     |

| Figure 3.15 Charge injection and Clock feed-through                                  | 37                     |

| Figure 3.16 Charge sharing[25]                                                       | 37                     |

| Figure 3.17 Concept of the charge pump in this design[26]                            | 38                     |

| Figure 3.18 Charge pump in this design                                               | 39                     |

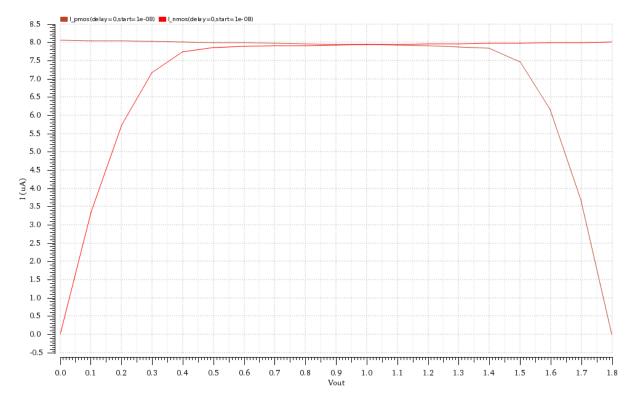

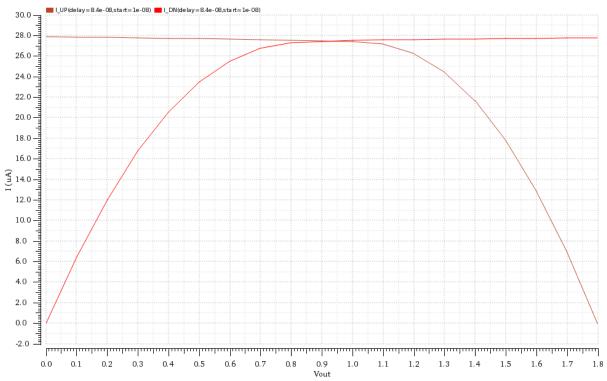

| Figure 3.19 CP simulation result, $\Delta \varphi = 0$ to $4\pi$                               | 40       |

|------------------------------------------------------------------------------------------------|----------|

| Figure 3.20 Simulation of <i>Istand</i>                                                        | 41       |

| Figure 3.21 Simulation of <i>Istand</i> + <i>IUP/DN</i>                                        | 41       |

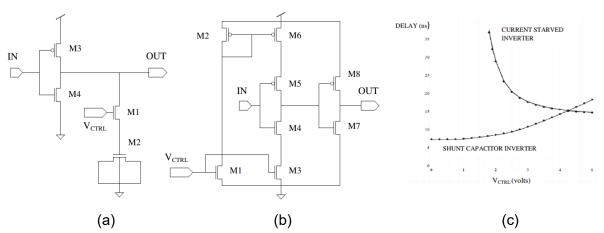

| Figure 3.22 Typical delay elements and their delay range[23]                                   | (a)      |

| Shunt capacitor (b) Current-starved (c) delay range                                            | 42       |

| Figure 3.23 Delay element in this work                                                         | 43       |

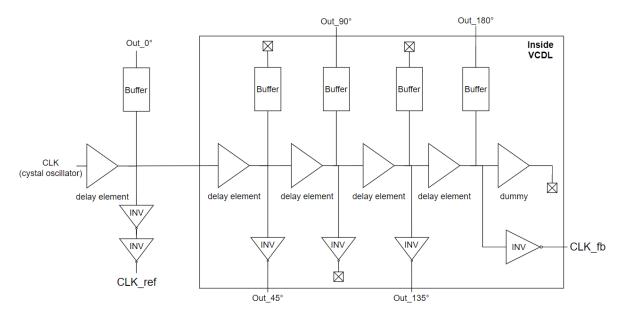

| Figure 3.24 The VCDL structure                                                                 | 43       |

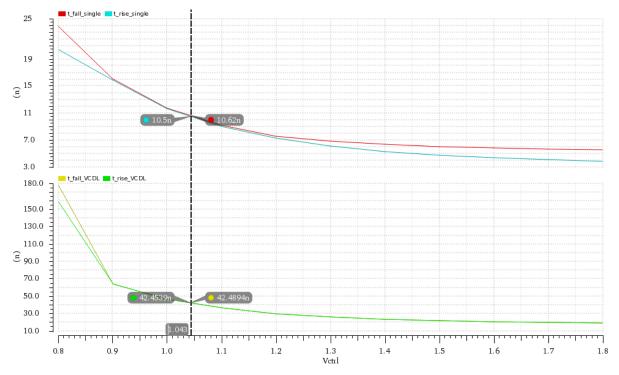

| Figure 3.25 Delay time of the single delay stage and the whole VCDL                            | 44       |

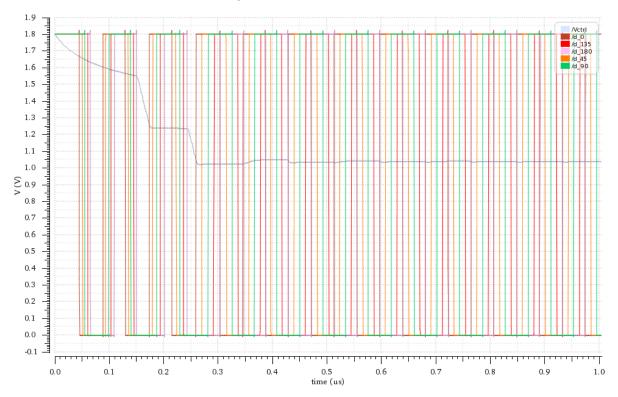

| Figure 3.26 The whole architecture of DLL                                                      | 45       |

| Figure 3.27 Operation of DLL                                                                   | 45       |

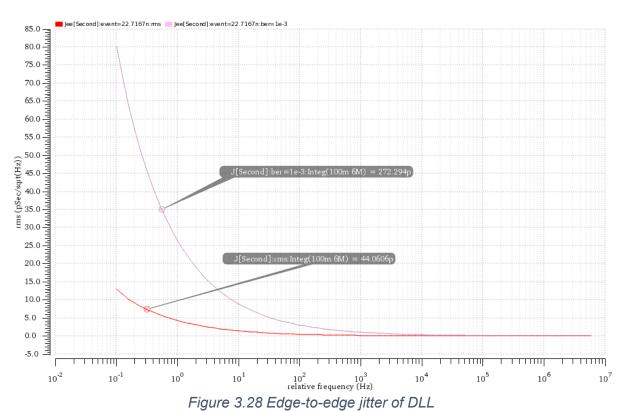

| Figure 3.28 Edge-to-edge jitter of DLL                                                         | 46       |

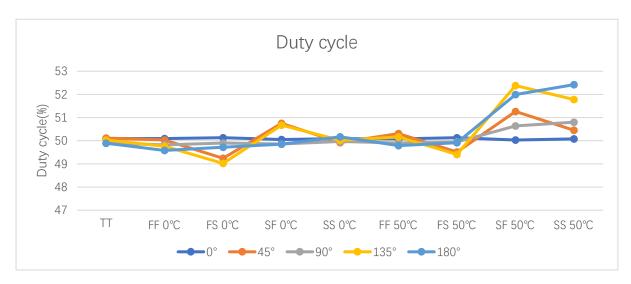

| Figure 3.29 Duty-cycle variation                                                               | 47       |

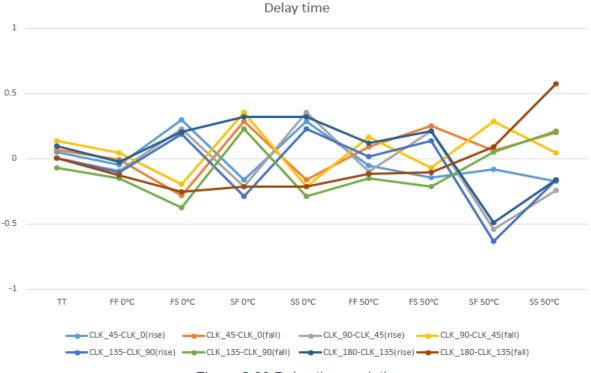

| Figure 3.30 Delay time variation                                                               | 47       |

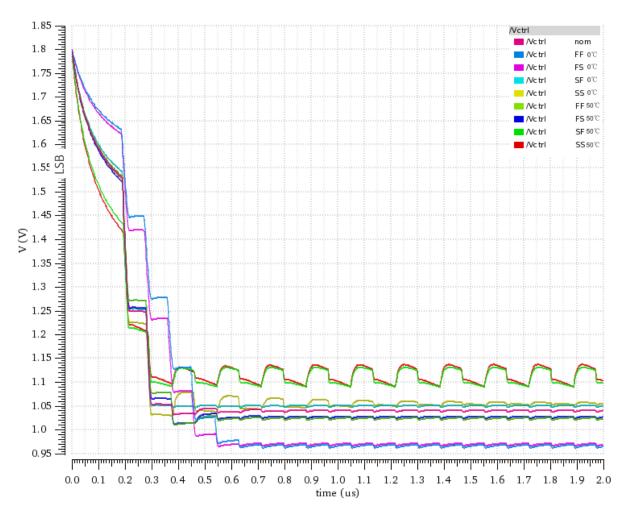

| Figure 3.31 Control voltage under all corners                                                  | 48       |

| Figure 4.1 Block diagram of the fine delay generation section                                  | 49       |

| Figure 4.2 Typical current weighted PI and the expected output voltage[27]                     | 50       |

| Figure 4.3 PI in this work                                                                     | 51       |

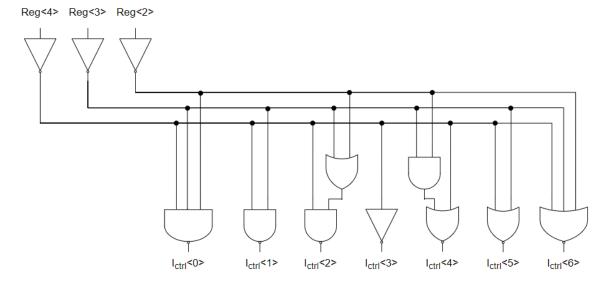

| Figure 4.4 3-to-7 Thermometer decoder                                                          | 52       |

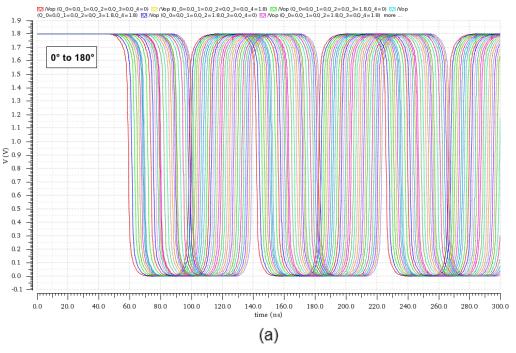

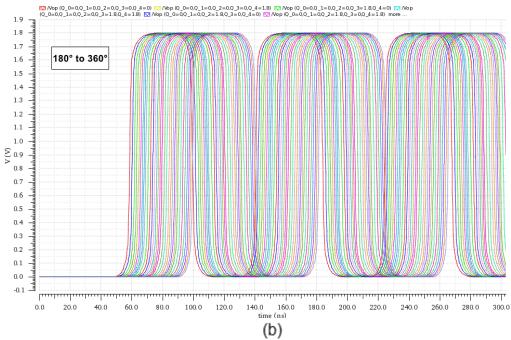

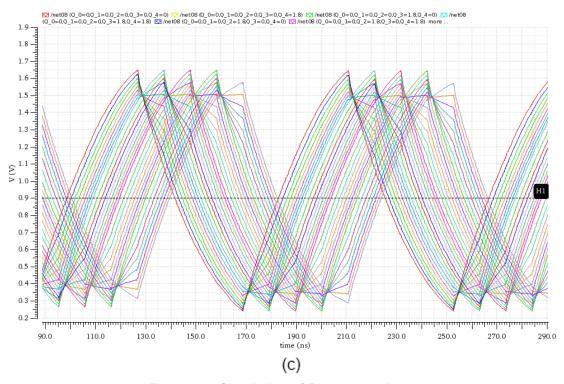

| Figure 4.5 Simulation of PI output voltage                                                     | (a)      |

| Output voltage of PI from 0° to 180° (b) Output voltage of PI from 180° to 360°                | (c)      |

| Output voltage of PI before the inverter                                                       | 54       |

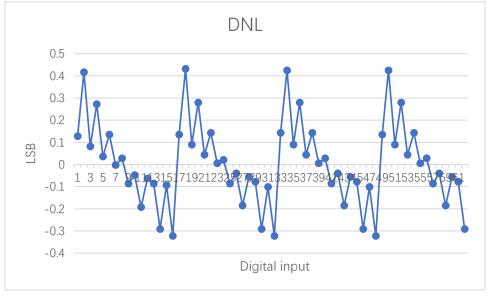

| Figure 4.6 DNL of the PI                                                                       | 54       |

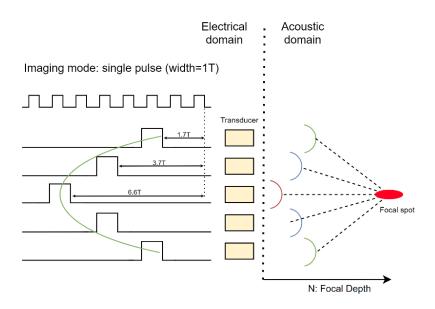

| Figure 5.1 Pulsed-wave for ultrasound imaging                                                  | 56       |

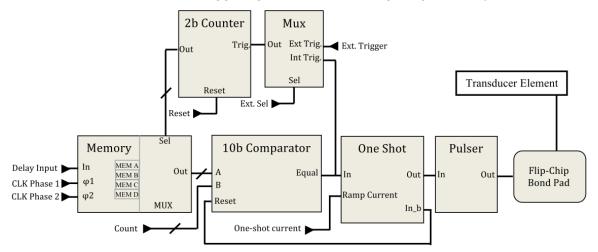

| Figure 5.2 Digital Tx circuit for ultrasound imaging[13]                                       | 57       |

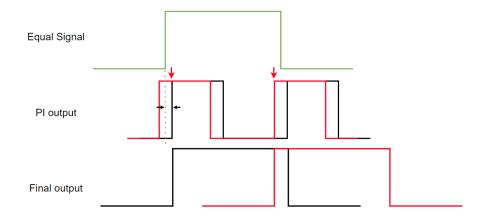

| Figure 5.3 PI output trigger Pulsed-wave                                                       | 58       |

| Figure 5.4 Triggering time for PI output and Equal signal                                      | 58       |

| Figure 5.5 the double DFF approach                                                             | 59       |

| Figure 5.6 Timing diagram of the double DFF approach                                           | 59       |

| Figure 5.7 The 5-bit asynchronous counter                                                      | 60       |

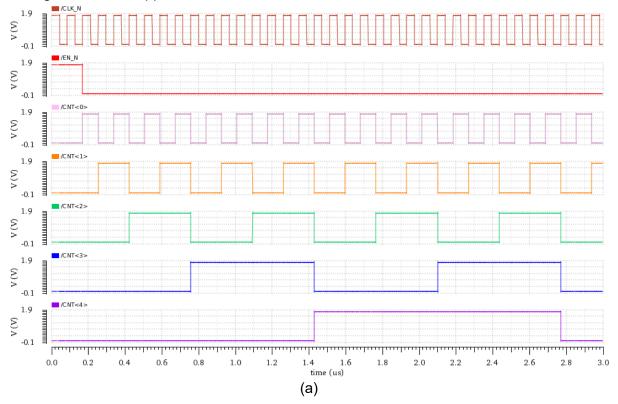

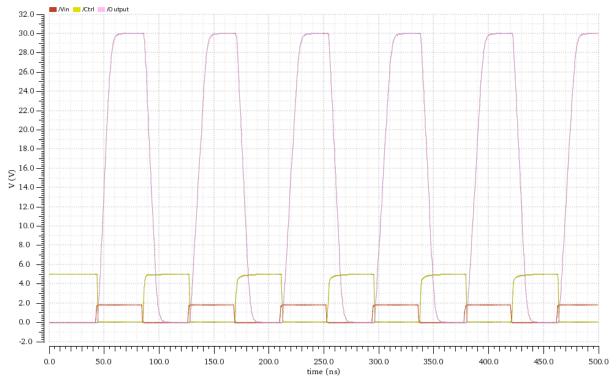

| Figure 5.8 The transient simulation of the counter                                             | (a)TT    |

| corner at 27°C (h) All corners at 0°C and 50°C                                                 | 61       |

| corner at $27^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | 01       |

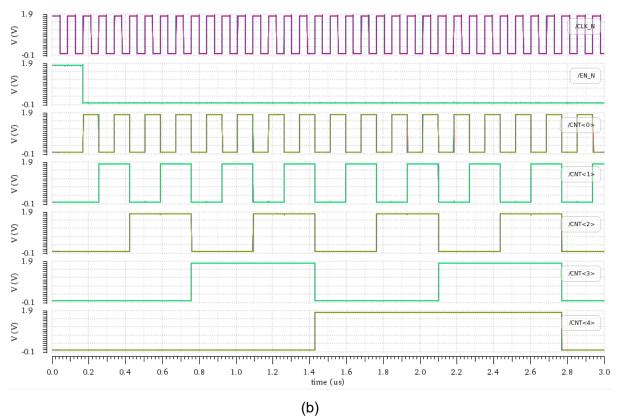

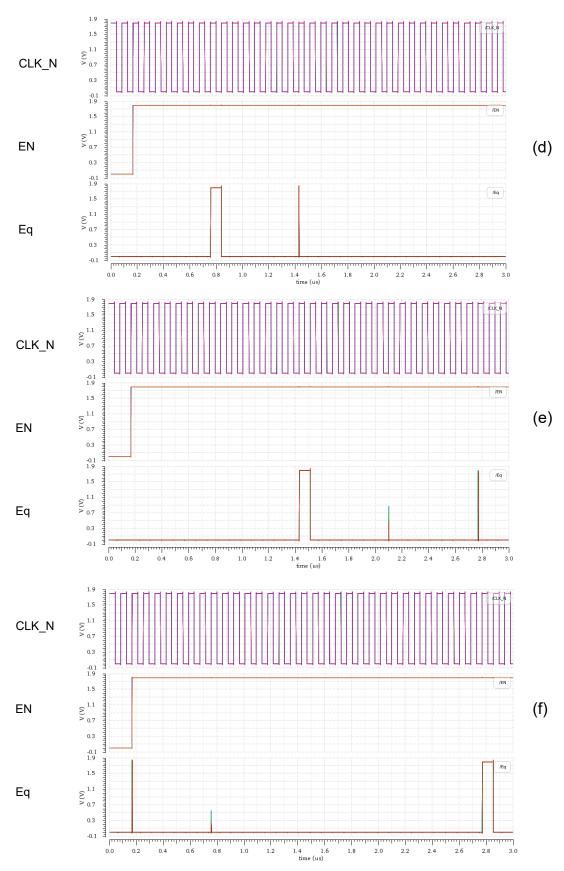

| Figure 5.9 Comparator topology (a)Three stages (b)large fan-in                                 | 61       |

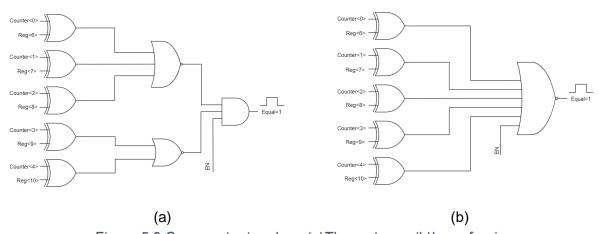

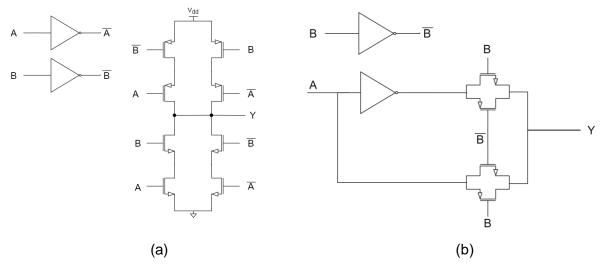

| Figure 5.10 XOR gate (a)CMOS logic (b)Transmission gate                                        | 62       |

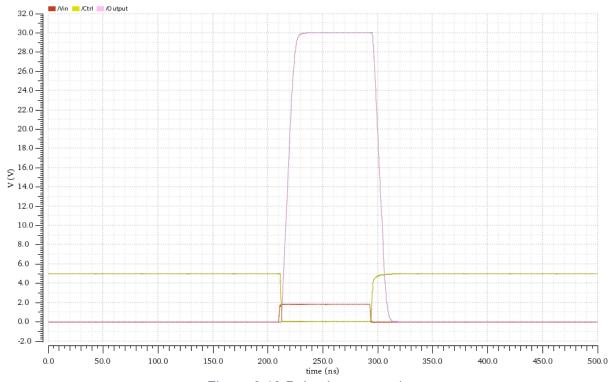

| Figure 5.11 Comparator simulation results in different corners and temp                        | (a)00001 |

| (b)00010 (c)00100 (d)01000 (e)10000 (f)00000                                                   | 64       |

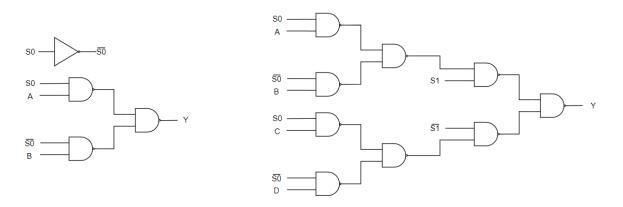

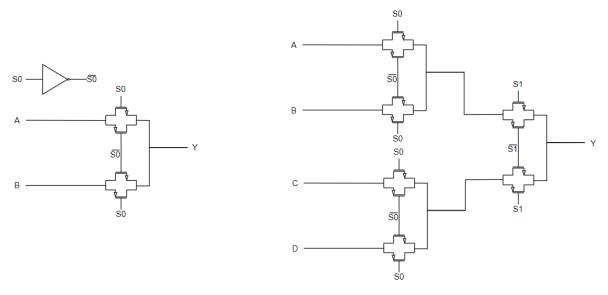

| Figure 5.12 MUX using CMOS logic gate                                                          | 65       |

| Figure 5.13 MUX using Transmission gate                                                        | 65       |

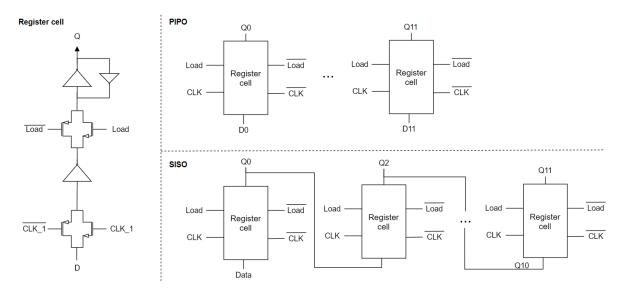

| Figure 5.14 Register cell and two operation modes                                              | 66       |

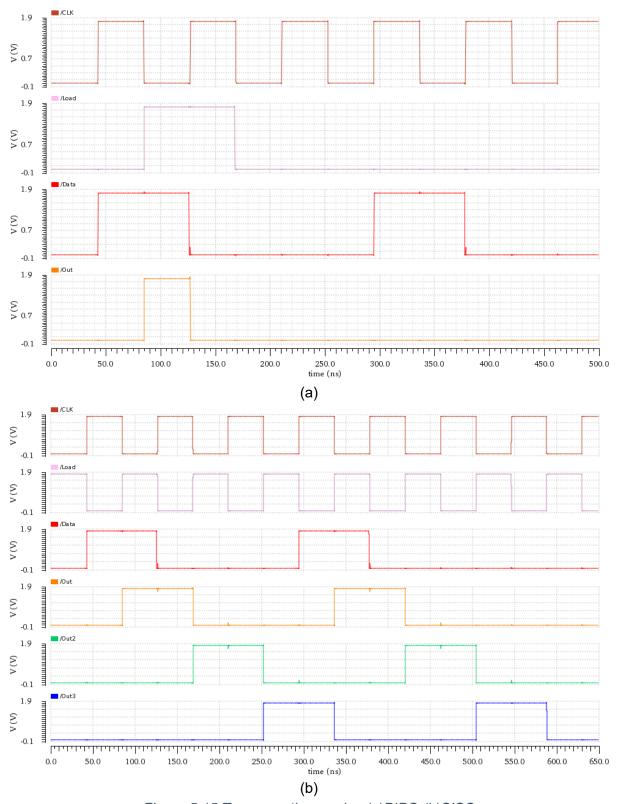

| Figure 5.15 Two operation modes (a)PIPO (b)SISO                                                | 67       |

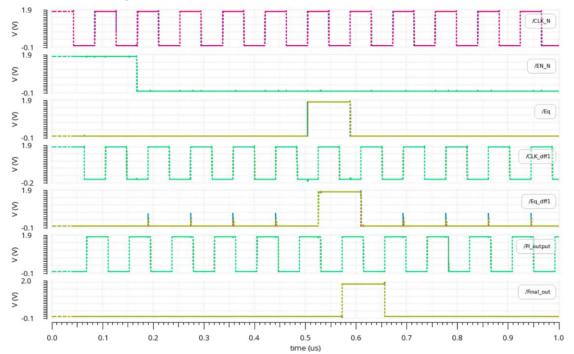

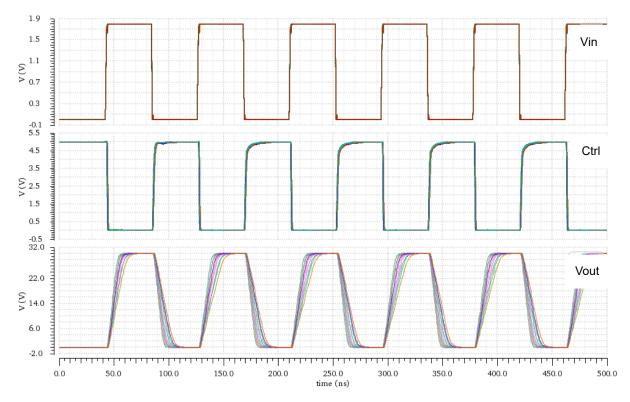

| Figure 5.16 All corners simulation for the imaging function                                    | 68       |

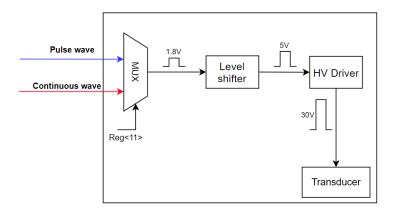

| Figure 6.1 block diagram of the transducer interface                                           |          |

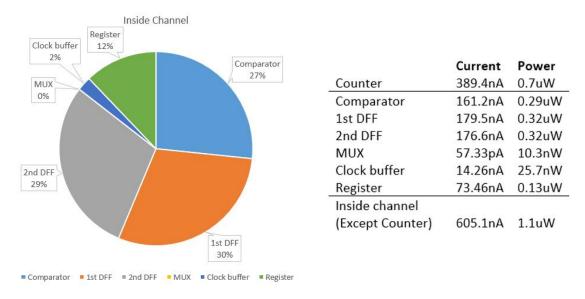

| Figure 6.2 1.8V, 5V, and 36V NMOS                                                              | 69       |

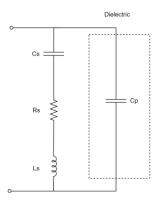

| Figure 6.3 Electrical model for piezoelectric transducer[32]                                   | 70       |

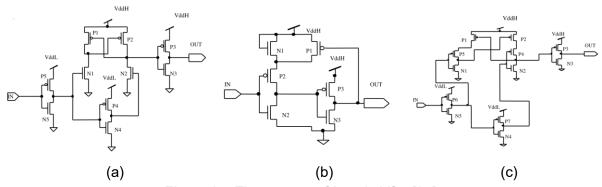

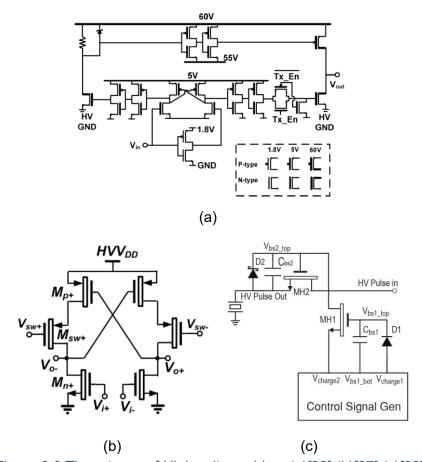

| Figure 6.4 Three types of Level shifter[35]:                          | (a)Conventional |

|-----------------------------------------------------------------------|-----------------|

| (b)Single supply (c)Contention mitigated                              | 71              |

| Figure 6.5 P2 current curve in single supply topology                 | 72              |

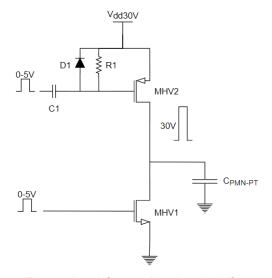

| Figure 6.6 Three types of High voltage driver (a)[28] (b)[38] (c)[39] | 73              |

| Figure 6.7 AC coupling level shifter                                  | 73              |

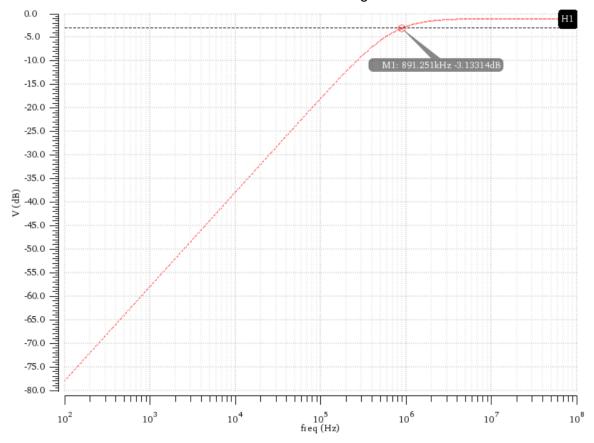

| Figure 6.8 RC high pass filter ac simulation                          | 74              |

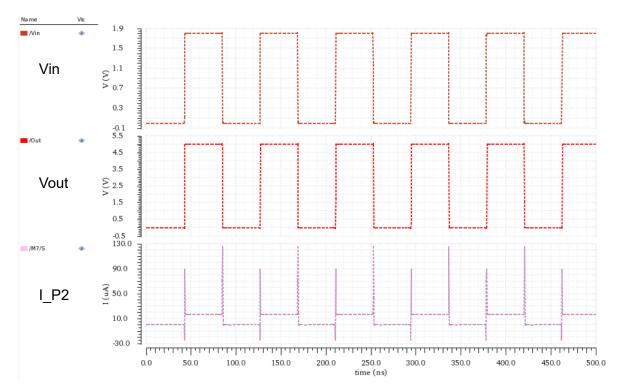

| Figure 6.9 Continuous wave mode                                       | 75              |

| Figure 6.10 Pulsed-wave mode                                          | 75              |

| Figure 6.11 All corners under 0°C and 50°C for the whole driver       | 76              |

| Figure 7.1 Complete block diagram of the whole design                 | 77              |

## List of Tables

| Table 2.1 Performance before and after quantization                     | 22 |

|-------------------------------------------------------------------------|----|

| Table 2.2 Values for the simulated variables                            | 22 |

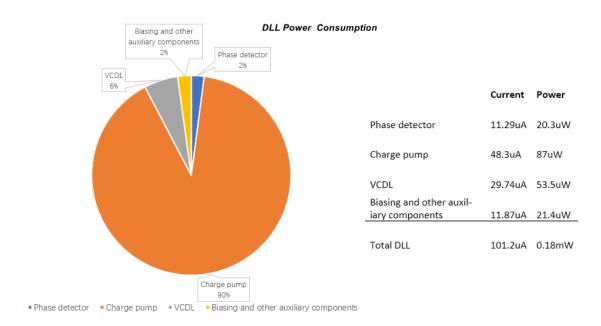

| Table 3.1 Power consumption of DLL                                      | 46 |

| Table 4.1 Control bits of current sources and related phase variation   | 52 |

| Table 4.2 Power consumption of the fine delay generation block          | 55 |

| Table 5.1 Power consumption of the devices in the pulsed-wave path      | 68 |

| Table 6.1 piezoelectric properties[31]                                  | 70 |

| Table 6.2 Duty cycle of 30V output wave under different conditions      | 74 |

| Table 6.3 Power consumption for each device in the Transducer interface | 76 |

#### Abstract

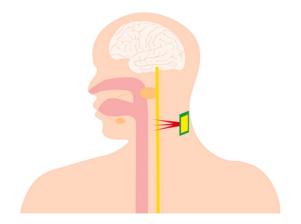

The main objective of this thesis is to design a transmitter channel which is implemented in a 2D phased-array ultrasound neuromodulation system aiming for the vagus nerve stimulation.

The vagus nerve has the widest distribution in the parasympathetic system and it oversees several important bodily functions such as the control of mood, immune response, digestion, and heart rate. The potential of vagus nerve neuromodulation in the medical area is huge with these functions and has been studied for decades. The traditional way of vagus nerve stimulation (VNS) is electrical stimulation which requires surgery to implant the stimulator under the skin. It has been proven that electrical VNS has therapeutic effects on many diseases such as rheumatoid arthritis, refractory epilepsy and depression. However, there are still several limitations to electrical VNS. Inside the vagus nerve, there are several fibers and some unwanted fibers will be stimulated because the spatial resolution of electrical VNS is relatively low. Side-effects including cough, throat pain, voice alteration, and dyspnea are caused due to inadequate spatial resolution. Compared with the electrical approach, focused ultrasound wave could provide a high spatial resolution and does not require any surgery. It has been proven that the ultrasound stimulation could modulate the neuron activity and applications have been conducted in the stimulation for the central and peripheral nervous system, including the vagus nerve. Using a 2-D phased array, the ultrasound VNS system could also tune its focal spot in a 3D space without any mechanical controlling stage, which enables the VNS device to be portable while remaining its precision. The detailed modulation mechanism of the VNS is still under discovery and the ultrasound VNS devices are of great potential with the advantages mentioned above. In an ultrasound VNS system, the transmitter is an essential section which determines the accuracy of spatial resolution and the amplitude of focal pressure. In this work, an ultrasound transmitter channel circuit is designed to be implemented in a 2-D phased array ultrasound VNS system.

**Keywords:** vagus nerve neuromodulation, ultrasound, transmitter, 2-D array

### Acknowledgements

The past two years I have spent at TU Delft was a fantastic journey and an unforgettable memory in my life. During these two years, I have been helped by many people, my respected teachers, my dear classmates and my beloved parents. When my graduation thesis is about to be completed, and when I am about to finish my master program study, I would like to express my gratitude to the mentors, friends, and family members who supported and helped me in these two years.

First of all, I would like to thank Dr. Tiago Costa, who guided my work in my graduation thesis, for his sincere teaching, concern and help. He is my daily supervisor at TU Delft and provided me not only the guidance in the thesis work but also the consultative talk when I was nervous. It would impossible for me to accomplish the entire design in the past year without him.

Secondly, I would like to express my thanks to Prof. dr. ir. Wouter Serdijn, the chairman of the bioelectronics group at TU Delft. With his broad knowledge and experience in the circuit design, he always enlightens me during the monthly meeting.

I also want to thank the members of the bioelectronics group especially members of the ultrasound team. It is lucky to work in such a good team with talented and enthusiastic students. The weekly meeting provides a wonderful space for us to discuss our work and it inspired me a lot in my work.

Finally, I want to thank my parents. They provided me with both mental and financial support in the past two years. Although we could only communicate through the phone when I was in Nederland, their care and smiles are the largest motivation for me. After I went back to China, they kept on encouraging and warming me to help me finish the thesis work. I appreciated a lot and I am quite proud of having them in my life.

#### **Chapter 1 Introduction**

In this chapter, the essential effects and the potential of the vagus nerve neuromodulation will be illustrated first, followed by the introduction of different methods on the vagus nerve stimulation (VNS). After the comparison, the ultrasound VNS appears to be a better approach than the traditional electrical VNS. The possible mechanism and essential parameters of the ultrasound VNS will be explained in details. The transmitter in an ultrasound VNS system is of great importance and its design is the main purpose of this thesis work. Prior arts of the transmitter and the design specifications will be demonstrated after introducing the architecture of the transmitter. At last, the organization of the whole thesis is shown.

#### 1.1 Vagus nerve

| Organ               | Function                                                                 |

|---------------------|--------------------------------------------------------------------------|

| Heart               | Slows heart rate                                                         |

| Lungs               | Cough reflex                                                             |

| Oesophagus          | Modulation of peristalsis                                                |

| Stomach             | Regulation of gastric motility                                           |

| Liver               | Sense glucose levels; Syppress hepatic glucose production                |

| Pancreas            | Regulatory roles in the secretion of insulin and pancreatic exocrine     |

| Small<br>intestines | Modulation intestinal microenvironment for intestinal immune homeostasis |

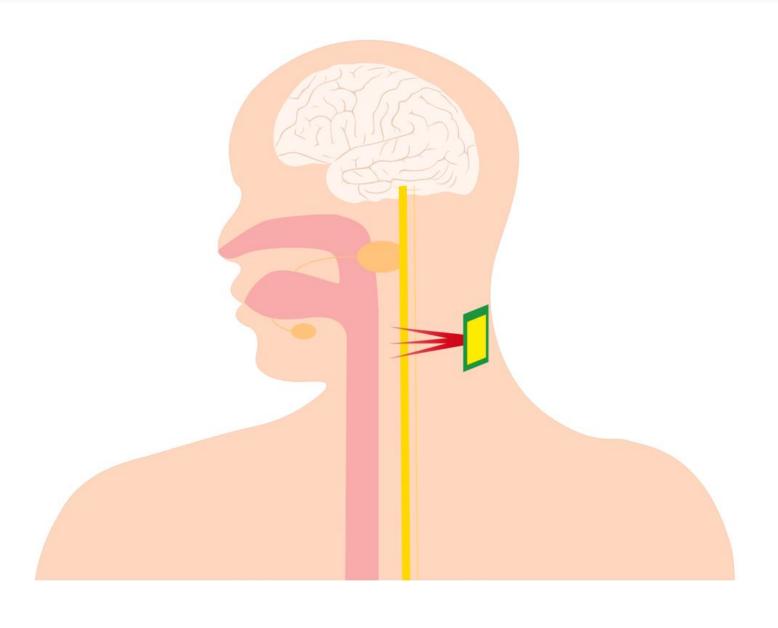

Figure 1.1 Vagus Nerve in Parasympathetic Nerve System [1] and related function[2]

The Vagus nerve is the 10<sup>th</sup> cranial nerve and the main contributor to the parasympathetic nervous system. It has the widest distribution in the body, as shown in Fig 1.1, from the brain to the abdomen, connecting the brain to the heart, lungs, stomach, and many other organs. These connections are built by the somatic and visceral afferent fibers, as well as general and special visceral efferent fibers in the vagus nerve. Thus, a vast array of crucial bodily functions are overseen by the vagus nerve, including control of mood, immune response, digestion, and heart rate[3]. The organs that the vagus nerve innervates and the related functions[2] have been studied by scientists are summarized and listed in Figure 1.1.

With these functions, the potential of vagus nerve neuromodulation in the medical area is huge and has been studied for decades. A relatively mature application is the VNS using in the treatment of refractory epilepsy and depression[4], which have also been approved by the Food and Drug Administration (FDA) in 1997 [5] and 2005 [6] separately. Further researches also illustrate the therapeutic effects of VNS in hypertension heart failure, rheumatoid arthritis, tinnitus, and stroke rehabilitation[7]. However, the inside mechanism of vagus nerve neuromodulation is not fully established and the efficacy varies from patient to patient with some side effects including cough, throat pain, voice alteration, and dyspnea[8]. Thus, the improvement in the VNS methods or devices would be vulnerable for a further understanding of the vagus nerve modulation and fewer side effects, which is also the motivation of this work. Historically, the VNS is conducted by an electrical stimulator, but focused ultrasound has also emerged to be an approach. The details and differences between these two methods are explained below.

#### 1.2 Vagus nerve stimulation

#### 1.2.1 Electrical VNS

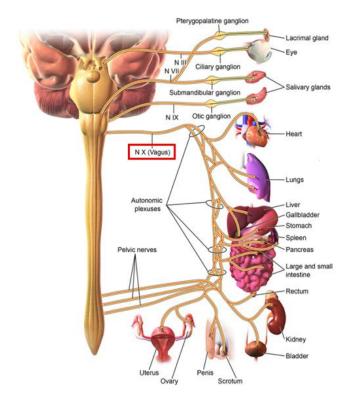

Figure 1.2 Electrical VNS[9]

As shown in Fig.1.2, normally an electrical stimulator is surgically implanted under patients' skin. The pulse generator delivers electrical pulses to cuff electrodes wrapped around the vagus nerve, near the neck where the vagus nerve is most accessible. The control of output current, signal frequency, pulse width, and on-time of signal could be tuned for different patients or different extent therapy. There are several commercial implantable VNS products, such as the SenTiva VNS Therapy by LivaNova[10] and the VNS Therapy system by Cyberonics[11]. The control of seizures improved over time[10], and according to[11], more than 60% of patients with refractory epilepsy gained 50% or more reduction in seizures.

However, there are several limitations of electrical VNS. First, it requires surgery, which might introduce more risk to the patients. Charging or replacing the battery would be a further problem. Second, currently, the spatial resolution of electrical stimulation is not high enough. Since the vagus nerve inside contains many fibers, or neuron axons, which execute different functions, a coarse stimulation activates some unwanted fibers and affects both the discovery of the vagus nerve modulation mechanism and the treatment effect. Although a non-invasive electrical VNS device also emerged (the gammaCore Sapphire[12]), the efficacy is affected, and spatial resolution is even worse when electrical signals have to pass through the skin. Besides, as a handheld device for patients, the gammaCore could not ensure the stimulation area is fixed on the vagus nerve during therapy. A real-time system would be preferred when VNS therapy is conducted. Despite the success of electrical VNS in the treatment of epilepsy and depression, more advanced VNS methods need to be developed for better spatial selectivity and neuromodulation efficacy. Ultrasound VNS emerged to be a good option.

#### 1.2.2 Ultrasound VNS

Ultrasound is a pressure wave with a frequency higher than the human hearing range (>20kHz). Ultrasound is widely used in the medical area as a diagnostic imaging modality since the 1970s, and its potential for neuromodulation has also been developed in the past few decades. When the ultrasound wave is propagating in biological tissue, both mechanical and thermal effects are caused and could be used for therapeutic application[4]. High-intensity focused ultrasound (HIFU, intensity>200W/cm²) has been used for non-invasive ablation[13], due to its deep penetration depth and millimetre spatial resolution. However, the thermal damage caused by HIFU is irreversible. In neuromodulation, on the other hand, low-intensity ultrasound (LIFU) is safe and reversible, thus being much more preferred. It is reported that LIFU in 0.5 – 100W/cm² could still produce bioeffects while avoiding tissue heating[8]. More importantly, a 90 µm spatial resolution is now achieved using 43 MHz LIFU, which was utilized to stimulate neurons in the salamander retina[14], which indicates more potential for ultrasound VNS.

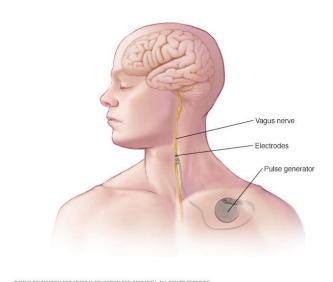

#### 1.2.2.1 Possible mechanism

Although the complete mechanism of ultrasound neuromodulation is still uncovered, hypotheses (Fig 1.3) are established based on experiments and observations[15]. One proposed model is that the ultrasound acoustic pressure causes compression and rarefaction of the cell membrane. These mechanical effects on membranes and ion channels will change the membrane conductance and channel activity. Another hypothesis is that the mechanical effects caused by ultrasound acoustic pressure contribute to the formation of a bilayer sonophore. This gives rise to the mechanically originated displacement currents which alter changes in membrane capacitance and voltage. Either the mechanical-only model or the mechano-electric model results in affecting the voltage-mediated activity of ion channels and changing the neuronal membrane conductance. Further understanding of the ultrasound neuromodulation requires devices with high spatial selectivity so that a specific region or fiber of the nerve could be stimulated without activating unwanted objectives.

Figure 1.3 non-thermal modulation of neural activity by LIFU[15]

#### 1.2.2.2 Structure and characteristics of an ultrasound system

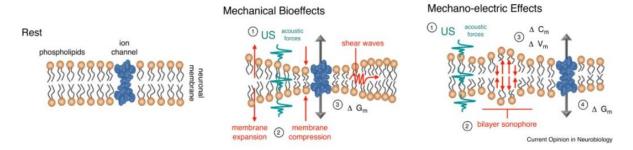

Figure 1.4 structure of an ultrasound system

As in Fig 1.4, a simple ultrasound system contains mainly four parts, the signal control block, the circuit section (transmitter and receiver), the piezoelectric transducer, and the medium area. The signal control is a computing unit where the input signal properties are pre-set and the received signals are processed. In neuromodulation, the bioeffects or treatment efficacy is mainly determined by the acoustic intensity and exposure time, both of the values pre-set in the signal control block. The acoustic intensity could be evaluated by the pressure amplitude, which is linearly proportional to the voltage amplitude of the electrical signal. As in equation 1.1, p is the output pressure,  $\varepsilon$  and  $\varepsilon_0$  are the relative dielectric permittivity and the permittivity in the vacuum, k is the coupling factor,  $d_{33}$  is piezoelectric constant and t is the thickness of the piezoelectric layer. All of these parameters are the properties of the transducer material, except V is the applied voltage. In chapter 2, pressure amplitude is used to evaluate the ultrasound output performance, while in the circuit design part, the applied voltage is focused on. Users could determine the output pressure through the signal control block, but the applied voltage is dependent on the transmitter circuit.

$$p = \frac{\varepsilon \cdot \varepsilon_0 \cdot V}{k \cdot d_{33} \cdot t} \tag{1.1}$$

Exposure time is fully controlled in the signal control block. Each input signal could be scaled down to three layers, the total signal domain, burst domain, and pulse domain, as seen in Fig 1.5 [16]. In a total time (TT) for a whole signal, each unit is one burst interval (BI) which contains one burst duration (BD) and one inter-stimulus interval (ISI). The ISI is set to avoid a constantly-on stimulation causing accumulated temperature increase and possible damage to

the target nerve. During the ISI, ultrasound imaging could be conducted since it does not require a long burst duration compared to neuromodulation. Inside each BD, the pulses pattern is determined by different applications. For ultrasound neuromodulation, long bursts of continuous waves are applied to ensure the nerve is stimulated. While for imaging, a single-pulsed waveform is applied where the pulse length (PL) is fixed and it will repeat several times at a pulse repetition frequency (PRF). Depending on different stimulation purposes, the exposure time could be altered easily in the signal control block. In this work, both a continuous waveform (CW) and a single-pulsed waveform (PW) are provided in the pulse domain layer.

Figure 1.5 signal timing properties related to exposure time[16]

The circuit section is directly connected or attached to the transducer. In the traditional application of ultrasound stimulation, a single crystal bulky transducer is used. As in Fig 1.6, the focusing area is relatively large and the pressure intensity is equally distributed in the focusing area. Although acoustic lenses could be added to improve the focusing capability and spatial resolution, this kind of transducer requires an external mechanical stage to change the focusing region. Manually moving the transducer to change the focal area is possible but the precision is worse, which is only acceptable in some imaging applications. A phased array (either 1D or 2D) could use a technique called beamforming to improve the focusing ability. Since there are several small transducer elements inside one phased array, each of them could generate an ultrasound wave to the targeting position. Contributed to the beamforming, all the different waves from each element could reach the same pre-determined position at the same time where these waves constructively interfere to achieve a high pressure intensity and spatial resolution. The beamforming is conducted in the transmitter as a key design consideration in this work and will be explained in detail in the next section. In a phased array, the spatial resolution is dominated by the acoustic frequency, array size, and the focal depth. Both 1D and 2D array could be achieved in a small and wearable device since the circuit section is attached to each transducer element. 1D arrays are commonly found in commercial ultrasound imaging probes, however, compared to the 1D array, a 2D array could tune the focal spot at any geometric position in a 3D-volumetric space, while the focusing area for a 1D array is only a 2D surface plane. The simulated target is the vagus nerve which might move slightly during the stimulation. In addition, the relative position of the vagus nerve varies from individual to individual. Hence, a 2D transducer array and beamforming transmitter are the desired structure for our design.

Figure 1.6 Focusing and tuning area for different transducer structure: single, 1D array, 2D array (each element in the 2D array is separated like in 1D array)

The last section of an ultrasound system is the medium area, where all the mechanical or thermal effects happen. Except for the mechanical reaction and related bioeffects caused by the acoustic pressure, reflection and absorption also are the dominant effects during the propagation of the ultrasound wave[17]. The acoustic wave propagates at different speeds in different mediums, such as the bone, nerve, or muscle, because the rigidity and density of them are different. Part of the acoustic wave reflects as echoes when it reaches a different material. These echoes carry information of their reflection boundaries, so they could be gathered and processed to form a diagnostic image, which allows the ultrasound imaging to be conducted at the same time so that a precise stimulation area is ensured. The absorption of the acoustic wave is due to the thermal energy conversion, which results in attenuation of the pressure amplitude. The attenuation is frequency and penetration depth related, which adds more limitations on the design of a transmitter.

#### 1.3 Transmitter and beamforming

As introduced above, an ultrasound VNS system is a combination work of all sections, requiring programming in signal control, circuit design for transmitter and receiver, manufacture of the transducer, and physical analysis of the target medium. The transmitter circuit is responsible for the beamforming technique for a 2D phased array, driving each transducer elements, and providing different modes of waveforms for the signal control block to conduct different function, which is the key design task of this thesis work.

In a 2D phased array, each transducer element will have a channel of CMOS circuit attached to it, containing either transmitting or receiving circuit, or both of them. In Fig 1.7, a transmitter channel receives the signal control orders, generates the required electrical signal then passes it to the transducer interface, where the signal will be level-shifted to a higher level so that it can drive the piezoelectric material. The beamforming functions normally are not fully achieved inside the channel considering the area consumption. Here, the dimension of each channel (or the pitch size) should be half of the ultrasound wavelength to avoid grating lobes which can dramatically decrease the stimulation and focusing performance. Due to these area constraints, it would be quite challenging to interface both the transmitting circuit and receiving

circuit inside one channel. Also, some components could be shared for all channels, so in Fig 1.7 the beamforming function is split between the channel (inside) and the periphery of the array (outside). The detailed arrangement of the circuit components is based on the required beamforming function.

Figure 1.7 circuits implementation in the ultrasound VNS system

Figure 1.8 beamforming of the transmitter in a 2D array

Beamforming is a technique for directional wave transmission or reception. In Fig 1.8, a row/column of transducer elements is shown to focus at a pre-determined spot. Each element has a different position where the ultrasound wave is sent. Considering an ideal and isotropic medium, the travelling time of each ultrasound wave is dependent on the travelling distance and the sound speed, which is given in equation 1.2. Ultrasound waves from different elements would reach the pre-determined spot at the same time if these wave signals are triggered with the appropriate time delays.

$$t_{travel} = \frac{N}{c \cdot \cos \alpha} \tag{1.2}$$

The difference of waveforms in neuromodulation and imaging also represents in the time delay settings. For a continuous wave (CW), the delay difference among different channels is always smaller than one time period (0 to 1T) since the signal is periodic. The requirement is a precise delay resolution, especially for two adjacent elements. However, the single-pulsed wave (PW) for imaging has a delay difference in a long period (>nT, n=0,1,2,3...) but with the same time resolution as for the CW mode. Because for ultrasound imaging, the focal spot should be the same while the intensity should be kept low to avoid thermal damage.

The transducer interface determines the driving voltage which directly affects the pressure amplitude as in equation 1.1. The spatial resolution of the beamforming transmitter is determined by the focal depth (N), wavelength  $(\lambda)$ , and array size (A), as in equation 1.3. All the exact values of the affecting variables will be gathered by the simulation results in chapter 2.

$$S_{res} = \frac{N\lambda}{A} \tag{1.3}$$

#### 1.4 Prior art and Thesis objective

Efforts have been done in the design of CMOS transmitter using in a 2D phased array during the past few decades. Aiming in different applications, the achieving methods and performance of the transmitter also vary.

A miniature 2D phased array ultrasound transmitter[18] is capable to achieve a maximum focal pressure over 100 kPa with a 5 V supply at 0.5 cm depth in tissue without any acoustic matching layer. The spatial resolution could reach 200 µm level. This work is using a 10 MHz ultrasound wave and 26x26 transducer array, aiming for neuromodulation, and the total size of the CMOS chip is 5x4 mm². However, the stimulation output waveform is only a continuous wave, which is not compatible with imaging applications. An additional mode of wave could be included in this transmitter to have real-time surveillance of the focal spot. Besides, the pressure amplitude and spatial resolution could be further improved. For the human primary visual cortex, the excitation pressure level is in the MPa range[19], which might differ for the vagus nerve, but a higher upper limit for the pressure is always preferred. Controlling signals could tune the actual output pressure by turning off some of the array channel circuits.

Another transmitter system for ultrasound imaging[13] contains up to 4 types of pulses for different imaging functions. A 32x32 2D array is implanted in this work, which achieves an imaging depth of up to 7.5 cm and 60V driving voltage. Although the penetration is much deeper, the emphasized performance of this work is not on spatial resolution and only 64 of the transducer elements are connected with transmitting circuits. The transmitter of this work is mainly digital, containing some large area consuming digital blocks, such as a 10-bit comparator, which would also be an obstacle to implement both transmitter and receiving circuits inside one channel.

In our proposed system, the ultrasound VNS device is desired to be attached to the neck and conduct both neuromodulation and ultrasound imaging. Aiming for a wearable device, the transmitter design would have some severe requirements on the chip area and power. The heat dissipation must be carefully controlled to avoid any thermal damage. The limited area is a huge obstacle for integrating both transmitter and receiver inside one channel, which calls for some arrangement techniques such as the sparsity control of array channels. The precise geometrical focusing ability and pressure amplitude still need to be ensured under a small-sized chip. Both the physical understanding of the vagus nerve stimulation and the circuit design for a valid transmitter to achieve the VNS functions are required for this thesis work. A list of general specifications are given in the table below, further design variables will be

derived based on the MATLAB simulation in the next chapter. Although the final aim of this system is the VNS for human, currently our work is only targeting the animal models (mice and rats). The specifications below are also based on the research data of mice.

| Performance            | Specifications |

|------------------------|----------------|

| Focal depth            | 5-7 mm         |

| Pressure at focal spot | >1 MPa         |

| Spatial resolution     | ~100 um        |

| ultrasound frequency   | >10 MHz        |

| Power of each channel  | <1 mW          |

Figure 1.9 proposed device and the general specifications

#### 1.5 Thesis organization

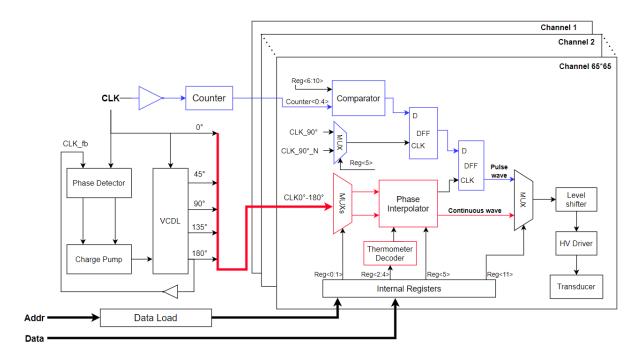

Figure 1.10 Transmitter design blocks

This thesis work presents the design of an ultrasound transmitter system for vagus nerve stimulation, which includes the MATLAB system-level simulation and the design of four circuit block, the coarse delay generation clocks, the stimulation CW wave generation block, imaging function block, and the transducer interface block. Containing the introduction chapter, there are seven chapters in total. The other chapters are:

Chapter 2 demonstrates the MATLAB simulation for the whole stimulating system. In this chapter, the neuromodulation and imaging function will be simulated in MATLAB to get the detailed values for the required design variables, including frequency, array size, geometrical focal depth, and the time delay configuration.

Chapter 3 illustrates the design of the coarse phase control block, which is a delay-lock loop including a phase detector, a charge pump, and a voltage-controlled delay line.

Chapter 4 discusses the fine delay control generation. Here the phase interpolator is chosen.

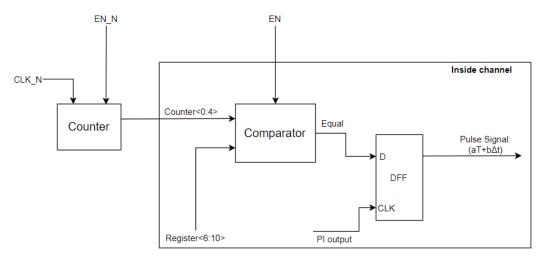

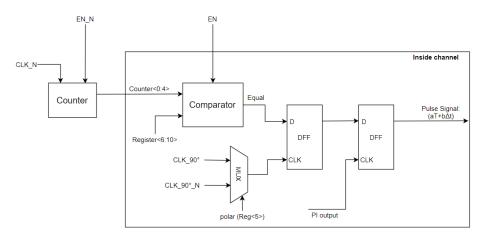

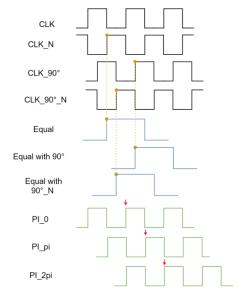

Chapter 5 introduces the embedded ultrasound imaging function block which is fully digital. Several digital components are included, such as counter, comparator, multiplexer, and register.

Chapter 6 shows the interface circuit for the transducer. It is responsible for driving the delayed signal to a higher level to activate the transducer.

Chapter 7 demonstrates the whole system and concludes the contributions and future perspective of this thesis work.

# Chapter 2 Stimulation model and Matlab simulation

In this chapter, a MATLAB simulation model that could achieve the transmitter functions are built and simulated. Based on the research data of the vagus nerve, specific design requirements for the circuit design and signal properties setting are derived, including the values of ultrasound frequency, array size, focal depth, and delay time. Additionally, the study of array sparsity is also tested to provide a potential solution for output pressure control and area saving.

#### 2.1 Stimulation model

Figure 2.1 MATLAB simulation model

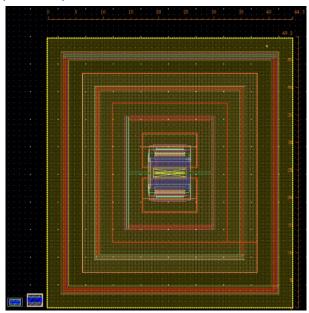

As shown in Fig 2.1, the whole process and its 3D space model from beamforming to pressure sensing in the ultrasound neuromodulation are built by MATLAB code using the k-wave toolbox. In Fig.2.1(a), the electrical domain is the signal generating section, where the code sets the transmitter properties (wave modes, array size, frequency, focal depth). In the acoustic domain, which is also shown in Fig.2.1(b), it corresponds to the medium where the acoustic wave propagates. We assume the medium is soft tissue and isotropic, with sound speed c =1540 m/s, medium density  $\rho = 1063 \, kg/m^3$ , and attenuation coefficient  $\alpha = 1 \, \text{dB/cm·MHz}$ . The transducer array is located in the y-z plane of medium space, and the acoustic wave, which propagates in all directions, is sensed by a sensor area in the x-z plane (the red square in the middle of the medium space). The whole space is composed of small-block grids with dimensions 30um\*30um\*30um. This grid size allows the configuration of each transducer element to be a 3x3 block and the pitch size (distance between the centre of two adjacent elements) to be 120um. The configuration for grid and pitch size is the same as previous work in [18] and is reused here in the consideration of simulation time, channel area, and fabrication process. Smaller dimensions such as 15um have been tested for the grid, but the simulation time is increased to several hours. In [18] only neuromodulation function is implemented, but in this work, more circuit components should be included in one channel. Keeping the pitch size to be 120um, which means a channel area of 120um\*120um, is an appropriate and conservative consideration. Additionally, the transducer must be diced into several elements to allow the different time-delay settings for each channel, which requires a fabrication process on a single piezoelectric material. The dimension of the edge between two elements could not be too small to fabricate, and 30um is proved to be an achievable value as in [18]. The main limitation of the pre-set pitch size is on the ultrasound frequency. As mentioned above, the pitch size should be smaller than half-wavelength to avoid side lobes. If so, from equation 2.1, then the ultrasound frequency could only be smaller than 6.4 MHz.

$$c = f\lambda \tag{2.1}$$

However, according to simulation, if the pitch size is larger than half-wavelength but smaller than one-wavelength, the existing side lobes do not have a significant effect on the focusing performance, especially in a large array. The limitation of the 120um pitch size now is mitigated and allows a frequency range from 6.4 MHz to 12.8MHz. Figures of simulation results will be shown later in this chapter. After introducing the model, the variables we need to simulate and their requirements are explained below.

#### 2.1.1 Variables under simulation

In the simulation model, the ultrasound frequency (f), size of the phased array (A), geometrical focal depth (N), and the time delay should be simulated to get appropriate values to fulfil the specifications mentioned in chapter 1.

#### **2.1.1.1 Frequency**

The ultrasound frequency (f) is the essential variable affecting the performance of both neuromodulation and imaging function. The following equations illustrate the relationship between frequency and each performance factor.

$$S_{spatial} = \frac{N\lambda}{A}$$

$$p = p_0 e^{-\alpha x}$$

(2.2)

$$p = p_0 e^{-\alpha x} \tag{2.3}$$

$$\alpha = af^b \tag{2.4}$$

In Eq 2.1 and 2.2, frequency is directly related to the spatial resolution of the focal spot. Spatial resolution is defined as the -3 dB dimension of the focal spot width as in Fig 2.1 (a). A smaller value of the  $S_{spatial}$  means a higher spatial resolution. Since the speed of sound is fixed, higher frequency gives a shorter wavelength and thus a finer spatial resolution. Eq 2.3 is the amplitude of focal pressure, where  $p_0$  is the original amplitude,  $\alpha$  is the attenuation coefficient and x is the displacement (penetration depth) of the ultrasound wave. Here the equation is for the ultrasound wave sent by every single element, and the total focal pressure is an accumulated value of all the waves. Because the distance from each element to the focal spot is different, the attenuation for the ultrasound wave from different elements is also different and has to be considered separately. Attenuation is highly frequency dependent and mainly caused by absorption. Since the acoustic wave causes compression and rarefaction when it is propagating in soft tissue, higher frequency gives rise to more vibration which is partly converted to random vibrational heat energy. This process is defined as absorption. Additionally, other effects such as scattering and beam divergence also contribute to the attenuation and are frequency-dependent. The attenuation coefficient is proportional to the frequency as in Eq 2.4, where a and b are material-related coefficients. As mentioned above, the medium in our

model is soft tissue thus the attenuation coefficient is  $\alpha=1 \text{dB/cm·MHz}$ . In the propagation of ultrasound waves, the higher the frequency, and the deeper it propagates, the more attenuation on the pressure amplitude. The simulation of frequency should find a high-frequency value but not cause too much attenuation.

#### 2.1.1.2 Array size

In the MATLAB model, the grid system we used only determines the dimension for each transducer element, but the array size is the dimension of the whole array which relates to the number of elements included. In this work, to achieve a 3D volume space stimulation, a 2D phased array is chosen, and its shape is square. The Array size (A) is given in NxN formation. In the future development, the different shape of the array could be used in different applications. The performance factors related to array size are the spatial resolution in Eq 2.2 and the focal pressure in Eq 2.5.

$$p_f \propto \frac{p_0 A}{N} \tag{2.5}$$

Here the  $p_f$  is the accumulated pressure amplitude in the focal spot and  $p_0$  is the amplitude for each element. A larger array contains more transducer elements, which means more waves will be sent to the focal spot, and hence the increased pressure. In the focal spot, the highestintensity area has a more rapid increase than the surrounding region, which results in a finer spatial resolution. Increasing the array size is a boost in both spatial resolution and focal pressure. However, there are several upper limits for increasing the array size. Firstly, our proposed device is a tiny and wearable one, aiming for the VNS for humans but will start with tests on mice. The dimension of the array would be better on the few-millimetre scale. The circuit design also suffers from a larger array. The distance between the focal spot and the centre transducer elements in the array is different from the distance between the focal spot and the corner elements. This difference increases with the rising of the array size. In pulsed-wave mode, the centre elements should send the wave much later than the corner ones to ensure all the waves reach the focal spot at the same time. So the larger array requires a large delay time which is processed and stored in the circuit components. The number of circuit components or the size of them will also be increased. Additionally, a large delay time value occupies more bits in the data transfer and processing, so the time of one pulse transmit in all channels will be longer and the rate of imaging will be affected. In the simulation, we should find the minimum array size which fulfils the spatial resolution and pressure specifications.

#### 2.1.1.3 Focal depth

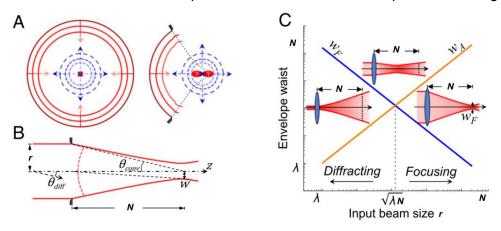

The actual focal depth of the phased array is different from the geometrical value we set in the MATLAB code. This difference is called the focal shift. To ensure the actual focal spot is in the pre-set location, an appropriate geometrical value is needed to be simulated. The focal shift is inevitable for a focusing system with a low Fresnel number  $N_{Fres} < 100$ . The Fresnel number reflects the relative contribution of focusing and diffraction effects for an aperture focusing model and is defined [20]:

$$N_{Fres} = \frac{r^2}{\lambda N} \tag{2.6}$$

Here r is the radius of the aperture, and it corresponds to the dimension of the array in our

system.  $\lambda$  is the wavelength and N is the focal depth. The focal shift is explained in the model of an aperture system in Fig 2.2. The focal shift will always exist if the focusing wave is not a perfect full spherical wave as in Fig 2.2 A. The red point in the middle is the source of the blue waves and the red waves are the reversed signal. The red wave will always focus on the middle position because of its circular symmetry. When this symmetry is broken such as the red focusing wave is only part of a spherical wave, the focusing position will change since there is information lost [20]. This partial wave focusing situation is similar to the aperture focusing model and our phased array focusing system. As shown in Fig 2.2B, the convergence and diffraction both exist in the spreading out of a wave in the aperture focusing model. The ratios of them are  $\theta_{conv} = r/N$  and  $\theta_{diff} = \lambda/r$  separately. If the convergence is dominating, the output waveform is more focusing and the actual focal spot will be close to the geometrical value. Otherwise, the focal spot will shift more back to the aperture as in Fig 2.2C.

Figure 2.2 Focal shift model [20]

In our case, assuming the minimum geometrical setting is 5mm and the minimum wavelength is 120um (corresponding to 12.8MHz) and the diameter of the array is 2.5mm as in [18], the ration  $\theta_{conv}/\theta_{diff}=10.4$ . The output is more focusing but the actual focal depth will always be smaller than the geometrical value. The simulation aims to find the appropriate geometrical value which allows the actual focal depth to meet the specification.

#### **2.1.1.4** Time delay

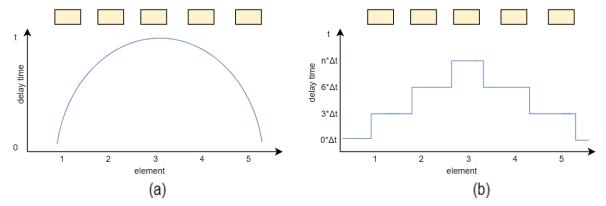

As mentioned in chapter 1, for neuromodulation, the input signal should be a burst of continuous wave and the phase difference among different channels is  $0{\sim}1T$ . For imaging, the input signal should be the pulsed wave and the phase difference is larger than one period (nT, n=1,2,3...). After setting a fixed f, A, and N, the delay values for each channel will be calculated in MATLAB and have to be achieved in the circuit design. In MATLAB, these delay values are calculated in a continuous value range, which gives the exact phase each channel needs. However, in the circuits, the generated delay time is based on a unit delay value, and all the delay should be integer multiples of this value. The unit delay value ( $\Delta t$ ) is defined as the minimum delay or the time resolution. A computation step called quantization should be conducted to convert the continuous values to quantized values. As shown in Fig 2.3, before quantization, the delay time for each element is a precise value in a continuous curve, while after quantization, the delay time is an approximate number to the precise value and is the integer times of  $\Delta t$ .

Figure 2.3 Quantization (a)before quantization (b)after quaantization

$\Delta t$  is given by:

$$\Delta t = \frac{T}{2^n}, n = 1, 2, 3...$$

(2.7)

T is the period of the ultrasound wave, and n should be simulated. The quantization process will degrade the spatial resolution if n is small, but a large n will increase the complexity and area of the circuit. The appropriate value for n is the minimum integer to keep the spatial resolution the same as the value before quantization. After deriving the minimum delay from the quantization bit n, all the delay values could be expressed using  $\Delta t$  as the unit. The delay time for neuromodulation and imaging could be given by:

$$0 \le t_{delay} < 2^n \cdot \Delta t \tag{2.8}$$

$$0 \le t_{delay} \le a \cdot T + b \cdot \Delta t, \ a, b = 1, 2, 3...$$

(2.9)

Eq 2.9 is for imaging, where  $a \cdot T + b \cdot \Delta t$  indicates the largest phase difference among all the channels. Normally this difference is between the centre element and the corner element, but the exact value for a and b depends on the array size and focal depth. Also, to achieve a 3D volumetric focusing ability, a  $\pm 15^{\circ}$  range from the middle of the sensing plane is simulated. The largest phase difference should cover different steering angles.

#### 2.1.2 Simulation setup

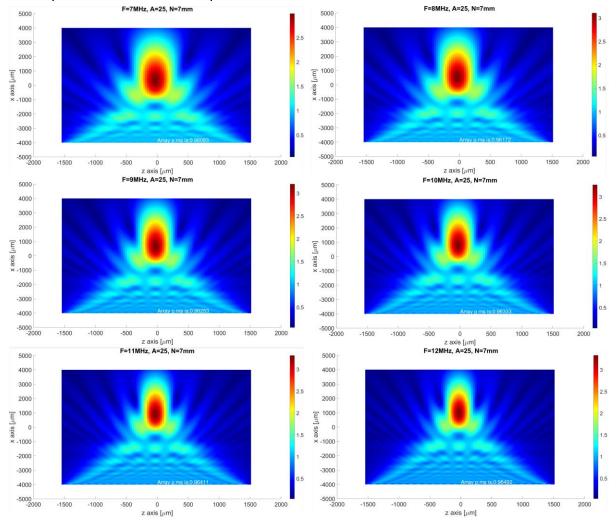

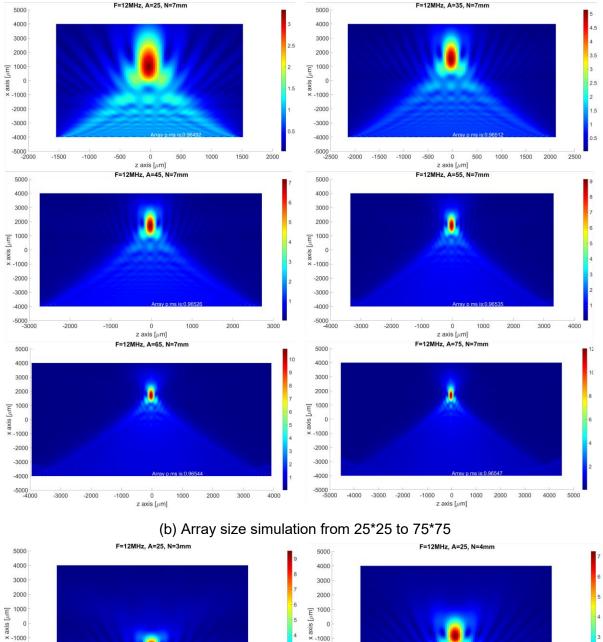

Since the spatial resolution and pressure are affected by several variables mentioned above, it would be hard to simulate all the variables at the same time. Each variable will be simulated in a reasonable range while the other variables will be fixed to constant values. The frequency will be simulated first because it determines the wavelength which affects the performance of A and N. Due to the pitch size limitation, the frequency will be swept from 7MHz to 12MHz with a step of 1MHz. The other factors are fixed at  $A = 25 \times 25$  (the array is 25\*25), N = 7mm (the setting focal depth).

The array size will be simulated next, from 25\*25 to 75\*75 increasing by 10 elements each time. The other factors are fixed at f = 12MHz, N = 7mm. The actual focal depth is affected by both the wavelength and the array dimension, so it will be simulated after f and A. The geometric value is tested from 3mm to 8mm with 1mm per step. The other factors are  $A = 25 \times 25$ , and f = 12MHz.

After all of these variables are fixed, the quantization bit will be simulated from n=1 until the appropriate value is found. Then the minimum delay and the largest delay difference could be extracted from the time delay matrix in MATLAB.

#### 2.2 Simulation results

#### 2.2.1 Output figures on the sensing plane (f, A, N)

The performance factors are extracted from the output figure of the sensing plane which is placed in the middle of the 3D model. The figure illustrates the pressure amplitude distribution, where the pressure value is normalized to the amplitude of a single element  $p_0$ . The highest value of this dimensionless pressure appears at the focal spot and is defined as  $p_f$ . Another factor called pressure gain is defined as  $p_f/p_{array}$  which illustrate the pressure amplification from the total phased array to the focal spot. With this pressure gain, how much of  $p_0$  is required to achieve the desired focal pressure will be easy to calculate. The spatial resolution is measured as the -3dB dimension of the focal spot width. The distance from the array to the focal spot is the actual focal depth.

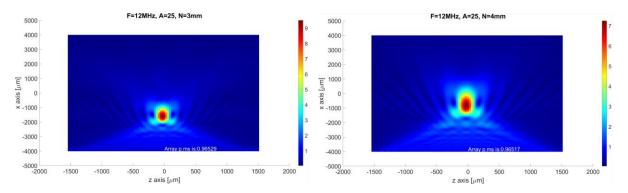

(a) Frequency simulation from 7 to 12MHz

-2000 -2000 -3000 -3000 -4000 -4000 -5000 -2000 -5000 -2000 -1500 -1000 1000 1500 2000 -1500 -1000 1000 2000 1500 z axis [μm] F=12MHz, A=25, N=5mm z axis [μm] F=12MHz, A=25, N=6mm 5000 4000 4000 3000 3000 2000 2000 3.5 axis = 1000 × -1000 ₹ 1000 0 2.5 -2000 -3000 -4000 -4000 -5000 -2000 -1500 1000 1500 2000 -1500 1000 1500

(c) Focal depth(geometrical) simulation from 3mm to 6mm

(d) Focal depth(geometrical) simulation from 7mm to 8mm Figure 2.4 Output figures of the sensing plane

From a general perspective, in the simulated frequency range, the size of the focal spot decreases with higher frequency, while the pressure gain is increased. The side lobe appears to be an issue although the beam size is reduced with higher frequency. However, after the array size simulation, it was found that the focusing performance improved dramatically with a larger array. The side lobe becomes acceptable when the array dimension is larger than 45. It is because the array size has a larger tuning range which allows more elements to focus at the focal spot. The pressure at the focal spot is boosted more than the regions of side lobes, thus the relative ratio of  $p_{sidelobes}/p_{focal}$  is reduced. As for the focal depth, the actual value does increase according to a larger geometrical value, but the focusing performance is worse due to a deeper position suffers from more attenuation. A set of more analytical figures will illustrate the detailed variations of the focusing performance using the data extracted from Fig 2.4.

#### 2.2.2 Detailed analysis of focusing performance

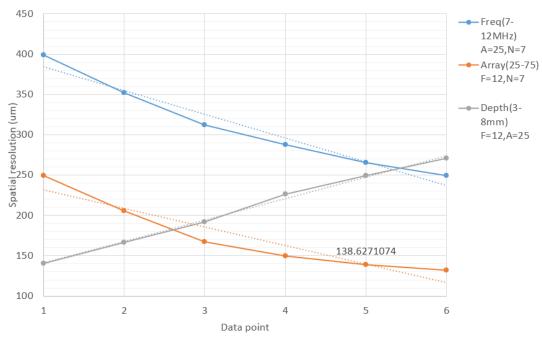

(a) Spatial resolution

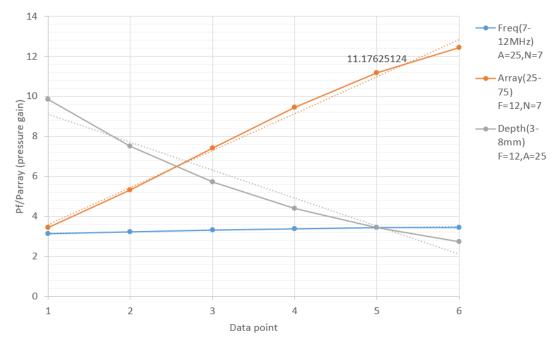

#### (b) Pressure gain $p_f/p_{array}$

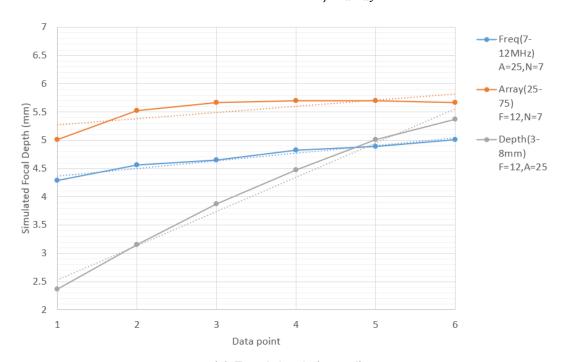

(c) Focal depth (actual)

Figure 2.5 Performance variations

In Fig 2.5, the data for three output performance factors are extracted from the figures of sensing plane. The variation curves demonstrate how the performance factor varies according to different variables. The comparison between the slope of the variation curves and the linear fit lines illustrates the variation speed.

The spatial resolution gets improved with either higher frequency and larger array, but the rate

of improvement is reduced gradually. The reduction is due to the attenuation both for the frequency curve and the array size curve. Higher frequency causes more vibration hence more energy converted to heat and lost. For a larger array, the transducer elements at the corner have the longest path to the focal spot, so these elements suffer from more attenuation because of the long distance. However, the slope of the focal depth curve does not change too much. Except for the attenuation due to a deeper penetration depth, the focusing ability is also changed. As discussed above, the ratio of convergence and diffraction  $\theta_{conv}/\theta_{diff}$  is affected by the wavelengths, diameter of the array and the geometrical focal depth. Here only the focal depth is changed which results in a smaller  $\theta_{conv}/\theta_{diff}$ , so the output pattern is more diffracting with a deeper depth. From the result of spatial resolution, the frequency and array size are expected to be as large as possible while the focal depth should be kept minimum as long as it reaches the depth of the vagus nerve.

The pressure gain shows an obvious trend with the array size or the focal depth while it varies little with the frequency. It has been mentioned above that a larger array contains more elements for focusing and a deeper focal spot will suffer more attenuation on the pressure amplitude. Considering the limited tuning range for the geometrical focal depth, a large array is the best approach to get a higher pressure gain among these three variables. A higher pressure gain will release the requirement on the original pressure  $p_0$  produced by a single element. Since  $p_0$  is determined by the transducer material and the circuit inside the channel, it will be discussed later in chapter 6.

The result of the actual focal depth is mainly based on the ratio  $\theta_{conv}/\theta_{diff}$ , where  $\theta_{conv}=$ r/N and  $\theta_{diff} = \lambda/r$ . When the frequency is swept from 7MHz to 12MHz, the wavelength is reduced from 220um to 128um and  $\theta_{diff}$  becomes smaller, hence the actual focal depth moves to a deeper position. The array size is increased from 25\*25 to 75\*75, corresponding to the diameter from 1.5mm to 4.5mm. However, the actual focal depth only increases when A spans from 25\*25 to 65\*65 and it drops when A becomes 75\*75. Extra tests using 85\*85 and 95\*95 arrays are conducted. The focal depth has a reduction of 30um and 90um compared to the 65\*65 array. One possible reason for this phenomenon would be the precision of the measurement of the focal spot. Because the output figure is composed of several 30um\*30um grid points, the actual highest intensity point might be smaller than this scale. When the array size is increased, the total area of the focal spot becomes smaller and the highest intensity point shifts to a smaller and more precise position. When the neuromodulation is conducted, a -3dB dimension area of the focal spot is recognized as the stimulation region, so this shift will not affect the modulation process. Further understanding of this phenomenon would require the experiment using the actual device. Also, according to the simulation result, the key parameter of controlling the actual focal depth is the geometrical value, not the array size.

After all these simulations, the ultrasound frequency is chosen to be 12MHz. The array size is 65\*65 which also considering the simulation time. When the array is increased from 65\*65 to 75\*75, the spatial resolution only improved 6um but requires an extra 40% of the simulation time. The total dimension of the array would be 7.8mm\*7.8mm with a 65\*65 array which is

relatively large. Further increasing the array size does not have a significant improvement and will increase the burden on circuit design and wire routing. When the f and A are determined, further test on the geometrical focal depth has been conducted. To achieve the expected focal depth from 5-7mm, the geometrical value should be 6.2mm(resulting in 5.01mm depth and 130um resolution) and 8.7mm(resulting in 7.05mm depth and 160um resolution).

#### 2.2.3 Time delay extraction

As mentioned above, the values of delay time created by the MATLAB code should be quantized in the form of integer multiples of the minimum delay  $\Delta t$ . The period of the ultrasound wave is based on the 12MHz frequency and is approximated to 84ns for a convenient calculation in circuit design. After the simulation, the quantization bit is chosen to be 6, so the minimum delay is:

$$\Delta t = \frac{84ns}{2^6} = 1.3125ns \tag{2.10}$$

The simulation figures with quantization bit = 6 are shown below:

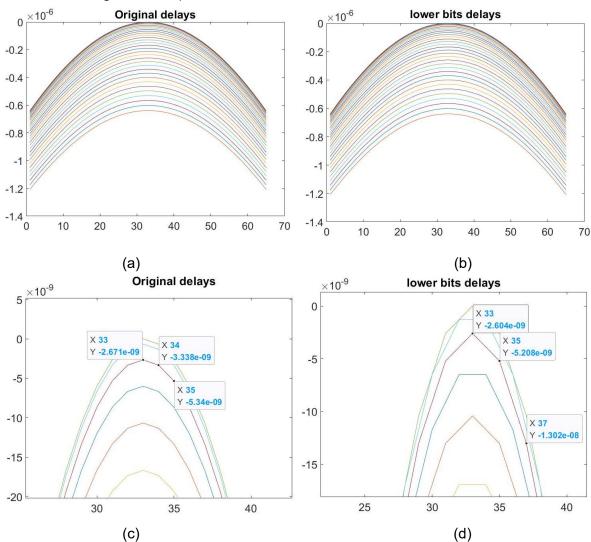

Figure 2.6 delay time before and after quantization (a)before quantization (b)after quantization (c)zoomed-in before quantization (d) zoomed-in after quantization

From Fig 2.6, the zoomed images show that after quantization the values of delay time are

multiples of the minimum delay. From a general view in (a) and (b), the overall delay curves are similar to those before quantization, so the performance factors will not be degraded by the quantization. The data in Table 2.1 proves that the performance especially the spatial resolution is similar to the one before quantization.

Table 2.1 Performance before and after quantization

| Quantiza-<br>tion | Fre-<br>quency | Array<br>size | Depth(geomet-<br>rical) | Depth(ac-<br>tual) | Spatial resolution | Pressure gain |

|-------------------|----------------|---------------|-------------------------|--------------------|--------------------|---------------|

| Before            | 12MHz          | 65*65         | 7mm                     | 5.7mm              | 138.63um           | 11.18         |

| After             | 12MHz          | 65*65         | 7mm                     | 5.7mm              | 138.31um           | 11.17         |

After quantization, the range of delay for the neuromodulation is  $0 \sim (2^6 - 1)\Delta t$  with a resolution of  $\Delta t$ . For imaging, the delay resolution is also  $\Delta t$  and the largest delay value is  $22 \cdot T - 7 \cdot \Delta t$ . These are the actual requirements for the circuit design.

All the variables from MATLAB simulation have been determined and listed below:

Table 2.2 Values for the simulated variables

| Variables                | Symbol                          | Value     |

|--------------------------|---------------------------------|-----------|

| Frequency                | f                               | 12MHz     |

| Period(approximated)     | T                               | 84ns      |

| Array size               | Α                               | 65*65     |

| Focal depth(geometrical) | N                               | 6.2~8.7mm |

| Delay resolution         | $\Delta t$                      | 1.3125ns  |

| Maximum delay            | $22 \cdot T - 7 \cdot \Delta t$ | 1.83us    |

#### 2.3 Sparsity

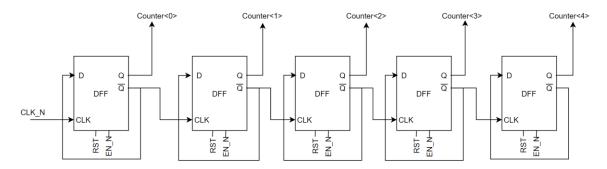

The channel area is a strict requirement for the circuit design, especially for the phased array with both transmitting(Tx) circuit and receiving(Rx) circuit. From some previous work such as [13] and [21], the Tx and Rx circuits are not embedded in the same channel. Also, for ultrasound imaging, the required spatial resolution and focal pressure are not as high as for the neuromodulation. Separating the Tx and Rx in different channels would be a good approach to release the area requirement for circuit design in each channel. The sparsity simulation is set to discover the performance factor variations when some of the transmitting channels are randomly turned off. These turned-off channels could be used to embed only Rx circuits if the spatial resolution and pressure are not reduced too much. The simulation has bee conducted by setting randomly 5% to 95% of the transducer element to be turned off. The other variables

are fixed at f = 12MHz, A = 65 \* 65, N = 7mm.

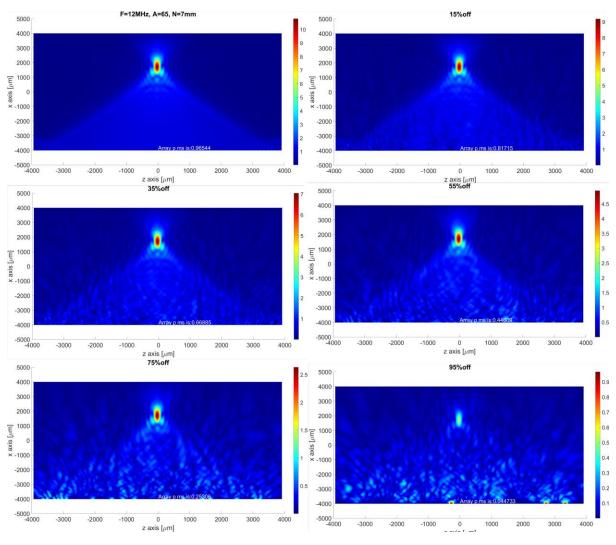

Figure 2.7 Output figures of the sparsity simulation

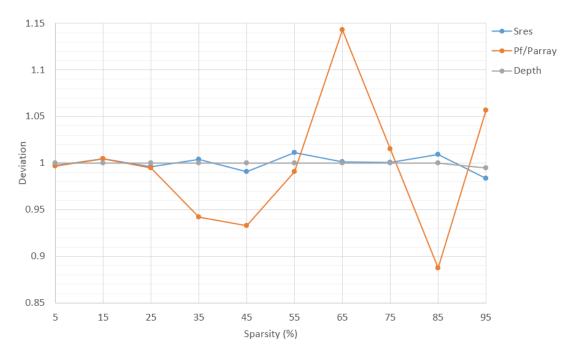

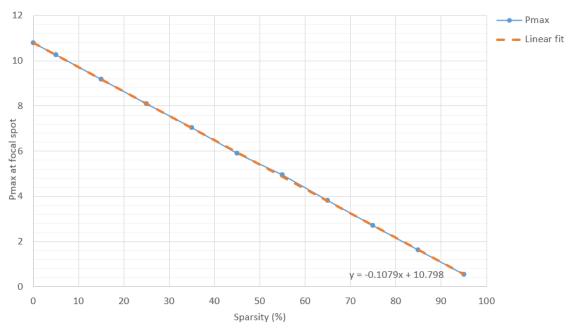

From Fig 2.7 it could be seen that with the increase of sparsity extent, the focal spot does not change the position, while the intensity is getting lower. The exact values of the performance are compared to the original one(no sparsity) to indicates the deviation in Fig 2.8. The spatial resolution and focal depth barely change in a range of  $\pm 2\%$ , and the pressure gain changes in a range of  $\pm 15\%$ . However, the actual focal pressure is linearly controlled by turning off some of the channels, without a change in the driving voltage. From this simulation, the random sparsity only modulates the focal pressure but keeps the focusing ability unchanged. The arrangement of separating Tx and Rx in different channels is allowed as long as the highest pressure for neuromodulation is adequate. It is even possible to leave some channel blank and use the area for adjacent channel interface circuit if that circuit occupies a large area. Another benefit of neuromodulation is the efficacy could be easily controlled by turning some of the channels for different patients. Further development of sparsity could be conducted on different positioning of the Tx and Rx channels or integrating Tx channels with different frequency.

Figure 2.8 Deviation of the performance factors due to sparsity

Figure 2.9 Modulation of sparsity on focal pressure

# Chapter 3 Coarse delay generation

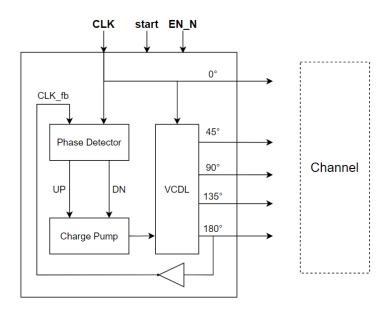

From this chapter, the circuit design to achieve the expected time delay will start. Chapter 3 and 4 are the circuits to generate the delay for neuromodulation, while chapter 5 is responsible for the circuit to generate the delay for imaging function. In this chapter, firstly the arrangement of coarse delay section and fine delay section will be introduced. Then the fundamentals of the delay locked loop (DLL) will be explained. The design of the DLL will be separated into three sections, each section containing one main component of the DLL. At last, an output simulation for the whole DLL will be shown.

# 3.1 Delay/phase map arrangement

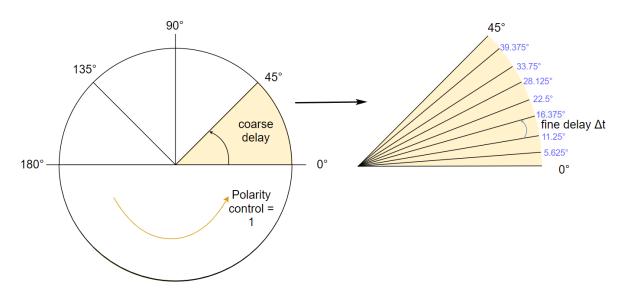

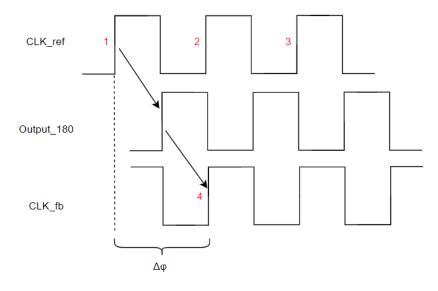

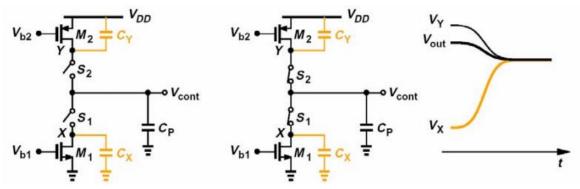

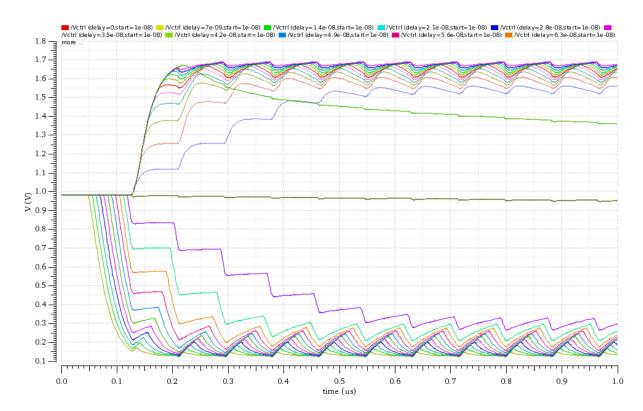

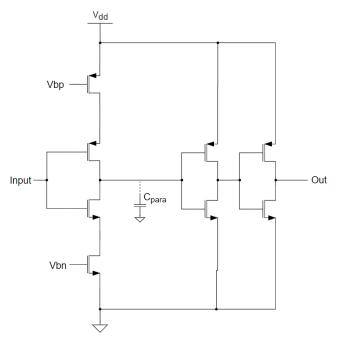

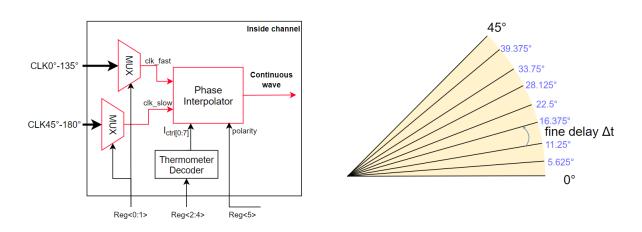

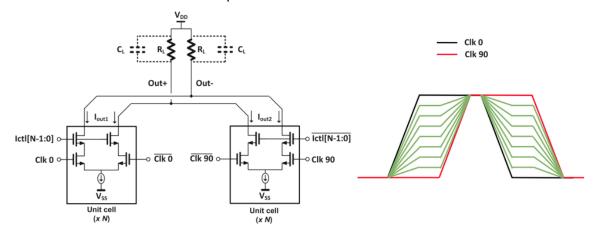

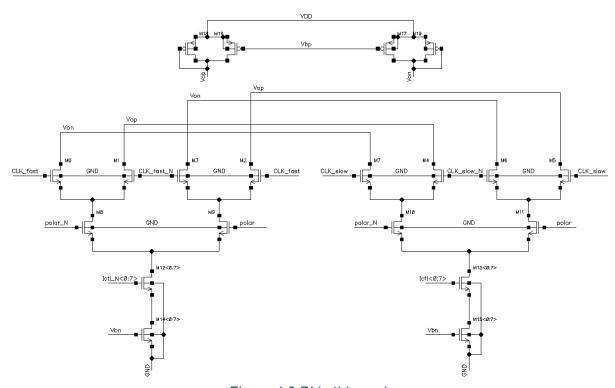

As discussed above, the required delay range for the neuromodulation is  $0 \sim (2^6-1)\Delta t$  where the resolution  $\Delta t = 1.3125 ns$ . Because in the neuromodulation, the wave signals are continuous, this delay range is corresponding to a phase map from 0 to  $2\pi$ . To achieve  $2^6$  values of the delay time, dividing the  $2\pi$  phase into a coarse section and a fine section is essential. Because the channel area is limited, it would be impossible to implement all the delay values inside the channel. Generating all the delay values outside the channel faces the obstacle of complicated wire routing. A reasonable arrangement of the phase map is shown in Fig 3.1, where the coarse delay is from  $0^\circ$  to  $180^\circ$  with a step of  $45^\circ$  and the fine delay is in a  $45^\circ$  range with a step of  $5.625^\circ$ . The five clocks from  $0^\circ$  to  $180^\circ$  will be generated outside the channels as the reference clocks and then are sent to each channel, where two adjacent reference clocks will be selected to generate a finer delay. A polarity control bit could be used to invert the input reference clocks for each channel which completes the phase map from 0 to  $2\pi$ .

Figure 3.1 Phase map of delay generation

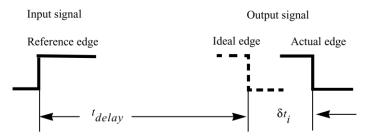

The requirements for the reference clocks in the coarse delay generation are the precision and stability. The minimum delay for the transmitter is  $\Delta t = 1.3125 ns$ , so the maximum delay error should be  $\Delta t/2 = 656.25 us$  to avoid the delay value changing to the next step. The power

and area limitations are relatively low because the coarse generation block is placed outside the channels and shared by all of them. The DLL is chosen to generate these reference clocks in our design, due to its advantages of low phase noise, no jitter accumulation and multiplephases output generation.

#### 3.2 Fundamentals of DLL

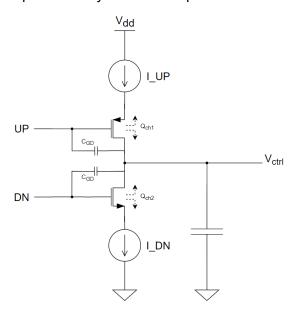

### 3.2.1 Architecture and operating principle

DLL is a precise delay generation circuit widely used in many timing applications, such as clock generation and signal synchronization[22]. Similar to the phased-locked loop(PLL), DLL is also using negative feedback to align the phase of a delayed output signal to a given input signal. The main difference between the DLL and the PLL is the architecture of how the output signal is delayed. In PLL, a voltage-controlled oscillator(VCO) is implemented while in DLL a voltage-controlled delay line(VCDL) is utilized. Due to the absence of the VCO, the DLL can provide a more excellent jitter performance than the PLL since the random timing error does not accumulate from cycle to cycle. As a first-order loop circuit, the DLL is also more stable and easy to design than the PLL. A block diagram illustrating all the components of a DLL is shown below.

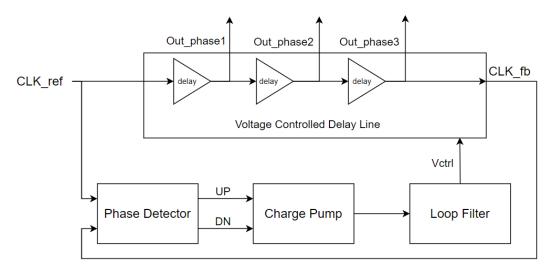

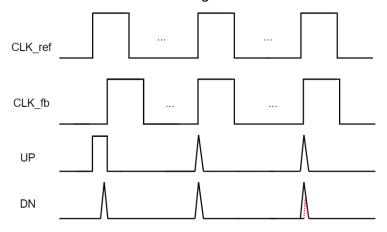

Figure 3.2 The block diagram of DLL

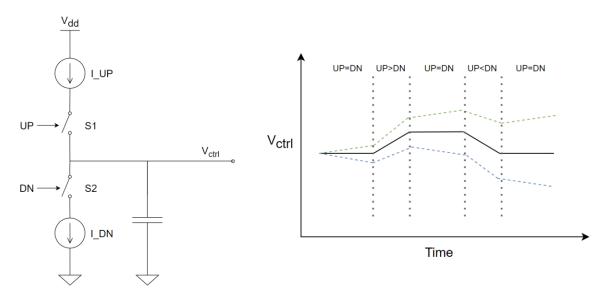

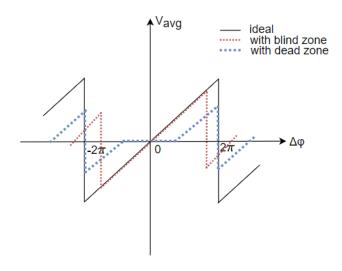

A typical DLL contains mainly three blocks, the phase detector(PD), the charge pump(CP) and the voltage-controlled delay line(VCDL). The loop filter is normally a single capacitor and it is considered together with the charge pump. The operation principle of a DLL is: The original clock (CLK\_ref) first propagates through the VCDL to generate a delayed clock (CLK\_fb) which will be sent back as one of the inputs of the PD. The PD will compare the phases of two input clocks and convert the phase difference to UP and DN signals which indicate the direction and magnitude of the phase error. This phase error will be converted in either voltage or current form in the CP to charge or discharge the loop filter capacitor. The voltage accumulated on the LF capacitor, also the control voltage for the VCDL, will increase or reduce based on the magnitude of the phase difference. The VCDL is composed of several delay stages as in Fig 3.2, and the delay time of each stage is equal and controlled by the Vctrl. Thus the total delay

on the CLK\_fb will also vary according to the Vctrl until the CLK\_fb is aligned to the CLK\_ref at a certain phase difference. The phase difference should be  $n\pi$ , n=0,1,2 ... when the CLK\_fb is aligned, and the exact value is dependent on the application. Once the output signal CLK\_fb is aligned, each delay stage inside the VCDL could provide a delayed signal and the phases are equally distributed with a step of  $n\pi/N$ , where N is the number of stages.

From the architectures, there are two types of DLLs. The difference between them is the input signal of the VCDL. One architecture is shown in Fig 3.2 where the input signal of VCDL is the same clock signal of the phase detector. This architecture is often used for frequency synthesis, clock generation and signal synchronization. In the other architecture, the CLK\_fb is generated by a signal CLK\_ref1 through the VCDL and then compared to a separate CLK\_ref2 through the PD. This architecture is often used for clock recovery circuits. In our design, the purpose is to generate reference clocks with multiple phases, so the first type is preferred.

From the circuit implementation, the DLLs could be divided into analog DLLs and digital DLLs. In Fig 3.2 it is a typical analog DLL. The digital DLL is also based on the negative feedback loop but the function blocks are made of digital circuit elements. For example, in a digital DLL, the charge pump is replaced by a control logic circuit such as a counter. The counting bits adds or reduces according to the UP/DN signal and then change the delay time of the delay line. The delay time variation of a digital DLL is also quantized which requires large bits of digital components to have a fine delay resolution. A low-bit digital DLL will result in great jitter at the output clocks. In an analog DLL, the delay control inside VCDL is continuous and sensitive to the control voltage, which allows more precise control of the output signals. Although the power consumption of an analog DLL is higher than a digital one and the design complexity is much enhanced, the analog DLL could provide a better jitter performance which is essential for our reference clocks generation. The problem of power consumption is released because the DLL is located outside the transmitter channel which results in a relatively low average power in each channel. Thus, an analog DLL is preferred in our design.

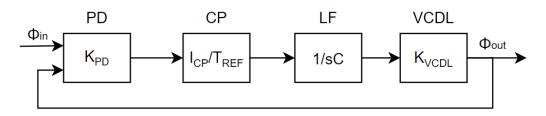

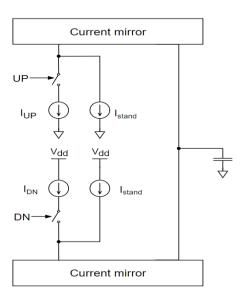

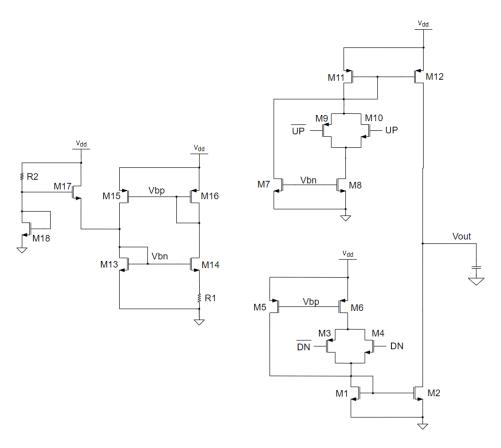

A loop dynamics model of the analog DLL is shown below for further analysis[23]. In Fig 3.3, the input phase  $\Phi_{in}$  is the original phase of signal CLK\_ref, and the output phase  $\Phi_{out}$  is the phase of the delayed signal CLK\_fb.  $K_{PD}$  is the gain of the phase detector with a unit of Volts/rad.  $I_{CP}$  is the charging current in the charge pump and  $T_{REF}$  is the period of CLK\_ref.  $K_{PD}$  is the gain of voltage-controlled delay line with a unit of rad/Volts. The loop filter is assumed as a single capacitor with its transfer function as F(s) = 1/sC.

Figure 3.3 Loop dynamics of analog DLL[23]

The output phase could be written as:

$$\Phi_{out} = (\Phi_{out} - \Phi_{in}) \cdot K_{PD} K_{VCDL} \cdot \frac{I_{CP}}{sC} \cdot f_{REF}$$

(3.1)

The transfer function of this loop is:

$$H(s) = \frac{\Phi_{out}}{\Phi_{in}} = \frac{1}{1 + \frac{s}{\omega_N}}, \omega_N = K_{PD} K_{VCDL} \cdot \frac{I_{CP}}{2\pi C} \cdot \omega_{REF}$$

(3.2)