#### Circuit Design for Highly Sensitive RF-Powered Wireless Sensor Nodes

Stoopman, Mark

10.4233/uuid:ac712c00-eb77-4097-9ab5-03c608e25923

**Publication date**

**Document Version**

Final published version

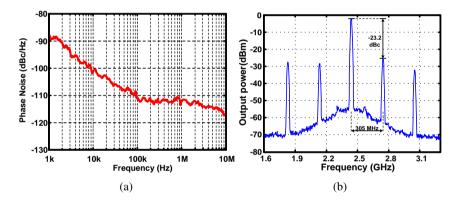

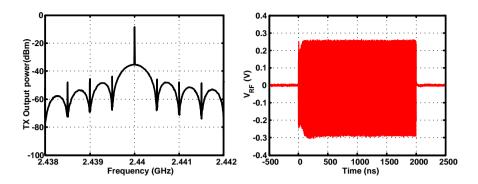

Citation (APA)

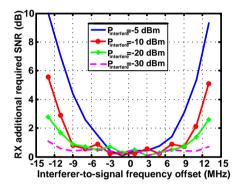

Stoopman, M. (2016). Circuit Design for Highly Sensitive RF-Powered Wireless Sensor Nodes. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:ac712c00-eb77-4097-9ab5-03c608e25923

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# **Circuit Design for Highly Sensitive RF-Powered Wireless Sensor Nodes**

**Mark Stoopman**

# Circuit Design for Highly Sensitive RF-Powered Wireless Sensor Nodes

#### **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op vrijdag 9 september 2016 om 12:30 uur

door

## **Mark STOOPMAN**

Elektrotechnisch ingenieur Delft University of Technology geboren te Rotterdam, Nederland Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. ir. W.A. Serdijn

#### Samenstelling promotiecommissie:

Rector Magnificus Technische Universiteit Delft, voorzitter Prof. dr. ir. W.A. Serdijn Technische Universiteit Delft, promotor

Onafhankelijke leden:

Prof. dr. ir. H.J. Visser Technische Universiteit Eindhoven Prof. dr. ir. P.G.M. Baltus Technische Universiteit Eindhoven

Prof. dr. ir. B. Nauta Universiteit Twente

Prof. dr. O. Yarovoy

Technische Universiteit Delft

Prof. dr. L.C.N. de Vreede

Technische Universiteit Delft

Anderen leden:

Dr. ir. K. Philips Imec/Holst Centre, adviseur

Keywords: RF energy harvesting, Antenna co-design, WSN, Power am-

plifier, Power management, Analog/RF IC design

Printed by: Ipskamp drukkers, the Netherlands

Copyright © 2016 by M. Stoopman

ISBN 978-94-028-0261-0

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

# **CONTENTS**

| Li | st of A | Abbreviations                                     | vi |

|----|---------|---------------------------------------------------|----|

| 1  | Intr    | roduction                                         | 1  |

|    | 1.1     | Energy Scavenged Wireless Sensor Nodes            | 1  |

|    | 1.2     | Market Forecast                                   | 2  |

|    | 1.3     | Target Applications                               | 3  |

|    | 1.4     | Design Challenges and Objectives                  | 5  |

|    | 1.5     | Organization of the Thesis                        | 6  |

| 2  | Mic     | ropower Energy Harvesting for WSNs                | 9  |

|    | 2.1     | The Power Balance                                 | 9  |

|    | 2.2     | Vibrational Energy Harvesting                     | 11 |

|    | 2.3     | Thermal Energy Harvesting                         | 13 |

|    | 2.4     | Photovoltaic Energy Harvesting                    | 15 |

|    | 2.5     | RF Energy Harvesting                              | 16 |

|    | 2.6     | Comparison                                        | 22 |

|    | 2.7     | Conclusions                                       | 23 |

| 3  | Syst    | tem Level Design                                  | 25 |

|    | 3.1     | System Level Description                          | 25 |

|    | 3.2     | RF Energy Harvesting                              | 27 |

|    | 3.3     | Power Management                                  | 28 |

|    | 3.4     | Frequency Synthesizer                             | 31 |

|    | 3.5     | RF Power Amplifier                                | 31 |

|    | 3.6     | Conclusions                                       | 32 |

| 4  | Ant     | enna-Electronics Interfaces in the Receiving Mode | 33 |

|    | 4.1     | Fundamental Antenna Parameters                    | 33 |

IV CONTENTS

|   | 4.2  | Wave     | Propagation and Available Power                    |

|---|------|----------|----------------------------------------------------|

|   | 4.3  | Anten    | na Equivalent Circuit Model 41                     |

|   | 4.4  | Wave     | Impedance and Impedance Matching 44                |

|   | 4.5  | Co-De    | esign of Antenna-Electronics Interfaces 45         |

|   |      | 4.5.1    | Co-Design Principle                                |

|   |      | 4.5.2    | Wireless Power Reception                           |

|   |      | 4.5.3    | Wireless Information Reception                     |

|   |      | 4.5.4    | Voltage, Current and Interface Impedance 48        |

|   | 4.6  | Co-De    | esign Examples                                     |

|   |      | 4.6.1    | Low Noise Amplifier                                |

|   |      | 4.6.2    | RF Energy Harvesting                               |

|   | 4.7  | Concl    | usions                                             |

| 5 | Higl | hly Sens | sitive RF Energy Harvester Design 57               |

|   | 5.1  | Introd   | uction                                             |

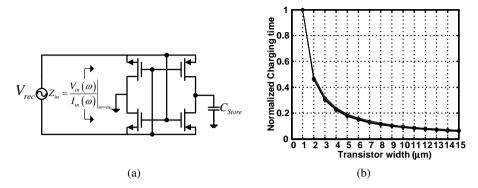

|   |      | 5.1.1    | Antenna-Rectifier Interface Modeling 59            |

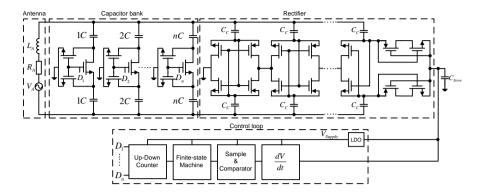

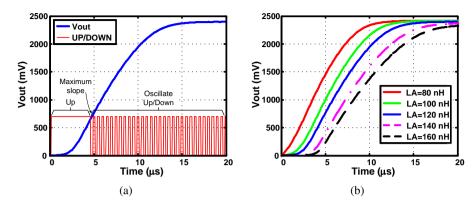

|   |      | 5.1.2    | Self-Calibrating Impedance Control Loop 61         |

|   | 5.2  | Rectifi  | ier Circuit Design                                 |

|   |      | 5.2.1    | Single Stage Rectifier 63                          |

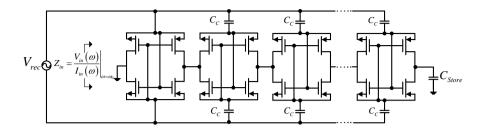

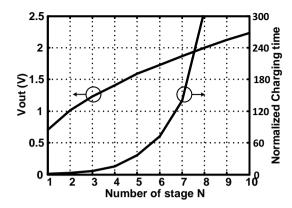

|   |      | 5.2.2    | Multi-Stage Rectifier 64                           |

|   |      | 5.2.3    | Rectifier Input Impedance 66                       |

|   |      | 5.2.4    | Switched Capacitor Bank 67                         |

|   |      | 5.2.5    | Reverse Current Leakage Reduction 68               |

|   |      | 5.2.6    | Control Loop Implementation                        |

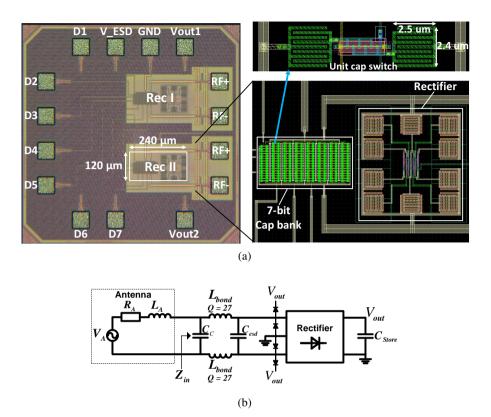

|   |      | 5.2.7    | Layout Design and Parasitic Components             |

|   | 5.3  | Anten    | na-Rectifier Co-Design                             |

|   | 5.4  | Experi   | imental Results                                    |

|   |      | 5.4.1    | Measurements in Anechoic Chamber                   |

|   |      | 5.4.2    | RF Energy Harvesting in a Realistic Environment 81 |

|   |      | 5.4.3    | Comparison with Previous Work 83                   |

|   | 5.5  | Concl    | usions                                             |

| 6 |      |          | Power Amplifier for Autonomous WSNs 85             |

|   | 6.1  | Introd   | uction                                             |

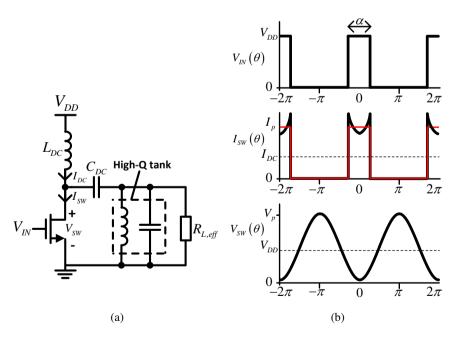

|   | 6.2  | Tuned    | Switching Power Amplifier Modeling 87              |

|   |      | 6.2.1    | PA Model Simplifications 88                        |

|   |      | 6.2.2    | PA Switch Losses                                   |

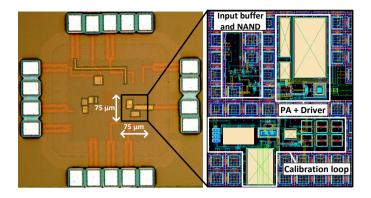

|   | 6.3  | Circui   | t Design                                           |

|   |      | 6.3.1    | Tuned Switching Power Amplifier 93                 |

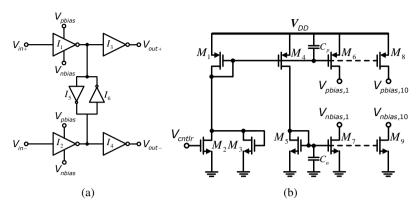

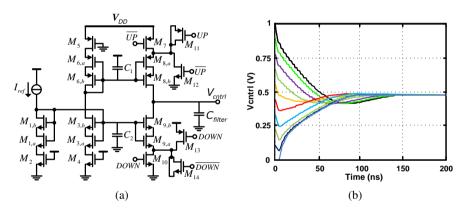

|   |      | 6.3.2    | PA Driver and Duty Cycle Calibration Loop 94       |

CONTENTS v

| Re | feren | ces      |                                       | 15   | q |

|----|-------|----------|---------------------------------------|------|---|

| C  | Sma   | ll Signa | l Analysis                            | 15   | 3 |

| В  | Ante  | nna Eq   | uivalent Circuit Model Limitations    | 14   | 9 |

| A  | Com   | ments (  | on RF Energy Harvesting Design Issues | 14   | 3 |

|    | 8.2   | Recom    | mendations for Future Research        | . 13 | 9 |

|    | 8.1   |          | Contributions of this Thesis          |      |   |

| 8  |       |          |                                       | _    |   |

| Q  | Con   | aluciono | and Recommendations                   | 13   | 7 |

|    | 7.11  | Conclu   | sion                                  | . 13 | 5 |

|    |       |          | Comparison with Previous Work         |      |   |

|    |       |          | Complete Transmitter                  |      |   |

|    |       |          | Power Management                      |      |   |

|    |       |          | RF Rectifier                          |      |   |

|    |       |          | Measurement Setup                     |      |   |

|    | 7.10  | •        | mental Results                        |      |   |

|    | 7.9   |          | Amplifier                             |      |   |

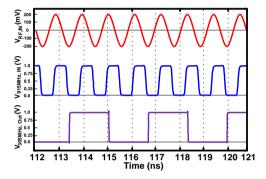

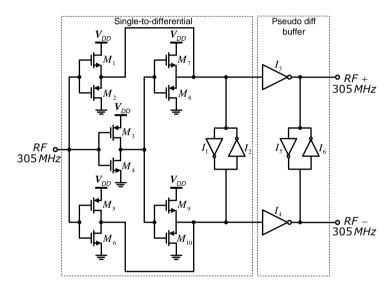

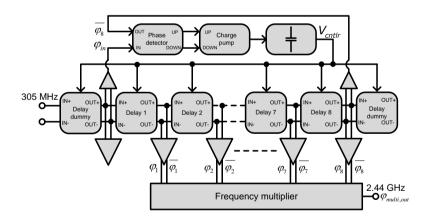

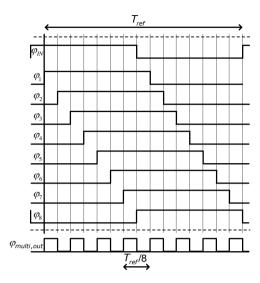

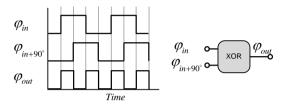

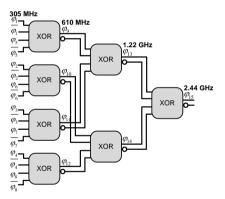

|    |       | 7.8.3    | Frequency Multiplier                  |      |   |

|    |       | 7.8.2    | Phase Detector and Charge Pump        |      |   |

|    |       | 7.8.1    | Voltage Controlled Delay Line         |      |   |

|    | 7.8   | Delay l  | Locked Loop and Frequency Multiplier  |      |   |

|    | 7.7   | _        | Ended-to-Differential Converter       |      |   |

|    | 7.6   |          | raction and Frequency Divider         |      |   |

|    | 7.5   |          | e Regulator                           |      |   |

|    | 7.4   |          | e-to-Current Converter                |      |   |

|    | 7.3   |          | e detector                            |      |   |

|    | 7.2   | Voltage  | Reference                             | . 10 | 5 |

|    | 7.1   | RF Ene   | ergy Harvester                        | . 10 | 4 |

| 7  | An F  | RF-Pow   | ered DLL-based 2.4 GHz Transmitter    | 10   | 3 |

|    | 6.5   | Conclu   | sions                                 | . 10 | 1 |

|    |       | 6.4.4    | Comparison with Previous Work         | . 10 | 1 |

|    |       | 6.4.3    | OOK and Pulse Shaping                 | . 10 | C |

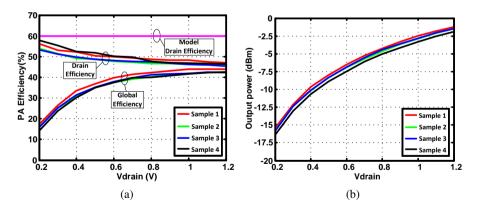

|    |       | 6.4.2    | Efficiency and Output Power           |      |   |

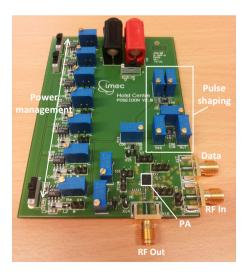

|    |       | 6.4.1    | Measurement Setup                     |      | 8 |

|    | 6.4   | Experi   | mental Results                        | . 9  | 7 |

|    |       | 6.3.4    | Pulse Shaping                         |      |   |

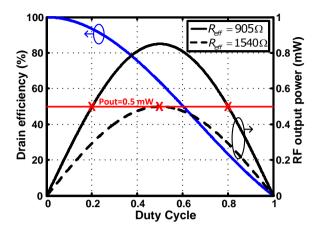

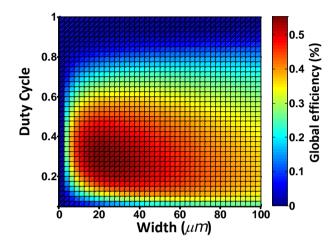

|    |       | 6.3.3    | Global Efficiency Optimization        | . 9  | 5 |

| Summary              | 171 |

|----------------------|-----|

| Samenvatting         | 175 |

| List of Publications | 179 |

| Acknowledgment       | 181 |

| Index                | 183 |

| About the Author     | 185 |

## LIST OF ABBREVIATIONS

ADC Analog-to-Digital Converter

CP Charge Pump

DLL Delay Locked Loop

DSP Digital Signal Processor

EIRP Equivalent Isotropic Radiated Power

EM Electromagnetic

ESD Electrostatic Discharge

FCC Federal Communications Commission

GE Global Efficiency

IC Integrated Circuit

IoT Internet of Things

ISM Industrial, Scientific and Medical

LDO Low-Dropout Regulator

LHP Left-Half Plane

LNA Low Noise Amplifier

LPF Low Pass Filter

MEMS Microelectromechanical System

MIM Metal-insulator-metal

MPPT Maximum Power Point Tracking

NF Noise Figure

OOK On-Off Keying

PA Power Amplifier

PCE Power Conversion Efficiency

PLL Phase-Locked Loop

PM Phase Margin

PSRR Power Supply Rejection Ratio

PVT Process-Voltage-Temperature

RF Radio Frequency

RX Receiver

SNR Signal-to-Noise Ratio

TX Transmitter

UGBW Unity Gain Bandwidth

VCDL Voltage Controlled Delay Line

WSN Wireless Sensor Node

## CHAPTER 1

## Introduction

## 1.1 Energy Scavenged Wireless Sensor Nodes

The vision of realizing a network of wireless sensor nodes (WSNs) attracted much attention over the years as it can serve a wide range of applications [1]. These WSNs can sense, process and wirelessly transmit information within the network such as temperature, humidity, location and sensor identification. This eliminates the need for wiring each individual sensor and thus can considerably reduce installation costs when deploying a large number of sensors. The targeted average power consumption of a WSN has been estimated by various authors to be in the order of 10 to 100  $\mu$ W [2–4], but strongly depends on the type of sensor and application. If this power is supplied by a battery, the maintenance costs can be relatively high compared to the initial purchase costs. For example, a network of 1500 WSNs with a battery lifetime of 4 years each will on average require one battery replacement per day. Although a network with 1500 connected devices may seem like a lot today, it is foreseen by various leading companies like NXP, Huawei, Qualcomm, Google, Cisco and Intel that the numbers of WSNs will exponentially grow over the coming years [5]. The market forecast of WSNs will be discussed further in Section 1.2.

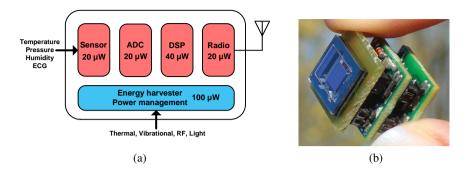

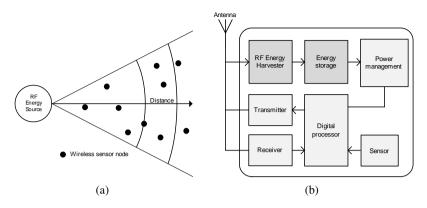

Providing the required power by means of an energy harvester makes the WSN truly autonomous and eliminates the need for battery replacement. Figure 1.1(a) shows a schematic representation of a typical energy scavenged WSN. The energy is supplied by an energy harvester that converts energy from one domain (for example thermal, mechanical or electromagnetic) into the electrical domain. A power management circuit subsequently distributes the harvested energy to the various circuit blocks such as a sensor, an Analog-

2 Introduction

Figure 1.1: (a) Schematic representation of a typical energy scavenged WSN [2]. (b) A 1 cm<sup>3</sup> cube shaped WSN powered from a vibrational energy harvester [6].

to-Digital Converter (ADC), a Digital Signal Processor (DSP) and a radio. Figure 1.1(b) shows an example of a 1 cm<sup>3</sup> cube shaped WSN powered only from a vibrational energy harvester [6].

The majority of today's WSNs however are still battery powered due to the many technological challenges of designing energy scavenged WSNs. First of all, the dependency of the available power on the surrounding environment is an important limitation as will be discussed more in Chapter 2. Another key reason why energy scavenged WSNs are not yet widely commercialized into products is the unequal balance between the power consumption of the WSN and the power generated by the energy harvester. As a consequence, the WSN is required to be heavily duty cycled and therefore spends the majority of its time in standby and harvesting mode, which limits the functionality and performance considerably. Moreover, the non-zero standby current consumption further limits the performance and becomes an important design factor. Innovations in both the energy harvester as well as the WSN circuit implementation are therefore required.

#### 1.2 Market Forecast

Accurately predicting the market value of WSNs over a ten year span is extremely difficult, if not impossible. Still, a range of reports and market forecasts have been published by independent research companies that all forecast substantial growth for the worldwide WSN market. This is a consequence of the progress made in affordable mass production and improved functionality which results in more applications and customer demands. Today's WSNs

unit prices are targeted at around \$10-\$15 and expected to decrease to \$9.80 in 2019 and \$0.40 in 2029 [7]. Eventually, WSNs will be small and cheap enough to for example be sprayed on floors, walls, buildings and roads.

IDTechEx forecasts that the total WSN market increases to \$1.8 billion by 2024 [7] whereas BCC Research estimates the global WSN market to reach \$4.3 billion by 2019 [8]. The wearable electronics market (medical, health-care, fitness, wellness sector), according to IDTechEx, will grow from over \$14 billion today to over \$70 billion in 2024 [9] due to the development investments of big companies such as Adidas, Nike, Philips, Samsung and Apple.

These forecasts all indicate that there is a huge number of potential applications for WSNs in the near future. Some of the target applications used for this thesis will be discussed next.

## 1.3 Target Applications

There are various potential applications that have inspired many research institutions and industry companies to explore WSNs. Some examples are industrial manufacturing, healthcare monitoring, agriculture, logistics, electronic shelf labeling, structural maintenance and the military [2, 10].

A more broadly described application is the 'Internet of Things', which was first coined by Kevin Ashton in 1999 [11] and describes the wireless connectivity between devices, systems and services via the internet. This includes everything from cell phones to cars, lighting, coffee makers, law enforcement agencies and wearable/implantable devices. These 'things' can share their data via the internet and have the ability to for example learn, memorize, monitor and notify their users and therefore extend the connectivity beyond traditional (local) machine-to-machine (M2M) communication. The company Cao Gadgets LLC for example developed a wireless sensor tag that monitors and records motion events and notifies its user in real-time via a phone or tablet with internet access [12]. Cisco estimates that 50 billion devices and objects will be connected to the internet by 2020, meaning that each person world wide will on average have six connected devices [13]. These kind of applications usually require a WSN with a low update rate (often less than one hertz) and a limited wireless range of several meters [14], which may be realizable with duty cycled energy scavenged WSNs.

In the remainder of this section, the main target applications for this thesis are discussed in more detail, which are smart buildings and warehouse inventory management.

4 Introduction

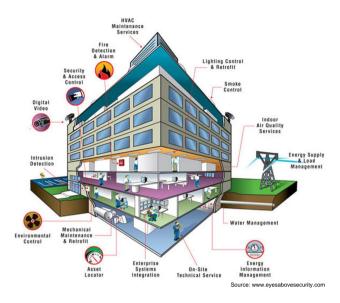

Figure 1.2: Illustration of various wireless sensor nodes in a smart building (courtesy of Eyes Above Security Systems Inc.).

#### **Smart Buildings**

The number of commercial buildings (i.e. office buildings, shopping malls and warehouses) in the United States alone sums up to approximately 5.6 million with a total of 8.11 billion m<sup>2</sup> of total floorspace [15]. The energy consumption of these buildings account for approximately 40% of total fossil fuel energy use [16]. With the rise of the world's most populous and fastest-growing countries such as China and India, it is expected that the energy consumed by these buildings will rise substantially in the near future. The impact on the environment is therefore high and long due to the building's long life cycle. This means that a huge opportunity exists to significantly reduce the net energy consumption. This is one of the driving forces behind so-called "smart buildings".

A smart building is a promising initiative and typical example of an IoT application. These intelligent systems require a large deployment of WSNs that for example monitor mechanical devices, temperature, light and the presence or absence of human beings as illustrated in Fig. 1.2. This allows to for example switch on the heating and lighting only in areas where they are needed. A network of WSNs consuming a few watt in total may thus enable total energy savings in the order of 10 to 30%, which can potentially lower the total

building power consumption by several kW [2]. The EnOcean Alliance for example develops energy harvesting wireless switches and sensors and claim 40% potential energy savings with 15% cost savings in new constructions and 70% cost savings in retrofits [17]. GreenPeak is another company that develops battery-powered radio chips for smart home applications like home security, lighting control and fire detection [18].

Besides reducing the net energy consumption, smart buildings can also provide intelligent monitoring of for example empty parking spaces, printers, waste bins, coffee machines and access control. Smart buildings thus have the potential to realize highly automated and efficient buildings with reduced energy consumption.

#### **Warehouse Inventory Management**

The average warehouse has a floor area of approximately 1000 m<sup>2</sup> [15]. In order to find a specific item in such a large area, an inventory list is required with the location of each item. Besides knowing the exact location, the food industry for example also benefits from knowing important conditions like the temperature, humidity and travel history of each item. Attaching a WSN with an unique identification number to each item thus allows the user to efficiently find remote items and view its conditions. In this scenario, it is important that the WSN costs need to be a fraction of the costs of the corresponding item and also relatively small in size.

## 1.4 Design Challenges and Objectives

The underlying objective of this thesis is to investigate, design and demonstrate an autonomous wireless sensor node powered solely by an energy harvester. One of the main challenges is to optimize the interface between the energy harvester and the WSN electronics for maximum sensitivity, efficiency and output power. This enables the possibility to use autonomous WSNs in new applications that previously where considered to be out of reach. The fundamental and practical limitations of various energy harvesters for the targeted application therefore first must be identified. The harvested energy should be utilized and distributed efficiently to each part of the WSN and thus requires efficient power management. Moreover, a suitable wireless communication system architecture is required that can be implemented with low power consumption and low cost. Hence, innovations at both the energy harvester as well as the power management and wireless communication system architecture.

6 Introduction

tecture are needed in order to improve the overall functionality and power efficiency, size, cost and reliability,

#### 1.5 Organization of the Thesis

The work presented in this thesis is organized as follows.

In **Chapter 2** a general overview is given of micropower energy harvesting related to WSN applications. Four different energy harvesting approaches will be explored: vibrational, thermal, photovoltaic and RF. For each approach, the pros and cons are evaluated with respect to the potentially generated power, reliability, size and design challenges.

In **Chapter 3**, a system level description is given of an RF-powered transmitter to be used for WSN applications. Several design aspects, challenges and requirements are discussed in this chapter, thereby providing a framework for the following chapters.

**Chapter 4** first treats some basic antenna and wave propagation fundamentals that lead to a general antenna equivalent circuit model. Subsequently, the co-design of antenna-electronics interfaces in the receiving mode is investigated, which includes optimum reception of wireless information and wireless power.

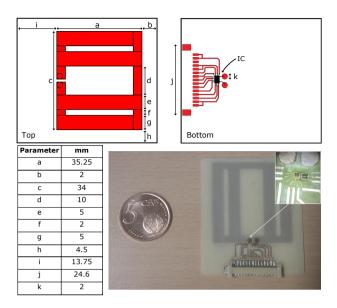

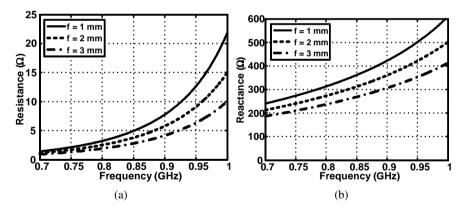

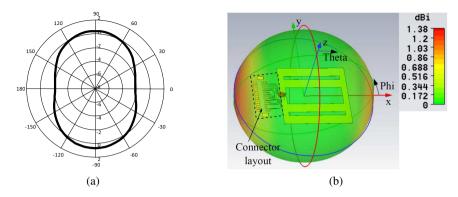

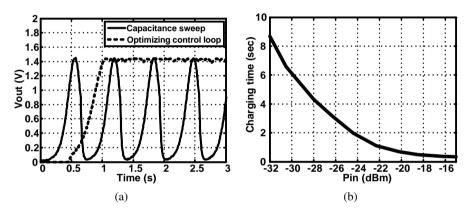

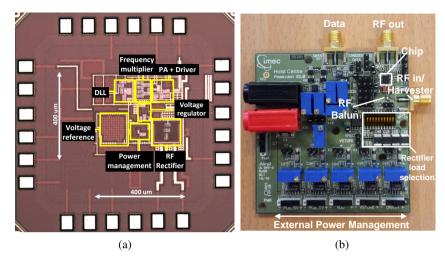

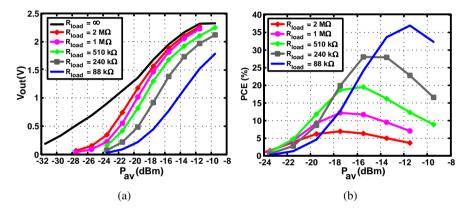

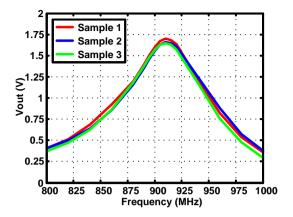

**Chapter 5** uses the conclusions from the previous chapter and discusses the design procedure of a compact self-calibrating and highly sensitive RF energy harvester in 90 nm CMOS technology. First the design challenges and the proposed solution are discussed, followed by the circuit design of an RF rectifier. Then, the co-design with a custom designed antenna is presented and the experimental results in an anechoic chamber are discussed.

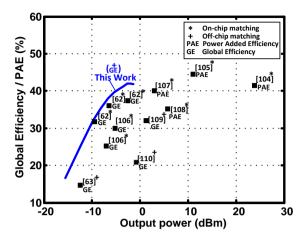

In **Chapter 6,** the theory and circuit design of a high efficient 2.4 GHz tuned switching power amplifier (PA) with <0 dBm output power is presented. An on-chip duty cycle calibration loop is proposed to enhance drain efficiency while the PA driver is optimized for high global efficiency. The experimental results of a 40 nm fabricated prototype are discussed and compared to the state-of-the-art.

**Chapter 7** combines the work of the previous chapters and presents a compact RF-powered 2.4 GHz transmitter in 40 nm CMOS. First the circuit design of various blocks is described such as RF energy harvesting, power management, RF extraction, frequency divider, delay locked loop and a frequency multiplier. Subsequently, the experimental results of the prototype TX are extensively reported.

Finally, conclusions and recommendations for future research are presented in **Chapter 8**.

8 Introduction

## CHAPTER 2

# MICROPOWER ENERGY HARVESTING FOR WSNs

People have been using nature's energy sources for hundreds of years by constructing various kinds of watermills and windmills. Today, large-scale wind turbines and solar power plants are developed to meet the 20% renewable energy target by the year 2020 set by the European Union [19].

The driving force for *micropower* energy harvesting is the desire to realize maintenance-free autonomous WSNs. In this chapter, first an overview is given of micropower energy harvesting in general related to WSN applications. Subsequently, four different energy harvesting approaches will be discussed: vibrational, thermal, photovoltaic and RF. For each approach, the pros and cons are evaluated with respect to potentially generated power, reliability, size and design challenges.

#### 2.1 The Power Balance

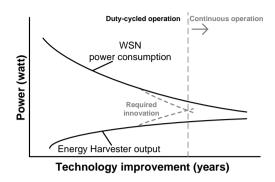

The Achilles' Heel of today's energy scavenged WSNs is the unequal balance between the power *consumption* of the WSN and the power *generated* by the energy harvester. This is shown graphically in Fig. 2.1. On one side of the scale, the power consumption of integrated circuits decreases over time with more advanced CMOS technologies and circuit designs. The energy harvester on the other side of the scale also benefits from these improvements and thus becomes more efficient in converting energy from other domains into electrical energy. Of course, these curves are highly speculative as they depend on many factors such as sensor functionality, type of harvester, the available power of the energy source and the application.

Figure 2.1: General power balance between energy harvester output and power consumption of a WSN.

It may be argued that the intersection of these two curves may be inevitable due to technology improvements. This however, may not be the case for a number of reasons. Firstly, the difference between the required power and the available power to the harvester may simply be too large for a specific application. A second reason is that the scaling of CMOS devices may not be beneficial for the performance of analog circuits. With a lower supply voltage, the performances at some point are limited by the circuit noise. If the signal-to-noise ratio and dynamic range are required to remain the same, then lowering the supply voltage can actually *increase* the power consumption. Hence, innovations at both the energy harvester and the WSN are needed in order to equalize the power balance. Once this can be realized, it will create the possibility to use autonomous WSNs in new applications that previously where out of reach.

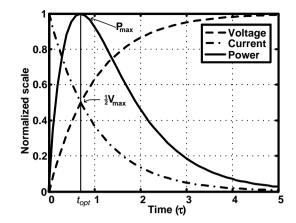

At the point where these curves intersect, the energy harvester provides enough power to continuously operate the WSN. For the majority of today's WSN applications, this point has not been reached yet, meaning that the WSN needs to be duty-cycled. With duty-cycled operation, the energy harvester output first is locally stored in a battery or (super)capacitor. When enough energy is accumulated over time, the WSN can be powered for a short period. This way, a mW power budget can be realized when harvesting at  $\mu$ W power levels.

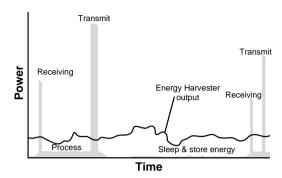

A typical power profile of a duty-cycled energy scavenged WSN is sketched in Fig. 2.2. The peak power consumption during transmitting and receiving typically is significantly higher than the energy harvester output, but is only required for a short time. Between reception and transmission, the

Figure 2.2: Typical power profile of a duty-cycle energy scavenged WSN.

WSN measures and processes the sensor input. For the rest of the time, it is in energy harvesting mode. Low-power and adaptive power management is thus required for optimum performance.

The power generated by the energy harvester can fluctuate strongly over time and depends on the type of energy harvester and its environment. To determine the potentially generated output power, first different types of energy harvesters need to be investigated and compared on aspects such as output power, reliability, size, costs and possible applications. The energy harvesters that will be briefly discussed in the following sections are vibrational, thermal, photovoltaic and RF energy harvesters.

## 2.2 Vibrational Energy Harvesting

Vibrational energy harvesters are well studied in the energy harvesting literature. Basically, there are three ways of converting vibrations into energy [20]:

- Electrostatic: A pre-charged capacitor with two opposing metal structures where one metal plate is displaced due to an external force. This external force changes the capacitance and voltage (assuming constant charge mode) and converts the mechanical motion in electrical energy.

- Piezoelectric: Vibration or movement causes the deformation of a piezoelectric material, thereby generating a charge.

- Electromagnetic: The displacement of a magnetic mass with respect to a coil produces a change in the magnetic flux. The change in flux generates a voltage.

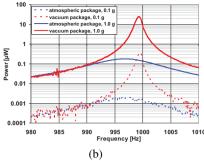

Figure 2.3: (a) Piezoelectric MEMS energy harvester and (b) measured generated power for an atmospheric and vacuum packaged device with acceleration of 0.1 g and 1.0 g (picture courtesy of Imec/Holst centre [6]).

Figure 2.3(a) shows a piezoelectric energy harvester that utilizes a vacuum-packaged microelectromechanical system (MEMS) to reduce the air damping, thereby improving the power output at all frequencies. The output power depends on the acceleration and the frequency of the vibration. Typically, vibrational energy harvesters are most sensitive to vibrations that are close to their natural frequency. The harvester thus needs to be designed for a specific frequency range that corresponds to the vibrations found in the targeted application.

Typical usage for vibrational energy harvesters are applications with moving parts such as machines, engines and other industrial devices. An intelligent car tire with built-in pressure sensors can for example be powered by means of a vibrational energy harvester. Each time when the tire with the embedded harvester contacts the road, a high amplitude shock of up to a few hundred g is generated for velocities above 80 km/h [21]. Each shock will cause the harvester to ring down at its natural resonance frequency and convert mechanical energy into electrical energy. Peak output powers of 489  $\mu$ W have been reported with an average output power of 42  $\mu$ W at 70km/h [21]. This power allows the wireless pressure sensor to communicate with the vehicle computer and indicate the driver when the tires are under-inflated. This not only prevents unneeded fuel pollution, but also makes the vehicle safer to drive.

Another well studied target application is energy harvesting from human motion to power wearable electronics. When running at 10 km/h, accelerations around 3 g with peaks up to 7 g can be expected [22]. This large potential source of energy has been used to develop energy harvesting shoes [23–25]

and backpacks [26] which can provide an average output power between 0.4-2 mW while walking at a frequency of roughly 1 Hz to 10 Hz. Although this output power is larger than that of the harvester example shown in Fig. 2.3(b), this energy harvester is also significantly larger in size (~200 cm<sup>2</sup>), which may be too big for many applications.

The open-circuit AC voltage of vibrational harvesters is relatively high compared to other harvesters and varies roughly between 0.8 and 10 V at a frequency of a few kHz at most. An AC/DC converter with these specifications can for example be implemented with active diodes combined with a DC-DC boost converter, resulting in very high power conversion efficiencies above 90% [27].

A major disadvantage of vibrational energy harvesters is that the number of applications that provide a reliable and constant source of energy near the resonant frequency is limited as the vibrations are often unpredictable. A more complete overview of energy harvesting from human and machine motions can be found in [28].

## 2.3 Thermal Energy Harvesting

Thermal energy harvesters are based on the Seebeck effect. When a temperature difference is established between two sides of dissimilar materials as illustrated in Fig. 2.4(a), a voltage develops between point A and B as described by

$$V_{AB} = -(\alpha_A - \alpha_B)(T_{hot} - T_{cold})$$

(2.1)

where  $V_{AB}$  is the potential difference [V],  $\alpha_A$  and  $\alpha_B$  are the Seebeck coefficients of materials A and B respectively [V/K] and  $(T_{hot} - T_{cold})$  is the temperature difference between the hot and the cold source [K] [20]. The output voltage of a single thermocouple is very small as the Seebeck coefficient is only in the order of 0.2 mV/K for semiconductor material. Either a very large temperature difference is thus required, or a large number of thermocouples (called a thermopile) connected thermally in parallel and electrically in series is needed.

A recent development in the area of wearable energy harvesters is a thermoelectric shirt with 16 thermopiles integrated between two textile layers of the shirt [29]. A temperature difference is created by placing the hot plate in contact with the skin under the textile, which is at a temperature of approximately  $37\ ^{\circ}C$ . The cold plate is placed about 4 mm from the cotton layer such that it is cooled by ambient air flow. When combining the harvested power of all

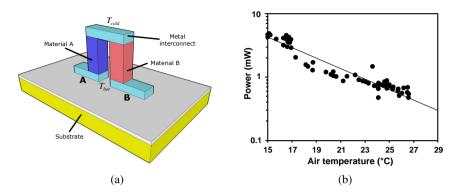

Figure 2.4: (a) Single thermocouple and (b) the measured generated power of a human subject wearing a thermoelectric shirt with multiple thermocouples (picture courtesy of Imec/Holst centre [29]).

16 thermopiles, an average output power between 0.5–5 mW was measured for ambient air temperatures between 27 and 15  $^{\circ}C$  as shown in Figure 2.4(b). Smaller sized thermal harvesters have also been mounted in a wrist-watch and generate an average power of about 250  $\mu$ W at 22  $^{\circ}C$  air temperature [30]. Another field of interest is the aerospace industry as aircrafts are exposed to large thermal gradients. Depending on the location of the harvester, peak generated power levels between 5-35 mW may be feasible [31].

The advantage of thermal energy harvesters is that there are no moving parts in contrast to the vibrational harvester, which allows reliable and long continuous operation. But unfortunately, thermal harvesters are inefficient for low temperature differences and require a large number of thermocouples to generate a sufficiently high voltage, making them expensive to fabricate. Alternatively, a smaller amount of thermocouples may be used in combination with a DC-DC converter that boosts the generated voltage to useful levels. The challenge then is to design a highly efficient converter that can operate at very low input voltages and is powered by the harvested energy itself. This has been the subject of many studies on inductive boost converters [32, 33] and charge pumps [34,35]. The reported efficiencies are ranging between 46-92%, depending on the input voltage, and can be used for input voltages as low as 20 mV [36].

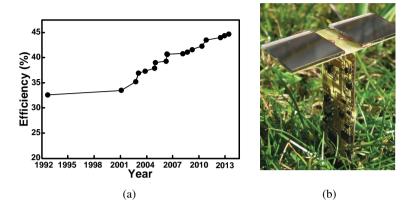

Figure 2.5: (a) Efficiency records of photovoltaic cells under solar spectra [38] and (b) a prototype of a solar powered WSN (picture courtesy of Mina Danesh [39]).

## 2.4 Photovoltaic Energy Harvesting

When a photon is absorbed by a photovoltaic cell, an electron-hole pair is generated provided that the incident photon has an energy greater than that of the material's bandgap. The presence of the internal electric field inside the p-n junction of the solar cell facilitates the separation of the photon generated electron-hole pairs and forces an electric current to flow through an external load. This process however is not 100% efficient as the sunlight spectrum consists of photons with different energy levels. Photons with energy less than the material's bandgap are not able to generate an electron-hole pair and thus do not contribute to the output current. A photon with more energy than the required bandgap energy loses its extra energy in the form of heat (unless the photon has exactly enough energy to create two or more electron-hole pairs). To prevent this loss mechanism, multi-junction cells with multiple bandgaps have been proposed over the years to absorb a broader range of photon energy levels. The record conversion efficiency of the last 20 years is illustrated in Fig. 2.5(a), showing an increased performance towards the current record efficiency of 44.7% [37]. Commercially (and cheaper) available photovoltaic cells however typically have a lower efficiency of about 20% or less.

For outdoor applications, the power density of solar radiation on the earth's surface is about 100 mW/cm<sup>2</sup> at noon on a clear day and roughly 30 mW/cm<sup>2</sup> or less for a cloudy day [20, 40]. Thus, a harvested power of about 6-20

mW/cm² can be expected when using commercially available photovoltaic cells. For indoor applications however, the situation is much different since the light intensity of artificial lighting conditions found in office buildings are typically below 100  $\mu$ W/cm² [41]. This limits the harvested power to about 10  $\mu$ W/cm² as a lower light intensity also corresponds to a lower conversion efficiency.

The challenge for small-scale solar harvesting is to generate sufficient power with limited area. Figure 2.5(b) shows an example of a WSN powered by a flexible photovoltaic cell that generates 20 mW under ideal outside conditions [40]. To minimize the WSN size, this prototype uses an antenna that is integrated on the back of the photovoltaic cell together with a radio transmitter, power management and a super capacitor. A maximum power point tracking (MPPT) circuit is required as a photovoltaic cell can operate over a wide range of voltages and currents for irregular light exposures [42]. In 2011, the university of Michigan presented a cubic-millimiter sized energy-autonomous wireless intraocular pressure monitor that is powered by a 0.07 mm<sup>2</sup> integrated solar cell [43]. Due to the extremely small size, the solar cell can only generate 80.6 nW of power. In this case, the circuit power consumption and its leakage current becomes very important to the overall performance of the WSN.

The disadvantage of photovoltaic energy harvesting is that the available power of the photovoltaic energy harvester is strongly dependent on the application and location. Solar energy harvesting is a very good candidate for outdoor applications with direct sunlight like greenhouses and farms, but may fall short compared to other type of energy harvesters for indoor applications.

## 2.5 RF Energy Harvesting

The transfer of wireless energy by means of electromagnetic waves can be categorized into non-radiative and radiative energy transfer. Near-field inductive coupling belongs to the non-radiative category and is based on two magnetically coupled coils in resonance. This energy transfer method has been extensively studied for wireless powering and is widely used for example to power implantable devices [44, 45]. For near-field coupling, the coils need to be in close proximity, typically within the same dimension as the coil. The coil dimension in turn is determined by the operating frequency, which often is in the order of a few MHz. Recently, Stanford University showed that significantly higher efficiencies can be obtained in the electromagnetic mid-field (a region between the near-field and far-field) when for example wirelessly

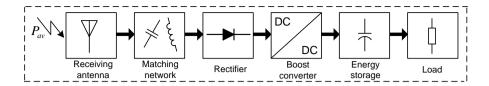

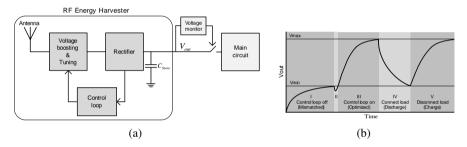

Figure 2.6: General receiving far-field RF energy harvesting system with power management [48].

transferring power to implantable devices [46]. Although this operating region extends the wireless range compared to near-field coupling, it is limited to about 3-10 times the coil radius [47], which may still be too short for WSN applications.

To further increase the wireless range, far-field power transfer needs to be used. Unlike inductively coupled systems, far-field systems radiate and receive in all directions when assuming an isotropic radiator and receiver. Although this can be conceived as a disadvantage as power is 'lost' in directions other than the desired one, it can be turned into an advantage for applications that require multiple targets spread out over a large area that need to be powered.

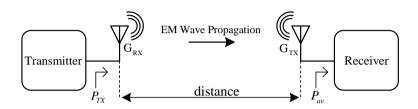

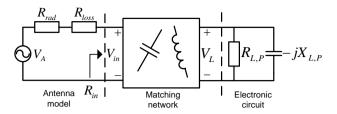

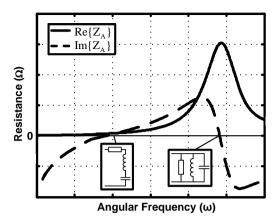

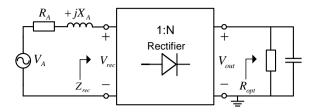

A far-field RF energy harvesting system generally consists of a receiving antenna, matching network, rectifier and power management (DC-DC converter) as illustrated in Fig. 2.6. The antenna converts the electromagnetic signals to electrical voltages and currents, which are related to the available power  $P_{av}$ , antenna impedance and the rectifier input impedance. The available power can originate from ambient or dedicated RF energy sources, which are briefly discussed below.

#### **Ambient RF Energy**

Ambient RF energy sources such as TV, GSM and WLAN base stations are omnipresent in most of today's societies. It thus sounds very promising to 're-use' these signals to realize truly autonomous wireless sensors. In [49], an experiment was conducted to measure the received signal strength and probability in urban and suburban areas between 800 and 900 MHz. In an urban area, the received signal strength was most likely to be around -20 to -40 dBm with a peak probability of 31% around -33 dBm. In a less dense populated environment, this peak was around -37dBm with a probability of 27%. Similar results have been found in [50], where the ambient RF power density at a distance between 25-100 meters from a 900 MHz GSM base station was

found to be between 0.01-0.1  $\mu$ W/cm<sup>2</sup> (around -30 to -20 dBm).

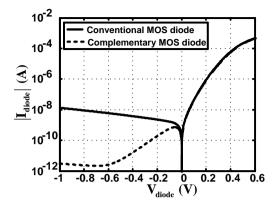

Whether or not these power levels are high enough to be used for RF energy harvesting, can be determined by calculating the rectifier startup power threshold. As practical components used for rectification need a minimum voltage in order to conduct current, the RF energy harvester is limited by the rectifier startup threshold voltage  $^{1}V_{rec,threshold}$ . The startup power threshold  $P_{startup}$  then is given by

$$P_{startup} = \frac{V_{rec,threshold}^2}{2\eta_A R_{rec,p}}$$

(2.2)

where  $\eta_A$  is the receiving antenna radiation efficiency and  $R_{rec,p}$  is the equivalent parallel input resistance of the rectifier [51]. For a single Schottky rectifier implementation with  $R_{rec,p} = 1 \text{ k}\Omega$ ,  $V_{rec,threshold} = 0.3 \text{ V}$  and  $\eta_A = 0.8$ , the minimum required power for rectification equals  $56.25 \mu\text{W}$  (-12.5 dBm). The power conversion efficiency will likely be low around this startup threshold as the diode is just barely forward biased. Typically, the rectifier becomes more efficient for larger input power levels. If  $V_{rec,threshold}$  for example can be reduced to 0.1V, the startup threshold is lowered to -22 dBm, giving a sensitivity improvement of 9.5 dB. Harvesting from ambient RF energy sources thus requires a very sensitive rectifier. In general, ambient RF power levels are considered to be too low to be used for RF energy harvesting as they are often around or below the power startup threshold of the rectifier.

There are however some scenarios with higher ambient RF power levels such as in high-density locations like public transport and festivals [52]. Another approach to is to simultaneously harvest from multiple frequency bands as demonstrated in [53].

#### **Dedicated RF Energy**

Alternatively, a more powerful and reliable *dedicated* RF energy source can be used in the vicinity of the devices that need to be powered wirelessly. The available power<sup>2</sup>  $P_{av}$  to the receiving antenna in free space using a perfectly aligned and conjugate matched antenna is described by the Friis transmission equation

$$P_{av} = \left(\frac{\lambda}{4\pi d}\right)^2 G_{RX} P_{EIRP} \tag{2.3}$$

<sup>&</sup>lt;sup>1</sup>The startup threshold voltage does not necessarily equal the diode or transistor threshold voltage, it is also a function of the number of rectifying stages and the rectifier circuit topology.

<sup>&</sup>lt;sup>2</sup>The concept of available power and other antenna fundamentals will be discussed in more detail in Chapter 4.

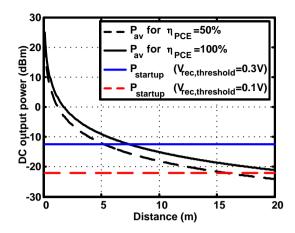

Figure 2.7: Calculated DC output power vs. distance with startup power threshold limit for  $P_{EJRP}$ =3.28 W,  $\lambda$ =0.345 m and  $G_{RX}$ =1.25.

where  $P_{EIRP}$  is defined as the Equivalent Isotropic Radiated Power (EIRP) of the RF source,  $G_{RX}$  is the receiving antenna gain of the RF harvester, d is the distance between the RF source and the receiving antenna and  $\lambda$  is the wavelength [54]. The maximum available power at a given distance from the RF source is thus limited by the frequency, antenna gain and the maximum allowed  $P_{EIRP}$ , which is defined by international regulations. The license-free Industrial, Scientific and Medical (ISM) frequency bands are often used for dedicated RF harvesting applications since they allow for a high  $P_{EIRP}$  with acceptable antenna sizes. The European Radio communications Commission (ERC) limits the maximum  $P_{EIRP}$  at 868 MHz to 3.28 W and to 4 W at 2.45 GHz [55]. The U.S. Federal Communications Commission (FCC) limits both the power levels at the 915 MHz and 2.45 GHz bands to 4 W EIRP [56]. As a practical example, Fig. 2.7 shows the harvested DC output power versus distance for the case of a rectifier power conversion efficiency  $\eta_{PCE}$  of 50% and 100%. A line-of-sight scenario is assumed with  $P_{EIRP}$ =3.28 W,  $\lambda$ =0.345 m (868 MHz) and  $G_{RX}$ =1.25. For  $\eta_{PCE}$ =50%, a DC output power of about 61.8  $\mu$ W can be achieved at a distance of 5 meter and 6.87  $\mu$ W at 15 meter. When calculating the power transfer efficiency to a single WSN at 5 meter, the efficiency is only 0.0019% as the power of the RF source is also radiated in other directions and does not contribute to the received power of the WSN. This approach is thus only cost efficient if a large multiple of WSNs is employed that are all powered by the same RF source. However, if an intelligent RF source is used that tracks the sensor node and steers a highly

directive beam towards the WSN when it requests charging, it is possible to improve the overal system efficiency.

The maximum wireless range however is limited by the startup power threshold as indicated by the horizontal lines in Fig. 2.7. In this example, a reduction in rectifier threshold voltage from 0.3V to 0.1V increases the maximum achievable distance from 5 meters to 15.7 meters for  $\eta_{PCE}$ =50%. This indicates the importance of minimizing  $P_{startup}$  in case the regulations do not allow to increase the radiated power any further.

#### Distribution of RF Harvested Power in an Office Environment

Even with a dedicated RF source, the harvested power can vary significantly in a realistic environment due to the many unknown variables in the propagation channel. To get a better understanding of the distribution of RF harvested power in various scenarios, an experiment was conducted.

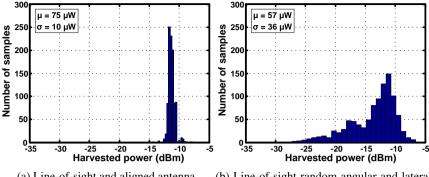

Fig. 2.8 shows the measured harvested RF power in an office room (~24 m²) at 915 MHz for three different scenarios using a Powercast P2110-EVAL-02 RF energy harvester [57] with 1 dBi receiving antenna gain at 3.5 meter distance from a single 3 W EIRP dedicated RF source. In each scenario, the harvested RF power is measured using 1000 samples taken over a period of 30 minutes.

The first figure shows a static office environment with line-of-sight and aligned antenna. The mean harvested power  $(\mu)$  is 75  $\mu$ W with a standard deviation  $(\sigma)$  of 10  $\mu$ W. The scenario shown in Fig. 2.8(b) shows the harvested power in case of a line-of-sight and random angular and lateral misaligned antenna. Here, a mean value of 57  $\mu$ W was measured with a standard deviation of 36  $\mu$ W. The last scenario is non-line-of-sight with random misaligned antennas in a highly dynamic office room with people walking in between the transmitter and RF harvester. The mean harvested power in this case was 25  $\mu$ W with a standard deviation of 21  $\mu$ W.

As expected, the average harvested power not only decreases in a more dynamic scenario, but also the standard deviation becomes relatively larger. Although these measurements strongly depend on the environment and the RF energy harvester being used, they demonstrate that the RF energy harvester needs to be designed for high sensitivity when used in a dynamic environment. These fluctuations therefore need to be considered at system level and again demonstrate the need for an intelligent RF source.

- (a) Line-of-sight and aligned antenna.

- (b) Line-of-sight random angular and lateral misaligned antenna.

(c) Non-line-of-sight with random angular and lateral misaligned antenna.

Figure 2.8: Measured distribution of RF harvested power in an office room (~24 m<sup>2</sup>) for different scenarios taken over a 30 minutes period.

Since the open-circuit AC antenna voltage of RF energy harvesters usually is relatively small (<0.5V) compared to vibrational energy harvesters, it poses a challenge for the rectifier design. Also the relatively high operating frequency in the ISM bands (GHz range) does not allow for a low-power active diode rectifier implementation. A complete and thorough study of the antenna-rectifier interface is thus required in order to optimize the overall system performance.

The advantage of RF energy harvesting is that it can be used in applications where vibrations, light and temperature gradients are not always available or unpredictable such as in warehouses and smart buildings. Moreover, besides delivering energy, the RF source can also serve as a communication hub and provide a system clock by modulating the RF carrier wave [58]. This unique advantage can greatly reduce the radio power consumption of the WSN as it eliminates an on-chip signal generator.

## 2.6 Comparison

A choice needs to be made which harvester is most suited for the target application (warehouse and smart buildings). To compare the four different energy harvesters, an overview is given in Table 2.1. The potential harvested power is compared per cm<sup>2</sup>, which gives a fair and good indication of the desired harvested power and required size.

When comparing only on harvested power density, it follows that outdoor photovoltaic and thermal industrial harvesting outperform other harvesters. However, these energy sources are likely not to be available for the target application. Also energy from human vibrations and ambient RF energy is considered not to be a reliable and useful source for the target application. This leaves indoor photovoltaic, thermal and dedicated RF energy harvesting as potential candidates, which have comparable power density levels. Dedicated RF energy harvesting however can serve a large variety of applications, even in thermally constant, dark and static environments. Moreover, additional possibilities such as using the RF energy source as a data and clock distribution hub greatly reduces the power consumption of the WSN. Also the fabrication costs of an RF antenna are much lower than that of a photovoltaic cell. With the advances in flexible electronics, the WSN and antenna can even be integrated on the same flexible substrate. With this reasoning, it is decided that RF energy harvesting is the most suited energy harvester for the target application.

2.7: CONCLUSIONS 23

| Table 2.1: Overview of potentially available and harvested power of various |

|-----------------------------------------------------------------------------|

| energy harvesters (based on data from [20]).                                |

|                | Power Source                              | Harvested Power Density        |

|----------------|-------------------------------------------|--------------------------------|

| Vibrational    |                                           |                                |

| Human          | 0.5 m at 1 Hz 1 m/s <sup>2</sup> at 50 Hz | $4 \mu \text{W/cm}^2$          |

| Industrial     | 1 m at 5Hz 10 m/s <sup>2</sup> at 1 kHz   | $100 \mu\mathrm{W/cm^2}$       |

| Photovoltaic   |                                           |                                |

| Indoor         | <0.1 mW/cm <sup>2</sup>                   | <10 μW/cm <sup>2</sup>         |

| Outdoor        | 30-100 mW/cm <sup>2</sup>                 | 6-10 mW/cm <sup>2</sup>        |

| Thermal Energy |                                           |                                |

| Human          | 20 mW/cm <sup>2</sup>                     | $30 \mu\text{W/cm}^2$          |

| Industrial     | 100 mW/cm <sup>2</sup>                    | 1-10 mW/cm <sup>2</sup>        |

| RF             |                                           |                                |

| Ambient        | $0.01\text{-}0.1 \ \mu\text{W/cm}^2$      | <0.03 μW/cm <sup>2</sup>       |

| Dedicated      | $0.5-50 \mu\text{W/cm}^2$                 | $0.15-20 \; \mu \text{W/cm}^2$ |

#### 2.7 Conclusions

An overview has been given of micropower energy harvesting for autonomous WSN applications. The unequal balance between the power consumption of the WSN and the power generated by the energy harvester requires most autonomous WSNs to be duty-cycled. When enough energy is harvested over time, the WSN can be powered for a short period. This way, a mW power budget can be realized when harvesting at  $\mu$ W power levels.

Four different energy harvesting approaches where discussed: vibrational, thermal, photovoltaic and RF. Outdoor photovoltaic and thermal industrial energy harvesters are able to generate more power than other harvesters, but do not match the target application (warehouse and smart buildings). Also the energy from ambient RF, human vibrations and human thermal sources are considered to be too low, not reliable and not available for the target application.

Dedicated RF energy harvesting however can offer a large variety of applications, even in thermally constant, dark and static environments. Moreover, additional possibilities such as using the RF energy source as a data and clock distribution hub greatly reduces the power consumption of the WSN. Also the fabrication costs of an RF antenna is relatively low. The design challenge for RF energy harvesting is the relatively small (<0.5V) open-circuit voltage of the receiving antenna at relatively high operating frequency in the ISM

bands (GHz range). Especially for low input power levels (i.e., a long wireless range), a very sensitive rectifier is required. A complete and thorough study of the antenna-rectifier interface is thus required in order to optimize the overall system performance.

The conclusions drawn in this chapter are used as input for the following chapter, in which a system level description is given and several design aspects are discussed for an RF-powered transmitter.

## CHAPTER 3

## SYSTEM LEVEL DESIGN

In the previous chapter it was concluded that RF-powered WSNs have the distinct advantage over other energy harvesting systems that they can operate wirelessly in a large variety of applications, even in thermally constant, dark and static environments. This chapter discusses several system aspects, challenges and requirements for the design of RF-powered WSNs.

## 3.1 System Level Description

The absence of a stable reference frequency in low cost and power efficient WSNs makes it very challenging to implement a low power wireless communication architecture. Passive RFID backscattering therefore has been a popular choice because of its simplicity and low power consumption [59,60]. By simply altering the input impedance of the RFID tag, the incoming RF wave is backscattered from the RFID antenna with different amplitude and phase and thus can be used to encode information. Since this process re-uses the energy from the incoming RF wave for wireless transmission, it is not required to generate an RF carrier and thus can be implemented with minimum power consumption. The functionality and operating range however are limited and the system can suffer from reader self-jamming as the backscattered signal is at the same frequency as the signal transmitted by the RFID reader [61]. Other solutions have been proposed that utilize a local oscillator for RF carrier generation [62]. This not only requires significant power, but also is very challenging to realize with sufficient accuracy over processvoltage-temperature (PVT) variations.

Surface acoustic wave (SAW) and film bulk acoustic resonators (FBARs) can provide a high Q and extremely accurate reference frequency and therefore

have been used to generate RF carriers in low power transmitters [63, 64]. These resonators however are relatively bulky and often cannot be integrated on chip, thereby increasing the fabrication costs of the WSN even further. In [65] a crystal-less RF-powered transceiver has been proposed. By using the 915 MHz received carrier frequency as reference frequency in a Phase-Locked Loop (PLL), an accurate 2.4 GHz signal could be realized to be used for wireless data transmission. These frequencies are conveniently located in the license-free Industrial, Scientific and Medical (ISM) bands [56] and thus can be used for frequency synthesis in order to realize a compact, frequency stable and power efficient solution. A similar architecture has been proposed in [66], where the received signal is fed into an injection-locked frequency multiplier to generate a 402 MHz carrier. Another architecture in [67] has been proposed for an RF-powered RFID tag with on-chip antennas. In this architecture, a 5.8 GHz dedicated RF source supplies both energy and a frequency reference that is used as clock for 3.1-10.6 GHz impulse radio ultrawideband (IR-UWB) transmission. Although the sensitivity of the tag itself is -14.22 dBm, the on-chip antennas greatly limit the wireless operating range to 7 cm.

Both the 902-928 MHz as the 2.405-2.47 GHz ISM bands are well established and widely used for various wireless communication standards. The combination of the two frequency bands therefore can be used in many RF-powered WSN applications. Since the limiting factor for maximum wireless range is likely to be the RF energy harvester and not the transmitter (TX), it is advantageous to use the lower 915 MHz ISM band for RF energy harvesting and the 2.4 GHz ISM band for wireless transmission. This is because antennas operating at lower frequencies have a larger effective area and therefore are more effective to capture energy from the incoming wave <sup>1</sup>. This translates into a longer wireless range but also requires a larger physical antenna area. The Effective Isotropic Radiated Power (EIRP) in the 915 MHz ISM band is limited to 4 watt (+36 dBm) by the Federal Communications Commission (FCC) [56], which enables a long wireless range.

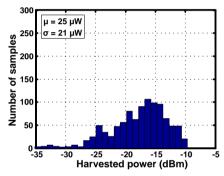

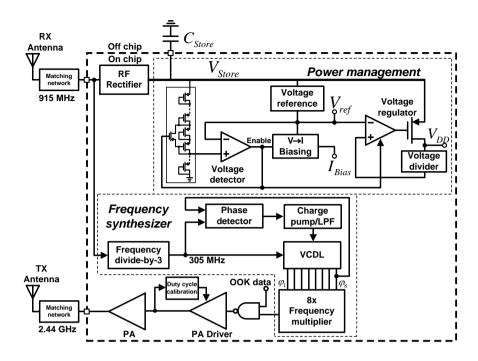

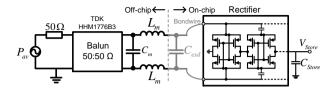

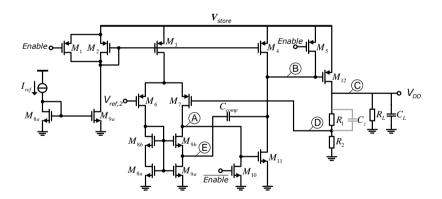

A system level description of the proposed RF-powered transmitter is illustrated in Fig. 3.1. The system consists of an RF energy harvester, power management unit, frequency synthesizer and an RF power amplifier. In this work, a dedicated RF source is assumed within the vicinity of the WSN that provides strong and reliable power in the 902-928 MHz ISM band. An RF energy harvester converts the captured electromagnetic (EM) energy by the

<sup>&</sup>lt;sup>1</sup>The concept of effective area and other antenna fundamentals will be discussed in more detail in Chapter 4.

Figure 3.1: Proposed RF-powered DLL-based transmitter.

antenna into electrical DC power. The harvested energy is first locally stored in an external capacitor until enough energy is accumulated to initiate wireless data transmission. The challenges and requirements for each block will be briefly discussed in the following sections.

## 3.2 RF Energy Harvesting

Apart from being designed for efficient power transfer, the RF energy harvester needs to be designed for superior sensitivity (i.e., minimize the required available power at the antenna to activate the TX). This leads to an increased area and distance that can be covered by the dedicated RF source.

Some other design challenges for RF energy harvesters have already been briefly introduced in Section 2.5 and will be extensively discussed in Chapters 4 and 5.

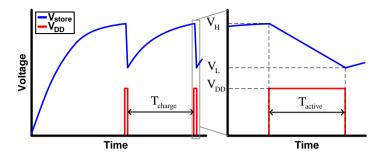

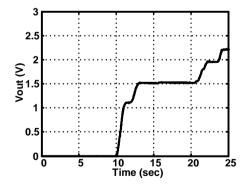

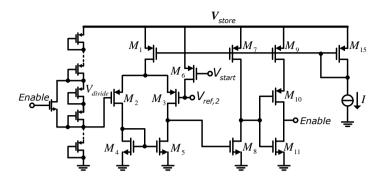

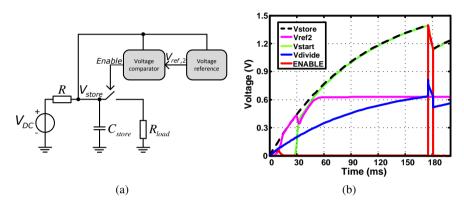

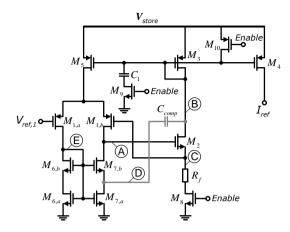

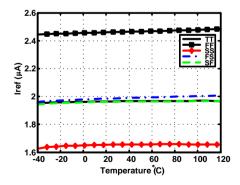

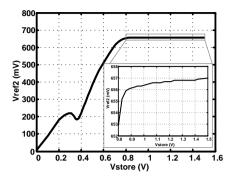

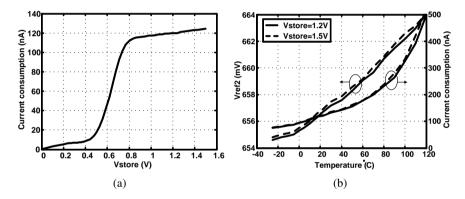

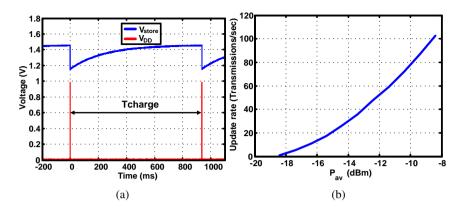

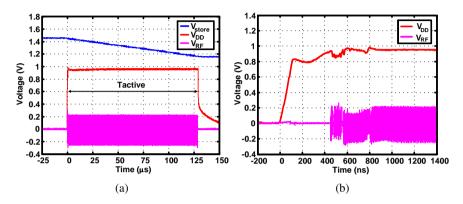

Figure 3.2: Power management time-domain waveforms. On the left an impression of the storage capacitor voltage and on the right a zoomed in figure illustrating the active period during wireless transmission.

### 3.3 Power Management

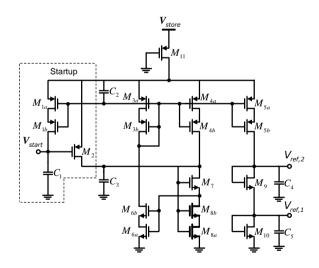

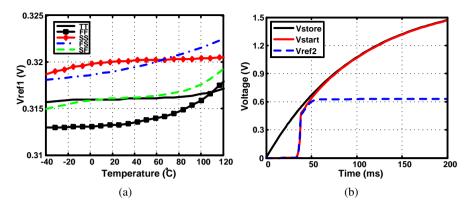

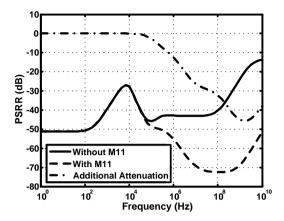

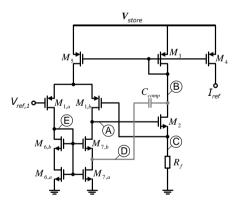

The power management unit illustrated in Fig. 3.1 consist of a voltage reference, voltage comparator, V-I converter and a voltage regulator. The voltage waveform across the storage capacitor  $C_{store}$  and supply voltage  $V_{DD}$  are sketched in Fig. 3.2 to illustrate the power management functionality. Here,  $V_L$  and  $V_H$  are defined as the low and high voltages that together with  $C_{store}$  determine the amount of stored energy available to the system.

When the system is in harvesting mode, the rectifier charges  $C_{store}$  to  $V_H$  while only the voltage reference and voltage comparator are enabled. When  $V_{store} \geq V_H$ , the voltage comparator enables the voltage regulator and V-I converter which provide a stable  $V_{DD}$  and reference current  $I_{ref}$  for the various circuit blocks while  $C_{store}$  is discharged from  $V_H$  to  $V_L$  due to the current drawn by the transmitter. The active time  $T_{active}$  is determined by  $C_{store}$ ,  $V_H$ ,  $V_L$ ,  $V_{DD}$  and the total current drawn by the system. Once  $V_{store} \leq V_L$ , the comparator disables the voltage regulator and the system returns to harvesting mode. The charging time  $T_{charge}$  is determined by the available RF power at the antenna, the RF rectifier efficiency, the storage capacitor and the power consumption of the voltage reference and comparator. To determine the system design variables, we first consider the voltage regulator efficiency of this system.

The energy efficiency of an ideal linear voltage regulator (neglecting its bias current) with a constant input and output voltage is simply given by  $\eta = V_{DD}/V_H$ . However, in this system the input voltage of the voltage regulator decreases linearly with time when assuming a constant current sink  $I_{load}$  as load. The energy at the input of the voltage regulator for  $V_{DD} \leq V_L \leq V_H$  is thus given by

$$E_{in} = \int_{t}^{t+T_{active}} I_{load}V_{store}dt$$

(3.1)

$$= I_{load} T_{Active} \frac{V_H + V_L}{2}$$

(3.2)

The energy delivered to the regulator load is simply given by

$$E_{out} = I_{load} V_{DD} T_{active} \tag{3.3}$$

The voltage regulator energy efficiency  $\eta_{regulator} = E_{out}/E_{in}$  then can be expressed as

$$\eta_{regulator} = \frac{2V_{DD}}{V_H + V_L}$$

$$= \frac{V_{DD}}{V_H} \frac{2}{1 + \frac{V_L}{V_L}}$$

(3.4)

$$= \frac{V_{DD}}{V_H} \frac{2}{1 + \frac{V_L}{V_H}} \tag{3.5}$$

Note that the second term in (3.5) indicates the relative improvement in efficiency compared to a voltage regulator with constant input and output voltage. To obtain a high efficiency, the differences between  $V_H$ ,  $V_L$ , and  $V_{DD}$  need to be as small as possible. The required values for  $V_{DD}$  and  $V_L$  are determined by the circuit's minimum supply voltage and the voltage regulator implementation. The value of  $V_H$  on the other hand depends on system parameters like total power consumption of the system, the amount of data that needs to be transmitted, type of modulation and the value of  $C_{store}$ .

To relate these design variables, first the required energy for wireless operation is calculated. In this work, the power amplifier (PA) input signal is modulated in order to realize On-Off Keying (i.e., the PA is switched on and off) while the remaining TX core circuits are always on during modulation to minimize the startup time. Hence, the average DC power consumed by the transmitter during transmission in this case can be written as

$$P_{DC,Tx} = mP_{DC,PA} + P_{DC,core} (3.6)$$

where m is the probability of transmitting a '0' and '1' data bit,  $P_{DC,PA}$  is the DC power consumption of the PA and  $P_{DC,core}$  is the DC power consumption of the remaining core circuits during transmission. Note that in this case  $P_{DC,Tx}$  and  $P_{DC,core}$  are calculated with respect to  $V_{DD}$  since the power loss due to the regulator voltage drop is included in  $\eta_{regulator}$ .

The required energy for wireless transmission is found by relating the amount of data to be sent, *Data* [bit], to the *Bitrate* [bit/s] and the regulator efficiency:

$$E_{req} = \frac{mP_{DC,PA} + P_{DC,core}}{\eta_{regulator}} \frac{Data}{Bitrate}$$

(3.7)

The energy available from the storage capacitor is given by

$$E_{av} = \frac{1}{2}C_{store}\left(V_H^2 - V_L^2\right) \tag{3.8}$$

The design variables of the system then can be related to the design specifications by substituting (3.5) into (3.7) and equating this with (3.8). Rearranging the terms gives

$$(mP_{DC,PA} + P_{DC,core})\frac{Data}{Bitrate} = C_{store}V_{DD}(V_H - V_L)$$

(3.9)

The system specifications are given on the left-hand side of (3.9) while on the right-hand side the design variables are found. In order to achieve high efficiency, a small difference between  $V_{DD}$ ,  $V_H$  and  $V_L$  is required as evident from (3.5). This increases the required  $C_{store}$ , which also simultaneously improves the system sensitivity (i.e., the minimum available power to reach  $V_H$ ) since the rectifier now requires less power at the antenna to charge  $C_{store}$  to  $V_H$ . For a given value of  $C_{store}$ , the minimum  $V_H$  is found by calculating

$$V_H = \frac{mP_{DC,PA} + P_{DC,core}}{C_{store}V_{DD}} \frac{Data}{Bitrate} + V_L$$

(3.10)

The active transmision time  $T_{active}$  is given by

$$T_{active} = \frac{C_{store}V_{DD}(V_H - V_L)}{mP_{DC,PA} + P_{DC,core}}$$

(3.11)

As an example, a simple WSN containing 128 bits of information with a 1  $\mu$ F storage capacitor, 500 kbps data rate,  $P_{DC,PA}$ =1.5 mW,  $P_{DC,core}$ =0.5 mW, m=0.5 (On-off keying modulation with equal probability of transmitting a '0' and '1' data bit),  $V_{DD}$ =1V and  $V_L$ =1.1V requires a minimum  $V_H$  of 1.42 V and allows for a transmission time of  $T_{active}$ =256  $\mu$ s. Using (3.5), a theoretical voltage regulator efficiency (neglecting bias currents) of 79.3% is found. With such a high efficiency, this voltage regulator actually approaches the efficiency of switching regulators, but with less ripple, area, noise and complexity [68].

Higher efficiencies can be achieved by for example increasing  $C_{store}$  such that the required  $V_H$  becomes lower. Although this increases the initial start-up charging time, it simultaneously improves the system sensitivity (i.e., the

minimum available power to reach  $V_H$ ) since the rectifier now requires less power at the antenna to charge  $C_{store}$  to  $V_H$ . A practical upper limit for the capacitor selection is set by the leakage current. Large (super)capacitors tend to have relatively high leakage current compared to the current output of the RF energy harvester. Although the leakage current decays over time, the initial leakage current of typical supercapacitors can be in the order of 10-30  $\mu$ A [69]. For the low power levels discussed in this thesis, the RF energy harvester is not able to supply this current and even if it can, a large portion of the harvested power will be wasted due to this leakage. Therefore the capacitor type should also be selected for relatively low leakage current. More details on loading effects can be found in Appendix A.

# 3.4 Frequency Synthesizer

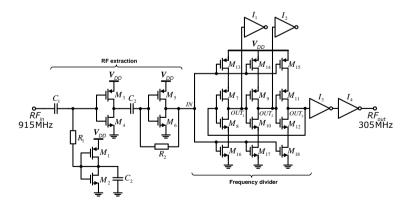

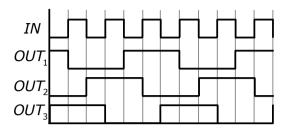

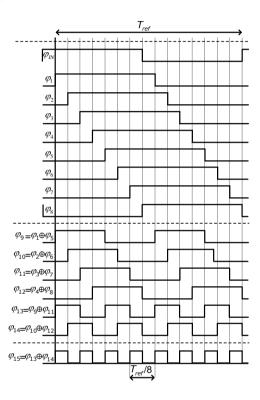

The transmitter RF carrier is derived from the received continuous RF wave at the input of the RF energy harvester in the 902-928 MHz ISM band. The interface between the antenna, RF energy harvester and the frequency divider needs to be optimized in order not to degrade the performance of each circuit block. By extracting the input frequency and applying a frequency multiplication of ratio 8/3, a transmitter RF carrier between 2.405-2.47 GHz can be realized that covers almost the entire license-free 2.4 GHz ISM band [56]. The 8/3 architecture has been proposed first in [65] and has been implemented using a frequency divider and PLL. In the proposed RF-powered transmitter shown Fig. 3.1, the RF input signal frequency first is divided by three and subsequently used as Delay Locked Loop (DLL) reference signal. The DLL consists of a phase detector, charge pump with Low Pass Filter (LPF) and a Voltage Controlled Delay Line (VCDL) that produces eight evenly spaced signals that are fed to an eight-times frequency multiplier. For a 915 MHz input, the majority of the circuits thus operates at 305 MHz while only the PA operates at 2.44 GHz. Since the DLL mainly consists of logic gates and does not require any inductors, it allows for a compact and area efficient solution. The DLL also is a single-pole system and thus inherently stable [70]. The implementation details of each block are discussed in Chapter 7.

### 3.5 RF Power Amplifier

The limited power budget and short-range application of a WSN usually requires a Power Amplifier (PA) with small output power (<0 dBm). These so called 'medium' PAs are very challenging to design with high global effi-

ciency  $(P_{out}/P_{DC,total})$  because the output power becomes comparable to the total power consumption of the WSN. Since the number of scientific publications on 2.4 GHz PAs with <0 dBm output power is very limited, Chapter 6 of this thesis is devoted to this topic.

The wireless transmitted information is encoded using On-Off Keying (OOK) modulation since it can be implemented with low complexity and low power consumption. This is achieved by simply enabling and disabling the PA. The power management and frequency synthesizer circuits are always on during modulation to minimize the startup time.

When following the previous WSN scenario example in Section 3.3 and assuming a PA efficiency of 50%, then a 1 mW (0dBm) power budget is available for wireless transmission. A possible receiving device might be an RFID reader, but can for example also be a smart phone or another (energy scavenged) WSN with a very strict power budget. Typically in these scenarios, it is foreseen that these WSNs use an ultra-low power wake-up receiver with limited data rate (<1 Mbps) and short wireless range. The wireless range depends on many different factors such as operating frequency, transmitter power, antenna gain, environment conditions and receiver sensitivity. Wake-up OOK receivers consuming sub- $100\mu$ W operating at 2.4 GHz are reported with a sensitivity of around -72 dBm at 100 kbps [71–74]. Assuming this scenario with a 0 dBm Tx output power at 2.4 GHz and -72 dBm receiver sensitivity, in its simplest form, allows for a theoretical wireless transmission distance of approximately 39 m.

#### 3.6 Conclusions

In this chapter a system level overview has been given of the challenges and requirements for RF-powered WSNs. The funcionality of the proposed RF-powered DLL-based transmitter has been briefly described. Furthermore, the relations between the design variables for the voltage regulator and power management have been derived and provide a framework for the circuit implementation. The design procedure and circuit implementation of highly-sensitive RF energy harvesters will be extensively discussed in Chapters 4 and 5, respectively. The power amplifier and frequency synthesizer circuit design will be discussed in detail in Chapter 6.

# **CHAPTER 4**

# ANTENNA-ELECTRONICS INTERFACES IN THE RECEIVING MODE

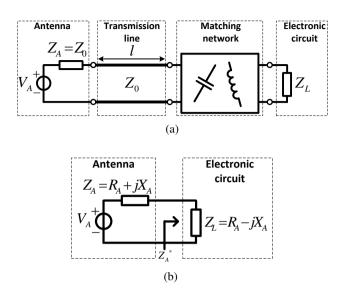

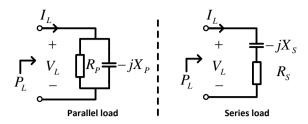

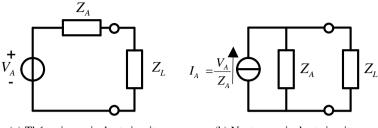

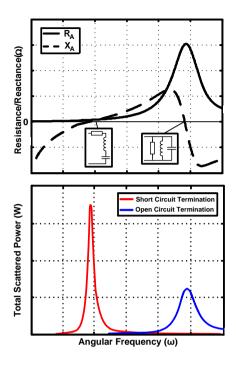

In this chapter, first the antenna and wave propagation fundamentals are discussed which leads to a general antenna equivalent circuit model. Subsequently, the co-design principles of antenna-electronics interfaces are presented for antenna systems in the receiving mode, which includes reception of wireless information and wireless power. Finally, two examples are treated to demonstrate the antenna-electronics co-design for the reception of wireless information (low noise amplifiers) and wireless power (RF energy harvesting).

#### 4.1 Fundamental Antenna Parameters

Antennas close the interface gap between the electronics and the electromagnetic (EM) radiating fields. They are therefore of great significance in any wireless system and can even be a performance-limiting factor in terms of size, bandwidth and efficiency. In order to optimize this interface for a desired performance, a firm understanding of both domains is essential. Therefore, the fundamental antenna parameters are defined first.

Antenna Definition An antenna is a *transducer* designed to transmit or receive EM waves. In other words, antennas convert electrical energy into electromagnetic energy and vice versa. The radiation mechanism of any antenna is based on the acceleration of electric *charge*. This creates a time-varying electric field which again gives rise to a magnetic field and both fields propagate away from the antenna at the speed of light in case of free space. Thus, time-varying *currents* produce radiation and incoming radiation can produce time-varying currents. Antenna design is all about influencing the current distribution of a certain structure so that radiation properties such as efficiency, directivity, bandwidth and radiation pattern are met.

**Radiation Pattern** The relative distribution of the radiated power as a function of the direction in space is defined as the radiation pattern. A hypothetical *isotropic* radiator radiates equally well in all directions such that the power uniformly spreads out across the surface of an imaginary sphere. The power density S [W/m<sup>2</sup>] at a distance d from a radiating isotropic RF source therefore equals the total radiated power by the transmitter divided by the surface area of a sphere:

$$S_{rad} = \frac{P_{rad}}{4\pi d^2} \tag{4.1}$$

The radiation intensity U in a given direction is defined as the power radiated from an antenna per unit solid angle and is defined as:

$$U = d^2 S_{rad} (4.2)$$

**Directivity** Isotropic antennas do not exist in practice but are used to define the directivity of an antenna. When assuming a non-isotropic lossless antenna, then by the law of energy conservation this antenna should radiate or receive more effectively in some directions than in others. The directivity D is the ratio between the radiation intensity in a given direction to the radiation intensity of an isotropic antenna:

$$D = \frac{U_{Antenna}}{U_{Isotropic}} = \frac{4\pi U_{Antenna}}{P_{rad}}$$

(4.3)

Note that if the direction is not specified, it usually implies the direction of maximum radiation intensity, indicated by  $D_0$ .

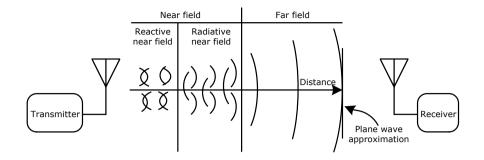

Figure 4.1: Radiation field regions with plane-wave approximation in the far-field.

**Radiation Fields** Near-and far-field can mean different things in different contexts. Defining the boundary between them is depending on the designers perspective and tolerances. There is not a definite boundary, but rather a transition from regions where either the reactive or the real power dominates [75]. For example, the boundary between the near and far-field can be defined as the distance from the antenna where the 1/d and 1/d² terms (distance) of the field components are equal. This boundary definition is commonly used and is given by  $d = \lambda/2\pi$ . Another boundary given by  $d = 2D^2/\lambda$  includes the size of the antenna and is valid for electrically large antennas [76,77]. Setting the boundary through the wave impedance involves determining at what distance from the antenna the EM wave impedance becomes 'constant'. An excellent paper is available which goes through the various definitions and boundaries of the near-field [78].

In general, the reactive near-field of an antenna is the field region where the reactive power dominates the total complex power. This reactive power is not radiated but stored inside the electromagnetic field near the antenna. The angular field distribution is dependent upon the distance from the antenna and often is too complex to predict. In the radiative near-field, the real power dominates the total complex power but the angular field distribution still is dependent upon the distance from the antenna. In the far-field, the real power dominates the total complex power and the angular field distribution in this field is essentially independent of the distance from the antenna. When a receiving antenna is located in the far-field of the radiating source as depicted in Fig. 4.1, the wave can be approximated as a plane wave.

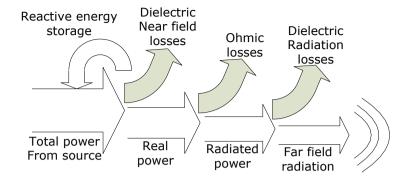

**Antenna Radiation Efficiency** The antenna radiation efficiency relates the radiated power to the power accepted by the antenna<sup>1</sup>:

$$\eta_A = \frac{P_{rad}}{P_{accented}} \tag{4.4}$$

The radiated power  $P_{rad}$  is found by integrating the power density over an closed surface with radius d (distance) enclosing the radiating structure. The power accepted by the antenna  $P_{accepted}$  is the actual power delivered to the antenna after taking any interface impedance matching losses into account (to be discussed in Section 4.2).

The antenna radiation efficiency can be subdivided into conductivity efficiency and dielectric efficiency

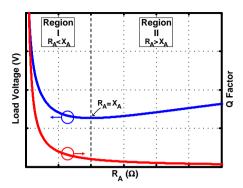

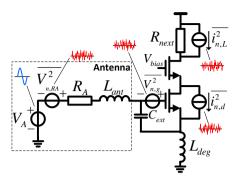

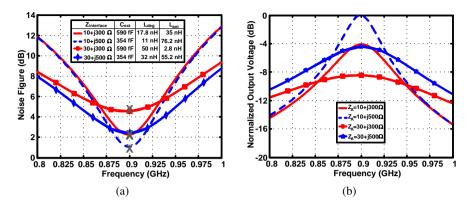

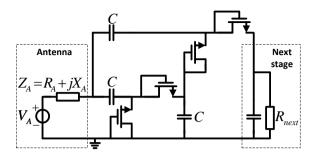

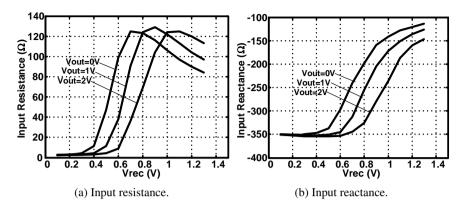

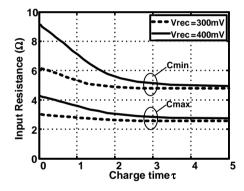

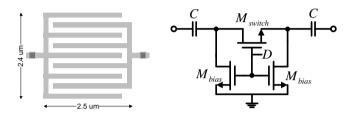

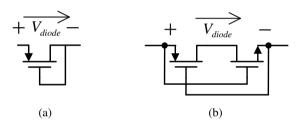

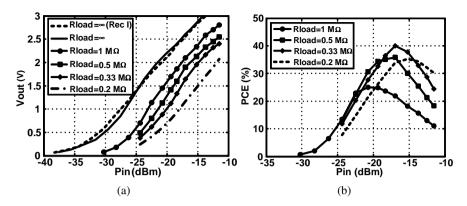

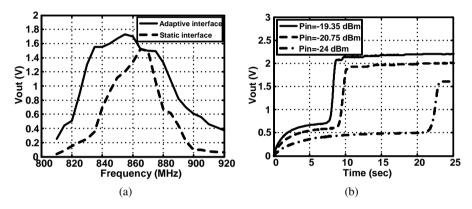

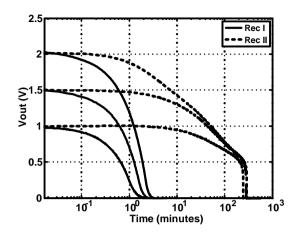

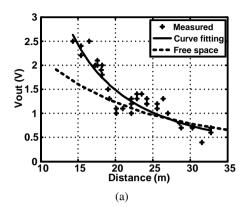

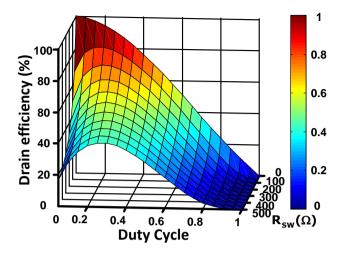

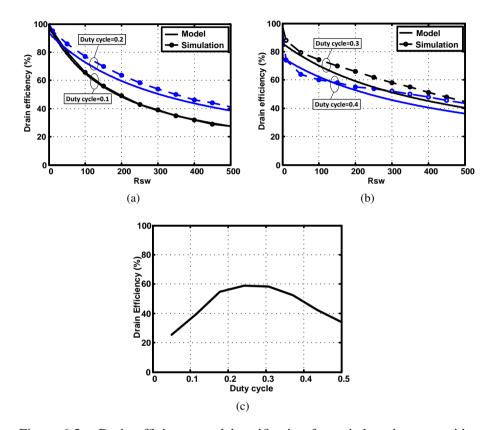

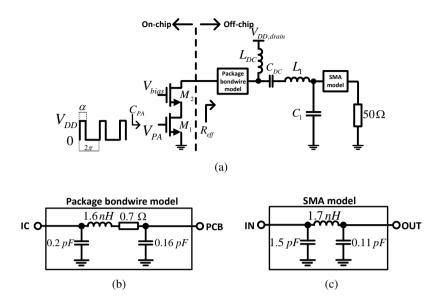

$$\eta_A = \eta_{cond} \cdot \eta_{dielectric} \tag{4.5}$$