### Variable-Frequency Soft-Switching Modulation of Non-Isolated DC-DC Converters and Compensation Circuits in WPT Systems

Yu, G.

DOI

10.4233/uuid:589f7376-57ef-4e2b-85f6-c79dc4b98a70

**Publication date**

**Document Version**

Final published version

Citation (APA)

Yu, G. (2025). Variable-Frequency Soft-Switching Modulation of Non-Isolated DC-DC Converters and Compensation Circuits in WPT Systems. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:589f7376-57ef-4e2b-85f6-c79dc4b98a70

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## Variable-Frequency Soft-Switching Modulation of Non-Isolated DC-DC Converters and Compensation Circuits in WPT Systems

Guangyao YU

# VARIABLE-FREQUENCY SOFT-SWITCHING MODULATION OF NON-ISOLATED DC-DC CONVERTERS AND COMPENSATION CIRCUITS IN WPT SYSTEMS

## Variable-Frequency Soft-Switching Modulation of Non-Isolated DC-DC Converters and Compensation Circuits in WPT Systems

## Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology, by the authority of the Rector Magnificus prof. dr. ir. T.H.J.J. van der Hagen, Chair of the Board for Doctorates, to be defended publicly on Wednesday 10, September 2025 at 10:00 o'clock

by

## Guangyao YU

Master of Science in Electrical Engineering, Delft University of Technology, The Netherlands, born in Zhejiang, China. This dissertation has been approved by the promotors.

#### Composition of the doctoral committee:

Rector Magnificus, Chairperson

Prof. dr. ir. P. Bauer, Delft University of Technology, promotor Dr. J. Dong, Delft University of Technology, promotor

*Independent members:*

Prof. dr. ir. M. Popov, Delft University of Technology Prof. dr. ir. A.H.M. Smets, Delft University of Technology

Prof. dr. D. Peftitsis, Norwegian University of Science and Technology

Dr. ir. P. Venugopal, University of Twente

Dr. ir. B.J.D. Vermulst Eindhoven University of Technology

Copyright ©2025 by Guangyao YU ISBN 978-94-6384-809-1

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

## **CONTENTS**

| Su                            | mma   | ry                  |                                                               | хi  |  |  |  |

|-------------------------------|-------|---------------------|---------------------------------------------------------------|-----|--|--|--|

| Sa                            | menv  | atting              |                                                               | xv  |  |  |  |

| Ab                            | brevi | ations              |                                                               | xix |  |  |  |

| 1                             | Intro | troduction          |                                                               |     |  |  |  |

|                               | 1.1   | Backgr              | ound and Motivation                                           | 1   |  |  |  |

|                               | 1.2   |                     | Objective and Research Questions                              | 2   |  |  |  |

|                               | 1.3   | Contril             | butions                                                       | 5   |  |  |  |

|                               | 1.4   | Thesis              | Outline                                                       | 6   |  |  |  |

| 2                             | Brie  | f Overv             | riew of WPT System Topology                                   | 7   |  |  |  |

|                               | 2.1   | WPT R               | Research Progress in Asia                                     | 8   |  |  |  |

|                               | 2.2   | WPT R               | Research Progress in Europe                                   | 14  |  |  |  |

|                               | 2.3   | WPT R               | Research Progress in USA                                      | 16  |  |  |  |

|                               | 2.4   | Summa               | ary and Discussion                                            | 20  |  |  |  |

|                               |       | 2.4.1               | A Brief Summary                                               | 20  |  |  |  |

|                               |       | 2.4.2               | Discussion                                                    | 20  |  |  |  |

| 3                             | Thre  | e-Mod               | e Variable-Frequency ZVS Modulation for FSBB Converter        | 23  |  |  |  |

|                               | 3.1   | Introdu             | action                                                        | 24  |  |  |  |

|                               | 3.2   | Workir              | ng principle of the modulation strategy                       | 27  |  |  |  |

|                               |       | 3.2.1               | Voltage Gain of the Four-Switch Buck+Boost Converter          | 27  |  |  |  |

|                               |       | 3.2.2               | Soft Switching under Buck-Boost-type Mode with Possible Modu- |     |  |  |  |

|                               |       |                     | lations                                                       | 28  |  |  |  |

|                               |       | 3.2.3               | Rms Value of the Inductor Current with Phase Shift            | 31  |  |  |  |

|                               |       | 3.2.4               | TCM-ZVS Buck, Boost Operation                                 | 37  |  |  |  |

|                               | 3.3   | Design              | Considerations                                                | 38  |  |  |  |

|                               |       | 3.3.1               | Inductance Value Selection                                    | 38  |  |  |  |

|                               |       | 3.3.2               | Resonant Circuit Analysis during Dead Time                    | 39  |  |  |  |

| 3.4 Experimental Verification |       | mental Verification | 42                                                            |     |  |  |  |

|                               |       | 3.4.1               | Steady State Operation                                        | 42  |  |  |  |

|                               |       | 3.4.2               | Benchmark with Different ZVS Modulation Schemes               | 47  |  |  |  |

|                               |       | 3.4.3               | Mode Transition Operation                                     | 48  |  |  |  |

|                               | 3.5   | Conclu              | sion and Future work                                          | 52  |  |  |  |

|                               | 3.6   | Appen               | dix A                                                         | 53  |  |  |  |

|                               | 3.7   | Appen               | dix B                                                         | 53  |  |  |  |

viii Contents

| 4 | Effe | cts of l | Parasitic Resistance on Reverse Switching Current                   | 55    |

|---|------|----------|---------------------------------------------------------------------|-------|

|   | 4.1  | Introd   | luction                                                             | . 56  |

|   | 4.2  | Descr    | iption of Variable-Frequency TCM-ZVS Modulation                     | . 58  |

|   |      | 4.2.1    | Brief Review of Variable-Frequency TCM-ZVS Modulation               | . 58  |

|   |      | 4.2.2    | Brief Introduction of Voltage-Mode TCM-ZVS Control                  | . 59  |

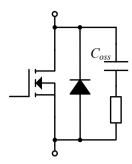

|   | 4.3  | TCM-     | ZVS Modulation Considering Parasitic Resistances                    |       |

|   |      | 4.3.1    | Derivation Procedures of General Expressions                        | . 60  |

|   |      | 4.3.2    | Application in an FSBB Converter                                    |       |

|   | 4.4  | Design   | n Consideration and Simulation Verification                         |       |

|   |      | 4.4.1    | Switching Frequency and Inductance Parameters Selection             | . 65  |

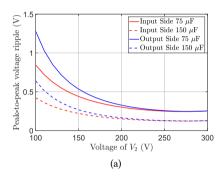

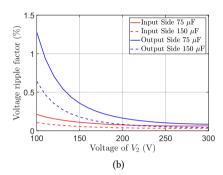

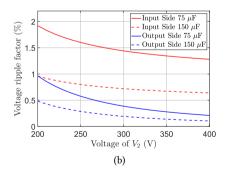

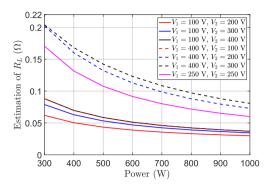

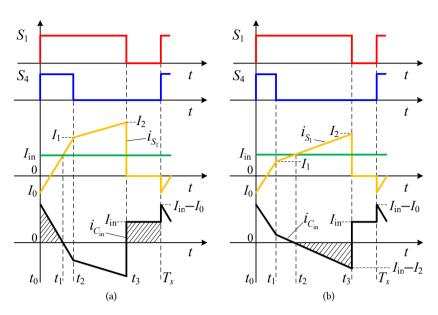

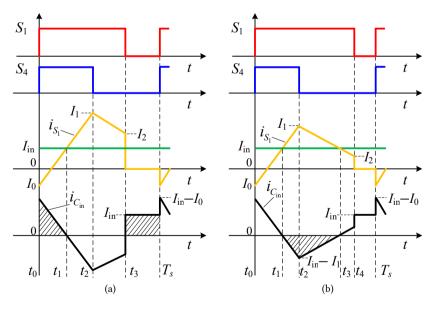

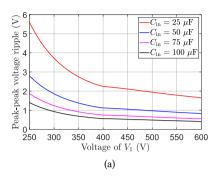

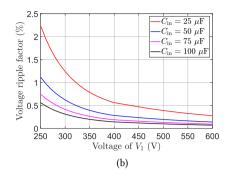

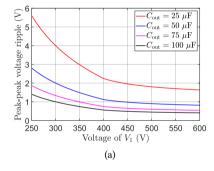

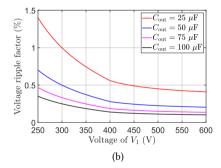

|   |      | 4.4.2    | Selection of Input and Output Capacitors                            | . 66  |

|   |      | 4.4.3    | Parasitic Resistances Estimation and Simulation Verification of the |       |

|   |      |          | Proposed Analysis                                                   | . 68  |

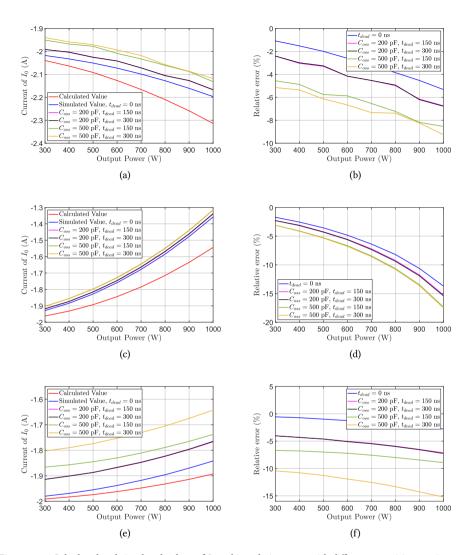

|   |      | 4.4.4    | Estimation of $I_0$ under Different Operating Cases                 |       |

|   |      | 4.4.5    | Discussion on Assumptions                                           | . 72  |

|   | 4.5  | Exper    | imental Verification                                                |       |

|   |      | 4.5.1    | Voltage Ripple Verification                                         |       |

|   |      | 4.5.2    | TCM-ZVS Operating Waveforms                                         | . 79  |

|   |      | 4.5.3    | Measured Values of Reverse Switching Current                        | . 80  |

|   |      | 4.5.4    | Efficiency and Thermal Performance                                  | . 82  |

|   | 4.6  | Concl    | usion                                                               | . 83  |

|   | 4.7  | Apper    | ndix                                                                | . 84  |

| 5 | Sing | gle Mod  | de Variable-Frequency ZVS Modulation For FSBB Converter             | 85    |

|   | 5.1  | Introd   | luction                                                             | . 86  |

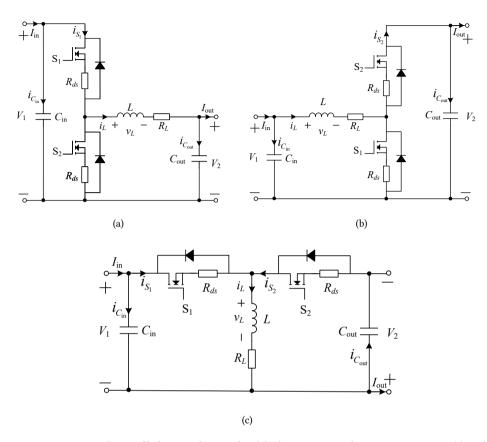

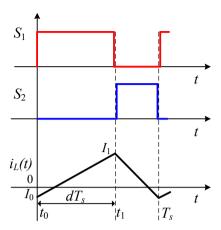

|   | 5.2  | Conve    | erter Operation Principle                                           | . 88  |

|   |      | 5.2.1    | Basics of Converter Operation                                       | . 88  |

|   |      | 5.2.2    | Simple ZVS Modulation Scheme with Seamless Mode Transition .        |       |

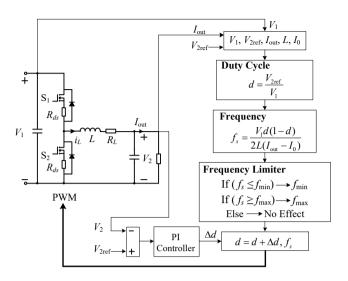

|   |      | 5.2.3    | Closed-loop Control Scheme                                          | . 92  |

|   | 5.3  | Desig    | n Consideration                                                     | . 93  |

|   |      | 5.3.1    | Selection of Inductance                                             | . 93  |

|   |      | 5.3.2    | ZVS Requirement on Switching Current Value                          | . 93  |

|   |      | 5.3.3    | Minimum ZVS Load                                                    | . 94  |

|   |      | 5.3.4    | $d_{ m max}$ Influence on Minimum ZVS Load and Inductor RMS Current |       |

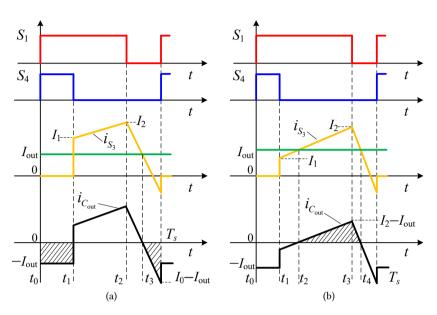

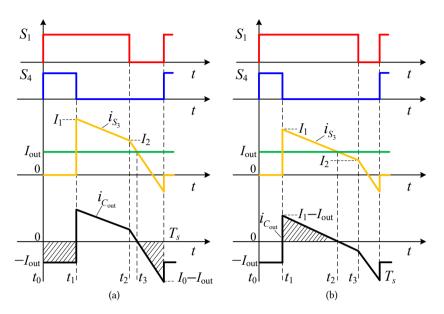

|   |      | 5.3.5    | Selection of Input and Output Capacitors                            | . 96  |

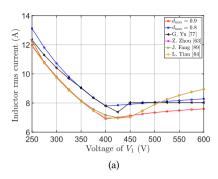

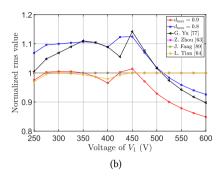

|   |      | 5.3.6    | Benchmark with Different ZVS Modulation Schemes on Inductor         |       |

|   |      |          | RMS Current                                                         | . 102 |

|   | 5.4  | Conve    | erter Losses Estimation                                             | . 104 |

|   |      | 5.4.1    | MOSFET Losses Estimation                                            | . 104 |

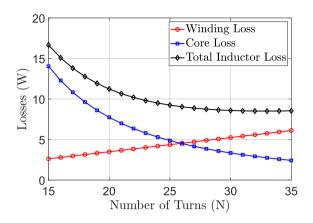

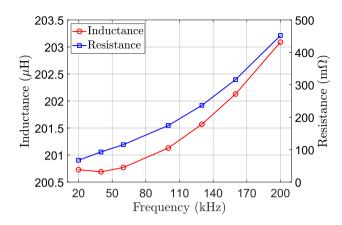

|   |      | 5.4.2    | Inductor Losses Estimation                                          | . 105 |

|   |      | 5.4.3    | Capacitor Losses Estimation                                         | . 106 |

|   |      | 5.4.4    | Estimated Losses and Efficiency                                     | . 106 |

|   | 5.5  | Exper    | imental Verification                                                |       |

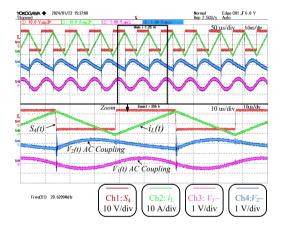

|   |      | 5.5.1    | Steady State Operation                                              |       |

|   |      | 5.5.2    | Efficiency and Thermal Performance                                  |       |

|   |      | 5.5.3    | Dynamic Operation Across Unit-Voltage Gain                          | . 111 |

Contents ix

|   | 5.6         | Conclu    | ısion                                                               | 13  |

|---|-------------|-----------|---------------------------------------------------------------------|-----|

|   | 5.7         | Appen     | dix A                                                               | 14  |

|   | 5.8         | Appen     | dix B                                                               | 15  |

|   | 5.9         | Appen     | dix C                                                               | 115 |

|   | 5.10        | Appen     | dix D                                                               | 19  |

|   |             | 5.10.1    | Steady State Operation                                              | 19  |

|   |             |           | Transition Operation under Constant Power                           |     |

| 6 | Imp         | roved I   | Peak Voltage Calculation Method for Compensation Compo-             |     |

|   | nen         |           | •                                                                   | 23  |

|   | 6.1         | Introd    | uction                                                              | 24  |

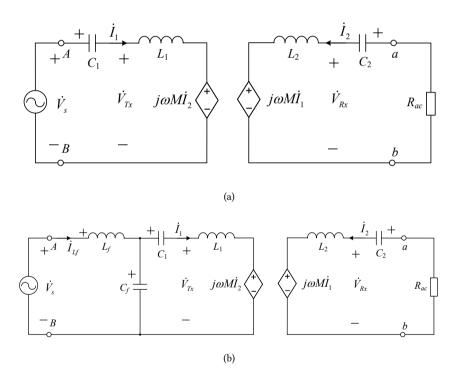

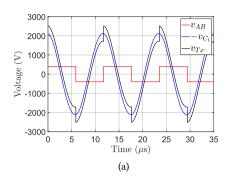

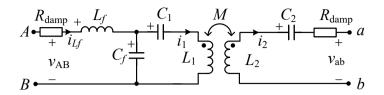

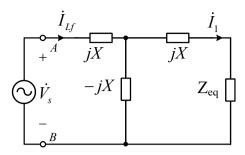

|   | 6.2         | S-S and   | d LCC-S Compensations                                               | 24  |

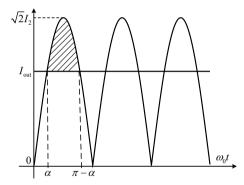

|   |             | 6.2.1     | Component Stress based on First Harmonic Approximation Method       |     |

|   |             | -         | (FHA)                                                               |     |

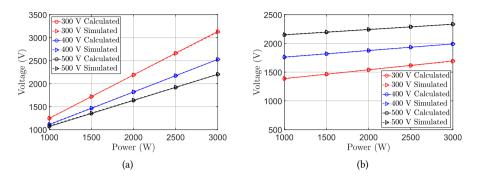

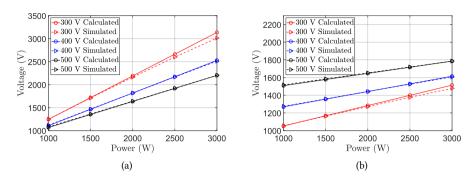

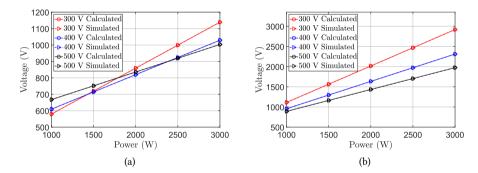

|   | 6.3         |           | racy of Derived Formulas                                            |     |

|   |             | 6.3.1     | S-S Compensation                                                    |     |

|   |             | 6.3.2     | LCC-S Compensation                                                  |     |

|   |             | 6.3.3     | Improved Method                                                     |     |

|   |             | 6.3.4     | Discussion on Improved Formulas                                     |     |

|   | 6.4         |           | tion Verification                                                   |     |

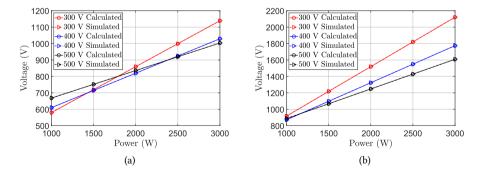

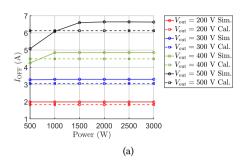

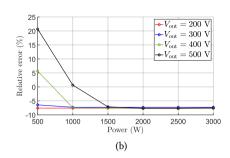

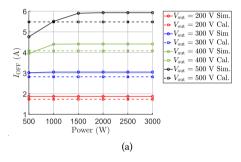

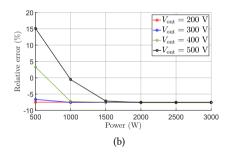

|   |             | 6.4.1     | S-S Compensation                                                    |     |

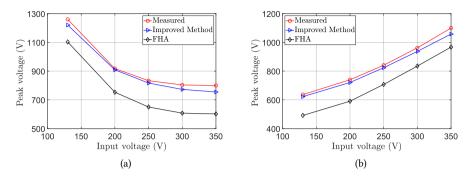

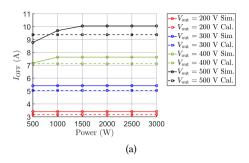

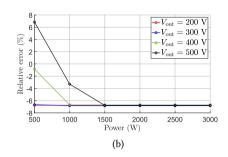

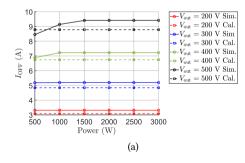

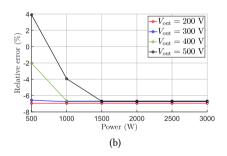

|   |             | 6.4.2     | LCC-S Compensation                                                  |     |

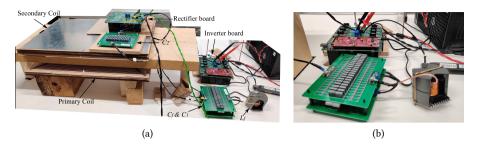

|   | 6.5         | -         | mental Validation                                                   |     |

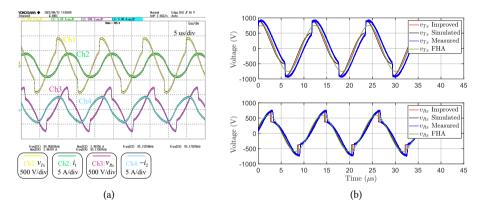

|   |             | 6.5.1     | S-S Compensation                                                    |     |

|   |             | 6.5.2     | LCC-S Compensation                                                  |     |

|   |             | 6.5.3     | Discussion                                                          |     |

|   | 6.6         | 6.5.4     | Voltage Stress over a Wider Operational Range                       |     |

|   | 6.7         |           | dix A                                                               |     |

|   | 6.8         |           | dix B                                                               |     |

|   | 0.0         | 6.8.1     | S-S Compensation                                                    |     |

|   |             | 6.8.2     | LCC-S Compensation                                                  |     |

|   |             |           | -                                                                   | .40 |

| 7 | Cur<br>Syst |           | stortion Modeling of a fully Compensated LCC-S based WPT            | 41  |

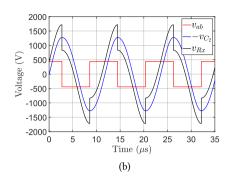

|   | 7.1         |           | uction                                                              |     |

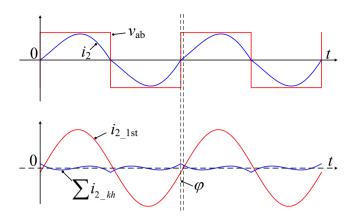

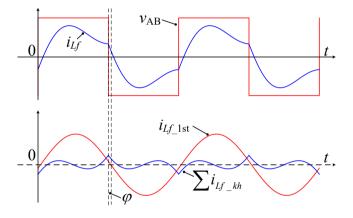

|   | 7.1         |           | sis Based on First Harmonic Approximation (FHA) Method              |     |

|   | 7.2         | 7.11a1y s | A specific simulation and calculation example                       |     |

|   | 7.3         |           | ced modeling Considering Harmonics from Both Sides                  |     |

|   | 7.5         | 7.3.1     | Derivation of High-order Harmonic Currents                          |     |

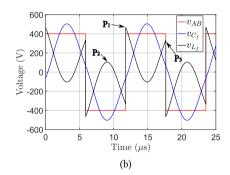

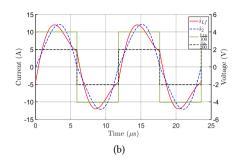

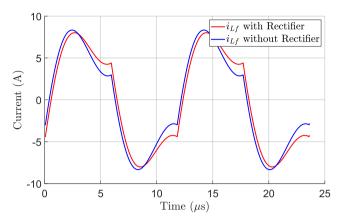

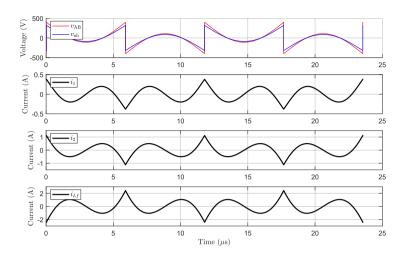

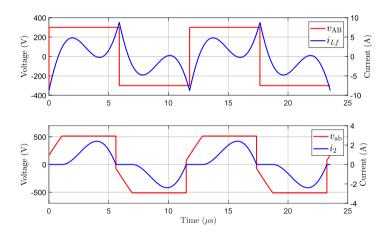

|   |             | 7.3.1     | Simulation Verification of Derived High-order Harmonic Currents . 1 |     |

|   |             | 7.3.2     | Contribution to Switching Current Due to First Harmonic Current. 1  |     |

|   | 7.4         |           | tion Verification                                                   |     |

|   | 7.1         | 7.4.1     | Simulation Verification of Switching Current                        |     |

|   |             | 7.4.2     | Result Discussion                                                   |     |

|   |             |           |                                                                     |     |

| X | Contents |

|---|----------|

|   |          |

|    | 7.5<br>7.6<br>7.7 | Conclusion and Future Work |

|----|-------------------|----------------------------|

| 8  | Con               | clusion 1                  |

|    | 8.1               | Research Questions         |

|    | 8.2               | Future Work                |

| Ad | knov              | vledgments 10              |

| Bi | bliog             | raphy 10                   |

| Li | st of             | Publications 1             |

| Αι | ıthor             | Profile 15                 |

## **SUMMARY**

Charging electric vehicles (EVs) via wireless power transfer (WPT) has emerged as a novel charging concept in recent years. Although the efficiency of the WPT charging featuring series-series (S-S) compensation has reached a very high level thanks to optimized magnetic coupler design, it is still sensitive to different operating conditions such as coupling coefficient. In order to enable efficient wireless power charging for EVs over a wide operational range, and to meet the charging requirement, additional power conversion control is needed. Meanwhile, the electrical stresses and current distortion in compensation circuits are also critical for the efficient and safe operation.

For a basic wireless power transfer system mentioned in many references, it typically includes at least two power conversion stages, which are dc-ac inversion stage and ac-dc rectification stage. The dc-ac stage converts the dc power source into high-frequency ac source to drive the primary coil while the ac-dc stage converts the ac current received by the secondary coil into dc source. In Chapter 2, a review on state-of-the-art WPT charging system topology has been conducted. Based on this review, it can be concluded that practical WPT charging systems usually have multiple power conversion stages, but it is difficult to conclude which is the best power conversion configuration and topology choice.

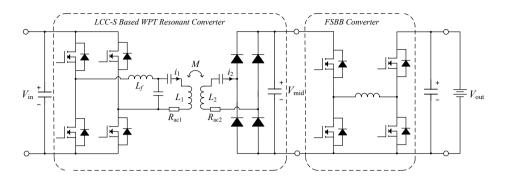

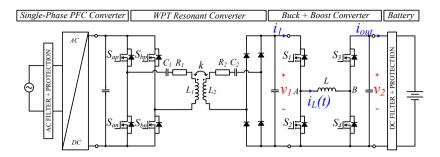

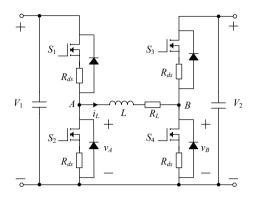

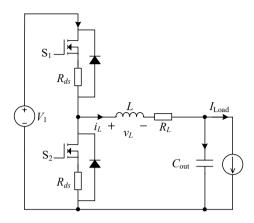

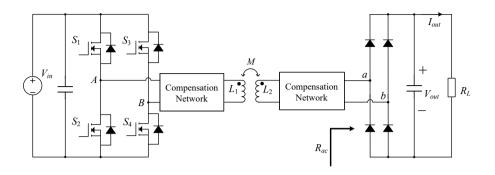

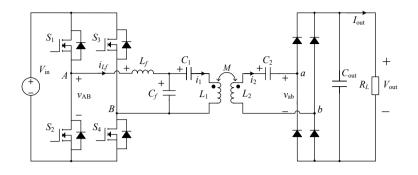

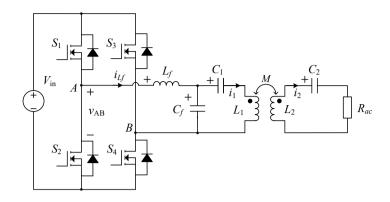

In this thesis, a WPT charging system featuring LCC-S compensation and a back-end FSBB converter was chosen as the research object, and this is based on the consideration of the following factors: 1) Compared with front-end power regulation, back-end power regulation avoids communication between primary and secondary sides during charging, which helps improve the system reliability; 2) From a safety perspective, an LCC-S based WPT system allows operation without a secondary coil or with an open circuit on the secondary side, which has a built-in safety advantage over S-S compensated WPT system; 3) Since the WPT coils already provide electrical isolation, a non-isolated dc-dc converter can be simply used to achieve dc voltage conversion. Compared to traditional boost or buck converters, the FSBB converter offers both voltage boost and buck functionality, making it more versatile and better suited for wireless charging systems.

The main research content of this thesis is divided into two parts. The first part delves into the four-switch buck+boost (FSBB) converter, which functions as an additional power conversion stage in the wireless charging system. Comprehensive and detailed analysis on the soft-switching modulation strategy on this converter was investigated and presented. The second part focuses on accurate modeling of electrical stresses and current distortion phenomenon for compensation topologies.

## **Soft-Switching Modulation of FSBB Converter**

This part focuses on the soft-switching modulation of the FSBB converter in order to achieve high-efficiency wide-range operation. At present, although hard-switched dc-dc converter can also reach peak efficiency above 99%, the switching losses cannot be

xii Summary

eliminated, which poses a challenge to the high-frequency or even ultra-high-frequency operation of the converter. With increasing requirement for higher power density and higher operating frequency, soft-switching modulation becomes necessary. Particularly, in this thesis, the soft-switching technique of zero-voltage switching (ZVS) was studied.

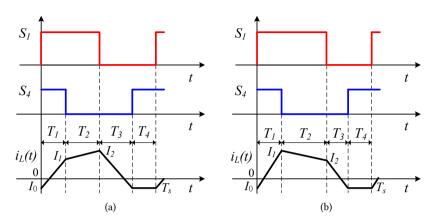

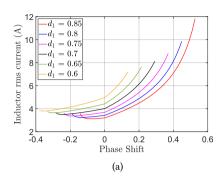

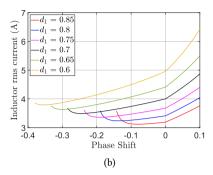

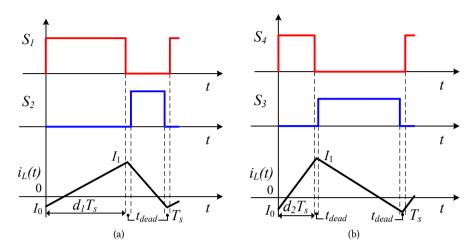

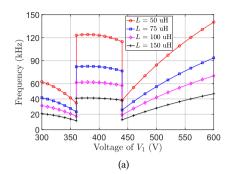

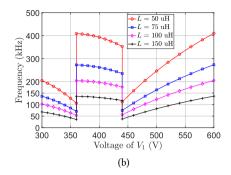

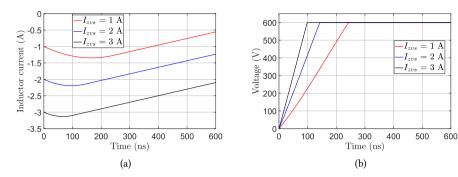

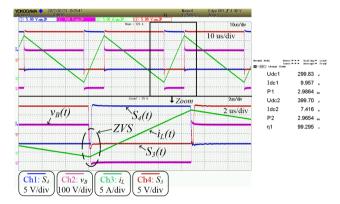

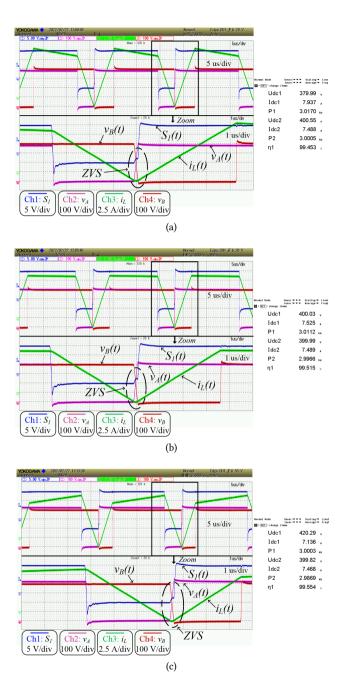

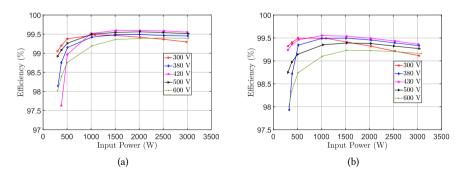

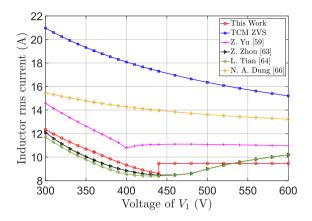

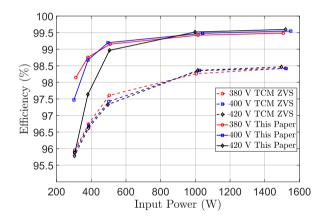

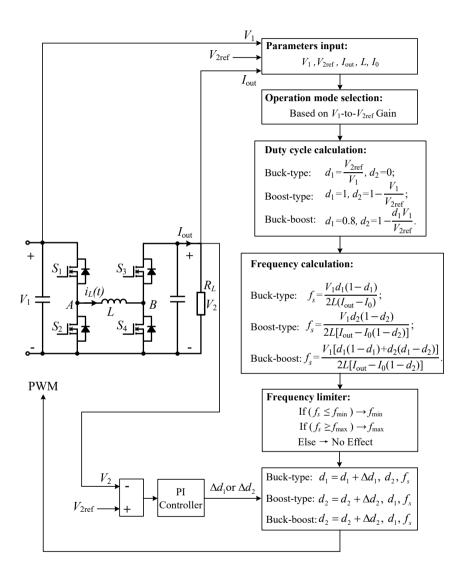

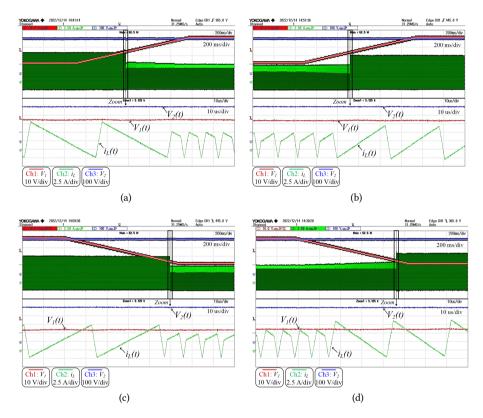

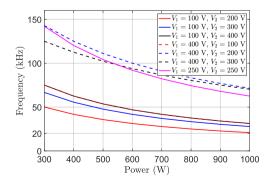

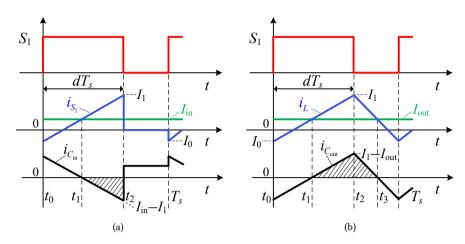

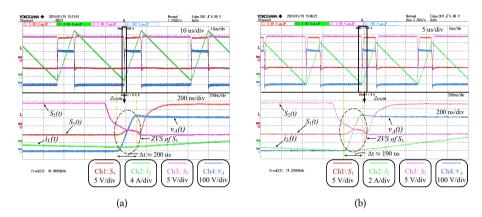

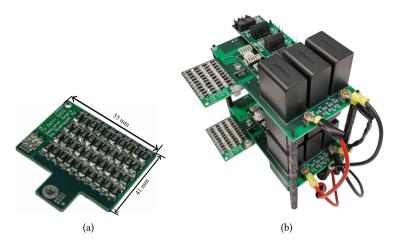

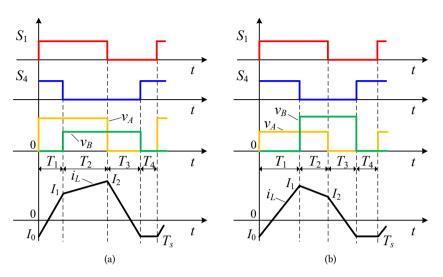

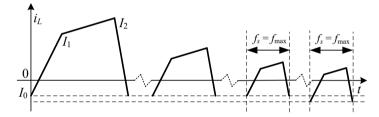

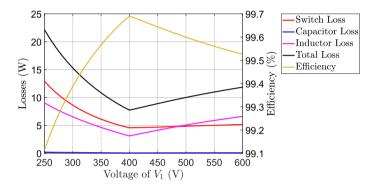

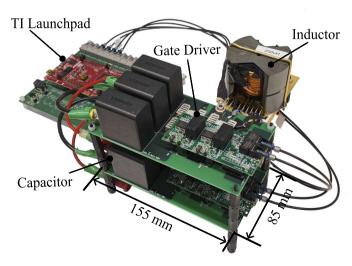

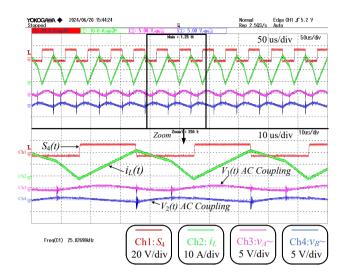

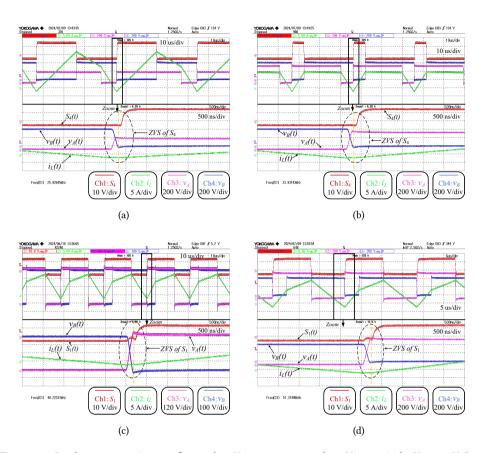

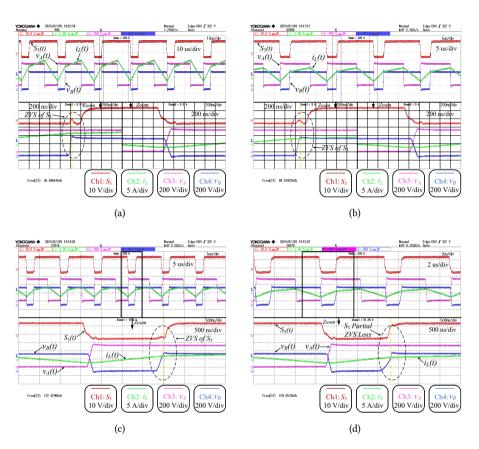

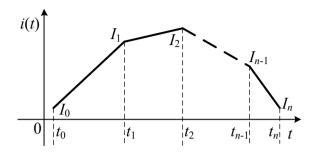

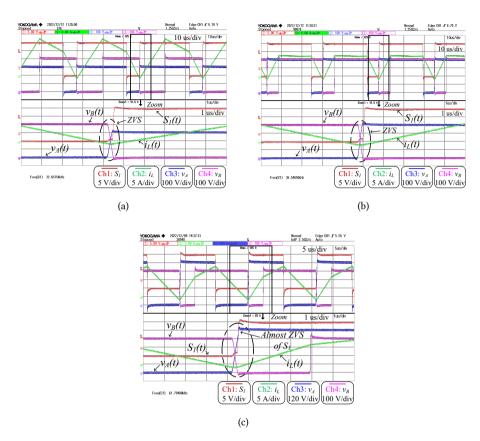

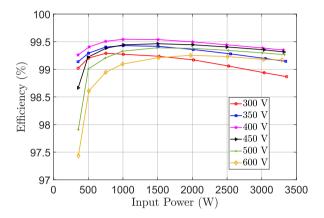

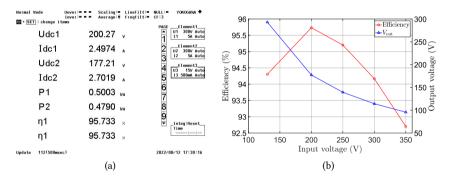

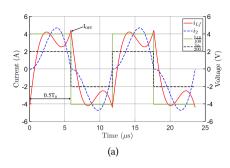

In Chapter 3, a three-mode variable-frequency ZVS modulation was proposed for the FSBB converter. The converter operation is subdivided into three operating regions according to the converter static voltage gain, i.e., buck-, buck-boost- and boost-type modes. Triangular current mode (TCM) modulation was adopted for buck-type and boost-type modes while in buck-boost-type mode when the voltage gain is close to unit, three-segment inductor current mode modulation was selected as the optimal modulation technique in terms of inductor rms current reduction and ease of operation. A 300–600 V input, 400 V output, 3 kW laboratory prototype was built to evaluate and validate the proposed concepts. The converter was tested over a wide power range from 10% to full rated load. The measured efficiency was always higher than 99%, i.e., between 99.2% and 99.6%, from 1 to 3 kW for all the considered input voltages.

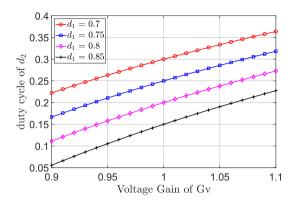

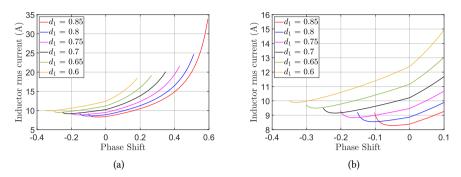

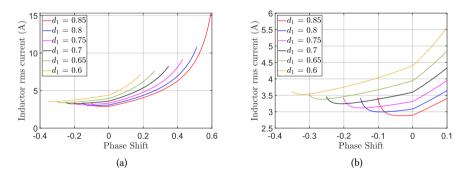

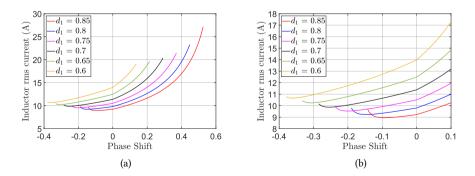

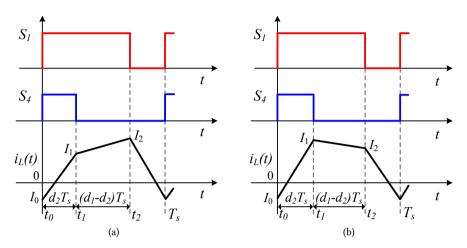

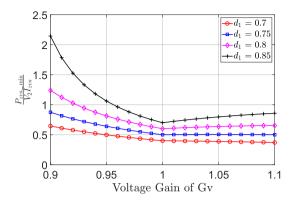

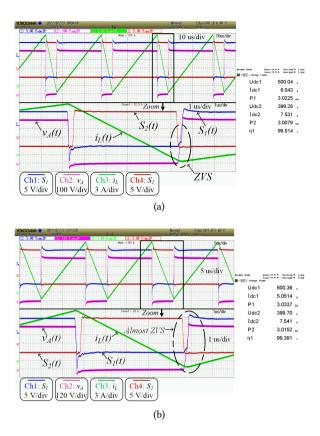

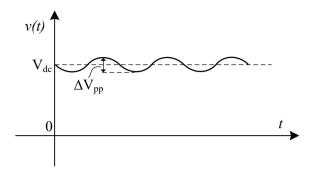

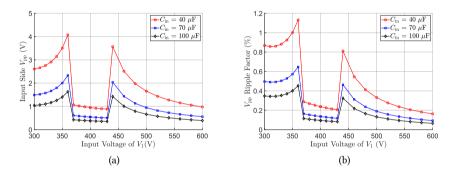

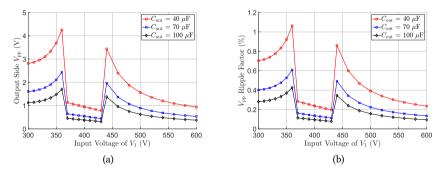

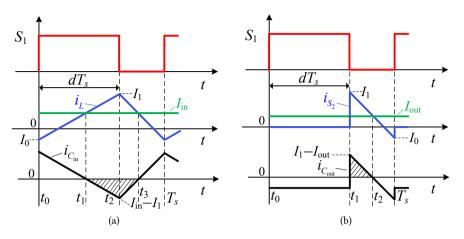

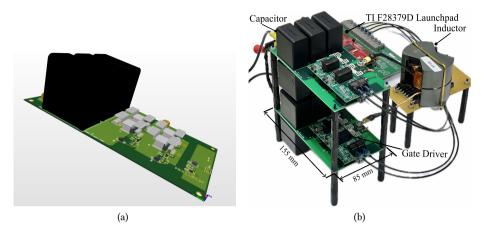

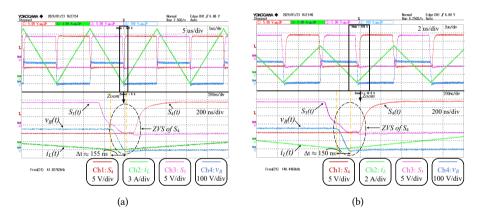

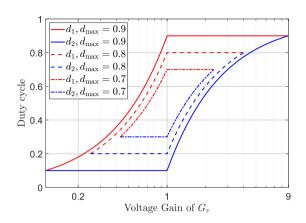

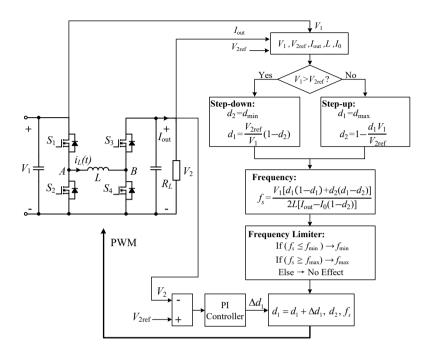

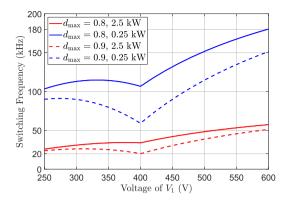

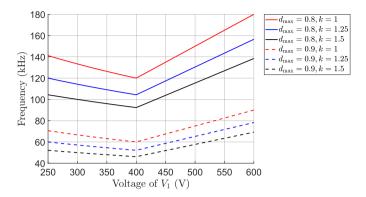

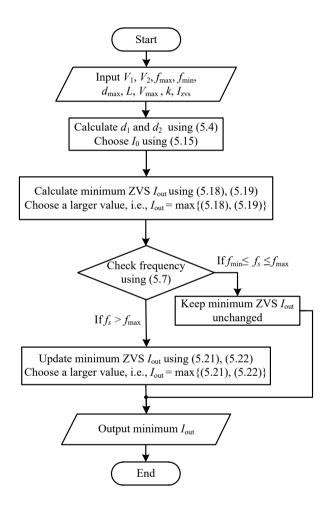

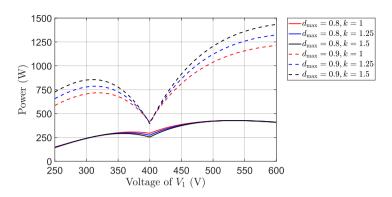

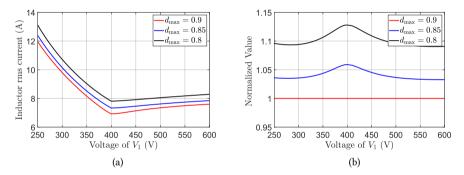

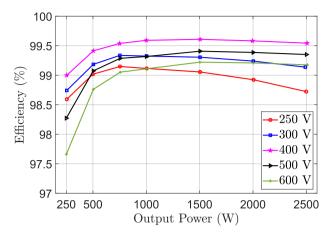

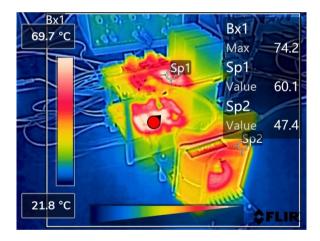

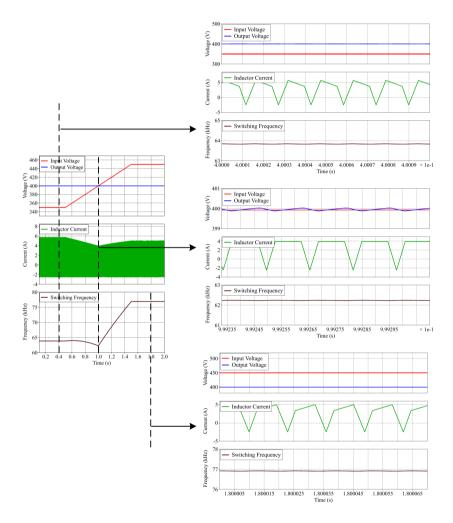

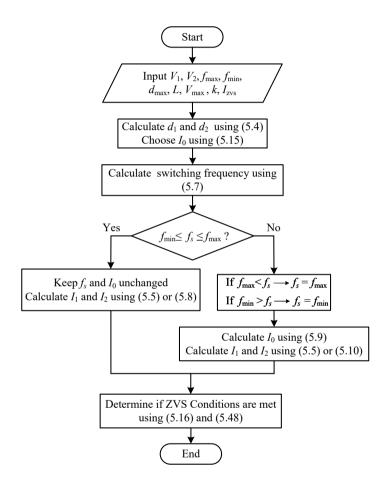

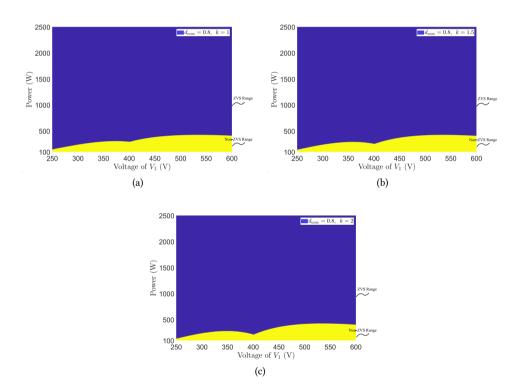

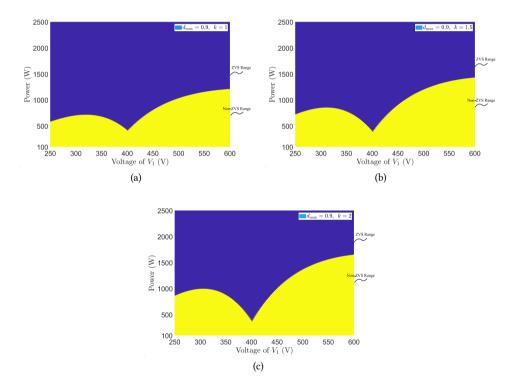

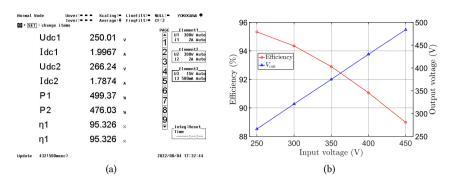

In Chapter 5, a single mode variable-frequency ZVS modulation was proposed. In this modulation method, the control variables of duty cycle and switching frequency are continuous at the unit voltage gain boundary, which is different from the three-mode variable-frequency ZVS modulation method. Basically, the three-segment inductor current mode modulation was extended to the whole operational range. By fixing the duty cycle for the switch in the buck-type or boost-type half-bridge circuit, and controlling the duty cycle of the switch in the other half-bridge circuit, the FSBB converter can realize a smooth transition at the unit voltage gain boundary without compromising the inductor rms current compared with TCM-ZVS modulation. Based on this, a simple closed-loop control was presented without the need of inductor or switch current detection. In addition, the capacitance selection of input and output capacitors was also analyzed in detail. An FSBB converter was built and tested to validate the proposed concepts with an input voltage of 250–600 V, output voltage of 400 V and output power of 250–2500 W.

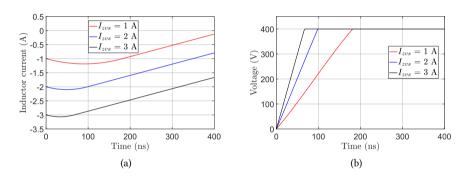

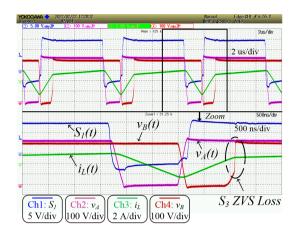

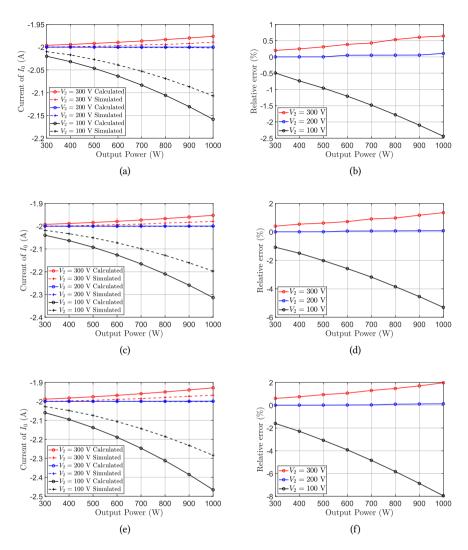

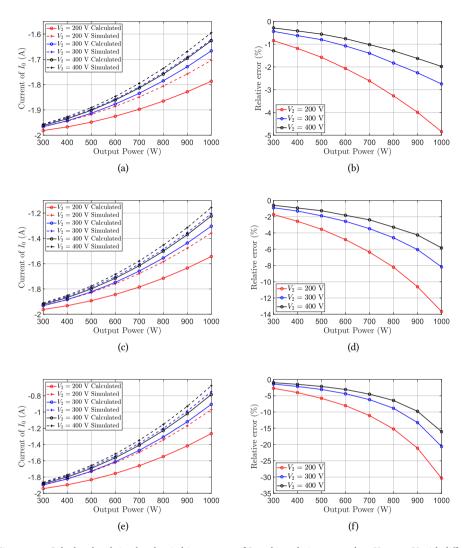

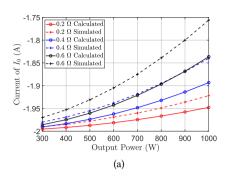

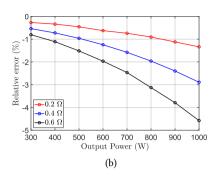

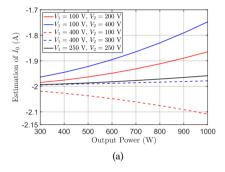

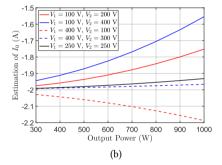

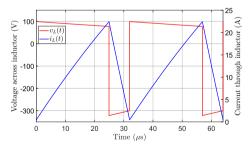

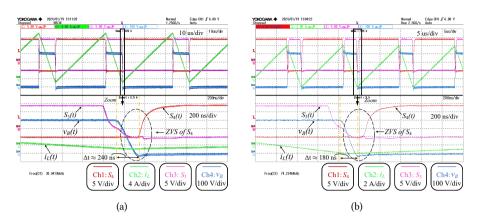

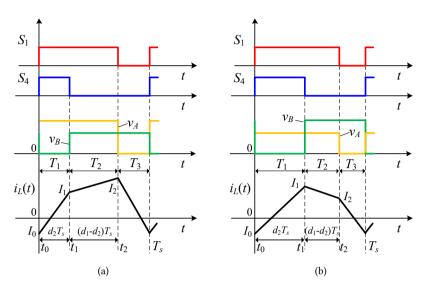

In fact, TCM-ZVS modulation can also be applied to the FSBB converter when input and output voltages are close, however, this will result in a large inductor rms current and is therefore not recommended in practice. For TCM-ZVS modulation, the reverse switching current through the inductor, which takes a negative value during the switching interval, is crucial for achieving soft switching for both switches in bidirectional buck, boost, and buck-boost converters. In an ideal situation without considering losses, this reverse switching current can be maintained at a constant value through variable-frequency technique, so the ZVS condition is always satisfied, however, this current value needs to be rethought in non-ideal situations because the decrease of this current (absolute value) could cause possible ZVS loss. Chapter 4 studied the parasitic resistance effects presented in the MOSFET switches and inductor on this reverse switching current for buck, boost and buck-boost converters under voltage-mode variable-frequency TCM-ZVS modulation respectively. Universal closed-form equations of the modified duty cycle and switching current were derived, which can be utilized to calculate the switching current under different operating conditions. The proposed analysis was evaluated and validated through an FSBB converter featuring TCM-ZVS buck, boost, and buck-boost operation capability. The operating voltage and power were from 100 V to 400 V, and 300 W to 1 kW, Summary xiii

respectively.

#### **Compensation Circuits**

This part focuses on the study of compensation circuits in terms of providing a more accurate calculation method for the electrical stresses in S-S and LCC-S compensated WPT systems, and a more accurate modeling on the current distortion in the LCC-S based WPT system.

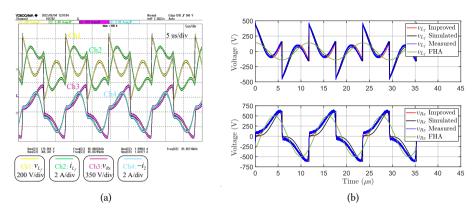

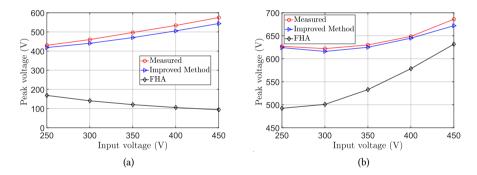

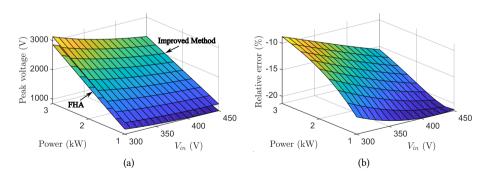

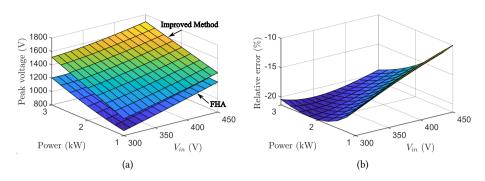

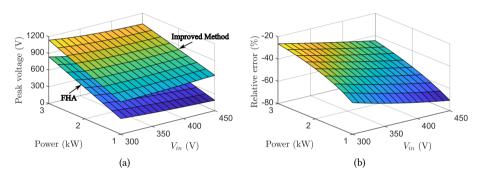

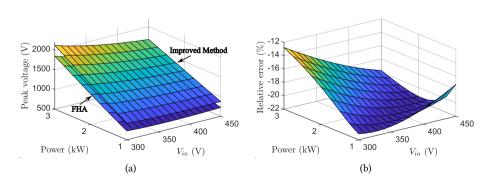

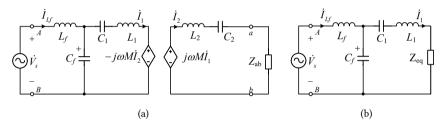

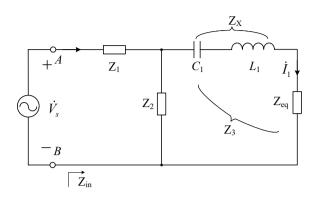

Accurately determining the electrical stresses of the compensation components is an important step in designing a reliable WPT system. However, it was found that the peak voltage calculation is not accurate enough for certain components when applying first harmonic approximation (FHA) method to the equivalent ac circuit. More precisely, the peak voltage calculated for the primary coil and secondary coil in S-S compensation, and the peak voltage calculated for the input resonant inductor and secondary coil in LCC-S compensation contained large errors compared with simulation results. Due to the high accuracy of the rms current calculation, an improved peak voltage calculation method in closed form was proposed in Chapter 6 based on Kirchhoff's voltage law considering the voltage across the related compensation capacitors. The proposed analysis was validated by both simulation and experiments.

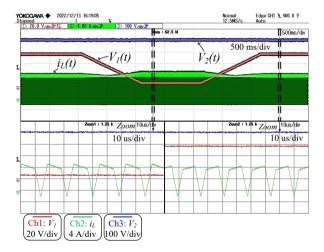

Due to the introduction of an additional LC branch in LCC-S compensation compared with S-S compensation, the current through the input resonant inductor has more distortion because of the influence from high-order harmonics. At the same time, the switching current through the input resonant inductor is closely related with the ZVS of the switches in the front-end H-bridge inverter. In order to calculate this switching current accurately, different from previous research, both the high-order harmonics from the primary and secondary sides were considered simultaneously in Chapter 7, and closed-form equations were derived. Unexpectedly, according to the analysis, the first-harmonic current also contributes to the switching current even for a fully compensated LCC-S based WPT system. The new method has shown an improved prediction of the switching current proved by simulation. However, it should be pointed out that the proposed analysis was based on the assumption that the square wave voltages on the primary and secondary sides are in phase, which requires further discussion.

## SAMENVATTING

Het opladen van elektrische voertuigen (EV's) via draadloze stroomoverdracht (WPT) is de afgelopen jaren uitgegroeid tot een nieuw oplaadconcept. Hoewel de efficiëntie van het WPT-oplaadsysteem met serie-serie (S-S) compensatie dankzij geoptimaliseerd magnetisch koppelingontwerp een zeer hoog niveau heeft bereikt, is het nog steeds gevoelig voor verschillende bedrijfsomstandigheden, zoals de koppelfactor. Om efficiënt draadloos opladen van EV's over een breed operationeel bereik mogelijk te maken en aan de oplaadeisen te voldoen, is extra vermogensomzettingscontrole nodig. Tegelijkertijd zijn de elektrische spanningen en de stroomvervorming in de compensatiecircuits ook cruciaal voor de efficiënte en veilige werking.

Voor een basis draadloos energieoverdrachtsysteem, zoals vermeld in veel referenties, omvat het doorgaans ten minste twee vermogensomzettingsstadia: een dc-ac omzettingsstadium en een ac-dc gelijkrichtingsstadium. Het dc-ac stadium zet de dc-voedingsbron om in een hoogfrequente ac-bron om de primaire spoel aan te drijven, terwijl het ac-dc stadium de ac-stroom die door de secundaire spoel wordt ontvangen, omzet in een dc-voedingsbron. In Hoofdstuk 2 is een overzicht gegeven van de meest geavanceerde structuur van WPT-oplaadsystemen. Op basis van dit overzicht kan worden geconcludeerd dat praktische WPT-oplaadsystemen meestal meerdere vermogensomzettingsstadia hebben, maar het is moeilijk te concluderen welke de beste configuratie en topologie voor vermogensomzetting is.

In dit proefschrift is een WPT-oplaadsysteem met LCC-S compensatie en een back-end FSBB-omzetter gekozen als het onderzoeksobject, en dit is gebaseerd op de overweging van de volgende factoren: 1) In vergelijking met front-end vermogensregeling vermijdt back-end vermogensregeling de communicatie tussen de primaire en secundaire zijde tijdens het opladen, wat de betrouwbaarheid van het systeem helpt te verbeteren; 2) Vanuit veiligheidssperspectief stelt een LCC-S-gebaseerd WPT-systeem werking zonder een secundaire spoel of met een open circuit aan de secundaire zijde mogelijk, wat een ingebouwd veiligheidsvoordeel biedt ten opzichte van een S-S gecompenseerd WPT-systeem; 3) Aangezien de WPT-spoelen al elektrische isolatie bieden, kan eenvoudig een niet-geïsoleerde dc-dcomzetter worden gebruikt om de gelijkspanningsomzetting te realiseren. In vergelijking met traditionele boost- of buck-omzetters biedt de FSBB-omzetter zowel spanningsverhoging als spanningsdaling, waardoor hij veelzijdiger is en beter geschikt voor draadloze oplaadsystemen.

De hoofdinhoud van het onderzoek in deze thesis is verdeeld in twee delen. Het eerste deel verdiept zich in de vier-schakelaar buck+boost (FSBB) converter, die fungeert als een extra vermogensconversiestap in het draadloze oplaadsysteem. Een uitgebreide en gedetailleerde analyse van de soft-switching modulatiestrategie voor deze converter werd onderzocht en gepresenteerd. Het tweede deel richt zich op de nauwkeurige modellering van elektrische spanningen en het fenomeen van stroomvervorming voor compensatietopologieën.

xvi Samenvatting

#### **Soft-Switching Modulatie van FSBB Converter**

In dit onderdeel ligt de nadruk op de soft-switching modulatie van de FSBB-converter om een hoogrendement en breedbandwerking te bereiken. Tegenwoordig kan een hardswitched dc-dc-omzetter hoewel ook een piekefficiëntie boven de 99% bereiken, de schakelverliezen niet worden geëlimineerd, wat een uitdaging vormt voor de hoge-frequentie of zelfs ultra-hoge-frequentie werking van de omzetter. Door de toenemende vraag naar hogere vermogensdichtheid en hogere bedrijfsfrequenties wordt zachte schakelmodulatie noodzakelijk. In dit proefschrift is met name de soft-switching techniek van nulspanningsschakeling (ZVS) bestudeerd.

In Hoofdstuk 3 werd een drie-modus variabele-frequentie ZVS-modulatie voorgesteld voor de FSBB-converter. De werking van de omzetter wordt onderverdeeld in drie werkingsgebieden op basis van de statische spanningsversterking van de omzetter, namelijk buck-, buck-boost- en boost-type modi. Voor de buck-type en boost-type modi werd TCM-modulatie (Triangular Current Mode) toegepast, terwijl in de buck-boost-type modus, wanneer de spanningsversterking dicht bij de eenheid ligt, drie-segment inductorstroommodusmodulatie werd geselecteerd als de optimale modulatietechniek in termen van reductie van de rms-stroom van de inductor en gebruiksgemak. Een laboratorium prototype van 300–600 V ingang, 400 V uitgang, 3 kW werd gebouwd om de voorgestelde concepten te bewijzen en te verifiëren. De omzetter werd getest over een breed vermogensbereik van 10% tot het volledige nominale vermogen. De gemeten efficiëntie was altijd hoger dan 99%, namelijk tussen 99,2% en 99,6%, van 1 tot 3 kW voor alle beschouwde ingangsspanningen.

Hoofdstuk 5 stelt single-mode ZVS-modulatie met variabele frequentie voor. Met deze modulatiemethode zijn de regelvariabelen van de duty cycle en de schakelingsfrequentie continu op de grens van eenheidsspanningsversterking, wat verschilt van de driemodus variabele-frequentie ZVS-modulatiemethode. In principe werd de drie-segmenten inductor stroommodus modulatie uitgebreid naar het gehele operationele bereik. Door de duty cycle voor de schakelaar in het buck-type of boost-type half-brug circuit vast te leggen en de duty cycle van de schakelaar in het andere half-brug circuit te regelen, de FSBB converter kan een soepele overgang realiseren bij de versterkingsgrens van de eenheidsspanning zonder dat dit ten koste gaat van de rms-stroom van de inductor, vergeleken met TCM-ZVS-modulatie. Een eenvoudige regelkring werd gepresenteerd zonder de noodzaak van detectie van spoelof schakelaarkringstroom. Daarnaast werd de selectie van de capaciteit van de invoer- en uitvoercondensatoren ook in detail geanalyseerd. Een FSBB-converter werd gebouwd en getest om de voorgestelde concepten te verifiëren, met een invoerspanning van 250–600 V, een uitvoerspanning van 400 V en een uitgangsvermogen van 250–2500 W.

TCM-ZVS-modulatie kan feitelijk ook worden toegepast op de FSBB-converter wanneer de ingangs- en uitgangsspanningen dicht bij elkaar liggen. Dit resulteert echter in een grote inductor-rms-stroom en wordt daarom in de praktijk niet aanbevolen. Voor TCM-ZVS-modulatie is de omgekeerde schakelstroom door de inductor, die tijdens het schakelinterval een negatieve waarde aanneemt, cruciaal om zachte schakeling te bereiken voor beide schakelaars in bidirectionele buck-, boost- en buck-boost-omvormers. In een ideale situatie, zonder rekening te houden met verliezen, kan deze omgekeerde schakelstroom op een constante waarde worden gehouden door middel van een variabele-frequentietechniek, de ZVS-voorwaarde is dus altijd vervuld. In niet-ideale situaties moet deze stroomwaarde

Samenvatting xvii

echter opnieuw worden bekeken, omdat de afname van deze stroom (absolute waarde) mogelijk ZVS-verlies kan veroorzaken. Hoofdstuk 4 onderzocht de effecten van parasitaire weerstand in de MOSFET-schakelaars en de spoel op deze omgekeerde schakelstroom voor buck-, boost- en buck-boost-omvormers onder spanningsgestuurde variabele-frequentie TCM-ZVS-modulatie. Universele gesloten vergelijkingen voor de gemodificeerde duty cycle en schakelsstroom werden afgeleid, die kunnen worden gebruikt om de schakelsstroom onder verschillende bedrijfsomstandigheden te berekenen. De voorgestelde analyse werd geverifieerd met behulp van een FSBB-converter met TCM-ZVS buck-, boost- en buck-boost-bedrijfsmogelijkheden. De bedrijfsspanning en het vermogen bedroegen respectievelijk 100 tot 400 V en 300 W tot 1 kW.

#### **Compensatie Circuits**

Dit gedeelte richt zich op de studie van compensatiecircuits in termen van het bieden van een nauwkeuriger berekeningsmethode voor de elektrische stress in S-S en LCC-S gecompenseerde WPT-systemen, en een nauwkeuriger modellering van de stroomvervorming in LCC-S gebaseerde WPT-systemen.

Het nauwkeurig bepalen van de elektrische stress van de compensatie componenten is een belangrijke stap bij het ontwerpen van een betrouwbaar WPT-systeem. Het werd echter vastgesteld dat de piekspanningsberekening niet nauwkeurig genoeg is voor bepaalde componenten wanneer de eerste harmonische benadering (FHA) methode wordt toegepast op het equivalente wisselstroomcircuit. Meer precies, de piekspanning berekend voor de primaire spoel en secundaire spoel in S-S compensatie, en de piekspanning berekend voor de invoerresonantie-inductor en secundaire spoel in LCC-S compensatie bevatte grote fouten in vergelijking met de simulatie-resultaten. Vanwege de hoge nauwkeurigheid van de rms-stroomberekening werd in hoofdstuk 6 een verbeterde berekeningsmethode voor de piekspanning in gesloten vorm voorgesteld, gebaseerd op de spanningswet van Kirchhoff, waarbij rekening wordt gehouden met de spanning over de gerelateerde compensatiecondensatoren. De voorgestelde analyse werd gevalideerd door zowel simulatie als experimenten.

Door de introductie van een extra LC-tak in LCC-S compensatie in vergelijking met S-S compensatie, vertoont de stroom door de invoerresonantie-inductor meer vervorming door de invloed van hogere harmonischen. Tegelijkertijd is de schakel stroom door de invoer resonant-inductor hangt nauw samen met de ZVS van de schakelaars in de voorste H-brugomvormer. Om deze schakelsstroom nauwkeurig te berekenen, werden in Hoofdstuk 7, in tegenstelling tot eerder onderzoek, zowel de hogere harmonischen van de primaire als de secundaire kant gelijktijdig in overweging genomen, en werden gesloten vergelijkingen afgeleid. Onverwacht, volgens de analyse, draagt de eerste-harmonische stroom ook bij aan de schakelsstroom, zelfs voor een volledig gecompenseerd LCC-S gebaseerde WPT-systeem. De nieuwe methode heeft een verbeterde voorspelling van de schakelstroom aangetoond, zoals bewezen door simulatie. Het moet echter worden opgemerkt dat de voorgestelde analyse is gebaseerd op de veronderstelling dat de vierkante golfspanningen aan de primaire en secundaire zijde in fase zijn, wat verdere discussie vereist.

## **ABBREVIATIONS**

**AC** Alternating Current

**BESS** Battery Energy Storage System

CC Constant Current

**CCM** Continuous Conduction Mode

**CV** Constant Voltage

**DC** Direct Current

**DCM** Discontinuous Conduction Mode

**EMI** Electromagnetic Interference

**EV** Electric Vehicle

**FHA** First Harmonic Approximation

**FSBB** Four-Switch Buck+Boost

**GA** Ground Assembly

**iGSE** Improved Generalized Steinmetz Equation

**IPT** Inductive Power Transfer

**LCC-S** Inductance and Double Capacitances-Series

**ORNL** Oak Ridge National Laboratory

PCB Printed Circuit board

PI Proportional-Integral

P-P Parallel- Parallel

**PWM** Pulse Width Modulation

RMS Root Mean Square

SiC Silicon Carbide

**SMD** Surface-Mounted Device

XX ABBREVIATIONS

**S-S** Series-Series

**SAE** Society of Automotive Engineers

TCM Triangular Current Mode

VA Vehicle Assembly

**WPT** Wireless Power Transfer

**ZCS** Zero Current Switching

**ZPA** Zero Phase Angle

**ZVS** Zero Voltage Switching

1

## Introduction

#### 1.1 BACKGROUND AND MOTIVATION

Road transport electrification has become a sustainable and effective means in climate change and air pollution mitigation. After more than 120 years of development since their introduction in the early 20th century together with internal combustion engine vehicles, electric vehicles (EVs) have finally become a viable solution for an increasing number of private and public transport drivers [1]. Some countries and cities have already announced measures towards the transition to electrified mobility.

The battery is the heart of an EV, providing the energy needed for propulsion and supporting the efficient operation of various systems in the vehicle. Although battery technology is constantly improving, for example, increased energy density and capacity, innovative battery charging solutions are still required to increase the acceptance of EVs and acceleration from traditional to electric mobility [2].

Transmission of power without wires has been envisioned since times of Nikola Tesla. Much achievement has been made in this field since the major success of lighting up a bulb with wireless power from two meters away in 2007 [3], [4]. Compared with traditional wired or plug-in charging systems, wireless power charging offers several benefits. Wireless charging can eliminate the need to plug and unplug cables, making it easier to charge EVs, and this also mitigates the safety concerns such as risk of sparks, short circuits or physical damage to ports caused by poor cable connection and moisture. Since no physical connection is required, wireless charging eliminates wear and tear on charging ports and cables, helping to extend the service life of electrical equipment.

A typical wireless power transfer (WPT) charging system comprises a transmitting unit that transmits the power and a receiving unit that receives this power wirelessly and uses it to charge the battery [5]. According to [5], WPT systems are classified into three categories: inductive, inductive-resonant and capacitive. In this thesis, only inductive-resonant method is discussed and studied, which combines the principles of both inductive and resonant coupling to efficiently transfer energy over a distance without the need for physical connection. In particular, a method of wireless power transfer using magnetic induction is also known as inductive power transfer (IPT). In order to achieve resonance, one can use compensation schemes with series and parallel capacitors and inductors. For

2 1 Introduction

Figure 1.1: Transmitting and receiving coils in an inductive-resonant WPT system [5].

example, Figure 1.1 shows the WPT coils in a resonant WPT system with compensation capacitors on each side. A detailed review on the WPT system topology will be presented in Chapter 2.

At present, optimal designs have already made the efficiency of WPT charging reach a very high level featuring series-series (S-S) compensation [6], [7], [8]. For example, the peak dc-dc efficiency was measured to be 97.2% at 20 kW in [7]. However, the shortcomings of these efficient wireless transmission systems are also obvious, and they are: 1) The peak efficiency was measured at aligned condition, when misalignment occurs, efficiency begins to drop significantly. For example, the dc-dc efficiency drops from 97.2% to 94.1% with 15 cm lateral misalignment [7]; 2) For S-S compensated WPT system, the power transfer efficiency reaches the peak at optimal operating point [9]. When the connected load deviates from this optimal working point, the system efficiency is no longer satisfactory. In summary, although wireless charging can currently achieve efficient power transmission, its working range for efficient power transmission is still narrow. Therefore, how to ensure its efficient operation across a wide range of working conditions to adapt to different scenarios has become an important research topic.

The research focus of this thesis is to study methods for enabling efficient wireless charging over a wide operational range. More precisely, this thesis mainly studies the high-efficiency wide-range operation strategy of non-isolated dc-dc converters and the accurate modeling method of wireless charging compensation network. The detailed study of these two parts provides feasible methods and strategies for the optimal operation of the entire wireless charging system. Briefly, it starts with the overview of state-of-the-art WPT system topology, and this introduces the need to study non-isolated dc-dc converters. Next, modulation strategies to enhance the efficiency performance of the dc-dc converters was researched, more specifically, the focus was on the soft-switching operation of the converter. In the second part, accurate modeling on the compensation topologies in terms of electrical stresses and current distortion phenomenon was given.

## 1.2 Thesis Objective and Research Questions

As indicated previously, the research objective of this thesis is as follows.

"To research the promising topology of a WPT charging system, and optimization on the operation of its power electronic conversion stages for high efficiency electric vehicle charging over a wide operating range."

More Specifically, the research focus is mainly divided into two parts. The first part

is on the research of high efficiency operation for non-isolated dc-dc converters over a wide operational range taking into account the wireless charging background. The second part is on the modeling of compensation networks for the purpose of achieving more accurate electrical stresses and distorted current calculation. These two parts represent two important subsystems of a whole WPT system. A breakdown of the research objective leads to several research questions as follows.

#### Question 1: What is the state-of-the-art topology of a WPT charging system?

In recent years, wireless power transfer has become a very popular research direction as mentioned previously. Numerous research outcomes on this topic are being published every year. Research on WPT topic can be mainly divided into three broad categories: 1) coil/pad designs; 2) compensation topologies; 3) power converters and control. Within each category, the available options are not unique. For example, with regard to compensation topology, one can choose serial or parallel compensation, lower order or high order compensation etc. On the other hand, different compensation methods have different output characteristics, which will affect the selection and operation of the peripheral circuits. Because of these uncertainties, it is necessary to conduct a comprehensive review of the current WPT charging systems with a focus on the corresponding system topology, and this will be addressed in Chapter 2.

## Question 2: How to optimize the operation of the FSBB converter such that it can operate efficiently over a wide operational range?

Since the WPT coil charging pads have already provided electrical isolation between the primary and secondary side, so one only needs to use non-isolated dc-dc converters if a dc-dc conversion stage is needed. Traditional buck and boost converters can only step down or step up the input voltages, which limits their wider applications. Although traditional buck-boost converter can not only step up but also step down the input voltage, it usually has a large inductor rms current, which lowers the converter efficiency. Different from these above mentioned converters, the four-switch buck+boost (FSBB) converter also features both voltage step-up and step-down functions, meanwhile, due to a greater degree of freedom, modulation strategy can be researched for its optimal operation. These characteristics make the FSBB converter a promising topology that can be used in a WPT charging system to help achieve high efficiency power transfer over a wide operational range. Therefore, research on optimal modulation strategy for the FSBB converter is necessary, which will be addressed in Chapter 3.

## Question 3: How the parasitic resistances affect the reverse switching current in a dc-dc converter featuring voltage-mode TCM-ZVS modulation?

Compared with hard-switching modulation such as continuous conduction mode (CCM) and discontinuous conduction mode (DCM) operation, traditional dc-dc converters based on a single active switch (this switch is referred to as the original switch in this paragraph) cannot achieve zero-voltage switching. However, one can simply replace the diode with an active switch, and then both switches can be soft-switched through TCM-ZVS modulation. In fact, TCM-ZVS modulation can also be applied to the FSBB converter. In TCM-ZVS

1 Introduction

1

modulation, the reverse switching current through the inductor is the key for the original switch to achieve soft switching. In an ideal case without losses, this switching current can be maintained as a constant value through variable-frequency control. On the other hand, detection of switching current at a high frequency is also a challenge. So variable-frequency voltage-mode TCM-ZVS modulation is preferred. However, in reality, losses is inevitable, so to study the influence on this switching current considering parasitic resistance is meaningful, and this question will be addressed in Chapter 4.

## Question 4: How to operate the FSBB converter with a smooth transition between step-up and step-down mode without compromising efficiency?

As mentioned previously, on one hand, the FSBB converter features both voltage step-up and step-down functions. On the other hand, due to the greater degree of control freedom, the FSBB converter can operate in different modulation modes. The optimal working mode obtained under buck and boost situations does not guarantee that the transition between these two modes will be seamless. Therefore, when the converter changes its operating mode, which usually happens near the unit input-to-output voltage gain, the converter can experience some severe operating oscillations. In order to reduce the negative effects caused by mode switching, an improved modulation strategy should be introduced while maintaining high efficiency operation of the converter. This question will be addressed in Chapter 5.

## Question 5: How to accurately determine the electrical stresses of the compensation components in an S-S and LCC-S compensated WPT system?

As mentioned in the first question, compensation topology is an indispensable part of the WPT system. Among the commonly used compensation topologies, S-S and LCC-S compensations are the two widely adopted topologies. S-S compensated WPT system features constant current output and while LCC-S compensated one features constant voltage output. To accurately determine the electrical stresses of the compensation components is a necessary step to design a reliable WPT system especially for a high-power system, where the resonant peak voltage could easily reach several kilovolts or more, and this presents a greater challenge to the insulation requirements of the components. It is found that the peak voltage calculation is not accurate enough for certain components when applying first harmonic approximation method to the equivalent ac circuit. This question will be addressed in Chapter 6.

## Question 6: How to model current distortion of the input resonant inductor in an LCC-S compensated WPT system?

Compared with S-S compensation, although LCC-S compensation introduces one more LC resonant tank in the primary side, one can use this extra LC circuit to produce a controllable current in the primary coil. This is a beneficial feature because it allows the secondary circuit to be open, but it is fatal to S-S compensation because, in theory, an open circuit from secondary side would induce an infinite current in the primary coil. Furthermore, with the help of serial compensation in the secondary side, constant voltage output can be achieved. On the other hand, the current distortion phenomenon from the

primary side is more obvious in an LCC-S compensated WPT system, and the switching current through the input resonant inductor is closely related with the ZVS realization of the switches in the front-end H-bridge inverter. Therefore, how to accurately and correctly model this current distortion is important. This question will be addressed in Chapter 7.

#### 1.3 Contributions

Targeting to give answers to the aforementioned research questions, the thesis has the contributions as follows.

- A literature review on state-of-the-art WPT charging system topology for electric vehicles was presented (**Chapter 2**).

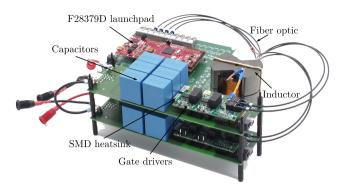

- A three-mode variable-frequency ZVS modulation was developed for the FSBB converter. Detailed closed-form equations for the operation of the converter were presented. A 3 kW SMD SiC MOSFET-based laboratory prototype with designed input voltage of 300–600 V and output voltage of 400 V was built to evaluate and validate the proposed concepts (**Chapter 3**).

- A universal analytical modeling and calculation method was proposed in closed form to calculate the reverse switching current for buck, boost and buck-boost converters under voltage-mode variable-frequency TCM-ZVS modulation respectively. An FSBB converter with operating voltage of 100–400 V and operating power of 300–1000 W was built to validate the proposed analysis (**Chapter 4**).

- An improved variable-frequency ZVS modulation was developed for the FSBB converter with a smooth transition between step-up and step-down mode. Detailed design procedures were presented. The proposed approach was evaluated and validated by an FSBB converter prototype with an input voltage of 250–600 V, output voltage of 400 V and output power of 250–2500 W (Chapter 5).

- An improved peak voltage calculation method was developed for the compensation components in S-S and LCC-S compensated WPT system, which was validated by both simulation and experimentation (**Chapter 6**).

- An improved analytical method was developed for accurate calculation of the switching current in a fully compensated LCC-S based WPT system, which was verified by simulation (Chapter 7).

6 1 Introduction

1

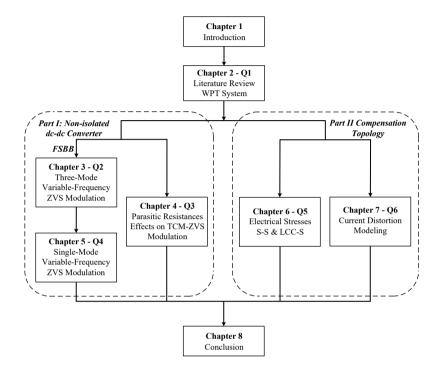

#### 1.4 THESIS OUTLINE

The outline of the remainder of this thesis and the interrelations between the chapters are schematically shown in Figure 1.2.

Figure 1.2: Outline of this thesis and the interrelation between the chapters.

2

## BRIEF OVERVIEW OF WPT SYSTEM TOPOLOGY

In this chapter, a brief overview of wireless power transfer system topology will be presented, which explains and illustrates the rationality and feasibility of introducing non-isolated dc-dc converters in wireless charging applications. The WPT research progress introduced in this chapter is divided into three categories by region. Although the literature study provides an overview of development trend and common design choices, it might not be able to cover all studies carried out recently because of the rapid development in this field. <sup>1</sup>

<sup>&</sup>lt;sup>1</sup>Part of this chapter is based on: G. Yu, T. B. Soeiro, J. Dong and P. Bauer, "Study of Back-end DC/DC Converter for 3.7 kW Wireless Charging System according to SAE J2954," 2021 IEEE 15th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), Florence, Italy, 2021, pp. 1-8, doi: 10.1109/CPE-POWERENG50821.2021.9501207.

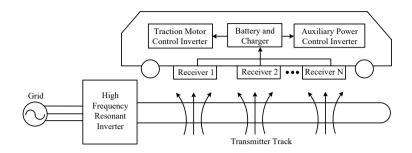

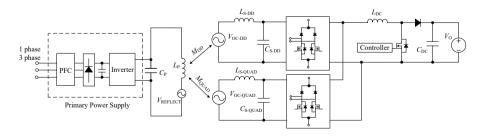

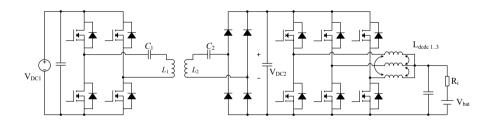

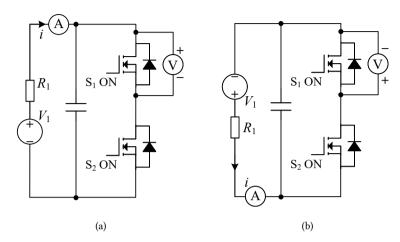

Figure 2.1: Power circuits of the inverter system in [10].

#### 2.1 WPT Research Progress in Asia

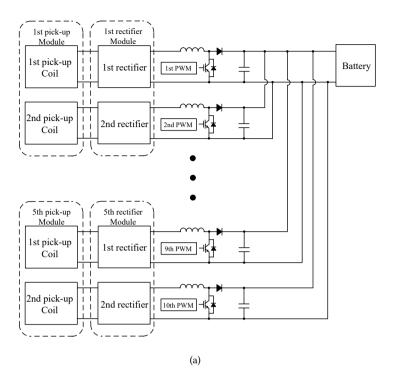

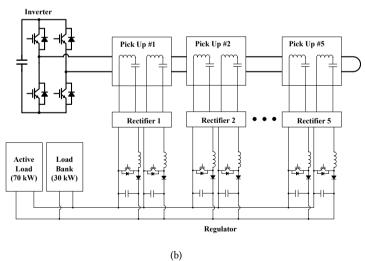

Jaegue Shin et al. from Korea Advanced Institute of Science and Technology (KAIST) built a 100 kW WPT system with 80% efficiency under 26-cm air gap in 2013 [10] . The power supply systems for the proposed system are shown in Figure 2.1. Five 20-kW pickup modules are adopted to obtain 100-kW power capacity, which is shown in Figure 2.2. From Figure 2.2, the inputs of ten boost converters are connected to the outputs of rectifiers while the outputs of ten boost converters are connected to a battery.

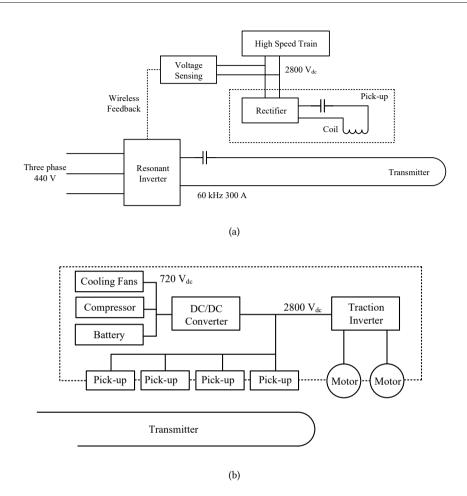

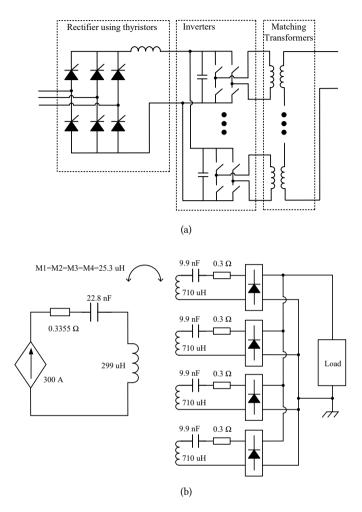

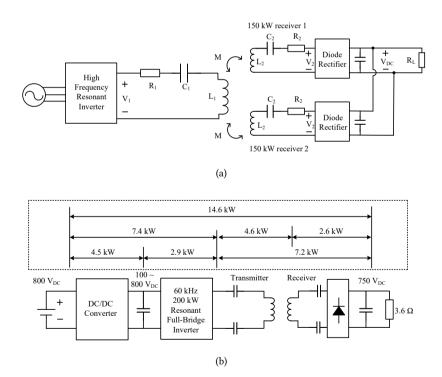

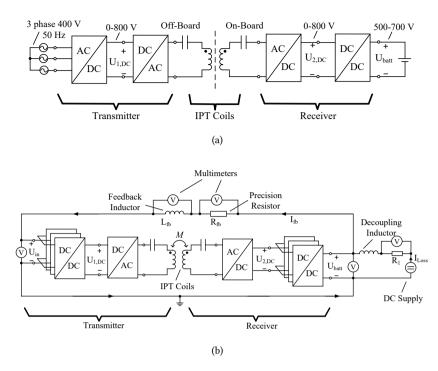

Jae Hee Kim et al. from Korea Railroad Research Institute designed and built a 1 MW inductive power transfer system that supplies power to the vehicle in 2015 [11]. The system efficiency was 82.7% at 60 kHz resonant frequency. Figure 2.3(a) shows the configuration of the WPT system for a high-speed train while Figure 2.3(b) shows the electric block diagram. The output voltage of the pick-ups was 2800 V for motor traction, and it was stepped down to 720 V for battery charging through dc-dc converters. The front-end dc voltage was acquired through a thyristor rectifier, and five 200 kW inverters were connected in parallel to convert the dc power to a 60-kHz power source, which is illustrated by Figure 2.4(a). Figure 2.4(b) shows the equivalent circuit with the parameters from the transmitter and pickup. The gap was 5 cm from core to core.

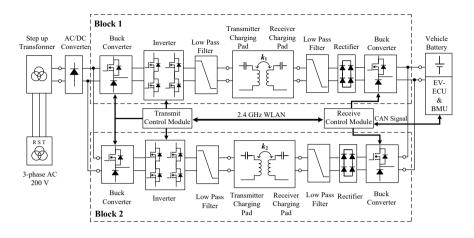

Seung-Hwan Lee et al. from University of Seoul developed a 180 kW inductive power transfer system for a tram in 2016 [12]. The measured efficiency of the system was 85% at 60 kHz and 172 kW output. The equivalent block diagram of the developed system is shown in Figure 2.5. From Figure 2.5, three 60 kW pick-ups and a voltage regulator were installed and delivered power to the battery. The air gap between the transmitter and the pick-up was 7 cm. The output terminals of the pick-ups were connected to diode rectifiers, and a boost regulator was used to supply a constant output voltage [12].

Seung-Hwan Lee et al. from University of Seoul proposed a design methodology for a 300 kW, over 96% coil-to-coil efficiency, online WPT system in 2016 [13]. The overall system block diagram is shown in Figure 2.6. The single 300 kW receiver was separated into two 150 kW receivers in parallel shown in Figure 2.7(a). Figure 2.7(b) shows the measured losses of each component at the rated operation. It can be concluded that the losses of the TX and RX coils dominated the total losses [13].

Tetsu Shijo, Shuichi Obayashi et al. from Toshiba Corporation developed a 44 kW

Figure 2.2: (a) Functional diagram of the online electric vehicle (OLEV) power receiver system [10]. (b) Lab construction of the WPT system [10].

Figure 2.3: (a) Configuration of the WPT system for a high-speed train [11]. (b) Electric block diagram of the train using WPT system [11].

WPT system for electric bus charging in the 85 kHz resonant frequency band in 2016 [14], [15], [16]. The transmission distance between the charging pads was 10-13 cm, and the total power transmission efficiency was larger than 85%. A two channel WPT system was adopted with opposite phase current in the transmitting coils to minimize the electromagnetic radiation [14], [15], [16]. Figure 2.8 shows the block diagram of the developed WPT system.

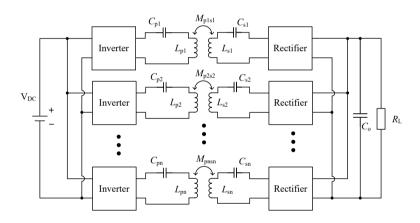

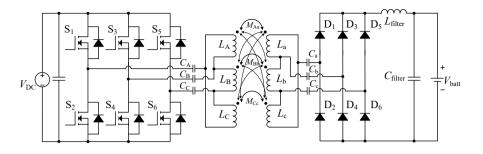

Abubakar Uba Ibrahim et al. from Zhejiang University built a 50 kW three-channel WPT prototype in 2020 with a dc-dc efficiency of 95.2% across 16 cm air gap [17]. The circuit topology is shown in Figure 2.9.

Ganesh R. Nagendra et al. from the University of Auckland developed a 10 kW on-road dynamic inductive power transfer charger with air-gaps ranging from 25-40 cm in 2017 [18]. A secondary power flow controller similar to the one shown in Figure 2.10 was used to regulate the power transfer to the EVs.

Figure 2.4: (a) Block diagram of the 1-MW resonant inverter for a high-frequency power source [11]. (b) Equivalent circuit of the transmitter and pickups [11].

Figure 2.5: Equivalent block diagram of the test-bed [12].

Figure 2.6: Overall system block diagram of a target online WPT system [13].

Figure 2.7: (a) Two 150-kW wireless power transfer system [13]. (b) Measured losses of the test-bed [13].

Figure 2.8: Block diagram of dual-block 44 kW wireless rapid charging system [14], [15], [16].

Figure 2.9: Circuit topology of a multichannel system without showing cross mutual inductance [17].

Figure 2.10: Secondary power flow controller [18].

Figure 2.11: (a) WPT system power conversion chain [8]. (b) Experimental setup with energy feedback at the dc link for direct power loss and efficiency measurements [8].

#### 2.2 WPT RESEARCH PROGRESS IN EUROPE

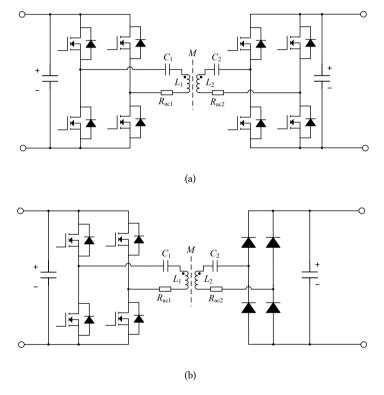

Roman Bosshard et al. from ETH Zurich developed a 50 kW WPT system operating at 85 kHz resonant frequency with an air gap of 16 cm in 2016. The dc-dc conversion efficiency (including all the power electronics stages) was 95.8% at 50 kW across 16 cm air gap while the efficiency dropped to 92% with a 15 cm coil misalignment [8], [19]. Figure 2.11 shows the power electronics architecture and the test setup of the WPT system [8]. Three parallel-interleaved buck+boost dc-dc converter modules with coupled magnetic components were adopted, which is shown in Figure 2.12 [19].

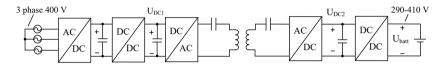

B. Goeldi and J. Tritschler et al. from Fraunhofer Institute developed a 22 kW WPT system operating at 100 kHz resonant frequency with over 97% efficiency (dc link to dc link) in 2015, and the nominal coil separation was 13.5 cm [20], [21]. The block diagram of the WPT charging system is shown in Figure 2.13.

Marinus et al. from University of Kiel developed a 6 kW SS-compensated WPT system prototype for low voltage battery charging application in 2015 [22]. The input voltage was 400 V and the output voltage was 24 V. Efficiency between 89% and 94.2% was achieved in any operating conditions between 1 and 6 kW output power. The air gap was between 20 mm and 100 mm while the resonance frequency was 60 kHz. The corresponding power electronic configuration of the system is shown in Figure 2.14.

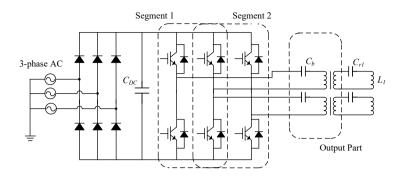

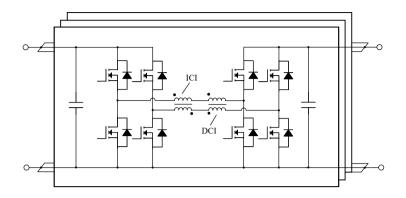

Jacopo Colussi et al. from Polytechnic University of Turin constructed a 100 kW three-

Figure 2.12: Buck+Boost converter with inverse-coupled inductor (ICI) and direct-coupled inductor (DCI) [19].

Figure 2.13: Block diagram of the WPT charging system [20].

Figure 2.14: Power electronic configuration of the system for high power and low voltage applications [22].

phase WPT prototype operating at 85 kHz with more than 94% dc-dc efficiency over 50 mm air gap distance in 2021 [23]. The dc input voltage was 580 V. The equivalent circuit is shown in Figure 2.15.

Daniel E. Gaona et al. from University of Cambridge built an 11.1 kW WPT system operating at 85 kHz utilizing nanocrystalline ribbon cores in 2021 [24]. The commonly used H-bridge inverter was connected to the transmitter coil while the receiver coil was connected to a passive full-wave diode rectifier.

Recently, Wenli Shi and Francesca Grazian et al. from Delft University of Technology built a 20 kW and 3.7 kW WPT prototypes in 2021 and 2022, respectively [6], [7]. Both prototypes operated at 85 kHz resonance frequency. The peak dc-dc efficiency was 97.2% for the 20 kW prototype while the peak dc-dc efficiency was 96.2% for the 3.7 kW one. The equivalent circuits for the two WPT systems are shown in Figure 2.16.

Figure 2.15: Equivalent circuit scheme of the WPT system [23].

Figure 2.16: Equivalent circuit of the WPT system in (a) [7] and in (b) [6].

# 2.3 WPT RESEARCH PROGRESS IN USA

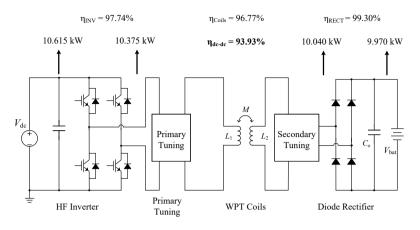

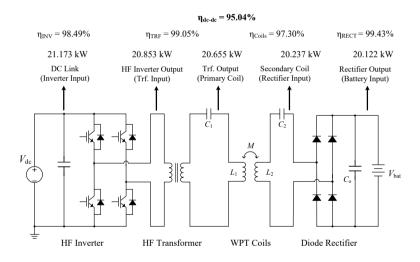

The Oak Ridge National Laboratory (ORNL) has done extensive research work in WPT. Veda P. Galigekere et al. from ORNL built a 10 kW LCC-S compensated WPT system with 94% efficiency in 2017 [25]. The system efficiency of each stage is shown in Figure 2.17. From Figure 2.17, the efficiency of the inversion stage was only 97.74%, however, this

Figure 2.17: System efficiency description of each stage [25].

Figure 2.18: Stage-by-stage power flow and efficiencies for 20 kW power transfer [26].

inversion stage typically could reach 99% efficiency with adoption of SiC MOSFETs and soft-switching technique nowadays. So, the dc-dc efficiency can be improved to 95%.

Omer C. Onar et al. from ORNL developed a 20 kW stationary WPT charging system for electric vehicle featuring series-series compensation in 2018 [26]. The dc-dc efficiency (inverter input to the vehicle battery terminals) was over 95%. Figure 2.18 shows the power flow and efficiencies for this WPT system [26].

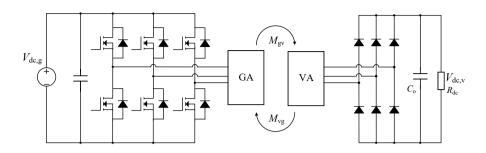

Jason Pries et al. from ORNL designed and made a novel three-phase 50 kW WPT system using series resonant networks in 2019 [27]. The dc-dc efficiency was 95% with a 15 cm air gap. The system diagram is shown in Figure 2.19.

Figure 2.19: WPT system diagram. The GA and VA blocks represent any series resonant circuit [27].

Figure 2.20: System-level schematic of the DLCC WPT charging system [28].

Figure 2.21: Equivalent circuit of the entire WPT system [29].

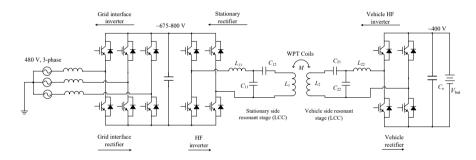

Mostak Mohammad et al. from ORNL designed and built a bidirectional 20 kW WPT charging system featuring double-sided LCC (DLCC) compensation network in 2020 [28]. The air gap was 28 cm, the input voltage was 800 Vdc and the output voltage was 350 Vdc, and the resonance frequency was 22 kHz. The grid-to-vehicle dc-dc efficiency was 96.1% while the vehicle-to-grid dc-dc efficiency was 96.2%. The system-level schematic of the WPT system is shown in Figure 2.20.

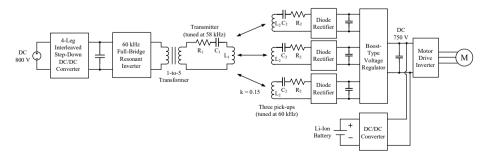

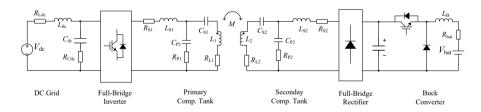

Reza Tavakoli et al. from Utah State University built a 25 kW dynamic WPT charging system for roadway electric vehicles in 2017 [29], [30]. The measured efficiency was 86%, and the equivalent circuit of the WPT system is shown in Figure 2.21.

Table 2.1: Summary of WPT research progress.

| References                                                         | Year | Power<br>(kW) | Resonance<br>Frequency<br>(kHz) | Power Conversion<br>Stages                                  | Voltage Range                                 | Compensation<br>Type         | System<br>Efficiency |

|--------------------------------------------------------------------|------|---------------|---------------------------------|-------------------------------------------------------------|-----------------------------------------------|------------------------------|----------------------|

| Jaegue Shin et al.<br>KAIST [10]                                   | 2013 | 100           | 20                              | AC-DC, DC-AC,<br>AC-AC, WPT Coil,<br>AC-DC, DC-DC           | 500 Vdc (Inverter)<br>-620 Vdc (Output)       | S-S                          | 80%                  |

| Jae Hee Kim et al.<br>Korea Railroad<br>Research Institute [11]    | 2015 | 1000          | 60                              | AC-DC, DC-AC,<br>AC-AC, WPT Coil,<br>AC-DC, DC-DC           | AC Grid-2800 Vdc<br>(720 Vdc)                 | S-S                          | 82.7%                |

| Seung-Hwan Lee et al.<br>University of Seoul [12]                  | 2016 | 180           | 60                              | DC-DC, DC-AC,<br>AC-AC, WPT Coil,<br>AC-DC, DC-DC           | 800 Vdc-750 Vdc                               | S-S                          | 85%                  |

| Seung-Hwan Lee et al.<br>University of Seoul [13]                  | 2016 | 300           | 60                              | DC-DC, DC-AC,<br>WPT Coils, AC-DC                           | 800 Vdc-750 Vdc                               | S-S                          | 90.4%                |

| Tetsu Shijo et al.<br>Toshiba Corporation [16]                     | 2016 | 44            | 85                              | AC-AC, AC-DC,<br>DC-DC, DC-AC,<br>WPT Coil, AC-DC,<br>DC-DC | AC Grid-300 Vdc                               | S-S                          | 85%                  |

| A. U. Ibrahim et al.<br>Zhejiang University [17]                   | 2020 | 50            | 85                              | DC-AC, WPT Coil,<br>AC-DC                                   | 800 Vdc-600 Vdc                               | S-S                          | 95.2%                |

| G. R. Nagendra et al.<br>University of<br>Auckland [18]            | 2017 | 10            | 40                              | AC-DC, DC-AC,<br>WPT Coil, AC-DC,<br>DC-DC                  | AC Grid-325 Vdc                               | P-P                          | NA                   |

| Roman Bosshard et al.<br>ETH [8]                                   | 2015 | 50            | 85                              | DC-DC, DC-AC,<br>WPT Coil, AC-DC,<br>DC-DC                  | 800 Vdc-800 Vdc                               | S-S                          | 95.8%                |

| B. Goeldi and<br>J. Tritschler et al.<br>Fraunhofer Institute [20] | 2015 | 22            | 100                             | AC-DC, DC-DC,<br>DC-AC, WPT Coil,<br>AC-DC, DC-DC           | AC Grid-(290–410) Vdc                         | S-S                          | 90.98%               |

| Marinus et al.<br>University of Kiel [22]                          | 2015 | 6             | 60                              | DC-AC, WPT Coil,<br>AC-DC, DC-DC                            | 400 Vdc-24 Vdc                                | S-S                          | 94.2%                |

| Jacopo et al.<br>Polytechnic University<br>of Turin [23]           | 2021 | 100           | 85                              | DC-AC, WPT Coil,<br>AC-DC                                   | 580 Vdc-380 Vdc                               | S-S                          | 94.1%                |

| Daniel et al.<br>University of<br>Cambridge[24]                    | 2021 | 11.1          | 85                              | DC-AC, WPT Coil,<br>AC-DC                                   | ~ 600 Vdc-~ 600Vdc                            | S-S                          | 95.5%                |

| Wenli Shi et al.<br>TU Delft [7]                                   | 2021 | 20            | 85                              | DC-AC, WPT Coil,<br>AC-DC                                   | 800 Vdc-800 Vdc                               | S-S                          | 97.2%                |

| Francesca et al.<br>TU Delft [6]                                   | 2022 | 3.7           | 85                              | DC-AC, WPT Coil,<br>AC-DC                                   | (360–500) Vdc<br>-(280–400) Vdc               | S-S                          | 96.2%                |

| Veda et al.<br>ORNL [25]                                           | 2017 | 10            | 22                              | DC-AC, WPT Coil,<br>AC-DC                                   | 355 Vdc-380 Vdc                               | LCC-S                        | 93.9%                |

| Omer et al.<br>ORNL [26]                                           | 2018 | 20            | 21-24                           | DC-AC, AC-AC,<br>WPT Coil,<br>AC-DC                         | (418–439) Vdc<br>-381 Vdc                     | S-S                          | 95%                  |

| Jason Pries et al.<br>ORNL [27]                                    | 2019 | 50            | 85                              | DC-AC, WPT Coil,<br>AC-DC                                   | ~ 555 Vdc-~ 585 Vdc or<br>~ 297 Vdc-~ 338 Vdc | 3-ph series<br>resonant tank | 95%                  |

| Mostak et al.<br>ORNL [28]                                         | 2020 | 20            | 22                              | AC-DC, DC-AC,<br>WPT Coil, AC-DC                            | (675–800) Vdc<br>-(320–400) Vdc               | LCC-LCC                      | 96.1%                |

| Reza et al.<br>Utah State<br>University [29], [30]                 | 2017 | 25            | 20                              | DC-AC, WPT Coil,<br>AC-DC, DC-DC                            | 600 Vdc-330 Vdc                               | LCC-LCC                      | 86%                  |

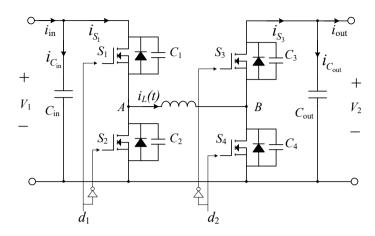

Figure 2.22: Schematic of LCC-S based WPT charging system with a back-end FSBB converter.

# 2.4 SUMMARY AND DISCUSSION

# 2.4.1 A Brief Summary

Based on the literature review, a table of summary on the design choices of recent remarkable works is given in Table 2.1.

# 2.4.2 Discussion

From the literature studied previously, it can be found that dc-dc converters have been widely adopted in the wireless power transfer charging systems. These dc-dc converters can be put on the primary side, secondary side or both sides for the purpose of power and voltage regulation. Since the WPT coils have already provided electrical isolation, so, non-isolated dc-dc converters can simply be used. In addition, compared with traditional buck and boost converters, which could only realize voltage step-down or step-up function, the FSBB converter can achieve both voltage step-down and step-up functions. Therefore, it is beneficial to adopt this dc-dc topology. In this thesis, a WPT charging system featuring LCC-S compensation and a back-end FSBB converter was chosen as the research object, and the schematic is shown in Figure 2.22.

There are several advantages with wireless charging solution shown in Figure 2.22, and they are as follows.

- Compared with font-end power regulation, back-end power regulation avoids communication between wireless charging pads during charging, which helps improve the system reliability.

- Different from S-S compensation, LCC-S based WPT system features inherent safety advantage. Because for the S-S compensated WPT system, when the inverter stage is operating, it is not allowed to have no secondary side coil or an open circuit on the secondary side, otherwise, the primary side is equivalent to a short circuit. To prevent such situations from occurring, this indicates that the S-S compensated WPT system needs to have more reliable, stable, and fast detection capabilities in this regard. But for LCC-S compensation, it is allowed to have no secondary coil or an open circuit on the secondary side.

|                    | Z1    | <b>Z</b> 2 | <b>Z</b> 3 |

|--------------------|-------|------------|------------|

| $L_1 \min (\mu H)$ | 185   | 212        | 224        |

| $L_1 \max (\mu H)$ | 217   | 223        | 227        |

| $L_2 \min (\mu H)$ | 214   | 207        | 198        |

| $L_2 \max (\mu H)$ | 232   | 214        | 203        |

| $k \min$           | 0.1   | 0.085      | 0.084      |

| k max              | 0.249 | 0.221      | 0.243      |

| $M \min (\mu H)$   | 19.89 | 17.80      | 17.69      |

| $M \max (\mu H)$   | 55.87 | 48.28      | 52.16      |

Table 2.2: Summary of the reference parameters from SAE J2954 for WPT1 power level.

• The back-end FSBB converter, which can provide both voltage step-up and step-down functions, enables wide-range operation for wireless charging purpose.

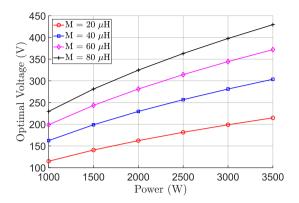

Further discussions on the third point are given, which explains why the FSBB converter has advantages in LCC-S based WPT system. The SAE J2954 [31], which is a standard for wireless power transfer for electric vehicles led by SAE International, covers the reference design up to 11.1 kVA input power as of 2020. Therein, three power level classes are defined: WPT1 for 3.7 kVA system, WPT2 for 7.7 kVA, and WPT3 for 11.1 kVA. Three different vertical distance classes (Z-classes) between the ground assembly (GA) and the vehicle assembly (VA) are given:  $\bf Z1=100-150$  mm,  $\bf Z2=140-170$  mm and  $\bf Z3=170-250$  mm. The ground clearance and the offset position of the coils will influence the coil coupling coefficients. The normative design specifications are given for three different Z-classes and are summarized in Table 2.2 [32]. Therein:  $L_1$  and  $L_2$  are the primary and secondary side coil self-inductance respectively; k is the magnetic coupling coefficient and M is the derived mutual inductance. As it can be seen, the mutual inductance can differ by as much as three times, and for a fully compensated LCC-S based WPT system, the output voltage can be expressed by (2.1)

$$V_{\rm mid} = \frac{M}{L_f} V_{\rm in},\tag{2.1}$$

where  $L_f$  is the inductance of the input resonant inductor. Therefore, for 400 V class battery, if a buck converter is used considering efficiency performance instead of a boost converter, then the voltage of  $V_{\rm mid}$  will vary between approximately 500–1500 V to guarantee that it is always larger than 400 V. Here, 500 V corresponds to the situation with a minimum value of mutual inductance, and it is assumed that  $L_f$  and  $V_{\rm in}$  remain unchanged. This means only switches with a withstand voltage of 1700 V or higher can be chosen, and currently, the selection of such switches on the market is limited. However, if an FSBB converter is used, the voltage of  $V_{\rm mid}$  can be selected, for example, between 200–600 V, and then, there will be more switches on the market that meet the voltage withstand requirements. On top of that, the printed circuit board (PCB) layout design of the power stage will also become easier with a lower bus voltage.

In addition to the above mentioned points, one can also consider the choice of  $V_{\rm mid}$  from the perspective of reducing coil losses, namely, to improve the efficiency of the WPT resonant stage. When the H-bridge inverter operates at resonant frequency with a square-wave output voltage, for a fully compensated LCC-S compensation, as will be described

Figure 2.23: Optimal voltage of  $V_{\rm mid}$  in terms of different power and mutual inductance values, assuming  $R_{\rm ac1}=R_{\rm ac2}$ .

in Chapter 6, the root mean square (rms) value of the primary coil current based on first harmonic approximation (FHA) method is

$$I_{1} = \frac{2\sqrt{2}V_{\text{in}}}{\pi\omega_{0}L_{f}} = \frac{2\sqrt{2}V_{\text{mid}}}{\pi\omega_{0}M},$$

(2.2)

where  $\omega_0$  is the resonant angular frequency. Assuming the processed power is  $P_0$ , then the rms value of the secondary coil current is

$$I_2 = \frac{\pi}{2\sqrt{2}} \cdot \frac{P_o}{V_{\text{mid}}}.$$

(2.3)

So, the total conduction losses are

$$P_{\text{cond}} = I_1^2 R_{\text{ac1}} + I_2^2 R_{\text{ac2}} = \frac{8}{\pi^2 \omega_0^2 M^2} \cdot V_{\text{mid}}^2 \cdot R_{\text{ac1}} + \frac{\pi^2}{8} \cdot \frac{P_o^2}{V_{\text{mid}}^2} \cdot R_{\text{ac2}}, \tag{2.4}$$

where  $R_{\rm ac1}$  and  $R_{\rm ac2}$  are the equivalent resistances of the two coils. From (2.4), one can derive the voltage value of  $V_{\rm mid}$  that minimizes the conduction losses, which is

$$V_{\text{mid}} = \frac{\pi}{2} \cdot \sqrt{\frac{\omega_0 M P_o}{2} \cdot \sqrt{\frac{R_{\text{ac2}}}{R_{\text{ac1}}}}}.$$

(2.5)

It can be seen from (2.5), the optimal voltage does not depend on the input voltage, but it depends on the power value. For example, Figure 2.23 shows this optimal voltage value with different mutual inductance and power as a reference. Although a strict and comprehensive analysis would require considering losses caused by other factors, the above quick and rough analysis still provides a reasonable range for selecting the voltage of  $V_{\rm mid}$  based on the coil recommendation from SAE J2954.

In summary, to achieve a safe and reliable WPT charging system that operates efficiently across a wide range of conditions with moderately complex control schemes, this thesis focuses on researching an LCC-S based WPT system combined with a back-end FSBB converter as the preferred topology.

3

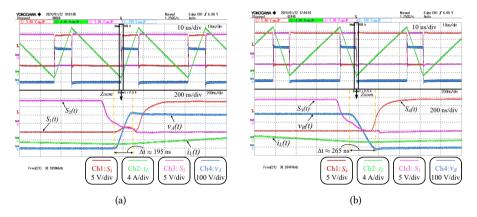

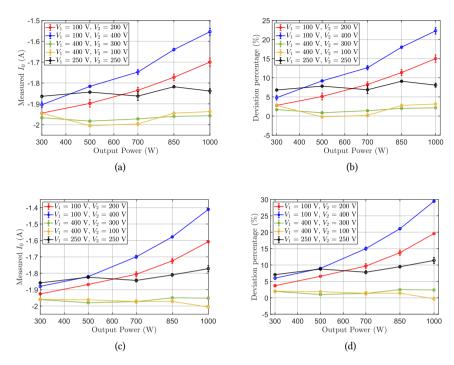

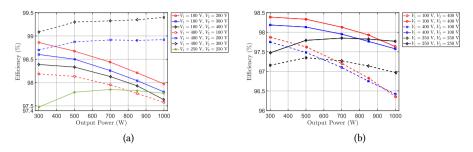

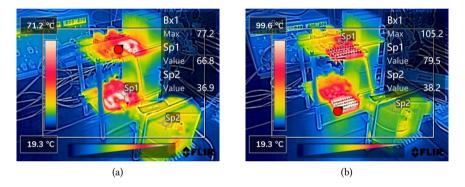

# THREE-MODE VARIABLE-FREQUENCY ZVS MODULATION FOR FSBB CONVERTER