#### Reducing Switching Artifacts in Chopper Amplifiers

Kusuda, Yoshinori

10.4233/uuid:62585ae8-da35-459e-bf90-f53f7d0de32c

**Publication date**

**Document Version** Final published version

Citation (APA)

Kusuda, Y. (2018). *Reducing Switching Artifacts in Chopper Amplifiers*. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:62585ae8-da35-459e-bf90-f53f7d0de32c

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Reducing Switching Artifacts in Chopper Amplifiers

Yoshinori Kusuda

## Reducing Switching Artifacts in Chopper Amplifiers

#### **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. dr.ir. T.H.J.J. van der Hagen; voorzitter van het College voor Promoties, in het openbaar te verdedigen op maandag 30 april 2018 om 15:00 uur

door

Yoshinori KUSUDA Elektrotechnisch ingenieur, Master of Science van Tokyo Instituut van Technologie, Japan geboren te Kobe, Japan Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. ir. K.A.A. Makinwa

#### Samenstelling promotiecommissie:

Rector Magnicus, voorzitter

Prof. dr. ir. K.A.A. Makinwa, Technische Universiteit Delft, promotor

#### Onafhankelijke leden:

Dr. Q. Fan Technische Universiteit Delft

Prof. dr. ir. E. Cantatore Technische Universiteit Eindhoven

Prof. dr. W.M.C. Sansen em.hgl Katholieke Universiteit Leuven

Prof. dr. ir. A.J.P. Theuwissen Technische Universiteit Delft Prof. dr. ir. W.A. Serdijn Technische Universiteit Delft

Prof. dr. ir. J.H. Huijsing em.hgl Technische Universiteit Delft

Printed by Ipskamp Printing, Enschede, the Netherlands

ISBN: 978-94-028-0997-8

Copyright © 2018 by Yoshinori Kusuda

All rights reserved. No part of this publication may be reproduced or distributed in any form of by any means, or stored in a database or retrieval system, without any prior permission of the copyright owner.

## **Contents**

| Chapter | 1 Introduction                                | 1  |

|---------|-----------------------------------------------|----|

| 1.1     | Precision Data Acquisition Signal Chain       | 2  |

| 1.2     | CMOS Operational Amplifiers                   | 3  |

| 1.2.    | Functionality                                 | 3  |

| 1.2.2   | 2 Offset and Noise                            | 5  |

| 1.2.    | 3 Summary                                     | 6  |

| 1.3     | Chopping Principle                            | 7  |

| 1.4     | Traditional Applications of Chopper Op-Amps   | 8  |

| 1.4.    | Sensor Signal Conditioning                    | 8  |

| 1.4.2   | 2 Current Sensing                             | 10 |

| 1.4.    | 3 Summary                                     | 11 |

| 1.5     | Newer Applications of Chopper Op-Amps         | 12 |

| 1.5.    | Biomedical Sensing Front-End                  | 12 |

| 1.5.2   | 2 Reference and DAC Buffers                   | 13 |

| 1.5.    | Process Control Data Acquisition Signal Chain | 14 |

| 1.6     | Challenges                                    | 15 |

| 1.7     | Organization of the Thesis                    | 15 |

| 1.8     | References                                    | 17 |

| Chapter | 2 Offset Cancellation Techniques              | 21 |

| 2.1     | Offset Trimming                               | 22 |

|         | MOS Switches                                  |    |

| 2.2.    | Realization and On-Resistance                 | 23 |

| 2.2.2   | 2 Charge Injection                            | 24 |

| 2.2.    | 3 Cancellation of Charge Injection            | 25 |

| 2.3     | Auto-Zeroing                                  | 27 |

| 2.3.    | Principle                                     | 27 |

| 2.3.2   | 2 Residual Offset                             | 27 |

| 2.3.    | Broadband Noise Folding                       | 28 |

| 2.3.4   |                                               |    |

| 2.4     | Chopping                                      | 31 |

| 2.4.1     | Up-Modulated Ripple                             | 31 |

|-----------|-------------------------------------------------|----|

| 2.4.2     | Glitches                                        | 33 |

| 2.4.3     | Input Bias Current and Residual Offset          | 34 |

| 2.4.4     | Dynamic Switching Conductance                   | 38 |

| 2.4.5     | Summary of the Errors                           | 39 |

| 2.5 Co    | mparison of the Techniques                      | 42 |

| 2.6 Re    | ferences                                        | 43 |

| Chapter 3 | Methods of Reducing Chopper Switching Artifacts | 47 |

| 3.1 Re    | sidual Offset Reduction Techniques              | 48 |

| 3.1.1     | Filtering the Glitches                          | 48 |

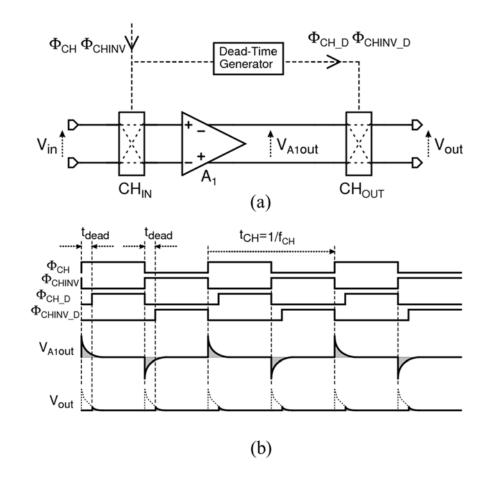

| 3.1.2     | Dead-Timed Down-Modulation                      | 50 |

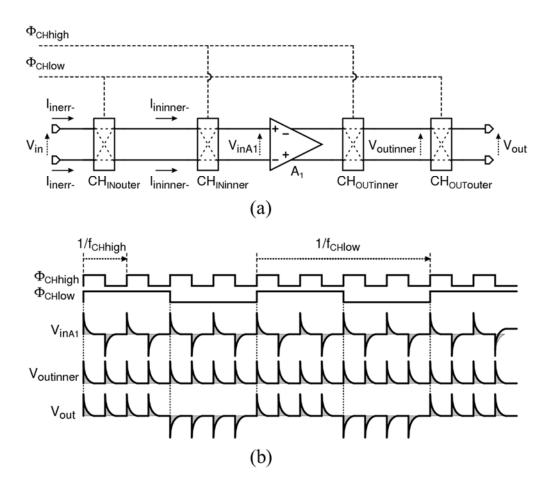

| 3.1.3     | Nested Chopping                                 | 50 |

| 3.2 Rij   | pple Reduction Techniques                       | 52 |

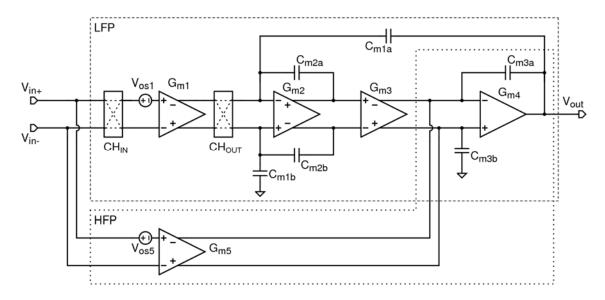

| 3.2.1     | Multi-Path Chopper Offset Stabilization         | 52 |

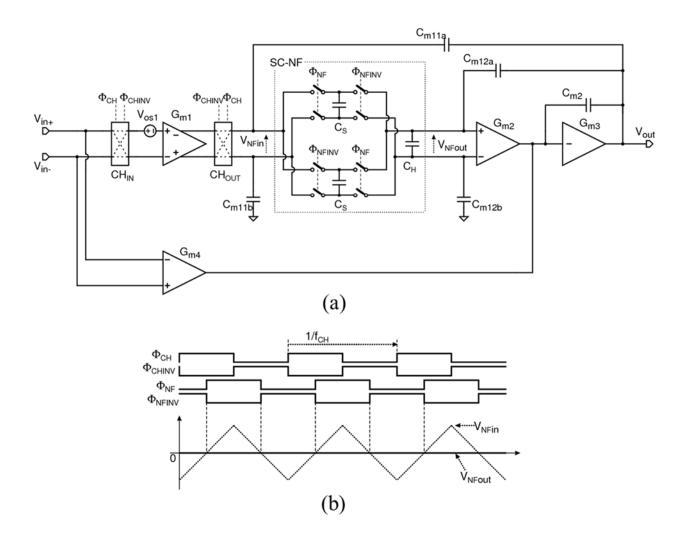

| 3.2.2     | Switched Capacitor Notch Filter                 | 54 |

| 3.2.3     | High-Pass Filtering                             | 56 |

| 3.2.4     | Initial Offset Trimming                         | 58 |

| 3.2.5     | Combination with Auto-Zeroing                   | 58 |

| 3.2.6     | AC-Coupled Ripple Reduction Loop                | 62 |

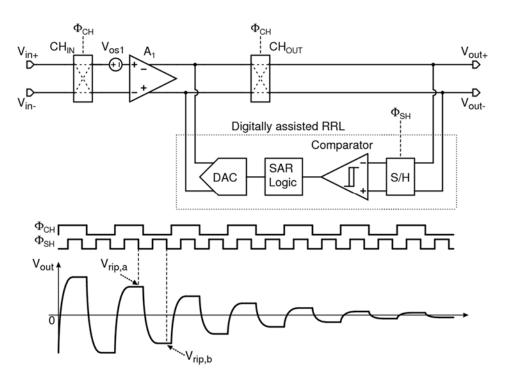

| 3.2.7     | Digitally Assisted Ripple Reduction Loop        | 64 |

| 3.3 Co    | mparison of the Techniques                      | 66 |

| 3.4 Re    | ferences                                        | 69 |

| Chapter 4 | Chopper Op-Amp with Auto-Correction Feedback    | 71 |

| 4.1 Mo    | otivation                                       | 72 |

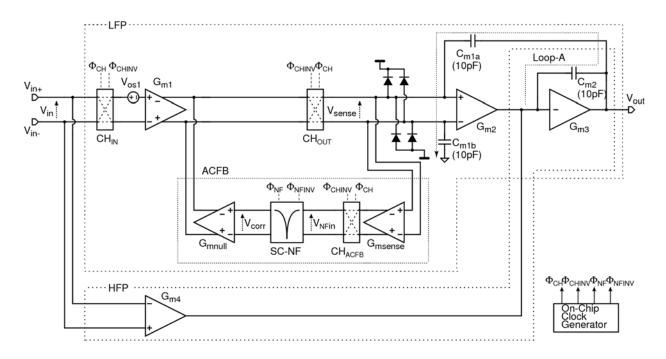

| 4.2 Op    | o-Amp and Ripple Reduction Architecture         | 73 |

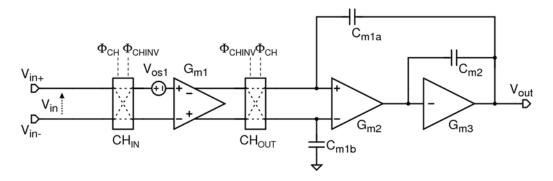

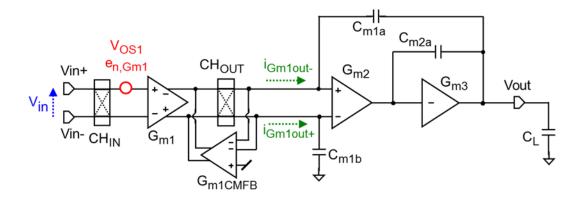

| 4.2.1     | Basic Three Stage Chopper Op-Amp                | 73 |

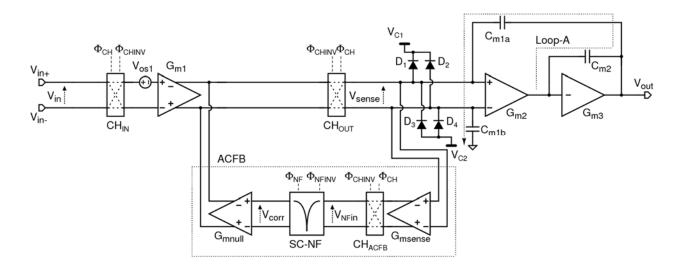

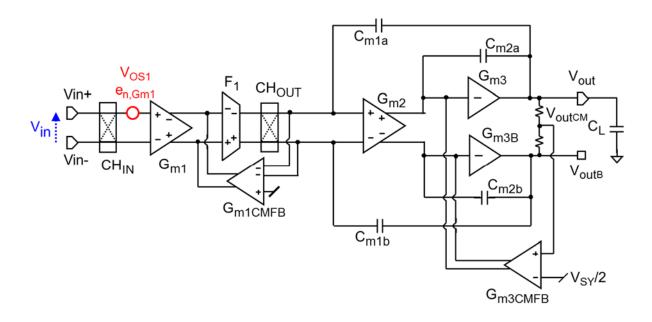

| 4.2.2     | Auto-Correction Feedback                        | 74 |

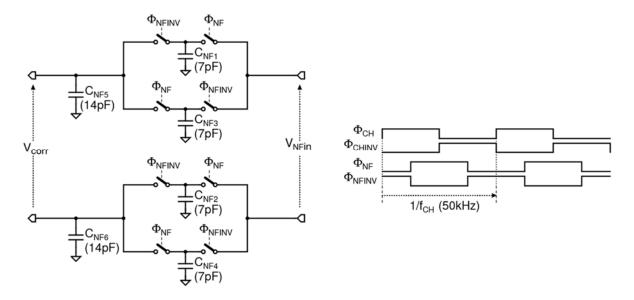

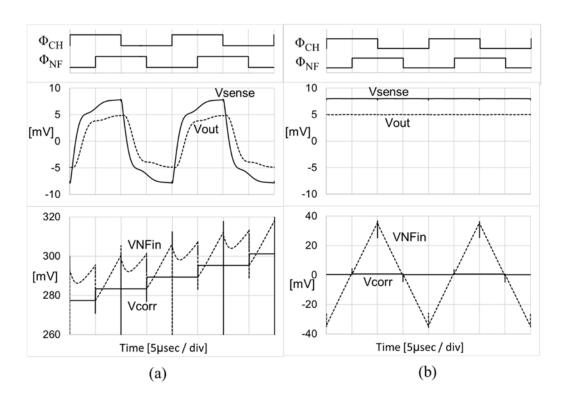

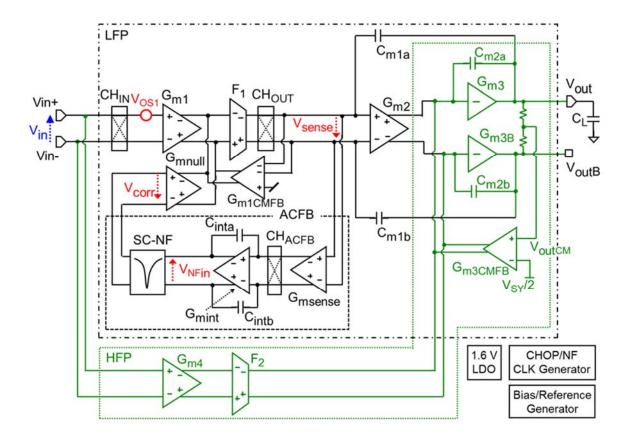

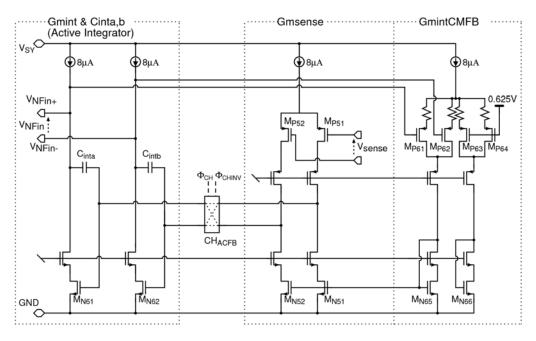

| 4.2.3     | Switched Capacitor Notch Filter (SC-NF)         | 75 |

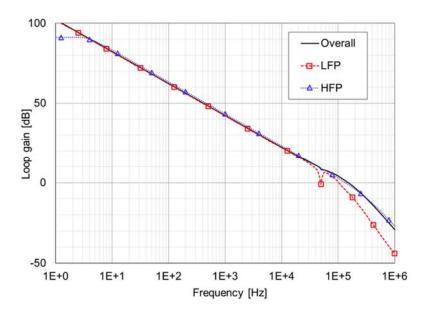

| 4.2.4     | High Frequency Path (HFP) and Overall Op-Amp    | 77 |

| 4.3 Re    | sidual Error Analysis                           | 79 |

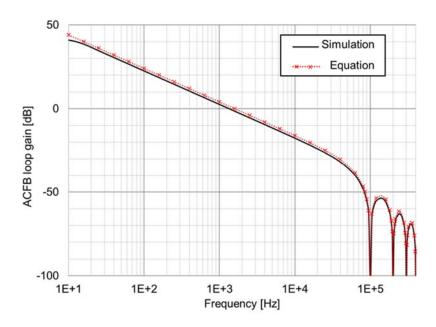

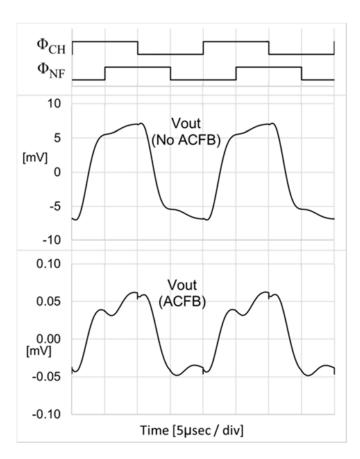

| 4.3.1     | ACFB Loop Gain                                  |    |

| 4.3.2     | Residual Ripple                                 | 82 |

| 4.3.3     | Residual Offset                                 |    |

| 4.3.4     | Summary                                         | 83 |

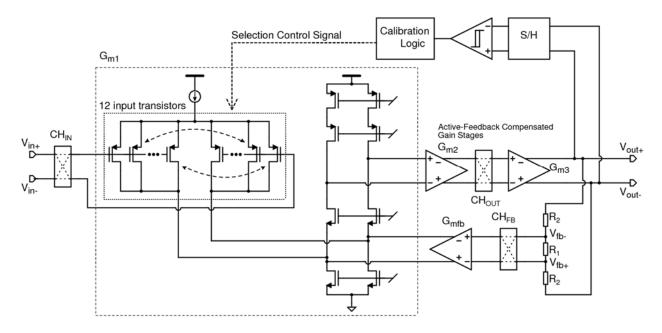

| 4.4 Ci    | rcuit Implementation                            | 86 |

|           |                                                 |    |

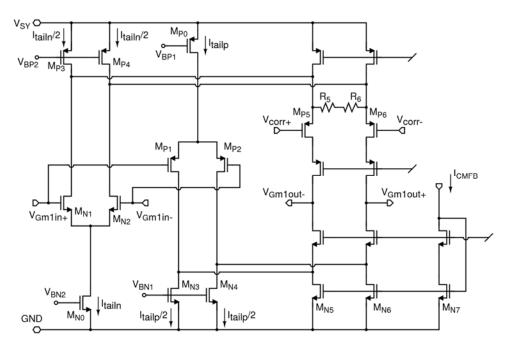

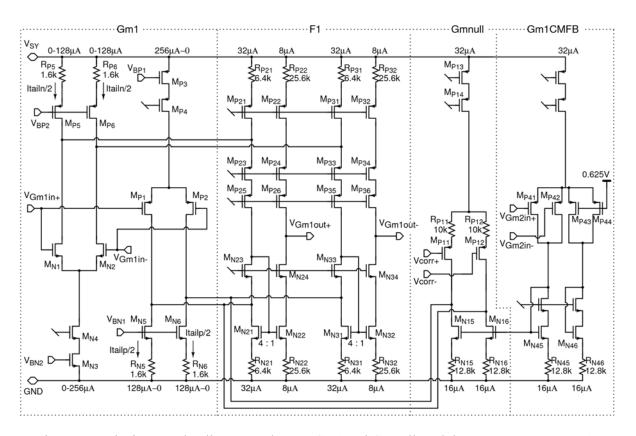

| 4.4    | 4.1  | Input and Nulling Transconductors                                        | 86    |

|--------|------|--------------------------------------------------------------------------|-------|

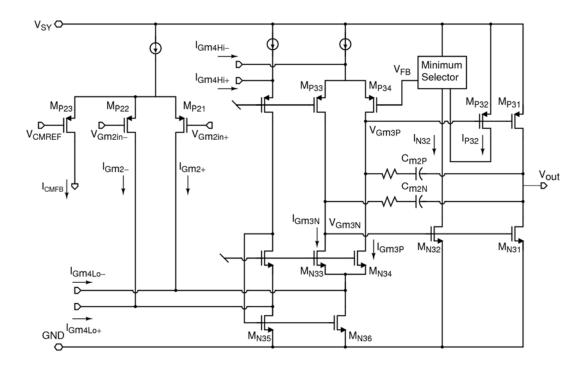

| 4.4    | 1.2  | Second, Output, and Feedforward Transconductors                          | 87    |

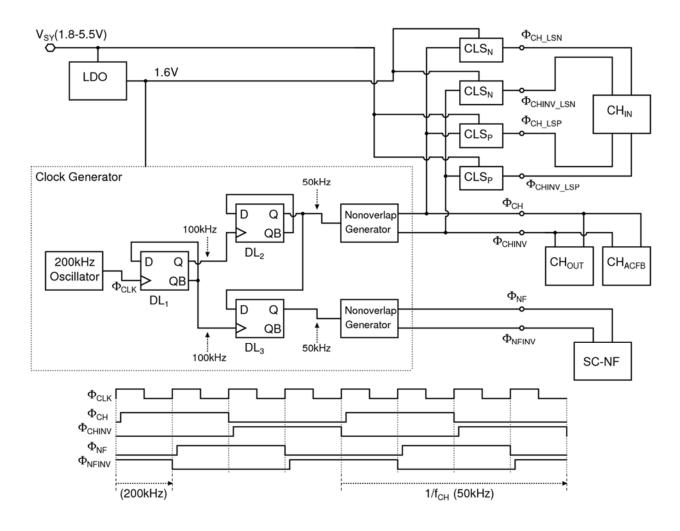

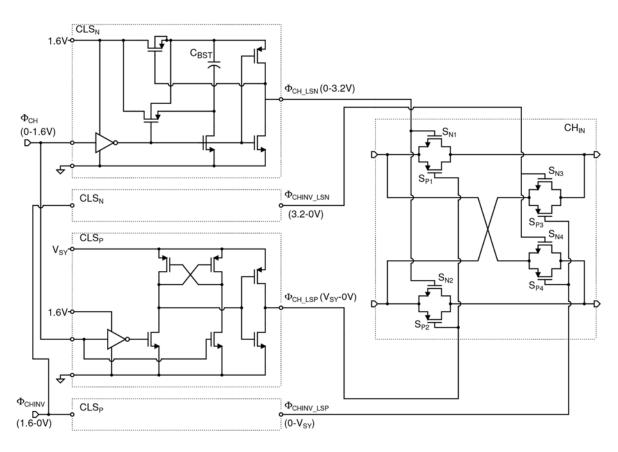

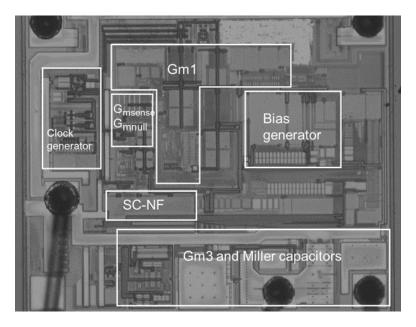

| 4.4    | 1.3  | Clock Generator                                                          | 88    |

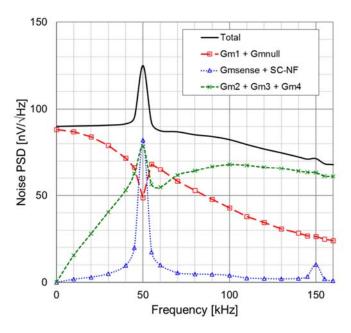

| 4.4    | 1.4  | Noise Analysis                                                           | 91    |

| 4.5    | Me   | asurement Results                                                        | 92    |

| 4.6    | Cor  | nclusions                                                                | 98    |

| 4.7    | Ref  | erences                                                                  | 100   |

| Chapte | er 5 | Chopper Op-Amp with Adaptive Clock Boosting Technique                    | 103   |

| 5.1    | Mo   | tivation                                                                 | 104   |

| 5.2    | Op-  | Amp Architecture                                                         | 105   |

| 5.2    | 2.1  | Conventional Three Stage Chopper Op-Amp and Frequency Compensation.      | 105   |

| 5.2    | 2.2  | Frequency Compensation Using a Current Attenuator and a Dummy Difference | ntial |

|        |      | Output                                                                   | 107   |

| 5.2    | 2.3  | Overall Op-Amp Employing Auto-Correction Feedback                        | 109   |

| 5.2    | 2.4  | ACFB Loop Gain Including Active Integrator                               | 110   |

| 5.2    | 2.5  | High Frequency Path (HFP)                                                | 112   |

| 5.3    | Tra  | nsconductor Circuits                                                     | 113   |

| 5.3    | 3.1  | Input and Nulling Transconductors with the Current Attenuator            | 113   |

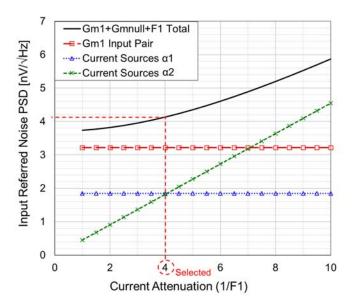

| 5.3    | 3.2  | Noise Analysis and Optimization                                          | 114   |

| 5.3    | 3.3  | Residual Offset and CMRR Analysis                                        | 116   |

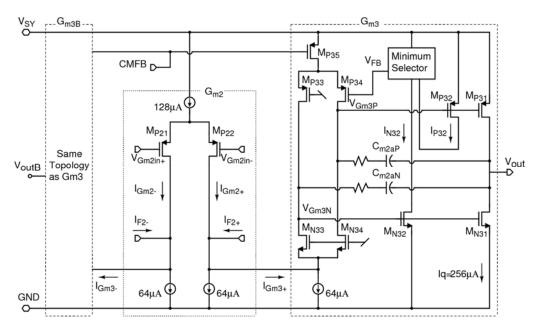

| 5.3    | 3.4  | Second and Output Transconductors                                        | 117   |

| 5.4    | Inp  | ut Chopper                                                               | 118   |

| 5.4    | 4.1  | Conventional CMOS Switches                                               | 118   |

| 5.4    | 1.2  | Input Chopper Employing Adaptive Clock Boosting Technique                |       |

| 5.4    | 1.3  | Adaptive Clock Booster Circuit                                           | 121   |

| 5.4    | 1.4  | Common-Mode Buffer                                                       | 123   |

| 5.5    | Me   | asurement Results                                                        | 124   |

| 5.6    | Cor  | nclusion                                                                 | 130   |

| 5.7    | Ref  | erences                                                                  | 132   |

| Chapte | er 6 | Auto-Zero and Chopper Op-Amp with Clock Interleaving and Input l         | Bias  |

|        |      | Current Trimming Techniques                                              | 135   |

| 6.1    | Mo   | tivation                                                                 | 136   |

| 6.2    | Inp  | ut Transconductor Architecture                                           | 137   |

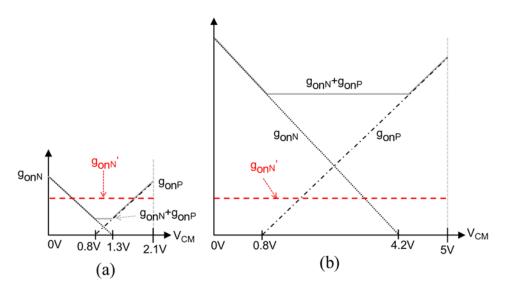

| 6.2    | 2.1  | Previous High Voltage Input Transconductors                              | 138   |

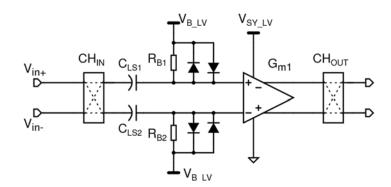

| 6.2    | 2.2  | Capacitively-Coupled Auto-Zero and Chopper Input Transconductor          | 139   |

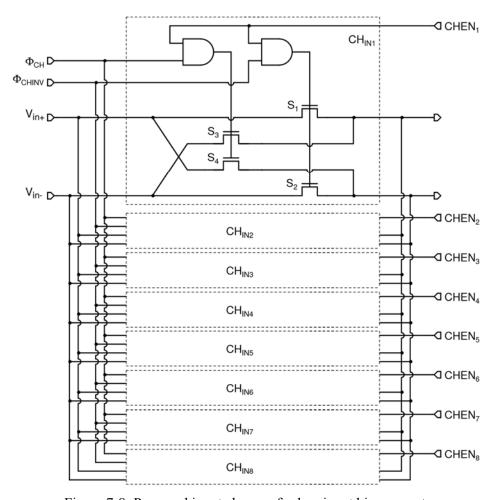

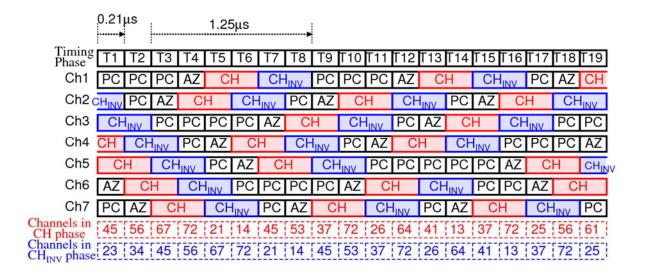

| 6.2       | .3 Six Input Channels and Clock Interleaving                                  | 140 |

|-----------|-------------------------------------------------------------------------------|-----|

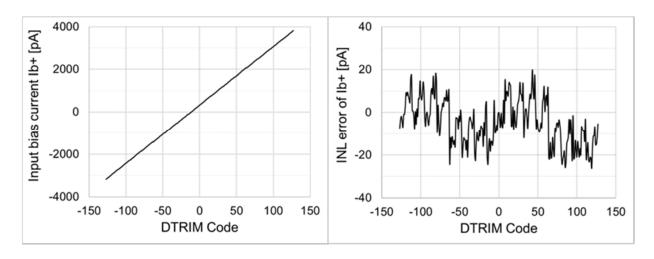

| 6.3       | Input Bias Current Trimming                                                   | 145 |

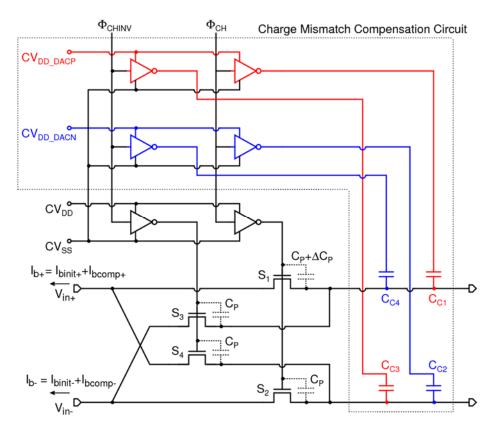

| 6.3       | .1 Input Switching Circuit Employing a Charge Mismatch Compensation Circuit . | 146 |

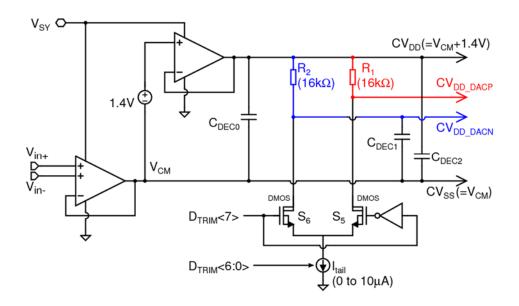

| 6.3       | .2 Common-Mode Tracking Regulator                                             | 147 |

| 6.4       | Overall Op-Amp Implementation                                                 | 149 |

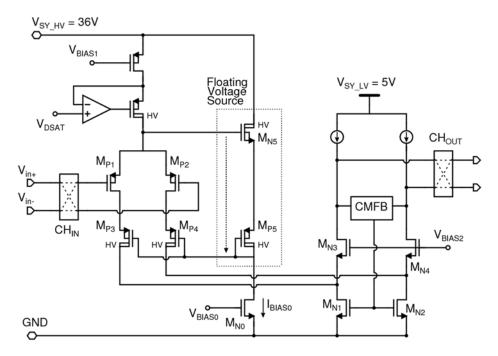

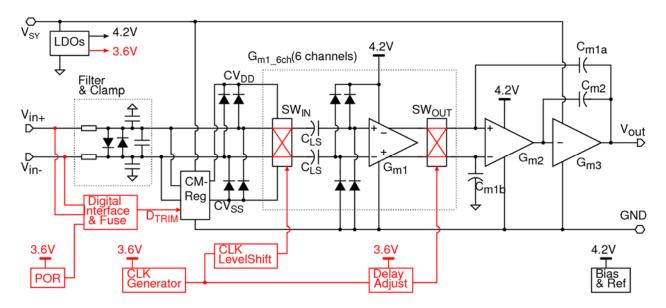

| 6.4       | .1 Overall Op-Amp Architecture                                                | 149 |

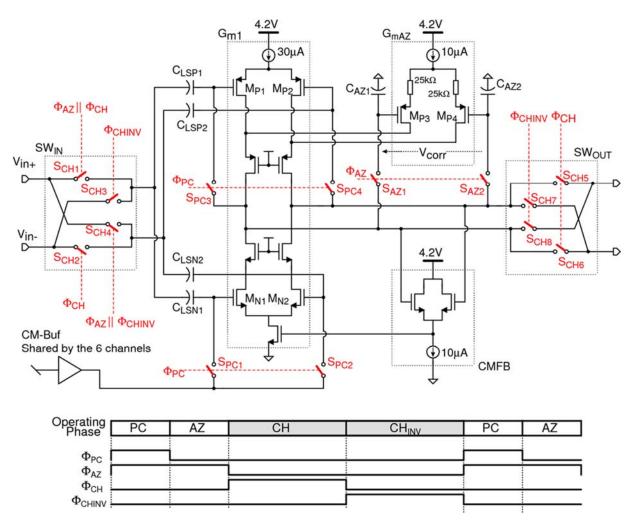

| 6.4       | .2 One Channel Input Transconductor                                           | 151 |

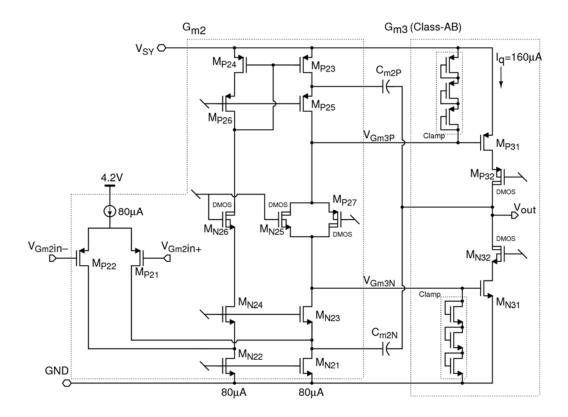

| 6.4       | .3 Second and Output Transconductors                                          | 153 |

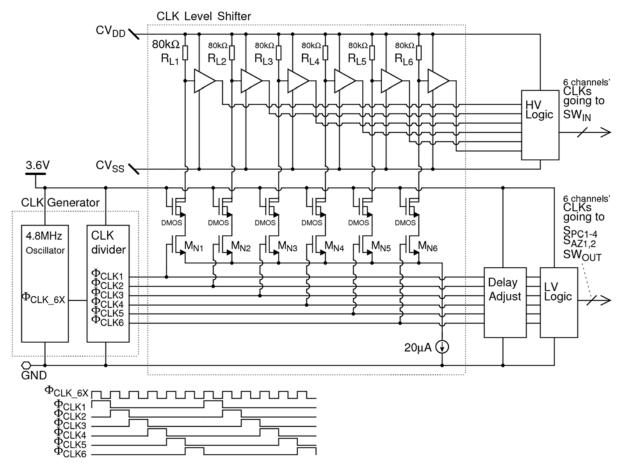

| 6.4       | .4 Clock Generator and Level Shifter                                          | 155 |

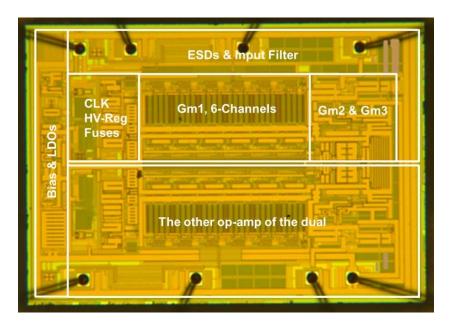

| 6.5       | Measurement Results                                                           | 156 |

| 6.6       | Conclusion                                                                    | 163 |

| 6.7       | References                                                                    | 164 |

| Chapte    | r 7 Conclusion                                                                | 167 |

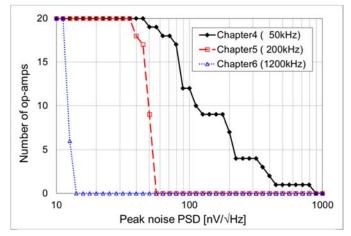

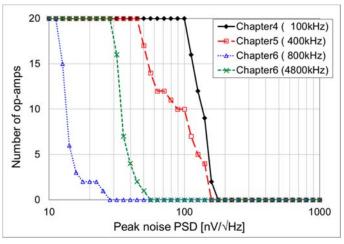

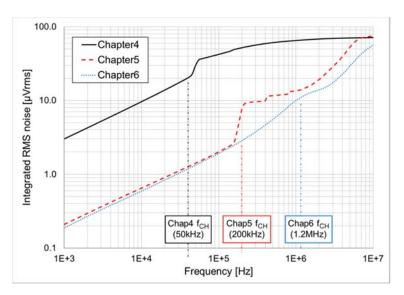

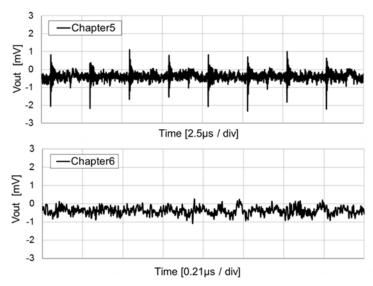

| 7.1       | Evolution over the Three Projects                                             | 168 |

| 7.2       | Benchmark                                                                     | 174 |

| 7.3       | Future Work                                                                   | 176 |

| 7.4       | Original Contributions                                                        | 178 |

| 7.5       | References                                                                    | 179 |

| Summa     | ry                                                                            | 181 |

| Samenv    | vatting                                                                       | 187 |

| List of p | publications                                                                  | 193 |

| About t   | he author                                                                     | 195 |

| Acknow    | vledgements                                                                   | 197 |

## Chapter 1

#### Introduction

This thesis describes the theory, design, and implementation of chopper amplifiers in CMOS integrated circuits (ICs). As the name implies, such amplifiers employ chopping to achieve low offset and low 1/f noise. Chopping is a circuit technique that involves up-modulating amplifier offset and low frequency noise to higher frequencies, and which therefore can achieve microvolt-level offset with very low temperature drift. On the other hand, it causes switching artifacts such as AC ripple and glitches at the amplifier's output, which usually need to be attenuated by low-pass filtering, thus decreasing the usable signal bandwidth. As a result, the use of chopper amplifiers has mainly been limited to low frequency applications. This thesis explores advanced circuit techniques to reduce such switching artifacts without decreasing the usable signal bandwidth, thus enabling the use of chopper amplifiers in a broader range of applications.

This chapter introduces the main objectives of this work. After a review of the key requirements of amplifiers in signal chains, the offset and low frequency noise behavior of a basic CMOS amplifier are described. Next, the chopping technique is presented, followed by a description of its traditional use in low frequency applications. Some newer applications are then described, which also require low offset and 1/f noise, but in which signal frequencies are too high for switching artifacts to be reduced by low-pass filtering. Lastly, the challenges associated with reducing switching artifacts in such applications are discussed.

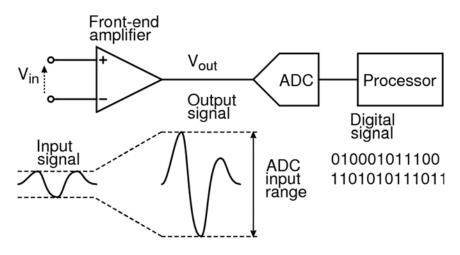

Figure 1-1: Precision data acquisition signal chain

#### 1.1 Precision Data Acquisition Signal Chain

In today's digital signal processing era, analog signals from the real world are ubiquitously acquired and converted into digital signals for use in factories, test equipment, and healthcare systems. The new Internet of Things (IoT) era will lead to the acquisition of even more analog signals in vehicles, buildings, and even homes [1,2]. As a result, manufacturers will need to develop a wide variety of data acquisition signal chains in less time and at lower cost. Those with a resolution of 16 bits or higher are classified as precision data acquisition signal chains typically intended for physical signals, such as light, sound, temperature, pressure, magnetic field, and force. Such signals have relatively low frequency spectra ranging from DC to a few kilohertz or at most up to a few hundred kilohertz.

Figure 1-1 shows an example of a precision data acquisition signal chain consisting of a front-end amplifier, an analog-to-digital converter (ADC), and a digital processor [3]. The amplitude of the input signal  $V_{in}$  is often smaller than the full scale input range of the ADC. Therefore, the front-end amplifier must amplify  $V_{in}$  and produce an output  $V_{out}$  with an amplitude large enough to utilize the full range of the ADC. The amplifier's input errors may dominate the overall system performance, since they are added before the signals are amplified. For instance, when the front-end amplifier is configured for a gain of 100 and its output is applied to a 16-bit

ADC with a 5V full scale input, an input error of only  $0.76\mu V$  corresponds to one LSB error in the resulting digital output. The offset and noise of the front-end amplifier must therefore be lower than this in order to maintain true 16-bit performance.

Other common requirements of a front-end amplifier are a wide input range and high common-mode rejection ratio (CMRR). This is because in certain applications, the input signals may be associated with common-mode noise and disturbances. Some applications, e.g. bridge readout, require the amplification of millivolt-level differential signals, while rejecting a few volts of common-mode noise. Additionally, the amplifier's input bias current should be low enough for applications where the input signal sources have high impedances. On top of all these requirements, cost and power efficiency are also important nowadays, especially since ADCs and digital processors have become cheaper and more power efficient thanks to the steady scaling of CMOS technology. In summary, front-end amplifiers are key elements of precision data acquisition signal chains, and can dominate their overall performance and cost.

#### 1.2 CMOS Operational Amplifiers

#### 1.2.1 Functionality

A front-end amplifier can be integrated on a single chip with an ADC, or can be realized off-chip with the help of a monolithic instrumentation amplifier (IA) or an operational amplifier (opamp). While the first two options often result in a more compact subsystem and/or optimized performance, monolithic op-amp based implementations offer design flexibility. By modifying their feedback networks, such op-amps can realize different closed-loop transfer functions and accept various types of input signals, such as single-ended or differential, voltages or currents etc. [4]. This thesis presents original op-amp designs implemented as monolithic ICs. However, most of the theory and techniques presented are also applicable to IAs and other integrated amplifiers.

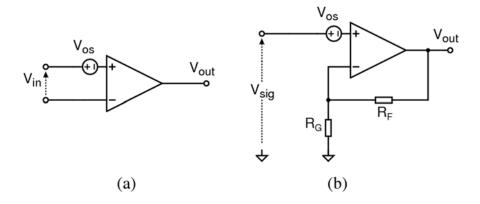

Figure 1-2: (a) Symbol of an op-amp; (b) closed-loop amplifier using an op-amp

Figure 1-2 (a) shows the symbol of an op-amp that amplifies a small differential input voltage  $V_{in}$  with a high open-loop gain  $A_{OL}$  [5-7]. This produces an output voltage  $V_{out}$  equal to:

$$V_{out} = A_{OL}(V_{in} - V_{os}),$$

(1-1)

where  $V_{os}$  is the input offset voltage. In fact, as shown in Figure 1-2 (b), an op-amp is usually configured as a closed-loop amplifier with an input signal  $V_{sig}$ . The output voltage  $V_{out}$  and closed-loop gain  $A_{CL}$  are determined by external gain-setting resistors  $R_G$  and  $R_F$ , and is given by:

$$V_{out} \equiv A_{CL} \left( V_{sig} - V_{os} \right)$$

(1-2)

$$A_{CL} = \frac{1}{1+\varepsilon} \left( 1 + \frac{R_F}{R_G} \right)$$

(1-3)

$$\varepsilon = \frac{1}{A_{OL}} \left( 1 + \frac{R_F}{R_G} \right),$$

(1-4)

where  $\varepsilon$  is a gain error due to an insufficient amount of  $A_{OL}$ . Additionally,  $V_{os}$  is superimposed onto  $V_{sig}$  and thus also degrades the precision. Therefore, op-amps should provide a sufficiently high open-loop gain and low offset to minimize the overall error. Those providing more than  $100 \text{dB} \ A_{OL}$  and less than  $100 \mu \text{V} \ V_{os}$  are classified as precision op-amps [8].

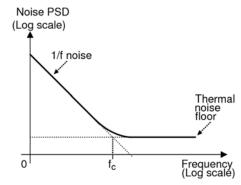

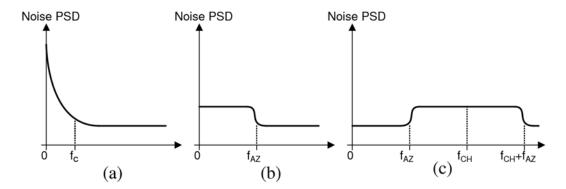

Figure 1-3: Noise PSD of a typical CMOS op-amp

#### 1.2.2 Offset and Noise

Offset is a deterministic DC error and is usually the result of the systematic and random device mismatch that occurs during IC fabrication. The amount of device mismatch depends on device size and process technology. Since individual op-amps will then have unique offsets, only the standard deviation and maximum value of this offset can be specified for a given design. Typical CMOS op-amps have maximum offsets in the order of a few millivolts to tens of millivolts [9]. Offset can change with temperature and the input common-mode voltage; these changes are expressed by offset drift and CMRR specifications.

Noise, on the other hand, is completely due to random processes. It can be modeled as a zero-mean random error signal that is superimposed on an input signal. Figure 1-3 shows the noise power spectral density (PSD) of a typical CMOS op-amp. At higher frequencies it is flat and dominated by thermal noise. This can be reduced by increasing the amplifier's input transconductance at the cost of current consumption. To evaluate the power efficiency of an amplifier, the noise efficiency factor (NEF) is defined as:

$$NEF = v_{n,rms} \sqrt{\frac{I_{tot}}{4kTV_{t}} \cdot \frac{1}{BW \cdot \pi / 2}}, \quad (1-5)$$

where  $v_{n,rms}$  is the total integrated RMS noise over frequency,  $I_{tot}$  is the current consumption,  $V_t$  is the thermal voltage equal to kT/q, and  $BW \bullet \pi/2$  is the noise bandwidth of the amplifier [10]. When  $v_{n,rms}$  is dominated by thermal noise, and is band-limited by a first order low-pass filtering, this equation can be simplified to:

$$NEF = e_n \sqrt{\frac{I_{tot}}{4kTV_t}}, \qquad (1-6)$$

where  $e_n$  is the input noise PSD. A differential pair realized by two bipolar transistors with no 1/f noise has an NEF of unity. On the other hand, a CMOS op-amp usually has a higher NEF due to various factors: the presence of more than one dominant noise source in its input stage; the current consumption of the subsequent gain stages; and the fact that for the same current the thermal noise of a MOS transistor is higher than that of a bipolar transistor. At lower frequencies, the noise PSD is dominated by 1/f noise, which increases as the frequency decreases [5]. The amount of 1/f noise and hence the corner frequency  $f_c$  depend on the device size and the process technology. Typical CMOS op-amps have corner frequencies in the range of a few kilohertz to tens of kilohertz.

#### *1.2.3 Summary*

CMOS op-amps suffer from considerable offset and 1/f noise which dominates their overall error in low frequency applications. Although such errors can be reduced by increasing device sizes, this will increase chip area and hence production cost. Offset can also be reduced by post-production trimming. However, this will usually not compensate well for offset drift over temperature. For these reasons, most precision op-amps have been realized in bipolar processes which offer lower offset and 1/f noise than CMOS processes. On the other hand, CMOS op-amps have a number of advantages, and thus are gaining popularity. First, most precision ADCs and digital processors are realized in CMOS processes, and so can be co-integrated with CMOS op-amps. Second, CMOS wafers are cheaper than bipolar or JFET ones. Third, digital logic and analog switches can be easily implemented in CMOS processes, enabling the use of various dynamic error correction techniques. Specifically, dynamic offset cancellation techniques such as auto-zeroing and chopping, can reduce offset and offset drift to levels significantly lower than those of trimmed bipolar op-amps [11]. Thus, chopper and auto-zero op-amps in CMOS processes have successfully served applications requiring microvolt-level offset, very low temperature drift, and/or low 1/f noise [11].

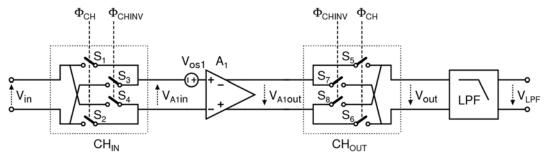

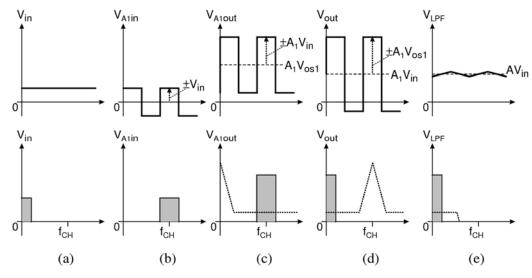

Figure 1-4: Functional diagram of chopping

Figure 1-5: Signal, offset, and noise in the time and frequency domains

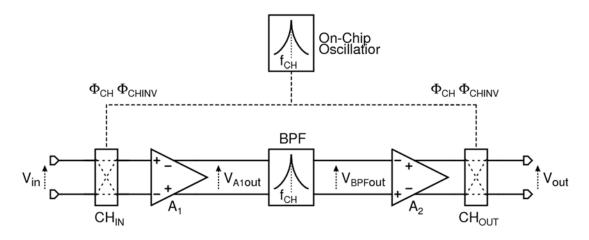

#### 1.3 Chopping Principle

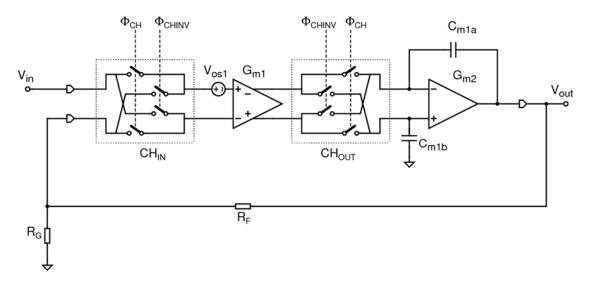

Chopping is a frequency modulation technique that is used to separate undesired offset and low frequency noise from low frequency signals [12]. Figure 1-4 shows a functional diagram of a chopper amplifier, consisting of an input chopper  $CH_{IN}$ , an amplifier  $A_I$ , an output chopper  $CH_{OUT}$ , and a low-pass filter (LPF). Additionally,  $A_I$  is associated with an undesired input offset  $V_{OSI}$ . The modulation is performed by  $CH_{IN}$  and  $CH_{OUT}$ , each of which consists of four switches  $S_{1-4}$  and  $S_{5-8}$ , respectively. These switches are driven by complementary clocks  $\Phi_{CH}$  and  $\Phi_{CHINV}$  operating at a chopping frequency  $f_{CH}$ .

Figure 1-5 shows the signal, offset, and noise in the time and frequency domains to

illustrate how they are modulated. A low frequency input signal  $V_{in}$ , shown in Figure 1-5 (a), is first up-modulated to  $f_{CH}$  by CH<sub>IN</sub> (Figure 1-5 (b)). Next,  $A_I$  amplifies the up-modulated signal along with the offset and noise (Figure 1-5 (c)). This up-modulated signal and the thermal noise around  $f_{CH}$  are then down-modulated back to baseband by CH<sub>OUT</sub>. Meanwhile, CH<sub>OUT</sub> up-modulates the offset and the low frequency noise to  $f_{CH}$ , and thus produces switching artifacts (Figure 1-5 (d)). The LPF attenuates the switching artifacts, so that in the low frequency signal only the thermal noise floor interferes (Figure 1-5 (e)). However, the cutoff frequency of the LPF needs to be set lower than  $f_{CH}$ , which limits the usable signal bandwidth.

#### 1.4 Traditional Applications of Chopper Op-Amps

As explained in the previous section, chopping up-modulates low frequency errors and produces switching artifacts. Thus, this technique has traditionally been used in low frequency applications, where offset and 1/f noise must be low, but in which high frequency noise can be attenuated by low-pass filters. This section reviews traditional applications of chopper op-amps along with the required performance.

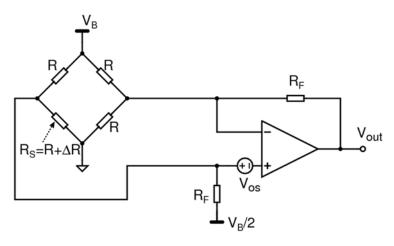

#### 1.4.1 Sensor Signal Conditioning

Sensors convert physical signals, such as light, sound, temperature, pressure, magnetic field, force, into electrical signals [13]. These electrical signals can be in the form of voltages, currents, resistances, or other quantities that are often quite small. Therefore, a front-end amplifier is required to produce a voltage output with an amplitude that is compatible with the full scale input of the ADC. Figure 1-6 shows a circuit diagram consisting of an op-amp and two gain setting resistors  $R_F$ , to amplify a bridge sensor signal [13]. The physical signal of interest is converted into a resistance change  $\Delta R$  in a resistive sensor  $R_S$ . Consequently, the front-end amplifier produces an output voltage  $V_{out}$  given by:

Figure 1-6: Bridge sensor and the front-end amplifier

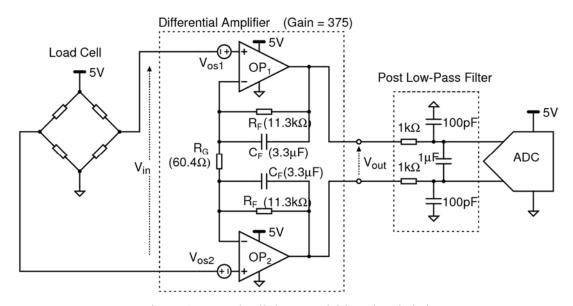

Figure 1-7: Load cell data acquisition signal chain

Table 1-1: System specification of Figure 1-7

|              | Op-amp error   |                 | ADC error  | Total error  |

|--------------|----------------|-----------------|------------|--------------|

|              | 1x op-amp      | 2x op-amp       |            |              |

|              | Input referred | Output referred |            |              |

| Offset       | 0.3 μV         | 159 μV          | 3 μV       | 273 LSB      |

| Offset drift | 2 nV/°C        | 1.0 μV/°C       | 0.01 μV/°C | 1.8 LSB/°C   |

| Noise PSD    | 5.6 nV/√Hz     | 3.0 μV/√Hz      | 1          | -            |

| Noise BW     | -              | 6.7 Hz          | -          | -            |

| RMS Noise    | -              | 8.1 μVrms       | 1.1 μVrms  | 13.6 LSB,rms |

$$V_{out} \approx \left(1 + \frac{R_F}{2R}\right) \cdot \left(\frac{\Delta R \cdot V_B}{2} + V_{os}\right) + \frac{V_B}{2},$$

(1-7)

where  $V_B$  is an excitation voltage for the bridge, and  $V_{os}$  is an input offset voltage of the op-amp. The input signal  $\Delta R \cdot V_B/2$  is often at the millivolt-level. Therefore, the op-amp must have a microvolt-level input offset, and provide a closed-loop gain  $(1+R_F/2R)$ , possibly of a few hundred or higher. Additionally, the offset must be stable with the changes in temperature or the input common-mode voltage that occur in many applications. Moreover, the 1/f noise should also be low, since signal frequencies are typically well below one kilohertz.

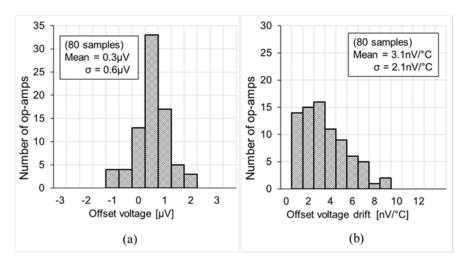

Figure 1-7 shows a specific example of a sensor data acquisition signal chain, consisting of a bridge load cell, a front-end differential amplifier, and a differential ADC [14]. The amplifier is configured for a gain of 375, with two op-amps  $OP_{1,2}$  and gain settling resistors  $R_G$  and  $R_F$ . Additionally,  $OP_{1,2}$  are chopper op-amps that have a  $0.3\mu V$  typical offset,  $2nV/^{\circ}C$  offset drift, and  $5.6nV/\sqrt{Hz}$  noise PSD [15]. The noise bandwidth is set to 6.7Hz with two feedback capacitors  $C_F$  and a low-pass filter. This filter attenuates the switching artifacts of the chopping at 200kHz by a factor of 90dB. The ADC has a 24-bit resolution with a 10V differential full scale input and a  $0.6\mu V$  LSB [16]. Table 1-1 lists the error contributions of the op-amps and the ADC, as well as the resulting total error. It can be seen that due to their high gain, the op-amps dominate the total error.

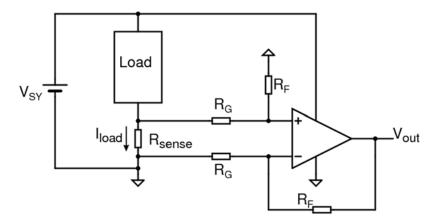

#### 1.4.2 Current Sensing

Another application example is in supply current sensing, the block diagram of which is shown in Figure 1-8 [17]. The goal is to monitor a load current  $I_{load}$  drawn from a DC power supply Vsy. A difference amplifier is realized by an op-amp and four resistors to amplify the voltage drop across a sense resistor  $R_{sense}$ . A relatively low voltage drop is preferred, in order not to affect the load. Therefore, the op-amp should have a low input offset to sense this low voltage drop. In this example,  $R_{sense}$  is placed between the load and the ground, setting the input common-mode voltage of the difference amplifier near the ground. In another example,  $R_{sense}$  can be placed between Vsy and the load, setting the input common-mode voltage near Vsy.

Figure 1-8: Current sensing amplifier for DC supply

Therefore, op-amps for this application should have wide input common-mode voltage ranges (ideally rail-to-rail).

#### 1.4.3 *Summary*

In sensor signal acquisition and DC supply current sensing applications, the input signals are quite small, with signal frequencies usually well below one kilohertz, thus amplifiers with high closed-loop gains are necessary. However, low-pass filters with low cutoff frequencies can be readily applied to attenuate the switching artifacts of chopping. These filters also limit the noise bandwidth, so that a relatively high thermal noise PSD is tolerable. Lastly, input source impedances are typically lower than a few  $k\Omega$ , so that nano-Ampere level input bias currents are also tolerable.

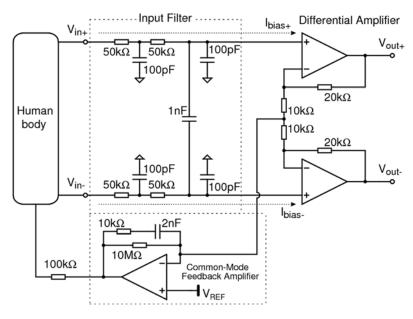

Figure 1-9: ECG front-end circuit

#### 1.5 Newer Applications of Chopper Op-Amps

As discussed in the previous section, chopper op-amps mainly serve applications where signal frequencies and signal source impedances are relatively low. However, a broader range of applications could be served, if the switching artifacts of chopping could be pushed to higher frequencies and/or if their magnitudes could be reduced. This section introduces some new applications that have previously been served by precision bipolar or JFET op-amps. It also discusses the extra requirements that chopper op-amps will have to meet to serve these applications, which form the main motivation for the work in this thesis.

#### 1.5.1 Biomedical Sensing Front-End

Biomedical sensing systems such as Electroencephalogram (EEG), Electrocardiogram (ECG), and Electromyogram (EMG) require front-end differential amplifiers to boost the tiny voltages picked up by electrodes on the patient's skin [18, 19]. Figure 1-9 shows the block diagram of a typical front-end, consisting of a common-mode feedback amplifier, an input filter, and a

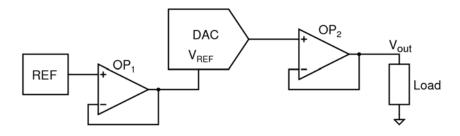

Figure 1-10: Precision DAC configuration

differential amplifier. Since the bandwidth of these biomedical signals is about 200Hz, chopper op-amps with low 1/f noise are preferred, and an external low-pass filter can be applied to attenuate the switching artifacts at the chopping frequency. However, as will be explained later, due to their input switching, chopper op-amps have input bias currents  $I_{bias+}$  and  $I_{bias-}$ . In conjunction with the  $100k\Omega$  input filter resistors required for patient isolation, this can cause significant errors. For instance, a 1nA bias current mismatch will cause a  $100\mu$ V differential input offset. To avoid such large errors, the input bias currents should be at the 100pA level or lower. Moreover, for portable and wearable applications, each op-amp should have a low power consumption under 100 microwatts, and fit into a small package such as SC-70. Furthermore, a wide supply voltage range including 1.8V is preferred in order to share the supply voltage with other components such as ADCs and digital processors.

#### 1.5.2 Reference and DAC Buffers

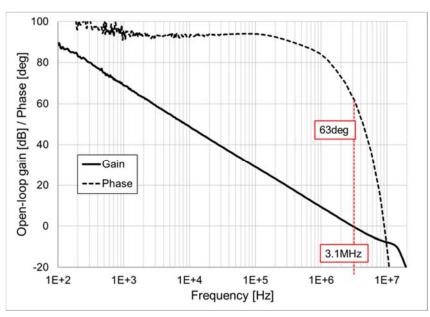

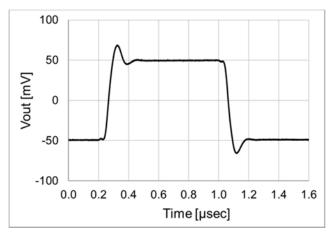

Precision op-amps are often used to buffer voltage references and DACs. Figure 1-10 shows an example of a precision DAC configuration, consisting of a reference, a reference buffer OP<sub>1</sub>, a DAC, and a DAC output buffer OP<sub>2</sub> [20]. DACs and ADCs often generate kickback on their reference pins, so that the buffers need to quickly recover and provide stable voltages. Similarly, ADCs often generate kickback on their input pins due to the sampling action of their input circuitry. The DAC output buffer OP<sub>2</sub> needs to provide wide input and output ranges, and to drive resistive and/or capacitive loads. As a result, any switching artifacts should be small and outside the signal band. This particular DAC is capable of generating a 2MHz output signal, so that the switching artifacts should be above a few Megahertz. Additionally, OP<sub>1</sub> and OP<sub>2</sub> should be stable and perform well in a unity gain configuration.

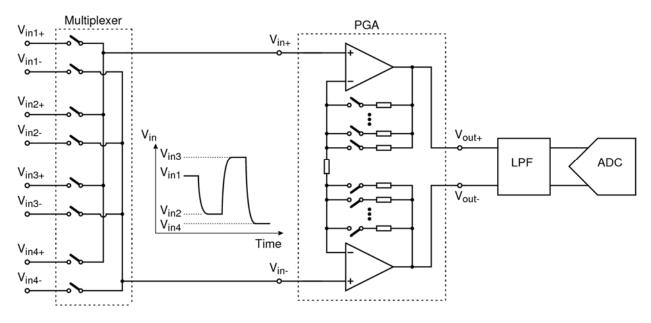

Figure 1-11: Process control signal acquisition chain with input multiplexer

#### 1.5.3 Process Control Data Acquisition Signal Chain

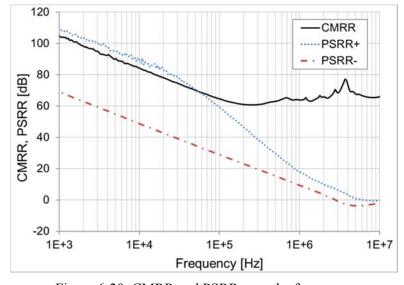

Process control data acquisition signal chains are used in many locations such as automated factories, oil refineries, aerospace systems, as well as in medical equipment [21]. Figure 1-11 shows a typical block diagram consisting of a multiplexer, a programmable gain amplifier (PGA), a low-pass filter (LPF), and an ADC. The PGA consists of two op-amps and resistors, and has a selectable gain, typically ranging from one to ten. Each of the differential input signals  $V_{in1-4}$  would represent physical signals, e.g. pressure, temperature, flow, etc., with frequencies typically below one kilohertz. However, when the multiplexer switches, the differential input of the PGA  $V_{in}$  quickly changes. This change can be as large as the full scale input of the ADC, and the allowed settling time may be only in the order of a few microseconds. Therefore, the closed-loop bandwidth of the PGA and the cutoff frequency of the LPF must be in the order of a few hundred kilohertz or higher. Any switching artifacts should then be minimized and be located above the Megahertz range. Additionally, the input signals may be at various common-mode levels with large common-mode noise, after being transmitted through a harsh environment. Therefore, the op-amp should also have a wide input common-mode voltage range, possibly up to  $\pm 10V$ , along with a high AC CMRR.

#### 1.6 Challenges

The previous sections discussed traditional applications of chopper op-amps, as well as some newer ones. To justify their development costs, chopper op-amp designs should cover as many of these applications as possible. This is especially true for a stand-alone op-amp IC or an op-amp IP core intended for use in a variety of other ICs. Such a chopper op-amp should have small switching artifacts located at higher frequencies, while achieving low offset and low 1/f noise. Additionally, a low noise PSD, wide supply range, and wide common-mode voltage range will allow the op-amp to be used in a broader range of applications.

The chopping frequency should be set high enough to extend the usable signal bandwidth and to cover the newer applications. However, apart from the traditional op-amp design trade-offs between noise PSD, current consumption, and die area, chopper op-amp design also involves specific trade-offs between noise PSD, chopping frequency, and residual offset, caused by the switching artifacts.

#### 1.7 Organization of the Thesis

This thesis presents circuit techniques that reduce the switching artifacts in chopper amplifiers, so as to achieve the levels of performance described in the previous section. Some of the proposed techniques can push the noise spectra peak to higher frequencies and reduce their magnitude, without significantly increasing the residual offset. Consequently, the proposed chopper op-amps offer wider usable signal bandwidths as well as superb DC performance, and therefore can be implemented in a broader range of applications.

Chapter 2 reviews three offset cancellation techniques—trimming, auto-zeroing, and chopping—including their advantages and disadvantages. In the review of the chopping technique, various switching artifacts are explained, including up-modulated ripple, output glitches, residual offset and input bias current, and gain reduction due to dynamic switching conductance. Next, Chapter 3 reviews some previous techniques that reduce some of these

switching artifacts.

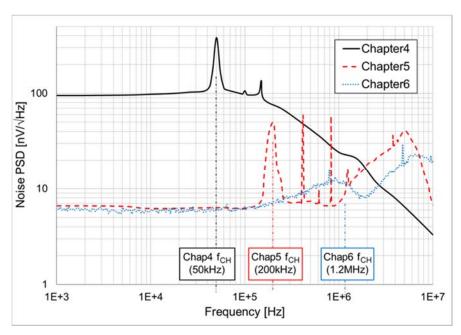

Some original contributions are presented in Chapters 4, 5 and 6. Each chapter presents an individual design project, along with the proposed techniques, the overall op-amp design, and the measurement results. In Chapter 4, a local feedback technique, called auto-correction feedback (ACFB) is proposed to reduce the up-modulated ripple. This technique is implemented in a low power chopper op-amp design that draws 13µA from a 1.8 to 5.5V supply, to serve low power applications.

Chapter 5 presents a chopper op-amp that achieves a 5.6 nV/VHz noise PSD and a  $0.5 \mu\text{V}$  maximum offset, to serve applications requiring very small low frequency error. In order to mitigate the trade-off between the noise PSD and the residual offset, an adaptive clock boosting technique is employed in the input chopper. This minimizes its charge injection and keeps it constant over the amplifier's rail-to-rail input common-mode voltage range.

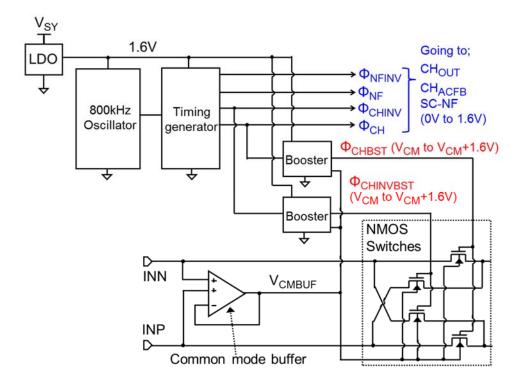

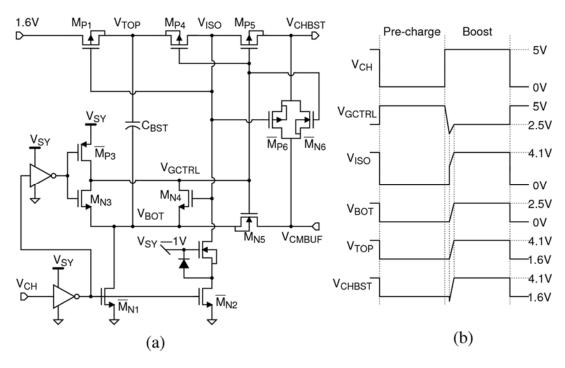

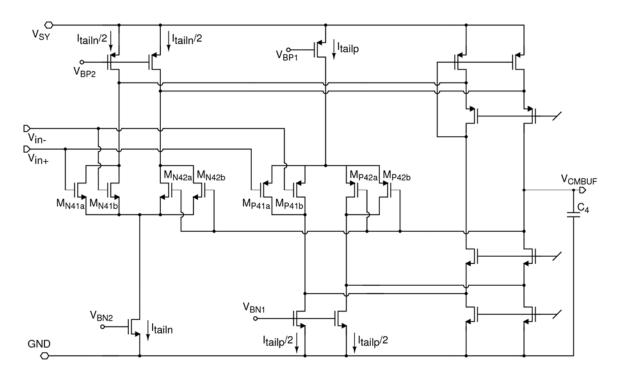

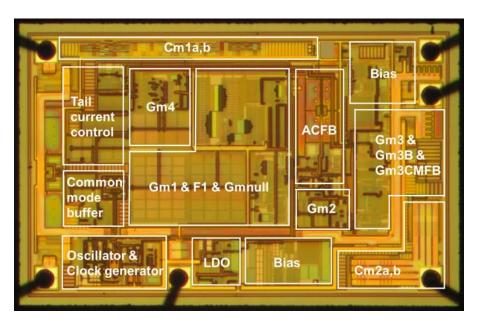

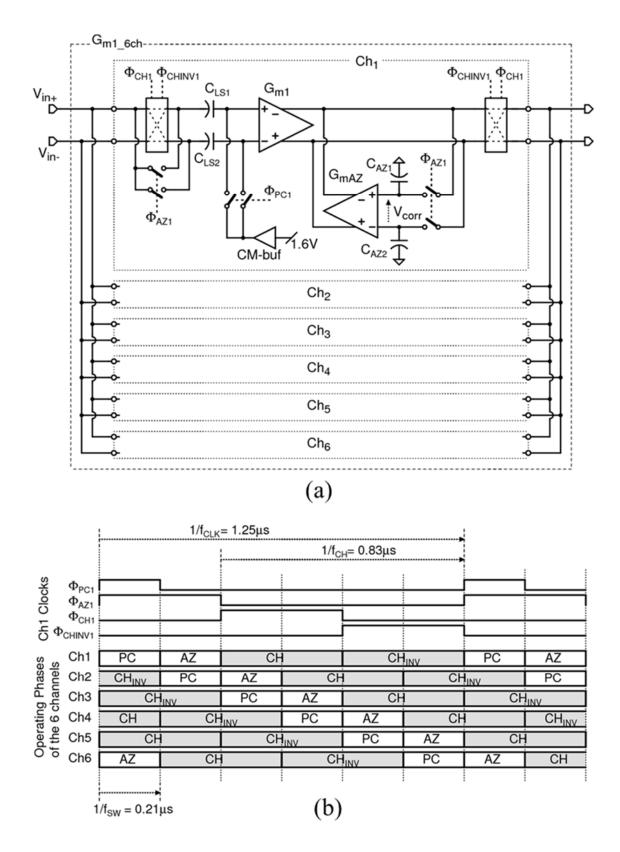

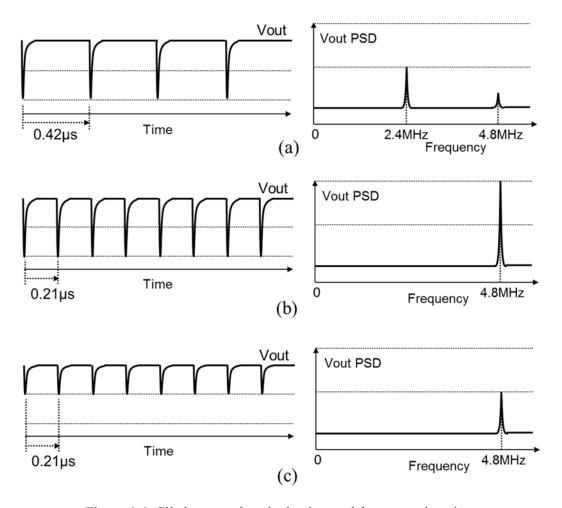

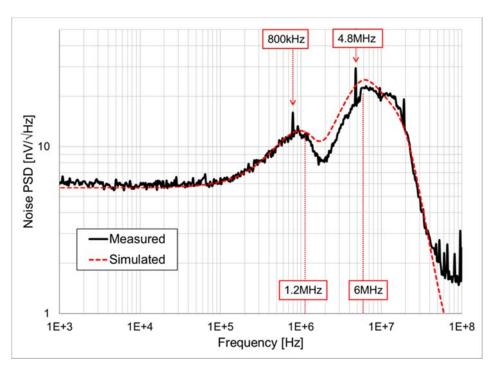

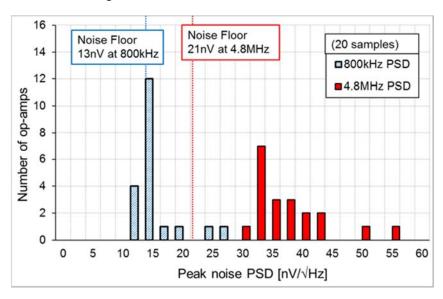

Chapter 6 presents a chopper op-amp, which operates from a 4.5-60V supply, and is intended to serve industrial applications that require wide supply and input common-mode voltage ranges as well as wide usable signal bandwidth. Two techniques are proposed to locate switching artifacts at higher frequencies and to reduce their magnitude. First, this op-amp employs six parallel input stages driven by 800kHz interleaved clocks, so as to locate the majority of the switching energy at 4.8MHz. Second, the input chopper incorporates a charge mismatch compensation circuit to reduce the maximum input bias current from 1.5nA to 150pA at post-production trimming. The thesis ends with Chapter 7, in which its original contributions are reviewed and the performance of the various designs is compared with the state-of-the-art.

#### 1.8 References

- [1] J. Bradley, J. Barbier, and D. Handler, "Embracing the Internet of Everything To Capture Your Share of \$14.4 Trillion", *Cisco Systems*, 2013, Accessed on March 2018, [Online] Available: <a href="http://www.cisco.com/web/about/ac79/docs/innov/IoE">http://www.cisco.com/web/about/ac79/docs/innov/IoE</a> Economy.pdf>.

- [2] B. Bateman, "IoT is driving an analog opportunity", *EE Times*, May 2015, Accessed on March 2018, [Online] Available: <a href="http://www.electronics-eetimes.com/en/iot-is-driving-an-analog-opportunity.html?cmp">http://www.electronics-eetimes.com/en/iot-is-driving-an-analog-opportunity.html?cmp</a> id=7&news id=222924930>.

- [3] M. Pachchigar, "Low Power Precision Data Acquisition Signal Chain for Space Constrained Applications", Accessed on March 2018, [Online] Available:

<a href="http://www.analog.com/media/en/technical-documentation/technical-articles/Low-Power-Precision-Data-Acquisition-Signal-Chain-for-Space-Constrained-Applications.pdf">http://www.analog.com/media/en/technical-documentation/technical-articles/Low-Power-Precision-Data-Acquisition-Signal-Chain-for-Space-Constrained-Applications.pdf</a>.

- [4] Texas Instruments, "AN-31 Op Amp Circuit Collection", May 2013, Accessed on March 2018, [Online] Available: <a href="http://www.ti.com/lit/an/snla140b/snla140b.pdf">http://www.ti.com/lit/an/snla140b/snla140b.pdf</a>>.

- [5] B. Razavi, "Design of Analog CMOS Integrated Circuits", McGraw Hill Companies, Inc., 2001.

- [6] W. Sansen, Analog Design Essentials, Springer, Dordrecht, the Netherlands, 2006.

- [7] J. H. Huijsing, *Operational Amplifier Theory and Design*, 2<sup>nd</sup> Edition, Springer, 2011.

- [8] Analog Devices, "MT-054 Tutorial, Precision Op Amps", Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/media/en/training-seminars/tutorials/MT-054.pdf">http://www.analog.com/media/en/training-seminars/tutorials/MT-054.pdf</a>.

- [9] Analog Devices, "MT-037 Tutorial, Op Amp Input Offset Voltage", Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/media/en/training-seminars/tutorials/MT-037.pdf">http://www.analog.com/media/en/training-seminars/tutorials/MT-037.pdf</a>.

- [10] M. S. J. Steyaert, W. M. C. Sansen, and C. Zhongyuan, "A Micropower Low-Noise Monolithic Instrumentation Amplifier For Medical Purposes", *IEEE J. Solid-State Circuits*, vol. 22, no. 6, pp. 1163-1168, Dec. 1987.

- [11] Analog Devices, "MT-055 Tutorial, Chopper Stabilized (Auto-Zero) Precision Op Amps", Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/media/en/training-seminars/tutorials/MT-055.pdf">http://www.analog.com/media/en/training-seminars/tutorials/MT-055.pdf</a>.

- [12] C. C. Enz and G. C. Temes, "Circuit Techniques for Reducing the Effect of Op-Amp Imperfections: Autozeroing, Correlated Double Sampling, and Chopper Stabilization", *Proc. of IEEE*, vol. 84, no. 9, pp. 1320-1324, Sept. 1996.

- [13] W. Kester, J. Bryant, and W. Jung, "Amplifiers for Signal Conditioning, Section 3", 1999, Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/media/en/training-seminars/design-handbooks/sensor-signal-cond-sect3.PDF">http://www.analog.com/media/en/training-seminars/design-handbooks/sensor-signal-cond-sect3.PDF</a>.

- [14] Analog Devices, "CN-0216: Precision Weigh Scale Design Using the AD7791 24-Bit Sigma-Delta ADC with External ADA4528-1 Zero-Drift Amplifiers", Sept. 2011, Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/media/en/reference-design-documentation/reference-designs/CN0216.pdf">http://www.analog.com/media/en/reference-design-documentation/reference-designs/CN0216.pdf</a>.

- [15] Analog Devices, "ADA4528 Datasheet", Jan. 2011, Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/media/en/technical-documentation/data-sheets/ADA4528-1\_4528-2.pdf">http://www.analog.com/media/en/technical-documentation/data-sheets/ADA4528-1\_4528-2.pdf</a>.

- [16] Analog Devices, "AD7791 Datasheet", Aug. 2003, Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/media/en/technical-documentation/data-sheets/AD7791.pdf">http://www.analog.com/media/en/technical-documentation/data-sheets/AD7791.pdf</a>>.

- [17] N. Zhao, W. Liao, and H. Sino, "High-Side Current Sensing with Wide Dynamic Range: Three Solutions", Dec. 2010, Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/library/analogDialogue/archives/44-12/high\_side.html">http://www.analog.com/library/analogDialogue/archives/44-12/high\_side.html</a>.

- [18] M. W. Hann, "Ultra Low Power, 18 bit Precision ECG Data Acquisition System", June 2013, Accessed on March 2018, [Online] Available: <a href="http://www.ti.com/lit/ug/slau516/slau516.pdf">http://www.ti.com/lit/ug/slau516/slau516.pdf</a>>.

- [19] R. F. Yazicioglu, P. Merken, R. Puers, and C. V. Hoof, "A 60 µW 60 nV/√Hz Readout Front-End for Portable Biopotential Acquisition Systems", *IEEE J. Solid-State Circuits*, vol. 42, no. 5, pp. 1100-1110, May 2007.

- [20] Analog Devices, "CN-0181: Precision, 16-Bit, Voltage Level Setting with Less than 5 mW Total Power Dissipation", Mar. 2011, Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/media/en/reference-design-documentation/reference-designs/CN0181.pdf">http://www.analog.com/media/en/reference-design-documentation/reference-designs/CN0181.pdf</a>.

- [21] M. Pachchigar, "Complete Sensor-to-Bits Solution Simplifies Industrial Data-Acquisition System Design", Apr. 2013, Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/library/analogdialogue/archives/47-04/sensor\_to\_bits.html">http://www.analog.com/library/analogdialogue/archives/47-04/sensor\_to\_bits.html</a>.

## Chapter 2

### Offset Cancellation Techniques

This chapter reviews offset cancellation techniques for amplifiers. First to be reviewed is offset trimming, in which offset is measured and then corrected at post-production test. Since the correction is performed only once, offset drift over time and temperature usually remains uncorrected. Next, after an explanation of the properties of MOS switches, a review is presented of dynamic offset cancellation techniques, such as auto-zeroing and chopping. Unlike offset trimming, these techniques periodically correct offset, and thus reduce offset drift and 1/f noise. However, as will be discussed, these techniques also have drawbacks, which include various residual DC and AC errors.

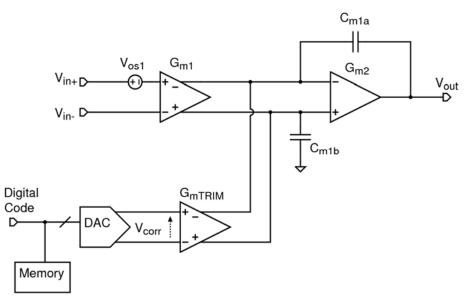

Figure 2-1: An offset trimmed op-amp

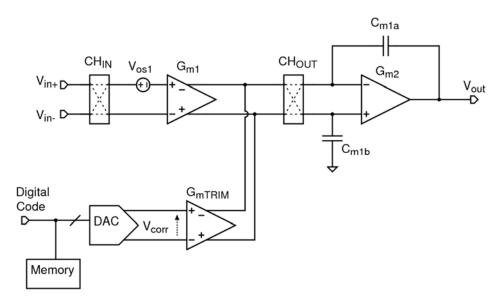

#### 2.1 Offset Trimming

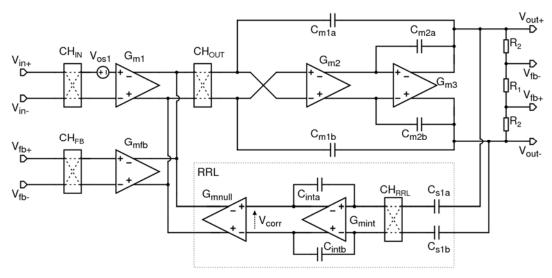

Offset trimming involves measuring the offset and then subtracting the resulting value thereafter [1,2]. Figure 2-1 shows an offset trimming implementation with a two stage op-amp. The signal path consists of input and output transconductors  $G_{m1}$  and  $G_{m2}$ , and frequency compensation capacitors  $C_{m1a}$  and  $C_{m1b}$ . Additionally, a trimming transconductor  $G_{mTRIM}$  and a DAC are implemented to subtract out an initial offset  $V_{os1}$ . At post-production test, first the correction voltage  $V_{corr}$  is set to zero, and then  $V_{os1}$  is measured externally. Next,  $V_{corr}$  is adjusted to:

$$V_{corr} = -\frac{G_{m1}}{G_{Trim}} V_{os1}, (2-1)$$

through the DAC, so that  $G_{mTRIM}$  cancels the offset current of  $G_{ml}$ . Then, the corresponding digital code is stored in on-chip memory, so that  $V_{osl}$  remains corrected thereafter.

However, CMOS input differential pairs have uncorrelated absolute offset and offset drift [3]. Thus, trimming the absolute offset at one temperature does not decrease the offset drift. For this reason, most trimmed CMOS op-amps have a maximum offset drift greater than a few

Figure 2-2: (a) An NMOS switch and (b) the on-conductance versus input voltage

$\mu V/^{\circ}C$  [4]. In 2011, Bolatkale reported a MOS-input op-amp achieving a 0.33 $\mu V/^{\circ}C$  maximum offset drift by biasing the input stage at two different currents, while trimming at one temperature [3]. However, the second gain stage uses complementary bipolar devices which are not available in every CMOS process. In 2013, another MOS-input op-amp achieving a  $0.8\mu V/^{\circ}C$  maximum offset drift was reported [5], where its offset is corrected at the ambient temperature by a first DAC, and then its offset drift over temperature is corrected at a higher temperature by a second DAC. However, this method requires offset measurements at two different temperatures for each op-amp unit, and thus increases production cost. Bipolar input differential pairs have correlated absolute offset and offset drift, and therefore can achieve lower offset drift. For instance, the one reported in [6] achieves a  $0.25\mu V/^{\circ}C$  maximum offset drift. Nevertheless, as discussed in Section 1.4.1, this level of offset drift is still insufficient in some sensor applications, which require offset drifts below  $0.1 \ \mu V/^{\circ}C$ . Additionally, bipolar op-amps are ruled out in some applications due to their high input bias current (several nano-Amperes) and high manufacturing cost.

#### 2.2 MOS Switches

#### 2.2.1 Realization and On-Resistance

This section explains the properties of the MOS switches that are used in the dynamic offset cancellation techniques. They can be realized by either NMOS or PMOS switches, or a

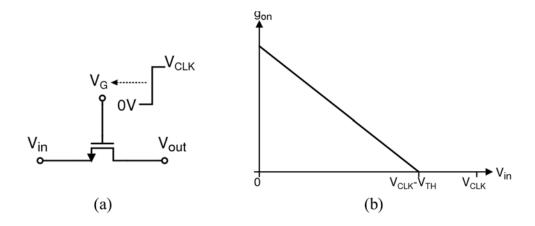

combination of both (CMOS switches), depending on the targeted input voltage range [7]. Figure 2-2 (a) shows an NMOS switch with input, output, and gate terminals  $V_{IN}$ ,  $V_{OUT}$ , and  $V_G$ . By driving  $V_G$  low to 0V, the switch turns off to isolate the two terminals  $V_{IN}$  and  $V_{OUT}$ . On the other hand, by driving  $V_G$  high to  $V_{CLK}$ , the switch turns on to connect the two terminals. When  $V_{OUT}$  is slightly larger or equal to  $V_{IN}$ , the on-conductance  $g_{on}$  between the two terminals is given by:

$$g_{on} = \beta \frac{W}{L} (V_{CLK} - V_{TH} - V_{IN}),$$

(2-2)

where  $\beta$  is the transconductance parameter,  $V_{TH}$  is the threshold voltage, and W and L are the channel width and length of the NMOS, respectively [7]. As suggested by this equation,  $g_{on}$  is proportional to both W and the overdrive voltage  $V_{CLK} - V_{TH} - V_{IN}$ , and thus varies with  $V_{IN}$  as plotted in Figure 2-2 (b). For a targeted range of  $V_{IN}$ , the switch must be made sufficiently wide to achieve the desired on-resistance and hence the thermal noise.

#### 2.2.2 Charge Injection

The amount of channel charge injection  $q_{ch,inj}$  and clock feedthrough  $q_{clk,inj}$  are proportional to the width [7]. They are given by:

$$q_{ch,inj} = WL \cdot C_{ox} \left( V_{CLK} - V_{TH} - V_{IN} \right) \qquad (2-3)$$

$$q_{clk,inj} = 2W \cdot C_{ov} \cdot V_{CLK} , \qquad (2-4)$$

where  $C_{ox}$  is the gate oxide capacitance per unit area, and  $C_{ov}$  is the gate overlap capacitance per unit of width. According to the two equations above,  $q_{ch,inj}$  also increases with the overdrive voltage  $V_{CLK} - V_{TH} - V_{IN}$ , while  $q_{clk,inj}$  increases with the clock swing  $V_{CLK}$ . Therefore, the resulting errors can depend on the supply voltage and the input voltage, which degrade the PSRR and the CMRR. This thesis uses the term *charge injection* to refer to the combination of a channel charge injection and clock feedthrough. When  $V_G$  rises, it generates a positive charge injection  $q_{ch,inj} + q_{clk,inj}$  that splits into the  $V_{IN}$  and  $V_{OUT}$  terminals. When  $V_G$  drops, it generates the same amount of charge injection but with opposite polarity.

Figure 2-3: Cancellation of charge injection by (a) complementary switch, (b) dummy switch, and (c) differential circuitry

#### 2.2.3 Cancellation of Charge Injection

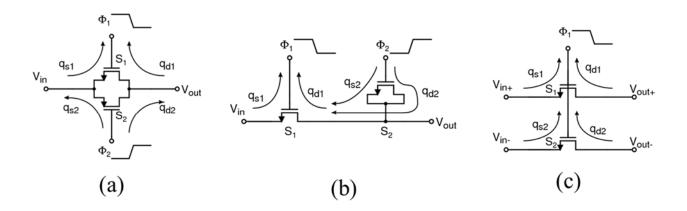

To cancel the charge injection of an NMOS switch  $S_1$ , a PMOS switch  $S_2$  can be added as shown in Figure 2-3 (a).  $S_1$  and  $S_2$  are driven by two complementary clocks  $\Phi_1$  and  $\Phi_2$ , respectively. As a result, the switches generate charge injection of opposite polarity that cancel each other out. However, this cancellation scheme only works when  $V_{IN}$  is exactly half of  $V_{CLK}$ . Otherwise, the two switches have unequal overdrive voltages, and thus generate unequal amounts of channel charge injection.

Another way to cancel charge injection is to add an NMOS dummy switch  $S_2$  as shown in Figure 2-3 (b).  $S_2$  is half the size of  $S_1$ , so that its charge injections  $q_{S2}$  and  $q_{d2}$  cancel that of  $S_1$  ( $q_{d1}$ ) at the  $V_{OUT}$  node. However, the  $V_{IN}$  and  $V_{OUT}$  nodes are often driven by unequal impedances. In this case, the overall charge injection of  $S_1$  is unequally split between these nodes, making this cancellation scheme ineffective.

The most effective solution is to use differential circuitry as shown in Figure 2-3 (c). Two NMOS switches  $S_1$  and  $S_2$  are driven by a single clock  $\Phi_1$ , generating a nearly equal amount of charge injection. As long as the impedances are balanced differentially, the charge injection mismatch is only due to coupling capacitance mismatch, which is in the order of 1% to 10%.

As will be explained later, charge injection causes DC residual offset and transient glitches

Figure 2-4: An auto-zero op-amp

in either chopper or auto-zero amplifiers. The residual offset is proportional to the amount of charge injection mismatch between differential switches. On the other hand, the magnitude of the glitches mainly depends on the absolute amount of charge injection. Therefore, both the mismatch and the absolute amount of charge injection should be minimized, while meeting the targeted on-resistance, and hence the thermal noise PSD.

### 2.3 Auto-Zeroing

Auto-zeroing is one of the two dynamic offset cancellation techniques available. Unlike offset trimming, it periodically measures and corrects offset, and thus reduces the offset drift and 1/f noise as well [7,8].

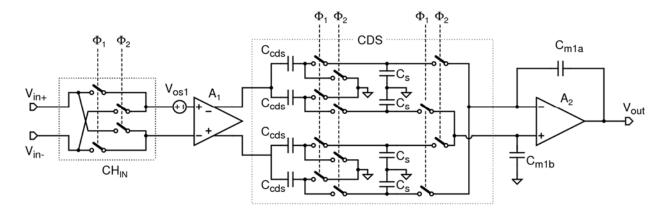

## 2.3.1 Principle

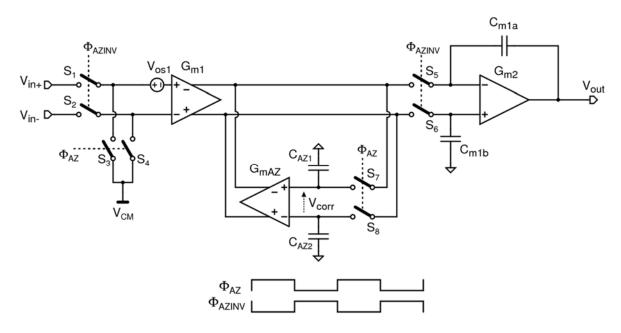

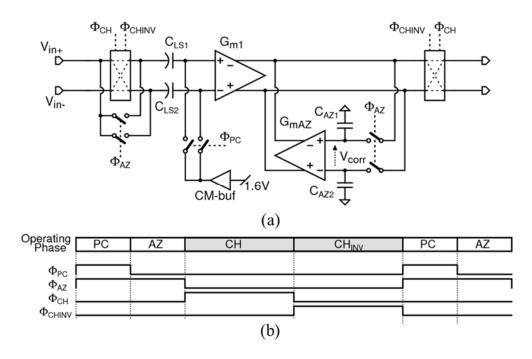

A block diagram of a two stage, auto-zeroed op-amp is shown in Figure 2-4. The signal path consists of input and output transconductors  $G_{m1}$  and  $G_{m2}$ . Additionally, it implements switches  $S_{I-8}$ , sampling capacitors  $C_{AZI,2}$ , and an auto-zeroing transconductor  $G_{mAZ}$ , to measure, sample, and cancel an input offset of  $G_{m1}$  ( $V_{os1}$ ). Switches  $S_{I-8}$  are driven by complementary clocks  $\Phi_{AZ}$  and  $\Phi_{AZINV}$ , operating at the auto-zeroing frequency  $f_{AZ}$ . The op-amp is in the auto-zero phase when  $\Phi_{AZINV}$  is high, and is in the amplification phase when  $\Phi_{AZINV}$  is high. In the auto-zero phase, the differential inputs of  $G_{m1}$  are shorted to a common-mode voltage  $V_{CM}$ , and the outputs are connected to the inputs of  $G_{mAZ}$  to form a local auto-zeroing feedback loop. Assuming the loop gain is infinite, the offset correction voltage  $V_{corr}$  is adjusted to:

$$V_{corr} = -\frac{G_{m1}}{G_{m47}} V_{os1}, \qquad (2-5)$$

so that  $G_{mAZ}$  cancels  $V_{os1}$ . When  $\Phi_{AZ}$  drops,  $V_{corr}$  is sampled by  $C_{AZ1,2}$ . Next, when the amplification phase begins, the differential inputs and outputs of  $G_{m1}$  are connected to the signal path, so that the op-amp can amplify the input signals. The resulting offset is zero in principle, since  $V_{os1}$  is still cancelled by  $G_{mAZ}$  with the sampled  $V_{corr}$  in the previous auto-zero phase.

### 2.3.2 Residual Offset

In the circuit of Figure 2-4, residual offset is the result of several imperfections [7]. First, the

auto-zeroing feedback has a finite loop gain  $A_{VAZ}$ , resulting in an error voltage. Second,  $G_{mAZ}$  also has an input offset  $V_{osAZ}$ . Third, sampling switches  $S_7$  and  $S_8$  generate charge injections  $q_7$  and  $q_8$ , when turning off. Their charge injection mismatch  $\Delta q_{AZ8,7} = q_{AZ8} - q_{AZ7}$  then flows into  $C_{AZ1,2}$ , and produces another error voltage. As a result, the correction voltage  $V_{corr}$  includes the combined error voltage  $V_{correrr}$  equaling:

$$V_{correrr} = \frac{1}{A_{vAZ}} \left( \frac{G_{m1}}{G_{mAZ}} V_{os1} \pm V_{osAZ} \right) \pm \frac{\Delta q_{8,7}}{C_{AZ1,2}}.$$

(2-6)

By multiplying this error by  $G_{mAZ}/G_{m1}$ , the residual input offset  $V_{os,res}$  obtained is:

$$V_{os,res} = \frac{1}{A_{vAZ}} \left( V_{os\,1} \pm \frac{G_{mAZ}}{G_{m1}} V_{osAZ} \right) \pm \frac{G_{mAZ}}{G_{m1}} \cdot \frac{\Delta q_{8,7}}{C_{AZ\,1,2}} . \quad (2-7)$$

To minimize this residual offset, the auto-zeroing loop gain  $A_{ZAZ}$  should be increased by using a cascoded topology. Additionally,  $C_{AZI,2}$  should be increased, and  $G_{mAZ}$  should be reduced with respect to  $G_{mI}$ . However, the tail current of  $G_{mAZ}$  must cover the maximum offset current of  $G_{mI}$ . Therefore, the transconductance should be reduced by employing long channel MOS devices or resistor degeneration. For instance, with  $A_{VAZ} = 80$ dB, a 10mV initial offset results in a 1 $\mu$ V residual offset. Additionally, with  $C_{AZI,2} = 10$ pF and  $G_{mAZ}/G_{mI} = 0.1$ , a 1fC charge injection mismatch will produce a  $10\mu$ V residual offset.

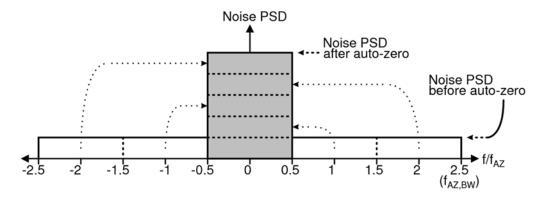

### 2.3.3 Broadband Noise Folding

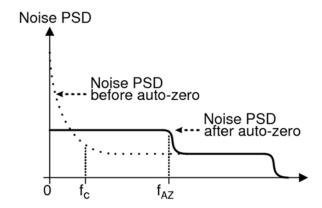

This subsection discusses the resulting noise PSD after auto-zeroing. The low frequency noise component of  $G_{m1}$  is also sampled by  $C_{AZ1,2}$  along with the offset, and thus is cancelled thereafter. On the other hand, the high frequency noise component changes quickly after being sampled, and thus is not effectively cancelled. Moreover, at the offset sampling, the noise PSD above  $f_{AZ}/2$  is folded back to the baseband frequencies between DC and  $f_{AZ}/2$ , as illustrated in Figure 2-5 [8,9]. The noise folding factor  $n_{fold}$  is defined as the ratio between the auto-zeroing loop bandwidth  $f_{AZ,BW}$  and  $f_{AZ}$ , and is given by:

Figure 2-5: Noise folding upon auto-zero sampling

Figure 2-6: Noise PSDs before and after auto-zeroing

$$n_{fold} \equiv \frac{2 f_{AZ,BW}}{f_{AZ}} = \frac{2}{f_{AZ}} \frac{G_{mAZ}}{2 \pi C_{AZ,1,2}}.$$

(2-8)

The larger  $n_{fold}$  is, the larger the resulting noise PSD is. Usually, this factor is greater than unity, since  $f_{AZ,BW}$  is set higher than  $f_{AZ}$  to allow the auto-zeroing loop to settle within one auto-zero phase.

Figure 2-6 shows the typical noise PSDs before and after auto-zeroing. The 1/f noise is effectively reduced to a negligible level by setting  $f_{AZ}$  well above its corner frequency  $f_c$ . However, below  $f_{AZ}/2$  the noise PSD is higher than the initial thermal noise floor due to the noise folding. In [10], a slow auto-zeroing loop is proposed to reduce  $n_{fold}$  below unity. Even so, the resulting noise PSD still exceeds the initial thermal noise floor by a factor of  $\sqrt{2}$ . Noise folding is one drawback that degrades the NEF of an auto-zeroed op-amp.

Figure 2-7: A ping-pong auto-zero op-amp

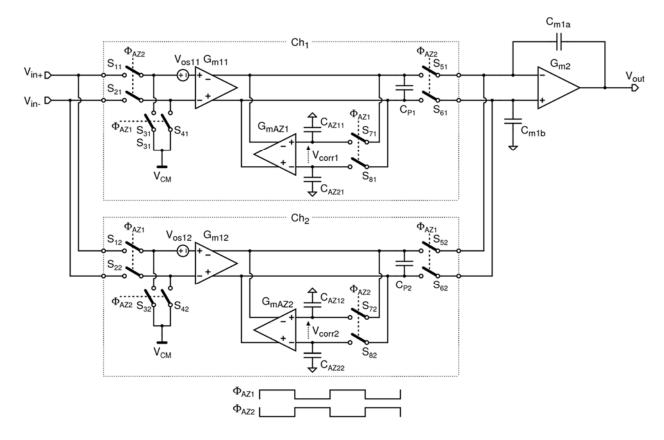

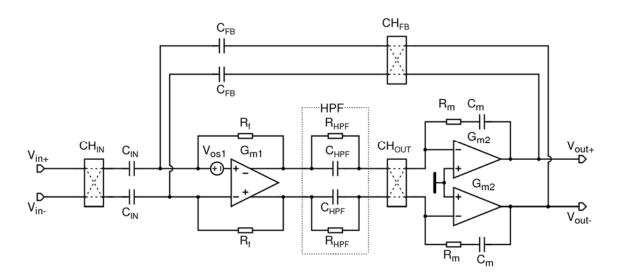

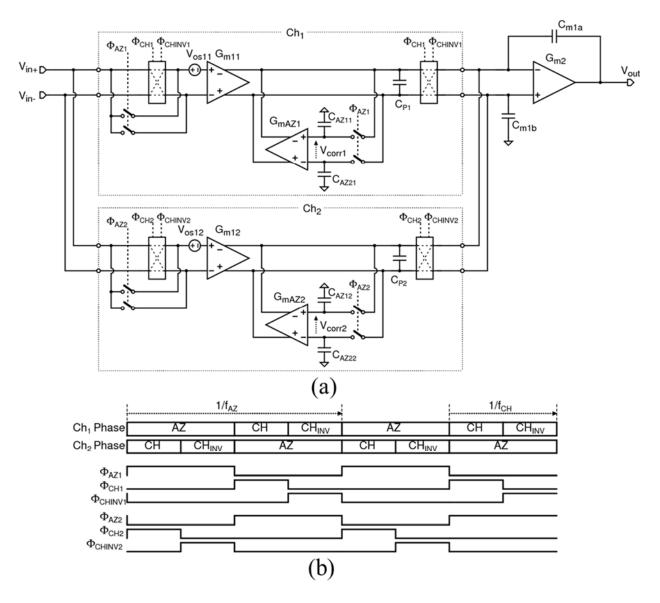

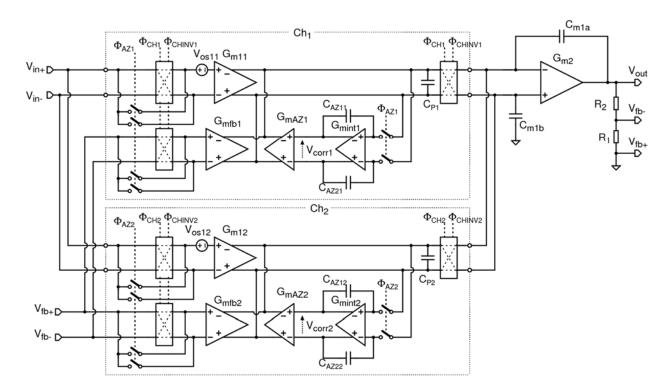

## 2.3.4 Ping-Pong Auto-Zeroing

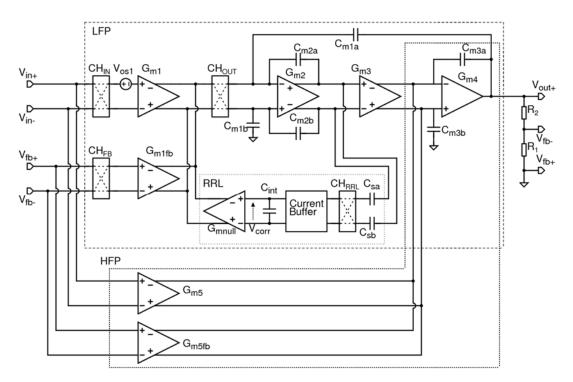

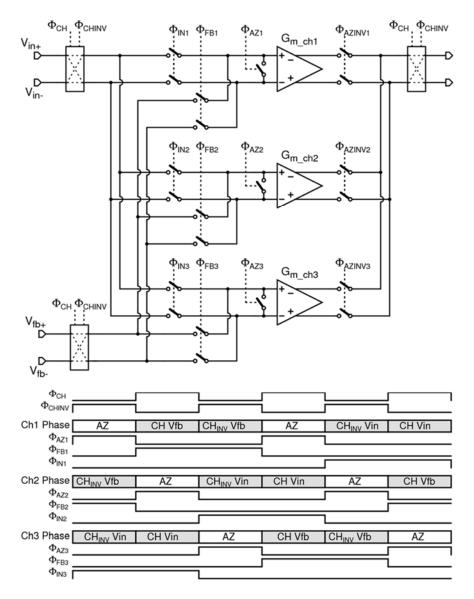

Another drawback of an auto-zeroed op-amp is that it is unable to amplify signals during the auto-zero phase. This is unacceptable in many applications where input signals need to be continuously amplified. This problem can be solved by operating two identical input channels complementarily (ping-pong) [11]. Figure 2-7 shows the circuit diagram, consisting of two parallel input channels Ch<sub>1</sub> and Ch<sub>2</sub> followed by an output transconductor  $G_{m2}$ . Each channel consists of the same circuit shown in Figure 2-4, and is driven by complementary clocks  $\Phi_{AZ1}$  and  $\Phi_{AZ2}$ . When  $\Phi_{AZ1}$  is high, Ch<sub>1</sub> is in the auto-zero phase while Ch<sub>2</sub> is in the amplification phase. In contrast, when  $\Phi_{AZ2}$  is high instead, the phases are reversed. Consequently, the input signal is always amplified by either channel. However, the additional input channel consumes extra current and die area.

Figure 2-8: Chopper op-amp in a closed-loop

### 2.4 Chopping

Chopping is the other dynamic offset cancellation technique. While auto-zeroing samples and cancels offset, chopping modulates the input signal and the offset to separate them from each other in the frequency domain [8]. Since chopping neither involves sampling nor introduces noise folding, the resulting noise PSD is only slightly higher than the initial thermal noise floor [8]. Moreover, the signals are continuously amplified without requiring ping-ponging of the two channels. Therefore, chopping can achieve low offset and low noise PSD in a more power efficient manner than auto-zeroing. Since the basic principles of chopping were already presented in Chapter 1, this section will go on to discuss the various AC and DC errors caused by switching artifacts.

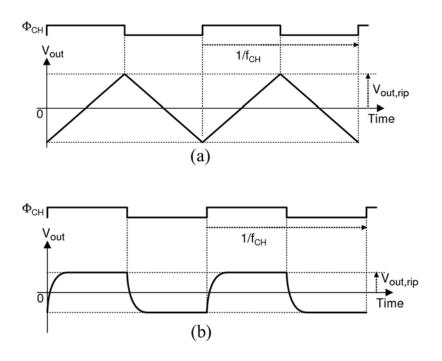

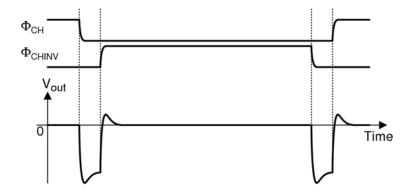

## 2.4.1 Up-Modulated Ripple

Figure 2-8 shows a two stage chopper op-amp with external gain setting resistors  $R_F$  and  $R_G$ . As explained in Section 1.3, the initial offset of  $G_{ml}$  ( $V_{osl}$ ) is up-modulated and becomes output

Figure 2-9: Output ripple (a) without feedback effect and (b) with feedback effect

ripple [12]. The amplitude of this ripple is affected by the closed-loop gain  $A_{CL}$  and the closed-loop bandwidth  $f_{CL}$  given by:

$$A_{CL} \approx 1 + \frac{R_F}{R_G} \tag{2-9}$$

$$f_{CL} = \frac{1}{A_{CL}} \frac{G_{m1}}{2\pi C_{m1a,b}}.$$

(2-10)

When the chopping frequency  $f_{CH}$  is well above  $f_{CL}$ , the ripple is produced in an open-loop manner with no feedback effect:  $V_{os1}$  is converted into a current by  $G_{m1}$ , up-modulated by CHout, and integrated over  $C_{m1a,b}$ . This results in a triangular output ripple as shown in Figure 2-9 (a); the peak amplitude  $V_{out,rip}$  is given by:

$$V_{out,rip} = \frac{G_{m1}}{4f_{CH}C_{m1a,b}}V_{os1}.$$

(2-11)

On the other hand, when  $f_{CH}$  is well below  $f_{CL}$ , the output ripple is produced in a closed-loop

Figure 2-10: Output glitch due to input charge injection

manner with the feedback effect. Thus, it settles to two constant voltages after every clock transition, as shown in Figure 2-9 (b). The amplitude  $V_{out,rip}$  is then given by:

$$V_{out\ rin} = A_{CL}V_{os1}.$$

(2-12)

For instance, with  $G_{ml} = 100 \mu S$ ,  $V_{osl} = 1 \text{mV}$ ,  $f_{CH} = 100 \text{kHz}$ ,  $C_{mla,b} = 10 \text{pF}$ , and  $A_{CL} = 100$ ,  $V_{out,rip}$  is 25mV according to (2-11). When  $A_{CL}$  is reduced to 10 while the other parameters remain the same,  $V_{out,rip}$  becomes 10mV according to (2-12). In either case, the amplitude of the ripple is quite large, and therefore needs to be attenuated in most applications.

#### 2.4.2 Glitches

The transient waveforms in a chopper amplifier have been drawn in Figure 2-9 (a) and (b), where the effect of charge injection is neglected. In fact, as illustrated in Figure 2-10, charge injection of the input switches causes output glitches [13,14]. First,  $\Phi_{CH}$  drops, injecting negative charge on the differential input pins. Soon thereafter,  $\Phi_{CHINV}$  rises, injecting almost the same amount of charges but with positive polarity. Ideally, these negative and positive charges cancel out instantaneously at each input pin, if the transitions of the two clocks occur at the exact same time. In practice, however, there must be some dead time between the two clocks, in order not to short the differential input pins with the switches. This generates short pulses on both input pins, resulting in an output glitch. Since this occurs in the order of a nanosecond, the op-amp is not fast enough to suppress this glitch via its feedback loop. The glitch amplitude depends on the

Figure 2-11: Output noise PSD of a chopper op-amp

source impedances, the dead time, and the amount of charge injection. Similarly, after a half chopping period,  $\Phi_{CHINV}$  drops and  $\Phi_{CH}$  rises, resulting in another glitch.

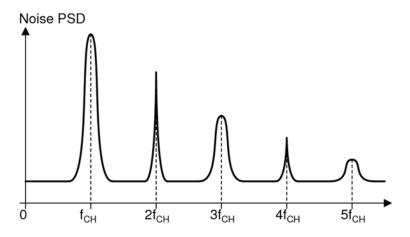

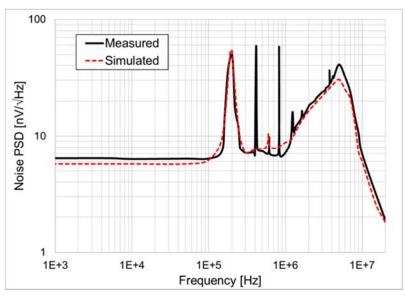

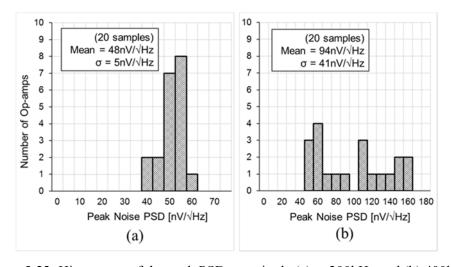

Figure 2-11 shows the output noise PSD of a chopper op-amp, taking both the ripple and the glitches into account. The PSD increases at the odd harmonics of the chopping frequency  $f_{CH}$  due to the up-modulated ripple, and at the even harmonics of  $f_{CH}$  due to the glitches. The noise spectra peak usually need to be attenuated by low-pass filters, which increases cost and limits the usable signal bandwidth [15]. Therefore, manufactures prefer chopper op-amps that have lower noise spectra peak at higher frequencies, so as to relax the requirement of the low-pass filters. On the other hand, a higher  $f_{CH}$  will produce higher residual offset and input bias current, as will be explained in the next subsection.

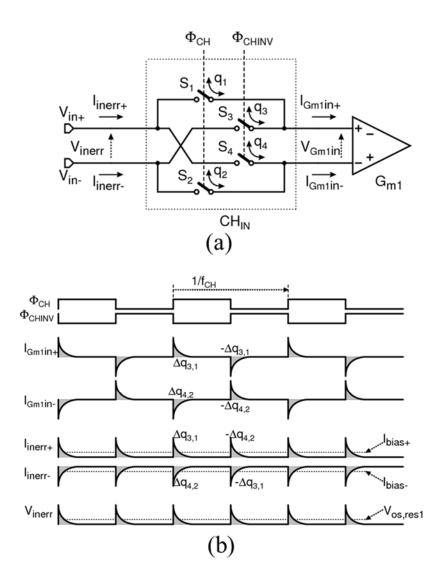

## 2.4.3 Input Bias Current and Residual Offset

Charge injection mismatch causes DC errors such as residual offset and input bias current [12,16]. Close inspection shows that only the charge injection mismatch in the signal path between the two choppers is down-modulated, and thus contributes to the DC errors. In contrast, the charge injection in the signal path outside the two choppers does not contribute to the DC errors, and therefore is neglected in this subsection for simplicity.

Figure 2-12: Input bias current due to input chopping: (a) circuit diagram; (b) transient waveforms

The charge injection mismatch generated by the input chopper CH<sub>IN</sub> is down-modulated and flows back to the amplifier's input pins. As shown in Figure 2-12 (a), CH<sub>IN</sub> consists of four switches S<sub>1-4</sub>, which inject charges  $q_{1-4}$  during every clock transition. Figure 2-12 (b) shows the resulting transient waveforms along with clock timings  $\Phi_{\text{CH}}$  and  $\Phi_{\text{CHINV}}$ . Ideally,  $q_3$  and  $q_4$  cancel each other out at the input of  $G_{m1}$ , as do  $q_4$  and  $q_2$ . However, charge injection mismatches  $\Delta q_{3,1} = q_3 - q_4$  and  $\Delta q_{4,2} = q_4 - q_2$  cause current glitches  $I_{Gm1in+}$  and  $I_{Gm1in-}$ , respectively. These AC current glitches are down-modulated by CH<sub>IN</sub>, and flow back to the differential input pins  $V_{in+}$

Figure 2-13: Residual offset due to output chopping: (a) circuit diagram; (b) transient waveforms

and  $V_{in-}$ . The resulting input error currents  $I_{inerr+}$  and  $I_{inerr-}$  include the DC bias components  $I_{bias+}$  and  $I_{bias-}$  given by:

$$I_{bias +} = f_{CH} \left( \Delta q_{3,1} - \Delta q_{4,2} \right)$$

(2-13)

$$I_{bias-} = -f_{CH} \left( \Delta q_{3,1} - \Delta q_{4,2} \right).$$

(2-14)

Moreover, in conjunction with the on-resistance of each switch  $R_{on}$ , these input bias currents cause a residual input offset voltage  $V_{os,res1}$  equal to:

$$V_{os,res1} = 2 f_{CH} (\Delta q_{3,1} - \Delta q_{4,2}) R_{on}$$

(2-15)

Additionally, source resistances driving the input pins should be added in series with  $R_{on}$  in the equation above, which will further increase  $V_{os,res1}$ . For instance, with  $f_{CH} = 100$ kHz and  $R_{on} = 1$ k $\Omega$ , a charge injection mismatch  $\Delta q_{3,1} - \Delta q_{4,2} = 10$ fF will result in  $I_{bias+} = 1$ nA,  $I_{bias-} = -1$ nA, and  $V_{os,res1} = 2\mu$ V. Furthermore, when each input pin is driven by a 10k $\Omega$  source resistance,  $V_{os,res1}$  increases to  $22\mu$ V.

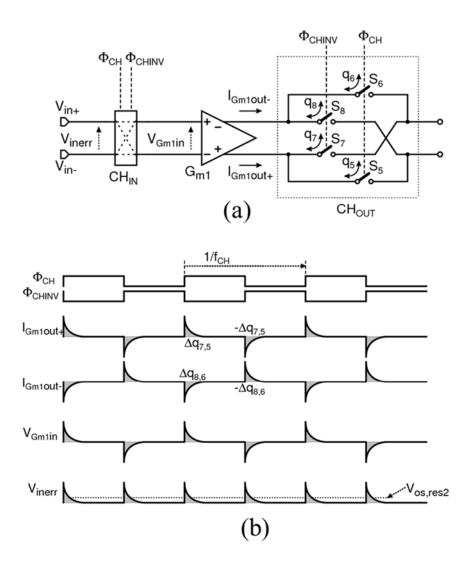

The charge injection mismatch of the output chopper CH<sub>OUT</sub> also causes residual offset. As shown in Figure 2-13 (a), CH<sub>OUT</sub> consists of four switches S<sub>5-8</sub>, which inject charges  $q_{5-8}$ . The charge injection mismatches  $\Delta q_{7,5} = q_7 - q_5$  and  $\Delta q_{8,6} = q_8 - q_6$  result in current glitches  $I_{Gmlout+}$  and  $I_{Gmlout-}$ , respectively, as shown in Figure 2-13 (b). The input transconductor  $G_{ml}$  absorbs these current glitches, resulting in voltage glitches  $V_{Gmlin}$  at its input. The input chopper CH<sub>IN</sub> then down-modulates  $V_{Gmlin}$ , so that the resulting input error voltage  $V_{inerr}$  includes a residual DC offset  $V_{os,res2}$  equal to:

$$V_{os,res2} = \frac{2f_{CH}(\Delta q_{5,6} - \Delta q_{7,8})}{G_{m1}}.$$

(2-16)

As indicated in the equations, these DC errors are proportional to the chopping frequency  $f_{CH}$ . Furthermore, they indicate that wider switches, which suffer from larger charge injection mismatch, cause larger DC errors.

Figure 2-14: Dynamic switching conductance due to chopping: (a) circuit diagram; (b) transient waveforms

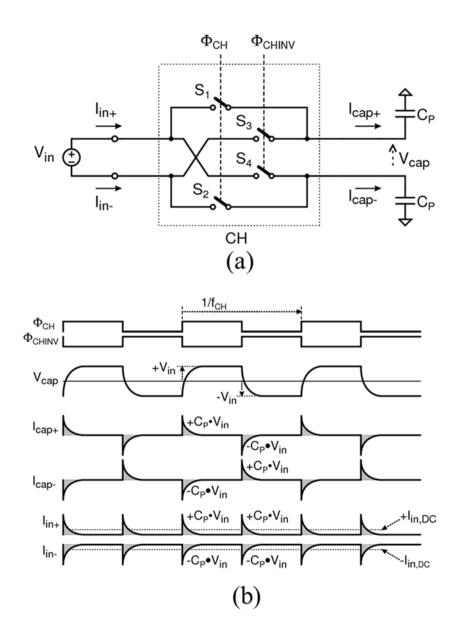

### 2.4.4 Dynamic Switching Conductance

Chopping also generates a dynamic conductance in conjunction with any capacitances at the switching nodes [16]. This is illustrated in Figure 2-14 (a), where a differential input voltage  $V_{in}$  is applied to a chopper CH. As shown in Figure 2-14 (b),  $V_{in}$  is up-modulated and results in an AC voltage output  $V_{cap}$ . Consequently, two capacitances  $C_P$  are charged every clock transition, which causes current glitches  $I_{cap+}$  and  $I_{cap-}$ . These current glitches are down-modulated by CH,

and become input currents  $I_{in+}$  and  $I_{in-}$ , including DC component  $I_{in,DC}$ . The dynamic switching conductance  $G_{switch}$  is defined as:

$$G_{switch} \equiv \frac{I_{DC,in}}{V_{in}} = 2f_{CH}C_P. \qquad (2-17)$$

Because of this effect, a chopper amplifier has a finite differential input conductance. However, this is usually not a problem for an op-amp amplifying DC or low frequency signals, since the differential input voltage is kept small by feedback. However, an instrumentation amplifier can have a large differential input voltage, and so should have a sufficiently low differential input conductance.

Additionally, the DC gain of the input transconductor  $G_{ml}$  decreases due to the switching conductance associated with the output chopper. This not only reduces the open-loop gain of the op-amp, but it also increases the residual offset contributed by a subsequent gain stage. For instance, with an 80dB gain of  $G_{ml}$ , a subsequent gain stage with an input offset of 10mV will give rise to a  $1\mu$ V residual input offset.

### 2.4.5 Summary of the Errors

As discussed earlier in this section, the switching artifacts due to chopping cause various DC and AC errors. The up-modulated ripple and the glitches caused by charge injection show up as noise spectra peak at the harmonics of the chopping frequency  $f_{CH}$ . Moreover, down-modulated charge injection mismatch causes DC errors such as residual offset and input bias currents.

Design parameters, such as the chopping frequency  $f_{CH}$  and the size of the switches, affect these AC and DC errors, and therefore should be properly chosen for a given design target. To sufficiently reduce the 1/f noise,  $f_{CH}$  should be set above its corner frequency. For applications requiring a wider signal bandwidth,  $f_{CH}$  should be further increased to relax the requirements of the low-pass filters. However, this increases the residual offset and input bias current, and decreases the effective DC gain of the input transconductor. Moreover, the variation of  $f_{CH}$  over temperature causes residual offset drift.

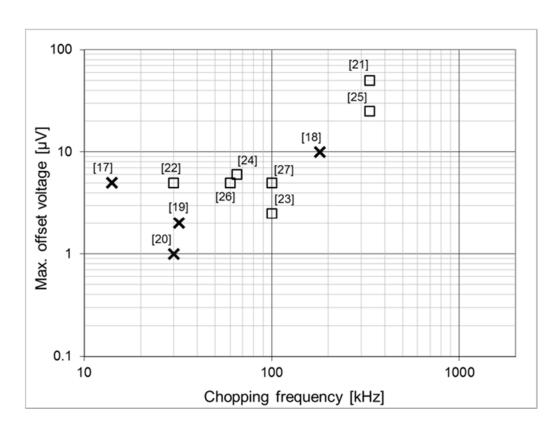

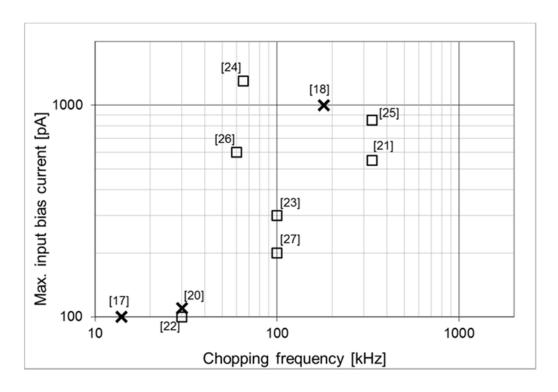

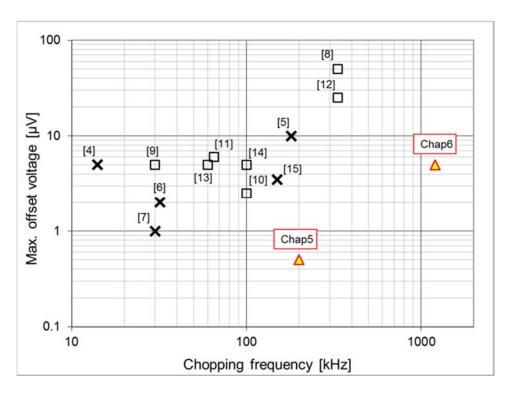

Figure 2-15: Maximum offset versus chopping frequency of previous chopper op-amps

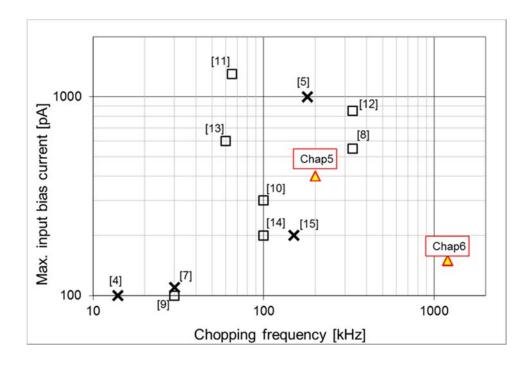

Figure 2-16: Maximum input bias current versus chopping frequency of previous chopper op-amps

The input switches must be made sufficiently wide to reduce the on-resistance for a targeted thermal noise PSD. However, this also increases their charge injection mismatch, and thus increases the residual offset and input bias current. When the chopping clocks have a fixed amplitude, the amount of charge injection changes with the input common-mode voltage. Consequently, the residual offset and input bias current also change with the input common-mode voltage, which degrades the CMRR and the common-mode input impedance. Moreover, wider switches produce larger glitches and hence larger noise spectra peak.

In summary, chopper op-amp design involves trade-offs between the DC error, the chopping frequency, and the noise PSD. Figure 2-15 shows the maximum offset versus the chopping frequency of previous chopper op-amps that have less than  $20nV/\sqrt{Hz}$  noise PSD [17-27]. Note that the specifications derived from conferences or journals are marked by crosses, while those derived from the datasheets of commercial products are marked by squares. It can be seen that their offset tends to increase with chopping frequency, and is typically greater than  $10\mu V$  for chopping frequencies above 100kHz. Figure 2-16 shows the maximum input bias current versus the chopping frequency. Like offset, input bias current tends to increase with chopping frequency, and is higher than 500pA for chopping frequencies above 200kHz.

Table 2-1: Comparison of the three low offset techniques

|                                | Basic | Trim   | Auto-zero | Chopper  |

|--------------------------------|-------|--------|-----------|----------|

| Offset                         | High  | Low    | Very low  | Very low |

| Offset drift over temperature  | High  | Medium | Very low  | Very low |

| Offset change with common mode | High  | Medium | Very low  | Very low |

| 1/f noise                      | High  | High   | Very low  | Very low |

| Continuous-time operation      | Yes   | Yes    | * No      | Yes      |

| Noise PSD in the base band     | High  | High   | Medium    | Low      |

| Noise PSD at fCLK              | Low   | Low    | Low       | High     |

| Noise PSD at 2fCLK             | Low   | Low    | Medium    | Medium   |

<sup>\*</sup> Requires ping-pong architecture to provide continuous operation

## 2.5 Comparison of the Techniques

This chapter has discussed three offset cancellation techniques: offset trimming, auto-zeroing, and chopping. Table 2-1 compares the three techniques with a basic CMOS op-amp that does not use an offset cancellation technique. Offset trimming only corrects offset at post-production test, and thus still results in high offset drift and 1/f noise.

Auto-zeroing and chopping both correct offset periodically, and therefore can achieve both very low offset that is stable over temperature, as well as very low 1/f noise. However, auto-zeroing introduces dead time, during which the offset is sampled and the op-amp is unavailable for signal amplification. To solve this problem, two input channels with ping-pong operation are required. Moreover, the offset sampling introduces high frequency noise folding, and thus results in higher in-band noise PSD than the initial thermal noise floor.

On the other hand, chopping is a frequency modulation technique that results in continuous-time amplification without requiring an extra input channel. The resulting in-band noise PSD is only slightly higher than the initial thermal noise floor. Therefore, this technique can achieve a low offset and low noise PSD op-amp in a more power efficient manner than auto-zeroing. The next chapter discusses the many techniques reported in recent years to reduce the residual offset and up-modulated ripple of chopper op-amps and instrumentation amplifiers.

### 2.6 References

- [1] J. H. Atherton and H. T. Simmonds, "An Offset Reduction Technique for Use with CMOS Integrated Comparators and Amplifiers", *IEEE J. Solid-State Circuits*, vol. 27, no. 8, pp. 1168-1175, Aug. 1992.

- [2] Analog Devices, "MT-037 Tutorial, Op Amp Input Offset Voltage", Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/media/en/training-seminars/tutorials/MT-037.pdf">http://www.analog.com/media/en/training-seminars/tutorials/MT-037.pdf</a>.

- [3] M. Bolatkale, M. A. P. Pertijs, W. J. Kindt, J. H. Huijsing, and K. A. A. Makinwa, "A Single-Temperature Trimming Technique for MOS-Input Operational Amplifiers Achieving 0.33 μV/°C Offset Drift", *IEEE J. Solid-State Circuits*, vol. 46, no. 9, pp. 2099-2017, Sept. 2011.

- [4] Analog Devices, "ADA4661-2 Datasheet", July 2013, Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/media/en/technical-documentation/data-sheets/ADA4661-2.pdf">http://www.analog.com/media/en/technical-documentation/data-sheets/ADA4661-2.pdf</a>.

- [5] Texas Instruments, "OPA192 Data Sheet", Dec. 2013, Accessed on March 2018, [Online] Available: <a href="http://www.ti.com/lit/ds/symlink/opa192.pdf">http://www.ti.com/lit/ds/symlink/opa192.pdf</a>>.

- [6] Analog Devices, "ADA4077 Datasheet", Oct. 2012, Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/media/en/technical-documentation/data-sheets/ADA4077-1\_4077-2\_4077-4.pdf">http://www.analog.com/media/en/technical-documentation/data-sheets/ADA4077-1\_4077-2\_4077-4.pdf</a>.

- [7] B. Razavi, Design of Analog CMOS Integrated Circuits, McGraw Hill, 2001.

- [8] C. C. Enz and G. C. Temes, "Circuit Techniques for Reducing the Effect of Op-Amp Imperfections: Autozeroing, Correlated Double Sampling, and Chopper Stabilization", *Proc. of IEEE*, vol. 84, no. 9, pp. 1320-1324, Sept. 1996.

- [9] R. Wu, J. H. Huijsing, and K. A. A. Makinwa, *Precision Instrumentation Amplifiers and Read-Out Integrated Circuits*, Springer, New York, 2013.

- [10] M. Pertijs and W. J. Kindt, "A 140 dB-CMRR current-feedback instrumentation amplifier employing ping-pong auto-zeroing and chopping", *IEEE J. Solid-State Circuits*, vol. 45, no. 10, pp. 2044-2056, Oct. 2010.

- [11] I. E. Opris and G. T. A. Kavacs, "A Rail-to-Rail Ping-Pong Op-Amp", *IEEE J. Solid-State Circuits*, vol. 31, no. 9, pp. 1320-1324, Sept. 1996.

- [12] J. F. Witte, K. A. A. Makinwa, and J. H. Huijsing, *Dynamic Offset Compensated CMOS Amplifiers*, Springer, New York, 2010.

- [13] J. Caldwell, "Intrinsic Noise Sources in Chopper Amplifiers", Accessed on March 2018, [Online] Available: <a href="http://e2e.ti.com/cfs-file.ashx/\_key/telligent-evolution-components-attachments/00-14-01-00-00-70-21-03/Chopper-Noise.pdf">http://e2e.ti.com/cfs-file.ashx/\_key/telligent-evolution-components-attachments/00-14-01-00-00-70-21-03/Chopper-Noise.pdf</a>.

- [14] STMicroelectronics, "Input bias current of a chopper amplifier", Oct. 2014, Accessed on March 2018, [Online] Available: <a href="http://www.st.com/st-web-ui/static/active/en/resource/technical/document/application">http://www.st.com/st-web-ui/static/active/en/resource/technical/document/application</a> note/DM00133793.pdf>

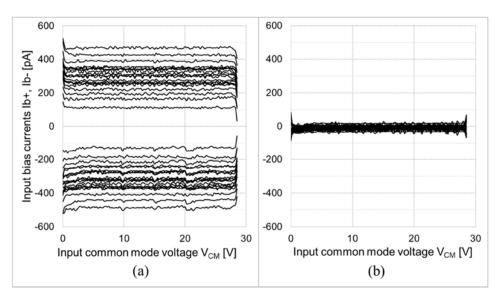

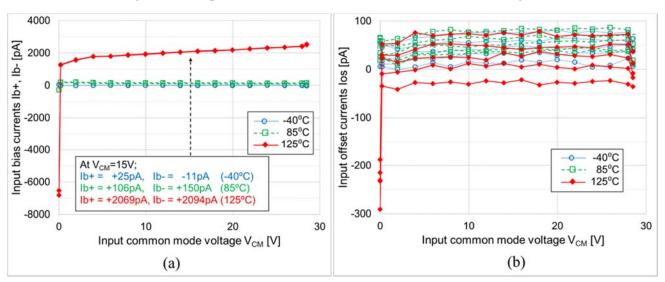

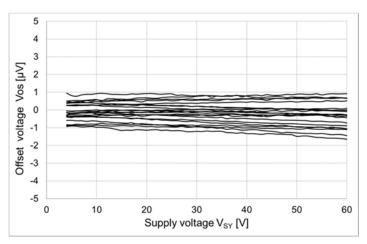

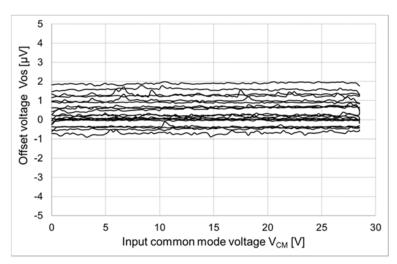

- [15] V. Wong and Y. Kusuda, "Zero-Drift Amplifiers: Now Easy to Use in High Precision Circuits", July 2015, Accessed on March 2018, [Online] Available: <a href="http://www.analog.com/library/analogdialogue/archives/49-07/Zero-Drift\_Amplifiers.pdf">http://www.analog.com/library/analogdialogue/archives/49-07/Zero-Drift\_Amplifiers.pdf</a>>.