# Thermal-Aware Design and Runtime Management of 3D Stacked Multiprocessors SUMEET KUMAR

Thermal-Aware Design and Runtime Management of 3D Stacked Multiprocessors

# Thermal-Aware Design and Runtime Management of 3D Stacked Multiprocessors

### Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof. ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op dinsdag 15 september 2015 om 12:30 uur door

### Sumeet Susheel KUMAR

Master of Science in Microelectronics, Technische Universiteit Delft

geboren te Kuwait City, Kuwait

This dissertation has been approved by: Promotor: Prof. dr. ir. A.-J. van der Veen

Copromotor: dr. ir. T.G.R.M. van Leuken

Composition of the doctoral committee:

| Rector Magnificus,             | voorzitter                                |

|--------------------------------|-------------------------------------------|

| Prof. dr. ir. AJ. van der Veen | Technische Universiteit Delft, promotor   |

| dr. ir. T.G.R.M. van Leuken    | Technische Universiteit Delft, copromotor |

| dr. A. Zjajo                   | Technische Universiteit Delft             |

#### Independent members:

| Prof. dr. J. Pineda de Gyvez | Technische Universiteit Eindhoven          |

|------------------------------|--------------------------------------------|

| Prof. dr. F. Pêcheux         | Laboratoire d'Informatique de Paris-6      |

| Prof. dr. D. Stroobandt      | Universiteit Ghent                         |

| Prof. dr. K.L.M. Bertels     | Technische Universitieit Delft             |

| Prof. dr. ir. G.J.T. Leus    | Technische Universitieit Delft, reservelid |

The research described in this dissertation was performed in the Circuits and Systems Group, Faculty of Electrical Engineering, Computer Science and Mathematics, of Delft University of Technology, Delft, The Netherlands. This work was partially supported by the CATRENE programme under the Computing Fabric for High Performance Applications (COBRA) project CA104.

ISBN 978-94-6186-513-7

Copyright © 2015 by Sumeet Susheel Kumar [sumeetskumar@ieee.org]

Printed by: Gildeprint Drukkerijen - The Netherlands

# Summary

The sustained increase in computational performance demanded by next-generation applications drives the increasing core counts of modern multiprocessor systems. However, in the dark silicon era, the performance levels and integration density of such systems is limited by thermal constraints of their physical package. These constraints are more severe in the case of *three-dimensional (3D)* integrated systems, as a consequence of the complex thermal characteristics exhibited by stacked silicon dies. This dissertation investigates the development of efficient, thermal-aware multiprocessor architectures, and presents methodologies to enable the simultaneous exploration of their thermal and functional behaviour.

Chapter 2 examines the efficiency of multiprocessor architectures from the perspective of the the memory hierarchy, and presents techniques that focus on the effective management and transfer of on-chip data in order to minimize the time spent waiting on memory accesses. In the case of shared-memory multiprocessors, this is achieved through the proposed *Persistence Selective Caching (PSC)* and *CacheBalancer* schemes that influence what data is stored in on-chip caches, where it is stored, and for how long. This enables the memory hierarchy to adapt to changing execution behaviour, balance resource utilization, and most importantly, reduce the average latency and energy per memory access. Further to this, Chapter 2 presents the *Pronto* system, which enables efficient data transfers in message-passing multiprocessors by minimizing the role of the processing element in the management of transfers. Pronto effectively decreases the overheads incurred in setting up and managing data transfers, thereby yielding shorter communication latencies. In addition, it also simplifies the semantics of data movement by abstracting implementation details of communications from the programmer, thus enabling transfers to be specified entirely at the task level.

The issue of thermal-aware design for 3D *Integrated Circuits (IC)* using *Nagata's* equation – a mathematical representation of the dark silicon problem – is investigated in Chapter 3. Significantly, the chapter explores the thermal design space of 3D ICs in terms of this equation, and proposes a high-level flow to characterize the specific

influence of individual design parameters on thermal behaviour of die stacks. The results of this exploration advance the state-of-the-art by providing new insights into the critical role of power density, thermal conductivity and stack construction in the formation of hotspots in 3D ICs. Building on these insights, the *Ctherm* framework is proposed for the thermal-aware design of *multiprocessor systems-on-chip (MPSoC)*. Ctherm enables the concurrent evaluation of thermal and functional performance of MPSoCs using automatically generated fine-grained area, latency and energy models for system components, and facilitates the exploration of thermal behaviour early in the system design flow. The efficacy of the framework is demonstrated using a number of practical design cases ranging from floorplanning and temperature sensor placement to application tuning. Together, the characterization and the Ctherm framework further our understanding of the thermal behaviour of die stacks, and provide a practical template for the realization of thermal-aware electronic design automation tooling for 3D ICs.

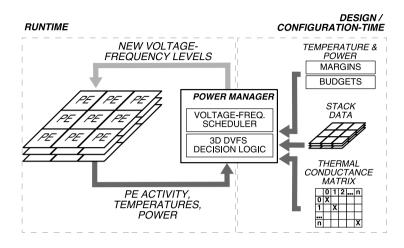

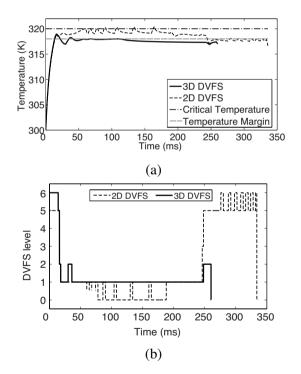

The management of thermal issues that arise in 3D MPSoCs at runtime is examined in Chapter 4. Temperature control is typically exercised by means of *Dynamic* Thermal Management (DTM) which continuously adapt the activity and power dissipation of system components. A significant disadvantage of state-of-the-art DTMs lies in their inability to account for the non-uniform thermal behaviour of die stacks, leading to the ineffective management of temperatures and in degraded system performance. In Chapter 4, a novel 3D Dynamic Voltage Frequency Scaling (DVFS) scheme is proposed that takes these non-uniformities into account within its power management algorithm, effectively maintains operating temperatures within a safe range, and maximizes system performance within the available thermal margins at individual processing elements. Furthermore, the chapter also presents an adaptive routing strategy to decrease the magnitude of thermal gradients in network-on-chip based 3D architectures, by directing traffic along paths of low temperature. The proposed Immediate Neighbourhood Temperature (INT) adaptive routing scheme actively steers interconnect traffic away from regions with thermal hotspots based only on temperature information available in the immediate neighbourhood, relying on the heat transfer characteristics of 3D ICs to avoid the need for a global temperature monitoring network. The consequent spreading of interconnect activity over multiple paths results in balanced thermal profiles, and decreased operating temperatures across the system.

Over the course of these chapters, this dissertation explores the critical issues impeding the realization of thermal-aware 3D stacked multiprocessors, and details a multifaceted approach towards addressing the challenges of dark silicon.

For my mother and father,

You have no idea how hard I've looked for a gift to bring you. Nothing seemed right. What's the point of bringing gold to the gold mine, or water to the ocean. Everything I came up with was like taking spices to the Orient. It's no good giving my heart and my soul because you already have these. So I've brought you a mirror. Look at yourself and remember me.

Rumi

# Contents

| 1 | Intr | oductio  | n           |                                                     | 1  |

|---|------|----------|-------------|-----------------------------------------------------|----|

|   | 1.1  | Motiva   | ation       |                                                     | 4  |

|   |      | 1.1.1    | Architec    | tural Efficiency                                    | 4  |

|   |      | 1.1.2    |             | Constraints                                         | 5  |

|   |      | 1.1.3    | Tempera     | ture Management                                     | 6  |

|   | 1.2  | Resear   | ch Questio  | ons                                                 | 6  |

|   | 1.3  | Disser   | tation Out  | line                                                | 7  |

|   | 1.4  | Public   | ation List  |                                                     | 9  |

| 2 | Arc  | hitectur | al Techni   | ques for Efficient On-Chip Data Management          | 11 |

|   | 2.1  | Naga /   | Architectur | re Overview                                         | 13 |

|   | 2.2  | Low-o    | verhead M   | lessage Passing with Pronto                         | 15 |

|   |      | 2.2.1    | Related V   | Work and Motivation                                 | 16 |

|   |      | 2.2.2    | The Pror    | to Message Passing System                           | 17 |

|   |      |          | 2.2.2.1     | Pronto API                                          | 17 |

|   |      |          | 2.2.2.2     | Hardware Architecture                               | 19 |

|   |      | 2.2.3    | Experim     | ental Evaluation                                    | 22 |

|   |      |          | 2.2.3.1     | End-to-end Message Transfer Latency                 | 24 |

|   |      |          | 2.2.3.2     | Communication Overheads                             | 25 |

|   |      |          | 2.2.3.3     | Application performance with Pronto                 | 26 |

|   |      |          | 2.2.3.4     | Impact of input dataset size                        | 28 |

|   |      |          | 2.2.3.5     | Impact of extraneous interconnect traffic on output |    |

|   |      |          |             | jitter                                              | 28 |

|   |      | 2.2.4    | Conclusi    | ons                                                 | 31 |

|   | 2.3  | Impro    | ving Data   | Cache Performance using Persistence Selective       |    |

|   |      | Cachir   | ng          |                                                     | 32 |

|   |      | 2.3.1    | Related V   | Work                                                | 32 |

|   |     | 2.3.2   | Persistence Selective Caching                          |

|---|-----|---------|--------------------------------------------------------|

|   |     |         | 2.3.2.1 Selective Caching Criteria                     |

|   |     |         | 2.3.2.2 Significance of Persistence Threshold          |

|   |     |         | 2.3.2.3 Limitations                                    |

|   |     | 2.3.3   | Evaluation                                             |

|   |     |         | 2.3.3.1 AMAT and Energy                                |

|   |     |         | 2.3.3.2 Overheads and Implementation Cost 41           |

|   |     | 2.3.4   | Conclusions                                            |

|   | 2.4 | Runtin  | ne Management of Shared Caches using CacheBalancer 42  |

|   |     | 2.4.1   | CacheBalancer                                          |

|   |     |         | 2.4.1.1 Access Rate based Memory Allocation 43         |

|   |     |         | 2.4.1.2 Pain-driven Task Mapping                       |

|   |     | 2.4.2   | Evaluation                                             |

|   |     | 2.4.3   | Conclusions                                            |

|   |     |         |                                                        |

| 3 | _   |         | he Thermal Design Space in 3D Integrated Circuits 55   |

|   | 3.1 | Signifi | cance of parameters                                    |

|   | 3.2 |         | al Characterization of Die Stacks                      |

|   |     | 3.2.1   | Experimental Setup and Validation 60                   |

|   |     | 3.2.2   | Characterization                                       |

|   |     |         | 3.2.2.1 Thermal Conductivity $(\kappa_{eff})$ 61       |

|   |     |         | 3.2.2.2 Die Thickness and Stack Depth $(l_{x,y,z})$ 64 |

|   |     |         | 3.2.2.3 Power Density $(Q/A)$                          |

|   |     | 3.2.3   | Conclusions                                            |

|   | 3.3 | Vertica | ll Interconnect                                        |

|   |     | 3.3.1   | Electrical Performance                                 |

|   |     | 3.3.2   | Area                                                   |

|   |     | 3.3.3   | Thermal Performance70                                  |

|   |     | 3.3.4   | Conclusions                                            |

|   | 3.4 | Therm   | al-Aware Design Space Exploration                      |

|   |     | 3.4.1   | Ctherm Framework                                       |

|   |     |         | 3.4.1.1 Physical Model Generation                      |

|   |     |         | 3.4.1.2 Thermal-Functional Co-simulation Platform 79   |

|   |     | 3.4.2   | Evaluation                                             |

|   |     |         | 3.4.2.1 Validation, Accuracy and Simulation Speed 81   |

|   |     |         | 3.4.2.2 Design Cases                                   |

|   |     | 3.4.3   | Additional Media                                       |

|   |     | 3.4.4   | Conclusions                                            |

| 4   | Run    | time Tei | mperatur    | e and Power Management for 3D Multiprocessors  | 93  |

|-----|--------|----------|-------------|------------------------------------------------|-----|

|     | 4.1    | Temper   | rature-Awa  | are DVFS for Stacked Die Architectures         | 95  |

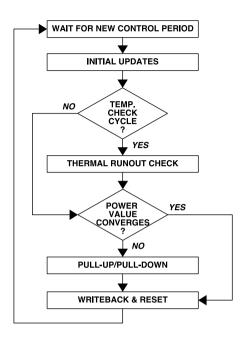

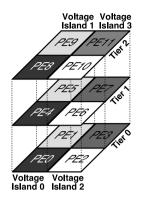

|     |        | 4.1.1    | 3D DVFS     | 5                                              | 96  |

|     |        |          | 4.1.1.1     | Initial Updates                                | 98  |

|     |        |          | 4.1.1.2     | Thermal Runout                                 | 98  |

|     |        |          | 4.1.1.3     | Convergence Check                              | 99  |

|     |        |          | 4.1.1.4     | Pull Up/Pull Down                              | 100 |

|     |        |          | 4.1.1.5     | Write-Back and Reset:                          | 100 |

|     |        | 4.1.2    | Implemen    | ntation Considerations                         | 100 |

|     |        | 4.1.3    | Evaluatio   | n                                              | 101 |

|     |        |          | 4.1.3.1     | Per-core Granularity                           | 102 |

|     |        |          | 4.1.3.2     | Island Granularity                             | 104 |

|     |        | 4.1.4    | Conclusio   | ons                                            | 107 |

|     | 4.2    | Temper   | rature-Aw   | are Adaptive Routing for Dynamically-Throttled |     |

|     |        | 3D Net   | works-on-   | Chip                                           | 108 |

|     |        | 4.2.1    | Backgrou    | ınd                                            | 109 |

|     |        | 4.2.2    | Immedia     | te Neighbourhood Temperature (INT) Adaptive    |     |

|     |        |          | Routing     |                                                | 110 |

|     |        |          | 4.2.2.1     | Temperature Monitoring                         | 111 |

|     |        |          | 4.2.2.2     | Temperature Channel Considerations             | 111 |

|     |        |          | 4.2.2.3     | Thermal-Aware Dynamic Throttling               | 112 |

|     |        |          | 4.2.2.4     | Temperature-Aware Adaptive Routing Algorithm   | 113 |

|     |        | 4.2.3    | Evaluatio   | n                                              | 114 |

|     |        |          | 4.2.3.1     | Characterization of Throttling                 | 114 |

|     |        |          | 4.2.3.2     | INT Evaluation                                 | 115 |

|     |        | 4.2.4    | Conclusio   | ons                                            | 119 |

| 5   | Con    | clusions |             |                                                | 123 |

|     | Addi   | tional C | ontribution | ns                                             | 128 |

|     | Futu   | re work  |             |                                                | 129 |

| Ac  | ronyr  | ns       |             |                                                | 133 |

| No  | tatior | 1        |             |                                                | 137 |

| Bił | oliogr | aphy     |             |                                                | 141 |

| Sa  | menva  | atting   |             |                                                | 155 |

vii

| Acknowledgements | 159 |

|------------------|-----|

| Curriculum Vitae | 165 |

| Propositions     | 167 |

| Stellingen       | 171 |

# Introduction

The increasing computational requirements of next-generation applications is an important driver for the development of high-performance microprocessors. Desktop processors from the early 2000s supported performance in the range of 100 *billion operations per second (BOPS)*, and traditionally utilized increasingly higher clock frequencies to scale performance. Consequently, these devices were rated with a *thermal design power (TDP)* of over 100W [1], necessitating the use of extravagant heatsinks and exotic methods for cooling [2]. Small form factor computing devices such as mobile phones and ultrabooks on the other hand impose extremely restrictive TDPs. For instance, in a modern smartphone, the digital workload consisting of control, data and signal processing aggregates to over 100 BOPS, however, with a power budget of only 1W [1]. Furthermore, even though the performance requirements of this workload increase by two orders of magnitude every five years, the power budget grows only minimally.

Chip multiprocessors  $(CMP)^1$  are an effective means of realizing such high computational performance. CMPs integrate a large number of simple processing elements (PE) that dissipate a relatively small amount of power, into a single integrated circuit (IC) package [3]. Workloads are divided into tasks that execute concurrently on PEs, yielding performance improvements that surpass conventional frequency upscaling. CMPs are thus based on the rationale that high performance can be realized better through computing in strength rather than computing in speed, with superior power efficiency. The viability of the concept is evident from the number of production ready CMPs in the market. Offerings from Ambric [4–7], PicoChip [8, 9], Tilera [10–12], Intellasys [13, 14] and NEC [15] integrate anywhere between 40 and 336 processing

<sup>&</sup>lt;sup>1</sup>Also referred to simply as multiprocessors

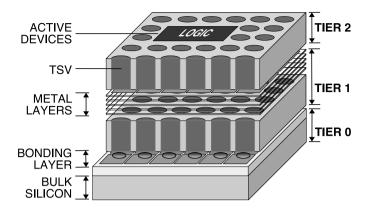

Figure 1.1. Cut away of a die stack illustrating *Through Silicon Via (TSV)* based vertical interconnections

elements within a single chip. The application domains for these processors are increasingly in the computing, multimedia and signal processing areas, involving large data sets with high throughput requirements. For instance, the 248-core PicoChip PC203 is primarily intended as a baseband processor for wireless networks. Similarly, the 128-core NEC IMAPCAR serves as an image recognition processor at the heart of automotive collision avoidance systems [16]. The physical constraints imposed by their operating environments, in both cases, limit TDP to under 3*W*.

Although the addition of PEs to multiprocessor arrays improves system performance, technology-related challenges limit the extent to which such arrays can be scaled up. The first challenge stems from the increase in die size that accompanies the integration of additional PEs. As yield decreases with increasing die size [17, 18], performance gains are obtained at the cost of manufacturability. The second, yet equally important challenge arises due to the limited *input/output (I/O)* bandwidth of pin-constrained multiprocessor and memory packages [19], which results in the performance improvements from the additional PEs being diminished due to memory and I/O contention [20].

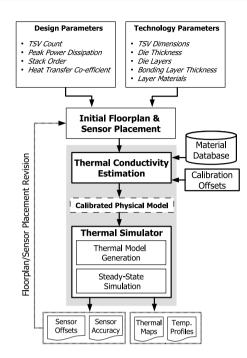

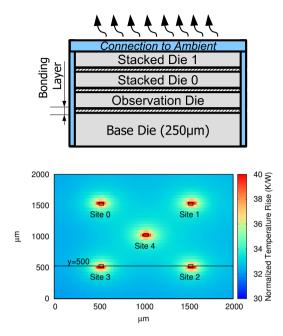

*Three-dimensional (3D)* integration is a promising solution to these limitations, facilitating the realization of large multiprocessors in the form of a stack of silicon dies [21–23]. The stacked dies are interconnected by means of vertical metal wires known as *Through Silicon Vias (TSV)*, as illustrated in Figure 1.1. 3D integration essentially reduces the area footprint of multiprocessors by converting planar area into stack height, effectively reducing the size of individual dies, and thus improving manufacturing cost. It further facilitates the integration of dies varying in function-

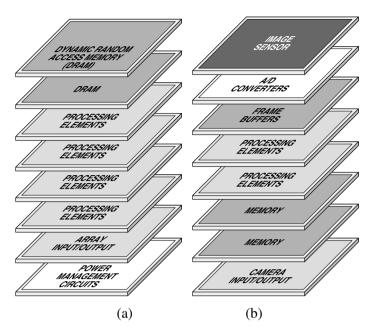

Figure 1.2. Illustration of 3D integrated systems. (a) Multiprocessor with stacked DRAM, I/Os and power management circuits (b) Integrated computer vision system with stacked image sensor, data conversion circuitry and processing elements.

ality and process technology node into a single IC package [20, 24]. Consequently, components such as the *Random Access Memory (RAM)* can be integrated within the stack [25–28], and made accessible to PEs through a high-bandwidth wide I/O interface [19], allowing system performance to be scaled with PE counts. Potentially, 3D could also be used to enable fully integrated systems incorporating sensors, data converters and PEs, as illustrated in Figure 1.2.

Current application trends indicate that future workloads will require computational performance in the range of 1 *trillion operations per second (TOPS)* [1], necessitating the use of *many-core* CMPs. At such large scales, however, architectural inefficiencies have a significant impact on both performance, as well as dependability. In addition, despite the benefits of 3D integration, die stacks exhibit complex thermal behaviour that can be detrimental to system performance.

### 1.1 Motivation

The challenges accompanying the efficient design and dependable operation of large scale CMPs can be grouped into three categories - architectural efficiency, thermal constraints, and runtime temperature management.

#### 1.1.1 Architectural Efficiency

Multiprocessor architectures can be broadly classified based on their communication model into two types - shared-memory and message-passing architectures. Shared-memory multiprocessors use a global memory space that is shared amongst all PEs. Data transfer between tasks executing on PEs is implicit, and is managed in hardware by the underlying memory hierarchy consisting of multiple on-chip caches. However, synchronization and data sharing must be explicitly managed within shared-memory architectures, and this increases complexity in applications with significant intertask communication. In message-passing based dataflow architectures [29] on the other hand, applications are described as a set of communicating tasks, with well defined input and output dependencies. Communicating tasks run asynchronously on separate PEs and exchange data between their local memories. Tasks fire once their inputs become valid, and are thus implicitly synchronized. In comparison with shared-memory, message-passing incurs a higher overhead since data transfers must be explicitly managed due to the absence of a global address space.

In both message-passing as well as shared-memory architectures, execution time refers to the amount of time required to complete execution of all constituent tasks within a given application program. For a task executing on a PE, the execution time  $(t_{task})$  is given as:

$$t_{task} = t_{instructions} + t_{memory} \tag{1.1}$$

where  $t_{instructions}$  represents the fraction of the task's execution time spent in arithmetic, logic and control instructions, and  $t_{memory}$  the time spent performing memory load-stores.  $t_{instructions}$  is largely a function of the code's complexity and size, as well as the PE's microarchitecture - specifically, factors such as instruction latency, branch predictor accuracy and issue-width [30]. On the other hand,  $t_{memory}$  is influenced by the management and transfer of on-chip data, and includes the time spent waiting for data to be fetched from remote memories, or lower levels of the memory hierarchy. The access latency of the memories, layout of data across memory banks, and the overheads incurred in managing transfers between them together contribute to  $t_{memory}$ , and influence the effective performance of the system. The efficient management and

transfer of on-chip data is therefore essential to realizing high-performance many core CMPs.

#### 1.1.2 Thermal Constraints

Power dissipation by components in ICs results in the generation of heat, which causes operating temperatures to rise. The generated heat is therefore evacuated from the system by means of a heatsink so as to maintain temperatures within the safe operating range, and prevent device failure [31]. Nagata [32] determined that the maximum allowable power dissipation in an IC is constrained by its physical construction, and the thermal efficiency of its cooling interfaces. Their relationship is given as:

$$\frac{\alpha N_G E}{t_{pd}} \le g \cdot \Delta T \tag{1.2}$$

where  $\Delta T$  is the maximum permissible difference between on-chip and ambient temperatures, and represents the available temperature margin at zero power dissipation. The relation thus indicates that for a planar IC, the activity rate ( $\alpha$ ), energy dissipation (E), clock period ( $t_{pd}$ ) and number ( $N_G$ ) of gates that can be integrated into a single chip is limited by the thermal conductance (g) of its interface with the ambience, as well as the ambient temperature. This limitation best describes the phenomenon termed by the semiconductor industry as *Dark Silicon*, a reference to the large sections of modern ICs powered down due to thermal considerations. Essentially, Nagata's equation dictates that to improve integration densities, components must either be utilized less, or must dissipate a smaller amount of power ( $E/t_{pd}$ ). Alternatively, either conductance to ambient temperature must be decreased. The latter serves to increase the magnitude of available temperature margin  $\Delta T$ .

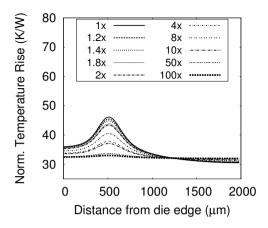

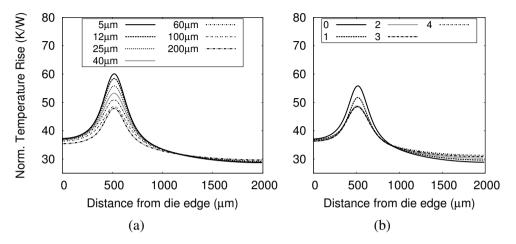

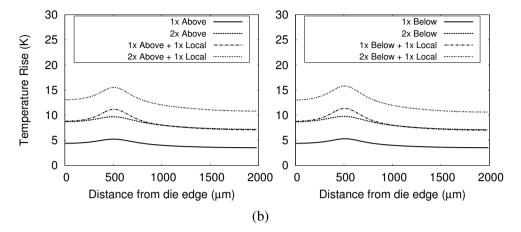

The issue of dark silicon is further complicated in the case of die stacks on account of their distinct thermal behaviour as compared to planar ICs. In 3D ICs, thermal conductance g is a function of the physical construction of the die stack, and the TSV-based vertical interconnect. The value of g drops as distance from the heatsink increases and as a result, the thermal constraints imposed by (1.2) vary throughout the die stack. System design approaches that ignore this effect run the risk of yielding thermally inefficient designs that inadequately utilize available temperature margins. In order to maximize the performance of a stacked die architecture, it is essential that the unique thermal characteristics of 3D ICs be taken into account during early stages of system design. A significant obstacle to achieving this lies in our relatively shallow understanding of the thermal behaviour of die stacks, and the influence of the design parameters established by Nagata's equation on operating temperatures. The realization of a thermal-aware design flow for 3D architectures is consequently predicated on the characterization of the thermal design space for die stacks.

#### 1.1.3 Temperature Management

The operating temperature at any point in the IC is dependent on the amount of heat generated within the system, and the rate at which it is conducted away towards heat sinking surfaces. The power dissipation of components is determined by  $\alpha$  and E, which vary depending on the nature of the workload being executed on the multiprocessor, and  $t_{pd}$ . When  $\alpha$  is balanced, all PEs dissipate a similar amount of power, and produce a uniform power density that results in heat generation spread across the complete area of the IC. However, imbalances in  $\alpha$  can lead to a spike in spatial power density and cause the formation of thermal hotspots. *Dynamic Thermal Management (DTM)* strategies are typically invoked in such circumstances to arrest rising temperatures and maintain them within safe margins. Such an action, on the other hand, imposes a performance penalty. The unique thermal characteristics of 3D ICs further complicate this behaviour by producing non-uniform temperature margins at different tiers of the stack. In order to uniformly extract the full performance of PEs in a multiprocessor, the DTM strategy must take into account the thermal characteristics of 3D ICs and the non-uniformities in temperature margins.

Thermal gradients are another undesirable consequence of unbalanced activity in multiprocessors, and result in the accelerated degradation of devices [31][33]. Reducing the magnitude of these gradients requires temperature awareness within the architecture, and mechanisms to dynamically steer system activity away from regions of high temperature.

# 1.2 Research Questions

The presented motivations can be condensed into the four research questions that are addressed by this dissertation.

- 1. How can the performance and efficiency of on-chip memory operations in multiprocessors be improved?

- 2. How do the physical design parameters in Nagata's equation affect the thermal behavior of 3D Integrated Circuits?

- 3. How can the knowledge of thermal behaviour be effectively leveraged in the design of 3D stacked multiprocessors?

- 4. How can the architecture and operating parameters be efficiently adapted at runtime to mitigate the severity of thermal issues, and improve execution performance?

Together, these questions encapsulate the key challenges and issues impeding the design and efficient operation of 3D stacked multiprocessor systems.

# 1.3 Dissertation Outline

This dissertation presents architectural techniques to enable the realization of efficient, high-performance multiprocessors, and facilitate runtime temperature management to ensure their dependable operation. Most importantly, it provides new insights into the complex thermal behaviour of 3D ICs, and illustrates how the design space of stacked die architectures can be effectively explored in order to maximize performance in the dark silicon era. This dissertation consists of two main themes, architecture and temperature, examined in light of the research questions outlined in the previous section.

**Chapter 2** presents techniques that aim at minimizing the amount of time spent by PEs in waiting on memory accesses  $(t_{memory})$ , as well as decreasing the energy dissipated within the memory hierarchy, through the efficient management of on-chip data. These include:

- *Pronto* a message-passing system that decreases the overheads for data transfers between communicating tasks in dataflow multiprocessors, yielding shorter transfer latencies than competing schemes.

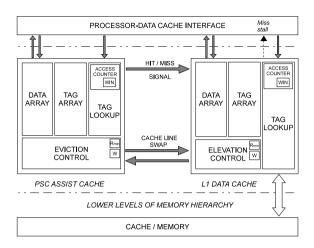

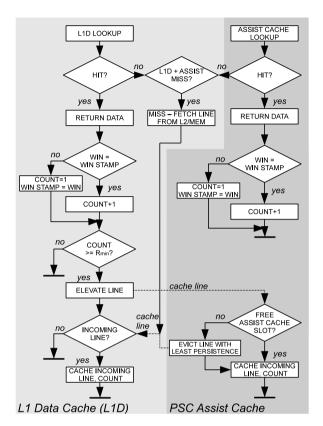

- *Persistence Selective Caching (PSC)* a selective caching scheme for first level data caches. PSC minimizes  $t_{memory}$  by decreasing the average latency for memory accesses, and improves efficiency by reducing the energy dissipated per access.

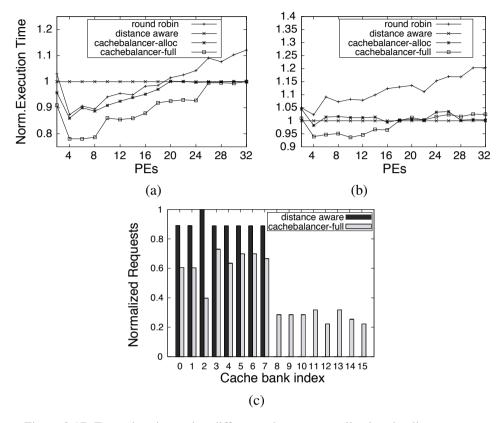

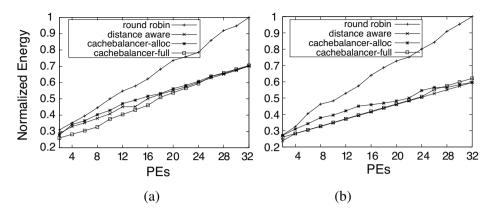

- *CacheBalancer* a runtime resource management scheme that balances the utilization of shared caches in multiprocessors, reducing the latency of accesses to dynamically allocated memory, as well as the system's energy density.

**Chapter 3** investigates the complex thermal characteristics of die stacks in terms of the design space described in (1.2). A high-level exploration flow is presented to examine the influence of stack composition, physical construction, power density and design of the vertical interconnect on the thermal behaviour of 3D ICs. This exploration provides new insights into the formation of hotspots in die stacks, and the role of individual design parameters in their mitigation.

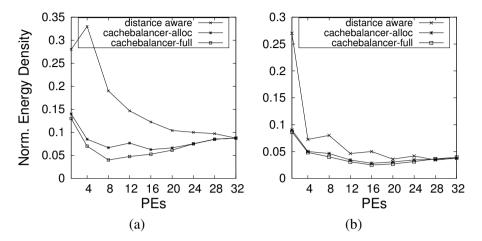

In order to apply these insights, Chapter 3 presents the *Ctherm* framework for the thermal-aware design of *multiprocessor systems-on-chip (MPSoC)*. Ctherm facilitates the concurrent evaluation of the thermal and functional performance of MPSoCs, enabling the holistic exploration of candidate design options. The framework automates the generation of fine-grained area, latency and energy models for components in order to accurately model power density, and hence thermal behaviour. Chapter 3 highlights the impact of modelling component internals on the accuracy of thermal estimates, and illustrates the potential of thermal-aware approaches across the design flow.

*Chapter 4* proposes DTM strategies for runtime temperature management in 3D MPSoCs. These include:

- *Temperature-Aware Dynamic Voltage Frequency Scaling (DVFS)* a runtime power manager that takes into account the non-uniformities in temperature margins within die stacks when scheduling voltage frequency levels for processing elements in the 3D MPSoC. The proposed strategy maximizes execution performance within the non-uniform thermal constraints prevalent in die stacks, and outperforms the conventional DVFS approach.

- *Immediate Neighbourhood Temperature (INT)* Adaptive Routing an adaptive routing strategy that balances thermal gradients and decreases hotspot magnitudes in 3D *networks on chip (NoC)* by actively steering interconnect activity away from regions of high temperature. The high degree of thermal coupling between stacked dies eliminates the need for system-wide propagation of temperature information, and enables adaptive routing decisions to be driven by a simple temperature monitoring network.

Together, the two strategies alleviate the severity of thermal issues in 3D MPSoCs, and maximize the performance of stacked-die multiprocessors within available temperature margins at runtime.

# 1.4 Publication List

The contributions of this dissertation have been disseminated through a number of refereed conference, journal and book publications, in addition to poster presentations and live demonstrations. Individual chapters include at the end a listing of their relevant publications. A comprehensive list of all the publications arising out of this dissertation is provided here as a general overview.

#### **Book Chapters**

1. S.S. Kumar, A. Zjajo, R. van Leuken, "Exploration of the Thermal Design Space in 3D Integrated Circuits", *Physical Design for 3D Integrated Circuits*, CRC Press, December 2015, *Invited Book Chapter*

#### **Journal Papers**

- 1. S.S. Kumar, A. Zjajo, R. van Leuken, "Immediate Neighbourhood Temperature Adaptive Routing for Dynamically-Throttled 3D Networks-on-Chip" *IEEE Transactions on Circuits and Systems II (TCAS-II), in press*

- S.S. Kumar, M.T.A. Djie, R. van Leuken, "Pronto: A Low Overhead Message Passing System for High Performance Many-Core Processors." *International Journal of Networking and Computing - Special Issue*, vol. 4, no. 2, pp. 307-320, July 2014

- S.S. Kumar, A. Aggarwal, R. Jagtap, A. Zjajo, R. van Leuken, "System Level Methodology for Interconnect Aware and Temperature Constrained Power Management of 3-D MP-SOCs" *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems, vol. 22, no. 7, pp. 1606-1619, July 2014

#### **Conference Papers**

- 1. S.S. Kumar, A. Zjajo, R. van Leuken, "Physical Characterization of Steady-State Temperature Profiles in Three-Dimensional Integrated Circuits" *Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS)*, 2015

- S.S. Kumar, A. Zjajo, R. van Leuken, "Ctherm: An Integrated Framework for Thermal-Functional Co-simulation of Systems-on-Chip" *Proceedings of the IEEE/Euromicro International Conference on Parallel, Distributed and Network-based Processing (PDP)*, pp.674-681, 2015

- 3. J. de Klerk, S.S. Kumar, R. van Leuken, "CacheBalancer: Access Rate and Pain Based Resource Management for Chip Multiprocessors", *Proceedings of the International Symposium on Computing and Networking (CANDAR)*, pp. 453-456, 2014

- 4. S.S. Kumar, R. van Leuken, "Improving data cache performance using Persistence Selective Caching," *Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS)*, pp.1945-1948, 2014

- S.S. Kumar, M.T.A. Djie, R. van Leuken, "Low Overhead Message Passing for High Performance Many-Core Processors," *Proceedings of the International Symposium on Computing and Networking (CANDAR)*, pp. 345-351, 2013

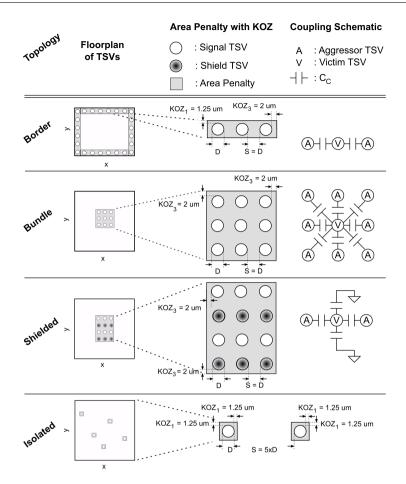

- R. Jagtap, S.S. Kumar, R. van Leuken, "A Methodology for Early Exploration of TSV Placement Topologies in 3D Stacked ICs" *Proceedings of the IEEE/Euromicro Conference on Digital System Design (DSD)*, pp.382-388, 2012

- 7. A. Aggarwal, S.S. Kumar, A. Zjajo, R. van Leuken, "Temperature constrained power management scheme for 3D MPSoC," *Proceedings of the IEEE Workshop on Signal and Power Integrity (SPI)*, pp. 7-10, 2012

#### **Posters and Demonstrators**

- 1. S.S. Kumar, A. Aggarwal, R. Jagtap, A. Zjajo, R. van Leuken, "Interconnect and Thermal Aware 3D Design Space Exploration", Invited Presentation and Poster, *ICT.OPEN*, Eindhoven, The Netherlands, 2013

- S.S. Kumar, R. van Leuken, A. Michos, A. Chahar, J. de Klerk, "Naga High-Performance Array Processor", Poster and Demonstrator, *University Booth – Design Automation and Test in Europe (DATE)*, Grenoble, France, March 2013

# Architectural Techniques for Efficient On-Chip Data Management

The evolution of microprocessors from single-core towards the present day manycore is driven by the performance requirements of next-generation applications. The effective translation of their large PE counts into actual execution performance, however, remains hinged upon the efficiency of their underlying hardware and software architectures.

Reiterating from Chapter 1, the execution time  $(t_{task})$  for a task executing on a PE is given as:

$$t_{task} = t_{instructions} + t_{memory} \tag{2.1}$$

where  $t_{instructions}$  represents the fraction of the task's execution time spent in arithmetic, logic and control instructions, and  $t_{memory}$  the time spent performing memory load-stores. While  $t_{instructions}$  is primarily a function of the PE's microarchitecture,  $t_{memory}$  is influenced by the efficiency of on-chip data management. Specifically, in the case of message-passing architectures,  $t_{memory}$  depends on the efficiency of data transfer between distributed memories, and the efficiency of the memory hierarchy in the case of shared-memory architectures.

In message-passing dataflow architectures, tasks execute concurrently on separate PEs, and communicate in a producer-consumer fashion according to their task graph [29]. Tasks begin execution once their inputs become ready, and upon completion, pass their output data to the next waiting task. Since communication in conventional message-passing architectures [34] is managed explicitly, the latencies for these operations is reflected in the execution time of tasks.

$$t_{task} = (t_{computation} + t_{mp}) + (t_{transfer} + t_{fc})$$

(2.2)

11

Thus, in addition to the time  $t_{computation}$  spent performing computations,  $t_{mp}$  is spent in executing message-passing library functions to manage transfers. Furthermore, although the actual transfer incurs an aggregate latency of  $t_{transfer}$ , an additional overhead  $t_{fc}$  is incurred in synchronizing and implementing flow control between the communicating tasks. The magnitude of  $t_{mp}$  and  $t_{fc}$  together indicate the efficiency of the message-passing implementation, and influence the overheads incurred during data transfers. Reducing these overheads is essential in improving execution performance.

In cache-based shared-memory architectures,  $t_{memory}$  can be represented in terms of *average memory access time (AMAT or*  $t_{AMA}$ ), a metric that indicates the efficiency of the memory hierarchy.

$$t_{task} = t_{instructions} + (M_A \cdot t_{AMA}) \tag{2.3}$$

where

$$t_{AMA} = \mu_{hit} \cdot t_{hit} + \mu_{miss} \cdot t_{miss}$$

(2.4)

$M_A$  refers to the total number of memory accesses made by the application,  $\mu_{hit}$ and  $\mu_{miss}$  are the hit and miss rate of the data cache, with latency  $t_{hit}$  and  $t_{miss}$ respectively. Although this equation holds for both instruction as well as data caches, we focus on the data memory hierarchy alone. *Hit rate* refers to the fraction of memory references for which the requested data is found within the PE's private Level-1 data *cache (L1D)*, while the remaining references constitute misses that necessitate a fetch operation from lower levels of the memory hierarchy. The latency for a reference resulting in a hit  $(t_{hit})$  depends on the configuration of the data cache, and is typically in the range of 1 - 3 clock cycles [35]. The penalty for a miss  $(t_{miss})$ , on the other hand, is much larger, and depends on the cache line size, bandwidth of the interconnect, miss rate of the lower level caches and their miss penalty. In network-on-chip (NoC) based multiprocessors,  $t_{miss}$  is also influenced by the communication distance (hop count) between PEs and the lower level caches, as well as by contention within the interconnect and shared caches. Improving execution performance for cache-based multiprocessors necessitates efficient data management within the system so as to increase hit rate, as well as minimize  $t_{hit}$  and  $t_{miss}$ .

In this chapter, we present three architectural techniques for efficient on-chip data management for both message-passing as well as shared-memory multiprocessors. These include:

1. *Pronto*: A low overhead message-passing system which simplifies the semantics of data movement between communicating tasks by performing buffer management, message synchronization and address translation directly in hardware. This results in transfer latencies upto 30% shorter than state-of-the-art proposals. In terms of (2.2), Pronto reduces  $t_{mp}$  by minimizing the role of the PE in

managing transfers, and  $t_{fc}$  through its use of reservation-based message flow control.

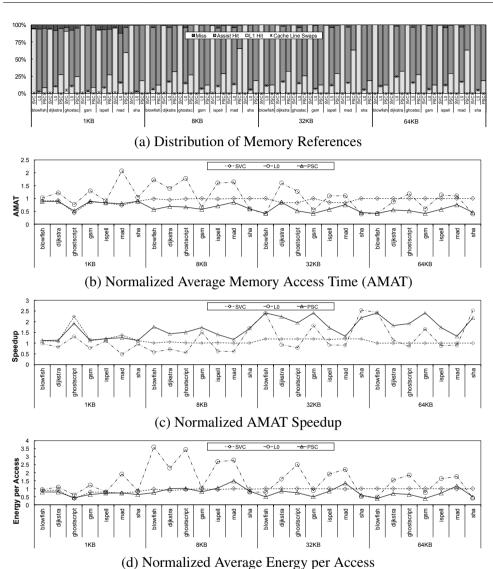

- 2. Persistence Selective Caching (PSC): A selective caching scheme that identifies reusable data at runtime, and services references to them from a low-latency assist cache. This reduces the hit latency  $t_{hit}$  for a majority of references, and yields  $t_{AMA}$  (AMAT) upto 59% lower than conventional data caches. In addition, the small size of the assist, coupled with its high hit rate result in a 75% reduction in average energy per access.

- 3. *CacheBalancer*: A runtime resource management scheme that balances the utilization of shared caches, and minimizes the cost of fetching data from lower levels of the memory hierarchy. CacheBalancer reduces shared cache contention by up to 60% and improves execution performance by 22%.

# 2.1 Naga Architecture Overview

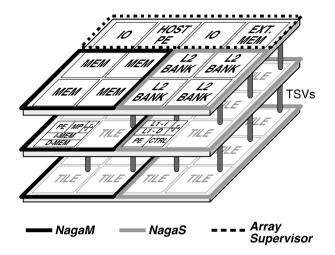

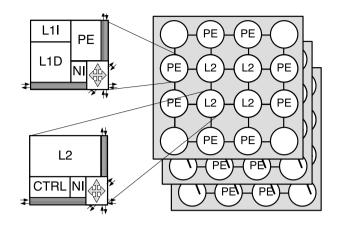

The base platform for this dissertation is a generic many-core processor architecture - Naga - targeted towards the acceleration of applications in the multimedia and computing domains. The distinct characteristics of each of these domains makes them well suited for either shared-memory, or message-passing architectures. While this makes the choice of communication model trivial for applications from either of the two domains, the general purpose nature of Naga necessitates the inclusion of both models in the architecture. The Alewife machine [36] was based on a similar line of reasoning, where Kubiatowicz argued that the advantages of a dual model stemmed from practical design considerations including communication cost, memory access latencies and programmability [37]. While the end goal for such integration is to enable flexibility in the selection of a communication model at the task level, this leads to a number of complications pertaining to the management of the memory address space, and interference between communications of the two models [37]. For the purpose of this dissertation, we avoid the complexities of such fine-grained mixed models, and instead utilize two separate sub-arrays, each implementing either shared-memory or message-passing. Naga thus incorporates two sub-arrays – the message-passing NagaM, and shared-memory NagaS. An illustration of these subarrays is shown in Figure 2.1. Among the architectural techniques presented in this chapter, Pronto uses the NagaM as its base system, while PSC and CacheBalancer use the NagaS.

Figure 2.1. Illustration of the Naga many-core with the shared-memory based NagaS, and message-passing NagaM sub-arrays

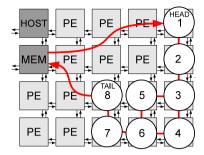

The *NagaM* sub-array is a dataflow accelerator primarily for multimedia and signal processing workloads. It uses  $\rho$ -VEX *Very Long Instruction Word (VLIW)* PEs [38] which provide a performance benefit by exploiting inherent *Instruction Level Parallelism (ILP)* within executing tasks. PEs are placed within tiles containing private data and instruction memories, and a message passing communication interface. At runtime, tasks are spawned and pinned onto PEs according to the task graph, with communicating nodes mapped as close to one another as possible, by a runtime mapper in the host processor. Each task executes asynchronously on a  $\rho$ -VEX PE upon its input data becoming ready, and produces data that similarly triggers the next task in the graph. Fast dual-ported memories (MEM) serve as data I/O for the task graph respectively. Although multiple are shown in Figure 2.1, we assume only a single dual-ported memory in the array for simplicity. A conceptual overview of the NagaM accelerator is provided in Figure 2.2.

*NagaS* on the other hand, is a conventional shared-memory architecture with a two-level cache memory hierarchy, intended for general purpose compute applications. Tiles incorporate a simple *Reduced Instruction Set Computing (RISC)* PE, private instruction and data caches, and a cache controller. In order to maximize cache memory bandwidth, L2 cache banks implement slicing [39] to split the shared address

Figure 2.2. NagaM accelerator with host processor (HOST), and dual ported memory buffer (MEM). Only the Head and Tail tasks of the mapped task graph read from and write to the memory buffer respectively.

space into *slices*, with each mapping to a single bank [40]. NagaS uses the threaded model of execution, allowing applications executing on the host to spawn threads on the array's PEs.

Both NagaM and NagaS use the *R3* NoC interconnect [41]. R3 is a wormhole routed, best-effort, packet-switched NoC that enables stacked-die architectures by facilitating the creation of 3D meshes with *Through Silicon Via (TSV)* based vertical links. The network uses a dimension-ordered *Z-X-Y* routing algorithm that routes interconnect traffic based only on source and destination network addresses. The simplistic architecture of the R3 NoC allows us to evaluate the actual impact of the architectural techniques presented in this chapter without any performance boosts due to interconnect optimizations. Interconnect performance is treated separately in Chapter 4.

### 2.2 Low-overhead Message Passing with Pronto

Existing message-passing implementations rely largely on feature-rich software libraries to manage the transfer of messages between PEs. Thus, in addition to specifying what data must be moved between executing tasks, the programmer must also manage the actual transfer and the corresponding resource reservations. This is detrimental for two reasons. Firstly, it results in communication operations being managed through the PE, thus increasing execution time as well as communication latency. Secondly, it requires the implementation aspects of the underlying message passing communications architecture to be exposed to the programmer, thereby increasing complexity. In this section we present *Pronto*, a low overhead message passing system for many-core processors. Data transfers with Pronto are initiated using a compact set of simple yet highly effective functions that provide a layer of abstraction separating the programmer's view of inter-task communication, and its actual implementation in the underlying hardware architecture. Operations such as address translation, synchronization of transfers and resource management are handled entirely in hardware, simplifying the programming model and minimizing the time spent by PEs in executing non-task related operations.

#### 2.2.1 Related Work and Motivation

A number of many-core processors, both in academia as well as the industry, implement message passing for inter-task communication. For instance, the 430-core *picoArray* uses basic message passing *put* and *get* functions to transfer data between concurrently executing tasks [42]. During compilation, tasks are mapped onto PEs and their communication flows converted into interconnect schedules. Since interconnect arbitration and resource reservations are performed at compile-time, communications do not incur any additional latency penalties related to these operations are runtime. The dataflow based Ambric Massively Parallel Processor Array [5] implements a similar methodology although with a hierarchical interconnect structure. The Intel SCC [43] on the other hand performs all required reservations at runtime rather than statically. Message passing is implemented through a global shared address space accessible through each PE's Message Passing Buffer (MPB) [44]. Tasks executing on PEs share data through virtual connections established by dynamically allocating common memory objects within this space, using functions from the *RCCE* library [45]. Synchronization, ordering of messages and shared accesses must be managed through a programmer-enforced protocol in software.

Apart from these implementations, there also exist individual message passing proposals based on the *MPI* standard [46] often with specific objectives. For instance, *QoS-ocMPI* adds *Quality of Service (QoS)* support into a subset of MPI functions, specifically for NoC based multiprocessors [34], thus allowing critical transfers to occur through a reserved channel, i.e. with *throughput guarantees*. Another proposal, *TMD-MPI* [47], adapts MPI towards supporting message passing between processors across multiple *Field Programmable Gate Arrays (FPGA)*. It essentially abstracts the complexity of inter-chip communication, instead providing the programmer with a homogeneous view of the system. Despite their merits, these proposals are largely based on the original MPI standard, which itself is intended for large distributed memory systems [46]. This objective of the standard reflects in the overheads incurred

due to its use in resource constrained many-core processors. Psota and Agarwal noted this in their proposal *rMPI*, indicating the need for a simple message passing *Application Programming Interface (API)* with a small memory footprint to replace MPI in chip multiprocessors [48].

The drawbacks of heavy software libraries reflect primarily in the latency of data transfers. Proposals without static scheduling and resource reservations often require the MPB and synchronization of data transfers to be explicitly managed by the programmer. These operations are performed through functions of the software library executed on the PE, and result in a non-zero  $t_{mp}$  that is dependent on the operation's latency. Consequently, the latency incurred to setup and manage transfers is higher than if the same were managed in hardware. Therefore, by removing the need for explicit management of the MPB and synchronization of data transfers through function calls, the latency of transfers could be greatly reduced. This would also serve to abstract the implementation of the message passing system from the programmer, and simplify the semantics of inter-task communication.

#### 2.2.2 The Pronto Message Passing System

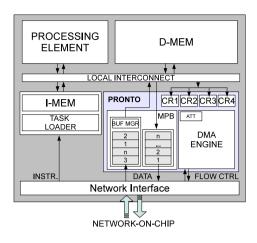

The performance gains of many-cores over sequential implementations are quickly lost as communication overheads approach task execution times [48]. In order to maximize throughput of the many-core array, it is important that message transfer latencies be kept low. By implementing transfer management functions in hardware, PEs are released from having to explicitly oversee data transfers, thereby allowing them to perform useful work instead. Pronto uses a *Direct Memory Access (DMA)* engine based message passing system for data transfers. Data blocks are moved between tile-local memories using hardware managed *Message Passing Buffers (MPB)* over the R3 NoC interconnect. Figure 2.3 illustrates the architecture of a NagaM PE tile with the Pronto message-passing interface.

#### 2.2.2.1 Pronto API

Executing tasks communicate through calls to four simple message passing functions of the Pronto API, as listed in Table 2.1. These functions are essentially shells that set Pronto's hardware registers with the parameters of the message transfer. In contrast to the heavy *send* and *receive* primitives of existing message passing libraries, our API's functions are extremely light-weight, consisting only of a few writes to memory mapped control registers.

#### 2. Architectural Techniques for Efficient On-Chip Data Management

Figure 2.3. NagaM tile containing a  $\rho$ -VEX processing element, local memories, Pronto message passing interface and a network interface

| Table 2.1. | Pronto | Message | Passing | API | for NagaM |

|------------|--------|---------|---------|-----|-----------|

|------------|--------|---------|---------|-----|-----------|

| FUNCTION     | ARGUMENTS                                                 |

|--------------|-----------------------------------------------------------|

| MP_send()    | destination task id, length, local memory address of data |

| MP_receive() | source task id, length, local memory address for data     |

| MP_mread()   | local memory address for data, length, MEM address        |

| MP_mwrite()  | local memory address of data, length, MEM address         |

The *MP\_send* and *MP\_receive* functions are always called in pairs between communicating tasks, with the calls specifying only the size of the message, its location in the tile's local memory, and the sender/recipient's task ID. This provides a high level of abstraction, hiding details such as the actual physical PE onto which tasks are mapped. Each argument of the function calls maps to a particular control register of the Pronto interface, as listed in Table 2.2. The Pronto architecture allows programmers to extend the software API by defining multiple message types through the *CR4* control register. During message transfers, the contents of this register are encoded into the message header (also known as *message envelope*), enabling control signaling between executing tasks.

#### 2.2.2.2 Hardware Architecture

The control registers together with the software API act as an interface between the executing application code and the Pronto hardware. Rather than actually performing

|              | CR1                  | CR2    | CR3                  | CR4        |

|--------------|----------------------|--------|----------------------|------------|

| MP_send()    | Local memory address | Length | Dest. Task ID        | Type (DAT) |

| MP_mwrite()  | Local memory address | Length | MEM address          | Type (MWR) |

| MP_receive() | Source Task ID       | Length | Local memory address | Type (DAT) |

| MP_mread()   | MEM address          | Length | Local memory address | Type (MRD) |

Table 2.2. Control Register Mappings

the transfer through software, the message passing functions of our API only configure Pronto's control registers to initiate transfers between communicating tasks. The actual transfer is performed and managed by the hardware architecture itself. The following subsections examine Pronto's management of the MPB, flow control and synchronization of messages, and its abstraction of physical addressing from the programmer.

(i) Address Translation As previously mentioned, the *MP\_send* and *MP\_receive* functions specify message transfers using task IDs of the recipient and source respectively, instead of their physical PE addresses. This is enabled by a per-tile *Address Translation Table (ATT)* programmed during task mapping, which translates programmer specified task IDs into the physical network addresses of the corresponding PEs. Consequently, the communication semantics for Pronto completely abstract details such as the physical address of PEs, and allow all inter-task communications to be specified at the task level itself. In addition to reducing the complexity of programming using message passing, this abstraction also permits task mappings to be adapted at runtime without requiring the software to be recompiled since physical addresses of PEs are not specified anywhere in the code.

(ii) **Buffer Management** Before any data can actually be transmitted, it is essential for the sending node's message passing interface to determine whether sufficient free space exists in the downstream MPB. This is achieved through the use of a *message envelope* containing the source node's physical address, the amount of MPB space requested and the type of the message. Envelopes are handled at the downstream node on a first-come-first-served basis, with accepted envelopes resulting in the MPB reserving the requested chunk of memory for the impending message. The *buffer manager* actively tracks the utilization of the MPB through a status table, as shown in Figure 2.4. Upon arrival of each message, the buffer manager translates the source node address into its corresponding task ID, and places this information together with the MPB memory address at which the message is located into a free tuple of the status

Figure 2.4. Illustration of buffer management and message ordering in the Message Passing Buffer (MPB)

table in a circular *FIFO*-like manner. A pointer indicates the oldest waiting message entry in the table, illustrated as an emboldened tuple in Figure 2.4. A successful reservation results in an acknowledgement to the upstream node indicating that the transfer may commence. In the event of insufficient MPB space, the corresponding envelope is buffered until the requested space becomes available. Therefore, no negative acknowledgements are returned, preventing repeated envelope transmissions from the stalled sender. Since only a single envelope is required per message regardless of its size, the overhead it poses remains fixed, and is quickly amortized during burst transfers.

Envelopes are generated automatically once an *MP\_send* call moves a complete block of data into the MPB. Therefore, destination MPB reservations are handled automatically by the DMA engine rather than explicitly by the programmer. The motivation for using a message envelope is two fold:

1. The R3 NoC used in the NagaM enforces a protocol allowing for a maximum payload of 64B (16 words) per packet. Larger payloads are split into multiple packets, each of which is arbitrated separately by the R3 router's round robin arbiter. Multiple tasks communicating concurrently with a downstream task would result in the latter's MPB being inundated with only parts of messages, necessitating a buffer of a larger capacity. On the other hand, the use of message

envelopes and the reservation based message flow control system ensures that received messages can always be stored as a whole, and that transfers commence only upon reservation of sufficient storage in the MPB. Furthermore, the mechanism simplifies buffer management by allocating memory on a permessage basis rather than per-source.

2. The message envelope and reservation based message flow control further ensure that packets belonging to messages in flight do not end up blocked in router FIFOs due to a full downstream MPB. Given the NoC's best effort nature, this would lead to blocked links, and give rise to the possibility of network deadlocks due to the absence of time-outs and packet dropping in the R3 architecture. Our mechanism therefore separates flow-control and buffering for the message passing system from that of the NoC.

Multiple requests from different upstream nodes to a single MPB are handled sequentially, although once accepted, transfers may proceed concurrently. This is possible since the buffer manager allocates disjoint blocks of memory to each transfer, allowing received words to be placed in their appropriate MPB memory locations simply based on their source. The *MP\_send* function does not specify the destination memory address for any transfer. Where this data is placed in the receiving node's local memory is determined by the arguments of the *MP\_receive* call at the destination, essentially simplifying the semantics of data movement in the system. Needless to say, each node may only hold one request (both active and pending) to any particular downstream node at any given point in time. Furthermore, words constituting a message must form a contiguous block in memory, i.e. they must be located at sequential memory addresses.

(iii) Ordering of Messages at Destination The buffer manager preserves the entry order of incoming data blocks using the status table, ensuring that the oldest received block is popped from the buffer when requested by the executing task. In the case of concurrent tasks with uneven loads where the upstream task generates multiple data blocks during a single run of the downstream task, this mechanism guarantees that blocks are consumed in the same order as they are generated. Received blocks are moved into the local data memory of the PE once the *MP\_receive* function with the corresponding source task ID is called.

In case a task produces more than one type of output data, a programmer defined protocol must be enforced to order the *MP\_send* and corresponding *MP\_receive* calls. This is because the functions do not include any details of the destination memory

address for the remote task, thus making it difficult to determine which data block the message contains. Given the nature of dataflow based programs and their definite input-output dependencies, this ordering is trivial to enforce. Therefore, if a task generates two outputs and sends them in one order, the downstream task must call *MP\_receive* in this exact same order. This is illustrated in Figure 2.4 which shows the MPB of a destination node receiving messages from a number of nodes, even before older messages already waiting in the buffer are consumed. When *MP\_receive* is called, the waiting messages from the requested source task ID are returned to the PE in the order in which they arrived.

The *MP\_receive* function is blocking, and hence stalls the PE until data from the specified source is received by the MPB. The *MP\_send* function, on the other hand, is non-blocking except for when the local MPB's output buffer is full in addition to the downstream MPB's input buffer. In this case, execution is stalled by clock-gating the local PE. Proper load-balancing of tasks to ensure that they incur similar execution times minimizes the occurrence of such buffer full/empty stalls. We illustrate this in the following subsection with the *JPEG* decoder.

#### 2.2.3 Experimental Evaluation

We evaluate Pronto using a cycle-accurate HDL based simulation model of NagaM. The model uses 18  $\rho$ -VEX processing elements connected over a 4x5 mesh topology network, with a single data memory buffer from which task graphs fetch their input data, and write their output to. Although a practical hardware implementation would place limitations on the size of this buffer, for the purpose of our simulations, we impose no such constraints. This does not affect the validity of the presented results since the evaluation focuses primarily on the message passing system within the array, and its consequent impact on application performance. The MPB is sized at 512B (128-words) for the input, and 256B (64-words) for the output.

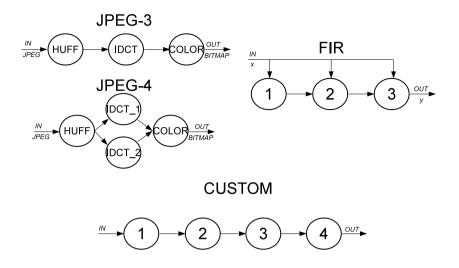

Three dataflow workloads are used to analyze the performance impact and scalability of Pronto: *JPEG* decoder, *Moving Average FIR* filter and a custom test workload. The *JPEG* decoder from the *MiBench* benchmark suite [49] implements the decoding of JPEG images into the Bitmap format. The conversion process involves three stages, namely *Huffman decoding*, *Inverse Discrete Cosine Transform (IDCT)* and *colour conversion*. The original sequential implementation of the JPEG decoder from the benchmark suite was parallelized manually by converting each of its three stages into concurrently executable tasks, with the Pronto API functions used for data transfer. After initial experiments, a more effective four-stage JPEG decoder was developed to overcome inefficiencies noted in our three-stage implementation. The two versions are

Figure 2.5. Task graphs for the JPEG-3, JPEG-4, FIR and CUSTOM workloads.

identified as JPEG-3 and JPEG-4, with the suffix signifying the number of concurrent stages in their task graphs. The input data set for these workload consists of a 512x512 pixel JPEG encoded image.

The *Moving Average FIR filter* workload is used in signal processing applications to remove unwanted noise in signals. The filter essentially implements the equation listed in (2.5), where *x* and *y* represent the input and output signals respectively, with *N* samples.

$$y[i] = \frac{1}{N}x[i] + \frac{1}{N}x[i-1] + \frac{1}{N}x[i-2] + \dots + \frac{1}{N}x[i-N-1]$$

(2.5)

The nature of this algorithm allows it to be partitioned into multiple concurrent tasks, each with a similar computational load. However, partitioning may only be beneficial upto a certain point, after which communication latencies become comparable to the execution time of tasks themselves, thus limiting further performance gains. The *Custom* application represents an ideal dataflow workload with identical concurrent tasks. Such partitioning can be expected to minimize execution stalls. Figure 2.5 illustrates the task graphs for the JPEG-3, JPEG-4, Moving Average FIR filter and Custom workloads.

The evaluation of Pronto consists of five separate experiments that determine:

1. End-to-end message transfer latency

|                        | LATENCY PER WORD (CYCLES) | BURST SIZE (WORDS) |

|------------------------|---------------------------|--------------------|

| OCMPI [34]             | 32.9                      | 256                |

| [50]-SHARED QUEUE      | 20                        | 64                 |

| [50]-SCRATCH QUEUE DMA | 9                         | 64                 |

| PRONTO                 | 6.48                      | 64                 |

Table 2.3. Comparison of average transfer latency per word

- 2. Communication overheads

- 3. Application performance with Pronto

- 4. Impact of input dataset size

- 5. Impact of extraneous interconnect traffic on output jitter

The following subsections describe each of these experiments, and provide an overview of the obtained results.

#### 2.2.3.1 End-to-end Message Transfer Latency

The performance of Pronto is first evaluated in terms of its message transfer latency per hop, i.e. the latency incurred in transferring a message between two adjacent nodes. For this, two tasks are pinned onto neighbouring PEs in the NagaM array. The first task generates a burst of 64 data words and transfers these using an MP\_send call to the second task which then receives the burst using MP\_receive. In order to accurately estimate the transfer latency, these measurements are performed without any extraneous interconnect traffic (zero network load). The obtained latencies are listed in Table 2.3. The same table also includes the transfer latency for similar sized bursts from literature - Francesco's Shared Queue and Scratch Queue DMA [50], and the MPI derivative for multiprocessors with on-chip interconnects - ocMPI [34]. Pronto is observed to have a transfer latency 30% lower than the closest distributed memory based proposal, Scratch Queue DMA [50]. Note that the use of a larger burst size of 256 words works in favour of ocMPI since the overheads of transfer setup are better amortized by large bursts. Despite this, the overall per word transfer latency of ocMPI is observed to be significantly larger than that of Pronto, indicating the higher transfer overheads of MPI-based systems.

The transfer of the message envelope and the downstream node's acknowledgement of buffer reservation impose a one-time latency overhead for each message. While message envelopes indicate the source node and quantum of MPB space

Figure 2.6. Breakdown of task execution as a fraction of its total execution time. The *transfer overhead* reflects the overhead imposed by message envelopes as a percentage of total execution time.

required at the destination, the former is already included into the packet header according to the R3's protocol. Therefore, the message envelope in NagaM is a 2-flit packet consisting of the header and a single flit containing an integer value of the required MPB space. The envelope length remains the same regardless of message size. A 64 word message on the R3 NoC is sent in 4 packets, or 68 flits in total. A single message envelope and the corresponding downstream MPB acknowledgement result in 3 additional flits (2 for the envelope and 1 for the acknowledgement) being exchanged between the nodes. This constitutes an overhead of under 5% for a 64 word message.

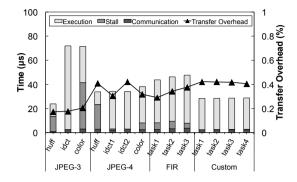

### 2.2.3.2 Communication Overheads

In order to determine the transfer overhead for messages in terms of total execution time, we mapped single instances of workload task graphs onto the array with zero network load. Figure 2.6 illustrates the fraction of total execution time spent in execution, stalls due to a full/empty MPB and in communication across different workloads. The same figure also indicates the overhead imposed by message envelopes as a fraction of total execution time. As previously mentioned, only one envelope and its corresponding acknowledgement are generated for each message transfer. Consequently, the number of envelopes and acknowledgements exchanged over the interconnect depends only on the number of messages transferred, and not their size. In general, the transfer overhead of the message envelopes constitutes less than 0.5% of the total execution time across all workloads. The time spent stalled due to a

full/empty buffer is primarily caused by imbalances between the tasks, and this can be reduced by precise partitioning and load-balancing. Frameworks such as Daedalus [51] enable such analysis and help in precise partitioning of workloads for high performance and scalability.

The consequences of inefficient partitioning in the case of the JPEG-3 workload are also illustrated in Figure 2.6. Initial runs of the workload on the NagaM array revealed an imbalance in the runtime of its three constituent stages. The IDCT stage in particular was observed to run close to six times as long as the Huffman decoding stage, resulting in repeated execution stalls for the latter. The IDCT stage was subsequently partitioned further into two concurrent tasks to address the imbalance in task loads, as shown earlier in Figure 2.5. The resulting implementation reduced buffer-related execution stalls by 38% and reduced execution time by 45% as compared to the three-stage version. Although the number of message transfers in both implementations is identical, Pronto's transfer overhead appears higher in the case of JPEG-4 due to the reduced execution time.

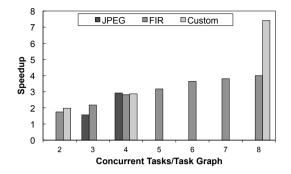

#### 2.2.3.3 Application performance with Pronto

Execution performance can be improved in two ways - by increasing the number of concurrently executing tasks through fine grained partitioning, and by increasing the number of instances of the task graph executing in parallel. We observe from Figure 2.7 that the former does not always yield significant returns. In the case of the FIR filter for instance, the speedup obtained through fine-grained partitioning tends to flatten out beyond 6 tasks for a 6400 sample input size as a consequence of the reduction in computational load per task to a level where communication latencies become significant.

Instantiation of multiple instances of the task graph on the other hand allows for exploitation of data-level parallelism, thus achieving greater speedup and higher throughput. Figure 2.8(a) reports the execution speedup for the workloads with a varying number of parallel instances of the task graph, over sequential execution on the host PE. A linear improvement in speedup is observed as the number of parallel instances executing on the NagaM array is increased. The corresponding throughputs for these workloads considering a 200MHz clock frequency are reported in Figure 2.8(b). Note that since the FIR workload generates output data blocks of size 376B as against 256B for the Custom workload, the two yield very similar throughputs despite their significantly different speedups. In comparison, the JPEG decoder generates larger output data blocks of size 768B, thus explaining its prominently higher throughput.

Figure 2.7. Performance improvements obtained with fine-grained partitioning

### 2.2.3.4 Impact of input dataset size

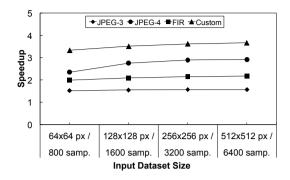

The runtime of all workloads is influenced by the size of their input datasets. When the number of concurrent tasks per task graph as well as the number of parallel instances of the task graph are fixed, the runtime can be expected to increase as the input dataset size is increased. A longer runtime can however be beneficial as it tends to amortize the impact of communication and configuration overheads. Most significantly, a longer runtime softens the impact of ATT configuration that occurs when the task graph is spawned on the NagaM array. To estimate the performance impact of such overheads, we varied the input dataset size for workloads, effectively changing their runtime. Figure 2.9 reports the speedup obtained over sequential execution across different dataset sizes.

The figure indicates small improvements in speedup with increasing dataset size. Note that with the 64x64/800 samples dataset, the overall execution time for most workloads is low enough for the the ATT configuration operation to constitute a moderate overhead. With larger dataset sizes on the other hand, speedup improvements are less pronounced, since the configuration operation no longer forms an appreciable fraction of total execution time. These results suggest that overheads of Pronto within the NagaM architecture are sufficiently low so as to yield similar speedups across a range of input dataset sizes.

#### 2.2.3.5 Impact of extraneous interconnect traffic on output jitter

Given the best-effort nature of NagaM's NoC, it is prudent to evaluate the impact of extraneous interconnect traffic on the variation in arrival rate of data blocks.

The eventual integration of NagaM and NagaS into a single multiprocessor array

Figure 2.8. (a) Execution speedup relative to sequential execution on the host PE (sequential exection times - *JPEG-4*:  $105.3\mu$ s, *FIR*:  $115.8\mu$ s and *Custom*:  $106.1\mu$ s) (b) Throughput at 200MHz

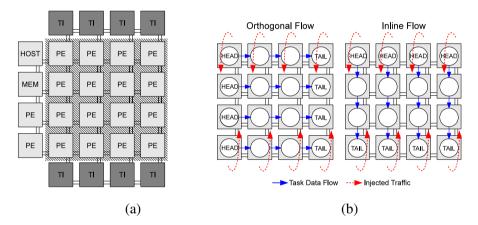

will cause the message-passing and shared-memory architectures to share a common system interconnect. For this reason, it is prudent to evaluate the impact of extraneous interconnect traffic due to the shared-memory NagaS, on the variation in arrival times for data blocks in the message-passing NagaM. This is done by emulating cache related traffic in the interconnect through a set of *Traffic Injectors (TI)* placed at the North and South edges of the array. Injectors at the northern edge emulate cache miss and write-back requests directed towards those on the southern edge. These requests vary in size from 4B (cache miss) to 64B (cache line write-back) at various injection rates, emulating extremely pessimistic miss rates. The injectors on the southern edge respond with appropriately sized packets to the requesting injector, as illustrated in Figure 2.10. Multiple parallel instances of a task graph are mapped onto PEs of the array, with task data blocks moving in a direction orthogonal to the injected synthetic

Figure 2.9. Speedup with varied input dataset sizes

Figure 2.10. (a) NagaM array with traffic injectors simulating cache traffic. Tasks are mapped to PEs within the highlighted region of the array. (b) Illustration of relative directions of task data and injected traffic - orthogonal and inline.

traffic. The output jitter is measured as the variation from expected arrival time for data blocks at the memory buffer (*MEM*) averaged over the entire execution of the workload for a given input dataset.

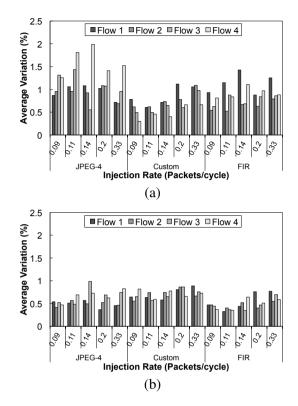

The measured output jitter for workloads at different injection rates for the case when task data blocks and synthetic traffic flow in orthogonal directions is reported in Figure 2.11(a). In order to provide a comparison, we adapted the traffic injectors and task mapping such that the injected traffic and task data blocks flow inline with one another as shown in Figure 2.10(b). The average variation across workloads and injection rates is observed to drop from the earlier peak of 2% to under 1% with this

Figure 2.11. Average arrival time variation for: (a) orthogonal flows and (b) inline flows

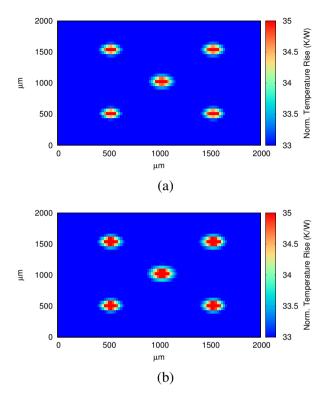

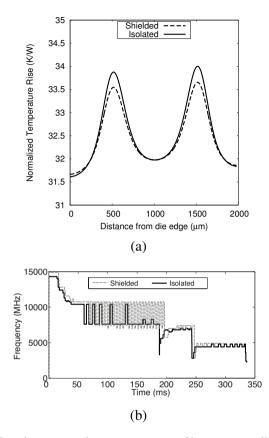

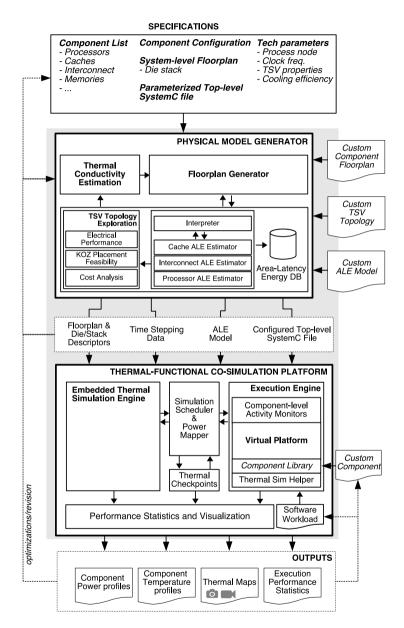

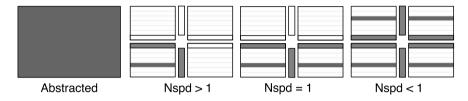

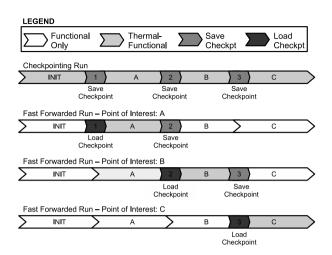

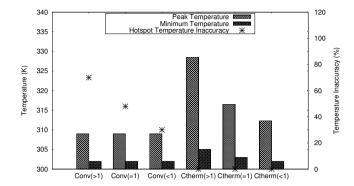

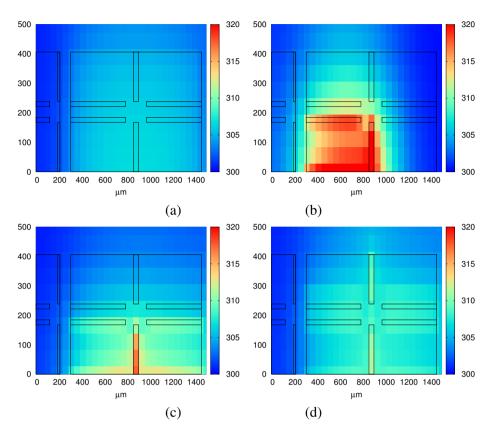

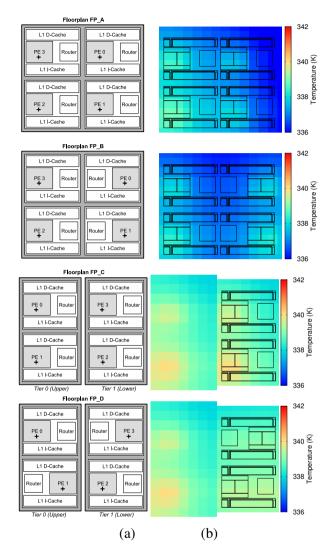

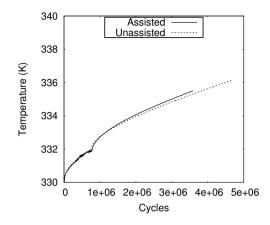

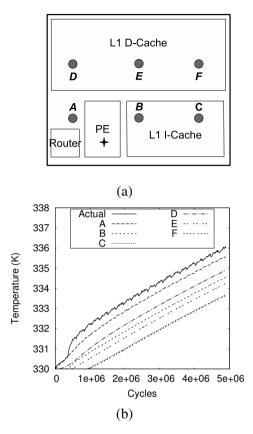

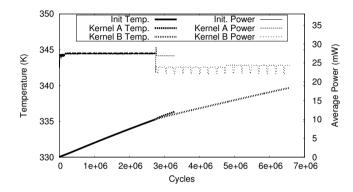

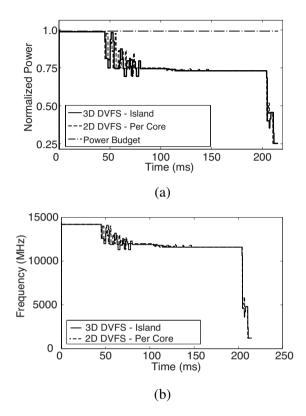

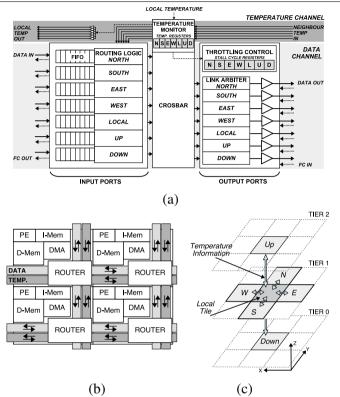

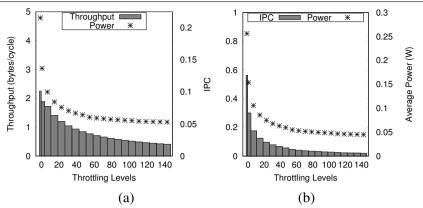

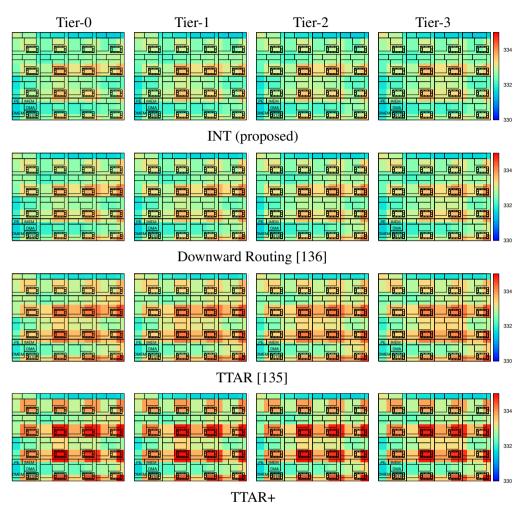

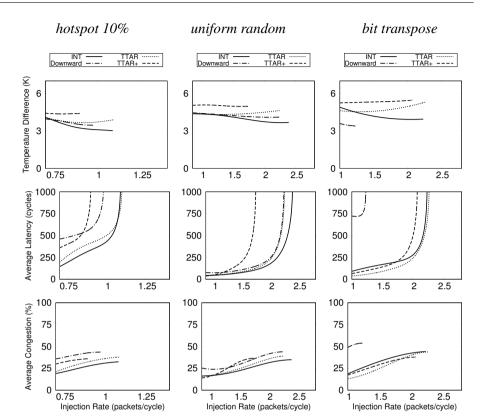

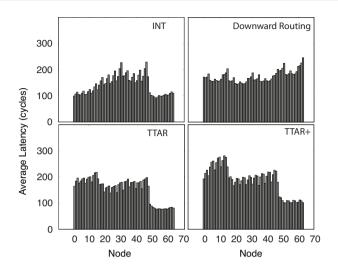

new mapping. This can be seen in Figure 2.11(b). Rather than the injection rate, it is the relative direction of interconnect traffic that significantly influences arrival time variations for data blocks.