## Attojoule Superconducting Thermal Logic and Memories

Wang, H.; Noordzij, N.; Mykhaylov, M.; Steinhauer, Stephan; Descamps, Thomas; Oksenberg, Eitan; Zwiller, Val; Esmaeil Zadeh, I.Z.

10.1021/acs.nanolett.4c06545

**Publication date** 2025

**Document Version** Final published version

Published in Nano Letters

Citation (APA)

Wang, H., Noordzij, N., Mykhaylov, M., Steinhauer, S., Descamps, T., Oksenberg, E., Zwiller, V., & Esmaeil Zadeh, I. Z. (2025). Attojoule Superconducting Thermal Logic and Memories. *Nano Letters*, *25*(11), 4401-4407. https://doi.org/10.1021/acs.nanolett.4c06545

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

pubsiacs.org/Nanol ett Letter

# Attojoule Superconducting Thermal Logic and Memories

Hui Wang,\* Niels Noordzij, Mischa Mikhailov, Stephan Steinhauer, Thomas Descamps, Eitan Oksenberg, Val Zwiller, and Iman Esmaeil Zadeh

Cite This: Nano Lett. 2025, 25, 4401-4407

**ACCESS** I

III Metrics & More

Article Recommendations

Supporting Information

**ABSTRACT:** Due to stringent thermal budgets in cryogenic technologies such as superconducting quantum computers and sensors, electronic building blocks that simultaneously offer low energy consumption, fast switching, low error rates, a small footprint, and simple fabrication are pivotal for large-scale devices. Here, we demonstrate a superconducting switch with attojoule switching energy, high speed (pico-second rise/fall times), and high integration density (on the order of  $10^{-2} \mu m^2$  per switch). It consists of a superconducting nanochannel and a metal heater separated by an insulating silica layer. We experimentally demonstrate digital gate operations utilizing these nanostructures, such as NOT, NAND, NOR, AND, and OR gates, with a few femtojoules of energy

consumption and ultralow bit error rates  $<10^{-8}$ . In addition, we build energy-efficient volatile memory elements with nanosecond operation speeds and a retention time over 10<sup>5</sup> s. These superconducting switches open new possibilities for increasing the size and complexity of modern cryogenic technologies.

KEYWORDS: Superconducting device, logic gate, memory device, digital circuits

C uperconducting circuits, thanks to their fast response and low dissipation, have become pivotal to a wide range of computing and sensing applications such as superconducting qubits and quantum processors, 1,2 infrared single-photon detectors,3 and superconducting neurons.4,5 However, scaling up the current technologies into practical superconducting systems is hampered by the heat load of processing and readout electronics and the limited available cooling budget of the cryogenic coolers. Thus, developing low-power-consumption electronics has become increasingly attractive as it can enhance the information processing capacity of superconducting quantum computers and sensors.

A great research effort has been invested in developing compatible cryogenic logic gates and memory cells, which are the building blocks of computing circuits, such as single-fluxquantum (SFQ) technology<sup>7-11</sup> or nanocryotrons (nTrons). 12,13 Various technologies that realize these building blocks all have their combinations of scaling challenges such as external magnetic field sensitivity, 14,15 need for additional timing circuits, 16,17 large cell dimensions, 18,19 destructive readout schemes, 13 insufficient operation speeds, 13,20 etc. As a result, there remains a demand for new technological concepts to realize both logic gates and memory cells for largescale, complex cryogenic technologies. For instance, electricfield-controlled cryotrons (EF-Trons)<sup>21-24</sup> have attracted significant scientific interests due to potential low energy dissipation and high switching frequency, but further studies are required in the dynamic performances and the reduction of the gate voltage. <sup>25,26</sup> Another promising candidate is the superconducting thermal switch where the superconductivity is

perturbed by the Joule heating effect from a heater, such as superconducting nanotransistors (SNTs),<sup>27</sup> planar heaternanocryotrons (P-hTrons),<sup>20</sup> and multilayer heater-cryotrons (M-hTrons),<sup>28</sup> due to the absence of the leakage between the heater and the superconducting channel. Previous works have shown the potentials of P-hTrons and M-hTrons with DC measurements<sup>27,28</sup> and electro-thermal simulations.<sup>28</sup> This work addresses the gap in dynamic characterization and the experimental realization of basic logic and memory cells based on superconducting thermal switches.

In this article, we characterize the static and transient responses of a novel superconducting thermal switch actuated by a metal heater on top of a superconducting nanochannel, as shown in Figure 1. We show that under proper operation conditions, the required switching energy of our devices is no more than a few hundred attojoules. Using these compact nanostructures, we successfully implement fundamental logic gates (NOT, NOR, NAND, AND, and OR). Implementation of these gates are significant, as by combining one (e.g., NOR or NAND) or more (e.g., AND/OR and NOT) types of logic gates, one can realize a complete set of logic operations. We also construct a volatile memory cell with a single super-

Received: December 24, 2024 Revised: March 6, 2025 Accepted: March 6, 2025 Published: March 10, 2025

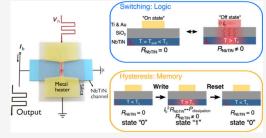

Figure 1. Characterization of the superconducting thermal switch. a, Schematic picture and b, scanning electron microscopy image of the superconducting thermal switch consisting of a NbTiN channel covered by a layer of silica and a metal heater. c, The device switches between the superconducting ("On") state and the resistive ("Off") state due to heat transfer from the metal layer via the silica to the NbTiN channel. d, Resistance of the NbTiN channel ( $R_{NbTiN}$ ) as a function of the bias current ( $I_b$ ) and the current through the metal heater ( $I_b$ ).

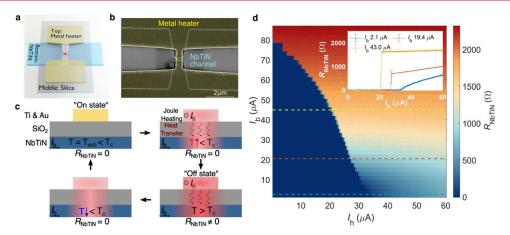

Figure 2. a, Schematic of the experimental circuit to test the transient response of the superconducting thermal switch. b, Voltage traces of a superconducting thermal switch with a clock input signal. Note: signal attenuations and amplifications have been accounted for, and the corrected curves are plotted (see Supporting Information section 2 for more details). The input signal is a 10 MHz square wave with a pulse duration  $\tau_h \approx 4.2$  ns and an amplitude  $V_h \approx 7.2$  mV. The device is biased with  $I_b = 28.5 \ \mu\text{A}$ , and the metal heater has a resistance  $R_b = 291.5 \ \Omega$ .

conducting thermal switch based on the persistence of the resistive state in the superconducting channel due to the self-heating effect. While superconducting nanowire memory cells based on flux trapping have been demonstrated using hTrons,  $^{28,30}$  the technology presented here is ultracompact ( $\sim\!10^{-1}~\mu\mathrm{m}^2$ ) and fabrication-friendly. Both the logic and the memory devices achieve fast operation (up to 100 MHz), outstanding energy efficiency (a few femtojoule per operation), and high reliability ( $10^{-8}\!\sim\!10^{-6}$  bit error rate). Therefore, these compatible cells offer a pragmatic approach to developing scalable and energy-efficient cryogenic electrical systems.

The structure of the superconducting thermal switch is depicted in Figure 1a. A metal (Ti and Au) heater is placed over a superconducting (NbTiN of 8–10 nm thickness) nanochannel with a thin insulating (SiO<sub>2</sub>) layer in between. As illustrated in Figure 1c, the local heat profiles are determined by Joule heat generation in the metal heater and phonon transport through the SiO<sub>2</sub> layer. As the local temperature exceeds the critical temperature  $T_c$ , the superconducting state of the NbTiN channel is disrupted, resulting in a resistive section ("Off state" in Figure 1c). The resistance in the NbTiN channel is determined by the area of the resistive region, which

is related to both the current through the heater,  $I_{\rm h}$ , and the bias current of the NbTiN channel,  $I_{\rm b}$ .

Devices were fabricated as detailed in Supporting Information Section 1. The sample was mounted at a base temperature of ~3 K. We first measured the response of the superconducting thermal switch in the steady state. Direct currents I<sub>h</sub> and I<sub>b</sub> were sent through the metal heater and the NbTiN channel, respectively, and the resistance of the NbTiN channel R<sub>NbTiN</sub> was measured (see Supporting Information Section 2). Figure 1d displays the results for a device with a NbTiN constriction of 0.5  $\mu$ m (width)  $\times$  0.1  $\mu$ m (length) and a metal heater of 0.1  $\mu$ m (width)  $\times$  0.5  $\mu$ m (length). The switching current decreases as the bias current increases due to a lower local critical temperature. As observed from the response curves at various bias currents in the inset, an abrupt change occurs at the switching point when the bias current  $I_b$  is high. This indicates that the resistive hotspot rapidly expands over the entire constriction due to the self Joule heat generation in the nanochannel. As reported in superconducting nanostrips,<sup>31</sup> we also observed hysteretic characteristics in the  $I_{\rm h}$ - $R_{

m NbTiN}$  measurements and the related discussion can be found in Supporting Information Section 4.2.

In order to evaluate the switching behavior of this device, we measured the transient response. A schematic of the measurement circuit is displayed in Figure 2a (a detailed electrical circuit diagram is illustrated in Supporting Information Section 2). When the input pulse amplitude on the heater triggers a local hotspot, i.e., the superconducting thermal switch is in the off state, the resistance of the NbTiN channel  $R_{\rm NbTiN}$  becomes large enough to redirect the current to the output amplifier, producing a high voltage level at the output. The dynamic switching energy of the device is calculated as  $E_{\rm h} = \tau_{\rm h} V_{\rm h}^2 / R_{\rm h}$ , where  $\tau_{\rm h}$  and  $V_{\rm h}$  are the duration and amplitude of a single input pulse on the heater, respectively.

Figure 2b shows a typical example of the input and output waveforms. It should be noted that the time delay between the input and output signals depends on the length of the associated cables and the differences between electronic components used in the experiment. Here, for easier comparison, the pulse traces are shifted to overlap. The superconducting thermal switch was biased at  $I_b = 28.5 \,\mu\text{A}$  and could be switched by an input pulse trace with a duration of  $\tau_{\rm h}$  $\approx$  4.2 ns and a frequency of 10 MHz, corresponding to a dynamic switching energy of  $E_{\rm h}$  = 746.9 aJ. The lowest dynamic switching energy measured was  $E_{\rm h}$  = 273.8 aJ when the NbTiN channel was biased close to the critical current (see Supporting Information Figure S6a). Such dynamic energy consumption is comparable with that of the modern CMOS switches (100 aJ  $\sim$  3 fJ). Considering the source-switch impedance mismatches and the connecting transmission lines, the estimated energy consumption presents a higher bound and may be much better (see details in Supporting Information Section 2). Taking into account the energy dissipation due to the current flowing through the channel, the entire switch was estimated to consume 1.658 fJ every switching operation. Further improvement of the energy efficiency can be achieved by scaling down the device dimension to reduce the amount of energy required to break the superconductivity.

The rise and the fall times of the transient response in Figure 2b are 271.8 and 339.1 ps, respectively. The inductor time constant  $L_k/R$  is not the main limiting factor due to the small NbTiN channel dimensions ( $L_k$  is estimated to be a few nH, see details in Supporting Information Section 1). Constrained by the temporal characteristics of the instrumentation (details in Supporting Information Section 2), the highest switching frequency we experimentally applied was 200 MHz (see Supporting Information Figure S6b). It can be observed that the output pulse duration in Figure 2b does not fully match the input pulse duration. This could be due to the switch-on delay time (see more measurements in Supporting Information Section 6) and the thermal recovery time after the heater switches off. As suggested in previous studies of similar multilayer structures, the switch-on delay could be decreased with a higher input power density or a higher bias current, which influences how fast the channel can be thermalized to the critical temperature.<sup>20,34</sup> The thermal recovery time is affected by the self-heating effect in the superconducting channel after deactivation of the heater. Apart from engineering the material properties to obtain better thermal coupling between the channel and the substrate, a feasible way to alleviate it is to select a proper constriction geometry as well as an appropriate electrical bias level to reduce the self-heating power density.<sup>35</sup>

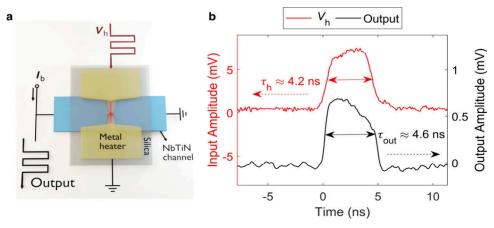

By controlling the resistance of the NbTiN channel, we designed a set of fundamental logic gates, e.g., NOT, NOR,

NAND, AND, and OR gates. Figure 3 shows the electrical circuits and normalized experimental results for NOT, NOR, and NAND gates. More examples can be found in Supporting Information, Figure S9.

Figure 3. Construction of fundamental logic gates. a-c, Implementation of fundamental logic gates NOT (a), NOR (b), and NAND (c) using superconducting thermal switches. Figures on the left are the schematic diagrams. Figures on the right are the corresponding experimental waveforms of the inputs (A, B) and output (Q), rescaled according to the logic HIGH and LOW levels. The resistive elements shown in the figures are  $R_0$  = 22 Ω,  $R_{\rm Load}$  = 50 Ω,  $R_{\rm p}$  = 100 Ω, and  $R_{\rm s}$  = 50 Ω.

In the NOT gate, a voltage source  $V_{\rm dc}$  is biased through the NbTiN channel of the superconducting thermal switch, in series with a 50  $\Omega$  load ( $R_{\text{Load}}$  in Figure 3a). When the voltage across the metal heater is in the logic HIGH level, the NbTiN channel is switched to the nonsuperconducting state, introducing a nonzero resistance (usually  $\sim k\Omega$ ) in the circuit. Therefore, the current through the load resistor is reduced when the superconducting thermal switch is off, leading to the logic LOW level at the output, as shown in Figure 3a. The bias voltage results in a power dissipation of  $V_{\rm dc}^2/(R_0+R_{\rm Load})\approx 13.9$ nW in the on state. Since the normal resistance generated in the NbTiN channel is on the order of a few hundred Ohm according to the static measurement, the energy dissipated in the channel and the bias circuit in the off state is negligible in comparison with the heater input energy. Therefore, the total off-state energy dissipation is around 1.43 fJ.

To implement an NOR gate, two superconducting thermal switches were connected in series (Figure 3b). Once either of

Nano Letters pubs.acs.org/NanoLett Letter

the NbTiN channels switches to the resistive state, more current is redistributed to the parallel resistor  $R_{\rm p}$ , leading to a logic LOW level across the output resistor  $R_{\rm Load}$ . Since both switches have significantly larger normal-state resistances than the parallel resistor, there is only a minor difference between the low voltage levels with only one switch or both switches in resistive state. Compared with the NOT gate, a higher static power ( $\sim$ 54.5 nW) was dissipated due to the resistor bridge in the on state. The energy dissipation in the biasing and observation circuit is approximately 0.457 fJ, and the input heating pulse energies on the two heaters are 1.54 fJ and 1.53 fJ, respectively. Thus, the resulting energy dissipation of the whole NOR gate in the off state is around 3.53 fJ.

Analogously, one can assemble two superconducting thermal switches in parallel to build a NAND gate. This implementation requires an appropriate gate threshold or a delicate circuit design (Supporting Information Figure S10). Figure 3c represents another more straightforward way to construct a NAND gate by connecting a NOT gate with an AND gate. Thanks to the insulation between the superconducting channel and the heater, the bias current and the heater current can be modulated simultaneously without considerable crosstalk. Therefore, the heater of a superconducting switch can be driven by the input signal B, while the bias current through the superconducting channel can be controlled by the other input signal A, forming an AND gate. The overshoot at the output, which can be observed in Figure 3c (as well as for the twostage logic circuit in Figure 4b), can be attributed to the offchip connection using coaxial cables between the two stages in

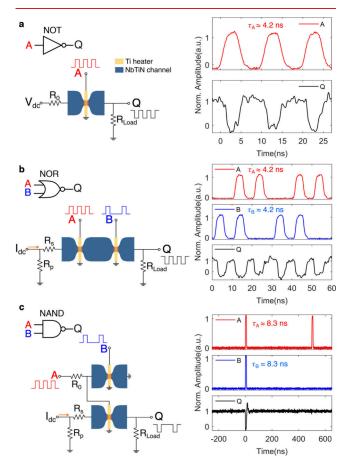

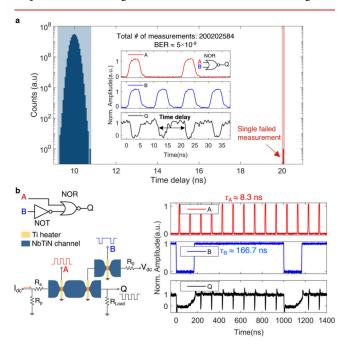

Figure 4. Bit error rate (BER) and driving ability of the logic gates. a, Correct (blue) and incorrect (red) operations of a NOR gate over  $2 \times 10^8$  measurements as used to calculate the bit error rate (BER). The inset displays typical input (A: 50 MHz with a pulse duration of 4.2 ns, B: 100 MHz with a pulse duration of 4.2 ns) and output signals (Q) of the NOR gate. The horizontal coordinate represents the time delay between the falling edges of two consecutive pulses at the output, which was triggered at 50% of the output pulse amplitude. b, Electrical diagram (left) and experimental results (right) of a simple logic circuit composed of a NOT gate and a NOR gate.

the initial experiments. During the switching-off time of 8.3 ns, the energy dissipated in the NAND gate is about 18.83 fJ. It can be further decreased by using a voltage source for the NOT gate to avoid the static power consumption in the resistor bridge, integrating elements completely on-chip to increase the signal transfer efficiency, or downscaling the superconducting thermal switch to achieve less energy dissipation.

One crucial merit of any logic gate is the bit error rate (BER), which is defined as the number of incorrect responses at the output divided by the total number of input events. We achieved a BER of  $5\times 10^{-9}$  for the NOR gate operation, as shown in Figure 4a. The two superconducting thermal switches were operated with input pulse energies of 1.40 (input A) and 1.18 fJ (input B). The single fail event among over 200 million measurements was detected by comparing the time delay between the two consecutive output pulses with the supposed period of the output signal, which was 10 ns for Figure 4a.

The construction of NAND gates by combining NOT and AND gates suggests that the superconducting thermal switches can drive consecutive logic gates, which is important in building more complex superconducting logic circuits. To further explore this, we constructed the circuit shown in Figure 4b, where a NOT gate and an NOR gate are connected to form a simple logic circuit in such a way that one gate drives the input (heater) of the next stage. The determining factor to trigger the heater in the next stage is to generate a HIGH voltage level exceeding its switching threshold. Since the switch in the NOT gate is supposed to stay in the superconducting state at logic HIGH output, the HIGH voltage level is mainly constrained by the critical current of the NOT gate. Thus, the superconducting thermal switch used in the NOT gate was designed to have a wider NbTiN channel in order to provide enough switching energy to the next stage.

Recently superconducting memory cells driven by both optical and electrical signals have been demonstrated using the hysteretic transition between the superconducting and the resistive state. These devices consume  $\sim\!600~\mu\mathrm{W}$  power in the resistive state and operate at speeds <50 kHz. In Figure 5, we present a novel approach to construct a volatile memory cell with a superconducting thermal switch, which allows a higher speed and lower energy consumption (see Supporting Information Figure S11 for alternative implementations).

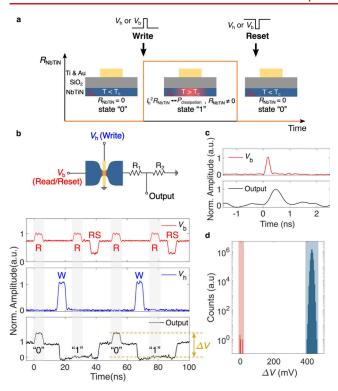

As depicted in Figure 5, the channel in a superconducting thermal switch can be intentionally latched into the non-superconducting state (state "1" in Figure 5a), if the electrothermal effect in the superconducting channel and the heat dissipation into the substrate reach an equilibrium. By reducing the power dissipated from the channel or the heater to alleviate the electro-thermal effect, the device can be reset back to the superconducting state (state "0" in Figure 5a).

In the example shown in Figure 5b, the Write or Reset operations are realized by increasing the heater voltage  $V_{\rm h}$  or decreasing the bias voltage  $V_{\rm b}$ . The "0" and "1" states of the device are distinguished based on the response at the output by sending a small pulse through the channel. When reading the resistive ("0") state, the output voltage level remains stable since  $R_{\rm NbTiN} \neq 0$  is dominant compared to the associated resistance, resulting in a negligible variation in the current flowing through the circuit; when reading the superconducting ("1") state, a pulse can be observed at the output due to  $R_{\rm NbTiN} = 0$ .

Figure 5. Memory operations of a superconducting thermal switch. a, Use of the superconducting thermal switch as a memory cell. b, Circuit diagram (top) and experimental characteristics (bottom) of the memory. The output Q is amplified by an AC-coupled amplifier (50  $\Omega$  input impedance).  $R_1=22$   $\Omega$  and  $R_2=50$   $\Omega$  are chosen for better impedance matching. Basic memory operations (bottom) are denoted as W for Write, RS for Reset, and R for Read ("0" for reading a superconducting state, where an output pulse is captured, and "1" for reading a resistive state, where no output signal is observed). c, Read operation of the state "0" with a subnanosecond input pulse. The output pulse has a fwhm of around 550 ps. d, Measurement of the BER based on the output voltage difference  $\Delta V$  between "0" and "1" state. The 4 incorrect measurements are marked in red, and correct measurements in blue. The total number of measurements is five million, leading to a BER of  $8\times 10^{-7}$ .

The memory could retain the states for over 10<sup>5</sup> s (see Supporting Information Figure S12). Speeds of up to 80 MHz were reached, which are a limit set by our instruments and do not represent the upper limit of our device. The Read operation reached subnanosecond speeds (Figure 5c), and the Write operation could be completed within  $\sim$ 5 ns (Figure 5b). A BER of  $8 \times 10^{-7}$  was measured with more than 5 million consecutive Read-Write-Read-Reset operations. The memory consumes 56.2 nW in the superconducting state (state "0"), and  $\sim 20$  nW in the resistive state (state "1"). The energy dissipation was around 1 fJ on the heater to write "1" and ~625 aJ in the channel to read "0". While the mentioned values are comparable with the state-of-the-art nTron memory and logic devices, 13 our technology additionally offers nondestructive readout and a small area ( $\sim 10^{-1} \, \mu \text{m}^2$ ), allowing for a high integration density (see Supporting Information Table S1 for an overview).

In conclusion, we demonstrated a superconducting thermal switch that takes only attojoules to trigger and has a total energy consumption on the order of femtojoules. The multilayered structure is fabrication-friendly and can be scaled down further. Utilizing these superconducting thermal

switches, we successfully constructed high-fidelity fundamental logic gates. Compared with standard CMOS logic gates,  $^{36}$  this superconducting logic family requires fewer switching elements and consumes only femtojoules of energy per operation. Furthermore, we realized Set-Reset memory operations using a single superconducting thermal switch with a low error rate on the order of  $1\times10^{-7}$  and a nanosecond operation speed.

The compactness and reliability of these logic gates is attractive for cryogenic applications, such as superconducting nanowire single-photon detectors (SNSPDs). SNSPDs are the main choice for optical signal detection in applications such as quantum communication,<sup>37</sup> due to their exceptional detection efficiency<sup>38,39</sup> and low time jitter,<sup>40</sup> but are difficult to combine into large arrays due to the complexity of their readout circuitry.  $^{41-43}$  As the cryostat provides  $\sim\!100$  mW cooling budget at 3 K and a single superconducting thermal switch can reach a power consumption <1  $\mu$ W, around a hundred thousand of current elements are afforded in the cryogenic system to construct digital circuits. Thus, it is a promising route to develop novel readout techniques by integrating SNSPDs with the compact, energy-efficient, and fabricationfriendly superconducting electronic components proposed here. Adjusting the device geometries and superconducting parameters can further improve the power efficiency and hence the integration capacity. Furthermore, the superconducting logic gates and memory cells have the potential to be utilized in high-performance cryogenic digital processors 44-47 as well as hybrid circuits that combine semiconducting and superconducting components. 34,48

## ASSOCIATED CONTENT

#### Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acs.nanolett.4c06545.

Fabrication process, electrical setup, additional measurements about switching behaviors, thermal crosstalk, switch-on latency, alternative approaches to realize logic or memory operations, and comparison with other superconducting devices (PDF)

## AUTHOR INFORMATION

## **Corresponding Author**

Hui Wang — Department of Imaging Physics, Delft University of Technology, 2628 CN Delft, The Netherlands; orcid.org/0009-0008-8487-7198; Email: h.wang-19@tudelft.nl

#### **Authors**

Niels Noordzij – Single Quantum B.V., 2628 CH Delft, The Netherlands

Mischa Mikhailov — Department of Imaging Physics, Delft University of Technology, 2628 CN Delft, The Netherlands; orcid.org/0000-0001-5645-5192

Stephan Steinhauer — Department of Applied Physics, Royal Institute of Technology (KTH), SE-106 01 Stockholm, Sweden; orcid.org/0000-0001-6875-6849

Thomas Descamps — Department of Applied Physics, Royal Institute of Technology (KTH), SE-106 01 Stockholm, Sweden; orcid.org/0009-0005-6875-5009

Eitan Oksenberg – Single Quantum B.V., 2628 CH Delft, The Netherlands Val Zwiller — Department of Applied Physics, Royal Institute of Technology (KTH), SE-106 01 Stockholm, Sweden

Iman Esmaeil Zadeh — Department of Imaging Physics, Delft University of Technology, 2628 CN Delft, The Netherlands; Single Quantum B.V., 2628 CH Delft, The Netherlands;

Complete contact information is available at: https://pubs.acs.org/10.1021/acs.nanolett.4c06545

orcid.org/0000-0002-3833-2508

#### **Author Contributions**

I.E.Z. and H.W. conceived and coordinated the project. N.N., M.M., I.E.Z. and H.W fabricated the samples. S.S., T.D. provided the superconducting films. I.E.Z and H.W. designed the experimental setup. H.W. carried out all experiments. All authors contributed to writing the article and reading and approving the final manuscript.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

I.E.Z. and H.W. acknowledge the funding from the FREE project (P19-13) of the TTW-Perspectief research program partially financed by the Dutch Research Council (NWO); I. E. Z. acknowledges funding from the European Union's Horizon Europe research and innovation programme under grant agreement No. 101098717 (RESPITE project) and No.101099291 (fastMOT project).

### REFERENCES

- (1) Berggren, K. Quantum Computing with Superconductors. *Proceedings of the IEEE* **2004**, *92*, 1630–1638.

- (2) Wu, Y.; et al. Strong Quantum Computational Advantage Using a Superconducting Quantum Processor. *Phys. Rev. Lett.* **2021**, 127, 180501.

- (3) Sobolewski, R.; Verevkin, A.; Gol'tsman, G. N.; Lipatov, A.; Wilsher, K. Ultrafast superconducting single-photon optical detectors and their applications. *IEEE Transactions on Applied Superconductivity* **2003**, *13*, 1151–1157.

- (4) Toomey, E.; et al. Superconducting Nanowire Spiking Element for Neural Networks. *Nano Lett.* **2020**, 20, 8059–8066.

- (5) Khan, S.; et al. Superconducting optoelectronic single-photon synapses. *Nature electronics* **2022**, *5*, 650–659.

- (6) Lecocq, F.; et al. Control and readout of a superconducting qubit using a photonic link. *Nature* **2021**, *591*, *575*–*579*.

- (7) Chen, W.; Rylyakov, A. V.; Patel, V.; Lukens, J. E.; Likharev, K. K. Superconductor digital frequency divider operating up to 750 GHz. *Appl. Phys. Lett.* **1998**, 73, 2817–2819.

- (8) Chen, W.; Rylyakov, A. V.; Patel, V.; Lukens, J. E.; Likharev, K. K. Rapid single flux quantum T-flip flop operating up to 770 GHz. *IEEE Transactions on Applied Superconductivity* **1999**, *9*, 3212–3215.

- (9) Nagasawa, S.; Hinode, K.; Satoh, T.; Kitagawa, Y.; Hidaka, M. Design of all-dc-powered high-speed single flux quantum random access memory based on a pipeline structure for memory cell arrays. *Supercond. Sci. Technol.* **2006**, *19*, S325.

- (10) Ryazanov, V. V.; et al. Magnetic Josephson Junction Technology for Digital and Memory Applications. *Physics Procedia* **2012**, *36*, 35–41.

- (11) Alam, S.; Hossain, M. S.; Aziz, A. A cryogenic memory array based on superconducting memristors. *Appl. Phys. Lett.* **2021**, *119*, 082602.

- (12) McCaughan, A. N.; Berggren, K. K. A Superconducting-Nanowire Three-Terminal Electrothermal Device. *Nano Lett.* **2014**, 14, 5748–5753.

- (13) Buzzi, A.; Castellani, M.; Foster, R. A.; Medeiros, O.; Colangelo, M.; Berggren, K. K. A nanocryotron memory and logic family. *Appl. Phys. Lett.* **2023**, *122*, 142601.

- (14) Suzuki, M.; Maezawa, M.; Hirayama, F. Effects of magnetic fields induced by bias currents on operation of RSFQ circuits. *Physica C: Superconductivity* **2004**, *412*–414, 1576–1579.

- (15) Goldobin, E.; Sickinger, H.; Weides, M.; Ruppelt, N.; Kohlstedt, H.; Kleiner, R.; Koelle, D. Memory cell based on a  $\varphi$  Josephson junction. *Appl. Phys. Lett.* **2013**, *102*, 242602.

- (16) Katam, N. K.; Pedram, M. Logic Optimization, Complex Cell Design, and Retiming of Single Flux Quantum Circuits. *IEEE Transactions on Applied Superconductivity* **2018**, 28, 1–9.

- (17) Tang, G. M.; Qu, P. Y.; Ye, X. C.; Fan, D. R. Logic Design of a 16-bit Bit-Slice Arithmetic Logic Unit for 32-/64-bit RSFQ Microprocessors. *IEEE Transactions on Applied Superconductivity* **2018**, 28, 1–5.

- (18) Bunyk, P.; Likharev, K.; Zinoviev, D. RSFQ TECHNOLOGY: PHYSICS AND DEVICES. *International Journal of High Speed Electronics and Systems* **2001**, *11*, 257–305.

- (19) Razmkhah, S.; Pedram, M. High-density superconductive logic circuits utilizing 0 and  $\pi$  josephson junctions. *Engineering Research Express* **2024**, *6*, 015307.

- (20) Zhao, Q.-Y.; et al. A compact superconducting nanowire memory element operated by nanowire cryotrons. *Supercond. Sci. Technol.* **2018**, *31*, 035009.

- (21) Paolucci, F.; De Simoni, G.; Solinas, P.; Strambini, E.; Puglia, C.; Ligato, N.; Giazotto, F. Field-effect control of metallic superconducting systems. *AVS Quantum Science* **2019**, *1*, 016501.

- (22) Puglia, C.; De Simoni, G.; Giazotto, F. Gate Control of Superconductivity in Mesoscopic All-Metallic Devices. *Materials* **2021**, *14*, 1243.

- (23) Ritter, M. F.; Fuhrer, A.; Haxell, D. Z.; Hart, S.; Gumann, P.; Riel, H.; Nichele, F. A superconducting switch actuated by injection of high-energy electrons. *Nat. Commun.* **2021**, *12*, 1266.

- (24) Ritter, M. F.; et al. Out-of-equilibrium phonons in gated superconducting switches. *Nature electronics* **2022**, *5*, 71–77.

- (25) Ruf, L.; Puglia, C.; Elalaily, T.; De Simoni, G.; Joint, F.; Berke, M.; Koch, J.; Iorio, A.; Khorshidian, S.; Makk, P. Gate control of superconducting current: Mechanisms, parameters, and technological potential. *Applied Physics Reviews* **2024**, *11*, 041314.

- (26) Ruf, L.; Scheer, E.; Di Bernardo, A. High-Performance Gate-Controlled Superconducting Switches: Large Output Voltage and Reproducibility. ACS Nano 2024, 18, 20600–20610.

- (27) Lee, S.-B.; Hutchinson, G. D; Williams, D. A; Hasko, D. G; Ahmed, H. Superconducting nanotransistor based digital logic gates. *Nanotechnology* **2003**, *14*, 188.

- (28) Baghdadi, R.; et al. Multilayered Heater Nanocryotron: A Superconducting-Nanowire-Based Thermal Switch. *Physical Review Applied* **2020**, *14*, 054011.

- (29) Chen, B.; Xue, H.; Pan, H.; Zhu, L.; Yan, X.; Wang, J.; Song, Y.; An, Z. Reconfigurable memlogic long wave infrared sensing with superconductors. *Light: Science & Applications* **2024**, *13*, 97.

- (30) Butters, B. A.; et al. A scalable superconducting nanowire memory cell and preliminary array test. *Supercond. Sci. Technol.* **2021**, 34, 035003.

- (31) Sidorova, M.; Semenov, A. D.; Hübers, H. W.; Gyger, S.; Steinhauer, S. Phonon heat capacity and self-heating normal domains in NbTiN nanostrips. *Supercond. Sci. Technol.* **2022**, *35*, 105005.

- (32) International technology roadmap for semiconductors 2.0 2015 edition. (2015). https://www.semiconductors.org/resources/2015-international-technology-roadmap-for-semiconductors-itrs (accessed Nov. 15, 2024).

- (33) Datta, S.; Chakraborty, W.; Radosavljevic, M. Toward attojoule switching energy in logic transistors. *Science* **2022**, *378*, 733–740.

- (34) McCaughan, A. N.; Verma, V. B.; Buckley, S. M.; Allmaras, J. P.; Kozorezov, A. G.; Tait, A. N.; Nam, S. W.; Shainline, J. M. A superconducting thermal switch with ultrahigh impedance for interfacing superconductors to semiconductors. *Nature electronics* **2019**, 2, 451.

- (35) Zheng, K.; Zhao, Q.-Y.; Kong, L.-D.; Chen, S.; Lu, H.-Y.-B.; Tu, X.-C.; Zhang, L.-B.; Jia, X.-Q.; Chen, J.; Kang, L.; Wu, P.-H. Characterize the switching performance of a superconducting nanowire cryotron for reading superconducting nanowire single photon detectors. *Sci. Rep.* **2019**, *9*, 16345.

- (36) Uyemura, J. P. In CMOS Logic Circuit Design; Uyemura, J. P., Ed.; Springer US, 2001; pp 193–258.

- (37) You, L. Superconducting nanowire single-photon detectors for quantum information. *Nanophotonics* **2020**, *9*, 2673–2692.

- (38) Chang, J.; Los, J. W. N.; Tenorio-Pearl, J. O.; Noordzij, N.; Gourgues, R.; Guardiani, A.; Zichi, J. R.; Pereira, S. F.; Urbach, H. P.; Zwiller, V.; et al. Detecting telecom single photons with 99.5–2.07 + 0.5% system detection efficiency and high time resolution. *APL Photonics* **2021**, *6*, 036114.

- (39) Colangelo, M.; et al. Large-Area Superconducting Nanowire Single-Photon Detectors for Operation at Wavelengths up to 7.4  $\mu$ m. *Nano Lett.* **2022**, 22, 5667–5673.

- (40) Korzh, B.; et al. Demonstration of sub-3 ps temporal resolution with a superconducting nanowire single-photon detector. *Nat. Photonics* **2020**, *14*, 250–255.

- (41) McCaughan, A. N.; Zhai, Y.; Korzh, B.; Allmaras, J. P.; Oripov, B. G.; Shaw, M. D.; Nam, S. W. The thermally coupled imager: A scalable readout architecture for superconducting nanowire single photon detectors. *Appl. Phys. Lett.* **2022**, *121*, 102602.

- (42) Oripov, B. G.; et al. A superconducting nanowire single-photon camera with 400,000 pixels. *Nature* **2023**, *622*, 730–734.

- (43) Hampel, B.; Mirin, R. P.; Nam, S. W.; Verma, V. B. A 64-pixel mid-infrared single-photon imager based on superconducting nanowire detectors. *Appl. Phys. Lett.* **2024**, *124*, 042602.

- (44) Zheng, K.; et al. A Superconducting Binary Encoder with Multigate Nanowire Cryotrons. *Nano Lett.* **2020**, *20*, 3553–3559.

- (45) Lombo, A. E.; et al. A superconducting nanowire-based architecture for neuromorphic computing. *Neuromorphic Computing and Engineering* **2022**, *2*, 034011.

- (46) Huang, Y.-H.; Zhao, Q.-Y.; Hao, H.; Liu, N.-T.; Liu, Z.; Deng, J.; Yang, F.; Ru, S.-Y.; Tu, X.-C.; Zhang, L.-B.; et al. Monolithic integrated superconducting nanowire digital encoder. *Appl. Phys. Lett.* **2024**, *124*, 192601.

- (47) Castellani, M.; et al. Nanocryotron ripple counter integrated with a superconducting nanowire single-photon detector for megapixel arrays. *Physical Review Applied* **2024**, *22*, 024020.

- (48) Zhao, Q.-Y.; McCaughan, A. N.; Dane, A. E.; Berggren, K. K.; Ortlepp, T. A nanocryotron comparator can connect single-flux-quantum circuits to conventional electronics. *Supercond. Sci. Technol.* **2017**, *30*, 044002.