# 24 GHz Receiver Design

## By Simonetta Rampu

## Delft University of Technology, September 2008

A thesis submitted to the Electrical Engineering, Mathematics and Computer Science Department of Delft University of Technology in partial fulfillment of the requirements for the degree of Master of Science.

Delft University of Technology, the Netherlands © Copyright by Simonetta Rampu, September. 2007

#### Approval

Name:

Simonetta Rampu

Degree:

Master of Science

Title of Thesis:

24 GHz Receiver Design

**Committee in Charge of Approval**:

Chair:

Professor John R. Long Department of Electrical Engineering

**Committee Members**:

Professor R.A.C.M.M. van Swaaij Department of Electrical Engineering

Marco Spirito Department of Electrical Engineering

## **Table of Contents**

| Chapter 1. Introduction and Motivation               |    |

|------------------------------------------------------|----|

| 1.1 Introduction to Wireless Sensor Networks         |    |

| 1.2 Physical Layer Optimization                      |    |

| 1.3 Design objectives and approaches                 |    |

| 1.4 Thesis Outline                                   |    |

| References                                           | 7  |

| Chapter 2. Low Power Architectures and FM Detectors  | 9  |

| 2.1 Modulation Schemes                               | 9  |

| 2.2 Data Rate                                        | 11 |

| 2.3 The frequency band                               | 12 |

| 2.4 Architecture review                              |    |

| 2.4.1 Direct conversion Architecture                 | 14 |

| 2.4.2 Low-IF Architecture                            | 15 |

| 2.4.3 Super-Regenerative Architecture                | 16 |

| 2.5 Frequency Detectors                              | 18 |

| 2.5.1 The Quadricorrelator                           |    |

| 2.5.2 Foster-Seeley Discriminator                    | 19 |

| 2.5.3. Quadrature detector                           | 20 |

| 2.6 Final choices                                    | 21 |

| 2.7 System requirements and possible link budget     | 22 |

| 2.8 Conclusions                                      | 25 |

| References                                           |    |

| Chapter 3. 24 GHz WSN Front End design               | 27 |

| 3.1 Possible challenges                              |    |

| 3.2 Detection Concept and System Design              |    |

| 3.3 Double stage receiver                            |    |

| 3.3.1 Low Noise Amplifier Design                     | 32 |

| 3.3.1.1 LNA topologies                               |    |

| 3.3.1.2 Input Impedance Design                       |    |

| 3.3.1.3 Simulation results                           |    |

| 3.3.2 Mixer Design                                   |    |

| 3.3.2.1 Theory and Mixing Concept                    |    |

| 3.3.2.2 Mixer Operation                              |    |

| 3.3.2.3 Simulation results                           |    |

| 3.3.3 Coupled Filter Design within Complete Receiver |    |

| 3.3.3.1 Phase Shifter Design                         |    |

| 3.3.4 Receiver Discussion                            |    |

| 3.3.5 IF amplifier                                   |    |

| 3.3.5.1 Simulation Results                           |    |

| 3.3.6 Final receiver simulation results              |    |

| 3.4 Common Gate Input Detector                       |    |

| 3.4.1 Simulation results                             |    |

| References                                           | 74 |

| Chapter 4. IC Layout                                      | 76  |

|-----------------------------------------------------------|-----|

| 4.1 Introduction to CMOS65 Technology                     | 76  |

| 4.2 Receiver Floor Plan                                   |     |

| 4.3 LNA-Detector Layout                                   | 77  |

| 4.4 Common Gate Input Detector                            | 81  |

| 4.5 ADS Momentum <sup>TM</sup> Simulations                | 82  |

| 4.6 Post Layout Simulations                               | 85  |

| References                                                |     |

| Chapter 5. Measurement results                            |     |

| 5.1 24 GHz WSN Receiver Measurement Considerations        |     |

| 5.2 Common gate input-detector measurements               | 90  |

| 5.2.1 Input impedance and sensitivity measurement results | 91  |

| 5.3 LNA-Detector receiver measurements                    | 94  |

| 5.3.1 Input impedance and sensitivity measurement results | 94  |

| 5.4 Oscillation Discussion                                | 98  |

| Chapter 6. Summary and Recommendations                    | 102 |

| Reference                                                 | 105 |

| Appendix. Compact Receiver Design                         | 106 |

| 1.1 Front-end Design                                      | 108 |

| 1.2 Simulation results                                    | 110 |

| 1.3 Downconverted Output Level Discussion                 | 115 |

| References                                                | 116 |

## List of Figures

| Fig.1. 1 Structure of a sensor node [1]                                                                   | 2   |

|-----------------------------------------------------------------------------------------------------------|-----|

| Fig.1. 2 WSN protocol stack [1]                                                                           |     |

| Fig. 2. 1 Superture of OOK and ESK [2]                                                                    | 11  |

| Fig.2. 1 Spectra of OOK and FSK [2]                                                                       |     |

| Fig.2. 2 Range vs. channel capacity of WLAN technology<br>Fig.2. 3 Typical homodyne/zero-IF receiver [13] |     |

| Fig.2. 4Typical low-IF receiver [13]                                                                      |     |

| Fig.2. 5Typical Super regenerative receiver [5]                                                           |     |

| Fig.2. 6 Quadricorrelator architecture [17]                                                               |     |

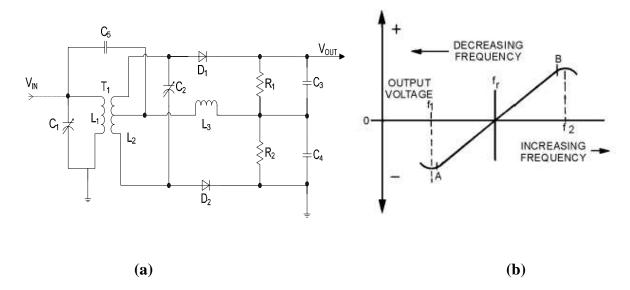

| Fig.2. 7a) Schematic implementation of Foster- Seeley detector; b) Frequency charact                      |     |

| of the detector [19]                                                                                      |     |

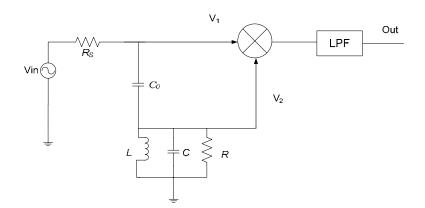

| Fig.2. 8Schematic implementation of the quadrature detector                                               |     |

| Fig.2. 9 Receiver architecture                                                                            |     |

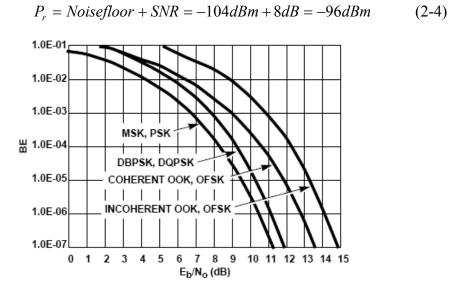

| Fig.2. 10 Probability of bit error for common modulation schemes [21]                                     |     |

|                                                                                                           |     |

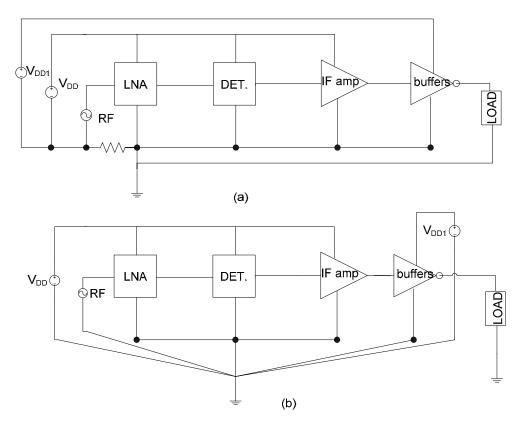

| Fig.3. 1 Block diagram                                                                                    |     |

| Fig.3. 2 System design with phase shifter diagram                                                         |     |

| Fig.3. 3 Simulated system output characteristic                                                           |     |

| Fig.3. 4 System overview of double stage receiver                                                         | 32  |

| Fig.3. 5 LNA topologies: common gate (a) and common source with inductive                                 | 2.5 |

| degeneration (b)                                                                                          |     |

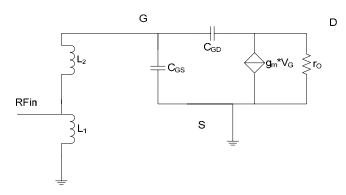

| Fig.3. 6 Small signal circuit of designed LNA                                                             |     |

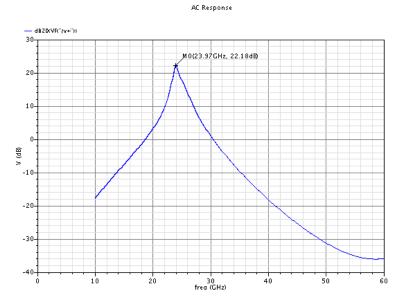

| Fig.3. 7 Schematic of LNA                                                                                 |     |

| Fig.3. 8 Simulated voltage gain                                                                           |     |

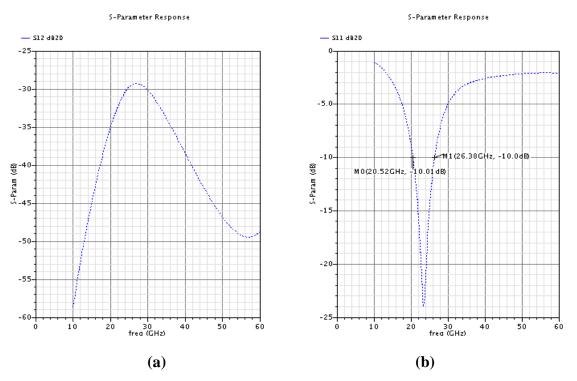

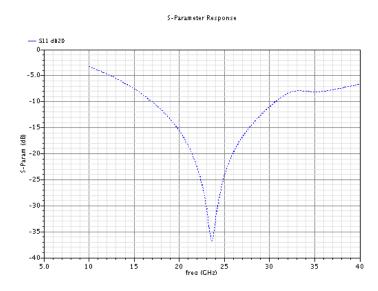

| Fig.3. 9 a) Reverse isolation, $S_{12}$ ; b) Input reflection coefficient, $S_{11}$                       |     |

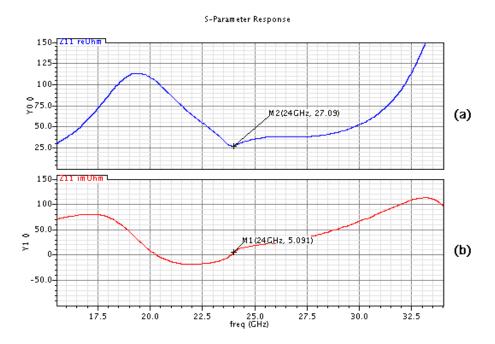

| Fig.3. 10 Simulated real (a) and imaginary part (b) of input impedance, $Z_{11}$                          |     |

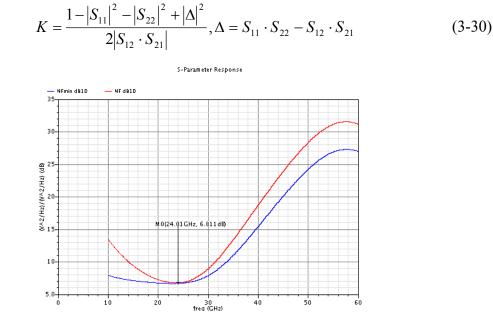

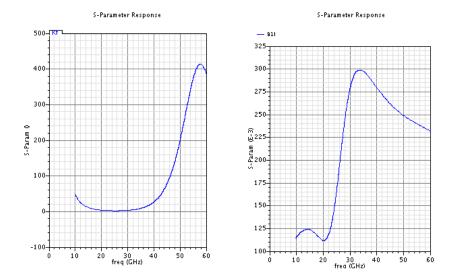

| Fig.3. 11 Simulated noise figure and minimum noise figure<br>Fig.3. 12 Stability factors                  |     |

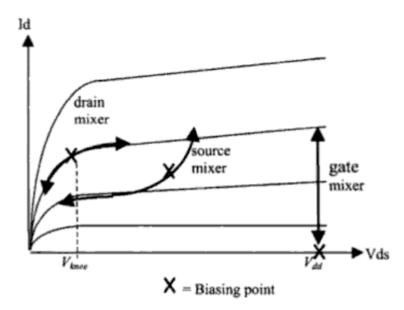

| Fig.3. 13 Bias points for gate, drain and source mixers and their paths while mixing.                     |     |

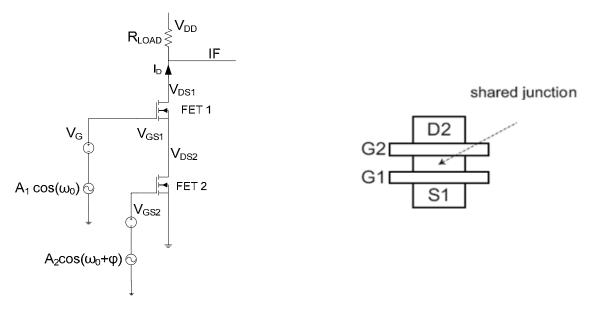

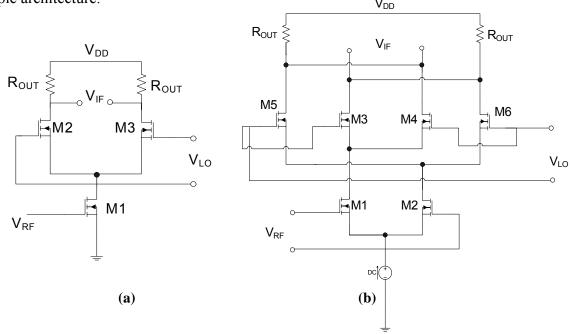

| Fig.3. 14 a) Schematic of dual gate mixer; b) shared junction                                             |     |

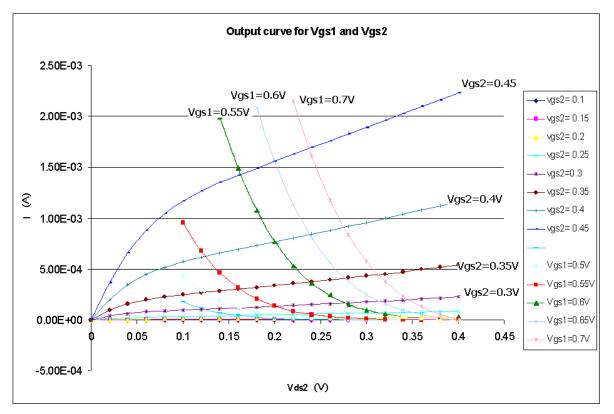

| Fig.3. 15 Lower FET drain voltage modulation by LO signal                                                 |     |

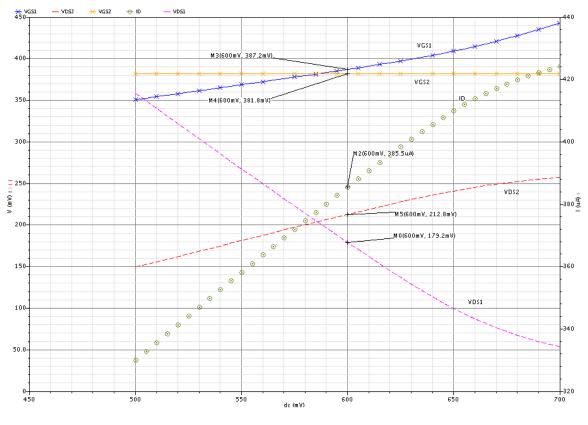

| Fig.3. 16 gm as a function of $V_{DS2}$ for different $V_{GS2}$                                           |     |

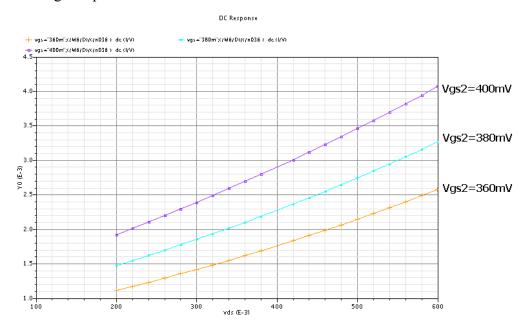

| Fig.3. 17 Simulated DC bias points                                                                        |     |

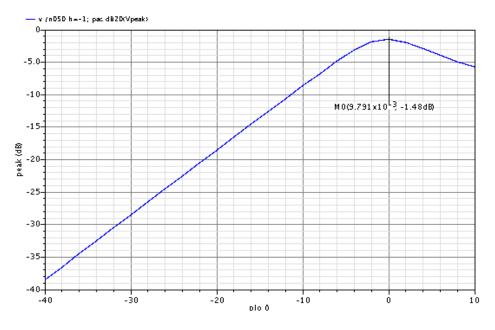

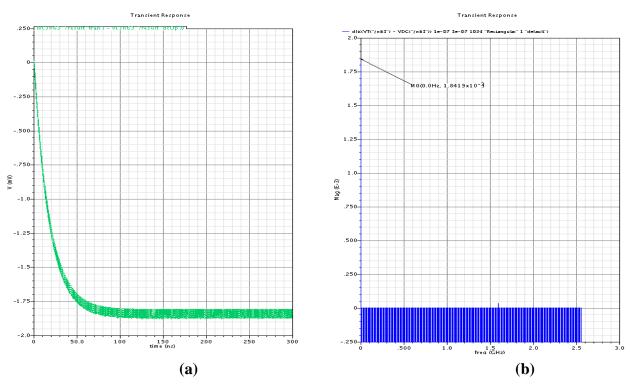

| Fig.3. 18 Conversion loss of the dual gate mixer                                                          |     |

| Fig.3. 19 a) Downconverted output signal; b) DFT transform performed on output vol                        |     |

|                                                                                                           | -   |

| Fig.3. 20 Simulated downconverted output level for a range of frequencies                                 |     |

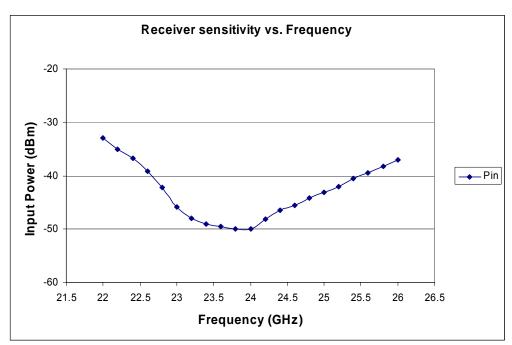

| Fig.3. 21 Simulated receiver sensitivity for different frequencies                                        |     |

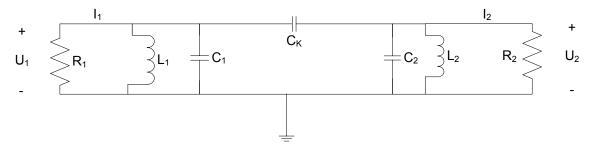

| Fig.3. 22 Schematic of coupled resonance filter                                                           | 55  |

| Fig.3. 23 Simplified schematic of the receiver                                                            |     |

| Fig.3. 24 Coupled resonance filter within the receiver                                                    | 57  |

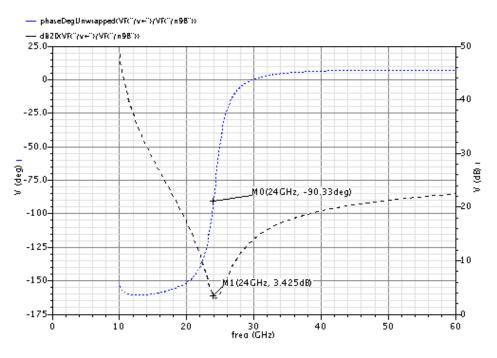

| Fig.3. 25 Simulated Phase Shift between the LO and RF signals                                             |     |

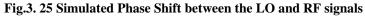

| Fig.3. 26 Coupled filter responses when $C_K$ is small (green line) and $C_K$ is larger (blue             |     |

| red curves)                                                                                               |     |

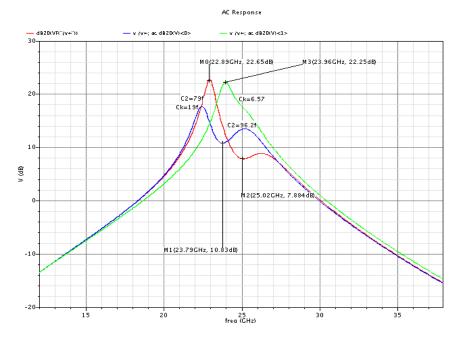

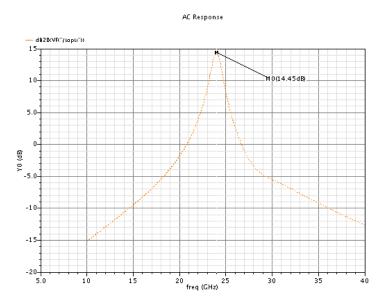

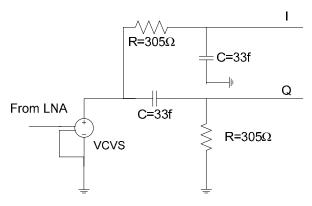

| Fig.3. 27 System level schematic of IF amplifier                                                          | 61  |

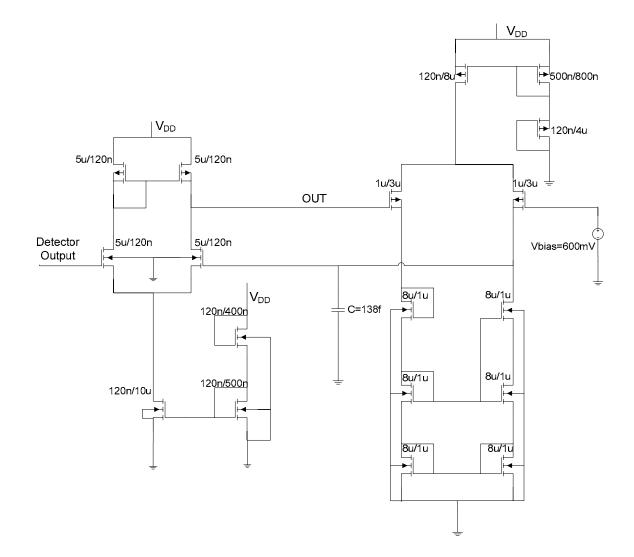

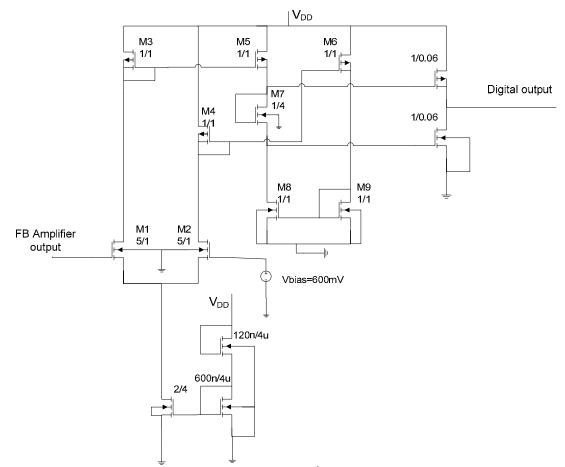

| Fig.3. 28 Transistor level schematic of feedback amplifier                                 | 63    |

|--------------------------------------------------------------------------------------------|-------|

| Fig.3. 29 Transistor level schematic of 2 <sup>nd</sup> stage of IF amplifier              | 64    |

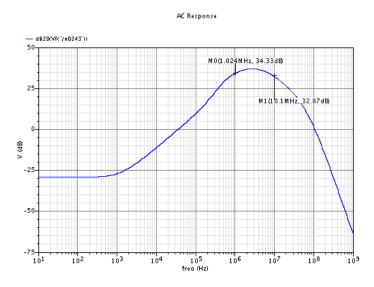

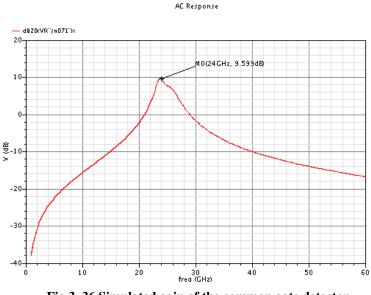

| Fig.3. 30 Frequency response of IF amplifier                                               | 65    |

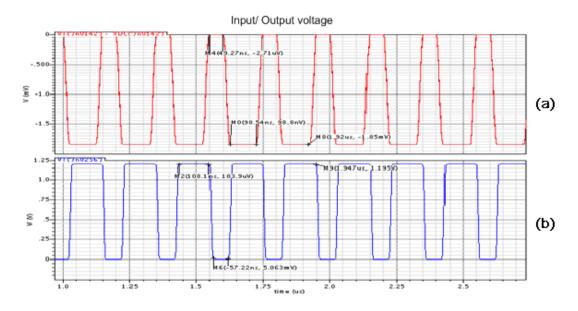

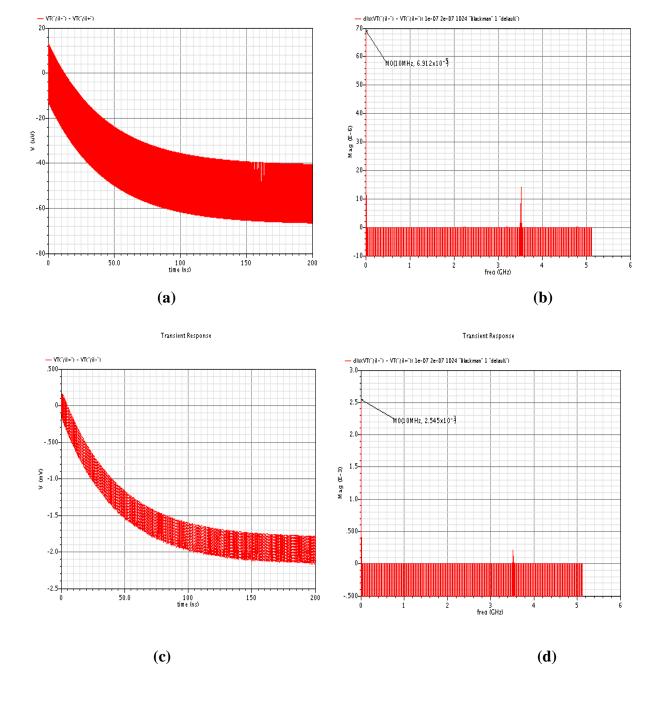

| Fig.3. 31Transient operation of IF amplifier (a) input and (b) output voltage              | 66    |

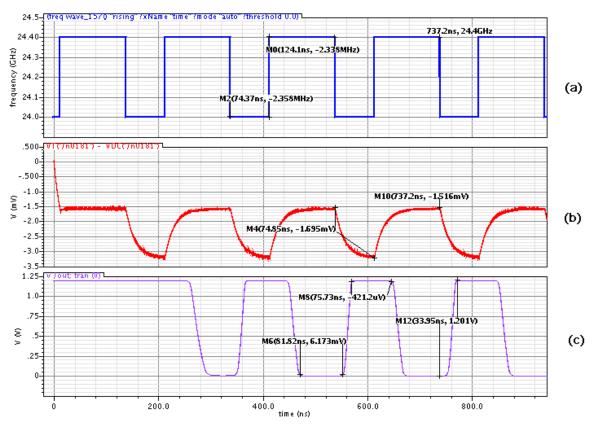

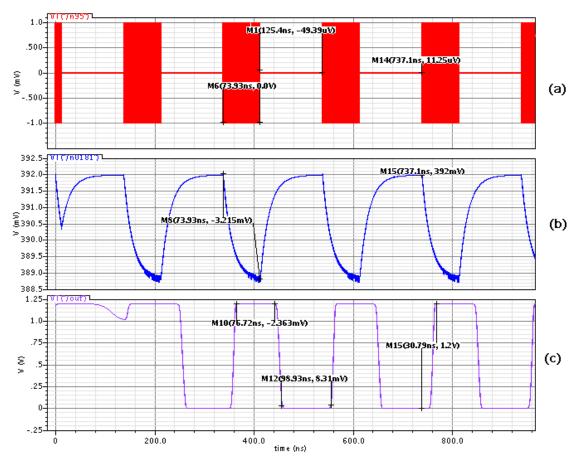

| Fig.3. 32 Receiver response at 24GHz and 24.4GHz with -50dBm input power                   | 67    |

| Fig.3. 33 Receiver response at 24GHz with -50dBm and -95dBm input power                    | 68    |

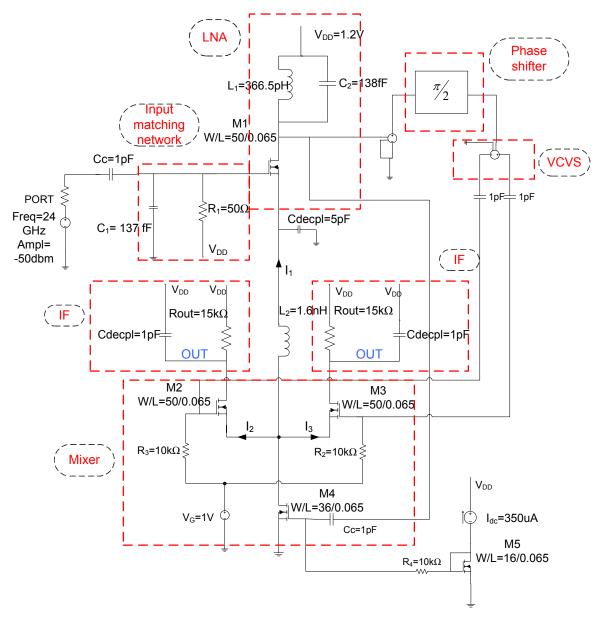

| Fig.3. 34 Schematic of LNA-detector                                                        |       |

| Fig.3. 35 Transistor level schematic of common gate detector                               |       |

| Fig.3. 36 Simulated gain of the common gate detector                                       | 72    |

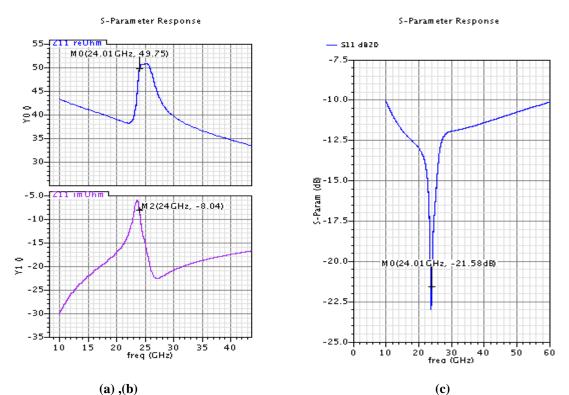

| Fig.3. 37 (a), (b) Simulated $Z_{IN}$ and (c) $S_{11}$                                     | 73    |

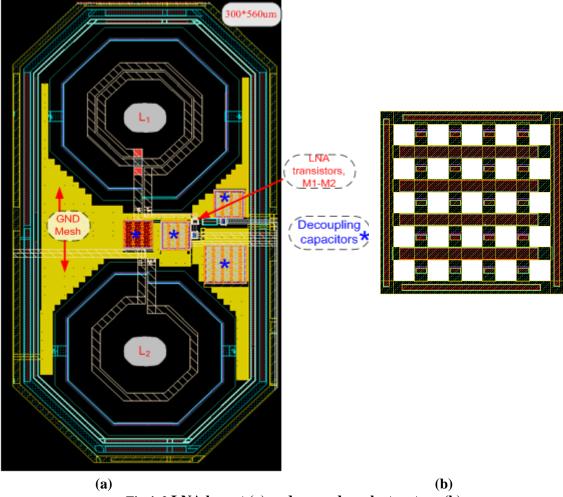

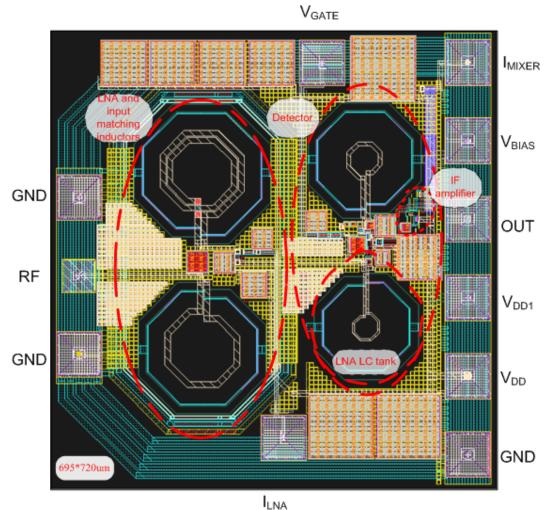

| Fig.4. 1 Floor plan for the LNA-detector receiver                                          | 77    |

| Fig.4. 2 LNA layout (a) and ground mesh structure (b)                                      |       |

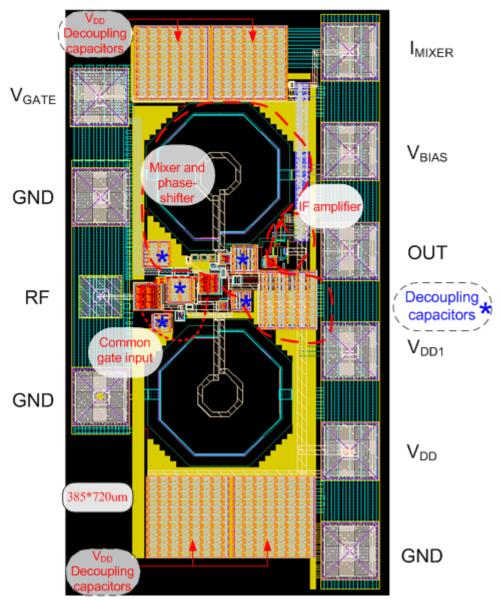

| Fig.4. 3 LNA-detector layout                                                               |       |

| Fig.4. 4 Common gate input detector                                                        |       |

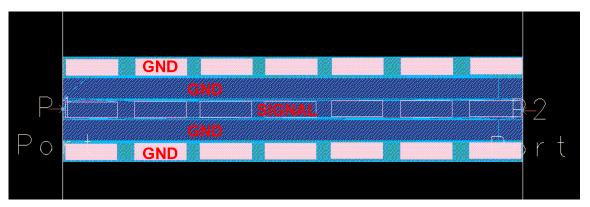

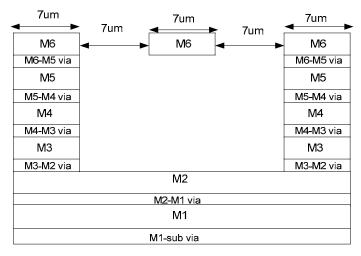

| Fig.4. 5 180µm line in Momentum                                                            |       |

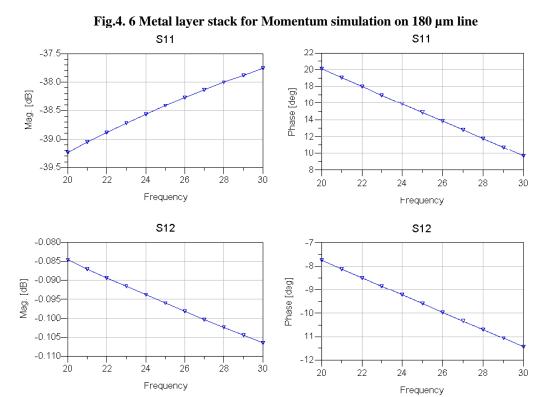

| Fig.4. 6 Metal layer stack for Momentum simulation on 180 µm line                          |       |

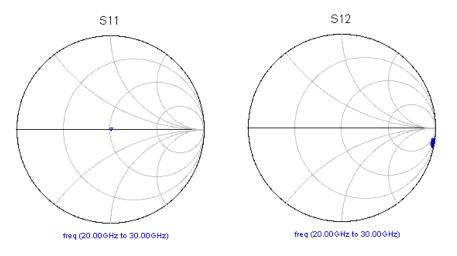

| Fig.4. 7 Rectangular and Smith chart view of S parameters                                  |       |

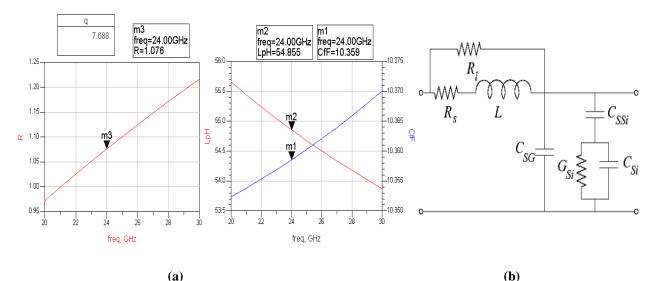

| Fig.4. 8 (a) Inductance, capacitance and resistance of 180µm line (b) Coplanar wavegu      |       |

| equivalent circuit [2].                                                                    |       |

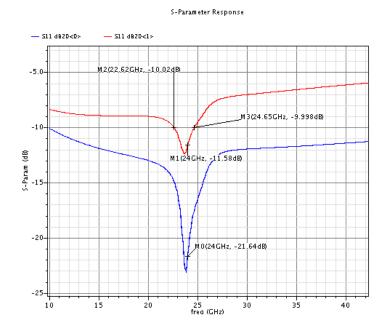

| Fig.4. 9 Input impedance matching with (red line) and without bond pad capacitance (b      | olue) |

|                                                                                            | 88    |

|                                                                                            | 0.0   |

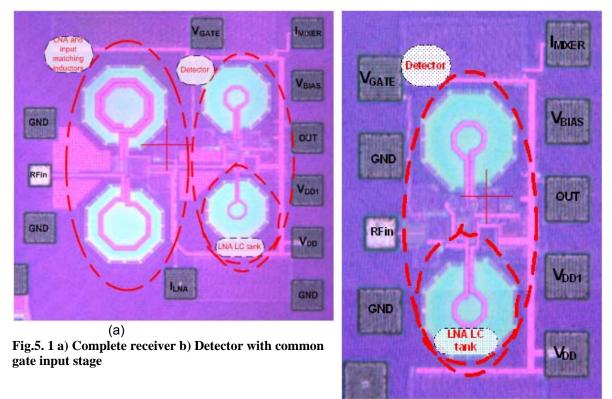

| Fig.5. 1 a) Complete receiver b) Detector with common gate input stage                     |       |

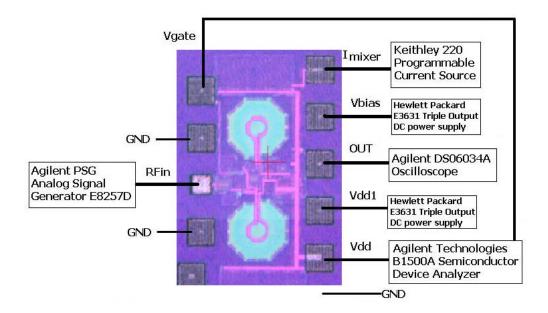

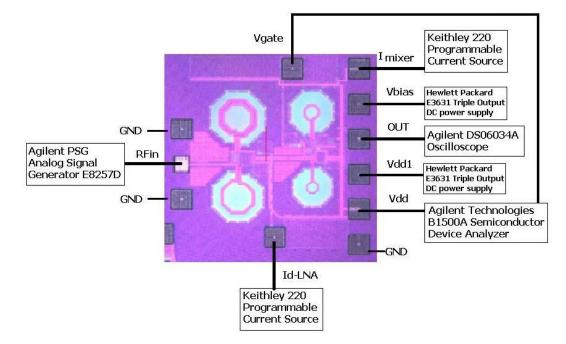

| Fig.5. 2 Measurement setup for common gate input detector                                  |       |

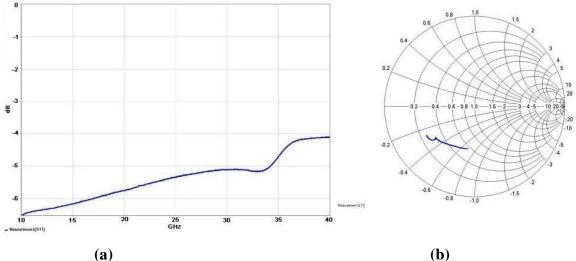

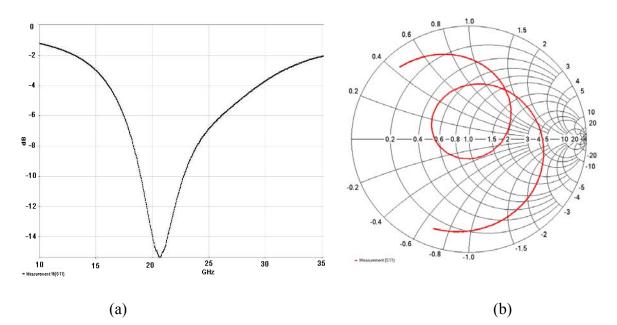

| Fig.5. 3 Detector input reflection coefficient in (a) rectangular and (b) smith chart view |       |

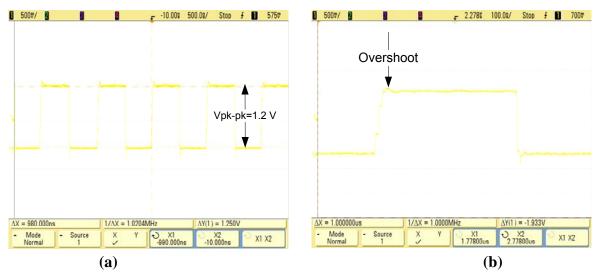

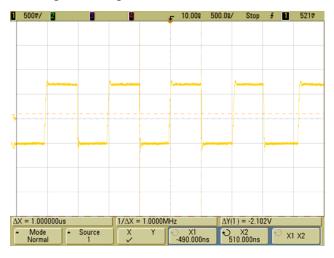

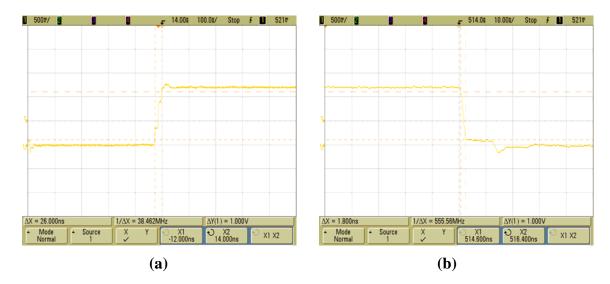

| Fig.5. 4 Output signal (a) with zoomed in view for FM modulated input (b)                  |       |

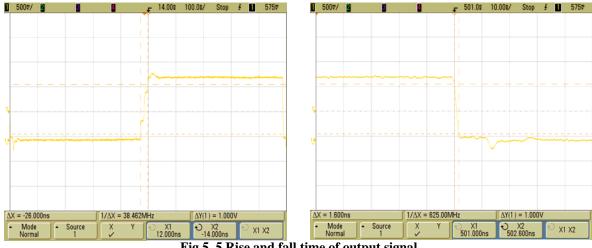

| Fig.5. 5 Rise and fall time of output signal.                                              |       |

| Fig.5. 6 Measurement setup for the LNA-detector                                            |       |

| Fig.5. 7 Complete receiver input reflection coefficient in a) rectangular and b) Smith ch  |       |

|                                                                                            |       |

| Fig.5. 8 Output signal for OOK modulated input                                             |       |

|                                                                                            | 96    |

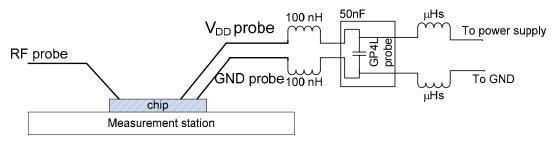

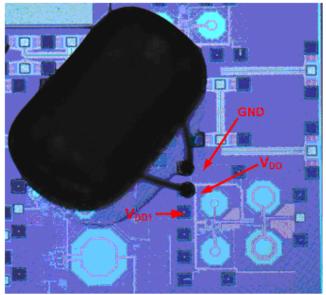

| Fig.5. 10 Equivalent circuit of measurement setup                                          |       |

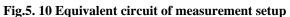

| Fig.5. 11 SMD capacitor wire-bonded on chip                                                |       |

| Fig.5. 12 (a) Distributed ground connection (b) star-ground connection                     | 101   |

| Fig. App. 1 Single balanced mixer topology (a) and Double balanced mixer topology (b)      | o).   |

|                                                                                            |       |

| Fig. App. 2 Schematic of compact receiver                                                  |       |

| Fig. App. 3 Smith Chart of impedance matching (a); network circuit (b)                     |       |

| Fig. App. 4 Input reflection coefficient, $S_{11}$                                         |       |

| Fig. App. 5 Simulated gain of compact receiver                                             |       |

| Fig. App. 6 Schematic of polyphase filter                                                  |       |

| Fig. App. 7 a) Simulated mixer output with polyphase filter phase shifter; b) DFT trans    |       |

| on output with polyphase filter phase shifter; c) Simulated mixer output with original p   |       |

| shifter; d) DFT transform on the output with original phase shifter                        |       |

## List of Tables

| Table 2. 1 Receiver specifications                               | 24 |

|------------------------------------------------------------------|----|

| Table 3. 1 LNA simulated results.                                |    |

| Table 3. 2 Simulated receiver results                            | 69 |

| Table 3. 3 Gain and NF of receiver RF blocks                     | 69 |

| Table 3. 4 Common gate input-detector simulated receiver results | 74 |

| Table 3. 5 Gain and NF of CG input- detector RF blocks           | 74 |

| Table 4. 1 Schematic vs. Post layout simulations results         |    |

| Table 5. 1 LNA-detector results with OOK modulated signal        |    |

|                                                                  |    |

# Acknowledgements

As a note on the completion of this thesis I wanted to give thanks to all those who supported me within this year.

For the circuit design and the development of this thesis special thanks goes to my daily supervisor Mihai Sanduleanu, who initiated this project and gave me the possibility to further my knowledge and gain a lot of experience in the RF world. He left his supervision to Eduard Stikvoort who became the daily supervisor from January 2008. To him I give my thanks for his insightful comments and his help for the completion of this thesis. I wish to thank my university supervisor, Prof. John Long, for his very helpful comments and support during this thesis.

From Philips Research, where this thesis has been developed, I appreciate the great help of Bob Theunissen and Henry van den Zanden regarding layout and ANY Cadence problems. Also, Dave van Goor for his help with measurements and Eduardo Alarcon for help regarding Momentum simulations. Also, Neil Bird, the group leader, for his ever present encouragement and Anton Tombeur for his insightful comments and great Belgian humor. The same thank you to all other researchers from the IC Design group who commented and helped me.

Other thanks goes to the fellow students who were working on their theses or were completing internships in this department: Neel, for his patience and support for my "why" questions, Amit, Nestor, Xc- Coby, for his calmness and always relaxed attitude, Dixian, for his help, Abhiram, Bruno, and Nahema. Also, this thesis would not have been completed without the support and great times spent with the Philips interns.

Last but not least, I wish to give special thanks to my parents who have always supported me and helped me through any problems! I thank them for the times they had to bear me talking about the thesis and trying their best to help.

### **Chapter 1. Introduction and Motivation**

The world of wireless sensor networks (WSN) has grown in the past years by showing potential for independent and robust functioning in extreme conditions. Ever since it emerged as a low cost, low power option to traditional wired sensors, many improvements have been developed, further upgrading the attainable specifications. Applications for wireless sensor networks are as broad as environment monitoring, military surveillance and smart homes [1, 2]. The main advantage of the sensor nodes is that they can be deployed in a variety of environments in a large number, such as hundreds or even thousands of nodes. Their miniature size (< 1 cm<sup>3</sup>) and extended lifetime function (>5 years) require them to be dependent on battery operation or energy scavenging [2]. Consequently, additional limits are placed on the design and structure of the sensor node for constraining power consumption. Solutions have been investigated in both networking algorithms and physical implementations of RF transceivers, which represent the main power hungry constituent of the sensor node. Further examination in the direction of optimizing the power consumed by the radio is much needed [1, 3].

This work presents a low power receiver front-end which focuses on the two basic requirements for WSN radios: bringing down the power consumption and simplifying the RF architecture. In this thesis, an overview of the system design is presented and discussed, followed by the circuit design and implementation of a 24 GHz receiver in a CMOS 65 nm technology.

#### **1.1 Introduction to Wireless Sensor Networks**

As the name suggests, wireless sensor networks are a network of closely spaced sensor nodes communicating in between each other via a wireless link. The sensor performs several functions: it detects information in the environment, processes the gathered data and further transmits it through a wireless data path. The network k can consist of a large number of sensors. For example, tens to thousands of sensors deployed around the area of interest being able to function autonomously are envisaged. Their multitude and small size are advantageous for a number of applications, including: environmental monitoring, smart buildings, and body area networks [4-6].

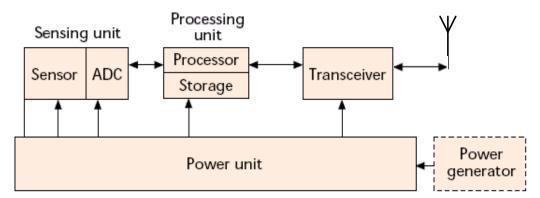

Each wireless sensor node has a certain system architecture, as shown in Fig.1.1. They include: sensing, processing, transceiver, and power units. The sensing unit provides two functions. It senses the environmental parameters and transforms the information of interest into digital signals using an analog to digital converter (ADC). Storing the signals of interest and managing the assigned tasks to be performed is performed by the processing unit. The transceiver unit sends and receives information to or from other nodes. The power unit provides the power for all the other units to perform their required assignments. The node may have other units attached depending on its application, such as the power generator unit [1]. All the units are integrated in a system-on-chip fashion, requiring them to occupy a small space and to be power aware [7].

Fig.1. 1 Structure of a sensor node [1]

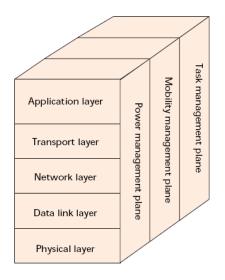

Yet another way to characterize a WSN is by the open systems interconnection (OSI) model. This model takes several so called layers into consideration and assigns different protocols to each layer. This protocol stack manages the sensor network's functioning. The protocols, shown in Fig. 1.2, enable the administration of power distribution, routing configuration, networking, and wireless communication.

The physical layer approaches ways to implement the radio taking in consideration modulation techniques, data rate, receiving and transmitting in an efficient manner. The

data link layer takes care of the data frame detection, medium access control and ensuring safe communication between the nodes. The medium access control (MAC) protocol is an integral part of the data link layer which sets a communication link for data transfer between the multitude of sensor nodes. The power, mobility and task management planes supply an integrated view on how the sensor nodes can manage and coordinate their power consumption, movement and task distribution [1].

Fig.1. 2 WSN protocol stack [1]

Among the layers presented, the implementation of the transceiver for the physical layer is focused upon in this work. This layer, as mentioned before, is the wireless communication enabling technology.

### **1.2 Physical Layer Optimization**

The sensitive issues regarding the physical layer within wireless sensor networks surround power consumption, high data rate transmission, and the modulation scheme used to encrypt the data. Among these, power consumption plays a significant role in terms of the structure of WSNs.

As mentioned above, the main characteristic of the sensor nodes is their capacity to manage tasks and further transmit the collected data on a limited power supply. They need to perform these tasks for a long time without the possibility of replenishing the power supply.

When defining a "long time", one should understand 1 to 5 years or even more. To further realize this, one can take the classic example of powering the sensor with a 1.5 V alkaline battery voltage, which has a 2000 mAh capacity and 30  $\mu$ A of leakage current. The lifetime of such a battery is defined by the following equation:

$$Lifetime = \frac{Capacity \cdot voltage}{I_{leak} \cdot voltage + P_{AVE}}$$

(1-1)

If the average power,  $P_{AVE}$ , is around 10  $\mu$ W to 100  $\mu$ W, the lifetime becomes 3 to 6 years. It is therefore the task of the sensor node to achieve this average power consumption [3]. In the following, several methods of realizing this daunting goal will be highlighted.

When figuring out the power distribution in the sensor node, it is found that the transceiver requires the most energy. The radio consumes generally more power than any other component in the sensor node. In [8], 76% of the total power is consumed by the transmitter of the transceiver. Therefore, optimizing the radio has been the attraction of much research. However, for true power optimization, the focus should be set not only on the physical layer level, but also on the MAC layer level. Radio optimization will not lead to lower power consumption if the routing, networking and data link layer of the sensor network do not have efficient algorithms to take care of the power distribution among the sensor's different components [3]. Nevertheless, the subject of this paper will only deal with constructing a power- aware radio.

As sensor nodes send and receive data packets on a set amount of time over an idle length of time or sporadically, these are therefore considered to be duty cycled, on the order of 0.1 to 1%. Duty cycling represents the ratio between the sleeping and active modes of the sensor nodes' radio. By employing such a low duty cycle, it is ensured that the radio will be woken up to perform its tasks for a very short period of time, thereby saving power. Hence, the  $P_{AVE}$  considered is based on this duty cycling, determined by limiting the time that the radio is turned on, which sets the requirements of the sensor node's overall power

consumption. Duty cycling is used by almost every WSN and has become a standard modality to achieve the average power [1, 3, 9].

Another way to reduce the power consumption is to design power-aware transceivers. Most transceivers use up to tens to hundreds of milliwatts of power when turned on. They cannot be integrated in small sensors even when duty cycling is performed. This implies that several components which consume more power have to be removed from the circuit architecture. Research has shown that one of the most power hungry components of transceivers is the phase-locked loop (PLL) synthesizer, which is required for start-up of the radio and power amplifiers, and needed for transmission of data. The PLL needs time to lock to the desired frequency before the data can be demodulated (for a receiver) or modulated (for a transmitter). Within this start-up time, the radio consumes significant amounts of power relative to the power dissipated during the active mode. For example, in [9], 38% of the active power is consumed during start-up time. When transmitting data, power amplifiers also require much energy. Transceivers based on architectures that can do without these components should be employed for a reduction in power on the order of a few mWs to less than 1mW.

Within the physical layer, power consumption is also dependent on the data bit rate required for the application and the modulation scheme chosen. Consequently, by selecting a certain data rate and modulation scheme, power optimization can be achieved as well.

Common modulation schemes implemented to limit power dissipation need to be of the simplest kind, such as: On/off keying (OOK), frequency shift keying (FSK), and M-ary modulation abound in literature [3, 9, 10]. Moving towards higher data rates, such as 5 to 10 Mbps can be used to reduce the energy per bit, which is the energy consumed by the sensor node in order to transmit or receive one bit of data [11]. These issues are discussed in chapter 2 of this work.

#### 1.3 Design objectives and approaches

The above solutions to the WSN radio design address the power consumption problem on different levels. This goal is better accomplished if a combination of the aforementioned approaches is implemented. A radio which employs duty cycling, a simple architecture, and a simple modulation scheme can ensure low power consumption. This is the direction that this work will also follow.

However, architectural simplification is the subject of this work. Choosing a low power architecture together with reducing the number of RF blocks can cut power consumption in order to achieve less than or about a mW. The traditional blocks in frequency translation architectures are reduced by selecting a different strategy for downconversion, employing frequency demodulators. Nonetheless, using frequency demodulators at 24 GHz with limited power requirements is a challenging task. Therefore, the aim of this work is to investigate whether it is possible to use frequency demodulators for downconversion at a relatively high frequency in a low power CMOS technology (with its inherent limitations). Thus, several trade-offs between power consumption, gain, linearity, and noise which are usually investigated are not emphasized in this work. Aspects such as gain and current consumption are focused upon.

In summary, this work considers the design of a 24 GHz receiver front-end employing a frequency discriminator as the downconversion block, using an FSK modulation scheme for a data rate of 5 Mbps.

#### **1.4 Thesis Outline**

Chapter 2 will present a qualitative overview of the state of the art receivers within the WSN context as well as frequency detectors. A discussion on architecture, modulation scheme, and data rate is held and a selection for each is made.

Chapter 3 provides the theoretical background, design and simulation results of the 24 GHz receiver consisting of an LNA, mixer, and phase shifter.

Chapter 4 provides information about the physical layout of the receiver test chip, post layout simulations and includes a discussion of the changes made to the receiver due to layout considerations.

Chapter 5 provides measurement results of the tested receiver and discusses what testing setup has been provided.

Finally, Chapter 6 presents a summary of what has been achieved in this thesis and presents insights for future work.

#### References

[1] I. F. Akyildiz, W. Su, Y. Sankarasubramaniam, and E. Cayirci, "A Survey on Sensor Networks", *IEEE Communications Magazine*, vol. 40, iss.8, pp. 102-114, Aug. 2002,.

[2] D. Puccinelli and M. Haenggi, "Wireless Sensor Networks: Applications and Challenges of Ubiquitous Sensing", *IEEE Circuits and Systems Magazine*, Third Quarter 2005, pp. 19-29.

[3] C. Enz,, N. Scolari, and U. Yodprasit, "Ultra Low-Power Radio Design for Wireless Sensor Networks", in *Radio-Frequency Integration Technology: Integrated Circuits for Wideband Communication and Wireless Sensor Networks Dig. Tech. Papers*, 2005., pp. 1-17.

[4] M. Haenggi, "Opportunities and Challenges in Wireless Sensor Networks," *Handbook of Sensor Networks: Compact Wireless and Wired Sensing Systems*, Boca Raton: CRC Press, 2004, pp. 1.1– 1.14

[5] R. Kurakake, Y. Nishizawa, K. Sakakura, H. Ouchi, M. Minami, and H. Morikawa,

"Magic Surfaces: A Smart Building Material for Indoor Sensing Infrastructures", in *Fourth Int. Conf. Networked Sensing Systems (INSS), 2007* pp. 213 – 220.

[6] D. Myung, B. Duncan, D. Malan, M. Welsh, M. Gaynor, and S. Moulton, "Vital dust: Wireless sensors and a sensor network for realtime patient monitoring," in *8th Annual New England Regional Trauma Conference*, 2002, pp. ??.

[7] G Asada, M Dong, T.S. Lin, F Newberg, G Pottie, W.J. Kaiser, and H.O. Marcy, "Wireless Integrated Network Sensors: Low-power System on a Chip", in *IEEE Solid-State Circuit Conference*, 1998, pp. 9-16.

[8] C.C. Enz, A. El-Hoiydi, J.-D Decotignie, and V. Peiris, "WiseNET: An Ultralow-Power Wireless Sensor Network Solution", *Computer*, vol. 37, iss. 8, pp. 62-70, Aug. 2004.

[9] E. Shih, S.H.Cho, N. Ickes, R. Min, A. Sinha, A. Wang, and A. Chandrakasan, "Physical Layer Driven Protocol and Algorithm Design for Energy Efficient Wireless Sensor Networks", in *Proc. of the 7th annual international conference on Mobile computing and networking (Mobicom)*, 2001, pp .272-286.

[10] B.W. Cook, A. Molnar, and K.S.J. Pister, "Low power RF design for sensor networks", in IEEE *Radio Frequency Integrated Circuit (RFIC) Symposium Dig. Tech. Papers*, 2005, pp. 357-360.

[11] A.Y. Wang and C.G. Sodini, "A Simple Energy Model for Wireless Microsensor Transceivers", *IEEE Comm. Mag.*, vol. 39, no. 7, pg.3205-3209, July 2004.

### **Chapter 2. Low Power Architectures and FM Detectors**

The issues regarding the physical layer optimization highlighted in the previous chapter are further discussed in this chapter. First, trade-offs between different modulation schemes and data rates are presented. Second, several state of the art receivers are presented and their architectures highlighted. Third, a discussion on frequency detectors is held and the role within the present work is displayed. Fourth, a link budget is derived presenting the system requirements. Finally, the chosen architecture, demodulator, data rate, and modulation scheme are discussed.

#### **2.1 Modulation Schemes**

As mentioned in the previous chapter, the choice of modulation scheme impacts the power performance of the receiver. The modulation directly influences the kind of receiver architecture that can be employed. For low power consumption, only the simplest architectures should be used. Therefore, higher level modulation schemes which require complex modulation and demodulation circuitry, are not considered for implementation. Such modulation schemes are

M-ary Phase Shift Keying (M-PSK), M-ary Quadrature Amplitude Modulation (M-QAM), and M-ary Frequency Shift Keying (M-FSK). M-ary modulation reduces the transmit time of the radio since it sends multiple bits per symbol, but the lower energy is not attained since the architecture requires complex analog-to-digital converters [1, 2]. A comparison between M-ary and binary modulation schemes is given in [3].

Thus, binary modulation schemes are most energy efficient, since they allow for simple analog demodulation. For example, by utilizing a continuous phase modulation system such as the binary scheme, the VCO in the transmitter can be directly modulated, removing the I and Q mixers needed in M-ary schemes [1]. The modulation schemes that are reviewed are on/off keying (OOK) and frequency-shift keying (FSK).

With an OOK modulation, the transmitter is turned on only while sending data, digital 1, while for a digital 0, the transmitter is off. This saves half of the power consumption. On the other hand, the oscillator needs to settle in less than a bit's period, which might not be fast enough in comparison to the data rate employed [2]. Furthermore, OOK is known for having poor spectral inefficiency due to varying amplitudes in the carrier wave and for being very susceptible to interferers [4].

FSK is another simple modulation scheme which can be also used in direct downconversion architectures. As OOK, FSK has simple modulation and demodulation circuitry, being ideal for low power applications. Unlike OOK, the transceiver is turned on at all times-for sending both digital 1s and 0s. An advantage of FSK which provides a solution to the flicker noise problem in direct downconversion receivers is that, for a sufficiently high FSK tone frequency, the downconverted signal is away from DC [5]. Furthermore, FSK is less responsive to interferers as the sensitivity is diminished.

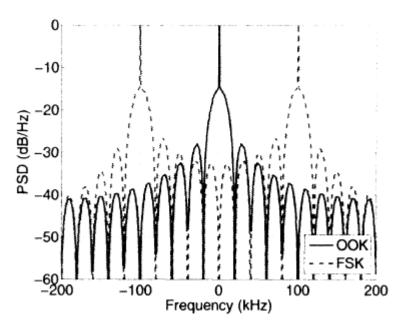

Fig. 2.1 shows the spectrum of the two modulation schemes examined above. OOK exhibits a single peak, implying that only one tone is available at a single time. FSK displays two tones at a single time as the frequency is shifted from one to another.

Due to the susceptibility to interferers, on-off keying is not selected for the receiver in this work. Instead, orthogonal FSK (OFSK) is the modulation scheme choice. OFSK has the advantage that the two keyed frequencies have no correlation: they are orthogonal to each other. Moreover, the bandwidth is higher, thus better discriminating between one tone and another.

Fig.2. 1 Spectra of OOK and FSK [2]

#### 2.2 Data Rate

Data rate selection is another issue that influences power consumption. Data rates used in WSN radios are predominantly in the order of tens to hundreds of kbps [8-12]. The common belief is that low data rate is associated with low power consumption. This statement also depends on the kind of transceiver architecture and RF blocks employed. Papers on low power radios report data rates below 1Mbps. However, energy per bit is a better metric for low power radios. Data rate evaluation can be interpreted within the total energy consumption of the radio node during active time. In [6], a model for calculating the total energy consumption of the radio node is given based on the start-up, receive and transmit times. A formula for calculating the energy per bit, *Eb/No*, is derived, as in Eq. 2-1. This energy is a WSN figure of merit, as it shows how much energy is required by the radio to transmit one bit.

$$E_{bit} = \frac{P_{LO} \cdot \left(t_{start} + t_{switch}\right)}{2 \cdot L_{pkt}} + \frac{1}{2 \cdot \eta} \cdot \gamma_{PA} \cdot d^n + \frac{P_{LO} + \frac{1}{2} \cdot P_{RX}}{r}$$

(2-1)

Where  $P_{LO}$  is the power consumption of the synthesizer;  $t_{start}$ , the settling time;  $t_{switch}$ , the time between the receive and the transmit mode;  $L_{pkt}$ , the length of the packet;  $\eta$ , the power efficiency of the power amplifier; d, the transmission distance;  $\gamma_{PA}$ , the factor depending on

the transmit/receive antenna gains; r, the data rate;  $P_{RX}$ , the power consumption of the receiver.

Since the energy per bit is inversely proportional to the data rate, a higher data rate results in lower energy per bit. For the same transceiver architecture, the derivation in [6] concludes that using higher data rate leads to lower energy per bit. To reduce the transmit time, the data can be sent in high bursts during the active time of the transmitter.

#### 2.3 The frequency band

The International Telecommunication Union issues free unlicensed bands for industrial, scientific, and medical (ISM) purposes. For the implementation of this receiver, the frequency of operation was chosen to be 24 GHz. It has a 250 MHz bandwidth, with a center frequency of 24.125 GHz. The choice of the ISM band also gives more degrees of freedom since the design does not need to adhere to any frequency, modulation, or data rate requirement specific to a certain standard. For example, the IEEE 802.15.4a standard created for the purpose of low cost low power applications, such as WSN, requires the use of BPSK or O-QPSK as modulation schemes. The data rates are limited to 20 kbit/s or 250 kbit/s, respectively, while the operation frequencies are constrained to 900MHz and 2.4GHz [7].

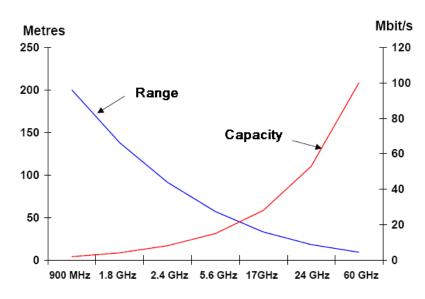

The choice of 24 GHz is both for research and practical reasons. Ever since the first working implementation concerning wireless sensor networks, the operation frequency has increased. The most successful projects were the "PicoRadio" from the UC Berkeley group which used a 100 kbit/s data rate at 1.9 GHz [8], the WiseNet transceivers which used less than 100 kbit/s data rate at frequencies less than 1 GHz [9], and a variety of other implementations at 2.4 GHz [10-12]. As shown in Fig 2.2, these low frequencies do not allow for higher data rate due to low bandwidth and SNR, independent of the modulation scheme employed. Furthermore, Fig.2.2 confirms that for higher frequencies, more capacity is available.

Another reason for moving up to the 24 GHz ISM band is the lack of interferers to corrupt the channel. At this frequency, signals can't penetrate through walls, thus reducing interference to a great extent. This is an advantage since, in comparison to the 2.4 GHz ISM band, there are significantly less interferers from other licensed bands such as WLAN and Bluetooth whose signals can go through walls.

The standard also allows for extra bandwidth. In the present system, OFSK modulation scheme is used. The extra bandwidth allows for a better signal detection. A higher channel bandwidth permits the two frequency tones in the spectrum to be farther away from each other making them easily recognizable than if they were closer to one another, as shown in Fig.2.1. The potential for an even higher data rate exists, as can be noted in Fig 2.2. One can see that for at 24 GHz, the potential data rate can be as high as 10 Mbit/s for a propagation range of 25 m. Furthermore, higher bandwidth allows more transmission of data, which can reduce the energy per bit, which is a key aspect for low power consumption.

From a circuit design point of view, the 24 GHz frequency band facilitates the miniaturization of circuit components. Passive components, such as on-chip microstrip inductors, are greatly reduced in value and thus in size. The antennas used in transceiver designs at this frequency are also diminished in size since the wavelength at 24 GHz is small-0.0125m.

Fig.2. 2 Range vs. channel capacity of WLAN technology

#### 2.4 Architecture review

The most significant power reduction can be achieved at the transceiver architecture level. As mentioned in Chapter 1, the architecture should not have power hungry components such as a frequency synthesizers, complicated modulation and demodulation circuits or even power amplifiers. The simplest kind of architectures should be aimed for. The following discussion reviews what possible architectures are wise to be employed for the application of WSNs.

#### 2.4.1 Direct conversion Architecture

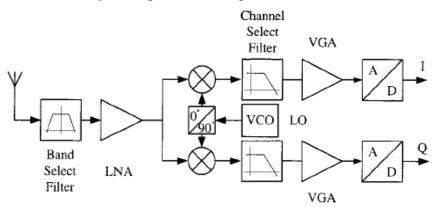

The homodyne architecture, shown in Fig.2.3, is also known as a direct conversion or zero IF. The receiver consists of a band select filter followed by a low noise amplifier (LNA) as in the classical heterodyne receiver. Since the intermediate frequency is set to zero, it allows image rejection by signal cancellation in two parallel-operating channels I and Q. The channel select filter is implemented via low pass filters which allow for easy tuning. Also, this is an easily integrated low cost solution in comparison to the bulky heterodyne receiver. The low number of chip components allows for flexibility and for integration possibility which ultimately saves power and chip area.

Fig.2. 3 Typical homodyne/zero-IF receiver [13]

Some weaknesses are observed in this architecture. Since the downconverted signal extends to DC, offset voltages might corrupt the signal. Another issue is the mismatch of the in-

phase/quadrature phase of the signal, which might alter the constellation diagram of the baseband signal. Flicker noise also constitutes a problem if CMOS is used for implementation. [13] Nevertheless, proper solutions have addressed these problems proving this architecture a viable candidate for many applications. Furthermore, many modulation schemes and data rates are applicable to this architecture.

An example for this architecture is the implementation in [14]. A direct conversion receiver is designed for the 802.15.4 standard developed especially for low power, low cost and low rate applications such as WSN. The receiver operates at 2.4GHz, and is applicable for binary phase- shift keying (BPSK), Offset quadrature phase-shift keying (O-QPSK) and parallel sequence spread spectrum (PSSS) modulation types. The LNA is designed using the inductive degeneration cascode amplifier with an extra gate source capacitor. The passive mixer converts the RF directly to baseband, dissipating no DC current. With the main focus on low power and low noise figure, the receiver achieves a NF of 3 dB, a 30 dB conversion gain, an IIP3 of -5 dBm and an IIP2 of 45 dBm. It consumes 2 mA from a 1.8 V power supply.

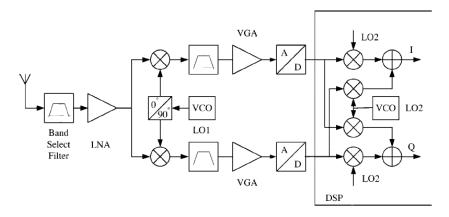

#### 2.4.2 Low-IF Architecture

Another architecture used in receivers is the low-IF, showed in Fig.2.4. It combines the advantages offered by the heterodyne and homodyne receivers. Here, the intermediate frequency is not zero, but one or two times the channel bandwidth. There are several advantages for choosing a low intermediate frequency rather than zero. The final downconversion is performed in the baseband circuitry. Due to the digital implementation, the image reject downconversion is done without mismatch in the I/Q components of the signal, a problem that occurred in the direct conversion receiver. Since the IF is on the order of MHz, also the requirements for the ADC are lowered. Another advantage over the zero-IF receiver is that DC offsets are no longer significant since the digital image reject down conversion is not sensitive to self-mixing or signal leakage. However, there is a disadvantage to this architecture: the resulting image signal can be stronger than the wanted signal. To keep up with the high linearity requirements, the ADC must then sample both the

wanted and the image signal. Along with this problem, in terms of power consumption, the number of components is higher [13].

Fig.2. 4Typical low-IF receiver [13]

An example for this architecture is the low IF transceiver given in [11]. It achieves very low power consumption, 2.5 mA in the maximum mode, from a 400 mV power supply operating at 2.4 GHz. It sacrifices image rejection in exchange for halving the power. The typical LNA is eliminated and the RF signal is directly fed to the I/Q passive mixers, which consume zero DC current. The highest power is dissipated by the VCO which produces both in-phase and quadrature outputs to drive the mixers with a high LO amplitude. In the maximum mode, the receiver achieves a noise figure of 11.8 dB, and an IIP3 of -7.5 dBm. The transmitter uses a PA with 44% efficiency, while the VCO has a phase noise of -106 dBc/Hz at 1 MHz offset.

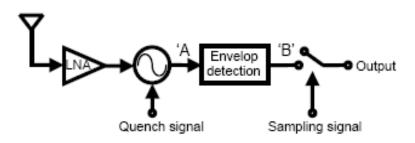

#### 2.4.3 Super-Regenerative Architecture

The third reviewed architecture is the super regenerative, shown in Fig. 2.5. It consists of an LNA, followed by an oscillator which is stopped periodically with a quenching signal. The oscillator is held near oscillation, which, in this mode, provides very high gain. By quenching the oscillator, the presence of RF signals can be distinguished. The result is fed to an envelope detector which demodulates the RF. This very simple architecture is mostly suited for low power and low cost applications such as WSN. An advantage is that a simple modulation scheme such as OOK or FSK can be employed as well. A big disadvantage to this architecture is that due to its high sensitivity (even -100 dBm) it is prone to interferers.

Also the oscillator might suffer from slow settling behavior which hinders high data rates to be used [5].

Fig.2. 5Typical Super regenerative receiver [5]

An example for this architecture is the transceiver in [15]. BAW resonators are used to reduce power consumption. The receiver consists of an isolation amplifier which converts the RF power to current and injects it to the detector oscillator. This further samples the RF input as the start-up condition for its oscillation, modifying the start-up envelope. The signal is sampled directly at RF, providing a large gain of over 55 dB. The envelope of the oscillation is detected by a nonlinear filter, while finally an OOK analog signal is formed. The receiver consumes a total of 400  $\mu$ A from a 1 V power supply and operates at 1.9 GHz. It achieves a sensitivity of -100.5 dBm. The efficiency of the low power amplifier in the transmitter is 27.5% while delivering 380  $\mu$ W.

Based on the wireless sensor network application, a receiver architecture is selected which is compatible with low power consumption, minimal number of RF blocks, and suitable modulation scheme. Even though all the architectures can achieve minimum power consumption as described in the references given, a different conversion architecture is chosen for the possibility of its simple implementation. The low-IF architecture is rejected due to the abundance of power-hungry components. Double downconversion can be accepted with a higher power consumption but not with 1 mA. Super regeneration is also affordable, but the sensitivity to interferers is too high to be finally considered.

#### **2.5 Frequency Detectors**

Frequency detectors are reviewed in this section in order to provide an alternative to standard frequency translation approaches and to provide a possible way to avoid the power hungry RF blocks that compose the architectures.

Frequency detectors are devices that recover the information content of a modulated wave. To receive FM signals, the receiver is made sensitive for frequency variations and insensitive to amplitude modulations. The response of such a frequency detector is a linear voltage to frequency characteristic.

Throughout the history of FM modulation and demodulation techniques, different classes of FM demodulators have been encountered. Early demodulators were based on slope detection which combined AM and FM detection. Later demodulators focused only on FM detectors which offered higher linearity and lower noise level.

The detectors reviewed in this section are the quadricorrelator, the Foster-Seeley discriminator and the quadrature detector. Their performance is analyzed and compared in the following sections.

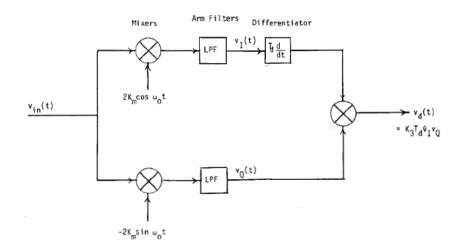

#### 2.5.1 The Quadricorrelator

The quadricorrelator, first presented by Sheaffer in 1942, provides frequency discrimination without being dependent on tuned circuits [16]. The quadricorrelator in itself is a frequency difference detector. Fig.2.6 shows the architecture of this FM detector. It consists of two mixers which convert the input passband signal into the I and Q components by multiplying them with an LO. The LO was first provided by a crystal oscillator which had a very stable frequency, as well as a stable voltage at the output of the discriminator. Thereafter, the difference terms resulting from the mixer multiplication pass through the low pass filters (LPF). The output of one of the LPF is differentiated, providing a 90° phase shift, while the other is left as is. Further on, the differentiated signal and the remaining signal are multiplied once more. The result is a DC component proportional to the frequency difference and a ripple component at twice the operation frequency. The DC component is used for FM demodulation, while the ripple component should be limited. An advantage of

this system is that the differentiator can be a high pass filter, a low pass filter, or a delay line, since the way the phase shift occurs is intrinsic to the functioning of the quadricorrelator. Also, since the phase shift is not provided by any tuned circuit, the system is very stable to temperature or process variation. Many improvements have been made to the original circuit. One version is the balanced quadricorrelator which cancels the mentioned ripple by adding another differentiator unit in the other circuit branch, and two more multipliers for cross multiplication with the low pass filtered signal [17].

Fig.2. 6 Quadricorrelator architecture [17]

A disadvantage of this detector is the number of components required for demodulation. Even though the balanced version presents more advantages in terms of cancelling the ripple and providing acceptable noise levels, it requires additional circuit blocks, which increase power consumption.

#### 2.5.2 Foster-Seeley Discriminator

Another very popular frequency detector was presented by Foster and Seeley in 1937 [18]. Fig. 2.7a shows a schematic implementation of the detector. At first, the Foster Seeley discriminator is similar to the slope detector, since it consists of two LC tanks tuned slightly below or above the center frequency. The detector is composed of a double tuned transformer in which the primary and secondary turns are tuned to the carrier frequency [19]. These convert frequency variations to amplitude variations, which are then rectified using a full wave DC rectifier and filtered to provide a DC output voltage. The output

varies in amplitude and polarity as the input varies in frequency, as shown in Fig.2.7b. For example, when the input frequency equals the carrier frequency, the output voltage is equal in amplitude but opposite in polarity; therefore it cancels out to 0. When the input frequency is higher than the center frequency the output voltage increases in the positive direction. In this case, the tank circuit acts more like an inductor, allowing more voltage on the upper branch and more voltage drop across resistor  $R_1$ . When the input frequency is lower than the center frequency, the opposite happens and the output voltage increases in the negative direction.

Fig.2. 7a) Schematic implementation of Foster- Seeley detector; b) Frequency characteristic of the detector [19]

The main disadvantage of the Foster-Seeley detector is the sensitivity to amplitude variations in the carrier signal, which appear at the detector output [19]. Moreover, a monolithic integrated circuit version is greatly hindered by the presence of the area

#### 2.5.3. Quadrature detector

consuming transformer.

The final FM detector presented in this review is the quadrature detector. Bilotti presented a new detector based on an analog multiplier [20]. The multiplier can be used for different applications including an FM detector. Fig. 2.8 shows a schematic implementation of the discriminator. The input to the quadrature detector is split in two signals of which one is fed to a tuned circuit and another to the input of a phase detector. The tuned circuit is

composed of a high reactance capacitor, which shifts the signal by 90°, and an LC tank which is resonant at the carrier frequency. In the original paper, the phase detector was an analog multiplier, which in later versions was replaced by a mixer. The mixer takes the two quadrature signals and multiplies them, producing an output proportional to the phase difference between them. The result of the multiplication is afterwards low pass filtered. In the case of an unmodulated signal, the downconverted result is an average of 0. For the case of a modulated FM signal, the total phase difference will be the sum of 90° plus the negative or positive phase change due to frequency deviation from the LC tank resonant frequency. If the frequency deviation is more positive, the voltage output increases; for the more negative deviation, the voltage output decreases. [20]

Fig.2. 8 Schematic implementation of the quadrature detector

The quadrature detector is more appropriate for IC integration, unlike the other detectors presented in this review. However, since it consists of a tuned circuit, the detector is liable to process and temperature variations. Nevertheless, its simplicity is appropriate for the WSN application.

#### 2.6 Final choices

Upon reviewing architectures most applicable to low power applications and several FM demodulators, a decision can be made as to what implementation is best in terms of the WSN requirements. The choice for the direct conversion architecture has already been made in the previous section. To reduce the power consumption and to provide a simple way to detect the OFSK signals, FM demodulators have been examined. While the

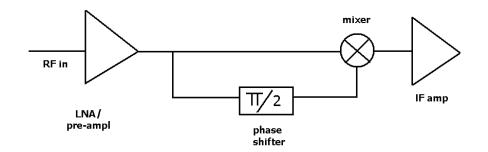

quadricorrelator and Foster Seeley detector equally present advantages in terms of performance, the quadrature detector is the only one that provides both reduced levels of power consumption and simplicity for IC integration. The implemented receiver uses the chosen demodulator and integrates it into the direct conversion architecture. As shown in Fig.2.9, the designed front end consists of an LNA, the FM demodulator and an IF amplifier.

Fig.2. 9 Receiver architecture

#### 2.7 System requirements and possible link budget

The most important performance characteristics for a receiver are its sensitivity and dynamic range. The receiver sensitivity is found by calculating the noise floor and the signal to noise ratio- SNR. This is given by Eq. 2.2 [21]:

$$SNR = \frac{E_B}{N_0} \cdot \frac{R}{B}$$

(2-2)

where  $E_B/N_0$  is the energy per bit to noise power spectral density ratio, R is the system data rate and B is the system bandwidth. Additionally,  $E_B/N_0$  depends on the modulation scheme and the desired system BER. Assuming bit error rate is  $10^{-3}$  and the modulation scheme is OFSK for a coherent detector, according to Fig. 2.10, the energy per bit to noise power spectral density ratio is 9 dB or 8 in magnitude. If the data rate is 5 Mbps and the system bandwidth 10 MHz, in view of Eq. 2-2, the SNR is 4 or 6 dB. An additional 2 dB margin is taken for extra losses.

The receiver sensitivity can be calculated by adding the SNR to the noise floor. The noise floor is found from Eq. 2-3 [21]:

Noisefloor =

$$k_B T \Delta f = 1.38 \cdot 10^{-23} \frac{J}{K} \cdot \Delta f$$

(2-3)

= -174 $dBm$  + 10log( $\Delta f$ )

where  $\Delta f$  is the bandwidth of the desired signal, indicated by approximately twice the chosen data rate. Therefore, the noise floor is -104dBm.

Receiver sensitivity without the addition of Noise Figure (NF) is given in Eq. 2-4:

Fig.2. 10 Probability of bit error for common modulation schemes [21]

Additionally, the minimum detectable signal is:

$$MDS = Noisefloor + SNR + NF$$

(2-5)

The transmit power equals [21]:

$$P_T = MDS - G_{TX} - G_{TR} + L_{fs} + Fade Margin$$

(2-6)

where  $G_{TX}$  and  $G_{RX}$  are the transmit antenna gain and receive antenna gain, respectively and  $L_{fs}$  the propagation loss. The fade margin represents the extra power the transmitter has to radiate to overcome the multipath interference. The fade margin is usually taken as 20 to 30 dB depending on link reliability. The antenna transmit and receive gain is taken as 5 dBi since patch antennas which provide high gain at these frequencies can be used. The  $\lambda/4$  patch antennas are furthermore small in size-3mm\*3mm- since the wavelength at 24 GHz is only 0.0125 m. The propagation loss is determined by Eq. 2-7 [21]:

$$L_{fs} = 20 \cdot \log\left(\frac{4 \cdot \pi \cdot d}{\lambda}\right) \tag{2-7}$$

where *d* is the distance between receiver and transmitter and  $\lambda$  is the wavelength. Given the wavelength of 0.0125 m and the distance between the sensor nodes is 1 m,  $L_{fs}$  is 60 dB. The transmitter specification for the transmit power is -10 dBm.

In view of Eq. 2-6:

$MDS = P_T$ -Fade Margin -  $L_{fs}$ +  $G_{TX}$ +  $G_{RX}$ =-20-60-10+10=-80 dB. From Eq. 2-5, the Noise Figure is estimated to be:

NF=MDS-Noisefloor -SNR= -80+96=16 dB

The receiver sensitivity is given then by:

$P_r$  = Noisefloor + SNR + NF + FM=-104+8+16+20= -60 dB

Although the previous derivation regarding receiver sensitivity leads to a usual result, it is expected that the input power is too small. This is due to the inherent functioning of the FM demodulator and the restricted 1 mA current consumption. As explained in section 2.5.3, the signal swing at the detector input determines the value of the downconverted signal. The signal swing is limited by the gain of the LNA prior to the detector, which in turn is limited by the current restriction. This is imposed as a figure of merit for the front-end design to examine whether the goal of this work can be accomplished. Also, linearity calculations for the link budget are not performed since the receiver inputs are small amplitude signals, posing limited distortion problems. Intermodulation distortion is not calculated since limited interferers, IIP3 can be sufficiently low to accommodate them. [22]

| RF frequency         | 24 GHz   |

|----------------------|----------|

| RF bandwidth         | 250 MHz  |

| RF input impedance   | 50 Ω     |

| Receiver sensitivity | <-60 dBm |

| NF                   | <16 dB   |

| Data rate            | 5 Mbps   |

| Transmit power       | -10 dBm  |

| Data link            | <1 m     |

| Current consumption  | <1 mA    |

| Supply voltage       | 1.2 V    |

Table 2. 1 Receiver specifications

#### **2.8 Conclusions**

This chapter reviewed the receiver architectures that lend themselves to the application of wireless sensor networks. A set of FM detectors as an alternative to the high power consuming RF downconversion blocks was also examined. Ideas with regard to limiting power dissipation such as choosing simple modulation schemes and a high data rate were also investigated. The next chapter presents the design strategy of the receiver based on the chosen architecture and FM detector. Two receiver implementations are presented from which one is selected for tape out.

#### References

[1] A. Chandrakasan, R. Min, M. Bhardwaj, S. Cho and A. Wang, "Power Aware Wireless

Microsensor Systems", in Proc. of the 32<sup>nd</sup> European Solid-State Device Research Conference, 2002, pp. 37–44.

[2] C. Enz,, N. Scolari, and U. Yodprasit, "Ultra Low-Power Radio Design for Wireless Sensor Networks", in *Radio-Frequency Integration Technology: Integrated Circuits for Wideband Communication and Wireless Sensor Networks Dig. Tech. Papers*, 2005, pp. 1-17.

[3] A. Wang, S. Cho, C.G. Sodini and A. P.Chandrakasan "Energy Efficient Modulation and MAC for Asymmetric RF Microsensor Systems" in *International Symposium on Low Power Electronics and Design*, pp. 106–111, Aug. 2001.

[4] D.C. Daly and A.P. Chandrakasan, "An Energy Efficient OOK Transceiver for Wireless Sensor Networks", *IEEE Journal Of Solid-State Circuits*, Vol. 42, No. 5, pp. 1003-1011, May 2007.

[5] W.-C.Fang, T.-H. Lin, "Low-Power Radio Design for Wireless Smart Sensor Networks", in *International Conference on Intelligent Information Hiding and Multimedia Signal Processing (IIH-MSP)*, 2006, pp.583-586.

[6] A.Y. Wang and C.G. Sodini, "A Simple Energy Model for Wireless Microsensor Transceivers", *IEEE Comm. Mag.*, vol. 39, no. 7, pp.3205-3209, July 2004.

[7] IEEE Computer Society, "802.15.4<sup>TM</sup> Part 15.4: Wireless Medium Access Control (MAC) and Physical Layer (PHY) Specifications for Low-Rate Wireless Personal Area Networks (LR-WPANs)", 2006, pg. 38, last accessed from "ww.

[8] J.M. Rabaey, J. Ammer, T. Karalar, L. Suetfei, B. Otis, M. Sheets and T. Tuan, "PicoRadios fo wireless sensor networks: the next challenge in ultra-low power design", in *Digest of Technical Papers: IEEE International Solid-State Circuit Conference (ISSCC)* 2002, vol. 1, pp. 200 – 201.

[9] ] C.C. Enz, A. El-Hoiydi, J.-D Decotignie, and V. Peiris, "WiseNET: An Ultralow-Power Wireless Sensor Network Solution", *Computer*, vol. 37, iss. 8, pp. 62-70, Aug. 2004.

[10] J.A. M. Järvinen, J. Kaukovuori, J. Ryynänen, J. Jussila, K. Kivekas, M. Honkanen and K.A.I.

Halonen, "2.4-GHz Receiver for Sensor Applications", *IEEE Journal Of Solid-State Circuits*, vol. 40, iss.7, pp.1426–1433, July 2005.

[11] B. W. Cook, A. Berny, A. Molnar, S. Lanzisera and K.S.J Pister, "Low-Power 2.4-GHz Transceiver With Passive RX Front-End and 400-mV Supply", *IEEE Journal of Solid-State Circuits*, vol. 41, iss.12, pp.2757-2766, Dec. 2006.

[12] C. C. Enz, J. Chabloz, J. Baborowski, C. Muller and D. Ruffieux, "Building Blocks for an Ultra Low-Power MEMS-based Radio", in *IEEE International Workshop on Radio-Frequency Integration Technology (RFIT)*, 2007, pp. 158-167.

[13] A. Springer, L. Maurer, and R. Weigel, "RF System Concepts for Highly Integrated RFICs for W-CDMA Mobile Radio Terminals", *IEEE Transactions on Microwave Theory and Techniques*, vol. 50, iss. 1, pp.254–267, Jan 2002.

[14] T.-K. Nguyen, N.-J. Oh, V.-H Le and S.-G. Lee, "A Low-Power CMOS Direct Conversion Receiver With 3-dB NF and 30-kHz Flicker-Noise Corner for 915-MHz Band IEEE 802.15.4 ZigBee Standard", *IEEE Transactions On Microwave Theory And Techniques*, Vol. 54, iss. 2, pp. 735-741, Feb. 2006

[15] B. Otis, Y.H. Chee and J. Rabaey, "A 400µx-RX, 1.6mW-Tx Super-Regenerative Transceiver for Wireless Sensor Networks", in *Digest of Technical Papers: IEEE International Solid-State Circuit Conference (ISSCC)* 2005, vol.1, pp. 396-397.

[16] C. F. Sheaffer, "The Zero-Beat Method of Frequency Discrimination", *Proceedings of the I.R.E.*, vol.30, iss.8, pp. 365-367, Aug 1942.

[17] F. M. Gardner, "Properties of Frequency Difference Detectors", *IEEE Transactions On Communications*, vol. 33, iss. 2, pp.131-138, Feb. 1985.

[18] D.E. Foster and S.W. Seeley, "Automatic Tuning, Simplified Circuits, and Design Practice", *Proceedings of the IRE*, vol.25, iss.3, pp.289-313, March 1937.

[19] Peter Vizmuller, "RF Design Guide: Systems, Circuits, and Equations", pg. 70-100, ISBN: 9780890067543, Artech House Publishers, Boston, USA, March 1995.

[20] A. Bilotti, "Applications of a Monolithic Analog Multiplier", *IEEE Journal Of Solid-State Circuits*, vol. 3, iss. 4, pp.373-380, Dec.1968.

[21] Jim Zyren, Al Petrick, "Tutorial on Basic Link Budget Analysis", application note June 1998 AN9804.1 <u>http://www.sss-mag.com/pdf/an9804.pdf</u>

[22] W.Wu, "17 GHz Receiver Front-end Design", Master Thesis, TU Delft, Feb.2007

### Chapter 3. 24 GHz WSN Front End design

This chapter presents the theory, design and simulation results of the front end. The concept behind the design is initially presented. Afterwards, the receiver is presented, discussing specifications and drawbacks. The individual RF blocks are presented and discussed in terms of the receiver specifications obtained in the last section of the previous chapter.

#### 3.1 Possible challenges

Decreasing power consumption and simplifying the architecture, regarded as design goals in Chapter 1, face some considerable challenges. Firstly, the 1 mA current consumption greatly restricts the kind of architecture, as discussed in Chapter 2. Secondly, at an operation frequency of 24 GHz, each circuit component has added parasitic behavior.

The low current constraint limits the amount of current distributed among the different blocks of the receiver. Therefore, for a feasible implementation, the number of RF blocks used should be minimized. The current consumption also limits the voltage gain achieved by transistors. As mentioned in the last section of chapter 2, gain is a key parameter in the front-end design, since it determines the signal amplitude at the mixer input. Therefore, it is important to keep this as high as possible.

Due to the high frequency operation, parasitic behavior of components have major influence on the overall circuit performance, such as decreasing the gain and providing an extra path by which the RF signal is lost. Furthermore, the high frequency selection also implies that for any small changes in component values, the entire AC behavior changes. Therefore, these changes must be properly taken into consideration.

Another effect of high frequency operation is that more current is needed for a specified gain. At low frequencies, high gain amplifiers are easily designed, but for high gain, more current is needed to obtain the same.

### 3.2 Detection Concept and System Design

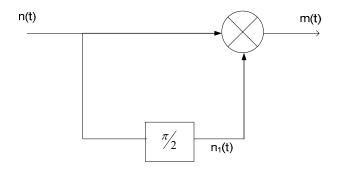

In this section, the quadrature detector is examined in terms of performance. The detector produces a maximum output when two 90° phase shifted signals are multiplied by the mixer. The output is proportional to the frequency shift from the central frequency. The detection concept is outlined in the block diagram of Fig. 3.1.

Fig.3. 1 Block diagram

Signal n(t) and  $n_1(t)$  are multiplied by the mixer to result in the output signal m(t). The two input signals can be described according to (3-1) and (3-2):

$$n(t) = A \cdot \sin\left(\omega \cdot t + \frac{\Delta f}{f_1} \cdot \sin(\omega_1 \cdot t)\right)$$

(3-1)

$$n_1(t) = A \cdot \sin\left(\omega \cdot t + \frac{\Delta f}{f_1} \cdot \sin(\omega_1 \cdot t) + \phi\right)$$

(3-2)

where *A* is the input signal amplitude,  $\omega$  is the operating frequency,  $\frac{\Delta f}{f_1}$  is the frequency deviation from the carrier frequency, and  $\phi$  is the phase shift. This signal representation is a particular form of FM modulated signals. The standard FM modulated signal is described by:

$$s(t) = A \cdot \left[ 2\pi \cdot f_c \cdot t + 2\pi \cdot k_f \cdot \int_0^t m(\tau) d\tau \right]$$

(3-3)

where  $k_f$  represents the frequency sensitivity of the modulator and m(t) represents the message signal.

Multiplying the two signals lead to the following:

$$m(t) = n(t) \cdot n_1(t) = A^2 \cdot \sin\left(\omega \cdot t + \frac{\Delta f}{f_1} \cdot \sin(\omega_1 \cdot t)\right) \cdot \sin\left(\omega \cdot t + \frac{\Delta f}{f_1} \cdot \sin(\omega_1 \cdot t) + \varphi\right)$$

28

$$=\frac{A^2}{2} \cdot \left(\cos\phi - \cos\left(2\cdot\omega\cdot t + 2\cdot\frac{\Delta f}{f_1} + \varphi\right)\right)$$

(3-4)

When  $\varphi$  is a linear function of the input signal n(t), then:  $\varphi = -\frac{\pi}{2} + \alpha \cdot x(t)$  (3-5) where  $\alpha$  is a proportionality factor.

After low pass filtering, the output signal m(t) becomes:

$$LPF(m(t)) = \frac{A^2}{2} \cdot \cos\phi = \frac{A^2}{2} \cdot \cos\left(-\frac{\pi}{2} + \alpha \cdot x(t)\right) = -\frac{A^2}{2} \cdot \sin(\alpha \cdot x(t))$$

(3-6)

Also, if  $(\alpha \cdot n(t)) \ll 1$  then

$$LPF(m(t)) \approx -\frac{A^2}{2} \cdot \alpha \cdot x(t)$$

(3-7)

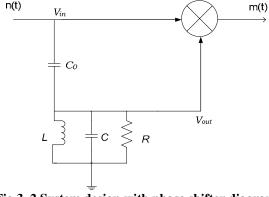

Once the low pass filtered output is determined, it is important to understand how to obtain the proportionality factor  $\alpha$ . This is further investigated in the phase shifter. To obtain a phase shifting action, the filter circuit shown in Fig 3.2 is determined.

Fig.3. 2 System design with phase shifter diagram

The transfer function of such a system is described by:

$$\frac{V_{out}}{V_{in}} = \frac{C_0}{C + C_0} \cdot \frac{L \cdot (C + C_0) \cdot s^2}{L \cdot (C + C_0) \cdot s^2 + \frac{L}{R} \cdot s + 1}$$

(3-8)

Given that:

$$\omega_0 = \frac{1}{\sqrt{L \cdot (C + C_0)}} \tag{3-9}$$

$$Q = \frac{R}{L \cdot \omega_0} = R \cdot \sqrt{\frac{C + C_0}{L}} = R \cdot (C + C_0) \cdot \omega_0$$

(3-10)

29

The frequency response of the system is:

$$H(j\omega) = \left(-\frac{C_0}{C+C_0} \cdot \frac{\omega^2}{\omega_0^2}\right) \cdot \frac{1}{\left(1-\frac{\omega^2}{\omega_0^2}\right) + j \cdot \frac{\omega}{Q \cdot \omega_0}}$$

(3-11)

The phase of  $H(j\omega)$  can be found from:

$$\varphi = \arctan\left(\frac{-\frac{\omega}{Q \cdot \omega_0}}{1 - \frac{\omega^2}{\omega_0^2}}\right)$$

(3-12)

When  $\omega \approx \omega_0$ , then  $\varphi = -\frac{\pi}{2}$ . If one further denotes,  $\varphi = -\frac{\pi}{2} + \alpha$ , with  $\alpha \ll 1$ , then  $\tan \alpha \approx \alpha$ . (3-13)

Since

$$\alpha = \varphi + \frac{\pi}{2}$$

, then

$$\alpha = \tan \alpha = \frac{1 - \frac{\omega^2}{\omega_0^2}}{\frac{\omega}{Q \cdot \omega_0}}$$

(3-14)

which leads to:

$$\alpha = \frac{Q \cdot (\omega_0 - \omega) \cdot (\omega_0 + \omega)}{\omega \cdot \omega_0}$$

(3-15)

When  $\omega \approx \omega_0$ ,

$$\alpha = \frac{2 \cdot Q(\omega_0 - \omega)}{\omega_0} \tag{3-16}$$

Therefore,

$$\varphi = -\frac{\pi}{2} + \frac{2 \cdot Q \cdot \Delta \omega}{\omega_0} \tag{3-17}$$

Inserting (3-16) into (3-7) leads to:

$$LPF(m(t)) \approx -\frac{A^2}{2} \cdot \frac{2 \cdot Q \cdot \Delta f}{f_0}$$

(3-18)

30

Equation (3-18) shows that the output is proportional to the frequency shift from the central frequency  $\omega_0$ . This is the idea highlighted at the beginning of this section. One can also notice that the output will be proportional to the square of the signal amplitude and to the inductor quality factor. Therefore, a high inductor quality factor and a high voltage swing at the input of the mixer leads to a high voltage output.

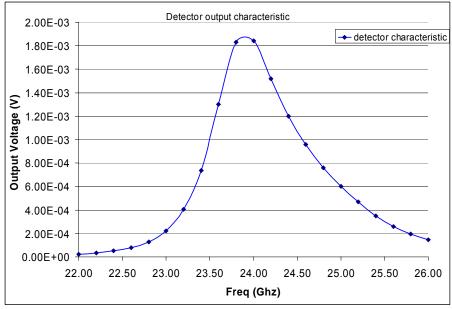

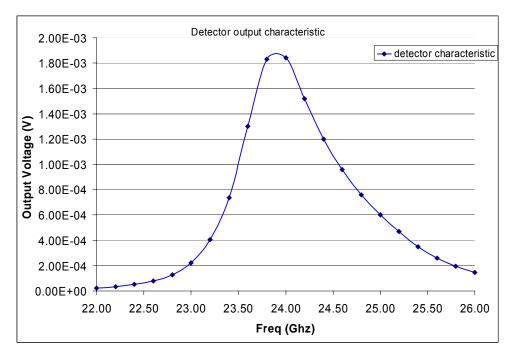

An example of the presented concept now follows. The characteristic of the detector is determined by inputting signals at different frequencies, 200 MHz apart. The phase shifter is designed to provide a 90 degrees phase shift at 24 GHz. This leads to a maximum voltage output at this frequency. Signals at other frequencies will lead to a lower output. Fig.3.3 shows a typical detector system output characteristic. For signals with a frequency closer to the center frequency, the output voltage is higher, while farther apart frequency signals are rejected. As seen in Fig.3.3, over a bandwidth of 800 MHz, from 23.6 to 24.4 GHz, the FM detector can detect signals higher than 1.2 mV. Aside from this bandwidth the detector rejects the signals. This shows a high selectivity of the entire system.

Fig.3. 3 Simulated system output characteristic

For the detector design, the aim is to achieve a DC output of 5 to 10mV, for an input level of -50dBm. Even though in Chapter 2 a derivation for the receiver sensitivity of -60 dBm

was made, the detector needs more input power to account for the relatively high signal swing to the mixer input.

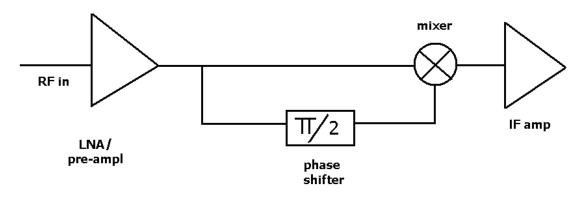

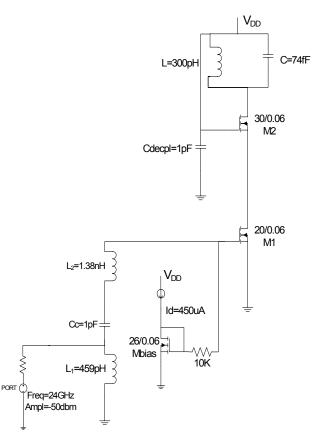

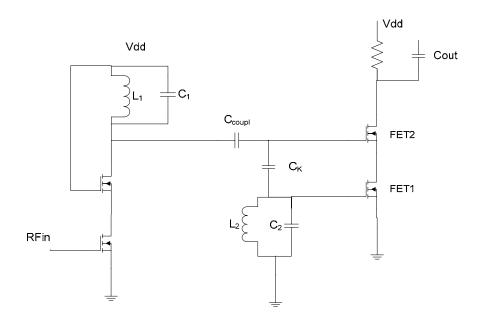

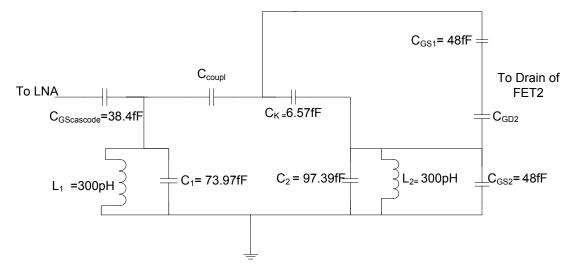

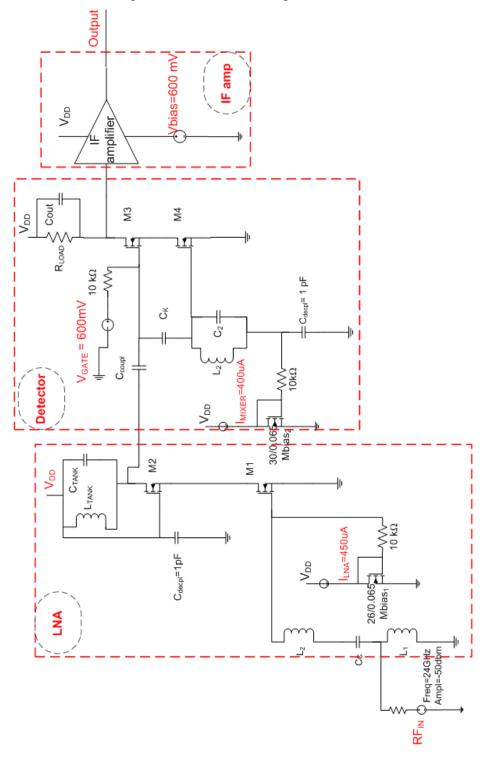

## 3.3 Double stage receiver

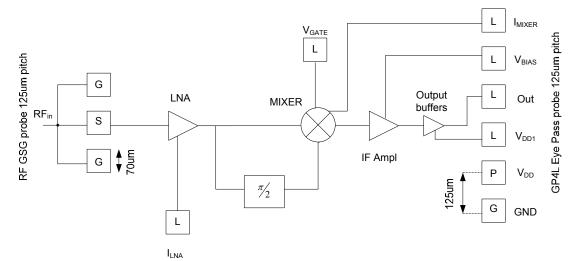

This section presents the architecture of the implemented receiver. The system overview is shown in Fig 3.4. The first block consists of a cascoded low noise amplifier or preamplifier with a resonant tank. The signal is then fed to the phase shifter and to the dual gate mixer. Following downconversion, the signal is amplified by the IF amplifier which produces a digital signal. Each individual block will be discussed in the following sections providing a theoretical background and the simulations performed.

Fig.3. 4 System overview of double stage receiver

Unless otherwise specified, the simulations are performed at a more realistic temperature of 60°C with a -50 dBm signal power.

## 3.3.1 Low Noise Amplifier Design

The low noise amplifier is the first circuit block the signal encounters coming from the antenna. Its function is to provide amplification in order to surpass the noise of the other receiver blocks while at the same time limiting the injection of its own noise. It must also sustain large signals with sufficient linearity, and provide a 50  $\Omega$  impedance match to the input source.

The most important requirements on the LNA's part are to provide conjugate matching, that is simultaneous noise and power match. Power matching is achieved by displaying the same impedance to the transistor's input as the one the source provides. In this way, it is ensured that the signal power is preserved without loss or reflections throughout the receiver blocks.

Noise matching, according to two port network theory, can be achieved when the noise figure is minimum. The noise figure is represented as [1]:

$$F = 1 + \left| \frac{v_A \cdot (Y_{cor} + Y_G) + i_u}{i_G} \right|^2$$

(3-19)

$$i_A = Y_{cor} \cdot v_A + i_u$$

(3-20)

where  $v_A$  and  $i_A$  are the noise sources of the network represented by a noise correlation matrix,  $Y_{cor}$ ;  $i_g$  is the generator noise current source;  $i_u$  is the uncorrelated noise current source and  $Y_G$  is the source admittance.

A further simplification of the equation, due to the fact that  $i_u$  and  $v_A$  are uncorrelated, leads to an expression for the noise figure in terms of impedances:

$$F = 1 + \frac{R_u}{R_G} + \frac{G_n}{R_G} \cdot \left[ (R_G + R_{cor})^2 + (X_G + X_{cor})^2 \right]$$

(3-21)

,where  $R_u$  is the uncorrelated noise resistance,  $G_n$ , the noise conductance,  $R_G$ , the generator resistor,  $R_{cor}$ , the correlation resistance,  $X_G$ , the generator reactance, and  $X_{cor}$ , the correlation reactance. From this expression, a minimum noise figure can be achieved when the derivative of F with respect to  $R_G$ , and  $X_G$  is zero. This yields an optimum resistance for

which noise is minimum:

$$R_{opt} = \sqrt{\frac{R_u}{G_n} + {R_{cor}}^2}$$

and an optimum reactance:  $X_{opt} = -X_{cor.}$

More generally, the noise figure expression can be found under the following form in terms of the generator admittance [1]:

$$F = F_{\min} + \frac{R_n}{G_g} \left[ \left( G_{opt} - G_g \right)^2 + \left( B_{opt} - B_g \right)^2 \right]$$

(3-22)

where  $Y_{opt}$  is the optimum admittance noise match;  $Y_G$ , the generator admittance;  $F_{min}$ , the minimum noise figure when  $Y_{opt}$  equals  $Y_G$ ; and  $R_n$ , the noise resistance which gives the sensitivity of the noise figure F to the source admittance.

It is well known that a noise match does not imply also an impedance match, therefore, a conjugate match is harder to obtain. For narrowband applications, conjugate matching is achieved by the inductive degenerative technique [2]. This technique has been quite popular in many LNA designs [3, 4].

Nevertheless, for wideband matching, it is not that useful. For the purpose of wideband input matching, the inductive degeneration is not employed in this work. A solution capable of spreading the input reflection coefficient over a wider frequency range, and also providing decent noise figure is aimed for. As mentioned in section 3.1, in this work, the LNA is meant to provide enough signal swing for the mixer to produce a good downconverted output voltage. Achieving a good noise figure is not a goal in this design. Primarily, voltage gain, wideband input matching, and limiting current consumption are emphasized as design goals.

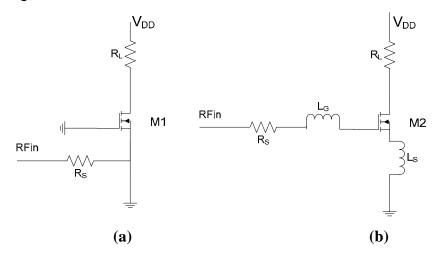

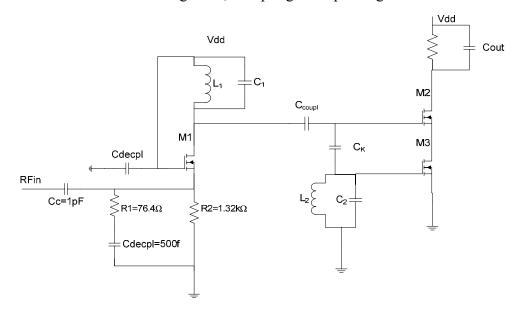

#### 3.3.1.1 LNA topologies

As mentioned in the previous section, the inductive degeneration technique which employs a common source amplifier and connects an inductor to both the gate and source, will not be used because of its narrowband application.

For a wideband application, several implementations were investigated. Wideband input matching has been achieved in [3] by employing a matching network consisting of an input LC ladder network which provides a larger tuning range. A transformer based matching network also has been implemented in [6], which achieves a conjugate match over the UWB range.

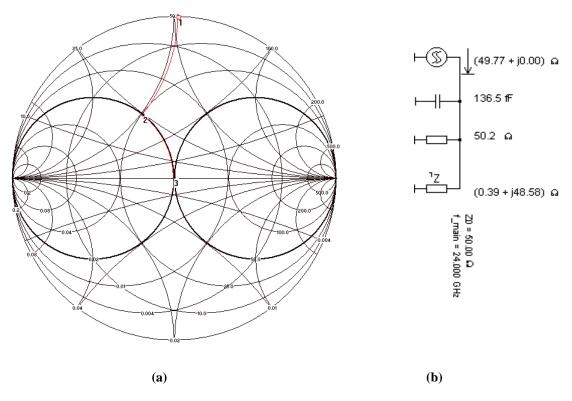

Wideband matching is desired in this receiver due to potential mismatch in the inductors from the resonant tank and from the input impedance matching network. Due to process variation in TSMC technology, the impedance matching inductors required for tuning away  $C_{GS}$  of the input transistor might produce an input reflection coefficient,  $S_{11}$ , shifted at a different frequency than was designed for. This will render operation at the LC tank design frequency useless. For a wideband match, this problem is not encountered since the reflection coefficient is designed to be lower than -10dB for a 7% variation of the operation frequency.