# A Low Power Continuous-Time Zoom ADC for Audio Applications

Gonen, Burak; Karmakar, Shoubhik; Veldhoven, Robert Van; Makinwa, Kofi

10.23919/VLSIC.2019.8778021

**Publication date**

**Document Version** Final published version

Published in

2019 Symposium on VLSI Circuits, VLSI Circuits 2019 - Digest of Technical Papers

Citation (APA)

Gonen, B., Karmakar, S., Veldhoven, R. V., & Makinwa, K. (2019). A Low Power Continuous-Time Zoom ADC for Audio Applications. In *2019 Symposium on VLSI Circuits, VLSI Circuits 2019 - Digest of Technical Papers* (pp. C224-C225). Article 8778021 IEEE. https://doi.org/10.23919/VLSIC.2019.8778021

# Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A Low Power Continuous-Time Zoom ADC for Audio Applications

Burak Gönen<sup>1</sup>, Shoubhik Karmakar<sup>1</sup>, Robert van Veldhoven<sup>2</sup>, Kofi Makinwa<sup>1</sup>

<sup>1</sup>Delft University of Technology, Delft, The Netherlands, <sup>2</sup>NXP Semiconductors, Eindhoven, The Netherlands

#### **Abstract**

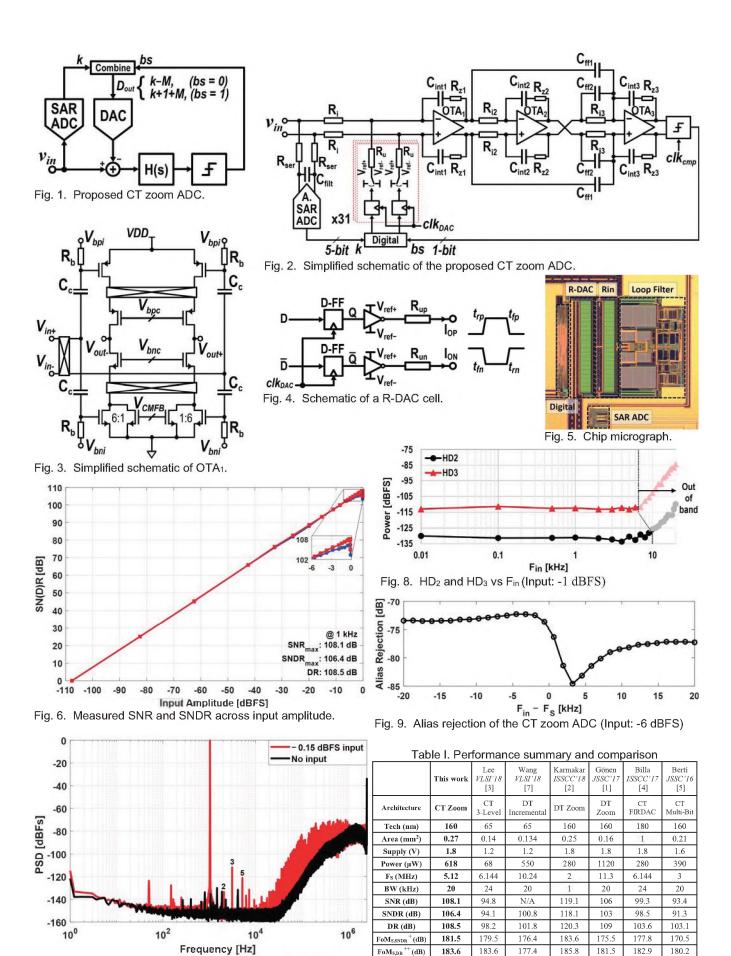

This paper presents a continuous-time (CT) zoom ADC for use in audio applications. Compared to previous zoom ADCs, its input impedance is mainly resistive, making it much easier to drive while still maintaining high energy efficiency. The prototype is fabricated in a 0.16  $\mu$ m CMOS process, occupies 0.27 mm<sup>2</sup> and achieves 108.5 dB DR, 108.1 dB SNR, 106.4 dB SNDR in a 20 kHz BW, while consuming 618  $\mu$ W. This results in a state-of-the-art Schreier FoM of 183.6 dB.

#### Introduction

ADCs intended for use in audio CODECs of battery powered devices must achieve high resolution and energy efficiency. These requirements can be met by discrete-time zoom ADCs [1,2]. However, their switched-capacitor input circuits draw high peak currents, which must be supplied by their input and reference drivers. Although CT ADCs do not have this problem, their SNR is typically limited to less than 100 dB in audio applications [3-5]. This paper describes an easy-to-drive CT zoom ADC with 108.1 dB SNR.

## Continuous-Time Zoom ADC

The proposed CT zoom ADC is shown in Fig. 1. It consists of an N-bit coarse asynchronous SAR ADC and a 1-bit fine CTDSM, which operate concurrently. The coarse ADC's output (k) satisfies  $k \cdot V_{LSB,C} < V_{in} < (k+1) \cdot V_{LSB,C}$  where  $V_{LSB,C}$  is the coarse quantization step, or least-significant bit (LSB). The references of the 1-bit CTDSM are then adjusted such that  $V_{ref+} = (k+1+M) \cdot V_{LSB,C}$  and  $V_{ref-} = (k-M) \cdot V_{LSB,C}$  where M is an over-ranging factor that ensures robustness to SAR ADC errors and delay. In this design, the speed of an asynchronous SAR ADC is optimally leveraged to allow M=1, compared to M=2 in [1]. This reduces the peak output current of OTA<sub>1</sub> by  $\sim 2\times$ , dramatically relaxing its linearity requirements.

Fig. 2 shows a simplified schematic of the ADC, which is sampled at F<sub>S</sub>=5.12MHz. For improved phase margin at F<sub>S</sub>, active-RC integrators with resistors (R<sub>z1-3</sub>) are employed. The input resistors ( $R_i=10k\Omega$ ) define the ADC's thermal noise, and are sized to ensure that self-heating-induced distortion is below -120 dB. A series resistor ( $R_{ser}$ =20k $\Omega$ ) and a small sampling capacitance (55fF), ensure that the SAR ADC's dynamic input impedance is comparatively high. Capacitors C<sub>ff1-3</sub> implement a feed-forward compensation scheme. A 31level NRZ R-DAC with DWA is used for low 1/f noise, low power and high linearity. Relatively large resistors (Ri2-3 =3.45M $\Omega$ ) and small capacitors (C<sub>int2</sub>=220fF, C<sub>int3</sub>=150fF) minimize both the loading of OTA2-3, and their area. A fixed loop delay of 1/8Fs accommodates the delay of both the comparator and the DWA logic. For robustness to process variations, the loop filter capacitors are tunable ( $\pm 15\%$ ).

In terms of noise and linearity, OTA<sub>1</sub> (Fig. 3) is the most critical active circuit block. It employs a pseudo-differential topology, whose linearity and swing is improved by the absence of tail current sources [6]. To mitigate its 1/f noise, it is chopped at F<sub>S</sub>. Via C<sub>C</sub> (=2pF), the chopped input signal is AC coupled to the gates of the N/PMOS input pairs. These are biased at constant gm via large resistors (R<sub>b</sub>=3M $\Omega$ ), thus ensuring that the coupling network's cut-off frequency is well below F<sub>S</sub>. The amplified output is then down-modulated at the

sources of the output cascodes. Since the bandwidth at these nodes is much greater than F<sub>S</sub>, the gain reduction due to chopping is negligible. CMFB regulation is achieved via an auxiliary NMOS input pair. The DC gain of OTA<sub>1</sub> is 60 dB, and due to the use of chopping, its 50Hz CMRR and PSRR exceed 70 dB and 100 dB, respectively. OTA<sub>2-3</sub> are current-starved inverters as in [1], and consume 12 times less power than OTA<sub>1</sub>.

Dynamic errors related to the transitions of an NRZ DAC, e.g. the mismatched rise/fall times of its unit currents, will cause inter-symbol interference (ISI). This, in turn, causes even-order distortion and quantization noise fold-back. DWA increases the unit transition rate, and actually worsens ISI by more than an order of magnitude, according to simulations.

In this work, a differential R-DAC is proposed to reduce the even-order distortion caused by ISI. As shown in Fig. 4, each differential unit can have four different rise/fall times:  $t_{rp}$ ,  $t_{rp}$ ,  $t_{fp}$ , and  $t_{fp}$ . The key observation is that ISI can be cancelled by matching the rising and falling edges of the positive and negative DAC units, i.e. by ensuring that  $t_{rp} = t_{rn}$ , and  $t_{fp} = t_{fn}$ . This is mainly determined by the mismatch of the DAC unit resistors  $R_{up}$  and  $R_{un}$ , and is designed to be quite low (< 1%) in order to meet the target SNDR. Since the on-resistance of the driving inverters is much less than  $R_u$ , their mismatch can be neglected. Two flip-flops are used for the positive and the negative halves of each DAC unit. These halves, including the driving inverters and flip-flops, are placed next to each other to improve their matching. The mismatch between the ISI error of different DAC units is shaped by DWA.

### **Measurement Results**

The prototype CT zoom ADC, shown in Fig. 5, has been realized in a  $0.16\mu m$  CMOS technology. It occupies an area of  $0.27~mm^2$ . The ADC consumes  $618~\mu W$  from a 1.8~V supply; the analog, DAC, clock and digital circuits consume 45%, 28%, 13% and 14%, respectively.

The measured peak SNR, SNDR and DR are 108.1 dB, 106.5 dB and 108.5 dB, respectively (Fig. 6). The measured output spectrum of the ADC is shown in Fig. 7. Peak SNDR is achieved with a -0.15 dBFS input signal, with HD<sub>3</sub> being the dominant distortion component at -113 dB, whereas the other harmonic components are below -120 dB. Fig. 8 shows HD<sub>2</sub> and HD<sub>3</sub> performance as the input frequency is swept from 10Hz to 20kHz. As expected, the shaped quantization noise becomes dominant outside this band. The coarse SAR ADC still requires an anti-aliasing filter. With an external RC low-pass filter ( $R_{ser}=20k\Omega$ ,  $C_{filt}=5pF$ ), the measured alias rejection of the overall ADC around F<sub>S</sub> is greater than -72 dB for -6 dBFS signals (Fig. 9). In Table I, the ADC's performance is summarized and compared to the state-of-theart. Despite being implemented in a relatively mature process, it achieves a FoM<sub>S,DR</sub> of 183.6 dB and FoM<sub>S,SNDR</sub> of 181.5 dB, which both correspond to state of the art energy efficiency.

# References

[1] B. Gönen, et al., JSSC, Jun. 2017 [2] S. Karmakar, et al., ISSCC, 2017 [3] C. Lee, et al., VLSI, 2018 [4] S. Billa, et al., ISSCC, 2017 [5] C. Berti, et al., JSSC, Jul. 2016 [6] M. S. Akter, et al., JSSC, Oct. 2018. [7] B. Wang, et al., VLSI, 2018

Fig. 7. Measured output spectrum (-0.15 dBFS @ 1 kHz)

\*FoMs,SNDR = SNDR + 10log(BW/Power) \*\*FoMs,DR = DR + 10log(BW/Power)