### Customizable Memory Schemes for Data Parallel Accelerators

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op

dinsdag 6 september 2011 om 10:00 uur

door

Chunyang GOU

Master of Science in Information and Communication Engineering Tsinghua University, China geboren te Sichuan, China Dit proefschrift is goedgekeurd door de promotor: Prof. dr. ir. H. J. Sips

Copromotor: Dr. ir. G. N. Gaydadjiev

Samenstelling promotiecommissie:

| Rector Magnificus              | voorzitter                                |

|--------------------------------|-------------------------------------------|

| Prof. dr. ir. H. J. Sips       | Technische Universiteit Delft, promotor   |

| Dr. ir. G. N. Gaydadjiev       | Technische Universiteit Delft, copromotor |

| Prof. dr. P. Stenström         | Chalmers University of Technology, Zweden |

| Prof. dr. A. Seznec            | IRISA/INRIA, Frankrijk                    |

| Prof. dr. J. Takala            | Tampere University of Technology, Finland |

| Prof. dr. K. G. Langendoen     | Technische Universiteit Delft             |

| Dr. G. K. Kuzmanov             | Technische Universiteit Delft             |

| Prof. dr. ir. AJ. van der Veen | Technische Universiteit Delft, reservelid |

#### ISBN 978-90-72298-23-2

Keywords: Computer Architecture, Data Parallel Accelerators, Parallel Memory Schemes, Customizable Memory Schemes

#### Copyright © 2011 Chunyang Gou

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

Cover design by Hani Alers and Nike Gunawan (www.hanike.nl) Printed in The Netherlands This thesis is dedicated to my family.

# Customizable Memory Schemes for Data Parallel Accelerators

Chunyang Gou

### Abstract

emory system efficiency is crucial for any processor to achieve high performance, especially in the case of data parallel machines. Processing capabilities of parallel lanes will be wasted, when data requests are not accomplished in a sustainable and timely manner. Irregular vector memory accesses can lead to inefficient use of the parallel banks/modules/channels and significantly degrade overall performance even when highly parallel memory systems are employed. This problem is also valid for many regular workloads exhibiting irregular vector accesses at runtime. This dissertation identifies the mismatch between the optimal access patterns required by the workloads and the physical data layout as one of the major factors for memory access inefficiency. We propose customizable memory schemes to address this issue in data parallel accelerators. More specifically, this thesis extends traditional approaches by proposing two new parallel memory schemes that alleviate bank conflicts for commonly used access patterns. We also propose a framework to capture and convey the access pattern information to the proposed parallel memory schemes. Furthermore, we describe techniques that dynamically adjust the instruction sequencer of a multithreaded vector architecture and customize the access patterns to improve on-chip, local memory efficiency. Last, we identify and exploit new locality type to dynamically adjust off-chip memory access granularity of manycore data parallel architectures, in order to improve main memory efficiency. We implemented our proposals as extensions of contemporary data parallel architectures and our evaluation results demonstrate that memory efficiency and overall system performance can be improved at minimal hardware cost, while at the same time programming overhead can be greatly reduced.

### Acknowledgements

I acknowledge the help and contributions from many people during my PhD at the computer engineering (CE) laboratory of TU Delft. First of all, I owe deep gratitude to the guidance from my supervisor, Dr. Georgi Gaydadjiev. He insisted on high quality research and always motivated me to face challenging problems. He is always open-minded to let me follow my interests and was patient with me even when I entered panic mode. He taught me how to formulate problems and abstract complexity. He sacrificed many late hours and weekends working together with me to meet the deadlines. I truly enjoyed and greatly benefited from the past several years for being his student.

I would like to express my sincere gratitude to Dr. Georgi Kuzmanov for his daily supervision during the first half of my thesis work. He helped me develop academic thinking skills, identify the research problems at the beginning, and write technical papers. His rich experience and generous guidance has greatly benefited my early academic career and the influence will definitely continue.

I am sincerely grateful to late Prof. Stamatis Vassiliadis for giving me the opportunity to study in the CE group. It was my privilege knowing him; his memory will always remain in my heart. I thank Dr. Koen Beltels for setting me on the track of the first visit to the CE group and later the many useful suggestions on both academic work and life. I am also thankful to Prof. Henk Sips for serving as my promotor, and grateful to the thesis committee professors for their invaluable feedback and comments despite the tight time schedule.

I considered myself lucky to have nice colleagues in an international environment of the CE group, without whom the life at Delft would not be complete. Many thanks to Jae Young Hur, Ioannis Sourdis, Christos Strydis, Sebastian Isaza, Arnaldo Azevedo, Dimitrios Theodoropoulos, Roel Meeuws, Vlad-Mihai Sima, Laiq Hasan and Nor Zaidi Haron for their kind help and insightful discussions which refreshed my mind from time to time. My special thanks go to past and current officemates in HB.15.230: Elena Panainte, Carlo Galuzzi, Humberto Calderón, Zubair Nawaz, Pavel Zaykov, Aqeel Wahlah, and Karthik Chandrasekar, for creating such a harmonious work place and sharing the numerous technical and non-technical chats with me. I thank Catalin Ciobanu and Bogdan Spinean for the close collaboration in the SARC accelerator memory design. I also thank Filipa Duarte and Faisal Nadeem for the nice cooperation in organizing the Computer Engineering Colloquium over the years.

Special thanks are due to the CE secretary Lidwina Tromp for her administrative assistance and generous help. My thanks are also due to Bert, Erik and Eef, the past and current CE system administrators, especially for their technical support in operating the HPC clusters used to run our simulations.

I truly appreciate the friendship with many great Chinese friends during my stay in the Netherlands. Yizhi Zhao, Zhijiang Chang and Yi Lu kindly assisted me in finding an accommodation at Delft and setting up the new career when I joined the group. Their support continued ever since. Yao Wang and Changlin Chen's joining us later strengthened our Chinese "minority" in the CE group with whom I enjoyed pleasant chats, wonderful meals and long-distance biking. Outside the group I am also grateful to Qi Jia, Jun Hou, Hongchao Pan, Yang Yang, Shiming Xu, Jin He..., for their generous help and the many unforgettable gatherings and trips we enjoyed together.

It is my privilege to work in the SARC and ENCORE projects sponsored by the European Commission. I thank all the excellent people of these projects and the fruitful collaboration with them from which I benefited a lot.

I would like to thank many wonderful teachers and friends at Tsinghua University who created the premises for me to study in the Netherlands. Particularly, I am most grateful to Prof. Weimin Zheng for introducing me to computer architecture research. Sincere gratitude also goes to Prof. Yingning Peng for directing my steps toward Computer Engineering during my master thesis work.

Last but certainly not least, I would like to thank my family. I am forever indebted to my grandparents and parents, for their endless love and unwavering support throughout my life. They taught and encouraged me to become a good person to the society. I thank my wife, Ling Zhang, for her love, patience, support, understanding and sharing the wonderful life with me. I also thank my sister for always loving and supporting her only younger brother. I sincerely thank my parents in law for their love, support and trust. I honor the memory of my grandaunt and maternal grandmother. The everlasting love from my family has always been the source of peace and inspiration in my heart.

Chunyang Gou

Delft, The Netherlands, September 2011

### Table of contents

| Ab  | stract          |                                                 | i  |  |  |

|-----|-----------------|-------------------------------------------------|----|--|--|

| Ac  | Acknowledgments |                                                 |    |  |  |

| Lis | st of Ta        | ables                                           | ix |  |  |

| Lis | st of Fi        | igures                                          | xi |  |  |

| Lis | st of A         | cronyms and Symbols                             | XV |  |  |

| 1   | Intro           | duction                                         | 1  |  |  |

|     | 1.1             | Data Parallel Architecture Evolution            | 1  |  |  |

|     | 1.2             | Programmable Data Parallel Accelerators         | 3  |  |  |

|     | 1.3             | Processor-Memory Performance Gap                | 5  |  |  |

|     | 1.4             | Parallel Memory Organizations and Accesses      | 8  |  |  |

|     | 1.5             | Problem Formulation                             | 12 |  |  |

|     | 1.6             | Machine Organization and Proposed Solutions     | 15 |  |  |

|     | 1.7             | Contributions                                   | 17 |  |  |

|     | 1.8             | Dissertation Organization                       | 18 |  |  |

| 2   | Rela            | ted Work                                        | 21 |  |  |

|     | 2.1             | Parallel Memory Schemes                         | 21 |  |  |

|     | 2.2             | Access Pattern and Data Layout Optimizations    | 28 |  |  |

|     | 2.3             | Off-chip Memory Access Scheduling               | 30 |  |  |

|     | 2.4             | Memory Access Optimizations on GPUs             | 31 |  |  |

|     |                 | 2.4.1 Avoiding GPU Shared Memory Bank Conflicts | 31 |  |  |

|     |                 | 2.4.2 GPU DRAM Access Optimizations             | 32 |  |  |

|     | 2.5             | Summary                                         | 33 |  |  |

| 3   | Conf            | lict-Free Parallel Memory Schemes               | 35 |  |  |

|     | 3.1             | Motivation                                      | 35 |  |  |

|   |      | 3.1.1 Definitions                                            | 36 |

|---|------|--------------------------------------------------------------|----|

|   |      | 3.1.2 Non-Redundant Parallel Memory Schemes Limitations      | 37 |

|   |      | 3.1.3 Strided Access in 2D Environment                       | 38 |

|   | 3.2  | Single-Affiliation Multiple-Stride Memory Scheme             | 40 |

|   |      | 3.2.1 Moving from Conflict-Free to Low Degree of Affiliation | 40 |

|   |      | 3.2.2 Hierarchical Single-Affiliation Parallel Memory Scheme | 42 |

|   |      | 3.2.3 Solving Module Conflicts in Single-Affiliation Schemes | 43 |

|   |      | 3.2.4 The Matched SAMS Scheme                                | 45 |

|   | 3.3  | 2DSMM: 2D Strided Multiaccess Memory Scheme                  | 46 |

|   | 3.4  | Hardware Design and Implementation                           | 49 |

|   |      | 3.4.1 SAMS Hardware Implementation                           | 50 |

|   |      | 3.4.2 Implementation of 2DSMM Scheme                         | 52 |

|   | 3.5  | Discussion                                                   | 65 |

|   | 3.6  | Summary                                                      | 67 |

| 4 | Prov | ding Multiple Views to Data                                  | 69 |

|   | 4.1  |                                                              | 69 |

|   | 4.2  |                                                              | 71 |

|   | 4.3  | The Extended SAMS Scheme                                     | 74 |

|   |      | 4.3.1 Original SAMS Scheme                                   | 74 |

|   |      | 4.3.2 Proposed Extensions                                    | 75 |

|   | 4.4  | Implementation and Integration                               | 77 |

|   |      | 4.4.1 SAMS Organization and Implementation                   | 77 |

|   |      | 4.4.2 Integration into the Cell SPE                          | 80 |

|   | 4.5  | Experimental Evaluation                                      | 83 |

|   | 4.6  | Summary                                                      | 92 |

| 5 | Addr | essing On-chip Bank Conflicts                                | 93 |

| • | 5.1  | •                                                            | 93 |

|   | 5.2  |                                                              | 95 |

|   |      | -                                                            | 95 |

|   |      | -                                                            | 97 |

|   | 5.3  |                                                              | 98 |

|   |      | -                                                            | 98 |

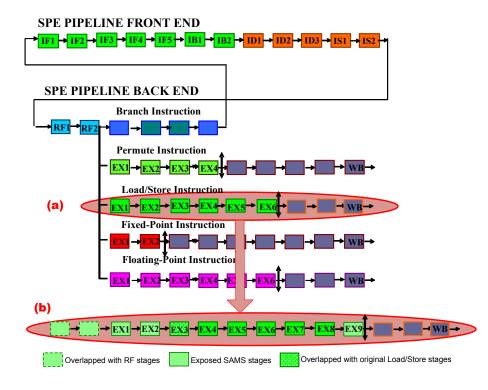

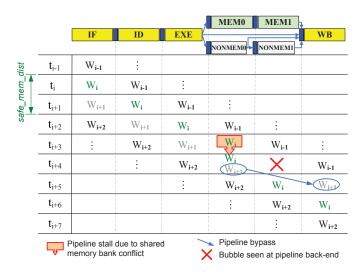

|   |      | 5.3.2 Bank Conflicts Impact on Pipeline Performance 1        | 01 |

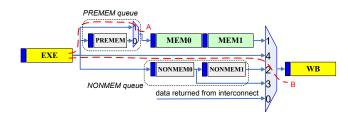

|   | 5.4  | Elastic Pipeline Design                                      | 03 |

|   |      | 5.4.1 Safe Scheduling Distance and Conflict Tolerance 1      | 04 |

|   |      | 5.4.2 Out-of-order Instruction Commitment                    | 05 |

|   |      | 5.4.3   | Extension for Large Warp Size                       |

|---|------|---------|-----------------------------------------------------|

|   |      | 5.4.4   | Hardware Overhead and Impact on Pipeline Timing 106 |

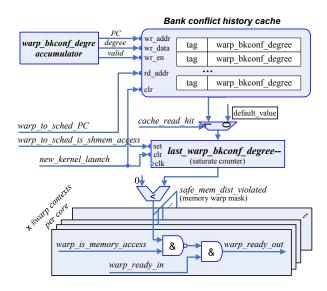

|   | 5.5  | Bank-   | conflict Aware Warp Scheduling                      |

|   |      | 5.5.1   | Obtaining Bank Conflict Information                 |

|   |      | 5.5.2   | Bank Conflict History Cache                         |

|   |      | 5.5.3   | Proposed Warp Scheduling                            |

|   |      | 5.5.4   | Hardware Overhead                                   |

|   | 5.6  | Experi  | mental Evaluation                                   |

|   |      | 5.6.1   | Effect on Pipeline Stall Reduction                  |

|   |      | 5.6.2   | Performance Improvements                            |

|   |      | 5.6.3   | Performance of Non-Conflicting Kernels 119          |

|   |      | 5.6.4   | Interaction with Off-chip DRAM Access 120           |

|   | 5.7  | Discus  | ssion                                               |

|   | 5.8  | Summ    | ary 123                                             |

| 6 | Impr | ovina D | RAM Access Efficiency                               |

| 0 | 6.1  |         | action                                              |

|   | 6.2  |         | round and Motivation                                |

|   | 6.3  | •       | ontal Locality Aware DRAM Scheduling                |

|   | 0.5  | 6.3.1   | Horizontal Locality                                 |

|   |      | 6.3.2   | Compiler and Runtime Access Pattern Analyzer 134    |

|   |      | 6.3.3   | Adaptive DRAM Access Granularity Scheduling 136     |

|   | 6.4  |         | architectural Extension                             |

|   | 0.4  | 6.4.1   | Vector MSHR (VMSHR)                                 |

|   |      | 6.4.2   | Elastic MSHR (VMSHR)                                |

|   | 6.5  |         | mental Evaluation                                   |

|   | 0.5  | 6.5.1   | Memory Bandwidth Requirement                        |

|   |      | 6.5.2   | DRAM Access Granularity Distribution                |

|   |      | 6.5.3   | Improved DRAM Efficiency                            |

|   |      | 6.5.4   | Improved DRAW Enclency                              |

|   |      | 6.5.5   | Memory Access Utilization                           |

|   |      | 6.5.6   | Effect on a GPU with Less Capable Interconnect 152  |

|   | 6.6  |         | ssion                                               |

|   | 0.0  | 6.6.1   | Effect of Large DRAM Data Packets                   |

|   |      | 6.6.2   | Impact of HW Cache                                  |

|   |      | 6.6.3   | Application to SPMD Barrel Processing               |

|   |      | 6.6.4   | Possible Improvement                                |

|   |      | 6.6.5   | Contrast to Closely Related Art                     |

|   |      | 0.0.5   | = 0                                                 |

|     | 6.7         | Summary                        | 157 |

|-----|-------------|--------------------------------|-----|

| 7   | 7.1         | Iusions and Future Directions  | 159 |

| Α   | SAMS        | S Conflict-Free Access Proof   | 165 |

| В   | <b>B</b> .1 | IM Properties and Formal Proof | 173 |

|     | •           | phy                            |     |

| Lis | t of Pu     | iblications                    | 195 |

| Sar | nenva       | tting                          | 197 |

| Cu  | rriculu     | m Vitae                        | 199 |

### List of Tables

| 3.1 | Delay and hardware usage of ATU                                                       |

|-----|---------------------------------------------------------------------------------------|

| 3.2 | 2DSMM scheme critical path and logic consumption 61                                   |

| 3.3 | 2DSMM scheme storage consumption 61                                                   |

| 4.1 | Stride control signals                                                                |

| 4.2 | Synthesis results of SAMS Multi-Layout Memory system 79                               |

| 4.3 | Selected benchmark suit                                                               |

| 4.4 | SAMS instructions, intrinsics and macros 85                                           |

| 4.5 | Changes over the original SPE and their impact                                        |

| 4.6 | SPU dynamic instruction count and execution time 88                                   |

| 5.1 | Benchmark shared memory BW requirement 100                                            |

| 5.2 | Elastic pipeline HW overhead per GPU core                                             |

| 5.3 | Hardware overhead of bank conflict prediction and warp mask generation (per GPU core) |

| 5.4 | The GPU processor configurations                                                      |

| 5.5 | Benchmark characteristics                                                             |

| 6.1 | Hardware cost of elastic MSHR with deferred reservation (per GPU core)                |

| 6.2 | Baseline GPU configuration <sup>†</sup>                                               |

| 6.3 | Benchmarks                                                                            |

| 6.4 | DRAM access granularity distribution                                                  |

# List of Figures

| 1.1 | Processor-memory performance gap                                                                                                              | 5  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | DRAM memory organization                                                                                                                      | 8  |

| 1.3 | 1D array storage in 4 banks (uniform bank access timing)                                                                                      | 9  |

| 1.4 | Bank conflicts in a multi-execution vector processing platform                                                                                | 10 |

| 1.5 | 1D array storage in 4 banks and memory accesses (non-uniform bank access timing)                                                              | 11 |

| 1.6 | Overview of the proposed customizable memory schemes                                                                                          | 16 |

| 1.7 | Customizable memory schemes                                                                                                                   | 18 |

| 2.1 | Stride-2 vector access to three schemes: (a) low-order inter-<br>leaving; (b) skewing (c) prime                                               | 22 |

| 2.2 | Prime memory system with unused cells                                                                                                         | 23 |

| 3.1 | Inherent limitation in multimodule memory assignment                                                                                          | 37 |

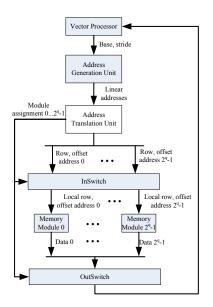

| 3.2 | SARC vector coprocessor memory addressing                                                                                                     | 39 |

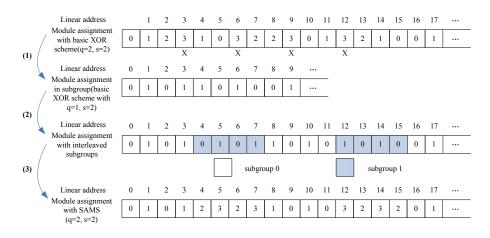

| 3.3 | SAMS single-affiliation scheme with $q = 2$ , $s = 2$                                                                                         | 41 |

| 3.4 | SAMS data arrangement example with 4 modules                                                                                                  | 44 |

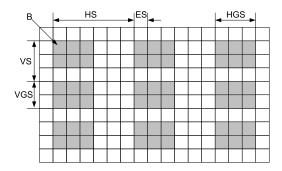

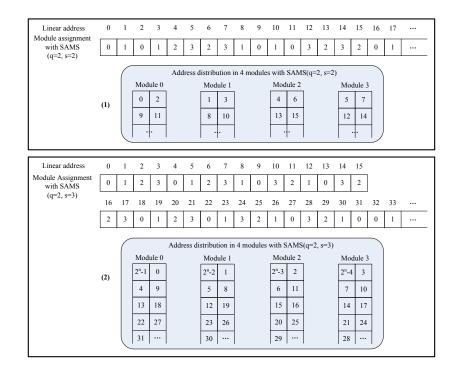

| 3.5 | 2D addressing scheme                                                                                                                          | 47 |

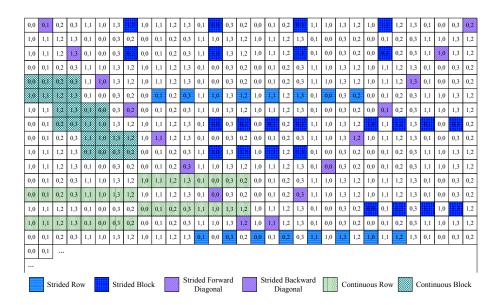

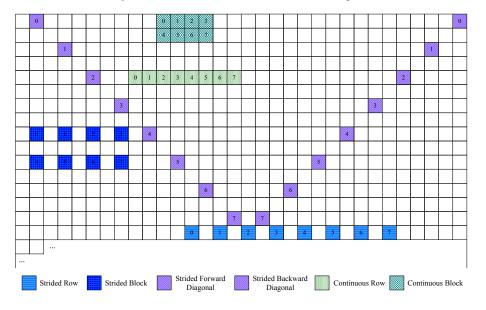

| 3.6 | Example of 2DSMM module assignment for $N = 16, 2^{p} = 2, 2^{q} = 4, 2^{vs} = 2, 2^{hs} = 2 \dots \dots \dots \dots \dots \dots \dots \dots$ | 48 |

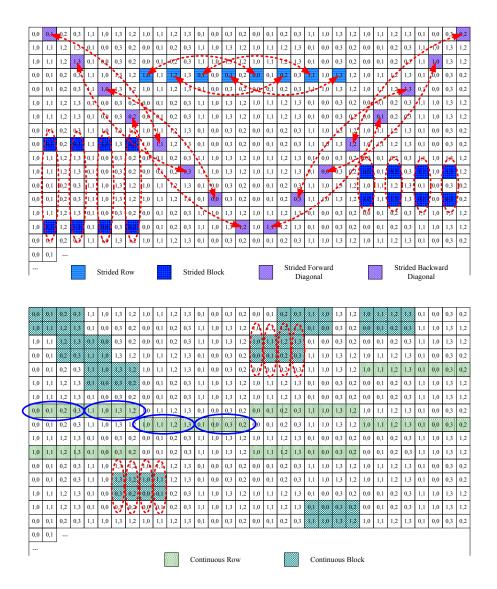

| 3.7 | 2DSMM access examples for $N = 32, 2^{p} = 2, 2^{q} = 4, 2^{vs} = 2, 2^{hs} = 2$                                                              | 49 |

| 3.8 | Parallel memory system based on customizable HW schemes .                                                                                     | 50 |

|     |                                                                                                                                               |    |

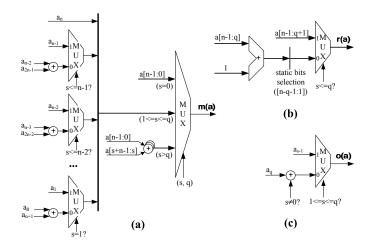

| 3.9  | SAMS address translation logic: (a)Module assignment,                                                                        |    |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

|      | (b)Row assignment, (c)Offset assignment                                                                                      | 51 |

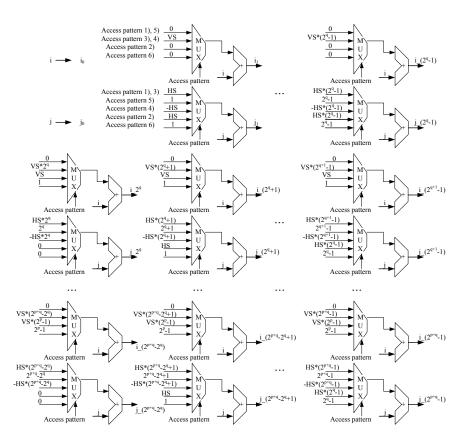

| 3.10 | 2DSMM address generation patterns                                                                                            | 53 |

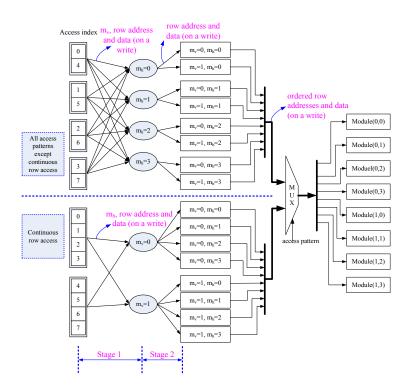

| 3.11 | 2DSMM address generation logic for six access patterns                                                                       | 54 |

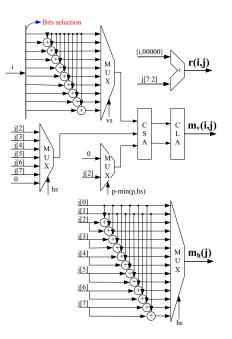

| 3.12 | 2DSMM address translation circuit with $M = 1024$ , $N = 256$ , $2^p = 2$ , $2^q = 4$                                        | 56 |

| 3.13 | 2DSMM properties for address & data routing simplification .                                                                 | 57 |

|      | 2DSMM address & data routing unit                                                                                            | 58 |

|      | Definition of access index for six 2DSMM access patterns                                                                     | 58 |

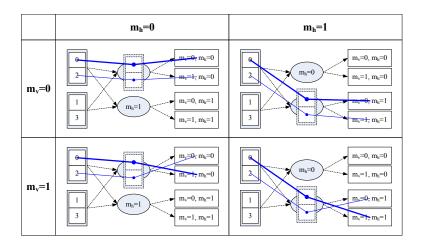

|      | 2DSMM address & data routing example $(2^p = 2, 2^q = 2)$ .                                                                  | 59 |

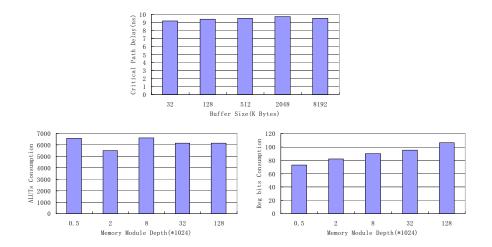

|      | 2DSMM memory module depth scaling in Stratix-II with $2^p = 2, 2^q = 4, data_width = 64 \dots \dots \dots \dots \dots \dots$ | 62 |

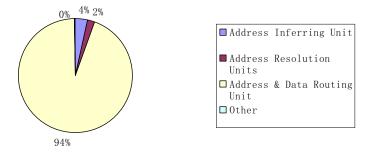

| 3.18 | 2DSMM ALUTs consumption breakdown in Stratix-II with $2^p = 2, 2^q = 4, data\_width = 64$ , memory module depth=8192         | 63 |

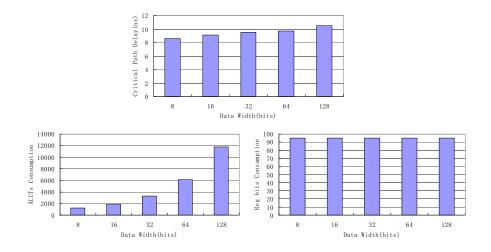

| 3.19 | 2DSMM data width scaling in Stratix-II with $2^p = 2$ , $2^q = 4$ , memory_module_depth = $32K$                              | 64 |

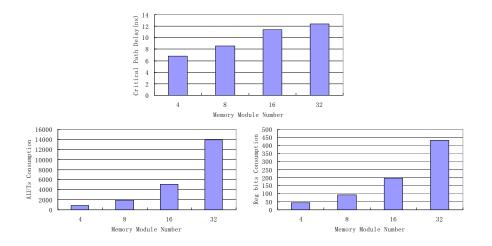

| 3.20 | 2DSMM memory module number scaling in Stratix-II with $data_width = 16$ , memory_module_depth = $16K$                        | 65 |

| 4.1  | Vector-matrix multiplication: multiple working data sets                                                                     | 71 |

| 4.2  | Sample vector-matrix multiplication code                                                                                     | 72 |

| 4.3  | The proposed multi-layout memory                                                                                             | 74 |

| 4.4  | Internal data layouts in SAMS Multi-Layout Memory                                                                            | 75 |

| 4.5  | SIMD memory organizations                                                                                                    | 77 |

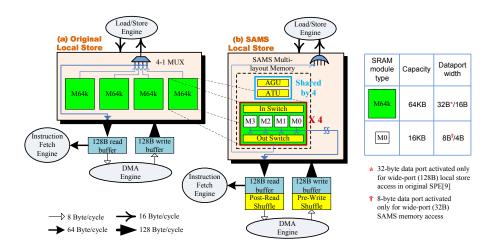

| 4.6  | SAMS Multi-Layout Memory Integration into the Cell SPE                                                                       | 81 |

| 4.7  | Exemplary load/store pipeline optimization: (a)original SPE [57], (b)SAMS integration with optimizations                     | 83 |

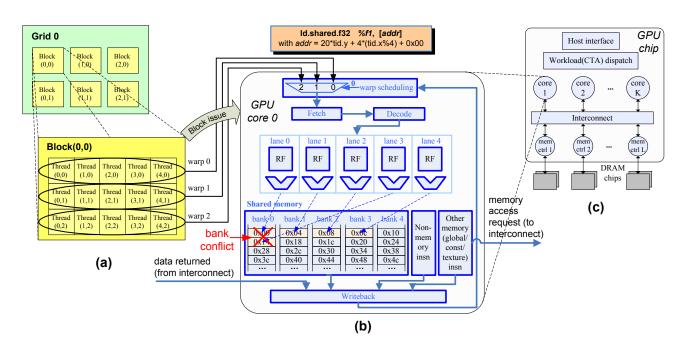

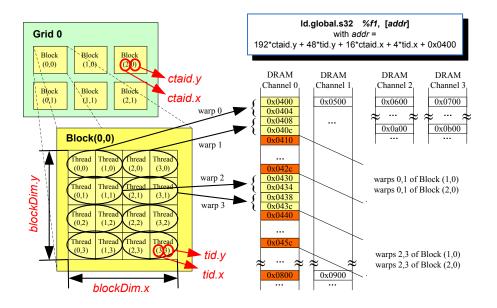

| 5.1  | (a)CUDA threads hierarchy; (b)thread execution in GPU core pipeline; (c)GPU chip organization                                | 96 |

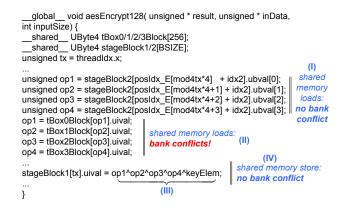

| 5.2  | AES source code                                                                                                              | 97 |

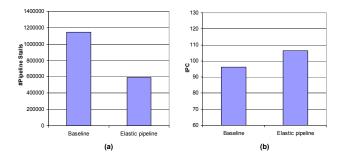

| 5.3  | Effect of elastic pipeline in: (a)reducing pipeline stalls and (b)improving performance                                      | 98 |

|      |                                                                                                                              |    |

| 5.4  | Baseline in-order pipeline: (a)unified memory stages and                                                  | 102  |

|------|-----------------------------------------------------------------------------------------------------------|------|

| ~ ~  | (b)split memory stages                                                                                    |      |

| 5.5  | Elastic pipeline                                                                                          | 103  |

| 5.6  | Elastic pipeline logic diagram                                                                            | 106  |

| 5.7  | Bank-conflict aware warp ready signal generation                                                          | 109  |

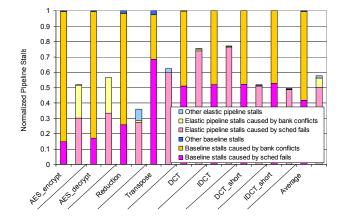

| 5.8  | Pipeline stall reduction. In each group: left bar: baseline GPU; right bar: elastic pipeline enhanced GPU | 115  |

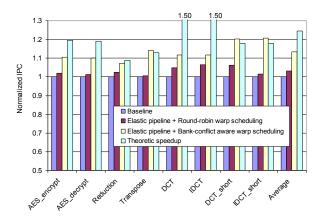

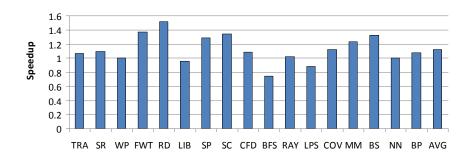

| 5.9  | Performance improvement                                                                                   | 117  |

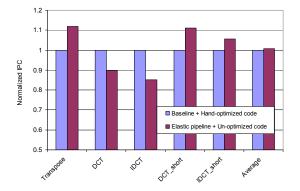

| 5.10 | Elastic pipeline vs hand-optimized code for conflicting kernels                                           | 119  |

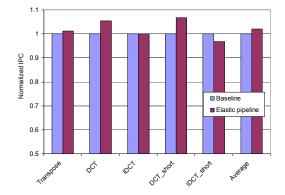

| 5.11 | Elastic pipeline performance for non-conflicting kernels                                                  | 120  |

| 5.12 | DRAM bandwidth impact                                                                                     | 121  |

|      | -                                                                                                         |      |

| 6.1  | Hierarchy and memory accesses of worker threads                                                           | 127  |

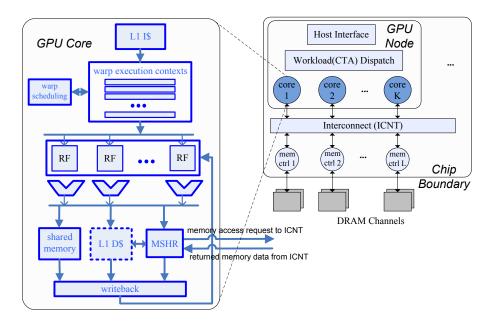

| 6.2  | Baseline GPU organization with barrel processing                                                          | 129  |

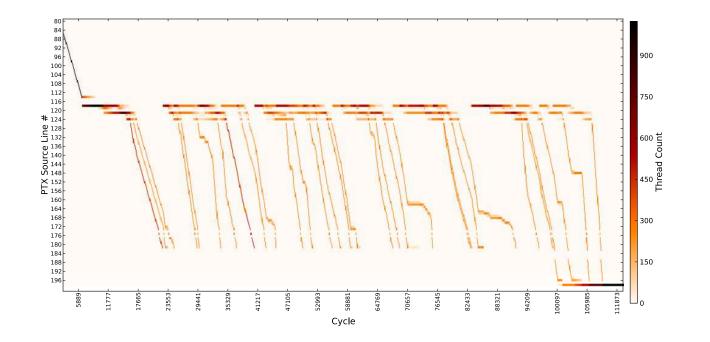

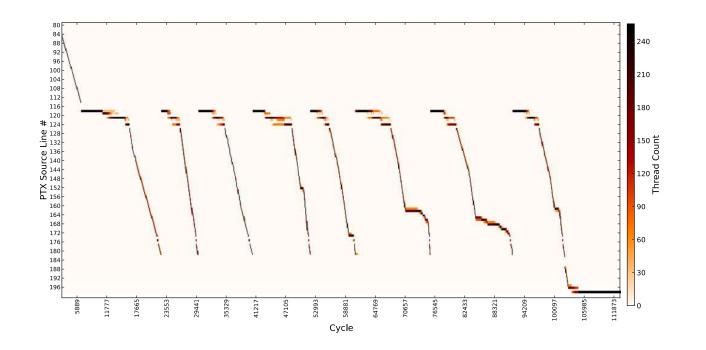

| 6.3  | Matrix multiplication PC-Histogram: all 4 CTAs                                                            | 132  |

| 6.4  | Matrix multiplication PC-Histogram: 1 CTA                                                                 | 133  |

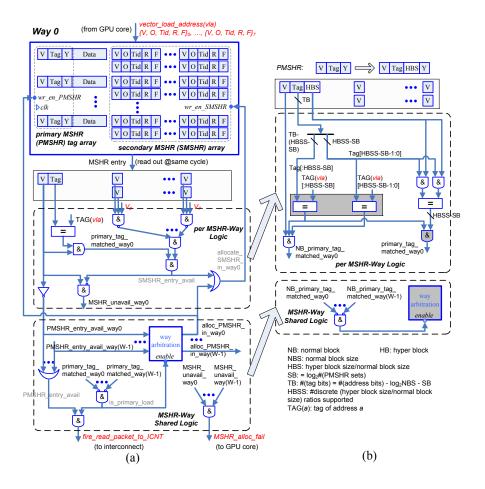

| 6.5  | VMSHR design: (a)baseline; (b)modifications for elastic MSHR                                              | 139  |

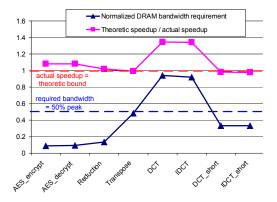

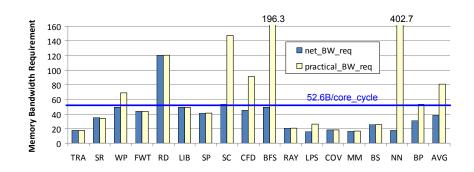

| 6.6  | Memory bandwidth requirement                                                                              | 146  |

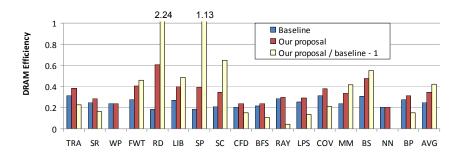

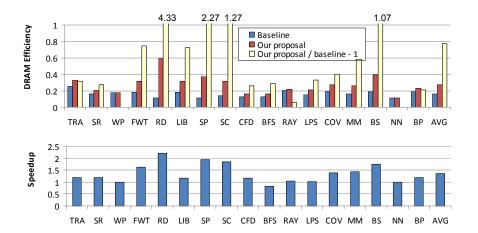

| 6.7  | DRAM efficiency                                                                                           | 149  |

| 6.8  | Speedup over the baseline                                                                                 | 150  |

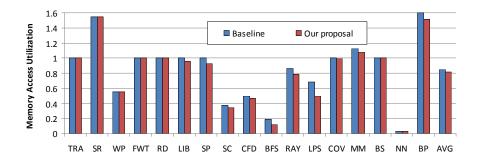

| 6.9  | Memory access utilization                                                                                 | 151  |

| 6.10 | DRAM efficiency improvement and overall performance                                                       |      |

|      | speedup ( <i>num_vcs</i> =1)                                                                              | 153  |

| . 1  |                                                                                                           | 1.00 |

| A.1  | Binary bits representation of $b = a + \delta \cdot 2^0$ when $1 \le s \le q$ .                           | 166  |

| A.2  | Binary bits representation of $b = a + \delta \cdot 2^1$ when $1 \le s \le q$ .                           | 167  |

| A.3  | The accessed addresses with stride $S = 2^s \ldots \ldots \ldots$                                         | 169  |

| A.4  | Binary bits representation of $b = a + \delta$ when $s > q$                                               | 170  |

| B.1  | Address sequence of strided row access                                                                    | 177  |

| B.2  | Address sequence of unit-stride row access                                                                | 180  |

| B.3  | Address sequence of strided forward diagonal access                                                       | 181  |

|      |                                                                                                           |      |

# List of Acronyms and Symbols

| AoS, SoA                              | Array of Structures, Structure of Arrays |

|---------------------------------------|------------------------------------------|

| ASIC                                  | Application Specific Integrated Circuit  |

| BW                                    | Bandwidth                                |

| CLA                                   | Carry Look-ahead Adder                   |

| CPU                                   | Central Processing Unit                  |

| CSA                                   | Carry Save Adder                         |

| CUDA                                  | Compute Unified Device Architecture      |

| DRAM                                  | Dynamic Random Access Memory             |

| DLP                                   | Data Level Parallelism                   |

| FPGA                                  | Field Programmable Gate Array            |

| FR – FCFS                             | 57                                       |

| FIFO                                  | First In, First Out                      |

| FLOP                                  | FLoating-point OPeration                 |

| FLOPS                                 | FLoating-point OPeration per Second      |

| GPP                                   | General Purpose Processor                |

| GPU                                   | Graphics Processing Unit                 |

| GPGPU                                 | General-purpose Processing on GPUs       |

| НРС                                   | High Performance Computing               |

| ILP                                   | Instruction Level Parallelism            |

| IPC                                   | Instructions Per Cycle                   |

| ISA                                   | Instruction Set Architecture             |

| LUT                                   | Lookup Table                             |

| МС                                    | Memory Controller                        |

| MD                                    | Molecular Dynamics                       |

| MIPS                                  | Million Instructions Per Second          |

| MSHR                                  | Miss Status Holding Register             |

| 000                                   | Out of Order                             |

| РСВ                                   | Printed Circuit Board                    |

| PMSHR                                 | Primary Miss Status Holding Register     |

| RTL                                   | Register-Transfer Level                  |

| SDRAM                                 | Synchronous Dynamic Random Access Memory |

| SIMD Single Instruction Multiple Data |                                          |

| SPMD                                  | Single Program Multiple Data             |

| SRAM                                  | Static Random Access Memory              |

| TLP                                   | Task Level Parallelism                   |

|                                       |                                          |

# Introduction

In the past decades, the amount of digital data newly created and processed worldwide has been steadily growing. It is quite clear that this trend is going to continue in the future. This introduces tremendous challenges for the processing capabilities of modern computer systems. Many of the widely used workloads follow a particular processing paradigm: the *same* computation is repeated for a massive number of data elements. Such paradigm, called *data parallel computing*, exists in many applications ranging from consumer and desktop computing (such as multimedia and 3D graphics) up to the highperformance domain (e.g., financial analysis, bioinformatics, physics simulation and more). Data parallel processing, known also as *single instruction multiple data* (SIMD) [45], demands more efficient computing and memory hierarchy schemes when compared to scalar approaches.

### **1.1 Data Parallel Architecture Evolution**

Vector supercomputers are the first best known examples of data parallel machines. Early successful implementations date back to the 1970s, with CDC Star-100 [33] and Texas Instruments ASC [148] as two representative examples. Such vector supercomputers were built with proprietary, dedicated vector processors and rather expensive, highly-banked memory arrays. Vector processing had played a central role in supercomputers and has been strikingly successful up to 1990s [6]. The most prominent vector supercomputers in history include the Cray series [126] and the NEC SX models [58].

The dominance of the vector supercomputers was gradually replaced by the "killer-micros" (high performance computers built using commodity micro-

processors) since early 1990s [42]<sup>1</sup>. Nonetheless, the growth of data parallel processing paradigm did not stop. In fact, since then more data parallel architectures have arisen in the commodity computing market. The advent of such data parallel computing facilities is driven by the growing importance of data intensive computing on desktops [28, 41], and is enabled by the advances of the semiconductor technology.

On one hand, various types of SIMD extensions, such as SSE [140], 3DNow [9], and Altivec [40], have been introduced into the general purpose processors, in the form of short vector datapaths tightly coupled to the original scalar pipelines. The *general purpose processor* (GPP) SIMD extensions typically provide moderate computation capability limited by short vectors, but have the merit of being compatible with legacy code (including system software). On the other hand, data parallel accelerators appeared in application domains such as home entertainment (e.g., the Cell processor [68, 120]), computer graphics (such as the *graphics processing units* (GPUs) [96, 113], and visual computing accelerators [128]). In contrast to GPP SIMD extensions, there is less burden of backward comparability in terms of executing legacy code and the programming styles are still evolving. As a result, these data parallel accelerators can be *specialized* for a narrower set of workloads. In doing so, both the hardware designs and the programming models can be highly customized to improve performance, power and chip area efficiency.

Besides the GPP SIMD extensions and accelerators mentioned above, huge amount of special-purpose hardwired functional units implemented by *application specific integrated circuits* (ASICs) have also been designed and utilized to exploit data parallelism for dedicated applications. ASIC based systems are necessitated when extremely high performance is required, or in case rigid cost/power constraints render the programmability as less important. Good examples are the Anton multiprocessor for high-speed *molecular dynamics* (MD) simulations from DE Shaw Research [132] and the video codecs presented in [25, 91]. Often, the design objectives of such special-purpose computing systems determines architectural choices which largely sacrifice flexibility and programmability. Although some of the techniques presented in this dissertation are also directly applicable to ASIC based systems, we focus our discussion to programmable data parallel accelerators because of their wider scope and because we strongly believe that such accelerators are a promising approach to process data parallel workloads.

<sup>&</sup>lt;sup>1</sup>Recently data parallel processors are returning to the Top 500 list [6] in modernized form (such as machines based on GPUs).

### **1.2 Programmable Data Parallel Accelerators**

In general, a *compute accelerator* [119] is a hardware entity *separate from* the host general purpose processor, that offers higher performance and better silicon area/power efficiency as compared to the host processor. This is achieved usually for a restricted class of applications in a very specific domain [119]. To achieve this, the target applications characteristics are heavily exploited during the design process. Naturally, such design choices can provide combined performance/area/power benefits at the expense of flexibility<sup>2</sup>. In early compute accelerators [2] this often resulted in fixed, hardwired datapath designs.

Recently, there seems to be a consensus that high-level programmability using general purpose programming languages becomes a requirement for accelerators [113, 114, 135]. High-level programmability with matured programming styles/models not only improves programmer productivity and code portability, it also increases applicability of the same accelerator substrate to a wider set of application domains. This has been demonstrated by recent proposals in, e.g., *general-purpose processing on GPUs* (GPGPU) [1, 114], unified visual computing accelerators [128], and unified accelerator architectures for imaging, video and next-generation immersive multimodal applications [135]. The economic rationale driving the merging of domain-specific accelerators is that, expanding the application domains range allows for potentially larger product volume resulting from increased shares in the marketplace.

For all programmable accelerators, the common essential aim is to exploit parallelism in the targeted applications. Naturally, application code parallelism can be categorized into three major types: *instruction-, task-*, and *datalevel*. While *instruction level parallelism* (ILP) has been intensively pursued by GPPs, task and data level parallelism are usually the primary targets of programmable accelerators. Task parallel accelerators scale well with irregular, dynamic and heterogeneous problems<sup>3</sup>, that correspond to the global application scope situation. However, they suffer from being less capable of capturing the potential computing efficiency available in data parallel kernels.

In contrast, data parallel accelerators are concerned with (local scope) kernels with regular and homogeneous processing behavior. There are at least two important features inherent to the assumed data parallel processing paradigm: 1) it is relatively easy to get high utilization of throughput architectures (e.g., par-

<sup>&</sup>lt;sup>2</sup>In this dissertation flexibility is used for expressing programmability and wide applicability. <sup>3</sup>Irregular problems/applications/workloads in this thesis denote those with irregular data

accesses and/or irregular control flows. (Ir)regular data access is elaborated in Section 1.5.

allel vector lanes); and 2) the pipeline frontend processing has high area/power efficiency due to the reduced frontend processing bandwidth requirements. The above two merits, plus the widespread data parallelism in emerging applications, naturally render data parallel architectures to be the primary choice for accelerator designs targeting regular and homogeneous workloads operating on large data sets.

Data and task parallelism are not mutually exclusive but rather complementary. Currently we have already seen commercial products with multicore GPPs and GPUs integrated on a single die [7, 12, 111]. These systems are able to provide suitable hardware substrates for combined data and task parallel processing. The more challenging issue of proper programming models and their efficient hardware interfaces, remains an open research question, the solution of which is still at its infancy. The merging process brings up a set of new challenges that have to be addressed in order to ensure the success of such co-exiting architectures. One particular example is the shared memory system infrastructure that has to efficiently support the memory accesses from both sides. The findings in this thesis can be viewed as one such step toward improving *memory access efficiency* (in terms of bandwidth utilization and access time) of such contemporary co-execution platforms.

Current data parallel processors often adopt local memories with no coherence support implemented in hardware (HW) and less provisions to reduce single thread latencies compared to GPPs. Such architectural choices often compromise the programmability to a certain extent, i.e., as restricted by specific programming styles/models. Generally speaking, the specific programming models exert nontrivial burdens on programmers, such as explicit management of parallelism and the memory hierarchy, which should be ideally avoided. This inspires a challenging research topic exploring novel programming models and architectures to relieve such burdens by striking the right balance between the hardware efficiency (in terms of performance gain/additional HW cost) and programming efforts. This was also the main motivation behind the Vector-Thread Architectures [80], Sequoal [43], Rigel [69], SARC [123] and ENCORE [4] research projects. The specialized programming models also provide opportunities for system-level optimizations, since, in general, more information about the application behavior is available when the code is written under specific constraints of programming styles/models. In addition, during execution additional information becomes available and can be utilized for performance optimizations. Based on the above observations, data parallel programming models/language extensions, compile-time analysis, runtime library optimizations, and architectural extensions will be jointly explored, to address the memory efficiency issues in this dissertation.

### **1.3 Processor-Memory Performance Gap**

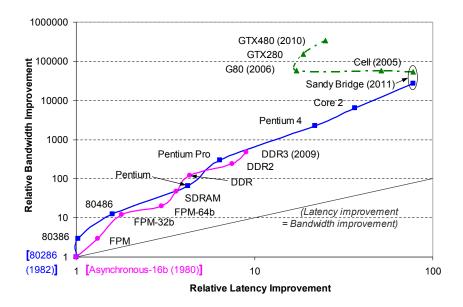

It is well known that memory density and capacity have grown along with the CPU computational capacity and complexity, however memory speed has not kept pace in this process. As a consequence, the processor-memory performance gap has steadily increased for decades, rendering memory access as a major bottleneck. Figure 1.1 shows the relative performance improvements

Figure 1.1: Processor-memory performance gap

of microprocessors and DRAM memories during the past 30 years, from both bandwidth and latency perspectives<sup>4</sup>. For memory graph the Asynchronous 16 bits memory system used by the industry in the eighties forms our baseline and for processors we have chosen Intel 80286 (without 80287 floating point coprocessor). All memory latencies are calculated under cold start assumptions. More precisely, we do not account for delays introduced by memory bank conflicts but consider only the accumulative numbers of Open Row and Col-

<sup>&</sup>lt;sup>4</sup>The idea of this plot and part of the source data are originated from [59]; other data are taken from public resources of respective vendors [64, 65, 112, 120].

umn access latencies. In respect to bandwidth, we considered a single channel memory configuration as adopted by the industry [65] at the corresponding time. The estimated bandwidth is the product of the frequency and the data port width. The microprocessor instruction latency is expressed by the absolute delay of the integer addition instruction. The instruction bandwidth is the product of the maximum achievable *instructions per cycle* (IPC) and the pipeline frequency. For data parallel processors<sup>5</sup> (the IBM *Cell Broadband Engine*, and three representative GPUs) we determine the latency similar to the microprocessors, while the relative bandwidth is in *floating point*<sup>6</sup> operations per second (FLOPS)<sup>7</sup>. We can safely relate data parallel architecture results to the 80286 base line since the frequencies of both pipelines (fixed/floating-point) are the same for the data parallel accelerators. The two graphs representing the microprocessors and the memories are aligned in time by using roughly the same start year, end year and similar time periods for the intermediate points.

We used the 4-core Intel *Sandy Bridge* processor to relate the raw computational capabilities of state of the art GPPs and data parallel accelerators. Note, that there is a difference between the instruction throughput and FLOPS metrics as shown in Figure 1.1. The 4-issue Sandy Bridge core implements *advanced vector extensions* (AVX) ISA which supports 256-bit vector operation (i.e., 8 FLOP) per cycle, hence, its peak FLOPS is twice as big as its peak instruction throughput. This shows two GPP trends: 1) that contemporary GPPs have the raw computational capabilities of data parallel accelerators more than 5 years old and 2) in order to cope with this delay, GPPs are heavily relying on wider SIMD lanes (exploiting more data parallelism).

Several observations can be drawn from Figure 1.1. First, the bandwidth has been improved at a significantly higher rate than latency, for both memories and processors. This is apparent by noticing that all three curves are well above the straight line representing identical bandwidth and latency growths. Moreover, it is quite clear that such disparity between the bandwidth and latency improvement ratio is going to continue. The reason for this is twofold. On one hand, since latency is constrained by laws of physics, its improvement can be mainly attributed to the process technology improvements resulting in increased clock frequency. This is becoming harder as we are approaching certain physical boundaries of the used technology. For example, power consumption is now becoming a major constraint that limits future clock frequency

<sup>&</sup>lt;sup>5</sup>In the rest of this thesis, we use the terms (*programmable*) data parallel accelerators and data parallel processors interchangeably.

<sup>&</sup>lt;sup>6</sup>We consider single precision floating point.

<sup>&</sup>lt;sup>7</sup>Fused multiply-add is considered as a single FLOP in our calculations.

increases. On the other hand, improving bandwidth is relatively easier. Exponential growth of transistor density, pushed by *Moore's Law* [99], has been successfully driving the industry for the past thirty years and is still continuing today and is used to improve on-chip bandwidth. Off-chip bandwidth is more expensive (e.g., chip pin-counts are limited, have high parasitic impedances and PCB traces engineering is costly) but still manageable at reduced scale. Thus, it is not surprising that the industry has, particularly at present time, opted for *throughput computing* (e.g., wider SIMD lanes, massive HW multithreading) as the "easy" way towards *aggregate* performance improvements. In fact, the parallel processing paradigm has been so widely spread, that almost all computers today are eventually parallel. For example, even hand-held devices (such as smart phones) are powered by multicores [111, 121].

Second, DRAM performance improvement has not kept pace with the processors, in terms of both bandwidth and latency, for the past thirty years. In fact, memory latency has been reduced by 7.6% per year, while the microprocessor latency reduction amounts to 15.6% on average. Similarly, the DRAM bandwidth annual compound increment is 22.8%, whereas for microprocessors it is 40.5%. The bandwidth growth rate for data parallel accelerators is even more impressive -55.8% for the past three GPU generations covering only 6 years. This trend has several important implications stated below.

To deal with the processor-memory latency gap, techniques to alleviate long memory latencies have become mainstream in microprocessor design. For example, caching and prefetching are widely adopted in microprocessors to *hide* memory latency and improve performance [59]. Interestingly, various prefetching techniques hide latency often at the expense of additional bandwidth consumption. In addition, hardware multithreading, a valid technique to *tolerate* long latencies, has been embodied in both CPUs and typical data parallel architectures (such as GPUs), as one of the main means to achieve high throughput. Hence, bandwidth is increased to compensate long latencies and provide high aggregate throughput.

The differences in processor-memory bandwidth improvements in time, have resulted in single memory unit being inadequate to feed its processor. In addition, the trend is clear that such disparity in processor and memory bandwidth is increasing (predicted from the last four memory/processor pairs). For sufficient memory bandwidth and reduced access latency, parallel memory systems with multiple memory units (e.g., banks/channels) are widely used in data parallel computers, from vector supercomputers [58, 126] to commodity data parallel accelerators [44, 51]. Despite the deployment of parallel memory units,

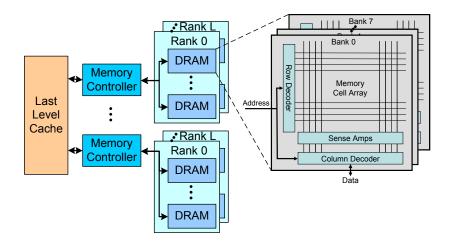

Figure 1.2: DRAM memory organization

efficient vector memory access<sup>8</sup> still remains one of the critical problems in data parallel computers.

### 1.4 Parallel Memory Organizations and Accesses

As described above, to mitigate the processor-memory performance gap, parallel memory organizations, with multiple memory units (such as banks, modules, and channels), have been proposed and successfully adopted in both early and contemporary high performance computers [83,87], microprocessors [89], and mobile processors [79,121]. In such memory organizations, parallel memory units can be independently indexed to service concurrent memory accesses, resulting in increased bandwidth and decreased latency. As an example, Figure 1.2 shows a typical DRAM memory subsystem organization, which consists of a few independent memory channels. Each channel, controlled by a memory controller (MC), manages a couple of independent memory *ranks* each of which employs several DRAM chips working in lock-step mode. Each DRAM chip is composed of several banks. While each bank can process MC commands independently, all banks inside the same chip must share their data/address buses.

Such parallel memory organizations, with abundant raw memory bandwidth,

<sup>&</sup>lt;sup>8</sup>Parallel/vector/SIMD memory access denote the same memory access paradigm, and are used interchangeably in this thesis (unless explicitly stated otherwise).

can *potentially* improve system performance. One should note that it is often challenging to *effectively* utilize the available bandwidth and achieve high *sustained bandwidth*. This is especially the case in a common execution environment where thousands of in-flight memory accesses, from multiple processing elements, are *competing* for the memory resources and interfering with each other. Indeed, the parallel memory access inefficiency is not a new problem; for example, it has been extensively studied for traditional vector memory accesses, as discussed in the following.

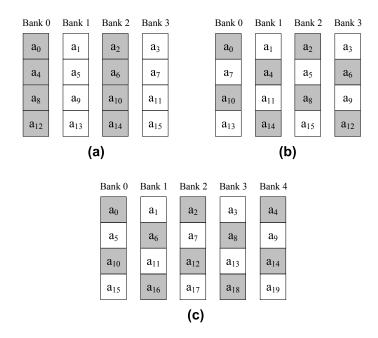

In traditional vector machines, parallel memory organizations were often presented and analyzed by an abstract model as shown in Figure 1.3. The model consists of parallel banks, each of which has independent address decoding logic (i.e., each bank can be indexed independently). While accesses to different banks can be simultaneously serviced, accesses to the same bank must be serialized (but with *uniform access timing*).

|                       | Bank 0          | Bank I                | Bank 2          | Bank 3          |

|-----------------------|-----------------|-----------------------|-----------------|-----------------|

| _                     |                 |                       |                 |                 |

| guin                  | a <sub>0</sub>  | a <sub>1</sub>        | a <sub>2</sub>  | a <sub>3</sub>  |

| cess ti               | a4              | <b>a</b> <sub>5</sub> | a <sub>6</sub>  | a <sub>7</sub>  |

| Uniform access timing | a <sub>8</sub>  | <b>a</b> 9            | a <sub>10</sub> | a <sub>11</sub> |

| Unifc                 | a <sub>12</sub> | a <sub>13</sub>       | a <sub>14</sub> | a <sub>15</sub> |

Bank 0 Bank 1 Bank 2 Bank 3

Figure 1.3: 1D array storage in 4 banks (uniform bank access timing)

In data parallel processors (such as vector processors), the data to be processed is usually stored in array structures. E.g., if a machine has *m* parallel memory units, we can store one-dimensional arrays across the units, in a format as Figure 1.3 shows, for m = 4. When concurrent memory accesses are to contiguous array elements, all memory units are working in parallel, allowing peak bandwidth. However, if only even array elements are accessed (the solid squares in Figure 1.3), the *effective bandwidth* is reduced by half, and, as a result, access latencies are penalized. This effect is usually referred to as "bank conflict" in the literature<sup>9</sup>. Depending on the microarchitecture, bank conflicts can result from interference either among operations executed by the same

<sup>&</sup>lt;sup>9</sup>Also known as "partition camping" in the scenario of DRAM accesses that skewed towards a subset of available DRAM channels [151].

vector access (*intra-vector interference*), or among different vector memory accesses from the same/different execution context(s) (*inter-vector interference*), as illustrated in Figure 1.4.

Figure 1.4: Bank conflicts in a multi-execution vector processing platform

It is clear that the memory inefficiency problem (such as bank conflict) also occur in scalar processing. The distinction between vector and scalar memory accesses, however, is that a single vector memory access comprises a group of scalar accesses, which are packed into a single instruction and executed together (normally in lockstep) following a specific pattern. As a result, interference may occur, not only among different vector memory accesses, but also among operations executed inside the same vector access. In fact, while intervector interference is similar to memory access interference in scalar processing, intra-vector interference is special in that it is decided by the vector access pattern, which is often predetermined (even for irregular access patterns) and usually predictable (even in case of dynamic patterns).

It should be pointed out that, there are also other sources of parallel memory inefficiencies beyond the bank conflicts modeled in Figure 1.3. Memory parallelism can be implemented at different HW levels, using various memory types, with different characteristics (such as uniform/non-uniform access timing, being fully pipelined or not). In fact, the simple model illustrated in Figure 1.3 did not take into account the timing diversity in accessing the same bank, limiting its application to only memory types with (relatively) uniform access timing (such as SRAM banks). The advantage of such model lies in its simplicity, which often results in closed-form mathematical formula that sufficiently describes the memory access behavior. On the other hand, however, for memory units with non-uniform access timing, the parallel memory model and thus the factors impacting the access performance become more complex.

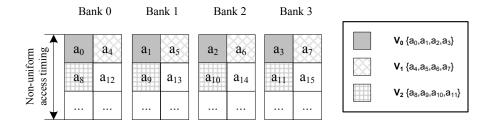

**Figure 1.5:** 1D array storage in 4 banks and memory accesses (non-uniform bank access timing)

For example, Figure 1.5 illustrates the parallel memory organization but with non-uniform bank access timing (DRAM). In this case, contiguous vector access is still conflict-free (similar to the case in Figure 1.3), however, the performance now depends also on the specific address sequence to each bank. E.g., when vector access  $\{a_0, a_1, a_2, a_3\}$  (V<sub>0</sub>) is followed by  $\{a_4, a_5, a_6, a_7\}$  $(V_1)$ , peak throughput is achieved since the second accesses *hit* the DRAM page buffer and can be serviced with lowest latency possible. Whereas when  $V_0$  is followed by  $\{a_8, a_9, a_{10}, a_{11}\}$  ( $V_2$ ), first the contents of the DRAM page  $(V_0 \text{ and } V_1)$  will have to be written back to the cell array (the "Pregarge" command); then  $V_2$  can be read out ("Activate") to the page buffer. The two additional steps (as compared to the page-hit case) incur wasted cycles on the data port and penalize memory performance. As a result, for the same vector accesses  $\{V_0, V_1, V_2\}$ , the ordering (e.g.,  $V_0 \rightarrow V_1 \rightarrow V_2$  vs  $V_0 \rightarrow V_2 \rightarrow V_1$ ) can have drastic impact on performance. Thus such inter-vector access ordering is also considered as an important part of the vector access pattern in case of non-uniform bank access timing.

Memory access interference is a serious problem, since the low utilization of parallel memory resources often incurs non-trivial system performance degradation even in case of *balanced* processor-memory designs<sup>10</sup>. On the other hand, naive solutions, such as employing arbitrarily large number of memory units for excessive raw bandwidth, result in *overdesigned* memory systems which often lead to prohibitive cost and power consumption. In fact, we have observed the trend of decreasing BW/FLOPS ratio in recent microprocessor and GPU generations (Section 1.3), which necessitates more efficient utilization of memory resources.

<sup>&</sup>lt;sup>10</sup>A *balanced* processor-memory design denotes that processor and memory bandwidths are matched.

From the above examples, it can be seen that both memory organization/data storage format and vector access patterns are of vital importance for highperformance parallel memory systems. When fixing one of the two, optimizing the other one can often improve system performance. To this end, *parallel* memory schemes have been designed for vector processing systems, usually optimized for a given set of vector access patterns. Traditionally, such schemes have been responsible mainly for two tasks. First, they manage specific organizations of parallel memory resources (e.g., at what memory hierarchy levels, and the number of parallel memory units at each level). Secondly, parallel memory schemes designate the corresponding low-level address mapping, from linear address space to the physical locations in the parallel units (e.g., row/bank/channel id). The goal of memory schemes is to increase access parallelism among multiple memory units and improve the performance, usually by supporting conflict-free vector accesses for the given set of vector access patterns. A more detailed study of parallel memory schemes in the literature will be introduced in Chapter 2.

#### **1.5 Problem Formulation**

As described in the sections above, memory system performance is crucial for any processor to achieve high performance, but especially for data parallel machines. The processing capability of parallel lanes can be efficiently utilized only when the data request is accomplished in a *sustainable* and *timely* manner. Unfortunately, even for parallel memory systems with adequate raw bandwidth, *irregular* access can lead to inefficient utilization of the parallel memory resources and significantly degrade overall performance.

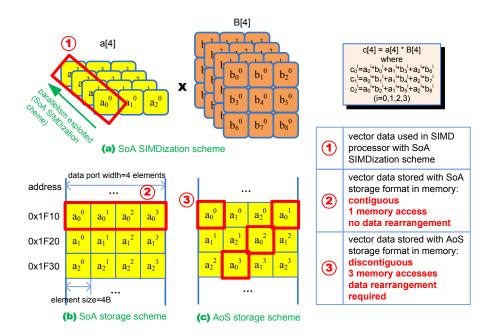

Vector memory access regularity is completely determined by *parallel memory access patterns* and *physical data layout*<sup>11</sup>. From a high-level point of view, all memory operations are executed on data parallel machines after two transformations. First, memory operations on working data elements are bundled into vector accesses, and mapped onto parallel hardware lanes for execution. This is done through the vectorization/SIMDization process which largely determines the memory access patterns of the code<sup>12</sup>. Second, the working data sets are mapped to their physical locations on the (usually multi-dimensional)

<sup>&</sup>lt;sup>11</sup>*Physical data layout* denotes the data layout in memory units and, as a result, the data access behavior (such as access timing).

<sup>&</sup>lt;sup>12</sup>Memory access patterns are also affected by runtime dynamics in multithreaded/out-oforder execution, such as GPUs.

memory topology containing multiple rows/banks/channels. This is realized by multiple entities crossing many computing system abstraction layers, from data structures definition at the program level down to the data layout instantiation in memory hardware. For the entire access pattern set, each type of physical data layout defines its own optimal pattern subset. Memory accesses on the specific physical data layout can obtain peak performance, only if its optimal patterns are followed. For the rest, the memory efficiency degrades. A good example is the memory hierarchy of a typical computing system, whose (default) data layout exclusively favors contiguous memory accesses. As such, accesses to continuous addresses are often referred to as "regular accesses".

In a single execution context (e.g., single-threaded vector processing), irregular memory accesses are typically originated from sparse data structures and/or highly irregular control flows. In addition, even applications which are generally regarded as regular and homogeneous can exhibit irregular vector memory accesses, e.g., access to a matrix column with row-majored storage format. In a multithreading scenario, concurrent memory accesses from multiple execution contexts can interfere with each other and end up with irregular accesses, even if memory access streams from individual execution are highly regular.

To summarize, in data parallel machines, memory accesses inefficiency roots in the mismatch between the actual parallel data access pattern and the one optimal for the physical data layout. Such a mismatch often results in memory bandwidth and latency inefficiencies, which penalize system performance. In particular, some typical scenarios of such inefficiencies include:

- For non-banked on-chip memory designs (adopted in some GPP SIMD extensions [140] and SIMD processors [68]), if the target addresses of a vector memory access are discontinuous, additional memory accesses and data rearrangement operations are required. This is widely known as the SIMDization data rearrangement overhead [11, 106, 124].

- For heavily banked on-chip memory designs (adopted in, e.g., GPUs), mismatch between the data access pattern and the physical data layout among banks incurs on-chip memory bank conflicts, similar to traditional vector processors [75]. Such bank conflicts result in pipeline stalls and overall performance degradation [54];

- For manycore architectures (such as GPUs), another issue is the interference among off-chip memory access streams from different cores [152]. Such interference often leads to hot DRAM channels, DRAM bank conflicts, and data bus read/write turn-around penalties [53].

As shown in Section 1.4, traditional parallel memory schemes utilize parallel hardware memory units, and manage low-level address mapping, to achieve conflict-free memory access for given vector access patterns. In this thesis, however, we notice that memory access patterns in contemporary data parallel processors are not necessarily hard-coded in the instruction set archi*tecture* (ISA) and exposed to the programmer (unlike the case in traditional vector processors). Thus, the access pattern information may not be taken for granted; instead, it is an important design consideration, from the system architect pointer of view. Therefore, we argue that, one should not be limited to just one memory hierarchy level when designing parallel memory schemes; instead, such schemes should be designed at system level, and consolidated with joint efforts often crossing the HW/SW boundaries. To this end, we propose customizable memory schemes, which extend conventional parallel memory schemes, by taking a holistic approach combining both memory access pattern extraction and exploitation. In such schemes, access pattern information is efficiently captured and utilized by customizing the low-level memory mapping with specific parallel memory schemes.

Additional techniques targeting parallel memory efficiency are also incorporated in our customizable memory schemes, in a broad sense. For example, with adequate memory access pattern information, the instruction sequencer in the pipeline front end (e.g., instruction/thread scheduling), the runtime scheduler (e.g., task scheduling), and the memory access scheduler (at the memory controller side) can also be customized, to better *adjust* the vector access patterns and *adapt* to the low level data layout and memory behavior for improved efficiency. Furthermore, vector access patterns and the physical data layout can be ideally coordinated for optimal performance, in a unified framework, similar in spirit to the compiler techniques that combine both vectorization and memory layout optimization [52, 106, 124].

The customizable memory schemes approach raises the following research questions, among others:

- How to design proper memory mapping schemes and provide a customizable yet generic mechanism for optimized layout of common data structures (e.g., 1D/2D arrays, *Array of Structures* (AoS));

- How to capture the minimal required information about the vector memory access pattern, and at which application phases;

- How to exploit the vector memory access pattern information to improve performance with low overhead, customizable hardware.

In answering the above questions, this dissertation aims at approaches to properly obtain the parallel memory access information, and leverage it to steer the co-designed hardware schemes. Such approaches are adapted to various contemporary data parallel architectures. In this way, customizable memory schemes significantly improve memory efficiency and overall performance, for both single data parallel core and manycore systems.

#### **1.6 Machine Organization and Proposed Solutions**

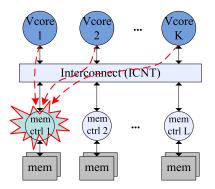

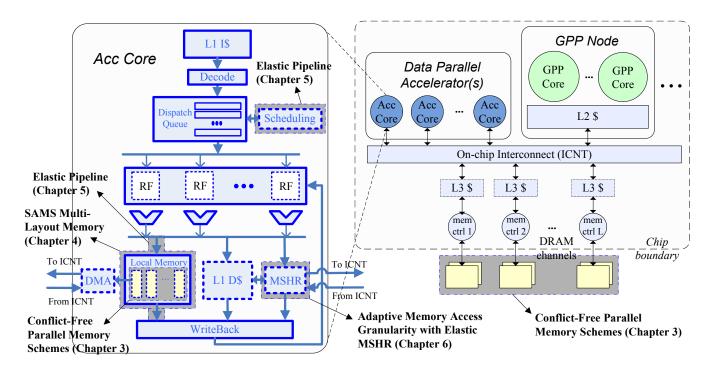

Figure 1.6 shows the organization of the baseline data parallel machine assumed in this thesis. This generic model is able to incorporate major contemporary multi/many-core data parallel accelerator variants. For example, the Cell processor [68] can be instantiated from Figure 1.6 with one GPP core and eight *synergistic processing element* (SPE) cores connected using a bidirectional ring bus. The SPE core has access to its local memory (called "local store" in the Cell SPE) and the attached DMA engine. Similarly, standalone GPUs can be instantiated with only accelerator cores connected by a crossbar, where both the local memory (called "shared memory" in NVIDIA GPUs) deployed at each core and the main memory are directly accessible by cores via specific load/store instructions. Furthermore, systems with GPU and CPU integrated on a single die [7, 12] can also be modeled with coexisting GPP and accelerator nodes as shown in Figure 1.6.

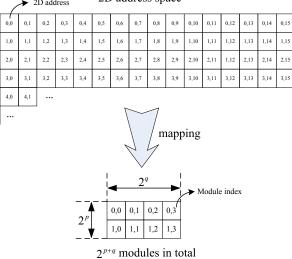

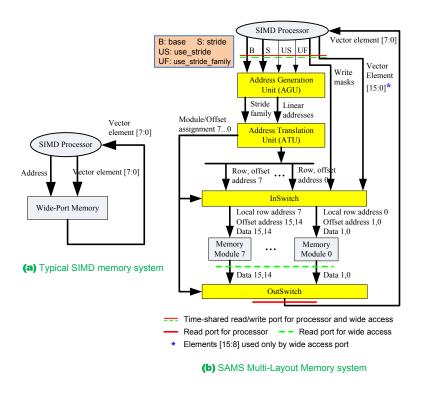

As discussed in Section 1.5, memory access inefficiency mainly roots in the mismatch between the parallel access patterns and the one favored by the physical data layout. This problem exists for both on-chip and off-chip memories, as highlighted in Figure 1.6. This will be addressed in Chapter 3, by introducing novel conflict-free parallel memory schemes (SAMS and 2DSMM). With such hardware parallel memory interleaving schemes, the physical data layout can be customized to support conflict-free vector access for strides from multiple stride families, in both 1D and 2D access environments.

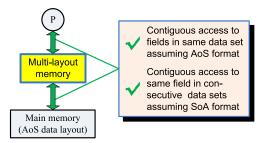

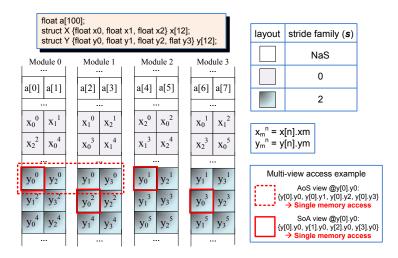

Bank interleaving schemes have been adopted in traditional vector supercomputers. However, to the best of our knowledge, it is less explored in literature how such HW schemes can be *efficiently* integrated into modern short vector SIMD processors. Chapter 4 gives an example (called "SAMS Multi-Layout Memory") for such integration *at system level*. In this chapter, both the Cell SPE pipeline HW extensions and the programming interfaces for expressing *Array of Structure* (AoS) and *Structure of Array* (SoA) access types are presented. We illustrate how to capture such high-level information in a

Figure 1.6: Overview of the proposed customizable memory schemes

programmer-friendly way and utilize it to orchestrate the HW parallel memory schemes and improve memory access efficiency.

Multithreaded data parallel architectures are becoming popular, such as GPUs and their variants (e.g., Larrabee [128]). In a multithreaded in-order SIMD execution, on-chip, local memory access bank conflicts can be *hidden*, by the elastic pipeline design (Chapter 5) which decouples shared memory bank conflicts from pipeline stalls. Furthermore, clustered bank conflicts can be resolved by the co-designed bank-conflict aware warp scheduling technique, as shown at the top of Figure 1.6.

Another memory inefficiency is incurred by the interference among off-chip memory access streams from different cores. In barrel execution of *single program multiple data* (SPMD) programs (adopted in, e.g., GPUs), there exists abundant inter-thread data locality (named "horizontal locality" in Chapter 6). Horizontal locality is exploited to address DRAM access interference among cores and hence improve system performance. This is achieved by a holistic DRAM bandwidth efficiency optimization framework with combined compile-time, runtime and architectural efforts. On the hardware side, an elastic vector *miss status holding register* (MSHR) unit with deferred reservation is proposed, as shown in Figure 1.6.

# **1.7** Contributions

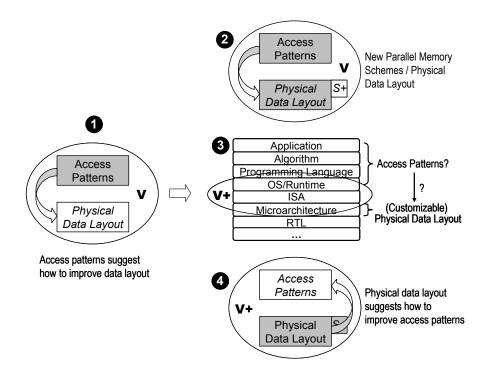

This dissertation proposes customizable memory schemes to address parallel memory access efficiency issues in data parallel accelerators, as illustrated in Figure 1.7. In this figure V denotes traditional vector architectures with memory access patterns hard-coded in the ISA and exposed to the programmer, while V+ denotes contemporary data parallel processors such as the Cell and GPUs. In traditional parallel memory schemes (① in Figure 1.7), access pattern information is usually assumed as given and hence efforts are often dedicated only to designing hardware memory schemes/physical data layout<sup>13</sup> for fixed access patterns. This thesis extends traditional parallel memory schemes and makes the following contributions:

• two new parallel memory schemes (*SAMS* and *2DSMM*) to cope with bank conflicts for widely used access patterns (**2** in Figure 1.7);

<sup>&</sup>lt;sup>13</sup>The HW memory scheme determines the layout/distribution of data in the memory units and hence the access behavior – i.e., the physical data layout.

Figure 1.7: Customizable memory schemes

- a framework (*SAMS Multi-Layout Memory*) to capture and convey the access pattern information to the customizable parallel memory scheme integrated into contemporary data parallel architectures (**2** and **3**);

- *elastic pipeline* that dynamically adjusts the instruction sequencer of a multithreaded vector architecture to customize the access patterns and improve the on-chip, local memory efficiency (③ and ④);

- *elastic MSHR* to exploit horizontal locality and adjust off-chip memory access granularity of a manycore data parallel architecture, hence improve the main memory efficiency (③ and ④).

# 1.8 Dissertation Organization

This dissertation is organized as follows.

**Chapter 2** gives an overview of the state of the art in solving memory access inefficiency problems in data parallel architectures. Specifically, it pro-

vides a survey on existing HW parallel memory schemes, techniques to reduce SIMDization data realignment overhead, techniques to relieve GPU on-chip memory bank conflicts, and techniques to address off-chip main memory efficiency issues in both GPUs and GPPs.

**Chapter 3** introduces two novel hardware parallel memory schemes to cope with vector access memory bank conflicts. The first scheme (SAMS) deals with supporting conflict-free 1D vector memory access for strides from two different stride families. The second proposal (2DSMM) explores hardware schemes to support 2D stride conflict-free vector memory accesses. Besides formal description, the hardware prototyping of the proposed schemes is also presented. The mathematical proof of corresponding conflict-free properties is shown in Appendices A & B.

**Chapter 4** proposes a system-level design to bridge the discrepancy between data representations in memory and those favored by SIMD processors by customizing the low-level address mapping. The HW SAMS parallel memory scheme is extended to provide both AoS and SoA views of the structured data accessed by the processor (multiple layout view). With such multi-layout memory, optimal SIMDization with low overhead, dynamically changing access patterns can be achieved. Experimental results show that the SAMS Multi-Layout Memory proposal has efficient hardware implementation while synthesized using standard cell library, and significantly decreases the dynamic instruction count and execution time, for representative workloads that operate heavily on array-based data structures.

**Chapter 5** presents a novel *elastic pipeline* design that minimizes the negative impact of on-chip memory bank conflicts on system throughput. A hardware *bank-conflict aware warp scheduling* technique is also designed to avoid bank conflicts clustering. Simulation results show the elastic pipeline together with the co-designed warp scheduling dramatically reduces the pipeline stalls and improves overall system performance for benchmarks with heavy bank conflicts, at trivial hardware overhead.

**Chapter 6** presents a holistic off-chip memory access efficiency optimization framework. Based on the framework, an adaptive DRAM access granularity scheme to exploit horizontal locality and reduce the memory access interference among cores is proposed. Experimental results show that the proposed techniques effectively improve the DRAM efficiency and overall system performance, with negligible hardware implementation cost.

Finally, Chapter 7 summarizes our findings and directions for future research.

# Related Work

s discussed in Chapter 1 one of the most critical design challenges in data parallel processors is imposed by the memory subsystem, expected to deliver sustained high bandwidth at reasonable latency [42, 79, 83]. In this chapter we will review the related state of the art in building data parallel centric memory subsystems. We will emphasize on the problems and existing solutions in contemporary mainstream data parallel architectures. Since this dissertation takes an access-pattern centric, systematic approach based on customizable memory schemes, we will first introduce the state of the art parallel memory schemes, which deal with the organization and low-level address mapping of memory subsystems with multiple memory banks/modules/channels. Then existing techniques on memory access patterns and data layout optimizations will be briefly summarized. At last, a survey of some recent progress in system-level memory access optimizations and, as a case study, the GPU memory access optimizations, is presented. Although the main focus of this dissertation is on programmable data parallel accelerators, we will also examine some relevant memory access optimization techniques from the GPP domain.

# 2.1 Parallel Memory Schemes

Parallel memories were introduced in early high performance processors [22] and later extensively adopted in vector supercomputers [58, 126]. Nowadays, there is a trend that general purpose systems are utilizing parallel memories in their memory hierarchy, such as the multibank on-chip cache organization in Niagara [77] and Opteron [70], multislice caches in Power processors [87, 133, 139], parallel on-chip eDRAM banks in the VIRAM processor [79], and interleaved DRAM banks in Rambus and other commercial-off-

**Figure 2.1:** Stride-2 vector access to three schemes: (a) low-order interleaving; (b) skewing (c) prime

the-shelf, monolithic DRAM modules.