## System in package for intelligent lighting and sensing applications

Dong, Mingzhi

10.4233/uuid:b9a684b9-b75f-4b59-b623-37c977ae8b85

**Publication date**

**Document Version**

Final published version

Citation (APA)

Dong, M. (2016). System in package for intelligent lighting and sensing applications. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:b9a684b9-b75f-4b59-b623-

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## **Propositions**

accompanying the dissertation

# SYSTEM IN PACKAGE FOR INTELLIGENT LIGHTING AND SENSING APPLICATIONS

by

#### Mingzhi Dong

- 1. A successful system in package relies on accurate multi-physical analysis and robust fabrication process. The former makes it possible and the latter makes it real.

- 2. Silicon microfabrication provides new SiP designs with a fast validation tool, yet not necessarily best cost effectiveness.

- 3. The bottleneck of the miniaturization of particulate matter sensors will be the shrinking of the air flow generating system, which the silicon-based SiP approach cannot help much about.

- 4. Emerging development of Internet of Things (IoT) requires extensive integration of technology (IoT).

- 5. Scientific research never ceases to bring surprises no matter how well it has been planned.

- 6. Time management is not only about getting things done on time, but also about doing right things at right time.

- 7. The closer a specific technology is to one's life, the more motivated one feels to make contribution to the development.

- 8. To make one device work is science; to make one batch work is engineering.

- 9. Pursuing doctorate is a goal that serves to organize and measure one's best energies and skills, and challenge that helps achieve a better version of oneself.

- 10. Writing a thesis is not only a process of reviewing one's achievement, but also a process of reflecting on one's flaws and unfulfillment, thus leading to mixed feelings towards it.

These propositions are regarded as opposable and defendable, and have been approved as such by the supervisor prof. dr. G. Q. Zhang.

## Stellingen

behorende bij het proefschrift

# SYSTEM IN PACKAGE FOR INTELLIGENT LIGHTING AND SENSING APPLICATIONS

door

#### Mingzhi Dong

- Een succesvol systeem in het pakket is gebaseerd op nauwkeurige multi-fysische analyse en robuuste fabricageproces. De voormalige maakt het mogelijk is en de laatste maakt het echt.

- 2. Silicon microfabrication biedt nieuw schip ontwerpen met een snelle validatieinstrument, maar niet per se de beste kosteneffectiviteit.

- 3. Het knelpunt van de miniaturisatie van fijn stof sensoren zullen het krimpen van de luchtstroom genererende systeem, dat de basis van silicium SiP aanpak niet veel over kan helpen.

- 4. Het onstaan van het "Internet of Things"(IoT) vereist extensieve intergratie van technologie (IoT).

- 5. Wetenschappelijk onderzoek zal altijd blijven verassen hoe goed het ook gepland is.

- 6. Tijdsmanagement gaat niet enkel en alleen over het op tijd af krijgen van zaken, maar ook over de juiste dingen op het juiste moment doen.

- 7. Hoe dichter een technolgie tot het eigen leven staat, hoe meer gemotiveerd iemand zich zal voelen om bij te dragen aan de ontwikkeling ervan.

- 8. Het laten functioneren van het product is aan de wetenschap; het maken van een partij is aan het ingineurswezen.

- 9. Het najagen van een doctoraat is een doel dat mede iemands vaardigheden en kunnen helpt organiseren en meten, en creert de mogelijkheid zichzelf te verbeteren.

- 10. Het schrijven van een thesis is niet alleen een proces waarbij iemands prestaties worden beoordeeld, maar ook een process van reflectie op iemands fouten en onvolkomendheden, wat leidt tot gemixte gevoelens jegens de thesis.

Deze stellingen worden opponeerbaar en verdedigbaar geacht en zijn als zodanig goedgekeurd door de promotor prof. dr. G. Q. Zhang.

# SYSTEM IN PACKAGE FOR INTELLIGENT LIGHTING AND SENSING APPLICATIONS

## SYSTEM IN PACKAGE FOR INTELLIGENT LIGHTING AND SENSING APPLICATIONS

### **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K. C. A. M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op maandag 19 september 2016 om 10:00 uur

door

# Mingzhi Dong

Master of Science, Tsinghua University geboren te Fushun, China.

#### Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. G. Q. Zhang

#### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof. dr. G. Q. Zhang, Technische Universiteit Delft, promotor

Onafhankelijke leden:

Prof. dr. J. L. Cao, Min. Science and Techn.

Prof. dr. C. P. Wong, Georgia Inst. of Technology

Prof. dr. ir. K. M. B. Jansen, IO

Prof. dr. ir. P. M. Sarro, EWI

Prof. dr. C. I. M. Beenakker, EWI

Overige leden:

Dr. E. Iervolino, Beijing DEFT Elec. Techn.

at the Institute of Semiconductors of Chinese Academy of Science

Keywords: system in package, intelligent lighting, particulate matter sensor

Printed by: IPSKamp Drukkers

Copyright © 2016 by Mingzhi Dong

ISBN 978-94-028-0268-9

An electronic version of this dissertation is available at

http://repository.tudelft.nl/.

# **PREFACE**

To my Mom

致: 我的母亲

Mingzhi Dong Delft, July 2016

# **CONTENTS**

| 1 | Intr  | oducti  | on                                           | 1  |

|---|-------|---------|----------------------------------------------|----|

|   | 1.1   | Backg   | ground                                       | 1  |

|   |       | 1.1.1   | SiP technology                               | 2  |

|   |       | 1.1.2   | Wafer level packaging                        | 3  |

|   | 1.2   | Applio  | cations enabled MtM                          | 4  |

|   |       | 1.2.1   | Function enrichment in solid state lighting  | 4  |

|   |       | 1.2.2   | Miniaturization of particulate matter sensor | 7  |

|   | 1.3   | Resea   | rch objective                                | 10 |

|   | 1.4   | Thesis  | s outline                                    | 10 |

|   | Refe  | erences | 3                                            | 11 |

| 2 | Silio | con-ba  | sed Packaging for SSL Applications           | 17 |

|   |       |         | luction                                      | 18 |

|   | 2.2   |         | nal design                                   | 18 |

|   |       | 2.2.1   | Remote phosphor                              | 19 |

|   |       | 2.2.2   | Integrated IC                                | 24 |

|   |       | 2.2.3   | Stacked silicon submounts                    | 29 |

|   |       | 2.2.4   | Conclusion                                   | 32 |

|   | 2.3   | Optic   | al design                                    | 33 |

|   | 2.4   | Fabrio  | cation process                               | 35 |

|   |       | 2.4.1   | Metallization in cavity                      | 36 |

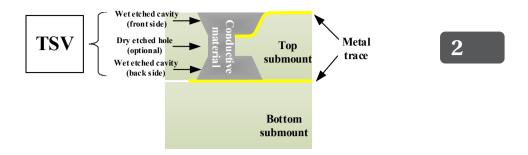

|   |       | 2.4.2   | Dedicated TSV process                        | 38 |

|   |       | 2.4.3   | Embedded passive device                      | 38 |

|   | 2.5   | Sumn    | nary                                         | 40 |

|   | Refe  | erences | 3                                            | 40 |

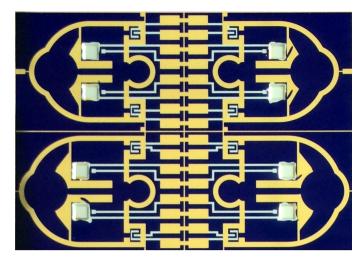

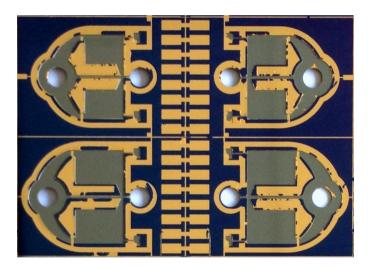

| 3 | 3D.9  | SiP Eng | abled Smart SSL Module                       | 43 |

| • |       |         | luction                                      | 44 |

|   | 3.2   |         | ept and Design                               |    |

|   |       |         | Module description                           |    |

viii Contents

|   |       | 3.2.2 Circuit Design                                        | 5 |

|---|-------|-------------------------------------------------------------|---|

|   |       | 3.2.3 Submount design                                       | 6 |

|   | 3.3   | Fabrication and assembly                                    | 0 |

|   |       | 3.3.1 Top submount                                          | 1 |

|   |       | 3.3.2 Bottom submount                                       | 2 |

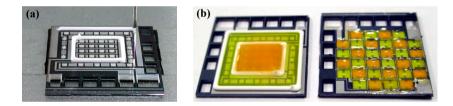

|   |       | 3.3.3 Assembly                                              | 5 |

|   |       | 3.3.4 Module integration                                    | 6 |

|   | 3.4   | Testing and Characterization                                | 7 |

|   |       | 3.4.1 Function validation                                   | 8 |

|   |       | 3.4.2 Thermal test                                          | 8 |

|   |       | 3.4.3 Optical test                                          | 0 |

|   | 3.5   | Conclusions and outlooks                                    | 1 |

|   | Refe  | erences                                                     | 2 |

| 4 | Silic | con Microfabrication based PM Sensor 6                      | 5 |

|   | 4.1   | Introduction                                                | 6 |

|   | 4.2   | System design                                               | 7 |

|   |       | 4.2.1 The sensing unit                                      | 8 |

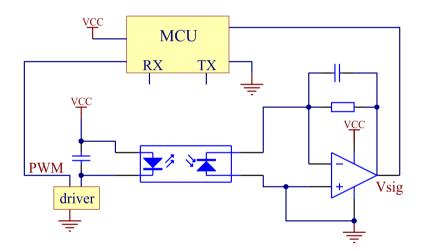

|   |       | 4.2.2 Control circuitry                                     | 3 |

|   | 4.3   | Fabrication and Assembly                                    | 4 |

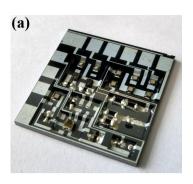

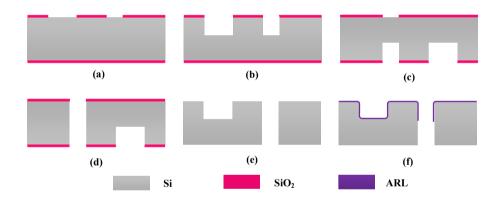

|   |       | 4.3.1 Bottom submount                                       | 4 |

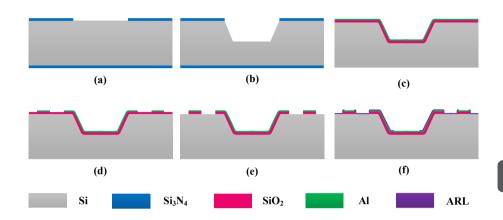

|   |       | 4.3.2 Top submount                                          | 5 |

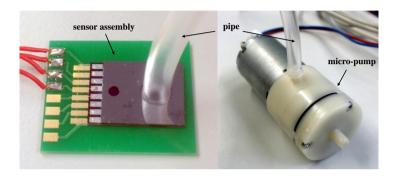

|   |       | 4.3.3 Final assembly                                        | 6 |

|   | 4.4   | Testing and Characterization                                | 7 |

|   |       | 4.4.1 Testing setup                                         | 7 |

|   |       | 4.4.2 Testing results                                       | 8 |

|   | 4.5   | Conclusion                                                  | 2 |

|   | Refe  | erences                                                     | 3 |

| 5 | Inte  | egrated Virtual Impactor Enabled PM <sub>2.5</sub> Sensor 8 | 7 |

|   | 5.1   | Introduction                                                |   |

|   | 5.2   | Design and Fabrication                                      | 9 |

|   |       | 5.2.1 Virtual impactor                                      |   |

|   |       | 5.2.2 Optical design                                        |   |

|   |       | 5.2.3 Submount fabrication                                  | 7 |

|   |       | 5.2.4 Packaging and assembling                              | 9 |

CONTENTS ix

|    | 5.3     | Testin  | ng and characterization          | . 99  |

|----|---------|---------|----------------------------------|-------|

|    |         | 5.3.1   | Lab testing                      | . 100 |

|    |         | 5.3.2   | Field testing                    | . 101 |

|    | 5.4     | Discu   | ssion and recommendation         | . 101 |

|    | Refe    | rences  | 3                                | . 103 |

| 6  | Con     | clusio  | ns and Outlook                   | 105   |

|    | 6.1     | Concl   | lusions                          | . 105 |

|    |         | 6.1.1   | Multi-physical design            |       |

|    |         | 6.1.2   | Silicon microfabrication process |       |

|    |         | 6.1.3   | Smart SSL module                 |       |

|    |         | 6.1.4   | Miniaturization of PM sensor     |       |

|    | 6.2     | Outlo   | ok                               | . 108 |

|    | Refe    | rences  | 3                                | . 108 |

| Su | ımma    | ary     |                                  | 111   |

| Sa | men     | vatting | g                                | 115   |

| Ac | knov    | vledge  | ements                           | 119   |

| Cı | ırricı  | ılum V  | <sup>7</sup> itæ                 | 123   |

| Li | st of l | Public  | ations                           | 125   |

1

# Introduction

#### 1.1. BACKGROUND

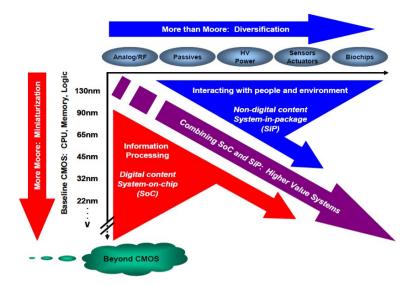

Human beings have entered era of "intelligence" and we have seen enormous advances in many aspects of our daily life. The human society is quickly transformed by knowledge accumulation and technology innovation. Man effort goes especially towards a self-learning and self-sustainable environment. The concept of "smart device" has penetrated into cities and communities, houses and vehicles, as well as many industries [1-3]. As more and more smart devices are equipped in our surroundings or even on or in our body, two main requirements are raised towards the devices themselves: increased functionalities and increased miniaturization. These requirements happen to reflect the mainstream trend in microelectronics industry. For decades the microelectronics industry has been fueled by Moore's law and the outcome is today's powerful integrated circuit (IC) with more functionalities and smaller sizes than ever before [4]. The "smart" trend in our daily lives is possible because of the development in the microelectronic industry. On the other hand, the increased functionalities and miniaturization can also be achieved through system level integration which goes beyond the boundaries of Moore's law into the area of "More than Moore" (or MtM). MtM refers to all technologies enabling nondigital functions that do not simply scale with Moore's law, but provide additional value in different ways - to migrate from the system board-level into the package (or system in package, SiP) or onto the chip [5]. Such combination of digital function with complementary non-digital content is depicted in Figure 1.1. In the following paragraphs, two key enabling technologies for MtM, SiP and wafer level packaging (WLP), will be introduced.

Figure 1.1: Dual trend in the International Technology Roadmap for Semiconductors (ITRS): diversification and miniaturization [6].

#### 1.1.1. SIP TECHNOLOGY

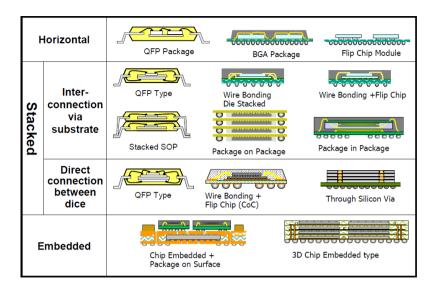

In general, MtM requires higher density of functionality beyond chip level and this drives the integration of function to migrate from board-level to package-level. The concept of SiP has been gaining popularity due to its capability to fulfill the semiconductor industry demands for higher level of integration and lower costs. From the ITRS white paper, SiP is defined as "a combination of multiple active electronic components of different functionality, assembled in a single unit that provides multiple functions associated with a system or sub-system. A SiP may optionally contain passive devices, MEMS (microelectro-mechanical systems), optical components and other packages and devices" [7]. Figure 1.2 depicts the major categories of SiP structures [8].

SiP possesses many advantages as an enabling technology of MtM [7]. It provides smaller form factor compare with discrete individually packaged devices. SiP enhances the system performance by means of shorter interconnections and better shielding. More importantly, it reduces time-to-market through concurrent development of module and system, more design flexibility and easy redesign. For volume production, the concept of SiP also helps reduce the cost by eliminating the IC packaging process and increasing yield. Besides, SiP has the generic compatibility with heterogeneous integration of various die technologies including Si, GaAs, SiGe, SOI, MEMS, etc., providing great benefit for MtM system integration [9].

1.1. BACKGROUND 3

Figure 1.2: Examples of SiP structures which can be generally divided into three categories: horizontal placement, stacked structures, and embedded structures [8].

#### 1.1.2. WAFER LEVEL PACKAGING

As more functionalities are integrated into one single package, the miniaturization of packaging becomes challenging. WLP has become a promising solution for highly integrated packaging [4]. WLP inherently enables the miniaturization of a package and thus a system since the achieved package owns almost the same size of the die. To realize 3D WLP, one of the key enabling technologies is the vertical interconnection between wafers, such as the most widely used through-silicon-via (TSV) approach. The attempt of implementing TSV technology into semiconductor industry has been trying for many years. However, due to many critical issues of this technology, the introduction into high volume manufacture has been hindered [10]. Different TSV players provide varied solution based on their unique technical strength, whereas the applications of TSV can be broadly categorized into three types [10]:

- (a) vertical interconnection to the backside of the wafer, with no die stacking, enabling chip-scale-packaging (CSP) by eliminating the reserved space for input/output (I/O) pads;

- (b) 2.5D integration, or TSV-enabled interposer technology, while the Si interposer acts as a packaging substrate for multiple dies mounted side-by-side on it; and

- (c) 3D integration, where active dies are equipped with TSVs and stacked on each

4 1. Introduction

other to form a die stack, which is expected to be the ultimate application of TSVs.

The WLP design equipped with TSV will become clear in following chapters of this thesis. Different from conventional TSV, dedicated process is oriented by the smart device applications and serves in the silicon interposer of 2.5D integration.

#### 1.2. APPLICATIONS ENABLED MTM

#### 1.2.1. FUNCTION ENRICHMENT IN SOLID STATE LIGHTING

Solid state lighting (SSL) refers to "a type of lighting that uses semiconductor light emitting diodes (LEDs), organic light emitting diodes (OLED), or polymer light emitting diodes (PLED) as sources of illumination rather than electrical filaments, plasma (used in arc lamps such as fluorescent lamps), or gas" [11]. Among all, LEDs are most used light source currently and gaining increasing interest from various applications due to the many advantages over traditional incandescent light source such as, "lower energy consumption, longer lifetime, improved physical robustness, smaller size, and faster switching" [12].

Traditionally the LED chips are packaged individually and used as discrete devices in systems. Nowadays, however, intelligent lighting applications require the LED package or module to deliver more functionalities while maintain small form factor. Currently available technologies for LED packaging are inherited from traditional IC industry that when applied to LEDs can often not fulfill the requirements. Common practice for consumer electronics in terms of packaging and assembly is mother circuit board plus packaged discrete devices. The problems of such solution for intelligent lighting applications are quite evident. First of all, the bulkiness of board level assembly hinders some application scenarios where the space is restricted. To reduce the system size, getting rid of the device package can be one way. As mentioned in Section 1.1, novel packaging methods are gaining popularity. Second of all, thermal management is crucial for LED applications because the heat density of the LEDs is relatively high. For applications to which form factor or cost is of little concern, the thermal issue can be solved by using large and complicated heat dissipation system. In other cases, neither the size nor the cost is affordable. Traditional board level assembly exhibits serious thermal issues for LED applications when more functionalities, meaning more components, are integrated. Last but not least, the market never stops seeking cheaper solutions. There is little room for cost reduction in the field of traditional packaging besides reducing material cost. Cost economical process for massive production is one direction where endeavors are kept inputting.

To find solutions for the aforementioned issues, attempts have been continuously made [13]. One direction is the adoption of silicon in the packaging and silicon-based SiP. The popularity of silicon comes from its unique features over other candidate materials, including high thermal and mechanical properties and compatibility with IC / MEMS processing. Moreover, the involvement of silicon means introducing semiconductor process into the LED packaging field. One of the obvious benefits of such introduction is the fact that tradition IC industry has developed a whole set of cost control strategy. Process-wise, technology like wafer level processing can greatly reduce the cost. Facility-wise, currently existed IC fabrication and packaging lines are accessible for emerging applications. Some key progresses will be reviewed in this section to show the technical directions.

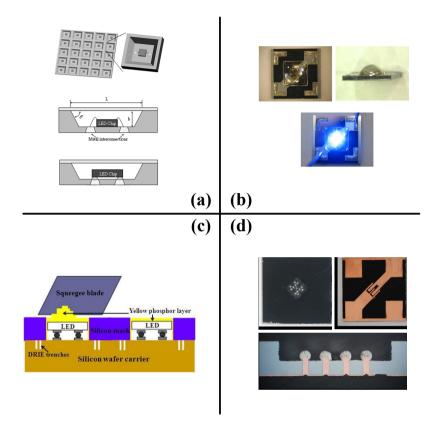

As early as the year of 2006, Tsou developed a silicon-based packaging platform with embedded solder interconnections for LEDs (Figure 1.3 (a)) [14]. The presented novel package design was enabled by silicon micromachining and proved to enhance the reliability and thermal management of high power LED packages. Clearly stated in the paper was that the technique could help achieve low-cost process by incorporating the advantages of traditional IC and MEMS packaging together, such as batch processing. Lee's research group has done extensive investigations on WLP process for LED applications. Wafer level lens molding process is fulfilled by integrated deep reactive-ion etching (DRIE) trenches without using any mold. Such process can be implemented into LED encapsulation as well as optical lens molding, as shown in Figure 1.3 (b) [15–17]. Wafer level phosphor printing process is developed or white LED packaging with improved conformity [18], followed by further integration of phosphor printing with moldless encapsulation (Figure 1.3 (c))[19]. A recent progress demonstrates feasible integration of copper-filled TSVs for 3D interconnection (Figure 1.3 (d))[20], which proves to be a complete packaging process for LED packaging.

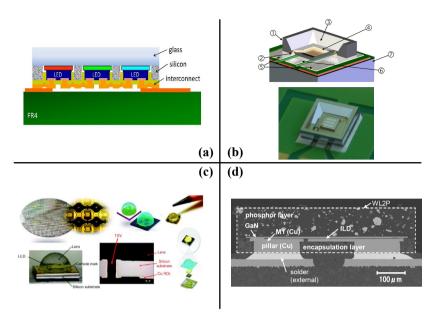

In industry, novel LED packaging technologies have also been demonstrated by various products. Philips demonstrated a fabrication technique for a multi-LED, multi-color module package (Figure 1.4 (a))[21]. This effort proves to be a first step towards high power LED packaging compatible with high working temperature. In 2007, Hymite released its new product HyLED $^{TM}$ , a silicon wafer packaging solution for high brightness (HB) LEDs (Figure 1.4 (b))[22]. As stated in the paper, the solution provides excellent thermal performance and satisfying reliability. TSMC and its subsidiary VisEra announced their new packaging technology for HB LEDs based on 8-inch wafer production line (Figure 1.4 (c))[23–26]. In 2012, Toshiba proposed a novel WLP technology for white LEDs (Figure 1.4 (d))[27]. The technology was claimed to achieve extremely low

6 1. Introduction

Figure 1.3: Silicon-based WLP for LEDs: (a) silicon-based packaging platform with embedded solder interconnections [14]; (b) wafer level LED encapsulation [15–17]; (c) wafer level phosphor printing [19]; (d) WLP for LEDs with integrated TSVs [20].

cost and small size and the package was confirmed to display enough robustness and excellent thermal performance.

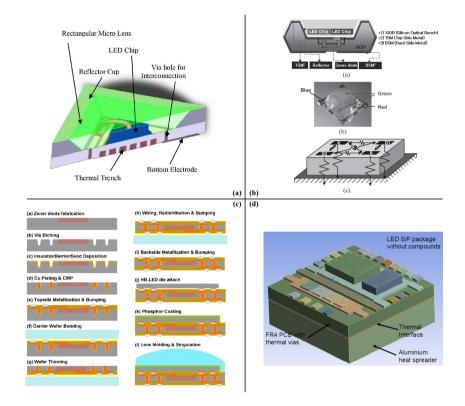

Though most of the above efforts provide wafer level or batch process, the output is mainly single LED package with no integrated functionality. Since one of the advantages of the silicon material is to enable direct integration of intelligence, using silicon simply as packaging substrate or submount seems to be a waste of talent. Samsung presented a new concept of multi-chip LED package with integrated thermal trenches and electrodes in silicon substrate (Figure 1.5 (a))[28]. The design was proved to provide enhanced thermal performance as well as improved light efficiency. LG Innotek demonstrated WLP design for white LEDs with multi-chip LEDs (Figure 1.5 (b))[29]. It made

Figure 1.4: Industrialized silicon packaging for LEDs: (a) multi-LED, multi-color module package [21]; (b) silicon-based HB LED package from Hymite [22]; (c) silicon-based HB LED package from TSMC [23, 24]; (d) WLP for white LEDs [27].

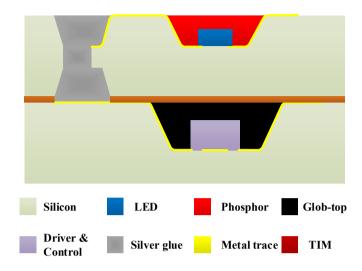

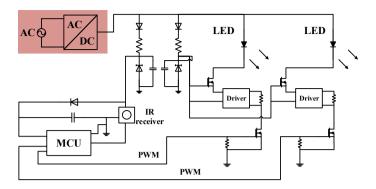

a further step of silicon integration by fabricating Zener diode in the silicon submount to facilitate thermal management of the LEDs. Similarly, EV Group also demonstrated the integration of Zener diode in their total solution of silicon-based WLP for HB-LEDs (Figure 1.5 (c))[30]. NXP made further attempt in the same direction (Figure 1.5 (d))[31]. Instead of silicon, a piece of PCB is used to demonstrate the design concept. The proposed LED SiP consists of LEDs, driver dies, and passive components, all of which are hosted on a QFN (quad-flat no-leads)-like package. In the following chapters of this thesis, silicon-based packaging platform for LED packages will be presented and a fully integrated SiP for smart LED module will be demonstrated.

#### 1.2.2. MINIATURIZATION OF PARTICULATE MATTER SENSOR

Particulate matter, or PM, is the term for a mixture of solid particles and liquid droplets found in the air [32]. With the increase of human activities, both living and manufacturing, over-exhausted particles in the air has become serious issue to human health [33–36]. More and more researches indicate that long-time exposure to particle polluted air is linked to many diseases. To avoid unhealthy exposure, people have demanding

Figure 1.5: Industrial attempt for system integration in silicon packaging for LEDs: (a) multi-chip LED package with integrated silicon-based thermal trenches and electrodes [28]; (b) WLP for white LEDs with multi-LEDs [29]; (c) silicon-based WLP for HB-LEDs with integrated Zener diode [30]; (d) PCB-based SiP for LED module [31].

desire to monitor the air quality, preferably at economical cost. In general, the finer the particles are, the more damage they will pose on human bodies because the deeper they can penetrate into the body. Real-time monitoring fine particles in the atmosphere has been a quite hot topic.

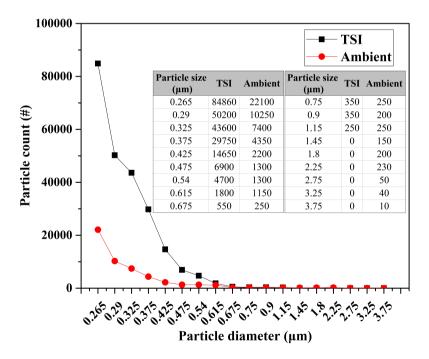

In laboratories, scientists have plenty of tools and methods to measure the particle concentration in sampled air. However, tools that do not require much professional knowledge or complicated operational procedures are not widely available. Especially, when required high measuring accuracy, few candidates can deliver satisfying performances. Different principles can be employed for measuring PM concentration, among which the optical methods, such as light scattering method, are most widely used in low cost monitors. The Sharp GP2Y1010 sensor is among the first commercial dust sensors with small size and low cost that to some extent can be used to monitor PM concentra-

tion [37]. Plenty of literatures are available online about the characterization and validation of this sensor and all validate that for this sensor PM concentration can be detected but only through careful calibration with trustable reference monitors. For instance, the TECO research group has conducted extensive validation of the Sharp sensor using their customized toolkit [38–41]. Some open access resource also demonstrates the application of the Sharp sensor [42]. Similar sensor from Shinyei (PPD42NS) has also been investigated on the performance and the characterization [43–48]. DSM501 is another dust sensor module from Samyoung but so far no validation results are available online [49]. In the evaluation report from US Environmental Protection Agency in 2014, several inexpensive portable PM monitors were evaluated at field conditions [50], and the same agency also provide a guidance for the selection of such sensors for personal use [51].

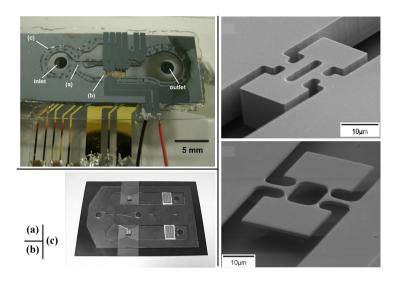

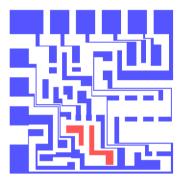

Silicon-based microfabrication provides the possibility of making very small devices and thus attracts increasing research interest for miniaturization of PM sensors [52]. Beside the optical methods, other methods including film bulk acoustic resonator (FBAR) [53], electrical low pressure impactor (ELPI) [54] and I-shaped bulk acoustic resonator (IBAR) [55] have also been investigated and sensors based on these methods are realized by silicon microfabrication, as shown in Figure 1.6. Beside the feasibility of miniaturization, the silicon-based process will enable further integration, as described in Section 1.1, and provide more benefits such as cost effectiveness. In this thesis, silicon microfabrication enabled PM sensor design will be presented with design optimization and full characterization.

#### 1.3. RESEARCH OBJECTIVE

This thesis focuses on developing novel SiP approach serving the need of MtM. The proposed approach is designed to serve applications with such requirements as highly integrated functionality but compact form factor, multi-physical design involved but simple fabrication process required, high reliability but low cost. These challenging trade-offs are the main obstacles that this research is set to overcome. One of the research approach employed in this thesis is the combination of the development of common design rules and the demonstration of specific applications. The design rules deal with the shared elements or aspects in the development of individual applications, and provide a technology platform for related applications. More considerations need to be taken into account when it comes to certain application based on the common platform. Multiphysical design will be intensely addressed in this thesis as it is the most challenging part in such system design, whereas the most valuable novelty of this research to the whole community.

10 1. Introduction

Figure 1.6: Silicon microfabrication enabled miniaturized PM sensor based on different operation methods: (a) FBAR [53]; (b) ELPI [54]; (c) IBAR [55].

#### 1.4. THESIS OUTLINE

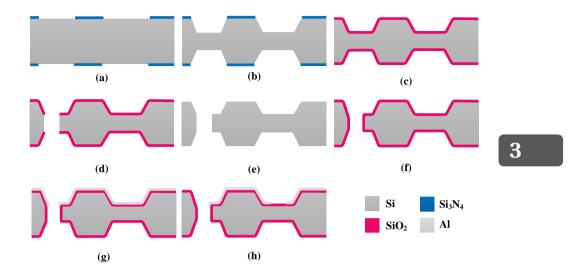

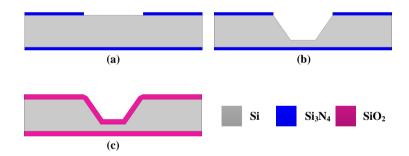

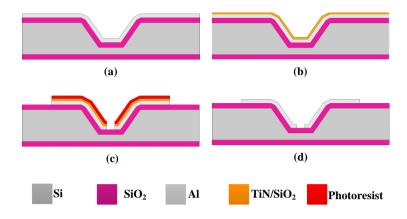

The rest of this thesis is structured as follows. Chapter 2 focuses on the silicon-based packaging design for SSL applications. Simulation assisted thermal analysis is firstly presented on three subjects: remote phosphor, integrated IC and stacked submounts. In a white LED package, phosphor acts as the color converter and the degradation of its performance highly depends on the working temperature. The remote phosphor design is an effective approach to improve the lifetime of phosphor and the LED module. Smart LED modules include LEDs, ICs, controllers and even sensors. The temperature of IC chips is strongly affected by the LEDs, the main source of heat. Thermal design is also conducted on a stacked silicon submount module, proposed approach for 3D SiP for SSL applications. Optical analysis is performed for silicon-based LED packaging to evaluate the light effect of silicon substrate. Some key processes widely used in silicon-based SSL packaging are also presented in Chapter 2. Special treatment is needed for metallization in deep cavity to obtain high quality of fabrication. Vertical interconnection is another enabling design for system integration. Conventional TSV does not always fit the need of heterogeneous integration. More dedicated and cost effective approach is presented in Chapter 2. As important parts of a electronic system, passive devices cost comparable area with ICs. Different designs for embedding passive devices into silicon submount are demonstrated at the end of Chapter 2. Based on the analysis in Chapter 2, Chap-

ter 3 focuses on fulfilling a miniaturized 3D SiP design for a smart lighting module. The multi-physical analysis is firstly performed based on the specific features of the application, covering thermal management, optical optimization and interconnection design. The SiP module is realized by silicon microfabrication and WLP process. Full characterization is conducted and the module shows satisfying performance in terms of thermal and optical parameters, proving the presented SiP design as promising approach for miniaturization of smart lighting application.

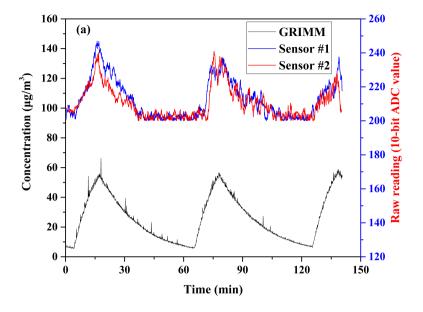

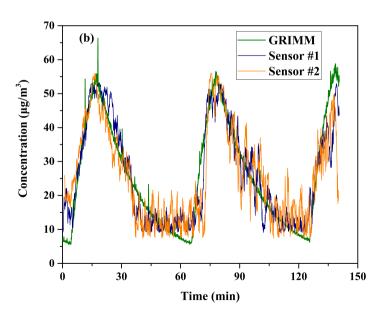

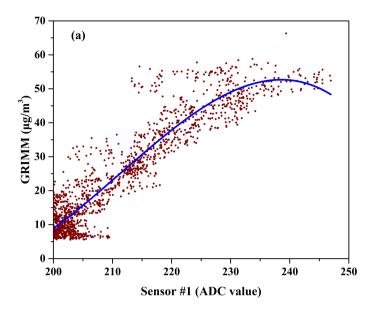

With the increasing public awareness of the impact of PM on human health, real-time monitoring of PM exposure level has attracted more interest than ever before. Chosen as another application scenario of MtM, miniaturized PM sensor is realized and presented in Chapter 4. Multi-physical analysis is needed for PM sensor design, but with more focus on enabling high sensitivity and accuracy of the measurement. Silicon microfabrication is used to realize the sensor. The testing results reveal that the sensor displays excellent performance, including high sensitivity and accuracy, low power consumption and compact size. In Chapter 5, an integrated virtual impactor (VI) is added to the PM sensor to enable detection of PM concentration in different size fractions. The design of the VI is optimized by both theoretical and simulation analysis. Systematic characterization and calibration is explained in detail in this chapter.

In Chapter 6 the main conclusions of this thesis are summarized. The achievement of this thesis opens more room for future potential applications as well as further technology development. An outlook towards the future work is also given at the end of the thesis.

#### REFERENCES

- [1] R. G. Hollands, Will the real smart city please stand up? intelligent, progressive or entrepreneurial? City 12, 303 (2008).

- [2] R. Harper, Inside the smart home (Springer Science & Business Media, 2006).

- [3] M. Behan and O. Krejcar, *Modern smart device-based concept of sensoric networks*, EURASIP Journal on Wireless Communications and Networking **2013**, 1 (2013).

- [4] J. Lau, C. Lee, C. S. Premachandran, and A. Yu, *Advanced MEMS packaging* (McGraw-Hill, 2010).

- [5] G.-Q. Zhang and A. V. Roosmalen, *More than moore* (Springer, 2009).

- [6] W. Arden, M. Brillouët, P. Cogez, M. Graef, B. Huizing, and R. Mahnkopf, *More-than-moore white paper*, Version **2**, 14 (2010).

[7] W. Chen, W. Bottoms, K. Pressel, and J. Wolf, *The next step in assembly and packaging: system level integration in the package (sip)*, ITRS White Paper **9** (2008).

- [8] http://www.itrs2.net/itrs-reports.html.

- [9] F. Roozeboom, A. Kemmeren, J. Verhoeven, F. Van den Heuvel, J. Klootwijk, H. Kretschman, T. Fric, E. van Grunsven, S. Bardy, C. Bunel, *et al.*, *More than moore: towards passive and si-based system-in-package integration*, in *Electrochem. Soc. Symp. Proc*, Vol. 8 (2005) pp. 16–31.

- [10] J. P. Gambino, S. A. Adderly, and J. U. Knickerbocker, An overview of through-siliconvia technology and manufacturing challenges, Microelectronic Engineering 135, 73 (2015).

- [11] https://en.wikipedia.org/wiki/Solid-state\_lighting.

- [12] https://en.wikipedia.org/wiki/Light-emitting\_diode.

- [13] S. Liu and X. Luo, *LED packaging for lighting applications: design, manufacturing, and testing* (John Wiley & Sons, 2011).

- [14] C. Tsou and Y.-S. Huang, *Silicon-based packaging platform for light-emitting diode*, Advanced Packaging, IEEE Transactions on **29**, 607 (2006).

- [15] R. Zhang and S.-W. R. Lee, *Wafer level encapsulation process for led array packaging*, in *Electronic Materials and Packaging*, 2007. *EMAP 2007. International Conference on* (IEEE, 2007) pp. 1–8.

- [16] R. Zhang and S. R. Lee, Wafer level led packaging with integrated drie trenches for encapsulation, in Electronic Packaging Technology & High Density Packaging, 2008. ICEPT-HDP 2008. International Conference on (IEEE, 2008) pp. 1–6.

- [17] R. Zhang and S. R. Lee, *Moldless encapsulation for led wafer level packaging using integrated drie trenches*, Microelectronics Reliability **52**, 922 (2012).

- [18] J. C. Lo, S. Lee, R. Zhang, and M. Li, Reverse wire bonding and phosphor printing for led wafer level packaging, in Electronic Components and Technology Conference (ECTC), 2012 IEEE 62nd (IEEE, 2012) pp. 1814–1818.

- [19] K. Chen, R. Zhang, and S. R. Lee, *Integration of phosphor printing and encapsulant dispensing processes for wafer level led array packaging*, in *Electronic Packaging Technology & High Density Packaging (ICEPT-HDP), 2010 11th International Conference on (IEEE, 2010)* pp. 1386–1392.

[20] R. Zhang, S. R. Lee, D. G. Xiao, and H. Chen, *Led packaging using silicon substrate with cavities for phosphor printing and copper-filled tsvs for 3d interconnection,* in *Electronic Components and Technology Conference (ECTC), 2011 IEEE 61st* (IEEE, 2011) pp. 1616–1621.

1

- [21] M. De Samber, T. V. d Ackerveken, M. Burghoom, N. Bruinsma, and E. Van Grunsven, A new embedded packaging technology for high power leds, in Electronics Packaging Technology Conference, 2008. EPTC 2008. 10th (IEEE, 2008) pp. 242–248.

- [22] T. Murphy, S. Weichel, S. Isaacs, and J. Kuhmann, *A silicon wafer packaging solution for hb-leds*, in *Manufacturing LEDs for Lighting and Display* (International Society for Optics and Photonics, 2007) pp. 67970F–67970F.

- [23] P. Garrou, M. Koyanagi, and P. Ramm, *Handbook of 3D Integration: Volume 3-3D Process Technology* (John Wiley & Sons, 2014).

- [24] C. Zinck, 3d integration infrastructure & market status, in 3D Systems Integration Conference (3DIC), 2010 IEEE International (IEEE, 2010) pp. 1–34.

- [25] C. G. Greisen, Semiconductor-based sub-mounts for optoelectronic devices with conductive paths to facilitate testing and binning, (2010), uS Patent 7,838,878.

- [26] C. G. Greisen, Semiconductor-based sub-mounts for optoelectronic devices with conductive paths, (2013), uS Patent 8,357,934.

- [27] A. Kojima, M. Shimada, Y. Akimoto, M. Shimojuku, H. Furuyama, S. Obata, K. Higuchi, Y. Sugizaki, and H. Shibata, *A fully integrated novel wafer-level led package (wl2p) technology for extremely low-cost solid state lighting devices*, in *Interconnect Technology Conference (IITC)*, 2012 IEEE International (IEEE, 2012) pp. 1–3.

- [28] W. K. Jeung, S. H. Shin, S. Y. Hong, S. M. Choi, S. Yi, Y. B. Yoon, H. J. Kim, S. J. Lee, and K. Yeol, *Silicon-based, multi-chip led package*, in *Electronic Components and Technology Conference*, 2007. ECTC'07. Proceedings. 57th (IEEE, 2007) pp. 722–727.

- [29] J.-M. Kang, J.-H. Choi, D.-H. Kim, J.-W. Kim, Y.-S. Song, G.-H. Kim, and S.-K. Han, *Fabrication and thermal analysis of wafer-level light-emitting diode packages*, Electron Device Letters, IEEE **29**, 1118 (2008).

- [30] T. Uhrmann, T. Matthias, and P. Lindner, Silicon-based wafer-level packaging for cost reduction of high brightness leds, in Electronic Components and Technology Conference (ECTC), 2011 IEEE 61st (IEEE, 2011) pp. 1622–1625.

14 References

1

[31] A. Gielen, P. Hesen, F. Swartjes, H. van Zeijl, F. Boschman, J. Bullema, R. Werkhoven, and S. Koh, *Development of an intelligent integrated led system-in-package*, in *Microelectronics and Packaging Conference (EMPC)*, 2011 18th European (IEEE, 2011) pp. 1–7.

- [32] https://www3.epa.gov/pm/basic.html.

- [33] M.-A. Kioumourtzoglou, J. D. Schwartz, M. G. Weisskopf, S. J. Melly, Y. Wang, F. Dominici, and A. Zanobetti, *Long-term pm2*. *5 exposure and neurological hospital admissions in the northeastern united states*, Environmental health perspectives **124**, 23 (2016).

- [34] E. Boldo, S. Medina, A. Le Tertre, F. Hurley, H.-G. Mücke, F. Ballester, I. Aguilera, et al., Apheis: Health impact assessment of long-term exposure to pm2. 5 in 23 european cities, European journal of epidemiology **21**, 449 (2006).

- [35] J. R. Brook, T. F. Dann, and R. T. Burnett, *The relationship among tsp, pm10, pm2. 5, and inorganic constituents of atmospheric participate matter at multiple canadian locations*, Journal of the Air & Waste Management Association **47**, 2 (1997).

- [36] X. Wang, X. Bi, G. Sheng, and J. Fu, *Hospital indoor pm10/pm2*. 5 and associated trace elements in guangzhou, china, Science of the Total Environment **366**, 124 (2006).

- [37] https://www.sharpsde.com/products/optoelectronic-components/model/GP2Y1010AU0F/#productview.

- [38] http://www.teco.kit.edu/.

- [39] M. Budde, R. El Masri, T. Riedel, and M. Beigl, *Enabling low-cost particulate matter measurement for participatory sensing scenarios*, in *Proceedings of the 12th international conference on mobile and ubiquitous multimedia* (ACM, 2013) p. 19.

- [40] M. Budde, P. Barbera, R. El Masri, T. Riedel, and M. Beigl, *Retrofitting smartphones* to be used as particulate matter dosimeters, in *Proceedings of the 2013 International Symposium on Wearable Computers* (ACM, 2013) pp. 139–140.

- [41] M. Budde, M. Busse, and M. Beigl, *Investigating the use of commodity dust sensors* for the embedded measurement of particulate matter, in Networked Sensing Systems (INSS), 2012 Ninth International Conference on (IEEE, 2012) pp. 1–4.

- [42] http://www.howmuchsnow.com/arduino/airquality/.

- [43] http://www.shinyei.co.jp/stc/optical/main\_ppd42ns\_e.html.

- [44] D. M. Holstius, A. Pillarisetti, K. Smith, and E. Seto, *Field calibrations of a low-cost aerosol sensor at a regulatory monitoring site in california*, Atmospheric Measurement Techniques **7**, 1121 (2014).

- [45] M. Gao, J. Cao, and E. Seto, *A distributed network of low-cost continuous reading sensors to measure spatiotemporal variations of pm2. 5 in xi'an, china,* Environmental pollution **199**, 56 (2015).

- [46] http://www.ijirset.com/upload/2015/february/76\_Evaluation.pdf.

- [47] E. Austin, I. Novosselov, E. Seto, and M. G. Yost, *Laboratory evaluation of the shinyei* ppd42ns low-cost particulate matter sensor, PloS one **10**, e0137789 (2015).

- [48] http://www.howmuchsnow.com/arduino/airquality/grovedust/.

- [49] http://www.samyoungsnc.com/products/3-1%20Specification%20DSM501.

pdf.

- [50] https://cfpub.epa.gov/si/si\_public\_record\_report.cfm?dirEntryId= 297517.

- [51] https://cfpub.epa.gov/si/si\_public\_record\_Report.cfm?dirEntryId= 277996.

- [52] M. Gad-el Hak, *The MEMS handbook* (CRC press, 2001).

- [53] I. Paprotny, F. Doering, P. A. Solomon, R. M. White, and L. A. Gundel, *Microfabricated air-microfluidic sensor for personal monitoring of airborne particulate matter: Design, fabrication, and experimental results*, Sensors and Actuators A: Physical **201**, 506 (2013).

- [54] H. Lim, D. Park, J. Maeng, J. Hwang, and Y. Kim, *Mems based integrated particle detection chip for real time environmental monitoring*, in *Micro Electro Mechanical Systems*, 2006. MEMS 2006 Istanbul. 19th IEEE International Conference on (IEEE, 2006) pp. 62–65.

- [55] A. Hajjam, J. C. Wilson, and S. Pourkamali, *Individual air-borne particle mass measurement using high-frequency micromechanical resonators*, Sensors Journal, IEEE 11, 2883 (2011).

# SILICON-BASED PACKAGING FOR SSL APPLICATIONS

Applications such as SSL embrace multi-physics design requirement. Besides optical consideration, thermal management is of great importance. This chapter focuses on the siliconbased packaging design for SSL applications. Simulation assisted thermal analysis is firstly presented on three key elements of SSL packages: phosphor, integrated IC and submount. In a white LED package, phosphor is used to convert color and the degradation of its performance links to the working temperature. The remote phosphor design is analysed and optimized. Smart LED module integrates LEDs, drivers, controllers and even sensors into a single package. The temperature of integrated ICs is strongly affected by LEDs, the main source of heat. Thermal analysis is also conducted on a structure of stacked silicon submounts, proposed approach for 3D SiP for SSL applications. Optical analysis is performed on silicon-based LED package to evaluate the light effect of the silicon submount. Several key processes development and optimization are also presented in this chapter. Metallization in cavity, commonly used in silicon -based packaging, needs special treatment to obtain high quality of fabrication. Another key enabling design is the interconnection within the integrated system. Conventional TSV does not always fit the need of heterogeneous integration. More robust and cost effective approach is presented in this chapter. As important parts of a electronic system, passive devices cost comparable area with ICs. Different designs for embedding passive devices into silicon submount are demonstrated at the end of this chapter.

Parts of this chapter have been published in Journal of Semiconductors 34, 5 (2013) [1] and Proceedings of 9th China International Forum on Solid State Lighting (ChinaSSL) (2012)[2, 3].

#### 2.1. Introduction

SL, represented by LEDs, has been rapidly replacing the traditional luminaires due to longer lifetime and lower energy consumption. For decades, man effort has been put into increasing light output of LED chips and reducing the cost to make the LED bulbs competitive with traditional luminaires. Recently, increasing need for smart lighting has emerged in our daily life that is made possible by the introduction of the LED itself and the need for cost reduction. Compared with other light sources, LEDs provide more colorful and tunable light. In era of MtM, smart lighting applications is embracing the trend of increased functionality and miniaturization. From the aspect of electronic packaging, new supporting technologies need to be developed.

Current approach for lighting system integration, like Philips hue bulbs, is based on standard printed circuit board (PCB) assembly [4]. The intrinsic bulkiness of this approach obstructs further function enrichment and miniaturization. Besides, thermal management of such system is extremely challenging. SiP technology has recently emerged and already shown potential in applications of radio frequency (RF) and networking. So far, SiP design for lighting system is quite new. Gielen proposed a design of intelligent integration of LED system, in which standard PCB was used as packaging substrate [5]. However, for LED applications, the main barriers for the implementation of PCB or other polymer-based substrates are insufficient thermal dissipation and coefficient of thermal expansion (CTE) mismatch-induced issues, such as unexpected warpage.

This chapter presents silicon-based packaging design for miniaturization of SSL applications. Thermal analysis is conducted on key elements of SSL packages. Optical effect of silicon submount is evaluated. Several dedicated process for SSL packaging are developed and presented. The design rules discussed in this chapter will be implemented and further demonstrated in Chapter 3 and can be used for other related applications, such sensor and MEMS packaging. The rest of this chapter is structured as follows. Section 2.2 discusses the simulation assisted thermal design on proposed SSL packaging. Optical design is presented in Section 2.3. Section 2.4 demonstrates several process development and a brief summary is given in Section 2.5.

#### **2.2.** THERMAL DESIGN

Thermal management is of great significance for SSL applications. At the device and packaging level, thermal design must be well taken care of so that the performance and lifetime of the whole system is guaranteed. In a LED package, materials with quite differ-

2.2. THERMAL DESIGN 19

ent thermal properties are dealt with when it comes to thermal management. To better understand the thermal effect on different materials and thus reduce the thermal impact on key components, simulation based analysis has been conducted. In the following section, discussions will focus on thermal design for three main elements in LED packages: phosphor, integrated IC and silicon submount. The thermal analysis in this chapter mainly focuses on the effect of the dimensional parameters. Material property also plays significant role in the thermal management and this chapter will also investigate the effect of the thermal interface material (TIM) that is widely used in SSL packages and modules.

#### **2.2.1.** REMOTE PHOSPHOR

Phosphor plays an important role in white color LEDs. The property and degradation of phosphor highly depends on the working temperature, which is affected by heat generated by LED dies and phosphor itself [6, 7]. In most of current white LED products, phosphor is directly applied onto LED dies, known as direct phosphor. The problem with direct phosphor is the thermal degradation of phosphor material due to the contact with LED dies, the temperature of which can be as high as 100 °C. The term of remote phosphor stands for the way of placement of phosphor element within a white LED module. Unlike traditional blue light based white LED where the phosphor is applied on LED chips directly, in remote phosphor design the phosphor element is positioned remotely from the LED source, thus heating of the phosphor by the LED is reduced, ensuring excellent spectral stability over time. It has already been applied into some commercialized products, like Philips MasterLED lamps [8]. Although the solution is effective against fast phosphor degradation, it is, however, facing the difficulty of integration and miniaturization. Again take Philips, the design of remote phosphor is good enough for regular lighting but may not easily be integrated into smaller LED modules which is probably the direction of next generation LED development. Another point to be noticed is that current remote phosphor solutions consume large amount of phosphor material which is of higher and higher price, meaning the cost is another driving force for developing new remote phosphor technologies.

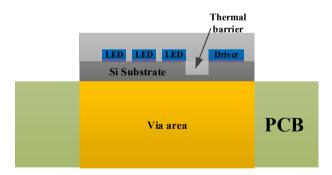

In our design, we propose a preform-based remote phosphor solution. In this approach, all LEDs and related driver circuitry are first encapsulated by polymer based material and then another preformed phosphor film is mounted on top. By this means, the phosphor and the LEDs are separated by a thin layer of polymer which acts as a thermal barrier to reduce the thermal impact on the phosphor.

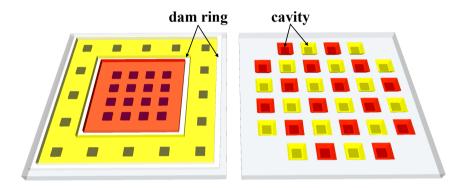

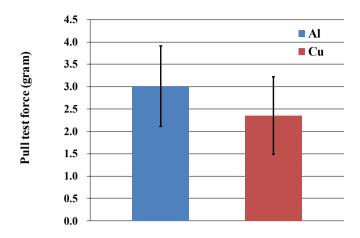

#### MODULE DESCRIPTION

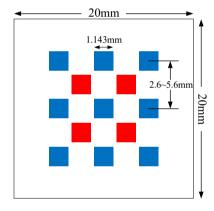

Phosphor is commonly used in LED package to convert the original light from the LED chips to get more colorful light or white light. Blue LEDs and red LEDs are usually used as light sources in the LED packages. Since individual LED acts as a point light source, to get conformal light output, multiple LEDs are placed in a package or luminaire. As a representative, a module consisting of thirteen LEDs is analysed in this section. Nine blue LEDs are arranged in a three-by-three array and four red LEDs form a two-by-two array, as shown in Figure 2.1. The cross-sectional structure is shown in Figure 2.2. All the LEDs are bonded onto a silicon substrate through TIM and then encapsulated by silicone. A layer of 3  $\mu$ m oxide on silicon substrate is also taken into consideration. The phosphor power is mixed with silicone and then cured to form a layer of 500  $\mu$ m on top of LEDs area. The whole module is attached onto an aluminum heat sink for heat dissipation. Dimensions of the module are listed in Table 2.1.

Figure 2.1: Layout of LEDs in the module (not to scale): nine blue LEDs (three-by-three array) and four red LEDs (two-by-two array).

#### SIMULATION MODEL

Finite element analysis (FEA) is a fast and effective way of investigating the effect of multiple systematic parameters and their interactions on the performance of a system. To evaluate the impact of the dimension of the LED module on the temperature distribution, FEA is firstly conducted by COMSOL [9] and the module of *heat transfer in solids* is used. The heat transfer mode considered in the analysis is conduction and convection while radiation that causes negligible effect is ignored. The heat is transferred through

Figure 2.2: Cross-sectional view of the LED module (not to scale).

Table 2.1: Dimension of the LED module.

| Component                | Dimension                                                             |

|--------------------------|-----------------------------------------------------------------------|

| LED die                  | 1143 μm × 1143 μm × 150 μm                                            |

| LED module               | $20 \text{ mm} \times 20 \text{ mm} \times (1.5 \sim 3.5) \text{ mm}$ |

| Heat sink                | $100 \text{ mm} \times 100 \text{ mm} \times 10 \text{ mm}$           |

| TIM layer (thickness)    | 10 μm                                                                 |

| Phosphor (thickness)     | 500 μm                                                                |

| Si substrate (thickness) | 525 µm                                                                |

Figure 2.3: Quarterly simulation model for thermal analysis of LED module with remote phosphor.

conduction between inner material boundaries and the outer boundary of the module is naturally convected with air unless a fixed temperature is set on some surface to simulate

2

the heat sink. The initial temperature of the module is set at room temperature (20 °C). Given the symmetry of the module, a quarterly model is simulated to save computation time, as shown in Figure 2.3. The horizontal / vertical distance between the centers of neighboring LEDs (hereinafter mentioned as pitch) determines the heat density within the module as well as the size of the whole module. The thickness of silicone encapsulant over LEDs (hereinafter mentioned as silicone thickness) affects the heat transferring between the phosphor and the LEDs. The area of the phosphor layer is linked to the amount of the phosphor consumed in each module and thus relates to the cost. To better absorb the light from the LEDs, the area of phosphor is larger than the projected LEDs area to cover as wide range of emitting angle as possible. The LEDs emit beam-like light and the light intensity peaks along the emitting axis. As the viewing angle moves away from the emitting direction, the light intensity drops quickly [10]. To simplify the parameter setting in the modelling, the angle of 45° is chosen, shown in Figure 2.2, as the effective emitting angle. Any light beyond this angle is ignored. Such optical simplification does not affect the thermal simulation.

For the simulation, 1W LED is considered and the light efficiency is assumed to be 30 %, typical value for LEDs of high quality [11], that is, 70 % of the whole power is converted into heat and dissipated to the ambient. The phosphor itself can also generate heat when converting light. Typically, the conversion efficiency of commonly used phosphor is around 90 % [12], which is also used in our simulation. The ranges of pitch and silicone thickness are listed in Table 2.2. The properties of materials are listed in Table 2.3.

Table 2.2: Range of variables for simulation.

| Variable           | Range        |

|--------------------|--------------|

| Pitch              | 1.3 - 2.8 mm |

| Silicone thickness | 0.5 - 3.5 mm |

#### **RESULTS AND DISCUSSION**

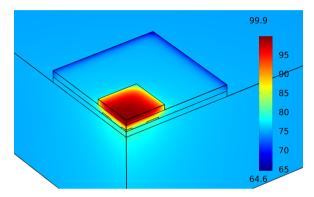

Firstly, the effect of the pitch is investigated while the silicone thickness is set as  $600 \, \mu m$ . Figure 2.4 shows a typical temperature distribution of the LED module.

The temperature of the phosphor is affected by the heat generated by LEDs and the phosphor itself. Even though the phosphor is encapsulated in silicone, the heat sink is still the dominant heat passage for phosphor due to the higher conductivity of heat sink material. This makes the heat generated inside the phosphor not easily get dissipated, so the temperature inside the phosphor is higher than LEDs.

2.2. THERMAL DESIGN 23

| Table 2.3: Therma | l property of | f the material | ls used in t | he simulation. |

|-------------------|---------------|----------------|--------------|----------------|

|-------------------|---------------|----------------|--------------|----------------|

| Material                              | Thermal conductivity (W/(m×K)) [13] |

|---------------------------------------|-------------------------------------|

| LED (Al <sub>2</sub> O <sub>3</sub> ) | 35                                  |

| Si                                    | 130                                 |

| $SiO_2$                               | 1.4                                 |

| Silicone                              | 0.22                                |

| TIM                                   | 10                                  |

| Al                                    | 160                                 |

Figure 2.4: Temperature distribution of the LED module (pitch = 1.3 mm, silicone thickness = 0.6 mm).

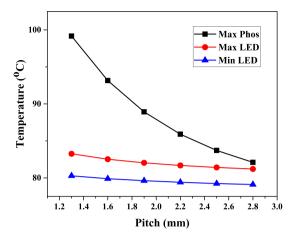

Figure 2.5 shows the temperature of phosphor and LEDs with various pitches. According to the simulation results, with increasing pitch the maximum temperature of phosphor is decreased dramatically meanwhile the temperature of LEDs only shows slight decrease. Based on this fact, we can conclude that the main reason for the reduction of the phosphor temperature is the decrease of the heat generation density and increase of the total cooling surface of phosphor because the area of phosphor layer increases as a function of the pitch. When the phosphor layer area is large enough, in this case, when the pitch is larger than 2.8 mm, so that the self-generated heat is negligible, the maximum temperature of phosphor goes down close to the temperature of LEDs.

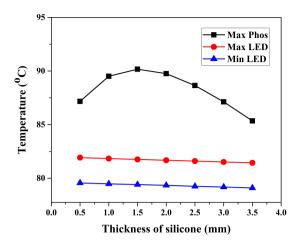

The second part of the simulation is to find out the relation between the silicone thickness and the phosphor temperature. With fixed pitch, the silicone thickness also shows impact on phosphor temperature according to the simulation results. Figure 2.6 shows the temperature of phosphor with different silicone thickness. With the increase of silicone thickness, the maximum temperature goes up first and then drops with further increase of silicone thickness. The silicone layer between the phosphor and the

Figure 2.5: Temperature change with pitch: maximum temperature of phosphor (black); maximum (red) and minimum (blue) temperature of LEDs.

LEDs can affect the phosphor temperature from two aspects: this silicone layer can increase the thermal resistance of the heat passage between the phosphor layer and the heat sink; also the silicone layer will change the phosphor layer area which is directly linked with the heat-generation density and cooling surface area. Therefore, with increasing the silicone thickness, on one hand the thermal resistance will increase and thus tend to increase the phosphor temperature, on the other hand, the increased phosphor layer area which is a function of silicone thickness, lowers the heat-generation density inside the phosphor and enlarges the cooling surface which leads to lower phosphor temperature. In our case, before the silicone thickness reaches 1.5 mm the increase of thermal resistance dominates the trend of phosphor temperature and with further increased silicone; the factors that tend to cool down the phosphor are dominant. A temperature peak of around 90 °C appears at silicone thickness of 1.5 mm. Based on the above discussion, if enough room in vertical direction, thicker silicone layer, for our case thicker than 1.5 mm, is preferred. Otherwise, for products the size of those is highly limited vertically, designers should be aware of the trend of phosphor temperature and choose proper silicone thickness to avoid the peak value of phosphor temperature.

#### 2.2.2. INTEGRATED IC

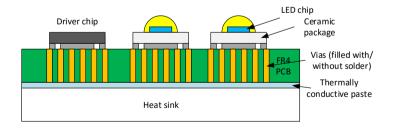

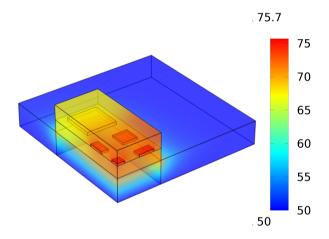

In conventional SSL module, packaged LEDs and driver ICs are assembled on PCBs, as shown in Figure 2.7. The type of the board can be metal-core PCB (MCPCB) or FR (flame

2.2. Thermal design 25

Figure 2.6: Temperature change with silicone thickness: maximum temperature of phosphor (black); maximum (red) and minimum (blue) temperature of LEDs.

retardant) 4-based PCB. However, with the increasing need for smaller and smarter lighting products, one potential solution is to integrate more components with LEDs, such as drivers, controllers and even sensors into a single package or module. The problem that comes with more integrated and compact packages is the thermal management of IC chips inside the packages. LEDs are the main source of heat in a LED module. When working, the LED temperature can be as high as 100 °C or even more for high power LEDs, while regular IC chips cannot withstand such high temperature. Typically, IC chips are designed to work under 85°C.

Figure 2.7: Crosss-sectional view of a conventional SSL module: packaged LEDs and ICs are separately mounted on PCB while the whole assembly is connected with a heat sink through TIM.

To solve this problem, there are two potential solutions: one is to enhance the ther-

mal tolerance of ICs and the other is to reduce the thermal impact of LEDs on ICs. The IC industry is a relatively mature industry and re-designing commonly used ICs would be neither cost-effective nor time-effective. In this section, we focus on finding out ways of reducing thermal impact of LEDs on ICs. The temperature distribution for integrated LED module is investigated and compared with the conventional SSL module.

#### SIMULATION MODEL

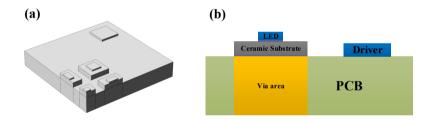

A nine-LED module integrated with four driver chips is used for simulation. For conventional SSL module, all LEDs are first packaged on ceramic substrates by a thin layer of TIM and then assembled with ICs (simulated as silicon) on a piece of PCB, as shown in Figure 2.8. For the integrated module, all the LEDs and driver ICs are mounted on a silicon substrate using TIM and then encapsulated by silicone, shown in Figure 2.9. The silicon substrate is attached on a piece of PCB through TIM. Quarterly model is simulated due to the symmetry of the module structure. The main dimensions of the models are listed in Table 2.4 and the thermal conductivity of the materials are listed in Table 2.5.

Figure 2.8: A conventional SSL module with nine LEDs and four ICs: (a)quarterly 3D model; (b) cross-sectional view.

Table 2.4: Demensions of simulation model.

| Layer              | Dimension                                                  |

|--------------------|------------------------------------------------------------|

| PCB                | $10 \text{ mm} \times 10 \text{ mm} \times 1.6 \text{ mm}$ |

| Ceramic substrate  | $2 \text{ mm} \times 2 \text{ mm} \times 0.5 \text{ mm}$   |

| Silicon substrate  | $12 \text{ mm} \times 12 \text{ mm} \times 0.8 \text{ mm}$ |

| LED chip           | $1 \text{ mm} \times 1 \text{ mm} \times 150 \mu\text{m}$  |

| Driver chip        | $2 \text{ mm} \times 2 \text{ mm} \times 200 \mu\text{m}$  |

| LED distance       | 1 mm                                                       |

| Silicone thickness | 1 mm                                                       |

|                    |                                                            |

2.2. THERMAL DESIGN 27

Figure 2.9: A integrated SSL module with nine LEDs and four ICs: (a) quarterly 3D model; (b) cross-sectional view.

Table 2.5: Material properties used in modelling.

| Material          | Thermal conductivity (W/(mK)) [13] |

|-------------------|------------------------------------|

| Ceramic substrate | 25                                 |

| FR4               | 0.3                                |

| FR4 + vias        | 10                                 |

| TIM               | 50                                 |

To simulate the heat sink, the temperature of the backside PCB is fixed at  $50\,^{\circ}$ C [14]. The PCB area under the LED packages and driver chips is with metal-filled via (effective thermal conductivity is set as  $10\,\text{K/(mW)}$ ). The power of the driver chip is consumed as  $0.5\,\text{W}$ .

#### RESULTS AND DISCUSSION

Figure 2.10 shows the temperature distribution of a conventional SSL module with the LED power of 1 W. There is a 15-20 °C drop from the LED (90 °C) to the PCB (around 70 °C). The temperature of the IC (69 °C) is slightly higher than the PCB / heat sink, but still much lower than the LED. If LEDs with higher power (2 W) are used, the temperature of the IC is not increased at all, while the temperature of the LEDs reaches 130 °C. Due to the thermal separation between the LEDs and the ICs, the thermal impact from the LEDs is not a serious issue for the ICs in conventional SSL modules. Actually, in many products the driver chips are put on a separate PCB, which makes the concern even less serious or eliminated.

In the case of integrated SSL module, the same LED power (1 W) results in lower LED temperature (76 °C) than the one in the conventional module, as shown in Figure 2.11. This is due to the higher thermal conductivity of silicon substrate over the ceramic ( $Al_2O_3$ ) substrate in traditional LED packages. Most of the heat generated in LEDs is

Figure 2.10: Temperature distribution of conventional SSL module with the LED power of 1 W.

Figure 2.11: Temperature distribution of integrated SSL module with LED power of 1 W.

conducted through the substrate to the heat sink. The integrated IC also shows similar temperature (68 °C) which does not seem to be impacted by the LEDs. When the power of LEDs increases to 2 W, the temperature of the LEDs and the ICs are 98 °C and 81 °C, respectively. Compared with traditional SSL module, LEDs still benefit from silicon while the ICs suffer from the same silicon substrate. The high thermal conductivity of silicon can transfer heat in lateral direction and behaviors like a bridge of heat between the LEDs and the ICs. The simulation results are summarized in Table 2.6.

Although silicon-based WLP provides the benefit of miniaturization, the thermal in-

Table 2.6: Results of the thermal simulation.

| Power of the LEDs           |     | 1 W | 2 W |

|-----------------------------|-----|-----|-----|

| Temperature of conventional | LED | 90  | 130 |

| SSL module (°C)             | IC  | 69  | 69  |

| Temperature of conventional | LED | 76  | 98  |

| SSL module (°C)             | IC  | 68  | 81  |

teraction between LEDs and ICs within SSL modules can be harmful. From the thermal management aspect, setting some thermal separation structure on the path of heat transfer can be effective approach. Figure 2.12 displays one possible design: based on the integrated SSL module, a trench is formed in the silicon substrate between the LEDs and the ICs; the encapsulant (for instance, silicone) fills the trench and acts as a thermal barrier duo to its lower thermal conductivity. Simulation result shows that by adding such thermal barrier the temperature of the ICs is reduced to 62 °C from 68 °C when the power of the LEDs is 1 W. Meanwhile, the temperature of the LEDs is slightly increased (1 °C). The thermal barrier blocks the heat generated by the LEDs from conducting laterally, which helps protect the integrated ICs from thermal damage and meanwhile lowers the efficiency of thermal dissipation of the LEDs. This trade-off needs to be considered especially when high power LED application involves.

Figure 2.12: Silicone filled trench enabled thermal barrier design for integrated SSL module: the trench is formed in the silicon substrate and filled by silicone during encapsulation.

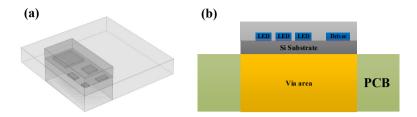

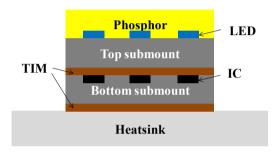

#### 2.2.3. STACKED SILICON SUBMOUNTS

As the integration level and miniaturization increases for applications like SSL, the packaging extends from 2D structure to 3D. Chips, substrates and packages can all be stacked [15]. When substrates are stacked in a SSL package, thermal issue can be more serious. One of the benefits that silicon substrate provides is the high thermal conductivity (130 W/mK) over polymer-based laminates (0.2 W/mK). In this section, thermal analysis is studied between silicon and polymer PCB. TIM, as thermal grease for die attach and substrate stacking, is widely used in SSL packages. The effect of TIM property on the temperature of the package is also investigated in this section.

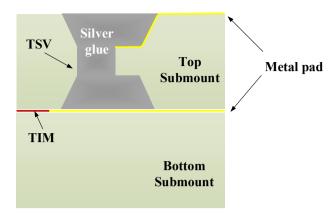

Figure 2.13: Cross-sectional view of integrated SSL module (not to scale): a stack of silicon submount with LEDs integrated on the top and ICs integrated on the bottom.

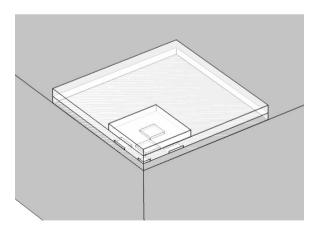

Figure 2.13 shows the structure of the proposed module with stacked silicon submounts. The top submount carries all the LEDs which are encapsulated with a layer of phosphor. The driver circuit components are embedded on the bottom submount. The two submounts are glued with TIM and the whole stack is adhered to a heat sink by the same TIM.

Table 2.7 summarizes the dimension and the material properties. The module contains 36 LEDs which are form into a  $6\times6$  array and the total power is 6 W, of which 5.7 W consumed on the LEDs and 0.3 W on the driver circuit. For the simulation, the luminous efficiency of the LEDs are still set as 70 % and natural convection is set between the outer surface of the module and the ambient air with an initial temperature of  $20^{\circ}$ C.

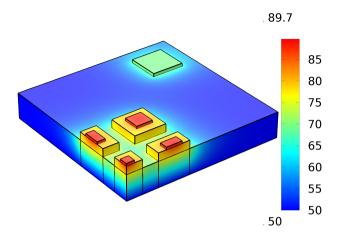

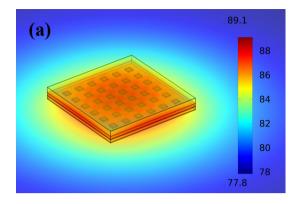

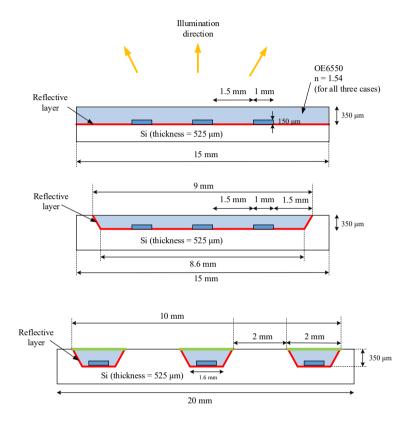

The temperature distribution of the module is simulated with silicon and PCB as submounts, respectively, and the result is shown in Figure 2.14. The thermal conductivity of TIM is set as 5 W/mK. It is evident that silicon submount shows much higher efficiency of heat dissipation. The temperatures of the LEDs and ICs in each case are summarized in Table 2.8. The LEDs and ICs integrated on silicon submounts show much lower tem-

2.2. THERMAL DESIGN 31

| Material               | Thermal conductivity (W/(mK)) [13] | Dimension<br>(mm <sup>2</sup> ) | Thickness (mm) |

|------------------------|------------------------------------|---------------------------------|----------------|

| Phosphor<br>(Silicone) | 0.22                               | 17 × 17                         | 1.0            |

| LED                    | 35                                 | $1 \times 1$                    | 0.2            |

| Silicon                | 130                                | $17 \times 17$                  | 0.5            |

| PCB                    | 0.5                                | $17 \times 17$                  | 0.5            |

| TIM                    | 1 ~ 30                             | $17 \times 17$                  | 0.1            |

| Heatsink               | 50                                 | 100 (diameter)                  | 2.0            |

Table 2.7: Modelling parameters: thermal conductivity and dimension.

perature than those on PCB submount. It is also noted that with silicon as submount, the temperature of the ICs is almost the same as the LEDs while in the case of PCB the LEDs show much higher temperature than the ICs because the heat dissipation from the LEDs through the ICs to the heat sink is blocked by lower thermal conductivity of the PCB.

Table 2.8: Simulation results of modules with different submounts.

|                  | Silicon |    | PCB |     |

|------------------|---------|----|-----|-----|

|                  | LED     | IC | LED | IC  |

| Temperature (°C) | 89      | 88 | 144 | 109 |

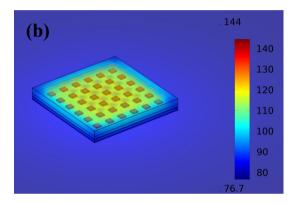

The effect of the TIM property on the module temperature is also investigated. Normally used TIM has a thermal conductivity of 1 ~ 10 W/mK [13]. Some newly developed material is claimed to have higher thermal conductivity over 30 W/mK [16]. For the simulation, the thermal conductivity is tuned between 1 to 30 W/mK, and the resulted maximum temperature of the module is depicted in Figure 2.15. Again, the silicon enabled module shows lower temperature. However, for both cases, the maximum temperature does not show obvious drop with increased thermal conductivity of TIM. This result shows that as long as the TIM layer is thin enough compared with other material layer, it is not the bottleneck on the path of the thermal dissipation. But if too much TIM is applied underneath the LEDs, especially for modules with poorly thermally conductive materials, such as the PCB submount, the situation can be made even worse.

Figure 2.14: Temperature distribution of modules with stacked submounts: (a) silicon submount; (b) PCB submount.

## 2.2.4. CONCLUSION

Silicon has higher thermal conductivity than most of the materials that are normally used as packaging substrate, such as ceramic, polymer-based laminates (PCB), MCPCB, etc. For SSL modules, silicon substrate can greatly ease the thermal issue due to fast spread of heat through silicon both vertically and laterally and help reduce the temperature of the LEDs whose performance and lifetime are highly linked with the temperature. When ICs are integrated with LEDs on the same silicon substrate, silicon cannot stop the heat transfer between the LEDs and the ICs, and in most cases this is not welcomed. If the thermal impact on the ICs is not acceptable, additional thermal barrier structure can be designed to block the heat from the LEDs.

2.3. OPTICAL DESIGN 33

Figure 2.15: The change of LED temperature with different TIMs.

## 2.3. OPTICAL DESIGN

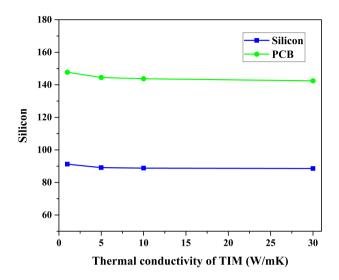

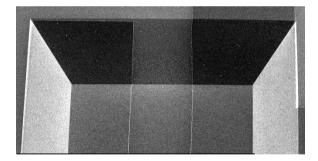

For SSL applications, optical design plays a significant role in the packaging design. To enhance the efficiency of light extraction from the light source, design of optical components, such as light reflector and lens, must be well taken care of. In most of the SSL modules, package plays a role of bridging the light source (LEDs) and the ambient. A properly designed package can make best of the light emitted from the LEDs and enhance the light efficiency of the whole module. Inside a SSL package, the substrate is usually not considered as an optical part, but it does affect the light effect of the package and the module. It is inevitable that the packaging substrate absorbs part of the light so one of the direction that endeavor has been put into is to increase the reflectivity of the substrate material. This can be achieved by modifying the topology of the substrate surface, or by depositing a layer of highly reflective material. In this section, we focus on the evaluation of silicon submount in terms of the light effect. A multi-LED module is selected as the analysis object. Different submount topologies that are evaluated include:

- a. planar surface submount, where all LEDs are mounted on a planar submount,

- b. Single cavity reflector, where all LEDs are mounted in one big cavity, and

- c. Individual cavity reflector, where each LED is mounted inside one cavity of its own.

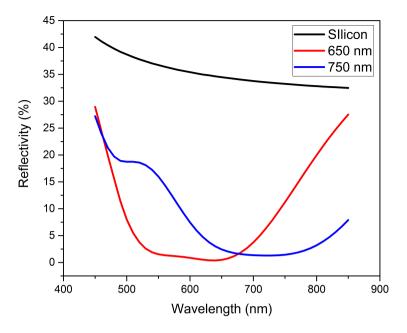

The cross-sectional schematics of the three structures with key dimensions are shown in Figure 2.16. In the range of visible light, silicon has a reflectivity of  $30 \sim 40$  % and the rest is either transmitted or absorbed [17]. To increase the reflection of silicon surface, a thin layer of aluminum is deposited. Among all metals, aluminum has second highest reflectivity, above 95 %, only lower than silver [18].

Figure 2.16: Cross-sectional view of SSL module with different topologies (top to down): planar design, single cavity reflector and individual cavity reflector.

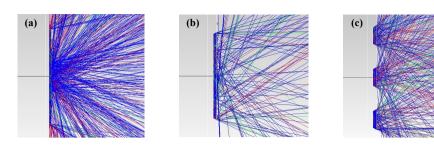

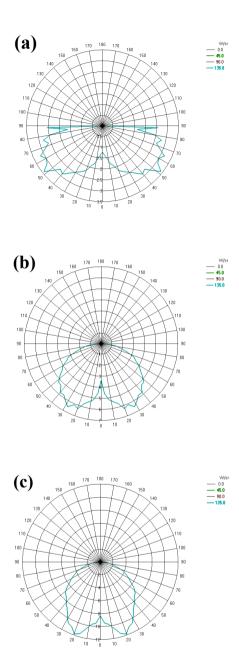

TracePro is used to simulate the light effect of each structure [19]. In each model, nine LEDs are simulated as light source and transparent silicone is molded on top as encapsulation. The wavelength of the LEDs is 650 nm and the total radiant flux is 10 mW. The absorption in the silicone is 3 % and light loss of each reflection is 5 % [20]. The representative ray tracing results are shown in Figure 2.17. More illustratively, the distribution of light intensity for each design is drawn in Figure 2.18.

The light emitting angle is defined as two times of the angle in the light intensity

2

Figure 2.17: Light ray tracing results (side view), (a) planar design, (b) single cavity reflector, and (c) individual cavity reflector.

distribution curve where the light intensity drops to 50 % of the maximum value. From the result shown in Figure 2.18, the light emitting angle is 180°, 135° and 110° for the three structures, respectively. The planar design gives the widest light emitting angle and lowest light efficiency. Because there is no light focusing structure, incident light with big angle of incidence has high chance of being reflected back by the flat surface of silicone. After multiple internal reflection, a big portion of light is either lost or escaped from the edge of the module, none of which contributes to the light extraction. For both structures with cavity reflectors, the light emitting angle is greatly narrowed down, namely, focused. Also, the angled sidewall of the cavities helps the light emitting through the surface of silicone and reduces the internal loss of light. When it comes to light emitting efficiency, the ratio of luminous flux to total radiant flux, as listed in Table 2.9, individual cavity reflector design shows the highest efficiency (74 %), more than twice of the one of the planar design.

Table 2.9: Light emitting efficiency and angle for each design.

| Design                      | Light emitting efficiency (%) | Light emitting angle (°) |

|-----------------------------|-------------------------------|--------------------------|

| Planar design               | 37                            | 180                      |

| Single cavity reflector     | 51                            | 135                      |

| Individual cavity reflector | 74                            | 110                      |

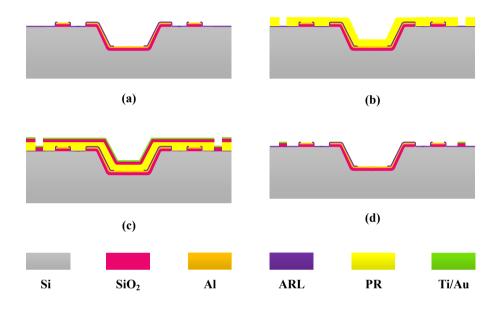

# **2.4.** FABRICATION PROCESS

The stacked silicon submount process mainly consists of two parts: the fabrication of submount and module assembly. The fabrication process can be basically fulfilled by standard silicon microfabrication process. Among all, some processes are intensively

Figure 2.18: Distribution of light intensity: (a) planar design, (b) single cavity reflector, and (c) individual cavity reflector.

used for applications like SSL where multiple heterogeneous chips are integrated based on silicon submount. This section will explain some representative processes which will be implemented into specific application development in later chapters.

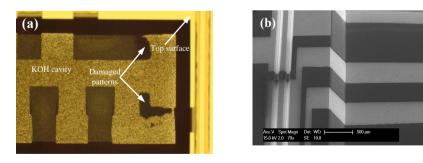

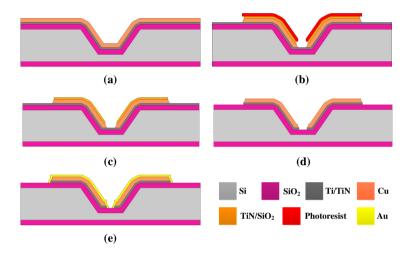

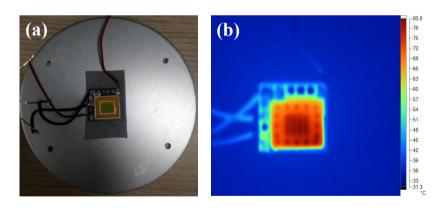

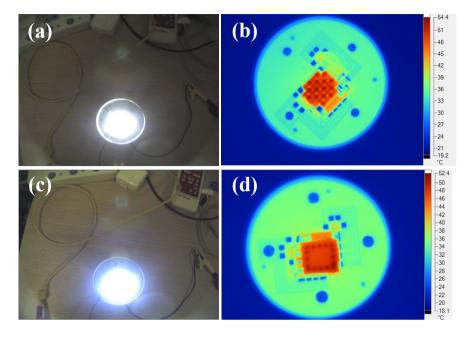

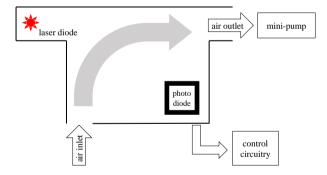

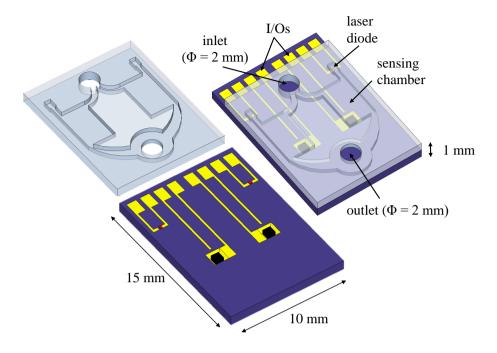

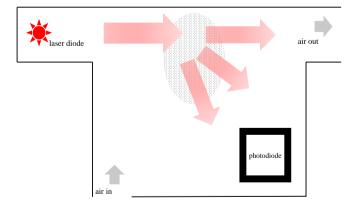

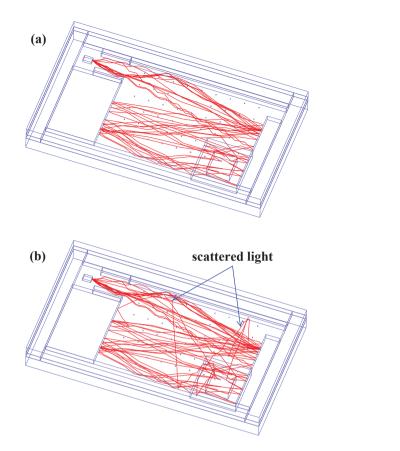

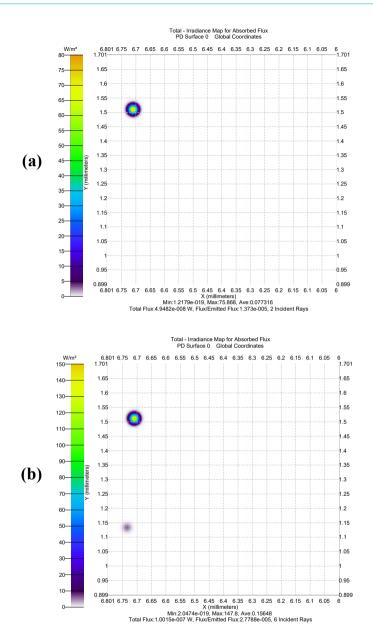

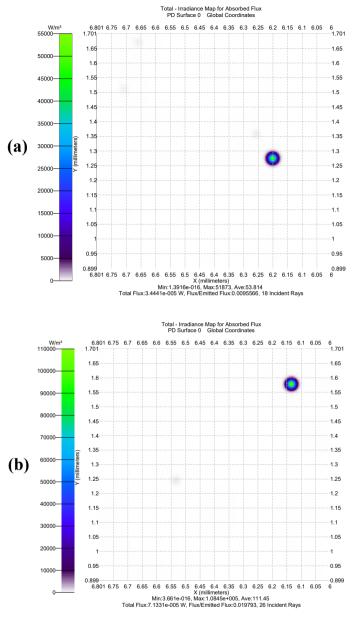

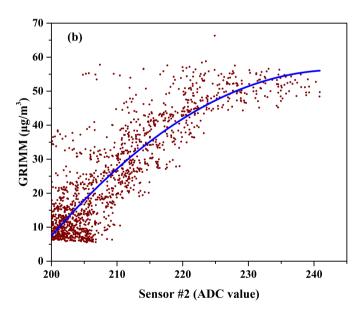

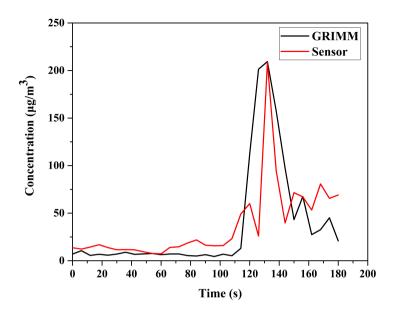

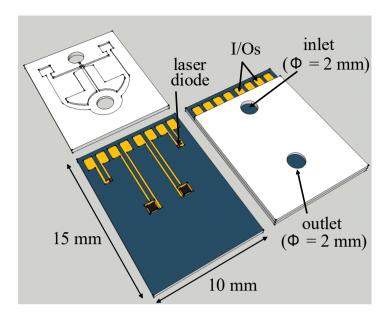

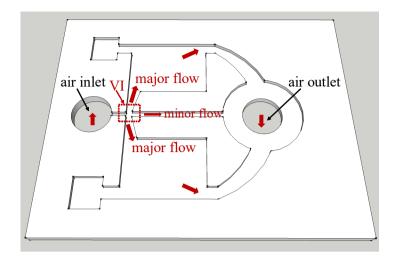

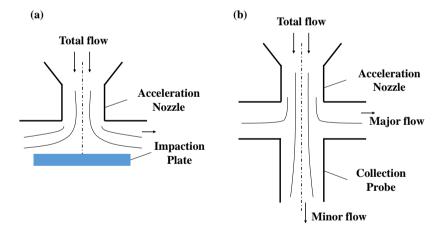

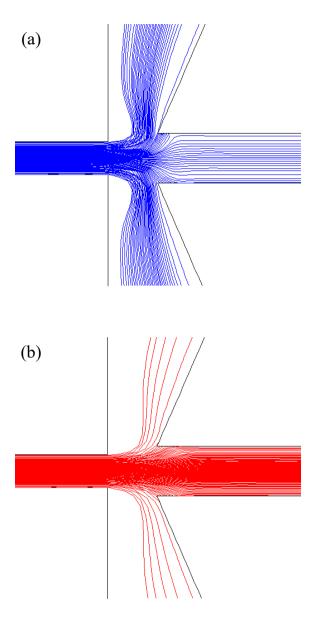

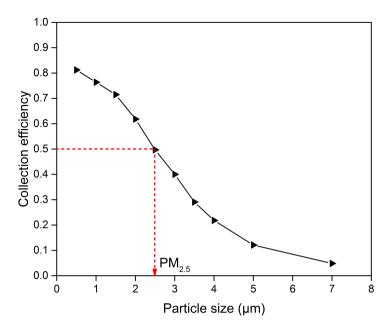

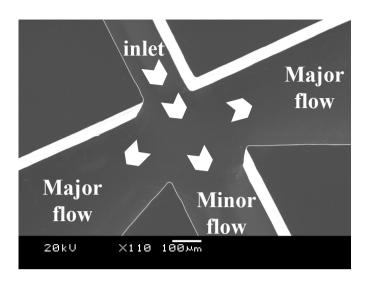

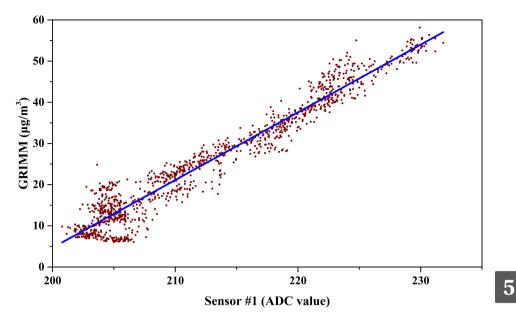

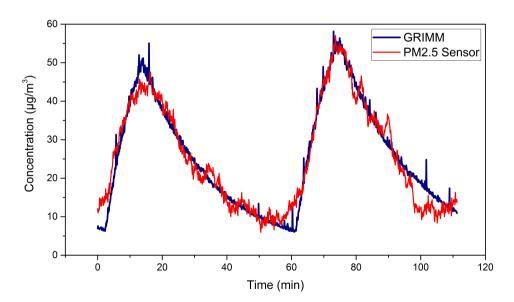

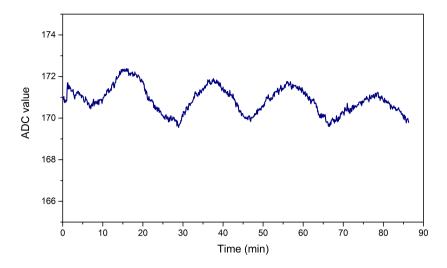

## **2.4.1.** METALLIZATION IN CAVITY