Runtime Support for Heterogeneous Multi-core Systems

Mojtaba Sabeghi

Mojtaba Sabeghi

Runtime Support for Heterogeneous Multi-core Systems

## Runtime Support for Heterogeneous Multi-core Systems

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op maandag 4 april 2011 om 12:30 uur

door

Mojtaba Sabeghi

Master in Computer Engineering Ferdowsi University of Mashhad geboren te Mashhad, Iran Dit proefschrift is goedgekeurd door de promotor: Prof.dr.ir H.J. Sips

Copromotor: Dr. K.L.M. Bertels

Samenstelling promotiecommissie:

| Rector Magnificus, voorzitter      | Technische Universiteit Delft, NL       |

|------------------------------------|-----------------------------------------|

| Prof.dr.ir H.J. Sips, promotor     | Technische Universiteit Delft, NL       |

| Dr. K.L.M. Bertels, copromotor     | Technische Universiteit Delft, NL       |

| Prof. Dr. B.H.H. Juurlink          | Technische Universität Berlin, DE       |

| Prof. Dr. M. Platzner              | Universität Paderborn, DE               |

| Prof. DrIng. M. Berekovic          | Friedrich-Schiller-Universität Jena, DE |

| Prof.dr.ir. P.F.A. Van Mieghem     | Technische Universiteit Delft, NL       |

| Dr. T. Stefanov                    | Universiteit Leiden, NL                 |

| Prof.dr.ir. P.M. Sarro, reservelid | Technische Universiteit Delft, NL       |

|                                    |                                         |

Mojtaba Sabeghi

Runtime Support for Heterogeneous Multi-core Systems

Delft: TU Delft, Faculty of Elektrotechniek, Wiskunde en Informatica - III

PhD Thesis Technische Universiteit Delft.

Met samenvatting in het Nederlands.

ISBN 978-90-72298-15-7

Subject headings: heterogeneous multi-core systems, runtime support, virtualization, reconfigurable systems, scheduling, profiling.

Cover designed by Javad Ghasemi, Babol. All rights reserved. gigantic.ant@gmail.com

Copyright © 2011 Mojtaba Sabeghi

This work is licensed under a Creative Commons Attribution-Noncommercial 3.0 Unported License. To view a copy of the full license, please see: http://creativecommons.org/licenses/by-nc/3.0/legalcode. Copyrights for components of this work owned by others must be honored.

Printed in The Netherlands

To my parents To my wife

# Runtime Support for Heterogeneous Multi-core Systems

Mojtaba Sabeghi

## Abstract

Multi-core processing platforms are one of the major steps forward in offering high-performance computing platforms. The idea is to increase the performance by employing more processing elements to perform a job. However, this creates a challenge for both hardware developers who build such systems and software designers who program those platforms.

On the hardware side, we can mention the problems on the interconnects management, memory hierarchies complexities and cache coherency problem. While on the software side, problems mainly arise in resource management, resource sharing and synchronization. One more fundamental problem on the software side is the inability to program such platforms with the conventional programming models. This is mainly because programming such platforms requires in-depth knowledge of hardware design.

In this dissertation, we address the software side problems by proposing a comprehensive runtime system which is responsible to manage the system resources and resolve all the conflicting issues when accessing computing resources. Furthermore, the runtime system offers the application developers with APIs and system primitives that abstract away the platform dependent details, and provides a consistent programming model. These primitives decouple the process of software development from hardware design and results in the software to be independent of the underlying hardware platform.

The proposed runtime system consists of a scheduler, a profiler, a transformer, a JIT compiler and a kernel library. A detailed description of each component is presented and the performance of the whole system as well as the imposed overhead of the component is discussed.

## Acknowledgements

Over the past years, I have benefited from the help, the inspiration and the encouragement offered by many people. This thesis in its present form would not have been possible without their generous support and I would like to take the chance here to express my appreciation.

First and foremost, I would like to thank my co-promotor, Dr. Koen Bertels for offering me the opportunity to pursue my PhD studies in Delft. He gave me the freedom to work on my own research interest and his support was always there for technical as well as personal problems. I would also like to thank Prof. Stamatis Vassiliadis for trusting my skills and accepting me in his research group. Unfortunately, I did not have the chance to use his help and support during my PhD. I sincerely thank my promotor Prof. Henk Sips for his help at the final stage of my PhD. I would like to extend my gratitude to my PhD examination committee for reading my thesis and giving me invaluable comments. A special thanks goes to Dr. Todor Stefanov and Prof. Ben Juurlink for their detailed comments on my thesis.

To respect those who first introduced me to the world of computer science research, I would like to express my gratitude to my former supervisor at Ferdowsi University of Mashhad, Prof. Mahmoud Naghibzadeh. I would also like to thank Dr. Hossein Deldari, Dr. Mohsen Kahani and Dr. Mohammad Hossein Yaghmaee from whom I learned the basics of the computer science.

The most valuable experiences during my PhD studies are associated with the people I have met in the university. In this spirit, I am very grateful to all the members of CE lab and especially to the members of the Delft Workbench

team. A very special thanks goes to Mr. Hamid Mushtaq with whom I had the chance to collaborate as his MSc advisor. I extend my sincere thanks to Dr. Cor Meenderinck and Mr. Roel Meeuws for helping me to translate the propositions and the abstract of my thesis into Dutch. I would like to especially thank Dr. Tariq Abdullah for reading my thesis and giving me detailed comments to improve my thesis quality. I am also thankful to Mr. Arash Ostadzadeh for proofreading my thesis. Special thanks go to Dr. Behnaz Pourebrahimi, Dr. Mahmood Ahmadi, Mr. Arash Ostadzadeh, Mr. Alireza Asadi and Dr. Mahmood Fazlali for being good friends and supportive whenever I needed them. I would also like to thank Zubair, Vlad, Razvan, Kamana, Yana, Jae, Ozana, Luyi and Thomas. My thanks also go to Lidwina, Monique, Bert, Eric and Eef for the support during these years. I would also like to thank the relatively large Persian community in Delft and other parts of the Netherlands. Meeting so many Iranians made me feel at home and gave me an opportunity to have a great social life in the Netherlands.

I would like to express my deepest thanks to my parents for their unwavering support, encouragement and trust in my abilities. I am really grateful to my sister, Narjes, who was always my main source of inspiration and motivation. I sincerely thank my brothers and sisters for their kindness and support.

Last but not least, I am extremely grateful to my wife for her love, support and understanding over the years. Without her encouragement and support, this thesis would not have been possible.

Mojtaba Sabeghi

Delft, The Netherlands, April 2011

# Table of Contents

| Ab  | stract   |          |                                           | i    |

|-----|----------|----------|-------------------------------------------|------|

| Ac  | know     | edgmen   | nts                                       | iii  |

| Ta  | ble of   | Content  | ls                                        | v    |

| Lis | st of Ta | ables    |                                           | ix   |

| Lis | st of F  | igures . |                                           | xi   |

| Lis | st of A  | lgorithm | ns                                        | xiii |

| Lis | st of A  | cronym   | s and Symbols                             | XV   |

| 1   | Intro    | duction  |                                           | 1    |

|     | 1.1      | Proble   | em Overview                               | 1    |

|     | 1.2      |          | tation Contribution                       | 4    |

|     | 1.3      |          | tation Organization                       | 5    |

| 2   | Back     | ground   | and Related Work                          | 9    |

|     | 2.1      | Target   | Architectures                             | 10   |

|     |          | 2.1.1    | The Xilinx Extensible Processing Platform | 10   |

|     |          | 2.1.2    | Convey HC-1                               | 11   |

|     |          | 2.1.3    | Freescale QorIQ P2 Series                 | 12   |

|     |          | 2.1.4    | STMicroelectronics Platform 2012          | 12   |

|     |          | 2.1.5    | Industrial Reference Platform             | 13   |

|     |          | 2.1.6    | hArtes Platform                           | 13   |

|     |          | 2.1.7    | Novo-G                                    | 14   |

|     | 2.2      | MOLE     | EN Hardware Organization                  | 15   |

|     | 2.3      | MOLE     | EN Programming Paradigm                   | 16   |

|     | 2.4      |          | n Tool Chain                              | 16   |

|     | 2.5      | Runtin   | ne Systems                                | 18   |

| 2.5.2       Pervasive Parallelism         2.5.3       ReconOS         2.5.4       HybridOS         2.5.5       ReconfigME         2.5.6       Warp Processing         2.5.7       UltraSONIC         2.5.8       hthreads         2.5.9       Other Runtime Systems         2.6       Virtualization         2.7       Comparison Methodology         2.8       Open Issues         2.9       Summary         3.1       Introduction         3.2       Sample Real World Applications         3.3.1       Scheduler         3.3.2       Profiler         3.3.3       Transformer | 20<br>21<br>22<br>22<br>23<br>23<br>23<br>23<br>24<br>25<br>26<br>28<br>29<br><b>31</b> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 2.5.4HybridOS2.5.5ReconfigME2.5.6Warp Processing2.5.7UltraSONIC2.5.8hthreads2.5.9Other Runtime Systems2.6Virtualization2.7Comparison Methodology2.8Open Issues2.9Summary3Runtime System3.1Introduction3.2Sample Real World Applications3.3.1Scheduler3.2Profiler                                                                                                                                                                                                                                                                                                                 | 21<br>22<br>22<br>23<br>23<br>23<br>24<br>25<br>26<br>28<br>29<br><b>31</b>             |

| 2.5.5       ReconfigME         2.5.6       Warp Processing         2.5.7       UltraSONIC         2.5.8       hthreads         2.5.9       Other Runtime Systems         2.6       Virtualization         2.7       Comparison Methodology         2.8       Open Issues         2.9       Summary         3.1       Introduction         3.2       Sample Real World Applications         3.3.1       Scheduler         3.3.2       Profiler                                                                                                                                    | 22<br>22<br>23<br>23<br>24<br>25<br>26<br>28<br>29<br>31                                |

| 2.5.5       ReconfigME         2.5.6       Warp Processing         2.5.7       UltraSONIC         2.5.8       hthreads         2.5.9       Other Runtime Systems         2.6       Virtualization         2.7       Comparison Methodology         2.8       Open Issues         2.9       Summary         3.1       Introduction         3.2       Sample Real World Applications         3.3.1       Scheduler         3.3.2       Profiler                                                                                                                                    | 22<br>22<br>23<br>23<br>24<br>25<br>26<br>28<br>29<br>31                                |

| 2.5.7       UltraSONIC         2.5.8       hthreads         2.5.9       Other Runtime Systems         2.6       Virtualization         2.7       Comparison Methodology         2.8       Open Issues         2.9       Summary         3.1       Introduction         3.2       Sample Real World Applications         3.3.1       Scheduler         3.3.2       Profiler                                                                                                                                                                                                       | 23<br>23<br>24<br>25<br>26<br>28<br>29<br>31                                            |

| 2.5.8       hthreads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23<br>24<br>25<br>26<br>28<br>29<br>31                                                  |

| 2.5.9       Other Runtime Systems         2.6       Virtualization         2.7       Comparison Methodology         2.8       Open Issues         2.9       Summary         3.1       Introduction         3.2       Sample Real World Applications         3.3.1       Scheduler         3.3.2       Profiler                                                                                                                                                                                                                                                                   | 24<br>25<br>26<br>28<br>29<br>31                                                        |

| 2.6       Virtualization         2.7       Comparison Methodology         2.8       Open Issues         2.9       Summary         3.1       Introduction         3.2       Sample Real World Applications         3.3       The Proposed Runtime System         3.3.1       Scheduler         3.3.2       Profiler                                                                                                                                                                                                                                                               | 25<br>26<br>28<br>29<br>31                                                              |

| <ul> <li>2.7 Comparison Methodology</li> <li>2.8 Open Issues</li> <li>2.9 Summary</li> <li>3 Runtime System</li> <li>3.1 Introduction</li> <li>3.2 Sample Real World Applications</li> <li>3.3 The Proposed Runtime System</li> <li>3.3.1 Scheduler</li> <li>3.3.2 Profiler</li> </ul>                                                                                                                                                                                                                                                                                           | 26<br>28<br>29<br>31                                                                    |

| 2.8       Open Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28<br>29<br>31                                                                          |

| 2.9       Summary         3       Runtime System         3.1       Introduction         3.2       Sample Real World Applications         3.3       The Proposed Runtime System         3.3.1       Scheduler         3.3.2       Profiler                                                                                                                                                                                                                                                                                                                                        | 29<br>31                                                                                |

| <ul> <li>3 Runtime System</li> <li>3.1 Introduction</li> <li>3.2 Sample Real World Applications</li> <li>3.3 The Proposed Runtime System</li> <li>3.3.1 Scheduler</li> <li>3.3.2 Profiler</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             | 31                                                                                      |

| <ul> <li>3.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |

| <ul> <li>3.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |

| <ul> <li>3.2 Sample Real World Applications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 32                                                                                    |

| 3.3       The Proposed Runtime System         3.3.1       Scheduler         3.3.2       Profiler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                                                       |

| 3.3.1       Scheduler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

| 3.3.2 Profiler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |

| 3.3.4 Kernel Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| 3.3.5 JIT Compiler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                         |

| 3.4 Interfacing Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |

| 3.5 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                         |

| 4 Task Abstraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 47                                                                                      |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |

| 4.1.1 MOLEN Programming Paradigm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |

| 4.1.2 The Runtime Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

| 4.2 MOLEN Runtime Primitives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |

| 4.2.1 SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

| 4.2.2 EXECUTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

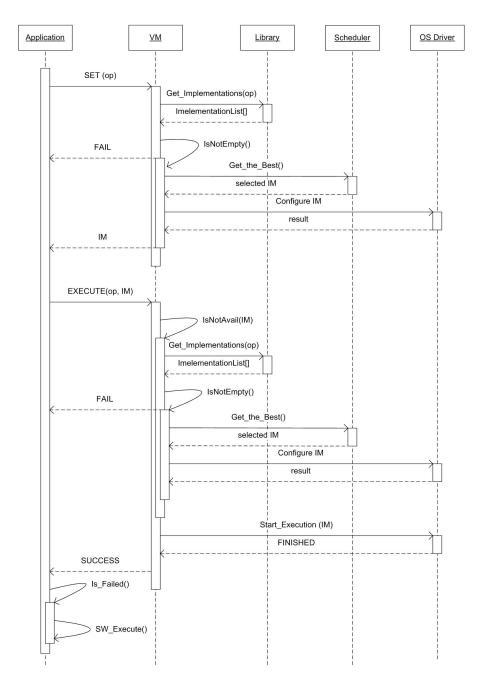

| 4.2.3 Dynamic Binding Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| 4.3 Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                         |

| 4.3.1 Overhead in a Single Call                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |

| 4.3.2 Overall Overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                         |

| 4.4 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ~-                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 63                                                                                      |

|     | 5.3     | Runtime Scheduling                       |

|-----|---------|------------------------------------------|

|     |         | 5.3.1 The Replacement Policy             |

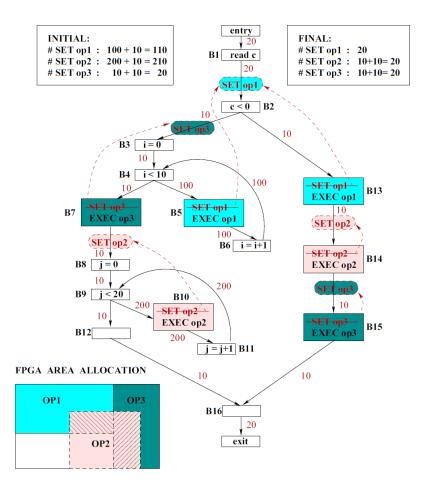

|     |         | 5.3.2 Configuration Call Graph           |

|     | 5.4     | Longest Distance in the Future           |

|     | 5.5     | Least Frequency in the Future            |

|     | 5.6     | Least Frequency in the Past              |

|     | 5.7     | Expected Time Improvement                |

|     | 5.8     | Evaluation                               |

|     |         | 5.8.1 Workload for Evaluation            |

|     |         | 5.8.2 Evaluation Results                 |

|     | 5.9     | Conclusion                               |

| 6   | Fuzz    | y Real-time Scheduling                   |

|     | 6.1     | Introduction                             |

|     | 6.2     | Fuzzy Inference System                   |

|     | 6.3     | The Proposed Fuzzy Model                 |

|     | 6.4     | The Proposed Algorithms                  |

|     | 6.5     | Performance Evaluation                   |

|     | 6.6     | Conclusion                               |

| 7   | Runt    | ime Profiling                            |

|     | 7.1     | Introduction                             |

|     | 7.2     | Design Choices                           |

|     | 7.3     | Design And Implementation 110            |

|     | 7.4     | Performance Evaluation                   |

|     |         | 7.4.1 Instrumentation Overhead           |

|     |         | 7.4.2 Sampling and Daemon Overhead       |

|     |         | 7.4.3 Sampling Accuracy                  |

|     |         | 7.4.4 Overall Overhead                   |

|     |         | 7.4.5 Percentage of Profilable Functions |

|     | 7.5     | Conclusion                               |

| 8   | Cond    | lusions                                  |

|     | 8.1     | Outlook                                  |

|     | 8.2     | Contributions                            |

|     | 8.3     | Open Issues and Future Directions        |

| Bił | oliogra | phy                                      |

| Lis | t of P  | ublications                              |

|     |         | tting                                    |

|     |         | e Author                                 |

|     |         | C 80000 14/                              |

# List of Tables

| 4.1                                               | Workload Kernels                                                                                                                                   | 0           |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 4.2                                               | Overall Execution Time                                                                                                                             | 51          |

|                                                   |                                                                                                                                                    |             |

| 5.1                                               | Kernel Specifications (ms)                                                                                                                         | 2           |

| 5.2                                               | Workload Set-ups                                                                                                                                   | 3           |

| 5.3                                               | The Tasks Execution Time and Number of Executed Tasks on                                                                                           |             |

|                                                   | RPs in each Set-up 8                                                                                                                               | 4           |

|                                                   |                                                                                                                                                    |             |

| 7.1                                               | Comparison of Different Types of Profilers                                                                                                         | 8           |

| 7.1<br>7.2                                        | Comparison of Different Types of Profilers                                                                                                         |             |

|                                                   |                                                                                                                                                    | 5           |

| 7.2                                               | Instrumentation Overhead (secs)                                                                                                                    | 5<br>5      |

| 7.2<br>7.3                                        | Instrumentation Overhead (secs)                                                                                                                    | 5<br>5<br>6 |

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> </ol> | Instrumentation Overhead (secs)       11         Sampling and Daemon Overhead       11         Sampling Accuracy of the Proposed Profiler       11 | 5<br>6<br>7 |

# List of Figures

| 2.1 | Extensible Processing Platforms                    | 10 |

|-----|----------------------------------------------------|----|

| 2.2 | Convey HC-1                                        | 11 |

| 2.3 | Freescale QorIQ P2 Series                          | 12 |

| 2.4 | Industrial Reference Platform                      | 13 |

| 2.5 | The hArtes Platform                                | 14 |

| 2.6 | MOLEN Hardware Organization                        | 15 |

| 2.7 | Design Tool Chain                                  | 17 |

| 2.8 | Pervasive Parallelism                              | 20 |

| 2.9 | ReconOS System Architecture                        | 21 |

| 3.1 | The Runtime Environment                            | 36 |

| 3.2 | Runtime System Layers                              | 37 |

| 3.3 | The Components Interaction                         | 41 |

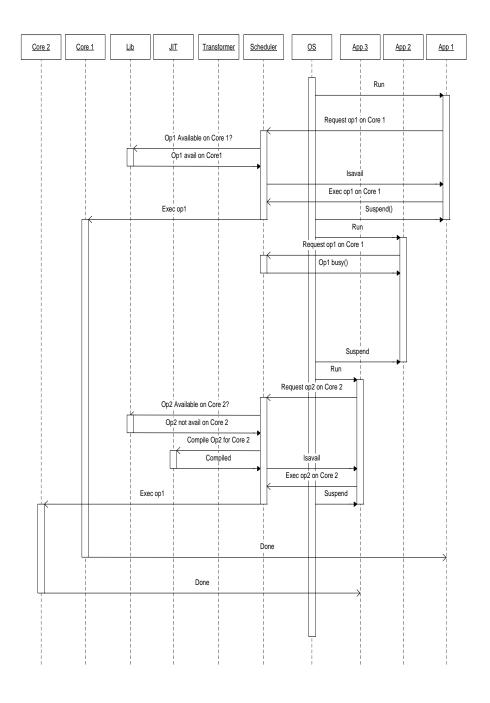

| 3.4 | Sequence Diagram of the First Case Study           | 43 |

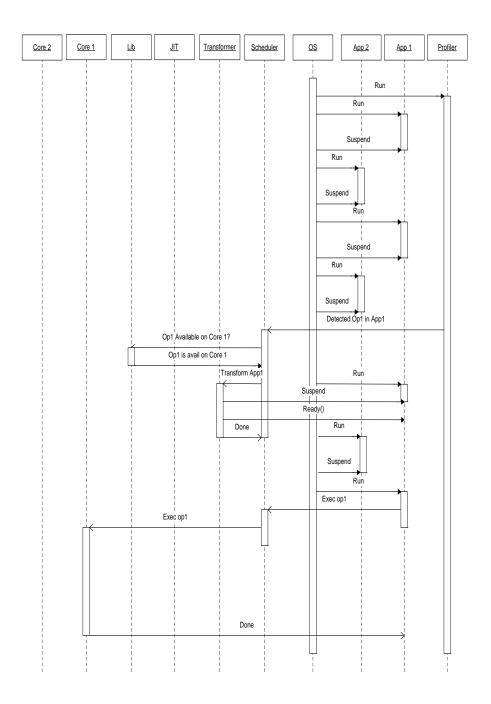

| 3.5 | Sequence Diagram of the Second Case Study          | 44 |

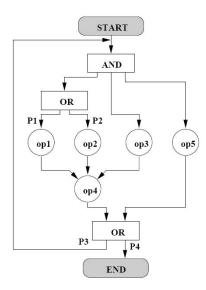

| 4.1 | The Operation Execution Process                    | 53 |

| 5.1 | Compiler Instruction Scheduling                    | 66 |

| 5.2 | A Sample CCG                                       | 70 |

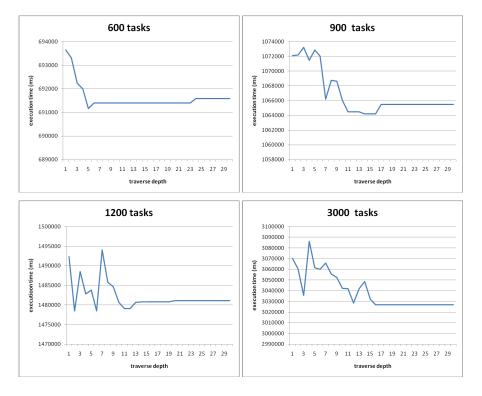

| 5.3 | Execution Time Reduces when Travel Depth Increases | 74 |

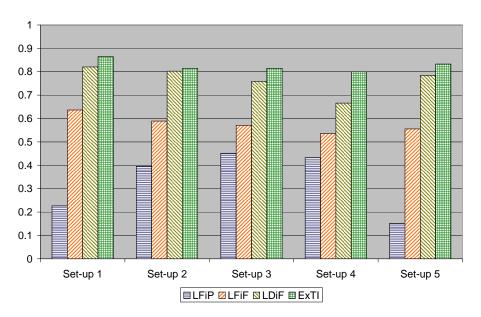

| 5.4 | Percentage of the Tasks Executed on RPs            | 86 |

| 5.5 | The Obtained Speedup                               | 86 |

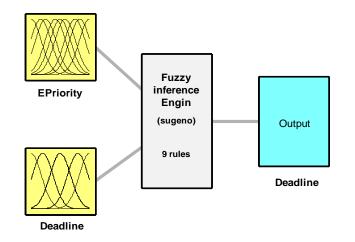

| 6.1 | Inference System Block Diagram                                   | 96  |

|-----|------------------------------------------------------------------|-----|

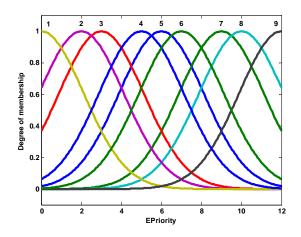

| 6.2 | Fuzzy Sets Corresponding to the External Priority                | 97  |

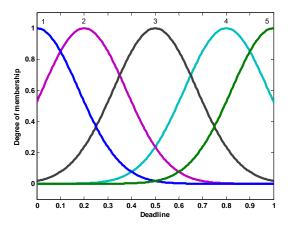

| 6.3 | Fuzzy Sets Corresponding to Deadline                             | 98  |

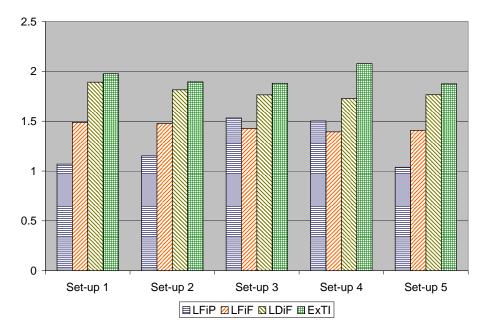

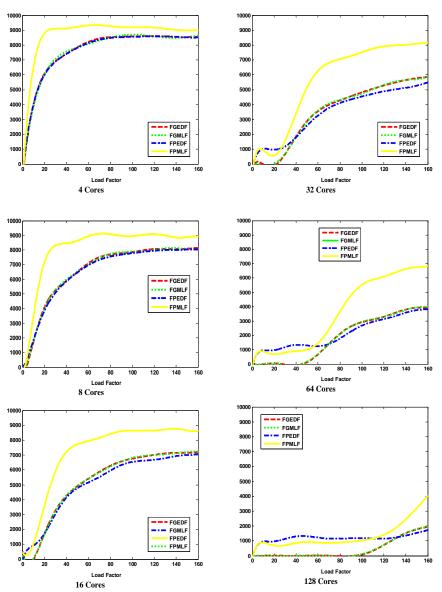

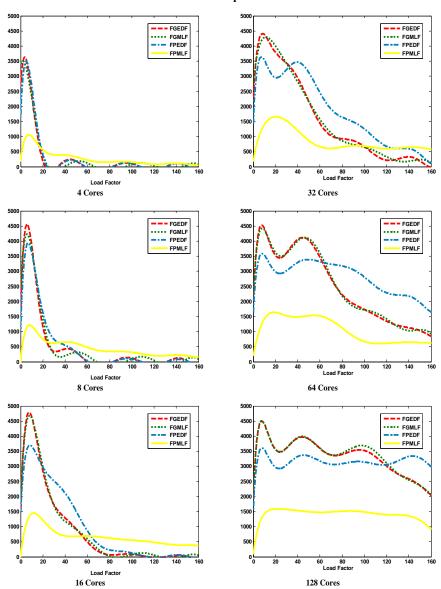

| 6.4 | Number of Misses                                                 | 101 |

| 6.5 | Number of Preemptions                                            | 102 |

| 7.1 | Interaction of Different Parts of the Proposed Profiler with the |     |

|     | Profiled Application and the Scheduler                           | 111 |

| 7.2 | Contents of the Profiler Frame                                   | 112 |

# List of Algorithms

| 4.1 | The SET API                                          | 54 |

|-----|------------------------------------------------------|----|

| 4.2 | The EXECUTE API                                      | 55 |

| 5.1 | Distance to the Next Call in a Single CCG            | 71 |

| 5.2 | Frequency of Calls from Current Node in a Single CCG | 71 |

| 5.3 | LDiF Scheduling Algorithm                            | 76 |

| 5.4 | LFiF Scheduling Algorithm                            | 78 |

| 5.5 | LFiP Scheduling Algorithm                            | 79 |

| 5.6 | ExTI Scheduling Algorithm                            | 80 |

| 6.1 | FGEDF Algorithm                                      | 99 |

| 6.2 | FPEDF Algorithm                                      | 99 |

|     |                                                      |    |

# List of Acronyms and Symbols

| API   | Application Programming Interface |

|-------|-----------------------------------|

| CCG   | Configuration Call Graph          |

| DSO   | Dynamic Shared Object             |

| DSP   | Digital Signal Processor          |

| EDF   | Earliest Deadline First           |

| ExTI  | Expected Time Improvement         |

| FIS   | Fuzzy Inference Systems           |

| FGEDF | Fuzzy Global EDF                  |

| FGMLF | Fuzzy Global MLF                  |

| FPEDF | Fuzzy Partitioned EDF             |

| FPMLF | Fuzzy Partitioned MLF             |

| FPGA  | Field-Programmable Gate Array     |

| GOT   | Global Object Table               |

| GPP   | General-Purpose Processor         |

| HW    | Hardware                          |

| ISA   | Instruction Set Architecture      |

| JIT   | Just in Time                      |

| LDiF  | Longest Distance in the Future    |

| LFiF  | Least Frequency in the Future     |

| LFiP  | Least Frequency in the Past       |

| MAL   | MOLEN Abstraction Layer           |

| MLF   | Minimum Laxity First              |

| OS    | Operating System                  |

| PIC   | Position Independent Code         |

| RM    | Rate Monotonic                    |

| RP    | Reconfigurable Processor          |

| SW    | Software                          |

| VM    | Virtual Machine                   |

| XREG  | Exchange Register                 |

|       |                                   |

## Introduction

1

In this dissertation, we propose a comprehensive runtime system that is integrated in heterogeneous multi-core systems to resolve all the conflicting issues between the applications running on them. Furthermore, this runtime system provides application developers with APIs and system primitives that abstract away platform-dependent details to offer a consistent programming model. It decouples the process of software development from hardware design and results in the software to be independent of the underlying hardware platform.

The runtime system consists of a scheduler, a profiler, a transformer, a JIT compiler and a kernel library. The detailed description of each component is presented and the performance of the whole system as well as the imposed overhead by each component is discussed.

#### **1.1 Problem Overview**

Employing multiple processing elements on a single chip is now becoming a trend in a wide range of computing platforms. These processing units can be homogeneous or heterogeneous. It has been proved [1,2] that this approach has several benefits such as lowering the power consumption and improving the performance.

It also seems to be a viable solution to keep the Moore's law alive for a couple of more years. The reason lies in the fact that increasing transistor densities with high clock rates demands more power and as a consequent generates more heat, which limits how fast the processor clock can go. As a result, manufacturers try to increase the performance of computing systems by increasing number of execution units on a single chip while keeping the clock fixed or even reducing the clock frequency.

However, hosting multiple cores on a single chip instead of one core creates some complexities at the hardware and the software design parts. On the hardware side, we can mention problems with the interconnects, memory hierarchies and cache coherency. While on the software side, problems mainly arise in resource management, resource sharing and synchronization. These problems are even worse when incorporating multiple heterogeneous cores. In fact, these problems are forming a new fundamental issue which can be named as *programmability wall*. This is due to the fact that programming these platforms with all the mentioned problems is really a difficult task and requires in-depth knowledge of the underlying software and hardware.

There are two main issues on the software side. First, how to divide a program into several parts so that each part can be executed on a separate core. Second, how to allocate these parts to different cores.

Even after solving these two issues, other problems may arise when multiple applications are to be executed on the same platform. In such a scenario, many competitions may exist between the applications. Therefore, the limited system resources have to be shared in a fair and transparent manner between the applications. It should be noted that most of these conflicts are only known at runtime, which means that a design time resource manager can not deal with these problems.

In our work, we target general purpose heterogeneous multi-core systems. This is in line with the technology movements towards employing heterogeneous processing elements in general purpose machines. In such systems, serving multiple applications which are running concurrently on the same machine is an obvious requirement. To address this requirement, a runtime environment is needed which is responsible to fully operate the system and address all the conflicting issues between competing applications. Furthermore, the runtime system has to offer the programmers with APIs and system primitives which abstract away the platform dependent details and provides a consistent programming model.

The proposed runtime system consists of a scheduler, a profiler, a transformer, a JIT compiler and a kernel library. The scheduler has to decide when and where a specific task has to be executed. It has to deal with conflicting objective such as performance, power consumption or cost. In our work, the scheduler, does not change the order of the tasks execution within an application. It only decides about the mapping. The runtime profiler analyses the code and stores statistics about computational intensity and number of referrals as well as the memory bandwidth being used of different parts of the code, the purpose of which is to allow the runtime system to identify compute intensive parts, which if implemented in hardware minimize the execution time of the running applications. The transformer has to modify the binary by augmenting the calls to the software version of the task with calls to the hardware implementation in a specific core. Furthermore, the transformer has to safely resolve and transfer the parameters required by the hardware implementation to a part of memory which can be easily accessed by that core. After the results have been calculated, the appropriate return values have to be safely sent back to the calling thread. The JIT compiler is actually a binary to binary compiler and is responsible to generate the binary for the target core from the available binary. Of course as the JIT process might be costly and time consuming, we can use the help of a library in which we keep the binaries of the tasks for different cores in order to avoid JIT compilation.

It should be mentioned, that our system serves multiple applications. Each application is composed of several tasks. Each task can be mapped to a certain core, or it can be executed on the general purpose processor. A certain task might be used in more than one application. To simplify the design and to be in line with the MOLEN programming paradigm, we assume that a task is in the

form of a function in the program code. Therefore, each function in the code is a task unless it is a very small function.

#### **1.2** Dissertation Contribution

The main task of the runtime system is to decide where, when and how an application or its constituent parts (i.e. tasks) should be executed. Therefore, the runtime system has to first analyse the code and extract information about the program execution. The program execution information includes among other things the computation intensity and frequency of each part of the code. Then, the runtime system has to decide which part of the code has to be executed on which core to achieve the required performance.

As the platform may host heterogeneous processing elements, each core might have a different binary standard and, therefore, the runtime system should be able to submit the workload for each core based on the core's binary standard. Considering the runtime decision making on the core allocation, this implementation binding is not known until runtime. Therefore, programmers need to express operations without knowing the actual implementation. In other words, the runtime system has to abstract away a task call from its actual implementation.

Based on the aforementioned criteria, the main contributions of this thesis can be summarized as follows:

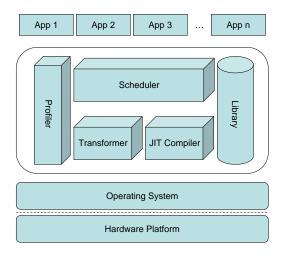

- We introduce a comprehensive runtime system together with a detailed discussion of its components and performance evaluation. We provide a detailed overview of the system layers and show how each layer interacts with the others. The most important layer is the virtualization layer which consists of a scheduler, a profiler, a JIT compiler, a transformer and a kernel library.

- 2. We define and implement a new task abstraction mechanism which extends the MOLEN programming paradigm. Using this mechanism, the

task implementation is separated from the task call. We extend the model in such a way that it is suitable for multitasking scenarios.

- 3. We present a detailed discussion of the scheduling requirements for heterogeneous multi-core systems and present some scheduling policies together with their performance evaluation. We introduce a number of new scheduling algorithms. Our scheduling decision making is based on the *distance in the future* and *frequency in the future* as well as *expected speedup*. We also introduce the configuration call graph as a viable source of information for the scheduler.

- 4. We employ fuzzy logic in the decision making process of the scheduler for the systems with real-time constraints. We model the inputs of the scheduler such as laxity and deadline as fuzzy variables and use a Sugeno inference engine [3] to derive the scheduling priorities.

- 5. We present a novel runtime profiler whose task is to analyse the running code and produce statistics about code execution such as the computation intensity and frequency of the execution. This profiler has to run concurrently with other applications on the end user's machine. Therefore, it needs to have a low overhead. Our runtime profiler has an overhead of less than 1.5%.

#### **1.3 Dissertation Organization**

This dissertation is organized as follows. Chapter 2 gives an overview on the background information and the related work. This chapter starts by giving a few examples of the target architectures. Next, we give a short summary of the MOLEN and the MOLEN programming paradigm as well as the MOLEN design tool chain. Then, we briefly describe some of the similar approaches toward runtime support for heterogeneous multi-core systems, which is followed by a section that motivates the need for virtualization. Afterwards, we present our comparison methodology in the thesis. At the end, we point out the open

issues and discuss our approach towards solving those issues.

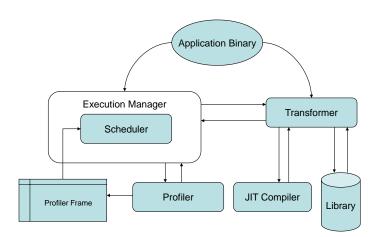

Chapter 3 presents our runtime system. In this chapter, we explain how the whole system is structured into layers. The system is divided into four layers; the application layer, virtualization layer, operating system layer, and hardware platform layer. The hardware platform layer is further divided into the MOLEN abstraction layer and the physical hardware layer. Furthermore, we explain the forming components of the runtime system. These components are the scheduler, the profiler, the transformer, the kernel Library, and the JIT compiler which are briefly discussed. Then, we explain the interaction mechanisms between different components. We also include two case study scenarios and show how the runtime system should react in those scenarios.

Chapter 4 explains how the MOLEN programming paradigm is extended to support multitasking and multi-application scenarios. Accomplish this, we use the same idea of MOLEN set and execute instructions to abstract the concept of a task. In this way, we decouple the task call from the task implementation. We also propose a binding mechanism to bind a task implementation to each task call. This is done by introducing the high level SET and EXECUTE APIs. At the end, we show the overhead of the proposed APIs using some experiments.

Chapter 5 presents our scheduler as a part of the runtime system. In this chapter, we show how we use a combination of design time and runtime scheduling in order to optimize the system performance. In the design time, we use the compiler to perform static task scheduling assuming single thread of execution. Then at runtime, the runtime scheduler performs the actual task scheduling having the scheduling decisions from the compiler as a hint. The runtime scheduler can also use the information provided by the runtime profiler. It can also use the information transferred from design time in the form of a Configuration Call Graph (CCG). Then, we present a number of scheduling policies as case studies and provide performance evaluations. We base our scheduling decisions on three different parameters. We show that *Expected Time Improvement* and *Longest Distance in the Future* are very good heuristics for the scheduling.

Chapter 6 focuses on the conditions in which we have real-time constraints. We use fuzzy logic to model the real-time constrains and to improve the scheduling decisions. Using deadline as a fuzzy parameter in real-time scheduling is more promising than laxity.

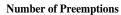

Chapter 7 describes the design and implementation of our runtime profiler, which can be used as a part of the runtime environment. The profiler is a combination of a sampling profiler and an instrumentation profiler. We discuss different parts of the profiler namely the *extractor*, *injector*, *sampler*, *profiler frame* and *daemon*. Then, we show the overhead of our profiler from different aspects. This is done by showing the overhead on instrumentation, sampling and the overall overhead. Besides, we compare the accuracy of our profiler with a popular design time profiler , *gprof*. All the presented results show that our profiler has very low overhead (less than 1.5%) and is as accurate as design time profilers.

Chapter 8 summarizes and concludes this dissertation. It gives a summary of this thesis, its contributions and findings. It then describes the remaining open issues and future research directions.

\_\_\_\_\_

# 2

## Background and Related Work

The increasing demand for high-performance computing platforms was always the main driving force for new advancements during the past years of development in computing technologies. This is valid in all the areas from high-end customized special-purpose computing in networking, telecommunications, and avionics to low-power embedded computing in desktop computing, portable computing, and video games.

Multi-core processing platforms are one of the major steps forward in offering high-performance computing platforms. The idea is to increase the performance by employing more processing elements to perform a job. However, this creates a challenge for both hardware developers who build such systems and software designers who program those platforms.

The basic idea of having a multi-core system is to overcome the major hardware design challenges such as the memory wall problem or the increase in power consumption. Secondly, to increase the performance by using more processing elements to execute a task, which is widely believed to be more efficient. These processing elements can be either homogeneous or heterogeneous.

In this work, we focus on heterogeneous multi-core platforms in which one or more general-purpose processors are the main processing elements and some special purpose processors work as coprocessors. Systems employing

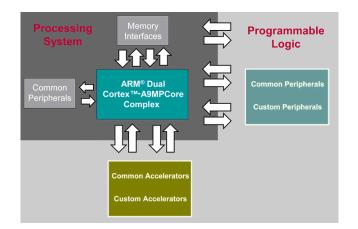

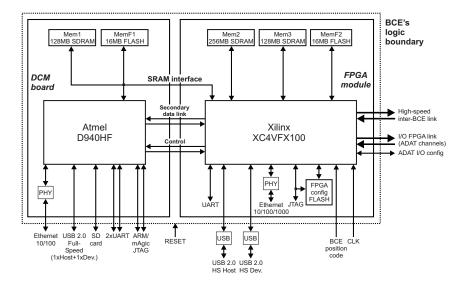

Figure 2.1: Extensible Processing Platforms

reconfigurable processors are our main concern. To clarify the scope and extent of our work, we give a brief introduction of some examples of the industrial target architectures in the following section.

#### 2.1 Target Architectures

Our target architecture is *heterogeneous multi-core platforms*. Such platforms consist of one or more general-purpose processors and some coprocessors. There are several industrial examples of such systems. In the following sections, we give a short introduction on the Xilinx Extensible Processing Platform, Convey HC-1, Freescale QorIQ P2 Series, STMicroelectronics Platform 2012, hArtes, and Novo-G platforms.

#### 2.1.1 The Xilinx Extensible Processing Platform

The Xilinx Extensible Processing Platform [4] offers a processor-centric design and development approach for achieving the processing power required to execute tasks involving high-performance processing and complex digital signal processing needed to meet their application-specific requirements, including

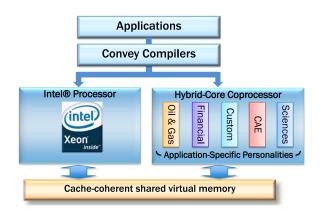

Figure 2.2: Convey HC-1

lower cost and power. It is an implementation of ARM's high-performance dualcore Cortex-A9MPCore processors and Xilinx advanced 28nm programmable logic. Figure 2.1 shows the block diagram of the Extensible processing platforms.

#### 2.1.2 Convey HC-1

The Convey HC-1 [5] is a heterogeneous computing system based on an industry-standard Intel processor and a proprietary coprocessor that share virtual memory and an instruction stream, creating a hybrid-core computing system. The coprocessor architecture supports user-defined, dynamically loadable instruction sets.

It combines the x86 family processors with hardware-based, application-specific instructions to accelerate HPC applications. The result is a tightly integrated system that gives many times the performance of a commodity server on key applications in oil and gas, financial analytics, bioinformatics, and other markets. Figure 2.2 depicts an overview of such a platform.

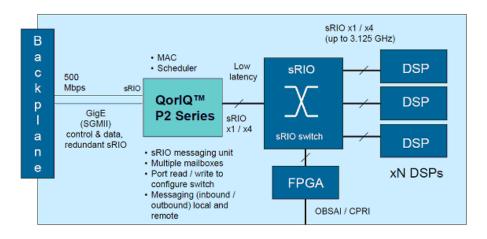

Figure 2.3: Freescale QorIQ P2 Series

#### 2.1.3 Freescale QorIQ P2 Series

The QorIQ P2 communications platform series [6] includes the P2020 and P2010 communications processors. It delivers high single-threaded performance per watt for a wide variety of applications in networking, telecom, military and industrial markets. The P2 series delivers dual- and single-core frequencies up to 1.2 GHz on a 45nm technology low-power platform. Figure 2.3 shows the block diagram of the P2 Series.

#### 2.1.4 STMicroelectronics Platform 2012

The P2012 provides flexibility through massive programmable and scalable architectures by enabling connection of a large number of decoupled STxP70 processors. The Platform 2012 computing fabric is composed of a variable number of "tiles" that can be easily replicated to provide scalability. Each tile includes a computing cluster with its memory hierarchy and a communication engine. The computing fabric operation is coordinated by a fabric controller and is connected to the SoC host subsystem through a dedicated bridge, having DMA capabilities. The P2012 computing fabric is connected to a host processor such as the ARM Cortex A9 via a system bridge.

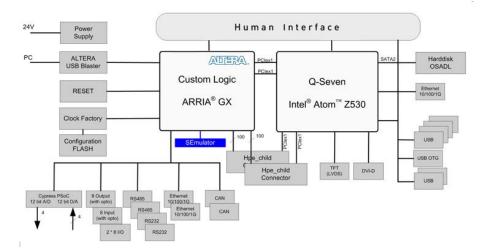

Figure 2.4: Industrial Reference Platform

#### 2.1.5 Industrial Reference Platform

The heart of the Industrial Reference Platform, as shown in Figure 2.4, is an Intel Atom processor and an ALTERA ARRIA FPGA, connected together PCI Express to support customer specific interface and logic requirements. The Industrial Reference Platform is a highly scalable and reconfigurable platform targeted at low power, high-performance industrial automation applications.

The flexibility of the Industrial Reference Platform also makes this system a potential platform for military, automotive, and consumer applications requiring the scalable processor performance of the Intel Atom and the reprogrammability of Altera Arria series FPGAs.

#### 2.1.6 hArtes Platform

The hArtes Platform [7], presented in Figure 2.5, provides a number of heterogeneous computing sub-systems, such as DSPs, general-purpose processors and reconfigurable elements. The system is composed of a certain number of independent blocks. Each block includes a general-purpose RISC proces-

Figure 2.5: The hArtes Platform

sor, a DSP processor, and an application-specific reconfigurable block. The application-specific reconfigurable block also incorporates a RISC processor. Each block is called Basic Configurable Element (BCE).

All the BCEs share the same structure and are able to run any selected thread of a large application.

# 2.1.7 Novo-G

With the promise of the reconfigurable computing in offering capability of one PetaOPS at 10K Watts, it is feasible to consider large scale reconfigurable supercomputing. Novo-G [8] is such a platform, which is used in Bioinformatics and other scientific and engineering domains. Novo-G currently features 192 Stratix-III E260 FPGAs in 48 quad-FPGA boards (plus one spare) with 1TB of memory. Most of the memory is directly attached to the FPGAs (4.25GB per FPGA) and is supported by 20 Gb/s InfiniBand, quad-core Xeons, GigE, PCIe, storage, etc.

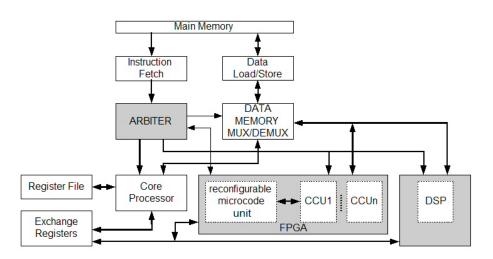

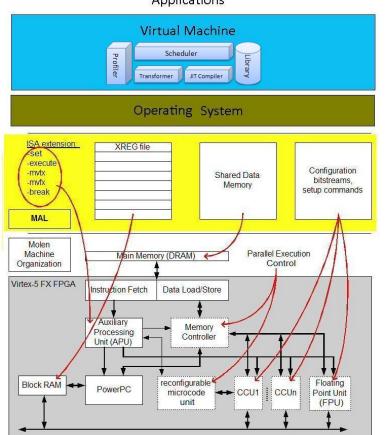

Figure 2.6: MOLEN Hardware Organization

# 2.2 MOLEN Hardware Organization

In the last section, we briefly introduced some of the hardware platforms that can be considered as target architecture for our work. One of the main issues in using those systems is the model of coupling and interaction among all the different processing elements as well as the memory and IO modules.

The MOLEN hardware organization is such a coupling and interaction model. MOLEN is established based on the tightly coupled co-processor architectural paradigm. Within the MOLEN concept, a general-purpose processor is assumed as the main processor, which controls all the coprocessors. Traditionally, MOLEN is designed for reconfigurable computers, however, without the loss of generality, all the MOLEN concepts can be employed effectively and efficiently in the domain of the heterogeneous multi-core systems.

In the context of reconfigurable systems, the general-purpose core processor controls the execution and reconfiguration of the reconfigurable coprocessors and tunes the latter to various application specific algorithms. Figure 2.6 represents the MOLEN machine organization for the reconfigurable systems.

In order to program MOLEN based platforms, the MOLEN programing

paradigm was introduced. We briefly describe the MOLEN programming paradigm in the next section.

# 2.3 MOLEN Programming Paradigm

The MOLEN programming paradigm presents a programming model for reconfigurable computing that allows modularity, general function like code execution and parallelism in a sequential consistency computational model. Furthermore, it defines a minimal ISA extension to support the programming paradigm. Such an extension allows the mapping of an arbitrary function on the reconfigurable hardware with no additional instruction requirements.

This is done by the introduction of new super instructions for operating the FPGA from the software. An operation, executed by the RP, is divided into two distinct phases: set and execute. In the set phase, the RP is configured to perform the required task and in the execute phase the actual execution of the task is performed. This decoupling allows the set phase to be scheduled well ahead of the execute phase, thereby hiding the reconfiguration latency. This phasing introduces two super instructions; *set* and *execute*.

Within the heterogeneous multi-core systems domain, the same super instruction can be used to manage the process of assigning a task to a special core and to control the task's execution on that core.

To facilitate the process of program development, a design tool chain is required. In the next section we present the design tool chain which is proposed for the MOLEN based platforms.

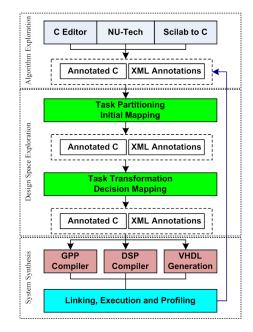

# 2.4 Design Tool Chain

The design tool chain, as shown in Figure 2.7, addresses the difficulty in programming heterogeneous multi-core platforms by assuming a single application execution scenario. It provides a semi-automatic support for the hardware/soft-

Figure 2.7: Design Tool Chain

ware co-design of such systems. The design starts with an application written in C and the final outcome is an executable with (modified) code mapped onto a multi-core platform consisting of a general-purpose processor, a DSP and an FPGA.

The tool chain embeds configuration bit streams for the reconfigurable components of the system. Thus providing a complete and operational system supported both at the software and at the hardware levels. In this way, the tool chain allows the developers to write applications for heterogeneous systems without requiring them to have intimate knowledge of the underlying hardware and its programming. The parallelism and mapping are specified in the code by using *pragmas* in the C code. These annotations can either be added manually by the developers or generated by tools. To specify parallelism, standard OpenMP pragma directives are used.

The design tool chain comprises of three toolboxes. Each of them takes a C-code as input and outputs processed files. The processed files are then fed

to the next toolbox. Figure 2.7 shows the interactions among those toolboxes. The top-level toolbox namely the Algorithm Exploration Toolbox is optional. Its purpose is just to generate C code from a Scilab code or from NU-Tech (a graphical software development tool).

Next is the Design Exploration toolbox whose task is to perform task partitioning and mapping. The task partitioning tool, known as Zebu, generates an efficient task graph [9] with the help of static profiling to identify the most efficient paths [10]. Afterwards, it performs transformation on the task graph to take into account the overhead of managing the parallel tasks. Finally, it generates a C Code annotated with pragmas for parallelization and mapping. The mapping tool hArmonic [11] is used to get an optimized mapping solution.

The last tool in the chain is the Synthesis toolbox. It contains a compiler for each processing element. The source for each processing element is compiled separately and then linked together to form a single binary. It uses a modified GCC compiler for the general-purpose processor. That compiler inserts MOLEN instructions to execute a kernel on FPGA. Moreover, Delft Workbench Automated Reconfigurable VHDL Generator (DWARV) [12] is used to perform C to VHDL translation for the FPGA.

# 2.5 **Runtime Systems**

The main problem with the design time tool chains is that they are not aware of the runtime status of the system. For single application scenarios, that is not a serious limitation. However, when moving towards multi-application scenarios in which the load of the system varies from time to time and the load is not known at design time, there should be a runtime system, which is responsible for the mapping decisions. To perform the mapping, the runtime system can use all the information provided by the design tool chain.

Due to the inherent complexity of the task assignment on the multi-core systems and especially on heterogeneous multi-core systems, the proposed runtime system needs to be very comprehensive. Looking at the literature, runtime systems commonly consist of many components which work together in order to operate the system and manage the resources. In this part, we give an overview on the related research on the runtime systems. It should be mentioned that all these runtime systems can be implemented - at least theoretically - on each of the target architectures presented in section 2.1.

#### 2.5.1 BORPH

BORPH [13] handles FPGA resources as if they were CPU's by introducing the concept of hardware process which behaves just like a normal user program except it is a hardware design running on a FPGA. The BORPH kernel provides standard operating system services, such as file system access, to the hardware processes. This allows hardware processes to communicate with the rest of the system easily, and systematically [14]. BORPH is based on the Linux kernel.

BORPH introduces the concept of hardware region. A region can be physically, the entire FPGA in a multi FPGA system, or a partially reconfigurable region within a FPGA. Hardware processes are spawned in those regions.

A user starts a hardware process by executing a BORPH Object File (BOF). When a BOF file is executed, the kernel examines hardware configurations encapsulated in that file. Based on this information, the kernel chooses and configures one or more suitable hardware regions [15].

The hardware and software components of user designs may run as communicating processes within BORPH's runtime environment. The familiar language independent UNIX kernel interface facilitates easy design reuse and rapid application development. A Simulink-based design flow that integrates with BORPH is employed for developing hardware designs,

Figure 2.8: Pervasive Parallelism

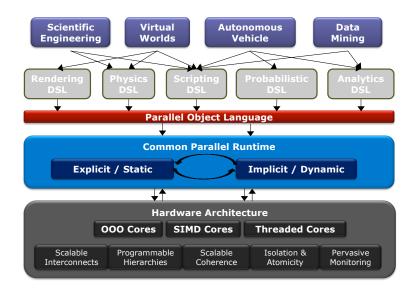

## 2.5.2 Pervasive Parallelism

The goal of the Pervasive Parallelism (PPL) [16] is to make parallelism accessible to the average software developers so that it can be freely used in all computationally demanding applications. PPL tries to extend the Java virtual machine approach by featuring a parallel object language to be executed on a common parallel runtime system. This way it can map Java language onto the respective computing nodes. Figure 2.8 gives an overview of the PPL structure.

#### 2.5.3 ReconOS

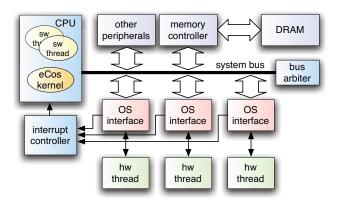

ReconOS [17] aims at the investigation and the development of a programming and execution model for dynamically reconfigurable hardware devices. ReconOS extends the concept of multithreaded programming to the reconfigurable logic [18]. Figure 2.9 shows an overview of the ReconOS architecture.

The described multithreaded design process allows accelerating critical system components through the reconfigurable hardware without sacrificing portability,

Figure 2.9: ReconOS System Architecture

flexibility, and the reusability. ReconOS enables designers to exploit both finegrained data parallelism as well as coarse-grained thread-level parallelism [19].

In the ReconOS execution environment, it is possible to synthesize multiple hardware threads to the same location in the FPGAs reconfigurable fabric. Using partial dynamic reconfiguration, the operating system is able to load hardware threads during runtime. This allows hardware multitasking between different hardware threads [20]

The ReconOS programming model provides the main abstractions for the application design including the definition of hardware tasks and services for task synchronization, communication, and scheduling [21]. Its execution model defines the runtime system which enables multitasking in dynamically reconfigurable hardware as well as across hardware/software boundaries [22].

#### 2.5.4 HybridOS

HybridOS [23] supports fine-grained reconfigurable accelerators integrated with general-purpose computing platforms. HybridOS is based on Linux implemented on the Xilinx XUP Boards.

The granularity of the computation on the FPGA is based on multiple data parallel kernels mapped into accelerators in HybridOS. These are accessed by

multiple threads of execution in an interleaved and space-multiplexed fashion [24].

HybridOS provides interface to the runtime system for applications using a library call approach. In addition, it interfaces the accelerator to plug into hybrid CPU/accelerator model using an accelerator framework.

#### 2.5.5 ReconfigME

ReConfigME is an operating system for reconfigurable computing that handles the loading of the IP cores on the FPGA platform [25]. In addition to runtime resource allocation, other services provided by an operating system such as abstraction of I/O and inter-application communication provide additional benefits to the users of a reconfigurable computer [26, 27].

The ReConfigME implementation is structured into three tiers consisting of user, platform, and operating system. These tiers are connected via a standard TCP/IP network [28]. The users connect to ReConfigME through a custom-built client interface, which enables them to load applications, transfer application data and configuration information, and monitor the reconfigurable computing platform status.

The application architecture in the ReConfigME consists of a data flow graph structure, memory based I/O, EDIF application file format, and the associated software only components.

### 2.5.6 Warp Processing

Warp processing [29] transforms computing intensive kernels running on a general-purpose processor to hardware. The Warp profiler is implemented as hardware and is used to detect kernels at runtime. Within the Warp Processors, a Dynamic CAD tool is used to map kernels to hardware. In addition, a binary updater is used to change the binary of the program running on the general-purpose processors, so that it can uses the FPGA. The Warp Processors can

generate code for the FPGA on the fly by using a Just in Time (JIT) compiler.

The Warp processors targets single application execution. All the optimizations are within one application. However, we target multi-application execution scenarios. Our kernels are more coarse grain that Warp. The Warp is basically focusing on the optimization of the loops and small parts within a single application.

#### 2.5.7 UltraSONIC