# A 13.56MHz Fully Integrated 91.8% Efficiency Single-Stage Dual-Output Regulating Voltage Doubler for Biomedical Wireless Power Transfer

Lu, Tiangi; Chang, Zu Yao; Jiang, Junmin; Makinwa, Kofi; Du, Sijun

DOI

10.1109/CICC57935.2023.10121186

**Publication date**

**Document Version** Final published version

Published in

Proceedings of the 2023 IEEE Custom Integrated Circuits Conference (CICC)

Citation (APA)

Lu, T., Chang, Z. Y., Jiang, J., Makinwa, K., & Du, S. (2023). A 13.56MHz Fully Integrated 91.8% Efficiency Single-Stage Dual-Output Regulating Voltage Doubler for Biomedical Wireless Power Transfer. In Proceedings of the 2023 IEEE Custom Integrated Circuits Conference (CICC) (pp. 1-2). IEEE. https://doi.org/10.1109/CICC57935.2023.10121186

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

## A 13.56MHz Fully Integrated 91.8% Efficiency Single-Stage Dual-Output Regulating Voltage Doubler for **Biomedical Wireless Power Transfer**

Tianqi Lu<sup>1</sup>, Zu-yao Chang<sup>1</sup>, Junmin Jiang<sup>2</sup>, Kofi Makinwa<sup>1</sup>, and Sijun Du1

<sup>1</sup>Delft University of Technology, Delft, the Netherlands

<sup>2</sup>Southern University of Science and Technology, Shenzhen, China

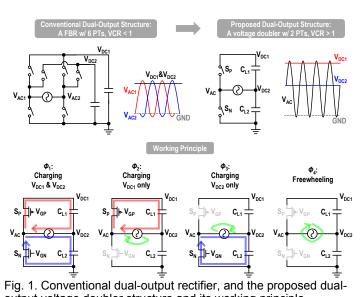

Dual-output regulating rectifier is highly desired in wireless power transfer (WPT) for sub-100mW bioimplants. Such rectifiers perform voltage rectification and dual-output regulation simultaneously, thus avoiding post DC-DC conversions and cascaded power losses [1-4]. However, the conventional dual-output structure suffers from a low voltage conversion ratio (VCR) (<1) due to the full bridge rectifier (FBR) topology (Fig. 1), severely limiting the receiver operation when wireless link condition varies [1-2]. In order to extend the operational range without increasing the power demand from the transmitter, [3] presents a charge-pump based dual-output rectifier; however, it uses 10 power transistors (PTs) and 8 off-chip capacitors, degrading the power conversion efficiency (PCE) and increasing the integration cost. Alternatively, the current-mode dual-output rectifier can realize a VCR higher than 1, but the output power is limited to less than 10mW [4], which is insufficient for advanced bioimplants. In this work, a 13.56MHz single-stage dual-output voltage doubler (DOVD) is proposed to address the above limitations, which employs only two PTs and a fully integrated design. It can achieve a peak VCR of 1.78 and outputs power up to 81mW with a 91.8% peak PCE.

The proposed DOVD consists of two PTs, SP and SN, and two output capacitors, C<sub>L1</sub> and C<sub>L2</sub>, in the power stage. Fig. 1 shows the working principle of the DOVD with 4-phase operation. When both outputs,  $V_{DC1}$  and  $V_{DC2}$ , need to be charged, the DOVD operates in  $\Phi_1$ , where both  $S_P$  and  $S_N$  are enabled to deliver power to  $C_{L1}$  and  $C_{L2}$ , respectively. When only V<sub>DC1</sub> needs to be charged, the DOVD switches to  $\Phi_2$ , where  $S_N$  is disabled so that only  $C_{L1}$  is charged. In  $\Phi_3$ , S<sub>P</sub> is disabled, and the DOVD charges C<sub>L2</sub> through S<sub>N</sub> to build V<sub>DC2</sub>. Due to the stack topology of C<sub>L1</sub> and C<sub>L2</sub>, V<sub>DC1</sub> also increases slightly when C<sub>L2</sub> is charged, but this can then be compensated by the controller, as will be explained later. When both V<sub>DC1</sub> and V<sub>DC2</sub> do not require energy from the AC input, the DOVD enters  $\Phi_4$ , the freewheeling phase, where both SP and SN are disabled.

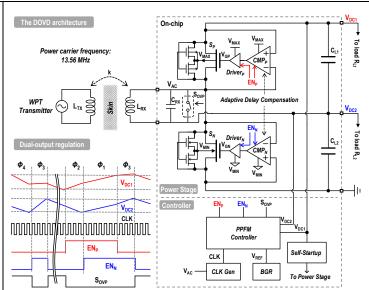

Fig. 2 presents the architecture of the proposed DOVD with controller and the operation principle of the dual-output regulation. S<sub>P</sub> (or S<sub>N</sub>) is controlled by the delay-compensated comparator CMP<sub>P</sub> (or CMP<sub>N</sub>) through the gate driver DriverP (or DriverN), functioning as a powerefficient active diode when enabled. To eliminate the dual-output cross-regulation issue, the parallel pulse frequency modulation (PPFM) controller is proposed, regulating V<sub>DC1</sub> and V<sub>DC2</sub> in two distinct hysteresis windows independently. If V<sub>DC1</sub> (or V<sub>DC2</sub>) reaches the lower hysteresis threshold, SP (or SN) will be enabled by signal ENP (or ENN) to charge CL1 (or CL2). When VDC1 (or VDC2) reaches the upper hysteresis threshold, SP (or SN) will be disabled. Selectively enabling the two PTs results in the 4-phase operation. In the freewheeling phase  $(\Phi_4)$ , an over-voltage protection block is activated by the controller (SovP) to limit the open-circuit VAC.

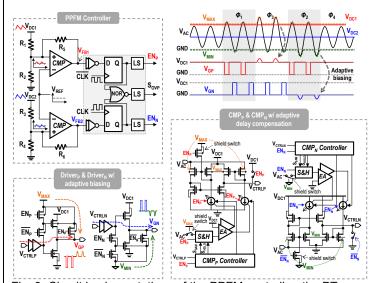

Fig. 3 shows the circuit implementation of the PPFM controller. To regulate V<sub>DC1</sub> and V<sub>DC2</sub>, the controller firstly employs two op-amp comparators (CMPs) to compare the divided versions of V<sub>DC1</sub> and V<sub>DC2</sub> with a reference voltage V<sub>REF</sub> generated on chip. The hysteresis window for V<sub>DC1</sub> (or V<sub>DC2</sub>) regulation is defined by the positive feedback resistor R<sub>5</sub> (or R<sub>6</sub>) and the resistive voltage divider. The control signals ENP, ENN and SOVP are then derived from the CMP outputs, V<sub>FB1</sub> and V<sub>FB2</sub>, synchronized with the CLK signal (recovered from VAC). Therefore, ENP, ENN and SOVP will not change until VAC roughly equals V<sub>DC2</sub>, resulting in a zero-voltage phase switching avoiding switching noise and efficiency degradation.

When the DOVD works in  $\Phi_2$  (or  $\Phi_3$ ) where  $S_N$  (or  $S_P$ ) is disabled, V<sub>AC</sub> can level up during the half period without resistive loading. The amplitude of V<sub>AC</sub> can easily go lower than -|V<sub>TH,N</sub>| (or higher than (V<sub>DC1</sub>+|V<sub>TH,P</sub>|)). To avoid the undesired channel conduction in S<sub>N</sub> (or

S<sub>P</sub>), Driver<sub>N</sub> (or Driver<sub>P</sub>) is designed to clamp V<sub>GN</sub> (or V<sub>GP</sub>) to the adaptive biasing  $V_{MIN}$  (or  $V_{MAX}$ ), which tracks the minimum (or maximum) voltage in the system, when  $S_N$  (or  $S_P$ ) is disabled, as shown in Fig. 3.

To drive S<sub>P</sub> (or S<sub>N</sub>) properly at 13.56 MHz, the delays in CMP<sub>P</sub> (or CMP<sub>N</sub>) and Driver<sub>P</sub> (or Driver<sub>N</sub>) need to be

Die micrograph.

compensated, or reverse currents and extra conduction losses could pop up. Therefore, CMPP and CMPN are designed to be switchedbiased push-pull comparators with adaptive delay compensation blocks [5] (Fig. 3). By sampling V<sub>AC</sub> at the turn-on/off moment of S<sub>P</sub> (or S<sub>N</sub>) and comparing it to V<sub>DC1</sub> (or GND) by the error amplifier, the gate-driving delay can steer the feedback loop tuning the bias current in the push-pull comparator, then aligning the turn-on/off timing of SP (or S<sub>N</sub>). The coupling/loading-insensitive delay compensation results in a high PCE. Moreover, shield switches are used to introduce V<sub>MIN</sub> (or V<sub>MAX</sub>) into CMP<sub>N</sub> (or CMP<sub>P</sub>), ensuring robust transistor shutoff when CMP<sub>N</sub> (or CMP<sub>P</sub>) is disabled in  $\Phi_2$  (or  $\Phi_3$ ).

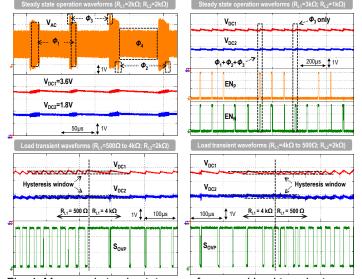

The proposed DOVD was fabricated in the 180nm BCD process, occupying a chip area of 0.4/3.68mm<sup>2</sup> with/without capacitors. The on-chip resonance capacitor C<sub>RX</sub> (518pF) is implemented by MIM capacitors; C<sub>L1</sub> and C<sub>L2</sub> are MOS/MIM stacking capacitors (3.9nF each). Fig. 4 shows the measured steady state operation waveforms and load transient waveforms of the DOVD. In the steady state, VAC amplitude changes dramatically, notifying 4-phase operation, which can also be verified by ENP and ENN. VDC1 and VDC2 are regulated at 3.6V and 1.8V, respectively, within preset hysteresis windows. The load transient waveforms were measured when RL1 was changed between  $500\Omega$  and  $4k\Omega$  in both directions and  $R_{L2}$  was kept equal to  $2k\Omega$ . No voltage undershoot/overshoot is observed at the transient moments, and more importantly, the cross-regulation issue is not observable because, by the nature of the proposed PPFM controller, the response of load transient is theoretically instantaneous and only determined by the preset hysteresis windows [6].

The top half of Fig. 5 shows the self-startup setting and the measured self-startup operation of the DOVD. During startup, the DOVD is forced to work as a passive voltage doubler by diode-connecting SP and S<sub>N</sub>. A V<sub>TH</sub>-based startup detector is designed to activate the DOVD mode when V<sub>DC1</sub> reaches V<sub>TH,ST</sub> (3V). The bottom half of Fig. 5 shows the measured VCR and PCE results of the DOVD. A VCR larger than 1 is easily obtained at V<sub>DC1</sub>, thanks to the voltage doubler topology. The peak VCR reaches 1.78 when R<sub>L1</sub>=R<sub>L2</sub>=4kΩ. Because only two PTs, with gate-driving delay compensated, are employed in the power stage, a high PCE is attained. The peak PCE reaches 91.8% when the total output power Pout is 33.5mW, and the PCE keeps higher than 87% when Pout is larger than 30mW.

Fig. 6 compares the proposed DOVD with state-of-the-art regulating rectifiers. This work is the only one simultaneously achieving: 1) dualoutput regulation, 2) higher-than-1 VCR, 3) up-to-81mW available Pout, while keeping a state-of-the-art PCE. By fully Integrating the resonance and output capacitors on chip, this work also achieves the smallest receiver volume (1.97mm<sup>3</sup>) and the highest power density (41.12mW/mm<sup>3</sup>) among the designs in the table.

#### Acknowledgement:

The authors would like to acknowledge EUROPRACTICE for MPW and design tool support.

### References:

[1] F. Marefat et al., ISSCC, Feb. 2020.

[2] F. -B. Yang et al., VLSI, Jun. 2022.

[3] Z. Xue et al., CICC, Apr. 2018.

[4] H. S. Gougheri et al., TBioCAS, vol. 13, no. 5, Oct. 2019.

[5] L. Cheng et al., JSSC, vol. 51, no. 3, Mar. 2016.

[6] J. Tang et al., ISSCC, Feb. 2021.

output voltage doubler structure and its working principle.

Fig. 2. Architecture of the proposed DOVD with controller, and the operation principle of its dual-output regulation.

Fig. 3. Circuit implementations of the PPFM controller, the PT drivers and the PT driving comparators.

Self-startup mechanism & Startup detector

Fig. 4. Measured steady-state waveforms and load transient responses.

| V <sub>MAX</sub> V <sub>DC</sub>  | R <sub>1</sub> 3                    | TH.ST = V<br>V <sub>THN</sub> + V <sub>THP</sub> Schmitt trigger EN <sub>ST</sub> | V <sub>AC</sub> V <sub>TH</sub> | ST                | 2V\$                                |

|-----------------------------------|-------------------------------------|-----------------------------------------------------------------------------------|---------------------------------|-------------------|-------------------------------------|

| V <sub>min</sub> V <sub>DC2</sub> | 2 R <sub>2</sub>                    |                                                                                   | Passive voltage d               | oubler DOVD       | 1.5V <b>\$</b>                      |

|                                   | ↑ L  cur  cur                       | rent limiting listor                                                              | EN <sub>ST</sub>                |                   | 280µs                               |

| 2.0 Mea                           | sured VCR vs. Load                  | 10                                                                                |                                 | sured PCE vs. Loa | ad                                  |

| 1.5                               | V <sub>DC1</sub>                    |                                                                                   | 91.                             | 8%                |                                     |

| ğ 1.0                             | V <sub>DC2</sub>                    | Efficiency (%)                                                                    | 0                               |                   | -                                   |

| 0.5                               | R <sub>L2</sub> = 2                 | 2 kΩ 7                                                                            | Maximum Pou                     |                   | R <sub>L2</sub> = 200 Ω             |

| 0.0 200 5                         | 00 1000 2000<br>R <sub>L1</sub> (2) | 6                                                                                 | 0 1000                          |                   | R <sub>L2</sub> = 2 kΩ<br>3000 4000 |

Fig. 5. The schematic and measured operation waveforms of the self-startup setting, and the measured VCR and PCE results.

|                                                | This work                                                         | [1] ISSCC 2020                    | [2] VLSI 2022                     | [3] CICC 2018                           | [4] TBCAS 2019                         |

|------------------------------------------------|-------------------------------------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------------|----------------------------------------|

| Technology                                     | 180-nm BCD                                                        | 180-nm CMOS                       | 180-nm CMOS                       | 180-nm CMOS                             | 350-nm CMOS                            |

| Input frequency                                | 13.56 MHz                                                         | 2 MHz                             | 6.78 MHz                          | 13.56 MHz                               | 1 MHz                                  |

| Chip area                                      | 0.4 mm <sup>2</sup> (w/o caps);<br>3.68 mm <sup>2</sup> (w/ caps) | 6 mm <sup>2</sup>                 | 2.32 mm <sup>2</sup>              | 0.66 mm <sup>2</sup>                    | 2.7 mm <sup>2</sup>                    |

| Receiver topology                              | Dual-output<br>regulating voltage<br>doubler                      | Dual-output full-bridge rectifier | Dual-output full-bridge rectifier | Charge-pump based dual-output rectifier | Current mode dual-<br>output rectifier |

| # of power transistors                         | 2                                                                 | 6                                 | 6                                 | 10                                      | 5                                      |

| Fully integrated<br>(off-chip<br>components)   | Yes                                                               | No<br>(2 capacitors)              | No<br>(2 capacitors)              | No<br>(8 capacitors)                    | No<br>(2 capacitors)                   |

| Receiver volume*                               | 1.97 mm <sup>3</sup>                                              | 5.64 mm <sup>3</sup>              | 3.44 mm <sup>3</sup>              | 8.56 mm <sup>3</sup>                    | 3.66 mm <sup>3</sup>                   |

| Output voltages<br>(# of regulated<br>outputs) | 1.8 V, 3.6 V (2)                                                  | 1.5 V, 2.5 V (2)                  | 3.7 V, 5 V (2)                    | 1.7 V, 2.75 V (2)                       | 2.6 V, 3.9 V (2)                       |

| Peak VCR                                       | 1.78 (R <sub>L1,2</sub> =4kΩ)                                     | 0.83**                            | 0.85**                            | 2.75                                    | 4.88**                                 |

| Maximum P <sub>OUT</sub>                       | 81 mW (R <sub>L1,2</sub> =200Ω)                                   | 65 mW                             | 300 mW                            | 10 mW                                   | 45 mW                                  |

| Peak PCE                                       | 91.8% (@ 33.5mW)                                                  | 90.75% (@ 65 mW)                  | 91.7% (@ 200** mW)                | 79% (@ 7.1 mW)                          | 75.3% (@ 4.7 mW)                       |

| Power density***                               | 41.12 mW/mm <sup>3</sup>                                          | 11.52 mW/mm <sup>3</sup>          | 8.02 mW/mm <sup>3</sup>           | 1.17 mW/mm <sup>3</sup>                 | 12.29 mW/mm <sup>3</sup>               |

<sup>\*</sup>Assuming off-chip capacitors have the most compact cases on PCB based on their values

Fig. 6. Performance summary of the proposed DOVD and comparison to state-of-the-art designs.

<sup>\*\*</sup>Estimated from plotted data.

<sup>\*\*\*</sup>Calculated by Maximum Pour Receiver volume