#### Technology platform for advanced neurostimulation implants The "chip-in-tip" DBS probe

Kluba, M.M.

10.4233/uuid:9dd9701b-343e-4f25-8d49-02652e839e32

**Publication date**

**Document Version** Final published version

Citation (APA)

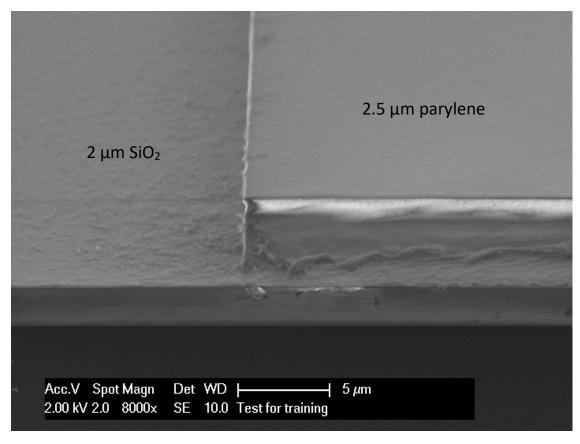

Kluba, M. M. (2022). *Technology platform for advanced neurostimulation implants: The "chip-in-tip" DBS probe.* [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:9dd9701b-343e-4f25-8d49-02652e839e32

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# TECHNOLOGY PLATFORM FOR ADVANCED NEUROSTIMULATION IMPLANTS

The "Chip-in-Tip" DBS Probe

## TECHNOLOGY PLATFORM FOR ADVANCED NEUROSTIMULATION IMPLANTS

THE "CHIP-IN-TIP" DBS PROBE

#### **Dissertation**

for the purpose of obtaining the degree of doctor

at Delft University of Technology

by the authority of the Rector Magnificus Prof.dr.ir. T.H.J.J. van der Hagen

Chair of the Board for Doctorates

to be defended publicly on

Monday, 31st January 2022 at 10:00 o'clock

by

#### Marta Maria KLUBA

Master of Science in Biomedical Engineering (double degree)

RWTH Aachen University, Germany

RUG University of Groningen, The Netherlands

and

Master of Science in Chemical Technology

AGH University of Science and Technology, Kraków, Poland

born in Oświęcim, Poland.

This dissertation has been approved by the promotor:

Promotor: Prof. dr. ir. R. Dekker

#### Composition of the doctoral committee:

Rector Magnificus, chairperson

Prof. dr. ir. R. Dekker Delft University of Technology, promotor

#### Independent members:

Dr. V. Giagka

Prof. dr. ir. P.M. Sarro Delft University of Technology

Prof. dr. P.J. French Delft University of Technology

Prof. dr. ir. J. Vanfleteren Ghent University, Belgium

Dr. G. Pandraud Ommatidia LIDAR, The Netherlands

Delft University of Technology

Dr. V.A. Henneken Philips Research, The Netherlands

Grant number: 2014-2-662155

Keywords: neurostimulation, directional deep brain stimulator, miniaturization, high-level integration, trench capacitor, high-definition flex-to-rigid, sealable trenches, cavity-BOX, biocompatible flip-chip, flexible interconnects, soft encapsulation, parylene, platinum, ceramics, parylene processing in cleanroom

Printed by: Ipskamp printing Cover designed by: M.M. Kluba

Copyright © 2022 by M.M. Kluba<sup>1</sup>

ISBN: 978-94-6384-296-9

An electronic version of this dissertation is available at:

http://repository.tudelft.nl

<sup>&</sup>lt;sup>1</sup> Author email: klubam@gmail.com

### **CONTENTS**

| Pretac | œe                                                          | 1  |

|--------|-------------------------------------------------------------|----|

| 1 In   | troduction                                                  | 3  |

| 1.1    | Neurostimulation                                            | 3  |

| 1.2    | State of the art                                            | 5  |

| 1.3    | Beyond the state of the art                                 | 6  |

| 1.4    | Flex-to-Rigid (F2R) platform                                | 7  |

| 1.5    | High-level components integration                           | 8  |

| 1.6    | Research objectives                                         | 9  |

| 1.7    | Outline of this thesis                                      | 9  |

| 2 Cl   | hip-in-Tip: Highly Integrated DBS Probe                     | 13 |

| 2.1    | Introduction                                                | 13 |

| 2.2    | Steerable brain stimulator (SBS) - directional DBS          | 13 |

| 2.3    | Chip-in-Tip                                                 | 15 |

| 2.4    | Directional DBS – The Chip-in-Tip design                    | 17 |

| 2.5    | Bio-compatible materials for implantable devices            | 22 |

| 2.6    | Component integration                                       | 24 |

| 2.7    | Packaging                                                   | 26 |

| 2.8    | Conclusions                                                 | 29 |

| 3 AS   | SIC Integration – Biocompatible Flip-chip                   | 33 |

| 3.1    | Introduction                                                | 33 |

| 3.2    | Test structures                                             | 34 |

| 3.3    | Enabling technologies                                       | 36 |

| 3.4    | Discussion and conclusions                                  | 44 |

| 4 In   | tegrating High-density Capacitors                           | 47 |

| 4.1    | Introduction                                                | 47 |

| 4.2    | Microchannels embedded in silicon                           | 49 |

| 4.3    | Wafer-scale integration for neural implant miniaturization  | 53 |

| 4.4    | Cavity-BOX SOI: Advanced silicon substrate for MEMS devices | 57 |

| 4.5    | Trench capacitor integration process                        | 68 |

| 4.6    | Conclusions                                                 | 78 |

| 5 Pa   | ckaging Technologies                                        | 81 |

| 5.1    | Introduction                                                | 81 |

| 5.2    | Device wrapping                                             | 81 |

| 5.3    | Device filling.                                             | 83 |

| 5.4    | Conclusions                                                 | 85 |

VIII CONTENTS

| 6 Pa   | arylene Processing in Microfabrication Cleanroom                | 87  |

|--------|-----------------------------------------------------------------|-----|

| 6.1    | Introduction                                                    | 87  |

| 6.2    | Adhesion in the parylene-platinum-based interconnects           | 88  |

| 6.3    | Cleaning wafers containing parylene                             | 96  |

| 6.4    | Contamination prevention in two-side wafer processing           | 98  |

| 6.5    | Parylene etching and patterning                                 | 100 |

| 6.6    | Platinum processing on top of parylene                          | 111 |

| 6.7    | Conclusions                                                     | 117 |

| 7 Pa   | arylene-platinum Flexible Interconnects "Top Stack" Approach    | 121 |

| 7.1    | Introduction                                                    | 121 |

| 7.2    | Test device design                                              | 122 |

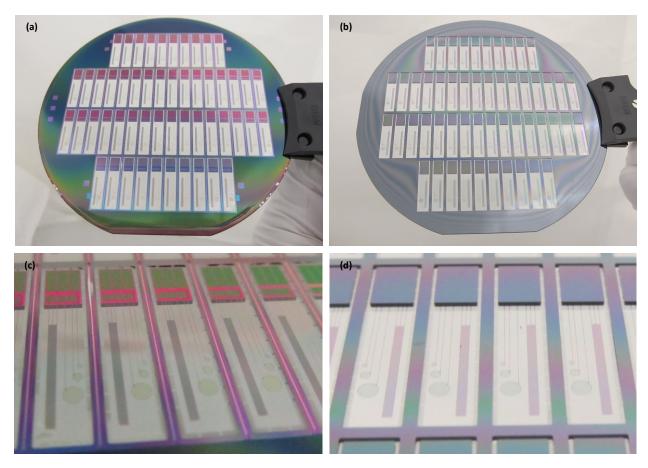

| 7.3    | Fabrication flowchart – "top stack"                             | 124 |

| 7.4    | Mask design                                                     | 127 |

| 7.5    | Device fabrication – results and discussion                     | 127 |

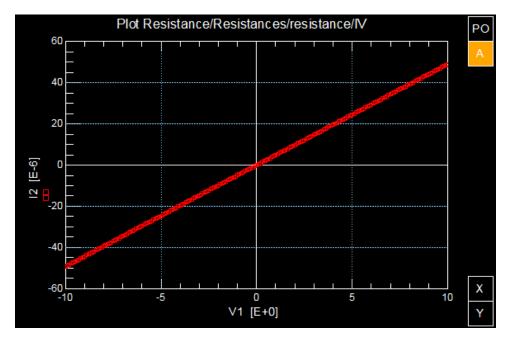

| 7.6    | Device evaluation                                               | 130 |

| 7.7    | Conclusions                                                     | 131 |

| 8 Ce   | eramic-parylene Flexible Interconnects "Parylene Last" Approach | 133 |

| 8.1    | Introduction                                                    | 133 |

| 8.2    | Test device design                                              | 134 |

| 8.3    | Fabrication flowchart - "parylene last"                         | 135 |

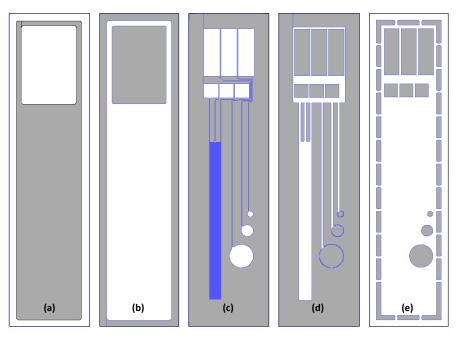

| 8.4    | Mask design                                                     | 138 |

| 8.5    | Technology modules                                              | 139 |

| 8.6    | Device fabrication                                              | 143 |

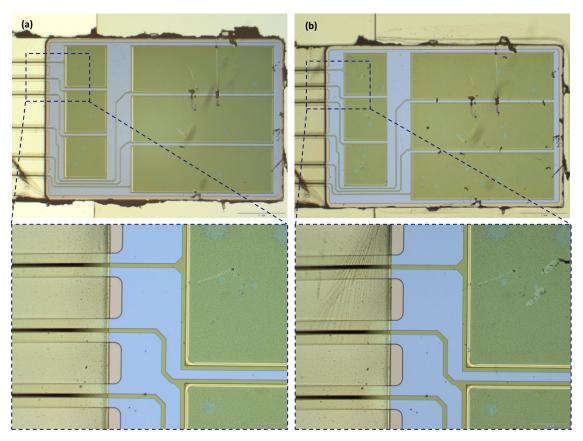

| 8.7    | Device evaluation                                               | 148 |

| 8.8    | Conclusions                                                     | 156 |

| 9 C    | onclusions                                                      | 161 |

| 9.1    | Conclusions                                                     | 161 |

| 9.2    | Contributions                                                   | 162 |

| 9.3    | Recommendations                                                 | 163 |

| Apper  | ndix A                                                          | 165 |

|        | ndix B                                                          |     |

|        |                                                                 |     |

|        | nary                                                            |     |

| Same   | nvatting                                                        | 171 |

| Ackno  | owledgments                                                     | 175 |

| List o | f Publications                                                  | 179 |

| Biogra | aphy                                                            | 181 |

This thesis was realized within the EU ECSEL JU project InForMed, grant number 2014-2-662155. The main goal of this project was innovation of tools and technologies for medical device fabrication and assembly, and to establish an integrated pilot line for their manufacturing and testing. To bridge the gap between research and industry production, cooperation between a number of international partners was started to bring together the knowledge and experience from both worlds.

Participating in the InForMed project had multiple implications for this thesis that is focused on the development of a highly integrated deep brain stimulation (DBS) probe. The choices made while designing the DBS probe, the selection of materials and fabrication methods, and the development of test protocols were carefully evaluated with the whole team. The initial goal of the project was to design, fabricate and test the directional DBS device that would need to fulfill all the requirements for implantable medical devices. However, after the end-user and leader of the DBS work package, Medtronic, had withdrawn from the project, many activities connected with device packaging and the final system assembly and testing were dropped. At that point the focus of the PhD project shifted towards the development of the necessary enabling technology modules, and the evaluation of their feasibility.

The manufacturing process should be easily scalable and transferable to the pilot line and finally to the industrial manufacturer. The alignment of the designed structures and the used fabrication and packaging methods and techniques was crucial since several manufacturing steps were performed at different fabrication sites. For this reason, only a limited number of technologies and materials could be considered for further investigation in this thesis. Moreover, the focus of the thesis was directed from quantitative research, including investigation of design variations and different materials and methods, towards a more qualitative evaluation of the jointly selected options, chosen based on the experience of the partners.

This work is a result of a collaboration with the following InForMed partners:

- CEA Leti, France;

- Comelec, Switzerland;

- Delft University of Technology (TU Delft), The Netherlands;

- Fraunhofer IZM (FIZM), Germany;

- ICSense, Belgium;

- Medtronic (MEDC), The Netherlands (2015-2016);

- Murata, France (former IPDiA);

- Okmetic, Finland;

- Philips Innovation Services (PInS), The Netherlands;

- Philips Research, The Netherlands;

- Picosun, Finland;

- Salvia BioElectronics, The Netherlands (2017-2018).

The majority of the design and processing work was performed at the Delft University of Technology (TU Delft) in the Else Kooi Laboratory (EKL). Therefore, to fabricate some proof of concepts devices and test devices in a coherent way, locally applicable rules regarding, for example, contamination had to be take into consideration. In some cases, a material of choice (e.g., platinum used for metallization) had to be replaced with the closest available substitute.

#### Introduction

#### 1.1 NEUROSTIMULATION

In 46 AD Scribonius Largus discovered the therapeutic properties of electrical stimulation when he used the torpedo fish (electric ray) to treat headaches [1]. Since then, not much research was carried out in the electrical stimulation of the body until the discovery of electricity around the 16th and 17th centuries. Consequently, a series of experiments carried out throughout the 18th and the 19th century demonstrated that electrical stimulation of nerves or the brain could induce twitching movement in a dead animal's limb [2][3]. Such a bodily response like limb movement was induced by applying current directly to the corresponding nerve or the region in the brain responsible for sending signals to that part of the body. The current activates the neural network, the signal travels down to the limb, and the muscle is activated [4].

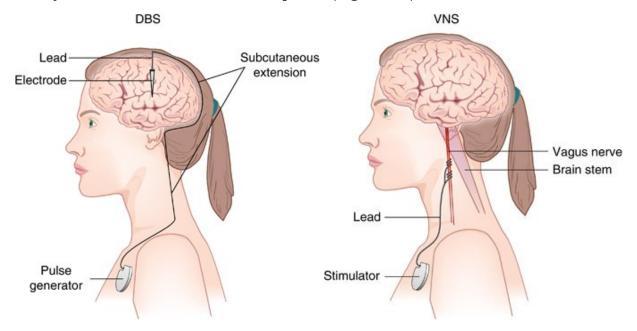

Since the 19<sup>th</sup> century, the field of neurostimulation – the intentional modification of the nervous system activity through targeted delivery of electrical stimuli - has changed enormously. Nowadays, nervous system stimulation is applied to induce or suppress not only a mechanical response, but it can also influence hearing, vision, immune system response, pain perception, and even mental state. The targeted neurostimulation therapy can compete with, or even outperform, the traditional chemical treatment [5][6]. The well-targeted electrical neuromodulation can help to reduce the whole-body side effects typical for traditional medications therapies. Furthermore, modern neurostimulation devices can precisely target very specific nerve bundles or regions in the brain. Also, they can be implanted in the body to aid easy delivery of the stimuli for an extended period (Figure 1.1).

Figure 1.1: Schematics of the implanted deep brain stimulator (DBS) and vagus nerve stimulator (VNS) [7].

4 Neurostimulation

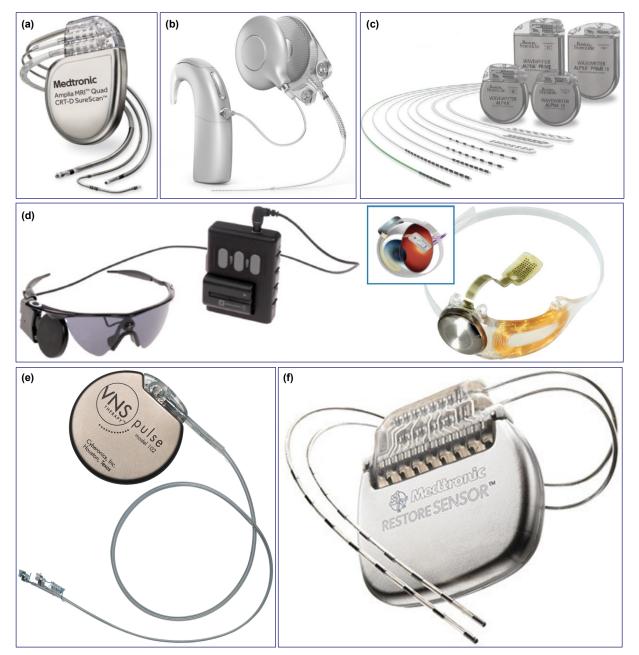

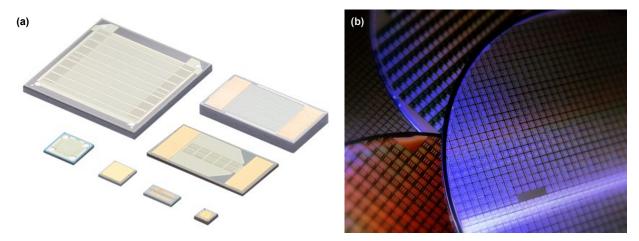

Many of the current implantable neurostimulation devices are commercially available on the market, and some are even recognized as an official medical treatment for specific conditions. Some examples of implantable biomedical devices are: cardiac stimulators to treat various types of heart arrhythmias; cochlear implants to restore hearing or retina implants to restore vision; spinal cord stimulators to treat chronic pain; vagus nerve stimulators to treat epilepsy and depression; and deep brain stimulators to treat Parkinson's disease, essential tremor, dystonia [8][9]. Examples of implantable bioelectronics are shown in Figure 1.2.

Figure 1.2: Examples of chronically implantable neurostimulation devices available on the market. (a) Cardiac implant (pacemaker) from Medtronic [10]. (b) Cochlear implant from Oticon Medical [11]. (c) Spinal cord stimulator from Boston Scientific [13]. (d) Retinal prosthesis system (Argus II) from Second Sight Medical Products [12]. (e) Vagus nerve stimulator from Cybertonics [14]. (f) Deep brain stimulator (DBS) from Medtronic [15].

INTRODUCTION 5

#### 1.2 STATE OF THE ART

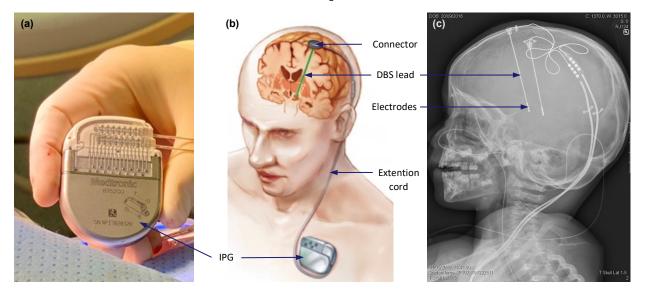

Traditional neurostimulation devices, such as an implantable deep brain stimulator (DBS), are composed of an implantable pulse generator (IPG), extension cord, and stimulation leads with electrodes on their distal end. The IPG is usually implanted underneath the skin in the patient's chest (Figure 1.3a,b). It contains a battery pack, telemetry coil, and circuitry for steering, sensing, diagnostic and communication management [16]. All these elements are enclosed in a rigid casing, usually made from titanium that is often additionally coated with a parylene layer. The case is hermetically closed to protect the implant from bodily fluids and protect the body from harmful substances that can be released from the implant.

Figure 1.3: Deep brain stimulation (DBS) device. (a) Implantable pulse generator (IPG) with two extension cords for operating two DBS leads [17]. (b) Schematic of the implanted one-lead DBS device composed of the IPG, extension cords with connectors, and the DBS lead [18]. (c) A two-year-old boy with implanted two-lead DBS device [19].

The multi-wired flexible extension cord is attached to the pulse generator through a series of connectors located on the titanium casing. The cord is composed of a coiled conductor (e.g., platinum-iridium wire) filled with silicone rubber (e.g., PDMS) and insulated with a polymer such as a polycarbonate urethane [20]. In the case of the DBS device, the extension cord runs from the IPG implanted in the chest, underneath the skin, to the skull. On the skull, the cord connects with the DBS leads and passes the signal from the pulse generator to the stimulation electrodes. To ease the implantation of up to 45 cm long extension cord [21][22], it is often split into two or three parts and reconnected again on the skull using connectors (Figure 1.3b).

The stimulation lead (usually 2 in the case of DBS) is implanted through the skull deep into the brain (Figure 1.3b,c). The lead is composed of a coiled conductor that transports the signal to the stimulation electrodes located on the tip of the DBS lead. The DBS lead and the electrodes are made from biostable and biocompatible platinum or platinum-iridium alloy located on a polymer-based (polyurethane) tip (Figure 1.4). The exposed electrodes are in direct contact with the tissue to form a neural interface with the brain and enable its stimulation.

Figure 1.4: Tip of the DBS lead with coiled conductor and four cylindrical electrodes located at the tip [23].

#### 1.3 BEYOND THE STATE OF THE ART

The advancements in the field of neurostimulation are impressive both from a technical and from a therapeutic point of view. The number of medical conditions that can be treated using existing or completely novel neurostimulation devices continues to grow. Unfortunately, some aspects of implantable bioelectronics devices have not changed for decades, even though they call for improvement.

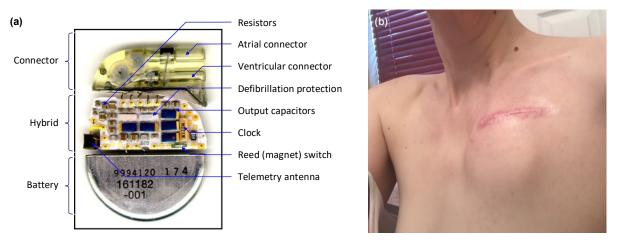

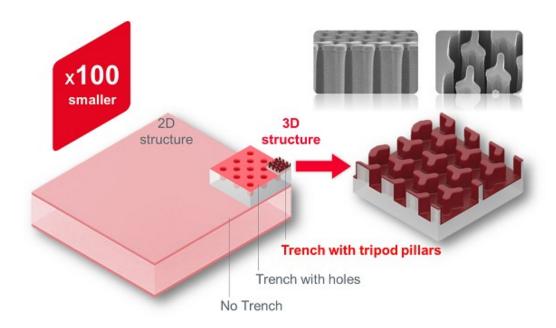

#### 1.3.1 Packaging vs. aesthetics and invasiveness

For example, the golden standard for encapsulating the implantable pulse generator (IPG) module remains a bulky titanium case that accommodates all the electronic components (Figure 1.5). Besides aesthetical aspects, implanting such a case involves rather invasive surgery, especially for implants where the targeted stimulation site is located far from the pulse generator unit (e.g., deep brain stimulator). Much research is currently going on in the field of soft encapsulation of long-term biomedical devices, which might not only allow for the miniaturization of the pulse generator unit but also bring it closer to the stimulation site [24]. The miniaturization process can be further improved by applying highly efficient or even rechargeable energy sources, energy-saving stimulation algorithms, reducing the size of the electronic components (e.g., employing high-capacity trench capacitors), or more space-efficient electronic components integration (e.g., flip-chip) [25].

Figure 1.5: (a) The anatomy of the cardiac pulse generator (pacemaker) [26]. (b) DBS pulse generator implanted under the skin on the chest [27].

#### 1.3.2 Manufacturing vs. resolution

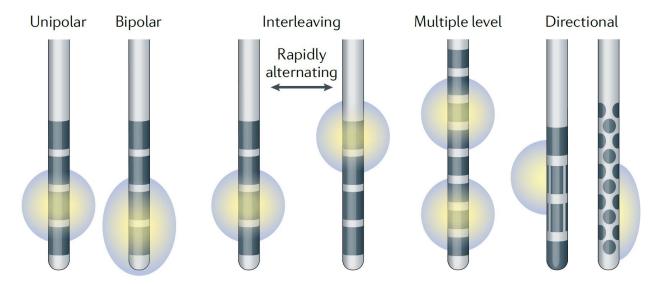

Another area for improvement concerns the labor-intensive manufacturing process. Techniques like soft lithography are commonly used to fabricate flexible stimulation leads with electrodes. They not only come at a high cost due to low throughput, but because of the low process resolution, they also limit the size, number, and distribution pattern of the electrodes that can be integrated at the tip of the lead. As a result, the most advanced stimulation leads available on the market contain only eight electrodes, even though in some cases, such as for DBS, the advantages of directional stimulation with a multitude of smaller electrodes (Figure 1.6) has been repeatedly proven [25][28][29][30]. The number and the design freedom of the electrodes located at the tip of the DBS lead can be improved by fabricating flexible structures on a flat silicon carrier using standard integrated circuit (IC) microfabrication techniques and consequent folding and rolling of such a device into the round shape of the DBS. In response to the resolution issue, Sapiens SBS has developed a wafer-based process allowing for the fabrication of DBS leads with up to 64 individual electrodes [31][32].

INTRODUCTION 7

Figure 1.6: Various DBS probe designs and stimulation patterns. Examples of standard, cylindrical electrodes (first five) and segmented electrodes (last two) that enable directional brain stimulation [25].

The fabrication of the lead designed by Sapiens with dozens of individually activated electrodes, and consequent trial implantations, allowed to show the benefits of directional stimulation. It can reduce the side effects of surrounding tissue overstimulation and enable the stimulation of new, smaller regions in the brain. Nevertheless, the lead has never been further developed and used for chronic stimulation because the number of contacts (one for each electrode) that had to be made during the surgical procedure was extremely challenging. Moreover, the wafer transfer technique and the consequent manual release of the flexible film with the electrodes are not scalable, somewhat cumbersome, and do not tend to have a high yield.

#### 1.3.3 Highly integrated silicon-based devices

To reach beyond state of the art in the implantable neurostimulation field, it seems essential to focus on further miniaturization of the implant and improvement of the stimulation resolution by increasing the number of electrodes. Looking at these challenges from the manufacturing point of view, it only seems logical to investigate IC-compatible microfabrication technologies, such as Flex-to-Rigid (F2R) [33]. The Flex-to-Rigid can tackle both of the objectives simultaneously by allowing for high-level components integration and further device miniaturization.

#### 1.4 FLEX-TO-RIGID (F2R) PLATFORM

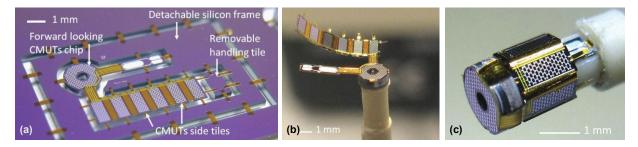

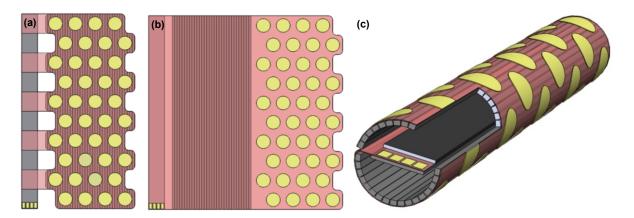

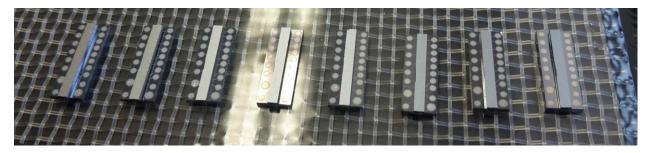

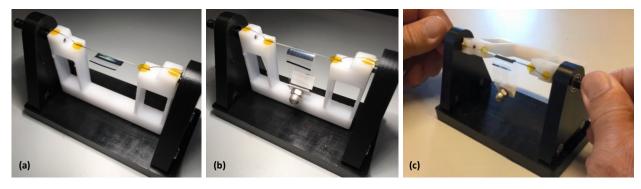

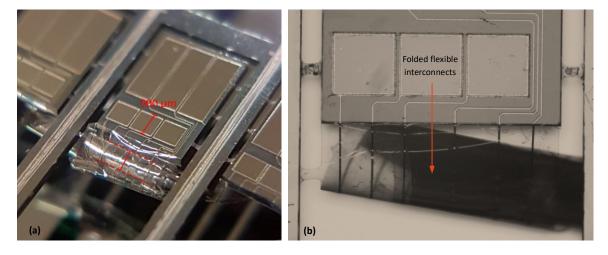

Flex-to-Rigid (F2R) is a generic platform that enables miniaturization of medical devices by permitting monolithic component integration into a semi-flexible device structure [33]. The technology is compatible with integrated circuit (IC) microfabrication techniques. Thanks to this, advanced electronic components can be fabricated on individual silicon islands and subsequently connected with flexible polyimide-aluminum-based interconnects. The device, such as the smart catheter equipped with MEMS ultrasound transducers (CMUTs), is fabricated on a silicon wafer, where it remains suspended using flexible tabs (Figure 1.7a). After it is released from the wafer (Figure 1.7b), the device can be folded or, like in the case of the smart catheter, wrapped around a shape (Figure 1.7c).

Figure 1.7: Semi-flexible demonstrator device fabricated in the Flex-to-Rigid technology comprising ultrasounds transducers (CMUTs) [33]. (a) The device suspended in the silicon frame using polymer-based tabs. (b) Mounting of the device released from the wafer. (c) The device mounted at the tip of the catheter.

Additionally, the F2R technology uses standard IC-compatible tools and techniques, making the fabrication process fully scalable, reducing the costs of bioelectronics device manufacturing, thereby making treatment more affordable and accessible.

#### 1.5 HIGH-LEVEL COMPONENTS INTEGRATION

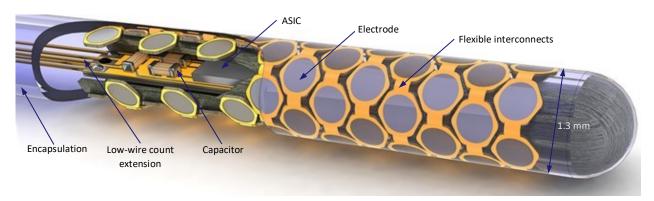

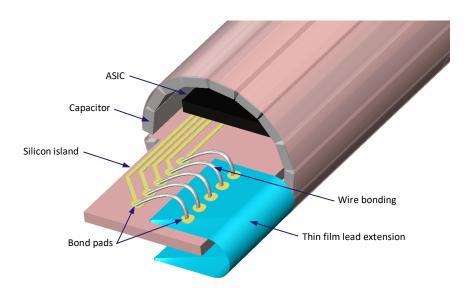

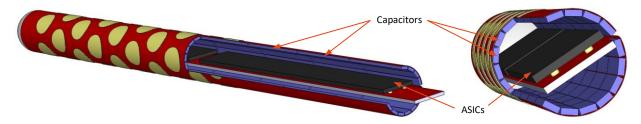

The F2R platform enables a high level of integration of components into the semi-flexible device structure. Integrating electronic components such as application-specific integrated circuits (ASICs) or capacitors directly in/on the silicon allows for the fabrication of a high-resolution stimulation device with a large number of electrodes without the need for complex leads and extension cords. For example, integrating signal multiplexing components at the tip of the deep brain stimulator (DBS) lead can ensure high stimulation resolution by enabling individual activation of multitude of electrodes, but at the same time significantly reduce the number of signal and power wires running down to the pulse generator (Figure 1.8). In this case, the flexible interconnects enable the folding of the integrated device into the desired, miniaturized shape. They can also make the bioelectronics device more flexible and thus more compatible with the human body (e.g., spinal cord stimulator, deep brain stimulator) or enable wrapping the implant around, for example, a nerve bundle (e.g., vagus nerve stimulator) [28].

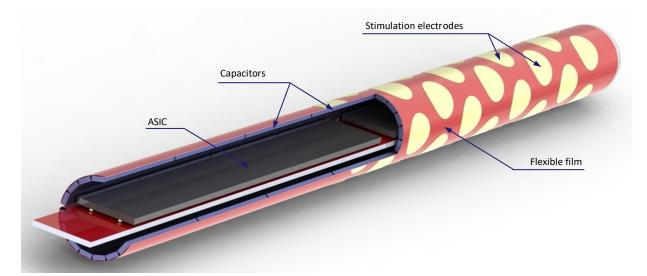

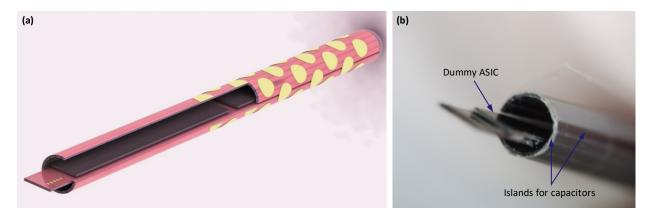

Figure 1.8: Impression of the highly-integrated directional deep brain stimulation probe with ASIC and safety capacitors integrated inside the tip of the probe. Source: InForMed.

Furthermore, direct integration of components into the stimulation part of the implant enables not only its miniaturization or improving mechanical compatibility with the human body. Moving components out of the implantable pulse generator (IPG) can significantly decrease its dimensions, making the treatment less invasive, and in the future, the IPG may even become obsolete.

INTRODUCTION 9

The current F2R platform uses polyimide and aluminum as base materials for the flexible interconnects. These materials are not suitable for long-term implantable neurostimulation devices. Aluminum is not a noble material, and as such, it might react with bodily fluids [24]. Polyimide is not an FDA-certified material for long-term use in the human body. Besides, polyimide manufacturers refuse to supply the material when it is intended to be used for implantable devices. Therefore, the Flex-to-Rigid technology needs to be developed into a platform containing only biocompatible and biostable flexible interconnects.

#### 1.6 RESEARCH OBJECTIVES

The research presented in this thesis was partially carried out within the EU ECSEL Joint Undertaking project InForMed. One of the objectives of this project was to develop a guideline for crossing the valley of death between academia and industry in the field of medical device microfabrication. Following that guideline, several technologies enabling the fabrication of innovative medical devices were developed, and the transfer of these processes from the laboratory to the pilot line or foundry was executed. Multidisciplinary teams were formed within the project involving academia, silicon wafer and electronic component manufacturers, packaging and coating specialists, and contractors. The project objectives and collected specialists created a perfect ground for tackling the challenges that are slowing down the development of current neurostimulation devices, such as deep brain stimulators (DBS). The interdisciplinary approach and the condition of process scalability and transferability to industry resulted in continuous balancing between the academic laboratory capabilities and industrial requirements, which strongly impacted the research done in this thesis.

The goal of the research presented in this thesis was to develop a set of enabling technologies that will turn the Flex-to-Rigid technology into a platform for the fabrication of highly integrated implantable medical devices. To achieve this, several critical aspects of this goal have been investigated, such as monolithic wafer-based component integration, biocompatible flip-chip on the semi-flexible Flex-to-Rigid devices, packaging and soft encapsulation for implantable devices, parylene processing in a microfabrication cleanroom, and the flexible implantable interconnect fabrication process itself. These topics have been investigated using a 40-electrode DBS device design as a demonstrator. The scope of this work is not to fabricate a fully functioning device but rather to develop the building blocks that will enable large-scale fabrication of implantable electronic devices that are compatible with industrial manufacturing.

#### 1.7 Outline of this thesis

In this thesis, a number of technologies have been developed to enable electronic component integration into long-them neurostimulation implants. Several aspects of design, fabrication, integration, and packaging of a highly integrated directional deep brain stimulation (DBS) probe have been investigated.

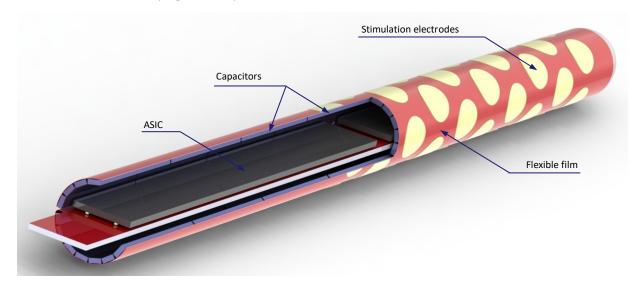

In Chapter 2, the parylene-based Chip-in-Tip DBS design is introduced. It allows for placing the steering ASICs (chips) and the necessary decoupling capacitors inside the tip of the DBS probe. This approach enables directional stimulation using forty independent electrodes and, at the same time, simplifies the implantation procedure by limiting the number of connections between the probe and pulse generator. The requirements are defined, and corresponding technologies and materials necessary to realize the design, fabrication, component integration, and packaging are investigated.

10 OUTLINE OF THIS THESIS

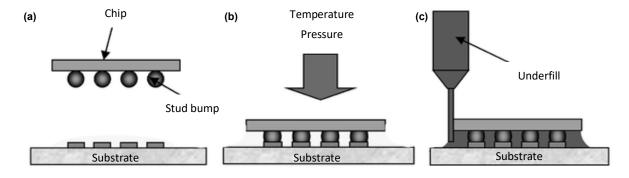

Chapter 3 focuses on the biocompatible flip-chip process for ASICs integration directly onto the DBS structure. The developed enabling technologies such as platinum-based stud bumping, platinum to platinum bonding, and biocompatible underfill are presented. The processes are verified using specially prepared test devices, representing the Chip-in-Tip DBS design.

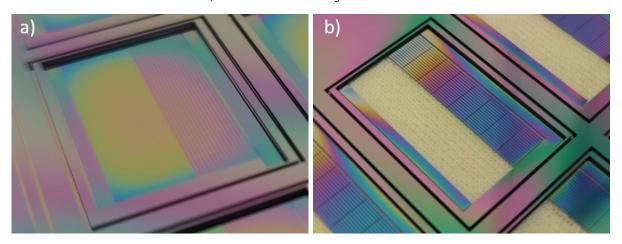

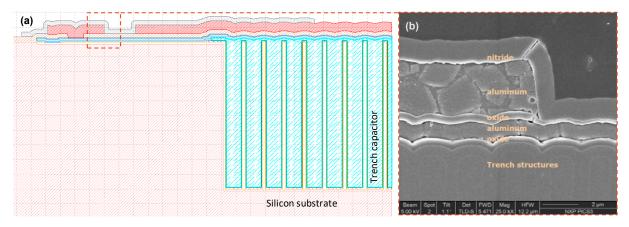

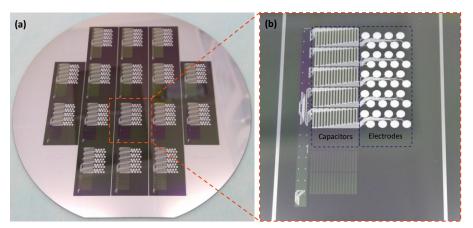

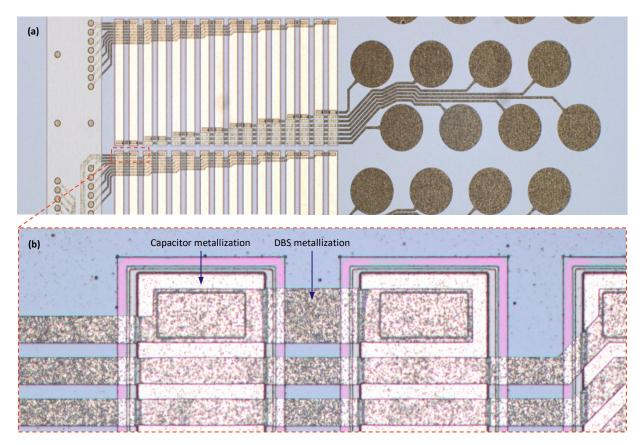

Chapter 4 presents the developed technologies enabling integration of high-density trench capacitors directly into an SOI substrate, further used to fabricate the semi-flexible DBS probe structure in the Flex-to-Rigid process. Two technologies are developed for the precise separation of capacitor structures. The first one employs sealable microchannels (trenches) embedded in silicon. The second one is based on the custom-developed SOI wafer with a patterned BOX layer – cavity-BOX. Next, the design and the fabrication process alignment strategy are established, and the feasibility of the inter-facility capacitors integration process is shown using a demonstrator device.

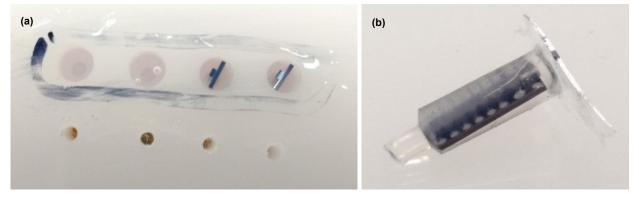

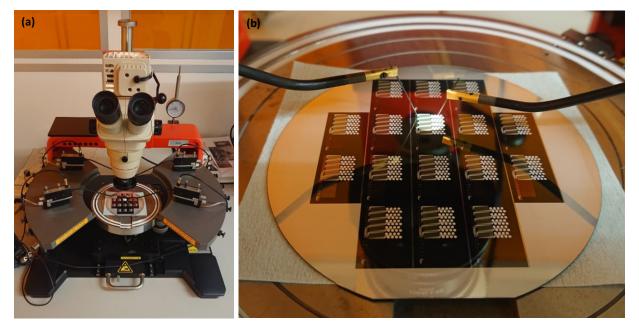

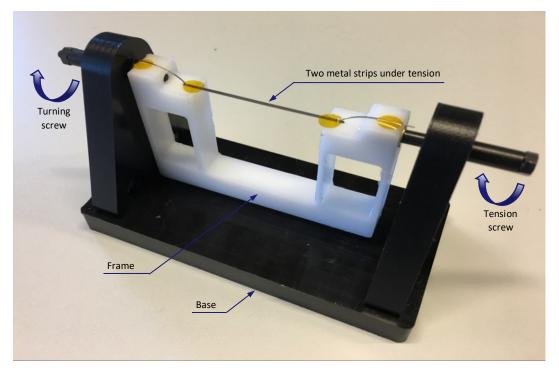

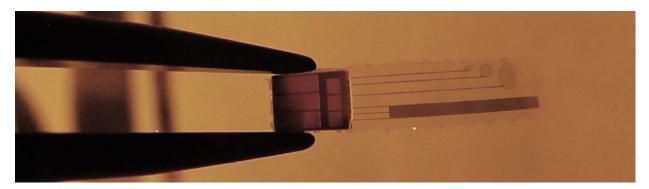

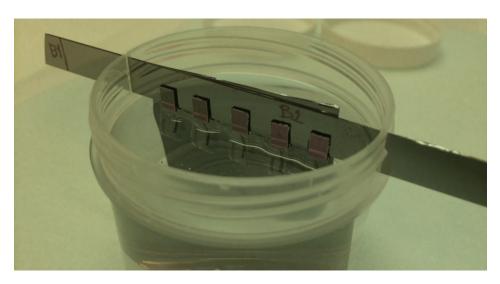

In Chapter 5, some aspects of the Chip-in-Tip DBS device packaging are investigated. First, a tool for wrapping the semi-flexible 2D structure into a cylindrical 3D DBS probe is developed. Thanks to applying a set of metal strips to mount the device, there is no need for inserting additional mechanical support inside the device. Next, the device filling method and material are selected and tested using parylene-silicon-based mockup DBS structures.

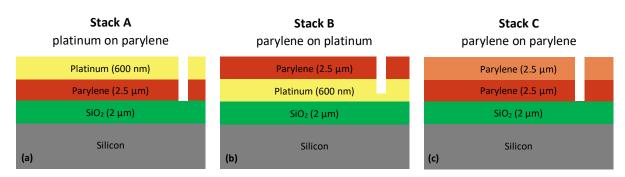

Chapter 6 concentrates on various aspects of processing wafers containing parylene in the EKL microfabrication cleanroom environment. Special attention is drawn to the fabrication of parylene-platinum-based flexible interconnects. First, the adhesion between the parylene and platinum is studied in various configurations. The influence of the standard microfabrication processes on the adhesion in the stacks is evaluated. Next, the processing aspects such as contamination prevention and cleaning of the wafers containing parylene and parylene patterning methods are investigated. Finally, the procedures for platinum processing on top of parylene are presented.

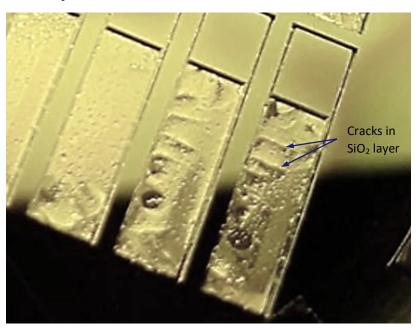

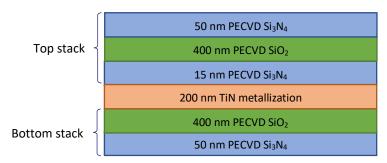

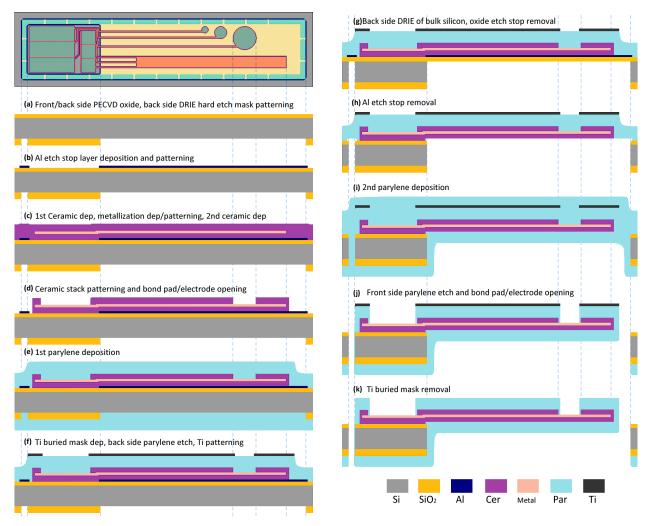

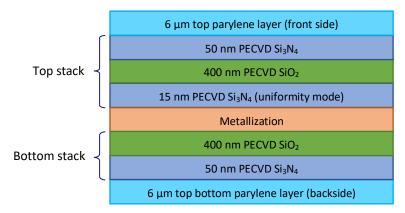

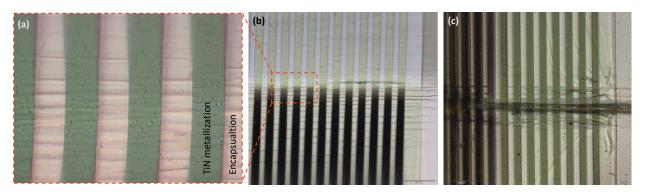

In Chapter 7 and Chapter 8, the technologies developed for parylene processing in a microfabrication cleanroom are applied to fabricate devices with parylene-based flexible interconnects. For that, a test device comprising flexible internets, comb-meanders structure, and a set of electrodes is designed, fabricated, and evaluated. In Chapter 7, the interconnects are fabricated by encapsulating platinum tracks in two layers of parylene deposited underneath and on top of the metallization using the "Top stack" approach. In Chapter 8, the titanium nitride (TiN) interconnects are encapsulated in parylene and a stack of additional ceramic layers SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>. In this process, the interconnects are first encapsulated in ceramics, and at the very end of the fabrication, the parylene encapsulation is deposited using the "Parylene Last" approach.

The general conclusions of this thesis, contributions to the field of microfabrication, and recommendations for future research are collected in Chapter 9.

#### REFERENCES

- [1] J. E. Jensen, R. R. Conn, G. Hazelrigg, and J. E. Hewett, "The Use of Transcutaneous Neural Stimulation and Isokinetic Testing in Arthroscopic Knee Surgery," The American Journal of Sports Medicine, vol. 13, no. 1, 1985, doi: 10.1177/036354658501300105.

- [2] M. Bresadola, "Medicine and Science in the Life of Luigi Galvani (1737-1798)," Brain Research Bulletin, vol. 46, no. 5, 1998, doi: 10.1016/S0361-9230(98)00023-9.

Introduction 11

[3] G. Fritsch and E. Hitzig, "Electric Excitability of the Cerebrum (Über die Elektrische Erregbarkeit des Grosshirns)," Epilepsy and Behavior, vol. 15, no. 2, 2009, doi: 10.1016/j.yebeh.2009.03.001.

- [4] P. Sanjuan-Alberte, M. R. Alexander, R. J. M. Hague, and F. J. Rawson, "Electrochemically Stimulating Developments in Bioelectronic Medicine," Bioelectronic Medicine, vol. 4, no. 1, 2018, doi: 10.1186/s42234-018-0001-z.

- [5] E. S. Krames, P. Hunter Peckham, A. R. Rezai, and F. Aboelsaad, "What Is Neuromodulation?," in Neuromodulation, vol. 1, 2009. doi: 10.1016/B978-0-12-374248-3.00002-1.

- [6] C. O. Oluigbo and A. R. Rezai, "Addressing Neurological Disorders with Neuromodulation," IEEE Transactions on Biomedical Engineering, vol. 58, no. 7, 2011, doi: 10.1109/TBME.2010.2102758.

- [7] M. A. Rosa and S. H. Lisanby, "Somatic Treatments for Mood Disorders," Neuropsychopharmacology, vol. 37, no. 1. 2012. doi: 10.1038/npp.2011.225.

- [8] T. E. Schlaepfer, B. H. Bewernick, S. Kayser, B. Mädler, and V. A. Coenen, "Rapid Effects of Deep Brain Stimulation for Treatment-Resistant Major Depression," Biological Psychiatry, vol. 73, no. 12, 2013, doi: 10.1016/j.biopsych.2013.01.034.

- [9] S. W. Lee, K. S. Min, J. Jeong, J. Kim, and S. J. Kim, "Monolithic Encapsulation of Implantable Neuroprosthetic Devices Using Liquid Crystal Polymers," IEEE Transactions on Biomedical Engineering, vol. 58, no. 8, 2011, doi: 10.1109/TBME.2011.2136341.

- [10] "CRT-D Amplia MRITM Pacemaker," Medtronic. https://www.medicalexpo.com (accessed Oct. 08, 2021).

- [11] "Cochlear Implants A Modern Miracle." https://www.oticonmedical.com (accessed Oct. 08, 2021).

- [12] Lyndon da Cruz, "5-Year Results with a Retinal Prosthesis System." https://retinatoday.com (accessed Oct. 08, 2021).

- [13] D. Lulic, A. Ahmadian, A. A. Baaj, S. R. Benbadis, and F. L. Vale, "Vagus Nerve Stimulation," Neurosurgical Focus, vol. 27, no. 3, 2009, doi: 10.3171/2009.6.FOCUS09126.

- [14] "AlphaTM SCS System," Boston Scientific. https://www.bostonscientific.com (accessed Oct. 08, 2021).

- [15] "Restore Sensor DBS: Mein Schmerztagebuch," Medtronic. https://docplayer.org (accessed Oct. 08, 2021).

- [16] M. Maleki, A. Alizadehasl, and M. Haghjoo, Practical cardiology. Elsevier, 2017. doi: 10.1136/bmj.1.5187.1715.

- [17] "Neurochirurgen ETZ Implanteren Neurostimulator bij Eerste Nederlandse Patiënt." http://tilburg.com (accessed Oct. 07, 2021).

- [18] "Baylor Neuroscientist Awarded BRAIN Grant to Study DBS to Treat OCD," 2016. https://www.academic-med.com (accessed Oct. 07, 2021).

- [19] "Two-Year-Old Receives Deep Brain Stimulation Implant," Jul. 12, 2019. https://www.medgadget.com (accessed Oct. 07, 2021).

- [20] "Lead and Extension Kits for Deep Brain Stimulation Systems. Clinician's Manual," St. Jude Medical, 2017. https://manuals.sjm.com (accessed Oct. 07, 2021).

- [21] "Brio Neurostimulation System: Summary of Safety and Effectiveness Data," St. Jude Medical, 2015. https://www.accessdata.fda.gov (accessed Oct. 07, 2021).

- [22] "VerciseTM DBS Leads Directions for Use," Boston Scientific, 2018. https://www.bostonscientific.com (accessed Oct. 07, 2021).

- [23] "SenSight DBS Directional Lead," Medtronic. https://www.medtronic.com (accessed Oct. 07, 2021).

- [24] C. Hassler, T. Boretius, and T. Stieglitz, "Polymers for Neural Implants," Journal of Polymer Science, Part B: Polymer Physics, vol. 49, no. 1. 2011. doi: 10.1002/polb.22169.

- [25] J. K. Krauss et al., "Technology of Deep Brain Stimulation: Current Status and Future Directions," Nature Reviews Neurology, vol. 17, no. 2, 2021, doi: 10.1038/s41582-020-00426-z.

12 REFERENCES

[26] D. Chesnutt, "Basics of Pacemaker," 2015. https://slideplayer.com (accessed Oct. 07, 2021).

- [27] S. Elseroad, "It is Not Brain Surgery! My DBS Process Told in Pictures," 2016. http://itisnotbrainsurgery.blogspot.com (accessed Oct. 07, 2021).

- [28] H. C. F. Martens et al., "Spatial Steering of Deep Brain Stimulation Volumes Using a Novel Lead Design," Clinical Neurophysiology, vol. 122, no. 3, 2011, doi: 10.1016/j.clinph.2010.07.026.

- [29] B. A. Teplitzky, J. Xiao, L. M. Zitella, and M. D. Johnson, "Sculpting Neural Activation Using Deep Brain Stimulation Leads with Radially Segmented Contacts," 2013. doi: 10.1109/NER.2013.6695899.

- [30] M. Keane, S. Deyo, A. Abosch, J. A. Bajwa, and M. D. Johnson, "Improved Spatial Targeting with Directionally Segmented Deep Brain Stimulation Leads for Treating Essential Tremor," Journal of Neural Engineering, vol. 9, no. 4, 2012, doi: 10.1088/1741-2560/9/4/046005.

- [31] "Medtronic Acquires Sapiens Steering Brain Stimulation," NeuroNews International, 2014. https://neuronewsinternational.com (accessed Oct. 07, 2021).

- [32] M. Picillo and A. Fasano, "Recent Advances in Essential Tremor: Surgical treatment," Parkinsonism and Related Disorders, vol. 22, 2016, doi: 10.1016/j.parkreldis.2015.09.012.

- [33] B. Mimoun, V. Henneken, A. van der Horst, and R. Dekker, "Flex-to-Rigid (F2R): A Generic Platform for the Fabrication and Assembly of Flexible Sensors for Minimally Invasive Instruments," IEEE Sensors Journal, vol. 13, no. 10, 2013, doi: 10.1109/JSEN.2013.2252613.

#### CHIP-IN-TIP: HIGHLY INTEGRATED DBS PROBE

#### 2.1 Introduction

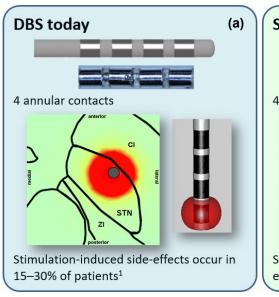

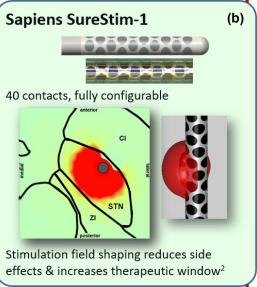

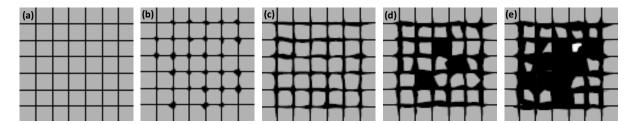

The application range for deep brain stimulation (DBS) devices is continuously widening. Neurologists worldwide are investigating the use of DBS for the treatment of new conditions going beyond physical impairments, such as Parkinson's disease or dystonia, to psychological diseases such as obesity, depression, or obsessive-compulsive disorder (OCD) [1]. The search for new applications is happening regardless of the fact that even the most advanced DBS leads available on the market are not yet able to precisely stimulate the targeted region in the brain without overstimulation of the surrounding tissue (Figure 2.1). Tissue overstimulation can lead to treatment failure and can cause serious side effects [2].

Figure 2.1: Brain stimulation patterns using DBS probe [3]. (a) Standard 4-contact DBS with cylindrical electrodes. Overstimulation of the internal capsule (CI) region in the brain is shown. (b) Directional 40-contact DBS with segmented oval electrodes precisely targeting the subthalamic nucleus (STN).

#### 2.2 Steerable brain stimulator (SBS) - Directional DBS

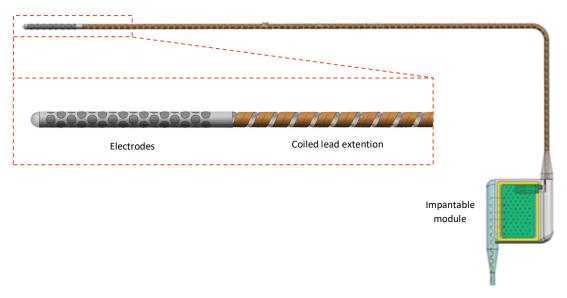

As a response to the omnipresent brain overstimulation with standard DBS devices, Sapiens has developed a high-resolution steerable brain stimulator (SBS) lead. It allows for adding directionality to the stimulation pattern of standard DBS devices (Figure 2.1). The SBS device incorporates up to 64 stimulation electrodes evenly distributed around the tip of the lead, a lead extension with forty coiled wires, an implantable module with electronics (multiplexing integrated circuit and capacitors), and an extension cord connecting the implantable module with an implantable pulse generator. Each circular electrode in the SBS device can be activated individually or in groups to achieve the best stimulation result [4]. Figure 2.2 illustrates several elements of the SBS device developed by Sapiens.

Figure 2.2: Directional Steerable Brain Stimulator (SBS) device with 64 individual electrodes, integrated coiled lead extension, and implantable module containing decoupling capacitors and multiplexing ASIC. Source: InForMed.

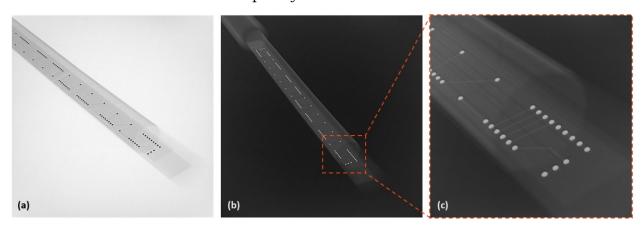

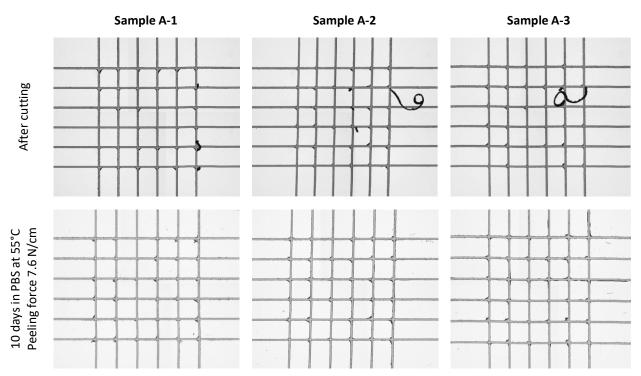

#### 2.2.1 Fabrication process

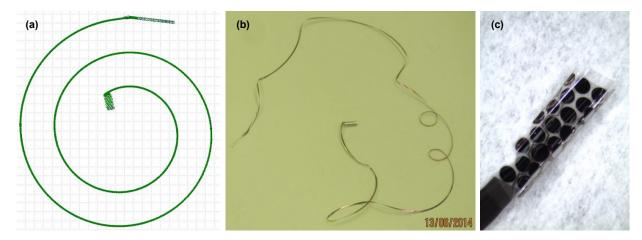

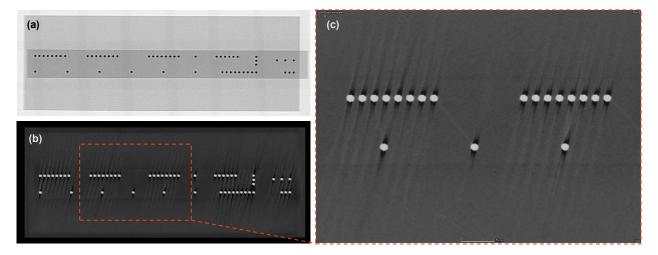

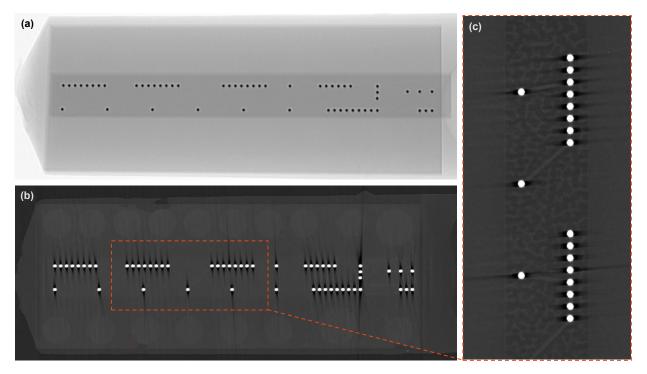

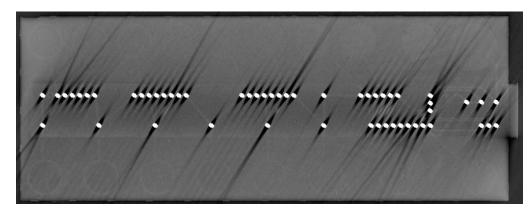

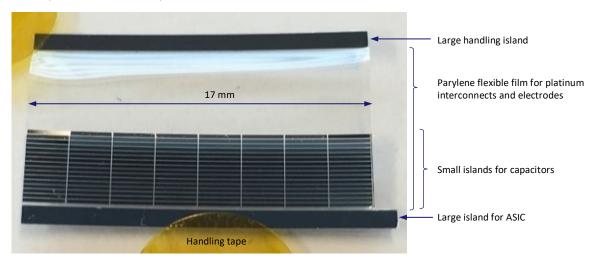

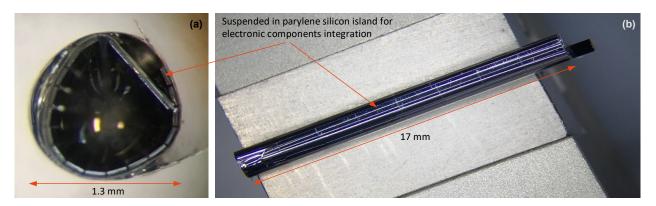

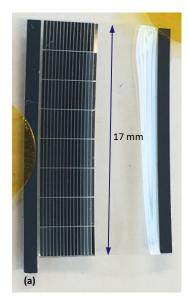

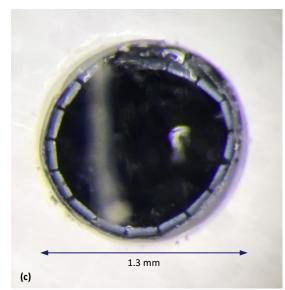

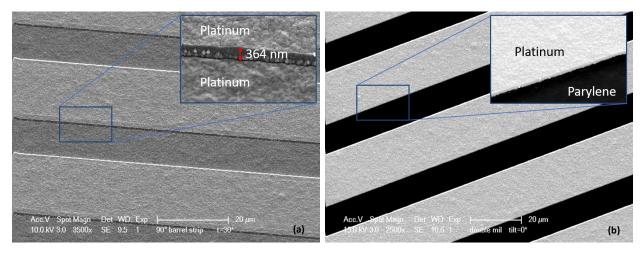

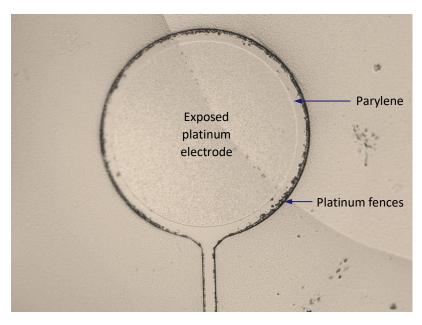

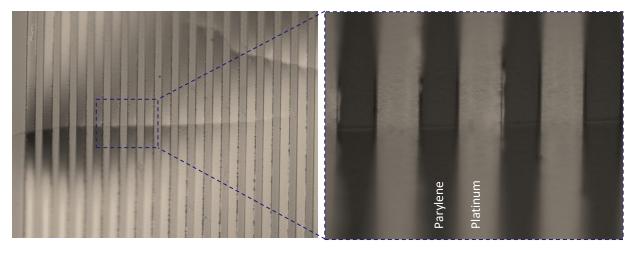

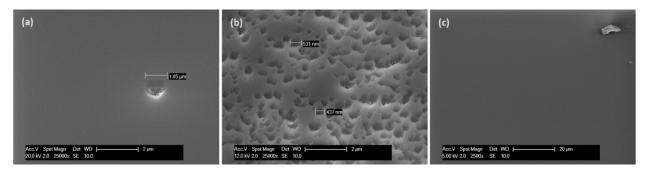

The current SBS lead is fabricated in a specially developed flat-film technology. The parylene-platinum-based flexible foil, later forming the lead, is fabricated on a silicon wafer using mostly techniques compatible with the standard IC microfabrication. A wafer transfer technique in combination with applying a sacrificial layer is used during the process to encapsulate the platinum-based metallization in parylene from both sides [3]. The finished wafer contains several leads attached to it using a sacrificial layer. Each lead comprises an approximately 50 cm long flexible foil with interconnects and 40 electrodes at its distal end (Figure 2.3a). At the end of the fabrication process, the leads are released from the wafer by dissolving the sacrificial layer in a suitable solvent (Figure 2.3b,c). Finally, the released lead is coiled and assembled into a long, round lead with a diameter of approximately 1.3 mm.

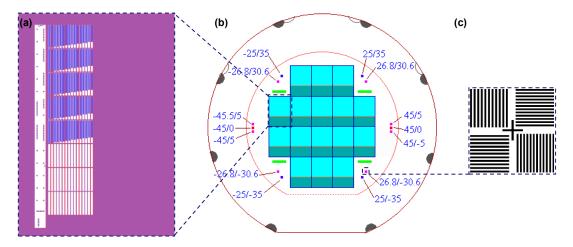

Figure 2.3: SBS lead composed of 40-electrodes and an integrated lead extension. (a) Device design and placement on a 6-inch silicon wafer. (b) Fabricated flexible device after release from the wafer. (c) Close up on the SBS tip containing 40-circular electrodes. Source: InForMed.

#### 2.2.2 Specifications

The SBS flat film technology enables fabrication and subsequent trial implantation of the high-resolution DBS lead. The therapeutic advances of directional stimulation, such as reducing side effects while maintaining the benefits of neurostimulation therapy, are evident. However, the SBS implant was never brought to the market due to the difficulties associated with connecting the 40-wire proximal end of the lead to the implantable module placed in the skull during surgery [5].

The thin-film fabrication process involves a rather costly and cumbersome wafer-transfer technique and a manual flexible foil release from the wafer. These methods reduce the yield of the manufacturing process. They are also not compatible with IC-microfabrication techniques, which prevents scaling-up of the production. Furthermore, besides a high resistance, the densely packed 40-track metallization compacted on a 1 mm wide and 50 cm long flexible foil makes the SBS lead fragile and prone to damage both during the assembly and during the implantation procedure.

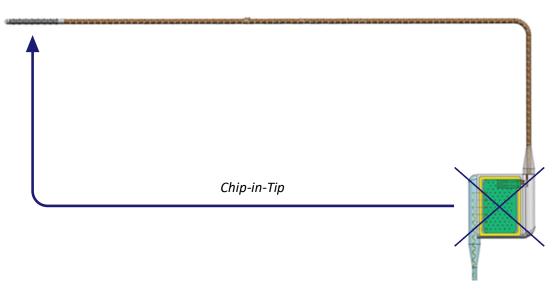

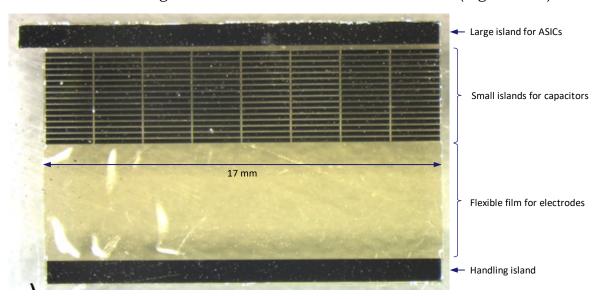

#### 2.3 Chip-in-Tip

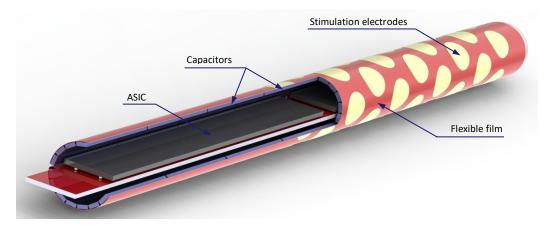

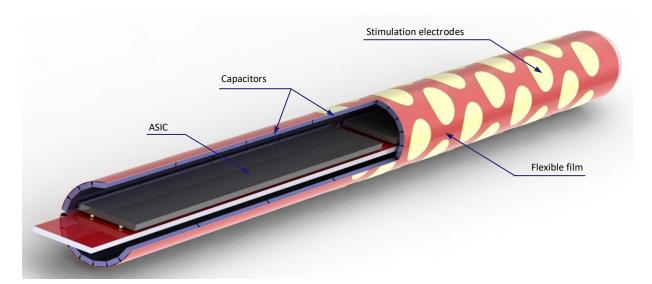

The issues associated with the multi-wire lead can be largely resolved by moving the electronics from the implantable module to the distal end of the lead – the *Chip-in-Tip* approach (Figure 2.4). After integrating the electronic components, such as multiplexing ASICs and decoupling capacitors on the tip of the SBS lead, the implantable module becomes redundant, and the 40-wire lead can be replaced with a simple, low wire count extension of the standard lead of the pulse generator.

Figure 2.4: Illustration of the Chip-in-Tip approach where electronic components such as multiplexing ASICs and blocking capacitors are moved from the implantable module to the tip of the DBS lead. The implantable module becomes redundant.

#### 2.3.1 Requirements

The Chip-in-Tip deep brain stimulation lead design must comply with a series of requirements set for the whole family of DBS devices. Like the standard DBS leads available on the market, it must have a round and stiff needle-like construction with a diameter of approximately 1.3 mm [6]. This will enable precise and possibly low invasive implantation using surgical tools already available on the market.

Next, the exterior part of the lead that is in contact with the human body must be made of biocompatible and biostable materials that are approved by the Food and Drug Administration (FDA) for use in long-term implantable medical devices [7]. It is highly recommended to only use biocompatible and biostable materials inside the implant to protect the body against harmful substances if the soft encapsulation layer fails.

16 CHIP-IN-TIP

Furthermore, the safety of the brain tissue stimulation must be secured. Each stimulation electrode is equipped with a blocking capacitor placed in series, usually between the electrode and the multiplexing ASIC. The decoupling capacitor blocks any potentially harmful DC voltage from reaching the brain tissue but allows the AC signal with a specific frequency and voltage (approximately 60-80 Hz and 3 V) to stimulate the brain [8].

On top of the requirements set for the standard DBS device, the Chip-in-Tip design must also meet the needs of directional DBS devices such as the SBS lead. Stimulation directionality must be ensured by incorporating a multitude of electrodes at the approximately 1 cm long distal end (tip) of the lead [9]. The 1 cm long tip of the lead ensures proper implantation into the targeted subthalamic nucleus (STN) with a maximum dimension of approximately 8.5 mm [10]. The electrodes, usually circular or oval, should be distributed evenly around the circumference of the lead. Besides fulfilling the manufacturing requirements, the difficulties connected with the multi-wire extension lead should also be addressed by replacing the complex lead extension with a simpler one with a low wire count (below ten wires).

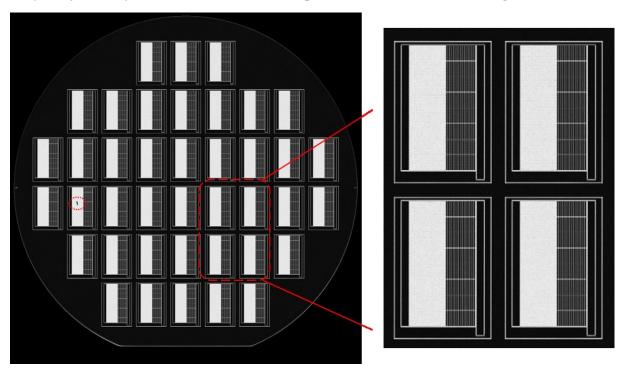

Finally, the method selected for lead manufacturing should be scalable and compatible with high-yield production. Techniques such as the manual release of devices using dissolvable release layers should be avoided and replaced by scalable manufacturing methods.

#### 2.3.2 Concept

In the Chip-in-Tip concept, *the chip* (ASIC) is integrated directly into *the tip* of the DBS lead. As a result, the number of interconnects in the lead extension can be limited to a few power and signal wires, regardless of the number of integrated electrodes. A consequence of moving the chip to the tip is that now also the DC blocking capacitors, placed between the ASIC and the electrodes, have to be integrated into the tip.

Figure 2.5: A 3D model of the Chip-in-Tip concept incorporating two ASICs (chips) and eighty blocking capacitors inside the tip of the 40-electrode DBS probe.

In the Chip-in-Tip approach, the Flex-to-Rigid (F2R) platform is employed to fabricate a semi-flexible structure into or onto which electronic components can be integrated using monolithic processes [11]. The F2R is a wafer-based, IC-compatible microfabrication process that allows for the fabrication of structures composed of silicon islands connected with flexible interconnects. The starting silicon wafer can already include

structures, such as high-density trench-based PICS3 capacitors [12] that are prefabricated in designated areas of the wafer. The stimulation electrodes can be integrated with the flexible interconnects forming the top layer of the device. After device fabrication, additional electronic components, such as the thinned-down ASICs, can be assembled onto the silicon islands, for example, by using flip-chip. The device with integrated electronics can then be folded into the needle-like shape of the DBS probe and filled with biocompatible silicone to form the DBS lead with 40 electrodes, distributed around its circumference (Figure 2.5).

In order to realize the Chip-in-Tip DBS concept, additional research of the presented technologies and methods is needed. The following topics are investigated in the subsequent sections of this chapter:

- The semi-flexible F2R structure design that enables accommodation of the ASICs and blocking capacitors in the DBS tip (Section 2.4).

- The biocompatible materials, suitable for implantable electronics that can replace the polyimide and aluminum-based interconnects used in the current F2R process (Section 2.5).

- The biocompatible ASIC mounting method (flip-chip) that can be performed on a substrate containing polymer-based interconnects and does not use potentially toxic or degrading materials for stud bumps (e.g., solder or gold) or as underfill (Section 2.6.1).

- The methodology for pre-integration of the blocking capacitors in the silicon starting substrate and the subsequent separation of the silicon islands containing the components using the F2R process with improved resolution (Section 2.6.2).

- The wrapping of the assembled device into a needle-like cylinder and its subsequent filling and encapsulation using biocompatible materials suitable for long-term implants (Section 2.7).

#### 2.4 DIRECTIONAL DBS – THE CHIP-IN-TIP DESIGN

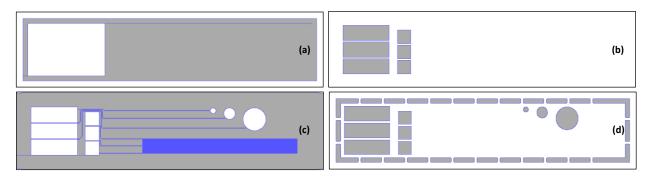

During the F2R-based design of the Chip-in-Tip DBS lead, both the 2D wafer architecture and the 3D shape of the lead after rolling had to be simultaneously taken into account from an early stage of the development. For each design feature, such as the distribution of the electrodes, the number and shape of the capacitor islands, the fabrication-related 2D design aspects, and the performance-related 3D design aspect were carefully evaluated.

In this section, first, the Chip-in-Tip DBS design process is described. Special attention is paid to the placement of the components on the 2D structure. Next, the potential fabrication flow is presented.

#### 2.4.1 Electrode placement and distribution

The developed DBS concept was modeled on the 40-electrode SBS device. The incorporated 40 round electrodes, each with a diameter of 0.7 mm, have a surface area of approximately 0.4 mm<sup>2</sup> following the design optimized by Sapiens. They are distributed evenly over the 5 mm wide and 10 mm long area that is later forming the 1.3 mm diameter probe (Figure 2.6a,b). To enhance the stimulation directionality, the electrodes are organized in a diagonal checkerboard pattern with ten rows, each containing four electrodes. After wrapping the device around the tip, the four electrodes will be evenly distributed around the circumference of the probe (Figure 2.6c).

Figure 2.6: The Chip-in-Tip DBS device showing the placement and distribution of the forty stimulation electrodes. (a) In a single-wrap DBS concept. (b) In a double-wrap DBS concept. (c) In a rolled-up state.

#### Single-wrap design

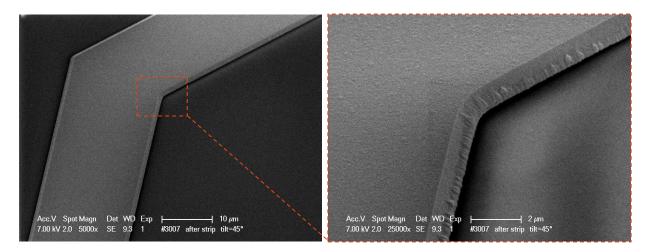

In the early stage of the design, the electrodes were placed directly above the segmented capacitor islands. The round shape of the probe was achieved in a single wrap, and it exploited the interlocking design of the capacitors (Figure 2.6a). However, during the single-wrap design detailing, several issues and concerns were identified:

- Placement of the electrodes directly on top of the capacitors limits their curvature in the final, wrapped state. The surface of the electrodes will follow the bends determined by the number of capacitor islands distributed around the circumference of the probe.

- The interlocking capacitor island design hinders the placement of capacitors in all the designated areas of the silicon wafer, especially in the small islands at the seam of the probe. Moreover, the presence of rigid silicon islands at the seam makes it difficult to precisely fold the device in a closed cylindrical shape without the risk of forming an approximately 80 µm gap reflecting the device layer thickness.

- The single-wrap design requires a complex design of the metallization running from the capacitors to the electrodes. Interconnects meander between the electrodes that occupy most of the available area. Therefore, their width and pitch are limited, resulting in a high interconnect resistivity.

#### Double-wrap design

To mitigate the issues mentioned above, the double-wrap design was developed (Figure 2.6b). In this approach, the electrodes are placed on a flexible film area extending to the right from the area with capacitor islands. The device is assembled into a cylindrical shape by wrapping the semi-flexible structure twice around the 1.3 mm circumference of the probe. During the first wrap, capacitors are evenly distributed around the circumference of the probe. During the second wrap, the electrodes are distributed over the capacitors. The separation of electrodes from the capacitors in the double-wrap design enables:

- Rounder surface of the electrodes and thus the whole probe.

- More straightforward capacitor islands design and distribution, which maximizes usage of the available surface area.

- Easier and more robust assembly, which eliminates the risk of gap forming at the seam of the probe.

- More relaxed metallization design with wider and thus more reliable and easier to manufacture interconnects.

Additionally, the double-wrap design makes it much easier to modify the shape and size of the electrodes or even enables the adding of extra electrodes for sensing purposes in the flexible area. Moreover, the relaxed metallization design permits using a single metallization layer to form the electrodes and interconnects.

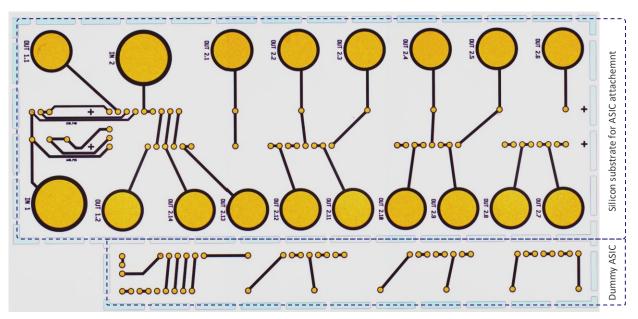

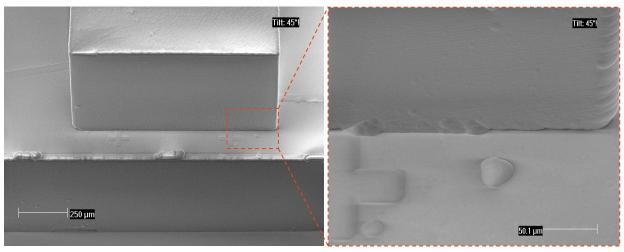

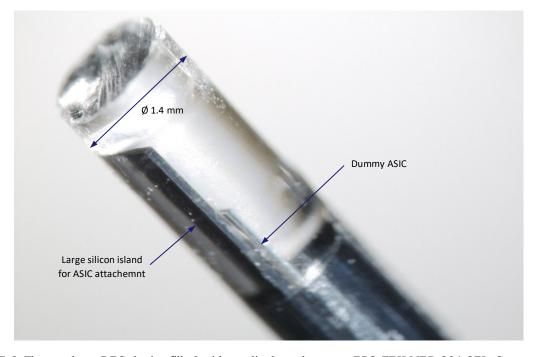

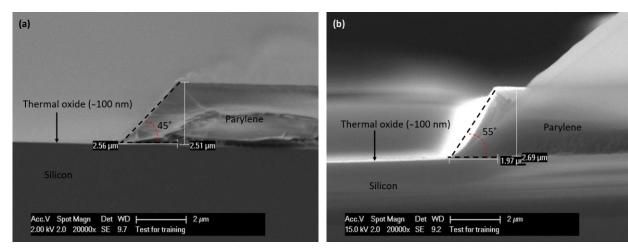

#### 2.4.2 ASIC integration

The most important element of the Chip-in-Tip design is the ASIC integration. The chip must be flip-chipped onto the designated silicon island of the F2R-structure using platinum bond pads with a diameter of 75  $\mu$ m. The island with the mounted chip must be folded inside the DBS probe cylinder (Figure 2.5), so the width of the silicon island holding the ASIC is limited to a maximum of 1 mm, and the ASIC thickness must not exceed 100  $\mu$ m. The silicon island with mounted ASIC is folded to the inside the tip at the bending radius of approximately 55  $\mu$ m.

After the discussion with project partner Medtronic and ASIC manufacturer ICSense, it was concluded that two ASICs with a length of approximately 8 mm and a width of 1 mm are needed to be able to operate all the electrodes individually. Chips with these dimensions can still be thinned down to  $100\,\mu m$  while maintaining sufficient mechanical strength for handling.

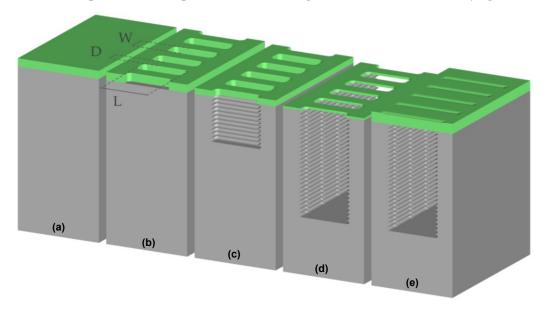

#### 2.4.3 Capacitors spatial distribution

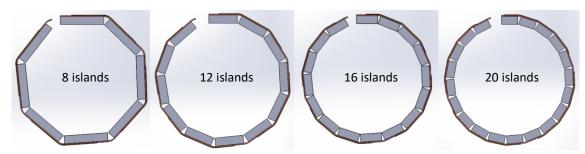

One of the first 3D-design considerations was the distribution of the silicon islands for the decoupling capacitors. On the one hand, increasing the number of islands around the circumference makes the probe rounder and more friendly for tissues (Figure 2.7). On the other hand, the design of the capacitors in PICS3 technology requires specific island dimensions. First, a silicon island thickness of 80 µm was chosen based on the selected trench capacitor technology requirements. Next, the length and width of the islands were determined to ensure adequate offset from the edge of the island, ensuring high-yield fabrication and sufficient mechanical strength [13].

Figure 2.7: Selected designs of capacitor islands number and their distribution around the DBS probe influencing the device roundness.

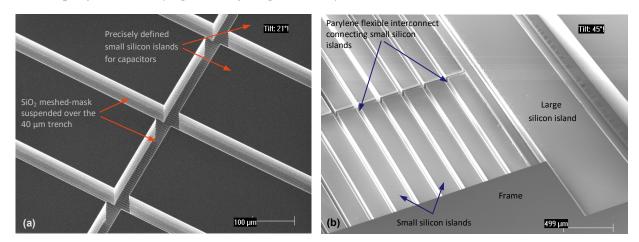

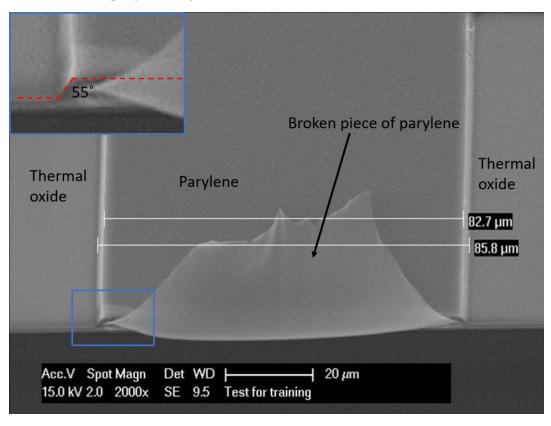

The most optimal distribution of the capacitor islands, resulting in the best compromise between the PICS3 design restrictions and the roundness of the probe, was achieved by using 16 islands. The individual islands have a width of 210  $\mu m$ , and they are physically isolated with 40  $\mu m$  wide trenches. The width of the trench ensures that the capacitors do not touch each other after the device wrapping into the 1.3 mm diameter probe. The physical separation is more space-efficient than isolating the capacitors using junction isolation. The number of islands around the circumference is limited to multiples of four to comply with the number of electrodes per row. In the Chip-in-Tip DBS design, the length of the islands is matched with the length of two rows of electrodes (2070  $\mu m$ ). Two capacitors, connected in parallel, are assigned to each of the eight electrodes. This allows for a simple metallization pattern with relatively short interconnects.

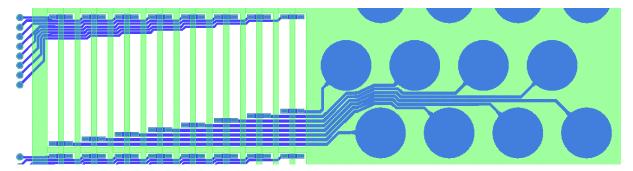

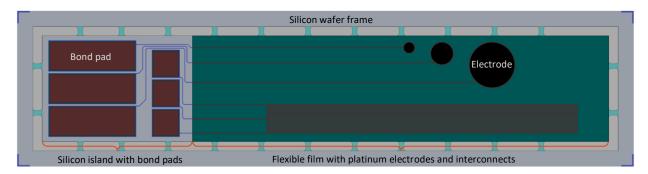

#### 2.4.4 Final design

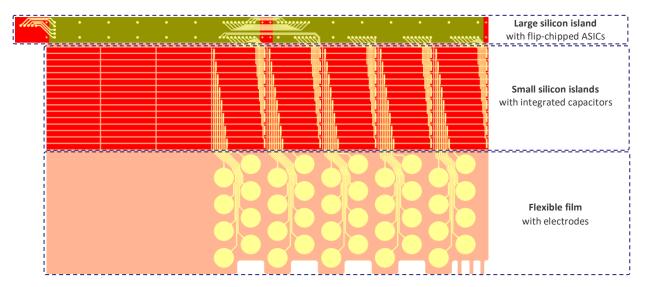

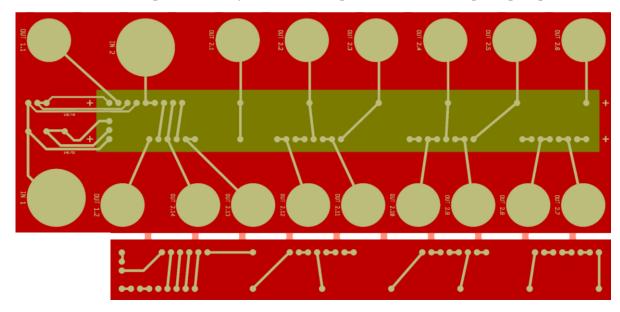

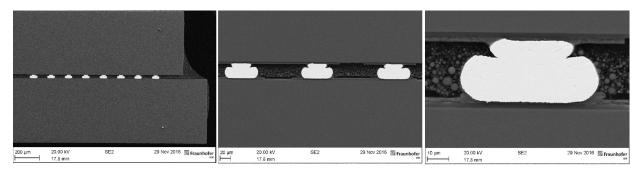

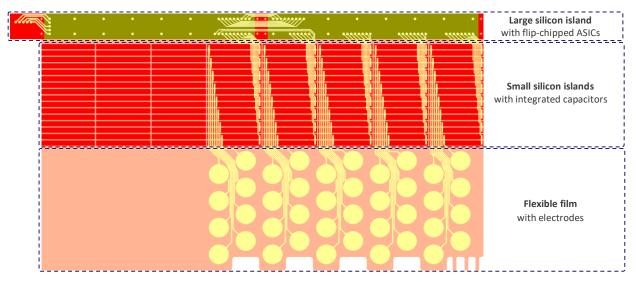

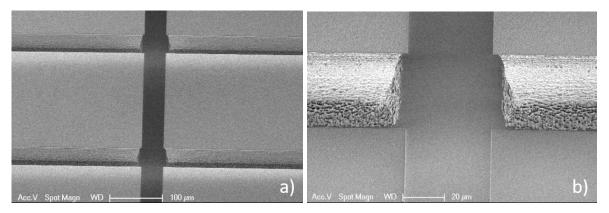

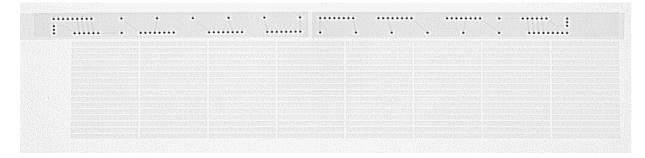

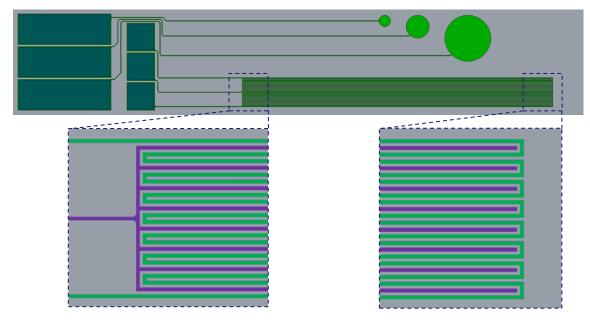

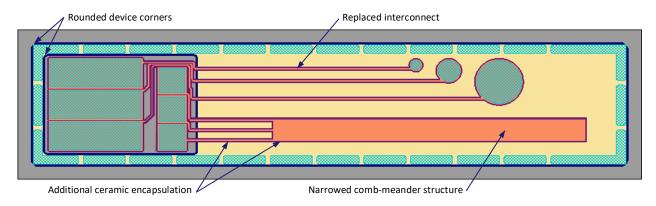

The final Chip-in-Tip DBS design is shown in Figure 2.8. The length of the DBS structure is 18 mm to be able to accommodate the two ASICs. The design comprises one large silicon island, 128 small silicon islands, and a flexible film area.

Figure 2.8: The 2D representation of the 40-electrode DBS design with integrated electronic components. The large silicon island (18 mm x 1 mm) contains the flip-chipped ASICs (green). The small silicon islands (210  $\mu$ m x 2070  $\mu$ m) are separated with 40  $\mu$ m wide trenches and accommodate prefabricated decoupling capacitors (red). The flexible film (17 mm x 5 mm) contains 40 flexible electrodes (yellow).

The ASICs are mounted onto the large (1 mm x 18 mm) silicon island. The island extends beyond the semi-flexible structure. On the extended part, bond pads are placed that will be used to connect to the lead extension after the device assembly into a cylinder-shaped probe.

The middle part of the DBS structure is filled with 128 small silicon islands separated by 40  $\mu$ m wide trenches. The islands are organized in 8 rows of 16 structures. The first five rows (80 islands) are meant for accommodating blocking capacitors. The last three rows of small silicon islands have been added to ensure the conformal shape of the rolled-up probe over its entire length.

The flexible film area contains 40 embedded stimulation electrodes with a diameter of 0.7 mm. The electrodes are distributed in a checkerboard pattern over ten rows, each one containing four electrodes. The end of the flexible film is patterned so that it does not cover any of the electrodes.

All the structures are connected with the flexible interconnects embedded in the flexible film. The individual interconnects run from the large silicon island, through the small silicon island, down to the electrodes. A set of bond pads and interconnects is also designed on the large silicon island to provide an assembly location for the lead extension and the ASICs, and to ensure communication between the chips.

The entire Chip-in-Tip structure, including bond pads, electrodes, and interconnects, is realized using a single metallization layer.

#### 2.4.5 Fabrication flowchart

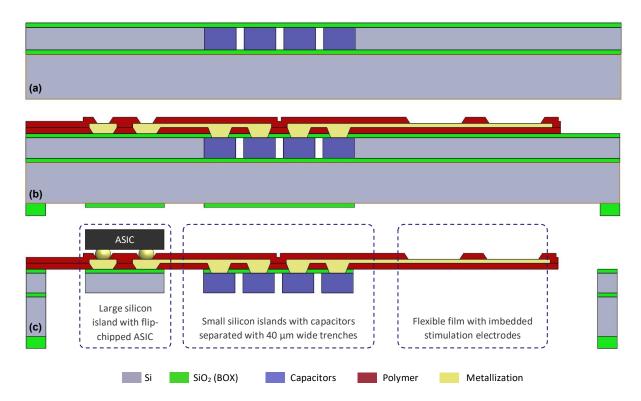

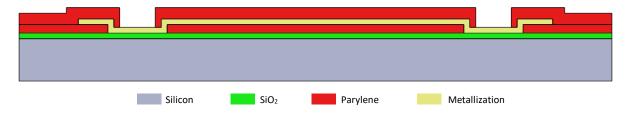

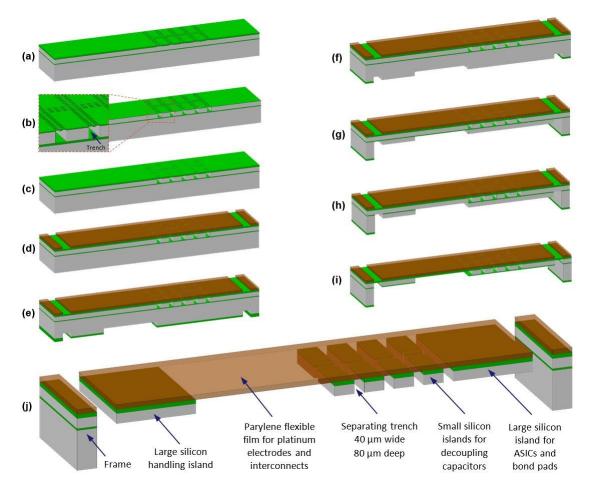

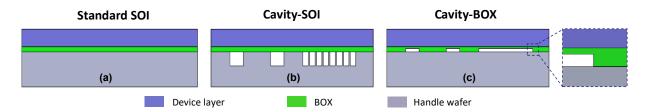

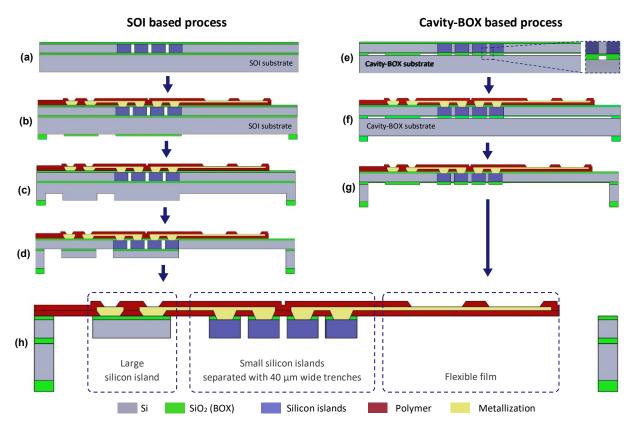

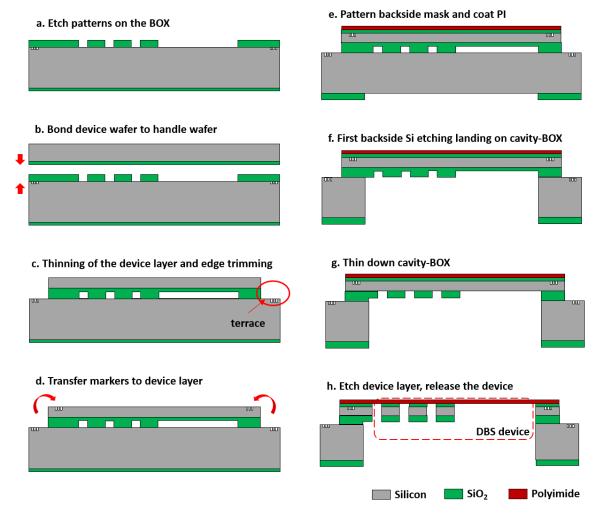

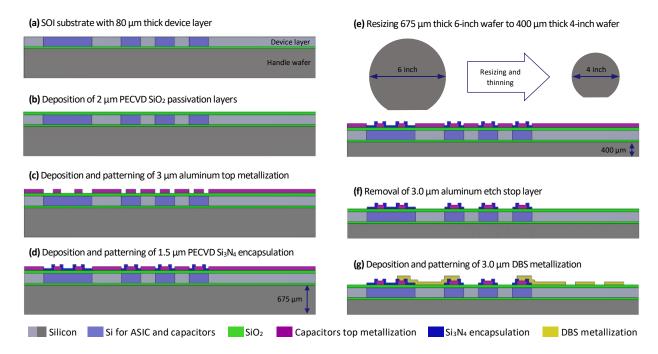

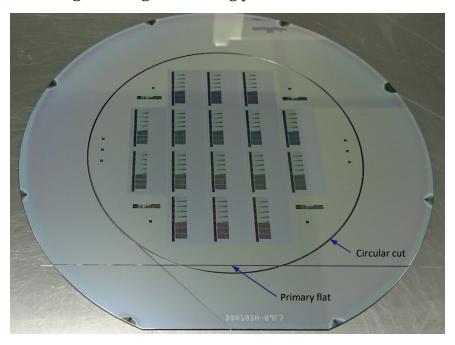

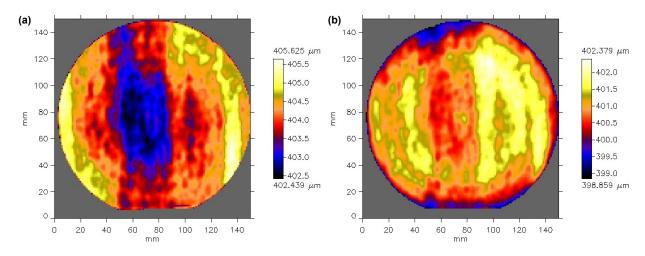

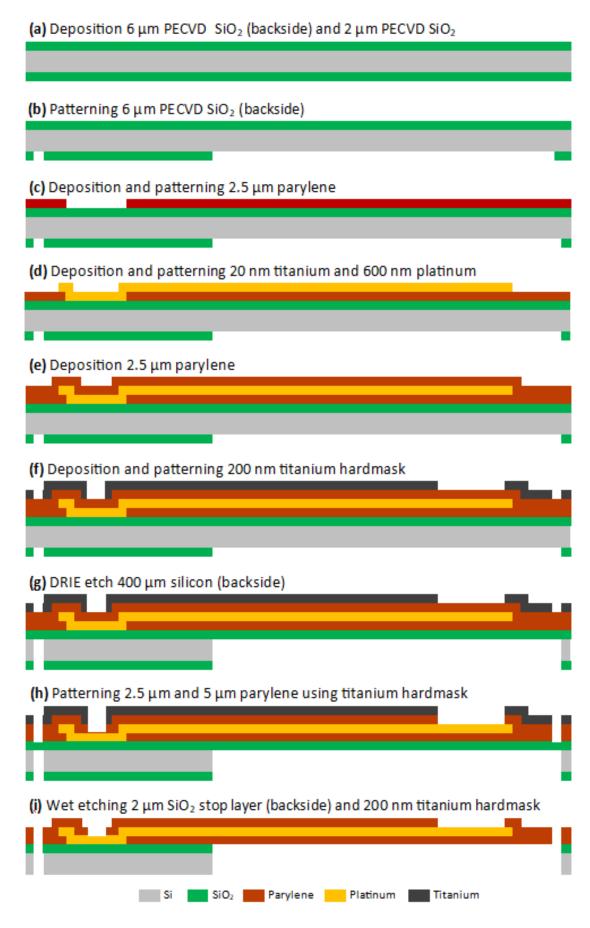

The F2R-based fabrication flow for manufacturing the final Chip-in-Tip DBS device is shown in Figure 2.9. A uniform thickness of all the silicon structures is ensured by using SOI substrates with an 80 µm thick device layer.

Figure 2.9: The simplified manufacturing process of the Chip-in-Tip DBS probe. (a) Fabrication of the trench capacitors on an SOI substrate with an 80  $\mu$ m thick device layer. In this flow, the structures are separated using sealable trenches. (b) Fabrication of the flexible film containing 40-stimulation electrodes, flexible interconnects, and a series of bond pads for ASIC attachment. (c) Device thinning and release using the F2R-based backside-DRIE process.

#### Capacitor prefabrication

The fabrication starts at the foundry of InForMed partner Murata by manufacturing the trench capacitors in the designated area of the device layer. Next, the substrates with prefabricated components are transferred to the EKL cleanroom, where the capacitors are isolated with 40  $\mu$ m wide and 80  $\mu$ m deep trenches (Figure 2.9a).

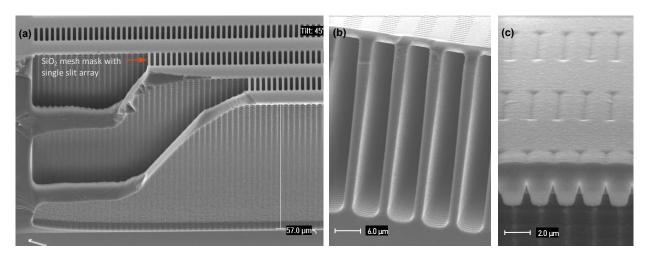

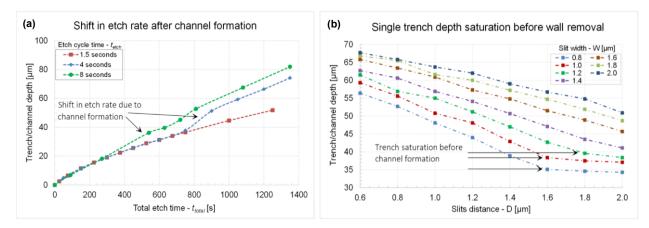

#### Capacitor separation

In this flowchart, the structures are separated in a front-side DRIE process, during which trenches are etched through a meshed  $SiO_2$  mask [14]. The trenches are subsequently sealed with a PECVD  $SiO_2$  layer to allow for further wafer-scale processing.

#### Flexible film fabrication

Next, a flexible film (approximately 10 µm thick) with embedded interconnects and electrodes is fabricated (Figure 2.9b). It is composed of two equally thick layers of parylene sandwiching metallization pattern in the stress-neutral plane.

#### Device thinning and release

Next, the semi-flexible DBS device is thinned down, and the flexible film is released (Figure 2.9c) in a two-step backside DRIE process [14]. After etching, the finished devices remain suspended in the wafer by means of flexible tabs. Thanks to this, the ASICs can be flip-chipped onto the designated silicon island in a wafer-based process. During flip-chip, the risk related to individual device handling can be minimized by automated pick-and-place equipment. Subsequently, the assembled DBS device can be removed from the wafer by laser cutting the flexible tabs.

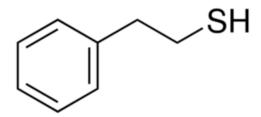

#### 2.5 BIO-COMPATIBLE MATERIALS FOR IMPLANTABLE DEVICES

The Chip-in-Tip DBS device and its fabrication flow were designed using the Flex-to-Rigid (F2R) technology. Hoverer, the current F2R platform is built on aluminum-polyimide-based flexible interconnects. Neither aluminum, which is prone to corrosion, nor polyimide are recommended for usage in implantable devices by the Food and Drug Administration (FDA). In order to realize the Chip-in-Tip design, the materials used to fabricate the flexible interconnects must be replaced with ones that are biocompatible, biostable, and certified for use in long-term neural implants.

#### 2.5.1 Flexible film

There is a number of polymers that are considered suitable for minimally invasive neural implant interfaces. The most common are polydimethylsiloxane (PDMS) and polymonochloro-p-xylene (parylene C) [15]. In this work, parylene C, further called parylene, was selected as the most suitable flexible film material. It is currently one of the most commonly used polymers to produce and encapsulate minimally invasive biomedical devices. Parylene is also commercially available, and it has the FDA approval with UPS Class VI biocompatibility [15][16][17][18].

#### Parylene properties

Parylene has excellent electrical and moisture barrier properties, and it is chemically and biologically inert. It also shows significantly lower permeability to gas and water compared to alternative biocompatible polymers such as PDMS [19]. Additionally, it has a low moisture absorption percentage below 1%. Furthermore, polymer-based implant soft-encapsulation is less stiff than the traditional metal-based casing, which improves the structural biocompatibility of the implant by reducing the mechanical mismatch between the device and tissue [15]. Some properties of parylene are listed in Table 2.1.

| Table 0 1  | Calastad | menantian | of namilana |    |

|------------|----------|-----------|-------------|----|

| 1uble 2.1. | seiecieu | properues | of parylene | C. |

|            |          |           |             |    |

| <b>Material Properties</b>        | Parylene C                 |

|-----------------------------------|----------------------------|

| Tensile strength (MPa)            | 69 1,2                     |

| Elongation at break (%)           | 200 1,2                    |

| Moisture absorption (%)           | 0.06-0.6 3                 |

| Young's Modulus (GPa)             | 3.2 4                      |

| Dielectric coefficient at 1kHz    | 3.1 1,2                    |

| Resistivity (Ω*cm)                | 6-8.8·10 <sup>16</sup> 1,2 |

| Refractive index                  | 1.639 1,2                  |

| Melting point (°C)                | 290 1,2                    |

| Glass transition temperature (°C) | 80-100 2                   |

$<sup>{}^{1}\</sup>text{Specialty Coating Systems, Parylene C [20]; }{}^{2}\text{PCT Parylene Properties [21]; }{}^{3}\text{Jeong, 2012 [22]; }{}^{4}\text{Noh, 2004 [23]}$

In the deposition chamber, all the exposed surfaces are coated with a layer of parylene with a uniform thickness. The final layer thickness is determined by the amount of used substrate (dimer) and the exposed surface in the deposition chamber. The process and tool can be tuned to achieve layer thicknesses ranging from several microns to hundreds of microns in a single deposition. The layer is highly conformal with excellent step coverage, and it is pinhole-free and stress-free [16][24].

#### Parylene deposition

Parylene is deposited using a chemical vapor deposition (CVD) process. First, a dimer substrate (para-xylene) is sublimated in a vaporizer at 150°C in close to vacuum conditions. The dimer gas flows into a pyrolysis furnace set between 690°C, where the dimer structure is turned into vapor saturated with monomer. Next, the vapor passes to the deposition chamber, where the polymerization occurs at room temperature and at a pressure of 30-50 mTorr [25][26].

#### Parylene in microfabrication cleanroom

Even though parylene is commonly applied in bioelectronics, it is still a relatively new material in a microfabrication cleanroom. Most applications use parylene as an encapsulation layer deposited at post-processing stages, which does not require further device processing in the cleanroom. The layer itself can be introduced in the cleanroom facility without major issues as it does not generate particles nor leaves residues in the tools [17].

However, particles can be generated during the tool preparation for the deposition process and when using standard surface masking techniques (such as masking tapes) to locally prevent parylene deposition. Therefore, the masking techniques must be replaced by cleanroom-friendly methods for selective parylene deposition, and, for the time being, the deposition must occur in an isolated, cleanroom-like space. In the future, a cleanroom-compatible parylene deposition tool should be considered [27].

The next step after introducing the parylene into a microfabrication cleanroom is the development of parylene compatible processes. For the monolithic fabrication of the parylene-platinum-based flexible interconnects that are present in the DBS design, several processing steps (discussed in detail in Chapter 6) must be optimized or developed from scratch:

- A local (one-side) parylene deposition technique,

- A selective and controlled parylene pattering method,

- Cleaning procedures suitable for wafers containing parylene layer,

- Parylene-compatible processing (e.g., <100°C) of the other layers present in the device (e.g., deposition of platinum on top of the parylene and its further patterning),

- Excellent adhesion between the layers of the parylene-based stack.

#### 2.5.2 Metallization

The Chip-in-Tip DBS design assumes a single metallization used for the fabrication of the electrodes, interconnects, and bond pads. Therefore, the selected metallization material and properties must comply with the requirements set for all of these components.

#### **Electrodes**

The electrodes are in direct contact with tissue and can significantly influence the performance of the device. Therefore, the selection of the electrode material is mainly driven by the requirements set for the stimulation electrodes. The stimulation electrodes must be biocompatible, biostable, and inert to the surrounding conditions in order to ensure safe and reliable stimulation. Besides, the electrodes must have good electrical and electrochemical properties such as high conductivity, good interface impedance, and charge delivery capacity to be able to deliver appropriate current to the stimulation side [5].

Currently, platinum is the most common material used for stimulation electrodes that make direct contact with tissue. This is mainly because of its high nobility, which makes the material biologically inert due to low reactivity and corrosiveness [28][29][30]. Platinum is also capable of constantly transferring stimulation charges to the tissue over an extended period [31]. Sometimes, a small fraction of iridium is added to the platinum alloy to improve the electrical properties of the metallization, such as charge storage capacity [32].

In this work, pure platinum is selected for the flexible interconnects and the electrodes. It can be straightforwardly deposited in contrast to the platinum-iridium alloys that require a highly optimized deposition process. Physical vapor deposition (PVD), also called sputter deposition, is used in this thesis to deposit a conformal platinum layer and to ensure a good metallization step coverage [33].

#### Interconnects

The most common materials for flexible interconnects used in implantable devices are gold and platinum or a combination stack composed of these materials [3][34]. In the combination stack, a micron-thick layer of gold (resistivity 2.44  $\mu\Omega$ ·cm [35]) serves as the main conductor, and a nanometer-thick layer of platinum (resistivity 10.5  $\mu\Omega$ ·cm [35]) serves as a biocompatible capping layer and to form the electrodes. This thesis explores a single-metallization approach. Therefore, only platinum is considered as metallization for the interconnects as well as the electrodes.

The resistivity of platinum is about five times higher than the resistivity of gold or aluminum (2.65  $\mu\Omega$ ·cm [35]). To compensate for the relatively low conductivity of the material, the width and thickness of the metal tracks should be maximized. The width is determined by design. The thickness of the interconnects is limited mainly by the flexibility of platinum, which has a relatively high Young's Modulus of 147 GPa [36] compared to aluminum with Young's Modulus of 69 GPa [36], which is used in the standard Flex-to-Rigid process.

#### Bond pads

The bond pads are located on the large silicon island, and they are formed in the same step as the other elements of the metallization (electrodes and interconnects). The bond pads are designed to enable flip-chip of the ASIC directly onto the semi-flexible DBS structure. The bond pads metallization must be thick enough to ensure good results during the bumping process [37].

In order to ensure the necessary flexibility and conductivity of the platinum-based flexible interconnects and sufficient thickness of the bond pads, the thickness of the platinum layer used in this thesis is limited to 600 nm. This thickness is also in line with the parylene-platinum-based interconnects used previously in the directional SBS device designed by Sapiens [3].

#### 2.6 Component integration

Two types of components have to be integrated into the tip of the DBS probe. These are the two multiplexing ASICs and eighty DC blocking capacitors. The integration processes are proposed in this subsection.

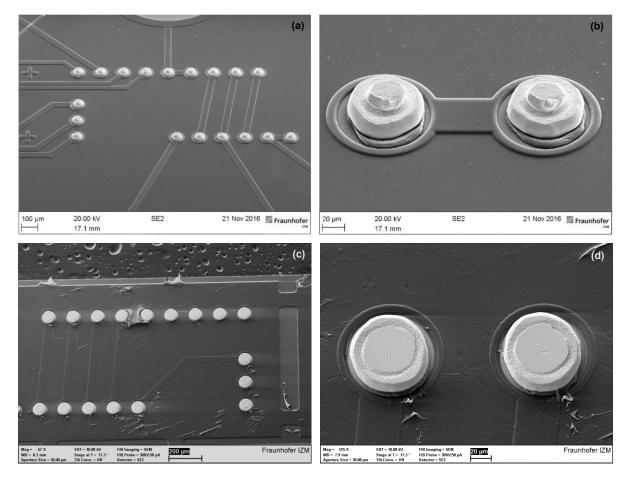

#### 2.6.1 ASICs integration

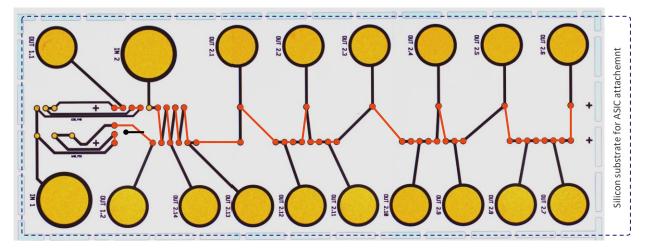

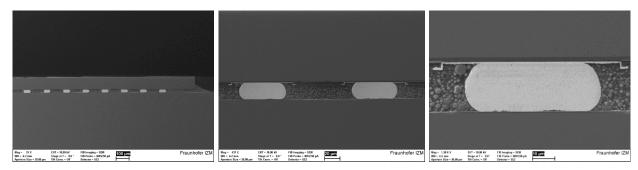

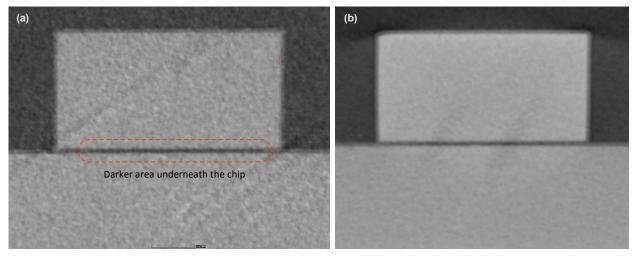

The two 1 mm wide, 8 mm long, and 100  $\mu$ m thick ASICs are flip-chipped onto a dedicated silicon island that contains an array of 600 nm thick platinum bond pads with a diameter of 75  $\mu$ m. For biocompatible flip-chipping, a platinum-based stud bumping process was developed, replacing the common solder or golden stud bumps.

The platinum-based flip-chip approach involves some challenging steps. For example, handling of the exceptionally thin and long ASICs and their attachment to the semi-flexible DBS structure requires practice and excellent manual skills. To ease the process, the flip-chip can be performed on a wafer level with the devices still attached to the wafer by means of the release tabs. A handle wafer with mirrored topography can be used to eliminate the height differences of the DBS structures.

Furthermore, some technological development of the flip-chip method itself is required. First of all, the temperature needed to perform stud bumping or chip bonding might exceed the temperature budget set for the parylene-containing substrate. Secondly, platinum is not a common material for flip-chip bumping. Therefore, a process for making well-adhering platinum stud bumps on platinum bond pads must be developed. Finally, extra attention must be paid to the chip underfill process. The underfill material must be fully biocompatible, and the process itself must be compatible with the parylene-based device.

The technological challenges and development points, such as fully platinum-based flip-chip or biocompatible underfill, have been investigated together with a project partner, Fraunhofer IZM. The results are discussed in Chapter 3.

#### 2.6.2 Capacitor integration

As mentioned before, the decoupling capacitors are fabricated by InForMed partner Murata in their PICS3 deep trench capacitor process. The wafers with capacitors are further processed in the DBS fabrication facility, EKL. The first challenge is the interfacility processing of the substrate. For this, a mutual design, a common alignment strategy, and compatible processing methods must be established. The strategy for a common product and process design and following feasibility study are discussed in detail in Section 4.5.

The next challenge is a precise separation of the prefabricated capacitors into islands (L x W x D: 2070  $\mu m$  x 210  $\mu m$  x 80  $\mu m$ ) by means of 40  $\mu m$  wide and 80  $\mu m$  deep trenches. In the standard F2R process, the islands are separated by 350  $\mu m$  wide trenches, etched from the backside of the wafer, that are only 50  $\mu m$  deep [11]. Two technologies have been developed to enable the capacitor integration process with the required narrow and deep trenches.

One method, described in Section 4.3, exploits a sealable trenches technology (Section 4.2) to define the silicon islands from the front side of the wafer and continue the wafer-level fabrication of the DBS structures after the trenches have been sealed. The other method employs a novel cavity-BOX SOI substrate. It allows for high-resolution device layer patterning during the backside DRIE process by using a pre-patterned hardmask formed in the buried oxide layer. The development of the cavity-BOX substrate and its application to the F2R process is presented in Section 4.4.

26 Packaging

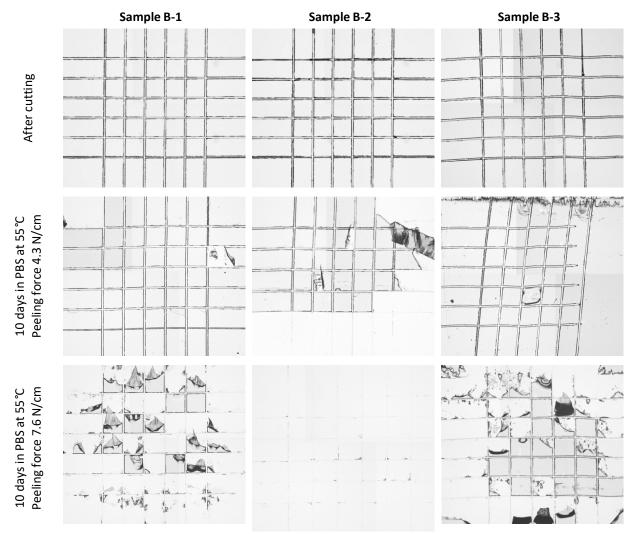

#### 2.7 PACKAGING

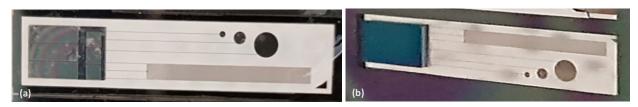

After fabrication, the flat DBS structure containing the integrated blocking capacitors and ASICs is suspended in a wafer frame. The structure still needs to be wrapped into a 1.3 mm diameter cylinder and packaged to form the final DBS lead. The following aspects of packaging are considered in this section:

- Device wrapping into a needle-like probe and consequent filling of the cylinder,

- Attachment of the lead extension to the microfabricated DBS tip,

- Final encapsulation of the DBS probe.

The device assembly into a complete system is not within the scope of this project. Instead, the focus is on the development of the device wrapping and filling technique. These topics are briefly introduced in this section and discussed in detail in the corresponding sections of Chapter 5. The other aspects of the packaging specific for the Chip-in-Tip DBS design, namely the lead extension attachment and final device encapsulation, are only briefly considered.

#### 2.7.1 Wrapping

The first stage of the packaging process is wrapping the DBS structure, with integrated capacitors and flip-chipped ASICs, into a probe with a diameter of 1.3 mm. In the case of rolled/wrapped devices such as the DBS probe, the most common practice is to use a thin titanium rod to which the device is attached and wrapped around it. The rod stays inside the device, and it becomes its structural element. The rod also ensures the stiffness of the device, which in the case of DBS probes, is crucial for proper device implantation.

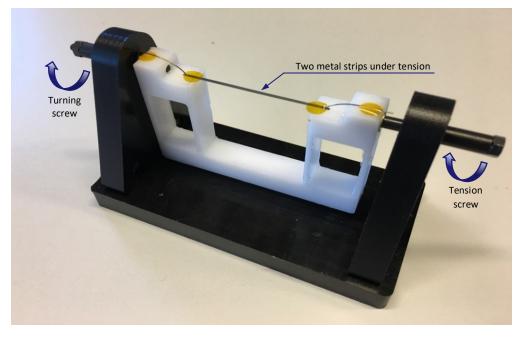

In the Chip-in-Tip design, the inside of the DBS device is occupied with the silicon island holding the ASICs. This implies that using a solid rod to wrap the device around it is not possible. Therefore, a custom tool has been designed to enable the wrapping of the device into a cylindrical shape (Figure 2.10). The tool enables fixing of the DBS device between two metal strips placed under tension, and wrapping of the device. Then, the tension is released, and the metal stripes are removed from the inside of the wrapped device. The tool and wrapping procedure are described in detail in Section 5.2.

Figure 2.10: Custom-designed tool for wrapping the DBS device into a cylinder-shaped probe. Source: PlnS.

In this method, there are no additional elements needed to wrap the DBS device into its needle-like shape. The two flexible layers of the double-wrap design are glued together using a thin film of biocompatible adhesive. The required stiffness of the DBS probe is ensured by the silicon islands distributed around its circumference and the cylinder filling material.

In general, the Chip-in-Tip DBS probe was designed so that the structures are self-aligning around the circumference during the double wrapping procedure. Several parameters of this manual process must be optimized in order to achieve the required shape and dimensions of the probe. For example, the transversal force applied to the device itself must be carefully adjusted not to cause damage to the device and yet to enable wrapping of the device into a closed cylinder with a properly closed ring of capacitors without overlapping the electrodes. The specific solutions and results for this procedure are presented in Section 5.2.

#### 2.7.2 Filling

After wrapping, the DBS device is hollow with a silicon island, holding the ASICs, floating inside the cylinder. The next step in the packaging process is filling the cylinder with a biocompatible material. From the construction point of view, the filler has to ensure the required device stiffness and mechanical strength by filling the cylinder and fixing all the loose elements. On top of that, the filling material must be biocompatible and suitable for application in long-term implantable devices. Finally, the filler must be thin enough to flow into all the voids inside the cylinder, also the hard-to-reach spaces between the capacitor islands.

Currently, the most common biocompatible filler used in DBS probes is silicone rubber (PDMS) [38]. To properly fill the DBS device, a relatively thin filler must be applied, possibly in combination with modern filling methods, such as injection molding or a vacuum centrifuge process. Silicon rubber tends to be too viscous (e.g., medical-grade silicon rubber 115 Pa·s [39]) to be able to fill the narrow spaces, such as the <40 µm gaps between the capacitors. Therefore, in Section 5.3, a medical-grade epoxy (viscosity from 0.1 to 0.2 Pa·s [40]) is tested as an alternative filling material for the DBS devices.

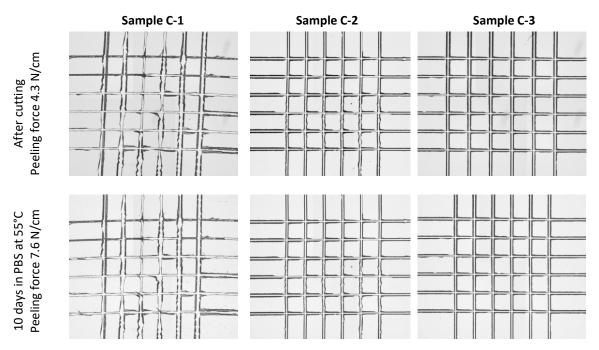

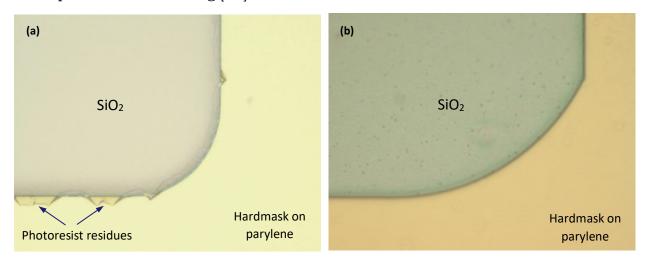

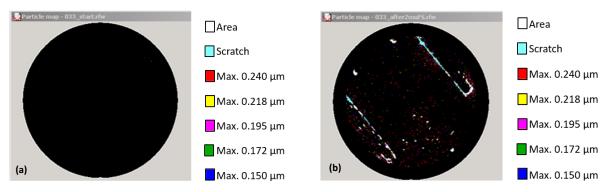

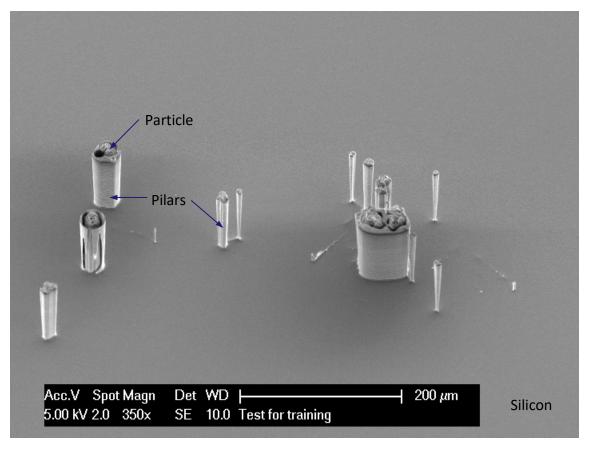

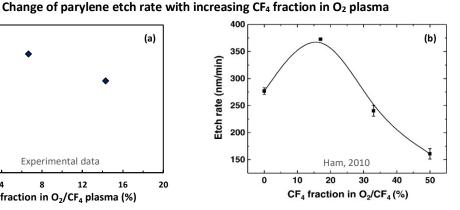

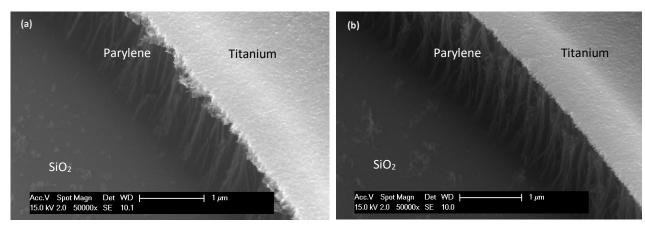

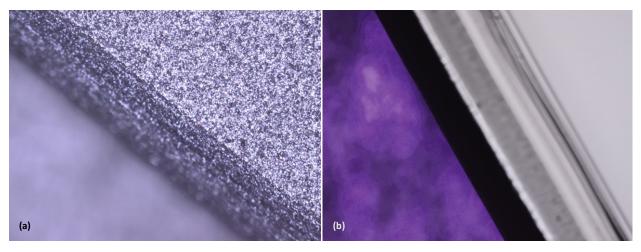

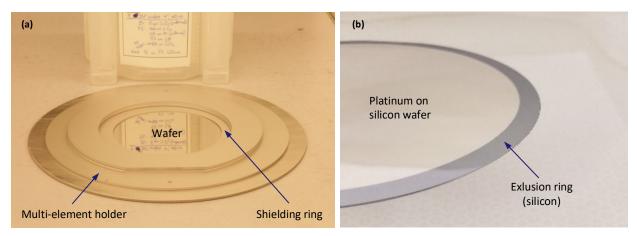

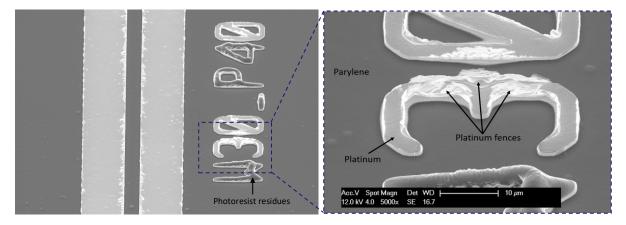

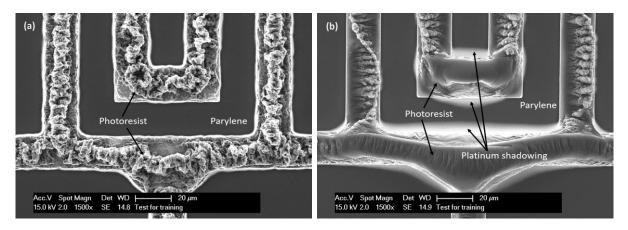

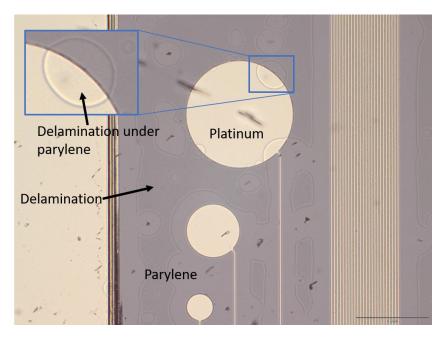

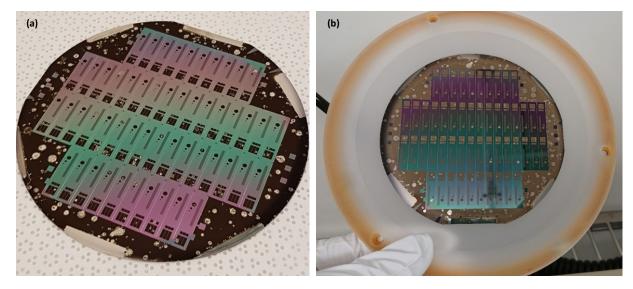

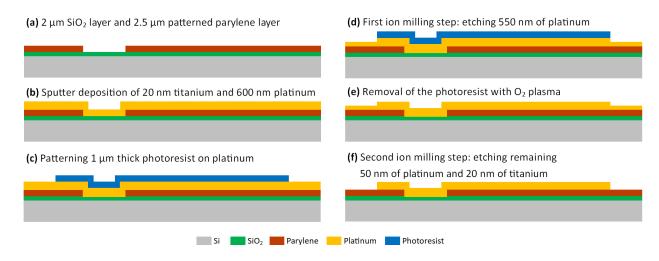

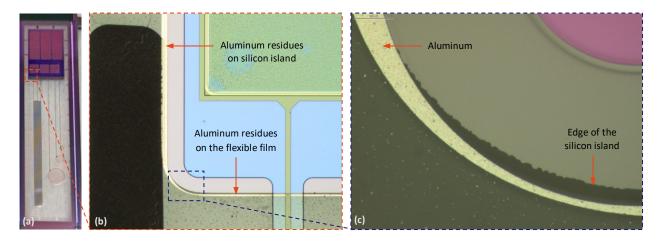

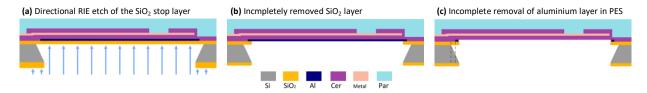

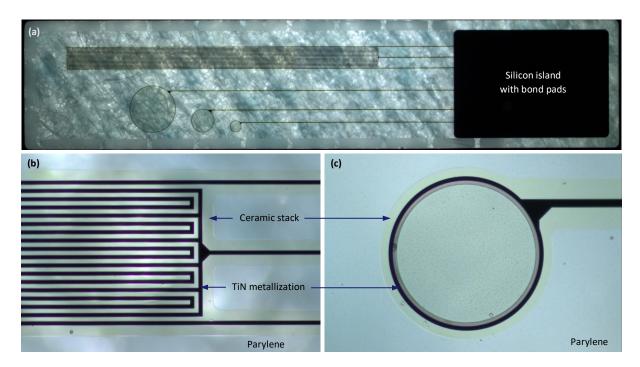

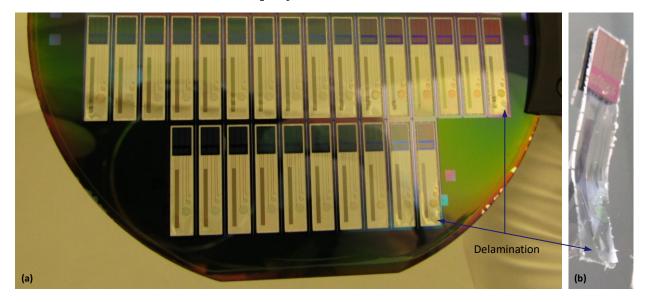

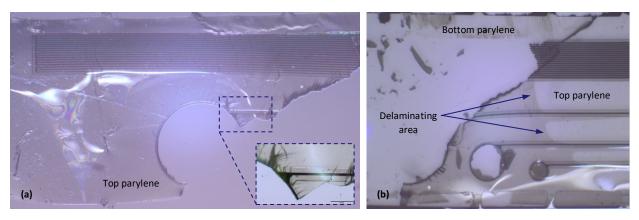

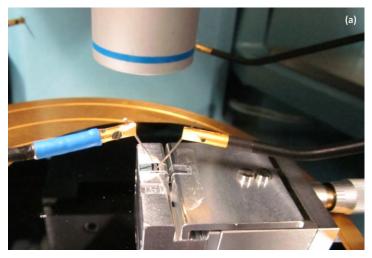

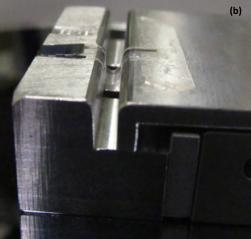

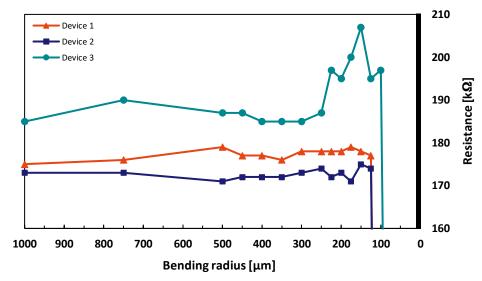

#### 2.7.3 Lead extension attachment