#### Computer Engineering Mekelweg 4,

2628 CD Delft

The Netherlands

http://ce.et.tudelft.nl/

### MSc THESIS

# Design and Implementation of a Range Trie for Address Lookup

Georgios Stefanakis

#### Abstract

CE-MS-2009-07

The rapid growth of internet traffic and the eminent shift from IPv4 to IPv6 addresses indicated the need for an efficient address lookup method that can keep pace with the ever-increasing throughput demands. As current address lookup solutions tend to become the bottleneck in internet routing, the efficient Range Trie address lookup method was designed for a hardware implementation in this thesis. A complete Range Trie hardware design was derived that is parameterizable in many of its aspects. The proposed design offers the required properties of low latency, high throughput and low memory requirements, while these properties scale well with the increase of the address width and/or the lookup table size. After implementing the Range Trie using 90nm ASIC process, an operating frequency of 540MHz up to 694MHz was achieved for IPv4 addresses, depending on the lookup table size (256-512K entries). For IPv6, the throughput was sustained between 442MHz up to 571MHz. For both IPv4 and IPv6, an OC-3072 (160Gbps) wire speed is supported for the worst-case of 512K ranges. The memory requirements ranged from a few KBytes up to 24 MBytes, while the occupied area ranged from  $0.014 \text{ cm}^2$  up to  $4.64 \text{ cm}^2$  and the power consumption ranged from 0.2 W up to 31 W depending on the address width (32, 64 or 128bits) and the lookup table size (256-512K entries).

# Design and Implementation of a Range Trie for Address Lookup

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

COMPUTER ENGINEERING

by

Georgios Stefanakis born in Athens, Greece

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

## Design and Implementation of a Range Trie for Address Lookup

#### by Georgios Stefanakis

#### Abstract

The rapid growth of internet traffic and the eminent shift from IPv4 to IPv6 addresses indicated the need for an efficient address lookup method that can keep pace with the ever-increasing throughput demands. As current address lookup solutions tend to become the bottleneck in internet routing, the efficient Range Trie address lookup method was designed for a hardware implementation in this thesis. A complete Range Trie hardware design was derived that is parameterizable in many of its aspects. The proposed design offers the required properties of low latency, high throughput and low memory requirements, while these properties scale well with the increase of the address width and/or the lookup table size. After implementing the Range Trie using 90nm ASIC process, an operating frequency of 540MHz up to 694MHz was achieved for IPv4 addresses, depending on the lookup table size (256-512K entries). For IPv6, the throughput was sustained between 442MHz up to 571MHz. For both IPv4 and IPv6, an OC-3072 (160Gbps) wire speed is supported for the worst-case of 512K ranges. The memory requirements ranged from a few KBytes up to 24 MBytes,, while the occupied area ranged from 0.014 cm² up to 4.64 cm² and the power consumption ranged from 0.2 W up to 31 W depending on the address width (32, 64 or 128-bits) and the lookup table size (256-512K entries).

**Laboratory** : Computer Engineering

Codenumber : CE-MS-2009-07

Committee Members :

Advisor: Dr.ir. Georgi N. Gaydadjiev, Assistant Prof., CE, TU Delft

Advisor: Dr. Ioannis Sourdis, CE, TU Delft

Chairperson: Dr. Koen Bertels, Associate Prof., CE, TU Delft

Member: Dr. Cristian Doerr, Assistant Prof., NAS, TU Delft

To those who inspire me...

## Acknowledgements

First of all, I am thankful to Ioannis Sourdis and Georgi Gaydadjiev for offering me this thesis topic and, most importantly, for their guidance and support during the progress of my research and also during my MSc studies. I would also like to thank all of my (current and previous) professors that brought me to where I stand now.

There are also a lot of people whose help was vital to the completion of this thesis. First of all, Ruben de Smet whom I collaborated with, as we both worked on the Range Trie method. Also, Rene van Leuken, Arjan van Genderen, Daniele Ludovici and Radu Stefan that assisted me with the issues regarding the successful usage of the Design Compiler tool. I am certain that there are also a lot more people that helped me with their insights and experience. I am thankful to you too.

I am grateful to my parents and my brother for their support and encouragement. I am also glad about the great friends I made during my stay in Delft. My life would definitely be less interesting without you. Many thanks to Angelos, Stavros, Maria, the Georges, Nikos and all the others that we spent time together and had fun.

Finally, I would like to thank the CE administrator, Erik de Vries, and the CE secretary, Lidwina Tromp, for their valuable technical and administrative assistance.

Georgios Stefanakis Delft, The Netherlands June 25, 2009

# Contents

| A             | cknov    | wledge: | ments                                           | V    |

|---------------|----------|---------|-------------------------------------------------|------|

| т:            | at of    | Figure  |                                                 |      |

| ы             | St OI    | Figure  | 25                                              | Xi   |

| Li            | st of    | Tables  |                                                 | xiii |

| $\mathbf{Li}$ | st of    | Acron   | yms                                             | xv   |

|               |          |         |                                                 |      |

| _             | <b>.</b> |         |                                                 | _    |

| 1             |          | oducti  |                                                 | 1    |

|               | 1.1      |         | ss Lookup                                       | 2    |

|               | 1.2      |         | m Statement                                     | 3    |

|               | 1.3      |         | Goals and Contributions                         | 4    |

|               | 1.4      | Thesis  | Overview                                        | 5    |

| 2             | Bac      | kgroun  | ıd                                              | 7    |

|               | 2.1      | Relate  | d Designs and Algorithms for Address Lookup     | 8    |

|               |          | 2.1.1   | Binary Trie                                     | G    |

|               |          | 2.1.2   | Path-Compressed Tries                           | 10   |

|               |          | 2.1.3   | Multibit Tries                                  | 11   |

|               |          | 2.1.4   | Level-Compressed Tries                          | 13   |

|               |          | 2.1.5   | Hierarchical Intelligent Cuttings (HiCuts)      | 13   |

|               |          | 2.1.6   | Binary Search on Length                         | 14   |

|               |          | 2.1.7   | Sequential Search on Values                     | 16   |

|               |          | 2.1.8   | Range Tree                                      | 16   |

|               |          | 2.1.9   | TCAMs                                           | 17   |

|               |          | 2.1.10  | IPstash                                         | 18   |

|               |          | 2.1.11  | Bloom Filters                                   | 19   |

|               |          | 2.1.12  | Tree Bitmap                                     | 21   |

|               |          | 2.1.13  | Pipelines                                       | 22   |

|               | 2.2      | The R   | ange Trie                                       | 23   |

|               |          | 2.2.1   | Range Trie description                          | 24   |

|               |          | 2.2.2   | Range Trie fundamental concepts and rules       | 25   |

|               |          | 2.2.3   | Range Trie structure and algorithm              | 30   |

|               |          | 2.2.4   | Construction of a Range Trie                    | 32   |

|               |          | 2.2.5   | A Range Trie supporting longest prefix matching | 34   |

|               |          | 2.2.6   | Range Trie achievements                         | 34   |

|               | 2.2      | C       | 0.777                                           | 25   |

| <b>3</b>         | $\mathbf{Des}$ | gn and Implementation                                                  | 37 |

|------------------|----------------|------------------------------------------------------------------------|----|

|                  | 3.1            | Range Trie iteration                                                   | 38 |

|                  |                | 3.1.1 Selecting parts of addresses                                     | 42 |

|                  |                | 3.1.2 Performing the comparisons                                       | 61 |

|                  |                | 3.1.3 Interpreting the comparison results                              | 68 |

|                  |                | 3.1.4 Deciding which branch to follow                                  | 77 |

|                  |                | 3.1.5 Top-level iteration module                                       | 79 |

|                  | 3.2            | Storing the Range Trie nodes in memory                                 | 83 |

|                  |                | 3.2.1 Memory organization                                              | 83 |

|                  |                | 3.2.2 Memory addressing scheme                                         | 86 |

|                  |                | 3.2.3 Range Trie node data structure                                   | 88 |

|                  |                | 3.2.4 Memory units' hardware details                                   | 90 |

|                  | 3.3            | The complete Range Trie design                                         | 92 |

|                  |                | 3.3.1 Integrating the iteration hardware and the memory structure into |    |

|                  |                | a pipeline                                                             | 92 |

|                  |                | 3.3.2 The Range Trie top-level module                                  | 95 |

|                  | 3.4            | Summary                                                                | 96 |

| 4                | Eva            | uation                                                                 | 99 |

|                  | 4.1            | Experimental setup                                                     | 99 |

|                  | 4.2            | Evaluation of the iteration stage                                      | 00 |

|                  | 4.3            | Evaluation of the complete design                                      | 09 |

|                  | 4.4            | Summary                                                                | 20 |

| 5                | Con            | elusions 12                                                            | 23 |

|                  | 5.1            | Summary                                                                | 23 |

|                  | 5.2            | Contributions                                                          |    |

|                  | 5.3            | Future suggestions                                                     |    |

| $\mathbf{B}^{i}$ | bliog          | raphy 13                                                               | 31 |

|                  |                |                                                                        |    |

# List of Figures

| 1.1  | Address lookup for routing                                                   | 1  |

|------|------------------------------------------------------------------------------|----|

| 1.2  | Address lookup problem specification                                         | 2  |

| 1.3  | Projected U.S. Internet traffic growth                                       | 3  |

| 2.1  | Address lookup search dimensions                                             | 9  |

| 2.2  | A binary trie                                                                | 10 |

| 2.3  | A path-compressed trie                                                       | 11 |

| 2.4  | A variable-stride multibit trie                                              | 12 |

| 2.5  | A Level-Compressed trie                                                      | 13 |

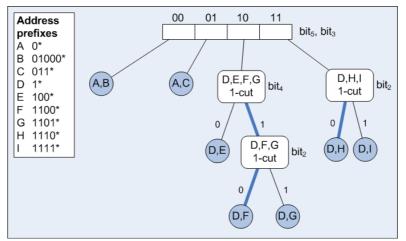

| 2.6  | A HiCuts tree for address lookup                                             | 14 |

| 2.7  | The modular packet classification approach                                   | 15 |

| 2.8  | A binary "search on length" approach                                         | 15 |

| 2.9  | A binary range tree                                                          | 17 |

| 2.10 | A multiway range tree                                                        | 17 |

| 2.11 | TCAM structure for address lookup                                            | 18 |

| 2.12 | The IPStash architecture                                                     | 19 |

| 2.13 | The Bloom filter data structure                                              | 20 |

| 2.14 | The tree bitmap data structure                                               | 21 |

|      | The CAMP pipeline approach                                                   | 23 |

| 2.16 | A Range Trie node and its ranges                                             | 24 |

| 2.17 | Example application of Range Trie Rule 1                                     | 26 |

| 2.18 | Example application of Range Trie Rule 2                                     | 27 |

| 2.19 | Example application of Range Trie Rule 3                                     | 28 |

| 2.20 | Example application of Range Trie Rule 4                                     | 29 |

| 2.21 | Example application of Range Trie Rule 5                                     | 29 |

| 2.22 | Example of a Range Trie structure                                            | 30 |

| 2.23 | A Range Trie node and its children                                           | 31 |

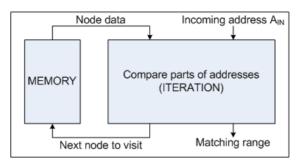

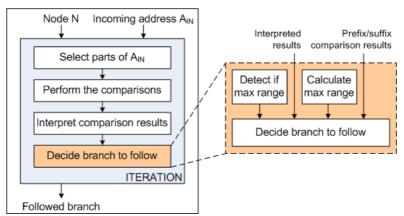

| 3.1  | Block diagram of the Range Trie method                                       | 37 |

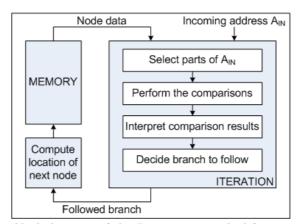

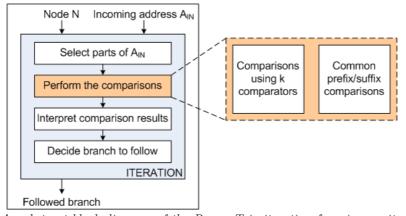

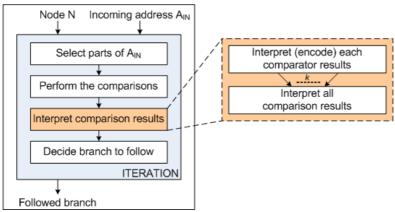

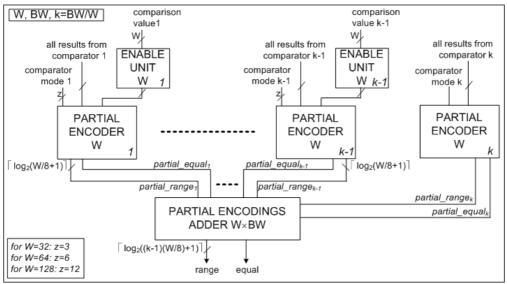

| 3.2  | Block diagram of the Range Trie iteration                                    | 39 |

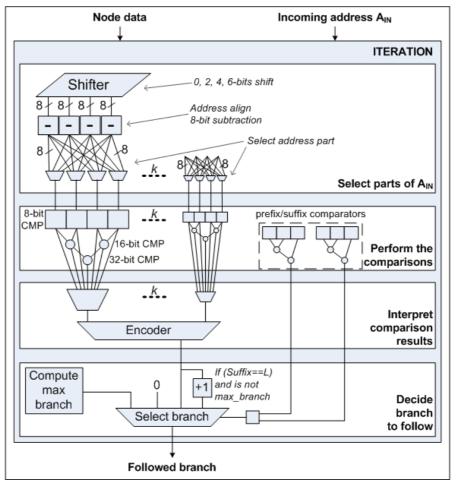

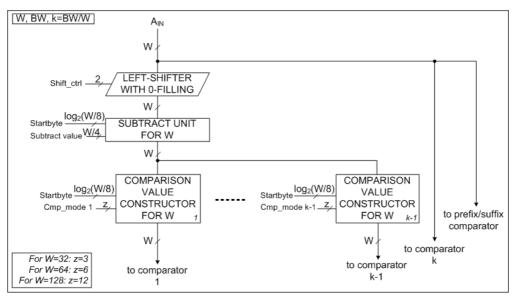

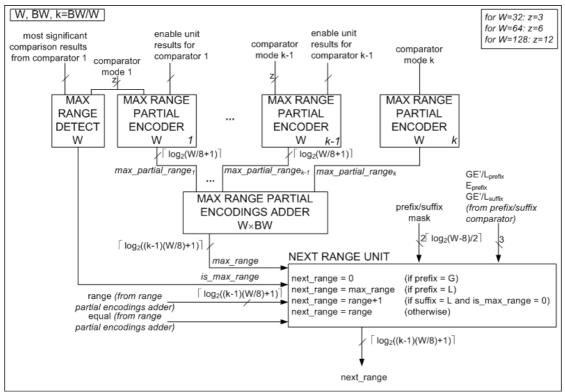

| 3.3  | Brief overview of the Range Trie iteration hardware                          | 41 |

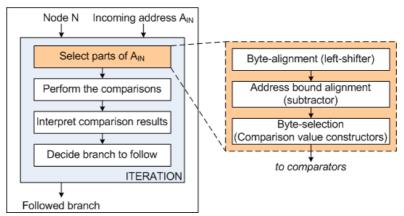

| 3.4  | Block diagram of the Range Trie iteration step 1 (select parts of addresses) | 43 |

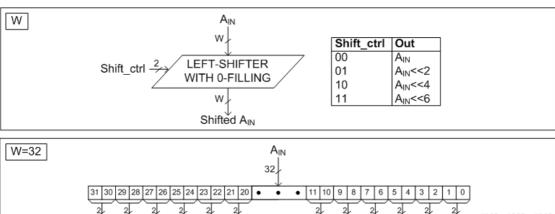

| 3.5  | Left-shifter with 0-filling (HW design)                                      | 46 |

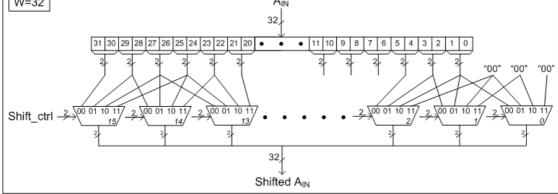

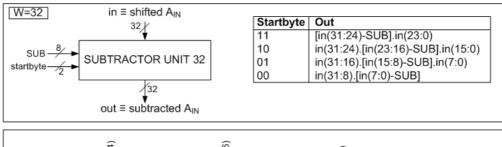

| 3.6  | Subtractor unit for W=32 (HW design)                                         | 47 |

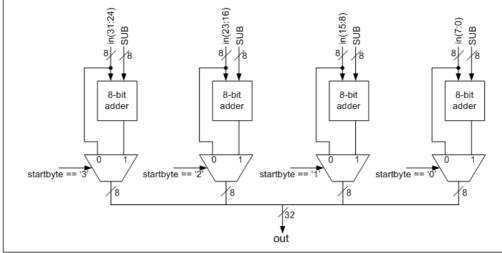

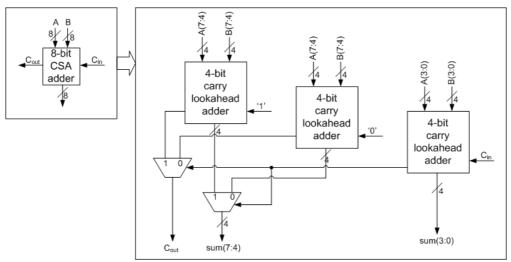

| 3.7  | 8-bit carry select adder (HW design)                                         | 48 |

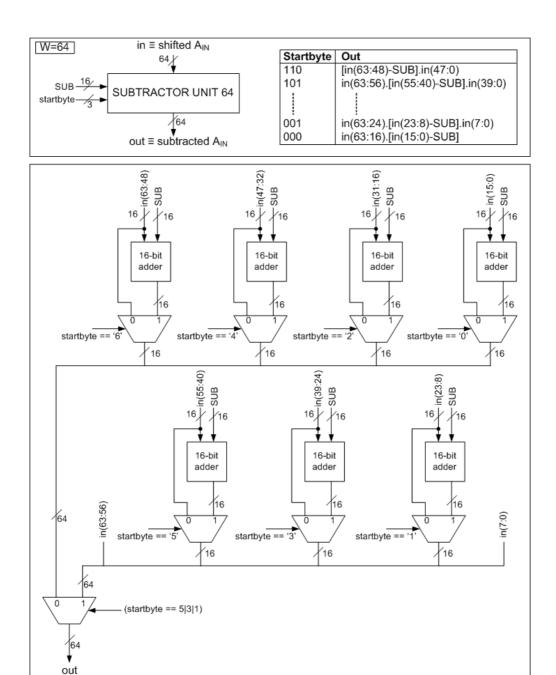

| 3.8  | Subtractor unit for W=64 (HW design)                                         | 50 |

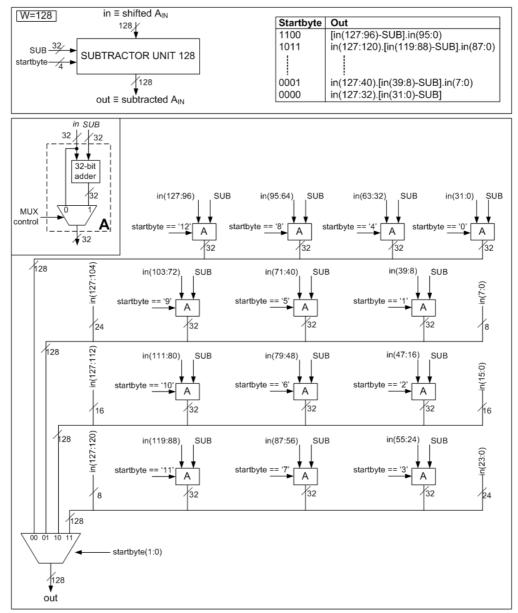

| 3.9  | Subtractor unit for W=128 (HW design)                                        | 51 |

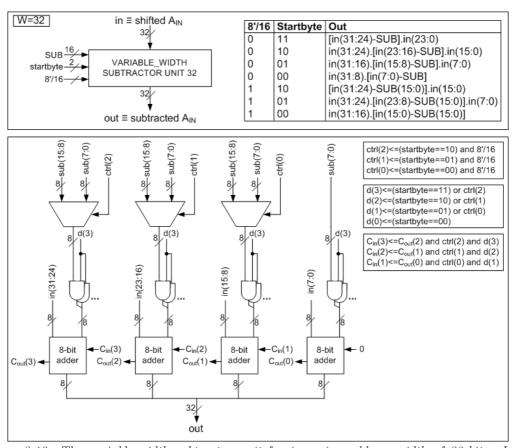

| 3.10 | Variable-width subtractor unit for W=32 (HW design)                          | 52 |

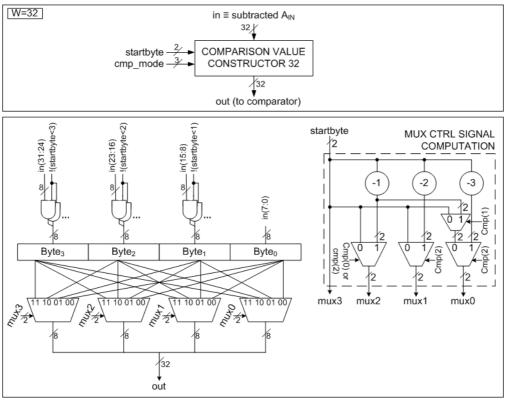

| 3.11 | Comparison value constructor for W=32 (HW design) $\dots$                    | 56 |

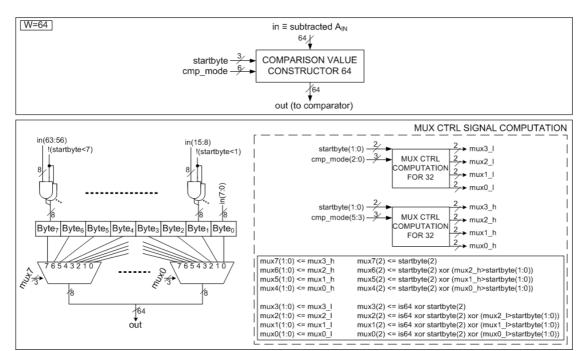

| 3.12 | Comparison value constructor for W=64 (HW design) $\dots$                    | 60 |

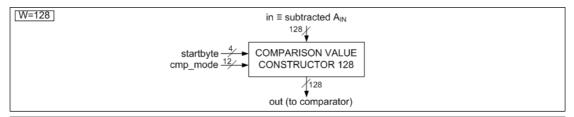

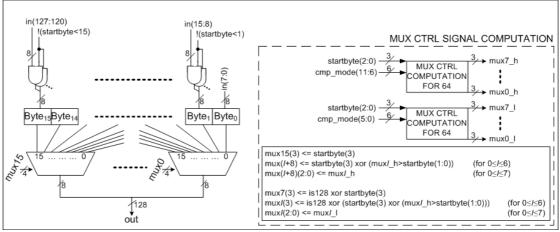

| 3.13 | Comparison value constructor for W=128 (HW design) $\dots$                   | 61 |

| 3.14 | Integrated HW design for selecting parts of addresses                        | 62 |

| 3.15 | Block diagram of the Range Trie iteration step 2 (performing the comparisons) | G C      |

|------|-------------------------------------------------------------------------------|----------|

| 9.10 |                                                                               | 62       |

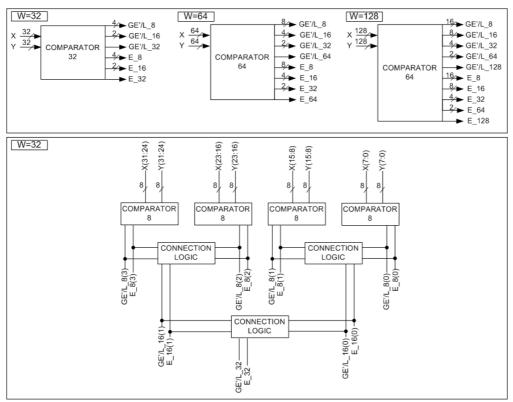

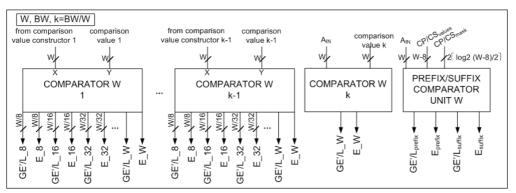

|      | Variable-width comparator for W (HW design)                                   | 64       |

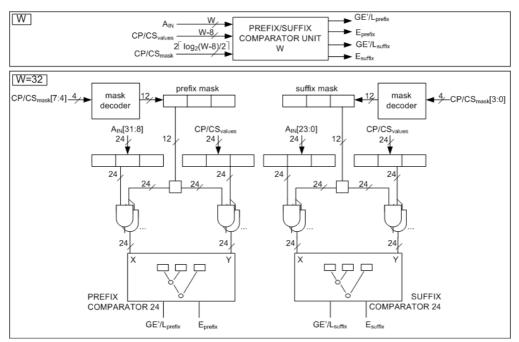

|      | Prefix/suffix comparator unit for W (HW design)                               | 66       |

|      | Integrated HW design for performing the comparisons                           | 66       |

| 3.19 | Block diagram of the Range Trie iteration step 3 (interpret comparison        | ec       |

| 2 20 | results)                                                                      | 68       |

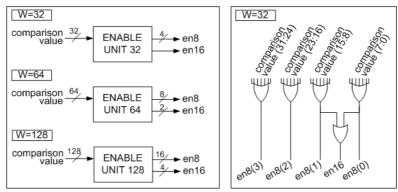

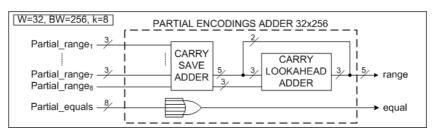

|      | Enable unit for W (HW design)                                                 | 71<br>72 |

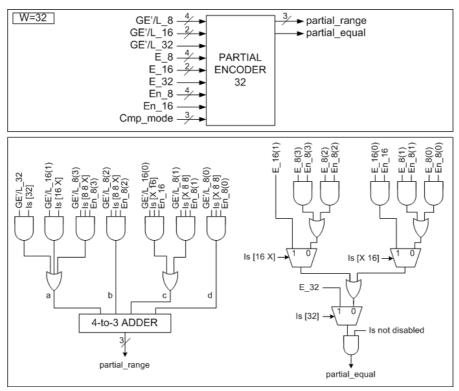

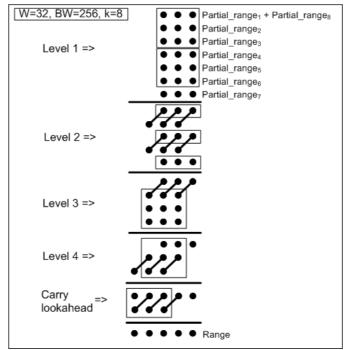

|      | Partial encoder for W=32 (HW design)                                          | 75       |

|      | Partial encodings adder for W=32 and BW=256 (HW design)                       | 75       |

|      | Integrated HW design for interpreting the comparisons results                 | 76       |

|      | Block diagram of the Range Trie iteration step 4 (decide branch to follow)    |          |

|      | Integrated HW design for deciding the next range value                        | 80       |

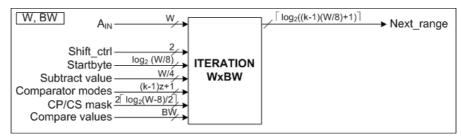

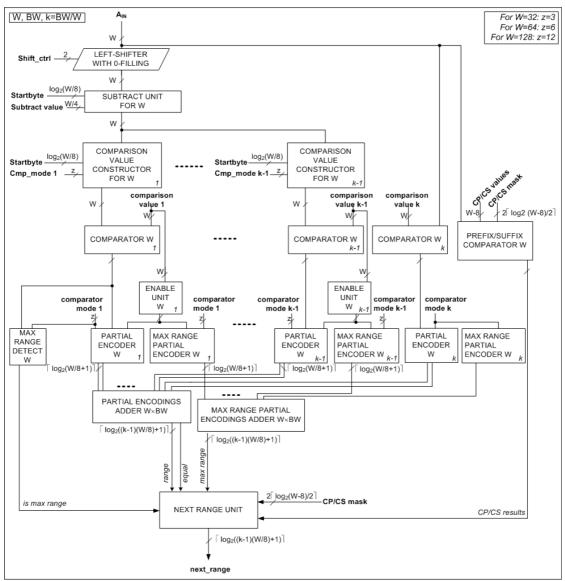

|      | Top-level iteration module                                                    | 81       |

|      | Integrated HW design of the Range Trie iteration                              | 82       |

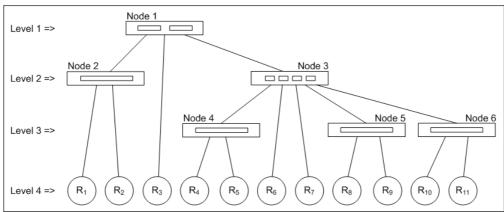

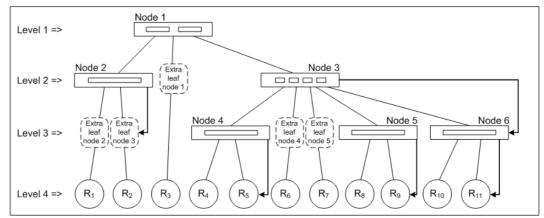

|      | A generic Range Trie                                                          | 84       |

|      | A generic Range Trie annotated for memory storage purposes                    | 85       |

|      | A Range Trie stored in memory                                                 | 85       |

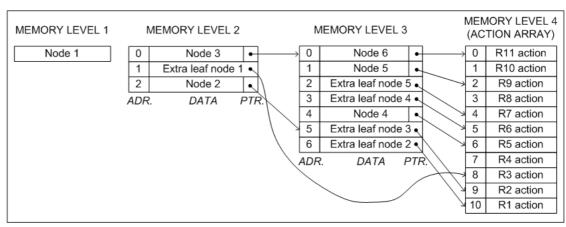

|      | A Range Trie node and its children organized in the memory units              | 87       |

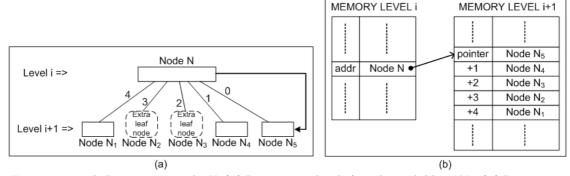

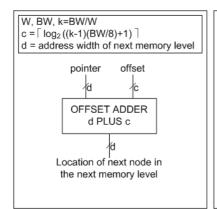

|      | Offset adder (HW design)                                                      | 88       |

|      | The node data structure                                                       |          |

|      | The memory unit HW design                                                     | 91       |

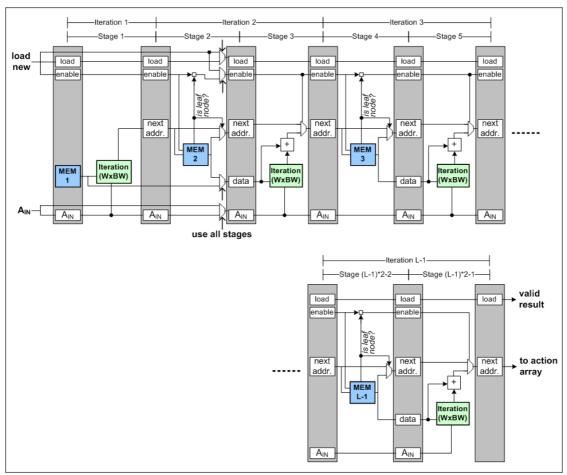

|      | Abstract Range Trie pipeline                                                  | 93       |

|      | The complete Range Trie pipeline (HW design)                                  | 94       |

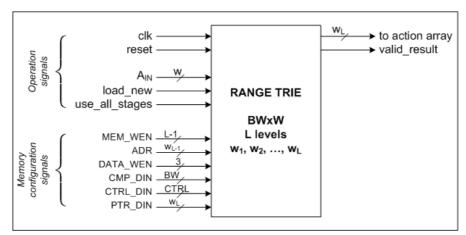

|      | The Range Trie top-level module                                               | 96       |

| 0.00 | 110 100160 1110 top 10001 110 auto 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1      |          |

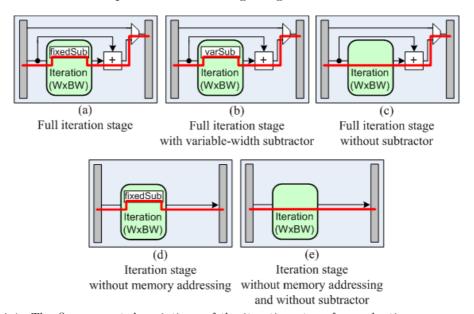

| 4.1  | Generated variations of the iteration stage for evaluation purposes $\dots$   | 101      |

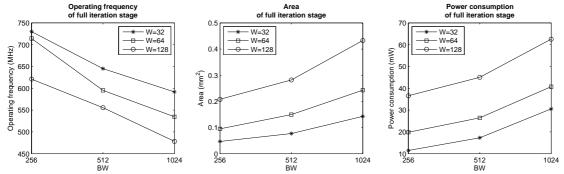

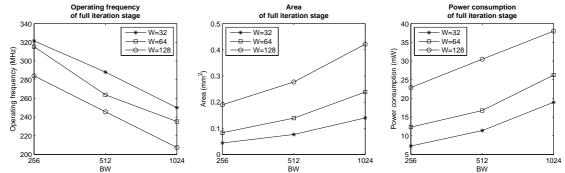

| 4.2  | Synthesis results for full iteration stage (90nm)                             |          |

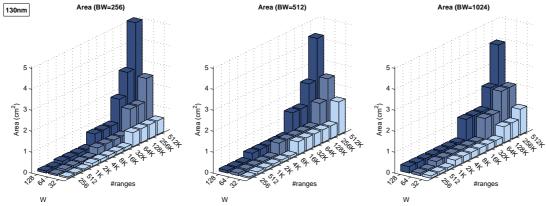

| 4.3  | Synthesis results for full iteration stage (130nm)                            | 103      |

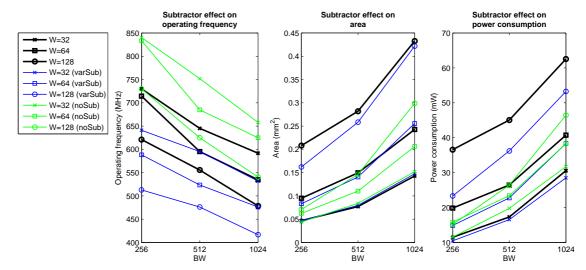

| 4.4  | The effect of bound alignment on the synthesis results for full iteration     |          |

|      | stage (90nm)                                                                  | 105      |

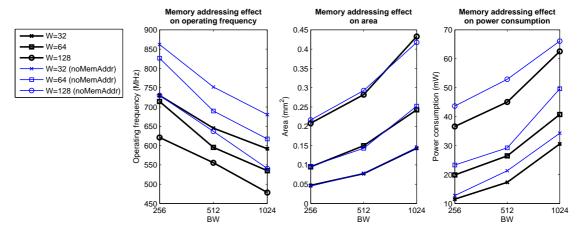

| 4.5  | The effect of memory addressing hardware on the synthesis results for the     |          |

|      | iteration stage (90nm)                                                        |          |

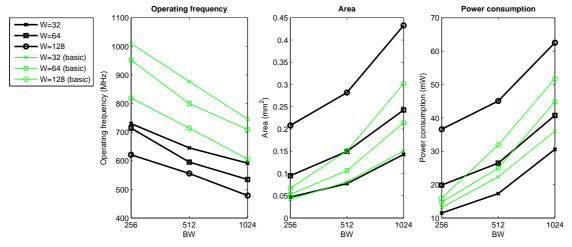

| 4.6  | The full iteration stage against the basic iteration stage (90nm)             |          |

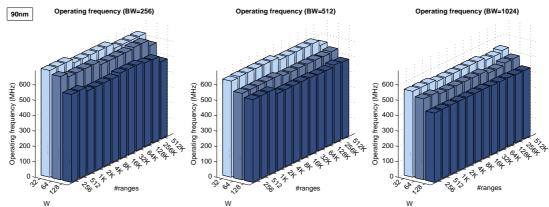

| 4.7  | Operating frequency results for all Range Trie instances (90nm)               |          |

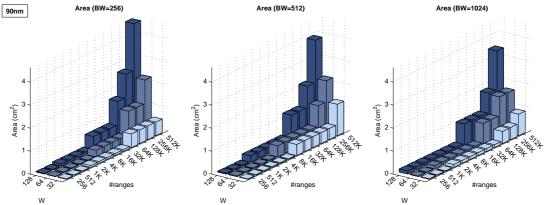

| 4.8  | Area results for all Range Trie instances (90nm)                              |          |

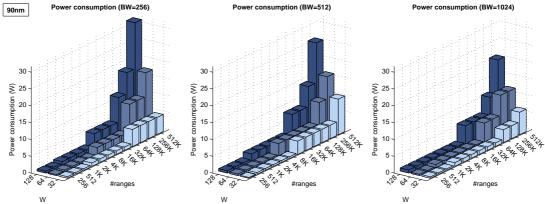

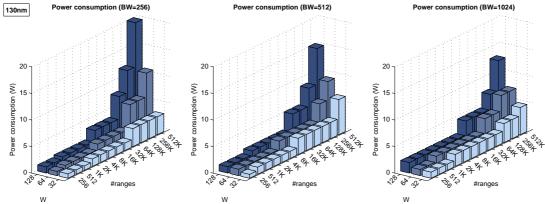

| 4.9  | Power consumption results for all Range Trie instances (90nm)                 |          |

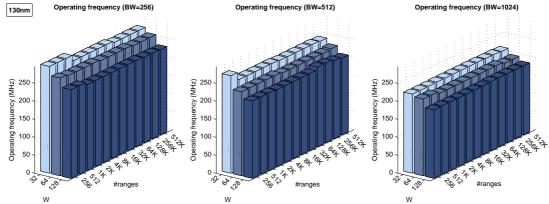

|      | Operating frequency results for all Range Trie instances (130nm)              |          |

|      | Area results for all Range Trie instances (130nm)                             |          |

|      | Power consumption results for all Range Trie instances (130nm)                |          |

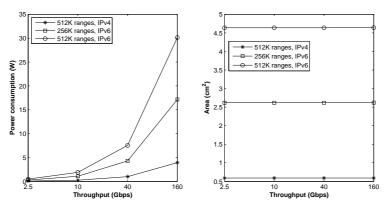

|      | Power consumption and area as a function of throughput (90nm)                 |          |

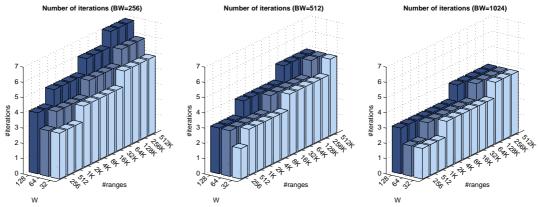

|      | Number of iterations of the synthesized Range Trie designs                    |          |

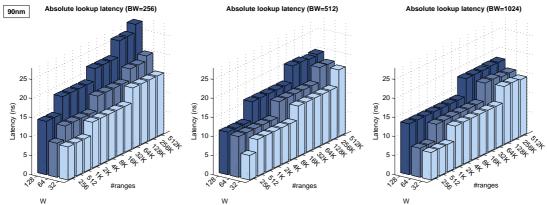

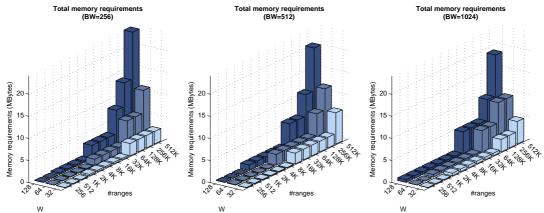

|      | Absolute lookup latency of the synthesized Range Trie designs (90nm)          |          |

| 4.16 | Memory requirements of the synthesized Range Trie designs                     | 118      |

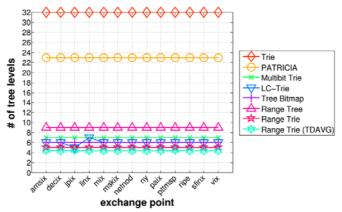

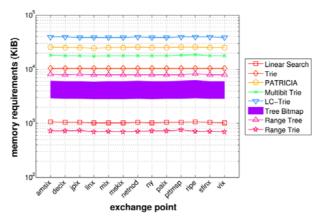

| 4.17 | Comparison of tree levels of various lookup methods             | 119 |

|------|-----------------------------------------------------------------|-----|

| 4.18 | Comparison of the memory requirements of various lookup methods | 119 |

# List of Tables

| 2.1 | Address ranges in address prefix format                                                                                    |

|-----|----------------------------------------------------------------------------------------------------------------------------|

| 3.1 | Operation of the comparison value constructor for W=32                                                                     |

| 3.2 | Binary representation of comparator modes for W=32                                                                         |

| 3.3 | Binary representation of comparator modes for W=64                                                                         |

| 3.4 | Binary representation of comparator modes for W=128 59                                                                     |

| 3.5 | The node data structure sizes                                                                                              |

| 4.1 | Synthesis results for full iteration stage (90nm)                                                                          |

| 4.2 | Synthesis results for full iteration stage (130nm)                                                                         |

| 4.3 | Synthesis results for full iteration stage with variable-width subtractor                                                  |

|     | $(90nm) \dots \dots$ |

| 4.4 | Synthesis results for full iteration stage without subtractor (90nm) 105                                                   |

| 4.5 | Synthesis results for iteration stage without memory addressing hardware                                                   |

|     | $(90nm) \dots \dots$ |

| 4.6 | Synthesis results for basic iteration stage without memory addressing                                                      |

|     | hardware and without subtractor (90nm)                                                                                     |

| 4.7 | Synthesized Range Trie instances                                                                                           |

| 4.8 | Synthesis results for all Range Trie instances (90nm and 130nm) 112                                                        |

# List of Acronyms

ASIC Application-Specific Integrated Circuit

BU-SLC Bottom-Up with Single Length Comparisons

BU-VLC Bottom-Up with Variable Length Comparisons

CAMP Circular, Adaptive and Monotonic Pipeline

CIDR Classless InterDomain Routing

FPGA Field-Programmable Gate Array

HiCuts Hierarchical Intelligent Cuttings

IP Internet Protocol

IPv4Internet Protocol version 4IPv6Internet Protocol version 6LC-TriesLevel-Compressed TriesMPPSMega Packets Per Second

PATRICIA Practical Algorithm To Retrieve Information Coded In Alphanumeric

SRAM Static Random Access Memory

TCAM Ternary Content Addressable Memory

TD-SLC Top-Down with Single Length Comparisons

TD-VLC Top-Down with Variable Length Comparisons

Introduction

"You 'll find your way, John. You always do."

-Benjamin Linus to John Locke

odern societies rely heavily on information. If information was to stay in one place, then there would be no much use of it. This is what led to the vast development and employment of information networks, ranging from simple computer networks to advanced telecommunication networks. In any of these cases, information travels throughout the network and it is imperative to find its way from its source to its destination.

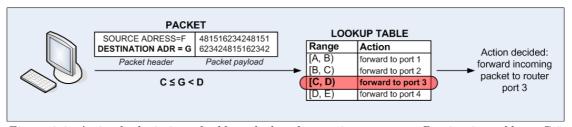

In the case of computer networks, information (represented as data) is divided into packets that are routed from the source towards the destination through intermediate nodes. Each packet consists of a header (that contains information about the source and the destination) and the payload (that contains the actual data). In each intermediate node it must be decided where to forward the packet based on a routing table and the destination. The destination address is looked up in the routing table to decide the action to be taken (see Figure 1.1). This process of searching in the routing table is called address lookup.

Figure 1.1: A simple depiction of address lookup for routing purposes. Destination address G is looked up and found to belong in range [C,D).

A lot of research is available regarding routing and its issues. This thesis focuses specifically on the address lookup problem in the context of internet routing and presents an efficient and scalable hardware design for address lookup based on the novel Range Trie algorithm introduced by I. Sourdis in [26].

The rest of this introductory chapter is organized as follows: Section 1.1 explains in more details the address lookup and gives an overview of its use in a variety of research fields. Section 1.2 focuses on the specifics of the address lookup current problems that motivated this thesis. Section 1.3 states the goals of this thesis and its contributions. Finally, section 1.4 concludes this chapter with an overview of the thesis.

#### 1.1 Address Lookup

It was previously stated that our focus is on address lookup. Address lookup is an elementary operation in computer networks (and information exchange networks in general). Every network routing element must support it and its significance triggered the development of the address lookup research field.

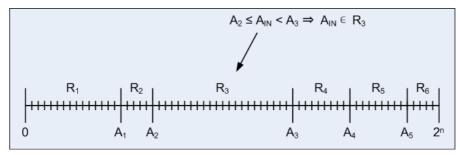

In computer networks, each network element is characterized by its Internet Protocol (IP) address. In the case of Internet Protocol version 4 (IPv4), each IP address is represented as a 32-bits wide binary number. Address lookup for computer networks may be defined as the procedure of determining the range that an IP address belongs to, out of a given set of IP address ranges (routing table). Given an address space  $[0, 2^n)$  and k unique IP addresses/bounds  $A_i$ , where  $0 < A_i < 2^n - 1$  and i = 1, 2, ..., k, that define k+1 address ranges  $R_j$  (j = 1, 2, ..., k+1), then an address lookup is to determine the range  $R_j$  an incoming address  $A_{IN}$  belongs to. In the case of IPv4, n = 32. Figure 1.2 depicts graphically an example address lookup, as specified above, for an address space consisting of 6 ranges (k = 5) and an incoming address  $A_{IN}$  belonging in range  $R_3$  ( $A_2 \le A_{IN} < A_3$ ).

Figure 1.2: Address lookup problem specification

Address lookup is not limited just to computer networks. It could also be applied to other research fields that may or may not relate to network routing. In general, this lookup process narrows down to determining in which range an address belongs to out of a given set of ranges.

A variety of research domains may need this function and thus a lot of research effort has been spent on address lookup. A list of some of these research fields follows:

- In *internet routing* [22], as mentioned, routers need to forward packets based on the destination IP address of a packet. The decision is made by searching the destination IP address in the router's lookup table.

- In packet classification [31], [13], [24], [9] a lookup must be performed for one or more of the packet header fields to classify the packet based on a set of rules and then perform a defined action.

- In *interprocessor communication*, the newly proposed progressive address translation of virtual addresses to physical ones [16] needs to perform a translation lookup as the interprocessor communication shares a common address space.

The rest of this thesis will focus more on the application of address lookup of IP addresses for routing purposes. In any case, the findings of this thesis could be applied to all the mentioned research fields that have a need for address lookup.

#### 1.2 Problem Statement

In the previous section, it was stated that a lot of research has been performed on address lookup for a variety of research fields. The question now is why deal with address lookup, since it is already a mature research domain, as old as network routing. In this section the issues that motivated this thesis are presented.

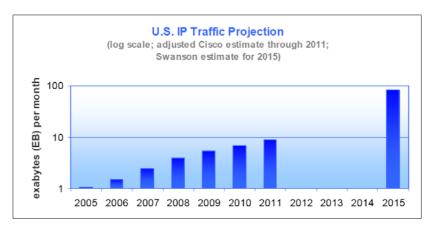

The rapid growth of internet traffic (see Figure 1.3), the increase in the number of network devices and the subsequent growing size of routing tables make more difficult for address lookup to keep pace with the increasing need for faster processing rates posed by the technological advancements in communication speed and bandwidth. Furthermore, the transition from the 32-bits wide IPv4 addresses to 128-bits wide IPv6 addresses demands for address lookup solutions that may scale efficiently in terms of the address width.

Figure 1.3: Projected U.S. Internet traffic growth until 2011 and for 2015. An exabyte equals to 2<sup>60</sup> bytes. (Source: [30])

The currently available lookup solutions have started lagging behind; they may have worked well for past routing conditions but need to be improved in order to handle the multi-gigabits-per-second traffic rates. In particular, a mechanism is desired for address lookup that has low latency, high throughput and low memory requirements. At the same time, it should scale efficiently when the address width and/or the number of ranges increases. By scaling efficiently, we mean that an increase in address width and/or the number of ranges should affect minimally the latency, throughput and memory requirements. Out of these requirements, extra effort must be placed on the memory requirements because the size/bandwidth of the memories tends to dictate the efficiency and cost of the implementations.

Although these requirements are targeted for dealing with upcoming internet routing problems, there are present also to the other research fields that use address lookup and they could benefit from solving these problems. In packet classification, a high throughput is still needed for looking up the multiple fields of the incoming packets, although the number of ranges is significantly smaller than those of internet routing. Similarly, in interprocessor communication [16], where the number of ranges is also small, there are higher constraints for lookup latency and throughput in order to sustain the performance of multicore systems.

In general, it could be said that the problem is that address lookup has the trend of becoming the bottleneck in the systems that they use it. An address lookup must be performed at wire speeds. At the same time the other requirements for a good lookup scheme (memory, scalability) should be considered [33]. The problem of designing such a scheme is the main motivation behind this thesis.

There is already a variety of algorithms and methods for address lookup that have started lagging behind, as already mentioned. This thesis focuses on the Range Trie algorithm introduced by I. Sourdis in [26] that promises to solve these problems.

The Range Trie algorithm posed an extra motivation behind this thesis because it is addressed here from the aspect of hardware design and implementation. Although the work in [25] and [6] proved the benefits of the Range Trie algorithm, this thesis focuses on an efficient hardware design and implementation of the Range Trie in order to sustain its benefits in a real-world design.

#### 1.3 Thesis Goals and Contributions

In the previous section, the problems that arise in current solutions for address lookup were described. This thesis tries to solve the problems mentioned before by an efficient hardware design and implementation of the Range Trie algorithm.

The goal of this thesis is a design and implementation of the Range Trie algorithm that exploits optimally the inherit characteristics of the Range Trie structure: (a) low lookup latency, (b) high throughput, (c) low memory requirements, (d) acceptable scalability of (a)-(c) in terms of the lookup address width and number of address ranges.

The contributions of this thesis are:

- A hardware design of the Range Trie algorithm: For the first time, the Range Trie algorithm is designed for a hardware implementation. During the design, extra effort was used to ensure that the hardware design exploits the characteristics of the Range Trie algorithm, as mentioned in (a)-(d) above. The resulting design is parameterizable in terms of address width, memory bandwidth and number of processing stages in order to accommodate the address lookup needs of the application under consideration.

- A complete design flow for hardware implementation and validation: A complete design flow was created for generating Range Trie instances. Starting from the required design parameters and a Range Trie structure, generated by Ruben de Smet in [6], a synthesizable design of a Range Trie is generated in a hardware description language, along with the means to (a) configure it according to the given structure and (b) validate its correct operation.

• Evaluation of the Range Trie design: A variety of Range Trie instances was generated and synthesized for 2 ASIC technologies (90nm and 130nm) in order to evaluate each design point in terms of operating frequency, area, power consumption and memory requirements. This design space exploration proved the Range Trie scalability and offers the designer a chance to choose the suitable parameters for its case. A comparison was performed with other existing solutions for address lookup. The findings may be used accordingly to other research fields that need address lookup.

The means to achieve the goals and the contributions of this thesis are presented in the rest of this text's chapters, as described in the following overview of this thesis.

#### 1.4 Thesis Overview

This section concludes the introductory chapter of this thesis and presents the overview of the following chapters.

In Chapter 2, the related work that exists in the literature regarding address lookup is presented. The presented solutions are both algorithmic approaches and hardware-targeting schemes and they origin mainly from the network routing and packet classification research domains. This chapter also introduces and details the Range Trie algorithm of [26] that is the main focus of this thesis.

Afterwards, the hardware design of the Range Trie algorithm is explained in detail in Chapter 3. All the design steps are discussed for obtaining a complete, synthesizable design. Chapter 4 presents and evaluates the results of synthesizing the Range Trie design for ASIC.

Finally, Chapter 5 concludes this thesis by summarizing its contributions and conclusions and by presenting some ground for future works.

Background

Address lookup is the operation of looking up in a table to find a range that an incoming address belongs to. As mentioned in Section 1.2, a good address lookup scheme should have low lookup latency, high throughput, low memory requirements and good scalability in terms of the lookup table size and the address width. There is already a variety of address lookup schemes but they have started lagging behind due to the recent internet traffic/speed growth. Thus, it is imperative to improve on the current schemes. The Range Trie algorithm, introduced in [26] promises a lookup scheme that satisfies the posed requirements. This Range Trie approach is the main focus point of this thesis.

In this chapter, the background material that is needed for the rest of this thesis will be presented. After discussing on a variety of related designs and algorithms for address lookup (Section 2.1), the Range Trie algorithm will be described (Section 2.2).

In order to understand the related methods for address lookup, it is important to start from the first attempts that tried to deal with the causes of the lookup problem.

Initially, the approach that was followed was to reduce the lookup tables growth rates by using different addressing schemes. The first addressing scheme that was used was a simple address allocation scheme that divided addresses into three classes. This is known as the *classful addressing scheme*. In this scheme the address was split into two parts: the network part, followed by the host part. There were three different classes of addresses with different network part widths. Addresses of class A, B, or C consisted of an 8, 16, or 24-bits network part and a corresponding 24, 16, or 8-bits host part. Doing an address lookup in this scheme was a relatively simple operation; a lookup was narrowed down to make an exact prefix match using standard algorithms based on hashing or binary search. This scheme worked well initially, but the continuous growth in the number of hosts and networks lead on the exhaustion of the IP address space rather quickly. Furthermore, the increase in the lookup table size was still prominent.

To deal with the problems of the classful addressing scheme, the classless interdomain routing (CIDR) addressing scheme was introduced [11]. With CIDR the prefixes may be of variable length, instead of 8, 16 or 24-bits wide. This scheme allowed for a more efficient use of the IP addresses, along with the aggregation of addresses. So, the lookup tables needed to keep less prefixes. The trade-off was that the lookup process got more complicated as it was now required to make a longest prefix match instead of an exact prefix match.

Despite the use of CIDR, the routing tables kept growing. This resulted in a shift in the research effort from trying to reduce the inherit growth of the lookup table sizes into finding more efficient lookup methods that are scalable with respect to the number of lookup table entries. At the same time, the lookup methods should have low memory requirements, low latency and fast lookup times. A new requirement that appeared with the introduction of IPv6 was to find lookup algorithms that are also scalable with respect to the address width.

As already mentioned, there is a plethora of currently available solutions for address lookup that try to achieve these requirements but have started to lag behind due to the internet traffic/speed growth. Some of these will be discussed in Section 2.1 of this chapter. In Section 2.2, the Range Trie algorithm, that is an improvement on the current solutions, will be presented in detail. The improvements of the Range Trie will be proven later in Chapter 4. Finally, this chapter concludes with its summary in Section 2.3.

#### 2.1 Related Designs and Algorithms for Address Lookup

In this section, a representative set of address lookup solutions which exist in the related literature will be presented.

Before proceeding, it must be noted that these solutions approach the address lookup problem from two equivalent sides; others consider it as a longest prefix matching problem, others as a range lookup problem. The actual difference is in the way that they represent the lookup table. The former approaches consider the lookup table as a set of address prefixes. Each address prefix is in the form of a binary number followed by a star, which actually represents the range of addresses that start with this binary number. The latter approaches consider the lookup table as a set of range bounds that define the address ranges. Both representations of the lookup tables are equivalent (see Table 2.1) and suitable for address lookup. Although the research problem is the same, the difference is in the means to solve it. Former approaches research on performing a longest prefix matching, while the latter try to find a matching range.

Table 2.1: The address ranges represented as equivalent address prefixes. These address ranges/prefixes will be used as an example lookup table in the methods discussed in the rest of this section.

|   | Address Range    | Address Prefix |

|---|------------------|----------------|

| a | [000000, 111111) | 0*             |

| b | [010000, 010010) | 01000*         |

| c | [011000, 100000) | 011*           |

| d | [100000, 111111] | 1*             |

| e | [100000, 101000) | 100*           |

| f | [110000, 110100) | 1100*          |

| g | [110100, 111000) | 1101*          |

| h | [111000, 111100) | 1110*          |

| i | [111100, 111111] | 1111*          |

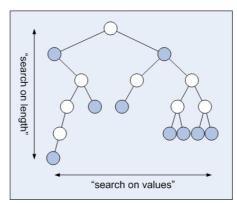

According to the taxonomy of Ruiz-Sanchez et. al. in [22] the existing address lookup solutions may be categorized into "search on length" or "search on values" approaches according to the dimension the search is based on (see Figure 2.1). Waldvogel et al. in

[32] added an extra classification of the methods depending on the type of the search traversal (sequential or binary search on length or values).

Figure 2.1: Address lookup search dimensions. The search space that is being traversed by a lookup method may be either on the length of the addresses ("search on length") or on their values ('search on values').

In the rest of this section, a variety of existing designs and algorithms for address lookup will be presented. These address lookup schemes may not come directly from the internet routing domain, but from other research domains that also need a form of address lookup, such as the packet classification research field. The presented related work is a mixture of algorithmic approaches to address lookup and hardware-targeting address lookup designs.

Specifically, in Sections 2.1.1 through 2.1.5 the sequential "search on length" approaches are considered starting from the elementary binary trie structure (in Section 2.1.1) and proceeding to more advanced trie structures. Then a binary "search on length" approach will be discussed in Section 2.1.6. Afterwards, the basics of sequential "search on values" will be presented in Section 2.1.7, followed by the binary "search on values" approach of range trees in Section 2.1.8. This section concludes with a set of hardware-targeting approaches in Sections 2.1.9 through 2.1.13.

#### 2.1.1 Binary Trie

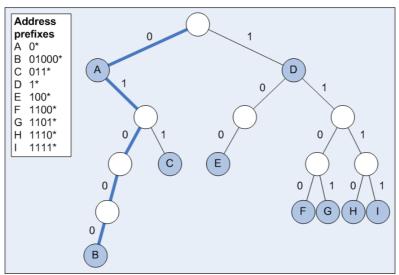

The most natural way to perform longest prefix matching for the purposes of address lookup is to represent the address prefixes using a trie. A trie performs a sequential "search on length". As shown on Figure 2.2, a trie is a tree-based data structure allowing the organization of prefixes on a binary basis by using the bits of prefixes to direct the branching [22].

Each node of the binary trie has at most two children, each one corresponding to the next bit of the address prefixes. A search in a trie is guided by the bits of the destination address. At each node, the search branches either left or right, depending on the next bit of the incoming address. This means that at the level l of the range trie, the l most significant bits of the incoming address have been inspected and address prefixes of length l may be matched. The search ends when there are no more branches to take and the search result is the last address prefix node encountered.

Figure 2.2: A binary trie for a set of address prefixes. Prefix nodes are shown in a darker color. As an example, the path followed to match the incoming address 010000 to prefix B is shown.

As mentioned, a binary trie search is a "search on length" sequential approach. At every step through the trie, the search space is reduced and a better match is trying to be found. A binary trie lookup for incoming addresses of length W takes O(W) steps. This means that the binary tries doesn't scale well in terms of the address width. Furthermore, they produce an unbalanced decision tree with large depth and relatively high memory requirements.

#### 2.1.2 Path-Compressed Tries

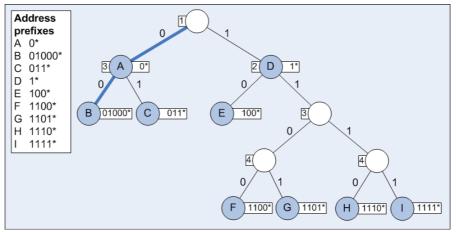

An improvement on the binary tries, presented in Section 2.1.1, are the *path-compressed tries* which are also a sequential "search on length" approach. Binary tries often suffer from long search paths that are a long sequence of one-child nodes (i.e. address prefix B in Figure 2.2). It may be avoided to traverse such paths and also reduce the needed memory by invoking a technique called *path compression*. Path compression removes one-way branch nodes, so that each non-leaf node has two child nodes, resulting in a more balanced trie with less levels. That way, during the traversal of the decision tree, some bits of the incoming address may not be inspected.

An example of applying path-compression on the trie of Figure 2.2 may be seen in Figure 2.3. Note that additional information is stored on the trie to ensure the correct matching operation during the traversal of the trie: (a) each node is annotated with the bit position of the incoming address to be inspected next and (b) prefixes may need to be stored in the nodes where path-compression was applied in order to perform a check that the prefix match is valid (due to the non-inspection of some bits on the one-child nodes paths, the depth of a node is no longer equal to the length of the address prefix stored).

Traversing the path-compressed trie is similar to the one of binary tries, except for

the following differences: (a) the bit of the incoming address to be inspected is the one indicated by the bit-number field in the visited node, instead of just the next bit, and (b) when a prefix node is encountered, a comparison to the actual address prefix is performed. If a match occurs, the prefix is stored as a match and the traversal continues. The procedure stops when reaching a leaf node or when a mismatch occurs. The result of the lookup is the last matched prefix.

Figure 2.3: A path-compressed trie for a set of address prefixes. Prefix nodes are shown in a darker color. As an example, the path followed to match the incoming address 010000 to prefix B is shown. The inspection starts from the 1st bit of the incoming address (0) and thus we go to the left. This is a prefix node, so a successful prefix matching is performed for the corresponding part of the incoming address (0) and prefix A is stored as a match. Then we skip the 2nd bit of the incoming address and its 3rd bit (0) will be inspected as indicated by the bit-number field and thus we go to the left. This is again a prefix node, so a successful prefix matching is performed for the corresponding part of the incoming address (01000) and prefix B is stored as a match. Since this is a leaf node, the process completes and it reports a match to prefix B.

Path-compression was first introduced in the PATRICIA scheme by Morrison in [19]. This was modified later by Sklower, in [23], to also support longest prefix matching and non-contiguous masks. The most commonly available implementation of a path-compressed trie is the one found in the BSD Unix kernel, also known as  $BSD\ trie$ , where during the lookup process a backtrack occurs in order to retrieve the longest prefix match. This means that the worst-case search time is O(2\*W), where W is the address width. Even for a efficient implementation of the BSD trie, the worst-case search time would be at best O(W). This indicates that the path-compressed trie does not scale well in terms of the address width. This is the reason why the rest sequential "search on length" approaches to be presented focus on improving the worst-case search time complexity by reducing the trie depth furthermore.

#### 2.1.3 Multibit Tries

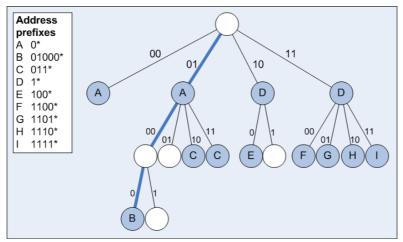

Multibit tries are an improvement of the binary tries. They are a sequential "search on length" approach that provides a constant factor improvement. Instead of inspecting

one bit at a time, they inspect several bits simultaneously. The number of bits that are inspected per step is called stride. As a result, the trie depth decreases and the branching factor of a node increases, as each node has now  $2^k$  child nodes, where k is the stride. A multibit trie may have a fixed stride (all nodes of a level have the same stride) or a variable stride. The process of searching in a multibit trie is almost identical to the binary trie, except that more bits may be inspected per step. An example variable-stride multibit trie based on the binary trie of Figure 2.2 is depicted in Figure 2.4.

Figure 2.4: A variable-stride multibit trie for a set of address prefixes. Prefix nodes are shown in a darker color. The stride of each node is the number of bits that need to be inspected in the next search step. Note the duplication and prefix expansion of nodes A, D and C. As an example, the path followed to match the incoming address 010000 to prefix B is shown.

Choosing the optimal strides is a trade-off between search speed (trie depth) and memory requirements (number of nodes). Because multibit tries cannot support arbitrary prefix lengths, it is needed to transform the prefix addresses into a compatible set where some prefixes need to be expanded. For example, in Figure 2.4, prefixes A and A needed to be expanded into 2 bits and prefix C into 4 bits. Prefix expansion leads to more memory use. Also, using a fixed stride tends to waste more memory due to unnecessary node duplications.

In [28], Srinivasan et al. present a method to select the optimal strides for fixed-stride tries and variable-stride tries, based on the given address prefixes. They use dynamic programming in order to minimize memory requirements and guarantee a worst-case search time.

Another practical approach for choosing the strides was followed from Gupta et al. in [12]. They noticed that in a typical backbone router of the time most of the address prefixes had a length of 24 bits or less. So, they opted for a first-level stride of 24 bits and a second-level stride of 8 bits. In this way, only two steps are needed for address lookup in the cost of extra memory resources (i.e. just the first-level memory size is 32 MBytes).

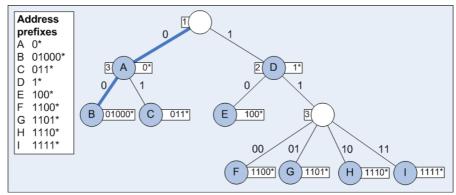

#### 2.1.4 Level-Compressed Tries

Nilsson et al. in [20] combined the multibit trie (see Section 2.1.3) with the path compression technique (see Section 2.1.2) to gain in search time. The new scheme they introduced is also a sequential "search on length" approach and is called *Level-Compressed Tries* (LC-Tries). In level-compression, k-level full binary subtries are recursively replaced with a corresponding one-level k-stride multibit trie. That way the initial k levels are "compressed" into one and the search time is reduced. An example LC-Trie is shown on Figure 2.5, based on the path-compressed trie of Figure 2.3.

Figure 2.5: A Level-Compressed trie for a set of address prefixes. It is the result of transforming the path-compressed trie of Figure 2.3 into a multibit trie. As an example, the path followed to match the incoming address 010000 to prefix B is shown.

An optimization to the level-compression technique is to loose the criterion for subtrie replacement. Instead of demanding a full binary subtrie, we may demand only a fraction of branches to be present. The required fraction is represented by the fill factor x ( $0 < x \le 1$ ) that may be used as the deciding value. The fill factor offers the possibility of a trade-off between time (trie levels) and memory requirements (number of nodes); using low fill factors decreases the trie depth, by increasing the branching factor, but may introduce unnecessary leaf nodes.

This approach of combining multibit tries with compression yields fast search times and has been used by various schemes, like the *full expansion/compression scheme* by Crescenzi et al. in [5] and the *Lulea algorithm* by Degermark et al. in [7].

#### 2.1.5 Hierarchical Intelligent Cuttings (HiCuts)

The *Hierarchical Intelligent Cuttings* (HiCuts) algorithm introduced by Gupta and McKeown in [14] is targeted for packet classification, where the search space is multi-dimensional.

In HiCuts, heuristic methods are used to partition the multi-dimensional space and to create a tree to search the partitioned space. Each leaf node of a HiCuts tree represents a small set (bucket) of matches that must be searched sequentially in order to obtain the best match. The characteristics of the HiCuts tree are decided based on the characteristics of the search space. The parameters of the HiCuts heuristics may be

tuned in for a trade-off between search time and memory requirements.

In our problem domain, where we deal with address lookup, the search space is single-dimensional. An example HiCuts tree for address lookup is depicted in Figure 2.6. Note that HiCuts actually constructs a variable-stride multibit trie with leaf nodes containing more than one address ranges.

Figure 2.6: A HiCuts tree for address lookup for a set of address prefixes. The HiCuts method has been applied for a single dimension in order to support the single-dimensional search space of address lookup. The maximum bucket size was set to 2 and the maximum number of cuts was set to 4. Bucket nodes are shown in a darker color. An example traversal for matching the incoming address 010000 is shown. Traversing the HiCuts tree directs us to bucket  $\{A, B\}$ , where a sequential longest matching procedure matches the incoming address to the address prefix B.

A similar approach to HiCuts was introduced by Woo in [34], called modular packet classification. This is a solution for the packet classification problem based on a multistage search over ternary strings representing the classification rules. There are three steps of searching performed to classify a packet: search an index jump table that points to a search tree, searching the corresponding tree to reach a bucket, search into the bucket to retrieve a match. The second and third search resemble the HiCuts procedure. The interesting part is the beginning of the search where selected bits of the input packet are addressing the index jump table. An example of modular packet classification modified for address lookup is depicted in Figure 2.7.

#### 2.1.6 Binary Search on Length

The trie "search on length" approaches presented so far were sequential approaches; in each step one or more bits of the incoming address were inspected leading to the reduction of the search space. Another sequential "search on length" approach would be to organize prefixes into different hash-tables according to their lengths and start the search from the hash-table holding the longest prefixes using hash techniques [32]. The latter technique does not result in a reduction of search time.

Waldvogel et al. in [32] suggested a binary "search on length" approach where the search space is reduced by half after every step. In each step the corresponding length hash-table is searched to check if a match exists in the given length and to decide how to proceed; in which half to continue the search. To ensure choosing the correct next step (checking for shorter or longer length) extra prefixes (called markers) are added to

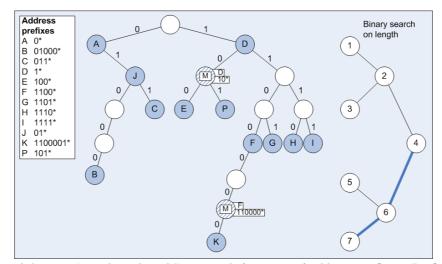

Figure 2.7: The modular packet classification approach for address lookup for a set of address prefixes. The approach has been applied for a single dimension in order to support the single-dimensional search space of address lookup. The maximum bucket size was set to 2 an the maximum number of cuts was set to 4. Bucket nodes are shown in a darker color. Bit; denotes the bit to be inspected. An example traversal for matching the incoming address 110000 is shown. Traversing the structure is the same with HiCuts, except for the first step were bits Bit5 and Bit3 (10) are searched in the index jump table and guide the search to the corresponding search tree.

Figure 2.8: A binary "search on length" approach for a set of address prefixes. Prefix nodes are shown in a darker color. Markers are notated with 'M'. The trie is not used during the search; it is present only for clarification. As an example, the path followed to match the incoming address 11000010 to prefix K is shown. We begin by searching in the table for length 4 and a match occurs with prefix f, so we move to search the table for length 6. A match occurs with the marker  $110000^*$ , so we move to search the table for length 7, where the final match with prefix K is found. (If the marker  $110000^*$  was not there, then a mismatch would have happened and we could not finally get the correct prefix match. If the incoming address was not an exact match with prefix K, then we would not be able to get the correct prefix match (i.e. prefix F). This is why marker nodes also hold the best matching prefix (i.e. prefix F) so far.)

the tables. So, when looking for a match in a specific prefix length table, if a match is found, the search proceeds to longer lengths; otherwise it proceeds to shorter lengths.

To perform the binary "search on length" a binary tree and the corresponding length prefix hash-tables are needed. Figure 2.8 is an example of such a structure. The trie in the figure is not needed but it is shown for clarification purposes. The search is performed by traversing the binary tree on the right-side. Depending on the visited node of the binary tree, the corresponding hash-table is checked for a match. Each hash-table for prefix length l stores the prefixes and markers of the level l of the trie.

#### 2.1.7 Sequential Search on Values

The simplest method for address lookup is a sequential "search on values". In this an exhaustive linear search is performed; the incoming address is attempted to be matched with each one of the address prefixes one by one. Every time that there is a match, the longest match is kept and the process continues until all the address prefixes have been checked. Although this scheme is straightforward and independent of the address width, the required time scales linearly with the number of address prefixes, so it is prohibited to be used in the current internet traffic conditions. Non-sequential "search on value" approaches are preferable and are presented in the following sections.

#### 2.1.8 Range Tree

The range tree is a typical binary "search on values" approach. Instead of moving on the length dimension, the search is performed by moving on the values dimension. This means that the range tree performs value comparisons to traverse the search space.

The search in a range tree is done in a similar way as the known binary search. In every node, one value is compared against the incoming address. Depending on the outcome of the comparison, we move to the next corresponding node, until a leaf node is reached and get a range match. The range tree divides the search space in two parts after every comparison. So, it is important to choose the optimal values to compare in every step. It must be noted that we no longer try to match address prefixes, but rather find the address range that an incoming address belongs to. This means that the values to be compared at each step must have the same width as the incoming address and the address prefixes have been expanded to this common length.

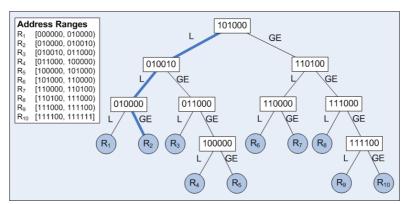

An example range tree may be seen in Figure 2.9. Note that the range table covers the entire address space. Range trees lead to more balances trees, with smaller depth, but the cost of memory accesses is higher, since more data need to be retrieved per step.

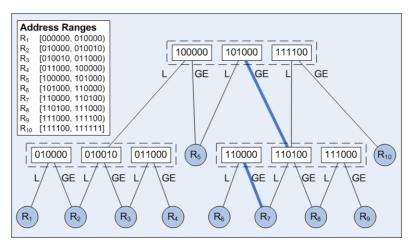

A descendant method of the range tree is the *multiway range tree* [33], where instead of a single comparison per step, more comparisons are performed. In a multiway range tree, internal nodes may have k branches by performing k-1 comparisons. An example multi-way range tree is shown in Figure 2.10 and is the equivalent of the single-way range tree of Figure 2.9. It can be seen that the tree depth was further reduced at the expense of higher needed memory bandwidth and resources.

Figure 2.9: A binary range tree for a set of address prefixes translated into range bounds. Range nodes are shown in a darker color. As an example, the path followed to match the incoming address 010000 to range  $R_2$  (prefix B) is shown. The search starts from the root node, where incoming address 010000 is compared to 101000 and is found to be smaller (L). Thus, we visit next its left child, where 010000 is found to be less (L) than 010010. The process continues until the range node  $R_2$  is reached.

Figure 2.10: A multiway range tree for a set of address prefixes translated into range bounds. Range nodes are shown in a darker color. As an example, the path followed to match the incoming address 110000 to range  $R_7$  (prefix F) is shown. The search starts from the root node, where incoming address 110000 is compared against 100000, 101000 and 111100 and is found to be larger (GE) than 101000 and less than 111100. Thus, we visit next the right node of the second level, where 110000 is found to be egual (GE) to 110000 and less (L) than 110100. So, we visit next node  $R_7$  which happens to be a range node and the search is completed.

#### 2.1.9 TCAMs

Using the hardware element of *Ternary Content Addressable Memories* (TCAMs) is an attractive hardware-based solution for constant-time address lookup. A TCAM, unlike regular memories, is addressable by data. The user supplies a query data and the memory tries to find it and returns the address that the data are stored (if they exist). Furthermore, TCAMs allow a third matching state "X" (don't care), instead of matching

just zeros and ones. This means that a memory entry in TCAMs may hold the binary value of the address prefix to be matched, along with a mask specifying which bits of the memory entry should be compared to the query data.

Such a structure is all that is needed to perform address lookup. The TCAM is set up with the address prefixes/masks, so that a longest prefix match may be done in every clock cycle (O(1) search time). Using TCAMs is like performing an exhaustive sequential "search on values" but in a completely parallel fashion; all the comparisons happen at the same time due to the TCAM structure (see Figure 2.11).

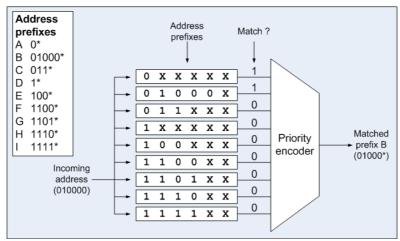

Figure 2.11: The TCAM structure for address lookup for a set of address prefixes. Note the existence of a priority encoder because multiple memory entries may match for a single search key. The TCAM has been properly set up with the address prefixes values and masks. An example lookup for matching the incoming address 010000 is shown.

Although TCAMs offer the best available lookup time, their use is reasonable only for small lookup tables. TCAMs suffer from four deficiencies [31]: (1) high cost per bit compared to other memory technologies, (2) storage inefficiency, (3) high power consumption, (4) limited scalability to long input keys.

In [27], Spitznagel et al. introduced the extended TCAM to address the power consumption and storage inefficiency problems of TCAMs by limiting the active regions of the device during a search and by employing a multi-level memory hierarchy. Despite the improvements, using TCAMs is still not a suitable solution for the future large-scale lookup problems.

#### 2.1.10 IPstash

In [17], Kaxiras and Keramidas proposed a memory architecture (the *IPStash*) for address lookup that acts as a TCAM replacement. Their approach offers higher performance and significant power savings compared to the TCAM approach, while allowing for high update rates.

Their proposed architecture is similar to the set-associative caches but is designed to facilitate address lookup (in particular longest prefix matching). IPStash holds a

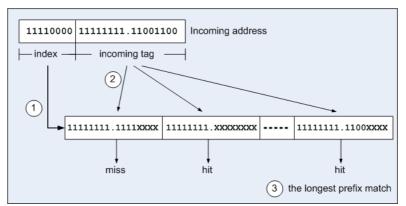

complete lookup table instead of just a small part of the data set (as caches do). It is based on the observation that address lookup only requires associativity depending on the routing table characteristics. To perform the address lookup in IPStash, first they define the index and tag parts of the incoming addresses. The index is set to a static length (i.e. the 8 most significant bits) and the tag is set to be a variable-number of N following bits. The IPStash lookup process consists of, first, storing the prefixes into a set-associative structure according to their indices and then determine within a set which is the longest prefix match based on the tags (see Figure 2.12).

Figure 2.12: The IPStash architecture for address lookup (longest prefix matching) for a set of address prefixes. The index (8 most significant bits) of the incoming address is used to "retrieve" (using an indexing function) a set of candidate matching prefixes out of a set-associative structure. Then each prefix in the set is attempted to be matched to the incoming address. What needs to be matched is the tag of the incoming address (the N bits following the index). The tag may be of variable length and this length is stored in the structure. Since there may be many candidate matches, the longest prefix match is chosen by determining which matched tag is wider.

To benefit from this approach they investigated on the lookup table characteristics in order to increase the index length (to address a larger number of sets) and partition the lookup table into classes (each with its own index). The resulting increase in index numbers and, thus, the requirement of extra hash functions led to the application of skew associativity where different indexing functions are used for each of the set-associative ways.

## 2.1.11 Bloom Filters

The Bloom filter, conceived by Bloom in 1970 [3], is a probabilistic data structure that is used to test if an element is a member of a set of elements or not. A Bloom filter is actually a bit-vector of m bits, initially all set to 0. Alongside, there are k hash functions defined, each one of them mapping a set element to one of the m bits of the Bloom filter. Before using the Bloom filter, it must be programmed for the given set of elements. To add a set element A, the element A is fed to the k hash functions in order to get k bit-vector positions and set them to 1. To search if an element B is part of the set of elements, the element B is fed to the k hash functions to get k bit-vector positions. If any of the bits in these k positions is 0, then B is not part of the set. Otherwise, if all

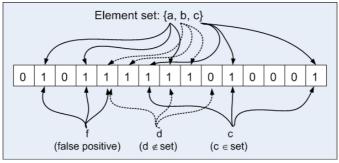

bits are 1, then B belongs to the set with a certain probability; B may either be a part of the set or not (false positive). This ambiguity comes from the fact that the bits of the Bloom filter may be set by any of the set elements. The probability of a false positive may be reduced (but not eliminated) by changing (a) the number of entries stored in a filter, (b) the size of the filter, (c) the number of hash functions used to probe the filter. An example of a Bloom filter is shown on Figure 2.13.

Figure 2.13: An example of the Bloom filter data structure. In this case the Bloom filter is 15-bits wide and there are three hash functions. The original set element that programs the Bloom filter is a, b, c. The 3 hash functions are applied for each element, resulting in the filling with ones of the corresponding positions in the bit-vector. Searching if element d belongs in the set fails, because one of the bits retrieved from the hash functions is 0. Examples of a successful search (for element c) and a false positive search (for element f) are also shown.

Another approach to Bloom filters are the counting Bloom filters [4], where m counters are used instead of an m bit-vector. The use of counters allows the deletion of elements from the original element set by decrementing the respective counters. This dynamically changing of the element set was not possible on the original Bloom filters. The trade-off is that a counting Bloom filter will occupy more space compared to the original Bloom filters.

Dharmapurikar et al. in [8] used Bloom filters for address lookup. Their approach consists of sorting the address prefixes by prefix length. For each prefix length they associated a Bloom filter and programmed it. Also, hash-tables were constructed for each prefix length. The search on this approach starts by performing parallel queries to the Bloom filters by querying the respective part of the incoming address. The result is a bit-vector stating the matches for each prefix length (false positives may occur in it). Afterwards, the corresponding length hash-tables are searched, starting from the longest prefix length ones. The search stops when a match is found or when all hash-tables indicated by the bit-vector have been searched. Searching in the hash-tables eliminates the effect of false positives.

Their motivation for using Bloom filters was to avoid the inefficient TCAMs and use modest amounts of SRAMs. The proposed architecture managed to achieve better performance and scalability than TCAM approaches. They researched on system configurations (amount and allocation of memories) to minimize the number of hashtable searches per address lookup. To succeed they introduced the use of (a) asymmetric Bloom filters (scaled width Bloom filters depending on the prefix distribution), (b) direct

lookup arrays (for smaller hash-tables) and (c) controlled prefix expansion<sup>1</sup> (to reduce the number of required filters). Performance may now stay constant for longer address widths or larger lookup tables, as long as memory requirements scale linearly with the number of address prefixes. Using Bloom filters for address lookup achieved on average-case one hash search per lookup or, at worst-case, two hash searches and one array access per lookup.

## 2.1.12 Tree Bitmap

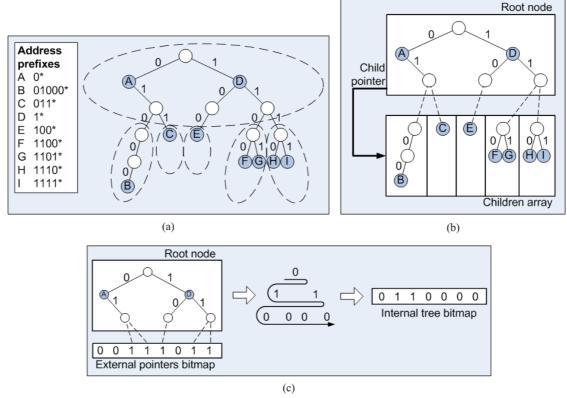

Eatherton et al. in [10] introduced the *tree bitmap* data structure that resembles a multibit trie and the compression techniques of Lulea [7]. Their main effort was into compressing the address prefixes as much as possible in order to reduce the memory access width of the lookup process.

Figure 2.14: The tree bitmap data structure. In (a), the original trie is shown partitioned into 3-stride multibit nodes. Each multibit node holds a position to an array as shown in (b). Note the single pointer to the beginning of the child array. The result array and result pointers are not shown (assume that the dark shaded prefix nodes point to it). The way to retrieve the two bitmaps of a multibit node is shown in (c).

<sup>&</sup>lt;sup>1</sup>Controlled prefix expansion [28] selects a small number of prefix lengths to be searched. The address prefixes with different length, than the selected ones, are expanded into multiple entries of the next higher selected length.

They used a data structure where they first partition the original trie into multibit nodes. Each multibit node is a k-level tree of the trie. For each multibit node, the necessary search information are encoded as: (a) a pointer to the children multibit nodes, (b) a bitmap for the internal stored prefixes of the multibit node and (c) a bitmap for the external pointers of the multibit node. All child nodes of a multibit node are stored contiguously in the memory, thus a single child pointer is required per node. At every step of the search, a multibit node produces the pointer to the next multibit node to be processed at the next step. When the search terminates, a result pointer points to the result array to determine the action to be taken by the lookup process. An example of a tree bitmap data structure is shown in Figure 2.14.

The tree bitmap data structure may be used with any structure of modern memories by tuning the multibit node strides for the specific memory characteristics. Changing the stride affects the number of bits that represent each multibit node data structure. Eatherton et al. applied a set of optimizations to further reduce the size of multibit nodes, such as: (a) initial array optimization, where an initial array is used like in modular packet classification (see Section 2.1.5), (b) end node optimization, where multibit nodes containing just a prefix node are eliminated and the necessary data are integrated to the parent multibit node, (c) split tree bitmaps, where the two bitmaps of a multibit node are retrieved through separated memory accesses, (d) segmented bitmaps, where a bitmap is split in two and (e) using CAM nodes that occupy the same space with a multibit node that has few internal prefixes.

## 2.1.13 Pipelines

Assuming that the lookup decision trees are stored in a memory, then performing the decision tree traversal requires multiple memory accesses to match the incoming address. To make the process faster a multiple-stage *pipeline* may be used, where the decision tree is organized in a multitude of memory units. The main issue with pipeline approaches is how to organize the decision tree in the pipeline stages in a balanced way to keep the memory utilization high, while retaining the ability for fast updates.

A lot of research exists on mapping a decision tree to pipeline stages. A simple approach is to match a tree level to a pipeline stage. In [15], Hasan and Vijaykumar describe a more elaborate scheme where a trie is mapped to pipeline stages based on the height of its nodes. They managed to achieve a scalable design that guarantees worst-case performance bounds.

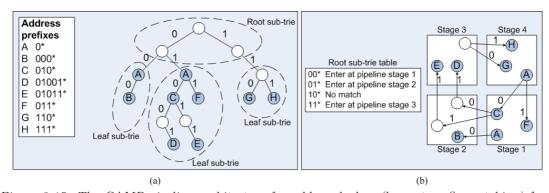

Another approach to pipeline is the use of circular pipelines, where a lookup may be initiated at any stage. Using a circular pipeline decouples the number of pipeline stages from the number of decision tree levels. In [18], Kumar et al. introduced the Circular, Adaptive and Monotonic Pipeline (CAMP) architecture, which is an extension of the circular pipelines. In CAMP, a trie is split into a root sub-trie and multiple leaf sub-tries (see Figure 2.15). The root sub-trie is implemented as a table that directs which leaf sub-trie to visit. Each leaf sub-trie is mapped to start at a different pipeline stage. They developed a mapping algorithm that results into a large number of small memory stages that facilitates a high troughput.

Figure 2.15: The CAMP pipeline architecture for address lookup (longest prefix matching) for a set of address prefixes. In (a), the original trie is depicted along with its partition into the root sub-trie and the leaf sub-tries. There has been a prefix expansion to ensure that all prefixes are longer than 2-bits. In (b), the leaf sub-tries are mapped to the pipeline stages and the pipeline stage to enter is determined by looking in the root sub-trie table.

## 2.2 The Range Trie

In the previous section, a multitude of current address lookup schemes was presented. These schemes have not managed to keep up with the pace of the internet traffic/speed growth. This pointed out the need for an address lookup method that has (a) low latency, (b) high throughput, (c) low memory requirements and (d) maintain these properties even if the lookup table size and address width are increasing. Furthermore, it would be useful if the lookup structure is fast to construct and update. A method promising to solve these problems, is the *Range Trie* algorithm introduced by Sourdis in [26] and it is presented in this section.

The Range Trie is a new approach for address lookup. It is considered to be between the range tree approaches and the trie approaches; hence the name Range Trie. While tries perform an exact match in parts of addresses and range trees perform comparisons of full addresses, the Range Trie lies between them by performing comparisons of parts of addresses. It may not be categorized neither as a "search on length" approach, nor as a "search on values" approach, but rather as a combination, as it tries to combine the benefits of each concept.

The Range Trie is a tree data structure that is traversed to perform the search, according to the algorithm specifications. The key effort during the construction of a Range Trie is to perform as many comparisons (on parts of addresses) as possible per traversal step and thus utilizing optimally the given memory bandwidth. Also, that way the branching factor of each node increases, resulting into a shorter tree structure.

In the rest of this section, all the details regarding the Range Trie algorithm are presented. Specifically, in Section 2.2.1 the Range Trie is introduced in more details, followed by Section 2.2.2, where the rules that guide the construction of a Range Trie are defined. In Section 2.2.3 the complete Range Trie structure is described, along with the search method to traverse the Range Trie to retrieve the matching range. An automatic way to construct a Range Trie structure using heuristic approaches is outlined in Section

2.2.4. Section 2.2.5 outlines the required modifications of the Range Trie algorithm in order to support also longest prefix matching. Finally, Section 2.2.6 concludes the Range Trie description by summarizing its achievements.

#### 2.2.1 Range Trie description

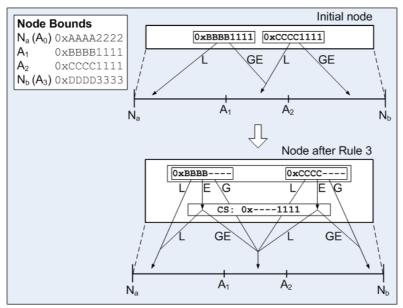

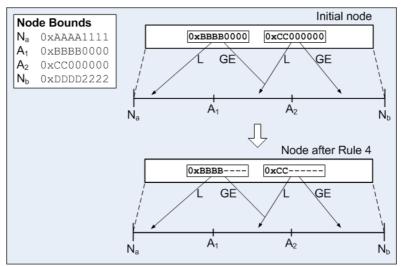

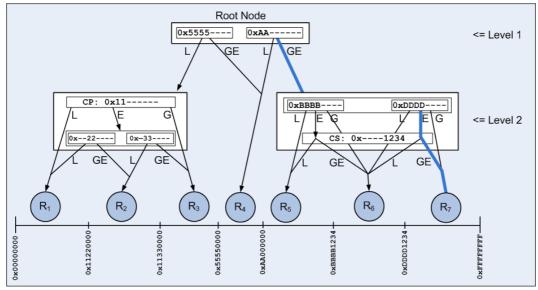

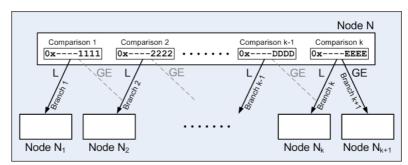

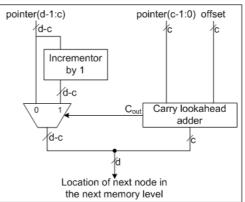

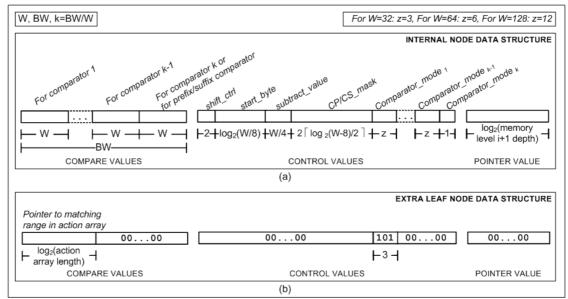

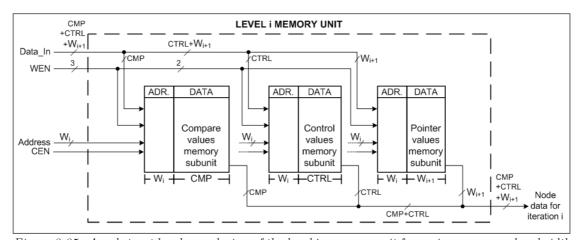

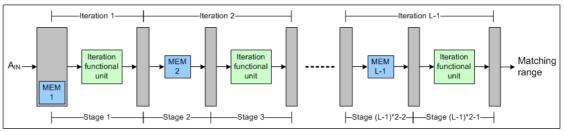

The Range Trie tackles efficiently the address lookup problem in the context of internet routing, but it may be used in other research fields requiring a form of lookup. The address lookup problem is defined as follows: Given an address space  $[0, 2^n)$  and r unique IP addresses/bounds  $A_i$ , where  $0 < A_i < 2^n - 1$  and i = 1, 2, ..., r, that define r+1 address ranges  $R_j$  (j = 1, 2, ..., r + 1), then an address lookup is to determine the range  $R_j$  an incoming address  $A_{IN}$  belongs to.