# p+ poly-Si(O<sub>x</sub>) passivating contacts for double-side textured c-Si solar cell

Chengli Hou

## p<sup>+</sup> poly-Si(O<sub>x</sub>) passivating contacts for double-side textured c-Si solar cell

by

Chengli Hou

to obtain the degree of Master of Science Sustainable Energy Technology at the Delft University of Technology, to be defended publicly on Friday August 26, 2022.

Student number: 5376068

Project duration: October 15, 2021 – August 26, 2022

Thesis committee: Prof. dr. ir. Olindo Isabella, TU Delft|EEMCS-ESE-PVMD|Full Professor|Supervisor

Prof. dr. ir. Miro Zeman, TU Delft|EEMCS-ESE-PVMD|Full Professor Dr. Massimo Mastrangeli, TU Delft|EEMCS-ME-ECTM|Assistant Professor

Dr. Guangtao Yang, Trina Solar|Senior Scientist|External

Dr. Zhirong Yao, TU Delft|EEMCS-ESE-PVMD|PostDoc researcher

This thesis is confidential and cannot be made public until August 26, 2022.

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## Acknowledgements

Firstly, I would like to thank my daily supervisors Dr.Zhirong Yao and Dr.Guangtao Yang for their continuously kind and careful guidances and advising on my thesis. Thank them for training me all the knowledge and equipment instructions at cleanroom and talking and discussing with me all the experiment designs, results, difficulties and corresponding theories no matter the results are good or not. Their knowledge really helps me a lot for my experiments. Then, I want to give thanks to my supervisor Prof.dr.Olindo Isabella who gave me the chance to carry out projects in c-Si solar cell aspects. And the c-Si cluster meeting held by him always gave me a lot of ideas and inspirations for my next steps.

Then, I want to thank all the people that ever help me with my projects in PVMD group, Dr.Paul Procel Moya for his plentiful knowledge on simulations, Dr.Can Han for her knowledge on TCO, Ir.Yifeng Zhao, Ir.Liqi Cao and Ir. Jin Yan for their help at lab. I also want to give thanks to the technicians Martijn Tijssen, Daragh O'Connor, Stefaan Heriman and Engin Ozkol at EKL, Pauline and Roald at Kavli Nanolab who were always there to deal with the troubles I came across with the equipments. And I also want to thank master students, Jing, Fabian, Katarina, Mohua, Marnix, Rutger who spent a lot of time at lab together with me and thanks to Astrid at TNO for help on ECV measurements and Bas at S-ALD for help on AlOx deposition.

My thanks also go to my colleges at office, Nida, Fabian and Jing for their help and accompany and also a lot of my friends in Delft, Jing Zhang, Wanyu Si, Zelin Wang, Qi Zheng, Yuanhao Liu, Zhiyi Wang and. etc for giving me a lot of fun and laughs. I will memorized the precious time we hang out for drinking, eating, travelling and hiking.

Then, I also want to give thanks to my parents for always supporting me both moral and financial and giving me a lot of love. I also want to thanks myself for the choices studying Sustainable Energy Technology at TU Delft and carry out thesis projects at PVMD group and never give up.

I will miss all the time spent at Delft!

Chengli Hou Delft, August 2022

## **Abstract**

Silicon solar cells account for about 95% of the total photovoltaic market share. Poly-Si passivating contacts are promising techniques enabling high performance c-Si solar cells with conversion efficiency over 26.0%. The highly absorptive nature of poly-Si materials makes the transparent passivating contacts attractive, such as poly-Si( $O_x$ ). However, the research of  $p^+$  poly-Si( $O_x$ ) passivating contacts on a textured surface with a *in-situ* doping nature is still missing. Therefore, in this thesis, the optimization of  $p^+$  poly-Si( $O_x$ ) carrier selective passivating contacts on double side textured wafers are given and the application in solar cells is demonstrated.

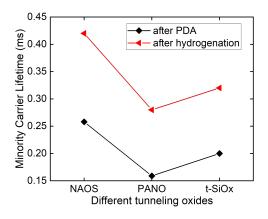

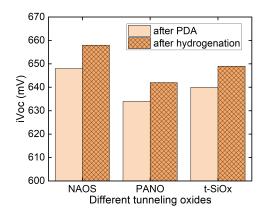

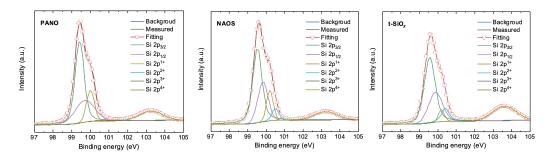

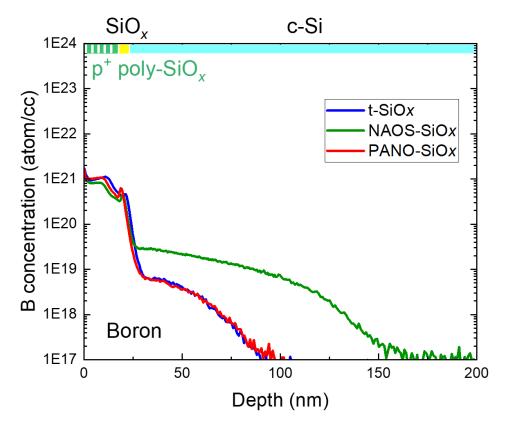

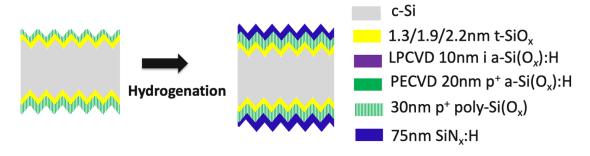

Firstly, the influences of different interfacial tunnelling oxides fabrication methods, nitric acid oxidation of silicon (NAOS-SiO<sub>x</sub>), plasma assisted N<sub>2</sub>O oxidation (PANO-SiO<sub>x</sub>), and thermal oxidation (t-SiO<sub>x</sub>) on the passivation of p<sup>+</sup> poly-Si(O<sub>x</sub>) passivating contacts are explored. It is found that Si<sup>4+</sup> stoichiometry in the tunnelling oxide layer is an indicator for its quality. There is a positive correlation between Si<sup>4+</sup> and SiO<sub>x</sub> density. The t-SiO<sub>x</sub> can be denser with higher Si<sup>4+</sup> compared to its counterparts NAOS-SiO<sub>x</sub> and PANO-SiO<sub>x</sub>. And fewer boron dopants in-diffuse phenomenon can be observed in the t-SiO<sub>x</sub> samples. Then, different intrinsic layer deposition approaches are explored. The intrinsic layer deposited by LPCVD results in higher i $V_{oc}$  compared to PECVD counterpart. The enhanced i $V_{oc}$  is given by suppressing the blistering which is caused by hydrogen accumulation at the interface between intrinsic layer and SiO<sub>x</sub>. It is assumed that less hydrogen accumulation exists in intrinsic layer deposited by LPCVD. Next, p<sup>+</sup> doping layer thickness is changed from 0 nm to 200 nm to observe its effect on the passivation quality. The optimum  $p^+$  doping layer thickness is found to be 100 nm with the highest  $iV_{oc}$ . After that, the hydrogenation process is introduced to enhance chemical passivation by coating SiN<sub>x</sub>:H and performing forming gas annealing. The highest i $V_{

m oc}$  with the standard hydrogenation process is 674 mV. In order to improve the hydrogen level of p<sup>+</sup> poly-Si(O<sub>x</sub>) passivating contacts, AlO<sub>x</sub>:H inserted layer is used for the hydrogen reservoir together with  $SiN_x$ :H. It results in an improved i $V_{oc}$  of 685 mV. It is assumed that the hydrogen in AlO<sub>x</sub>:H diffuses into c-Si/p<sup>+</sup> poly-Si(O<sub>x</sub>) interface and enhances the chemical passivation.

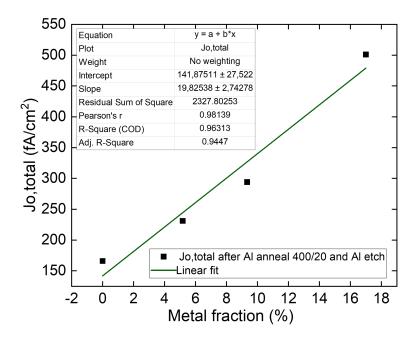

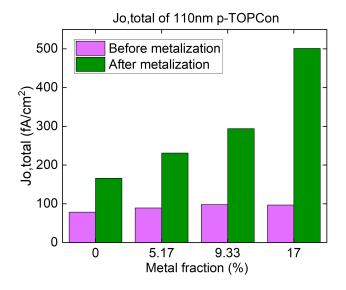

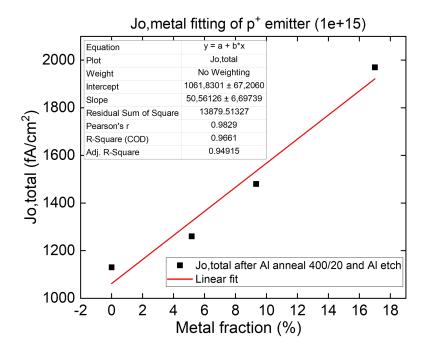

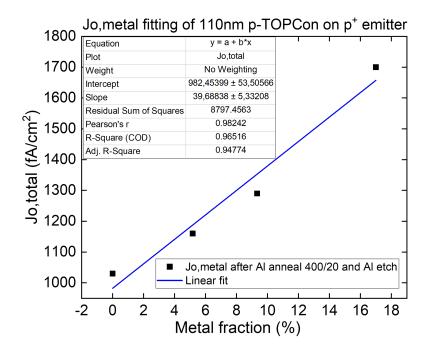

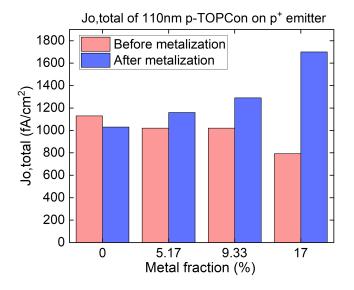

Besides, metallization methods of  $p^+$  poly-Si(O<sub>x</sub>) passivity contacts are also studied. There are two approaches to complete the metallization process. Firstly, with thin p<sup>+</sup> poly-Si(O<sub>x</sub>) passivating contacts, TCO is required to provide with the lateral and vertical carrier transport as respect to the carrier collection. However, it commonly brings with the TCO introduced sputtering damage. The iV<sub>oc</sub> losses are 70-90 mV when TCO is sputtered on p<sup>+</sup> poly-Si(O<sub>x</sub>) passivating contacts. When the thickness of p<sup>+</sup> doping layer is over 50 nm, sufficient lateral conductivity can be provided with thick p<sup>+</sup> poly-Si(O<sub>x</sub>) passivating contacts. Therefore, it can directly contact with metal which is the second method of metallization. However, when utilizing this metallization method, the metal induced recombinations need to be taken into consideration when contacting with  $p^+$  poly-Si( $O_x$ ) passivating contacts. Thus, the plot of  $J_{o,total}$  along with different metal fractions is fitted to extract  $J_{o,metal}$  of p<sup>+</sup> poly-Si(O<sub>x</sub>) passivating contacts with 100 nm p<sup>+</sup> doping layer. When contacting with evaporated aluminium, the measured  $J_{\text{o,metal}}$  is around 91 fA/cm<sup>2</sup>. In addition, after calculating, there is 24 mV i $V_{\text{oc}}$  loss when p<sup>+</sup> poly-Si(O<sub>x</sub>) passivating contacts contacting with metal. It is smaller than the loss induced by TCO sputtering. Therefore, the thick p<sup>+</sup> poly-Si(O<sub>x</sub>) passivating contacts with 100 nm p<sup>+</sup> doping layer directly contacting with metal is used as metallization method for the application in c-Si solar cell. In addition, after linear fitting and calculating,  $\rho_c$  between p<sup>+</sup> poly-Si(O<sub>x</sub>) passivating contacts with 100 nm boron doped layer and c-Si is about 23 m $\Omega$ · cm<sup>2</sup>.

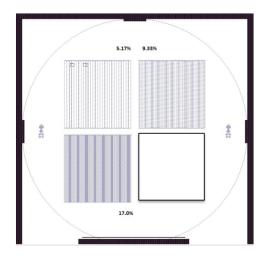

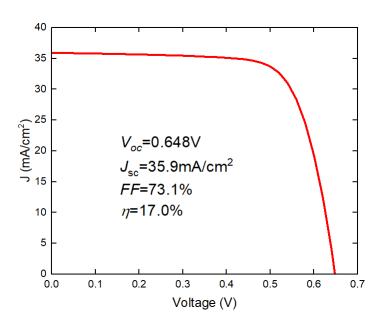

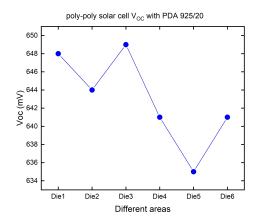

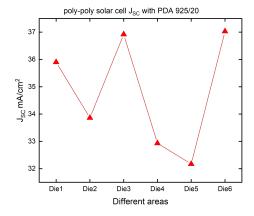

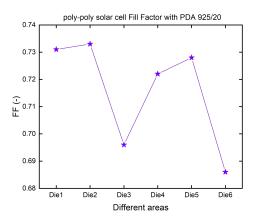

Finally,  $p^+$  poly-Si(O<sub>x</sub>) passivating contact is applied in c-Si solar cells together with  $n^+$  poly-Si(O<sub>x</sub>) passivating contact as front surface field. The poly-poly solar cell of the highest quality has the following electrical performance :  $V_{oc}$  is 648 mV,  $J_{sc}$  is 35.9 mA/cm<sup>2</sup>, FF is 73.1% and  $\eta$  is 17.0%. A roadmap to realize 22% is given by addressing the bottlenecks of poly-Si(O<sub>x</sub>) passivating contacts based c-Si solar cells.

## Contents

| A  | cknov | wledgements i                                                   |

|----|-------|-----------------------------------------------------------------|

| ΑI | ostra | ct i                                                            |

| 1  | Intro | oduction 1                                                      |

|    |       | Working principle of the solar cells                            |

|    | 1.2   | Solar cell loss mechanisms                                      |

|    |       | 1.2.1 Optical losses                                            |

|    |       | 1.2.2 Electrical losses                                         |

|    | 1.3   | poly-Si(O <sub>x</sub> ) passivating contacts                   |

|    | 1.0   | 1.3.1 Surface formation                                         |

|    |       | 1.3.2 Interfacial oxides                                        |

|    |       | 1.3.3 poly-Si(O <sub>x</sub> ) thin films                       |

|    |       | 1 7 ( ^/                                                        |

|    |       |                                                                 |

|    | 4.4   | 1.3.5 Hydrogenation                                             |

|    | 1.4   | Application in c-Si solar cells                                 |

|    |       | 1.4.1 Metallization                                             |

|    |       | 1.4.2 Solar cells                                               |

|    | 1.5   | Motivation and objectives                                       |

|    |       | 1.5.1 Motivations                                               |

|    |       | 1.5.2 Objectives                                                |

|    | 1.6   | Thesis outline                                                  |

| 2  | Exp   | erimental methods and Process techniques 22                     |

| _  |       | Fabrication process                                             |

|    |       | 2.1.1 c-Si absorber                                             |

|    |       | 2.1.2 Passivation samples preparation                           |

|    |       | 2.1.3 Solar cells fabrication                                   |

|    | 2.2   | Characterization techniques                                     |

|    | 2.2   | 2.2.1 Optical performance                                       |

|    |       | 2.2.2 Surface morphology                                        |

|    |       | 2.2.3 Lifetime and $J_0$ measurement                            |

|    |       |                                                                 |

|    |       | 2.2.4 Compositional analysis                                    |

|    |       | 2.2.5 Current-voltage measurement                               |

| 3  | Pas   | sivation of $p^+$ poly-Si( $O_x$ ) passivating contacts 45      |

|    | 3.1   | Absorber surface                                                |

|    | 3.2   | Interfacial oxides                                              |

|    | 3.3   | Ultra-thin $p^+$ poly-Si(O <sub>x</sub> ) thin films            |

|    |       | 3.3.1 Intrinsic layer deposition methods                        |

|    |       | 3.3.2 t-SiO <sub>x</sub> layer thickness                        |

|    |       | 3.3.3 Pre-annealing                                             |

|    |       | 3.3.4 PECVD p <sup>+</sup> doping layer optimization            |

|    | 3.4   | Optimization of hydrogenation scheme                            |

|    |       | TCO sputtering damage                                           |

|    |       | Thick p <sup>+</sup> poly-Si(O <sub>x</sub> ) thin films        |

|    | 0.0   | 3.6.1 p <sup>+</sup> doped layer thickness                      |

|    |       |                                                                 |

| 4  |       | stact properties of $p^+$ poly-Si( $O_x$ ) passivating contacts |

|    |       | Contact resistivity                                             |

|    | 49    | Metal-induced recombination 72                                  |

Contents

| 5  | App  | olication in c-Si solar cells                                      | 8′ |

|----|------|--------------------------------------------------------------------|----|

|    | 5.1  | Passivation optimization of ion-implanted p <sup>+</sup> emitter   | 8  |

|    |      | 5.1.1 NAOS protective layer                                        |    |

|    |      | 5.1.2 AlO <sub>x</sub> :H capping layer optimization               |    |

|    |      | 5.1.3 FGA conditions                                               |    |

|    |      | 5.1.4 Boron doping profile                                         | 8  |

|    | 5.2  | i-TOPCon solar cell on DST wafers                                  | 8  |

|    |      | 5.2.1 Electrical performance                                       | 8  |

|    | 5.3  | poly-poly solar cell on DST wafers                                 | 88 |

|    |      | 5.3.1 Electrical performance                                       | 88 |

| 6  | Con  | nclusions and Outlooks                                             | 92 |

|    | 6.1  | Conclusions                                                        | 92 |

|    |      | Outlooks                                                           |    |

|    |      | 6.2.1 p <sup>+</sup> poly-Si(O <sub>x</sub> ) passivating contacts |    |

|    |      | 6.2.2 poly-Si(O <sub>x</sub> ) solar cells                         |    |

| Re | fere | nces                                                               | 95 |

## List of Figures

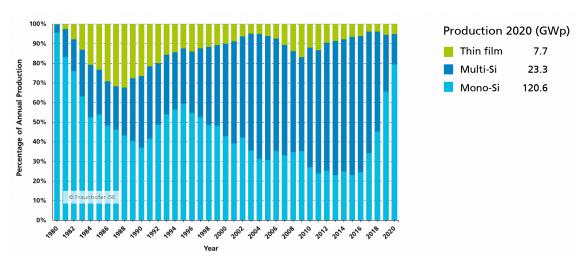

| 1.1  | Percentage of Global Annual Production [30] and [63]                                                               | 2   |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

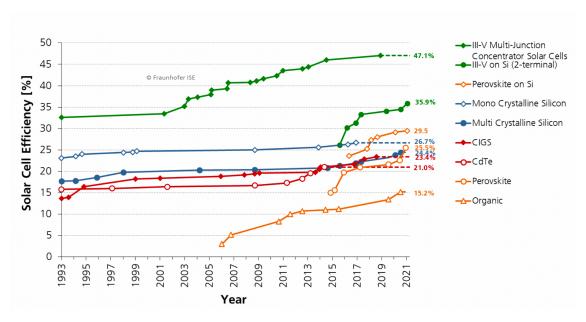

| 1.2  | Development of Laboratory Solar Cell Efficiencies [30] and [63]                                                    | 2   |

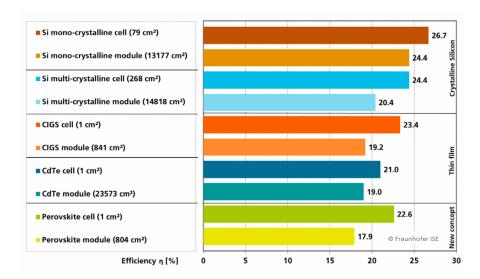

| 1.3  | Best lab cells versus Best lab modules [30] and [63]                                                               | 3   |

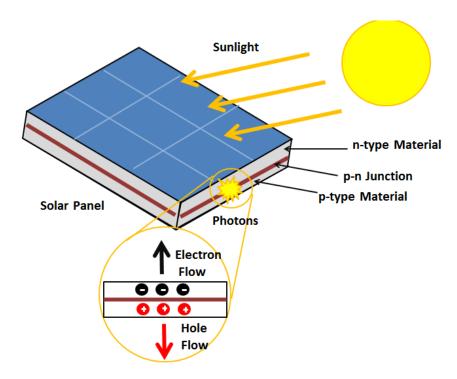

| 1.4  | Simple schematic of photovoltaic effect                                                                            | 4   |

| 1.5  | (a)Illustrating the absorption of a photon in a semiconductor with bandgap $E_{G}$ . The                           |     |

|      | photon with energy $E_{ph}$ =hv excites an electron from $E_i$ to $E_f$ . At $E_i$ a hole is created.(b)If         |     |

|      | $E_{ph}>E_G$ , a part of the energy is thermalized.[77]                                                            | 5   |

| 1.6  | The doping process illustrated using the bonding model.(a) A phosphorus (P) atom re-                               |     |

|      | places a Si atom in the lattice resulting in the positively-ionized P atom and a free elec-                        |     |

|      | tron.(b) A boron (B) atom replaces a Si atom resulting in the negatively ionized B atom                            |     |

|      | and a hole.[77]                                                                                                    | 6   |

| 1.7  | Formation of a space-charge region, when n-type and p-type semiconductors are brought                              |     |

|      | together to form a junction. The coloured part represents the space-charge region. [77]                            | 7   |

| 1.8  | A very simple solar cell model.(1)Absorption of a photon leads to the generation of an                             |     |

|      | electron-hole pair.(2)Usually, the electrons and holes will recombine.(3)With semiperme-                           |     |

|      | able membranes the electrons and the holes can be separated.(4)The separated elec-                                 |     |

|      | trons can be used to drive an electric circuit. (5)After the electrons have passed through                         |     |

|      | the circuit, they will recombine with holes.[77]                                                                   | 8   |

| 1.9  | The <i>J-V</i> characteristics of a p-n junction in the dark and under illumination[77]                            | 9   |

|      | The loss mechanisms of solar cell[77]                                                                              | 10  |

|      | Schematic of thermallization losses of spectral mismatch losses[77]                                                | 10  |

|      | Schematic of non-absorption losses of spectral mismatch losses[77]                                                 | 11  |

|      | Schematic of anti-reflection coating to reduce reflection losses                                                   | 11  |

|      | Schematic of texturing to reduce reflection losses                                                                 | 11  |

|      | Schematic of Shockley-Queisser efficiency[77]                                                                      | 12  |

|      | Schematic of Radiative recombination, Auger recombination and SRH recombination [77]                               |     |

|      | Illustrating dangling bonds (surface defects) on a semiconductor surface[77]                                       | 13  |

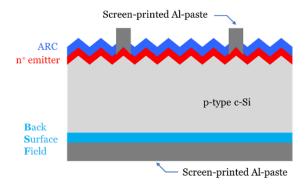

|      | Simple schematic of Al BSF solar cell                                                                              | 13  |

|      | Simple schematic of PERC solar cell                                                                                | 13  |

|      | FBC solar cell with TOPCon configuration [81]                                                                      | 14  |

| 1 21 | Single-diode model of solar cell                                                                                   | 14  |

|      | The influences of series resistance $R_s$ on the I-V characteristics of solar cell                                 | 15  |

|      | The influences of shunt resistance $R_p$ on the I-V characteristics of solar cell                                  | 15  |

|      | Simple schematic of all the solar cell losses                                                                      | 15  |

|      | Simple schematic of charge carriers transporting in n <sup>+</sup> poly-Si(O <sub>x</sub> ) carrier selective pas- | . • |

| 0    | sivating contacts                                                                                                  | 18  |

| 1 26 | H,O chemical passivation                                                                                           | 18  |

| 0    | THE SHORMOUN PROGRAMMENT                                                                                           | . • |

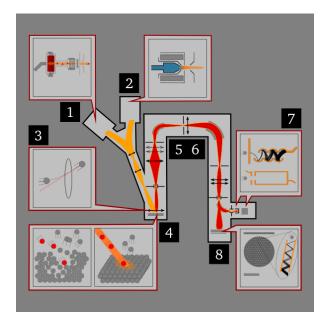

| 2.1  | Simple schematic of LPCVD equipment                                                                                | 24  |

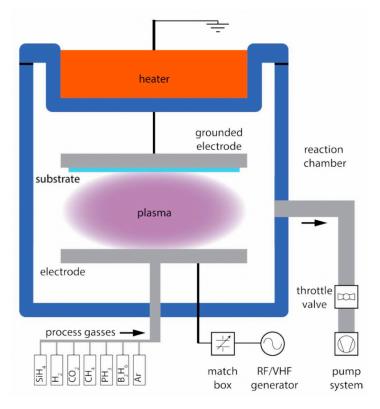

| 2.2  | Simple schematic of PECVD equipment                                                                                | 25  |

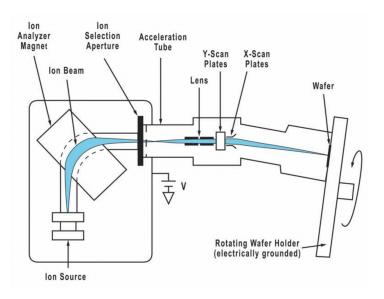

| 2.3  | Simple schematic of ion-implantation equipment                                                                     | 26  |

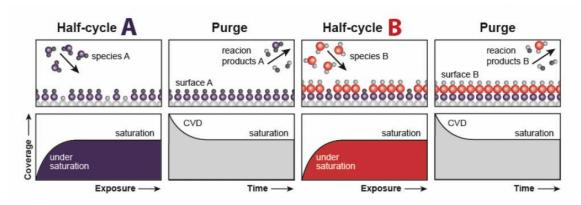

| 2.4  | Schematic of ALD process flowchart                                                                                 | 27  |

| 2.5  | Simple schematic of ALD process                                                                                    | 27  |

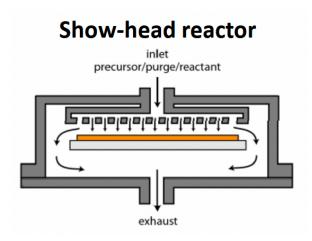

| 2.6  | Simple schematic of thermal-ALD equipment                                                                          | 28  |

| 2.7  | Schematic of spatial ALD                                                                                           | 28  |

| 2.8  | Simple schematic of spatial ALD equipment                                                                          | 29  |

| 2.9  | Simple schematic of sputtering equipment                                                                           | 29  |

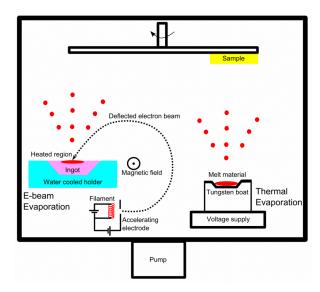

|      |                                                                                                                    | 30  |

|      | Simple schematic of evaporation equipment [93]                                                                     | 31  |

List of Figures vi

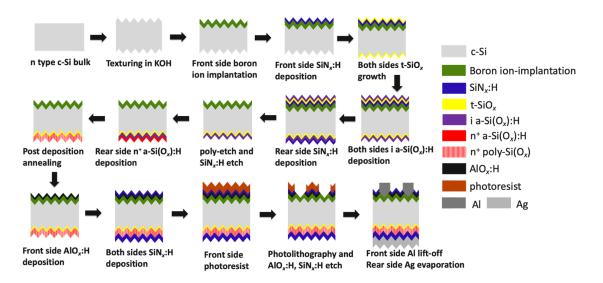

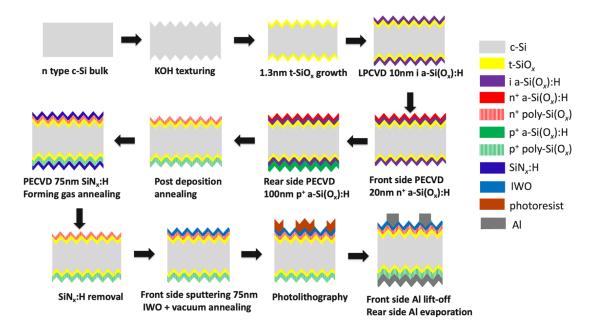

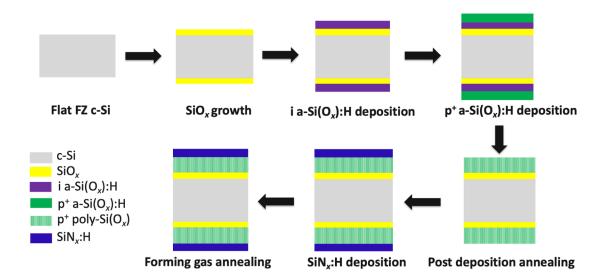

| 2.12 | Simple schematic of i-TOPCon mono-facial solar cell on DST wafers                                                                              | 31             |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.13 | Flowchart of texturing process                                                                                                                 | 32             |

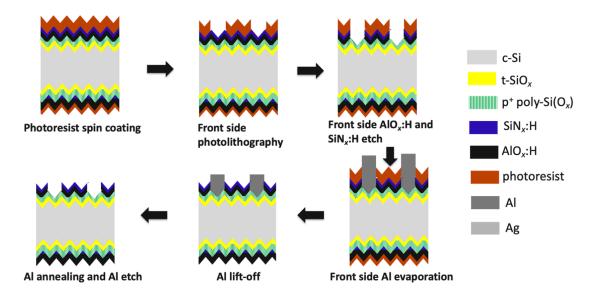

| 2.14 | Simple flowchart for poly-poly mono-facial solar cell                                                                                          | 34             |

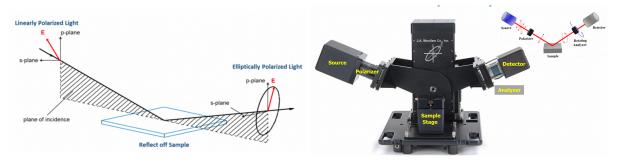

| 2.15 | Schematic of the principle of Spectroscopic ellipsometry                                                                                       | 37             |

| 2.16 | Simple schematic of Spectroscopic ellipsometry by J. A. Woollam Co.                                                                            | 37             |

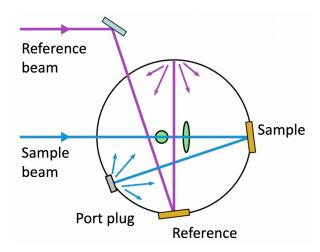

| 2.17 | Simple schematic of the reflectance measurement equipment                                                                                      | 38             |

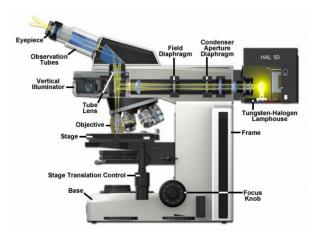

| 2.18 | Simple schematic of the components of the microscope [66]                                                                                      | 38             |

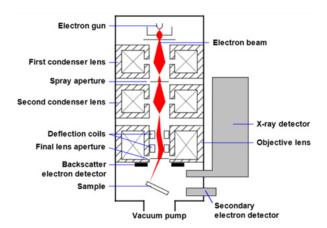

|      | Simple schematic of SEM[39]                                                                                                                    | 39             |

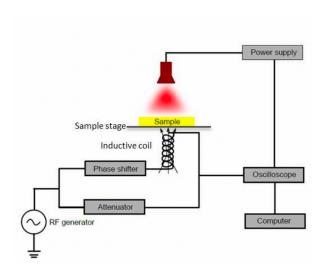

|      | Schematic of the Sinton WCT-120 lifetime tester                                                                                                | 41             |

| 2.21 | Simple schematic of Sinton WCT-120 Photoconductance Decay Lifetime Tester                                                                      | 41             |

| 2.22 | Simple schematic of the components of SIMS[86]                                                                                                 | 42             |

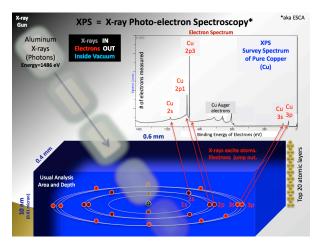

| 2.23 | Simple schematic of XPS measurement[87]                                                                                                        | 42             |

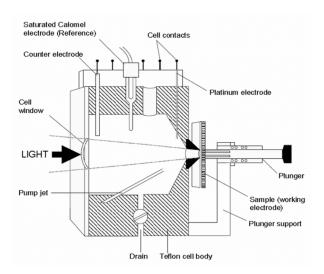

|      | Simple schematic of ECV profiling[48]                                                                                                          | 43             |

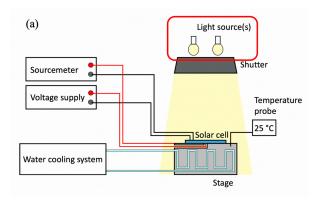

| 2.25 | Simple schematic of Wacom Current-Voltage measurement                                                                                          | 44             |

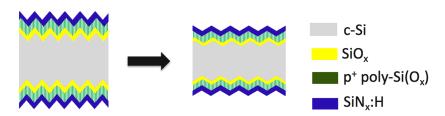

| 3.1  | The sample structure for the experiment on abosorber surface. The aim of the experi-                                                           |                |

|      | ment is to explore the influences of both poly-etch duration time and and times of NAOC                                                        |                |

|      | on the optical and electrical performance of $p^+$ poly-Si(O <sub>x</sub> ) passivating contacts.                                              | 45             |

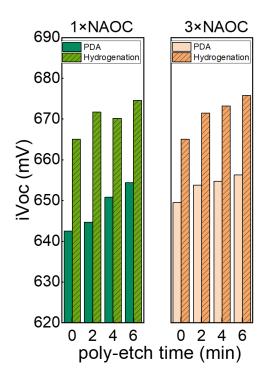

| 3.2  | The influences of poly-etch time and times of NAOC on the electrical performance of p <sup>+</sup>                                             |                |

|      | poly-Si(O <sub>x</sub> ) passivating contacts                                                                                                  | 46             |

| 3.3  | The effects of poly-etch time and times of NAOC on the optical properties of p <sup>+</sup> poly-                                              |                |

|      | Si(O <sub>x</sub> ) passivating contacts                                                                                                       | 46             |

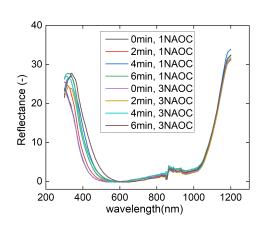

| 3.4  | Different types of interfacial silicon oxide layers have various properties as reported by                                                     |                |

|      | van der Vossen,R et al and Huang, Y et al. [37][85]                                                                                            | 47             |

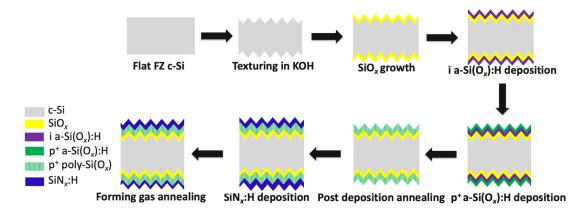

| 3.5  | Fabrication process for experiments of different tunnelling silicon oxide types on DSP                                                         |                |

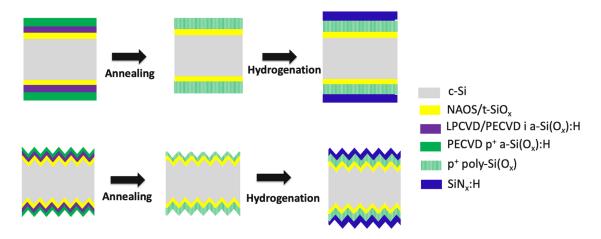

|      | wafers                                                                                                                                         | 47             |

| 3.6  | Fabrication process for experiments of different tunnelling silicon oxide types on DST                                                         |                |

|      | wafers                                                                                                                                         | 49             |

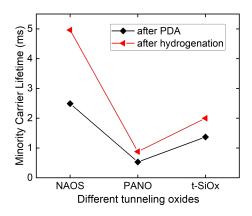

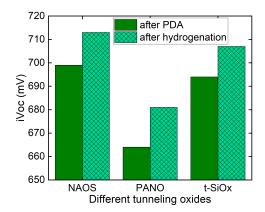

| 3.7  | Minority carrier lifetime of three samples with different tunnelling silicon oxide types on                                                    |                |

|      | DSP wafers                                                                                                                                     | 49             |

| 3.8  | $iV_{oc}$ of three samples with different tunnelling silicon oxide types on DSP wafers                                                         | 49             |

| 3.9  | Minority carrier lifetime of three samples with different tunnelling silicon oxide types on                                                    |                |

|      | DST wafers                                                                                                                                     | 50             |

| 3.10 | $iV_{oc}$ of three samples with different tunnelling silicon oxide types on DST wafers                                                         | 50             |

| 3.11 | XPS measurement results of three different silicon oxide types                                                                                 | 50             |

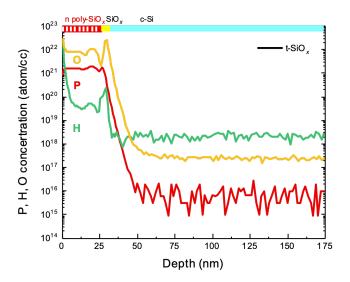

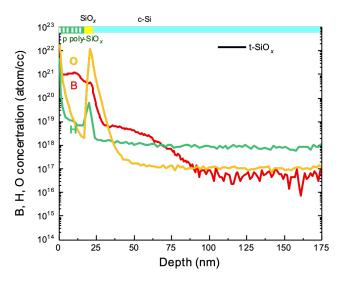

| 3.12 | SIMS measurement results of three different silicon oxide types                                                                                | 51             |

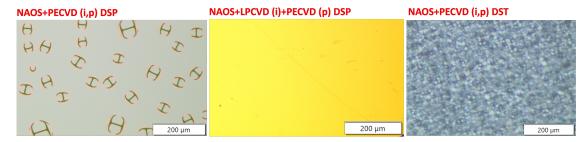

| 3.13 | Structures for testing the blistering conditions and corresponding passivation quality                                                         | 52             |

| 3.14 | Blistering conditions of different structures observed under optical microscope.                                                               | 52             |

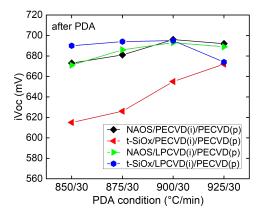

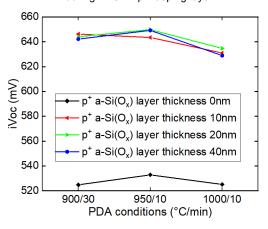

|      | $iV_{oc}$ of four different testing structures as above mentioned after different PDA conditions                                               | 53             |

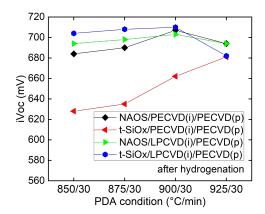

|      | $iV_{oc}$ of four different testing structures as above mentioned after hydrogenation                                                          | 53             |

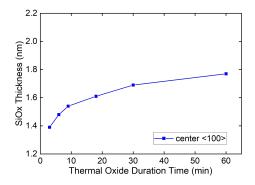

|      | t-SiO <sub>x</sub> thickness changes with oxidation time                                                                                       | 54             |

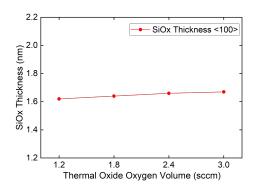

|      | t-SiO <sub>x</sub> thickness changes with oxygen volume ratio during thermally oxidation                                                       | 54             |

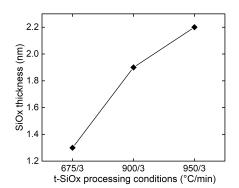

|      | t-SiO <sub>x</sub> thickness changes with oxidation temperature                                                                                | 54             |

|      | Simple schematic of the fabricated samples with thicker t-SiO <sub>x</sub>                                                                     | 55             |

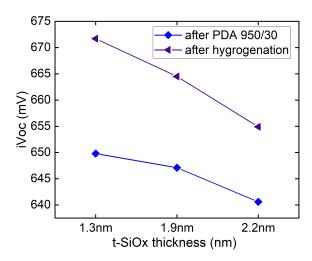

|      | Passivation results of samples with thicker t-SiO <sub>x</sub> tunnelling layer                                                                | 56             |

|      | Passivation results of $p^+$ poly-Si(O <sub>x</sub> ) passivating contacts with thicker t-SiO <sub>x</sub> tunnelling                          |                |

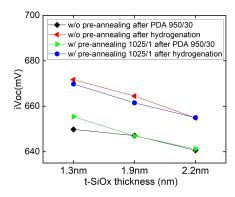

|      | layer and pre-annealing 1025/1                                                                                                                 | 57             |

| 3.23 | Passivation results of $p^+$ poly-Si(O <sub>x</sub> ) passivating contacts with thicker t-SiO <sub>x</sub> tunnelling                          |                |

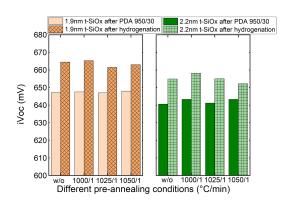

|      | layer and different pre-annealing conditions ranging from 1000/1 to 1050/1                                                                     | 57             |

| 3.24 | Passivation results of p <sup>+</sup> poly-Si(O <sub>x</sub> ) passivating contacts with different O concentration                             | -              |

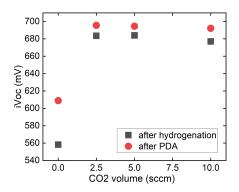

| 0.2  | during PECVD p <sup>+</sup> doping layer                                                                                                       | 59             |

| 3 25 | Passivation results of p <sup>+</sup> poly-Si(O <sub>x</sub> ) passivating contacts with different B concentration                             | 55             |

| 5.20 |                                                                                                                                                |                |

|      |                                                                                                                                                | 50             |

| 3 26 | during PECVD p <sup>+</sup> doping layer                                                                                                       | 59             |

| 3.26 | during PECVD $p^+$ doping layer . Passivation results of $p^+$ poly-Si(O <sub>x</sub> ) passivating contacts with different $p^+$ doping layer |                |

|      | during PECVD p <sup>+</sup> doping layer                                                                                                       | 59<br>59<br>61 |

List of Figures vii

|             | SIMS results of $p^+$ poly-Si(O <sub>x</sub> ) passivating contacts                                                                                                                                      | 61       |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

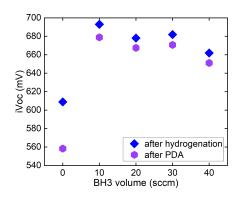

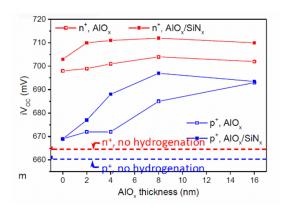

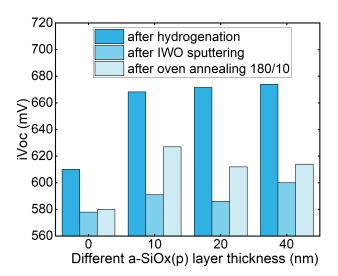

|             | The passivation results with $AIO_x$ :H and $AIO_x$ :H/SiN <sub>x</sub> :H as capping layer(s) during hydrogenation process[5]                                                                           | 62       |

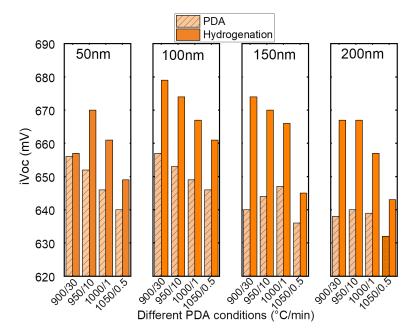

| 3.30        | The passivation results with different capping layer(s) during hydrogenation process and the corresponding different post deposition annealing conditions[5]                                             | 62       |

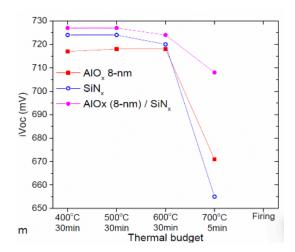

| 3.31        | Fabrication process of IWO sputtering damage on textured p <sup>+</sup> poly-Si(O <sub>x</sub> ) passivating contact                                                                                     | 63       |

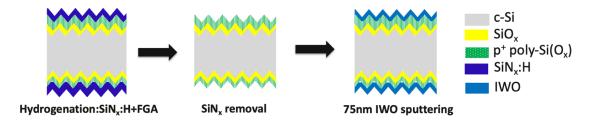

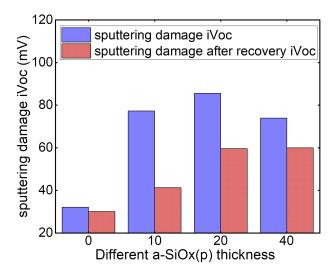

| 3.32        | The influences of p <sup>+</sup> doping layer thickness during PECVD on the TCO sputtering damage of textured surface                                                                                    | 63       |

| 3.33        | The corresponding $iV_{oc}$ degradation caused by IWO sputtering before and after oven annealing recovery                                                                                                | 64       |

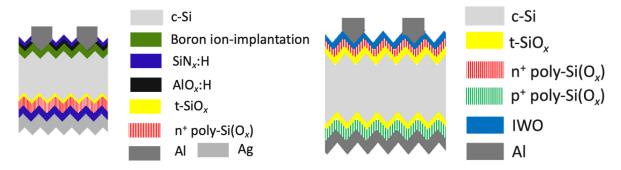

| 3.34        | Simple schematic of i-TOPCon solar cell                                                                                                                                                                  | 65       |

|             | Simple schematic of poly-poly solar cell                                                                                                                                                                 | 65       |

|             | Influence of $p^+$ doped layer thickness on the passivation quality of thicker $p^+$ poly-Si(O <sub>x</sub> ) passivating contacts (>50nm)                                                               | 66       |

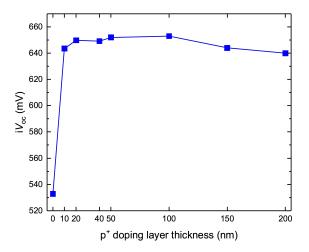

| 3.37        | Influence of $p^+$ doped layer thickness on the passivation quality of $p^+$ poly-Si(O <sub>x</sub> ) passivating contacts (0-200nm)                                                                     | 66       |

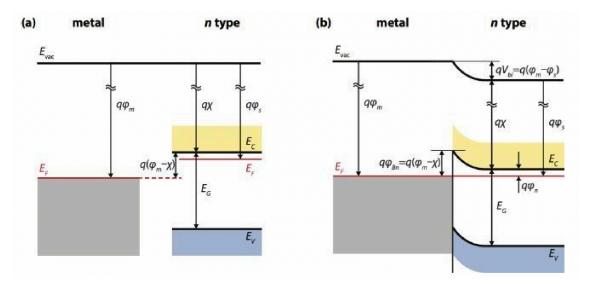

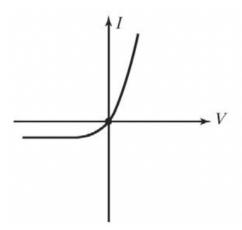

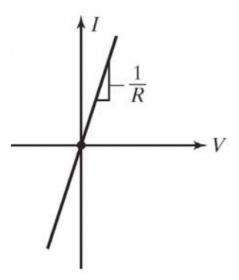

| 4.1         | (a) The band diagrams of a metal and an n-type semiconductor that are separated from each other.(b) The band diagram of a junction between a metal and an n-type semiconductor[77]                       | 68       |

| 4.2         | I-V curve when metal contacting Si in schottky contact                                                                                                                                                   | 69       |

| 4.3         | I-V curve when metal contacting Si in ohmic contact                                                                                                                                                      | 70       |

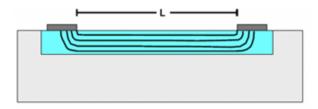

| 4.4         | Schematic of transfer length                                                                                                                                                                             | 71       |

| 4.5         | Schematic of metal pad                                                                                                                                                                                   | 71       |

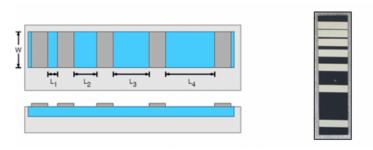

| 4.6         | linear fitting curve of the TLM method to measure the contact resistance                                                                                                                                 | 71       |

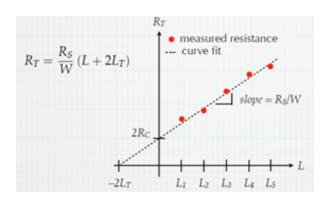

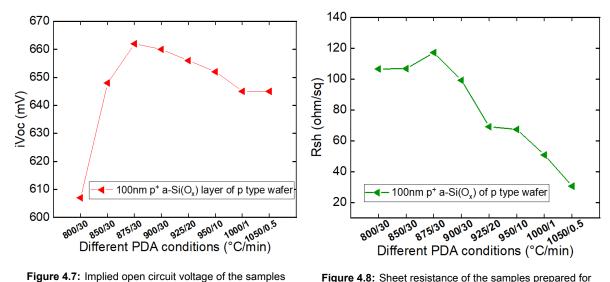

| 4.7         | Implied open circuit voltage of the samples prepared for measuring contact resistivity through TLM                                                                                                       | 72       |

| 4.8         | Sheet resistance of the samples prepared for measuring contact resistivity through TLM                                                                                                                   | 72       |

| 4.9         | The linear fitting curve of the sample with 100 nm boron doping layer and post deposition annealing at 875°C duration for 30 minutes                                                                     | 73       |

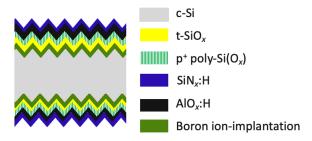

| 4.10        | Testing structure (1) 110 nm p <sup>+</sup> poly-Si(O <sub>x</sub> ) passivating contact for measuring $J_{o,metal}$                                                                                     | 75       |

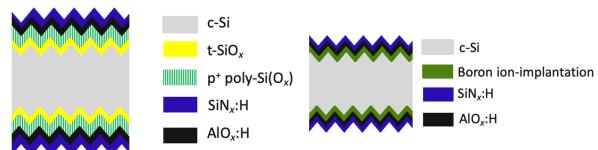

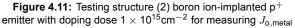

|             | Testing structure (2) boron ion-implanted p <sup>+</sup> emitter with doping dose $1 \times 10^{15} \text{cm}^{-2}$ for measuring $J_{\text{o,metal}}$                                                   | 75       |

| 4.12        | Testing structure (3) 110 nm p <sup>+</sup> poly-Si(O <sub>x</sub> ) passivating contacts on boron ion-implanted                                                                                         | , 0      |

|             | p <sup>+</sup> emitter with doping dose $1 \times 10^{15} \text{cm}^{-2}$ for measuring $J_{\text{o,metal}}$ .  The mask with different metal fractions for measuring metal-induced recombination cur-   | 75       |

| 4.10        | rent density                                                                                                                                                                                             | 76       |

| 4.14        | Flowchart of measuring the metal-induced recombination current density starting from photolithography                                                                                                    | 76       |

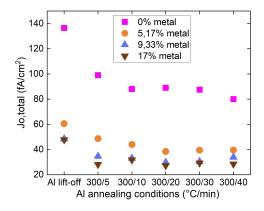

| 4.15        | The total recombination current density after different Al annealing conditions when the temperature is 300°C                                                                                            | 77       |

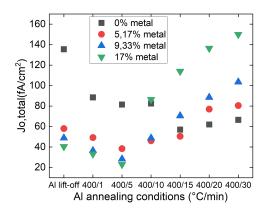

| 4.16        | The total recombination current density after different Al annealing conditions when the temperature is 400°C                                                                                            | 77       |

| <u>4</u> 17 | $J_{\text{total}}$ linear fitting curve of 110nm p <sup>+</sup> poly-Si(O <sub>x</sub> ) passivating contacts                                                                                            | 78       |

|             | $J_{\text{o,total}}$ values of 110 nm p <sup>+</sup> poly-Si(O <sub>x</sub> ) passivating contacts                                                                                                       | 78       |

|             | $J_{0,\text{total}}$ linear fitting curve of p <sup>+</sup> emitter                                                                                                                                      | 79       |

|             | $J_{\text{o,total}}$ values of p <sup>+</sup> emitter                                                                                                                                                    | 79<br>79 |

|             | $J_{0,\text{total}}$ values of p <sup>+</sup> enfitter.<br>$J_{0,\text{total}}$ linear fitting curve of 110nm p <sup>+</sup> poly-Si(O <sub>x</sub> ) passivating contacts on p <sup>+</sup> emitter.    | 80       |

|             | $J_{\text{o,total}}$ inteal fitting curve of Frontin p * poly-Si(O <sub>x</sub> ) passivating contacts on p * emitter                                                                                    | 80       |

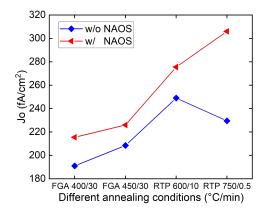

| 5.1         | Recombination current density of p <sup>+</sup> emitter with or without NAOS on it before hydro-                                                                                                         |          |

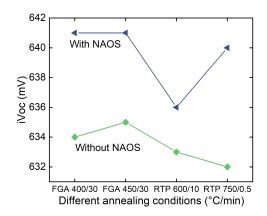

|             | genation with different AlO <sub>x</sub> :H/SiN <sub>x</sub> :H annealing methods and conditions  Implied open circuit voltage of p <sup>+</sup> emitter with or without NAOS on it before hydrogenation | 82       |

| 5.2         | with different $AlO_x$ :H/SiN <sub>x</sub> :H annealing methods and conditions                                                                                                                           | 82       |

List of Figures viii

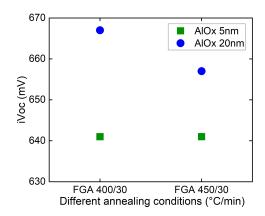

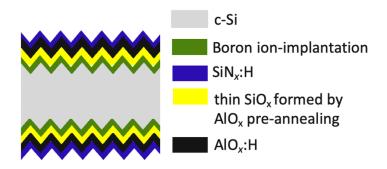

| 5.3  | Implied open circuit voltage of $AIO_x$ :H/SiN <sub>x</sub> :H capping layer stack passivation on $p^+$ emitter with different $AIO_x$ :H thickness                                                         | 83 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.4  | Simple schematic of AlO <sub>x</sub> :H pre annealing                                                                                                                                                       | 83 |

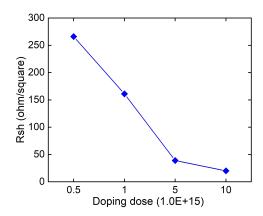

| 5.5  | The relations between sheet resistance and doping dose during ion implantation of p <sup>+</sup> emitter                                                                                                    | 84 |

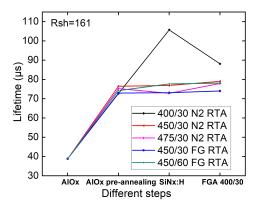

| 5.6  | Minority carrier lifetime of $p^+$ emitter of $161\Omega/\Box$ as sheet resistance with different AlO <sub>x</sub> :H pre annealing conditions                                                              | 84 |

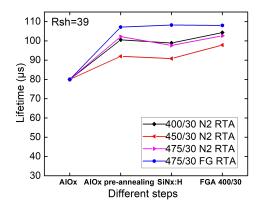

| 5.7  | Minority carrier lifetime of p <sup>+</sup> emitter of $39\Omega/\Box$ as sheet resistance with different AlO <sub>x</sub> :H pre annealing conditions                                                      | 84 |

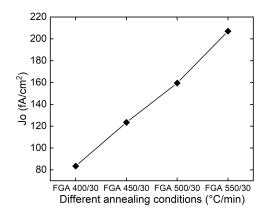

| 5.8  | Recombination current density of AlO <sub>x</sub> :H/SiN <sub>x</sub> :H capping layer stack passivation on p <sup>+</sup> emitter with different FGA conditions                                            | 85 |

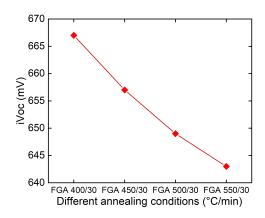

| 5.9  | Implied open circuit voltage of AIO <sub>x</sub> :H/SiN <sub>x</sub> :H capping layer stack passivation on p <sup>+</sup> emitter with different FGA conditions                                             | 85 |

| 5.10 | The ECV profiling of $p^+$ emitter sample with the doping dose $5\times10^{14} cm^{-2}$ activated in TEMPRESS tube furnace at EKL and reference $p^+$ emitter sample from industry with unknown doping dose | 86 |

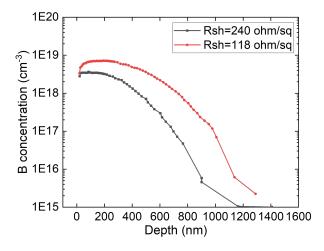

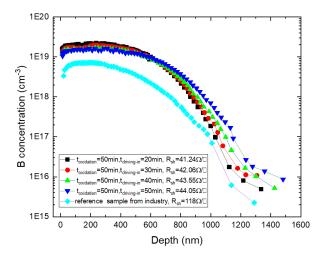

| 5.11 | The ECV profiling of $p^+$ emitter samples of doping dose of $5 \times 10^{15} \text{cm}^{-2}$ with different driving-in time and reference $p^+$ emitter sample from industry with unknown doping dose     | 86 |

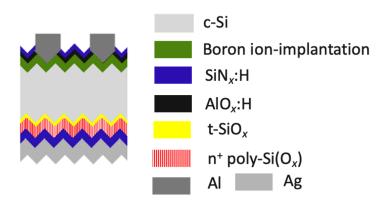

| 5 12 | Simple schematic of i-TOPCon monofacial solar cell                                                                                                                                                          | 87 |

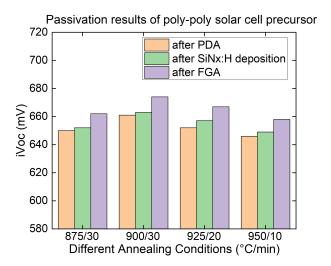

|      | Passivation quality of poly-poly mono-facial cell precursors                                                                                                                                                | 88 |

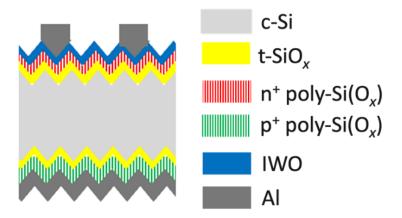

|      | Simple schematic of poly-poly monofacial solar cell                                                                                                                                                         | 89 |

|      | Electrical performance of poly-poly mono-facial cell precursors with the highest efficiency                                                                                                                 | 89 |

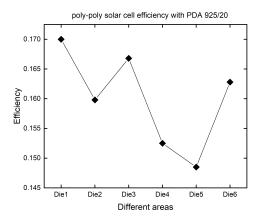

|      | Efficiency of poly-poly mono-facial cell precursors for 6 different dies with cell precursors                                                                                                               |    |

|      | post deposition annealing at 925 °C duration for 20 minutes                                                                                                                                                 | 90 |

| 5.17 | Open circuit voltage of poly-poly mono-facial cell precursors for 6 different dies with cell                                                                                                                |    |

|      | precursor post deposition annealing at 925°C duration for 20 minutes                                                                                                                                        | 90 |

| 5.18 | Short circuit current density of poly-poly mono-facial cell precursors for 6 different dies                                                                                                                 |    |

|      | with cell precursor post deposition annealing at 925°C duration for 20 minutes                                                                                                                              | 90 |

| 5.19 | Fill factor of poly-poly mono-facial cell precursors for 6 different dies with cell precursor                                                                                                               |    |

|      | post deposition annealing at 925 °C duration for 20 minutes                                                                                                                                                 | 90 |

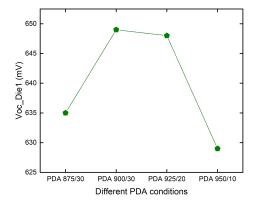

| 5.20 | $V_{ m oc}$ of die 1 with 4 different PDA conditions                                                                                                                                                        | 91 |

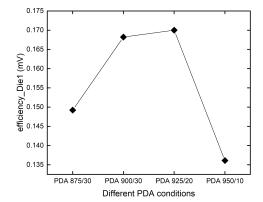

| 5.21 | $\eta$ of die 1 with 4 different PDA conditions                                                                                                                                                             | 91 |

## **List of Tables**

| 2.1 | TOPSIL n-type FZ c-Si waters details and properties                                                                                                                                     | 22 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | plasma-SiO <sub>x</sub> tunnelling oxide layer PECVD parameters                                                                                                                         |    |

|     | $p^+$ a-Si(O <sub>x</sub> ):H doping layer PECVD parameters                                                                                                                             |    |

| 3.4 | XPS measurement results of three different silicon oxide types                                                                                                                          |    |

| 3.5 | Passivation of $p^+$ poly-Si(O <sub>x</sub> ) passivating contacts of different t-SiO <sub>x</sub> thickness and with or without pre-annealing                                          | 58 |

| 3.6 | The recipe for changing the O concentration during PECVD on flat surface                                                                                                                | 58 |

|     | The recipe for changing the B concentration during PECVD on flat surface                                                                                                                | 60 |

| 3.8 | The $iV_{oc}$ and minority carrier lifetime of samples with ALD AlO <sub>x</sub> :H and PECVD SiN <sub>x</sub> :H stacks as capping layer for the optimization of hydrogenation process | 62 |

| 4.1 | Metal-induced recombination current density of samples of three different structures                                                                                                    | 77 |

|     | $V_{\text{oc}}$ for 6 various dies with 4 different PDA conditions                                                                                                                      |    |

1

### Introduction

Energy is the foundation of the world's economic and social development. With the large consumption of traditional fossil energy and the deterioration of human living environment, the development of clean renewable energy has attracted the attention of governments all over the world. Renewable energy includes solar energy, wind energy, geothermal energy, water energy and so on. The sun is a ball of gas that generates heat through nuclear fusion reaction in its center and the radiation intensity is close to the blackbody radiation with a temperature of 6000K. Nuclear fusion reaction constantly takes place inside the sun, constantly radiating energy to the outside. So, the solar energy is inexhaustible which is the best choice to solve the problem of energy shortage in the 21<sup>st</sup> century. The utilization of solar energy is mainly divided into two ways: one is the conversion of solar energy into heat energy for utilizing. The other is the conversion of solar energy into electricity for using, namely photovoltaics.

Photovoltaics is a fast-growing market: The compound annual growth rate (CAGR) of cumulative PV installations including off-grid was 34% between year 2010 to 2020. Wafer size increased and by keeping the number of cells larger, PV module sizes are realized allowing a power range beyond 600 W per module. Si-wafer based PV technology accounted for about 95% of the total production in 2020. The share of mono-crystalline technology is now about 84% (compared to 66% in 2019) of total c-Si production that can be discovered in Figure 1.1 and [65],[63].

The record lab cell efficiency is 26.7% [91]for mono-crystalline and 24.4% for multi-crystalline silicon wafer-based technology that can be discovered in Figure 1.2 and [63], [30]. In the last 10 years, the efficiency of average commercial wafer-based silicon modules increased from about 15% to 20% and more. In the laboratory, best performing modules are based on mono-crystalline silicon with 24.4% efficiency which can be seen in Figure 1.3 and [63],[30]. Record efficiencies demonstrate the potential for further efficiency increases at the production level.

#### 1.1. Working principle of the solar cells

The working principle of solar cells is based on the photogenerating volt effect of semiconductors. The so-called photogenerating volt effect is an effect that produces electromotive force and current when the charge distribution in the object is changed when the object is illuminated. Crystalline silicon solar cell is essentially a large area of diode, composed of PN junction, passivation film and metal electrode. The simple schematic can be discovered in Figure 1.4.

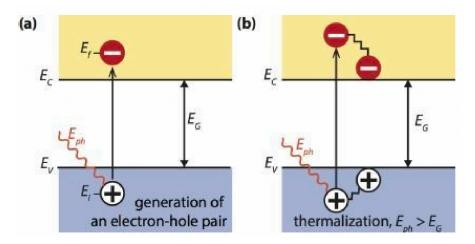

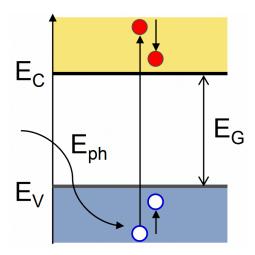

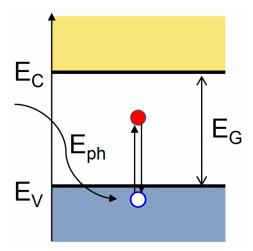

The photogenerating volt effect can be divided into three basic processes. Firstly, when illuminating, due to the absorption of photons, charge carriers are generated in the materials which can form a junction. In an ideal semiconductor, electrons can only populate energy levels below valence band edge,  $E_{\rm v}$ , and above conduction band edge,  $E_{\rm c}$ . However, between these two bands, the electrons cannot occupy the energy states. Hence, this energy difference is called the band  ${\rm gap}E_{\rm G}$ . And  $E_{\rm G}$ = $E_{\rm c}$ - $E_{\rm v}$ . If the photon with an energy  $E_{\rm ph}$  larger than band  ${\rm gap}E_{\rm G}$ , the electrons are excited, then a void which

Figure 1.1: Percentage of Global Annual Production [30] and [63]

Figure 1.2: Development of Laboratory Solar Cell Efficiencies [30] and [63]

is an unoccupied energy state is left behind. The void behaves like a particle with positive elementary charge, is called a hole. The holes can also be considered as charge carriers that can move through the semiconductors. Thus, the absorption of a photon can lead to the creation of an electron-hole pair which can be discovered in Figure 1.5 and [77]. Usually, the electron-hole pair will recombine and the energy will then be released.

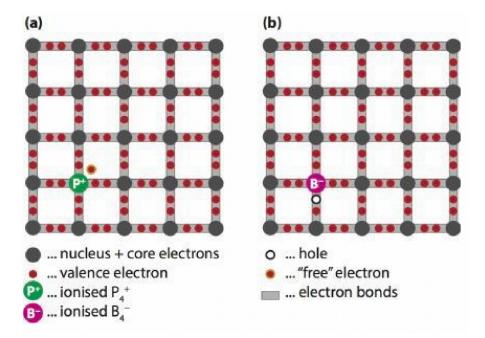

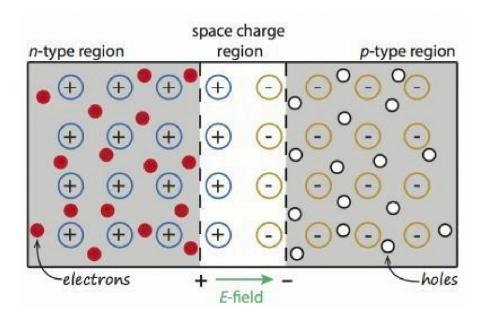

Secondly, the photo-generated charge carriers in the junction will then be separated. Normally, the separation of charge carriers is done by a p-n junction. The p-type region is normally formed by doping with boron with three valence electrons on the outer shell which is illustrated in Figure 1.6 and [77]. One valence electron less will induce a hole and a fixed negative charge. Then in the p-doped regions, there are a lot of holes and fixed negative charges. Similarly, the n-type region is usually formed by doping with phosphorous with five valence electrons on the outer shell which can be shown in Figure 1.6. Then in the n-doped region, there are plenty of electrons and fixed positive charges. When a p-type and an n-type semiconductor are brought together, a very large difference in electron concentration between n- and p-type regions causes a diffusion current of electrons from the n-type material across the metallurgical junction into the p-type material. Similarly, the difference in hole concentration causes

Figure 1.3: Best lab cells versus Best lab modules [30] and [63]

a diffusion current of holes from the p- to the n-type material. Due to this diffusion process, the region close to the metallurgical junction becomes almost completely depleted of mobile charge carriers. The gradual depletion of the charge carriers gives rise to a space charge created by the ionized donor and acceptor atoms that is not compensated by the mobile charges any more. This region of the space charge is called the space-charge region or depleted region. Regions outside the depletion region, in which the charge neutrality is conserved, are denoted as quasi-neutral regions which can be illustrated in Figure 1.7 and [77].

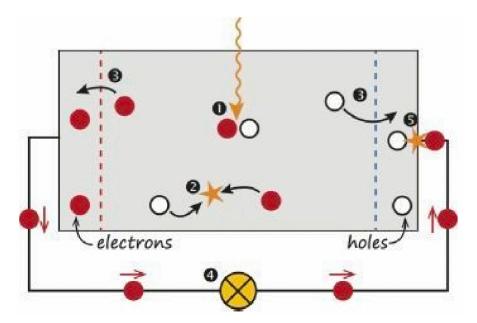

The space charge around the metallurgical junction results in the formation of an internal electric field which forces the charge carriers to move in the opposite direction than the concentration gradient. In addition, due to the electric field, a difference in the electrostatic potential is created between the boundaries of the space-charge region. Across the depletion region, the changes in the carrier concentration are compensated by changes in the electrostatic potential. Through the p-n junction, the holes and electrons are drawn to opposite polarities and ready for collecting before they combine which can be discovered in Figure 1.8 and [77].

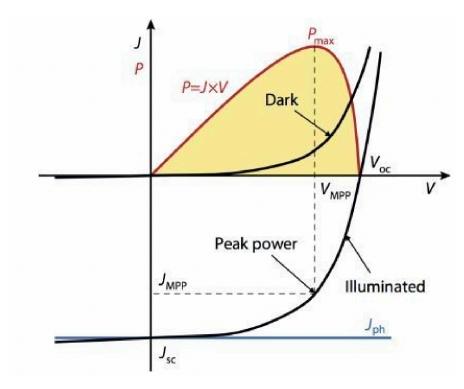

And finally, the photo-generated charge carriers will be collected at the terminals of the junction. The external electric circuit is required to collect the electrons. The main parameters that are used to characterize the performance of solar cells are the peak power  $P_{\rm max}$ , the short circuit current density  $J_{\rm sc}$ , the open circuit voltage  $V_{\rm oc}$ , and the fill factor FF. These parameters are determined from the illuminated J-V characteristic. The conversion efficiency  $\eta$  can be determined from these parameters.

The short circuit current  $I_{\rm sc}$  is the current that flows through the external circuit when the electrodes of the solar cell are short circuited. The parameters that decide  $J_{\rm sc}$  are the diffusion lengths of minority carriers. The open-circuit voltage is the voltage at which no current flows through the external circuit which represents the maximum voltage that a solar cell can deliver.  $V_{\rm oc}$  can be calculated by equation 1.1, where  $J_{\rm oh}\gg J_{\rm o}$  is the approximation.

$$V_{oc} = \frac{K_B T}{q} ln(\frac{J_{ph}}{J_o} + 1) \approx \frac{K_B T}{q} ln(\frac{J_{ph}}{J_o})$$

$$\tag{1.1}$$

$V_{\rm oc}$  is a measure of the amount of recombination in the device. The fill factor is the ratio between the maximum power  $P_{\rm max}$ generated by a solar cell and the product of  $V_{\rm oc}$  with  $J_{\rm sc}$ . The calculation equation is 1.2,at mpp the solar cell has the maximum power output.

Figure 1.4: Simple schematic of photovoltaic effect

$$FF = \frac{J_{mpp}V_{mpp}}{J_{SC}V_{OC}} \tag{1.2}$$

The conversion efficiency is calculated as the ratio between the maximal generated power and the incident power. Solar cells are measured under the STC, where the incident light is described by the AM1.5 spectrum and has an irradiance of  $I_{in}$ =1000  $W/m^2$ . It can be calculated by equation 1.3,

$$\eta = \frac{P_{max}}{I_{in}} = \frac{J_{mpp}V_{mpp}}{I_{in}} = \frac{J_{sc}V_{oc}FF}{I_{in}}$$

$$\tag{1.3}$$

The *J-V* characteristics of a p-n junction in the dark and under illumination which is also the simple schematic of the external parameters can be shown in Figure 1.9 and [77]

#### 1.2. Solar cell loss mechanisms

#### 1.2.1. Optical losses

#### Spectral mismatch

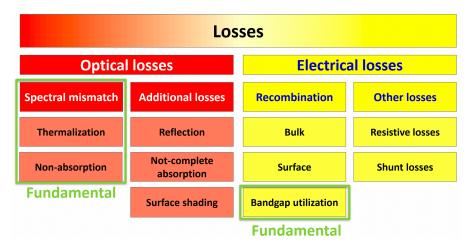

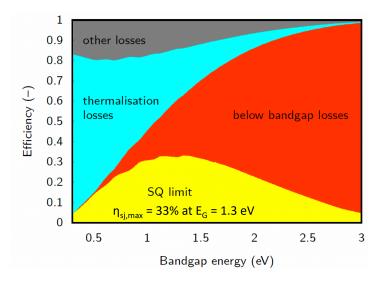

The losses of solar cell can be divided into two parts that can be shown in Figure 1.10. One is optical losses and the other is electrical losses. The fundamental losses of optical losses are mainly spectral mismatch that includes thermalization and non-absorption. In principle, only photons with energy higher than the bandgap energy of the absorber can generate electron-hole pairs. Since the electrons and holes tend to occupy energy levels at the bottom of the conduction band and the top of the valence band, respectively. On one hand, the extra energy that the electron-hole pairs receive from the photons is released as heat into the semiconductor lattice in the thermalization process which can be discovered in Figure 1.11. The corresponding efficiency to thermallization losses is called  $P_{\rm use}$  and the equation is shown in Equation 1.4. On the other hand, photons with energy lower than the bandgap energy of the absorber are in principle not absorbed and cannot generate electron-hole pairs which is called non-absorption losses that can be shown in Figure 1.12 and the corresponding equation is called  $P_{\rm abs}$  that is shown in Equation 1.5. Both of these losses are thus related to the spectral mismatch between

Figure 1.5: (a)Illustrating the absorption of a photon in a semiconductor with bandgap  $E_{\rm G}$ . The photon with energy  $E_{\rm ph}$ =hv excites an electron from  $E_{\rm i}$  to  $E_{\rm f}$ . At  $E_{\rm i}$  a hole is created.(b)If  $E_{\rm ph}$ > $E_{\rm G}$ , a part of the energy is thermalized.[77]

the energy distribution of photons in the solar spectrum and the bandgap of a semiconductor material [73].

$$P_{use} = \frac{E_G \int_0^{\lambda_G} \Phi(\lambda) d\lambda}{\int_0^{\lambda_G} P(\lambda) d\lambda}$$

(1.4)

$$P_{abs} = \frac{\int_0^{\lambda_G} P(\lambda) d\lambda}{\int_0^{\infty} P(\lambda) d\lambda}$$

(1.5)

The ultimate conversion efficiency is as the following Equation 1.6.

$$\eta_{ult} = P_{use} \times P_{abs} = \frac{E_G \int_0^{\lambda_G} \Phi(\lambda) d\lambda}{\int_0^{\lambda_G} P(\lambda) d\lambda} \times \frac{\int_0^{\lambda_G} P(\lambda) d\lambda}{\int_0^{\infty} P(\lambda) d\lambda}$$

(1.6)

#### Reflection

Part of the light is reflected and the other part is transmitted when light arrives on an interface between two media. The interface is therefore characterized by the wavelength-dependent reflectivity  $R(\lambda)$  and transmittance  $T(\lambda)$ . All the reflections and transmissions at the different interfaces in the solar cell result in a total reflectance between the solar cell and the surrounding air. Hence, a part of the incident energy that can be converted into a usable energy by the solar cell is lost by reflection[77]. The corresponding equation is (1-R) and R can be calculated by Fresnel equation that can be seen in Equation 1.7.

$$R = \left| \frac{n_{air} - n_{Si}}{n_{air} + n_{Si}} \right|^2 \tag{1.7}$$

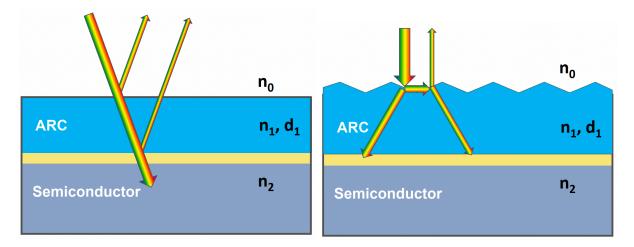

The reflection losses can be reduced by anti-reflection coating and texturing. The schematic of anti-reflection coating and texturing can be shown in Figure 1.13 and Figure 1.14. The optimum thickness for anti-reflection coating can be seen in Equation 1.8 and Equation 1.9.

$$n_1 = \sqrt{n_0 n_2} \tag{1.8}$$

$$d_1 = \lambda/4n_1 \tag{1.9}$$

**Figure 1.6:** The doping process illustrated using the bonding model.(a) A phosphorus (P) atom replaces a Si atom in the lattice resulting in the positively-ionized P atom and a free electron.(b) A boron (B) atom replaces a Si atom resulting in the negatively ionized B atom and a hole.[77]

#### Surface shading

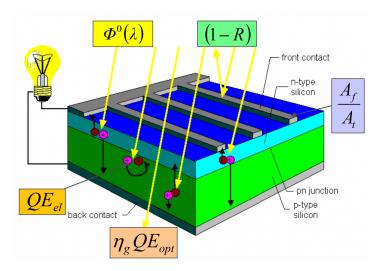

In most c-Si solar cells thin metal strips are placed on the front side of the solar cell that serve as front electrodes. The metal-covered area does not allow the light to enter the solar cell because it reflects or slightly absorbs the incident light. The area that is covered by the electrode decreases the active area of the solar cell. The total area of the cell as  $A_{\rm tot}$  and the cell area that is not covered by the electrode as  $A_{\rm f}$ , the fraction of the active area of the cell is determined by the ratio which is called the active area coverage factor  $C_{\rm f}$  which the equation is shown in Equation 1.10. The resulting loss is called the surface shading loss.

$$C_f = \frac{A_f}{A_{tot}} \tag{1.10}$$

#### **Not-complete absorption**

Due to the limited thickness d of the absorber layer and the different absorption coefficient  $\alpha$  with various thickness , not all the light entering the absorber layer is absorbed. Incomplete absorption in the absorber due to its limited thickness is an additional loss that lowers the energy conversion efficiency. The incomplete absorption loss can be described by the internal optical quantum efficiency  $IQE_{\rm op}$ , which is defined as the probability of a photon being absorbed in the absorber material. Since there is a chance that a highly energetic photon can generate more than one electron-hole pair, the quantum efficiency for carrier generation  $\eta_{\rm g}$ , which represents the number of electron-hole pairs generated by one absorbed photon. Usually  $\eta_{\rm g}$  is assumed to be unity. Therefore, the equation corresponding to not-complete absorption can be shown in Equation 1.11 and Equation 1.12.

$$\eta_{=}\eta_{q}IQE_{op} \tag{1.11}$$

$$T = exp(-\alpha d) \tag{1.12}$$

**Figure 1.7:** Formation of a space-charge region, when n-type and p-type semiconductors are brought together to form a junction.The coloured part represents the space-charge region.[77]

#### **Parasitic absorption**

When light penetrates into a material, it will be partially absorbed as it propagates through the material. The absorption of light in the material depends on its absorption coefficient and the layer thickness. In general, light is absorbed in all layers of the solar cell. All the absorption in layers other than the absorber layer is loss. It is called the parasitic absorption [28].

## 1.2.2. Electrical losses Bandgap utilization

The bandgap utilization efficiency is given by  $\eta_v$  which tells the fraction of the bandgap that can be used as open circuit voltage. The corresponding equations can be discovered in the following Equation 1.13, Equation 1.14, Equation 1.15 and Equation 1.17

$$\eta_v = \frac{qV_{oc}}{E_G} \tag{1.13}$$

$$J = J_o exp[\frac{qV}{KT} - 1] - J_{ph}$$

(1.14)

Then,

$$V_{oc} = \frac{KT}{q} ln[\frac{J_{ph}}{J_o} + 1]$$

(1.15)

Thus,

$$\eta_v(E_G) = \frac{KT}{E_G} ln[\frac{J_{ph}(E_G)}{J_o(E_G)} + 1]$$

(1.16)

The maximum efficiency for single junction solar cell is given by Equation 1.17,

Therefore, the schematic of Shockley-Queisser efficiency can be discovered in Figure 1.15[17].

$$\eta_{sj} = \eta_{ult} \eta_v FF \tag{1.17}$$

Figure 1.8: A very simple solar cell model.(1)Absorption of a photon leads to the generation of an electron-hole pair.(2)Usually, the electrons and holes will recombine.(3)With semipermeable membranes the electrons and the holes can be separated.(4)The separated electrons can be used to drive an electric circuit. (5)After the electrons have passed through the circuit, they will recombine with holes.[77]

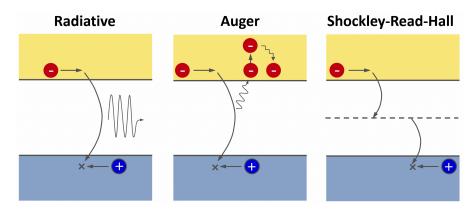

#### **Bulk recombination**

Bulk recombination includes three different kinds of recombination, Radiative recombination, Auger recombination and Shockley-Read-Hall recombination.

#### **Radiative recombination**

Radiative recombination occurs when an electron in the conduction band recombines with a hole in the valence band and the excess energy is emitted in the form of a photon. Radiative recombination is thus the radiative transition of an electron in the conduction band to an empty state (hole) in the valence band.Radiative recombination is the recombination mechanism that dominates in direct bandgap semi-conductors such as GaAs. However, Si is indirect bandgap material. Therefore, in Si, the radiative recombination can be considered negligible [33].

#### **Shockley-Read-Hall recombination**

In Shockley-Read-Hall recombination (SRH), also called trap-assisted recombination, the electron in transition between bands passes through a new energy state (localized state) created within the band gap by a dopant or a defect in the crystal lattice; such energy states are called traps. An electron can get trapped in this energy state, where it can recombine with a hole. Since traps can absorb differences in momentum between the carriers, SRH is the dominant recombination process in silicon and other indirect bandgap materials. However, trap-assisted recombination can also dominate in direct bandgap materials under conditions of very low carrier densities (very low level injection) or in materials with high density of traps such as perovskites[1][95].

The Shockley-Read-Hall recombination can be decided by Equation 1.18 for holes and Equation 1.19 for electrons.

$$R_{SRH} = C_p N_T (p - p_0) = \frac{p - p_0}{\tau_{p,SRH}}$$

(1.18)

Figure 1.9: The J-V characteristics of a p-n junction in the dark and under illumination[77]

$$R_{SRH} = C_n N_T (n - n_0) = \frac{n - n_0}{\tau_{n,SRH}}$$

(1.19)

$C_{\rm p}$  is called the hole capture coefficient.  $C_{\rm n}$  is called the electron capture coefficient.  $au_{\rm p,SRH}$  is the lifetime of holes in an n-type semiconductor.  $au_{\rm n,SRH}$  is the lifetime of electrons in an p-type semiconductor.  $N_T$  is the trap density. And  $p_0$  is the hole concentration under thermal equilibrium. Finally,  $n_0$  is the electron concentration under thermal equilibrium.

#### **Auger recombination**

Auger recombination is a non-radiative three particles process where the excess energy from the electron-hole recombination is transferred to electrons or holes that are subsequently excited to higher energy states within the same band instead of giving off photons (the radiative process). The Auger recombination is dominant in direct bandgap material such as Si [43][26].

Auger recombination rate can be decided by Equation 1.20.

$$R_{Aug} = R_{eeh} + R_{ehh} = C_n n^2 p + C_p n p^2 (1.20)$$

As Auger recombination is a three particle process, the Auger recombination rate  $R_{\text{Aug}}$  strongly depends on the charge carrier densities for the electrons n and holes p.  $C_{\text{n}}$  and  $C_{\text{p}}$  are the proportionality constants that are strongly dependent on the temperature.  $R_{\text{eeh}}$  is dominant when the electrons are the majority charge carriers, while  $R_{\text{ehh}}$  is dominant when the holes are the majority charge carries. In strongly doped n-type silicon with a donor concentration  $N_{\text{D}}$  under low-level injection, it can be assumed that  $n \approx N_{\text{D}}$  and hence that the eeh process is dominant. Similarly, for strongly doped p-type silicon with acceptor concentration  $N_{\text{A}}$ , it can be assumed that  $p \approx N_{\text{A}}$  and hence the ehh process being dominant. As the Auger recombination under these conditions is proportional to the square of the doping levels, the more important it becomes, the higher the doping.

Figure 1.10: The loss mechanisms of solar cell[77]

Figure 1.11: Schematic of thermallization losses of spectral mismatch losses[77]

The schematic of radiative recombination, Auger recombination and SRH recombination can be illustrated in Figure 1.16.

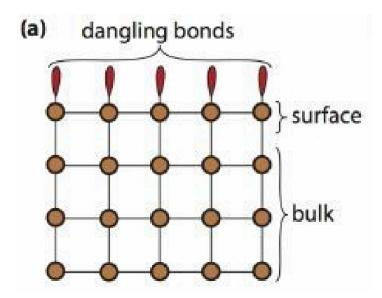

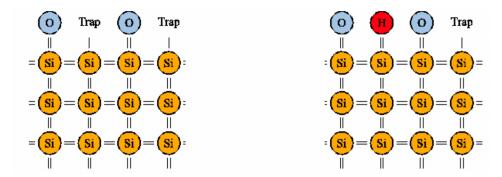

#### **Surface recombination**

At a silicon surface many valence electrons on the surface cannot find a partner to create a covalent bond with. The result is a so-called dangling bond, which is a defect that can be discovered in Figure 1.17. Due to these defects, many surface trap states are created within the band gap. These defects will also induce SRH recombination. In very pure semiconductors, recombination might be dominated by surface recombination.

The surface recombination rate  $R_s$  for an n-type semiconductor can be approximated with the following equation Equation 1.21,

$$R_s \approx V_{th} \sigma_p N_{ST} (p_s - p_0) \tag{1.21}$$

$V_{\rm th}$  is the thermal velocity in cm/s.  $N_{\rm ST}$  is the surface trap density in cm<sup>-2</sup>, and  $\sigma_{\rm p}$  is the capture crosssection for holes in cm<sup>2</sup>.  $p_{\rm s}$  is the hole concentration at the surface and  $p_0$  is the equilibrium hole concentration in the n-type semiconductor. For a p-type semiconductor,  $\sigma_{\rm p}$  can be replaced by  $\sigma_{\rm n}$ ,  $p_{\rm s}$  by  $n_{\rm s}$ , and  $p_0$  by  $n_0$ .

Figure 1.12: Schematic of non-absorption losses of spectral mismatch losses[77]

Figure 1.13: Schematic of anti-reflection coating to reduce reflection losses

Figure 1.14: Schematic of texturing to reduce reflection losses

For high quality solar cells, it is crucial to have a low surface recombination velocity  $S_{\rm r}$ , which can be achieved in two different ways: first,  $S_{\rm r}$  can be made low by reducing the trap density  $N_{\rm ST}$ . In semi-conductor technology,  $N_{\rm ST}$  can be reduced with passivation. Because of the thin layer on the surface, the valence electrons on the surface can form covalent bonds, such that  $N_{\rm ST}$  is reduced. Secondly, the excess minority carrier concentration at the surface  $(p_{\rm s} \ {\rm or} \ n_{\rm s})$  can be reduced, for example by high doping of the region just underneath the surface in order to create a barrier. Because of this barrier, the minority carrier concentration is reduced and hence the recombination rate  $R_{\rm s}$  [71][84].

## **Surface passivation Chemical passivation**

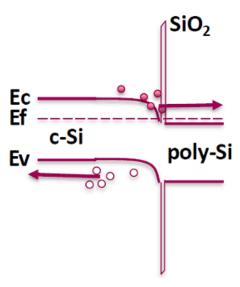

The chemical passivation reduced the dangling bonds and minimized the defect trap density  $N_{\rm ST}$  at the surface or interface and thus reducing the surface recombination velocity and rate. The dangling bonds at the surface can be passivated by O atoms and also H atoms. It can be achieved by depositing passivating layer on the surface of the c-Si. For example, the surface dangling Si atom bonds can form Si-O bonds with the O atom in the thin passivating layer. This can largely reduce the surface recombination. Furthermore, after hydrogenation process, more Si atom dangling bonds can be passivated by H atom to form Si-H bonds that can further reduce the defect density at the surface and interface.

Figure 1.15: Schematic of Shockley-Queisser efficiency[77]

Figure 1.16: Schematic of Radiative recombination, Auger recombination and SRH recombination [77]

#### Field effect passivation

The field effect passivation reduced the surface recombination through reducing the excess minority carrier concentration  $(p_s$  or  $n_s$ ) at the surface, for example by highly doping of the region in order to create a barrier. Because of this barrier, the minority carrier concentration is reduced and hence the recombination rate  $R_s$  is largely reduced at the same time. Field effect passivation is the formation of an internal electric field on the surface of the wafer by highly doped layers that induces majority charge carriers migration, at the same time blocking the migration of minority charge carriers to the interface. The additional highly doped layer, increases the concentration difference and the corresponding band bending between the majority charge carriers and minority charge carriers at the surface which can also be called carrier selective and thus reducing the possibility of the two carriers recombining at the interface. Apart from highly doped layer, the field effect passivation or the internal electrical field can also be achieved by adding the fixed charges like the positive charges in SiO<sub>x</sub> and capping layer which are suitable to passivate n-type semiconductor and also the negative charges in capping layer AlO<sub>x</sub>: H that are suitable to passivate the p-type semiconductor. In addition, by creating the work function difference like metal oxides MoO<sub>x</sub> .etc dopants free passivation. In summary, the internal field effect and the induced band bending can attract majority charge carrier and repel minority charge carriers to reduce the surface recombination [36], [90] and [15].

As the development of solar cells, it is discovered that the recombination at the contact can not be ignored. Especially when the thin films contacting with metal can cause severe recombination losses that can be seen as the limit factor for the improvement of the efficiency of c-Si solar cells. Therefore, at first, it is found that there are a lot of metal-Si interface recombinations in the Aluminium BSF solar

Figure 1.17: Illustrating dangling bonds (surface defects) on a semiconductor surface[77]

Ag front grid  $SiN_x$  emitter p-type Si  $SiO_2/SiN_x$

Figure 1.18: Simple schematic of AI BSF solar cell

Figure 1.19: Simple schematic of PERC solar cell

cell that can be discovered in Figure 1.18. Then, in addition, the PERC solar cell is proven to be high efficiency. But, there also exist a few metal-Si interface recombinations in the PERC solar cell although it has local BSF which is illustrated in Figure 1.19. At the same time, the procedures for producing PERX solar cell seem very complicated that are required to be simplify. The carrier-selective passivating contacts can largely reduce the recombination losses at the contact with good passivation quality and in the meanwhile, it can also let Si contact with full area metal that largely reduce the complexity during producing. And it is also proven to be high efficiency.

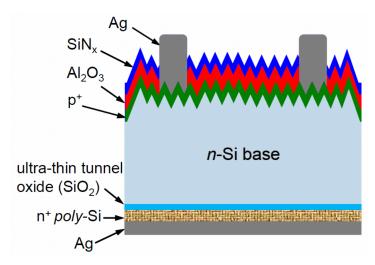

Carrier-selective passivating contacts can largely minimize the interface defect density and without it, plenty of interface recombination will exist. The highest efficiency front-back contacted (FBC) solar cell has been completed by the TOPCon configuration with poly-Si contact[7]. It shows that TOPCon solar cell and the poly-Si( $O_x$ ) carrier selective passivating contacts have large potentials to be further explored and discovered. In this FBC TOPCon solar cell, the front side is  $p^+$  emitter while at the rear side,  $n^+$  poly-Si( $O_x$ ) passivating contact has been implemented contacting with full area metal back contact to collect charge carriers that can be seen in Figure 1.20. The bad passivation quality of  $p^+$  poly-Si( $O_x$ ) passivating contacts especially on textured wafers decides that the front side can just be  $p^+$  emitter for pursing high efficiency solar cells. The  $p^+$  poly-Si( $O_x$ ) on flat surface have better passivation quality. However, if  $p^+$  poly-Si passivating contact is located at front side, the optical properties and parasitic absorption will become big problems. Therefore, the exploration on improving the passivation quality of  $p^+$  poly-Si passivating contact on textured surface is still undergoing.

Figure 1.20: FBC solar cell with TOPCon configuration [81]

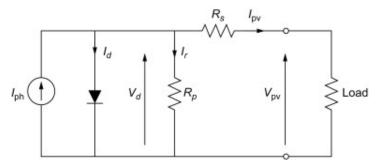

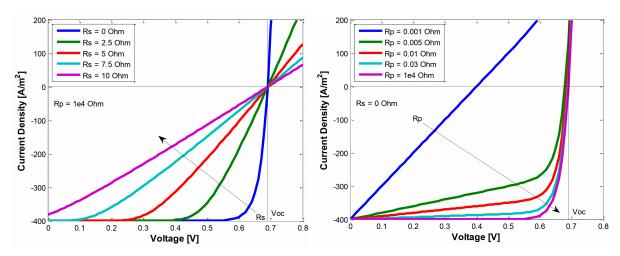

#### **Resistive losses and Shunt losses**

The single-diode solar cell model is illustrated in Figure 1.21. The series resistance  $R_{\rm s}$  can be result of the bulk resistance of semiconductor, the bulk resistance of metal electrodes and the dominant contact resistance between semiconductor and metal. The influences of  $R_{\rm s}$  can be seen in Figure 1.22. From the figure, it can be discovered that the larger the series resistance is , the worse the I-V characteristic of the solar cell is. The shunt resistance  $R_{\rm p}$  can be result of leakage across P-N junction around the edge and crystal defects, pinholes, impurity precipitates. The influences of  $R_{\rm p}$  can be seen in Figure 1.23. From the figure, it can be discovered that the larger the shunt resistance is , the better the I-V characteristic of the solar cell is. Therefore, the series resistance ought to be as small as possible and the shunt resistance should be as large as possible.

Figure 1.21: Single-diode model of solar cell

Then, finally, considering all the losses mentioned above, the efficiency  $\eta$  of the solar cell is given by the following formula Equation 1.22, as illustrated in Figure 1.24.

$$\eta = \frac{E_G \int_0^{\lambda_G} \Phi(\lambda) d\lambda}{\int_0^{\lambda_G} P(\lambda) d\lambda} \times \frac{\int_0^{\lambda_G} P(\lambda) d\lambda}{\int_0^{\infty} P(\lambda) d\lambda} \times \frac{A_f}{A_{tot}} \times (1 - R) \times \eta_g IQE_{op} \times IQE_{el} \times \frac{qV_{OC}}{E_G} \times FF \qquad \textbf{(1.22)}$$

#### 1.3. poly-Si( $O_x$ ) passivating contacts

#### 1.3.1. Surface formation

The surface of c-Si absorber can be polished or textured. The poly-Si( $O_x$ ) passivation quality on flat can be better. However, the reflection on flat surface can be very large which may do harm to the efficiency

Figure 1.22: The influences of series resistance  $R_s$  on the I-V Figure 1.23: The influences of shunt resistance  $R_p$  on the I-V characteristics of solar cell characteristics of solar cell

Figure 1.24: Simple schematic of all the solar cell losses

of the solar cell. Therefore, to increase the optical performance and light traping of the cell, the surface can be textured by tetramethyl ammonium hydroxide (TMAH) and potassium hydroxide (KOH) to prepare inverted pyramids on the surface. It is found that TMAH solution has higher undercut rate and lower <100> plane etch rate than KOH solution, and the <111>/<100> etch rate ratio of TMAH is two to three times that of KOH solution. Additionally, etch rate of  $SiO_x$  mask is an order of magnitude lower in TMAH than in KOH. Besides, surface morphology analysis indicates that TMAH etching can obtain much higher quality inverted pyramids of sharp vertex, smooth <111> sidewall and uncontaminated surface than KOH etching, which makes TMAH etching samples show better anti-reflection properties [18]. It reveals that TMAH is more attractive for the preparation of inverted pyramids than KOH. But TMAH can bring more organic contaminations to the c-Si wafers.

Rounding and smoothing of pyramidal structures is an imporant part to decrease the defect densities at the c-Si surface after texturing. Through immersing the samples in an anisotropic poly-Si etching solution which consists of HF and HNO<sub>3</sub>, the sharp pyramids will be smoothed.

#### 1.3.2. Interfacial oxides

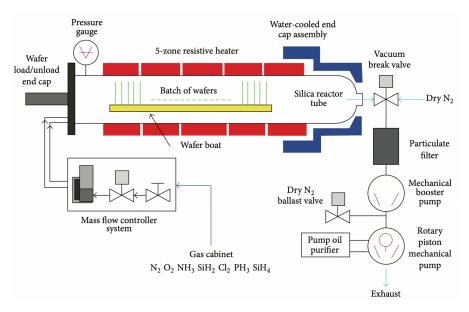

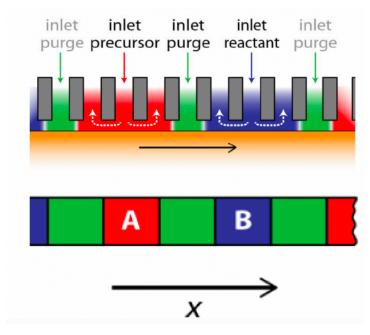

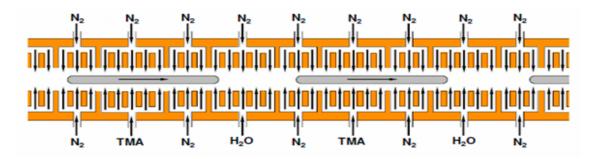

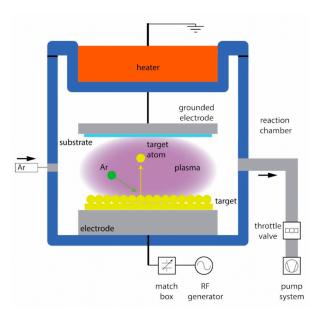

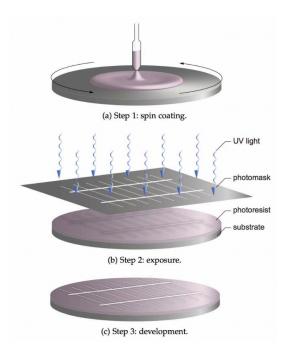

In most cases, the poly- $Si(O_x)$  carrier selective passivating contacts are composed of c-Si/ultra-thin  $SiO_x$ /doped poly- $Si(O_x)$  stack. The ultra-thin  $SiO_x$  layer firstly induced Si-O bonds and therefore form-