# The DELFT-JAVA Engine

Clair Johnston Glossner

Computer Engineering Laboratory Faculty of Electrical Engineering Delft University of Technology P.O. Box 5031, NL-2600 GA Delft, The Netherlands

November 5, 2001

| - |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

# The DELFT-JAVA Engine

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof.ir. K.F. Wakker, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op maandag 5 november 2001 om 16.00 uur

door

Clair Johnston GLOSSNER

Master of Science in Electrical Engineering National Technological University geboren te Lock Haven, Pennsylvania, U.S.A. Dit proefschrift is goedgekeurd door de promotor:

Prof.dr. S. Vassiliadis

#### Samenstelling van de promotiecommissie:

Rector Magnificus, voorzitter Technische Universiteit Delft, Nederland

Prof. dr. S. Vassiliadis Technische Universiteit Delft, Nederland, promotor

Prof. dr. N.J. Dimopoulos University of Victoria, Canada

Prof. dr. M. Valero

Universitat Politecnica de Catalunya, Spanje

Prof. dr. ir. P.M. Dewilde

Technische Universiteit Delft, Nederland

Prof. dr. ir. Th. Krol Universiteit Twente, Nederland

Prof. ir. G.L. Reijns Technische Universiteit Delft, Nederland Dr. S. Cotofana Technische Universiteit Delft, Nederland

#### CIP-DATA KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Clair Johnston Glossner III The DELFT-JAVA Engine

Clair Johnston Glossner III. – [S.l.: s.n.]. – Ill.

Thesis Technische Universiteit Delft. – With ref. – With summary in Dutch

ISBN 90-407-2255-2

Subject headings: computer arithmetic, computer design and engineering, multimedia enhancements, hardware accelerators, multimedia processors, multimedia architecture, java processor.

Cover design is "The Horsemen" of Java's Mount Bromo. Courtesy of asiafoto.

Copyright © 2001 Clair Johnston Glossner III

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

Printed in The Netherlands

# Dedication

This dissertation is dedicated to my loving wife, Lisa, who has persevered through three advanced degrees while I worked more than full time. She has encouraged me to complete this work through job changes, physical relocations, four children, many late hours of work, and many even later hours of writing papers and this dissertation.

# The DELFT-JAVA Engine

### Clair Johnston Glossner

## Abstract\_\_\_\_\_

**n** this dissertation, we describe the DELFT-JAVA engine - a 32-bit RISCbased architecture that provides high performance JAVA program execution. More specifically we describe a microarchitecture that accelerates JAVA execution and provide details of the DELFT-JAVA architecture for executing JAVA Virtual Machine bytecode. The basic architecture implements a Media Processor with Signal Processing capabilities. The perspective of the approach is that to maximally accelerate a compiled application, the machine language should accurately reflect the type of operations the compiler specifies. Except where JAVA Virtual Machine operations are unusually complex, we prefer to allow the compiler to optimize directly to the implementation. This is independent of any particular machine organization. The architecture is then a superset of the JAVA Virtual Machine and provides operations that are necessary for system execution (e.g., I/O, supervision, etc.). Rather than just supporting the JAVA Virtual Machine, the architecture takes a more general purpose approach in that it also is intended to be programmed from a number of additional high-level languages including C and C++. Furthermore, we introduce the concept of JAVA dynamic instruction translation, a new approach to JAVA hardware acceleration. In hardware assisted dynamic translation, JAVA Virtual Machine instructions are translated on-the-fly into the DELFT-JAVA instruction set. The hardware requirements to perform this translation are not excessive. Consequently, support for JAVA language constructs are also incorporated into the processor's Instruction Set Architecture. This technique allows application level parallelism inherent in the JAVA language to be efficiently utilized as instruction level parallelism. In addition to dynamic translation, a special Link Translation Buffer (LTB) can be used to improve the performance of dynamic linking. In addition, there are some key organization structures which we deem appropriate to provide architectural support for including: a) synchronization for multithreaded organizations, b) garbage collection, c) array bounds checking, d) real-time caches, e) multiple machines which can time-share the same datapath (e.g., the JAVA Virtual Machine and Media Processing functions), and f) vector/dsp operations. By building several models of the DELFT-JAVA engine, we were able to characterize performance metrics of kernels executing on our processor. We found that when compared to realizable stack-based machines, our techniques could improve performance by 2.7x. Furthermore, by converting stack-based dependencies into pipeline dependencies, we showed that out-of-order superscalar machines could remove up to 60% of the hazards.

| - |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

## Acknowledgments

would like to thank prof.dr. Stamatis Vassiliadis for his patience, encouragement, guidance, and assistance in completing this research. His insights into high- performance processors significantly shaped the development of this dissertation. I would also like to acknowledge his wonderful abilities as a chef. His multitalented capabilities made my studies with him a complete joy.

I would like to thank prof.dr. Fred Brooks of the University of North Carolina. His love of computer architecture sparked a latent interest for me in computer architecture. The historical context in which he described machines of old and new created an environment that cultivated my interest in computer architecture.

Furthermore, I would like to thank my officemate prof.dr. Sorin Cotofana. We have had many wonderful artistic and philosophical discussions together. I really appreciate the education you gave me on European culture.

I also thank Lidwina Tromp and Mihaela Dirlea for their generous help in formatting the thesis. I am particularly indebted to Lidwina for her help in the design of the cover of this thesis. I am also very thankful that Casper Lageweg translated the samenvatting and stellingen.

I would also like to thank and acknowledge Alexandru Berlea who contributed portions of the garbage collection work for this dissertation.

Finally, I would like to thank dr. Jerry Pechanek. Jerry introduced me to prof.dr. Vassiliadis, mentored me in computer architecture, and imparted more wisdom to me than nearly all others whom I've come in contact with. My life is greatly enriched for the years I worked with Jerry. Especially memorable were all the great travels we shared together - especially Paris and the train.

John Glossner

Carmel, NY, May 2001

| - |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

# **Contents**

| De | edicat | ion                               | V    |

|----|--------|-----------------------------------|------|

| Al | bstrac | et                                | vii  |

| A  | cknov  | vledgments                        | ix   |

| LI | IST O  | F FIGURES                         | XV   |

| LI | IST O  | F TABLES                          | xvii |

| Ll | IST O  | F PROGRAMS                        | XX   |

|    |        |                                   |      |

| 1  | Intr   | oduction                          | 1    |

|    | 1.1    | Related Work + Open Questions     | . 4  |

|    | 1.2    | Framework of the Presentation     | . 9  |

| 2  | JVN    | 1: Brief Introduction             | 13   |

|    | 2.1    | Stack Machines and Java Execution | . 15 |

|    |        | Stack Operations                  | . 15 |

|    | 2.2    | Memory (Storage) Organization     | . 18 |

|    |        | 2.2.1 Spaces                      | . 19 |

|    |        | 2.2.2 Memory (Storage) Access     | . 22 |

|    | 2.3    | Operations                        | . 25 |

|   |                                        | 2.3.1                                                   | Operation Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28                                         |

|---|----------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

|   |                                        | 2.3.2                                                   | JAVA Virtual Machine Operation List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28                                         |

|   | 2.4                                    | Instruc                                                 | ction Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45                                         |

|   |                                        | 2.4.1                                                   | Supervision and I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49                                         |

|   |                                        | 2.4.2                                                   | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51                                         |

| 3 | Delf                                   | t-Java A                                                | Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 53                                         |

|   | 3.1                                    | Memo                                                    | ry (Storage) Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54                                         |

|   |                                        | 3.1.1                                                   | Spaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54                                         |

|   |                                        | 3.1.2                                                   | Storage Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56                                         |

|   | 3.2                                    | Operat                                                  | tions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60                                         |

|   | 3.3                                    | Instruc                                                 | ction Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73                                         |

|   | 3.4                                    | Superv                                                  | vision and I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 79                                         |

|   | 3.5                                    | Java S <sub>1</sub>                                     | pecific Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 82                                         |

|   | 3.6                                    | Conclu                                                  | asion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 84                                         |

| 4 | Mic                                    | roarchit                                                | tecture and Java Acceleration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 85                                         |

|   | 4.1                                    | Dynan                                                   | nic Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 86                                         |

|   | 4.2                                    | Examp                                                   | ole Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 88                                         |

|   |                                        | _                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                            |

|   | 4.3                                    | Hardw                                                   | vare Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 91                                         |

|   | 4.3<br>4.4                             |                                                         | rare Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 91<br>93                                   |

|   | -                                      | Link T                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                            |

|   | 4.4                                    | Link T<br>LTB A                                         | Cranslation Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93                                         |

|   | 4.4<br>4.5                             | Link T<br>LTB A                                         | Cranslation Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93<br>96                                   |

|   | 4.4<br>4.5                             | Link T<br>LTB A<br>Concur<br>4.6.1                      | Cranslation Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93<br>96<br>100                            |

|   | 4.4<br>4.5<br>4.6                      | Link T<br>LTB A<br>Concur<br>4.6.1<br>Garbag            | Cranslation Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93<br>96<br>100                            |

|   | 4.4<br>4.5<br>4.6<br>4.7               | Link T<br>LTB A<br>Concur<br>4.6.1<br>Garbag<br>Related | Cranslation Buffer   Acceleration   Buffer   Acceleration   In the result of the properties o | 93<br>96<br>100<br>106                     |

| 5 | 4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9 | Link T<br>LTB A<br>Concur<br>4.6.1<br>Garbag<br>Related | Cranslation Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93<br>96<br>100<br>106<br>107              |

| 5 | 4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9 | Link T LTB A Concur 4.6.1 Garbag Related Conclu         | Translation Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93<br>96<br>100<br>106<br>107<br>12<br>113 |

|     | 5.3                           | LTB R    | esults                            | 118 |

|-----|-------------------------------|----------|-----------------------------------|-----|

|     |                               | 5.3.1    | Available Performance             | 119 |

|     |                               | 5.3.2    | Workload Characterization         | 120 |

|     |                               | 5.3.3    | LTB Characterization              | 121 |

|     |                               | 5.3.4    | LTB Conclusions                   | 122 |

|     | 5.4                           | Java F   | FT Results                        | 123 |

|     | 5.5                           | Garbaş   | ge Collection Results             | 128 |

|     |                               | 5.5.1    | Copy Collector Experiment         | 128 |

|     |                               | 5.5.2    | Generational Collector Experiment | 135 |

|     | 5.6                           | Conclu   | asions                            | 141 |

| 6   | Con                           | clusions | S                                 | 143 |

|     | 6.1                           | Major    | Contributions                     | 149 |

|     | 6.2                           | Open 1   | Issues                            | 151 |

| Sa  | menv                          | atting   |                                   | 153 |

| Bil | bliogr                        | aphy o   | f C. John Glossner                | 155 |

| Bio | Biography of C. John Glossner |          |                                   |     |

| Bil | bliogr                        | aphy     |                                   | 165 |

# **List of Figures**

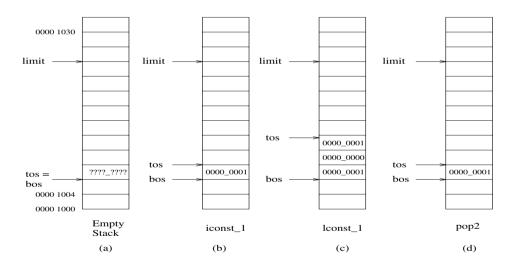

| 2.1 | Stack Example                                                                                                | 14  |

|-----|--------------------------------------------------------------------------------------------------------------|-----|

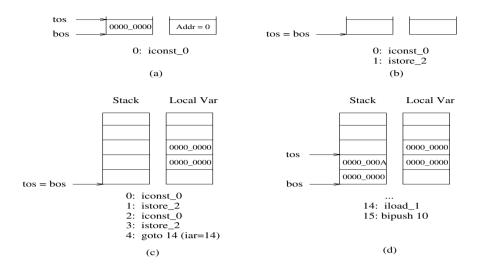

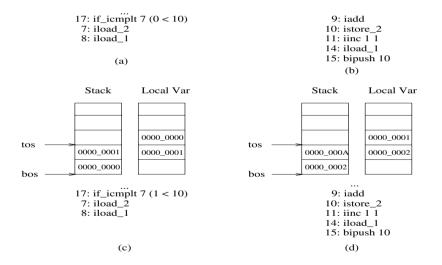

| 2.2 | Stack Execution Example                                                                                      | 17  |

| 2.3 | Bytecode Stack (cont.)                                                                                       | 17  |

| 2.4 | JVM Operand Address Formats                                                                                  | 23  |

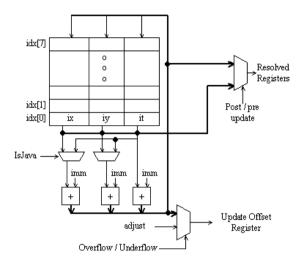

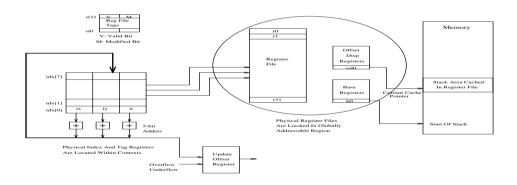

| 4.1 | Indirect Register Access                                                                                     | 86  |

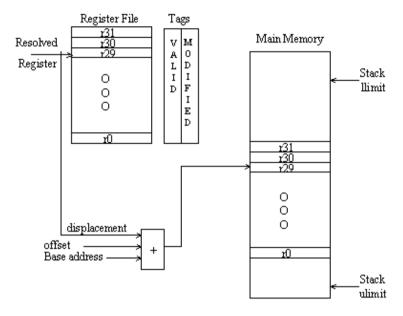

| 4.2 | Indirect Register Mapping                                                                                    | 87  |

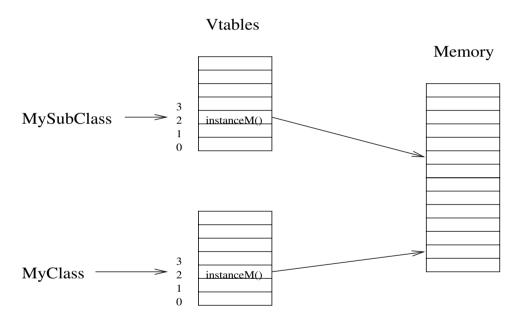

| 4.3 | C++ Virtual Table Implementation                                                                             | 95  |

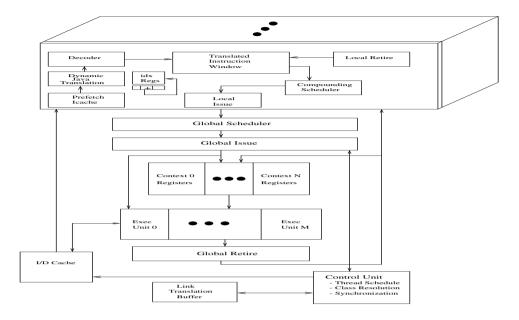

| 4.4 | Link Translation Buffer                                                                                      | 99  |

| 4.5 | Concurrent Multithreaded Organization                                                                        | 100 |

| 4.6 | Concurrent Multithreaded Registers                                                                           | 102 |

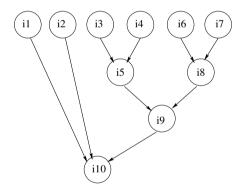

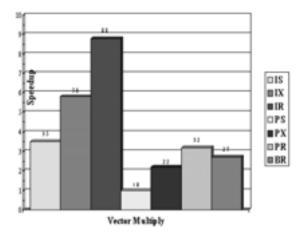

| 4.7 | Vector Multiply Dependency Graph                                                                             | 106 |

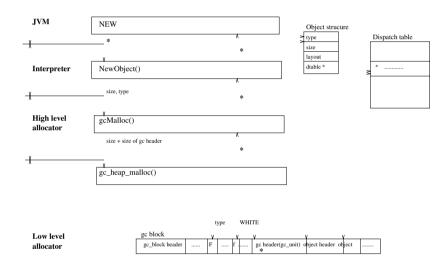

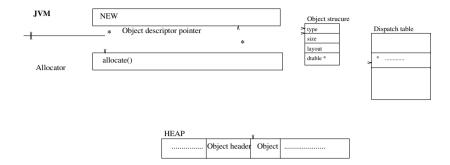

| 4.8 | Object allocation in the Kaffe JVM                                                                           | 110 |

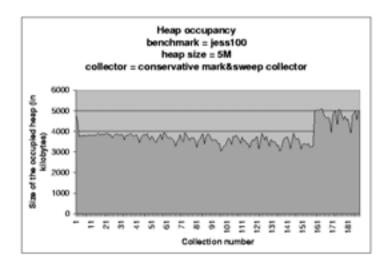

| 4.9 | Heap occupancy in the <i>jess</i> benchmark, when interpreted by the CC Kaffe JVM with a heap of 5 Megabytes | 111 |

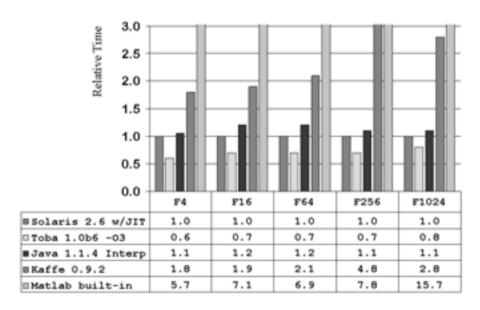

| 5.1 | Performance Results                                                                                          | 117 |

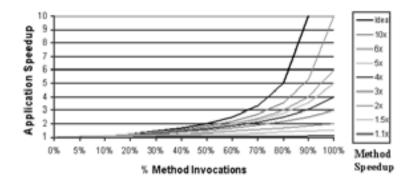

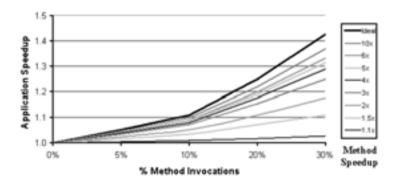

| 5.2 | Application Speedup Versus Method Speedup                                                                    | 119 |

| 5.3 | Application Speedup Versus Method Speedup                                                                    | 119 |

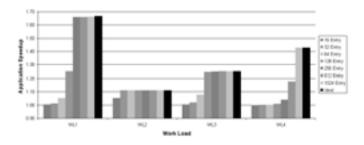

| 5.4 | Application Speedup Versus LTB Cache Size for Workloads .                                                    | 121 |

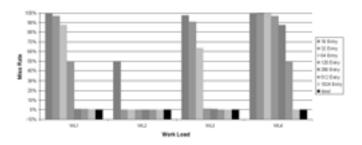

| 5.5 | LTB Miss Rate Versus Entries for Workloads                                                                   | 122 |

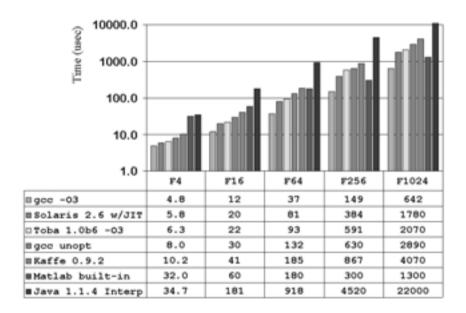

| 5.6 | Traditional FFT Speedup                                                                                      | 124 |

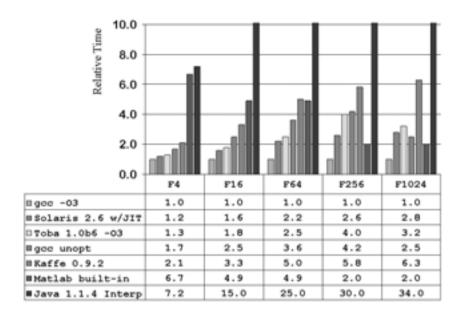

| 5.7 | Relative Traditional FFT Speedup                                                                             | 125 |

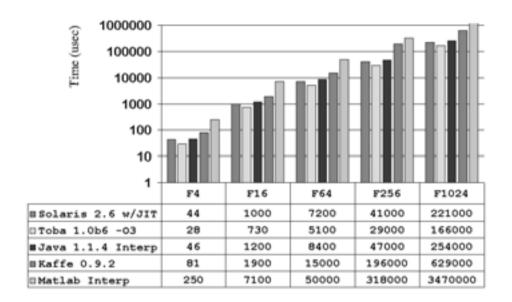

| 5.8 | Tensor FFT Speedup                                                                                           | 126 |

| 5.9  | Tensor FFT Relative Speedup                                                                                   | 126 |

|------|---------------------------------------------------------------------------------------------------------------|-----|

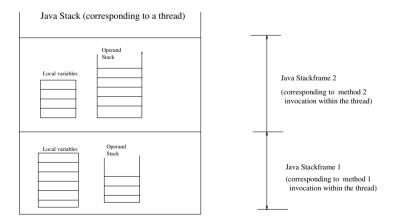

| 5.10 | A thread's stack in Java                                                                                      | 129 |

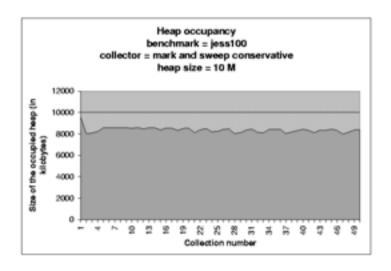

| 5.11 | Heap occupancy in the jess benchmark, when interpreted by the MS Kaffe JVM with a heap of 5 Megabytes         | 133 |

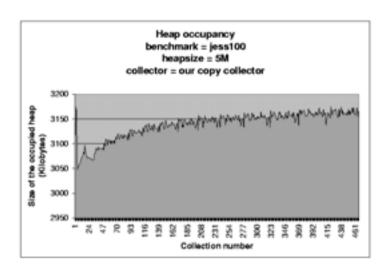

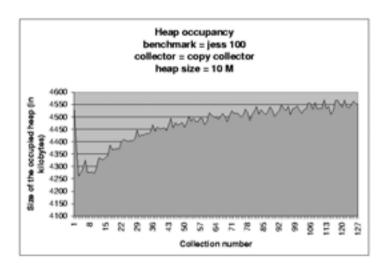

| 5.12 | Heap occupancy in the <i>jess</i> benchmark, when interpreted by the CC Kaffe JVM with a heap of 5 Megabytes  | 134 |

| 5.13 | Heap occupancy in the <i>jess</i> benchmark, when interpreted by the MS Kaffe JVM with a heap of 10 Megabytes | 135 |

| 5.14 | Heap occupancy in the jess benchmark, when interpreted by the CC Kaffe JVM with a heap of 10 Megabytes        | 136 |

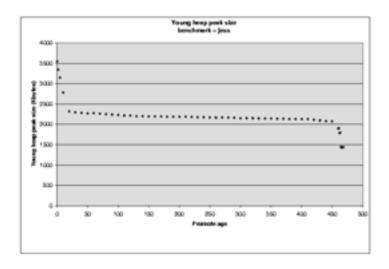

| 5.15 | Young heap peak size in the jess benchmark                                                                    | 139 |

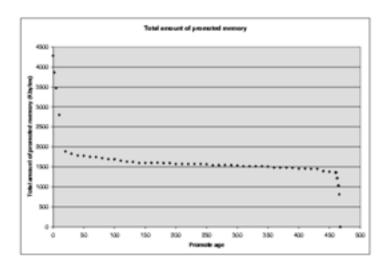

| 5.16 | Total amount of promoted memory jess benchmark                                                                | 140 |

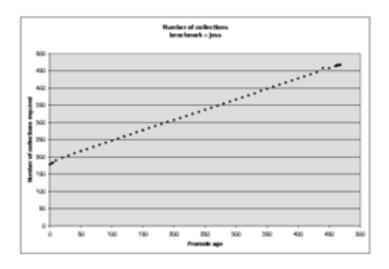

| 5.17 | Number of collections required for different promote ages in the jess benchmark                               | 141 |

# **List of Tables**

| 2.1  | JVM Memory Spaces                                             | 19 |

|------|---------------------------------------------------------------|----|

| 2.2  | JAVA Virtual Machine Datatypes                                | 26 |

| 2.3  | JVM Data Movement Instructions                                | 29 |

| 2.4  | JVM Load Constant Instructions                                | 29 |

| 2.5  | JVM Load Constant Instructions                                | 30 |

| 2.6  | JVM Store Constant Instructions                               | 31 |

| 2.7  | JVM Format Transformation Instructions                        | 32 |

| 2.8  | JVM Conversion Instructions                                   | 33 |

| 2.9  | JVM Logical Connective Instructions                           | 33 |

| 2.10 | JVM Shift Instructions                                        | 34 |

| 2.11 | JVM Add and Subtract Instructions                             | 35 |

| 2.12 | JVM Multiplication and Division Instructions                  | 36 |

| 2.13 | JVM Floating Point Add and Subtract Instructions              | 37 |

| 2.14 | JVM Floating Point Multiplication and Division Instructions . | 39 |

| 2.15 | JVM Comparison Results                                        | 39 |

| 2.16 | JVM Comparison Instructions                                   | 40 |

| 2.17 | JVMArray Element Types                                        | 41 |

| 2.18 | JVM Array Creation Instructions                               | 41 |

| 2.19 | JVM Array Load Instructions                                   | 42 |

| 2.20 | JVM Array Store Instructions                                  | 42 |

| 2.21 | JVM Array Miscellaneous Instructions                          | 42 |

| 2.22 | JVM Object Creation Instructions                              | 43 |

| 2.23 | JVM Object Manipulation Instructions           | 43 |

|------|------------------------------------------------|----|

| 2.24 | JVM Miscellaneous Object Instructions          | 44 |

| 2.25 | JVM Miscellaneous Instructions                 | 44 |

| 2.26 | JVM Integer Conditional Branch Instructions    | 46 |

| 2.27 | JVM Reference Conditional Branch Instructions  | 47 |

| 2.28 | JVM Unconditional Branch Instructions          | 47 |

| 2.29 | JVM Switch/Case Instructions                   | 47 |

| 2.30 | JVM Method Invocation Instructions             | 48 |

| 2.31 | JVM Return Instructions                        | 48 |

| 2.32 | JVM Subroutine Instructions                    | 49 |

| 2.33 | JVM Interlock Instructions                     | 50 |

| 3.1  | DELFT-JAVA Datatypes                           | 57 |

| 3.2  | DELFT-JAVA Operation Categories                | 59 |

| 3.3  | DELFT-JAVA Load and Store Operations Function  | 61 |

| 3.4  | DELFT-JAVA Load and Store Operations Syntax    | 62 |

| 3.5  | DELFT-JAVA Format Transformation Operations    | 62 |

| 3.6  | DELFT-JAVA Data Code Transformation Operations | 63 |

| 3.7  | DELFT-JAVA Logical Connective Operations       | 63 |

| 3.8  | DELFT-JAVA Composite Logic Operations          | 64 |

| 3.9  | DELFT-JAVA Shift Operations                    | 64 |

| 3.10 | -                                              | 65 |

| 3.11 | DELFT-JAVA Absolute Value Operation            | 66 |

|      | DELFT-JAVA Add Operations Function.            | 67 |

|      | DELFT-JAVA Add Operations Syntax               | 67 |

|      | DELFT-JAVA Multiply/Divide Operations          | 68 |

|      | DELFT-JAVA Multiply/Divide Operations          | 68 |

|      | DELFT-JAVA Compare Operation                   | 71 |

|      | DELFT-JAVA Comparison Results                  | 71 |

|      | DELFT-JAVA Vector Permute Operation.           | 72 |

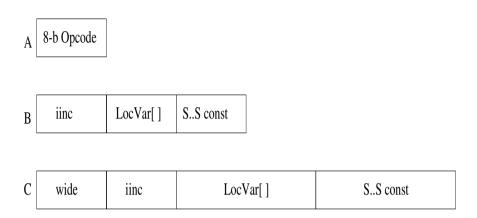

|      | DELFT-JAVA Wide Prefix                         | 73 |

|      |                                                |    |

| 3.20 | DELFT-JAVA Program Completion                             | 13  |

|------|-----------------------------------------------------------|-----|

| 3.21 | DELFT-JAVA Relative Branch Conditions with Compare        | 75  |

| 3.22 | DELFT-JAVA Relative Branch Conditions with Compare        | 75  |

| 3.23 | DELFT-JAVA Floating Point Branch Conditions               | 76  |

| 3.24 | DELFT-JAVA Floating Point Branch Conditions               | 76  |

| 3.25 | Trap Instructions                                         | 77  |

| 3.26 | DELFT-JAVA Return from Trap/Interrupt Instruction(16-bit) | 77  |

| 3.27 | Delegation Operations                                     | 78  |

| 3.28 | DELFT-JAVA Return Operations                              | 78  |

| 3.29 | DELFT-JAVA Atomic Operations Function                     | 79  |

| 3.30 | DELFT-JAVA Atomic Operations                              | 79  |

| 3.31 | DELFT-JAVA Privileged Operations                          | 80  |

| 3.32 | DELFT-JAVA Privileged Operations                          | 80  |

| 3.33 | DELFT-JAVA Control Registers I                            | 80  |

| 3.34 | DELFT-JAVA Control Registers II                           | 81  |

| 3.35 | DELFT-JAVA JVM specific Instructions                      | 83  |

| 3.36 | DELFT-JAVA LTB specific Instructions                      | 84  |

| 4.1  | Instructions with Special Support                         | 92  |

| 5.1  | Model Characteristics                                     | 116 |

| 5.2  | Machine Performance                                       | 118 |

| 5 3  | Workload Characteristics                                  | 120 |

# **List of Programs**

| 2.1  | A Simple JAVA Program              |

|------|------------------------------------|

| 2.2  | Simple JAVA Bytecodes              |

| 4.1  | Indirect Instructions              |

| 4.2  | Vector Multiply Example            |

| 4.3  | Compiled Inner Loop Bytecode 89    |

| 4.4  | Translation Bytecode               |

| 4.5  | Final Delft-JavaInstructions       |

| 4.6  | C++ Method Invocation              |

| 4.7  | JAVA Method Invocation             |

| 4.8  | JAVA Method Invocation Bytecode 96 |

| 4.9  | Garbage Collection Interface       |

| 4.10 | Garbage Collection Roots           |