# QuMAsim: A Quantum Architecture Simulation and Verification Platform

Mengyu Zhang

<CE-MS-2018-023>

#### Abstract

Quantum microarchitecture is a key component in bridging the gap between quantum software and quantum hardware of a fully programmable quantum computer. Confronting the control problem of superconducting quantum processors, an experimental microarchitecture (QuMA) has been proposed in previous work. As the size of the target quantum chip continues to evolve, the complexity of QuMA scales up accordingly. This increase in complexity has led to a growing challenge in QuMA's design, development, and verification. To solve these problems, we build a QuMA simulator which can automate the current QuMA verification process and accelerate the design phase of QuMA. We called this simulator QuMAsim. The first version of QuMAsim is based on CC-Light, an instance of QuMA for controlling a surface-7 superconducting qubit chip. Then this simulator is extended to be self-configurable for different quantum chips. Several applications are built based on this simulator. The verification platform consists of the simulator, the VHDL implementation of QuMA and a validator is designed to automate the verification procedure. In addition, we built a quantum virtual machine based on QuMAsim, which includes other quantum software and simulators to simulate the execution of quantum algorithms on each layer of the quantum computer. We demonstrate the potential of QuMAsim by performing some experiments with it and its applications, including the gearbox circuit simulation.

# QUMASIM: A QUANTUM ARCHITECTURE SIMULATION AND VERIFICATION PLATFORM

by

### Mengyu Zhang

in partial fulfillment of the requirements for the degree of

**Master of Science** in Microelectronics

at the Delft University of Technology, to be defended publicly on Friday August 24, 2018 at 14:00 AM.

Supervisor: Prof. dr. K. L. M. Bertels

Thesis committee: Prof. dr. K. L. M. Bertels TU Delft

Prof. dr. L. Dicarlo TU Delft Dr. C. G. Almudever TU Delft

An electronic version of this thesis is available at http://repository.tudelft.nl/.

Dedicated to my family and friends

## **CONTENTS**

| Li | ist of Figures vi |                                                  |      |  |  |  |

|----|-------------------|--------------------------------------------------|------|--|--|--|

| Li | st of             | Tables                                           | ix   |  |  |  |

| Li | st of A           | Acronyms                                         | хi   |  |  |  |

| Ac | knov              | wledgements                                      | xiii |  |  |  |

|    |                   |                                                  |      |  |  |  |

|    |                   |                                                  |      |  |  |  |

| 1  |                   | roduction                                        | 1    |  |  |  |

|    | 1.1               |                                                  |      |  |  |  |

|    |                   | Research motivation                              |      |  |  |  |

|    |                   | Organization                                     |      |  |  |  |

|    | 1.7               | Organization                                     | 3    |  |  |  |

| 2  |                   | ekground                                         | 5    |  |  |  |

|    | 2.1               | Quantum Computing Basics                         |      |  |  |  |

|    |                   | 2.1.1 Qubits                                     |      |  |  |  |

|    |                   | 2.1.2 Quantum Gates                              |      |  |  |  |

|    | 0.0               | 2.1.3 Universal Quantum Computation              |      |  |  |  |

|    |                   | Full Stack Quantum Computer                      |      |  |  |  |

|    | 2.3               | Hardware                                         |      |  |  |  |

|    |                   | <ul><li>2.3.1 Superconducting Qubits</li></ul>   |      |  |  |  |

|    |                   | 2.3.3 Implication on the Control                 |      |  |  |  |

|    |                   | 2.3.4 Quantum Microarchitecture                  |      |  |  |  |

|    | 2.4               | Quantum Instruction Set Architecture             |      |  |  |  |

|    | 2.4               | 2.4.1 QISA overview                              |      |  |  |  |

|    |                   | 2.4.2 eQASM                                      |      |  |  |  |

|    | 2.5               | Compiler and Language.                           |      |  |  |  |

|    |                   |                                                  |      |  |  |  |

| 3  |                   | nulator implementation                           | 15   |  |  |  |

|    | 3.1               | QuMA Structure                                   |      |  |  |  |

|    |                   | 3.1.1 Overview                                   |      |  |  |  |

|    |                   | 3.1.2 Quantum Pipeline                           |      |  |  |  |

|    |                   | 3.1.3 Classical Pipeline                         |      |  |  |  |

|    | 2.2               | 3.1.4 Comprehensive Feedback Control             |      |  |  |  |

|    | 3.2               | Simulator Implementation                         |      |  |  |  |

|    |                   | 3.2.1 Goals and Requirements                     |      |  |  |  |

|    |                   | 3.2.2 SystemC                                    |      |  |  |  |

|    |                   | 3.2.3 QuMAsim overview                           |      |  |  |  |

|    | 3.3               |                                                  |      |  |  |  |

|    | 3.3               | 3.3.1 Quantum Layout Information                 |      |  |  |  |

|    |                   | 3.3.2 Instruction Set Architecture Modifications |      |  |  |  |

|    |                   | 3.3.3 Final Implementation                       |      |  |  |  |

|    | 3.4               |                                                  |      |  |  |  |

|    | 5.4               | 3.4.1 Triggered output                           |      |  |  |  |

|    |                   | 3.4.2 Register values                            |      |  |  |  |

|    |                   | 3.4.3 Measurement results                        |      |  |  |  |

|    |                   | 3 4 4 Instruction under execution                | 27   |  |  |  |

vi Contents

|     | 3.5   | Conclusion                             | 27 |

|-----|-------|----------------------------------------|----|

| 4   | App   | lications                              | 29 |

|     | 4.1   | Verification Platform                  | 29 |

|     |       | 4.1.1 Overview and approach selection  | 29 |

|     |       | 4.1.2 Implementation                   | 30 |

|     | 4.2   | Quantum Virtual Machine                |    |

|     |       | 4.2.1 Overview                         |    |

|     |       | 4.2.2 OpenQL Framework                 |    |

|     |       | 4.2.3 Simulation Platform              | 33 |

|     |       | 4.2.4 A Real Implementation            |    |

|     | 4.3   | Conclusion                             | 39 |

| 5   | Exp   | eriments                               | 41 |

| Ū   |       | Verification Experiment                | 41 |

|     | 0.1   | 5.1.1 Testbench                        |    |

|     |       | 5.1.2 Verification Environment         |    |

|     |       | 5.1.3 Result                           |    |

|     | 5.2   | Full Stack Simulation                  |    |

|     | 3.2   | 5.2.1 Simulation Environment           |    |

|     |       | 5.2.2 CNOT-measurement test            |    |

|     |       | 5.2.3 Gearbox Circuit Simulation       |    |

|     | 5.3   | Microarchitecture Design Experiment    |    |

|     | 5.5   | 5.3.1 Different Microwave Setup        |    |

|     |       | 5.3.2 Implementation                   |    |

|     |       | •                                      | 43 |

| 6   |       | ······································ | 51 |

|     | 6.1   | Conclusion                             | 51 |

|     | 6.2   | Future Work                            | 52 |

| Bil | bliog | raphy                                  | 53 |

# **LIST OF FIGURES**

| 2.1 | Overview of quantum computer system stack                                                     | 8<br>sion |

|-----|-----------------------------------------------------------------------------------------------|-----------|

| ۷.۷ | line crossover. (c) Vertical I/O                                                              | 9         |

| 2.3 | Layout of a surface code using 7 qubits                                                       | 10        |

| 2.4 | The relationship between control unit and quantum processor                                   | 10        |

| 2.5 | Schematic of how to control a Surface-17 chip                                                 | 11        |

| 2.3 | Schematic of now to control a surface-17 cmp                                                  | 11        |

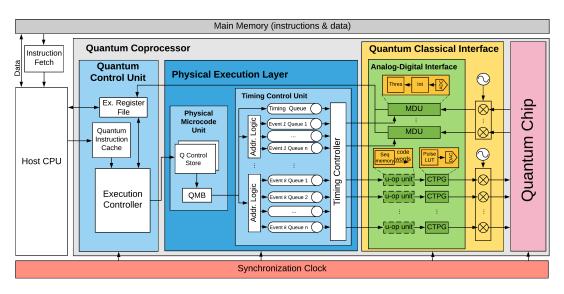

| 3.1 | Overview of the structure of QuMA_v1                                                          | 15        |

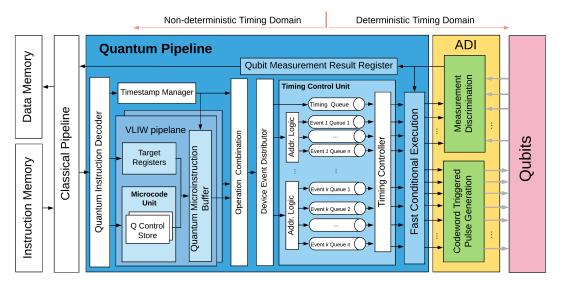

| 3.2 | Overview of the structure of QuMA_v2, it is more complex compared to QuMA_v1 since it needs   |           |

|     | to control more qubits                                                                        | 16        |

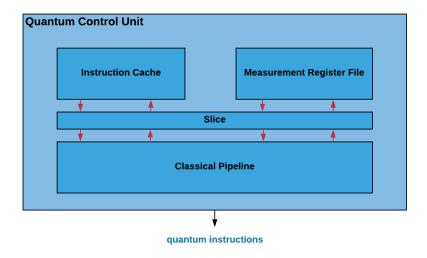

| 3.3 | Quantum control unit structure                                                                | 18        |

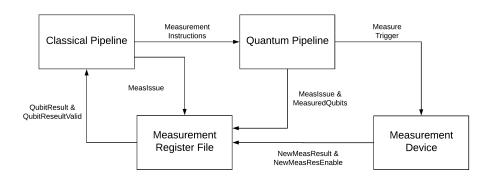

| 3.4 | Comprehensive feedback control logic                                                          | 19        |

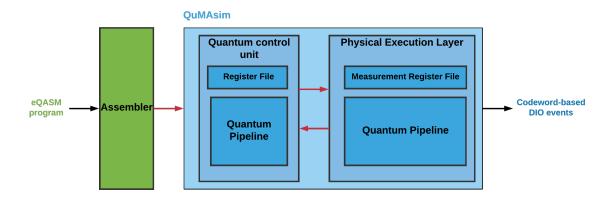

| 3.5 | The overall structure of QuMAsim                                                              | 21        |

| 3.6 | The quantum processor architecture for surface-17                                             | 23        |

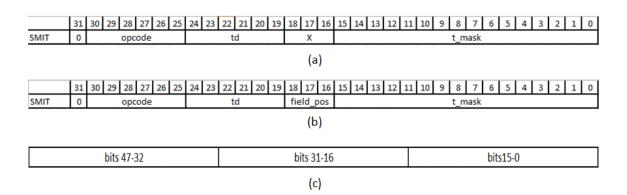

| 3.7 | Modifications on microarchitecture for SC17                                                   | 24        |

| 3.8 | The modifications for SMIT instruction. (a) The SMIT binary format for SC7 chip. (b) The SMIT |           |

|     | binary format for SC17 chip. (c) T-mask register structure for SC17 chip                      | 24        |

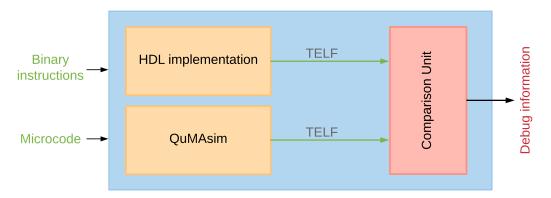

| 4.1 | Structure of the verification platform, which consists of QuMAsim, the HDL implementation     |           |

|     | and a validator                                                                               | 30        |

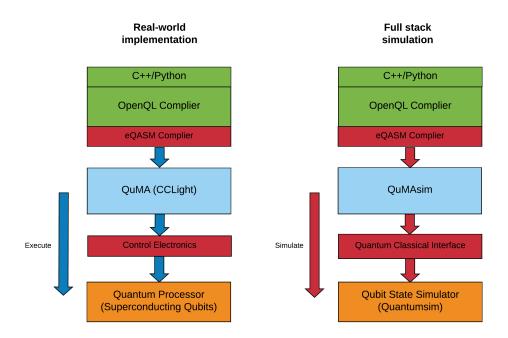

| 4.2 | Structure of the real-world implementation and structure of the full stack simulator          | 33        |

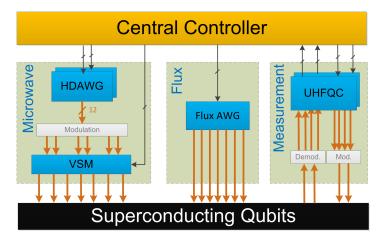

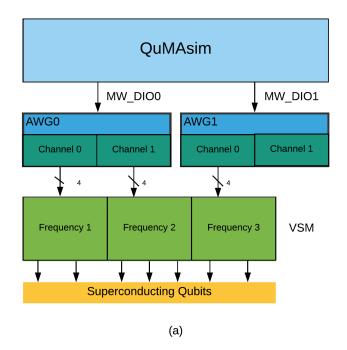

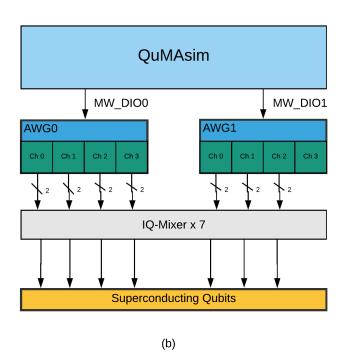

| 4.3 | Control electronics between central controller and superconducting qubits                     | 33        |

| 4.4 | OpenQL framework structure                                                                    | 34        |

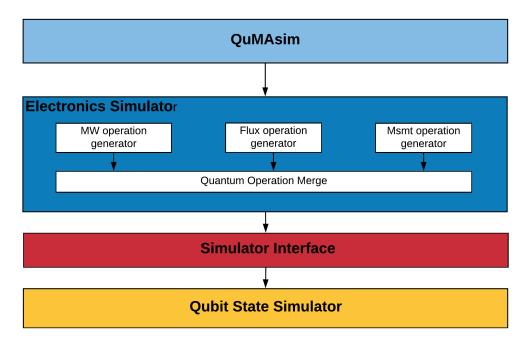

| 4.5 | Structure of electronics simulator in the full stack quantum simulator                        | 35        |

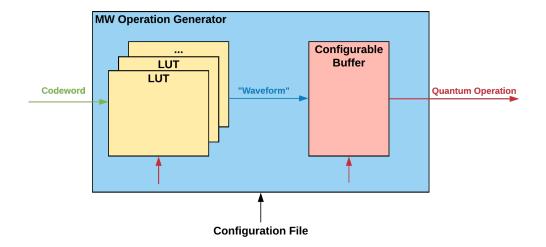

| 4.6 | Structure of the microwave operation generator                                                | 36        |

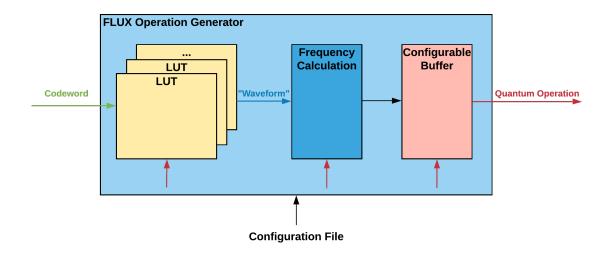

| 4.7 | Structure of the flux operation generator                                                     | 36        |

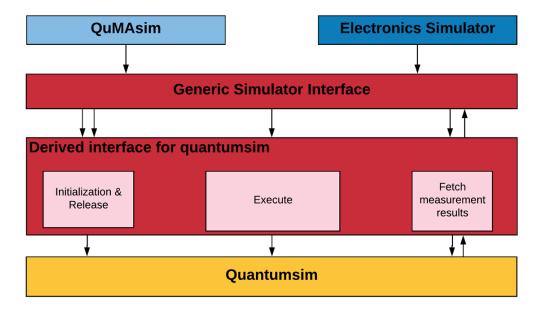

| 4.8 | Simulation interface which connects QuMAsim and electronics simulator to QuantumSim. This     |           |

|     | interface is derived from a generic simulator interface for all simulation back-ends          | 37        |

| 4.9 | Detailed functions for controlling QuantumSim in the interface                                | 38        |

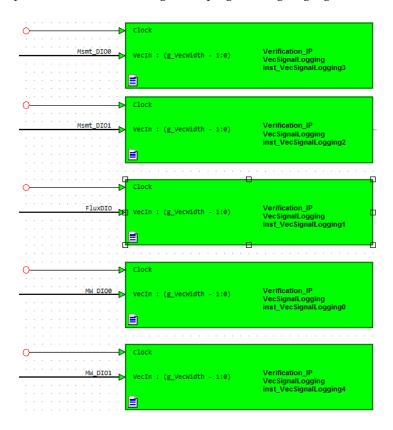

| 5.1 | Recording modules for tracing the DIO outputs of VHDL implementation of QuMA_v3. These        |           |

|     | modules are instantiated from the verification library                                        | 42        |

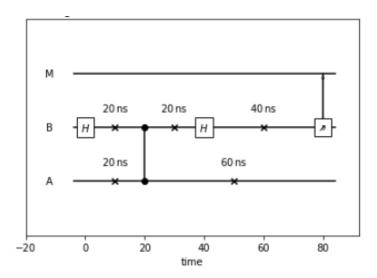

| 5.2 | An example of the CNOT-measurement circuit                                                    | 43        |

| 5.3 | The 150 measurement results of qubit 0 generated by the quantum virtual machine               | 45        |

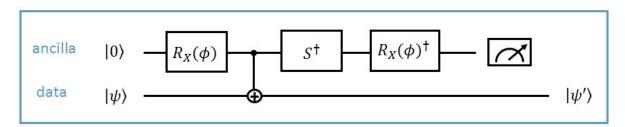

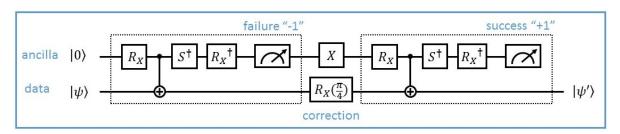

| 5.4 | A special case of gearbox circuit                                                             | 45        |

| 5.5 | Level-1 gearbox circuit implemented by recycling the same qubit as the ancilla qubit. The se- |           |

|     | quence of operations to the case of a single failure followed by correction and success       | 46        |

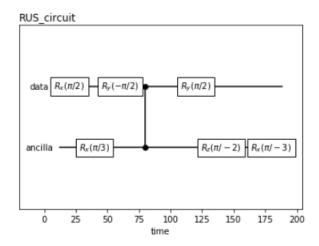

| 5.6 | The experimental implementation of a RUS block                                                | 46        |

| 5.7 | (a) The microwave setup used in CC-Light. (b) Proposed new microwave setup                    | 50        |

# LIST OF TABLES

| 2.1 | Quantum circuit of some commonly-used quantum gates                                | 7  |

|-----|------------------------------------------------------------------------------------|----|

| 2.2 | Overview of eQASM Instructions. The operator $::$ concatenates the two bit strings | 13 |

| 5.1 | Measurement probabilities of the the theoretically achieved quantum state          | 47 |

| 5.2 | Simulation result without errors                                                   | 48 |

| 5.3 | Simulation result with errors                                                      | 48 |

| 5.4 | Simulation time with and without comprehensive feedback control                    | 48 |

## LIST OF ACRONYMS

**QuMA** Quantum MicroArchitecture

QISA Quantum Instruction Set Architecture

**QEC** Quantum Error Correction

NISQ Noisy Intermediate-Scale Quantum

**QASM** Quantum Assembly Languages

NN Nearest-Neighbour

**QCU** Quantum Control Unit

FPGA Field-Programmable Gate Array

SC7 Surface Code 7

SC17 Surface Code 17

**CPU** Central Processing Unit

**RTL** Register Transfer Level

**VLIW** Very Long Instruction Word

**SIMD** Single Instruction Multiple Date

**SOMQ** Single Operation Multiple Qubit

VSM Vector Switch Matrix

**UVM** Universal Verification Methodology

## **ACKNOWLEDGEMENTS**

First of all, I would like to express my appreciation to my thesis supervisor Prof. Koen Bertels for granting me the opportunity to do my master project in the field of quantum computing. He also gave me the opportunity to involve myself in a number of academic activities and discussions of the entire Quantum and Computer Engineering (Q&CE) department. It is my honour and luck to be able to complete my master project under his supervision.

I would like to thank my colleagues from the Quantum Computer Architecture Lab for all the discussions and fun moments. Special thanks to Xiang Fu for the great support and the detailed guidance on my master project. He offered me a lot of help at the beginning and inspired me at every stage of my work to help me complete this project in a field I am not familiar with. I also want to express my thanks to Leon Risebos, Nader Khammassi, Lingling Lao and Imran Ashraf for all the spontaneous discussions that help me better understand quantum computing to motivate the research. As a master student, I am able to participate in all academic discussions and meetings held in the lab, as well as those entertainment hours. I truly felt part of the team.

I would also like to thank Jeroen van Straten for providing me with guidance on VHDL advanced coding techniques. The DiCarlo group provided a very good working environment for my project, because my work is based on the real hardware. I am especially grateful to Brian Tarasinski for helping me understand the areas of research I have rarely understood before. Without the help from them, my project will be difficult to carry out.

I would like to take this opportunity to thank my fellow batchmates at TU Delft, Jian Zheng, Mingfeng Li, Saiyi Wang, Ye Li, Xiaoming Wen, for those cherished moments in the 10th floor of the faculty of EEMCS.

Finally, I would like to thank my beloved family, my girlfriend, and all the friends who have given me unconditionally love and support over the last two years. During my time studying abroad, I can always rely on them to overcome the bad times in this period.

Thank you all very much!

Mengyu Zhang Delft, August 2018

1

## Introduction

#### 1.1. CONTEXT

Quantum computing has the potential to solve several computational problems that are intractable for classical computers. A quantum algorithm exploits quantum phenomena, namely superposition and entanglement, to achieve speedup over the best classical algorithm solving the same problem. The most famous examples are factoring large numbers using Shor's algorithm [1] and searching an unordered database using Grover's search [2]. These algorithms may require millions or even billions of physical qubits which is far from current technology. This difference causes a significant resource gap between practical quantum algorithms and real quantum computers.

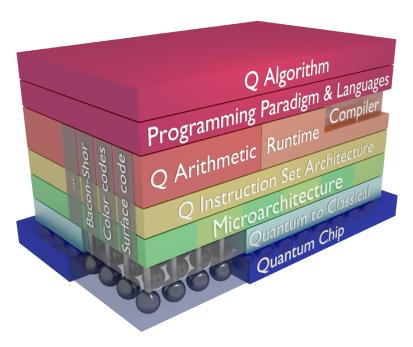

Useful quantum computation would require a full stack architecture. To construct a universal and fully programmable quantum computer, clarifying the required component of a quantum computer is essential. In the QuTech quantum computer system stack [3], multiple layers from top level quantum algorithms to underlying quantum chips are included in a full stack quantum computer. In the middle of this system view, the Quantum Instruction Set Architecture (QISA) and the Quantum Microarchitecture layers play a key role in bridging the gap between quantum software and quantum hardware.

Nowadays, research in quantum computer engineering has focused primarily at devising high-level programming languages and compilers, and building reliable low-level quantum hardware. Relatively little studies have focused on how to control operations on experimental quantum processors. However, with Noisy Intermediate-Scale Quantum (NISQ) cite preskill2018quantum devices with 50 to hundreds of qubits coming soon, we need to start thinking about how to use the compiler output to fully control the quantum chip. To solve this problem, an experimental microarchitecture (QuMA) is proposed in [3] for controlling a superconducting quantum processor.

In our lab, two instances of QuMA are implemented using Field-Programmable Gate Array (FPGA). QuTech Control Box (CBox) targets controlling one or two qubits. The quantum control microarchitecture in CBox is QuMA, which can execute QuMIS instructions. Since there are only a few QuMIS instructions which are low-level and tightly bound to the hardware, the structure of QuMA is relatively simple. Addressing controlling more qubits and the inherent quantum operation issue rate problem of QuMA, we designed an executable QISA, eQASM, which is instantiated to 32-bit instruction set to control seven qubits and implemented by an updated version of the control microarchitecture, Central Controller-Light (CC-Light).

Compared to QuMA, the updated QuMA microarchitecture QuMA\_v2 outputs a larger number of signals to orchestrate the behavior of underlying analog devices to control the seven qubits. The VLIW and SOMQ execution, and the selective broadcasting supported by Vector Switch Matrix (VSM), ask for more complex addressing logic and dynamic checking to avoid conflict operations. Comprehensive feedback control requires interaction between the classical pipeline and the quantum pipeline, and between the non-deterministic timing domain and the deterministic timing domain, which can stall the pipeline for an indefinite number of cycles depending on the quantum program. All these contribute to a higher complexity of control microarchitecture, which pose a big challenge in its design, development, and verification.

2 1. Introduction

#### 1.2. RESEARCH MOTIVATION

The current development flow of QuMA suffers from several drawbacks. At the design stage, we can only do a limited design space exploration (DSE) at abstraction level since we lack information of the inner structure of QuMA by using the diagram-based method. After design phase, we need to directly write HDL to describe the entire system which is very rigid since it has no flexibility. Then at the verification stage, it requires the hardware programmer to check the correctness of multiple signals in simulation for every eQASM program in the benchmark. All these drawbacks lead to a low-efficient and error-prone development flow.

Based on the experience with the design of classical processors, all the three steps (DSE, development, and verification) can be boosted via automation. Therefore, a new approach has been proposed to automate this procedure as much as possible. In this new method, we will perform a high-level modelling at first which can explore design possibilities at high level. Then a platform is used to do automated simulation and verification with low-level details. After we make sure this design can fulfill the requirements, it is finally implemented on hardware like FPGA.

The DSE can be performed via a configurable simulator for the quantum control microarchitecture, like simulators for classical processors such as gem5 [4]. Besides, the verification of the HDL implementation can be automated using the universal verification methodology (UVM) [5], which would require a simulator to reference values for the checking points for each input program. Thus, a dedicated simulator for QuMA is required to achieve the automation of the QuMA development flow.

#### 1.3. RESEARCH APPROACH

A simulator that describe the target system at a relatively low level (preferably at register-transfer level) can help the automation of the DSE, development, and verification of QuMA. During the research period of the thesis, we designed a simulator called QuMAsim to fulfill these requirements. We also built several applications based on QuMAsim to exploit its potential to help the design and verification of QuMA. Finally, we did some experiments to prove the capability of QuMAsim and demonstrate its use cases.

To achieve the goal of an automated development process, QuMAsim needs to be implemented as a cycle-accurate and hardware-based simulator. There are several challenges in implementing such a simulator:

- 1. We want this simulator contains all low-level constraints of quantum microarchitecture that are exposed in the discussion of [3], and we are targeting verification over the VHDL implementation. Ensuring that the simulator can demonstrate all of the functions of proposed QuMA is challenging.

- 2. Since we need to implement this simulator using a low-level description, its flexibility is bounded to be limited. In order to explore the design space, we hope that the simulator can be automated for different configurations. How to make this simulator as configurable as possible will be a problem.

- 3. The simulation environment would also be a problem. First, we want all user could do easy simulation regardless of their operating systems. Second, there should be a method to communicate QuMAsim simulation and HDL simulation, since one of our targets is to implement a verification platform.

QuMAsim is built with respect to these challenges. In this project, we take CC-Light as a starting point to build the first version of QuMAsim. QuMAsim also takes the eQASM program as input and outputs quantum operations with their respective timing information. We have tested multiple eQASM programs and compare its results to CC-Light to check its correctness. The first version is also supposed to control a 7-qubit quantum chip, just like CC-Light. QuMAsim can be used for design space exploration. Before implementing the VHDL description of a new QuMA, the simulator could easily test the new design and help us to compare different possibilities of the microarchitecture. Besides, QuMAsim is developed to be self-configurable for different quantum processors, such as a Surface Code 17 (SC17) quantum chip. Inversely, now QuMAsim can be used to verify the correctness of VHDL implementation by comparing the signals of interest from both simulations. In this work, an application called verification platform is built based on this purpose.

In addition, a quantum virtual machine is implemented on the basis of QuMAsim and other quantum software/emulators. OpenQL[6] is a high-level quantum programming framework which has an eQASM back-end and generates executable code for the CC-Light. So the user can write his quantum algorithm in the OpenQL high-level language then compile it to generate the eQASM code. There are also some qubit state simulator like QX [7] and QuantumSim [8] which can perform the quantum simulation. In this work, we connect the QuMAsim to QuantumSim so the generated operations could be executed on the error model

1.4. Organization 3

provided by QuantumSim. The measurement results could be sent back to QuMAsim to realize feedback control. In this way, the correctness of quantum programs can be checked at both architecture level and qubit state level.

#### 1.4. ORGANIZATION

This thesis is structured as follows:

Chapter 2 introduces the relevant background information for this thesis. It provides some basic knowledge of quantum computing and gives a broad view about a fully programmable quantum computer.

Chapter 3 discusses the implementation of QuMAsim. In this chapter, we introduce the basic structure of this simulator and the main function of each module. We also show how to make this simulator work in a full stack system view, including assembler and instruction set architecture.

In chapter 4, the applications that are built based on QuMAsim are introduced. We first discuss the modifications that we made for a self-configurable simulator. Then the working principles of the verification platform and quantum virtual machine are explained in detail.

Some experiments are performed on QuMAsim and the results are reported in Chapter 5.

Finally, we conclude and give recommendations for future work in Chapter 6.

## **BACKGROUND**

#### 2.1. QUANTUM COMPUTING BASICS

#### 2.1.1. **QUBITS**

Qubits are the fundamental elements of quantum computers just like classical bits in a physical system where classical bit has two exclusive states, 0 or 1 and can only be in one of them at a certain point in time. These two states are represented by  $|0\rangle$  and  $|1\rangle$ . Qubits can be in a linear combination of these two states which can be represented by

$$|\psi\rangle = \alpha |0\rangle + \beta |1\rangle, \tag{2.1}$$

where

$$\alpha, \beta \in \mathbb{C}$$

and  $|\alpha|^2 + |\beta|^2 = 1$ . (2.2)

Using the logical states as a basis, this superposition state can be represented by a complex-valued two-vector

$$|\psi\rangle = \begin{bmatrix} \alpha \\ \beta \end{bmatrix}. \tag{2.3}$$

The probabilistic nature of qubits presents themselves when being measured. The measurement probability of each state is the square of its amplitudes. Observing a qubit collapses its state t one of the possible measurement outcomes and destroys the information in the probability amplitudes. As a result,  $\alpha$  and  $\beta$  are not directly observable.

In classical computers, n bits can only be in one of the  $2^n$  possible states at a time. As a consequence, the entire system can only process this solo state read from the n bits at one time. The second feature of qubits extends the capabilities of classical bits and it is entanglement. Qubits can be entangled with each other which means that the state of the entire system cannot be described by the tensor product of each qubit state. An example of a non-entangled state is

$$|\psi\rangle = \frac{1}{\sqrt{2}}|00\rangle + \frac{1}{\sqrt{2}}|01\rangle = |0\rangle \otimes \frac{1}{\sqrt{2}}(|0\rangle + |1\rangle),\tag{2.4}$$

this state can still be written as the tensor product of two individual states and is therefore not entangled. The state

$$|\psi\rangle = \frac{1}{\sqrt{2}}(|00\rangle + |11\rangle),\tag{2.5}$$

is entangled since it can not be written as two individual states.

6 2. Background

#### 2.1.2. QUANTUM GATES

Quantum gates are used to manipulate the quantum state. These gates can be expressed as matrices and of which the effect can be modeled into matrix-vector multiplication. All quantum gates are arbitrary unitary matrices which means that quantum gates are always reversible. These operators can be simultaneously applied to the entire superposition which gives rise to quantum parallelism. On the other hand, superposition and entanglement provide an exponential state space as discussed before. Both facts will contribute to the speedup of quantum computers compared to classical computers.

Quantum gates could be divided into two types: single-qubit gates and multiple-qubit gates. A single-qubit gate can be represented as a  $2 \times 2$  unitary matrix and is a rotation on the Bloch sphere. A simple example of single qubit gate is Pauli-X gate which rotate the qubit by  $\pi$  along the x axis. A few other basic single qubit gates are the Pauli-Y, Pauli-Z and Hadamard gate. Especially the Hadamard gate is interesting since it maps a computational basis state to a superposition state.

Multiple-qubit gates are essential for creating entanglement and a well-known example is controlled-NOT (CNOT) gate. CNOT transfers the basis state  $|a\rangle\otimes|b\rangle$  to another basis state  $|a\rangle\otimes|b\oplus a\rangle$ . There are more two-qubit gates like Controlled-phase (CPhase) gate. Three-qubit gates also exist and one commonly-used example is the Toffoli gate, also known as the controlled-controlled NOT or CNOT gate. It is similar to CNOT gate but has two control qubits. Table 2.1 presents some of the useful quantum gates for this thesis.

Measurement of a state is inherently probabilistic depending on the amplitude of the vector in measurement basis. The quantum state collapses the wave-function to one of its classical eigenvalues. This is called projective measurement and is a significant difference from classical theories where measurement does not destroy the original state tested. Thus multiple measurements are required to reconstruct the probability distribution of the state. The exact complex amplitude cannot be measured, thus allowing a degree of freedom. This arbitrary phase factor can be ignored with no effect of the solution probability.

#### 2.1.3. Universal Quantum Computation

Like *NAND*, *NOR* gate sets in classical logic, there exists a universal set of gates on quantum logic that allows any arbitrary quantum gate to be decomposed with members of the set. An example of a universal set of quantum gates is *H*, *T*, *CNOT*. Any universal gate set should at least contain a multiple-qubit gate and a non-Clifford gate.

A universal quantum gate set could help realize universal quantum computation. Moving towards a broader view of constructing a useful quantum computer, several requirements need to be fulfilled given by DiVincenzo's criteria [9]:

- 1. A scalable physical system with well characterized qubits

- 2. The ability to initialize the state of the qubits to a simple fiducial state.

- 3. Long relevant decoherence times.

- 4. A universal set of quantum gates.

- 5. A qubit-specific measurement capability.

- 6. The ability to inter-convert stationary and flying qubits.

- 7. The ability to faithfully transmit flying qubits between specified locations.

#### 2.2. FULL STACK QUANTUM COMPUTER

Figure 2.1 provides a high-level view of the quantum system stack. This stack consisting multiple layers. The bottom layers are quantum chip together with quantum to classical interface. These two layers are technology dependent and many implementations focus on improving the fragility of qubits. Different technologies have been investigated like superconductors [10, 11], trapped ions [12] and nitrogen-vacancy centers [13]. Among these technologies, superconducting qubits give the biggest potential for scalability so the rest of paper only focus on this technology. Besides physical qubits, logical qubits also draw attention with performance improved by quantum error correction. But this is out of the scope of NISQ to be discussed, so we will only pay attention to the noisy qubits in this thesis.

The middle layers are the control microarchitecture and Quantum ISA. QISA provides a interface to communicate software and hardware just like in classical architectures. QISA usually includes both quantum

| Gate Name       | Gate Circuit   | Gate Unitary                                                                                                                                                                                                                                                                                             |

|-----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Identity        | <u> </u>       | $\begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}$                                                                                                                                                                                                                                                           |

| Hadamard        | <u>—</u> H     | $\frac{1}{\sqrt{2}} \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix}$                                                                                                                                                                                                                                       |

| Pauli-X         | X              | $\begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix}$                                                                                                                                                                                                                                                           |

| Pauli- <i>Y</i> | <u> </u>       | $\begin{bmatrix} 0 & -i \\ i & 0 \end{bmatrix}$                                                                                                                                                                                                                                                          |

| Pauli-Z         | <u></u>        | $\begin{bmatrix} 1 & 0 \\ 0 & -1 \end{bmatrix}$                                                                                                                                                                                                                                                          |

| Rotation-X      | $Rx(\theta)$   | $\begin{bmatrix} \cos\frac{\theta}{2} & -i\sin\frac{\theta}{2} \\ -i\sin\frac{\theta}{2} & \cos\frac{\theta}{2} \end{bmatrix}$                                                                                                                                                                           |

| Rotation-Y      | — <i>Ryθ</i> — | $\begin{bmatrix} \cos\frac{\theta}{2} & \sin\frac{\theta}{2} \\ \sin\frac{\theta}{2} & \cos\frac{\theta}{2} \end{bmatrix}$                                                                                                                                                                               |

| Rotation-Z      | [ <i>Rzθ</i> ] | $\begin{bmatrix} e^{-i\frac{\theta}{2}} & 0 \\ 0 & e^{i\frac{\theta}{2}} \end{bmatrix}$                                                                                                                                                                                                                  |

| Т               | <u> </u>       | $\begin{bmatrix} 1 & 0 \\ 0 & e^{i\frac{\pi}{4}} \end{bmatrix}$                                                                                                                                                                                                                                          |

| Phase           | <u></u>        | $\begin{bmatrix} 1 & 0 \\ 0 & i \end{bmatrix}$                                                                                                                                                                                                                                                           |

| CNOT            | <u> </u>       | $\begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{bmatrix}$                                                                                                                                                                                                         |

| CPhase          |                | $\begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & -1 \end{bmatrix}$                                                                                                                                                                                                        |

| Toffoli         |                | $\begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 & 0 \end{bmatrix}$ |

Table 2.1: Quantum circuit of some commonly-used quantum gates.

instructions and classical instructions since a quantum computer will always consist of both computing components [14]. These instructions are fed into a control microarchitecture and decoded into required control signals with precise timing. These control signals are processed by quantum to classical interface based on the specific quantum technology. These signals are translated into required pulses and sent to quantum chip.

The top layer represents quantum algorithms that are described by high-level quantum programming languages like Scaffold [15] and  $\text{LIQ}Ui|\rangle$  [16]. These algorithms lack the low-level hardware information and assumes that all operations can be executed perfectly. Compilers help to provide these information so the quantum algorithms can be executed by the potential quantum hardware. In compilation layer, these algorithms are compiled into a series of instructions that defined by QISA.

8 2. Background

Figure 2.1: Overview of quantum computer system stack

#### 2.3. HARDWARE

#### 2.3.1. SUPERCONDUCTING QUBITS

Nowadays, there are various potential quantum technologies being pursued to implement qubits, such as trapped ions [12, 17], quantum state in superconducting circuits [10, 11, 18], nuclear spins or electron spins in silicon [19–21], and nitrogen-vacancy centers [13, 22]. Other candidates like Majorana femion based topological qubits (not yet built) are actively being researched as well. The currently most promising technologies are trapped ions and superconducting qubits, both of which have demonstrated to satisfy the DiVincenzo criteria [10, 11, 17, 23].

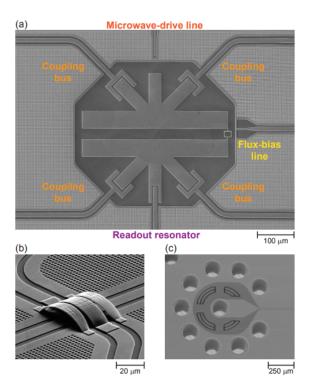

As stated before, this thesis focus on superconducting qubits. Superconducting integrated circuits are Josephson junction based harmonic oscillators coherently controllable and measurable by magnetic flux pulses and microwaves. The performance of superconducting qubits benefits from the non-linearity of Josephson junctions and surrounding microwave circuitry. These systems have potentially excellent scalability since this technology have not encountered any hard physical limits. Superconducting qubits are usually fabricated with well-established fabrication techniques such as photo and electron-beam lithography. However, superconducting qubits also suffer from drawbacks like low coherence times. This also makes quantum error correction very important for this type of system [24–28].

Transmon [29] is a promising technology which achieves error rates lower than the fault-tolerance threshold for surface code. A universal gate set which comprised of single-qubit gates (mainly x and y rotations) and the CZ gate is used at here. The transmon is a lumped-element nonlinear LC resonator. The first-excited state is used as the qubit  $|0\rangle$ . The transition frequency between these state can be tuned by controlling the flux through the loop between the two Josephson junctions.

Figure 2.2 shows a prototype seven-port transmon developed in Dicarlo lab, Delft University of Technology. The vertical I/O will be realized either using through-silicon through-silicon-vias or bump bonding in a flip-chip arrangement.

For transmon qubits, single-qubit gates are executed by applying calibrated microwave pulses (typically 20 ns) through microwave-drive lines. These pulses are commonly generated by single-modulation of a carrier using functions generated by an Arbitrary Waveform Generator (AWG). The phase of the carrier determine the axis of rotation operations and the amplitude decides the rotation angle. Some predefined calibrated microwaves are stored and employed for specific pulses (e.g.,  $\pi$  and  $\pi/2$ ). Arbitrary single-qubit gates can be decomposed into x- and y-axis rotations so all quantum operations could be applied by this methodology although it will cost longer operation sequences.

The most frequently used two-qubit gate is CZ gate. Such a gate can be performed between qubits coupled

2.3. Hardware 9

Figure 2.2: Images at various scales of implementation of surface-code fabric. (a) Starmon qubit. (b) Transmission-line crossover. (c) Vertical I/O.

to a common resonator or capacitor. It is realized by applying calibrated flux pulses (usually 40 ns) to the flux-bias line. If the frequency of these two qubits are calibrated suitably, they could be coupled together for the CZ gate.

Qubit measurement exploit qubit-state dependent fundamental frequency of a resonator which is coupled both to the qubit and to a feedline. Feedlines consist of readout resonators which are simultaneously interrogated using frequency-division multiplexing. A pulsed measurement usually lasts for 300 ns - 2  $\mu$ s and is transferred through the feedline to project the qubit state to  $|0\rangle$  or  $|1\rangle$ . Demodulation, integration, and discrimination of the transmitted signal is used to generate the measurement result.

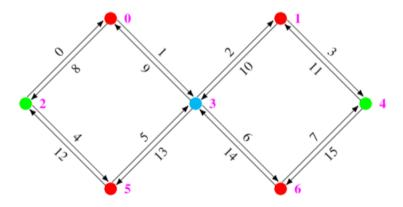

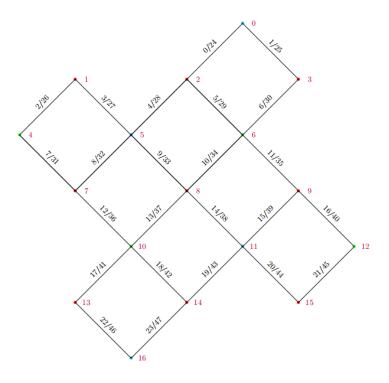

#### 2.3.2. QUANTUM CHIP TOPOLOGY

The surface code is a promising topological QEC code and attracts a lot of experimental research [30]. Although we do not consider about error corrections in NISQ era, the fabricated quantum chip is targeting to the future technology. A surface code using 7 qubits which is also known as Surface Code 7 (SC7) can form a logical qubit and is used for testing in this thesis. The example Figure 2.3 shows the topology of a quantum chip of SC7. As we can see from this layout, the SC7 processor uses four data qubits (in red) and three ancilla qubits (in green and blue). The ancilla qubits are used to check X/Z parity between interact to the data qubits.

The surface code has convenient two-dimensional layout with only nearest-neighbor qubit interactions. For example, qubit 2 and 3 can not be applied a two-qubit gate directly since they are not connected. This problem could be solved by using qubit 0 or 5 to swap the information. This is related to the mapping of quantum circuits and will not be further discussed in this thesis since it is not part of our work.

For control simplicity, we named each qubit in the processor and each direct edge that connects nearest qubit pairs. For example, edge number 0 represents the edge which connects qubit pair 2-0 while qubit 2 acts as left qubit (control qubit) and qubit 0 is right qubit (target qubit). There are 7 qubits and 16 edges for this SC7 chip and these information should be stored in the controller of this chip. These numbers will scale up as the number of qubits increases, and the method to solve this problem will be discussed later in section 4.

10 2. Background

Figure 2.3: Layout of a surface code using 7 qubits

#### 2.3.3. IMPLICATION ON THE CONTROL

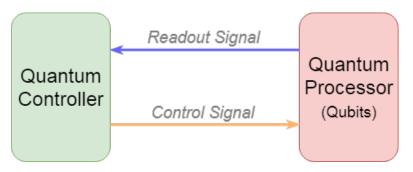

In quantum computing, the data is stored and processed in qubits. To perform quantum operations, analog pulses are generated by an external controller and then applied on qubits. In contrast to classical computing, the operations are transferring around while the data is stationary on computing bits. In classical processors, data is stored and processed in binary format and the digital system share the homogeneity among different subsystems. But data in quantum computing could be entangled in qubits so the data evolves in o format encoded in superposed states. Thus. the difference between quantum data and control signals leads to the separation of quantum controller and quantum processor. A quantum controller usually use AWGs to generate the required pulses for the targeting qubits. Figure 2.4 displays how the control unit communicates with quantum chip.

Figure 2.4: The relationship between control unit and quantum processor  $% \left( 1\right) =\left( 1\right) \left( 1\right) \left($

A more detailed implementation of quantum controller which targets to a SC17 chip consisting of transmon qubits that we have introduced before is shown in Figure 2.5 [31]. Each qubit has a dedicated flux line, a microwave-drive line and a readout resonator fore readout. These 17 dispersively-coupled resonators are grouped onto three different feedlines and two-qubit operations are applied through bus resonators by opting for coupling nearest-neighbor data and ancilla transmons. The microwave-drive lines and flux-bias lines are driven by AWGs and the feedlines are driven by UHFQC. The information about these control electronics will not be elaborated at here but we do notice that there are some limitations brought by them. How to handle these control electronic specifications will be discussed in later sections.

#### 2.3.4. QUANTUM MICROARCHITECTURE

In our discussion, quantum computer architectures comprise two parts: Quantum Instruction Set Architecture (QISA) and Quantum Microarchitecture (QuMA). These two layers bridge the gap between software and hardware in quantum computing. Currently, quantum processors are controlled by well-defined electrical signals like microwave pulses with precise timing. To generate these signals, some dedicated electronics devices are used to control the quantum chips. However, this control methodology suffers from high resource consumption, control complexity and low scalability. Therefore, it is necessary to design a microarchitecture to improve the performance of controller.

2.3. Hardware

Figure 2.5: Schematic of how to control a Surface-17 chip

The main challenges in designing such a control microarchitecture are listed below:

• Complex analog waveform control. The input signal of quantum processors are complex analog signals since quantum operations are performed by sending well-defined analog pulses. The measurement outcome of qubits also resides in the output analog signals which means the output signal of quantum processors are also analog signals. A commonly used method to produce the required pulses uses arbitrary waveform generators (AWGs). The well-defined analog pulses are calibrated and placed in the memory of these devices before executing quantum algorithms.

Measurement results are contained in an analog signal and a discriminator is required to perform integration and discrimination on this signal. The software-based discriminator sufferers from problems like long latency which makes real-time feedback control impossible. Thus, a scalable measurement discrimination method with short latency constitutes a challenge.

- Instruction definition. The quantum instruction set architecture (QISA) is the diving line between quantum hardware and quantum software. It is challenging to design an instruction set that considering the low-level constraints of the interface to the quantum processor, e.g., timing information. It is difficult for quantum compilers to generate technology-dependent instructions for the following reasons:

- 1. The constraints of quantum processor will affect the layout of qubits used in the algorithm, e.g., the nearest-neighbour constraint.

- 2. Quantum technology is rapidly evolving and new methods of implementing quantum gates are continuously being introduced. It is important to find a way to introduce these changes without affecting the rest of architecture.

- 3. It is difficult to support a set of technology independent quantum instructions and their current state of the art.

12 2. Background

A quantum microarchitecture, QuMA [3], for a superconducting quantum processor is presented to solve these problems. The input of QuMA is a binary file generated by a compiler where classical and quantum code are combined. The entire architecture uses a heterogeneous model and classical code is executed by the classical host CPU. The quantum code contains auxiliary classical instructions and quantum instructions, and is executed by the quantum co-processor. More detailed introduction about it will be displayed in Section 3.1.

#### 2.4. QUANTUM INSTRUCTION SET ARCHITECTURE

#### 2.4.1. QISA OVERVIEW

QISA is an essential component of a fully stack quantum computer since it is the dividing line between hardware and software. To achieve that, QISA target to be mathematically equivalent to the circuit model in an efficient way, with or without interacting with classical computing resources. Most proposed quantum assembly language like f-QASM [32]. However, they do not fully take into account the low-level constraints to interface with NISQ processors. For example, a generally neglected but crucial constraint in the NISQ era is the timing of operations, which may ruin the computation process when not effectively scheduled. Another example of a low-level constraint is that only a limited number of different operations can be applied on qubits at the same time with some control electronics. Besides, quantum-classical heterogeneous computing is required by some quantum algorithms, such as variational quantum eigensolver. But existing instruction sets do not either define an heterogeneous programming model or reveal enough information about the underlying programming model. Therefore, an executable QASM-based QISA, named eQASM, is proposed in [33]. We will use this instruction set in the rest of this thesis.

#### 2.4.2. EQASM

The design of eQASM is guide by several main principles. eQASM should contain well-defined methods to specify the timing of quantum operations. It should be simple to allow a straightforward implementation by the microarchitecture. The quantum operation issue rate is a potential bottleneck of the quantum microarchitecture and should be addressed, e.g. by densely encoding the instructions such as done with SIMD and VLIW for classical architectures. In addition, low-level hardware information should be included in a configuration file and exposed in eQASM to enable platform-specific optimization.

Based on the the principles described above, the characteristics of eQASM are listed below:

- Efficient timing specification:eQASM defines a more efficient method to explicitly specify the timing of quantum operations at the instruction level.

- SOMQ execution: Addressing the quantum operation issue rate problem, eQASM introduces Single-Operation-Multiple-Qubit (SOMQ) execution, which can considerably increase quantum code density.

- VLIW architecture: eQASM adopts a Very-Long-Instruction-Word (VLIW) architecture to further increase the quantum operation issue rate; a single quantum instruction can contain multiple quantum operations.

- Runtime feedback: eQASM defines two kinds of feedback: fast conditional execution for simple but fast feedback, and comprehensive feedback control for arbitrary user-definable feedback.

- User-configurable quantum operations. eQASM postpones the specification of available quantum operations in the instruction set from QISA design time to compile time. The operations can be configured by the programmer.

- Supporting quantum experiments. Tailored for the NISQ technology, eQASM can be used to efficiently

describe quantum algorithms as well as quantum experiments to calibrate qubits and quantum operations.

Table 2.2 gives an overview of eQASM instructions.

The functions of these instructions are introduced as following:

• Control instructions. Compare and branch instructions will consist of control logic of eQASM. CMP is used to compare the values of two registers. The result is stored in the branch register which is represent as *B*. The status of condition is represented by three flag bits, and the computation of these three flag bits are listed below:

| Туре           | Syntax                                                                    | Description                                                                                 |

|----------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Control        | CMP Rs, Rt                                                                | Compare GPR Rs and Rt and store the result into the comparison flags.                       |

|                | BR <comp. flag="">, Offset</comp.>                                        | Jump to PC + Offset if the specified comparison flag is '1'.                                |

|                | FBR <comp. flag="">, Rd</comp.>                                           | Fetch the specified comparison flag into GPR Rd.                                            |

| Data Transfer  | LDI Rd, Imm                                                               | Rd = sign_ext(Imm[190], 32).                                                                |

|                | LDUI Rd, Imm, Rs                                                          | Rd = Imm[140]::Rs[160].                                                                     |

|                | LD Rd, Rt(Imm)                                                            | Load data from memory address Rt + Imm into GPR Rd.                                         |

|                | ST Rs, Rt(Imm)                                                            | Store the value of GPR Rs in memory address Rt + Imm.                                       |

|                | FMR Rd, Qi                                                                | Fetch the result of the last measurement instruction on qubit i into GPR Rd.                |

| Logical        | AND/OR/XOR Rd, Rs, Rt<br>NOT Rd, Rt                                       | Logical and, or, exclusive or, not.                                                         |

| Arithmetic     | ADD/SUB Rd, Rs, Rt                                                        | Addition and subtraction.                                                                   |

| Waiting        | QWAIT Imm                                                                 | Specify a timing point by waiting for the number of cycles indicated by the immediate value |

|                | QWAITR Rs                                                                 | Imm or the value of GPR Rs.                                                                 |

| Target Specify | SMIS Sd, <qubit list=""> SMIT Td, <qubit list="" pair=""></qubit></qubit> | Update the single- (two-)qubit operation target register Sd (Td).                           |

| O. Bundle      | *[a0 0  ] a0 0 [.I9]                                                      | Applying operations on qubits after waiting for a small number of cycles indicated by PI.   |

Table 2.2: Overview of eQASM Instructions. The operator:: concatenates the two bit strings.

```

X = unsigned(Rs) >= unsigned(Rt)

Y = unsigned(Rs) > unsigned(Rt)

Z = sign(Rs) ^ sign(Rt)

```

We can obtain the condition by implementing logic operation on the flag bits. For example, the values in two registers are equal when

```

X * Y = 1

```

Branch is used to determine whether the classical controller should execute instructions in sequence or jump to a specific point. The program counter will load the address of a specific instruction if the condition matches branch register. Otherwise it will increment itself to load the next instruction. A mathematical description is given below:

```

PC = branch register matches condition ? specific address: PC + 1

```

- Data transfer instructions. These instructions are used for common-purpose load operation. LDI is used for signed numbers and LDUI for the unsigned. For the signed operation, the immediate number will be loaded to the target register. Notice that the value of register needs to be sign-extended to ensure the correct result. For the unsigned operation, the immediate number is loaded into the upper bits of target register while its lower bits is determined by the resource register. Fetch branch register (FBR) is used for load operation with specific purpose. The FBR instruction will set the target register to 1 or 0 based on the branch condition. Fetch measurement result (FMR) is more complex and is used to fetch the result of the last measurement operation. This instruction helps realize comprehensive feedback control logic which is introduced in section 3.1.4.

- Logical and arithmetic instructions. These instructions are simple and straightforward: they are used for logical and arithmetical operations. All these instructions have two operands which are stored in Rs and Rt, and the result will be put into destination register (Rd).

- Quantum waiting instructions. These two instructions are used to specify the interval between previous timing point and the following timing point. The supported waiting time range is from 0 to  $2^{20}-1$ . In the QWait instruction, you can use the 20-bit immediate value to specify the waiting time. In the QWaitR instruction, you can specify the general purpose register Rs, of which the low 20 bits are used as the waiting time. Zero waiting time is also supported in the hardware, of which the effect is nothing.

- Target specify instructions. In QuMA, the target of a quantum gate is specified by a mask. A mask is firstly stored in a register and then readout by the quantum operation instruction. There are two

14 2. Background

register files used to store the masks for single-qubit gates and two-qubit gates, which are labeled with "S" and "T", separately. The instruction SMIS and SMIT are used to set the mask for single-qubit gates and two-qubit gates, respectively.

• Quantum bundle instructions. Bundle is used for specifying quantum instructions which contain quantum operations. In current QuMA, each bundle contains two VLIW instructions and can be processed by VLIW pipelanes in quantum pipeline. The definition of quantum operations is flexible since we want this instruction set as technology independent as possible.

#### 2.5. COMPILER AND LANGUAGE

Quantum algorithms should be described by specific languages and compiled by quantum compiler. To enable quantum programmers to express complex algorithmic constructs, a high-level programming language is needed. A number of programming languages exist, such as Scaffold [15], Quipper [34] and  $\text{LIQ}Ui|\rangle$  [16]. All these programming languages mostly target large-scale quantum computation, with little consideration in low-level constraints required by nowadays and near-term quantum devices. Microsoft Quantum Development Kit is using the recently proposed Q# [35], a quantum-focused domain-specific programming language, which highlights a heterogeneous quantum computing model which can safely interleave classical and quantum computations. These high-level quantum programming languages with compiler support have been proposed to efficiently describe quantum applications.

The compiler bridges the semantic gap between the quantum algorithm and the quantum hardware. The high-level quantum algorithms are translated into quantum operations and produce executable machine code for the target quantum platform. Quantum compilers usually provide several functionality such as synthesis of quantum circuits. Quantum circuit are reversible and has to be optimally decomposed in a series of quantum gates which belonging to a universal gate set. Compilers also need to consider quantum error correction. Logical qubits are encoded into several physical qubits and QASM instruction for performing operations on such encoded qubits are generated. Additionally, the compiler also maps the quantum circuit to the topology of the real quantum processor. In high-level algorithms, the circuit description does not usually consider physical limitations such as nearest-neighbour constraint. It is therefore important to optimize the mapping process. The QASM based quantum instructions are then translated into eQASM which also include the timing and physical qubit identifiers. These instructions are sent to the microarchitecture for execution on the quantum processor.

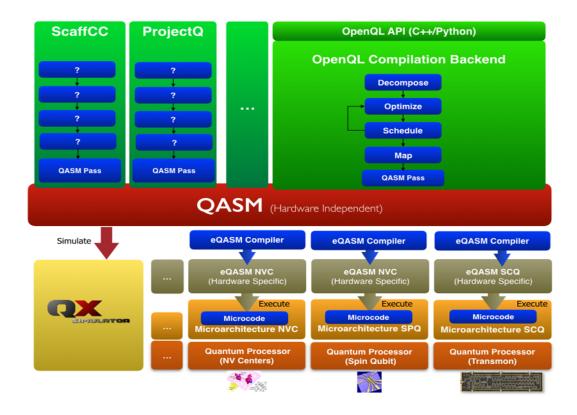

In this project, we use the OpenQL framework as the compiler to convert the quantum algorithms to microarchitecture executable QASM programs. The OpenQL framework is under development at QuTech, which allows hybrid quantum-classical coding in high-level programming languages like Python or C++. A more detailed description of OpenQL can be found in section 4.2.2.

## **SIMULATOR IMPLEMENTATION**

In the previous chapter, we saw that a controller microarchitecture is required to solve the control challenges in full stack quantum computer. In this chapter, we first discuss the structure of an instance of QuMA which is named CC-Light, then we present the QuMA simulator, QuMAsim. The first version of QuMAsim is based on CC-Light, then further improvements are made.

#### 3.1. QUMA STRUCTURE

#### **3.1.1. OVERVIEW**

As stated in Section 2.3, there are many control difficulties need to be solved for quantum computer. The first version of QuMA is proposed in [3] and the diagram is showed in Figure 3.1. QuMA is a heterogeneous architecture which includes a classical CPU as a host and a quantum co-processor as an accelerator. QuMA accepts a binary file generated by the OpenQL compiler infrastructure [6]. These instructions are processed and generate micro operations at a deterministic timing. The analog-digital interface converts digital signals into corresponding analog pulses which will perform quantum operations on qubits.

Figure 3.1: Overview of the structure of QuMA\_v1

The main mechanisms used in this architecture are:

Codeword-based event control. The analog-digital interface divides the QuMA into digital signals and analog signals. From left to right, the codeword-based triggers are translated into pulses representing quantum operations on the qubits. From right to left, readout waveform is digitized and processed to discriminate the measurement outcomes as binary results by the measurement discrimination unit. Therefore, this mechanism allows controlling analog pulse generator using instructions. Fast and flexible feedback control is enabled since the waveform are not required to be uploaded during runtime.

2. Queue-based event timing control. The timing control unit implements queue-based event timing control in QuMA. It divides QuMA into two parts: on the left side is the non-deterministic timing domain and on the right side is the deterministic timing domain. In the non-deterministic timing domain, all control operations are executed in an as-fast-as-possible style. In the deterministic timing domain, quantum operations are stored in the queues and are emitted with specific time stamp. So the output of the timing control unit have very precise timing information.

The timing control unit consists of a timing queue and multiple event queues. The time stamps are stored in timing queue and a clock is used to control the read request of this queue. The counter value is the intervals between two consecutive timing points and a time stamp is read out when the counter countdown to zero. At that time, this time point is broadcast to all event queues and every buffered events with corresponding time stamp is emitted to the analog-digital interface.

3. Multilevel instruction decoding. QuMA also focus on flexibility of instruction decoding. In quantum pipeline, the initial binary instructions are decoded into codeword-based events before the timing control unit. By enabling multilevel instruction decoding, the quantum instruction can fill the queues as fast as possible without worrying about complex analog waveform control with rigid timing constraints. This scheme is implemented through multiple modules and will be introduced in later stage.

These mechanisms help to realize the quantum operation execution. Besides it, there is also a quantum control unit in this QuMA which is dedicated to the classical control of the entire quantum program. This unit consists of classical pipeline, measurement register file and instruction cache. All binary instructions are stored in the instruction cache before execution and then are fetched by classical pipeline. The classical instructions are processed inside the classical pipeline and the quantum instructions are sent into quantum pipeline. The measurement results are stored in the measurement register file which is used to achieve comprehensive feedback control. The detailed functions of quantum pipeline and the classical control unit will be explained in the following sections.

To control a larger number of qubits, multiple new techniques are used in the second version of QuMA which is showed in Figure 3.2. Very-Long-Instruction-Word (VLIW) architecture and Single-Operation-Multi-Qubit (SOMQ) execution are used to address the quantum operation issue problem. Besides, the comprehensive feedback control logic is implemented so we use the measurement results to do some conditional operation. We will discuss the details of this architecture in the following sections.

Figure 3.2: Overview of the structure of QuMA\_v2, it is more complex compared to QuMA\_v1 since it needs to control more qubits

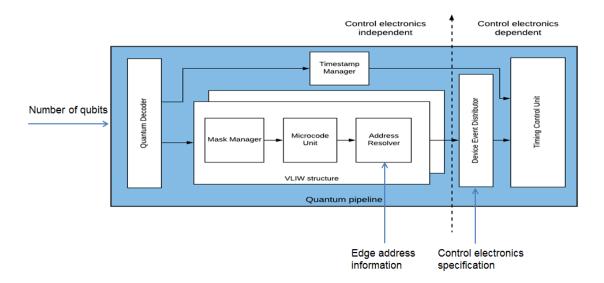

#### 3.1.2. QUANTUM PIPELINE

The quantum pipeline consists of multiple modules that help to realize the above schemes. Generally, the quantum instructions are processed in this pipeline and generate quantum operations with precise timing information for the analog-digital interface. It also registers the measurement results sent back from analog-digital interface and report them back to classical pipeline. In the following paragraphs we discuss the main function of each module inside quantum pipeline:

- Quantum Instruction Decoder: this module decodes the binary instructions. There are two kinds of quantum instructions: mask instructions, operation instructions and wait instructions. Mask instructions are used to define the mask registers which consist of single-qubit mask and two-qubit mask. Operation instructions contain the quantum operations and their targeting qubits. The targeting qubits information is stored in corresponding mask registers and will be read out in the following stage. Every operation instruction contains timing information as well as wait instructions. As long as an interval time is defined in these instruction, a valid signal will be set for the following module to generate a time stamp. For operation instructions, the opcode is also decoded from it binary and will be used as index of control store which will be explained later.

- Mask Register File: for mask instructions, the mask register will write the value decoded from binary

instruction. For operation instructions, the value of targeting register will be read out. There are two

kinds of register in this module, single-qubit register and two-qubit register. For single-qubit register,

the mask value is encoded as the qubit number while the edge number information is encoded in twoqubit register.

- Timestamp Manager: as mentioned in quantum instruction decoder, a time stamp is generated for every instruction as long as a timing difference is defined. Notice that this manager is outside the VLIW pipelane since the VLIW instructions from one single operation instruction share the same time stamp. Besides the time stamp for operations, there are also some timing points are generated. These timing points are directly sent to the timing queue in the timing control unit while the time stamps are grouped with corresponding quantum micro-operations in operation combiner.

- Microcode Unit: this microcode method is introduced in [36] and it enables flexible complex instruction definition using the same hardware implementation. In microcode unit, the quantum instructions are translated into a sequence of microinstructions based on the microprograms uploaded into the Q control store. The micro operations are codeword-based as stated before so the content of the control store is based on the opcode and left/right codewords.

- There is an address decoder submodule which works in parallel with control store. The mask value is fed into this decoder to generate the operation selection signal. This signal is used to select the left/right operation of the two-qubit pair and is sent to quantum microinstruction buffer together with the left and right microinstructions.

- Quantum Microinstruction Buffer. In this module, quantum microinstructions for quantum gates are

decomposed into separate micro-operations. The input microinstructions are multiplexed based on

the selection signal. Together with microcode unit, the multilevel instruction decoding scheme is realized through a opcode microinstruction micro-operation path.

- Operation Combination. After VLIW pipelane, the micro-operations from different VLIW instructions should be combined. In this module, a conflict check is applied at first to see if any operation violation on qubits. These operations are aligned together after passing this conflict check. Notice that the pre-interval of zero is supported at here, which means the operations will pend on this module until the next instruction arrived. And these two consecutive instruction will align again if the pre-interval of the second instruction is zero. This module is also the place that the time stamps are grouped together with micro-operations.

- Device Event Distributor. The output of the previous module are the quantum operations for each qubit. But in real control these operations should be grouped into different events for different control electronics as mentioned in Section 2.2.4. All quantum operations are divided into three types at here: microwave, flux and measurement. All input operations are translated into different events based on the information of control electronics like AWG and UHFQC. Then these events are pushed to the

event queues in the timing control unit. Device event distributor divides the entire QuMA into control electronics independent domain and control electronics dependent domain.

• Timing control unit. Timing control unit is used to realize the queue-based event timing control. The function of this module is described above.

#### 3.1.3. CLASSICAL PIPELINE

The above section introduced the function of quantum pipeline and explained how quantum instruction is executed. Now we will discuss about the classical control a little bit. The structure of the quantum control unit is shown in Figure 3.3. The functions of these units are listed below.

Figure 3.3: Quantum control unit structure

- Instruction Cache: in current CC-Light design, the instruction cache is not really a cache yet. It is just a memory where all binary instructions generated from the quantum program are stored. But in future design where a heterogeneous architecture will be implemented, this memory is supposed to be implemented as a cache between the classical pipeline and host CPU. There is a Program Counter (PC) which indicates the position of current instruction. The PC increments itself during usual time unless a branch takes place. When the branching signal from classical pipeline is set, the PC value changes to the targeting address and the corresponding signal is read out. When branching finished, there is also a branch done signal to indicate the classical pipeline recover from the stall and continue to process.

- Classical Pipeline: classical pipeline is implemented as a four-stage pipeline where the stages are: instruction fetch, decode, execute and write back. The main function of instruction fetch stage is to control the branch signal. The pipeline stop running when the previous instruction was a taken branch and start running when the instruction cache reports that a branch command was serviced. The branch target address will also be calculated and sent to instruction cache at here.

In the decoding stage, the binary instruction is decoded. We know that eQASM supports some auxiliary classical instructions like compare and logical operations and these instructions are used for classical control. If the instruction is a quantum instruction, it will be forwarded to quantum pipeline directly. The stalling logic also locates in decode stage. There are three stalling situations: stall when quantum measurement registers are not ready for more measurement instructions pending in the queue, stall when the quantum pipeline is not ready for more instructions, stall when we are executing an FMR instruction and the ready signal is low. The first situations are easy to understand and the last one is due to the feedback control logic and will be explained later.

After the decoding stage, the source (S) and target (T) operands and operation type are generated for the execution stage. The basic operations (AND, OR, ADD, etc) and compare operations (CMP, TEST)

are executed in this stage. Then the results are sent to write back stage if the result needs to be write to a classical register. Thus, the execution of classical pipeline is finished.

- Measurement Register File: this file contains the registers which are used to store the measurement results which are sent back from analog-digital interface. These values can be fetched by FMR instruction and used for conditional execution. The detailed logic is much more complex and is explained in the following section.

- Slice: the slice is a configurable register slice that can be placed between sub modules to improve FPGA timing. Any number of these units can be inserted. There are two kinds of register slice that can be inserted: ready slice and data slice.

#### 3.1.4. COMPREHENSIVE FEEDBACK CONTROL

Figure 3.4 shows the logic of comprehensive feedback control in QuMA\_v2. This logic starts from classical pipeline when a measurement instruction is processed. The measurement instruction is sent into quantum pipeline and finally generates a measure trigger for the measurement device. Inside the quantum pipeline, a measurement issue signal "Measissue" and a measured qubits signal "MeasuredQubits" are generated. These signals indicate that there are some measurement operations applied on certain qubits during the execution and are sent to the measurement register file.

When the measurement triggers the measurement device, it would generate corresponding analog waveform to apply measurement operations on quantum processor, which usually take 300ns to  $2\mu s$ . The measurement device collects the results and return them to QuMA. The results are sent into the measurement analysis module where the measurement result and valid signals for each qubit are sorted. Then these two signals will be sent into measurement register file and can be fetched by classical pipeline.

Figure 3.4: Comprehensive feedback control logic

In eQASM, a fetch measurement result (FMR) instruction is used to fetch the measurement result from measurement register file to a general purpose register file. Then this result can be used for conditional operation like compare and branch. The measurement instruction does not stall the microarchitecture but this instruction will.

The measurement result of a measurement instruction can only be returned after a period of time since it is issued from the classical pipeline to the quantum pipeline. This latency can range from hundreds of nanosecond to several microseconds due to three factors:

- Quantum pipeline requires several processing stages to translate the measurement instruction into corresponding measurement events. It requires around 7 cycles.

- Measurement events are buffered in an event queue in the timing control unit before its execution. It can introduce an indefinite latency depending on previous quantum instructions, which latency can range from tens of nanosecond to several microseconds.

- After the measurement events are fired from the timing control unit and sent to the measurement device, e.g., UHFQC, it takes a period of time for the measurement device and the qubits to accomplish the entire measurement process. It can introduce a latency from 400 ns to 3 us.

The existence of this latency means that, the FMR instruction cannot directly get the measurement result of the last measurement instruction for the target qubit in many cases. So, the microarchitecture must handle the latency introduced by the measurement process, by stalling the execution of FMR instruction when required.