### Scaling Aspects of Silicon Spin Qubits

Boter, Jelmer

10.4233/uuid:dad7f8c1-c798-44a4-a987-e40eec5195d3

**Publication date**

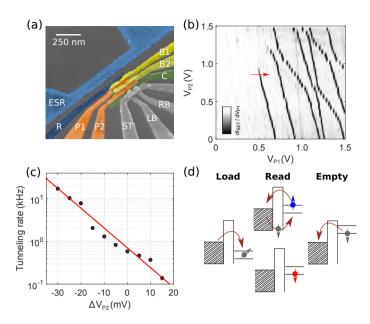

**Document Version** Final published version

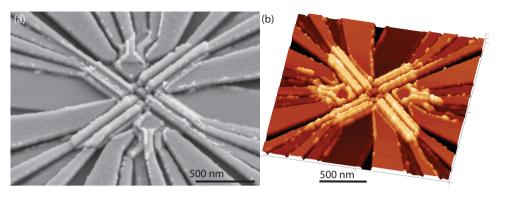

Citation (APA)

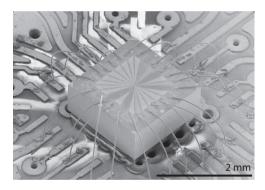

Boter, J. (2020). Scaling Aspects of Silicon Spin Qubits. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:dad7f8c1-c798-44a4-a987-e40eec5195d3

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# SCALING ASPECTS OF SILICON SPIN QUBITS

# SCALING ASPECTS OF SILICON SPIN QUBITS

### **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. dr. ir. T. H. J. J. van der Hagen, voorzitter van het College voor Promoties, in het openbaar te verdedigen op donderdag 23 januari 2020 om 15.00 uur

door

# Jelmer Matthijs BOTER

Master of Science in Applied Physics, Universiteit Twente, Enschede, Nederland,

geboren te Hengelo (O), Nederland.

Dit proefschrift is goedgekeurd door de promotor.

Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof. dr. ir. L. M. K. Vandersypen, Technische Universiteit Delft, promotor

Onafhankelijke leden:

Dr. C. G. Almudever, Technische Universiteit Delft Prof. dr. S. D. C. Wehner, Technische Universiteit Delft Prof. dr. L. DiCarlo, Technische Universiteit Delft

Prof. dr. ir. F. A. Zwanenburg, Universiteit Twente

Overige leden:

Dr. J. S. Clarke, Intel Corporation

Dr. ir. M. Veldhorst, Technische Universiteit Delft

Keywords: quantum computation, quantum dots, spin qubits, silicon

Printed by: Gildeprint, Enschede - www.gildeprint.nl

Cover design by: Thomas van Tilburg

Copyright © 2019 by Jelmer Matthijs Boter

Casimir PhD Series, Delft-Leiden 2019-44

ISBN 978-90-8593-426-4

An electronic version of this dissertation is available at https://repository.tudelft.nl/ and via https://www.jelmerboter.nl/proefschrift.

*I Have a Dream*Martin Luther King Jr.

# **CONTENTS**

| Su | ummary                              | ix                                                             |

|----|-------------------------------------|----------------------------------------------------------------|

| Sa | amenvatting                         | хi                                                             |

| 1  | Introduction  1.1 Quantum mechanics | 1<br>2<br>2<br>4<br>5<br>7                                     |

| 2  | Theory  2.1 Quantum computation     | 9<br>10<br>10<br>11<br>12<br>12<br>13<br>20<br>25              |

| 3  | References                          | 31<br>32<br>32<br>32<br>33<br>33<br>35<br>40<br>42<br>42<br>43 |

| 4  | References                          | 49                                                             |

viii Contents

|                      | 4.6<br>4.7<br>Refe                                   | Summary and conclusion                                                  | 53<br>53<br>57                                           |  |  |  |  |  |

|----------------------|------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|

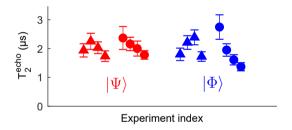

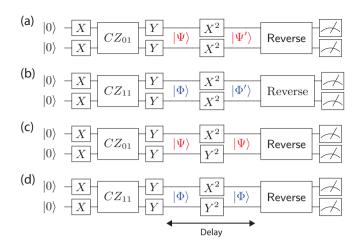

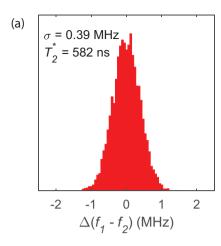

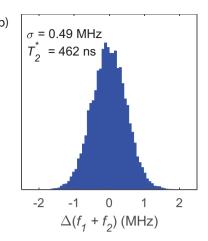

| 5                    | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8 | tial Noise Correlations in a Si/SiGe Two-Qubit Device Introduction      | 61<br>62<br>63<br>64<br>65<br>67<br>67<br>68<br>69<br>77 |  |  |  |  |  |

| 6                    | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8 | Darse Spin Qubit Array with Integrated Control Electronics Introduction | 81<br>82<br>83<br>84<br>85<br>85<br>87<br>87<br>88       |  |  |  |  |  |

| 7                    | 7.1<br>7.2                                           | Conclusion and Outlook Conclusion                                       | 91<br>93<br>93<br>94<br>96                               |  |  |  |  |  |

| A                    | Inte                                                 | egration scheme                                                         | 101                                                      |  |  |  |  |  |

| Ac                   | knov                                                 | wledgements                                                             | 109                                                      |  |  |  |  |  |

| Curriculum Vitæ      |                                                      |                                                                         |                                                          |  |  |  |  |  |

| List of Publications |                                                      |                                                                         |                                                          |  |  |  |  |  |

# **SUMMARY**

To harness the potential of quantum mechanics for quantum computation applications, one of the main challenges is to scale up the number of qubits. The work presented in this dissertation is concerned with several aspects that are relevant in the quest of scaling up quantum computing systems based on spin qubits in silicon. Few-qubit experiments are maturing quickly, but simultaneously the lacuna between them and large-scale quantum computers is filled with a combination of science and engineering challenges. The challenges that are addressed in this dissertation are reliable and reproducible sample fabrication, qubit resilience to temperature, spatial correlations in the noise affecting the qubits, and co-integration of qubits with classical control electronics.

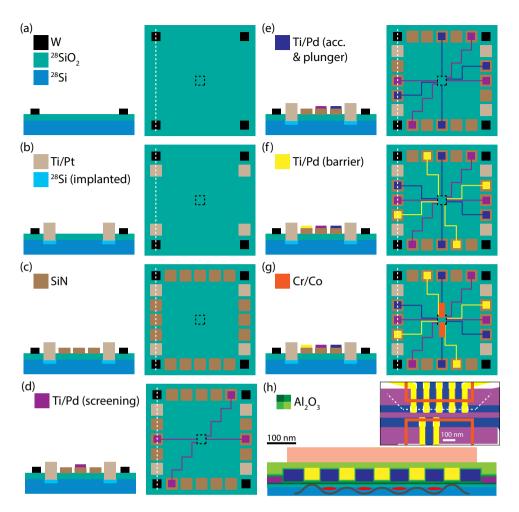

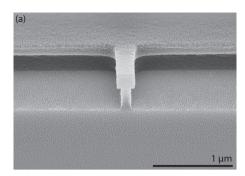

I start with describing the development of an integration scheme for silicon spin qubits in an academic cleanroom environment, as several research groups have demonstrated over the last years. This has allowed them to successfully fabricate and operate silicon spin qubit devices. The development of such a scheme is crucial for the fabrication of proof-of-principle devices, and the testing of several design variations for more and more complex qubit devices, before transferring the optimal designs to industrial foundries that are generally less flexible. Moreover, it is essential for performing paramount few-qubit experiments in the near term. The developed scheme has been successfully implemented in the next chapter of this thesis.

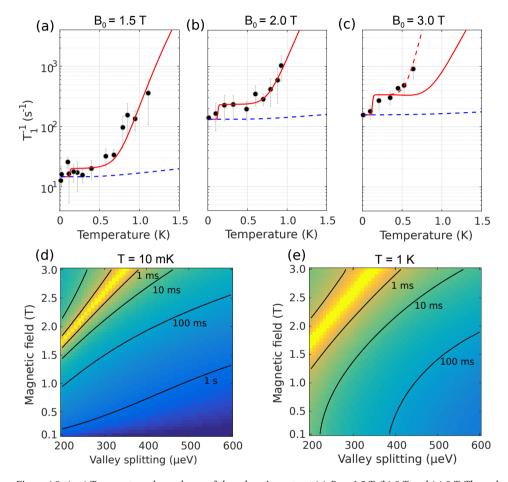

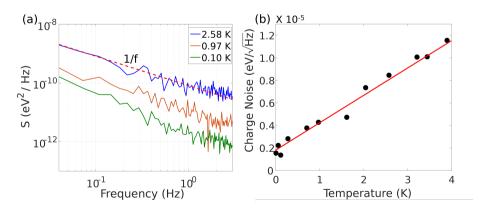

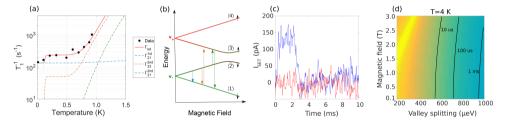

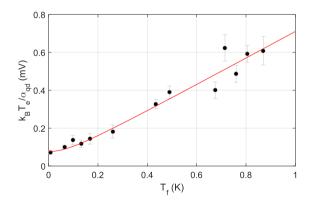

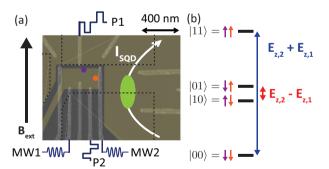

In the first experiment, we investigate the effect of temperature on the spin lifetime, as a first step towards higher temperature operation of silicon spin qubits. Spin qubit operation at elevated temperatures will be required to allow for co-integration of qubits with classical control electronics on a single chip, since the heat load associated with this electronics will be too much to deal with at the current qubit operation temperature of ~10 mK. At a temperature of ~1-4 K, significantly more cooling power is available (see for example CERN's Large Hadron Collider). Such co-integration would alleviate the interconnect bottleneck and facilitate the implementation of local control in large-scale devices. We find only a modest temperature dependence and measure a spin relaxation time of 2.8 ms at 1.1 K (still much longer than the record spin dephasing time measured in such a system). In addition, we present a theoretical model and use it in combination with our experimentally obtained parameters to demonstrate that the spin relaxation time can be enhanced by low magnetic field operation and by employing high-valleysplitting devices. Together with more recent work, this experiment demonstrates no fundamental limitations to prevent high-temperature operation of silicon spin qubits. Simultaneously, bringing classical control electronics to lower temperatures also is an active research area.

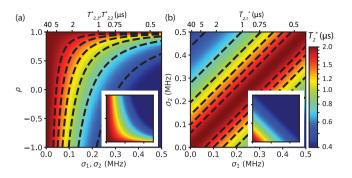

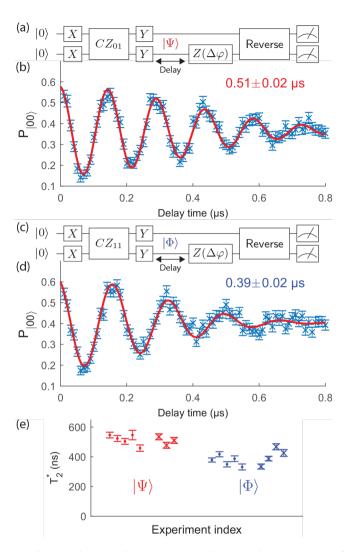

The second experiment uses maximally entangled Bell states of two qubits to study spatial correlations in the noise acting on those two qubits. Spatial correlations in qubit errors hinder quantum error corrections schemes that will be required for fault-tolerant large-scale quantum computers, as these schemes are commonly derived under the as-

x Summary

sumption of negligible correlations in qubit errors. Therefore, it is important to know to what extent the noise causing these errors is correlated. We find only modest spatial correlations in the noise and gain insight in their origin. The data is in accordance with decoherence being dominated by a combination of nuclear spins and multiple distant charge fluctuators coupling asymmetrically to the two qubits. We recommend to perform similar experiments in isotopically purified silicon to eliminate the effect of nuclear spins and in isolation study spatial correlations in charge noise. Furthermore, our insights show how correlations can be either maximized or minimized through qubit device design. For these reasons, the prospects for the development and implementation of quantum error correction schemes in fault-tolerant large-scale quantum computers are promising.

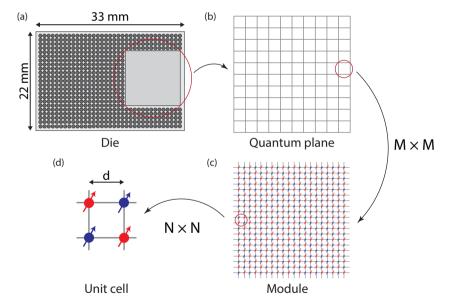

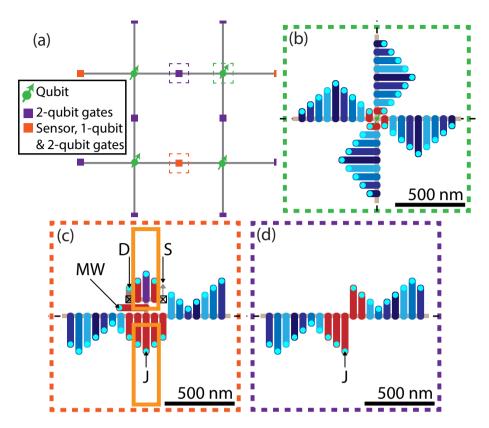

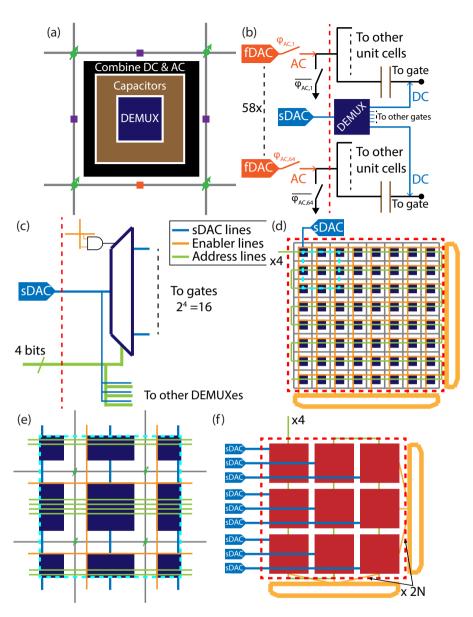

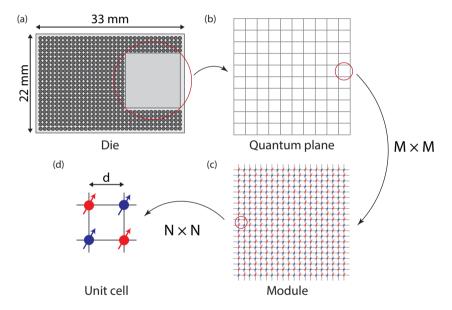

Finally, after having studied several aspects that are relevant to determine the suitability of silicon spin qubits for large-scale quantum computation in the preceding experiments, we propose a concrete physical implementation of co-integrated spin qubits with classical control electronics in a sparse spin qubit array. While the community usually claims compatibility of silicon spin qubits with conventional CMOS fabrication, existing proposals make assumptions that remain to be validated. Implementing quantum error correction protocols in a sparse array has been studied, but the description of a physical implementation was largely missing. The sparseness of the array allows for integration of local control electronics, as shown to be promising earlier in this thesis. Specifically, we propose to implement sample-and-hold circuits alongside the qubit circuitry that would allow to offset inhomogeneity in the qubit array. This enables individual local control and shared global control, resulting in an efficient line scaling. The scalable unit cell design fits  $2^{20}~(\approx 10^6)$  qubits in  $\sim 150~\text{mm}^2$ . We assess the feasibility of the proposed scheme, as well as its physical implementation and the associated footprint, line scaling and interconnect density.

Jelmer Boter

# SAMENVATTING

Eén van de voornaamste uitdagingen bij het benutten van het potentieel van quantummechanica voor quantumcomputertoepassingen is het vergroten van het aantal qubits. Het werk in dit proefschrift richt zich op verschillende aspecten die relevant zijn voor de zoektocht naar het opschalen van quantumcomputers gebaseerd op spinqubits in silicium. Experimenten met enkele qubits worden snel complexer, maar tegelijkertijd bevindt zich een combinatie van wetenschappelijke en technische uitdagingen in de leemte tussen deze experimenten en quantumcomputers op grote schaal. De uitdagingen die in dit proefschrift behandeld worden, zijn betrouwbare en reproduceerbare qubitfabricage, temperatuurbestendigheid van qubits, plaatsafhankelijke correlaties in de ruis die qubits beïnvloedt, en het samenbrengen van qubits met aansturingselektronica.

Ik begin met het beschrijven van de ontwikkeling van een fabricagemethode voor spinqubits in silicium in een academische cleanroomomgeving, zoals meerdere onderzoeksgroepen in de afgelopen jaren hebben laten zien. Dit heeft hen in staat gesteld om succesvol siliciumspinqubits te vervaardigen en aan te sturen. Het ontwikkelen van een dergelijke methode is cruciaal voor het vervaardigen en aansturen van *devices* waarmee de basisprincipes getest kunnen worden, en voor het testen van verschillende ontwerpvarianten voor complexere *devices*, voordat de optimale ontwerpen worden overgebracht naar de doorgaans minder flexibele industriële fabricagefaciliteiten. Tevens is dit noodzakelijk voor het uitvoeren van essentiële enkele-qubitexperimenten op de kortere termijn. De ontwikkelde fabricagemethode is succesvol toegepast in het volgende hoofdstuk van dit proefschrift.

In het eerste experiment bestuderen we het effect van temperatuur op de spinlevensduur, als een eerste stap in de richting van het opereren van spinqubits in silicium bij hogere temperaturen. Hogeretemperatuuroperatie van spinqubits zal noodzakelijk zijn om het samenbrengen van qubits met klassieke aansturingselektronica mogelijk te maken, aangezien de dissipatie veroorzaakt door deze elektronica te groot is om mee om te gaan op de huidige qubitoperatietemperatuur van zo'n ~10 mK. Bij een temperatuur van ~1-4 K is significant meer koelvermogen beschikbaar (zie bijvoorbeeld de Large Hadron Collinder van CERN). Dergelijke integratie zou de interconnect bottleneck verlichten en zou het implementeren van lokale controle in devices met vele qubits faciliteren. We vinden een beperkte temperatuurafhankelijkheid en meten een spinrelaxatietijd van 2.8 ms bij 1.1 K (nog steeds veel langer dan het record voor de spinfasecoherentietijd gemeten in dergelijke systemen). Tevens presenteren we een theoretisch model en gebruiken dit in combinatie met onze experimenteel verkregen parameters om te demonstreren dat de spinrelaxatietijd verlengd kan worden door te opereren bij lage magneetvelden en door gebruik te maken van devices met een grote valleisplitting. Dit experiment toont, samen met recenter werk, aan dat er geen fundamentele beperkingen zijn die hogeretemperatuuroperatie van siliciumspinqubits in de weg staan. Tegelijkertijd is het een actief onderzoeksgebied om klassieke elektronica naar lagere temperaturen te brengen.

xii Samenvatting

Het tweede experiment maakt gebruik van maximaal verstrengelde Bell-toestanden van twee quantumbits voor het bestuderen van plaatsafhankelijke correlaties in de ruis werkend op deze quantumbits. Plaatsafhankelijke correlaties in qubitfouten belemmeren quantumfoutcorrectieprotocollen die noodzakelijk zullen zijn voor foutbestendige quantum computers op grote schaal, omdat deze protocollen in het algemeen zijn ontwikkeld onder de aanname van verwaarloosbare correlaties in gubitfouten. Het is daarom van belang om inzicht te krijgen in de mate waarin de ruis die deze fouten veroorzaakt gecorreleerd is. We meten slechts beperkte plaatsafhankelijke correlaties in de ruis en verkrijgen inzicht in de oorzaken daarvan. De data zijn in overeenstemming met decoherentie die met name wordt veroorzaakt door een combinatie van kernspins en meerdere ladingsfluctuatoren op enige afstand van de quantumbits die asymmetrisch koppelen met de twee quantumbits. We adviseren om vergelijkbare experimenten uit te voeren in isotopisch verrijkt silicium om het effect van kernspins uit te sluiten en zo plaatsafhankelijke correlaties in ladingsruis afzonderlijk te bestuderen. Tevens laten onze inzichten zien hoe correlaties gemaximaliseerd of geminimaliseerd kunnen worden door middel van het fysieke qubitontwerp. Vandaar dat de vooruitzichten voor de ontwikkeling en implementatie van quantumfoutcorrectieprotocollen in foutbestendige groteschaalquantumcomputers veelbelovend zijn.

Nadat we in de voorgaande experimenten verschillende aspecten hebben bestudeerd die van belang zijn bij het vaststellen van de geschiktheid van siliciumspinqubits voor de toepassing in groteschaalquantumcomputers, komen we ten slotte met een voorstel voor een concrete fysieke implementatie van spingubits geïntegreerd met klassieke aansturingselektronica in een spinqubitraster met dunne qubitbezetting. Hoewel de gemeenschap doorgaans claimt dat siliciumspinqubits verenigbaar zijn met conventionele CMOS-fabricage, doen bestaande voorstellen aannames die nog gevalideerd moeten worden. Het implementeren van quantumfoutcorrectie in een dunbezet spinqubitraster is onderzocht, maar de beschrijving van een fysieke implementatie ontbrak grotendeels. Dat het raster dunbezet is, maakt het mogelijk om lokale aansturingselektronica te integreren, waarvan eerder in dit proefschrift is aangetoond dat dit veelbelovend is. Concreet stellen we voor om sample-and-hold-circuits, die het mogelijk maken om inhomogeniteit in het raster te compenseren, te implementeren naast de qubitcircuits. Dit maakt individuele lokale controle en gedeelde rasterbrede controle mogelijk, wat resulteert in een efficiënte schaling van het aantal controledraden. Met het schaalbare eenheidscelontwerp beslaan  $2^{20}$  ( $\approx 10^6$ ) qubits  $\sim 150$  mm<sup>2</sup>. We beoordelen de haalbaarheid van het voorstel, met inbegrip van de fysieke implementatie en het bijbehorende oppervlak, de bijbehorende schaling van het aantal draden en verbindingsdichtheid.

Jelmer Boter

# INTRODUCTION

I think I can safely say that nobody understands quantum mechanics.

Richard P. Feynman

The world around us is governed by the theory of quantum mechanics instead of well-known classical physics. Everyday life does not usually reveal the intriguing properties of the theory that was developed more than a century ago, but at the fundamental level everything around us is quantum, and we really need quantum mechanics to explain some of the phenomena we observe. The ability to understand and control continuously growing quantum systems, such as atoms and molecules, has progressed significantly over the last decades, facilitating a better understanding of quantum mechanics and how it describes Nature. Researchers all over the world work hard to harness quantum properties such as superposition and entanglement in a new type of computer that is fundamentally different from classical computers. We are at the brink of building prototype quantum computers and experiencing a major breakthrough, but we can only guess what will be future applications of such systems. Without any doubt, interesting times lie ahead of us.

### 1.1. QUANTUM MECHANICS

Several experiments around the dawn of the 20<sup>th</sup> century could not be explained by the known laws of classical physics. One of the famous examples is the photoelectric effect for which Albert Einstein earned his Noble Prize. In his 1905 paper [1], he advanced the theory of light being composed of discrete packets (quanta) of energy, which we now know as photons. Later experiments proved his hypothesis, and that light not only behaves as waves, but also has a particle-like nature. Conversely, the double-slit experiment showing interference effects for electrons means they are not just particles, but they do behave wave-like in certain situations [2]. These are key examples of how the laws of quantum mechanics govern what happens at the smallest scale.

Wave-particle duality, superposition and entanglement are (somewhat counterintuitive) main concepts in quantum mechanics. Superposition is the notion that a particle can be in multiple states simultaneously, for example at several places. Entanglement refers to particles sharing a joint state that can not be described as the combination of the states of the individual particles. The state of the individual particles in an entangled state is not well-defined, at least, until a measurement takes place, because then the wave function collapses and a definite state for each particle will be measured.

The counter-intuitive features of the quantum theory are sometimes hard to accept. Even Einstein was of the opinion the theory was incomplete, as he wrote down with Podolski and Rosen in their famous Gedankenexperiment [3]. Despite this, the theory has proven to be very successful in describing what happens in the world surrounding us. Quantum mechanics makes accurate predictions that can be experimentally verified, and already has significant contributions to society, for example the laser and magnetic resonance imaging (MRI).

### 1.2. QUANTUM SIMULATION AND COMPUTATION

Two potential future applications of quantum mechanics are quantum simulation and quantum computation, as proposed already in the 1980s by Richard Feynman [4]. As Nature behaves quantum mechanically, the only way to properly simulate it is by using a quantum mechanical system. This is because superposition and entanglement make the number of states available to a quantum mechanical system grow exponentially with system size, while for a classical system the number of states grows linearly. Therefore, a quantum mechanical system quickly becomes intractable in a classical simulation as it grows. This exponential growth of complexity is also the origin of an enormous potential of computational power if quantum mechanics can be exploited to perform calculations. Opportunities of quantum computation lie, for example, in the field of material science (discovery of a high temperature superconductor) and drug design (more targeted selection of potential active substances).

Research groups all over the world, together with industry partners, are working on developing the quantum bit (qubit), the basic building block of a quantum computer. Analogous to how a classical bit, which is a two-level system that can be 0 or 1, can be used to store and process classical information, a quantum mechanical two-level system, that can be in a superposition of  $|0\rangle$  and  $|1\rangle$ , can be used as a qubit to store and

<sup>&</sup>lt;sup>1</sup>The |...⟩ notation indicates quantum states.

process quantum information. In addition, more and more attention is devoted to the other required parts of the quantum computing stack, such as control electronics and software. To harness the full potential offered by quantum computation, millions of qubits are required for fault-tolerant quantum computation, in order to fully describe the complex systems of interest, while being able to detect and correct errors in the calculation by means of quantum error correction (QEC).

However, before fault-tolerant quantum computers will become available, devices consisting of roughly 50 qubits or more, will already be capable of classically intractable, albeit useless, calculations. John Preskill came up with the terms *quantum supremacy* [5] and *Noisy Intermediate Scale Quantum (NISQ)* technology [6] to describe this era ahead of us. Quantum supremacy refers to performing a task on a quantum device that cannot be performed by any existing classical computer. Google made demonstrating quantum supremacy one of their major milestones and recently announced to have achieved this [7]. However, IBM says they could simulate Google's experiment on a classical supercomputer in 2.5 days, albeit without actually performing the simulation [8]. In the near future, the number of qubits working together will maximally be a few hundred (intermediate scale) and their control will not be perfect (noisy). This will limit what can be done with such systems, but they still will open up possibilities to explore new physics and facilitate progress towards larger-scale quantum devices, and therefore the NISQ era already is a very interesting time for physicists.

### QUBIT IMPLEMENTATIONS AND QUANTUM COMPUTER DEVELOPMENT

Several possible physical systems to implement a qubit exist. The main qubit candidates are trapped ions, cold atoms, superconducting qubits, spin qubits in quantum dots, spin qubits in nitrogen-vacancy centers in diamond and topological qubits based on Majorana fermions. They are at different stages of maturity, but for all of them the number of qubits in a single system is far from the millions required for large-scale quantum computation. All candidates have their advantages and disadvantages, and at this moment it is not yet clear which type or combination of qubit(s) is most suited. Industry puts most effort in superconducting qubits (Google, IBM, Rigetty and Intel), spin qubits in silicon quantum dots (Intel, CEA-Leti, STMicroelectronics, HRL and Imec) and topological qubits (Microsoft).

### THE DIVINCENZO CRITERIA

Any type of qubit should fulfill a set of requirements, known as the DiVincenzo criteria [9], for it to be a viable candidate for large-scale quantum computation. These criteria are the following:

1. Scalable physical system with well characterized qubits

For a physical system to act as a good qubit, its internal energy levels, including the

coupling between them, should be known accurately, as well as interactions with

other qubits and external fields. Furthermore, it should be, in principle, possible

to increase the number of qubits to an arbitrary number.

$<sup>^2</sup>$ Computing the final state resulting from a random gate sequence on  $\sim$ 50 qubits is classically not possible on current hardware.

2. Ability to initialize the state of the qubits to a simple fiducial state

Naturally, a set of qubits on which a computation is performed should be in a

well-known state before a computation commences for it to give a meaningful outcome. In addition, to be able to detect and correct errors during computation by

means of quantum error correction, a continuous supply of qubits in their ground

state is required.

### 3. Long relevant decoherence times

Quantum information has to be retained throughout the duration of the computation that is being performed. Qubits loose their quantum information due to decoherence. They can be protected from this by means of quantum error correction if the qubit coherence survives much longer than the time it takes to perform a single quantum operation.

### 4. Universal set of quantum gates

To be able to perform universal quantum computation, qubits should offer the possibility to perform single- and two-qubit operations. It has to be possible to compose a complete set of quantum gates from the native interactions present.

5. Qubit-specific measurement capability

To determine the outcome of a computation, it should be possible to measure the state of individual qubits. Ideally, such a measurement does not depend on the state of nearby qubits and leaves the state of the rest of the quantum computer unchanged.

Spin qubits in silicon quantum dots, the focus of this dissertation, can in principle satisfy all of these criteria and will be introduced in the next section.

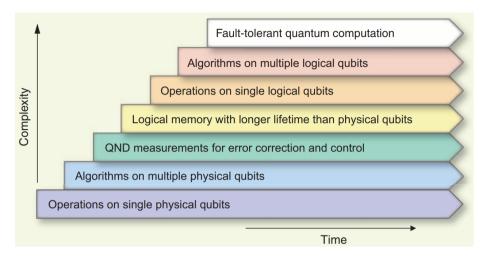

### THE DEVELOPMENT STAGES OF QUANTUM INFORMATION PROCESSING

Michel Devoret and Robert Schoelkopf later formulated seven stages (of increasing complexity) in developing quantum information processing [10]. These steps are depicted in Fig. 1.1. David DiVincenzo, who came up with the aforementioned criteria, referred to these steps as *complexity steps* and he expects that the upcoming future will be guided by these principles.<sup>3</sup> The DiVincenzo criteria are related to the first two stages that only involve physical qubits, while in the later stages quantum error correction and logical qubits play a role.

### 1.3. SILICON SPIN QUBITS

SILICON spin qubits store quantum information in the spin degree of freedom of electrons trapped in small conductive islands in silicon (see Sec. 2.2 for more details). For spin qubits in silicon quantum dots [11, 12] several few-qubit experiments, such as the demonstration of long coherence times [13], (high-fidelity) single- [13–16] and two-qubit gates [17–20], quantum algorithms [21], quantum non-demolition measurements [22, 23], strong spin-photon coupling [24–26] and long distance spin-spin coupling [27], have been demonstrated. Therefore, silicon spin qubits have already demonstrated most of the aforementioned DiVincenzo criteria and are promising candidates to

<sup>&</sup>lt;sup>3</sup>David DiVincenzo, *Looking back at the DiVincenzo criteria*, QuTech Blog (2018)

Figure 1.1: The development of quantum computation in seven stages of increasing complexity, where each step requires full proficiency over the preceding steps. Current research is still mostly focused on the lower stages, and silicon spin qubits are at the third stage with the recent demonstration of quantum non-demolition (QND) measurements [22, 23]. Adapted from Ref. [10].

be used in quantum computation, because their small footprint and compatibility with conventional CMOS fabrication make them attractive for scaling [28]. However, increasing the number of qubits (to the millions required for fault-tolerant quantum computation) still comes with challenges and for that reason the focus of this dissertation is on the scaling of silicon spin qubits.

Among other factors, qubit fabrication has to be reliable and reproducible, noise processes that cause qubit relaxation and decoherence (at elevated temperatures) have to be understood, and methods to control a large number of qubits have to be developed. These three aspects of scaling are the focus of the work presented in this dissertation, and will be discussed in the separate chapters. Therefore, the goal of this dissertation can be summarized as enabling next steps in the quest for larger quantum computation systems based on silicon spin qubits by solving some of the physics and engineering challenges involved in scaling.

### **1.4.** Thesis outline

The work presented in this dissertation is all motivated by the overarching goal of scaling up the system size and increasing the number of silicon spin qubits. The individual chapters discuss separate projects motivated by this goal, but do not directly build on each other. In what follows, the organization of this dissertation is sketched together with the connections between different chapters.

Chapter 2 provides the theoretical background for the work presented in the other chapters that follow. Quantum computation in general and spin qubits in silicon in particular are discussed. 6 1. Introduction

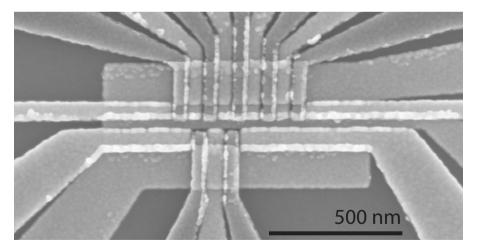

• **Chapter 3** presents work on the development of a reliable and reproducible integration scheme for silicon quantum dot structures, that are meant for spin qubit experiments, in an academic cleanroom environment.

- A silicon spin qubit device fabricated following these fabrication recipes is used in

Chapter 4 for experiments on the dependence of spin relaxation on temperature

and the external magnetic field, as well as the temperature dependence of charge

noise. The purpose of this work is to assess the prospects of operating silicon spin

qubits at elevated temperatures, which would allow for on-chip integration of clas sical control electronics.

- Chapter 5 discusses a study of spatial noise correlations in a Si/SiGe two-qubit system based on Bell state coherences. We assess to what extent the assumption of negligible correlations in qubit errors in most quantum error correction schemes, on which large-scale quantum computers will have to rely, is justified.

- After having studied several aspects that are relevant to determine the suitability

of silicon spin qubits for the use in large-scale quantum computers in the preceding chapters, Chapter 6 presents a proposal for the design of a large-scale array of

spin qubits that locally integrates classical control electronics. We assess the feasibility of such a design by considering the required electronic components, and the

associated footprint, line scaling, interconnect density and heat load.

- Finally, in **Chapter 7** I summarize the key findings of this dissertation and draw some conclusions. Furthermore, I give an outlook for further research towards a large-scale quantum computer based on silicon spin qubits.

1

### REFERENCES

- [1] A. Einstein, Über einen die Erzeugung und Verwandlung des Lichtes betreffenden heuristischen Gesichtspunkt, Annalen der Physik **322**, 132 (1905).

- [2] O. Donati, G. P. Missiroli, and G. Pozzi, *An Experiment on Electron Interference*, American Journal of Physics **41**, 639 (1973).

- [3] A. Einstein, B. Podolsky, and N. Rosen, *Can Quantum-Mechanical Description of Physical Reality Be Considered Complete?*, Physical Review **47**, 777 (1935).

- [4] R. P. Feynman, *Simulating physics with computers*, International Journal of Theoretical Physics **21**, 467 (1982).

- [5] J. Preskill, *Quantum computing and the entanglement frontier*, Proceedings of the 25th Solvay Conference on Physics (2012).

- [6] J. Preskill, Quantum Computing in the NISQ era and beyond, Quantum 2, 79 (2018).

- [7] F. Arute *et al.*, *Quantum supremacy using a programmable superconducting processor*, Nature **574**, 505 (2019).

- [8] E. Pednault, J. A. Gunnels, G. Nannicini, L. Horesh, and R. Wisnieff, Leveraging Secondary Storage to Simulate Deep 54-qubit Sycamore Circuits, arXiv:1910.09534.

- [9] D. P. DiVincenzo, *The Physical Implementation of Quantum Computation*, Fortschritte der Physik **48**, 771 (2000).

- [10] M. H. Devoret and R. Schoelkopf, *Superconducting Circuits for Quantum Information: An Outlook*, Science **339**, 1169 (2013).

- [11] D. Loss and D. P. DiVincenzo, *Quantum computation with quantum dots*, Physical Review A **57**, 120 (1998).

- [12] F. A. Zwanenburg, A. S. Dzurak, A. Morello, M. Y. Simmons, L. C. L. Hollenberg, G. Klimeck, S. Rogge, S. N. Coppersmith, and M. A. Eriksson, *Silicon quantum electronics*, Reviews of Modern Physics 85, 961 (2013).

- [13] M. Veldhorst, J. C. C. Hwang, C. H. Yang, A. W. Leenstra, B. de Ronde, J. P. Dehollain, J. T. Muhonen, F. E. Hudson, K. M. Itoh, A. Morello, and A. S. Dzurak, *An addressable quantum dot qubit with fault-tolerant control fidelity*, Nature Nanotechnology **9**, 981 (2014).

- [14] E. Kawakami, P. Scarlino, D. R. Ward, F. R. Braakman, D. E. Savage, M. G. Lagally, M. Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, *Electrical control of a long-lived spin qubit in a Si/SiGe quantum dot*, Nature Nanotechnology 9, 666 (2014).

- [15] E. Kawakami, T. Jullien, P. Scarlino, D. R. Ward, D. E. Savage, M. G. Lagally, V. V. Dobrovitski, M. Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, *Gate fidelity and coherence of an electron spin in a Si/SiGe quantum dot with micromagnet*, PNAS 113, 11738 (2016).

- [16] J. Yoneda, K. Takeda, T. Otsuka, T. Nakajima, M. R. Delbecq, G. Allison, T. Honda, T. Kodera, S. Oda, Y. Hoshi, N. Usami, K. M. Itoh, and S. Tarucha, *A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than* 99.9%, Nature Nanotechnology **13**, 102 (2018).

- [17] M. Veldhorst, C. H. Yang, J. C. C. Hwang, W. Huang, J. P. Dehollain, J. T. Muhonen, S. Simmons, A. Laucht, F. E. Hudson, K. M. Itoh, A. Morello, and A. S. Dzurak, *A two-qubit logic gate in silicon*, Nature **526**, 410 (2015).

- [18] D. M. Zajac, A. J. Sigillito, M. Russ, F. Borjans, J. M. Taylor, G. Burkard, and J. R. Petta, *Resonantly driven CNOT gate for electron spins*, Science **359**, 439 (2018).

- [19] X. Xue, T. F. Watson, J. Helsen, D. R. Ward, D. E. Savage, M. G. Lagally, S. N. Coppersmith, M. A. Eriksson, S. Wehner, and L. M. K. Vandersypen, *Benchmarking Gate Fidelities in a Si/SiGe Two-Qubit Device*, Physical Review X **9**, 021011 (2019).

- [20] W. Huang, C. H. Yang, K. W. Chan, T. Tanttu, B. Hensen, R. C. C. Leon, M. A. Fogarty, J. C. C. Hwang, F. E. Hudson, K. M. Itoh, A. Morello, A. Laucht, and A. S. Dzurak, *Fidelity benchmarks for two-qubit gates in silicon*, Nature **569**, 532 (2019).

- [21] T. F. Watson, S. G. J. Philips, E. Kawakami, D. R. Ward, P. Scarlino, M. Veldhorst, D. E. Savage, M. G. Lagally, M. Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, *A programmable two-qubit quantum processor in silicon*, Nature **555**, 633 (2018).

- [22] J. Yoneda, K. Takeda, A. Noiri, T. Nakajima, S. Li, J. Kamioka, T. Kodera, and S. Tarucha, *Repetitive single electron spin readout in silicon*, arXiv:1910.11963.

- [23] X. Xue, B. D'Anjou, T. F. Watson, D. R. Ward, D. E. Savage, M. G. Lagally, M. Friesen, S. N. Coppersmith, M. A. Eriksson, W. A. Coish, and L. M. K. Vandersypen, *Repetitive quantum non-demolition measurement and soft decoding of a silicon spin qubit,* arXiv:1911.08420.

- [24] N. Samkharadze, G. Zheng, N. Kalhor, D. Brousse, A. Sammak, U. C. Mendes, A. Blais, G. Scappucci, and L. M. K. Vandersypen, *Strong spin-photon coupling in silicon*, Science **359**, 1123 (2018).

- [25] X. Mi, M. Benito, S. Putz, D. M. Zajac, J. M. Taylor, G. Burkard, and J. R. Petta, *A coherent spin-photon interface in silicon*, Nature **555**, 599 (2018).

- [26] A. J. Landig, J. V. Koski, P. Scarlino, U. C. Mendes, A. Blais, C. Reichl, W. Wegscheider, A. Wallraff, K. Ensslin, and T. Ihn, *Coherent spin–photon coupling using a resonant exchange qubit*, Nature **560**, 179 (2018).

- [27] F. Borjans, X. G. Croot, X. Mi, M. J. Gullans, and J. R. Petta, *Long-Range Microwave Mediated Interactions Between Electron Spins*, arXiv:1905.00776.

- [28] L. M. K. Vandersypen, H. Bluhm, J. S. Clarke, A. S. Dzurak, R. Ishihara, A. Morello, D. J. Reilly, L. R. Schreiber, and M. Veldhorst, *Interfacing spin qubits in quantum dots and donors–hot, dense and coherent*, npj Quantum Information 3, 34 (2017).

# **THEORY**

This chapter provides the theoretical background relevant for the work presented in this thesis. First, a brief introduction to relevant general quantum computation concepts is given, followed by an explanation of the basics of spin qubits in silicon quantum dots.

## 2.1. QUANTUM COMPUTATION

Q UANTUM mechanics offers a fundamentally different way of computation, which makes it possible to solve certain problems that cannot be solved in a reasonable time by even the most powerful classical computers. This section introduces the basic concepts of quantum computation.

### 2.1.1. QUANTUM BITS

A quantum bit (qubit) is the quantum mechanical analog of a classical bit. A classical bit is formed by a classical two-level system and equivalently a qubit is formed by a quantum mechanical two-level system. While a classical bit can be either in 0 or 1, a qubit in general is in a quantum mechanical superposition of  $|0\rangle$  and  $|1\rangle$ :

$$|\psi\rangle = \alpha |0\rangle + \beta |1\rangle, \tag{2.1}$$

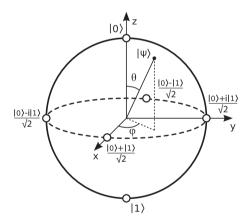

with  $|\alpha|^2+\left|\beta\right|^2=1$  to ensure normalization. The probability for the qubit to collapse to the  $|0\rangle$  or  $|1\rangle$  state upon measurement, is given by  $|\alpha|^2$  and  $|\beta|^2$ , respectively. Without loss of generality, it is possible to write  $\alpha=\cos\left(\frac{\theta}{2}\right)$  and  $\beta=e^{i\varphi}\sin\left(\frac{\theta}{2}\right)$ . Here,  $\theta$  determines the amplitude (and probability) of the two basis states, and  $\varphi$  sets the relative phase between these states. Following this definition, the state of a qubit can be represented on the Bloch sphere, see Fig. 2.1. All possible qubit states defined by Eq. 2.1 lie on the surface of this unity sphere.

Figure 2.1: Bloch sphere representation of a qubit. The qubit basis states  $|0\rangle$  and  $|1\rangle$  lie at the poles of the sphere. The four other cardinal states on the  $\hat{x}$  and  $\hat{y}$  axis are also indicated. A general qubit state  $|\psi\rangle$  is defined by  $\theta$  and  $\varphi$ , as given by Eq. 2.1 and the definition of  $\alpha$  and  $\beta$  in the main text. Adapted from en.wikipedia.org (courtesy of Smite-Meister).

Quantum information is fragile and will be lost over time as a result of several processes. Relaxation is the decay of the excited state ( $|1\rangle$ ) to the ground state ( $|0\rangle$ ), which is related to the projection of the qubit state on the  $\hat{z}$  axis of the Bloch sphere, so to  $\theta$ . The corresponding characteristic timescale is called  $T_1$ . Decoherence refers to the randomization of the phase  $\varphi$  of the qubit state, which corresponds to the direction in the  $\hat{x} - \hat{y}$  plane of the Bloch sphere. Decoherence takes place at the timescale  $T_2^*$ .

A multi-qubit generalization of the Bloch sphere picture does not exist, but a general N-qubit state can be represented by a  $2^N \times 2^N$  matrix, called a density matrix. The diagonal elements of a density matrix describe the population of the different N-qubit states, while the off-diagonal elements quantify the coherences between these states. For example, the density matrix corresponding to the two-qubit Bell state  $|\Psi^+\rangle = \frac{|01\rangle + |10\rangle}{\sqrt{2}}$  is, in the  $\{|00\rangle, |01\rangle, |10\rangle, |11\rangle\}$  basis, given by

$$\rho_{|\Psi^{+}\rangle} = \frac{1}{2} \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 1 & 1 & 0 \\ 0 & 1 & 1 & 0 \\ 0 & 0 & 0 & 0 \end{bmatrix}. \tag{2.2}$$

#### SINGLE- AND TWO-OUBIT GATES

Creating a single-qubit state corresponding to any point on the Bloch sphere in general requires a combination of rotations (i.e. single-qubit gates) about two independent axis. For example, one has to be able to perform rotations about the  $\hat{x}$  and  $\hat{z}$  axis, but the two axis do not necessarily have to be orthogonal. This required controllability is referred to as two-axis single-qubit control. In general, single-qubit gates are described by  $2 \times 2$  unitary matrices that are a linear combination of the identity matrix and the Pauli matrices.

To harness the full potential of quantum computation, it is required to create entanglement between qubits. The Bell state  $|\Psi^+\rangle = \frac{|01\rangle + |10\rangle}{\sqrt{2}}$  is a maximally entangled state in which the two entangled qubits share a well-defined joint state, while the state of the individual particles is not defined. One of the qubits is in  $|0\rangle$  and the other qubit is in  $|1\rangle$ , but which of them is in  $|0\rangle$  and which is in  $|1\rangle$  is undetermined.

To create entanglement between qubits, two-qubit gates (described by  $4\times4$  unitary matrices) are required. The prototypical example of a two-qubit gate is the controlled-NOT (CNOT) gate. The CNOT gate flips the target qubit if the control qubit is in the  $|1\rangle$  state, while the target qubit is unaffected if the control qubit is in the  $|0\rangle$  state. In the  $\{|00\rangle, |01\rangle, |10\rangle, |11\rangle$  basis the CNOT gate is described by the matrix:

$$U_{CNOT} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{bmatrix}. \tag{2.3}$$

It can be proven that any logical multi-qubit gate can be composed from single-qubit gates and the CNOT gate, and for that reason this is called a universal gate set for quantum computation [1].

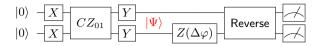

A common way to represent a quantum computation consisting of single- and multiqubit gates, is a quantum circuit diagram. Figure 2.2 shows an example of a quantum circuit diagram. Each horizontal line represents a qubit, a block interrupting a line represents a gate and a block connecting lines is a multi-qubit gate.

### **2.1.2.** QUANTUM ERROR CORRECTION

As already mentioned, quantum states are fragile and interaction with the environment causes decoherence, resulting in loss of quantum information. However, qubit control,

Figure 2.2: Quantum circuit diagram used in the experiments described in Ch. 5 to create the Bell state  $|\Psi\rangle=\frac{|01\rangle-i|10\rangle}{\sqrt{2}}$  starting from the  $|00\rangle$  state. The X and Y blocks represent 90 degree single-qubit rotations around the  $\hat{x}$  and  $\hat{y}$  axis, respectively, the Z block represents a rotation over  $\Delta \phi$  around the  $\hat{z}$  axis, and the  $CZ_{01}$  block represents the two-qubit controlled-phase gate that phases the  $|01\rangle$  state by -1, while leaving the other states unaffected. Here, the Reverse block implies execution of the preparation sequence in the reverse order and the blocks containing a dial represent single-shot measurements of the qubit.

and consequently quantum computation, relies on controlled interactions with the environment. Therefore, it is necessary to be able to deal with the inevitable errors occurring during any computation. For that purpose quantum error correction (QEC), analogous to classical error correction, has been developed. QEC makes it possible to detect and correct errors in a quantum computation by encoding a logical qubit in multiple physical qubits. Two types of (physical) qubits exist, based on their function: the data qubits store the qubit state, while the ancilla qubits are used to detect errors.

If the error probability is sufficiently low (below a constant threshold), i.e. if the fidelity of the individual operations is sufficiently high, the overall error can be reduced at the expense of more overhead by encoding the logical information in more and more physical qubits. In this situation, quantum computation is said to be fault-tolerant and can be performed with arbitrary precision [2].

Several QEC schemes exist, with the surface code as the most well-known example [3]. A concrete example is Surface-17, which encodes one logical qubit in 17 physical qubits [4]. The surface code has an error threshold of  $\sim$ 1% [5]. This threshold, as well as most other thresholds, is derived under the assumption of negligible correlations in individual qubit errors.

## 2.2. SPIN QUBITS IN SILICON QUANTUM DOTS

T HE work in this thesis is focused on spin qubits in silicon quantum dots. This section first introduces gate-defined semiconductor quantum dots. Then, a brief overview of spin qubit implementations is given, followed by a discussion of several aspects that are relevant for (single-)spin qubits. Finally, the relevant properties of silicon for spin qubits are discussed.

### **2.2.1.** SEMICONDUCTOR QUANTUM DOTS

Quantum dots (QDs) are tiny regions of conducting material in an environment of insulating material. Several types of QDs exist, but the work in this thesis only concerns lateral gate-defined QDs in semiconductors [6]. Due to the small size of these QDs (10-100 nm), it takes a finite energy to add an extra electron, because of Coulomb repulsion, as described by the constant-interaction model [7]. The additional energy required to add an extra electron to a QD is given by its charging energy  $E_C = \frac{e^2}{2C}$ , and a sufficiently

<sup>&</sup>lt;sup>1</sup>Here  $e = 1.602 \cdot 10^{-19}$  C is the elementary charge and C is the total capacitance of the QD.

large charging energy allows to control the number of electrons confined in a QD accurately down to the single-electron regime. Furthermore, the small size also causes the orbital levels of electrons in such islands to be quantized. Adding electrons to a QD one by one shows shell filling and therefore quantum dots are often called artificial atoms [8].

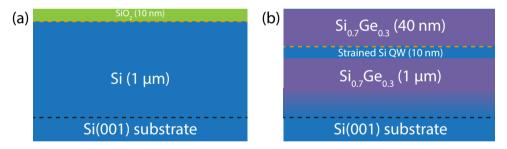

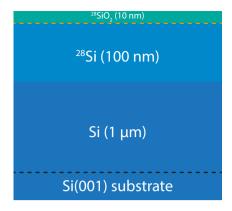

To create lateral gate-defined QDs, first a two-dimensional electron gas (2DEG) is formed by confinement at an interface in a heterostructure. Band gap differences between the materials result in strong confinement in the vertical direction, which yields quantization of the electron motion perpendicular to the interface. The 2DEG is either supplied with electrons from a doping layer in the heterostructure (depletion-mode QDs) or induced by accumulation gates (accumulation-mode QDs). Examples of such material systems are gallium arsenide/aluminium gallium arsenide (GaAs/AlGaAs), silicon/silicon germanium (Si/SiGe) and silicon/silicon dioxide (Si/SiO<sub>2</sub>). The latter is also referred to as Si-MOS, after the metal-oxide-semiconductor (MOS) stack. The work in this thesis concerns Si/SiGe and Si-MOS and these material systems are discussed in more detail later in this section. After forming the 2DEG, fine gate electrodes on top of the heterostructure allow to locally tune the potential landscape in the 2DEG by setting the gate voltages, thereby forming QDs that are isolated from other dots and the reservoirs by tunnel barriers. The same gate electrodes can be used to control the number of electrons in the ODs.

The number of electrons in a QD can be determined from transport measurements through the QD, but alternatively can also be measured non-invasively and very accurately by using a nearby charge sensor. A quantum point contact (QPC) [9] or QD [10] in the proximity of the QD to be sensed can be used as a charge sensor. As another possibility, one of the gate electrodes used to define the QD can be used for dispersive charge sensing [11]. The measurement of the occupation of a QD with a charge sensor does not depend on the tunnel barriers of the QD, which makes a charge sensor more suitable for the few-electron regime than transport measurements.

For the experiments in this thesis a sensing QD has been used. This method relies on the fact that transport through a QD is only possible if one (or more) of the discrete energy levels is (are) within the bias window between source and drain, while transport is not allowed otherwise due to Coulomb blockade. Transport through a QD that is tuned on the flank of one of its Coulomb peaks is very sensitive to its electrostatic environment, which makes it possible to discriminate single electrons in the environment of the sensing dot. A sensing QD can be used in transport, possibly in combination with lock-in techniques [12], or alternatively, the sensing dot can be embedded in a resonant circuit for RF sensing [10].

### **2.2.2. S**PIN QUBITS

Having established the ability to trap a single electron in a quantum dot, this electron, being a spin-1/2 particle, offers the canonical example of a quantum mechanical two-level system formed by the electron spin-up and spin-down states. The spin of an electron is an intrinsic angular momentum giving rise to a magnetic dipole moment. The magnitude of this dipole moment is given by the Bohr magneton  $\mu_B = 9.274 \cdot 10^{-24}$  J/T.

As a result, an external magnetic field  $B_{ext}$  splits the spin-up and -down states in energy due to the Zeeman effect by

$$E_Z = g\mu_B B_{ext},\tag{2.4}$$

where g is the electron g-factor ( $g \approx 2$  in silicon). The spin states of an electron in a magnetic field serve as the computational basis states of a qubit in what is referred to as a single-spin qubit or Loss-DiVincenzo (LD) qubit [13].

The single-spin qubit is the simplest form of a spin qubit, but several other implementations of spin qubits exist, which employ spin states of more than one electron in more than one quantum dot to define a qubit. In contrast with the single-spin qubit, all other types of spin qubits constitute an effective pseudo-spin two-level system. Examples of other spin qubit implementations are the singlet-triplet qubit (two electrons in two dots) [14], the hybrid qubit (three electrons in two dots) [15], the (always-on) exchange-only qubit (three electrons in three dots) [16, 17], as well as the quadrupolar exchange-only qubit (four electrons in three dots) [18]. All these spin qubit implementations attempt to mitigate certain decoherence mechanisms or to reduce the experimental requirements at the expense of complexity.

In general, using spin states as basis states for a qubit has the advantage of long coherence times, compared to for example a charge qubit [19], because spin does not interact directly with electric noise. However, spin-orbit coupling does provide an indirect coupling, which still causes decoherence, albeit less than for charge qubits. With a reduced effect of electrical noise sources, the hyperfine interaction also is a relevant decoherence mechanism for spin qubits. Spin-orbit coupling and the hyperfine interaction are discussed below.

#### SPIN-ORBIT COUPLING

An electron moving in an electric field  $\vec{E}$ , will experience a magnetic field in its own reference frame as a result of relativity. The effective magnetic field is proportional to  $\vec{E} \times \vec{p}$ , where  $\vec{p}$  is the momentum of the electron, so it depends on the orbital motion of the electron, thereby coupling the spin of the electron to its orbital motion. In solids, such electric fields can originate from the absence of structural inversion symmetry or bulk inversion symmetry. Interfaces in general have structural inversion asymmetry, which causes Rashba spin-orbit interaction [20]. Bulk inversion asymmetry occurs for example in the zinc-blende structure of GaAs and gives rise to the Dresselhaus contribution to the spin-orbit interaction [21].

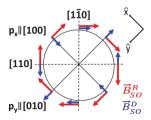

Figure 2.3: Rashba (red) and Dresselhaus (blue) contributions to the spin-orbit field  $\vec{B}_{SO}$  for an electron moving in two dimensions with momentum  $\vec{p}$ . Here  $|\alpha| \neq |\beta|$ ,  $\alpha < 0$  and  $\beta > 0$ . Adapted from Scarlino *et al.* [22].

Spin-orbit interaction in two dimensions is described by the Hamiltonian

$$H_{SO}^{2D} = \alpha(-p_{\nu}\sigma_{x} + p_{x}\sigma_{\nu}) + \beta(-p_{x}\sigma_{x} + p_{\nu}\sigma_{\nu}), \tag{2.5}$$

where  $\alpha$  and  $\beta$  describe the strength of the Rashba and Dresselhaus terms, respectively,  $p_i$  is the *i* component of the momentum of the electron and  $\sigma_i$  is the Pauli *i* spin matrix.  $\alpha$  is determined by the material(s) and the confinement potential, and  $\beta$  depends on material properties and  $\langle p_z^2 \rangle$  [23]. As depicted in Fig. 2.3, the Rashba and Dresselhaus contributions to spin-orbit interaction add up, cancel or are perpendicular for motion in certain directions. The total strength of the spin-orbit interaction is therefore anisotropic and is characterized by the distance an electron has to travel for a spin-orbit-induced  $\pi$ rotation, known as the spin-orbit length  $l_{SO}$ .

In the presence of spin-orbit coupling, the eigenstates are admixtures of spin and orbital states [24]. Electric noise does not couple directly to spin, but will couple to the orbital part leading to spin relaxation [24–26]. The most important source of electric field fluctuations in experimental setups with proper filtering is formed by phonons. Only acoustic phonons contribute, since optical phonons typically have energies much higher than the Zeeman energy [27]. Deformation potential phonons deform the crystal lattice inhomogeneously and are relevant in all semiconductors, while piezoelectric phonons cause homogeneous strain and only play a role in polar crystals [23]. Spin-orbit coupling does, to leading order, not give rise to pure dephasing of electron spins [28].

#### HYPERFINE INTERACTION

The spin of an electron in a quantum dot interacts with the spin of nuclei in the host material via the hyperfine interaction. The Fermi contact hyperfine interaction between the electron spin and nuclear spins is described by the Hamiltonian

$$H_{HF} = \sum_{i=1}^{N} A_i \vec{I}_i \cdot \vec{S} = g \mu_B \vec{B}_N \vec{S}, \tag{2.6}$$

where  $A_i$  is the interaction strength of the electron spin with the spin of nucleus i that depends on the overlap of the electron wave function with nucleus i,  $\vec{l}_i$  and  $\vec{S}$  are the spin operators for nucleus i and the electron, respectively, and  $\vec{B}_N = \sum_{i=1}^N \frac{A_i \vec{l}_i}{g \mu_B}$  is an effective magnetic field (Overhauser field) describing the ensemble of nuclear spins acting on the electron spin, similar to an external magnetic field [23, 29].

The unknown and fluctuating nature of the Overhauser field results in a random evolution of the electron spin, causing decoherence [30–33]. The timescale of nuclear spin dynamics is typically longer than for the electron spin, so the Overhauser field assumes a quasi-static random value. For a Gaussian distributed Overhauser field with standard deviation  $\sigma_N$ , the electron spin coherence shows a Gaussian decay with timescale [23, 30]

$$T_2^* = \frac{\sqrt{2}\hbar}{g\mu_B \sigma_N},\tag{2.7}$$

where  $\hbar = \frac{h}{2\pi}$  is the reduced Planck constant. In usual experimental settings, the energy scale of the hyperfine interaction is much smaller than the Zeeman energy, so hyperfine interaction does not lead to spin relaxation.

### ELECTRON SPIN RESONANCE AND ELECTRIC DIPOLE SPIN RESONANCE

Single-qubit gates for single-spin qubits are based on the interaction of spin with magnetic fields. The Zeeman effect lifts the degeneracy of spin states in a magnetic field, as expressed in Eq. 2.4. Additionally, an oscillating magnetic field  $B_1$  perpendicular to the static field that splits the spin-up and spin-down states, drives Rabi transitions between these states if its frequency f matches the energy difference ( $hf = g\mu_B B_{ext}$ ). This is called electron spin resonance (ESR) and its most direct implementation is by applying an oscillating magnetic field by passing an alternating current with frequency f through an on-chip microwave stripline close to the electron spin. This has been demonstrated both in GaAs [34] and silicon devices [35]. Careful stripline design results in bulky structures, making it challenging to properly implement several striplines in one device and to achieve individual addressability of several electron spins. Furthermore, dissipation in the stripline causes sample heating, but this can be circumvented by using a superconducting material for the stripline.

Alternatively, an electron can also be made to experience an effective oscillating magnetic field by moving it back and forth in a spatially varying magnetic field, thereby driving spin transitions if the frequency of the oscillating motion matches the energy difference between the spin-up and spin-down states. In that case the coupling is indirect, via the charge of the electron, and the effect is referred to as electric dipole spin resonance (EDSR). A magnetic field varying on the length scale of quantum dots can be generated by micron sized magnets in the proximity of the dots, as proposed by Tokura *et al.* [36] and first demonstrated by Pioro-Ladrière *et al.* [37]. The magnitude of the effective oscillating magnetic field is given by

$$B_{MM}^{ac} = \frac{eE_{ac}l_{orb}^2 \left| \frac{\partial B_{x,y}}{\partial z} \right|}{E_{orb}},$$

(2.8)

where e is the electron charge,  $E_{ac}$  is the amplitude of the varying electric field,  $l_{orb}$  is the spatial extend of the wave function,  $\frac{\partial B_{x,y}}{\partial z}$  is the gradient of the transverse magnetic field component (x,y) in the direction of movement caused by the electric field (z) and  $E_{orb}$  is the confinement energy. Spin-orbit coupling (SOC) can also give rise to an effective magnetic field experienced by a moving electron, and for that reason the magnetic field gradient generated by micromagnets is sometimes called an artificial spin-orbit field. In GaAs, SOC can be used as an efficient driving mechanism [38], but SOC is weak in bulk silicon and spin-orbit driving therefore is inefficient. Nevertheless, interface effects allow for spin-orbit-like driving of silicon spin qubits [39, 40].

For single-spin qubits, the required two-axis control is achieved by microwave driven rotations based on E(D)SR around the  $\hat{x}/\hat{y}$  axis, and rotations around the  $\hat{z}$  axis by updating the rotating reference frame in software [41].

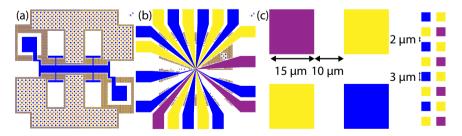

### MICROMAGNET DESIGN FOR EDSR

A magnetic field in general has components in all three spatial directions as well as gradients of each component in all three directions, so in total there are twelve relevant quantities to consider in designing micromagnets for EDSR driving of spin qubits. Fortunately, Maxwell's equations and symmetry reduce this number. This section first makes

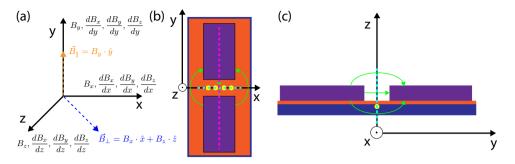

Figure 2.4: (a) The coordinate frame used for the discussion on micromagnets. All three directions have a magnetic field component and a gradient of all three components in that direction associated with it. An external magnetic field is applied in the  $\hat{y}$  direction resulting in the indicated parallel and perpendicular field components. (b,c) A simple micromagnet design (purple rectangles) that is symmetric in the cyan and magenta lines. The qubits are indicated by yellow circles at the blue-orange interface in the heterostructure. Magnetic field lines are sketched in green.  $B_x$  and  $B_z$  vanish in the  $\hat{x}$ - $\hat{z}$  plane at y=0 (indicated by the cyan lines).

some definitions and then gives an overview of what is relevant for micromagnet design to facilitate further discussions.

The coordinate frame used in this discussion is defined in Fig. 2.4. The 2DEG is formed in the  $\hat{x}$ - $\hat{y}$  plane, with the qubits along the  $\hat{x}$  axis. An in-plane external magnetic field is applied along the  $\hat{y}$  direction,  $\hat{y}$  so the  $\hat{y}$  component of the magnetic field generated by the micromagnet(s) is parallel to the external magnetic field:  $\vec{B}_{\parallel} = B_y \cdot \hat{y}$ . The  $\hat{x}$  and  $\hat{z}$  components of the micromagnet field add up to form the perpendicular magnetic field:  $\vec{B}_{\perp} = B_x \cdot \hat{x} + B_z \cdot \hat{z}$ .

The qubit frequency is defined by the absolute value of the total magnetic field via the Zeeman splitting as given by:

$$f = \frac{g\mu_B |\vec{B_{tot}}|}{h},\tag{2.9}$$

where  $|\vec{B_{tot}}| = \sqrt{B_x^2 + B_y^2 + B_z^2}$  is the vector sum of the field components of the total magnetic field in all three directions. For a magnet design symmetric in the  $\hat{x}$ - $\hat{z}$  plane indicated by the cyan lines in Figs. 2.4(b,c),  $B_x$  and  $B_z$  vanish in this plane. Since the qubits are in this plane,  $B_x$  and  $B_z$  vanish at the positions of the qubits, and  $B_y$  is the only relevant component;  $B_y$  is maximum in this plane. The qubit addressability is determined by the gradient of the parallel magnetic field component along the axis connecting the qubits, which is now given by  $G_{\parallel} = \frac{\partial B_{\parallel}}{\partial x} = \frac{\partial B_y}{\partial x}$ . This gradient, however, does also cause decoherence and therefore should be minimized given the required minimal addressability, so one has to find a balance between addressability and decoherence. The qubits are assumed to be driven in the  $\hat{y}$  direction,  $\hat{y}$  so the gradient responsible for driving of the

<sup>&</sup>lt;sup>2</sup>Applying the external magnetic field along the long axis of the micromagnets is most logical, but for more complicated designs the long direction might not be obvious. Furthermore, in general the external magnetic field can be applied in another direction and this choice affects the following discussion. It is important to consider the effect on the magnetization of the micromagnet(s).

<sup>&</sup>lt;sup>3</sup>Depending on the gate design, the qubits can be driven in both the  $\hat{x}$  and  $\hat{y}$  direction. This choice affects the

electron spin is given by:  $G_{\perp} = \frac{\partial B_{\perp}}{\partial y} = \sqrt{\left(\frac{\partial B_x}{\partial y}\right)^2 + \left(\frac{\partial B_z}{\partial y}\right)^2}$  [42]. Here, the quantization axis is assumed to be fixed in the  $\hat{y}$  direction, which to first-order is correct, since  $B_x$  and  $B_z$  vanish at the positions of the qubits. All other gradients  $\left(\frac{\partial B_x}{\partial x}, \frac{\partial B_y}{\partial z}, \frac{\partial B_y}{\partial y}, \frac{\partial B_z}{\partial z}, \frac{\partial B_z}{\partial x}\right)$  purely cause decoherence and should be minimized.

The stationary Maxwell equations in free space:

$$\nabla \times \vec{B} = \left(\frac{\partial B_z}{\partial y} - \frac{\partial B_y}{\partial z}\right)\hat{i} + \left(\frac{\partial B_x}{\partial z} - \frac{\partial B_z}{\partial x}\right)\hat{j} + \left(\frac{\partial B_y}{\partial x} - \frac{\partial B_x}{\partial y}\right)\hat{k} = 0, \tag{2.10}$$

$$\nabla \cdot \vec{B} = \frac{\partial B_x}{\partial x} + \frac{\partial B_y}{\partial y} + \frac{\partial B_z}{\partial z} = 0,$$

(2.11)

give relations between the nine magnetic field gradients:

$$\frac{\partial B_z}{\partial y} = \frac{\partial B_y}{\partial z},

\frac{\partial B_x}{\partial z} = \frac{\partial B_z}{\partial x} = 0,

\frac{\partial B_y}{\partial x} = \frac{\partial B_x}{\partial y},

\frac{\partial B_x}{\partial x} = \frac{\partial B_y}{\partial y} = \frac{\partial B_z}{\partial z} = 0,$$

(2.12)

where the two equal-to-zero statements (that equate five of the gradients to zero) are true for a design that is symmetric in the  $\hat{x}$ - $\hat{z}$  plane indicated by the cyan lines shown in Figs. 2.4(b,c). This might not be true for a more complex design that is optimized for driving and addressability, but a careful design should minimize the effects of these five gradients that purely cause decoherence.

The four remaining gradients result in driving  $\left(\frac{\partial B_x}{\partial y}\right)$  and addressability  $\left(\frac{\partial B_y}{\partial x}\right)$ , or cannot be circumvented as a consequence of the Maxwell equations  $\left(\frac{\partial B_y}{\partial z}\right)$ . The main contribution to the driving gradient is  $\frac{\partial B_z}{\partial y}$ , which therefore should be maximized. Simultaneously also the decohering gradient  $\frac{\partial B_y}{\partial z}$  will be maximized, but that cannot be prevented.  $\frac{\partial B_x}{\partial y}$  forms a smaller contribution to the driving and has the same magnitude as the addressability gradient  $\frac{\partial B_y}{\partial x}$ . These gradients should be minimized, while yielding the required minimal addressability.

### **EXCHANGE INTERACTION**

Two-qubit gates for single-spin qubits exploit the exchange interaction between two electron spins. The exchange interaction arises from the Pauli exclusion principle, which states that two identical fermions are required to have an anti-symmetric wave function under particle exchange. Therefore, a symmetric spin wave function (triplet) has to be

discussion that follows. However, as will become clear, driving in the  $\hat{x}$  direction is ineffective for the design considered here.

associated with an excited, higher energy state, while an anti-symmetric spin wave function (singlet) can be combined with the ground state. The result is an effective interaction between the spins of two electrons, which is expressed by the Hamiltonian

$$H = -J\vec{S}_1 \cdot \vec{S}_2,\tag{2.13}$$

where J is the exchange interaction strength and  $\vec{S}_i$  is the spin operator for electron i. In solids, the magnitude and sign of J depend on wave function overlap and material properties. Positive J favors parallel spin alignment giving rise to ferromagnetism, while negative J favors anti-parallel spins giving rise to antiferromagnetism.

In spin qubits in quantum dots, the strength of the exchange interaction can be controlled by gate voltages via the tunnel coupling, because of its dependence on wave function overlap allowing for a tunable two-qubit interaction. Exploiting the exchange interaction for two-qubit gates was first proposed by Loss and DiVincenzo [13, 16]. Under its influence  $|\downarrow\uparrow\rangle$  evolves into  $|\uparrow\downarrow\rangle$  and back, because the singlet and triplet spin states are the eigenstates of the exchange interaction. Starting from  $|\uparrow\downarrow\rangle$ , proper timing of the interaction creates the maximally entangled state  $\frac{|\downarrow\uparrow\uparrow\uparrow\downarrow\rangle}{\sqrt{2}}$ . This operation is known as the  $\sqrt{SWAP}$  gate [1]. In the presence of a difference in Zeeman energy between two single-spin qubits, the exchange interaction still mediates two-qubit interaction, but flip-flop terms are suppressed by the difference in qubit energy. The resulting Hamiltonian is of Ising type and the native two-qubit gate is the controlled-phase (CZ) gate [43], which (up to single-qubit rotations) adds a phase to a specific two-qubit state:  $CZ_{ij}|m,n\rangle = (-1)^{\delta(i,m)\delta(j,n)}|m,n\rangle$  for  $i,j,m,n\in\{0,1\}$  [44].

#### SPIN READOUT

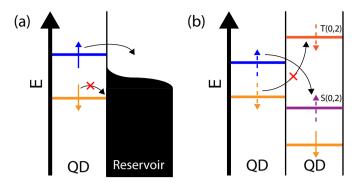

Single-shot readout of individual spins relies on spin-to-charge conversion, because the magnetic moment of a single electron spin is very small and therefore hard to detect directly. As discussed before, the number of electrons in a QD can be determined accurately by a nearby charge sensor, which allows to discriminate between different spin states if these states have a different charge configuration associated with them. The two most common methods used for spin readout are *Elzerman* readout (based on energy-selective tunneling) [45] and Pauli spin blockade (PSB) readout [46]. These two methods are explained below and the corresponding energy diagrams are shown in Fig. 2.5.

Elzerman readout relies on the energy difference between spin-up and spin-down states in a magnetic field. By tuning the electrochemical potential of the reservoir in between the spin energy levels, only an electron in the excited spin state is allowed to tunnel out to the reservoir, while an electron in the spin ground state will stay on the QD. An electron tunneling out and in again can be detected by a nearby charge sensor and signals the electron was in the excited spin state. If no tunnel event is detected, the electron was in its spin ground state. For a high readout fidelity, the Zeeman energy has to be sufficiently large compared to the thermal energy:  $E_Z \gg k_B T$ .

PSB readout discriminates singlet and triplet spin states. Starting in the (1,1) charge state and pulsing to the (0,2) charge state, under the right conditions a singlet spin state will be able to tunnel to the (0,2) charge configuration, while a triplet state will remain in the (1,1) configuration, because the triplet (0,2) state is higher in energy than the singlet

Figure 2.5: Energy diagrams for spin-to-charge conversion for spin readout in silicon. (a) For Elzerman readout the Fermi level of the reservoir is tuned in between the spin-up and spin-down energy levels. A spin-up electron can tunnel out, while a spin-down electron is trapped inside the QD. (b) For Pauli spin blockade (PSB) readout the right dot contains a spin-down reference electron. A spin-up electron in the left dot is able to tunnel to the singlet state in the right dot, while the triplet state is too high in energy for a spin-down electron to tunnel to the right dot.

state. Similar to Elzerman readout, the different charge configurations can be distinguished by a nearby charge sensor, signaling the combined spin state of the two electrons.

### **2.2.3. SILICON**

Gallium arsenide (GaAs) for a long time has been the workhorse material for quantum dot experiments, because of its high material quality. Pioneering work on spin qubits has been performed in GaAs devices, having resulted in the demonstration of two-qubit gates for both singlet-triplet [47] and single-spin qubits [48]. However, all nuclei in GaAs carry spin, which gives rise to a strong hyperfine interaction between the electron spin and nuclear spins resulting in fast electron spin decoherence [47, 49]. Silicon based devices have the advantage of less spinful nuclei and therefore hold a strong promise as hosts for spin qubits. The advantage of fewer nuclear spins, as well as other relevant properties of silicon, will be discussed below. In addition, the fabrication of silicon quantum dots is largely compatible with conventional CMOS industry, which allows for large-scale manufacturing of silicon spin qubits and on-chip integration of classical control electronics [50].

### HYPERFINE INTERACTION, SPIN-ORBIT COUPLING, SPIN RELAXATION AND G-FACTOR

In natural silicon, only 4.7% of the nuclei carry a spin, so the hyperfine interaction is small compared to GaAs, and isotopic purification allows to reduce the concentration of spinful nuclei even further [51]. In the context of the Avogadro project, silicon with a  $^{29}$ Si concentration of 50 ppm has been produced [52], and several experiments in spin qubit devices with residual  $^{29}$ Si concentration of 100–1000 ppm have been performed. As a result, spin coherence times are enhanced with a current record of  $T_2^* = 120~\mu s$  for quantum dot single-spin qubits [35], while for donors an even longer coherence time of  $T_2^* = 270~\mu s$  has been obtained [53].

Spin-orbit coupling in silicon is weak compared to GaAs, because of the lower atomic number and smaller band gap. Furthermore, bulk inversion asymmetry is absent in bulk silicon, so there is no Dresselhaus SOC, and the contribution is small otherwise. Finally, silicon does not have a polar crystal, so piezoelectric phonons do not exist. As a result, spin relaxation in silicon is slow compared to GaAs and a relaxation time  $T_1 \approx 3$  s has been measured in a Si/SiGe quantum dot [54].

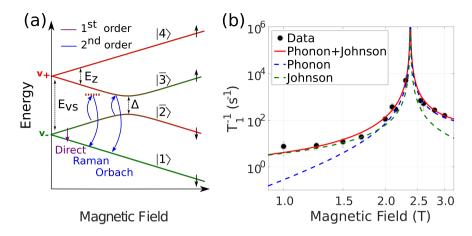

Electron spin relaxation in silicon quantum dots is expected to be dominated by Rashba SOC and phonon-induced modulation of the g-factor [25, 55–57]. Rashba SOC arises from the structural inversion asymmetry at the interface where the 2DEG is formed and at low temperature depends on magnetic field as  $T_1^{-1} \propto B^7$ . For quantum dots in Si(001) wafers, <sup>4</sup> relaxation caused by Rashba SOC is fastest for  $B \parallel [100]$ , [010] and slowest for  $B \parallel [001]$ , respectively. Phonon-induced modulation of the g-factor at low temperature yields  $T_1^{-1} \propto B^5$  with fastest relaxation for  $B \parallel [100]$ , [010], while relaxation vanishes for  $B \parallel [001]$ , [110]. Recently, another mechanism involving spin-valley mixing [58] has been experimentally demonstrated [59]. The dependence of spin relaxation on temperature and magnetic field in a Si-MOS quantum dot is studied in Ch. 4, and the results presented there are in agreement with the latter mechanism.

The electron g-factor in silicon is close to the free-electron value ( $g \approx 2$ ), so spin-down is the ground state in silicon, in contrast to GaAs where a negative g-factor ( $g \approx -0.44$ ) implies that spin-up is the ground state.

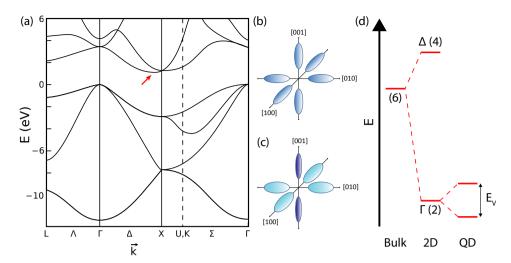

### CONDUCTION BAND VALLEYS

For silicon, the bottom of the conduction band is not located at the center of the Brillouin zone ( $\Gamma$  point), but at non-zero wave vector along the  $\Delta$  direction in between the  $\Gamma$  and X high symmetry points. As a result, there are six degenerate minima at  $k_0 \approx \pm 0.85 \times \frac{2\pi}{a_0}$  in the  $\hat{x}$ ,  $\hat{y}$  and  $\hat{z}$  directions, where  $a_0$  is silicon's lattice constant. The band structure of silicon is shown in Fig. 2.6(a).

In two-dimensional structures, confinement lifts the four in-plane  $\Delta$  valleys to much higher energies. In silicon/silicon-germanium (Si/SiGe) heterostructure in-plane strain also contributes to this effect. The remaining two-fold degeneracy of the  $\Gamma$  valleys is lifted by breaking of the inversion symmetry in the direction perpendicular to the 2DEG. This is the result of confinement at the interface where the 2DEG is formed and vertical electric fields. The energy difference between the two lowest valley states is referred to as the valley splitting, as depicted in Fig. 2.6(d).

Spin qubit experiments are potentially hindered by the presence of a low-lying excited valley state. If the valley splitting is not sufficiently large compared to the thermal energy  $E = k_B T$ , the excited valley state can be thermally populated, as was experimentally observed by Kawakami *et al.* [61]. First, this limits the initialization, manipulation as well as readout fidelity. Second, the exchange interaction often used for control of spin qubits (see Sec. 2.2.2) originates in the Pauli exclusion principle for fermions. Valleys offer an additional degree of freedom, which can render the exchange interaction ineffective [62]. Third, if the Zeeman energy and valley splitting are equal, states with both different spin and valley nature cross, and the combination of spin-orbit coupling and valley-orbit coupling gives rise to a second order spin-valley coupling, resulting in

<sup>&</sup>lt;sup>4</sup>The growth direction for Si(001) wafers is [001].

Figure 2.6: (a) Band structure of bulk silicon. The degenerate conduction band minimum is indicated by the red arrow. Adapted from de.wikipedia.org (courtesy of Cepheiden) [60]. (b,c) Constant energy surfaces (schematic, not to scale) near the conduction band minima for (b) bulk and (c) 2D silicon. The ellipsoids indicate a different curvature (and hence effective mass) in the longitudinal and transverse directions. In 2D structures (c) the parallel and perpendicular valleys split (courtesy of Pasquale Scarlino). (d) Valley splitting in silicon (schematic, not to scale). In bulk silicon, the conduction band minimum is six-fold degenerate (indicated between brackets), while in 2 dimensions the four  $\Delta$  valleys are much higher in energy than the two  $\Gamma$  valleys. The  $\Gamma$  valleys are further split by the valley splitting  $E_V$  in OD structures.

fast spin relaxation in a hot spot. This was demonstrated by Yang *et al.* [59] and is used in the experiments presented in Ch. 4. Finally, switching between valleys in general results in a shift of the qubit frequency, causing the phase to be randomized, which result in decoherence on the timescale of the valley switching.

The experiments presented in Ch. 4 aim for increasing the operation temperature of silicon spin qubits, for which a large valley splitting is beneficial. Instead of being a nuisance, the valleys can also be used as an asset, for example in a valley qubit [63]. This has been experimentally demonstrated in Refs. [64, 65], but at present cannot compete with other semiconductor qubit implementations.

### **EFFECTIVE MASS**

Transport and orbital properties at low temperature are affected by the effective mass  $m^*$ , which is inversely proportional to the curvature of the energy bands:  $m^* \propto \left(\frac{\partial^2 E}{\partial k^2}\right)^{-1}$ . The tunnel rate is, to first order, proportional to  $\exp(-m^*E_B)$  for a tunnel barrier of height  $E_B$ , so a large effective mass gives a lower tunnel coupling. In addition, the orbital confinement energy is given by  $E_{orb} \propto \left(m^* r_{dot}^2\right)^{-1}$ , which implies tighter confinement in a smaller dot is required to achieve the same orbital energy in materials with a larger effective mass.