# Computer Engineering Mekelweg 4, 2628 CD Delft The Netherlands http://ce.et.tudelft.nl/

MSc THESIS

## Dynamically Reconfigurable Fault-Tolerant Design of $\rho$ -VEX Softcore Processor

#### MUHAMMAD USMAN SALEEM

#### Abstract

CE-MS-2018-16

Over the past many years, technology scaling has resulted in a continuous reduction of lateral and vertical dimensions of transistors. The technology scaling, on the one hand, has led to a commensurate performance gain for very-large-scale integration (VLSI) circuits, but on the other hand, has also made such circuits more vulnerable to ionizing radiations which can cause single event effects(SEEs). These SEEs may cause the underlying user circuitry to deviate from its normal behavior. Devices that are destined for space missions need special protection for such kind of anomalies as space environment is filled with massive amount of high energy particles and ionizing radiations. In this thesis, the design, implementation, and verification of a fault-tolerant  $\rho$ -VEX, a softcore processor, is presented, so that it could be used as an attractive alternative to expensive radiation-hardened processors for space-based applications.  $\rho$ -VEX is a VLIW based, dynamically reconfigurable processor. Keeping in line with its inherent attribute, a dynamically reconfigurable faulttolerant mode is presented in this work, which provides the running application an option to activate and deactivate the fault-tolerant mode multiple times. In this mode, for the protection of processor pipeline, a non-traditional TMR approach that requires 3 lanegroups

running in 2-way mode is implemented. For the reliability of user memories, Hamming codes are implemented as an ECC coding scheme. The functionally of our fault-tolerant design is verified by using both a simulation-based platform (ModelSim) and an on-board FPGA platform (ML605 development kit). To measure the fault-tolerant capabilities of the  $\rho$ -VEX core, saboteurs are used to artificially inject faults at various predefined locations in the core. The obtained results have shown that our design can mitigate all injected single faults in the pipeline and double faults in the caches, without triggering any failure. The dynamically configurable fault-tolerant feature is obtained at the cost of about 30% additional resource utilization and 20% reduction in the maximum operating frequency.

## Dynamically Reconfigurable Fault-Tolerant Design of $\rho-\text{VEX}$ Softcore Processor

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

EMBEDDED SYSTEMS

by

MUHAMMAD USMAN SALEEM born in PAKISTAN

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

## Dynamically Reconfigurable Fault-Tolerant Design of $\rho$ -VEX Softcore Processor

#### by MUHAMMAD USMAN SALEEM

#### Abstract

Over the past many years, technology scaling has resulted in a continuous reduction of lateral and vertical dimensions of transistors. The technology scaling, on the one hand, has led to a commensurate performance gain for very-large-scale integration (VLSI) circuits, but on the other hand, has also made such circuits more vulnerable to ionizing radiations which can cause single event effects (SEEs). These SEEs may cause the underlying user circuitry to deviate from its normal behavior. Devices that are destined for space missions need special protection for such kind of anomalies as space environment is filled with massive amount of high energy particles and ionizing radiations. In this thesis, the design, implementation, and verification of a fault-tolerant  $\rho$ -VEX, a softcore processor, is presented, so that it could be used as an attractive alternative to expensive radiation-hardened processors for space-based applications.  $\rho$ -VEX is a VLIW based, dynamically reconfigurable processor. Keeping in line with its inherent attribute, a dynamically reconfigurable fault-tolerant mode is presented in this work, which provides the running application an option to activate and deactivate the fault-tolerant mode multiple times. In this mode, for the protection of processor pipeline, a non-traditional TMR approach that requires 3 lanegroups running in 2-way mode is implemented. For the reliability of user memories, Hamming codes are implemented as an ECC coding scheme. The functionally of our fault-tolerant design is verified by using both a simulation-based platform (ModelSim) and an on-board FPGA platform (ML605 development kit). To measure the fault-tolerant capabilities of the  $\rho$ -VEX core, saboteurs are used to artificially inject faults at various predefined locations in the core. The obtained results have shown that our design can mitigate all injected single faults in the pipeline and double faults in the caches, without triggering any failure. The dynamically configurable fault-tolerant feature is obtained at the cost of about 30% additional resource utilization and 20% reduction in the maximum operating frequency.

**Laboratory** : Computer Engineering

Codenumber : CE-MS-2018-16

Committee Members :

Advisor: Dr .ir. J.S.S.M. Wong, CE, TU Delft

Chairperson: Dr .ir. J.S.S.M. Wong, CE, TU Delft

Member: Dr. ir. A. van Genderen, CE, TU Delft

Member: Dr. A. Menicucci, SE, TU Delft

Dedicated to my family and friends

### Contents

| $\mathbf{Li}$ | st of          | Figures                               | ⁄ii           |

|---------------|----------------|---------------------------------------|---------------|

| $\mathbf{Li}$ | st of          | Tables                                | ix            |

| $\mathbf{Li}$ | st of          | Acronyms                              | cii           |

| A             | cknov          | wledgements x                         | iii           |

| 1             |                | oduction                              | <b>1</b><br>3 |

|               | 1.1<br>1.2     | Research question & thesis objectives | 3             |

|               | 1.3            | Thesis outline                        | 4             |

| 2             | Bac            | kground                               | 5             |

|               | 2.1            | FPGA                                  | 5             |

|               | 2.2            | The $\rho$ -VEX architecture          | 6             |

|               |                | 2.2.1 Exploiting parallelism          | 6             |

|               |                | 2.2.2 VLIW architecture               | 7             |

|               |                | 2.2.3 Soft-core processors            | 7             |

|               |                | 2.2.4 The $\rho$ -VEX processor       | 8             |

|               | 2.3            | 1                                     | 12            |

|               |                |                                       | 12            |

|               |                | 0 0                                   | 16            |

|               | 2.4            | 1                                     | 17            |

|               |                |                                       | 17            |

|               | ~ <b>-</b>     |                                       | 24            |

|               | 2.5            | Conclusion                            | 26            |

| 3             | $\mathbf{Des}$ |                                       | <b>27</b>     |

|               | 3.1            | 1                                     | 27            |

|               |                | 3.1.1 Processor architecture          | 27            |

|               |                | 0                                     | 28            |

|               | 3.2            |                                       | 29            |

|               | 3.3            |                                       | 29            |

|               | 3.4            | 0 1                                   | 30            |

|               |                |                                       | 30            |

|               |                | v                                     | 36            |

|               |                | v G                                   | 38            |

|               | 3.5            |                                       | 39            |

|               | 3.6            | Design verification                   | 40            |

|    |        | 3.6.1    | Fault injection method                     | 40        |

|----|--------|----------|--------------------------------------------|-----------|

|    |        | 3.6.2    | Fault injection locations                  | 41        |

|    | 3.7    | Conclu   | asion                                      | 41        |

| 4  | Imp    | olemen   | tation                                     | 43        |

|    | 4.1    | Fault-   | tolerant $\rho$ -VEX core                  | 43        |

|    |        | 4.1.1    | Majority voters & replication units        | 44        |

|    |        | 4.1.2    | EDAC implementation                        | 46        |

|    |        | 4.1.3    | Double error correction in caches          | 47        |

|    |        | 4.1.4    | Interaction between TMR and EDAC domains   | 48        |

|    |        | 4.1.5    | Reconfiguration                            | 49        |

|    | 4.2    | Design   | validation                                 | 50        |

|    |        | 4.2.1    | Saboteur                                   | 50        |

|    |        | 4.2.2    | Status monitoring registers                | 50        |

|    | 4.3    | Conclu   | ision                                      | 51        |

| 5  | Ver    | ificatio | on and Results                             | <b>52</b> |

|    | 5.1    | Test e   | nvironment                                 | 52        |

|    |        | 5.1.1    | Test platform                              | 52        |

|    |        | 5.1.2    | Test applications                          | 53        |

|    | 5.2    | Functi   | onal testing                               | 53        |

|    | 5.3    | Fault-   | tolerance verification                     | 58        |

|    | 5.4    | Cost a   | and overhead of fault-tolerance            | 60        |

|    |        | 5.4.1    | Additional hardware / Resource utilization | 60        |

|    |        | 5.4.2    | Timing results                             | 62        |

|    | 5.5    | Conclu   | asion                                      | 62        |

| 6  | Con    | clusio   | a                                          | 64        |

|    | 6.1    | Summ     | ary                                        | 64        |

|    | 6.2    |          | contributions                              | 65        |

|    | 6.3    |          | e work                                     | 67        |

| Bi | ibliog | graphy   |                                            | 73        |

## List of Figures

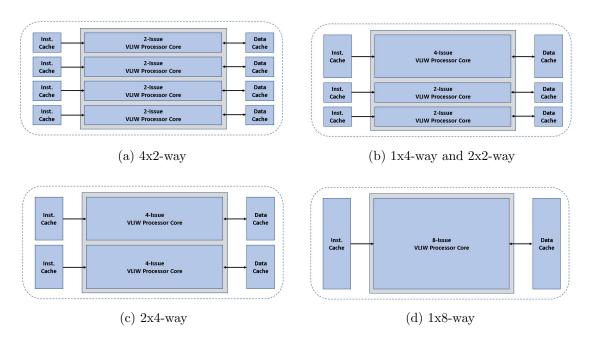

| 2.1        | $\rho$ -VEX configuration modes                                                                                                                                                                               | 10       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

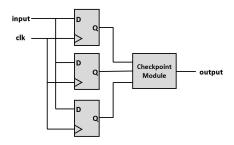

| 2.2        | TMR for flip-flop                                                                                                                                                                                             | 19       |

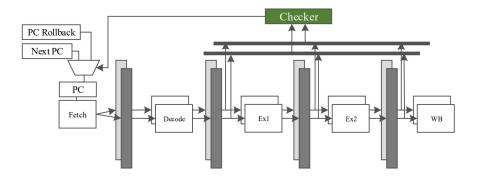

| 2.3        | DWC with comparison                                                                                                                                                                                           | 20       |

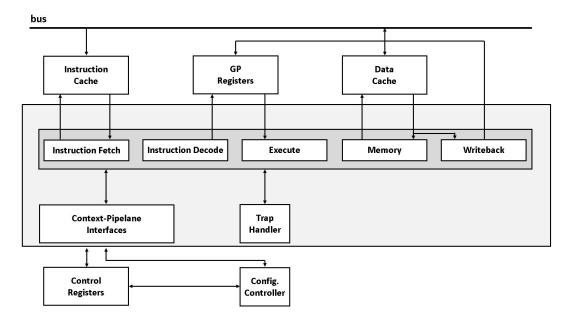

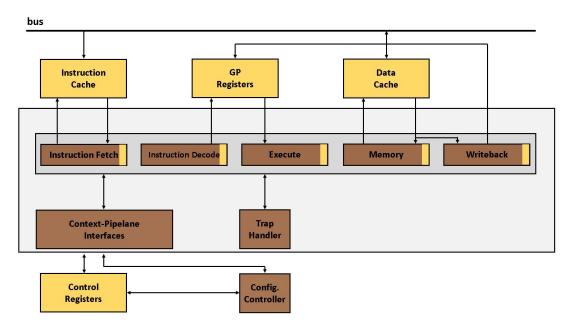

| 3.1<br>3.2 | Block level overview of $\rho$ -VEX along with caches Block level diagram indicating susceptibility to radiations (yellow color shows susceptibility to SEUs, while brown color shows susceptibility to SETs) | 28<br>30 |

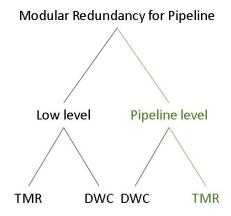

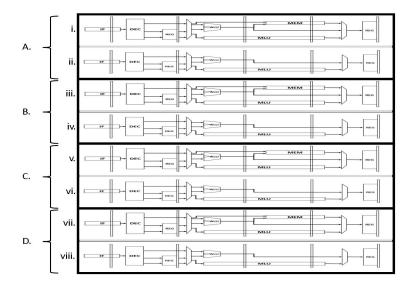

| 3.3<br>3.4 | Flow graph showing modular redundancy options at the pipeline level . $\rho\text{-VEX}$ pilelanes                                                                                                             | 32<br>33 |

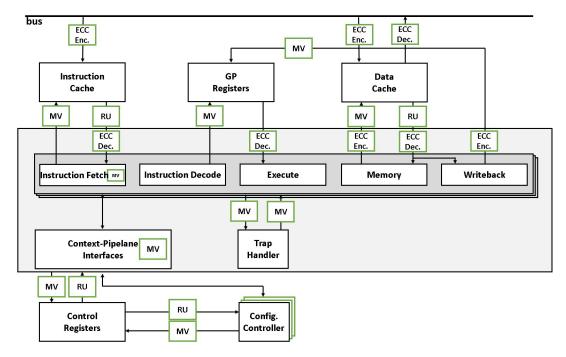

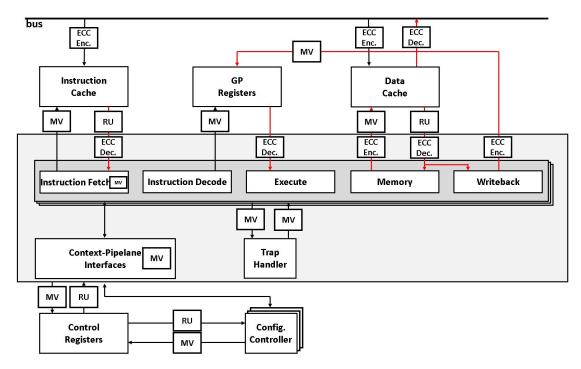

| 4.1        | Top-level block diagram of the fault-tolerant $\rho	ext{-VEX}$ core                                                                                                                                           | 43       |

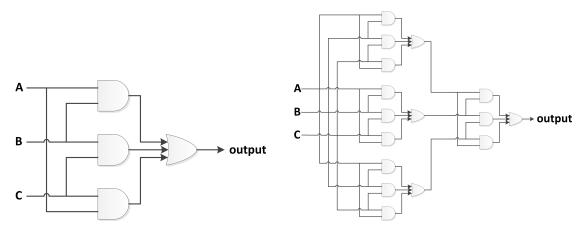

| 4.2        | 1-bit majority voter                                                                                                                                                                                          | 44       |

| 4.3        | Triplicated 1-bit majority voter                                                                                                                                                                              | 44       |

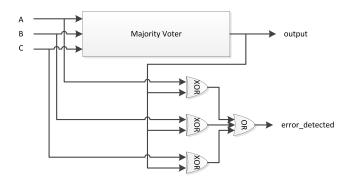

| 4.4        | Error detection logic for the majority voter                                                                                                                                                                  | 45       |

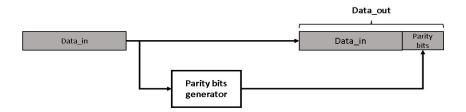

| 4.5        | Hamming code encoder                                                                                                                                                                                          | 47       |

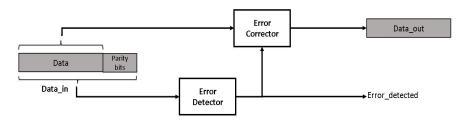

| 4.6        | Hamming code decoder                                                                                                                                                                                          | 47       |

| 4.7        | Double error correction mechanism for caches                                                                                                                                                                  | 48       |

| 4.8        | Interaction between TMR and EDAC domains                                                                                                                                                                      | 48       |

| 4.9        | Configuration word encoding for the fault-tolerant mode                                                                                                                                                       | 49       |

| 4.10       | $\rho$ -VEX in 8way non-fault-tolerant mode                                                                                                                                                                   | 50       |

| 4.11       | $\rho$ -VEX in fault-tolerant mode                                                                                                                                                                            | 50       |

| 4.12       | Block diagram of saboteur                                                                                                                                                                                     | 51       |

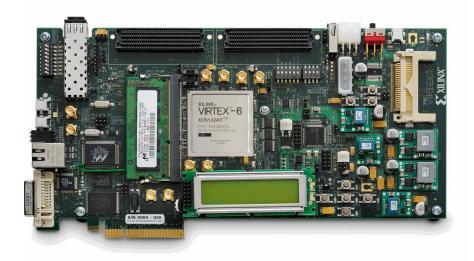

| 5.1        | ML605 - The FPGA development board used in this project                                                                                                                                                       | 53       |

| 5.2        | Part of an application showing how reconfiguration can be requested                                                                                                                                           | 54       |

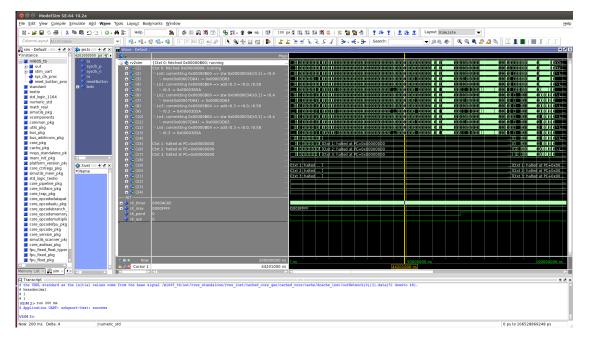

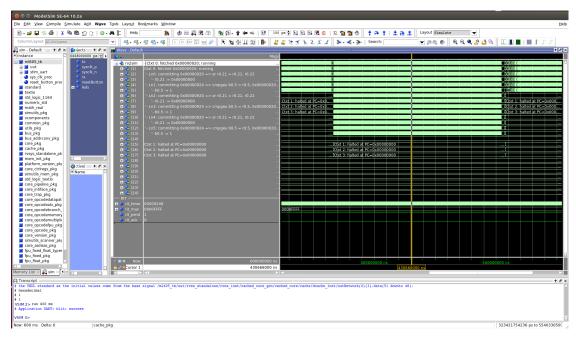

| 5.3<br>5.4 | Instantiation template used for the system                                                                                                                                                                    | 55       |

|            | a fault-tolerant mode and then back to the 8-way mode                                                                                                                                                         | 55       |

| 5.5        | Screenshot of ModelSim showing reconfigurations from 2-way mode to a fault-tolerant mode and then back to the 2-way mode                                                                                      | 56       |

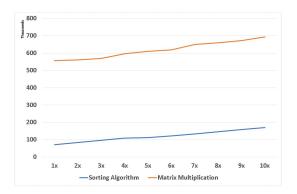

| 5.6        | Total overhead in terms of clock cycles when multiple reconfigurations are requested                                                                                                                          | 58       |

| 5.7        | Reconfiguration logic overhead in terms of clock cycles when multiple reconfigurations are requested                                                                                                          | 58       |

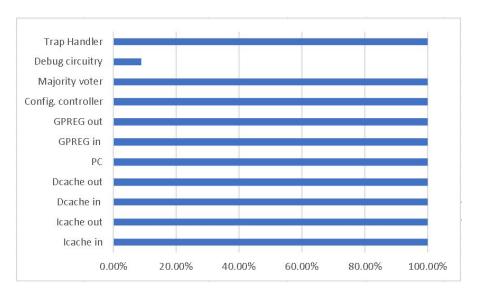

| 5.8        | The results from the fault injection tests showing the percentage of cor-                                                                                                                                     |          |

|            | rected faults                                                                                                                                                                                                 | 59       |

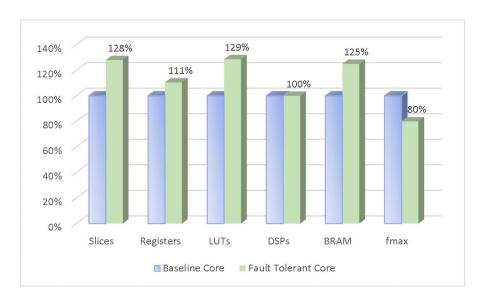

| 5.9        | The relative resource utilization                                                                                                                                                                             | 61       |

| 5.10       | The long delay paths in the fault-tolerant o-VEX core                                                                                                                                                         | 62       |

## List of Tables

| 2.1 | Design-time configuration parameters of $\rho$ -VEX processor       | 10 |

|-----|---------------------------------------------------------------------|----|

| 2.2 | Main sources of the space radiations                                | 14 |

| 2.3 | Listing of TID limits for Xilinx FPGAs                              | 14 |

| 2.4 | Truth table for checkpoint mechanism                                | 18 |

| 2.5 | SEC code parameters                                                 | 21 |

| 2.6 | SECDED / Hsiao code parameters                                      |    |

| 2.7 | BCH code parameters                                                 | 23 |

| 2.8 | RS code parameters                                                  | 24 |

| 3.1 | Synthesis results for the baseline $\rho$ -VEX softcore             | 29 |

| 3.2 | Comparison of TMR and ECC schemes (adopted from [1])                | 37 |

| 3.3 | Evaluation of various fault injection techniques                    | 40 |

| 4.1 | Truth table for the majority voter                                  | 45 |

| 4.2 | Specifications for the Hamming code                                 | 46 |

| 5.1 | Powerstone benchmark suite                                          | 54 |

| 5.2 | Active clock cycles taken by the benchmark suite                    | 57 |

| 5.3 | Resource utilization comparison of the original core and the fault- |    |

|     | tolerant core                                                       | 61 |

### List of Acronyms

ALU Arithmetic Logic Unit

ASIC Application-Specific Integrated Circuit

**BRAM** Block Random Access Memory

CMOS Complementary Metal Oxide semiconductor

**COTS** Commercial Off-The-Shelf

CPU Central Processing Unit

**DLP** Data-Level Parallelism

DRAM Dynamic Random Access Memory

**DWC** Duplication With Compare

**ECC** Error Correcting Code

**EDAC** Error Detection and Correction

**FF** Flip-flop

FPGA Field-Programmable Gate Array

**GF** Galois Field

GPU Graphics Processing Unit

**HDL** Hardware Description Language

IC Integrated Circuit

ILP Instruction-Level Parallelism

LCM Least Common Multiple

${f LEO}$  Low Earth Orbit

${f LUT}$  Lookup Table

PC Program Counter

SAA South Atlantic Anomaly

**SEC** Single Error Correction

SECDED Single Error Correction, Double Error Detection

**SED** Single Error Detection

**SEE** Single Event Effect

${\bf SEFI}$  Single Event Functional Interrupt

**SEL** Single Event Latch-up

${f SET}$  Single Event Transient

${f SEU}$  Single Event Upset

SIMD Single Instruction Multiple Data

SoC System on Chip

**SRAM** Static Random Access Memory

${f TID}$  Total-Ionizing Dose

**TLP** Thread-Level Parallelism

TMR Triple Modular Redundancy

VHDL Very High Speed Integrated Circuit Hardware Description Language

VLIW Very Long Instruction Word

**VLSI** Very-Large-Scale Integration

### Acknowledgements

First of all, I would like to thank my supervisor, Dr. Stephan Wong, without his help this work could not have been completed. His continuous guidance and support throughout the span of this thesis kept me motivated and committed. Additionally, I would also like to extend my gratitude to Jeroen van Straten who provided technical assistance and helped me in getting started with the project. Although he had a lot of work of his own, I could always drop by and ask for his help.

I also want to express thanks to my colleague and seniors that include Jacko, Omar, Imran and Nauman for their company as I could often visit them to have a little chitchat. Many thanks also go to the QCE Feestcommissie who kept organizing various social events and gatherings to help us remember that there's a whole world outside TU.

And finally, the most important one, I wish to thank my parents and siblings, without them I would never have come to the end of this master studies. They have been there for me since day one, and continue to be by my side no matter what.

MUHAMMAD USMAN SALEEM Delft, The Netherlands August 21, 2018

Introduction

Since the beginning of mankind, humans have felt a primordial urge to explore - to blaze new trails, map new lands, and answer profound questions about ourselves and our Universe. The quest to unravel the mysteries led to the launch of a first artificial satellite named Sputnik 1 in 1957 [2]. This successful launch, a remarkable achievement, thus began the space age, and since then, spacecrafts are being launched into and beyond the Earth's orbit. These robotic emissaries follow in the footsteps of their predecessors and are testaments to our long-lived desire to understand our place in the Cosmos. However, these space missions come with their own intrinsic challenges. The harsh space environment in which spacecraft operates poses many challenges to the spacecraft designers. The spacecrafts are subject to faults caused by equipment failure or environmental impacts, such as radiations, vibrations or temperature extremes. The anomalies introduced in the spacecraft electronics have been known since the very first day of space exploration [3] [4] [5] [6]. Therefore, to sustain the harsh environment of space, systems must be robust enough to operate reliably for the desired duration with little or no maintenance.

Space missions are subject to a heavy dose of radiations in the form of cosmic rays and the solar wind, exposing them to alpha particles, protons, heavy ions, X-rays and ultraviolet radiations. Interaction of these radiations with matter results in atomic displacement (rearrangement of atoms in a crystal lattice) or ionization, with the potential of causing soft errors which may lead to permanent or transient damage to the system. Soft errors are caused by transistors changing their state unintended due to significant amounts of energy disposed of by striking particles. Initially, only deep-space missions such as interplanetary missions were the main concern for such soft-errors as compared to missions close to Earth/Moon because they operate in relatively very high radiations enriched environment. Missions targeted at lower orbits were not very vulnerable because their operating environment has relatively low radiations. Larger footprints of transistor provided benefits to such low-Earth orbit missions in the sense that they could sustain a strike by a low energy particle. But with the advancement in technology, the transistor size is becoming smaller and smaller (Moore's law), which means the amount of energy required for a state change of transistor is also becoming smaller. Although, providing huger performance improvements, this decrease in the footprint of a transistor is making devices more vulnerable to radiation-induced faults. These effects were first reported in 1975 for ICs used in satellites in space [5]. Over the past years, the transistor size has further decreased so much, that nowadays soft errors are also being experienced at LEO satellites [7] and normal flight altitudes for civilian aviation [8]. Using older technology (larger transistor footprint) is not a very feasible option these days, as the demands for more advanced missions require more

computational ability and lower power consumption. Therefore, other solutions need to be explored to get rid of anomalies introduced by the radiations.

The radiation-hardened electronics components are available commercially in the market and can mitigate the effects of radiations to an extent. The problem with such solutions is that besides providing very limited options for customization, they are also highly expensive. For the last several years, we have observed an increasing trend in student satellites. Student satellite projects like AAUSAT4 from Aalborg University(Denmark), e-st@r-II from Politecnico di Torino (Italy), OUFTI-1 from University of Lige (Belgium), Delfi-C<sup>3</sup> and Delfi-n3Xt from Delft University of Technology (Netherlands) are few examples in this regard [9] [10]. All such satellite projects usually share a common problem of funding and limited resources. Use of expensive radiation-hardened components is not a very feasible option. Therefore, low-cost COTS are preferred for these projects. The issue with such low-cost solutions is that they come with limited reliability assurance. Therefore, there is a high need for non-expensive solutions that can be trusted for their reliability in a harsh space environment.

Traditionally, many space-based applications use microprocessors for on board processing as the development of software is relatively less expensive. In 1977, the RCA 1802 was the first microprocessor selected for spaceflight when it was used for the Galileo probe mission to Jupiter [11] [12]. Since then microprocessors are considered an integral part of most space missions. For most applications, the performance of a modern CPU is sufficient, but for real-time computationally intensive applications, microprocessors alone are not enough. Customized application specific hardware is a way to go for such applications. FPGA, a reconfigurable chip used for designing dedicated hardware for computationally intensive tasks, provides a more appropriate platform for such applications. They can provide solutions in an order of magnitude faster than the software algorithms developed for commercial general purpose microprocessor. In addition to providing high-performance gain, FPGA also offers benefits of allowing in-orbit customization (design changes), which helps in correcting errors or updating system design in order to cope with new missions requirements after launch. All these attributes make FPGA an attractive option for the remote space missions.

Specialized designs on FPGA often include a softcore, a customized CPU that based on its design can possess reduced or extended functionality of a commercial microprocessor. Today, there are multiple softcore processors available in the market, developed by open source communities and (large) companies. Open source softcores provide the user more possibilities for modification or customization of the core as source files of the design are available. However, the softcores developed by companies are often proprietary and expensive licenses are required to use them. Regardless of the source of these softcore processors, if these are intended to be used in space missions, these must possess the ability to sustain the harsh environment and handle soft errors, as any lapse might lead to a mission failure.

The  $\rho$ -VEX, a dynamically reconfigurable softcore processor, is developed by Com-

puter Engineering department of the Delft University of Technology(Netherlands). It is an open-source VLIW based processor. The distinguishing feature of  $\rho$ -VEX is its ability to adapt itself to available ILP and TLP to utilize the available computational resources more efficiently. The goal of this thesis is to modify the softcore such that it can handle soft errors for future opportunities in the high safety and security-critical domain, and provide student satellites a reliable option as an alternative to expensive solutions. This document will describe the way in which the fault-tolerant attribute of  $\rho$ -VEX is designed, implemented and verified.

#### 1.1 Research question & thesis objectives

In this work, the existing design of  $\rho$ -VEX softcore is taken as the starting point and efforts are put to make it fault-tolerant. To be developed variant of this softcore is targeted at high safety and critical space-based applications, such that correct execution flow could not be influenced by single event effects without such anomalies being detected. The research question/problem statement can be formulated as:

How can the  $\rho$ -VEX softcore be extended so that it becomes a reliable option for space-based critical missions?

Based on the problem statement, thesis objectives are defined as:

- The design must be able to detect and correct errors in the execution stages of  $\rho\text{-VEX}$ .

- The design must make on-chip memories robust against soft-errors.

- The design must be dynamically (runtime) reconfigurable.

- The design must be implemented on an FPGA while taking platform independence into account.

- The design must be verified for its correctness.

#### 1.2 Methodology

A research methodology is defined to find a solution for the proposed research question and to achieve the thesis objectives. This methodology is specified as follows:

- Investigate the possible causes and impacts of single event effects in soft-cores.

- Investigate existing solutions for the mitigation of single event effects.

- Explore the  $\rho$ -VEX platform to analyze possible and feasible solutions.

- Implement the most suitable solution in a modular and efficient way

- Verify the implemented functionality comprehensively using conformance tests in simulation and benchmarks in hardware for its correctness

- Analyze the results of the implementation.

- Propose recommendations for future development of the implemented solution.

#### 1.3 Thesis outline

The thesis is organized in the following way:

Chapter 2 provides the background knowledge required for this thesis. It provides details about the  $\rho$ -VEX platform and describes its distinguishing features. Details about space environment and its impact on electronics are also provided. Based on these impacts and their causes, different solutions to mitigate their effects in processors are discussed. Lastly, methods for verification of fault-tolerant systems are investigated.

Chapter 3 analyses the architecture of the baseline processor for its susceptibility to radiation-induced faults. It then performs a comparative analysis of various available options to explore their reliability and suitability for our design. Fault mitigation techniques for pipeline stages and memory elements are evaluated and best-suited options for our platform are identified. After finalizing the entire design, fault injection mechanism is selected from different possible options to validate the desired functionality of our design.

Chapter 4 provides the implementation level details of the fault-tolerant design. After providing a high-level description of the design, it explains the design of each basic building block added to make the core robust. Finally, this chapter discusses the implementation of fault injection mechanism and the addition of status-monitoring registers to thoroughly validate the core functionality and fault-tolerant behavior.

Chapter 5 deals with the verification of our design and presents the results associated with the fault-tolerant core. It provides details about the platforms and benchmark used to check the correctness of the design. Statistics of fault injection tests are also discussed in the chapter. Besides testing the functionally of the core, the results of synthesis are also presented as they provide an indication of the cost of the design and its performance.

Finally, the chapter 6 summarizes the whole thesis, presents the main contributions and lists recommendations for the future work.

Background

This chapter details the background knowledge required for this thesis. In Section 2.1, a brief overview of FPGA will be provided, and in Section 2.2, the details of the processor platform that is used in this thesis, i.e.,  $\rho$ -VEX will be provided. Its implementation, features, configuration modes and working will be discussed. Afterwards, in Section 2.3, details about the space environment and how it induces anomalies in electronics especially in processors will follow. Subsequent sections will then deal with mitigation techniques found in the literature to make processors robust for space missions, and finally, various methods to validate the resilience of fault-tolerant systems will be discussed.

#### 2.1 FPGA

Knowledge of the underlying architecture is helpful in understanding both how the user design is implemented and how the space environment can it. As an FPGA platform is used for this thesis project, it is helpful to present its overview first. Field-programmable gate arrays (FPGAs) are configurable integrated circuit based on a high logic density regular structure, which can be customized by the end user to realize different designs [13]. It can support designs varying from simpler logic gates (AND, OR etc) to much complicated designs such as processors. The circuitry of an FPGA contains two-dimensional arrays of logic blocks and interconnects. Logic blocks are programmed to implement some functionality, while interconnects are programmed using switch boxes to establish connections among these logic blocks. The name "Field Programmable" comes from the unique attribute of FPGA that end-user can configure it after its manufacturing. Based on the technology by which design data is stored on FPGA, they can be divided into various categories that include SRAM-based, flash based and antifuse-based FPGA.

FPGA fills the performance gap between application-specific integrated circuits (ASICs) and general purpose processors. ASICs are the fastest processing elements for computationally intensive workload and can utilize a lot of parallelism. They are tailored especially for some target workload. However, the problem with ASICs is that they are only economical if produced in bulk quantity, otherwise they provide a very expensive solution. On the other hand, general-purpose processors provide an easy and relatively inexpensive solution, as building software is comparatively easy and economical. But the performance of such processors is constrained by the inherent sequential nature of software that runs on them. FPGA provides the parallel nature of ASIC along with the ease of implementation of software. They can provide relatively high performance as compared to microprocessors for compute-intensive applications. Moreover,

few classes of FPGA (e.g., SRAM, flash based) also possess the distinguishing feature that circuit design on them can be reconfigured multiple times. This re-programmable nature of FPGA makes it very suitable for space-based missions, as besides providing application specific hardware, it can also be reconfigured during the mission to remove any anomalies or design faults, and new design can also be added to cope with changing mission requirements.

Design to be implemented on FPGA can be created in various ways. This could be schematic based, hardware descriptive language (HDL) based or combination of both. Most commonly used HDLs are VHSIC hardware description language (VHDL), Verilog and SystemC. Selection of a design method and HDL is a designer's prerogative. The  $\rho$ -VEX, a soft-core processor platform that will be used in this thesis work is written entirely in VHDL. Therefore, to maintain the consistency, new design to turn existing one into a fault-tolerant design is also implemented in VHDL.

#### 2.2 The $\rho$ -VEX architecture

The processor platform that is used in this work is  $\rho$ -VEX. It stands for reconfigurable VLIW example (VEX). Its architecture is based on VEX, i.e., the example architecture from the book "Embedded computing: a VLIW approach to architecture, compilers and tools" by Joseph A. Fisher, Paolo Faraboschi, and Cliff Young [14].  $\rho$ -VEX is a VLIW based soft-core processor that has been developed to exploit parallelism in an application to achieve better performance. Before explaining it further in detail, there are a few concepts that need to be understood. Considering that, subsequent sections will provide a brief overview of various types of computational parallelism, VLIW architectures and softcore processors, followed by the design, features, and working of the  $\rho$ -VEX processor.

#### 2.2.1 Exploiting parallelism

In the domain of processors, parallelism refers to the opportunities in an application to find independent operations and execute them simultaneously rather than running sequentially. Exploiting parallelism in an application can increase its performance manifold times and this increase in performance is proportional to the degree of parallelism found in the application. In this section three widely known parallelism mentioned in [15] are discussed:

#### Instruction-level parallelism

Instruction-level parallelism (ILP) refers to the existence of independent instructions in an application program. These independent instructions can be run simultaneously with other instructions in the same clock cycle. The amount of ILP that can be extracted from an application depends on the data dependencies and branches present in the instruction stream. Super-scalar and VLIW architectures are the platforms that exploit ILP in an application. In case of VLIW processors, finding independent instructions is the job of a compiler, while in case of super-scalar processors dedicated run-time control hardware is responsible for it. ILP can also be combined with any other type of

parallelism to further complement the performance gain.

#### Data-level parallelism

Data-level parallelism (DLP) refers to distributing the data across different computing nodes and executing them in parallel. These different computing nodes receive a small chunk of data and perform the identical operation on it in parallel, and the results are then combined to get a single finalized result. Single instruction multiple data (SIMD) is a form of DLP as it exploits parallelism in a data stream. Graphics processing unit (GPU) is another example that exploits DLP.

#### Thread-level parallelism

Thread-level parallelism (TLP) refers to executing multiple tasks of an application in different threads of a multi-threaded system or in different cores of a multi-core system. Multi-core systems can have multiple homogeneous or heterogeneous processing elements on which subprograms of a bigger program can be run simultaneously to exploit parallelism and get better performance. These subprograms can either communicate with and wait for each other, or they can also run completely independent of each other.

#### 2.2.2 VLIW architecture

Processors based on a very-long instruction word (VLIW) architecture exploits ILP to get better performance. VLIW architecture contains multiple independent functional units that are capable of executing multiple instructions in parallel. By packing multiple instructions in a single long instruction word, these instructions can be executed in parallel in the same clock cycle to take advantage of ILP and reduce the overall execution time of an application. The maximum number of instructions that can be packed in a single instruction word and are supported by a given VLIW based processor is known as an Issue-Width.

Finding data dependencies and packing of independent instructions in an instruction word is done at the compile time and thus in VLIW architecture, the code is statistically scheduled. The burden of scheduling the instructions lies on the compiler and is done only once. This behavior is better off in both energy and logic area of a processor as compared to other platforms that do dynamic scheduling, e.g., superscalar processors. The downside of a VLIW processor is that the code is compiled for a specific issue width and it cannot run on a different issue width. It needs to be recompiled for a different issue width. Furthermore, in practice, the full issue-width cannot always be used as it is limited by the level of dependencies present among the instructions. It is the responsibility of the compiler to schedule instructions as efficiently as possible with the help of various scheduling algorithms.

#### 2.2.3 Soft-core processors

Embedded systems based on soft-core processors are becoming very popular these days. A soft-core processor is a microprocessor that can be fully implemented in logical primitives of an FPGA and it provides the user a substantial amount of flexibility in design through the configurable nature of an FPGA.

When designing some complex embedded system using an FPGA, quite often we need some kind of processor to handle various system tasks. One way is to use commercial-off-the-shelf (COTS) microprocessor and mount it on the same board with FPGA and use some standard interface to communicate with FPGA. This is a viable option and most commonly used, but it comes with few limitations. For example, an application that needs some additional peripheral functionality that a COTS microprocessor do not provide, can not benefit from this discrete solution.

The other option is to embed the hardcore processor on the chip, which means it gets dedicated silicon on the chip. This allows the processor to run at the same frequency as it would run in a discrete way and theoretically provides the same level of performance. Many such solutions exist in the market nowadays. One example is Zynq-7000 SoC family. Zynq-7000 devices come with dual-core ARM Cortex-A9 processors integrated with Artix-7 or Kintex-7 based programmable logic for better performance and maximum design flexibility[16]. However, the issue with hard processors is that they can not be customized to better meet the needs of a particular system.

Soft-core processors, on the other hand, provides user much flexibility of design. They can entirely be implemented on an FPGA. The user, as per the requirements of its system, can make the design which has reduced or extended functionality than a hard processor. However, these soft-core processors also have few constraints. Because of the implementation in reconfigurable logic, they do not beat hard processors in operating frequency and run at a relatively lower frequency. In fact, they can not beat the performance, area, and power of hard-core processors, but still, for many embedded applications, soft-core processors are a preferred option, e.g., the applications which prefer expanded functionality over increased frequency. Soft-core provides a low-cost solution and can also be re-targeted to a new technology without much effort. Few examples of soft-core processors are LEON3, MicroBlaze, and OpenRISC. Many major FPGA vendors also provide soft-core processors in their product offerings.

#### 2.2.4 The $\rho$ -VEX processor

The  $\rho$ -VEX is a softcore processor based on VLIW architecture. It is a 32-bit big endian architecture. The distinct feature of  $\rho$ -VEX is that its architecture is designed such that the key metrics that include the issue width and the number of available multiplication units are configurable. This feature allows the processor parameters to be tailored to suit the ILP and arithmetic instruction mix of a certain application once the software is available. The need for  $\rho$ -VEX arose because the existing VLIW based softcore processors, e.g., [17] [18] [19] suffered from one of the following drawbacks [20]:

- Either compiler or processor design is not open source

- Toolchain lacks in good support

- Limited options for parametrized customization or extension

To overcome all these shortcomings,  $\rho$ -VEX was introduced in [21]. It is developed entirely by the students and Ph.D. candidates of the TU Delft. Over the period of time, there have been many revisions of it. However, for this thesis work, the latest version of

$\rho$ -VEX has been used.

Let us here introduce some terminology that will be used very often in this thesis in reference to  $\rho$ -VEX. As it is a VLIW processor, this means that each instruction can specify multiple independent operations. Such operations are called *syllables*, a full instruction is called a *bundle*. The part of a VLIW processor that executes a syllable is called a lane (also referred as pipelane in this thesis). It contains computational resources to execute a syllable. The use of word *instruction* in this thesis may be used for either a bundle or a syllable, depending on the context. A VLIW processor capable of executing n-syllables per cycle is referred as n-way VLIW processor and the number of lanes running together as a part of a single processor are known as *issue width* of the processor.

#### Reconfigurability

The  $\rho$ -VEX is a parametrized processor that can be configured at design time and reconfigured at run-time. It must be noted here that this is not an FPGA reconfiguration, which means that we don't need to reconfigure and load the bitstream every-time we request reconfiguration. Here reconfiguration means a process within the system described by a single FPGA bitstream. There is no full or partial reloading of bitstream required. All resources required to do the switching are inferred from the hardware description, and the overhead of reconfiguration is mere pipeline flush.

The distinguishing feature of  $\rho$ -VEX is its ability to adapt itself to available ILP and TLP to utilize the available computational resources more efficiently. It can do so by dynamically changing the mapping between threads and issue slots. Though the total number of pipelanes are fixed, pipelanes can be distributed among different programs running in parallel, and this redistribution can be done at run-time. The core can behave as a large VLIW processor when high ILP is available, or in case of high TLP, it can behave as multiple smaller VLIW processors.

The default configuration of  $\rho$ -VEX consists of eight execution lanes called pipelanes. Not all of these pipelanes can be separated and operated independently. At least two consecutive pipelanes, often referred as lanepairs, must run together. minimum configuration that  $\rho$ -VEX can achieve is a 2-way (often referred as 2-issue) configuration. Figure 2.1 depicts various configuration modes of  $\rho$ -VEX. The core can be split up to four smaller cores (2-way) as depicted in Figure 2.1a or it can run as a single larger core (8-way) as depicted in Figure 2.1d. If an application has high ILP then to get better performance and utilize the available resources more efficiently, the core is run in full 8-way configuration, executing up to eight independent instructions in parallel. On the other hand, if an application has high TLP and lesser ILP, then running core in full mode will not provide a performance increase. Additionally, it will also be a wastage of available resources. Therefore for such scenario, the core has the ability to split up to four smaller 2-way VLIW cores, that can run four threads independently in parallel to each other resulting in increased performance. Each independent thread has its own state, called a *context*, consisting of the register files, PC, and other control registers. The core can also be reconfigured into two 4-ways cores (2.1c or one 4-way and two 2-way cores (2.1b, if required.

The parameters that can be configured at design time are listed in Table 2.1 [20].

Figure 2.1:  $\rho$ -VEX configuration modes

Table 2.1: Design-time configuration parameters of  $\rho$ -VEX processor

| Resources        | Parameters                                         |

|------------------|----------------------------------------------------|

| General          | Issue width, Number of hardware context            |

| Functional units | Number, Type and location, Support operations      |

| Register file    | Register file size                                 |

| Interconnect     | Presence of forwarding logic, memory bandwidth     |

| Caches           | Presence of caches, cache size and cache line size |

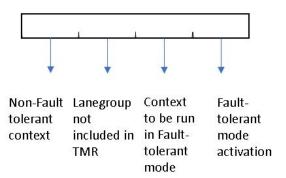

#### Configuration word encoding

The encoding for the value that is written to the reconfiguration register is called configuration word. The size of configuration word is at most 32-bits, but in the current version of  $\rho$ -VEX, only least significant 16 bits are required to describe the configuration. The encoding is done in hexadecimal form. Each lane group (pipelane pair) of  $\rho$ -VEX is mapped to a nibble (four bits). The three least significant bits of each nibble specify the context it needs to be connected if the fourth most significant bit is zero, or a special mode if it is one. At this point, the only special mode defined is disabling the lane group, and it corresponds to nibble 8. Values 9 through F are reserved for future work.

An example would explain the configuration word encoding better. Consider an eight-way  $\rho$ -VEX with four lane groups and four contexts. 0x0000 then specifies a 1x8 lane configuration, with eight lanes working on context 0. 0x3210 specifies a 4x2 lane configuration, with first lane pair working on context 0, second on context 1, third on context

2 and fourth on context 3. 0x0013 specifies a 1x4 and 2x2 way lane configuration, with four lanes working on context 0, two lanes working on context 1 and two lanes working on context 3. 0x8800 would map to a 1x4 way configuration with four lanes running context 0 while remaining four lanes are deactivated or in power-down mode.

One must be careful when requesting a reconfiguration as not all the possible nibble combinations are valid. Following guidelines must be followed:

- Any context should be mapped to the power of two contagious lane groups. For example, 0x2030 and 0x8111 are invalid configuration words because these do not follow this rule.

- The nibble in configuration word can take value from zero to the number of hardware contexts minus one in order to map to a context. Nibble 8 is an exception which is explained earlier. Configuration words 0x 7711 is invalid for a configuration with four hardware contexts. Besides 8, the maximum nibble value that can be taken in this scenario is 3.

- The nibble in the configuration word corresponding to the non-existent lanegroups should be set to zero. For example, for a configuration with four hardware contexts, 0x00008210 is a valid configuration but 0x88888210 is not.

- A set of lane groups assigned to a single context should be aligned properly. For example, 0x0110 is invalid while 0x0011 is a valid configuration word.

#### Requesting a reconfiguration

There are three ways in which a reconfiguration of  $\rho$ -VEX processor can be requested.

- Writing new configuration word to the *context control register* (CRR) from a program running on the core.

- Writing new configuration word to the bus reconfiguration request (BCRR) global control register from the debug bus. This mechanism is similar to the first, except it is triggered externally, from outside the core.

- Using the sleep and wake-up system of the  $\rho$ -VEX. This involves writing new configuration word to wake-up configuration (WCFG) register and setting the flag in sleep and wake-up control (SAWC) register.

Usually, the new configuration is committed within something in the order of ten of cycles after its request, depending on how long it takes the configuration controller to pause and store the state of affected contexts. Reconfiguration can also be rejected sometimes. The reasons for the rejections can be following:

- Another context or the debug is requesting a new configuration simultaneously. The intended context might lose arbitration in this case.

- Configuration word does not comply with the encoding guidelines and is rejected.

#### 2.3 Space environment

Anomalies in the spacecraft electronics have been known since the very beginning of space era. Space environment is a critical scenario for electronics in the sense that it contains a massive amount of radiations, and remote maintenance of space electronics is also not a feasible option in most of the cases. There are mainly two reasons that induce faults in electronic circuits namely radiations and device aging [22].

#### 2.3.1 Radiation effects

The one prominent feature that distinguishes the space environment is the presence of huge amount of radiations. Radiation can be defined as energy in transit in the form of high-speed particles and electromagnetic waves[23]. Radiations can be divided into two categories: ionizing and non-ionizing

- Ionizing radiations are radiations that possess enough energy to remove electrons from the orbits of atoms, resulting in charged particles. Examples include gamma rays, neutrons, and protons. Effects of ionizing radiation are different than normal ions formation that happens in an ordinary chemical reaction, such as the formation of table salt from Sodium and Chlorine. In such reactions, electron(s) is(are) released from outer most orbit to form a positively charged ion. While in case of ionizing radiations (if energy is sufficient), electrons from the inner orbits can be released, resulting in a very unstable atom which is highly chemically reactive.

- Non-ionizing radiations are radiations that do not possess sufficient energy that is required to remove electrons from their orbits. Examples are visible light, radio waves, and microwaves. Such radiations are not a concern for electronics equipment.

Space radiations are mainly ionizing radiations which contain highly energetic charged particles. Three naturally occurring sources of space radiations are trapped radiations, galactic cosmic radiations, and solar particle events [23].

#### • Trapped radiations

The Sun releases a stream of charged particles, known as solar wind, out into the space. The intensity of it depends on the amount of activity on the surface of Sun. This solar wind contains ions of many elements, however, the major chunk is of protons and electrons. When these particles tend to penetrate in Earth's atmosphere, Earth's magnetic field provides a hindrance to it. Earth's magnetic field is produced because of the rotation of Earth's iron core and it extends thousands of kilometers from Earth's interior out into the space. Most of the charged particles get deflected by the Earth's magnetic field, however, some become trapped in it. They are contained in one of the two magnetic rings surrounding the Earth commonly known as Van Allen radiation belts. The inner belt, extending from an altitude of about 1,000 to 8,000 miles, contains high concentration of electrons (hundreds of keV) and energetic protons (hundreds of MeV), while outer belt, extending from 12,000 to 25,000 miles, contains mainly

high energy electrons (0.1-10 MeV) [4][24].

Apart from the Apollo missions, NASA's manned spaceflight missions have stayed well below the altitude of the Van Allen belts[23]. However, there is an area where a part of inner Van Allen belt comes really close to Earth's surface, dipping down to an altitude of about 200 km. It is known as south atlantic anomaly(SAA) and is caused by the non-concentricity of the Earth and its magnetic dipole. This is the region where Earth's magnetic field is weakest relative to an idealized Earth-centered dipole field, which leads to an increased concentration of energetic particles in it. The largest part of radiation exposure to spaceflight missions occurs in SAA. Lower earth orbit flights traverse a portion of SAA six or seven times a day[23].

#### • Galactic cosmic radiations

Galactic cosmic rays (GCR) are highly energetic background source of energetic particles that constantly bombard the Earth. They originate outside the solar system, very likely from the explosive events like supernova. These high energy particles consist of ionized atoms ranging from Hydrogen (accounting for 89% of GCR spectrum) to Uranium [25]. These particles travel at the large fractions of the speed of light and have tremendous energy. Earth's magnetic field provide shielding for spacecraft for most of GCR, however, they have access over the polar regions where the magnetic fields are open to interplanetary missions[23].

#### • Solar particle events

Solar particle events (SPE) are injections of high energetic particles emitted by the Sun into interplanetary space. These particles include mainly protons, electrons and alpha particles. SPE occurs when the particles emitted by the Sun become accelerated either close to the Sun during a solar flare (highly concentrated, explosive release of energy) or in interplanetary space by coronal mass ejection (huge bubbles of plasma threaded with magnetic field emitted by the Sun) shocks. These particles impose significant operational constraints on space missions. Storm shelters with a significant amount of shielding are required to lower the radiation dose to tolerable levels for astronauts, and the critical equipment sensitive to such high dose need to be turned off to avoid soft errors or other radiation-induced damages [26].

The effects caused by the space radiations on the spacecraft depend on its orbit and the source of radiations. Energy level of main components that constitute the space environment mentioned in [3] are presented in Table 2.2.

The particles hitting the space electronics can either result in temporarily change in the behavior of some circuit (a soft error) or they permanently damage the circuit (a hard error). Two most widely known radiation effects on spacecraft electronics mentioned in [27] are TID and SEEs.

| Radiation belts      | Electrons        | eV - 10 MeV                         |

|----------------------|------------------|-------------------------------------|

|                      | Protons          | $\mathrm{keV}$ - 500 $\mathrm{MeV}$ |

| Solar flares         | Protons          | $\mathrm{keV}$ - 500 $\mathrm{MeV}$ |

|                      | Ions             | 1 to a few 10 MeV/n                 |

| Galactic cosmic rays | Protons and ions | Max flux at about 300 MeV/n         |

Table 2.2: Main sources of the space radiations

#### 2.3.1.1 TID

For long space missions or missions for extremely high radiations environment, such as interplanetary missions, accumulation of ionizing particles over the period of time could cause failure of components/FPGAs. This accumulation of ionizing radiation in electronics is referred as the total-ionizing dose (TID).

The amount of radiations which a particular component gets depend on a number of factors: orbit, duration of the mission, placement inside the spacecraft and the amount of outer shielding around the spacecraft. A short mission in the low-Earth orbit might only expose the FPGAs to 1-5 krad per year, while a mission to Jupiter might accumulate 10-100 krad per week [27]. This accumulation of ionizing radiation causes degradation in transistors. As mentioned in [28], the oxide trapped charges lead to a decrease in the threshold voltage of the n-channel transistor and cause an increase in the case of the p-channel transistor. This threshold voltage (the minimum voltage that is required to turn on the device) is a crucial factor in determining characteristics of a transistor and corrupting its value can entirely change the behavior of circuitry.

Different types of FPGAs can withstand a different dose of TID before the components failures. Table 2.3 lists TID tolerance limit for Xilinx FPGAs provided in [27]. Mitigation against TID will not be discussed in this thesis further and it is proposed that FPGA selection must be done carefully as per the mission needs, to avoid any TID based anomalies.

| Table 2.3:    | Listing   | of TID  | limits f                             | or Xiliny | FPC As                  |

|---------------|-----------|---------|--------------------------------------|-----------|-------------------------|

| Table $z.5$ . | 1.1861119 | 01 1117 | 111111111111111111111111111111111111 | OF A HIHX | $\Gamma \Gamma \Box AS$ |

| FPGA       | TID limit |

|------------|-----------|

|            | krad      |

| Virtex     | 100       |

| Virtex-II  | 200       |

| Virtex-4   | 250       |

| Virtex-5   | 340       |

| Virtex-5QV | 1000      |

| Virtex-6   | 380       |

#### 2.3.1.2 Single event effects

SEEs are unintended effects caused by the interaction of a single ionizing, energetic particles with electronic components. These ionizing particles can be primary, like heavy ions and alpha particles or secondary, created by a nuclear reaction of a particle with silicon or any other atom of the die. SEEs occur when the accumulation of charge liberated by the ionizing particles become more than the electric charge stored on a sensitive node [29] (a node in a circuit whose electric potential can be changed by accumulation or internal injection of electrical charges).

SEEs induced by the deposition of energy from ionizing particles can either by non-destructive or destructive, based on their effects. Non-destructive SEEs are transient effects and a device can be recovered by resetting or reconfiguring, while, destructive SEEs are permanent in nature and have a persistent effect even after resetting or reconfiguring the device [22]. Four widely known single event effects are SEL, SEU, and SET. [27].

#### • SEL

Single event latch-up (SEL) is a radiation-induced version of latch-up <sup>1</sup>. It affects the behavior of parasitic thyristors in CMOS technology. A single energetic particle can switch PNPN structures from high impedance state to a low impedance state, which causes an abnormal amount of current flow through the sensitive regions of the device structure causing it to lose its functionality. This current increase happens in a very small period of time (milliseconds) making to difficult to detect the current increase before the component gets damaged. In some cases, components retain some partial functionality after the event, but most components do not function at all after the event [27]. All CMOS components have a potential for SEL sensitivity.

FPGAs provided by all the main manufacturers these days are latch-up immune. Xilinx and Microsemi have published reports verifying latch-up immunity in high radiation environment[30, 31]. In back days, Altera devices had very low SEL immunity and, therefore, was not recommended for space-based applications[32] but now modern SRAM based Altera devices such as Stratix-IV possesses very high SEL immunity[33]. By careful selection of FPGA, single event latch-ups can be avoided, so they will not be discussed further in this thesis.

#### • SEU

Single event upsets (SEUs) are anomalies caused in the memory cells because of radiations. The susceptibility to SEU depends on the type of memory elements (SRAM, DRAM etc). For SRAM-based FPGAs, SEU corrupts the values stored in [27]:

- LUTs

- Routing

- On-chip SRAM

$<sup>^1</sup>$ Generation of a low-impedance path in CMOS chips between VDD and GND due to the interaction of parasitic PNP and NPN bipolar junction transistors

#### - User flip-flops

If it is the dynamic data that gets corrupted in on-chip SRAM or user flip-flops, then this corrupted value will be overwritten. In case, routing logic or LUT gets affected, then it will not recover on its own. SEU will remain persistent until or unless that part is reprogrammed via on-line or off-line reconfiguration.

#### • SET

Single event transient (SET) is a voltage pulse in a combinatorial logic, that gets introduced by a single ionizing particle strike. This voltage pulse results in an erroneous data propagating through the circuit. Unlike SEUs, measuring SETs in SRAM based FPGAs is a challenging task. SET cross-section is 10-1000 times smaller than the SEU cross-section of the reconfigurable fabric[27]. The cross-section is a measurement of the sensitivity to SEU or SET from heavy ions and protons. Dealing with SETs is more challenging as it is observed that even in modern SEU immune FPGAs, such as Mircrosemi ProASIC3 and Xilinx Virtex-5QV, the reconfigurable fabric and input/output blocks are SET sensitive[27]. For SRAM based FPGAs, PLLs and multipliers are SET sensitive.

#### 2.3.2 Aging effects

Aging effects can incur in all electronics regardless of the environment in which they operate. The reason these aging effects get more serious attention for long-lasting space missions is that system maintenance or substitution of some faulty component is very difficult and in many cases, not possible at all. Errors induced because of the aging are permanent in nature and their four main causes mentioned in [34] are TDDB, EM, NBTI, and HCE.

#### • TDDB

Time-dependent dielectric breakdown (TDDB) is reduction in the gate oxide thickness caused by the trapping of charges in the oxide that creates an electric field.

#### • EM

Electromigration (EM) is development of void in metal lines caused by heavy current densities over a period of time.

#### • NBTI

Negative bias thermal instability (NBTI) is an increase in threshold and consequent decrease in drain current and trans-conductance in MOSFETs, caused by interface traps and some preexisting traps located in the bulk of dielectric.

#### • HCE

Hot-carrier effects (HCE) is a creation of traps at the oxide surface, affecting the I-V characteristics of a transistor caused by electrons trapped in the oxide.

These aging effects for a spacecraft mission can be avoided or greatly reduced by carefully selecting the components/FPGAs, which can tolerate such effects throughout the lifetime of the mission. Mitigation and tolerance against such age-related anomalies will not be covered in this thesis and is declared out of scope for this thesis work.

#### 2.4 Fault-tolerance in processors

Microprocessors are very important components for space missions as they control lifesupport equipment, navigation, on-board processing and data handling. Their failure can have catastrophic consequences. Therefore, before sending them into space, it must be made sure that they can sustain the space environment and operate reliably in it.

#### 2.4.1 Fault mitigation techniques

For a harsh radiation environment like space, mitigation techniques must be employed to protect softcore processors from SEEs. These mitigation approaches can be broadly categorized in two ways: software based and hardware based fault-tolerance.

#### Software based:

Software-based fault-tolerance techniques provide less expensive and more flexible solutions. They are becoming more popular following the race in satellite miniaturization and trending use of COTS in space applications. In such cases, redundancy in hardware in either not possible or not a feasible option, thus software solutions are the savior in such cases. The main idea behind software-based fault-tolerance approaches is executing the same critical program multiple times and having the results evaluated by some checkpoint mechanism. These executions can either be in parallel to each other or in a sequential manner. Checkpoint to determine correct results of multiple executions is always sequential as it can only operate after results from all the executing elements are received.

A software-based fault-tolerance approach for shared memory multicore platform is presented in [35]. This approach is based on using redundant multithreaded processes to detect soft errors. There are also many other approaches that include securing conditional branches by encoding-based comparison result with the redundancy of control-flow-integrity (CFI) protection mechanism, software fault-tolerance via vectorization, error detection by selective procedure call duplication and multi-stage software solution incorporating various techniques together. [36] [37] [38] [39]. However, the focus of this thesis is on hardware based solutions and software solutions (if needed) can always be included later to further enhance the fault-tolerant capabilities.

#### Hardware based:

Hardware-based fault-tolerance techniques are based on incorporating additional hardware to detect or correct the errors in the system. Although it incurs additional area overhead, they are becoming more popular and considered more reliable. Hardware redundancy can be static or dynamic: static redundancy means all additional hardware works simultaneously and any error detected is masked immediately, while dynamic redundancy means additional hardware in only activated when current hardware detects an anomaly and starts malfunctioning. Subsequent sections will discuss various hardware fault-tolerance approaches in particular to the softcore processors.

#### 2.4.1.1 Fault-tolerance in pipeline

Pipeline in a processor is the part where most of the data get manipulated. Therefore, protection of this part is a must in order to make a processor fault-tolerant. Two most widely used approaches to introduce redundancy in the pipeline are triple modular redundancy (TMR) and duplication with compare (DWC).

#### TMR

Triple modular redundancy (TMR), as the name suggests is a technique in which the hardware module is replicated three times. All three modules then execute the same process and their results are fed to a checkpointing module, which then decides the correct value. Checkpointing module usually works on the majority principle, which means that if one out of three modules produces erroneous value, then the checkpointing module will mask the erroneous value and produce a correct result because two modules (out of three) produced correct values. This behavior is also depicted in Table 2.4

| A | В | C | Output |

|---|---|---|--------|

| 0 | 0 | 0 | 0      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 0      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 0      |

| 1 | 0 | 1 | 1      |

| 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 1      |

Table 2.4: Truth table for checkpoint mechanism

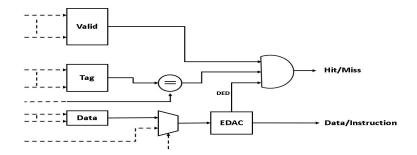

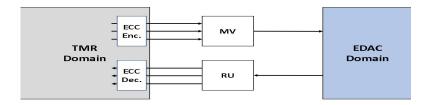

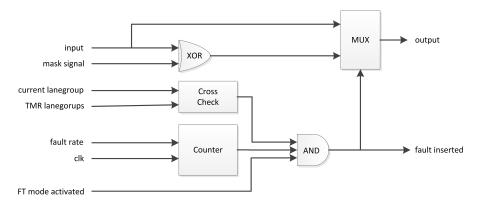

All the three modules running under TMR must be in strict lockstep. Lockstep means that all the processes run the same program, exactly same instruction sequences, memory loads/stores and interrupts. A strict lockstep needs the processor to run identically on a cycle-by-cycle basis. TMR in processor pipeline can be implemented in twofold ways: either the whole pipeline is triplicated or the flip-flops in the pipeline are triplicated. [40] propose an approach in which the complete pipeline is triplicated and all the signals of the pipelines that could be from/to general purpose registers, data memory, and instruction memory pass through some kind of checkpointing mechanism. On the other hand, [41], as depicted in figure 2.2, propose an approach in which all the flip-flops that are used for pipeline latches/registers are triplicated and after each TMR, outputs pass through checkpointing unit before entering the next pipeline stage.

#### **DWC**

Duplication with compare (DWC) is a technique which uses duplication of the module and a checkpointing mechanism to detect upsets. This technique provides relatively less area overhead as compared to TMR, but in addition to just duplication, it also needs a rollback mechanism to take the process back to a previous synchronized stage every

Figure 2.2: TMR for flip-flop

time an upset is detected.

Processes must also be in strict lockstep for this approach. Results from both modules are fed to the checkpointing mechanism which just passes the data across in case both inputs are same, but in case of conflicting outputs, it (temporarily) suspends the further execution of the process. One way to tackle the upset after detection is to reset the processor and restart the program from the beginning. The other way is to reset the state of the processor to a previously stored stable state. This approach provides a better and more efficient solution and is mentioned in [42]. In this, state of the processor is periodically saved when a program executes. State of processor involves state registers, contents of general purpose register files and other memory hierarchies such as caches and main memory. When an anomaly is detected, the rollback mechanism takes the process back to the most recently stored state to recover. If the anomaly is detected more frequently then after suspending the processor execution, FPGA bitstream scrubbing [43] [44] [45] is performed to repair any upsets that may exist in FPGA configuration memory. This periodically saving of state in DWC approach can be expensive in terms of both area and performance.

Another slightly modified DWC approach is mentioned in [46] and depicted in figure 2.3. In this, the checkpoint mechanism is used to compare output signals inside the pipelines that are executing duplicated instructions. These signals include results of arithmetic operations, jump address of a branch or values of memory operations. Whenever an anomaly is detected, a rollback mechanism flushes the pipeline and fetches the uncommitted instruction again. As the anomaly is detected before the memory and register files are modified, flushing the pipeline and executing the last uncommitted instruction works. The only state that needs to be saved in this case is the program counter (PC) value for the last instruction.

#### 2.4.1.2 Fault-tolerance in memory cells

Besides the pipeline, the processor also includes several memory elements that constitute register file, instruction memory, and data memory. These memory elements are often implemented in dynamic random access memory (DRAM), static random access memory (SRAM) or flip-flops (FF). These memories are known as user memories. Besides user memories, FPGAs also have configuration memory that stores the design information. Both of these memories need to be protected against single event ef-

Figure 2.3: DWC with comparison

fects(SEEs). Protection schemes for both kinds of memories will be discussed separately.

#### User memory

User memory stores the application data that is being processed. Modular redundancy approaches explained earlier for pipeline protection can be used to protect this memory against SEEs. Individual register and flip-flop can be duplicated or triplicated, along with some comparison mechanism to detect and correct errors. However, it is not very economical in terms of area overhead to replicate memory cells twice or thrice along with adding correction logic. [47] shows that TMR is economical for control and datapath circuits or for single registers as in pipeline, but when it comes to a group of registers, caches, and embedded memories, error correcting codes are better options, even though encoders and decoders introduce a performance penalty due to extra delay on the critical path.

Error correcting codes (ECCs) are the most commonly used protection scheme for memories. They are based on the principle of adding extra bits to the data word to form a code word. These extra bits are computed based on the bits in the data word, thus providing redundancy such that errors in the data word can be detected or corrected. Error correcting codes can be categorized into two categories:

## • Block code

Information is considered as blocks and these codes are applied on a block-by-block basis. Blocks might be independent of each other.

#### • Convolution code

Information is considered as a stream and these codes along with current data might also depend on preceding data.

For memory elements of the processor, block codes are usually applied. Convolution codes are difficult/almost impossible to apply as values in register files and data memory are usually independent of each other. Instructions can also be considered mainly independent to each other although there might be some form of dependency between consecutive instructions. Subsequent sections will provide an overview of most commonly used error correcting codes.

#### • Hamming code

One of the most well-known error correcting code is Hamming code, that was introduced by R. W. Hamming in 1950 [48]. In his paper, three types of codes namely single error detecting (SED), single error correcting (SEC) and single error correcting, double error detecting (SECDED) were introduced.

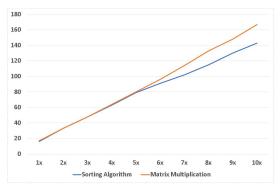

## - Single error detecting (SED) code