# Understanding and mitigating resistive losses in fired passivating contacts role of the interfaces and optimization of the thermal budget

Libraro, S.; Morisset, A.; Hurni, J.; Genç, E.; Antognini, L.; Bannenberg, L. J.; Famprikis, T.; Ballif, C.; Hessler-Wyser, A.; Haug, F. J.

10.1016/j.solmat.2023.112591

**Publication date** 2023

**Document Version** Final published version

Published in

Solar Energy Materials and Solar Cells

Citation (APA)

Libraro, S., Morisset, A., Hurni, J., Genç, E., Antognini, L., Bannenberg, L. J., Famprikis, T., Ballif, C.,

Hessler-Wyser, A., & Haug, F. J. (2023). Understanding and mitigating resistive losses in fired passivating contacts: role of the interfaces and optimization of the thermal budget. *Solar Energy Materials and Solar* Cells, 263, Article 112591. https://doi.org/10.1016/j.solmat.2023.112591

## Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

ELSEVIER

Contents lists available at ScienceDirect

# Solar Energy Materials and Solar Cells

journal homepage: www.elsevier.com/locate/solmat

# Understanding and mitigating resistive losses in fired passivating contacts: role of the interfaces and optimization of the thermal budget

S. Libraro <sup>a,\*</sup>, A. Morisset <sup>a</sup>, J. Hurni <sup>a</sup>, E. Genç <sup>a</sup>, L. Antognini <sup>a</sup>, L.J. Bannenberg <sup>b</sup>, T. Famprikis <sup>b</sup>, C. Ballif <sup>a,c</sup>, A. Hessler-Wyser <sup>a</sup>, F.-J. Haug <sup>a</sup>

#### ABSTRACT

This work presents a study of p-type passivating contacts based on  $SiC_x$  formed via a rapid thermal processing (RTP) step, using conditions compatible with the firing used to sinter screen-printed metallization pastes in industry. The contributions of the two interfaces (wafer/contact and contact/metal) to the contact resistivity are first decorrelated, identifying tunnelling at the wafer interface as the main contribution. We then investigate the influence of the active dopant concentration on the contact resistivity and the  $SiC_x$  sheet resistance and propose strategies to reduce both resistances by increasing the thermal budget applied during RTP. Lastly, we discuss potentials and limitations of implementing the investigated stacks as rear side contacts of p-type devices with localized metallization. We demonstrate that increasing the thermal budget during RTP can effectively mitigate resistive losses and enhance contact performance and we show that an oxide layer that can withstand high thermal budgets is the key factor for obtaining simultaneously high passivation quality and good electrical properties. We investigate three different oxide types grown by HNO<sub>3</sub> immersion, UV-O<sub>3</sub> exposure and N<sub>2</sub>O plasma oxidation. The latter is demonstrated to be a promising candidate for an application in devices fabricated with high RTP thermal budget.

#### 1. Introduction

Tunnel oxide passivating contacts (PCs) based on poly-Si layers have enabled solar cell conversion efficiencies above 26 % [1,2]. Formation of PCs normally starts with the growth of a thin silicon oxide (SiO<sub>x</sub>) layer (~1-2 nm) at the c-Si wafer interface, followed by the deposition of a polycrystalline Si or amorphous Si layer. In the latter case, next, an annealing process is performed to crystallize the amorphous deposited layer, thereby providing stability to the poly-Si contact during the subsequent high-temperature processing steps. This annealing step is typically carried out at temperatures between 800°C and 900 °C [3,4] or sometimes up to 1050 °C [5,6] and for dwell times ranging from minutes to hours. Besides crystallization of the Si, this step also promotes the activation of dopants within the poly-Si layer. Moreover, it allows the dopants to diffuse through the SiOx and into the wafer, thus creating a shallow highly doped region in the c-Si [7]. Lastly, the thin SiO<sub>x</sub> also undergoes chemical and structural changes during this high temperature step [8-10].

Due to their compatibility with the high temperature processes that are routinely used by the photovoltaics industry, poly-Si contacts are

now experiencing a growing popularity among industrial manufacturers, with industrial cell efficiencies that have been rapidly improving in recent years [11-13].

Using Earth-abundant, low-cost materials and fabrication conditions that are compatible with industrial processing is key to enable a smooth transition of poly-Si contact technology from research to industry. A possible simplification of this transition may be represented by the suppression of the long annealing at high temperature usually required for contact formation. As an alternative to long-annealed poly-Si contacts, p-type fired passivating contacts (FPCs) have been demonstrated, which make use of a shorter annealing to activate the dopants in the poly-Si layer [14]. This process, which consists of a rapid heating to a peak temperature around 800 °C and dwell times of only a few seconds, is compatible with the firing step employed in industry for the sintering of the metal paste. Thus, these FPC structures could provide an alternative to the localised rear-side contacts used in current p-type passivated emitter and rear cells (PERC) since they can be processed without the need for laser opening of the rear dielectric. In particular, previous work on FPCs has demonstrated their capability to achieve low saturation current density (J<sub>0</sub>) values below 10 fA/cm<sup>2</sup> [15]. Replacing the

E-mail address: sofia.libraro@epfl.ch (S. Libraro).

a École Polytechnique Fédérale de Lausanne (EPFL), Institute of Electrical and Micro Engineering (IEM), Photovoltaics and Thin-Film Electronics Laboratory (PV-lab), Rue de la Maladière 71b. 2002. Neuchâtel. Switzerland

b Department of Radiation Science and Technology, Faculty of Applied Sciences, Delft University of Technology, 2629JB, Delft, the Netherlands

<sup>&</sup>lt;sup>c</sup> CSEM Sustainable Energy Center, Rue Jaquet-Droz 1, CH-2002, Neuchâtel, Switzerland

<sup>\*</sup> Corresponding author.

partial rear contact scheme of PERC with this optimized FPC structure has the potential to improve the cell efficiency above 25 % [15].

In traditional poly-Si contacts, the presence of the shallow doped region promotes tunnelling through the  $SiO_x$ , thanks to a favourable band-edge alignment between the wafer and the doped poly-Si layer [16]. Additionally, the shallow doped region enhances surface passivation by reducing the presence of recombination centres for minority carriers. In contrast, due to the shorter thermal treatment applied to FPCs, dopant diffusion across the  $SiO_x$  is suppressed and surface passivation and charge carrier transport rely on the accumulation region formed at the wafer interface, as well as on a low defect density at the c-Si/SiO<sub>x</sub> interface [14,17]. These, in turn, are strongly dependent on processing conditions that must be carefully tuned to ensure efficient charge transport and high passivation quality in these contacts.

Whereas previously reported FPC results often display these layers at the solar cell's rear side with a low-temperature, full-area metallization [15], integrating FPCs into industrial processing requires compatibility with high-temperature screen-printing and firing, where the use of localized metal fingers instead of full area contacts is the commonly chosen approach [18]. This introduces further challenges and requirements regarding contact resistivity and lateral conductivity compared to the case of a full-area metal contact; these parameters must be carefully optimized in order to minimize resistive losses that could negatively affect the fill factor (FF).

For long-annealed poly-Si contacts, the in-diffused region can promote low contact resistivity at the c-Si/SiO $_{\rm X}$ /poly-Si interface as well as provide a region with high lateral conductivity between the metal fingers. In the case of FPCs, satisfying these requirements solely through careful tuning of the poly-Si layer properties becomes essential; this, in turn, requires a thorough understanding and control of the interplay between the various process parameters and properties of the contacts.

In this contribution, we investigate FPCs based on p-type  $SiC_x$  layers, targeting their application as rear-side contacts in c-Si. We address the associated challenges and potential applications of the stacks in devices with localized metallization.

In particular, we focus on characterizing their electrical properties and optimizing them to minimize resistive losses. We study the dependence of the contact resistivity and lateral conductivity on processing temperature, separating the role of the wafer/PC and PC/metal interfaces. With the goal of reducing silver consumption (as used in silver paste screen printing), we compare the performance of various metals, namely an indium tin oxide/silver (ITO/Ag) stack, which was used to contact FPCs in previous publications [15,19] as well as aluminium and molybdenum contacts. These alternative metals possess suitable work functions that make them promising candidates for establishing low contact resistivity to p-type layers [20]. Additionally, we examine the impact of the thermal budget applied during firing on the passivation

quality. We identify a range of processing parameters where high passivation quality and good electrical conductivity can be obtained simultaneously. This is accomplished by introducing an interfacial oxide layer that can withstand a higher thermal budget.

#### 2. Experimental

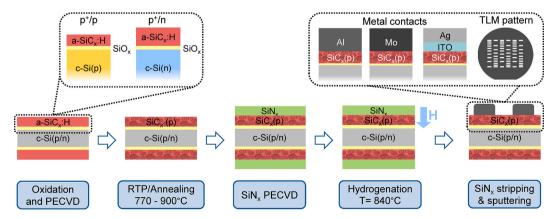

The different processing steps for sample fabrication are shown in Fig. 1. Symmetrical test structures were fabricated on 200-μm thick shiny-etched (SE) float-zone wafers with (100) orientation, either p-type or n-type doped with a resistivity of 2  $\Omega$  cm. After etching and cleaning, a thin (~1.3 nm) interfacial oxide was grown chemically on all samples by immersion in HNO $_3$  (69 %, 80 °C, 10 min). For some samples, this chemical oxide was removed by a 1 min HF dip, and two other kind of oxides were tested, grown by UV-O3 exposure for 2 min or by plasma enhanced chemical vapour deposition (PECVD). The thickness of the oxide layers obtained with these two techniques was found to be comparable with the thickness of the chemical oxide (~1.3 nm). For the PECVD oxide samples, the wafers were subjected to a plasma treatment using H<sub>2</sub> and N<sub>2</sub>O as precursor gases, which resulted in the growth of an oxide layer at the wafer surface (referred to as "plasma oxide" in the following sections). After oxidation of the c-Si, a hydrogenated amorphous a-SiC<sub>x</sub>(p):H layer (containing about 2.5 at% of C) was deposited by PECVD at 200 °C for all samples (KAI-M, Unaxis). The thickness of the a-SiC<sub>x</sub>(p):H was  $\sim$ 40 nm on the p-type wafers and  $\sim$ 120 nm on the ntype substrates (denoted as p<sup>+</sup>/p and p<sup>+</sup>/n structures, respectively). The higher thickness of the  $SiC_x$  for  $p^+/n$  structures is chosen to ensure sufficient lateral conductivity for electrical characterization. Subsequently, rapid thermal processing (RTP) was used to crystallize the layers and activate their dopants (Jipelec 200). Temperatures between 770  $^{\circ}\text{C}$  and 920  $^{\circ}\text{C}$  and dwell times between 3 and 30 s were explored. More details on the experimental procedure can be found in Ref. [14].

Lastly, the samples were hydrogenated by growing a layer of hydrogen-rich silicon nitride (SiN $_x$ :H) by PECVD (SINA, Meyer Burger) and then firing at a set temperature of 840 °C for a few seconds in a ceramic roller furnace (CAMINI, Meyer Burger). After hydrogenation, the SiN $_x$ :H layers were removed by dipping the samples in a 5 % HF solution.

Minority carrier lifetime and implied open-circuit voltage (iVoc) were measured on unmetallized samples prior to  $SiN_x$  removal with a Sinton WCT-100 instrument.

For samples dedicated to metallization, after dipping in 5 % HF solution to remove the parasitic oxide at the  $\mathrm{SiC}_x$  surface and sputtering Al, Mo, or an ITO/Ag bilayer (Leybold Univex-450B for Al and Mo and MRC P603, NIHON MRC Co. for ITO/Ag) through a shadow mask, the contact resistivity was measured using the transfer length method (TLM) on assputtered samples and after a 30 min curing at 200 °C carried out in air

Fig. 1. Schematics of the process flow for fabrication of  $SiC_x$  passivating contacts. The two different sample configurations  $(p^+/p \text{ and } p^+/n)$  are shown as well as the tested metal contacts. A top view schematic of the metallization pattern used for TLM measurements is also included.

atmosphere. The evaluation of the contact resistivity after curing was included in the study to test the compatibility with the process flow of our demonstrator solar cells, which includes a step at the end for curing the defects that could result from the sputtering of the metal contacts.

The samples were cleaved along the TLM pattern to avoid lateral current spreading. The true distances between the pads were measured by optical microscopy to account for deposition of material under the shadow masks. For the  $p^+/p$  structures, the current spreading into the wafer was corrected according to the 2D analytical method described in Ref. [21]. The  $\mathrm{SiC}_x$  layer between the metal pads was not removed, as the lateral conductivity of this layer is much lower than the one of the wafer, as discussed below.

The contact resistivity characteristics expected for the tunnel junction were modelled according to Refs. [22,23]. For the metal/SiCx contact resistivity, the contribution expected for thermionic field emission (TFE) was modelled according to Ref. [24]. The active carrier density was determined by combining ellipsometry (UVISEL, Horiba Jobin Yvon), UV–Vis spectrometry (Lambda 950 with integrating sphere, PerkinElmer), and IR transmission (Vertex 90 FTIR, Bruker) measurements following the method described in Ref. [19]. The sheet resistance of the layers was obtained from 4 point probe measurements on  $p^+/n$  structures.

X-ray photoelectron spectroscopy (XPS) measurements were performed with a ThermoFisher K-Alpha spectrometer equipped with a focused monochromatic Al Kα source (1486.6 eV) anode operating at 36 W (12 kV, 3 mA), a flood gun operating at 1 V, 100  $\mu$ A and the pass energy of the analyser set to 150 eV. The base pressure in the analysis chamber was approximately  $2.10^{-9}$  mbar. For each sample, an area scan of 3000  $\times$  3000  $\mu m^2$  was performed using a grid of 90 400  $\times$  400  $\mu m^2$ points that are partially overlapping. The samples were transferred from the glove box to the spectrometer inside a dedicated ThermoFisher vacuum transfer module to avoid air-exposure. In the analysis, the binding energy was corrected for the 0.3 eV charge shift using the primary C1s hydrocarbon peak at binding energy BE = 284.8 eV as a reference. The data were fitted using 70 % Gaussian and 30 % Lorentzian line shapes (weighted least-squares fitting method) and nonlinear Shirley-type background using the ThermoFisher Avantage software.

#### 3. Results and discussion

#### 3.1. Contact resistivity for $p^+/n$ and $p^+/p$ structures

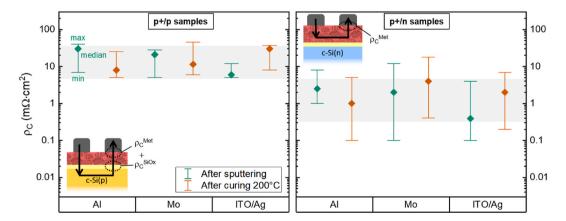

Fig. 2 shows contact resistivity data for three different metals measured on samples featuring n-type and p-type wafers (p $^+$ /n and p $^+$ /

p, respectively), for RTP at 800 °C and a dwell time of 8 s (corresponding to the optimal conditions found in our previous publications for HNO3 and UV-O3 oxide [15,19]). In both cases, HNO3 immersion was used to grow the thin interfacial oxide. The two types of sample structures are used for the following reasons: for the p<sup>+</sup>/p samples, current flow between the TLM pads occurs mostly in the wafer, whose sheet resistance  $R_{sheet}$  is two orders of magnitude below the one of the SiC<sub>x</sub> (~100  $\Omega$ /square for c-Si wafer compared to >10 k $\Omega$ /square for 40 nm SiC<sub>x</sub> layer). The measured  $\rho_C$  is therefore a sum of the contributions coming from the wafer/SiO<sub>x</sub>/SiC<sub>x</sub> interface ( $\rho_C^{SiOx}$ ) and the SiC<sub>x</sub>/metal interface  $(\rho_G^{Met})$ . To assess the impact of lateral transport within the SiC<sub>x</sub> layer on these structures, we conducted TLM measurements both before and after removing the material between the metal pads using reactive ion etching (RIE). Remarkably, our findings indicate comparable results for 40 nm layers, confirming the negligible contribution of current flow in the SiC<sub>x</sub>. Detailed results can be found in the Supplementary Information.

In the case of p<sup>+</sup>/n structures, transport occurs mostly in the SiC<sub>x</sub> layer due to the blocking p/n junction at the wafer interface and thus only  $\rho_C^{Met}$  is measured. For these structures, the SiC<sub>x</sub> layer has been deposited with a thickness of ~120 nm to ensure sufficient lateral conductivity to perform the contact resistivity measurements with enough accuracy. We verified that the different thicknesses of the SiC<sub>v</sub> layers for the p<sup>+</sup>/p and p<sup>+</sup>/n structures do not create any additional difference in the measured contact resistivity by comparing the active doping concentration in the layer in the two cases, and we found them to be comparable within the measurement error. Furthermore, we compared the contact resistivities on p<sup>+</sup>/p structures for 40 nm and 120 nm SiC<sub>x</sub> layers and found no significant difference in the results, both layer thicknesses yielding values in the range 15–25 m $\Omega$  cm<sup>2</sup>. The data relative to these additional experiments are reported in the Supplementary Information. The current flow in the two different sample structures is also illustrated in Fig. 2.

The data reveal that, for all the samples, the contact resistivity values are an order of magnitude lower for the case of  $p^+/n$  structures than for  $p^+/p$ . This indicates that the largest contribution to the resistivity originates from  $\rho_C^{SiOx}$ . The three tested metals all perform similarly, which points towards comparable values for their effective Schottky barriers. Nevertheless, the three metals show a different behaviour with respect to the changes in the contact resistivity after a thermal treatment. Aluminium contacts exhibit decreased contact resistivity in both  $p^+/p$  and  $p^+/n$  samples. This could be attributed to the reduction of a residual native oxide on the  $SiC_x$  surface, which improves the Al–Si contact [25,26]. Conversely, the samples metallized with ITO/Ag contacts show an increase in contact resistivity after curing; this effect has previously been explained with the effusion of O from the ITO, which

Fig. 2. Contact resistivity on c-Si(p)/SiO<sub>x</sub>/SiO<sub>x</sub>(p)/metal or c-Si(n)/SiO<sub>x</sub>/SiC<sub>x</sub>(p)/metal structures either directly after metal sputtering or after curing at 200 °C for 30 min. The chemical oxide was used for this experiment. The schematics illustrate the sample structures as well as the current path between TLM pads. The grey area corresponds to the range where the median values lie to highlight the difference between the  $p^+/p$  and  $p^+/n$  samples. For each conditions, 5 different samples were measured.

facilitates the growth of an oxide layer at the  $SiC_x/ITO$  interface [27]. The trend of Mo contacts is less clear, and contact resistivity values change little after curing. This behaviour appears to be consistent with previous observations reported in the literature, in which no reduction of the surface  $SiO_x$  by Mo was observed and the electrical properties of Si/Mo direct contacts were found to be unchanged after annealing up to  $600~^{\circ}C$  [28].

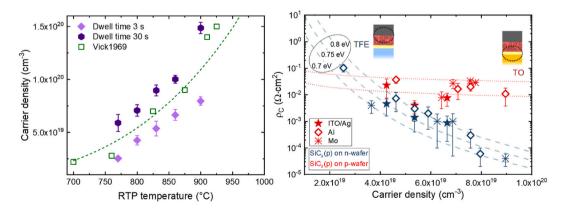

# 3.2. Influence of the active carrier concentration on the electrical properties of the contacts

The dependence of the active doping concentration on the RTP temperature and dwell time is depicted in the left panel of Fig. 3 and compared to literature data for the solubility of boron in crystalline silicon [29]. The data in Fig. 3 show increasing active carrier density towards higher firing temperatures and dwell times. For both dwell times of 3 and 30 s, the obtained concentrations follow closely the trends observed in the data from previous work [29]. We expect the concentration of active dopants to have an impact on the contact resistivity since the doping concentration controls the induced accumulation layer in the c-Si as well as the width of the space charge region at the metal interface.

#### 3.2.1. Contact resistivity

The right panel of Fig. 3 presents the contact resistivity as a function of the carrier density for p<sup>+</sup>/n and p<sup>+</sup>/p structures, together with the predicted behaviour for thermionic field emission (TFE) and tunnelling (TO) dominated transport at the metal/SiCx and c-Si/SiOx/SiCx interfaces, respectively [24]. For this experiment, contact resistivity was measured after sputtering of the metal contacts, and the curing step was not performed. The contact resistivity for p<sup>+</sup>/n samples decreases towards higher carrier density (corresponding to a higher thermal budget applied during RTP), which agrees well with the predicted behaviour and indicates that increasing the RTP temperature can significantly reduce  $\rho_C^{Met}$ . For p<sup>+</sup>/p samples, the contact resistivity appears to reach saturation at higher carrier densities; this behaviour can be explained by tunnelling-dominated transport across the c-Si/SiO<sub>x</sub>/SiC<sub>x</sub> interface, which is less sensitive to doping than TFE. This shows that the reduction in  $\rho_C^{SiOx}$  expected from increasing the RTP temperature is limited compared to  $\rho_C^{Met}$ . The data reported so far were measured on samples with a chemical oxide at the c-Si/SiCx interface. On another batch of p<sup>+</sup>/p samples where the thin oxide was obtained by UV-O<sub>3</sub> exposure (not shown here) no major differences were observed in the experiment in terms of contact resistivity compared to HNO<sub>3</sub> samples presented in this section. This suggests that the two processes result in oxide layers with similar thicknesses and with similar tunnelling probabilities for hole transport.

The contact resistivity data obtained from TLM measurements conducted on Al, Mo, and ITO/Ag contacts do not exhibit any preference for a specific Schottky barrier height. This observation is unexpected, considering that differences in the work function of these contact materials should show up particularly in the case of  $p^+/n$  samples. A possible explanation for this discrepancy could be the presence of a not fully etched parasitic oxide layer on the surface of the  $\mathrm{SiC}_{x}$ . This could increase the measured contact resistivity and thus minimize the effect of the work function of the different tested metals. This topic will be addressed in a following section.

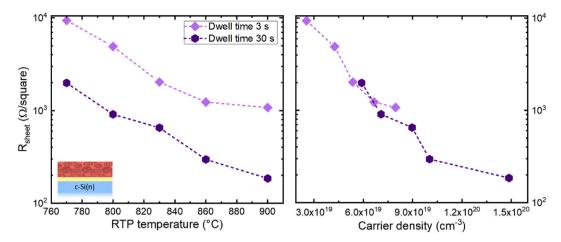

#### 3.2.2. $SiC_x$ lateral conductivity

Increasing the RTP thermal budget of p<sup>+</sup>/n structures also changes the sheet resistance of the  $\mathrm{SiC}_{\mathrm{X}}$  layers as a consequence of the increased activation of dopants. Fig. 4 illustrates the dependence of  $R_{sheet}$  on the thermal budget during RTP (left) and on the concentration of active dopants (right). In contrast to what was previously observed for  $\rho_C^{\mathrm{SiOx}}$ , the sheet resistance can be further decreased as carrier density increases, without limitation in the probed range. This demonstrates that, while a higher thermal budget may not result in a significant reduction in contact resistivity, it can substantially decrease  $R_{sheet}$ , a parameter of interest when applying localized metallization to the layers. This will be covered in greater detail in the following.

#### 3.3. XPS analysis of $SiC_x$ (p) surface

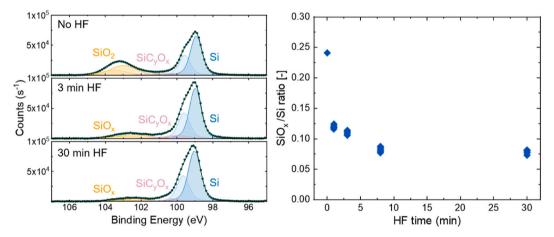

The contact resistivity data presented in Figs. 2 and 3 show a large spread, which could be tentatively explained by a residual oxide of variable thickness on top of the  $\mathrm{SiC}_X$  that was not fully etched by the 1 min dip in 5 % HF used for these experiments. As previously mentioned, this could also explain why no dependence on the metal work function was observed for the data in the right panel of Fig. 3, especially for the p<sup>+</sup>/n structures. To investigate this point, XPS measurements were performed on several samples that were subjected to different HF times. On each sample, 90 measurements were performed leading to acquire information on the uniformity across the sample. The data and fitted peaks are depicted in the left panel of Fig. 5. Data relative to samples with three different HF times are shown as an example (the complete dataset can be found in Supplementary information). The Si 2p signal was fitted with at least two pairs of peaks: one pair at BE  $\approx$  99 eV representing the Si signal (blue) and one or two pairs at BE  $\approx$  101–103 eV

Fig. 3. Left: dependence of the active carrier concentration on the RTP temperature and dwell time. The error bars correspond to the uncertainty on the results of the fitting procedure. Literature data on the solubility of B in c-Si are shown with empty symbols, whereas the fit of the experimental data is shown in dashed lines. Right: Dependence of the contact resistivity on the active carrier concentration. Dotted lines show the modelled contribution for transport at the c-Si/SiO $_x$ /SiC $_x$  interface ("TO", red dotted line) for two different values of the band bending induced across the oxide. Dashed lines show the contribution at the SiC $_x$ /metal interface ("TFE", light blue dashed line) for three values of the Schottky barrier. Contact resistivity data for p+/p (red) and p+/n structures (blue) are shown for the three chosen metals. Median values over three samples are shown, and the error bars represent the standard deviation. The chemical oxide was used for this experiment.

Fig. 4. Sheet resistance measured on p+/n structures for different RTP temperatures and dwell times (left).  $R_{sheet}$  as a function of the active carrier concentration (right).

Fig. 5. Left: Detailed scan of the Si2p signal for three different HF times. The different colours highlight the pairs of peaks used for the fitting. Right:  $SiO_x/Si$  peak ratio from XPS scans, as a function of different HF times. On the samples, multiple measurements were performed leading to multiple values for each HF time.

representing the  $SiO_x$  peak (yellow). The intensity of the Si 2p peak was used to determine the ratio between the  $SiO_x$  to Si peak intensity to monitor the presence of  $SiO_x$  on the sample surface, and the results are shown in the right graph of Fig. 5. For each condition, 10 data points out of 90 are represented in the plot. The peak ratio shows a steep decrease from 0 to 1 min HF, and subsequently a slower decrease up to 8 min. For longer HF times, the peak ratio remains constant and never reaches zero.

The observation that the  $SiO_x/Si$  ratio never reaches zero could indicate that the parasitic  $SiO_x$  layer is never completely removed from the surface even after long HF dip duration. A possible explanation for this effect is that during the RTP, some boron from the  $SiC_x(p)$  layer may segregate into the surface oxide, leading to a B-rich  $SiO_x$  that is stable in HF for longer time compared to a pure native oxide. We speculate that the non-uniform etching of this oxide over the wafer surface could explain the large spreading observed in contact resistivity results. This hypothesis is also consistent with the observation that the largest spreading is found for  $p^+/n$  samples, where the contribution from the parasitic oxide layer would have a greater influence than in the case of  $p^+/p$  samples. These findings imply that improved surface control of the samples is required, and that additional techniques other than a simple HF dip may be needed to eliminate the parasitic oxide prior to metallization.

#### 3.4. Application as rear side contact: impact on the series resistance

The contact resistivity data shown in Fig. 2 were obtained with a RTP

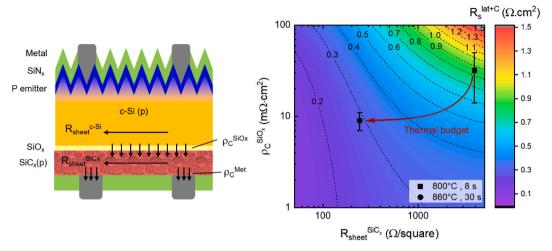

temperature of 800 °C and dwell time of 8 s, which correspond to the optimum processing conditions used to produce SiC<sub>x</sub> layers according to previous experiments. The obtained  $\rho_C$  values are mostly in the range of 10–40 m $\Omega$  cm<sup>2</sup>, which is acceptable for full area metal contacts (leading to relative FF loss below 0.5 % [30]). However, the current industry standard for solar cells manufacturing involves localized metal contacts on both sides of the cells, which reduces paste usage and opens the possibility for bifacial cells. To minimize considerable series resistance losses, the contact resistivity requirements are more severe in this scenario than in the case of full area metallization. Nevertheless, the results presented earlier show that it is possible to slightly improve the contact resistivity by increasing the RTP thermal budget. Furthermore, this boosts considerably the lateral conductivity of the SiC<sub>x</sub> layer (as seen in Fig. 4), allowing the current to laterally flow not only in the wafer, but also in the SiC<sub>x</sub> layer. A more detailed investigation was therefore performed in order to understand the influence of these parameters on the series resistance in the case of localized metal contacts applied to the SiC<sub>x</sub> layers. For this, the well-established description of the resistive losses occurring between two conductive layers coupled by a contact-resistivity was followed [31-33].

Fig. 6 depicts the effect of  $\rho_C^{SiOx}$  and  $R_{sheet}^{SiCx}$  on the series resistance in a  $p^+/p$  structure with localized metallization according to Ref. [32]. An example of the targeted cell structure, where the SiC<sub>x</sub> contact is integrated at the rear side of a cell featuring the phosphorus emitter typical of PERC, is also shown on the left. In the right panel of Fig. 6, the dotted lines show separate contours for the series resistance, which correspond

Fig. 6. Left: targeted cell structure where the  $SiC_x(p)$  is integrated on the rear side with localized metal contacts. Right: dependence of the series resistance contribution from the rear contact  $(R_s^{lat + C})$  on the contact resistivity and sheet resistance of the  $SiC_x$ . Data corresponding to two different windows of RTP conditions are shown as an example. The model parameters are:  $ρ_c^{Met} = 1 \text{ m}Ω \text{ cm}^2$ ,  $V_{mpp} = 630 \text{ m}V$ ,  $N_{dop} = 7.2 \cdot 10^{15} \text{ cm}^{-3}$ , finger pitch = 1.85 mm, finger width = 50 μm.

approximately to a change of 0.5 % in the FF [30]. The graph includes sheet resistance and contact resistivity data corresponding to "low" (800 °C for 8 s) and "high" (860 °C for 30 s) thermal budget. The graph shows two distinct parameter ranges where  $\rho_C^{SiOX}$  and  $R_{sheet}^{SiOX}$  influence  $R_s$  in different ways.

For the case of high  $R_{sheet}^{SiCx}$  (> 3 k $\Omega$ /square), current flow occurs primarily in the wafer, and  $\rho_c^{SiOx}$  must be as low as possible to maintain a small  $R_s$ . Thus, one would have to revert to a full area metal cover to provide sufficient lateral conductivity in the rear contact. Lower  $R_{sheet}^{SiCx}$  (300  $\Omega$ /square and below) allows current to flow laterally in both the SiC<sub>x</sub> and in the wafer. In this case,  $R_s$  is less sensitive to changes in contact resistivity, which becomes less critical for the device performance and allows for local contacts. These results highlight the interest of working at high thermal budget, since in this range sufficient lateral conductivity can be provided by the SiC<sub>x</sub> layer and requirements on the contact resistivity are relaxed.

## 3.5. Passivation quality

In addition to the electrical properties of the SiC<sub>x</sub> layers, the applied thermal budget also influences the passivation. This topic has been extensively investigated by different groups, and similar trends for the evolution of the passivation as a function of the applied thermal budget have been observed [34-38]. Typically, two ranges are observed in which passivation initially improves with increasing thermal budget up to an optimum and subsequently decreases toward higher temperatures. The optimal thermal budget represents the compromise between two competing effects: on one hand, the increased dopant activation and shallow diffusion of dopants across the SiOx obtained with higher temperature maximizes field effect passivation. On the other hand, too high thermal budget results in a damage to the thin interfacial SiOx layer, causing a loss of chemical passivation. Furthermore, excessive dopant diffusion in the crystalline silicon has been also identified as a source of passivation loss at high temperatures, as it enhances Auger recombination.

For FPCs, very similar trends have been reported, with an initial improvement of the passivation as the thermal budget increases, followed by a drop above the optimum temperature [15,19,39]. Because the short dwell times of RTP do not allow for significant dopant diffusion across the oxide, these contacts primarily rely on dopant activation within the poly-Si layer to promote accumulations of holes or electrons in the c-Si, as well as on the integrity of the silicon oxide layer that provides chemical passivation.

The behavior of the passivation quality as a function of the applied

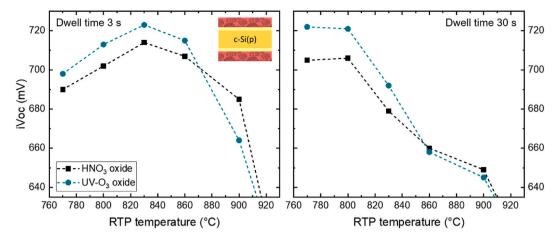

thermal budget was investigated by using symmetrical p<sup>+</sup>/p samples. Fig. 7 depicts the implied  $V_{oc}$  ( $iV_{oc}$ ) values for various RTP temperatures and dwell times of 3 (left) and 30 (right) seconds. The two different oxides show very similar trends with respect to temperature and dwell time, with the UV-O3 oxide outperforming the chemical one over most of the studied parameter range. The observed trends are consistent with other findings reported in literature for poly-Si based contacts. For the shorter dwell times, passivation improves initially with increasing temperature, reaches an optimum at 830 °C, and then declines towards higher temperatures. The initial improvement in passivation could be attributed to increased doping activation in the SiCx, promoting hole accumulation at the wafer interface. For longer dwell times, the lowest temperatures of 770 °C and 800 °C show comparable performance, but at 830 °C the  $iV_{oc}$  already drops dramatically. The drop could be explained by the creation of interfacial defects across the oxide, which become detrimental for higher temperatures and longer dwell times [15], or even by the disruption of the oxide layer for the highest thermal budgets.

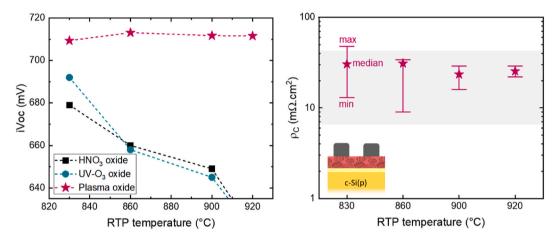

The iVoc results shown in Fig. 7 demonstrate that HNO3 or UV-O3 oxides do not provide high enough surface passivation at high thermal budget. Therefore, a third oxide layer was developed with the goal of obtaining improved stability at high temperatures and longer dwell times, and thus accessing the high thermal budget range that was shown to be beneficial in terms of electrical conductivity. This oxide layer is based on N<sub>2</sub>O plasma-assisted oxidation by PECVD, which has already shown improved resistance to high temperature processes compared to more commonly used oxide layers [40,41]. The data obtained with this oxide layer are depicted in Fig. 8 (left) in comparison with the HNO3 and UV-O3 results in the high temperature range (data reproduced from Fig. 7). The plasma oxide samples exhibit a completely different trend than the other layers included in this study. In particular, stable passivation quality up to 920 °C is shown, with the  $iV_{oc}$  remaining constant above 710 mV. The right panel of Fig. 8 displays the contact resistivity data obtained with the plasma oxide samples for an ITO/Ag metallization. The values lie in the same range as the results obtained with chemical and UV oxides, represented by the grey area. This makes the plasma oxide an excellent option to work in the high thermal budget range, enabling to maintain both high passivation quality and high electrical conductivity at the same time. We speculate that the improved stability at high thermal budget may originate from the higher density of this oxide layer compared to chemical and UV-O3 ones. The superior performance of this oxide layer could also be related to a composition closer to that of stoichiometric SiO2, which was shown to have a positive impact on thermal stability of oxide layers [9,42]. Moreover,

Fig. 7. Implied  $V_{oc}$  data measured on symmetrical samples featuring a chemical (black squares) and a UV-O<sub>3</sub> (blue circles) oxide, for a RTP with 3 s (left) and 30 s (right) dwell time.

Fig. 8. Left: implied  $V_{oc}$  data measured on symmetrical samples for chemical (black), UV-O<sub>3</sub> (blue) and plasma (pink) oxides, for a RTP with dwell time of 30 s in the higher temperature range. Right: contact resistivity data measured for the plasma oxide samples for different RTP temperatures. The grey area represents the range of values that was obtained with chemical and UV-O<sub>3</sub> oxides, corresponding to the data reported in Figs. 2 and 3.

accumulation of N at the c-Si interface has been reported in previous studies, where strong Si–N bonds substitute the weaker ones normally present at the interface [43]. The presence of the stronger bonds may also explain the improved stability of the  $N_2O$  oxide at high thermal budget. The investigation of this topic is beyond the scope of this work and will be treated in a follow-up publication.

#### 4. Conclusions

By separating the impact of  $\rho_C^{SiOX}$  and  $\rho_C^{Met}$  on charge transport performing TLM measurements on p<sup>+</sup>/p and p<sup>+</sup>/n structures, we have shown that the results did not strongly depend on the chosen metallization, which opens the interesting possibility of Ag-free contacts to the poly-Si layers. Increasing the RTP temperature can significantly reduce  $\rho_C^{Met}$ , whereas the contribution from the tunnel oxide can only be lowered to a lesser extent. Nonetheless, an increased thermal budget improves the lateral conductivity of the SiCx layer, which is important when using localized metallization. We showed that using a high thermal budget for the RTP is critical for limiting the influence of the rear contact on the series resistance. We investigated an alternative oxidation process based on N2O plasma treatment of the wafer surface, which demonstrated improved stability in the high thermal budget range compared to the other oxide layers studied in this work. The introduction of this oxide layer did not have significant effect on the contact resistivity of the stacks. Therefore, we identify the plasma oxide layer as

a promising candidate to allow for successful integration of the studied layers into devices with localized metallization.

#### CRediT authorship contribution statement

S. Libraro: Writing – original draft, Visualization, Methodology, Investigation, Data curation. A. Morisset: Writing – review & editing, Supervision, Investigation, Funding acquisition, Data curation. J. Hurni: Writing – review & editing, Investigation, Data curation. E. Genç: Writing – review & editing, Investigation, Data curation. L. Antognini: Writing – review & editing, Investigation, Formal analysis, Data curation. L.J. Bannenberg: Writing – review & editing, Investigation, Data curation. T. Famprikis: Writing – review & editing, Investigation, Data curation. C. Ballif: Writing – review & editing, Project administration, Funding acquisition. A. Hessler-Wyser: Writing – review & editing, Supervision, Conceptualization. F.-J. Haug: Writing – review & editing, Supervision, Funding acquisition, Formal analysis, Conceptualization.

### Declaration of competing interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

#### Data availability

The supplementary information and data underlying this contribution are available on the Zenodo repository under the following https://doi.org/10.5281/zenodo.7982438.

#### Acknowledgements

The authors gratefully acknowledge support by the Swiss National Science Foundation (SNF) for the project IMPACT (grant No. 200021\_185064), by the Swiss Federal Office for Energy (OFEN) within the project iPrecise (SI/502115-01) and from the European Union's Horizon 2020 research and innovation program under the Marie Skłodowska-Curie grant agreement nos. 101028491 and 101066486. Xavier Niquille is thanked for the wet chemical cleaning of the wafers.

#### References

- [1] F. Haase, et al., Laser contact openings for local poly-Si-metal contacts enabling 26.1\%-efficient POLO-IBC solar cells, Sol. Energy Mater. Sol. Cells 186 (2018) 184–193, https://doi.org/10.1016/j.solmat.2018.06.020. March.

- [2] A. Richter, et al., Design rules for high-efficiency both-sides-contacted silicon solar cells with balanced charge carrier transport and recombination losses, Nat. Energy 6 (4) (2021) 429–438, https://doi.org/10.1038/s41560-021-00805-w.

- [3] F. Feldmann, M. Bivour, C. Reichel, M. Hermle, S.W. Glunz, Passivated rear contacts for high-efficiency n-type Si solar cells providing high interface passivation quality and excellent transport characteristics, Sol. Energy Mater. Sol. Cells 120 (2014) 270–274, https://doi.org/10.1016/j.solmat.2013.09.017. PART A.

- [4] F. Feldmann, M. Simon, M. Bivour, C. Reichel, M. Hermle, S.W. Glunz, Efficient carrier-selective p- and n-contacts for Si solar cells, Sol. Energy Mater. Sol. Cells 131 (2014) 100–104, https://doi.org/10.1016/j.solmat.2014.05.039.

- [5] J.Y. Gan, R.M. Swanson, Polysilicon emitters for silicon concentrator solar cells, Conf. Rec. IEEE Photovolt. Spec. Conf. 1 (1990) 245–250, https://doi.org/ 10.1109/pvsc.1990.111625.

- [6] U. Römer, et al., Recombination behavior and contact resistance of n+ and p+ poly-crystalline Si/mono-crystalline Si junctions, Sol. Energy Mater. Sol. Cells 131 (2014) 85–91, https://doi.org/10.1016/j.solmat.2014.06.003.

- [7] F. Feldmann, J. Schön, J. Niess, W. Lerch, M. Hermle, Studying dopant diffusion from Poly-Si passivating contacts, Sol. Energy Mater. Sol. Cells 200 (April) (2019), 109978, https://doi.org/10.1016/j.solmat.2019.109978.

- [8] G. Nogay, et al., Crystalline silicon solar cells with coannealed electron- And holeselective SiCx passivating contacts, IEEE J. Photovoltaics 8 (6) (2018) 1478–1485, https://doi.org/10.1109/JPHOTOV.2018.2866189.

- [9] J.I. Polzin, et al., Temperature-induced stoichiometric changes in thermally grown interfacial oxide in tunnel-oxide passivating contacts, Sol. Energy Mater. Sol. Cells 218 (2020), 110713, https://doi.org/10.1016/j.solmat.2020.110713. July.

- [10] A. Morisset, T. Famprikis, F.J. Haug, A. Ingenito, C. Ballif, L.J. Bannenberg, In situ reflectometry and diffraction investigation of the multiscale structure of p-type polysilicon passivating contacts for c-Si solar cells, ACS Appl. Mater. Interfaces 14 (14) (2022) 16413–16423, https://doi.org/10.1021/acsami.2c01225.

- [11] D. Yan, et al., Polysilicon passivated junctions: the next technology for silicon solar cells? Joule 5 (4) (2021) 811–828, https://doi.org/10.1016/j.joule.2021.02.013.

- [12] D. Chen, et al., 24.58\% total area efficiency of screen-printed, large area industrial silicon solar cells with the tunnel oxide passivated contacts (i-TOPCon) design, Sol. Energy Mater. Sol. Cells 206 (2020) 1–8, https://doi.org/10.1016/j. solmat.2019.110258. September 2019.

- [13] LONGi, LONGi Sets Record of 25.09\% for N-type TOPCon Cell Efficiency, 2021. LONGi solar news release [online], https://www.longi.com/en/news/7477/, 07.09.23

- [14] A. Ingenito, et al., A passivating contact for silicon solar cells formed during a single firing thermal annealing, Nat. Energy 3 (9) (2018) 800–808, https://doi. org/10.1038/s41560-018-0239-4.

- [15] A. Ingenito, et al., Implementation and understanding of p+ fired rear hole selective tunnel oxide passivating contacts enabling 22% conversion efficiency in p-type c-Si solar cells, Sol. Energy Mater. Sol. Cells 219 (2021), https://doi.org/ 10.1016/j.solmat.2020.110809.

- [16] H. Steinkemper, F. Feldmann, M. Bivour, M. Hermle, Numerical simulation of carrier-selective electron contacts featuring tunnel oxides, IEEE J. Photovoltaics 5 (5) (2015) 1348–1356, https://doi.org/10.1109/JPHOTOV.2015.2455346.

- [17] M. Lehmann, et al., Analysis of hydrogen distribution and migration in fired passivating contacts (FPC), Sol. Energy Mater. Sol. Cells 200 (2019), 110018, https://doi.org/10.1016/j.solmat.2019.110018. June.

- [18] X. Zhang, et al., Mass production of crystalline silicon solar cells with polysilicon-based passivating contacts: an industrial perspective, Prog. Photovoltaics Res. Appl., no. November 2021 (2022) 1–11, https://doi.org/10.1002/pip.3618.

- [19] F.-J. Haug, et al., Contributions to the contact resistivity in fired tunnel-oxide passivating contacts for crystalline silicon solar cells, IEEE J. Photovoltaics 9 (6) (2019), https://doi.org/10.1109/JPHOTOV.2019.2939880.

- [20] D.K. Schroder, D.L. Meier, Solar cell contact resistance—a review, IEEE Trans. Electron. Dev. 31 (5) (1984) 637–647, https://doi.org/10.1109/T-ED.1984.21583.

- [21] S. Eidelloth, R. Brendel, Analytical theory for extracting specific contact resistances of thick samples from the transmission line method, IEEE Electron. Device Lett. 35 (1) (2014) 9–11, https://doi.org/10.1109/LED.2013.2290602.

- [22] H.C. De Graaff, J.G. De Groot, The SIS tunnel emitter: a theory for emitters with thin interface layers, IEEE Trans. Electron. Dev. 26 (11) (1979) 1771–1776, https://doi.org/10.1109/T-ED.1979.19684.

- [23] N. Folchert, M. Rienäcker, A.A. Yeo, B. Min, R. Peibst, R. Brendel, Temperature-dependent contact resistance of carrier selective Poly-Si on oxide junctions, Sol. Energy Mater. Sol. Cells 185 (May) (2018) 425–430, https://doi.org/10.1016/j.solmat.2018.05.046.

- [24] F.A. Padovani, R. Stratton, Field and thermionic-field emission in Schottky barriers, Solid State Electron. 9 (7) (1966) 695–707, https://doi.org/10.1016/ 0038-1101(66)90097-9.

- [25] S.A. Campbell, Sci. Eng. Microelectron. Fabric. 34 (1996) 4.

- [26] K. Katkhouda, et al., Aluminum-based rear-side PVD metallization for nPERT silicon solar cells, IEEE J. Photovoltaics 4 (1) (2014) 160–167, https://doi.org/10.1109/JPHOTOV.2013.2288018.

- [27] L. Tutsch, et al., Implementing transparent conducting oxides by DC sputtering on ultrathin SiOx/poly-Si passivating contacts, Sol. Energy Mater. Sol. Cells 200 (May) (2019), 109960, https://doi.org/10.1016/j.solmat.2019.109960.

- [28] S.S. Cohen, M.J. Kim, D.M. Brown, G. Gildenblat, Direct molybdenum contacts to silicon, Appl. Phys. Lett. 46 (7) (1985) 657–659, https://doi.org/10.1063/ 1.95519.

- [29] G.L. Vick, K.M. Whittle, Solid solubility and diffusion coefficients of boron in silicon, J. Electrochem. Soc. 116 (8) (1969) 1142, https://doi.org/10.1149/ 1.2412239.

- [30] M.A. Green, Accuracy of analytical expressions for solar cell fill factors, Sol. Cell. 7 (3) (1982) 337–340, https://doi.org/10.1016/0379-6787(82)90057-6.

- [31] K.C. Huang, D.B. Janes, K.J. Webb, M.R. Melloch, A transfer length model for contact resistance of two-layer systems with arbitrary interlayer coupling under the contacts, IEEE Trans. Electron. Dev. 43 (5) (1996) 676–684, https://doi.org/ 10.1109/16.491242.

- [32] J. Haschke, G. Christmann, C. Messmer, M. Bivour, M. Boccard, C. Ballif, Lateral transport in silicon solar cells, J. Appl. Phys. 127 (11) (2020), https://doi.org/ 10.1063/1.5139416.

- [33] D. Turkay, K. Tsoi, E. Donercark, R. Turan, S. Yerci, Spreading resistance modeling for contact resistivity extraction in ohmic multilayer structures with circular electrodes, IEEE Trans. Electron. Dev. 68 (12) (2021) 6344–6351, https://doi.org/ 10.1109/TED.2021.3117187.

- [34] F. Feldmann, M. Bivour, C. Reichel, M. Hermle, S.W. Glunz, Passivated rear contacts for high-efficiency n-type Si solar cells providing high interface passivation quality and excellent transport characteristics, Sol. Energy Mater. Sol. Cells 120 (2014) 270–274, https://doi.org/10.1016/j.solmat.2013.09.017. PART

- [35] G. Nogay, et al., Interplay of annealing temperature and doping in hole selective rear contacts based on silicon-rich silicon-carbide thin films, Sol. Energy Mater. Sol. Cells 173 (2017) 18–24, https://doi.org/10.1016/j.solmat.2017.06.039.

- [36] D. Yan, A. Cuevas, S.P. Phang, Y. Wan, D. Macdonald, 23\% efficient P-type crystalline silicon solar cells with hole-selective passivating contacts based on physical vapor deposition of doped silicon films, Appl. Phys. Lett. 113 (6) (2018), https://doi.org/10.1063/1.5037610.

- [37] A. Morisset, et al., Evolution of the surface passivation mechanism during the fabrication of ex-situ doped poly-Si(B)/SiOx passivating contacts for highefficiency c-Si solar cells, Sol. Energy Mater. Sol. Cells 221 (2021), https://doi.org/ 10.1016/j.solmat.2020.110899. June 2020.

- [38] J. Linke, et al., Poly-Si thickness and temperature dependent oxide disruption induced by penetration of the interfacial oxide in (p) poly-Si/SiOx passivating contacts, Sol. Energy Mater. Sol. Cells 246 (August) (2022) 1–8, https://doi.org/ 10.1016/j.solmat.2022.111890.

- [39] L. David, et al., Fired-only passivating poly-Si on oxide contacts with DC-sputtered in-situ phosphorous-doped silicon layers, 37th Eur. Photovolt. Sol. Energy Conf. Exhib. (2020) 184–187.

- [40] M. Stöhr, J. Aprojanz, R. Brendel, T. Dullweber, Firing-stable PECVD SiO xN y/n-Poly-Si surface passivation for silicon solar cells, ACS Appl. Energy Mater. 4 (5) (2021) 4646–4653, https://doi.org/10.1021/acsaem.1c00265.

- [41] H. Xing, et al., Plasma treatment for chemical SiOx enables excellent passivation of p-type polysilicon passivating contact featuring the lowest J0 of ~ 6 fA/cm 2, Sol. Energy Mater. Sol. Cells 257 (2023), 112354, https://doi.org/10.1016/j. solmat.2023.112354. December 2022.

- [42] A. Moldovan, F. Feldmann, M. Zimmer, J. Rentsch, J. Benick, M. Hermle, Tunnel oxide passivated carrier-selective contacts based on ultra-thin SiO2 layers, Sol. Energy Mater. Sol. Cells 142 (2015) 123–127, https://doi.org/10.1016/j.solmat.2015.06.048.

- [43] A. Masuda, A. Morimoto, M. Kumeda, T. Shimizu, Y. Yonezawa, T. Minamikawa, Novel oxidation process of hydrogenated amorphous silicon utilizing nitrous oxide plasma, Appl. Phys. Lett. 61 (7) (1992) 816–818, https://doi.org/10.1063/ 1.107754.