Delft University of Technology

## Enhanced Thermal Management of a 1.2 kV SiC MOSFET Half-Bridge Fan-Out Panel-Level Packaging with Nanocopper Sintering Die-Attachment

Chen, Wei; Chen, Junwei; Gu, Chao; Tian, Tiancheng; Fan, Xuejun; Zhang, Guoqi; Fan, Jiajie

**DOI**

[10.1109/ECTC51687.2025.00084](https://doi.org/10.1109/ECTC51687.2025.00084)

**Publication date**

2025

**Document Version**

Final published version

**Published in**

Proceedings - IEEE 75th Electronic Components and Technology Conference, ECTC 2025

**Citation (APA)**

Chen, W., Chen, J., Gu, C., Tian, T., Fan, X., Zhang, G., & Fan, J. (2025). Enhanced Thermal Management of a 1.2 kV SiC MOSFET Half-Bridge Fan-Out Panel-Level Packaging with Nanocopper Sintering Die-Attachment. In *Proceedings - IEEE 75th Electronic Components and Technology Conference, ECTC 2025* (pp. 473-480). (Proceedings - Electronic Components and Technology Conference). IEEE. <https://doi.org/10.1109/ECTC51687.2025.00084>

**Important note**

To cite this publication, please use the final published version (if applicable).

Please check the document version above.

**Copyright**

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**

Please contact us and provide details if you believe this document breaches copyrights.

We will remove access to the work immediately and investigate your claim.

**Green Open Access added to [TU Delft Institutional Repository](#)

as part of the Taverne amendment.**

More information about this copyright law amendment

can be found at <https://www.openaccess.nl>.

Otherwise as indicated in the copyright section:

the publisher is the copyright holder of this work and the

author uses the Dutch legislation to make this work public.

# Enhanced Thermal Management of a 1.2 kV SiC MOSFET Half-bridge Fan-out Panel-Level Packaging with Nanocopper Sintering Die-attachment

Wei Chen

Academy for Engineering & Technology; Shanghai Engineering Technology Research Center of SiC Power Device, Fudan University

Shanghai, China

chenw21@m.fudan.edu.cn

Xuejun Fan

Department of Mechanical Engineering, Lamar University

Beaumont, USA

xuejun.fan@lamar.edu

Junwei Chen

Academy for Engineering & Technology; Shanghai Engineering Technology Research Center of SiC Power Device, Fudan University

Shanghai, China

chenjw24@m.fudan.edu.cn

Guoqi Zhang

EEMCS Faculty, Delft University of Technology

Delft, the Netherlands

g.q.zhang@tudelft.nl

Chao Gu

Academy for Engineering & Technology; Shanghai Engineering Technology Research Center of SiC Power Device, Fudan University

Shanghai, China

24110860040@m.fudan.edu.cn

Tiancheng Tian

Academy for Engineering & Technology; Shanghai Engineering Technology Research Center of SiC Power Device, Fudan University

Shanghai, China

tianchengtian@boschman.nl

Jiajie Fan\*

Academy for Engineering & Technology; Shanghai Engineering Technology Research Center of SiC Power Device, Fudan University

Shanghai, China

Research Institute of Fudan University in Ningbo Ningbo, China

\*Corresponding: jiajie\_fan@fudan.edu.cn

**Abstract**—Sintered nano-copper (Cu) improves the thermal performance of SiC MOSFET Fan-Out Panel-Level Packaging (FOPLP), a widely adopted method for miniaturizing electronic systems and modules. This study presented, for the first time, the prototyping and characterization of a 1.2 kV SiC MOSFET FOPLP half-bridge power module using sintered nano-Cu die attachment (FOPLP\_Cu), and compared it with a reference module using conductive Ag adhesive interconnects (FOPLP\_Ag). Thermal, mechanical, and electrical co-simulations proved that FOPLP\_Cu exhibited superior performances with lower thermal resistance, power loop parasitic inductance, and thermal deformation, achieving values of 0.14 °C/W (with double-sided cooling), 3.15 nH (@100 kHz), and 9.05e-5 m, respectively. In contrast, FOPLP\_Ag showed higher values of 0.24 °C/W, 3.27 nH, and 1.04e-4 m. It is worth noting that due to the higher elastic modulus of sintered nano Cu, FOPLP\_Cu experienced increased thermal stress. The internal structure analysis of the packaged devices, conducted using CSAM, showed that both FOPLP\_Cu and FOPLP\_Ag had well-formed interconnections, with no signs of delamination in the EMC, RDL, or interconnect layers. Thermal testing showed that FOPLP\_Cu achieved a single-side thermal resistance of 1.95 °C/W, representing a 22% improvement compared to FOPLP\_Ag's 2.5 °C/W. Electrical testing further demonstrated that FOPLP\_Cu had lower on-state resistance compared to FOPLP\_Ag, while maintaining comparable breakdown voltage, threshold voltage, and body diode forward voltage drop.

**Index Terms**—Fan-out panel-level packaging (FOPLP), Sintering nano Cu, parasitic inductance, SiC MOSFET, thermal resistance.

## I. INTRODUCTION

SiC MOSFETs offer a range of significant advantages, such as high conversion efficiency, low energy loss, fast switching speed, and the ability to function at elevated

junction temperatures [1-4]. These characteristics make them highly suitable for applications in electric vehicle (EV) inverters and onboard chargers (OBCs) [5-7]. The inverter's role is to convert direct current (DC) from the high-voltage battery into alternating current (AC) to power the electric motor, while the OBC converts AC from external chargers into DC to recharge the battery. In EV systems, the efficiency, reliability, and compact form factor of SiC MOSFETs are critical, making them indispensable for the effective design of core components.

In space-limited automotive applications, high power density and miniaturized power converters can save space and extend the driving range of EVs. SiC MOSFETs with FOPLP packaging provide a compact design with reduced parasitic elements and improved reliability, offering superior performance compared to traditional TO discrete packages and stacked power module designs. In FOPLP packaging, the SiC chip is embedded in a PCB-like substrate, and a redistribution layer (RDL) routes the SiC MOSFET's functions to the package terminals. This design significantly reduces inductance and shrinks the overall size. Several companies (REAL IZM, Infineon, Schweizer, Magna and so on) and research institutions (Virginia Tech, Université Grenoble Alpes, Zhejiang University, etc.) have conducted pioneering research on SiC MOSFET FOPLP, covering single-chip discrete devices, multi-chip phase-leg modules, and inverter systems[8-11].

Sintered Cu die attachment greatly enhances the electrical, thermal, and mechanical performance of FOPLP, but no successful integration has been reported to date. This paper first designed and validated an FOPLP half-bridge with sintered Cu die attachment through simulations, then developed the packaging process and experimentally

verified its functionality. The paper is structured as follows: Section II introduces the SiC MOSFET FOPLP half-bridge concept and packaging processes; Section III presents the simulation study of the FOPLP with sintered Cu die attachment; Section IV experimentally validates the packaging's functionality; and Section V provides the conclusions.

## II. SiC MOSFET FANOUT PANEL LEVEL PACKAGING

This section introduced the concept of FOPLP and examines the feasibility of integrating sintered Cu into the SiC MOSFET FOPLP half-bridge.

### B. Fanout Panel Level Packaging Structure

FOPLP technology exhibits remarkable advantages in the packaging of SiC MOSFETs. Its miniaturized (ultra-thin) design makes it compatible with high power density applications. The high level of integration facilitates the consolidation of multiple functional modules, streamlining the design and improving system performance. Additionally, the adoption of RDLs in place of traditional wire bonds reduces inductance and minimizes switching losses, making it especially appropriate for high-frequency applications. Moreover, in large-scale production, the high efficiency and yield of FOPLP significantly reduce manufacturing costs, positioning it as an ideal choice for the miniaturization of SiC MOSFET packages. This paper aims to enhance the thermal performance and reliability of FOPLP through the introduction of sintered Cu die attachment.

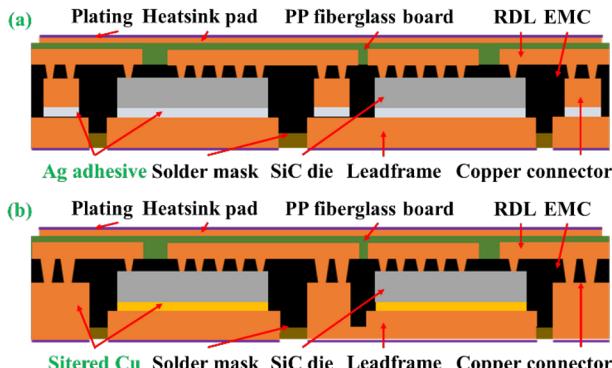

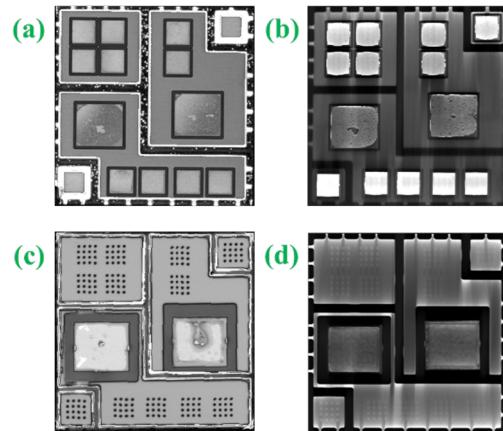

Fig. 1 Structural schematic of the SiC MOSFET half-bridge module with FOPLP packaging: (a) Ag adhesive interconnector; (b) Sintered Cu interconnector.

Efficient thermal management is essential for the proper functioning of high-power half-bridge packages. Key characteristics of high-quality packaging include parasitic parameters, electrical properties, robustness, and mechanical performance. This study presented a novel FOPLP technology for SiC MOSFET half-bridge power modules. To improve thermal performance, a nano Cu sintering die

attachment was introduced into the FOPLP process, designated as FOPLP\_Cu. A sample of FOPLP using silver (Ag) conductive adhesive served as a reference, labeled FOPLP\_Ag. FOPLP\_Ag, illustrated in Fig. 1 (a), comprised several key components: leadframe, Ag adhesive, SiC dies, Cu connector, EMC, Polypropylene (PP) fiberglass board, RDL, and heatsink pad. In contrast, FOPLP\_Cu featured a sunken half-hollow leadframe, with the SiC dies connected to the leadframe's cavities via sintered Cu, as shown in Fig. 1 (b). The surface height of the dies closely matched that of the leadframe, eliminating the need for a Cu connector, which aids in flux cancellation for achieving lower stray inductance.

### B. Packaging Structure process fo FOPLP

The SiC MOSFET die (S1M040120B) from SICHAIN Semiconductor, rated at 1200 V, 80 A, and 40 mOhm, was utilized for the research. The die dimensions were  $4.134 \times 3.74 \times 0.2$  mm<sup>3</sup>. The surface metallization of the gate and source pads comprised Ni/Pd/Au, whereas the drain's surface metallization included Ti/Ni/Ag. A panel measuring 508mm  $\times$  203 mm<sup>2</sup> was used as the substrate.

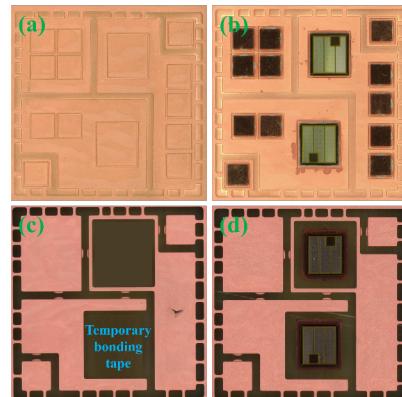

For FOPLP\_Ag, conductive Ag adhesive (WON128-T) from CORE-CHEMI was used to bond the die and Cu connector. The adhesive was cured in a nitrogen furnace (RDS Magazine Dryer, rehm-group) at 175°C for 60 minutes. Fig. 2 (a) shows the panel (substrate) with grooves outside the die and Cu connector soldering areas to prevent adhesive overflow and die displacement. Fig. 2 (b) displays the result after die attachment.

Fig. 2 The Cu substrate of a single half-bridge package unit: (a) and (b) FOPLP\_Ag before and after die attachment; (c) and (d) FOPLP\_Cu before and after die attachment;

For FOPLP\_Cu, a hollow panel was used, as shown in Fig 2. (c). Before die attachment, temporary bonding tape was applied to the bottom surface of the hollow panel. A sandwich structure, consisting of the SiC die, sintered layer, and a 0.1 mm Cu plate, was placed in the hollow of the panel, with the temporary bonding tape providing support.

The sintering process of the sandwich structure involves the following steps: (1) The SiC die and Cu plate were prepared, with the Cu plate cleaned for 300 seconds at 200°C in a formic acid environment; (2) Nano Cu paste was screen-printed onto the copper plate; (3) The paste was dried for 300 seconds at 120°C in a nitrogen atmosphere to remove organic materials; (4) The SiC die was placed on the dried nano Cu layer with 50 N of force applied; (5) The structure was sintered for 20 minutes at 20 MPa and 250°C in a pressure-assisted sintering furnace (Sinterstar Innovate-F-XL, Boschman). Fig. 2 (d) shows the sandwich structure mounted on the hollow panel.

### III. THERMAL, MECHANICAL AND ELECTROMAGNETICS SIMULATIONS AND ANALYSES

This section assessed the impact of die attachment and the package substrate on the performance of FOPLP using finite element (FE) simulations. This section performed thermal resistance testing to validate the package's heat dissipation, followed by a thermo-mechanical virtual prototyping analysis of its mechanical behavior, conducted using Ansys Workbench 2021r1. Finally, the parasitic inductance of the SiC MOSFET FOPLP was extracted using Ansys Q3D 2021, and the impact of switching frequency on it was examined.

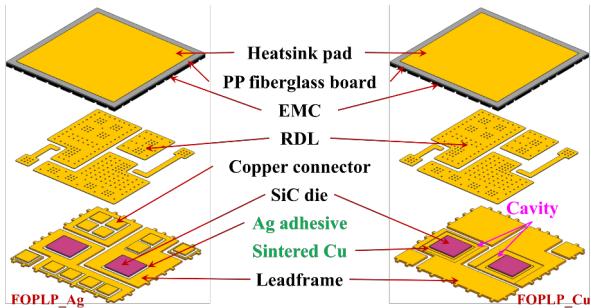

The study commenced with the development of three-dimensional models for FOPLP\_Ag and FOPLP\_Cu. As shown in Fig. 3, both FOPLP\_Ag and FOPLP\_Cu demonstrated similar internal structures and shared identical package outline drawings (POD). Apart from the die attachment materials, both structures utilized the same packaging materials, with the heatsink pad, RDL, connector, and leadframe constructed from Cu. The material parameters, including density, thermal conductivity (K), coefficient of thermal expansion (CTE), Young's modulus (E), and Poisson's ratio (ν), are detailed in TABLE 3 and were utilized in the thermal and mechanical simulations.

Fig. 3 The three-dimensional exploded views of FOPLP\_Ag and FOPLP\_Cu structures.

#### A. Thermal analysis

Effective heat dissipation is crucial for the long-term

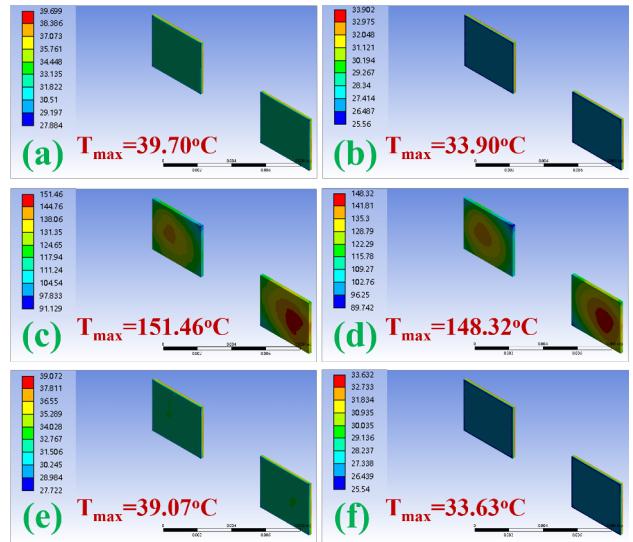

reliability of packaging, and thermal management constitutes a significant portion of the total system cost. For high power density and miniaturized SiC FOPLP packages, designing for heat dissipation presents a necessary challenge. Steady-state thermal simulations were performed for both FOPLP\_Ag and FOPLP\_Cu, with thermal power set at 58.5 W ( $V_{GS}=15$  V,  $I_D=40$  A,  $V_{DS}=1.46$  V) and an ambient temperature of 25°C. Both heatsink and solder pads act as heat dissipation surfaces, each subjected to a fixed temperature constraint of 25 °C. The ambient temperature is set at 25 °C. Both the heatsink pad and solder pad can function as heat dissipation surfaces, allowing for potential double-side cooling. A fixed temperature constraint of 25°C will be applied to the heat dissipation surfaces. The material parameters employed in the thermal simulation are presented in TABLE 1. Fig. 4 illustrates the simulated temperature distributions of SiC dies in both FOPLP\_Ag and FOPLP\_Cu under various cooling conditions. Considering the simulated results, the thermal resistance ( $R$ ) can be calculated using the following equation:

$$R = (T_{junction} - T_{ambient}) / P_{th} \quad (1)$$

where  $T_{junction}$  represents the maximum simulated temperature of the die,  $T_{ambient}$  denotes the ambient temperature, and  $P_{th}$  indicates the internal heat power.

Fig. 4. The simulated temperature distribution results in the SiC dies: (a) FOPLP\_Ag using the heatsink pad for cooling; (b) FOPLP\_Ag using the solder pad for cooling; (c) FOPLP\_Ag with double-side cooling; (d) FOPLP\_Cu using the heatsink pad for cooling; (e) FOPLP\_Cu using the solder pad for cooling; (f) FOPLP\_Cu with double-side cooling.

The thermal resistance of FOPLP\_Ag and FOPLP\_Cu under different cooling conditions is shown in TABLE 2. As illustrated in Fig. 4 and TABLE 2, the heat dissipation performance was insufficient when only the heatsink pad was used. This is due to the poorly conductive PP material,

which has a thermal conductivity of approximately 1.2 W/m·°C, positioned between the heatsink pad and both the die and the RDL. For both FOPLP\_Ag and FOPLP\_Cu, the improvement achieved with double-side cooling, compared to using the solder pad, was modest, around 5%. The thermal resistance for double-side cooling was 0.24 °C/W for FOPLP\_Ag and 0.14°C/W for FOPLP\_Cu. The sintered Cu in FOPLP\_Cu showed better thermal conductivity than the silver adhesive. In addition, the Cu connector in FOPLP\_Cu was equipped with an Ag adhesive connection, which further increased thermal resistance.

TABLE 1

THERMAL-MECHANICAL PARAMETERS OF DIFFERENT MATERIALS

| Materials   | Density (g/cm <sup>3</sup> ) | K (W/m·°C) | CTE (ppm/°C) | E (GPa) | $\nu$ |

|-------------|------------------------------|------------|--------------|---------|-------|

| Cu          | 8.9                          | 401        | 18           | 110     | 0.34  |

| SiC         | 3.2                          | 130        | 5.1          | 400     | 0.14  |

| Sintered Cu | 8.0                          | 256.46     | 17.5         | 95      | 0.30  |

| Ag adhesive | 5.4                          | 20         | 54           | 49      | 0.36  |

| EMC         | 1                            | 1.5        | 9            | 15      | 0.38  |

| PP          | 1                            | 1.2        | 56           | 4       | 0.3   |

TABLE 2

DEFINITIONS AND VALUES OF THERMAL RESISTANCE

| Package type | symbol          | Definition                                         | Value (°C/W) |

|--------------|-----------------|----------------------------------------------------|--------------|

| FOPLP_Ag     | R <sub>JH</sub> | From junction to heatsink pad                      | 2.16         |

|              | R <sub>JS</sub> | From junction to solder pad                        | 0.25         |

|              | R <sub>JD</sub> | From junction to case with double-side dissipation | 0.24         |

| FOPLP_Cu     | R <sub>JH</sub> | From junction to heatsink pad                      | 2.10         |

|              | R <sub>JS</sub> | From junction to solder pad                        | 0.15         |

|              | R <sub>JD</sub> | From junction to case with double-side dissipation | 0.14         |

### B. Thermal-mechanical analysis

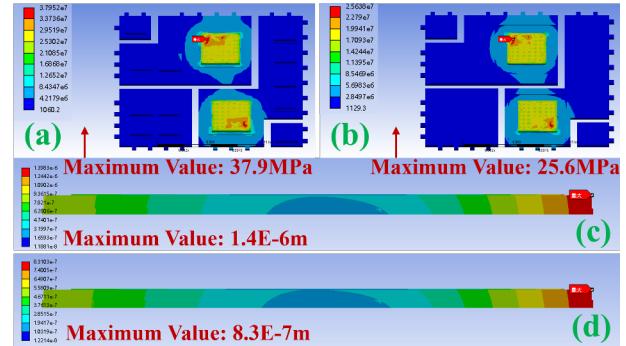

The heat produced by SiC MOSFETs during operation induces a rise in their temperature. This increase, coupled with uneven temperature distribution, creates substantial stress within the package, particularly at interfaces between materials with different CTE. Accumulated stress can result in interface delamination and crack formation. This part discussed thermal-mechanical simulations of FOPLP\_Ag and FOPLP\_Cu under double-side cooling conditions. The simulations used the package's temperature distribution, shown in Fig. 4, as input and applied remote displacement constraints with fixed displacement and rotation set to zero. The material parameters are provided in TABLE 1. The simulation results are shown in Fig. 5. FOPLP\_Ag reached a maximum stress of 37.9 MPa with a deformation of 1.4E-

6 m, while FOPLP\_Cu showed a lower maximum stress of 25.6 MPa and deformation of 8.3E-7 m, benefiting from its lower operating temperature compared to FOPLP\_Ag. The maximum stress and deformation for both FOPLP\_Ag and FOPLP\_Cu occurred at the die surface and the corners of the package, respectively.

Fig. 5 Static thermo-mechanical simulation results caused by dies heating: (a) stress for FOPLP\_Ag; (b) stress for FOPLP\_Cu; (c) deformation for FOPLP\_Ag; (d) deformation for FOPLP\_Cu.

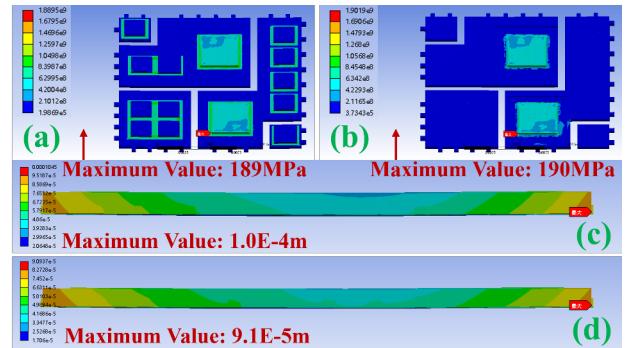

Fig. 6 Static thermo-mechanical simulation results caused by changes in environmental temperature: (a) stress for FOPLP\_Ag; (b) stress for FOPLP\_Cu; (c) deformation for FOPLP\_Ag; (d) deformation for FOPLP\_Cu.

When external environmental temperatures change, such as during thermal cycling/shock tests and reflow soldering, stress and deformation occur within the package. Simulations were conducted based on the reflow soldering temperature curve, as the environmental temperature rose from 25°C to 320°C. Using remote displacement constraints with fixed displacement and rotation at zero, the results, shown in Fig. 6, indicate that FOPLP\_Ag experienced a maximum stress of 189 MPa and deformation of 1.0E-4 m, while FOPLP\_Cu recorded 190 MPa and 9.1E-5 m. In the FOPLP structure, the die's solder pad side, which contains more Cu, resulted in an imbalance compared to the heatsink pad side, leading to a "smile face" deformation with temperature increases. FOPLP\_Cu underwent less deformation due to its sunken half-hollow leadframe, which reduces the Cu volume on the solder pad side. The

maximum stress for both FOPLP\_Ag and FOPLP\_Cu occurred at the corner in die's lower surface, with FOPLP\_Cu showing slightly higher stress due to the higher E value of the sintered Cu.

### C. Extraction of Parasitic Inductance

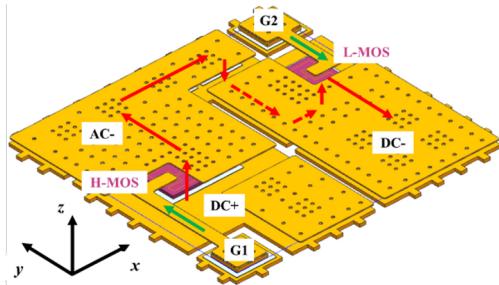

Parasitic inductance, an inherent characteristic of conductors, is influenced by material and structural design. It significantly limits the switching speeds of SiC MOSFETs, with higher parasitic inductance increasing switching losses. The parasitic inductance of the power loop

Fig. 7 The layout design of the redistribution layer and its current path in a SiC MOSFET half-bridge module with FOPLP packaging.

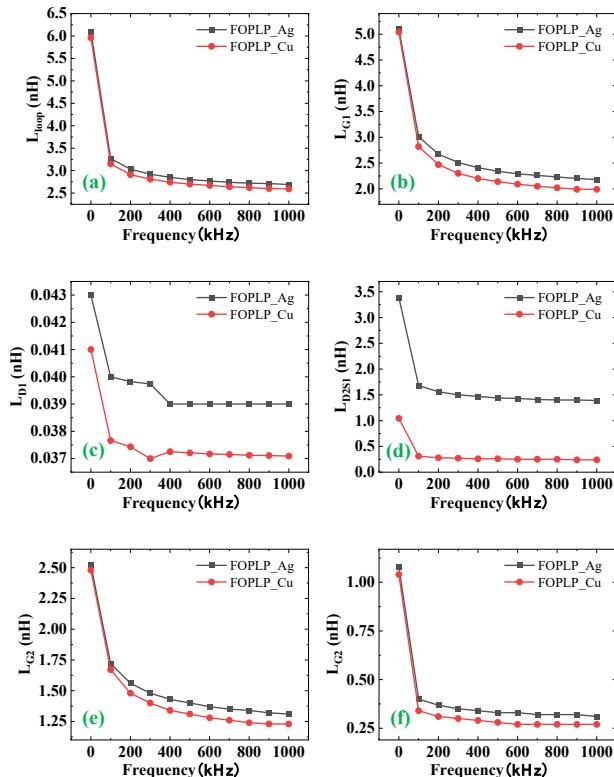

Fig. 8 The simulated parasitic inductance results for FOPLP\_Ag and FOPLP\_Cu: (a) Loop parasitic inductance; (b) G1 parasitic inductance; (c) D1 parasitic inductance; (d) D2S1 parasitic inductance; (e) G2 parasitic inductance; (f) S2 parasitic inductance

and partial parasitic inductance of the SiC FOPLP half-bridge were extracted through simulation. The bulk conductivity of Cu and sintered Cu is set at 5.8E7 S/m, and Ag adhesive at 7E6 S/m. The relative permittivity of SiC is set at 10. The sweep frequency ranges from 0 to 1000 kHz. The power loop path from the drain of the high-side SiC MOSFET to the source of the low-side SiC MOSFET is illustrated in Fig. 7.

The simulated package parasitic inductances of both FOPLP\_Ag and FOPLP\_Cu are illustrated in Fig. 8. The packaging parasitic inductance is influenced by the switching frequency. Due to the skin effect and proximity effect, it decreases with increasing switching frequency. At a frequency of 100 kHz, the power loop parasitic inductances for FOPLP\_Ag and FOPLP\_Cu were 3.15 nH and 3.27 nH, respectively. Compared to FOPLP\_Ag, the inductance value for FOPLP\_Cu decreased by approximately 4%, as the height difference between the die and leadframe in FOPLP\_Cu is smaller, and the sintered Cu in FOPLP\_Cu exhibits greater bulk conductivity.

## IV. PACKAGE PERFORMANCE ANALYSIS

In this section, to verify the functionality of both FOPLP\_Ag and FOPLP\_Cu packages, electrical, and thermal performances tests were conducted on the packaged devices.

Fig. 9 Internal structural scanning of packaged samples: (a) CSAM of FOPLP\_Ag; (b) X-RAY of FOPLP\_Ag; (c) CSAM of FOPLP\_Cu; (d) X-RAY of FOPLP\_Cu.

### A. Internal structure analysis

Both C-SAM (VUE 250-P, OKOS) and CT (xradia 620 versa, ZEISS) techniques were used to detect potential defects in the packages, the results are showed in Fig. 9. In the FOPLP\_Ag packages, no significant delamination was observed, though some defects were found in the solder layers. Interconnects for smaller Cu connectors ( $2*2 \text{ mm}^2$ ) had only a few voids, while interconnects for larger SiC die

exhibited more voids, with some being quite large. The FOPLP\_Cu packages showed no delamination or major void defects in the die interconnects.

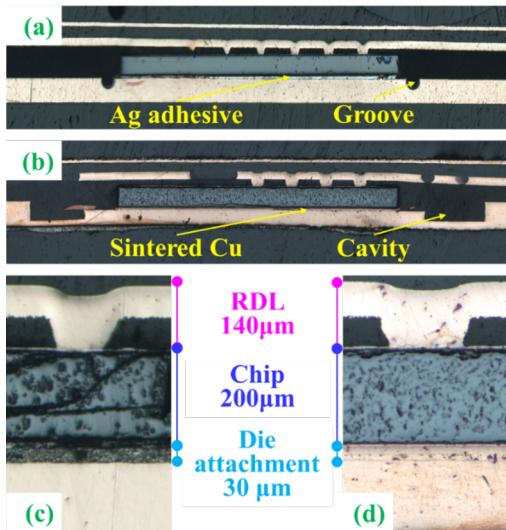

After processes such as resin embedding, cutting, polishing, and grinding, cross-sectional images of FOPLP\_Ag and FOPLP\_Cu were obtained, as shown in Fig.10 (a) and (b). These images highlighted the use of Ag adhesive in FOPLP\_Ag and sintered Cu in FOPLP\_Cu, along with the groove in FOPLP\_Ag and the cavity in FOPLP\_Cu. For FOPLP\_Cu, the images also showed the 0.1 mm Cu plate electroplated to connect with the hollow panel. Magnified cross-sectional images in Fig.10 (c) and (d) reveal that in both FOPLP\_Ag and FOPLP\_Cu, the Cu in the blind vias formed a strong mechanical bond with the die's top surface. The die's bottom surface was bonded to the substrate using Ag adhesive in FOPLP\_Ag and sintered Cu in FOPLP\_Cu, with a bond line thickness (BLT) of about 30  $\mu\text{m}$ .

**Fig. 10.** Cross-section images showing high MOS in both FOPLP\_Ag and FOPLP\_Cu: (a) overall view of FOPLP\_Ag; (b) magnified view of FOPLP\_Ag; (c) overall view of FOPLP\_Cu; and (d) magnified view of FOPLP\_Cu.

#### B. Static and switching parameter analysis

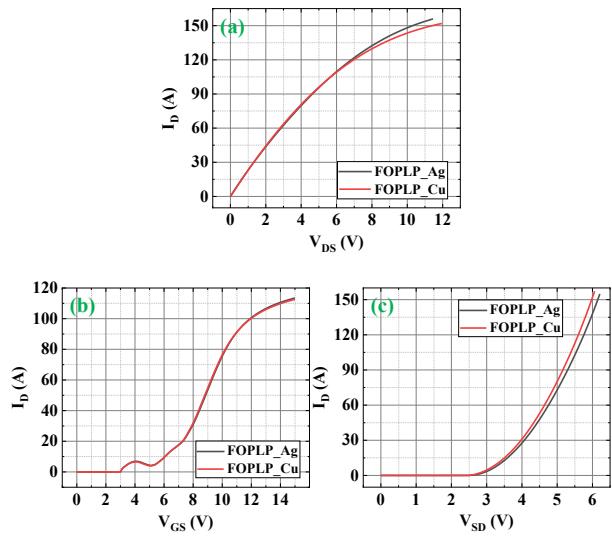

To evaluate the functionality of FOPLP\_Ag and FOPLP\_Cu packaging, several electrical parameters were experimentally tested, including output characteristics, transfer characteristics, body diode forward characteristics, and parasitic capacitance using a curve tracer (B1506A, Keysight).

Fig. 11 (a) shows the output characteristics for both FOPLP\_Ag and FOPLP\_Cu, with the gate-source voltage ( $V_{GS}$ ) set at 15 V and the drain-source voltage ( $V_{DS}$ ) increasing from 0 V to 12 V in 0.1 V steps. The plot reveals no clear distinction between the linear and saturation

regions of the SiC MOSFET, and as  $V_{DS}$  increased, the drain current ( $I_D$ ) did not reach saturation. Fig.11 (b) shows the transfer characteristics of FOPLP\_Ag and FOPLP\_Cu, measured with a  $V_{DS}$  of 20 V and  $V_{GS}$  increasing from 0 V to 15 V in 0.1 V increments. The SiC MOSFETs exhibited high threshold voltages, sharp turn-on regions, wide operating voltage ranges, and minimal drain current saturation. Fig. 11 (c) shows the body diode forward characteristics for both FOPLP\_Ag and FOPLP\_Cu, with a  $V_{GS}$  of 0 V and diode forward voltage ( $V_{SD}$ ) increasing from 0 V to 6 V in 0.1 V steps. The curves reveal that the SiC MOSFET body diodes exhibited a notably high forward conduction voltage. These characteristics make SiC MOSFETs ideal for applications requiring high temperature tolerance, high voltage, and high frequency.

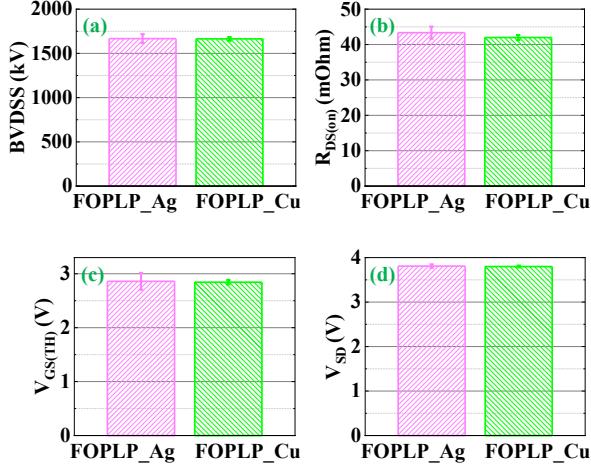

To compare the packaging performance of FOPLP\_Ag and FOPLP\_Cu, static parameters such as breakdown voltage ( $BVDSS$ ),  $R_{DS(ON)}$ , threshold voltage ( $V_{GS(TH)}$ ), and  $V_{SD}$  were extracted, as shown in Fig. 12. The results indicate that the  $R_{DS(ON)}$ s for FOPLP\_Ag and FOPLP\_Cu were 43.4 mOhm and 42.0 mOhm, respectively. FOPLP\_Cu showed a lower on-resistance compared to FOPLP\_Ag, with a reduction of about 3%. Additionally, both FOPLP\_Ag and FOPLP\_Cu maintained similar breakdown voltage, threshold voltage, and body diode forward voltage drop.

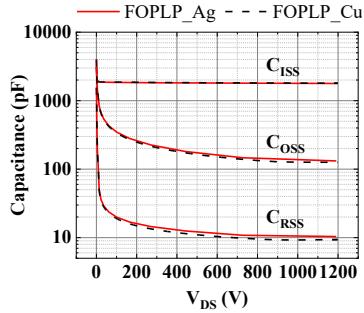

The switching behavior of SiC MOSFETs is mainly determined by the charge and discharge cycles of parasitic capacitances, including  $C_{GS}$ ,  $C_{DS}$  and  $C_{GD}$ . Among these, the  $C_{GD}$  is the most critical and complex, as it creates a feedback loop between the MOSFET's output and input. This  $C_{GD}$  consists of a fixed gate oxide capacitance ( $C_{ox}$ ) and a nonlinear SiC depletion layer capacitance ( $C_{GDj}$ ).

**Fig.11.** Characteristic curve testing of FOPLP\_Ag and FOPLP\_Cu: (a) output characteristics; (b) transfer characteristics; (c) body diode forward characteristics.

Under test conditions with a  $V_{GS}$  of 0 V and a frequency of 1 MHz, the input capacitance ( $C_{ISS}$ ), output capacitance ( $C_{OSS}$ ), and reverse transfer capacitance ( $C_{RSS}$ ) for both FOPLP\_Ag and FOPLP\_Cu were evaluated, as shown in Fig. 13. The  $C_{ISS}$  values were similar for both, while  $C_{OSS}$  and  $C_{RSS}$  values for FOPLP\_Cu were significantly lower than those for FOPLP\_Ag.

Fig. 12. Static parameter measurements of FOPLP\_Ag and FOPLP\_Cu: (a) BVDS; (b)  $R_{DS(ON)}$ ; (c)  $V_{GS(TH)}$ ; (d)  $V_{SD}$ .

Fig. 13. Parasitic input, output, and reverse capacitance testing for FOPLP\_Ag and FOPLP\_Cu

Fig. 14. Differential structure function of thermal resistance from junction to heatsink pad: (a) FOPLP\_Ag; (b) FOPLP\_Cu.

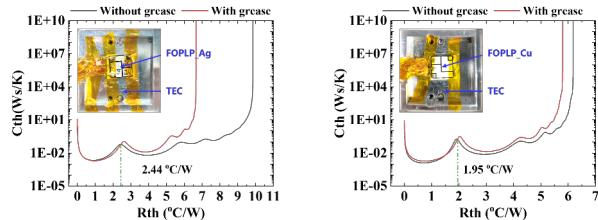

### C. Thermal resistance analysis

To evaluate thermal performance, thermal resistance measurements for FOPLP\_Ag and FOPLP\_Cu were

conducted using the T3Ster from Mentor. The thermal resistance was measured using a dual-interface method, where the FOPLP heatsink pad was coupled with or without thermal grease to the temperature control platform. The tests applied a 2 A current to heat the body diode, with a 50 mA test current.

As shown in Fig. 14, the thermal resistance values for FOPLP\_Ag and FOPLP\_Cu using heatsink pad for cooling were 2.5 °C/W and 1.95 °C/W, respectively. FOPLP\_Cu demonstrated about 22% lower thermal resistance than FOPLP\_Ag, mainly due to the high thermal conductivity of sintered Cu and the absence of low-conductivity interconnect layers typically introduced by the Cu connector.

### V. CONCLUSION

This paper introduced a sintered Cu die attachment for the SiC MOSFET Fanout Panel Level Packaging (FOPLP) half-bridge module, offering superior thermal, electrical, and mechanical performance compared to the conductive Ag adhesive attachment used as a reference. A systematic approach, including simulation-based design, development, and performance testing, was successfully completed and validated. The key conclusions are as follows:

(1) A hollow panel was used to integrate sintered Cu into the FOPLP. The pre-sintered sandwich structure, including the SiC die, sintered layer, and 0.1 mm Cu plate, was embedded into the hollow panel and electrically connected via electroplating.

(2) Simulations showed that FOPLP with sintered Cu achieved lower inductance, thermal resistance, parasitic inductance, and thermal-mechanical deformation compared to FOPLP with Ag adhesive. However, due to the higher modulus of elasticity of sintered Cu, FOPLP with sintered Cu experienced slightly higher thermal stress.

(3) Experimental validation confirmed the proposed packaging process can be effectively implemented, with no delamination observed. The functionality of SiC MOSFETs in FOPLP was verified through static characteristics, switching characteristics, and thermal resistance measurements. FOPLP with sintered Cu also exhibited lower thermal resistance due to the high thermal and electrical conductivity of the sintered Cu.

This research advances miniaturized, high-energy-density packaging for SiC MOSFETs and lays the foundation for the commercial-scale application of SiC FOPLP.

### ACKNOWLEDGEMENTS

This work was supported by National Natural Science Foundation of China (52275559).

## REFERENCES

- [1] W. Li, W. Chen, J. Jiang, H. Tang, G. Zhang, and J. Fan, "Double-sided numerical thermal modeling of fan-out panel-level MOSFET power modules," *Case Studies in Thermal Engineering*, vol. 52, p. 103763, 2023/12/01/ 2023. doi: <https://doi.org/10.1016/j.csite.2023.103763>.

- [2] W. Li *et al.*, "Double-sided heat dissipation numerical modeling of an embedded half-bridge power module with multiple chips," in *2024 25th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE)*, 2024, pp. 1-8. doi: 10.1109/EuroSimE60745.2024.10491576

- [3] W. Chen, J. Jiang, A. H. Meda, M. S. Ibrahim, G. Zhang, and J. Fan, "A Thin and Low-Inductance 1200 V SiC MOSFET Fan-Out Panel-Level Packaging With Thermal Cycling Reliability Evaluation," *IEEE Transactions on Electron Devices*, vol. 70, no. 5, pp. 2268-2275, 2023. doi: 10.1109/TED.2023.3263150.

- [4] E. A. Jones, F. F. Wang, and D. Costinett, "Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 3, pp. 707-719, 2016. doi: 10.1109/JESTPE.2016.2582685.

- [5] X. She, A. Q. Huang, L. Ó, and B. Ozpineci, "Review of Silicon Carbide Power Devices and Their Applications," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 10, pp. 8193-8205, 2017. doi: 10.1109/TIE.2017.2652401.

- [6] H. R. Kotadia, P. D. Howes, and S. H. Mannan, "A review: On the development of low melting temperature Pb-free solders," *Microelectronics Reliability*, vol. 54, no. 6, pp. 1253-1273, 2014/06/01/ 2014. doi: <https://doi.org/10.1016/j.microrel.2014.02.025>.

- [7] T. Laurila, V. Vuorinen, and M. Paulasto-Kröckel, "Impurity and alloying effects on interfacial reaction layers in Pb-free soldering," *Materials Science and Engineering: R: Reports*, vol. 68, no. 1, pp. 1-38, 2010/03/1/ 2010. doi: <https://doi.org/10.1016/j.mser.2009.12.001>.

- [8] T. Huesgen, "Printed circuit board embedded power semiconductors: A technology review," *Power Electronic Devices and Components*, vol. 3, p. 100017, 2022/10/01/ 2022. doi: <https://doi.org/10.1016/j.pedc.2022.100017>.

- [9] W. J. Hsu, J. Tong, Q. Huang, and A. Q. Huang, "Packaging and Characterization of an Ultra Compact 1200V PCB SiC MOSFET Half-Bridge Module," in *2023 IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2023, pp. 2604-2608. doi: 10.1109/APEC43580.2023.10131178

- [10] T. Gottwald, M. Martina, C. Marczok, M. Laumen, B. Flieger, and O. Wendt, "Power embedding," in *CIPS 2022; 12th International Conference on Integrated Power Electronics Systems*, 2022, pp. 1-7. doi: <https://doi.org/10.1109/CIPS52525.2022.9790017>.

- [11] A. Röhrich and C. Rössle, "Chip Embedding of Power Semiconductors in Power Circuit Boards," *ATZelektronik worldwide*, vol. 13, no. 6, pp. 56-59, 2018/12/01 2018. doi: 10.1007/s38314-018-0074-1.