# A Current Re-Use Quadrature RF Receiver Front-End for Low Power Applications **Blixator Circuit**

Barzgari, Mohammad; Ghafari, Ali; Meghdadi, Masoud; Medi, Ali

10.1109/JSSC.2022.3147101

**Publication date**

**Document Version** Final published version

Published in IEEE Journal of Solid-State Circuits

Citation (APA)

Barzgari, M., Ghafari, A., Meghdadi, M., & Medi, A. (2022). A Current Re-Use Quadrature RF Receiver Front-End for Low Power Applications: Blixator Circuit. *IEEE Journal of Solid-State Circuits*, *57*(9), 2672-2684. https://doi.org/10.1109/JSSC.2022.3147101

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

30 dB, an IIP3 higher than -30 dBm, and image rejection

# A Current Re-Use Quadrature RF Receiver Front-End for Low Power Applications: Blixator Circuit

Mohammad Barzgari<sup>®</sup>, *Student Member, IEEE*, Ali Ghafari<sup>®</sup>, *Associate Member, IEEE*, Masoud Meghdadi<sup>®</sup>, *Member, IEEE*, and Ali Medi, *Senior Member, IEEE*

Abstract—This article presents the theory and implementation of a quadrature and differential RF front-end receiver. Combining balun, low-noise amplifier (LNA), mixer, and oscillator in a single stage, the proposed circuit, named the Blixator, is well suited for low-power applications. The baseband's transimpedance amplifier (TIA) also shares part of its dc current with the Blixator cell, resulting in sub-milliwatt power consumption. To avoid additional power and area by quadrature LO generation, the I/Q signals are generated at RF, employing the inductors already required for providing the dc current path of the LNA transistors. The expressions for gain, noise figure (NF), and phase noise of the voltage-controlled oscillator (VCO) are derived, and the behavior of the circuit is thoroughly investigated. The prototype of the Blixator receiver is implemented in a 0.18-μm CMOS technology. The experimental results show a NF of 10.5 dB, an IIP3 of -15.5 dBm, at the maximum gain, and an image rejection of 23 dB, which meets the requirements for the Bluetooth Low Energy (BLE) standard. The circuit consumes only 340- $\mu$ W, from a 0.8-V supply, and its die area is 0.75 mm<sup>2</sup>.

Index Terms—Blixator, Bluetooth Low Energy (BLE), impulse sensitivity function (ISF), Internet of Things (IoT), low-noise amplifier—mixer—voltage-controlled oscillator (LMV).

#### I. INTRODUCTION

THE development of Bluetooth Low Energy (BLE), ZigBee, and energy-harvesting applications, such as wireless sensor networks, wearable devices, personal body-area networks, and the Internet of Things (IoT), is justified by evolution of ultra-low-power (ULP) radios. The main challenge in the design of these ULP radios is to minimize their power consumption and footprint [1]–[11]. In such applications, the performance can be sacrificed in order to extend the battery lifetime. In BLE receivers, a noise figure (NF) better than

Manuscript received 23 October 2021; revised 29 December 2021; accepted 23 January 2022. Date of publication 15 February 2022; date of current version 26 August 2022. This article was approved by Associate Editor Pui-In Mak. (Corresponding author: Masoud Meghdadi.)

Mohammad Barzgari is with the Department of Electrical Engineering, Sharif University of Technology, Tehran 11155-1639, Iran (e-mail: mohammad.barzgari@ee.sharif.edu).

Ali Ghafari is with the Department of Quantum and Computer Engineering, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: ghafari1994@gmail.com).

Masoud Meghdadi is with the Faculty of Electrical Engineering, Shahid Beheshti University, Tehran 19839-69411, Iran (e-mail: m\_meghdadi@sbu.ac.ir).

Ali Medi is with the Department of Electrical Engineering and the Faculty of Electrical Engineering, Sharif University of Technology, Tehran 11155-1639, Iran (e-mail: medi@sharif.edu).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2022.3147101.

Digital Object Identifier 10.1109/JSSC.2022.3147101

of about 21 dB are sufficient to meet the requirements [12], which leaves the voltage-controlled oscillator (VCO) as the most power-hungry block in the receiver chain. The required phase noise specification is about −105 dBc/Hz at an offset of 3 MHz [12]. Although this requirement is fairly relaxed, satisfying it at ULP radios is still challenging and requires power-efficient oscillator design. There has been a huge effort in the literature to increase the power efficiency in oscillators and their figure of merits (FoMs) [13]–[25]. On the other hand, low-noise amplifiers (LNAs), VCOs, and other RF blocks typically occupy large die areas, because of the bulky spiral inductors, which are used in biasing, impedance matching, and LC-tank networks. Circuit and current-reuse topologies are proper solutions to reduce both area and power consumption of the system, by incorporating multi-task blocks. The LNA, mixer, and VCO (LMV) cell introduced in 2006 by Liscidini et al. [26] is one of the first current and circuit reuse topologies, suited for low-power receivers. The oscillator and mixer are merged, while the oscillator also contributes in mixing, reducing the power consumption to 5.4 mW. The I/Q generation was implemented in LO, using a quadrature oscillator, which requires two dedicated LC tanks and additional die area. Overall, three internal inductors and one external inductor were used. In 2010, Tedeschi et al. [27] proposed an LMV circuit, with I/Q signal generation implemented in RF, using capacitive degeneration. As a result, the oscillator's LC tank was shared among the I/Q paths. Capacitive degeneration, however, produces an input impedance with negative real part, which calls for careful design and accurate simulations to avoid instability. The work was successful to reduce the power consumption to 3.6 mW. An effort in 2015 was made by Selvakumar et al. [12] to apply the most optimum oscillator in an LMV cell, in order to reduce the power, as much as possible. As a result, the complementary oscillator was employed, requiring only a slight increase in the minimum required supply voltage. The circuit has the minimum power dissipation, so far, among all the LMV cells. It consumes only 0.6 mW, and its die area is drastically efficient. The I/Q signals are elegantly generated by an RC network at the RF input, which, however, is rather sensitive to the parasitics and may result in degraded image rejection. None of the LMV structures described above have used differential RF signals and double-balanced mixers. Another circuit was introduced by Lin et al. [7] based on the Blixer cell (i.e., balun, LNA,

0018-9200 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See https://www.ieee.org/publications/rights/index.html for more information.

and mixer). The three blocks are stacked to share the same dc bias current. The active balun produces differential signals that are fed into a double-balanced mixer, while the power-hungry oscillator is not merged, consuming its own dc current. The overall power dissipation of the circuit is about 2.7 mW. A huge effort has also been made on receiver chain designs, without current and circuit reusing techniques. These works focused on power-efficient designing of each block, individually, and then cascading them in the chain. As an example, Yi *et al.* [28] reported a receiver chain for energy-harvesting applications in 2018, consuming only 382  $\mu$ W from a 0.18-V supply voltage. The circuit, however, includes four inductors and occupies a 1.65-mm² die area.

This article presents another generation of circuit and current-reuse topologies, named the Blixator circuit (i.e., balun, LNA, mixer, and oscillator). In this work, balun has been added to the LMV circuit. Accompanied with the I/Qgenerator, this is the first circuit to produce all 0, 90, 180, and 270 phases at RF to inject the quadrature RF signals to the double-balanced mixer. The oscillator used in the introduced Blixator circuit exploits a multi-turn transformer to couple the LO signal to the gate of the double-balanced mixer. The whole system is more compact with a lower number of stacked transistors. Therefore, the minimum needed voltage and power is reduced for proper operation of the circuit. Transimpedance amplifier (TIA) shares part of its current with the LNA. Therefore, the LNA is biased at a higher dc bias current, which enhances its noise and linearity performances. A passive LC network acts as a hybrid quadrature generator at the input and, at the same time, provides the dc current path for the LNA. Only two inductors and one transformer are exerted, with no external components. It would also be possible to implement the hybrid quadrature generator only with one transformer to make it more area efficient, but at the cost of increased I/Q mismatch. To the best of authors' knowledge, implemented in a 0.18-µm CMOS technology, the presented receiver front end shows competitive performance compared with the stateof-the-art works.

This article is organized as follows. Section II presents the implementation of the Blixator cell. Section III discusses gain, input matching, and the I/Q generation circuit, followed by a noise analysis in Section IV. The pulling of the oscillator under RF blockers is investigated in Section V. Section VI presents the prototype implementation details and measurement results, and finally, the conclusions are drawn in Section VII.

#### II. BLIXATOR CELL

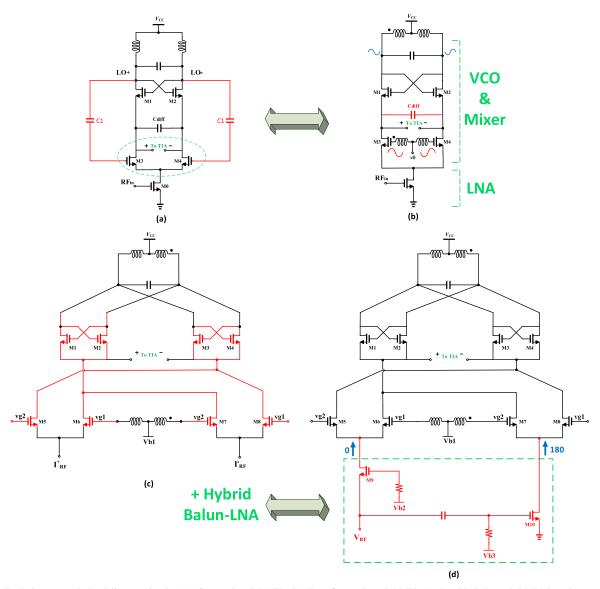

Fig. 1 shows an evolution toward the Blixator circuit, as the core of the proposed low-power RF front end. Starting from the conventional LMV cell introduced in [26], because of its low  $V_{\rm DD}$  capability [see Fig. 1(a)], it is possible to make some modifications in the oscillator circuit to reduce the power consumption even further. For instance, the inductors can be replaced with a transformer for coupling the LO signal to the gates of  $M_3$  and  $M_4$  (as the main mixer), as shown in Fig. 1(b). Exploiting the signal amplification, caused by the transformer, this will either increase the conversion gain or relax the required LO level, resulting in reduced power consumption, in comparison with conventional LMVs. The

capacitor  $C_{\rm diff}$  closes the current loop at RF frequencies while exhibiting a high impedance at IF frequencies. In this structure, the mixer transistors (M<sub>3</sub> and M<sub>4</sub>) are driven deeply into the triode region. Thus, their required voltage headroom is reduced ( $V_{\rm DS} \simeq 0$ ), making it possible to further reduce the supply voltage. Moreover, a better 1/f noise performance is obtained.

The LMV, shown in Fig. 1(b), uses a single-balanced mixer to down-convert the RF signal to IF frequencies. Hence, it suffers from LO-to-IF feed through. In order to use the double-balanced mixer and to eliminate the capacitor  $C_{\text{diff}}$ , the oscillator core can be reconfigured according to Fig. 1(c). This is done by splitting each of the core transistors into two transistors, half in size compared to the previous ones and then connecting them in a semi-parallel way. The used double-balanced mixer structure suppresses the LO-IF feedthrough, compared to the single-balanced mixer. Therefore, the signal swing at the output of the mixer is significantly relaxed, improving the performance. The other advantages of a double-balanced design over a single-balanced counterpart include better rejection of common-mode noises, such as the substrate noise, increased linearity, improved suppression of spurious products, and inherent isolation between all ports. It will be shown that the double-balanced mixer also enhances the immunity to input blockers around  $\omega_{LO}$  and  $2\omega_{LO}$  [29]. Adding a balun and LNA to the present circuit will complete the final portrait of the Blixator (Balun + LNA + Mixer + Oscillator) circuit, as shown in Fig. 1(d). The active hybrid Balun + LNA split the RF signal into 0° and 180° RF currents. While some mismatches between the two paths may exist, the double-balanced mixer will also act as a current balancer to reject any amplitude and phase mismatches between the currents of two paths [7]. Noise cancellation in the balun-LNA improves the noise performance and makes it possible to trade it with power.

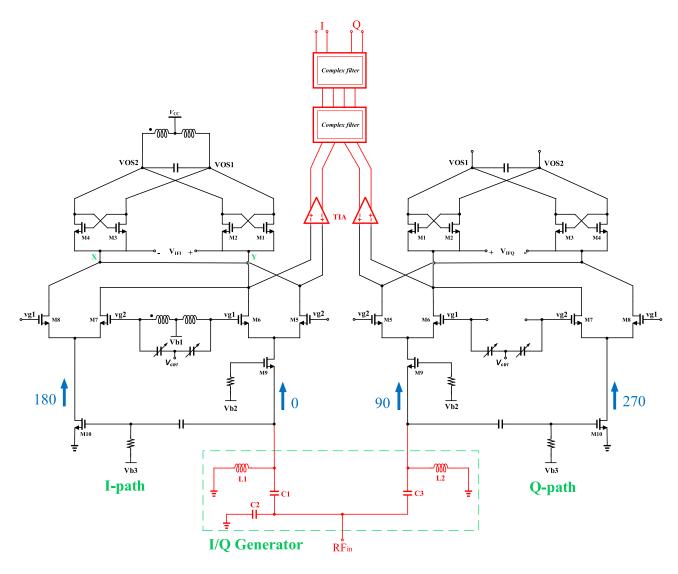

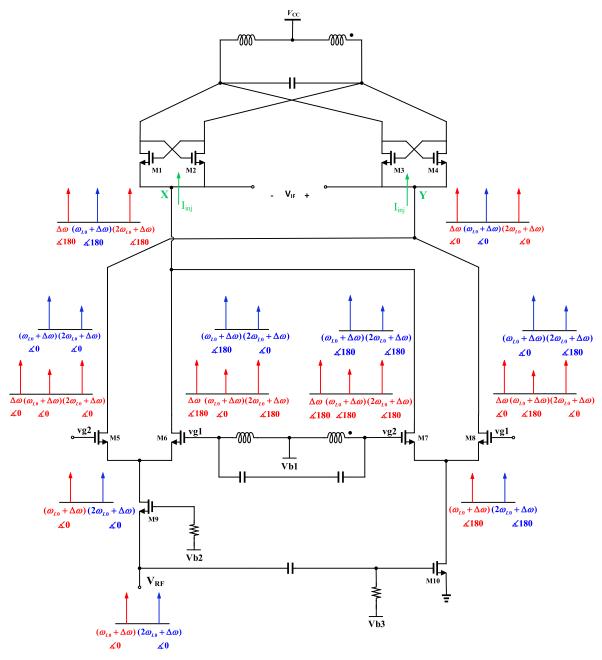

Fig. 2 shows the complete low-power receiver RF front end. An I/Q generator produces the quadrature signals at the input port. This block includes two separate inductors, which also provides the dc current path for the commongate (CG) transistors. The input matching circuit is also realized by this stage. A high passive gain is achieved, which made it possible to obtain the input matching with a low  $g_{m9}$  of 0.5 mS, substantially lower compared to the 20 mS required to obtain an input impedance of 50  $\Omega$ . In more advanced technology node and because of the lower parasitics, one can bias the transistors even closer to the sub-threshold region to have better current efficiency  $(G_m/I_d)$  to obtain the same trans-conductances at lower dc currents.

As it is clear, all the blocks in the circuit are multi-task compatible with context of circuit and current-reuse structures for low-power applications, in which both the area and the power consumption are the most important constraints. Moreover, the Q-channel shares the same oscillator tank with the I-channel. This is one of the benefits of implementing quadrature signals at the RF port. It is possible to implement quadrature signals at the LO port by employing a quadrature oscillator, but at the cost of additional transformer and area penalty. The main drawback of quadrature signal generation at the RF port is that it deteriorates the NF of the circuit, which is less important in low-power applications.

Fig. 1. Evolution toward the Blixator circuit. (a) Conventional LMV. (b) Transformer-based LMV. (c) Double-balanced LMV based on transformer configuration. (d) Blixator circuit (I channel).

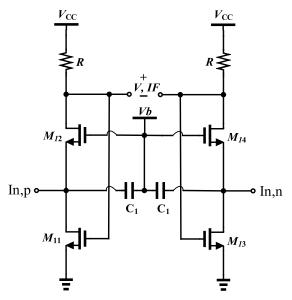

A different transimpedance amplifier with internal feedback is used in this work to reduce the input impedance at IF and to increase the conversion gain. Fig. 3 shows the differential TIA with low input impedance that is employed in the Blixator circuit. The TIA's input impedance is

$$R_{\text{in,TIA}} = \frac{1}{g_{m12}(1 + g_{m11}R)} \tag{1}$$

which is reduced by a factor of  $(1+g_{m11}R)$ , over a large bandwidth, in comparison with conventional CG TIAs. At higher frequencies, the loop gain is reduced, which increases the input impedance. The capacitor  $C_1$  provides the required low impedance at higher frequencies, suppressing the out-of-band interferences. Part of the TIA's dc bias current is reused in LNA, which helps in linearity improvement and NF reduction. To obtain a good virtual ground for a given bias current, the size of  $M_{11}$  and  $M_{12}$  should be increased. The TIAs in the I/Q paths are followed by a two-stage complex baseband filter, with a topology similar to that used in [12].

#### III. IMPEDANCE MATCHING AND GAIN ANALYSIS

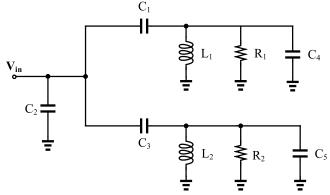

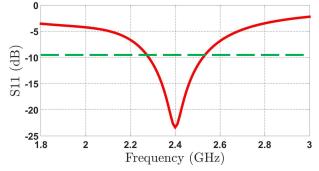

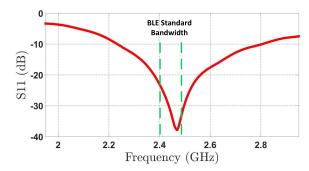

Fig. 4 shows the equivalent circuit that models the input impedance of RF port. It includes I/Q generator circuit and the parasitic elements of balun-LNA. The limited power budget does not allow to have  $g_{m9} = g_{m10} = 1/Rs$  or 20 mS. Even assuming  $G_m/I_d$  of 20 V<sup>-1</sup> for the LNA transistors (which corresponds to  $f_T$  of below 10 GHz in 180 nm at subthreshold),  $g_m = 20$  mS would require 1-mA dc bias, which would result in a total of 4 mA for the LNA, very far from the used budget of 0.32 mA. Therefore, a value of 0.5 mS is used for  $g_{m9}$  (and  $g_{m10}$ ), which leads to a CG input impedance of  $2 k\Omega$ . It should be noted that since the input impedance of the CG transistors is 2 k $\Omega$ , the parallel resistance of the inductors  $L_1$  and  $L_2$  also contribute in  $R_1$  and  $R_2$ . According to our post-layout simulations,  $R_1$  is about 1 k $\Omega$  and  $R_2$  is about 700  $\Omega$  in Fig. 4. Fig. 5 shows that the implemented hybrid network has provided a wideband input matching. The simulated  $S_{11}$  is better than -10 dB for about 0.26-GHz bandwidth (2.27–2.53 GHz), which is more than enough for BLE applications. By some algebraic calculations, it can be shown that for

Fig. 2. Proposed current re-use low-power receiver RF front end.

the required 90° phase difference between the I and Q paths, we should have

$$\alpha_1 \alpha_2 Q_{p1} Q_{p2} = -1 \tag{2}$$

where  $Q_{p1}=(R_1/(L_1\omega))$  and  $Q_{p2}=(R_2/(L_2\omega))$  are the equivalent quality factors of the inductors and  $\alpha_1=1-(L_1C_1+L_1C_4)\omega^2$  and  $\alpha_2=1-(L_2C_3+L_2C_5)\omega^2$ . Similarly, to have equal amplitudes in I and Q paths, it requires

$$\left(\frac{L_1 C_1}{L_2 C_2}\right)^2 = \frac{\alpha_1^2 + Q_{p1}^{-2}}{\alpha_2^2 + Q_{p2}^{-2}}.$$

(3)

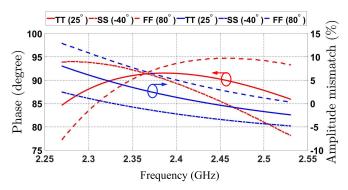

Fig. 6 shows the simulated phase and amplitude mismatch between the I/Q paths over different process and temperature corners in worst cases (TT 25°, SS  $-40^{\circ}$ , and FF  $80^{\circ}$ ) in the designed circuit, which shows acceptable matching in the bandwidth of interest. Monte Carlo simulations (200 samples) have also been run at  $f_{\rm RF} = 2.4$  GHz to find the amplitude and phase mismatches between the I/Q paths. These simulations show that the maximum phase mismatch is about 3.5° and the maximum amplitude mismatch is about 5%. The Monte Carlo simulation (200 samples) has also been run for the overall

IRR of the receiver. The results illustrate that image rejection varies from 22.5 to 28.5 dB (almost  $\pm 3$  dB around the mean value).

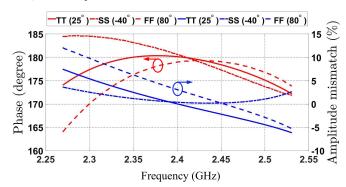

The simulation is repeated to find out the amplitude and phase mismatch of (0 and 180) signals in the I-channel at LNA output. As shown in Fig. 7 in the frequency band of 2.35–2.45 GHz, which covers the BLE standard, the variations for amplitude and phase of the paths are about 6% and 4°, respectively. The result is the same for (90 and 270) signals in Q-channel because of symmetry in the circuit.

The effective current gain from mixer stage through the IF load TIA is

$$A_{I,\text{Mixer}} = \frac{2}{\pi} \left( \frac{R_{\text{CC}}(t)}{R_{\text{CC}}(t) + R_{\text{in,TIA}}} \right) = \frac{2}{\pi} \alpha_{\text{div}}$$

(4)

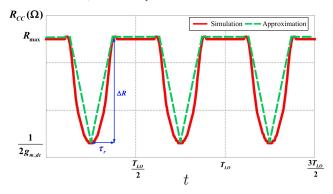

where  $\overline{(.)}$  denotes the time average and  $R_{\rm CC}(t)$  is the equivalent time-variant impedance seen at the source of the cross-coupled  $M_1$  and  $M_2$  and  $M_3$  and  $M_4$  transistors. As a matter of fact, the ideal current gain of  $2/\pi$  is degraded by the non-zero  $R_{\rm in,TIA}$  and the finite  $R_{\rm CC}(t)$ , which is a time-variant resistance, as shown in Fig. 8 [30]. The impedance  $R_{\rm max} = 1/g_{m,\rm ON}$

Fig. 3. Low input impedance transimpedance amplifier.

Fig. 4. Equivalent circuit for calculating the input impedance of receiver.

Fig. 5. Input matching (S<sub>11</sub>) of receiver.

corresponds to the source impedance of the ON-transistor; once the other transistor is turned off,  $R_{\rm min}=1/2g_{m,\rm dc}$  corresponds to the source impedance at equilibrium,  $T_{\rm LO}$  is the LO period, and  $\tau_r$  is the rise time. With respect to the approximate model of  $R_{\rm CC}(t)$  in Fig. 8,  $\alpha_{\rm div}$  can be calculated as

$$\alpha_{\text{div}} = \frac{4\tau_r}{T_{\text{LO}}} \left[ 1 - \frac{R_{\text{in,TIA}}}{\Delta R} \ln \left( \frac{R_{\text{in,TIA}} + R_{\text{max}}}{R_{\text{in,TIA}} + R_{\text{min}}} \right) \right]$$

$$+ \left( 1 - \frac{4\tau_r}{T_{\text{LO}}} \right) \frac{R_{\text{max}}}{R_{\text{in,TIA}} + R_{\text{max}}}$$

$$\approx \frac{R_{\text{max}}}{R_{\text{max}} + R_{\text{in,TIA}}} \left[ 1 - \frac{4\tau_r}{T_{\text{LO}}} \cdot \frac{\Delta R}{R_{\text{max}}} \cdot \frac{R_{\text{in,TIA}}}{R_{\text{in,TIA}} + R_{\text{min}}} \right].$$

(5)

Fig. 6. Phase and amplitude mismatch between I/Q paths over different process and temperature corners (TT corner 25°, FF corner  $80^{\circ}$ , and SS corner  $-40^{\circ}$ ) at LNA input.

Fig. 7. Phase and amplitude mismatch between  $0^{\circ}$  and  $180^{\circ}$  signal paths over different process and temperature corners (TT corner  $25^{\circ}$ , FF corner  $80^{\circ}$ , and SS corner  $-40^{\circ}$ ) at LNA output.

Fig. 8. Impedance at the source of oscillator cross-coupled transistors.

In the designed circuit,  $\alpha_{div}$  is about 0.85. Finally, the transconductance of the Blixator can be written as

$$G_{m,\text{Blix}} = \frac{1}{2} \times \text{Gain}_H \times g_{m,\text{LNA}} \times A_{I,\text{Mixer}}$$

(6)

where  $Gain_H$  is the passive gain of the hybrid section,  $g_{m,LNA}$  is the loaded transconductance of the LNA, and the one-half factor represents the equal current division between I/Q paths. Therefore, the total conversion gain will be

$$CG = G_{m, \text{Blix}} \times R_{G, \text{TIA}}$$

=  $\frac{1}{\pi} \times \text{Gain}_{H} \times g_{m, \text{LNA}} \times \alpha_{\text{div}} \times R_{G, \text{TIA}}$  (7

where  $R_{G,TIA} = R/(1 + g_{m11}R)$  is the transimpedance gain of the TIA.

It should be noted that gain control is necessary for a practical system. This can be conveniently done in IF, by adjusting

the gain in TIA (e.g., by switching R) or in the complex filter. The RF circuit is fairly linear due to the current-mode operation of the mixer and the low input impedance of the TIA. Simulations show that the input P-1 dB of the RF receiver is about -26 dBm, which is sufficient for most situations, provided that the IF gain is lowered to prevent its saturation. Nevertheless, gain control in RF can also be helpful for improving the dynamic range. A viable option is to add a switchable floating resistor array between the drains of  $M_9$  and  $M_{10}$ , to steer part of the RF signal to the virtual ac ground.

#### IV. Noise Analysis

In conventional receivers, there is no noise cross effect between VCO phase noise and circuit NF, but in current and circuit reuse topologies such as the Blixator cell, the noise of different components of various parts has crosstalk with each other. Hence, the oscillator-mixer and TIA components contribute in system NF and LNA-mixer-TIA contribute in the phase noise of VCO. This makes the noise analysis more complicated. For simplicity, the noise analysis is first conducted based on the Blixator cell shown in Fig. 1(d), while the results are finally extended to the quadrature circuit shown in Fig. 2.

#### A. Noise Figure

Starting from the LNA, all the noise contributors are considered at the TIA's output voltage. While noise of the CG transistor  $M_9$  is canceled at the differential output, <sup>1</sup> the output noise current contribution of the common-source transistor  $M_{10}$  [in Fig. 1(d)] can be calculated as

$$\overline{v_{\text{on,LNA}}^2} = 4kT\gamma g_{m10}\alpha_{\text{div}}^2 R_{G,\text{TIA}}^2.$$

(8)

It should be noted that the flicker noise of  $M_{10}$  up-converts to LO frequencies and will not appear at the IF output. Only the finite IP2 of the mixer can cause the flicker noise of  $M_{10}$  to be appeared at the output.

A high gate bias voltage of  $V_{B1}$  is chosen for biasing the mixer transistors ( $M_5$ – $M_8$ ). As a result, once being turned on, the mixer transistors are quickly driven into the triode region. Thus, it is assumed that the mixer switches are toggling between off and triode regions during the circuit operation. The thermal noise contribution of the mixer transistors ( $M_5$ – $M_8$ ) can be explained by direct and indirect mechanisms. In the direct mechanism, the noise generated by the mixer is considered during the overlap time of the switches. Following the method presented in [31], but also considering the non-zero input impedance of the TIA, the resulting differential output noise current can be approximately written as

$$\overline{v_{\text{on,Mix}}^2} \simeq \frac{32 \times 4kT\gamma}{3S \times T_{\text{LO}}} \mu_n C_{\text{ox}} (W/L)_{5-8} V_{\text{eff}}^2 \beta_{\text{div}}^2 R_{G,\text{TIA}}^2$$

(9)

where S is the slope of the single-ended LO during the zero crossings,  $T_{\rm LO}$  is the oscillation period,  $V_{\rm eff}$  is the dc effective voltage of the switches,  $\mu_n$  is the electron mobility,  $C_{\rm ox}$  is the

<sup>1</sup>Our simulations show that the noise contribution of  $M_9$  can also be neglected in the quadrature circuit, as shown in Fig. 2. Moreover, there is negligible noise contribution from the I path in the Q path and vice versa, because of the adequate isolation of the hybrid circuit.

gate oxide capacitance, and  $(W/L)_{5-8}$  is the aspect ratio of the mixer transistors. Also,  $\beta_{\rm div}$  is the effective current division coefficient between the TIA,  $R_{\rm CC}(t)$ , and the output impedance of the switches, during the overlap times, when all switches are ON. A good approximation for  $\beta_{\rm div}$  is

$$\beta_{\text{div}} \simeq \frac{R_{\text{in,TIA}}^{-1}}{R_{\text{in,TIA}}^{-1} + R_{\text{min}}^{-1} + \frac{4}{3}\mu_n C_{\text{ox}}(W/L)_{5-8} V_{\text{eff}}}$$

(10)

where  $(4/3)\mu_n C_{\rm ox}(W/L)_{5-8}V_{\rm eff}$  is the average output conductance of the switches, during the overlap times, in which  $R_{\rm CC}(t)$  is also approximated by  $R_{\rm min}$ . By exploiting the transformer and enhancing the LO signal at the gate of the switches, S will also be improved, which significantly reduces the noise contribution of the mixer, as suggested by (9).

In the indirect mechanism, the parasitic capacitance at the tail node of the mixer is also considered and results in noise contribution from the switches, even outside the overlap times [31]. Our simulations, however, show that the direct mechanism is dominant in the designed Blixator. Therefore, the indirect mechanism is neglected. In theory, the switch flicker noise also appears at the output [31]. The flicker noise of the mixer can also be neglected in the designed circuit according to the simulations.

Now, let us investigate the noise contribution of the oscillator transistors  $(M_1-M_4)$ . The thermal current noise of these transistors can be decomposed into two components: 1) the current that is drawn from the drains to the ground and 2) the same current flowing from ground to the sources of  $M_1-M_4$ . It can be seen that the first current (as well as the noise current contribution of the tank loss) does not appear at the differential output. Consequently, only the second current (i.e., the noise current from the ground to the source of the cross-coupled pairs) is important. A good approximation for the resulting output noise is

$$\overline{v_{\text{on,Osc}}^2} \simeq 4 \times 4kT \gamma \, \overline{g_{m1}(t)} \alpha_{\text{div}}^2 R_{G,\text{TIA}}^2$$

(11)

where  $\overline{g_{m1}(t)}$  is the average transconductance of the core transistors, which can be approximated as  $0.5/R_{\text{max}}$ . Finally, the output noise contribution of the TIA can be written as

$$\overline{v_{\text{on,TIA}}^2} = 2 \times 4kT \left[ \gamma g_{m11} \alpha_{\text{div}}^2 R_{G,\text{TIA}}^2 + \gamma g_{m12} R^2 (1 - \alpha_{\text{div}})^2 + R \left( 1 - \frac{\alpha_{\text{div}} g_{m11} R}{1 + g_{m11} R} \right)^2 \right].$$

(12)

Consequently, the total NF of the Blixator circuit (either of I or Q channels) is found as

$$NF \simeq 1 + \frac{\gamma g_{m10} \alpha_{\text{div}}^2}{R_S G_{m,\text{Blix}}^2} + \frac{32 \gamma \mu_n C_{\text{ox}} (W/L)_{5-8} V_{\text{eff}}^2 \beta_{\text{div}}^2}{3 S T_{\text{LO}} R_s G_{m,\text{Blix}}^2} + \frac{2 \gamma R_{\text{max}}^{-1} \alpha_{\text{div}}^2}{R_S G_{m,\text{Blix}}^2} + \frac{2 \gamma g_{m11} \alpha_{\text{div}}^2 + 2 \gamma g_{m12} (1 - \alpha_{\text{div}})^2 (1 + g_{m11} R)^2}{R_S G_{m,\text{Blix}}^2} + \frac{2 R^{-1} [1 + g_{m11} R (1 - \alpha_{\text{div}})]^2}{R_S G_{m,\text{Blix}}^2}$$

$$(13)$$

TABLE I CALCULATED AND SIMULATED NF DISTRIBUTION

| Noise Source  | NF Calculation | NF Simulation |

|---------------|----------------|---------------|

| LNA           | 33.2%          | 28.7%         |

| Mixer         | 15.9%          | 17.7%         |

| TIA           | 37.3%          | 38.2%         |

| Hybrid        | _              | 1.7%          |

| Oscillator    | 12.5%          | 13.7%         |

| Total NF (dB) | 8.7            | 9.8           |

Fig. 9. Simplified noise model of the oscillator.

where  $R_S$  is the input source impedance. Simulations show that the contributions from LNA and TIA are the most dominant terms. Increasing gain of the LNA (or  $G_{m,Blix}$ ) will minimize the NF. Thus, increasing the LNA's bias current improves the noise performance, but at the cost of extra power budget. Reusing the TIA's current in the LNA, therefore, significantly reduces the required power consumption, as both blocks have the most impact on NF. Table I shows the calculated NF based on (13) and the simulations results. Neglected in previous current-reuse works, the NF contribution of the TIA is indeed significant, because of the limited power budget.

#### B. Phase Noise

Fig. 9 shows the simplified noise model for the Blixator cell. The resistor  $R_P$  models loss of the equivalent inductor obtained by the electromagnetic (EM) simulation, and  $G_{\rm M}(t)$  and  $G_{\rm DS}(t)$  refer to the time-variant transconductance and channel conductance of the core transistors, respectively, while the noise contribution of the rest of the circuit is modeled with  $i_{n,{\rm Tail}}^2$  at the source node of the cross-coupled pair. Also,  $h_{\rm RP}$ ,  $h_{\rm D}$ , and  $h_{\rm Tail}$  are the non-normalized ISFs corresponding to tank, core devices, and tail noise sources, respectively. The non-normalized ISFs are extracted by accurate PXF simulations using SpectreRF.

According to the linear time-variant (LTV) phase noise model [32]  $N_i$ , the effective phase noise produced by the ith device is calculated by

$$N_{i} = \frac{1}{2\pi} \int_{0}^{2\pi} h_{i}^{2}(\omega_{0}t) \overline{i_{n,i}^{2}(\omega_{0}t)} d(\omega_{0}t)$$

(14)

where  $\overline{i_{n,i}^2(\omega_0 t)}$  is the *i*th noise current power spectral density (PSD) and  $h_i(\omega_0 t)$  is its relevant non-normalized ISF function. Thus, for each  $R_P$ , we have

$$N_{\rm RP} = \frac{1}{2\pi} \int_{0}^{2\pi} h_{\rm RP}^{2}(\omega_{0}t) d(\omega_{0}t) \cdot \frac{4kT}{R_{\rm P}}.$$

(15)

Similarly, the effective phase noise resulted by  $G_{\rm M}(t)$  and  $G_{\rm DS}(t)$  for each of the transistors is as follows:

$$N_{\rm GM} = \frac{1}{2\pi} \int_0^{2\pi} h_{\rm GM,eff}^2(\omega_0 t) d(\omega_0 t) \cdot \overline{i_{\rm n0,GM}^2}$$

(16)

$$N_{\text{GDS}} = \frac{1}{2\pi} \int_0^{2\pi} h_{\text{GDS,eff}}^2(\omega_0 t) d(\omega_0 t) \cdot \overline{i_{\text{n0,GDS}}^2}$$

(17)

where  $\overline{i_{n0,GM}^2} = 4kT\gamma \max(G_M)$ ,  $\overline{i_{n0,GDS}^2} = 4kT \max(G_{DS})$ , and

$$h_{\text{GM,eff}}(\omega_0 t) = h_D(\omega_0 t) \cdot \sqrt{\frac{G_{\text{M}}}{\max(G_{\text{M}})}}$$

(18)

$$h_{\text{GDS,eff}}(\omega_0 t) = h_D(\omega_0 t) \cdot \sqrt{\frac{G_{\text{DS}}}{\max(G_{\text{DS}})}}.$$

(19)

The induced flicker noise by transistors can also be written as

$$N_{1/f} = \left[\frac{1}{2\pi} \int_0^{2\pi} h_{1/f}(\omega_0 t) d(\omega_0 t)\right]^2 \overline{i_{n0,1/f}^2}$$

(20)

where  $\overline{i_{\mathrm{n0,1/f}}^2} = (\mathrm{KF}/f^{\mathrm{AF}}) \cdot \mathrm{max}(G_{\mathrm{M}}^2)$  and

$$h_{1/f}(\omega_0 t) = h_D(\omega_0 t) \cdot \frac{G_{\mathcal{M}}}{\max(G_{\mathcal{M}})}.$$

(21)

The next step is to calculate the phase noise contribution of  $\overline{I_{n,\text{tail}}^2}$  in Fig. 9. Since our simulations show that the contributions of mixer and TIA components in the total phase noise are negligible, we will only consider the LNA transistors  $M_9$  and  $M_{10}$ . First, the time-domain noise transfer function from these noise sources through the source node of the cross-coupled pairs will be evaluated. Then, the resulting function multiplied by the tail ISF will result in the phase noise contribution of these stages. Such a calculation is valid according to the bank theory [33], and it is similar to the phase noise evaluation of the tail current source in classes B, C, and F oscillators.

The injected current noise at node X (source of the left cross-coupled pair in Fig. 2) can be written as

$$i_{n,X} = p(t) \times i_{n,M10} + p'(t) \times i_{n,M9}$$

(22)

where  $i_{n,M9}$  and  $i_{n,M10}$  are the noise currents of  $M_9$  and  $M_{10}$ , respectively, p(t) is a square wave toggling between one and zero with a period of  $T_{LO}$ , and p'(t) = 1 - p(t) is its complement. Similarly, the injected current noise at node Y (source of the right cross-coupled pair in Fig. 2) is

$$i_{n,Y} = p(t) \times i_{n,M9} + p'(t) \times i_{n,M10}.$$

(23)

In order to obtain the noise currents injected to the oscillator cores, both  $i_{n,X}$  and  $i_{n,Y}$  are multiplied by the same current division coefficient of

$$\xi_{\text{div}} \simeq \frac{\overline{R_{\text{CC}}^{-1}(t)}}{R_{\text{in,TIA}}^{-1} + \overline{R_{\text{CC}}^{-1}(t)}}$$

(24)

where, for simplicity and similar to our previous derivations, it is assumed that the coefficient is approximately constant over the oscillation period. The ISF of both injected currents is the same and can be written as

$$h_{\text{Tail}}(\omega_0 t) = \sum_{n=0}^{\infty} a_{2n} \cos(2n\omega_0 t + \phi_{2n}).$$

(25)

The noise contribution of LNA components in oscillator phase noise can be calculated as

$$\phi_{n,\text{LNA}} = \xi_{\text{div}} \left( i_{n,X} + i_{n,Y} \right) h_{\text{Tail}}(\omega_0 t)$$

$$\simeq \xi_{\text{div}} \sum_{n=0}^{\infty} a_{2n} \cos(2n\omega_0 t + \phi_{2n}) \cdot \left( i_{n,M9} + i_{n,M10} \right). \tag{26}$$

Extracting the dc and harmonics of the effective ISF results in

$$\phi_{n,\text{LNA}}\big|_{\text{DC}} = \xi_{\text{div}} a_0 \cos(\phi_0) \left( i_{1/f,M9} + i_{1/f,M10} \right)$$

$$= h_{\text{LNA},1/f}(\omega_0 t) \cdot \left( i_{1/f,M9} + i_{1/f,M10} \right)$$

$$\phi_{n,\text{LNA}}\big|_{2\omega_0} = \xi_{\text{div}} a_2 \cos(2\omega_0 t + \phi_2) \cdot \left( i_{\text{th},M9} + i_{\text{th},M10} \right)$$

$$= h_{\text{LNA}}(\omega_0 t) \cdot \left( i_{\text{th},M9} + i_{\text{th},M10} \right).$$

(28)

The dc term is responsible for flicker noise up-conversion of the LNA components. Expanding and clustering the same terms in the above equations and then calculating the RMS value of the coefficients of the effective  $ISF(\phi_{n,LNA})$  results in

$$N_{\text{LNA},1/f} = \left[ \frac{1}{2\pi} \int_{0}^{2\pi} h_{\text{LNA},1/f}(\omega_{0}t) d(\omega_{0}t) \right]^{2} \cdot \left( i_{1/f,M9}^{2} + i_{1/f,M10}^{2} \right)$$

$$N_{\text{LNA}} = \frac{1}{2\pi} \int_{0}^{2\pi} h_{\text{LNA}}^{2}(\omega_{0}t) d(\omega_{0}t) \cdot 4kT\gamma \left( g_{M9} + g_{M10} \right).$$

(30)

Consequently and considering the number of components in both I and Q paths, the overall phase noise of the Blixator circuit is

$$\mathcal{L}(\Delta\omega) = 10 \log_{10} \left( \frac{8N_{\text{GM}} + 8N_{\text{GDS}} + 8N_{1/f} + 2N_{\text{RP}}}{2(\Delta\omega)^2} + \frac{2N_{\text{LNA}} + 2N_{\text{LNA},1/f}}{2(\Delta\omega)^2} \right).$$

(31)

Table II outlines the consistency between the calculated phase noise distribution according (31) and the simulated ones. The simulated total phase noise is slightly worse than the calculated one because more noise sources are considered. Besides that, some second-order effects, such as the overlap time when both  $M_7$  and  $M_8$  or  $M_5$  and  $M_6$  are ON, are neglected. The oscillator tank and core transistors have the major phase noise contributions. Nevertheless, it is interesting that the flicker noise of the LNA transistors is also considerable and should be accounted for in the circuit design flow.

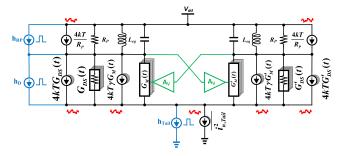

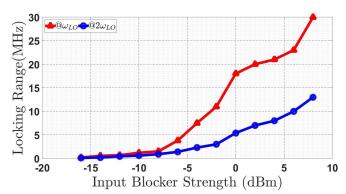

### V. PULLING EFFECT

The susceptibility of the Blixator circuit should be evaluated against injection pulling for blockers around both  $\omega_{LO}$  and  $2\omega_{LO}$ . Fig. 10 shows the blocker terms produced at each node of the circuit due to RF input blockers at  $\omega_{LO}$  and  $2\omega_{LO}$ . In particular, the terms around  $2\omega_{LO}$  injected at the sources of the cross-coupled pairs may cause the oscillator to operate like an injection locking frequency divider, being pulled or even locked to half of the divider frequency or produce spurs, if exerted in a phase-locked loop (PLL) [34]–[37]. PLL has

TABLE II

CALCULATED AND SIMULATED PN DISTRIBUTION

| Noise Source                         | PN Calculation | PN Simulation |  |

|--------------------------------------|----------------|---------------|--|

| Oscillator Tank                      | 50.2%          | 56.2%         |  |

| Oscillator NMOS Core (Thermal Noise) | 23%            | 20.9%         |  |

| Oscillator NMOS Core (Flicker Noise) | 1.6%           | 1.3%          |  |

| TIA (Thermal Noise)                  | -              | 0.2%          |  |

| TIA (Flicker Noise)                  | -              | 0.03%         |  |

| Mixer (Thermal Noise)                | _              | 0.33%         |  |

| Mixer (Flicker Noise)                | _              | 0.04%         |  |

| LNA (Thermal Noise)                  | 6.8%           | 4.2%          |  |

| LNA (Flicker Noise)                  | 17.4%          | 16.8%         |  |

| Total PN @ 1MHz (dBc/Hz)             | -120.85        | -119.6        |  |

not been included in this work, but the proposed Blixator circuit could easily be inserted into a traditional PLL structure. This is possible because, at RF, the merged circuit looks like a traditional LC oscillator, preserving the tuning capability and, hence, the possibility to be exerted in conventional PLL architectures. Generally, there is no so much issue with PLL operation in the Blixator circuit. It seems that there is no difference between this receiver and other conventional receivers from a PLL point of view. It is only known that the phase noise will be affected by the properties of the PLL. For example, the closed-in phase noise will be dominated by the PLL, instead of the VCO. As it is shown in Fig. 10, the double-balanced mixer partially cancels out the terms produced by  $2\omega_{LO}$  blocker, and there will be no corresponding even harmonics at nodes X and Y. Only  $\omega_{LO}$  blocker produces even harmonics at nodes X and Y, which may potentially pull or lock the oscillator. However, as can be seen in Fig. 10, these blocker terms appear out of phase at nodes X and Y. Consequently, their overall injection effect is canceled at the oscillator output. In general, and assuming any blocker  $V_{RF}$  at the input, we can write the currents injected at nodes X and Y as follows:

$$I_X = g_{m9} V_{RF} \xi_{div} \cdot p'(t) - g_{m10} V_{RF} \xi_{div} \cdot p(t)$$

(32)

$$I_Y = g_{m9} V_{RF} \xi_{div} \cdot p(t) - g_{m10} V_{RF} \xi_{div} \cdot p'(t).$$

(33)

Therefore, the overall injection will be

$$I_X + I_Y = (g_{m9} - g_{m10})V_{RF}$$

(34)

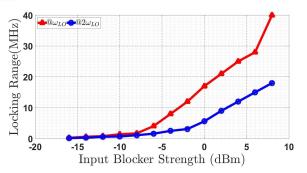

which is approximately zero, because  $g_{m9} \simeq g_{m10}$  to have proper balun operation and acceptable noise cancellation. Similar injection cancellation also happens in the Q channel circuits. Fig. 11 shows pulling susceptibility due to nearby interferers at different frequency offsets. The plotted curve shows the (locking range =  $\omega_{LO}$ - $\omega_{inj}$  = offset from LO) versus blocker power. For each input blocker power, the offset frequency is lowered until it reaches the locking range of the receiver. It shows that at an offset frequency of 1 MHz, the oscillator can be locked only with an input power of -8 dBm, which is well above the saturation point of the receiver. This demonstrates the immunity of Blixator circuit to the pulling phenomenon since it is not possible to have such large blockers feeding directly into Blixator. Simulations also show that the proposed double-balanced circuit should be considerably more immune (about 8 dB), compared to a similar single-balanced design. It should also be noted that increasing the input power (power of input blockers) of circuit causes the LMV cell and

Fig. 10. Pulling effect of fundamental and second harmonic components at RF input.

Fig. 11. Locking range versus blockers power at input RF port.

the TIAs to operate in an abnormal state, making the analysis of the problem very difficult.

$\label{thm:table III} \mbox{Power Consumption of Sub-Blocks in the Blixator Cell}$

| Sub-block                  | Consumption           |

|----------------------------|-----------------------|

| Blixator+TIA               | $322 \mu A$           |

| VCO                        | $222 \mu A$           |

| TIA                        | $2 \times 50 \ \mu A$ |

| LNA                        | $322 \mu A$           |

| Baseband Complex Filter    | $103 \ \mu A$         |

| Total Current              | $425 \mu A$           |

| Total Power (supply 0.8 V) | 340 $\mu W$           |

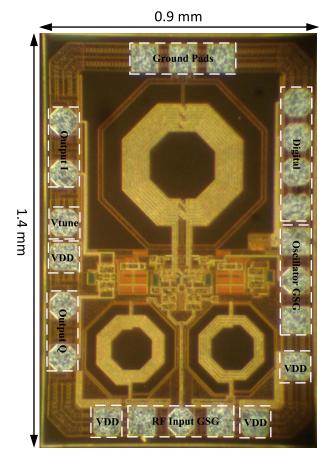

#### VI. IMPLEMENTATION AND MEASUREMENTS

## A. Prototype Implementation

A prototype of Blixator cell is designed and implemented in a standard 0.18- $\mu$ m CMOS process with a core area of 0.75 mm<sup>2</sup>, for low-power applications, such as BLE. The die

|                                     | JSSC'14 [7]                                  | JSSC'15 [12]                     | JSSC'18 [28]                               | ISSCC'18 [1]                           | ISSCC'20 [9]                                           | JSSC'20 [11]                    | This Work                    |

|-------------------------------------|----------------------------------------------|----------------------------------|--------------------------------------------|----------------------------------------|--------------------------------------------------------|---------------------------------|------------------------------|

| Application                         | 2.4GHz ZigBee                                | 2.4GHz BLE                       | 2.4GHz BLE                                 | 2.4GHz BLE                             | 2.4GHz BLE                                             | 2.4GHz BLE                      | 2.4GHz BLE                   |

| Architecture                        | Blixer +<br>Hybrid Filter +<br>Passive RC-CR | Current Re-use<br>Quadrature LMV | LNA +<br>Class-D VCO +<br>Passive I/Q Gen. | Interference-Tolerant +<br>Hybrid-Loop | LNTA +<br>Passive Mixer +<br>4 <sup>th</sup> order BPF | LNTA +<br>Mixer +<br>FIR Filter | Blixator +<br>Complex Filter |

| External<br>Component               | Zero                                         | 1 Inductor +<br>1 Cap            | Zero                                       | Zero                                   | Zero                                                   | Zero                            | Zero                         |

| VDD (V)                             | 0.6 & 1.2                                    | 0.8                              | 0.18                                       | 1                                      | 0.5                                                    | 0.7                             | 0.8                          |

| Power (mW)                          | 2.7                                          | 0.6                              | 0.38                                       | 1.2*                                   | 0.89*                                                  | 0.37                            | 0.34                         |

| NF (dB)                             | 9                                            | 15.1 to 15.8                     | 11.3                                       | 6                                      | -                                                      | 5.5                             | 10 to 10.5                   |

| VCO Phase Noise<br>(dBc/Hz) @ 1 MHz | -105.4 <sup>♯</sup>                          | -105 <sup>‡</sup>                | -105 to -107.5 <sup>‡</sup>                | -                                      | -                                                      | -                               | -118.1                       |

| IIP3 (dBm)                          | -6                                           | -15.8 to -16.8                   | -12.5                                      | -                                      | -13.1                                                  | -7.5                            | -14 to -15.5                 |

| IRR (dB)                            | 28                                           | 30.5 to 37.3                     | 26.2                                       | -                                      | -                                                      | -                               | 23 to 27                     |

| Voltage Gain (dB)                   | 55                                           | 55.5 to 56.1                     | 34.5                                       | 68                                     | 43.1                                                   | 61                              | 57                           |

| BB Style                            | With I/Q                                     | With I/Q                         | With I/Q                                   | Without I/Q                            | With I/Q                                               | With I/Q                        | With I/Q                     |

| BB Filtering                        | 3 Complex Poles                              | 2 Complex Poles                  | 3 Real Poles                               | LPF + PGA                              | 4 <sup>th</sup> -order<br>Butterworth                  | FIR Filter                      | 2 Complex Poles              |

| Active Area (mm <sup>2</sup> )      | 0.3                                          | 0.25                             | 1.65                                       | 1.64 <sup>‡</sup>                      | 1.9 <sup>‡</sup>                                       | 0.5                             | 0.75                         |

| CMOS Tech.                          | 65 nm                                        | 130 nm                           | 28 nm                                      | 65 nm                                  | 22 nm FDSOI                                            | 22 nm FDSOI                     | 180 nm                       |

TABLE IV

PERFORMANCE OF DIFFERENT RF RECEIVER FRONT-ENDS

Fig. 12. Die micrograph.

photograph is shown in Fig. 12. All used RF transistors in the Blixator circuit are thin-oxide low- $V_{\rm th}$  devices. A low-

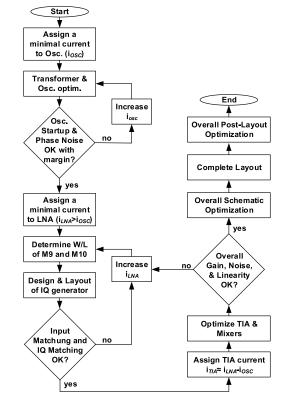

Fig. 13. Proposed design flow for Blixator circuit.

IF architecture is chosen, with an IF center frequency of 2 MHz and a channel bandwidth of 1 MHz. Only two inductors and one transformer are exploited, resulting in a modest area occupation, without requiring any external component. The quadrature differential signals are produced on-chip to not

Fig. 14. Measured input impedance matching  $(S_{11})$ .

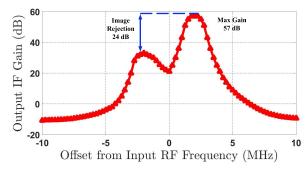

Fig. 15. Measured ac transfer function of the Blixator circuit.

only minimize common-mode signals induced by parasitics but also to provide good image rejection characteristics. Large on-chip supply bypass MOS capacitors are used to filter the supply noise. Fig. 13 shows a flow graph, which summarizes the design steps for the proposed RF receiver front end. As it is clear, the main goal is to minimize the power consumption while meeting the other BLE specifications. The main step is to assign minimum current to oscillator without start-up issue. Using a huge transformer (with enough quality factor) increases the parallel resistance of the tank. The transformer is designed based on extensive EM simulations. Linewidth, number of turns, line spacing, and inner radius of transformer have been optimized to obtain the highest possible quality factor. Consequently, lower trans-conductance is needed to compensate for the loss of the tank, resulting in lower required power consumption. Moreover, exploiting the signal amplification, caused by the transformer, enhances the mixer drive. This either improves the conversion gain or relaxes the required oscillator's power to maintain the same mixer drive.

Table III shows the current consumption of all blocks in the circuit. The TIA shares its current with the Blixator core, which consumes a total current of 322  $\mu$ A. This current is absorbed by the balun-LNA and divided between VCO and the TIAs. Because of the used low-power oscillator topology and due to the used multi-turn 4:5 transformer, the VCO requires only 222  $\mu$ A. The circuit is simulated in many corner cases to obtain the worst case scenario (SS corner  $-40^{\circ}$ ) for oscillator start-up. While the voltage swing is reduced to  $\pm 0.1$  V, the receiver is still functional. Although simulations show that the conversion gain slightly reduces (less than 2 dB), the proposed Blixator cell still meets the BLE specs. Also, in the typical corner, the supply voltage is reduced from 0.8 to 0.7 V and the oscillator spectrum is checked. While the oscillator still starts up, the phase noise has been degraded but still meets the BLE

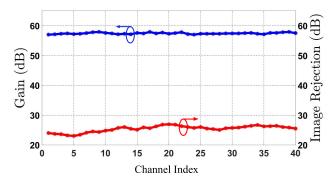

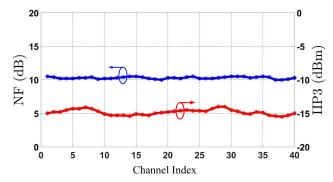

Fig. 16. Gain and image rejection versus BLE channel index.

Fig. 17. IIP3 and NF versus BLE channel index.

requirement of -105 dBc/Hz at 3 MHz. Consequently, it can be concluded that the proposed transformer-based oscillator and the mixed structure can safely operate with these levels of power, with no start-up issue. It should be noted that (in worse case) the oscillator start-up and the required amplitude can be guaranteed by exploiting the amplitude detection and control methods and tuning the biasing current [38], [39].

Tuning the oscillator makes it possible to select the desired IF channel. An 18% tuning range is provided for the oscillator to ensure covering of all BLE channels.

#### B. Measurement Results

The RF input pad is wire-bonded to the  $50-\Omega$  trace, which is connected to the Keysight E5071C vector network analyzer for  $S_{11}$  measurements. Fig. 14 shows the measured  $S_{11}$  of the proposed low-power receiver, showing a desirable return loss of better than 15 dB, over the entire BLE band. Fig. 15 shows the measured transfer function of the receiver, at the maximum gain, by sweeping the RF input frequency with respect to the LO frequency, for the first BLE channel. The results show a maximum gain of 57 dB, with less than 1-dB variations, and a minimum image rejection of 24 dB across the channel bandwidth. Fig. 16 reports the gain and image rejection measurements for all BLE channels. The gain variation is less than 1 dB across the BLE channels, which shows that the receiver bandwidth is sufficiently wide to operate in the entire ISM band. The measured image rejection varies from 23 to 27 dB, which is well above the required 21 dB for the BLE standard. Fig. 17 shows the NF and IIP3 measurements. The NF ranges between 10 and 10.5 dB that corresponds to an equivalent receiver sensitivity of better than -89.5 dBm. Measured using the two-tone intermodulation

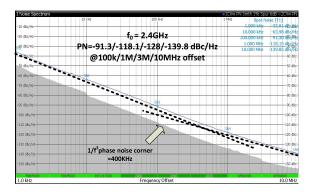

Fig. 18. Blixator phase noise measurement at 1-kHz-10-MHz frequency offsets.

Fig. 19. Injection locking susceptibility due to blockers at  $\omega_{LO}$  and  $2\omega_{LO}$ .

test, the IIP3 varies between -15.5 and -14 dBm over the entire channels. Open-drain buffers are embedded on chip at the oscillator outputs for phase noise measurements. The output of one of the buffers was wire-bonded to a  $50-\Omega$  trace on the test board, whereas the other one was terminated by a 50- $\Omega$  on-chip resistor. The 50- $\Omega$  trace was connected to Rohde & Schwarz FSWP signal-source analyzer for phase noise measurement. Fig. 18 shows the measured phase noise of Blixator for a 2.4-GHz carrier. The measured phase noise of the receiver is -118.1 dBc/Hz at 1-MHz offset, completely meeting the requirements of BLE standard. Fig. 19 reports the susceptibility of the Blixator cell to nearby blockers at  $\omega_{LO}$  and  $2\omega_{LO}$ . Due to the selectivity of the input matching network and topology of the receiver, the Blixator cell is well immune against RF port blockers. The measurements show that at a frequency offset of 1 MHz, the oscillator can be locked only with an input power of -8.5 dBm, which is well above the saturation point of the Blixator receiver.

Table IV summarizes the performance of the Blixator receiver and compares it with some recent state-of-the-art works. Employing only two inductors and one transformer and by using circuit and current-reuse techniques, the Blixator is successful to minimize the total power consumption of the chip. It should be noted that by exploiting lower technology nodes, the power consumption can be even further reduced. As it can be seen from Table IV, the best phase noise performance is achieved, with only  $340-\mu W$  power consumption, while all requirements of the BLE standards are satisfied with reasonable margins.

#### VII. CONCLUSION

A quadrature current-reuse receiver RF front end for low-power applications, consuming only 340  $\mu$ W from a 0.8-V

supply voltage, has been reported. Exploiting current and circuit reuse techniques in the introduced Blixator circuit makes it possible to merge multiple functionalities at low power consumption. The proposed receiver has been completely analyzed, the equations describing gain, impedance matching, NF, and phase noise have been derived, and oscillator locking range has been investigated. Implemented in a 0.18  $\mu$ m CMOS technology node, the proposed receiver achieves the lowest power consumption among state-of-the-art works while occupying small footprint and meeting all the specifications of the BLE standard with reasonable margins.

#### REFERENCES

- [1] H. Liu et al., "An ADPLL-centric Bluetooth low-energy transceiver with 2.3 mW interference-tolerant hybrid-loop receiver and 2.9 mW singlepoint polar transmitter in 65 nm CMOS," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2018, pp. 444–446.

- [2] M. Ding et al., "A 0.8 V 0.8 mm<sup>2</sup> Bluetooth 5/BLE digital-intensive transceiver with a 2.3 mW phase-tracking RX utilizing a hybrid loop filter for interference resilience in 40 nm CMOS," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2018, pp. 446–448.

- [3] Y.-H. Liu et al., "13.2 A 3.7 mW-RX 4.4 mW-TX fully integrated Bluetooth low-Energy/IEEE802.15.4/proprietary SoC with an ADPLLbased fast frequency offset compensation in 40 nm CMOS," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2015, pp. 1–3.

- [4] Y.-H. Liu et al., "24.1 A 770 pJ/b 0.85 V 0.3 mm<sup>2</sup> DCO-based phase-tracking RX featuring direct demodulation and data-aided carrier tracking for IoT applications," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2017, pp. 408–409.

- [5] A. H. M. Shirazi, H. M. Lavasani, M. Sharifzadeh, Y. Rajavi, S. Mirabbasi, and M. Taghivand, "A 980μW 5.2 dB-NF current-reused direct-conversion Bluetooth-low-energy receiver in 40 nm CMOS," in Proc. IEEE Custom Integr. Circuits Conf. (CICC), May 2017, pp. 1–4.

- [6] Y.-H. Liu et al., "A 1.9 nJ/b 2.4 GHz multistandard (Bluetooth low energy/ZigBee/IEEE802.15.6) transceiver for personal/body-area networks," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2013, pp. 446–447.

- [7] Z. Lin, P.-I. Mak, and R. P. Martins, "A 2.4 GHz ZigBee receiver exploiting an RF-to-BB-current-reuse Blixer + hybrid filter topology in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 49, no. 6, pp. 1333–1344, May 2014.

- [8] F.-W. Kuo et al., "A Bluetooth low-energy transceiver with 3.7-mW all-digital transmitter, 2.75-mW high-IF discrete-time receiver, and TX/RX switchable on-chip matching network," IEEE J. Solid-State Circuits, vol. 52, no. 4, pp. 1144–1162, Apr. 2017.

- [9] M. Tamura et al., "30.5 A 0.5 V BLE transceiver with a 1.9 mW RX achieving -96.4 dBm sensitivity and 4.1 dB adjacent channel rejection at 1 MHz Offset in 22 nm FDSOI," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2020, pp. 468-470.

- [10] M. Silva-Pereira, J. T. de Sousa, J. Costa Freire, and J. Caldinhas Vaz, "A 1.7-mW -92-dBm sensitivity low-IF receiver in 0.13-μm CMOS for Bluetooth LE applications," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 1, pp. 332–346, Jan. 2019.

- [11] B. J. Thijssen, E. A. M. Klumperink, P. Quinlan, and B. Nauta, "2.4-GHz highly selective IoT receiver front end with power optimized LNTA, frequency divider, and baseband analog FIR filter," *IEEE J. Solid-State Circuits*, vol. 56, no. 7, pp. 2007–2017, Jul. 2021.

- [12] A. Selvakumar, M. Zargham, and A. Liscidini, "Sub-mW current reuse receiver front-end for wireless sensor network applications," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 2965–2974, Dec. 2015.

- [13] E. Hegazi, H. Sjoland, and A. A. Abidi, "A filtering technique to lower LC oscillator phase noise," *IEEE J. Solid-State Circuits*, vol. 36, no. 12, pp. 1921–1930, Dec. 2001.

- [14] A. Mazzanti and P. Andreani, "Class-C harmonic CMOS VCOs, with a general result on phase noise," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2716–2729, Dec. 2008.

- [15] L. Fanori and P. Andreani, "Class-D CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3105–3119, Dec. 2013.

- [16] M. Babaie and R. B. Staszewski, "A class-F CMOS oscillator," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3120–3133, Dec. 2013.

- [17] M. Babaie and R. B. Staszewski, "An ultra-low phase noise class-F2 CMOS oscillator with 191 dBc/Hz FoM and long-term reliability," *IEEE J. Solid-State Circuits*, vol. 50, no. 3, pp. 679–692, Mar. 2015.

- [18] D. Murphy, H. Darabi, and H. Wu, "Implicit common-mode resonance in LC oscillators," *IEEE J. Solid-State Circuits*, vol. 52, no. 3, pp. 812–821, Mar. 2017.

- [19] K. Kwok and H. C. Luong, "Ultra-low-voltage high-performance CMOS VCOs using transformer feedback," *IEEE J. Solid-State Circuits*, vol. 40, no. 3, pp. 652–660, Mar. 2005.

- [20] A. Mostajeran, M. S. Bakhtiar, and E. Afshari, "25.8 A 2.4 GHz VCO with FOM of 190 dBc/Hz at 10 kHz-to-2 MHz offset frequencies in 0.13μm CMOS using an ISF manipulation technique," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2015, pp. 1–3.

- [21] O. El-Aassar and G. M. Rebeiz, "A 350 mV complementary 4-5 GHz VCO based on a 4-Port transformer resonator with 195.8 dBc/Hz peak FOM in 22 nm FDSOI," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2019, pp. 159–162.

- [22] O. El-Aassar and G. M. Rebeiz, "26.5 A 0.1-to-0.2 V transformer-based switched-mode folded DCO in 22 nm FDSOI with active step-down impedance achieving 197 dBc/Hz peak FoM and 40 MHz/V frequency pushing," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2019, pp. 416–418.

- [23] C. C. Lim, H. Ramiah, J. Yin, P.-I. Mak, and R. P. Martins, "An inverse-class-F CMOS oscillator with intrinsic-high-Q first harmonic and second harmonic resonances," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3528–3539, Dec. 2018.

- [24] F. Wang and H. Wang, "A noise circulating oscillator," *IEEE J. Solid-State Circuits*, vol. 54, no. 3, pp. 696–708, Mar. 2019.

- [25] M. Barzgari, A. Ghafari, A. Nikpaik, and A. Medi, "Even-harmonic class-E CMOS oscillator," *IEEE J. Solid-State Circuits*, early access, Nov. 18, 2021, doi: 10.1109/JSSC.2021.3124971.

- [26] A. Liscidini, A. Mazzanti, R. Tonietto, L. Vandi, P. Andreani, and R. Castello, "Single-stage low-power quadrature RF receiver frontend: The LMV cell," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2832–2841, Dec. 2006.

- [27] M. Tedeschi, A. Liscidini, and R. Castello, "Low-power quadrature receivers for ZigBee (IEEE 802.15.4) applications," *IEEE J. Solid-State Circuits*, vol. 45, no. 9, pp. 1710–1719, Sep. 2010.

- [28] H. Yi, W.-H. Yu, P.-I. Mak, J. Yin, and R. P. Martins, "A 0.18-V 382-µW Bluetooth low-energy receiver front-end with 1.33-nW sleep power for energy-harvesting applications in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 53, no. 6, pp. 1618–1627, Jun. 2018.

- [29] F. Piazza and Q. Huang, "A high linearity, single-ended input double-balanced mixer in 0.25 μm CMOS," in *Proc. 24th Eur. Solid-State Circuits Conf.*, Sep. 1998, pp. 60–63.

- [30] S. S. K. Ho and C. E. Saavedra, "A low-noise self-oscillating mixer using a balanced VCO load," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 8, pp. 1705–1712, Aug. 2011.

- [31] S. Chehrazi, A. Mirzaei, and A. A. Abidi, "Noise in current-commutating passive FET mixers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 2, pp. 332–344, Feb. 2010.

- [32] A. Hajimiri and T. H. Lee, "A general theory of phase noise in electrical oscillators," *IEEE J. Solid-State Circuits*, vol. 33, no. 2, pp. 179–194, Feb. 1998.

- [33] J. Bank, "A harmonic-oscillator design methodology based on describing functions," in *Doktorsavhandlingar vid Chalmers Tekniska Hogskola*. Gothenburg, Sweden: Department of Signals and Sytems, Circuit Design Group, Chalmers University of Technology, 2006, pp. 1–225.

- [34] B. Hong and A. Hajimiri, "A general theory of injection locking and pulling in electrical oscillators—Part I: Time-synchronous modeling and injection waveform design," *IEEE J. Solid-State Circuits*, vol. 54, no. 8, pp. 2109–2121, Aug. 2019.

- [35] B. Hong and A. Hajimiri, "A general theory of injection locking and pulling in electrical oscillators—Part II: Amplitude modulation in LC oscillators, transient behavior, and frequency division," *IEEE J. Solid-State Circuits*, vol. 54, no. 8, pp. 2122–2139, Aug. 2019.

- [36] A. Mirzaei et al., "The quadrature LC oscillator: A complete portrait based on injection locking," IEEE J. Solid-State Circuits, vol. 42, no. 9, pp. 1916–1932, Aug. 2007.

- [37] B. Razavi, "A study of injection locking and pulling in oscillators," *IEEE J. Solid-State Circuits*, vol. 39, no. 9, pp. 1415–1424, Sep. 2004.

- [38] W. Deng, K. Okada, and A. Matsuzawa, "Class-C VCO with amplitude feedback loop for robust start-up and enhanced oscillation swing," *IEEE J. Solid-State Circuits*, vol. 48, no. 2, pp. 429–440, Feb. 2013.

- [39] A. D. Berny, A. M. Niknejad, and R. G. Meyer, "A 1.8-GHz LC VCO with 1.3-GHz tuning range and digital amplitude calibration," *IEEE J. Solid-State Circuits*, vol. 40, no. 4, pp. 909–917, Apr. 2005.

Mohammad Barzgari (Student Member, IEEE) received the B.Sc. and M.Sc. degrees in electrical engineering from the Sharif University of Technology, Tehran, Iran, in 2014 and 2016, respectively, where he is currently pursuing the Ph.D. degree in microelectronics.

His research interests include RF and microwave integrated circuit design, phased array systems, and CMOS mixed-mode analog circuits.

**Ali Ghafari** (Associate Member, IEEE) is currently pursuing the Ph.D. degree with the Delft University of Technology, Delft, The Netherlands.

He is currently a Researcher at the Qutech Group, Delft University of Technology.

Masoud Meghdadi (Member, IEEE) received the B.Sc. degree in electrical engineering from the Amirkabir University of Technology, Tehran, Iran, in 2005, and the M.Sc. and Ph.D. degrees in electrical engineering from the Sharif University of Technology, Tehran, in 2007 and 2013, respectively.

He is currently an Assistant Professor with the Faculty of Electrical Engineering, Shahid Beheshti University, Tehran. His current research interests include high-frequency, analog, and mixed-mode circuits and systems.

Ali Medi (Senior Member, IEEE) received the B.Sc. degree from the Sharif University of Technology, Tehran, Iran, in 2001, and the M.Sc. and Ph.D. degrees in electrical engineering from the University of Southern California, Los Angeles, CA, USA, in 2003 and 2007, respectively.

He was a Research Assistant with the UltRa-Lab, University of South California, where he was involved in the fields of analog and RF circuit design for ultrawideband systems. He was with Broadcom Corporation, San Jose, CA, USA, where he was

involved in the development of RF blocks for GSM cell phone transceivers. He is currently a Professor with the Electrical Engineering Department, Sharif University of Technology. His current research interests include RF and microwave integrated circuits and wideband analog circuit design.