# MSc THESIS

## Flash Memory Device: Electrical Modeling and Simulation

Ronnie Klanderman

CE-MS-2012-15

#### Abstract

Flash memory, created in the early eighties and based upon EEP-ROM, has become a very popular non-volatile memory since the start of the millennium. A Flash memory cell consists of 1 MOS transistor with a floating gate. The floating gate (in between the channel and the control gate) is able to trap electrons due to writing mechanisms (e.g. Fowler Nordheim and Channel Hot Electron Injection) and hereby changing the threshold level of the transistor. Flash also has different cell array architectures that define its read and write speed, and geometrical size. The array architectures called NOR and NAND are currently most popular. NOR is advantageous for high speed read and writing, however the NAND architecture is more compact and therefore more suitable for mass data storage. By creating a functional model of a Flash memory device, design of an electrical Flash memory device and its simulation can be simplified. After studying Flash cell models in literature, a Flash cell model and complete memory device will be presented in this Thesis. This study has also led to distinction between "Static" and "Dynamic" Flash cell models. Static models need a voltage or current source to change the threshold voltage. This results in 2 models, one for writing and another for reading. Dynamic models can use equations

as behavioral blocks to ensure a threshold voltage change at the transistor and have one model to represent both reading and writing. In order to show simulation results of a Flash memory device, a 2x2 bit NOR and 1x2 bit NAND will be presented for analysis. Both with a dynamic cell model. Fowler Nordheim and Channel Hot Electron Injection are also taken into account in the presented net lists. The simulations have been done in HSPICE, an industrial version of SPICE (Simulation Program with Integrated Circuit Emphasis).

# Flash Memory Device: Electrical Modeling and Simulation

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE

$\mathrm{in}$

#### COMPUTER ENGINEERING

by

Ronnie Klanderman born in Mombasa, Kenia

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

### Flash Memory Device: Electrical Modeling and Simulation

#### by Ronnie Klanderman

#### Abstract

**lash** memory, created in the early eighties and based upon EEPROM, has become a very popular non-volatile memory since the start of the millennium. A Flash memory cell consists of 1 MOS transistor with a floating gate. The floating gate (in between the channel and the control gate) is able to trap electrons due to writing mechanisms (e.g. Fowler Nordheim and Channel Hot Electron Injection) and hereby changing the threshold level of the transistor. Flash also has different cell array architectures that define its read and write speed, and geometrical size. The array architectures called NOR and NAND are currently most popular. NOR is advantageous for high speed read and writing, however the NAND architecture is more compact and therefore more suitable for mass data storage. By creating a functional model of a Flash memory device, design of an electrical Flash memory device and its simulation can be simplified. After studying Flash cell models in literature, a Flash cell model and complete memory device will be presented in this Thesis. This study has also led to distinction between "Static" and "Dynamic" Flash cell models. Static models need a voltage or current source to change the threshold voltage. This results in 2 models, one for writing and another for reading. Dynamic models can use equations as behavioral blocks to ensure a threshold voltage change at the transistor and have one model to represent both reading and writing. In order to show simulation results of a Flash memory device, a 2x2 bit NOR and 1x2 bit NAND will be presented for analysis. Both with a dynamic cell model. Fowler Nordheim and Channel Hot Electron Injection are also taken into account in the presented net lists. The simulations have been done in HSPICE, an industrial version of SPICE (Simulation Program with Integrated Circuit Emphasis).

| Laboratory<br>Codenumber | Computer Engineering<br>CE-MS-2012-15 |  |  |  |  |

|--------------------------|---------------------------------------|--|--|--|--|

| Committee Members        | :                                     |  |  |  |  |

| Advisor:                 | Dr. Ir. Zaid Al-Ars, CE, TU Delft     |  |  |  |  |

| Chairperson:             | Dr. Koen Bertels, CE, TU Delft        |  |  |  |  |

| Member:                  | Dr. Ryoichi Ishihara, EE, TU Delft    |  |  |  |  |

| Member:                  | Dr. Ir. Michiel Pertijs, EE, TU Delft |  |  |  |  |

# Contents

| List of Figures  | vi  |

|------------------|-----|

| List of Tables   | vii |

| Acknowledgements | ix  |

| 1        | Intr | oduction                             | L |

|----------|------|--------------------------------------|---|

|          | 1.1  | Memory Technology                    | L |

|          |      | 1.1.1 Magnetic Devices               | 2 |

|          |      | 1.1.2 Optical Devices                | 2 |

|          |      | •                                    | 3 |

|          | 1.2  |                                      | 3 |

|          | 1.3  | Introduction to the Flash Cell       | 7 |

|          | 1.4  | Thesis Objective and Outline         | 3 |

| <b>2</b> | Flas | h Cell and Array Architecture        | • |

|          | 2.1  | Flash Memory Cell                    | ) |

|          |      | 2.1.1 Flash Cell Threshold Voltage   | ) |

|          |      | 2.1.2 Multi-Level Flash Cell         | 2 |

|          | 2.2  | Flash Writing                        | 3 |

|          |      | 2.2.1 Erasing a Flash cell           | 3 |

|          |      | 2.2.2 Programming a Flash Cell       | 1 |

|          |      | 2.2.3 Reading a Flash cell           | 1 |

|          |      | 2.2.4 Flash Writing Management       | 3 |

|          | 2.3  | Flash Writing Mechanisms             | 3 |

|          |      | 2.3.1 CHEI                           | 3 |

|          |      | 2.3.2 FN Tunneling                   | 3 |

|          | 2.4  | Flash Array Architectures            | ) |

|          |      | 2.4.1 NOR Architecture               | ) |

|          |      | 2.4.2 NAND Architecture              | ) |

|          |      | 2.4.3 AND Architecture               | 2 |

|          |      | 2.4.4 DINOR Architecture             | 3 |

|          |      | 2.4.5 Array Architecture Overview    | 3 |

|          | 2.5  | Flash Process Technology             | 1 |

| 3        | Flas | h Memory Device 27                   | 7 |

|          | 3.1  | Memory Modeling                      | 7 |

|          | 3.2  | Functional Flash Memory Device       | ) |

|          |      | 3.2.1 Reading and Writing in the FFM | ) |

|          |      | 3.2.2 Basic Functional Flash Model   | 1 |

|              |                                                                    | 3.2.3 Flash Memory Device Model                                                                                                                                                                                                                   | 32                                                              |

|--------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 4            | <b>Elec</b><br>4.1<br>4.2                                          | Overview Flash Cell Modeling                                                                                                                                                                                                                      | <b>37</b><br>37<br>38<br>39<br>39                               |

|              |                                                                    | 4.2.3       Larcher et. al.                                                                                                                                                                                                                       | $40 \\ 40 \\ 42$                                                |

|              | 4.3                                                                | 4.2.6 Published Overview                                                                                                                                                                                                                          | 43<br>43                                                        |

| 5            | <ul> <li>Mod 5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul> | Flash Memory Periphery Blocks5.1.1 Decoder5.1.2 Flash Cell5.1.3 Sense Amplifier5.1.3 Sense AmplifierFlash Memory Model: 1 Bit ISFC5.2.1 Simulation ResultsFlash Memory Model: 2x2 Bit NOR5.3.1 Simulation ResultsFlash Memory Model: 2x1 Bit NAND | <b>45</b><br>45<br>45<br>47<br>48<br>49<br>51<br>53<br>56<br>58 |

| 6            | <b>Con</b><br>6.1<br>6.2                                           | Conclusion                                                                                                                                                                                                                                        | <b>61</b><br>61<br>61                                           |

| $\mathbf{A}$ | Net                                                                | list: 1 bit ISFC                                                                                                                                                                                                                                  | 63                                                              |

| В            | $\mathbf{Net}$                                                     | list: 2x2 bit NOR                                                                                                                                                                                                                                 | 67                                                              |

| С            | $\mathbf{Net}$                                                     | list: 2x1 bit NAND                                                                                                                                                                                                                                | 71                                                              |

| Bi           | ibliog                                                             | raphy                                                                                                                                                                                                                                             | 74                                                              |

# List of Figures

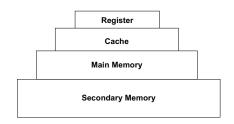

| 1.1  | memory hierarchy levels                                                                           | 2  |

|------|---------------------------------------------------------------------------------------------------|----|

| 1.2  | main memory technology categories                                                                 | 2  |

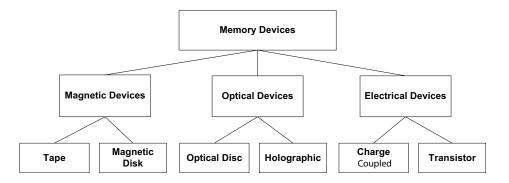

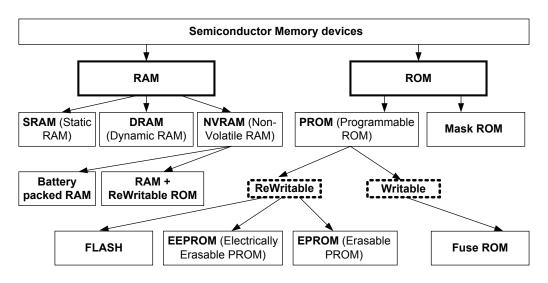

| 1.3  | RAM and ROM devices                                                                               | 4  |

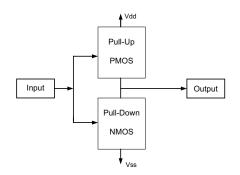

| 1.4  | CMOS circuit                                                                                      | 4  |

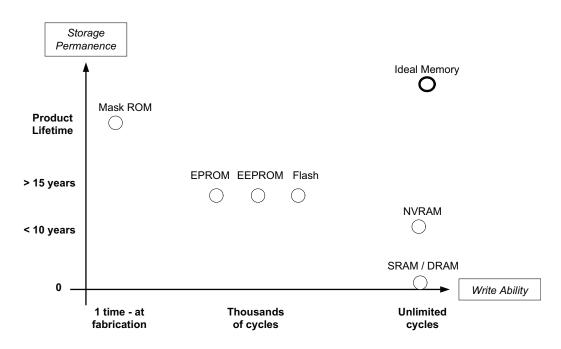

| 1.5  | storage permanence and write ability of transistor based memory; [21]                             | 5  |

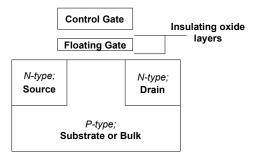

| 1.6  | basic 1T cell storage device                                                                      | 7  |

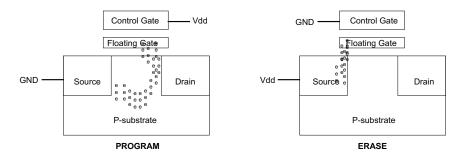

| 1.7  | writing a 1T flash cell storage device                                                            | 8  |

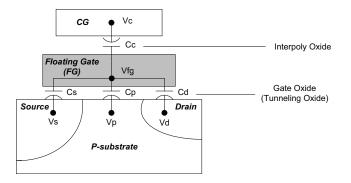

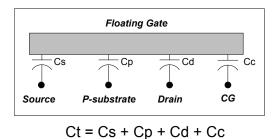

| 2.1  | schematic cross section and electrical model of an FG device                                      | 10 |

| 2.2  | parallel capacitors in an FG device model                                                         | 11 |

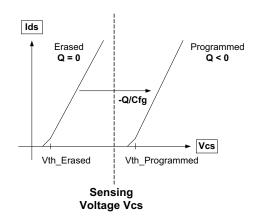

| 2.3  | I-V characteristics of an FG device                                                               | 12 |

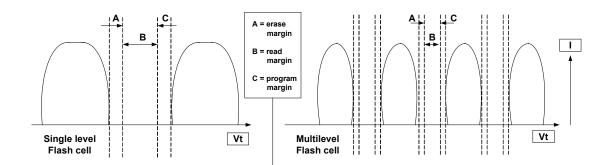

| 2.4  | single and multi-level Flash cell margins                                                         | 13 |

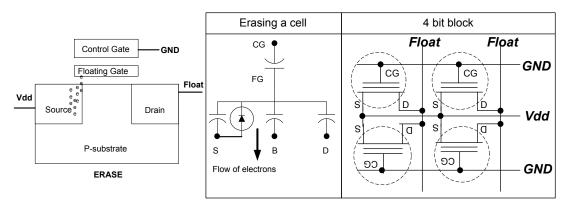

| 2.5  | erasing a Flash cell                                                                              | 14 |

| 2.6  | programming a Flash cell                                                                          | 14 |

| 2.7  | reading a Flash cell                                                                              | 15 |

| 2.8  | timing diagram writing process                                                                    | 15 |

| 2.9  | blocks and corresponding words of NOR                                                             | 15 |

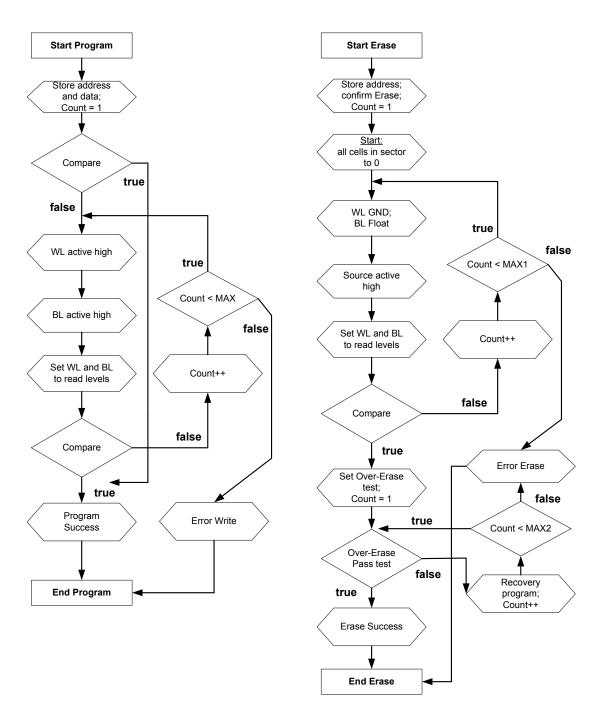

| 2.10 | writing method flow chart                                                                         | 17 |

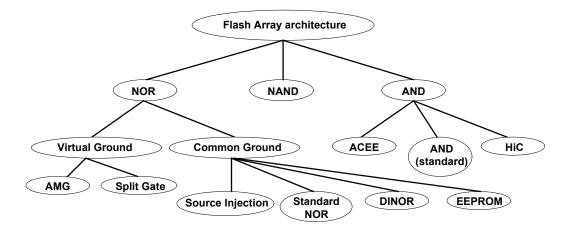

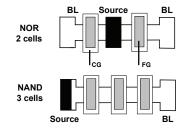

|      | Flash array architecture overview                                                                 | 19 |

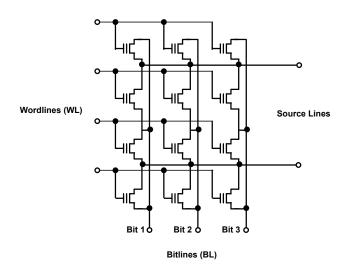

| 2.12 | NOR architecture                                                                                  | 20 |

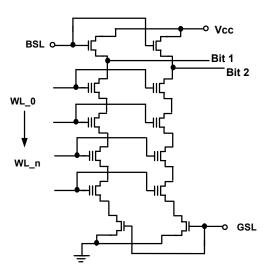

| 2.13 | NAND architecture                                                                                 | 21 |

| 2.14 | NOR and NAND cell placement comparison; simple geometrical view                                   | 22 |

| 2.15 | AND architecture                                                                                  | 22 |

| 2.16 | DINOR architecture                                                                                | 23 |

| 2.17 | silicon wafer; front end: simplified process of circuit preparation                               | 25 |

| 3.1  | abstract modeling levels; [16]                                                                    | 28 |

| 3.2  | functional $(S/D)$ RAM model; [16]                                                                | 28 |

| 3.3  | reduced functional $(S/D)RAM$ model; [16]                                                         | 29 |

| 3.4  | functional Flash model $(FFM)$                                                                    | 30 |

| 3.5  | reduced functional Flash model $(RFFM)$                                                           | 31 |

| 3.6  | simplified FFM that adheres to RFFM                                                               | 32 |

| 3.7  | basic functional Flash model (BFFM)                                                               | 33 |

| 3.8  | Flash cell cross section; $[11]$                                                                  | 33 |

| 3.9  | layout of a 64 Mb Flash memory device; [11]                                                       | 34 |

| 3.10 | simplified layout of a sector from Figure 3.9                                                     | 34 |

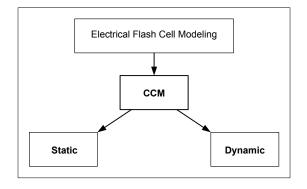

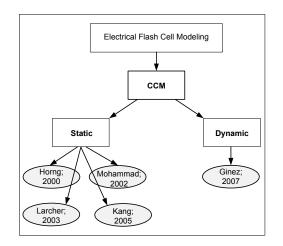

| 4.1  | types of electrical Flash cell modeling $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 37 |

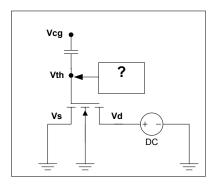

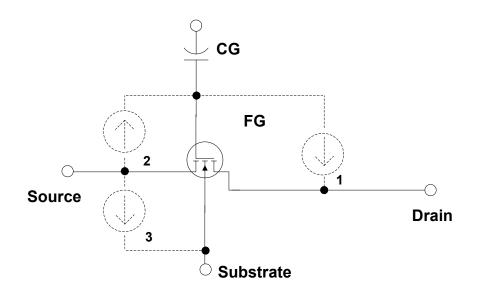

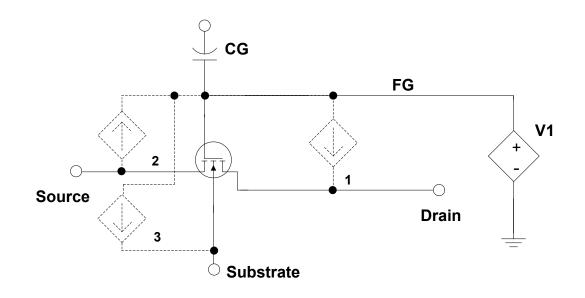

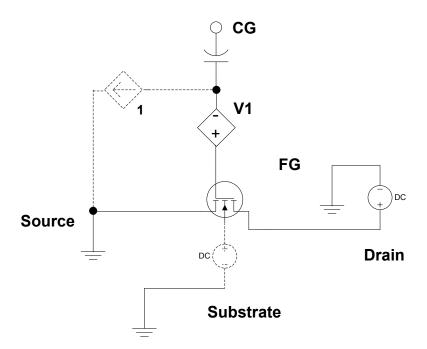

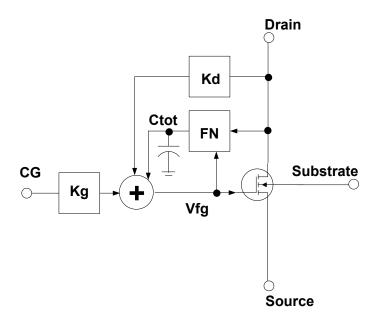

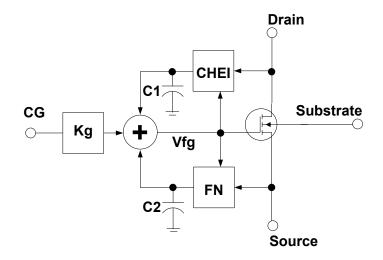

| 4.2  | FG component(s) to simulate writing mechanism                                                     | 38 |

| 4.3  | electrical Flash cell by Horng et. al                                                             | 39 |

| 4.4  | electrical Flash cell by Mohammad                                                                 | 40 |

| 4.5  | electrical Flash cell by Larcher et. al                                                           | 41 |

| 4.6  | electrical Flash cell by Kang et. al                                                                     | . 41 |

|------|----------------------------------------------------------------------------------------------------------|------|

| 4.7  | electrical Flash cell by Mauroux et. al. and Ginez                                                       | . 42 |

| 4.8  | published Flash cell overview                                                                            | . 43 |

| 4.9  | industry standard electrical Flash cell $\hfill \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | . 44 |

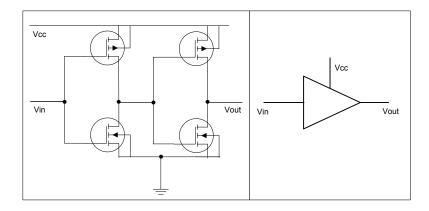

| 5.1  | buffer - 2 cascaded inverters                                                                            | . 46 |

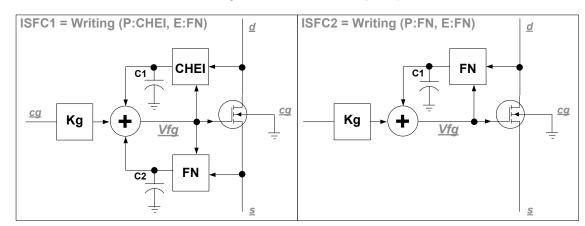

| 5.2  | ISFC types                                                                                               | . 47 |

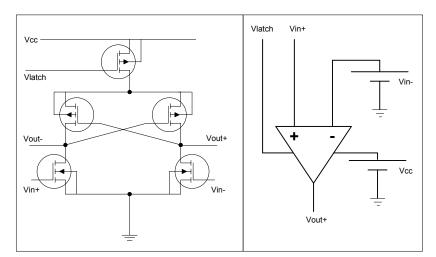

| 5.3  | sense amplifier - latched comparator                                                                     | . 48 |

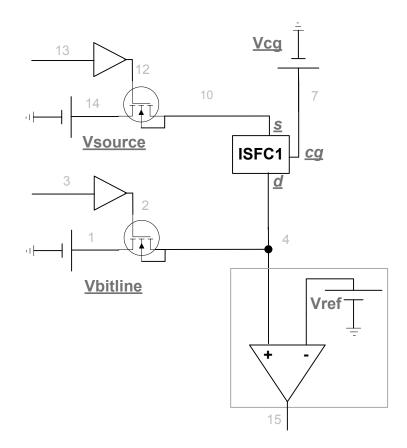

| 5.4  | NOR array type BFFM - 1 cell ISFC1                                                                       | . 49 |

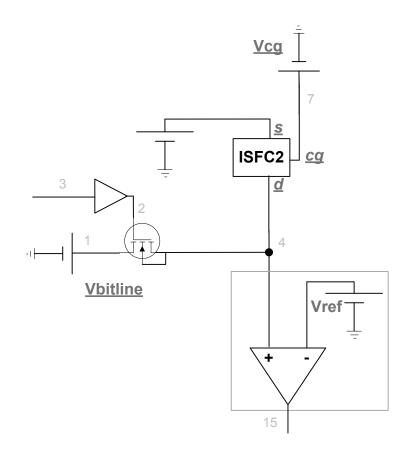

| 5.5  | NAND array type BFFM - 1 cell ISFC2                                                                      |      |

| 5.6  | NOR cell states                                                                                          | . 50 |

| 5.7  | NAND cell states                                                                                         |      |

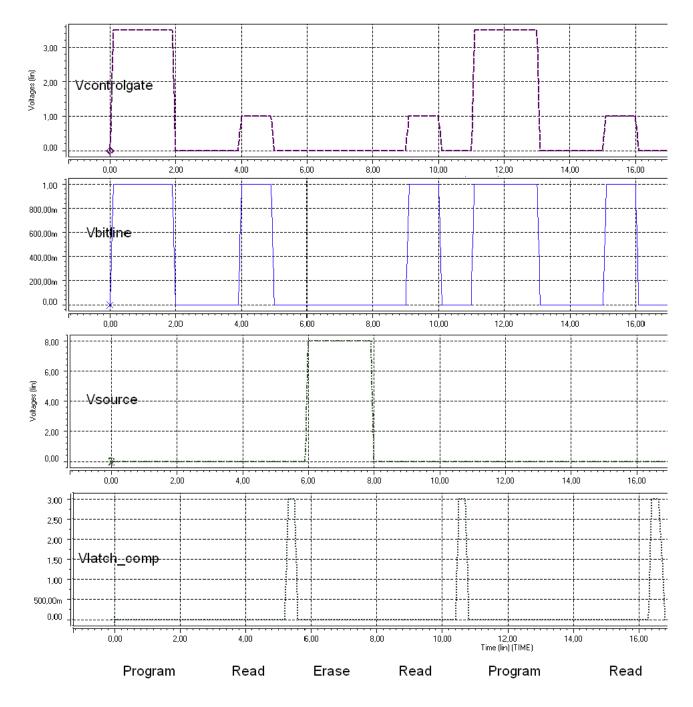

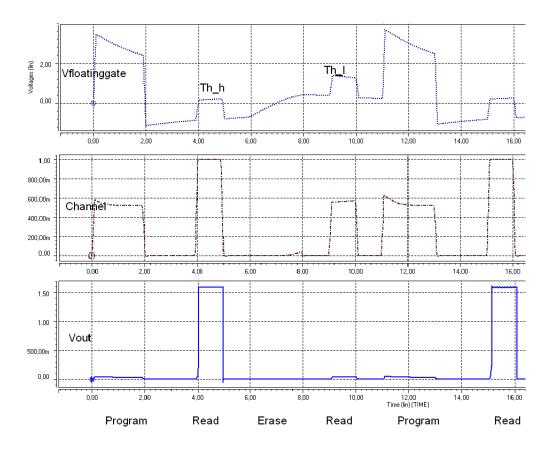

| 5.8  | 1 bit ISFC: program, erase and read - $1/2$                                                              | . 52 |

| 5.9  | 1 bit ISFC: program, erase and read - $2/2$                                                              | . 53 |

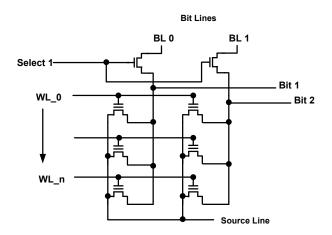

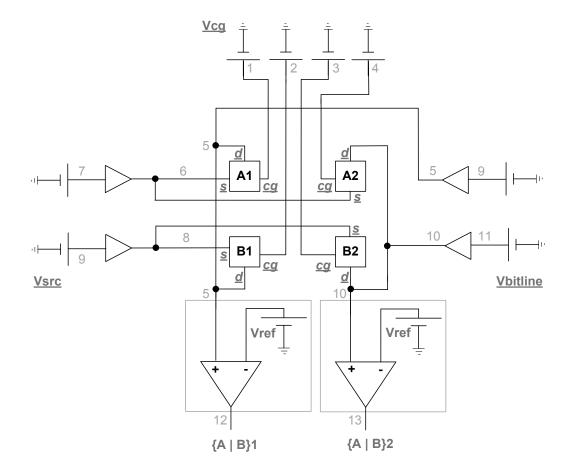

| 5.10 | 2x2 NOR array                                                                                            | . 54 |

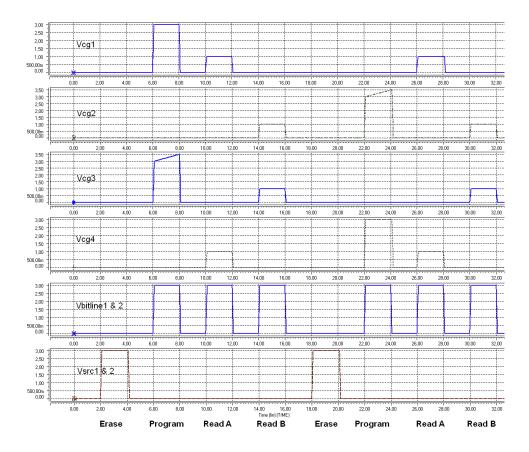

| 5.11 | 2x2 NOR: erase, program and read - $1/2$                                                                 | . 55 |

| 5.12 | $2 \times 2 \times 2$ NOR: erase, program and read - $2/2 \ldots \ldots \ldots \ldots \ldots \ldots$     | . 56 |

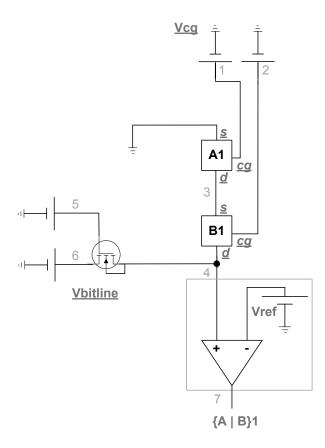

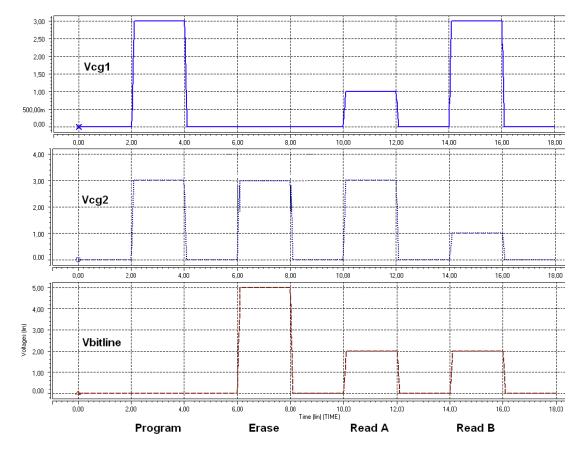

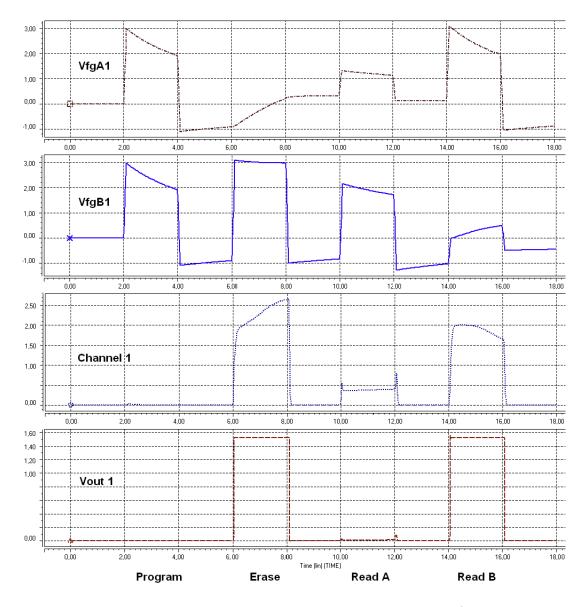

| 5.13 | 2x1 NAND array                                                                                           | . 57 |

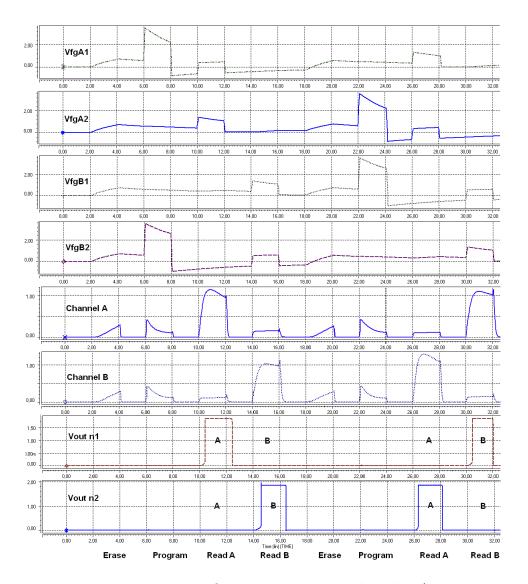

| 5.14 | $1x^2$ NAND: erase, program and read - $1/2$                                                             | . 59 |

| 5.15 | 1x2 NAND: erase, program and read - $2/2$                                                                | . 60 |

|      |                                                                                                          |      |

# List of Tables

| 1.1 | characteristics of different transistor based memories; [1] [4] [18] [21] $\ldots$ | 6  |

|-----|------------------------------------------------------------------------------------|----|

| 2.1 | generations of the Flash memory cell                                               | 13 |

| 2.2 | Flash memory manufacturers in the late nineties                                    | 19 |

| 2.3 | NOR read and write voltages; [4]                                                   | 20 |

| 2.4 | NAND read and write voltages; [4]                                                  |    |

| 2.5 | AND read and write voltages; [4]                                                   | 23 |

| 2.6 | figures of merit of popular Flash array architectures                              | 24 |

| 2.7 | basic process flow of Flash technology; [4]                                        | 25 |

| 5.1 | 1 bit ISFC table                                                                   | 51 |

| 5.2 | source values of the NOR array                                                     | 54 |

| 5.3 | 2x2 NAND simulation results                                                        | 55 |

| 5.4 | source values of the NAND array                                                    | 58 |

## Acknowledgements

Three months before I was supposed to graduate in 2009 I took on a job as Software Engineer with a contracting company. It was just before the financial crisis hit our economy. I was happy to get a good offer because it somewhat changed after this event and good offers in the IT market declined for people fresh from University or College.

This choice resulted in me not finishing my Thesis that year and due to working on my career and experiencing all the changes in life, I procrastinated and almost quit. I still had to finish 2 more chapters to complete it. 2010 came and went and I still didn't manage to do anything. I think being ashamed for being idle and very busy with work at the same time prevented me from discussing it with my supervisor. Prolonging it felt safe until it became too painful. Somehow I finally contacted my supervisor and to my surprise he gave me another chance to complete my work. "It's up to you" he said. He was right. Making a choice can change everything.

Thank you Dr. Ir. Zaid Al-Ars for giving me this second chance and for our many late night discussions. Memories of going to class have been replaced by packing dinner and eating it while driving to Delft after my work day ended. We would then discuss models and I learned a lot from how you structure and reason. Also, I would like to thank Marjolijn for her patience and support. Last but not least, thank you Mother for all you have done for me. Thanks everyone.

Ronnie Klanderman Delft, The Netherlands October 8, 2012

# 1

We live in a world of growing possibilities regarding communication and computation. All this is made possible by computers with three general features: data exchange (in/out), data processing (logic) and data storage (memory). As the field of Computer Engineering keeps on advancing, computers are becoming more efficient at all three of these features. The future of computing devices is one where memory (which is already a substantial part of many devices) will increase even more with respect to logic. [6] While facilitating more memory on integrated circuits, we also aim at improving their general features. When storing more data however we also tend to create more faults in the creation of memory cells due to complicated processes. To study these kind of introduced and other faults, we can use electrical models to simulate them.

Flash memory devices were introduced in the eighties [3] and have become quite popular since then. Increasingly more products are using Flash memory technology. It is becoming more difficult to name digital devices without Flash memory. Flash's popularity is mainly due to its property of retaining binary digits (*bits*) without the need of a continuous power source. As soon as it is written (programmed or erased), it only requires power for its bits to be read. In this Thesis, we discuss the development of an electrical Flash memory model.

In the first section of this chapter, we will look at general memory technologies. In Section 1.2 we will explore transistor based memory devices and in Section 1.3 we will look at Flash memory technology. In Section 1.4 we will look at the objectives of this project and we will end this chapter with a section that outlines the rest of the Thesis.

#### 1.1 Memory Technology

Memory for computing devices can be categorized in several hierarchies. We categorize memory type to specify the different storage locations of data during the processing of an instruction. In Figure 1.1 we distinguish four levels in this hierarchy of types. Register level is shown at the top and is considered to be the fastest accessible memory. At the lower end of Figure 1.1 we see the slowest accessible memory.

We can classify memories in three main memory technology categories shown in Figure 1.2. We will briefly discuss these memory technologies and go into more details of transistor based memory devices in Section 1.2. Flash memory is transistor based.

Figure 1.1: memory hierarchy levels

#### 1.1.1 Magnetic Devices

Magnetic memory devices hold the highest market share in the computer industry and is also the oldest data storage technology. Magnetic tape devices store large quantities of data at relatively low costs. It uses an inductive head that translates incoming electrical signals to a magnetic field which is captured on moving tape. This tape is sensitive to the magnetic variations, thus registering data. However, the performance of magnetic tape is far from ideal and can wear out because of the constant exposure to the inductive head. By innovating magnetic tape, the idea of a magnetic disk came to pass. It uses a low mass slider. This slider has an inductive head that floats at a precise distance from the magnetic medium. Magnetic disks are still the most common storage devices in desktop computers. However, solid state disks (a Flash memory device) are gaining in popularity and will soon probably replace magnetic disks in computer sales. Magnetic memory devices generally represent the lower part of the memory hierarchy system depicted in Figure 1.1. We call this secondary memory.

Figure 1.2: main memory technology categories

#### 1.1.2 Optical Devices

Optical memory devices are also well represented as storage devices in the computer industry. Most popular are the optical disc's (e.g. CD-ROM, DVD-ROM). When buying software, e.g. office applications and games, consumers mostly acquire it via the optical disc. With the disc, data is written onto the surface by using dots and spaces. A laser beam then detects the stream of bits by their reflection while rotating. As for holographic storage devices, they mainly store data as images in crystals by using a laser beam to change the refractive index of the crystal. Similar to magnetic memory devices, optical memory devices are part of the lowest memory hierarchy shown in Figure 1.1.

#### 1.1.3 Electrical Devices

Of the electrical devices category, the *CCD* (Charge Coupled Devices) is quite a niche in the computer industry. CCD's control the electrical charge from and to a memory element. The electrical charge in this device determines the logic level it holds. CCD's are also serially accessed, which is slower than random access of memory cells in parallel. We commonly find these devices in the field of digital imaging and they are also placed in the lower memory hierarchy shown in Figure 1.1.

For fast read and write times regarding data storage, transistor based devices are better suited than the previous ones. In fact, they have the best read and write time compared to all the other devices discussed. Transistor based memory devices are used extensively on and near data processing units. These devices dominate the upper three parts of the memory hierarchy in Figure 1.1. We will look at the transistor based memory devices in the next section. Transistor based memory is made in the semiconductor industry. In the semiconductor industry, memory devices are either categorized as RAM (Random Access Memory) or ROM (Read Only Memory) as shown in Figure 1.3. Also, semiconductor memory devices can be distinguished in two types, namely volatile and non-volatile memory. RAM memory has a volatile nature and ROM memory non-volatile. Volatile memory need continuous power to retain data, i.e. the transistor based circuit requires power to keep the data of its cells. Non-volatile memory retains data after it has been written (i.e. programmed or erased). A cell represents the smallest quantity of data in a memory device, i.e. a bit. Flash memory cells however are capable of storing n bits in a single cell. We will discuss this concept later after we discuss the different memory types depicted in Figure 1.3 in the next section.

#### 1.2 Transistor Based Memory Devices

Transistors are elementary building blocks in computer systems. They function as switches and by grouping specific types we obtain the logic and memory that builds an electrical system. The transistors used in high density memory devices such as Flash memory devices are called MOS (Metal Oxide Semiconductor) transistors. MOS transistors are available in two types, NMOS (Negative MOS) where a given voltage at the gate causes it to conduct electricity between gate and source, and a voltage below this given value closes it from conducting. PMOS (Positive MOS) works the other way around, where a given voltage at the gate stops it form conducting electricity between gate and source. NMOS is currently more used due to its operational speed. It switches faster. Both MOS transistors combined make a CMOS (Complementary MOS) circuit and this combination is frequently used in the current semiconductor

Figure 1.3: RAM and ROM devices

industry. The basic layout of a CMOS circuit is depicted in Figure 1.4. CMOS circuits are especially popular to use due to low power consumption. Figure 1.4 is either pulled up or down. By constructing combinations of CMOS circuits we are able to create logical gates, e.g. NAND and NOR. In turn, these logical gates are the building blocks of contemporary digital circuits that make up our computing systems.

Figure 1.4: CMOS circuit

Let us look at the *write ability* of memory. This is the number of times that a memory can be written, e.g. programmed (i.e. logical 1) or erased (i.e. logical 0). We can also look at memory in terms of *storage permanence*, which refers to the duration of reliably retaining data in memory cells when power is disconnected. Intuitively, we can say that an ideal memory device is one with an unlimited write ability and infinite storage permanence. Figure 1.5 depicts an overview of write ability and storage permanence of transistor based memories.

Figure 1.5 shows that SRAM (Static RAM) and DRAM (Dynamic RAM) have an unlimited write ability. However the storage permanence is almost zero in time, thus

Figure 1.5: storage permanence and write ability of transistor based memory; [21]

marking these memories as volatile devices. Flash is limited to thousands of cycles of data writing. Its storage permanence results in at least a decade of reliable data storage, marking Flash as a non-volatile memory device. We will briefly discuss the memories depicted in Figure 1.5 and go into more details regarding Flash memory in the next section.

Mask ROM is by far the most durable memory type with the lowest programmability. The internal logic is programmed at fabrication time by using a set of masks. The memory lookup table that will be hard wired is one that must be tested extensively before fabrication and the number of these memory chips produced for each programmed lookup table should be relatively large because of the production costs.

EPROM (Electrically Programmable ROM) is a programmable ROM with a transistor that uses an FG (Floating Gate). An FG is able to trap charge on an isolated plate. This plate is surrounded by an oxide layer that traps electrons. The electrons are injected into the FG by using a high programming voltage, approximately 20 V. To erase data, this charge must be drained from the FG. An EPROM has an erase window that enables charge drainage by exposing the cell to rays of ultraviolet light for a certain time, i.e. 5 to 30 minutes. An EPROM is written in total. This means all memory cells are involved in the write process. Table 1.1 depicts the characteristic of this transistor based memory.

An *EEPROM* (Electrically Erasable PROM) is programmed and erased electrically. The efforts put into making EPROM electrically erasable has led to the EEPROM. Like the EPROM, it also has an FG that can trap and drain charge. EEPROM devices can write words of data, which is more effective than the EPROM. Also, due to its electrical erasing and programming of words, write times are considerably faster. Table 1.1 depicts the characteristic of this memory type.

*Flash* memory is an extension of the (x)PROM family. Similar to the others it uses an FG to trap charge. Flash devices can program or erase individual blocks of words. Making it even more effective than the EEPROM. This capability can improve write times when dealing with a large number of data. Table 1.1 depicts the characteristic of this transistor based memory. We will discuss more of the Flash cell in Chapter 2.

SRAM uses a flip-flop structure of generally 4 to 6 transistors to make up a cell. The name static is coined because this memory stores data (logical 0 or 1) as long as the transistors are powered. SRAM is used for high performance data traffic, e.g. cache memory, due to its fast write times. SRAM is represented in the upper 2 memory hierarchy levels depicted in Figure 1.1. Its characteristics are also depicted in Table 1.1.

DRAM uses a transistor and a capacitor to store cell data. This charge storage however is of temporary nature and the capacitor needs to be recharged due to the gradual leakage of power. Its design is very compact compared to SRAM but needs refreshing. A DRAM cell's refresh rate is in the magnitude of microseconds. The third memory hierarchy level namely main memory, is represented by DRAM. This is shown in Figure 1.1. Table 1.1 also depicts the characteristic of this transistor based memory.

*NVRAM* (Non-Volatile RAM) devices can be divided in two groups, the battery packed RAM and the combination of RAM with ROM. The battery packed RAM contains an SRAM with its own power supply that can last for as long as 10 years. The RAM with ROM combination stores its complete RAM content into an EEPROM just before the power supply is turned off. It reloads this content from the EEPROM back into the RAM when the power goes back on. These hybrid memory types may prove to be advantageous in the near future.

| Criterion           | EPROM        | EEPROM       | Flash          | SRAM     | DRAM            |

|---------------------|--------------|--------------|----------------|----------|-----------------|

|                     |              |              |                |          |                 |

| Cell size           | 1-2          | 3-4          | 1              | 4-6      | 1 - 2           |

| Memory type         | non-volatile | non-volatile | non-volatile   | volatile | volatile        |

| Write ability       | $n \ 10^4$   | $n \ 10^4$   | $n  10^5$      | $\infty$ | $\infty$        |

| Storage permanence  | 10+ yrs      | 10+ yrs      | 10+ yrs        | nns      | $n \mathrm{ms}$ |

| In-system writing   | no           | yes          | yes            | yes      | yes             |

| Typical write speed | -            | 2-3 s        | $1 \mathrm{s}$ | 15  ns   | 60  ns          |

| Typical read speed  | 90  ns       | 200  ns      | 100  ns        | 15  ns   | 60  ns          |

Table 1.1: characteristics of different transistor based memories; [1] [4] [18] [21]

#### **1.3** Introduction to the Flash Cell

The principles memory cells with an FG were successfully put into practice in the late sixties and resulted in the (x)PROM family. In the late seventies, Toshiba was working on a new version of EEPROM. [8] At the time, the EEPROM was an expensive memory type and a major challenge was to reduce its production costs. This was achieved by reducing the number of transistors that make up the cell and has led to the 1T (1 Transistor) Flash cell. The 1T Flash cell was complemented with a multi-byte writing scheme and was given the name 'Flash' because it was possible to erase a complete array of cells.

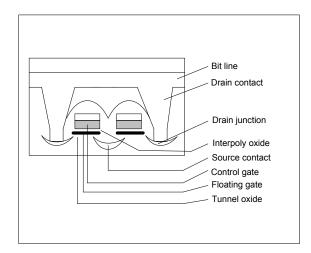

Figure 1.6 depicts 1T cell storage device. The main difference between a MOS transistor and 1T Flash is the capacitive FG. The gate of a 1T Flash, *CG* (Control Gate), is used for writing the cell by influencing the charge on the FG. Similar to an NMOS transistor, the industry standard 1T Flash has an N-type source and drain that are doped with donor atoms. The P-type substrate is doped with acceptor atoms. The FG and CG are doped with donor atoms and are divided by insulating oxide layers. Like a MOS transistor, Flash cells can be put in *cutoff* (CO), *triode* (TR) and *saturation* (SR) mode. [17] The general way of programming a Flash cell is by setting CG to a high voltage. This results in a pull of electrons from the substrate of the 1T Flash. As for erasing, the CG is set to low and the source of the 1T Flash is set to a high voltage. This results in a drainage of electrons toward the source. Flash cells are a remarkable product of CMOS process technology. We will have a more detailed look at the 1T Flash cell in the next chapter.

Figure 1.6: basic 1T cell storage device

A simple scheme for programming and erasing a Flash cell is depicted in Figure 1.7. For a Flash memory cell to be programmed, source is set to GND and Control Gate is set to a high voltage, Vdd. We see that electrons are pulled up toward the FG by getting enough energy to be pulled through the oxide layer. They become trapped in the FG. For erasing, we see that the trapped charge (electrons within the FG) is pulled toward the source through the oxide layer. The charge is then removed from FG, rendering the cell erased. The charged FG, which represents a programmed cell, has a higher threshold voltage than an erased cell. This is due to the trapped electrons on the FG that require the CG voltage to be higher in order to set the cell in saturation mode. The capacitive nature of the FG gives this functionality by trapping or draining charge.

Figure 1.7: writing a 1T flash cell storage device

Flash memory devices have different cell array architectures. Popular Flash architectures are NOR and NAND. The adapted Flash architecture determines how a cell is read and written. These architectures result in different memory characteristics, e.g. read and write times. Flash memory manufacturers choose an architecture based upon its characteristic. NOR and NAND are the most used Flash array architectures. NOR is characterized by its fast data transfers, but it is slower to program and erase than the NAND. It also has a larger cell area than a NAND.

#### 1.4 Thesis Objective and Outline

This Thesis has been written in order to create an electrical Flash memory model. The objective is to develop an electrical model of a Flash memory device, based upon a functional model and the industry standard Flash memory cell. Chapter 2 targets the Flash cell and cell array architectures. Chapter 3 will further explore the Flash memory model by discussing a functional model for the Flash memory device. In Chapter 4 we will discuss electrical Flash cell models that have been published. We will then create and simulate their equivalent. In Chapter 5 we will create an industry standard electrical Flash memory model based upon our functional model and industry standard Flash cell. Finally we will conclude our discussion of Flash memory devices in Chapter 6.

We discussed the basics of memory technology in Chapter 1. Now we will further explore the Flash memory cell. A Flash cell has an FG and in this chapter we will look at its characteristics. This will give us insight in the behavior of a Flash cell. Also, we will look at some popular architectures used in Flash cell array structures.

In Section 2.1 we will look more closely at the Flash cell. Reading and writing the Flash cell will be discussed in Section 2.2. In Section 2.3 we will look at the mechanisms that make Flash writing possible. The Flash cell array architectures are discussed in Section 2.3 and in Section 2.5 we will discuss Flash cell technology and process.

We will use the Industry Standard memory Flash cell as a reference. [4] As stated by [3], Flash memory cells can be categorized in generations (Table 2.1). Our Flash reference cell is of the first generation. This generation is well documented in Flash memory literature and it does not limit our discussion of the Flash cell and memory device. Also, the more advanced Flash cell types are based upon these principles. Through the years Flash cell size has decreased and writing mechanisms and methods have improved due to research, best practices and technological improvements in CMOS process.

#### 2.1 Flash Memory Cell

A memory device has an array of cells, which are the grouped bits. If we would use a MOS transistor to model a memory cell we need more than one transistor in case of an SRAM memory. For a Flash cell however a single MOS would suffice together with components to approach the effects of the FG. When looking at models of Flash cells in literature, it is described as a "full CMOS process in which the building blocks to get an ad hoc floating gate device are incorporated" [4]. The FG introduces a capacitive character at the MOS gate that can change the threshold voltage of this cell. The following equation describes the threshold of a regular MOS transistor [11],

$$V_{th} = K_1 - \frac{Q}{C_{ox}} \tag{2.1}$$

where  $K_1$  is a constant depending on channel doping, gate oxide thickness, and substrate material. Q is the charge with respect to gate oxide, and  $C_{ox}$  is the capacitance of the gate oxide. The threshold voltage  $V_{th}$  can be changed by altering the charge between the gate and channel,  $\frac{Q}{C_{ox}}$ . In SR (saturation) region we get Equation 2.2 for  $I_d$  and in TR (triode) region we get Equation 2.3

$$I_d = K_2 (V_{gs} - V_{th})^2 (2.2)$$

$$I_d = K_2[(V_{gs} - V_{th})V_{ds} - V_{ds}^2]$$

(2.3)

where constant  $K_2$  has units of current per  $(volt)^2$  and  $V_{gs}$  is the potential between gate and source. [17]

#### 2.1.1 Flash Cell Threshold Voltage

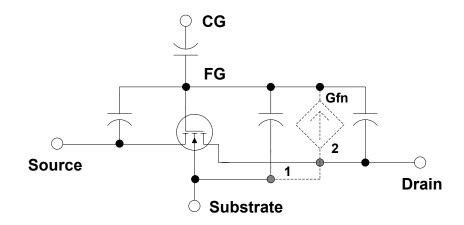

The threshold voltage of a Flash cell is a very important characteristic. It will define how a cell is written i.e. programmed or erased. With an industry standard cell a high threshold voltage means the cell is programmed. In Figure 2.1 a generic FG device is depicted. Its structure adheres to the ETOX structure proposed in the late eighties. [4] ETOX (EPROM Tunnel Oxide) is a FG transistor cell designed and made by Intel.

Figure 2.1: schematic cross section and electrical model of an FG device

The charge stored within an FG device  $(C_t)$  results in a potential,  $V_{fg}$ , that can be described by the following equation [4]:

$$V_{fg} = \frac{C_c}{C_t} V_c + \frac{C_s}{C_t} V_s + \frac{C_d}{C_t} V_d + \frac{C_p}{C_t} V_p + \frac{Q}{C_t}$$

(2.4)

where  $V_c, V_s, V_d, V_p$  are the control gate, source, drain and bulk or p-substrate respectively and Q is the charge within the FG. [4] Ct is the total capacitance which can be seen directly if one looks at the electrical model in Figure 2.2.

When we read a Flash cell based upon Figure 2.1, the bulk and source may be grounded. During a write operation, the FG will be charged or discharged to GND. We therefore change Equation 2.4 to 2.5 and refer all potentials to source. Note that these equations apply only if we read the cell. We will discuss writing mechanisms later in this chapter.

Figure 2.2: parallel capacitors in an FG device model

$$V_{fgs} = \frac{C_c}{C_t} V_{cs} + \frac{C_d}{C_t} V_{ds} + \frac{Q}{C_t}$$

(2.5)

We can then rewrite Equation 2.5 by defining  $\frac{C_c}{C_t}$  (capacitance between control gate and FG, divided by the total capacitance) as the *coupling factor*  $\alpha$ .

$$V_{fgs} = \alpha (V_{cs} + \frac{C_d}{C_c} V_{ds} + \frac{Q}{C_c})$$

(2.6)

The characteristics of a cell depend upon the threshold voltage of the gate. Because we cannot access the FG, we need to look at the control gate, CG. The characteristics of an FG device depends on the threshold voltage (which is  $V_{Tfgs}$ ) beyond which the devices starts to conduct current. We therefore need to control  $V_{Tfgs}$  through the CG. We will use the T abbreviation in the equations to describe this. At FG, we disregard  $\frac{C_d}{C_c}V_{ds}$  because we are not changing any potential here. When applying a voltage to CG, we get the following threshold equation [4]:

$$V_{Tcs} = \frac{1}{\alpha} V_{Tfgs} - \frac{Q}{C_c} \tag{2.7}$$

Equation 2.6 now has a similar shape as Equation 2.1 that describes a MOS transistor, and we can use 2.7 to describe the written states of an FG device. Figure 2.3 depicts the programmed and erased states according to Equation 2.7.

Based upon Figure 2.3, an erased cell has a low threshold voltage because it has no charge trapped within the FG. This is described by Equation 2.8. For a programmed cell, the threshold voltage is high due to the charge trapped within the FG. The FG has a collection of trapped electrons, and therefore with comparison to source, or GND, it has charge Q. This charge results in an addition of potential, we can see this in Equation 2.9. We therefore get a cell with a higher threshold voltage.

$$Erased: V_{Tcs} = \frac{1}{\alpha} V_{Tfgs} - 0 = \frac{1}{\alpha} V_{Tfgs}$$

(2.8)

Figure 2.3: I-V characteristics of an FG device

$$Programmed: V_{Tcs} = \frac{1}{\alpha} V_{Tfgs} - \frac{Q}{C_c}$$

(2.9)

As for the current between drain and source of an FG transistor in SR (Equation 2.10) and TR (Equation 2.11) region, we get the following equations [4]:

$$I_{ds} = K_2 \alpha (V_{gs} - V_{th} + \frac{C_d}{C_c} V_{ds})^2$$

(2.10)

where  $V_{gs}$  is the potential between gate and source.

$$I_{ds} = K_2 [(V_{gs} - V_{th}V_{ds} - (\frac{C_d}{C_c} - \frac{1}{2\alpha})V_{ds})^2]$$

(2.11)

The coupling factor gives us the ability to create equations that can be used to calculate the FG threshold voltage and the current of a cell. We will refer to the change of threshold level in a Flash cell due to the capacitive nature of FG as *CCM* (Capacitive Coupling Method).

#### 2.1.2 Multi-Level Flash Cell

The demand for high density non-volatile memory devices in the computer market is rapidly growing. Alongside the design of more memory in a device, multi-level storage is an important development in current Flash design. Multi-level storage is a single memory cell that represents more than one bit. This can be done by using more than two threshold states  $(V_{th})$ . It is the most efficient way of making use of cell size. However there are tradeoffs that need to be taken into account when dealing with multi-level storage, such as a higher programming voltage needed resulting in memory cells that wear out more quickly. This results in less write cycles compared to single level Flash cells. Reading cells becomes more complex as well due the multiple levels regarding detection. Figure 2.4 depicts the different margins of

a single and multi-level Flash cell. The interested reader is referred to [4] for more details.

Figure 2.4: single and multi-level Flash cell margins

#### 2.2 Flash Writing

Writing a Flash cell requires high voltages on different nodes. In this thesis we will use the first generation Flash cell as a reference for our discussion. Table 2.1 depicts 3 generations of Flash cell writing voltages for CG, Drain and Source. Currently Flash cells are far more advanced than any of these generations and have been successfully manufactured in 32nm CMOS technology with NAND cell architecture. [12]

| Table 2.1: generations of the Flash memory cell |                                                  |                                                 |                                              |  |  |  |

|-------------------------------------------------|--------------------------------------------------|-------------------------------------------------|----------------------------------------------|--|--|--|

| Activity                                        | 1st generation                                   | 2nd generation                                  | 3rd generation                               |  |  |  |

|                                                 | 1990 - 1997                                      | 1995-2000                                       | 1998 onward                                  |  |  |  |

| Program cell                                    | Control Gate: 12V<br>Drain: 5V<br>Source: GND    | Control Gate: 10V<br>Drain: 5V<br>Source: GND   | Control Gate: 8V<br>Drain: 4V<br>Source: GND |  |  |  |

| Erase cell                                      | Control Gate: GND<br>Drain: FLOAT<br>Source: 12V | Control Gate: -8V<br>Drain: FLOAT<br>Source: 5V | Control Gate: -8V<br>Drain: 8V<br>Source: 8V |  |  |  |

#### 2.2.1 Erasing a Flash cell

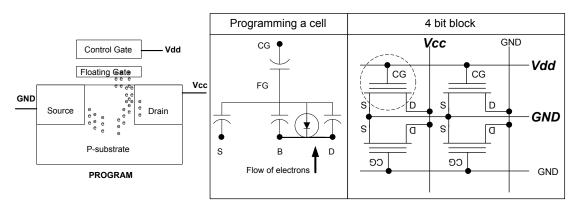

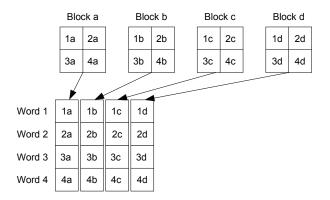

Figure 2.5 depicts a Flash cell being erased. It also shows one cell, and a 4 bit block of cells. To illustrate the writing process of an array of cells we will use the NOR architecture. We will discuss NOR and other Flash cell architectures in more detail in Section 2.5.

A Flash memory array is divided in blocks. All cells in a NOR array block are erased simultaneously. This is depicted by the circles. The control gates are set to GND and a

high voltage (Vdd) is applied to all sources. It is common that a read-check is performed after an erase operation to make sure all cells are erased in the entire block. Table 2.1 shows the voltage values of erasing a first generation cell. Erase time typically lies between 100ms - 1s. [4]

Figure 2.5: erasing a Flash cell

#### 2.2.2 Programming a Flash Cell

Figure 2.6 depicts a Flash cell being programmed. Programming a Flash cell happens one bit at a time for a single block. Different blocks can therefore be programmed simultaneously. When storing one bit at a time in each block n blocks are needed to represent an n-bit word. Programming time for a cell ranges between 1 - 10us. [4]

Figure 2.6: programming a Flash cell

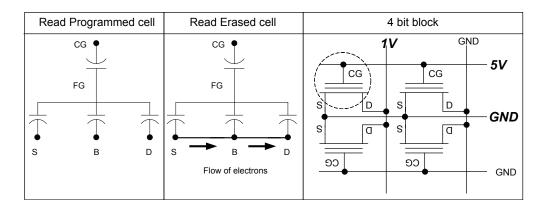

#### 2.2.3 Reading a Flash cell

Access time for reading ranges between 50 - 100ns. [18] Figure 2.7 depicts this situation. A programmed Flash cell has a higher threshold level than an erased cell. This means that the logical state can be regarded as logical 0, i.e. cutoff mode for the cell therefore no current flows. As for an erased cell, the opposite is true. Figure 2.9 gives a simplified

illustration of how the blocks in a NOR array can be represented as words. Note that each array architecture has its own bit representation structure of a word. Logically we only need to distinguish the written modes and convert them to a logical 1 or 0 when sensing the states.

Figure 2.7: reading a Flash cell

Figure 2.8: timing diagram writing process

Figure 2.9: blocks and corresponding words of NOR

When writing Flash devices, we need to keep reliability in mind. An FG cell is

very delicate and disturbances may occur with an adjacent cell due to writing with high voltages. To minimize these effects, programming only one cell at a time in a NOR block is more responsible. When reading a cell with 1V, disturbances are kept low. If reliability issues improve, a more parallel programming process could become possible in a block. Current generations have very low programming voltages and use select transistors to keep disturbances in blocks and adjacent cells to a minimum.

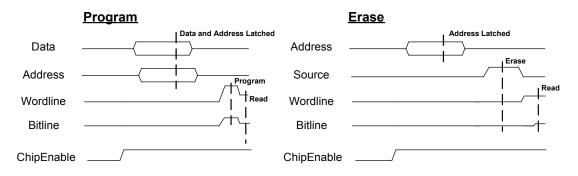

#### 2.2.4 Flash Writing Management

Flash memories generally have their own memory management. This combination of logic and memory (e.g. tables) simplifies the usage of the Flash memory device and ensures a correct writing process. The writing process or algorithm can be depicted in a simplified flow chart in Figure 2.10.

For programming, management stores address and data, and sets a counter variable for this specific process. To minimize unnecessary cell activity the bits are checked at the specified address. If the cells are not programmed then these cells are targeted for programming. If the counter exceeds the maximum number of program tries, we encounter a programming error. When a comparison needs to be made, a read operation of the cells is performed.

For erasing this process is slightly different. At first no comparison is made, the entire block is erased and checked afterwards. This means that already erased cells also undergo this process. The management therefore checks if there is not any sign of over erasure of cells. Checking for programming or erasing errors can for one indicate a problem with the FG.

#### 2.3 Flash Writing Mechanisms

FG devices use writing mechanisms for programming and erasing a cell. Two commonly used mechanisms for FG devices are *FN Tunneling* (Fowler-Nordheim Tunneling) and *CHEI* (Channel Hot Electron Injection). [4] Tunneling mechanisms generally use less current than injection mechanisms. It is therefore more advantageous to use a tunneling mechanism. However, the tunneling mechanism is relatively slower than the injection mechanism. FN Tunneling is used for programming and erasing whereas CHEI is mainly used for programming.

#### 2.3.1 CHEI

CHEI is a write mechanism that is also called "Hot Carrier Injection". It is a mechanism where the electron collects enough energy to overcome a potential barrier. The electrons that flow through the channel are 'heated' by a large lateral electric field between drain and source. This means that the electrons are given a boost via a bias potential at the drain, and therefore gain enough kinetic energy to pass through the oxide barrier

Figure 2.10: writing method flow chart

towards the FG. The hot electrons travel from source towards the drain and near the drain region they have energy to overcome the SiO2 energy barrier. They then get injected into the floating gate due to the electric field ( $E_{ox}$ ) across the channel. [11]

CHEI is difficult to describe mathematically due to its many unknown physical

parameters and character. However, a model called the "Lucky Electron" model has been able to describe its nature analytically. This model has specific criteria that includes gaining sufficient kinetic energy in an electron without losing energy due to collisions. An equation can be described that determines the gate current in Equation 2.12. [10]

$$I_{CHE} = \alpha_{ox} I_{sub} exp \frac{-\beta_{ox}}{E_{ox}}$$

(2.12)

where  $\alpha_{ox}$  and  $\beta_{ox}$  are fitting parameters,  $E_{ox}$  is the electric field into the tunnel dielectric and  $I_{sub}$  is the substrate current.

$$I_{sub} = I_{DS} \frac{a_i}{b_i} V_{sat} exp \frac{-\beta_i}{V_{sat}}$$

(2.13)

where  $I_{DS}$  is the channel current,  $a_i$  and  $b_i$  are impact ionization coefficients, and  $V_{sat}$  is the saturation potential.  $I_{DS}$  can be determined by an equation that takes channel width W, channel length L, inversion charge, surface potential, and carriers effective mobility (which is a function of the linear and quadratic mobility attenuation factors, saturation voltage and carrier velocity saturation) into account.

#### 2.3.2 FN Tunneling

FN Tunneling tunnels electrons through a layer of oxide (of an exact rounded triangular barrier) and is an important tunneling mechanism for thin oxide barriers. Compared to CHEI it can achieve the needed effect with less power. It is a form of quantum tunneling, a phenomenon where particles have been given sufficient energy to break through a barrier (an energy state) due to an electrostatic field. The electric field across the oxide layers determine the measure of electrical current density through the oxide layer. Typically the oxide thickness is about 10 nm from FG to P-substrate. A distance of less than 6 nm will result in insulation failure, thus a bad functioning FG cell. A simplified version of the Fowler-Nordheim equation describing the tunneling current is shown in Equation 2.14. [14] [20]

$$I_{FN} = A(E_{ox})^2 exp \frac{-B}{E_{ox}}$$

(2.14)

$$A = \frac{q^3 m}{8\pi h \phi_b m_*} \tag{2.15}$$

$$E_{ox} = \frac{V_{app} - V_{fb}}{t_{ox}} \tag{2.16}$$

$$B = 4(2m^8)^x \frac{\phi_b^y}{3h_*q} \tag{2.17}$$

where h is Planck's constant,  $\phi_b$  is 3.2 eV, m is the mass of a free electron,  $m_*$  is the effective mass of an electron in the SiO2 gap (0.26 m),  $h_*$  is 0.16 h, x is 0.5, y is 1.5,  $V_{app}$  is the applied voltage across the oxide,  $V_{fb}$  is the flat band voltage and  $t_{ox}$  is the thickness of the oxide.

#### 2.4 Flash Array Architectures

The architecture used in a block of cells will determine the characteristics of a memory device, i.e. block size and access time. These architectures fundamentally differ in group wise connection of CG, Drain and Source, and also in writing mechanism and voltage. We will look at 4 of the most widely used array architectures, namely NOR, NAND, AND and DINOR (Divided Bit line NOR).

Figure 2.11: Flash array architecture overview

In Table 2.2 an overview is given of the 4 popular Flash array architectures and manufacturers that have produced Flash memory devices based on them.

| NAND     | AND                        | DINOR                                 |

|----------|----------------------------|---------------------------------------|

|          |                            | DINOI                                 |

|          |                            |                                       |

| Toshiba  | Hitachi                    | Hitachi                               |

| National | Mitsubishi                 | Mitsubishi                            |

| AMD      |                            | Motorola                              |

| Fujitsu  |                            |                                       |

| Samsung  |                            |                                       |

|          |                            |                                       |

|          |                            |                                       |

|          | National<br>AMD<br>Fujitsu | National Mitsubishi<br>AMD<br>Fujitsu |

| Table | 2.2: | Flash | memory | man    | ufacturers | in | the | late | nineties |

|-------|------|-------|--------|--------|------------|----|-----|------|----------|

|       | NT/  |       |        | 、<br>、 |            |    | DT  | NOD  |          |

The NOR architecture we will discuss is also called *standard NOR*, which is a common ground architecture. This term is used for a structure where every two FG cells have

a common source and drain. Figure 2.6 depicts this structure. The common source is a diffusion line connected to ground via a dedicated metal wire every 16 bit lines. A virtual ground architecture is quite similar to a common ground architecture, except for a dedicated metal wire every 64 bit lines.

#### 2.4.1 NOR Architecture

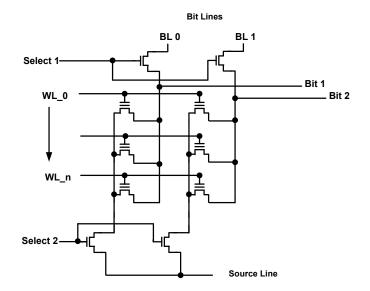

The NOR (common ground) architecture is one where each cell can be read directly, i.e. having to pass through any other cell which are cells in serial. Similar to the logical OR gate, NOR has an 'OR' setup regarding its cells being read, thus its name. We can see in the figure that the sources of 2 cells are connected to each other. Figure 2.5 and 2.6 have shown this characteristic. Programming is generally done via CHEI and erasing via FN Tunneling. Figure 2.12 depicts the NOR architecture. Table 2.3 depicts the levels of reading and writing the NOR cell.

Figure 2.12: NOR architecture

| Mode    | CG  | Drain | Source |

|---------|-----|-------|--------|

|         |     |       |        |

| Read    | 5V  | 1V    | GND    |

| Program | 12V | 5V    | GND    |

| Erase   | GND | float | 12V    |

Table 2.3: NOR read and write voltages; [4]

#### 2.4.2 NAND Architecture

The NAND architecture has a different block structure than NOR. It has a serial structure directly connecting the cells from source to drain. It is therefore possible to

place the cells closer to one another. A block is generally formed by groups of 16 serially connected cells with 2 select transistors (the BL select transistor (BSL) and the ground select transistor (GSL) in Figure 2.13) in each group. If a cell is selected, the other cells must be set to read-through. When reading a cell in this architecture, access time will be slower than reading the cell more directly as with the NOR architecture. Also, due to the read-through nature, a higher voltage is needed for write operations in each block.

An erased cell has a negative threshold voltage in the NAND architecture. A programmed cell has a positive threshold voltage. The CG of the selected cell to be read is set to 0V and the others are set to read through, which is above the programmed cell threshold. To create the negative threshold voltage in a cell (erased cell), the bulk is set to 20V, the CG to 0V and the CGs of unselected cells to 0V. For a positive threshold (programming) the bulk is set to 0V, the CG to 20V and the other CGs are set to 10V. [4] Programming and erasing is generally done via FN Tunneling. Figure 2.13 depicts the NAND architecture. Table 2.4 gives an overview of the levels of reading and writing the NAND cell.

Figure 2.13: NAND architecture

| Table 2.4: NAND read and write voltages; [4] |     |               |      |       |       |

|----------------------------------------------|-----|---------------|------|-------|-------|

| Mode                                         | CG  | unselected CG | Bulk | BSL   | GSL   |

|                                              |     |               |      |       |       |

| Read                                         | GND | $5\mathrm{V}$ | GND  | 5V    | 5V    |

| Program                                      | 20V | 10V           | GND  | 5V    | GND   |

| Erase                                        | GND | GND           | 20V  | float | float |

The NAND architecture has approximately 40 percent more cells on an area compared to NOR. Figure 2.14 depicts an illustration of cell placement. NAND is

generally used for mass data storage and is a slower memory to write.

Figure 2.14: NOR and NAND cell placement comparison; simple geometrical view

#### 2.4.3 AND Architecture

The AND architecture is more or less a combination of NOR and NAND. It has better access times than NAND due to its structure. Also, the cells can be placed closer to each other than in the NOR architecture. The AND architecture adopts the reverse convention of cell programming and erasing, i.e. the AND developers have agreed that a low threshold voltage corresponds to a programmed cell and a high threshold to an erased cell. [4] As for programming and erasing, FN Tunneling is commonly used. Figure 2.15 depicts the AND architecture. Table 2.5 depicts the levels of reading and writing the AND cell.

Figure 2.15: AND architecture

| Mode    | CG  | BL    | Source |

|---------|-----|-------|--------|

|         |     |       |        |

| Read    | 5V  | 1V    | GND    |

| Program | -8V | 6V    | Float  |

| Erase   | 10V | Float | -8V    |

Table 2.5: AND read and write voltages; [4]

#### 2.4.4 DINOR Architecture

The DINOR architecture is similar to the AND architecture. The major difference between them is that DINOR has a common ground connection without a select transistor. Like an AND array, this architectures benefits from better access time than NOR, with even less area than AND due to the common ground connection. This architecture also has a reversed convention for programming and erasing and FN Tunneling is generally used for programming and erasing. Figure 2.16 depicts the DINOR architecture. The AND read and write voltages apply to this architecture as well.

Figure 2.16: DINOR architecture

#### 2.4.5 Array Architecture Overview

In the previous subsections we have seen that an array architecture is accessed either in parallel or serially. A combination can also be applied, i.e. AND. This can even be complemented by including specific structures (e.g. a tree structure) with select transistors in order to make the design faster. This eventually determines the size of the array, the read and write time. Cell process technology also has a great influence on performance. Manufacturers will use a specific combination of these to create a device.

We will now look at some figures of merit in Table 2.6 describing the previous Flash array architectures. [4] These figures represent *cell size*, *process complexity* (this is di-

rectly linked to the process of manufacturing the cell), array efficiency (a correlation of cell and array complexity to the product implementation and yield), general purpose application (both high performance and data storage purpose), and high voltage requirements. This last figure describes the level of complexity of the CMOS process needed that enables it to withstand high voltages. Note that these figures range from 1 to 3 with 1 representing the best overall performance. There are many more figures of merit, this selection is shown to give an indication of the many subtleties that impact Flash array performance.

| . popula | r riasn a                    | rray arc                                                                                                                       | mectures                                             |

|----------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| NOR      | NAND                         | AND                                                                                                                            | DINOR                                                |

|          |                              |                                                                                                                                |                                                      |

| 3        | 1                            | 2                                                                                                                              | 1                                                    |

| 2        | 2                            | 3                                                                                                                              | 3                                                    |

| 2        | 2                            | 3                                                                                                                              | 3                                                    |

| 1        | 3                            | 1                                                                                                                              | 1                                                    |

| 2        | 3                            | 3                                                                                                                              | 3                                                    |

|          |                              |                                                                                                                                |                                                      |

| 10       | 11                           | 12                                                                                                                             | 11                                                   |

|          | NOR<br>3<br>2<br>2<br>1<br>2 | NOR         NAND           3         1           2         2           2         2           1         3           2         3 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

Table 2.6: figures of merit of popular Flash array architectures

# 2.5 Flash Process Technology

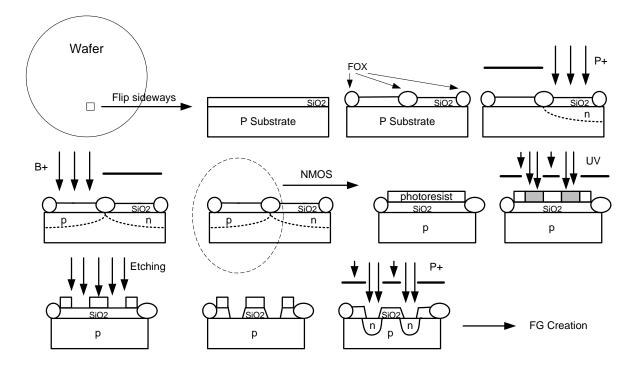

As discussed, Flash process is full CMOS with specific methodologies to create an FG. This means that standard CMOS technology steps with additional complex features have to be taken. [4] CMOS circuits are fabricated on and in a silicon wafer. This wafer is doped with donor atoms. Phosphorus is used to create an n-type wafer and Boron for a p-type wafer. By exposing the wafer to air the SiO2 layer is grown, i.e. Si + O2. This can be done a lot faster by exposing the silicon to hot steam. However, a side effect is that a hydrogen impurity occurs in the silicon. Figure 2.17 depicts a simplified air grown process. It also shows the Field Oxide (FOX) regions that are grown to isolate active p-well and n-well regions. This technique is also called LOCOS (Local Oxidation of Silicon). [2] This figure shows the basics of circuit preparation.

Besides the usual requirements of standard CMOS in terms of access time and low operation voltage, a high voltage is needed for writing operations and this involves FN Tunneling or Injection. Amongst others, it is required that writing takes place without degrading data retention. All these requirements make Flash technology very difficult to master. Flash technology process can be divided in a front end and back end shown in Table 2.7.

Isolation is needed to prevent parasitic leakage current between neighboring cells. The cells must sustain high voltages (of greater than 10V). This is especially needed in areas where the circuitry is very dense (e.g. row decoding area). After well and channel

Figure 2.17: silicon wafer; front end: simplified process of circuit preparation

| Table 2.7: basic process flow                                                                                                                | of Flash technology; [4]                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Front End                                                                                                                                    | Back End                                                                                      |

| <ol> <li>1) Isolation</li> <li>2) Well and Channel doping</li> <li>3) Cell structure definition</li> <li>4) Transistor definition</li> </ol> | <ul><li>5) Interlevel Dielectric</li><li>6) Interconnections</li><li>7) Passivation</li></ul> |

doping to acquire the different MOS parts, cell structure is thoroughly defined in order to create reliable cells. After these steps, the FG is added to the circuit. Figure 2.17 ends with this step and afterwards transistor definition is completed. In order to reduce intrinsic charge loss between the channel and FG, the phosphorus content in between them is carefully concentrated. This is the interlevel dielectric part of the process. After these steps, all the required contacts are made and surface planarization is applied. The last step is to protect the circuit against contamination compounds by passivation. After this step the floating gate is added to the MOS transistor. The interested reader is referred to [4] for more details of these last steps. Note that each manufacturer has its own methodologies. We will discuss Flash memory as a whole from a functional point of view in the next chapter. In the previous chapter we have seen the Flash cell and its structure in arrays in order to give us a better understanding of its nature due to the FG characteristics and cell array architecture. This chapter will give us a functional level overview of a Flash memory device. From this functional model we will develop an electrical Flash memory device model in the next chapters.

In Section 3.1 of this chapter we will look at memory modeling in general, based upon the traditional RAM memory overview. This memory type was thoroughly described in [16]. Section 3.2 will give us an overview of the functional Flash memory model. This will enable us to construct a simplified electrical model based upon these functional blocks, without any detailed design from specific manufacturers.

# 3.1 Memory Modeling

Models enable us to simplify and structure an entity and its environment. Structuring further adds simplification because a specific model then only targets the relevant aspects and phenomena for discussion. We can look at a memory in terms of what it should do (behavioral), in terms of blocks that make sure its main function is accomplished (functional), in terms of how the circuit is connected with electrical components (electrical) and how these components are created with its specific dimensions and technology (geometrical).

By looking at a functional model of a memory, we can logically determine and verify the behavior of the system. At this level one does not have to get bogged down by electrical details and this abstraction enables a technology-independent and general approach. However, going more into details gives one the ability to create accurate simulations to verify the levels above. In this thesis, we will therefore focus upon the functional and use this to create electrical model. Figure 3.1 gives an overview of the modeling levels described in [16].

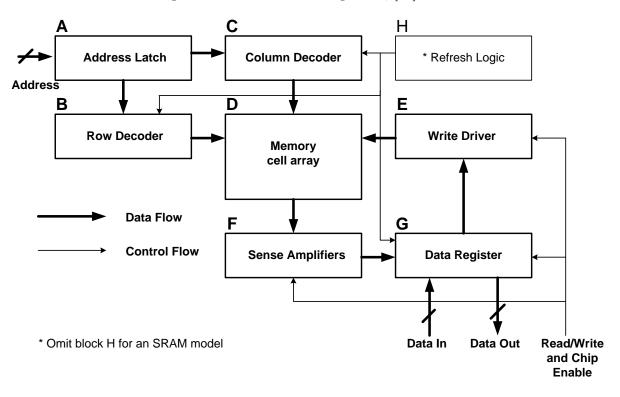

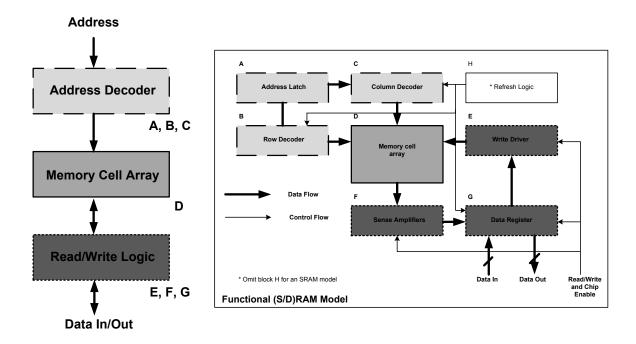

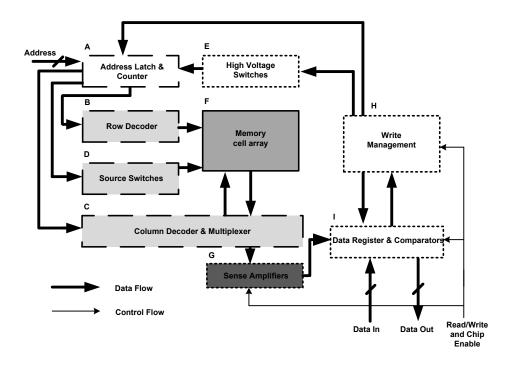

A traditional memory is the RAM device. Figure 3.2 depicts the functional model of this memory device. Block A functions as a latch and targets the appropriate rows and columns. Block D is set up in a specific structure to represent the words of memory. Block F amplifies the bit(s) from the array in order to represent the stored bit(s) to the outside world. Block G functions as gateway to the outside world by either storing bit(s) for reading. Block E functions as read and write control.

| Model type        | Description                                                                                                                                                       | Example                                                             |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Behavioral Model  | Specification of a system. A description of what needs to happen and how. Due to invisibility of internals it is also called a <b>black-box</b> model.            | for (i=0; i <k; i++)<br="">{<br/>f = r - (t &lt;&lt; i);<br/>}</k;> |

| Functional Model  | Functional description of a system.<br>Assumptions are made of the internal<br>structure. Also called a grey-box model.                                           | Register 1<br>Control                                               |

| Logical Model     | Logical description of a system at the level of Logical gates. Basically a sub-level of the functional description.                                               |                                                                     |

| Electrical Model  | Electrical description of a system with<br>the knowledge of internal structure, i.e.<br>interconnections of transistors. Also<br>called a <u>white-box</u> model. |                                                                     |

| Geometrical Model | Model with specifics of the layout of<br>the circuit, i.e. doping levels and physical<br>distances such as transistor channel<br>width.                           | Figure 2.15                                                         |

Figure 3.1: abstract modeling levels; [16]

Figure 3.2: functional (S/D)RAM model; [16]

Figure 3.3: reduced functional (S/D)RAM model; [16]

## **3.2** Functional Flash Memory Device

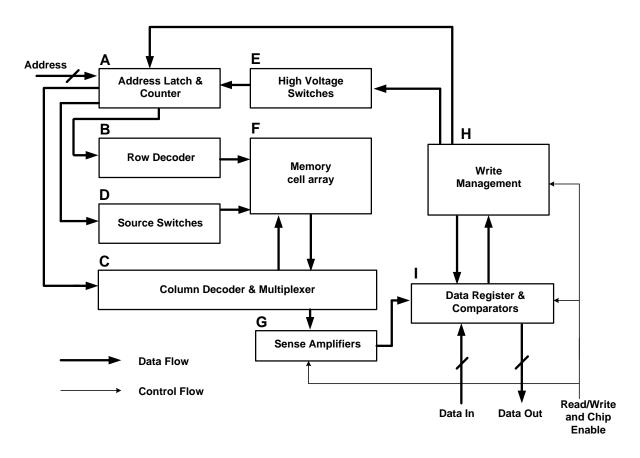

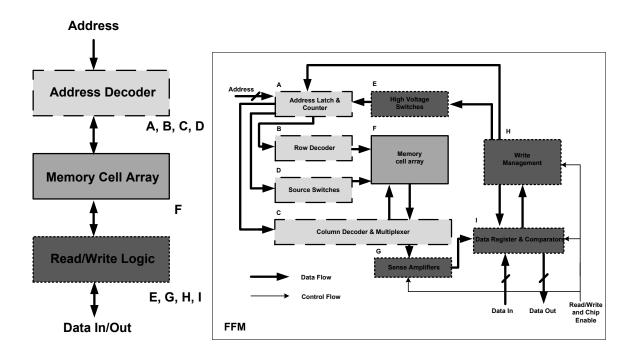

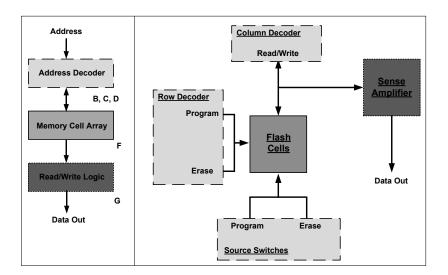

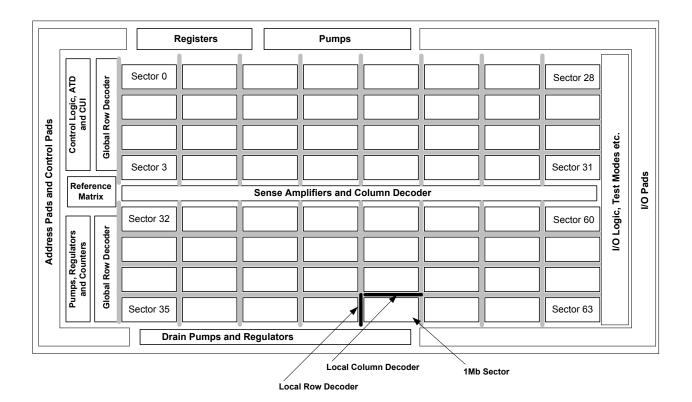

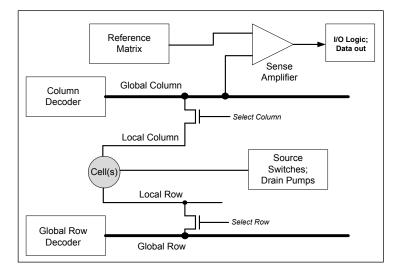

To transform the functional RAM model in Figure 3.2 into a Flash model, we need to take the nature of a Flash cell into account. To read a Flash cell we do not yet need any high voltages but this changes as soon as we want to write a Flash cell. We also need to take source voltages into account when erasing. This gives the need of an extra decoder or source switch. The write driver needs to be a unit that enables write management, we discussed this in Section 2.1.4. Based upon the flow chart, we also need to compare a cell with the preferred state (hardwired) and have counters that keep track of the number of write tries (more than n write tries may reveal an overwritten cell). There are more considerations one can take to model a detailed Flash memory device, but we will stop here. We can simplify Figure 3.2 to a reduced form shown in 3.3. The functional Flash model (*FFM*) is depicted in Figure 3.4. By modeling it this way, it looks slightly like the functional RAM model proposed by [16].

An architectural block diagram of a Flash memory device described in [4] is similar to our FFM aside from several detailed blocks such as a command interpreter (preparing the device to execute a decoded instruction) and spare logic. We will use this FFM to construct an even more basic model that will form the basis of our electrical model.

If we look at the FFM more closely, we see that apart from the changes in data flow and unit functions we have discussed, there is also a difference in the column decoder.

Figure 3.4: functional Flash model (FFM)

In the FFM it is placed below the array of cells and it has a multiplexer. We will see in Section 3.2.2 that the sense amplifier and column decoder are placed close to each other. A reduced model of FFM (RFFM) is depicted in Figure 3.5. By combining the internal units we see that we end up with a reduced functional model that looks exactly the same as Figure 3.3.

## 3.2.1 Reading and Writing in the FFM

The following steps are required for reading data [4] in the FFM in Figure 3.4:

'Read/Write' and 'Chip Enable' are set

Data registers (I) are set to 'Read data'

3) Write Management (H) sets Address Latch (A),

Row decoder (B) targets CG,

Column Decoder (C) targets BL,

Source Switch (D) targets source

4) Column Multiplexer (C) sends data to Sense Amplifiers (G)

5) Sense Amplifiers (G) sends data to Data registers (I)

Figure 3.5: reduced functional Flash model (RFFM)

6) Data register (I) provides Data Out

These steps are needed for writing data [4] in the FFM:

1) 'Read/Write' and 'Chip Enable' are set