### Microfluidic Tissue Barrier Sensor Chip with Integrated Microelectrodes and Ultrathin Microporous Membrane

Tawade, Pratik V.; Aydogmus, Hande; Ivancevic, Lovro; Yeh, Jia Jun; Gkouzioti, Vasiliki; Frimat, Jean Philippe; Den Toonder, Jaap; Mastrangeli, Massimo

DOI

10.1109/MEMS61431.2025.10918254

Publication date 2025

**Document Version**Final published version

Published in

2025 IEEE 38th International Conference on Micro Electro Mechanical Systems, MEMS 2025

Citation (APA)

Tawade, P. V., Aydogmus, H., Ivancevic, L., Yeh, J. J., Gkouzioti, V., Frimat, J. P., Den Toonder, J., & Mastrangeli, M. (2025). Microfluidic Tissue Barrier Sensor Chip with Integrated Microelectrodes and Ultrathin Microporous Membrane. In *2025 IEEE 38th International Conference on Micro Electro Mechanical Systems, MEMS 2025* (pp. 426-429). (Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems (MEMS)). IEEE. https://doi.org/10.1109/MEMS61431.2025.10918254

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

## MICROFLUIDIC TISSUE BARRIER SENSOR CHIP WITH INTEGRATED MICROELECTRODES AND ULTRATHIN MICROPOROUS MEMBRANE

Pratik V. Tawade<sup>1</sup>, Hande Aydogmus<sup>1,2</sup>, Lovro Ivancevic<sup>1</sup>, Jia-Jun Yeh<sup>1,3</sup>, Vasiliki Gkouzioti,<sup>4,5</sup>, Jean-Philippe Frimat<sup>4,5</sup>, Jaap den Toonder<sup>3</sup>, and Massimo Mastrangeli<sup>1\*</sup>

<sup>1</sup>Department of Microelectronics, Delft University of Technology, The Netherlands

<sup>2</sup>Else Kooi Laboratory, Delft University of Technology, The Netherlands

<sup>3</sup>Department of Mechanical Engineering, Eindhoven University of Technology, The Netherlands

<sup>4</sup>Department of Neurology, Leiden University Medical Center, Leiden, The Netherlands

<sup>5</sup>Department of Human Genetics, Leiden University Medical Center, Leiden, The Netherlands

#### **ABSTRACT**

We present a novel silicon-based organ-on-chip (OoC) device featuring integrated microelectrodes to assess barrier function in biological tissue co-cultures. The microfluidic device consists of two vertically-stacked microchannels separated by a submicron-thin, microporous silicon nitride membrane, enabling in vivo-like proximity for co-cultured tissues. The integrated four-probe electrode geometry on slanted microchannel sidewalls ensures unobstructed optical access to the membrane and consistent measurement repeatability. Experimental validation through electrical impedance spectroscopy supported the device's sensitivity to sodium chloride concentration. Fabricated through a scalable, wafer-scale batch process, the device additionally demonstrated biocompatibility and optical transparency, representing a significant advancement for in situ tissue barrier assessments.

#### **KEYWORDS**

barrier-on-chip, microfabrication, microfluidics, organ-on-chip, trans-epithelial electrical resistance

#### INTRODUCTION

Organs-on-chip (OoCs) are advanced microfluidic cell culture devices featuring tissue perfusion and embedding into a dynamic, in vivo-like synthetic microenvironment [1]. Cells in OoCs are arranged to emulate tissue and organlevel microphysiology, allowing researchers to study complex tissue interfaces as well as the chemical and mechanical microenvironments characteristic of specific organs. This way, OoC technology enables the development of in vitro (sub)organ models that closely mimic in vivo counterparts, including those of e.g. the brain [2], heart [3], and intestine [4]. As the demand for more biologically complex and accurate OoC models grows, so does the need for precise monitoring tools to assess their functionality [5]. Reliable assessment of OoC systems requires sensing techniques that deliver continuous information on both the physical and chemical conditions within the microenvironment. Monitoring of tissue barriers is one essential need, as it serves as a critical indicator of epithelial or endothelial tissue viability and functionality. One of the most effective methods for tissue barrier assessment is the measurement of trans-epithelial electrical resistance (TEER). TEER is a rapid, non-invasive assay used to evaluate the integrity and differentiation of epithelial monolayers, with electrical impedance across the tissue correlating to the formation of tight junctions between neighboring cells [6]. While TEER measurements have become a standard for assessing cell

monolayer integrity in traditional cultures, applying this method within OoC systems presents technical challenges [7]. Current designs that include TEER electrodes within OoCs often offer scarce reproducibility of electrode placement, lack stable electrical readings, and impede visual inspection of the cells [8]. In this work, we present a novel silicon-based OoC device featuring wafer-level microfabrication of stacked microchannels (200 µm-wide and 5 mm-long) with integrated microelectrodes and separated by a ultra-thin, microporous silicon nitride (SiN) membrane. The device was designed to enable highly-repeatable and sensitive TEER measurements across virtually any cell co-culture seeded across the membrane. We detail the fabrication process, alongside electrochemical and biological characterizations of the sensor chip, and outline its packaging into a compact OoC module for OoC platforms.

#### **FABRICATION PROCESS**

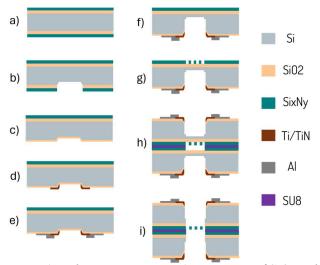

The full fabrication process flow of the device is sketched in Fig. 1. The process begins with pairs of 300 µm-thick, double-side polished silicon wafers. The initial step involved growing a 150 nm-thick silicon dioxide (SiO<sub>2</sub>) layer through wet oxidation of the silicon substrates in a furnace (Tempress) at 1100 °C. This oxide layer is retained throughout most of the process and serves as a protective layer for the final membrane release, achieved via deep reactive ion etching (DRIE). Following oxidation, a 150 nm-thin low-stress SiN layer was deposited on both sides of the wafers using low-pressure chemical vapor deposition (LPCVD) (Fig. 1a). The SiN layer fulfills a twofold function: it acts as hard mask during subsequent wet etching of silicon on one side of the wafers, and provides the substrate for membrane patterning on the other. The SiN layer on the bottom wafer side was processed lithographically to define the channel outline, and then selectively etched by RIE using C<sub>2</sub>F<sub>6</sub> plasma, exposing the underlying oxide layer in the patterned areas. The oxide layer was thereby etched with C<sub>2</sub>F<sub>6</sub>/CHF<sub>3</sub> plasma to reach the silicon surface (Fig. 1b).

The next step in the process involved etching the exposed silicon substrate to form shallow slanted sidewalls. Anisotropic wet etching with tetramethylammonium hydroxide (TMAOH) is commonly used for this purpose. Due to differing etch rates between Si crystallographic planes, with the (100) plane etching significantly faster than the (111), this method produces sidewalls angled at 54.7° relative to a (100) wafer's surface [9]. Etching was performed in a 25% v/v TMAOH water solution at 85 °C with constant agitation. The temperature-dependent etch rate increases as

the temperature rises; and constant agitation ensures a steady provision of reactants at the silicon surface, thus enforcing a sustained though progressively-declining etch rate. The process was carefully timed to produce approximately 15  $\mu$ m-deep trenches in the silicon, corresponding to the slanted sidewalls along the channels (Fig. 1b). Following the etching process, the residual SiO<sub>2</sub>/SiN layer stack, which served as hard mask, was removed using the previously-mentioned dry etching chemistry.

Before substrate metallization, it is crucial to electrically insulate the silicon surface to prevent potential conductivity issues. For this purpose, a 200 nm-thick SiO<sub>2</sub> layer was deposited on the wafer's top side using plasmaenhanced chemical vapor deposition (PECVD) with SiH<sub>4</sub>/N<sub>2</sub>O gases at 400 °C (Fig. 1c).

Figure 1: Fabrication process: a) Deposition of SiO<sub>2</sub> and SiN on both sides of 4" Si wafers, b) masked anisotropic wet etching of Si to form slanted sidewalls, c) passivation of the wafer backside with SiO<sub>2</sub>, d) patterning of TiN electrodes on the slanted sidewalls, e) patterning of Al bonding pads, f) Deep reactive ion etching of Si to form deep straight channels, g) patterning of SiN on the frontside to form the microporous membrane, h) bonding of two wafers mediated by SU-8, i) release of the membrane by Bosch etching of the remaining Si followed by wet etching of SiO<sub>2</sub>.

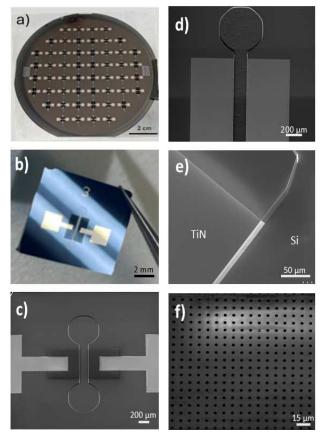

To integrate the electrodes, a 20 nm-thin titanium (Ti) adhesion layer and a 300 nm-thin layer of titanium nitride (TiN) were sequencially sputtered at 6 kW power and 350 °C and later lithographically-patterned to define the microelectrodes on the slanted sidewalls (Fig. 1d and Fig. 2d). In view of the significant topography present by this stage across the substrate, multiple passes of spray coating, each followed by soft backing, were introduced to deposit a conformal and uniform layer of photoresist, and ensure in particular accurate coverage of electrode edges. After photolithographical patterning of the resist layer, the metal stack was dry-etched using an inductively-coupled plasma reactive ion etcher (ICP-RIE, Trikon Omega 201) with a Cl<sub>2</sub>/HBr plasma to define the electrode structures (Fig. 2e). Bonding pads were then fabricated by sputtering and subsequently patterning a 1 µm-thick Si-rich Al layer. The layer was etched through a photopatterned resist mask using Cl<sub>2</sub>/HBr chemistry to form bonding pads connected to the electrodes (Fig. 1e and Fig. 2c).

In the subsequent step, the microfluidic channels were opened using DRIE (SPTS Rapier), which employs the Bosch process to create straight vertical walls by alternating etch and passivation phases. The etching was conducted in two stages to achieve a step profile between the channel inlet/outlet and the membrane area to separate the top and bottom channel regions. First, a 40  $\mu$ m-deep trench was etched in the membrane area using SF6/C4F8 plasma. After this, the channel area was patterned and etched by means of a thicker layer of photoresist, applied through multiple spray coating passes to accommodate the increased topography. The channel area was etched to a total depth of 260  $\mu$ m, leaving approximately 40  $\mu$ m of silicon to mechanically support the SiN membrane during the subsequent processing steps.

Figure 2: Fabrication highlights. a) Full wafer stack, containing 52 devices, b) single diced chip, c) scanning electron microscope (SEM) image of a fully-metallized single device, d) SEM image of the electrodes and microchannel, e) SEM close-up of a TiN electrode over a slanted sidewall, and f) SEM image of the porous membrane.

The wafers were at this stage divided into two batches: in one batch, porous membranes were patterned on the frontside, while in the other the SiN was removed from the membrane area. To create the porous SiN membrane, photoresist was spin-coated onto the first batch of wafers and exposed through a mask with 3  $\mu m$ -wide circular opening and 10% porosity using a stepper (Fig. 2f). The SiN layer was then etched to form the pores using a  $C_2F_6$  plasma. In the second batch of wafers, the SiN layer was similarly etched away from the frontside.

Next, pairs of wafers—i.e., one with a patterned porous membrane, and the other without—were aligned and bonded together to form the full device stack, including the stacked microchannels separated by the ultrathin SiN membranes. Wafer-level thermo-compression bonding was mediated by SU-8, a high-strength, biocompatible, chemically- and thermally-stable adhesive [10]. SU-8 was spin-coated on the bonding sides of both wafers, soft-baked at 95 °C and subsequently patterned by lithography. The coated wafers were aligned and bonded by means of a wafer bonder (AML) under vacuum at 120 °C, under an applied bonding force of 2.5 kN.

The final steps involved releasing the membranes and wafer dicing. Photolithographic patterning on each surface of the bonded wafers was used prior to etching away the residual 40 µm of silicon as well as SiO<sub>2</sub> on both sides, and finally releasing the membranes with SF<sub>6</sub>/C<sub>4</sub>F<sub>8</sub> plasma etching. Once fabrication was complete, the wafers were diced to obtain 52 10-by-10 mm<sup>2</sup> chips (Fig 2b).

#### **EXPERIMENTAL RESULTS**

The fabricated and singulated chips were tested for electrical functionality prior to *in vitro* biocompatibility and preliminary cell culture tests. The electrical characterization was conducted using an electrochemical setup with reference/counter and working electrodes using a common electrolyte. *In vitro* biocompatibility experiments were carried out using Human Umbilical Vein Endothelial Cells (HUVECs).

#### **Electrochemical characterization**

Electrochemical impedance spectroscopy (EIS) was conducted to estimate the impedance of the microelectrodes. EIS characterizes the resistance and reactance of microelectrodes by applying an alternating current or voltage across a range of frequencies and measuring the system's response. This technique provides insights into the electrochemical behavior and properties of the system [11].

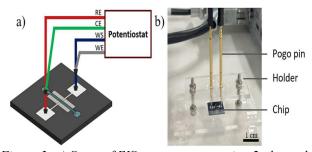

Figure 3: a) Setup of EIS measurements using 2-electrode 4-terminal connection mode, with the working (WE), working sense (WS), counter (CE), and reference (RE) electrodes. b) Connections to single chip's top electrodes.

The microfluidic channel containing TiN slanted-side-wall electrodes was filled with NaCl solutions at concentrations of 0.1 mM, 1 mM, and 10 mM. To minimize the influence of wire resistance during measurements, a 4-terminal connection was used in the 2-electrode setup (Fig. 3). The chip consisted of one TiN microelectrode serving as both the counter and reference electrode, while the other TiN microelectrode functioned as the working and sensing

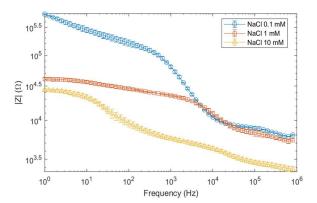

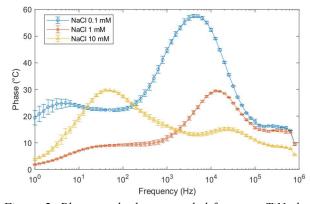

electrode. The electrodes were connected to a portable potentiostat (PalmSens4) via pogo pins, which were in turn coupled to the system with crocodile clips. A sinusoidal waveform with 20 mV<sub>RMS</sub> amplitude and a frequency range of 1 Hz to 1 MHz was applied as the driving input. Three measurements were conducted for each NaCl concentration. The results of impedance (Fig. 4) and phase (Fig. 5) measurements evidenced the interplay of solution resistance and electric double-layer capacitance across NaCl concentrations The overall impedance decreases as NaCl concentration increases due to the improved ionic conductivity (Fig 4). At lower concentrations (0.1 mM), the system exhibits a predominantly capacitive response at low frequencies, as indicated by the highest phase angle (Fig 5). This behavior can be attributed to the pronounced doublelayer capacitance effect due to the limited availability of ions for charge screening. As the concentration increases, the system transitions to a resistance-dominated regime with a more compact double-layer and reduced solution resistance.

Figure 4: Impedance data recorded from two TiN electrodes in 0.1 mM, 1 mM and 10 mM NaCl solutions. Error bars represent the standard deviation out of three independent measurements for each concentration.

Figure 5: Phase angle data recorded from two TiN electrodes in 0.1 mM, 1 mM and 10 mM NaCl solutions. Error bars represent the standard deviation out of three independent measurements for each concentration.

#### **Biological characterization**

HUVECs were cultured in Endothelial Cell Growth Medium (ECGM) (211-500, Cell Applications Inc) supplemented with 10% Fetal Bovine Serum (FBS) and 1% Penicillin/Streptomycin (P/S). After 3 days of culture, the cells were harvested using accutase (A6964, Sigma-Aldrich)

and resuspended in ECGM to be used for seeding (125k cells per membrane) on the membranes. Prior to seeding, the membranes were coated with fibronectin (50  $\mu g/mL$ ) for 1 hour.

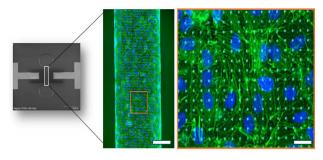

Cells on membranes were fixed with 4% paraformal-dehyde for 10 minutes and permeabilized with 0.5% Triton-X100 for 10 minutes. The nuclei (NucBlue Live ReadyProbes, R37605, Thermo Fisher Scientific, Rosnysous-Bois, France) and actin (ActinGreen 488 Ready-Probes, R37110, Thermo Fisher Scientific) were stained for 30 minutes in the dark at RT. Images were obtained using the Keyence BZ-X800 micro-scope. Fig. 6 shows that cells are able to spread and grow on the porous membrane.

Figure 6: Human endothelial cells (HUVECS) cultured for 48h on-chip (green=actin, blue=nucleus). Scale bars: 100 μm (middle) and 15 μm (right)..

#### **CONCLUSION**

We have demonstrated the wafer-level fabrication of a novel silicon-based organ-on-chip device with integrated microelectrodes designed for TEER-based assessment of barrier function in biological tissue co-cultures. The device features two vertically-stacked microchannels separated by a submicron-thin, microporous, optically-transparent silicon nitride membrane. Electrochemical characterization confirmed the functionality of the microelectrodes, while biological testing verified the biocompatibility and optical transparency of the membrane. These results anticipate further studies with human barrier-forming induced pluripotent stem cells to quantify barrier integrity in real-time.

Future work will focus on packaging the device to enable seamless fluidic and electrical access, facilitating continuous measurements within cell co-culture microenvironments. In particular, we will aim to configure the device into a compact and standardized fluidic and electric module compatible with integration onto the fluidic board of the modular Smart Organ-on-Chip platform (Smart OoC).

#### **ACKNOWLEDGEMENTS**

The authors would like to thank the staff at the Else Kooi Laboratory and members of Electronics, Components, Technology and Materials (ECTM) group of TU Delft for their help and support. This publication is part of the LymphChip project with project number NWA-ORC 2019 1292.19.019 of the NWA research program Research on Routes by Consortia (ORC), which is funded by the Netherlands Organization for Scientific Research (NWO), and of the SMART Organ-on-Chip consortium, which is funded by the NWO-TTW Perspective Program of the NWO, project number P19-03.

#### REFERENCES

- [1] S. N. Bhatia and D. E. Ingber, "Microfluidic organs-on-chips," *Nat Biotechnol*, vol. 32, no. 8, pp. 760–772, Aug. 2014, doi: 10.1038/nbt.2989.

- [2] L. M. Griep *et al.*, "BBB ON CHIP: microfluidic platform to mechanically and biochemically modulate blood-brain barrier function," *Biomed Microdevices*, vol. 15, no. 1, pp. 145–150, Feb. 2013, doi: 10.1007/s10544-012-9699-7.

- [3] M. Dostanic *et al.*, "A Miniaturized EHT Platform for Accurate Measurements of Tissue Contractile Properties," *J. Microelectromech. Syst.*, vol. 29, no. 5, pp. 881–887, Oct. 2020, doi: 10.1109/JMEMS.2020.3011196.

- [4] R. Moerkens *et al.*, "An iPSC-derived small intestine-on-chip with self-organizing epithelial, mesenchymal, and neural cells," *Cell Reports*, vol. 43, no. 7, p. 114247, Jul. 2024, doi: 10.1016/j.celrep.2024.114247.

- [5] P. Tawade and M. Mastrangeli, "Integrated Electrochemical and Optical Biosensing in Organs-on-Chip," *ChemBioChem*, vol. 25, no. 3, p. e202300560, Feb. 2024, doi: 10.1002/cbic.202300560.

- [6] R. Thuenauer, E. Rodriguez-Boulan, and W. Römer, "Microfluidic approaches for epithelial cell layer culture and characterisation," *Analyst*, vol. 139, no. 13, pp. 3206–3218, 2014, doi: 10.1039/C4AN00056K.

- [7] B. Srinivasan, A. R. Kolli, M. B. Esch, H. E. Abaci, M. L. Shuler, and J. J. Hickman, "TEER Measurement Techniques for In Vitro Barrier Model Systems," *SLAS Technology*, vol. 20, no. 2, pp. 107– 126, Apr. 2015, doi: 10.1177/2211068214561025.

- [8] O. Y. F. Henry, R. Villenave, M. J. Cronce, W. D. Leineweber, M. A. Benz, and D. E. Ingber, "Organs-on-chips with integrated electrodes for transepithelial electrical resistance (TEER) measurements of human epithelial barrier function," *Lab Chip*, vol. 17, no. 13, pp. 2264–2271, 2017, doi: 10.1039/C7LC00155J.

- [9] K. E. Bean, "Anisotropic etching of silicon," *IEEE Trans. Electron Devices*, vol. 25, no. 10, pp. 1185–1193, Oct. 1978, doi: 10.1109/T-ED.1978.19250.

- [10] C. T. Pan, P. J. Cheng, M. F. Chen, and C. K. Yen, "Intermediate wafer level bonding and interface behavior," *Microelectronics Reliability*, vol. 45, no. 3–4, pp. 657–663, Mar. 2005, doi: 10.1016/j.microrel.2004.10.019.

- [11] A. Ch. Lazanas and M. I. Prodromidis, "Electrochemical Impedance Spectroscopy—A Tutorial," *ACS Meas. Sci. Au*, vol. 3, no. 3, pp. 162–193, Jun. 2023, doi: 10.1021/acsmeasuresciau.2c00070.

#### **CONTACT**

\*M. Mastrangeli, m.mastrangeli@tudelft.nl