### Fan-Out Panel-Level PCB-Embedded SiC Power MOSFETs Packaging

Hou, Fengze; Wang, Qidong; Chen, Min; Zhang, Guoqi; Ferreira, Braham; Wang, Wenbo; Ma, Rui; Su, Meiying; Song, Yang; More Authors

10.1109/JESTPE.2019.2952238

**Publication date** 2020

**Document Version**

Accepted author manuscript

Published in

IEEE Journal of Emerging and Selected Topics in Power Electronics

Citation (APA)

Hou, F., Wang, Q., Chen, M., Zhang, G., Ferreira, B., Wang, W., Ma, R., Su, M., Song, Y., & More Authors (2020). Fan-Out Panel-Level PCB-Embedded SiC Power MOSFETs Packaging. *IEEE Journal of Emerging* and Selected Topics in Power Electronics, 8(1), 367-380. Article 8894039. https://doi.org/10.1109/JESTPE.2019.2952238

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Fan-Out Panel-Level PCB-Embedded SiC Power MOSFETs Packaging

Fengze Hou<sup>®</sup>, Wenbo Wang, Rui Ma, Yonghao Li, Zhonglin Han, Meiying Su, Jun Li, Zhongyao Yu, Yang Song, Qidong Wang, Min Chen, Liqiang Cao, Guoqi Zhang, Fellow, IEEE, and Braham Ferreira, Fellow, IEEE

Abstract—In this article, a novel fan-out panel-level printed circuit board (PCB)-embedded package for phase-leg silicon carbide (SiC) metal-oxide-semiconductor field-effect transistor (MOSFET) power module is presented. Electro-thermomechanical co-design was conducted, and the maximum package parasitic inductance was found to be about 1.24 nH at 100 kHz. Compared with wire-bonded packages, the parasitic inductances of the PCB-embedded package decreased at least by 87.6%. Compared with blind via structure, the thermal resistance of the proposed blind block structure reduced at most by about 26%, and the stress of the SiC MOSFETs decreased by about 45.2%. Then, a novel PCB-embedded packaging process was developed, and three key packaging processes were analyzed. Furthermore, effect of PCB-embedded package on static characterization of SiC MOSFET was analyzed, and it was found that: 1) Output current of PCB-embedded package was decreased under a certain gate-source voltage compared to SiC die; 2) Miller capacitance of SiC MOSFET was increased thanks to parasitic capacitance induced by package; and 3) compared with SiC die, nonflat miller plateau of the PCB-embedded package extends, and as drain-source voltage increases, the nonflat miller plateau extends. Lastly, switching characteristics of the PCB-embedded package and TO-247 package were compared. The results show that the PCB-embedded package has smaller parasitic inductances.

Index Terms—Electro-thermo-mechanical codesign, printed circuit board (PCB)-embedded package, phase-leg silicon carbide (SiC) metal-oxide-semiconductor field-effect transistor

Manuscript received May 31, 2019; revised September 25, 2019; accepted October 21, 2019. Date of publication November 7, 2019; date of current version February 3, 2020. This work was supported by the National Natural Science Foundation of China under Grant U1730143. Recommended for publication by Associate Editor Yajie Qiu. (Corresponding authors: Wenbo Wang; Liqiang Cao; Guoqi Zhang; Braham Ferreira.)

F. Hou is with the Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China, with the Department of Microelectronics, Delft University of Technology, 2628 Delft, The Netherlands, and also with the National Center for Advanced Packaging, Wuxi 214135, China (e-mail: houfengze@ime.ac.cn).

W. Wang is with the Shenzhen Institute for Wide Bandgap Semiconductors (WinS), Shenzhen 518055, China (e-mail: wenbo.wang@iwins.org).

R. Ma, M. Su, J. Li, Z. Yu, Y. Song, Q. Wang, and L. Cao are with the Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China, and also with the National Center for Advanced Packaging, Wuxi 214135, China (e-mail: caoliqiang@ime.ac.cn).

Y. Li and M. Chen are with the College of Electrical Engineering, Zhejiang University, Hangzhou 310027, China (e-mail: calim@zju.edu.cn).

Z. Han is with the Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China.

G. Zhang is with the Department of Microelectronics, Delft University of Technology, 2628 Delft, The Netherlands (e-mail: g.q.zhang@tudelft.nl).

B. Ferreira was with the Department of Electrical Sustainable Energy, Delft University of Technology, 2628 Delft, The Netherlands. He is now with the Department of Telecommunication Engineering, University of Twente, 7522 Enschede, The Netherlands (e-mail: j.a.ferreira@utwente.nl).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JESTPE.2019.2952238

(MOSFET) power module, static characterization, switching characterization.

#### I. Introduction

CILICON carbide (SiC) is a promising semiconductor material under high operating temperature, high blocking voltage, and high switching frequency applications due to its excellent electrical and thermal properties. Compared with Si counterparts, wide bandgap energy and low intrinsic carrier concentration of 4H-SiC enable SiC devices to operate at much higher temperature (approximately five times higher than Si) [1]-[5]. 4H-SiC also possess a higher breakdown field strength (ten times of Si), which allows SiC power devices to have a much thinner drift region and higher doping concentration for a given voltage rating than their Si counterparts. The thinner and higher doping drift region greatly reduces specific on-resistance of the SiC devices, facilitating the use of unipolar SiC power metal-oxide-semiconductor field-effect transistor (MOSFET) device. The SiC MOSFETs reported to date already significantly outperform any available Si counterparts at the same voltage rating in terms of reduced switching losses and at least 5-10 times higher switching frequencies [6]. Compared with Si counterparts, SiC MOSFET has a smaller chip size, resulting in significantly reduced internal parasitic capacitances, hence a much faster intrinsic switching speed [7]. Therefore, SiC MOSFET has the potential to revolutionize the industry of power electronics.

In a power module, the superior properties of a SiC MOSFET cannot be exploited if it is used simply as a direct drop-in replacement of Si device [8]. Owing to the fast switching speed capability, the switching characteristics of SiC MOSFET are more susceptible to parasitic elements, such as the parasitic inductances of interconnections and parasitic capacitances [9]. The high dv/dt at turn-on transient easily leads to the arm crosstalk due to the miller capacitance and the high di/dt at turn-off transient easily induces voltage overshoot thanks to the parasitic inductance [10].

Up to now, conventional wire-bonded interconnection is still the most preferred technology for packaging SiC MOSFET. However, wire-bonds have an inherent parasitic inductance that can exceed 10 nH [11], an excessive voltage overshoot of a wire-bonded SiC MOSFET package is easily produced at high speed switching transients. The large voltage overshoot may damage the SiC MOSFET by exceeding its absolute maximum ratings, increasing power losses, introducing substantial electromagnetic interference (EMI) noise, thereby affecting

2168-6777 © 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

the reliability of the MOSFET [11], [12]. In order to avoid the large overshoot, low inductance design of SiC MOSFET package is needed.

Moreover, power density of SiC MOSFET is higher than those of Si counterparts due to the smaller size. And power loss generated by SiC MOSFET increases with frequency, most of it is only dissipated through the bottom side of the wire-bond package. A cooling system that can remove the heat through dual sides will be much more efficient.

Besides, with the wire-bonded interconnection structure, under high ambient temperature or high operating temperature, thermally induced stress/strain resulting from the coefficient of thermal expansion (CTE) mismatch among the constituent materials could lead to wire failure, die attach (DA)/die crack, package warpage, etc. [13].

New packaging interconnection techniques need to be developed to push the development of SiC power module. So far, several wire-bondless interconnection packages for SiC MOSFET module have been developed, e.g., planar packaging, press-pack, and 3-D packaging.

As a wire-bondless interconnection technology, printed circuit board (PCB) embedded SiC MOSFET package is a potential solution with small form factor, lightweight, and simple process technology. PCB-embedded package, also called "Chip in Polymer" technology, was first introduced by Fraunhofer IZM and TU Berlin. The ultrathin semiconductor chips were embedded into the build-up layers of PCB together with integrated passive components. Electrical interconnection between chip and outer-layer footprints were realized by laser-drilled and metallized microvias [14]–[16].

In recent years, PCB-embedded packaging technology has been applied to power module. This mainly includes two types of process flows: face-up and face-down processes [17]. The DA materials used in the two processes are different. For face-down process, it is a nonconductive adhesive, whereas for face-up technology, except for nonconductive adhesive, it can also be solder, sintered Cu/Ag, etc. The latter is more suitable for high power-density vertical dies, such as insulator gate bipolar transistor (IGBT), power diode, power MOSFET, etc.

There have been some developments in the PCB-embedded power module. Leadframe-based PCB-embedded packaging technology is one of the major representatives [18], [19]. The power dies are soldered or sintered onto a Cu leadframe, and the resulting assembly is then fully embedded in a prepreg or resin-coated copper (RCC) material. Electrical interconnection of the dies with outer layers is realized through PCB vias and redistribution layers (RDLs). Besides, Pascal et al. [20] proposed an innovative PCB-embedded packaging technology. They used a piece of nickel foam to create a pressed contact between the top side of a PCB-embedded power die and the rest of the circuit. AT&S developed a panellevel PCB-embedded technology known as embedded component packaging (ECP) [21]. Yang et al. [22] presented a PCB-embedded power MOSFET. The power MOSFETs were soldered onto a Cu foil with a solder resist pattern and embedded in an RCC foil. However, all these package structures are asymmetrical in the thickness direction, which could easily cause larger stress and strain under harsh environments.

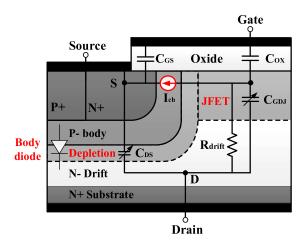

Fig. 1. Typical structure of half SiC DMOSFET cell with equivalent parasitic capacitances.

Besides, heat generated by power devices is mainly dissipated into the ambient only through bottom side. Symmetry package structure with double-sided cooling can relieve the thermally induced stress and improve the heat dissipation performance of the PCB-embedded power module.

Up to now, there are few reports on PCB-embedded SiC MOSFET power module. Scientific challenges in the design and implementation of PCB-embedded SiC MOSFETs packaging, e.g., heat dissipation, thermo-mechanical reliability, and packaging process, have not been well dealt with. After packaging, accurate characterization of the custom module is also a challenge. These issues must be handled more carefully in the development of SiC MOSFET power module packaging.

In Section II of this article, SiC MOSFET and phaseleg power module were introduced. In Section III, a novel fan-out panel-level PCB-embedded packaging technique for SiC MOSFET power module was proposed. In Section IV, electro-thermo-mechanical co-design of the PCB-embedded SiC MOSFETs package was conducted. In Section V, a brief description of process flow of the PCB-embedded package was given, key PCB-embedded packaging process and failure analysis were performed, and improved package process was suggested. In Section VI, the static characteristics of SiC MOSFET and PCB-embedded package were analyzed and compared. The effects of PCB-embedded package on I-V, C-V, and gate charge characteristics of SiC MOSFET were investigated, respectively. In Section VII, the switching characteristics of SiC MOSFET in the PCB-embedded phase-leg power module and the TO-247 discrete package were analyzed and compared.

#### II. SiC MOSFET AND PHASE-LEG POWER MODULE

SiC MOSFET comprises more than 10 000 small parallel-connected N-Channel enhancement mode MOSFET cells. A cross section of half DMOSFET cell with equivalent parasitic capacitances is illustrated in Fig. 1 [23]. The SiC MOSFET device is fabricated by beginning with an N-drift layer grown on a heavily doped N+ substrate. The drift layer is sandwiched between N+ substrate and p-body, creating a

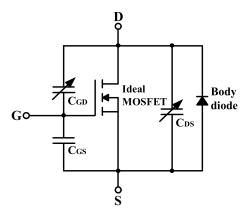

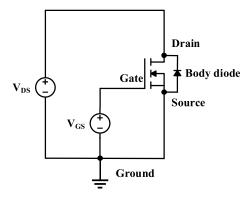

Fig. 2. Equivalent circuit model of the SiC MOSFET.

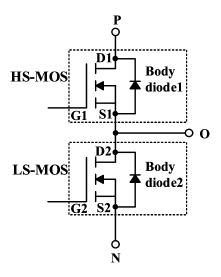

Fig. 3. Circuit diagram of phase-leg SiC MOSFET power module.

vertical body diode. The body diode is a PiN diode and is anti-parallel with the SiC MOSFET channel. The foremost characteristic of PiN diode is in the turn-off transient where reverse recovery can be observed as a result of minority carrier extraction from the drift layer [24], [25].

Fig. 2 shows the equivalent circuit model of the SiC MOSFET. It is composed of an ideal MOSFET which is described as a voltage-controlled current source, three parasitic capacitances, and an anti-parallel body diode. Parasitic capacitances of SiC MOSFET include gate—source capacitance ( $C_{\rm GS}$ ), drain—source capacitance ( $C_{\rm DS}$ ), and gate—drain capacitance ( $C_{\rm GD}$ ) [9], [10], [23].  $C_{\rm GS}$  consists of a constant overlap oxide capacitance between gate and source and a constant capacitance between gate and source metallization, which are in parallel.  $C_{\rm DS}$  is the bias-dependent depletion capacitance of P-body/N-drift junction and is given by

$$C_{\rm DS} = C_{\rm DS0} \left( \frac{V_{\rm bi}}{V_{\rm bi} + V_{\rm DS}} \right)^M \tag{1}$$

where  $C_{DS0}$  is a constant,  $V_{bi}$  is the built-in potential between P-body and N-drift junction, and M is a fitting parameter.

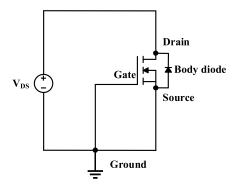

Fig. 3 shows a circuit diagram of phase-leg SiC MOSFET module, which consists of a high-side SiC MOSFET (HS-

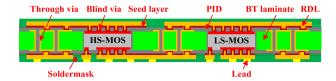

Fig. 4. Structure schematic of the PCB-embedded SiC MOSFETs package.

TABLE I

GEOMETRY STRUCTURE SIZE OF EACH COMPONENT

| Component     | Size (mm)                         |  |  |

|---------------|-----------------------------------|--|--|

| Chip          | 3.36×3.10×0.186                   |  |  |

| Soldermask    | 15×15×0.04                        |  |  |

| PID           | 15×15×0.04                        |  |  |

| Chip pitch    | 6                                 |  |  |

| BT laminate   | 15×15×0.186                       |  |  |

| Through via   | Diameter = $0.15$ , Pitch = $0.4$ |  |  |

| Blind via     | Diameter = $0.1$ , Pitch = $0.2$  |  |  |

| RDL thickness | 0.025                             |  |  |

MOS) and a low-side SiC MOSFET (LS-MOS). Body diode in the SiC MOSFET is utilized to replace external freewheeling diode. Unlike traditional Si devices, SiC MOSFET has shorter lifetime of minority carriers so that not a large reverse recovery current is estimated, which enables the body diode of the SiC MOSFET to be a brilliant diode with almost no reverse recovery charge and forward recovery voltage [24].

## III. FAN-OUT PANEL-LEVEL PCB-EMBEDDED PACKAGING

#### A. Packaging Structure

Fig. 4 shows the structure schematic of the fan-out panel-level PCB-embedded package for phase-leg SiC MOSFET power module. The package mainly consists of a pair of SiC dies (HS-MOS and LS-MOS), PCB-embedded material (BT laminate), photo imageable dielectric (PID), electrical interconnection (seed layers, RDLs, blind vias, and through vias), and lead. Geometry size of each component is listed in Table I.

The SiC MOSFETs are embedded in the PCB. Electrical interconnection between SiC MOSFETs and out-layer footprint is realized by PCB vias and RDLs. Compared with conventional wire-bonded interconnections, the PCB-embedded technology eliminates Al wire-bonds, direct bond ceramic (DBC) substrate, DA, and encapsulation structure, manufacturing processes are, accordingly, simplified. The PCB-embedded SiC MOSFET power module has merits of lightweight, thin profile, low parasitic inductances, structure symmetry, double-sided cooling, etc.

#### B. Packaging Materials

In order to withstand high-temperatures beyond 175 °C and high-voltages over 1200 V, and improve thermomechanical reliability of the PCB-embedded SiC MOSFETs,

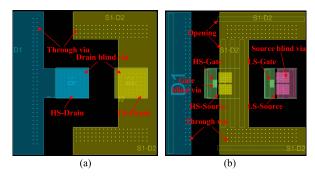

Fig. 5. Packaging layout of the PCB-embedded SiC MOSFETs. (a) Front-side. (b) Backside.

copper clad laminate (CCL-HL832NSF) and prepreg (GHPL-830NSF) from Mitsubishi Gas Chemical were selected. CCL-HL832NSF was a double-sided copper-clad BT laminate (E-glass fiber-reinforced BT resin) with high Tg and low CTE. And GHPL-830NSF was a sheet of BT prepreg (E-glass fiber-reinforced uncured BT resin). In order to obtain the BT laminate with almost the same thickness as the SiC die, BT prepreg was used. In our previous work [27], characterization of the PCB-embedded package materials for SiC MOSFETs were performed. The experimental results showed that the PCB-embedded materials could withstand high temperatures beyond 200 °C and high voltages above 1200 V. Tg was as high as over 260 °C and CTE matched well with SiC. Besides, a novel PID film was used as a laminating dielectric material.

#### C. Packaging Layout

Fig. 5 displays front-side and backside of the PCB-embedded SiC MOSFETs packaging layout. The package has a size of  $15 \times 15 \times 0.36$  mm<sup>3</sup>. The Cu coverage of front-side and backside RDL is about 63% and 57%, respectively, so the package will take on a "smile" shape when cooling down from stress-free high temperature.

#### IV. ELECTRO-THERMO-MECHANICAL CODESIGN

In order to evaluate the electrical, thermal, and mechanical performances of the PCB-embedded SiC MOSFETs, the electro-thermo-mechanical co-design was performed. Parasitic inductances of the PCB-embedded SiC MOSFETs package were first extracted, and the effects of switching frequency on parasitic inductances were analyzed. Then, thermal modeling was conducted to verify the heat dissipation performance of the package. Thirdly, thermo-mechanical virtual prototyping was applied to analyze the mechanical behavior of the package.

#### A. Package Parasitic Inductances Extraction

Parasitic inductances induced by package structure are especially critical for fast switching of SiC MOSFETs. The ANSYS Q3D Extractor was used to extract parasitic inductances of the PCB-embedded SiC MOSFETs. Fig. 6(a) and (b) shows the extraction model of the PCB-embedded SiC

Fig. 6. Extraction model of the PCB-embedded SiC MOSFETs package. (a) Front-side. (b) Backside.

TABLE II

DEFINITIONS, SOURCES, AND SINKS OF

PACKAGE PARASITIC INDUCTANCES

| Parasitic inductance | Definition               | Source                                          | Sink         |

|----------------------|--------------------------|-------------------------------------------------|--------------|

| $L_{\mathrm{D1}}$    | HS-MOS drain inductance  | Interfaces between blind vias and HS-MOS drain  | P terminal   |

| $L_{ m Gl}$          | HS-MOS gate inductance   | Interfaces between blind vias and HS-MOS gate   | GD1 terminal |

| $L_{ m S1-O}$        | HS-MOS source inductance | Interfaces between blind vias and HS-MOS source | O terminal   |

| $L_{	ext{O-D2}}$     | LS-MOS drain inductance  | Interfaces between blind vias and LS-MOS drain  | O terminal   |

| $L_{ m G2}$          | LS-MOS gate inductance   | Interfaces between blind vias and LS-MOS gate   | GD2 terminal |

| $L_{ m S2}$          | LS-MOS source inductance | Interfaces between blind vias and LS-MOS source | N terminal   |

Fig. 7. Parasitic inductances of the PCB-embedded SiC MOSFETs package dependent on switching frequency.

MOSFETs package. Table II lists the definitions, sources, and sinks of the package parasitic inductances.

Fig. 7 shows the parasitic inductances of the PCB-embedded SiC MOSFETs package dependent on frequency. The sweep frequency range was 20 kHz-1 MHz. As shown in the figures, the parasitic inductances of the PCB-embedded package decreased with the frequency due to the skin and proximity effect. From 20 to 200 kHz, the parasitic inductances dropped evidently. When the frequency kept on increasing

from 200 kHz to 1 MHz, the parasitic inductances decreased slowly and leveled off.

From Fig. 4, it can be seen that the drains of the two MOSFETs are connected to the package terminals by blind vias, front-side RDLs, through vias, and backside RDLs, whereas the sources and gates are connected to the package terminals through blind vias and backside RDLs, so the drain inductances are much higher than the source/gate inductances. As shown in Fig. 7, the HS-MOS drain inductance  $L_{\rm D1}$  is about 0.845 nH at 100 kHz, and LS-MOS drain inductance  $L_{\rm O-D2}$  is about 1.24 nH at 100 kHz which is the largest in the package. Other parasitic inductances in the package are lower than 15 pH. Compared with conventional wire-bonded packages, in which parasitic inductances exceed 10 nH, Therefore, the parasitic inductances of the PCB-embedded package decreased by 87.6% at least.

#### B. Thermal Modeling Analysis

Thermal conductivities of PCB-embedded materials are relatively low. Furthermore, heat flux of SiC MOSFET is higher than those of Si counterparts with the same voltage rating due to smaller size and higher switching frequency, so more efficient cooling solution for PCB-embedded SiC MOSFETs package is required. Conventional single-sided cooling design is difficult to achieve the heat dissipation requirement. A cooling method that could remove the heat through double-side will be much more efficient.

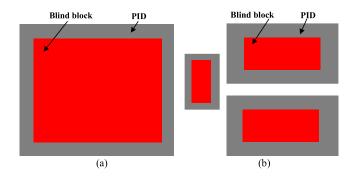

As shown in Fig. 4, SiC MOSFETs are communicated with outer interconnection layers through blind vias in the PID film. The blind vias are filled with Cu through sputtering and plating. However, because the diameter of blind via is only  $100~\mu m$ , Cu coverage above the pads of SiC MOSFETs is relatively low, which is only about 3.2%. In order to improve the heat dissipation of the PCB-embedded SiC MOSFETs package, it is necessary to increase the Cu coverage above the die pads. However, if only increasing the amount or diameter of blind via, the increase of Cu coverage above the chip pads is limited.

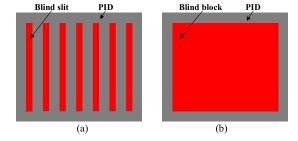

In this article, blind block was proposed to increase the Cu coverage above the die pads, thus improving the heat dissipation capability of the PCB-embedded SiC MOSFETs. The blind block can be formed by PID exposure and development, panel-level physical vapor deposition (PVD), and RDL interconnection techniques. The structure diagram of blind block above the SiC MOSFET pads is shown in Fig. 8(a) and (b), respectively.

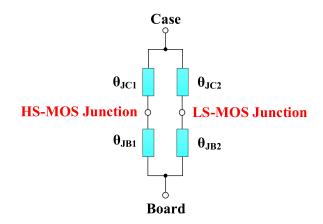

Fig. 9 shows a compact thermal resistance network model of the PCB-embedded SiC MOSFETs. The model includes junction-to-case thermal resistance ( $\theta_{JC}$ ) and junction-to-board thermal resistance ( $\theta_{JB}$ ) of the PCB-embedded package.

$\theta_{JB}$  and  $\theta_{JC}$  of the PCB-embedded package were analyzed through ANSYS ICEPAK. Table III compares the thermal resistances of the blind via and blind block structures. From the table, it can be calculated that the thermal resistance of the proposed structure reduced by about 26% at most.

#### C. Thermo-Mechanical Virtual Prototyping

Prior to PCB-embedded SiC MOSFETs packaging process, thermo-mechanical simulation was carried out using ANSYS

Fig. 8. Structure diagram of blind block above the MOSFET pads. (a) Drain. (b) Gate and source.

Fig. 9. Compact thermal resistance network model of the PCB-embedded SiC MOSFETs package.

TABLE III

COMPARISON OF THERMAL RESISTANCE BETWEEN THE

BLIND VIA AND THE BLIND BLOCK STRUCTURE

| Structure above pads | θ <sub>JC1</sub><br>(K/W) | θ <sub>JC2</sub><br>(K/W) | θ <sub>JB1</sub> (K/W) | θ <sub>JB2</sub><br>(K/W) |

|----------------------|---------------------------|---------------------------|------------------------|---------------------------|

| Blind via            | 0.502                     | 0.522                     | 0.262                  | 0.558                     |

| Blind block          | 0.386                     | 0.386                     | 0.256                  | 0.455                     |

$\label{thm:table_iv} \mbox{TABLE IV}$  Thermo-Mechanical Properties of the Packaging Materials

| Component      | Material        | Tg (°C) | E (GPa)     | CTE<br>(ppm/°C)              | υ    |

|----------------|-----------------|---------|-------------|------------------------------|------|

| MOSFET         | 4H-SiC          |         | 400         | 5.1                          | 0.14 |

| BT<br>laminate | 832NSF          | 275 °C  | See Fig. 10 | $\alpha 1=5.3;$ $\alpha 2=3$ | 0.18 |

| PID            | PVI-3<br>HR100S | 160-165 | 3.5         | α1=45;<br>α2=120             | 0.3  |

| RDL            | Cu              |         | 129         | 17.3                         | 0.34 |

| PCB via        | Cu              |         | 129         | 17.3                         | 0.34 |

Mechanical APDL to provide guidelines. Effect of Cu coverage above the chip pads on von Mises stress was optimized.

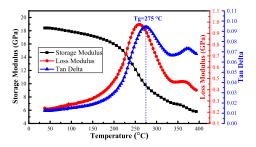

Table IV lists thermo-mechanical properties of the packaging materials. The storage modulus, loss modulus, and tan delta of the BT laminate dependent on temperature are shown in Fig. 10. As shown in the figure, Tg of the laminate was up to 275 °C, which was much higher than most other PCB materials. For other materials, SiC was considered as isotropic and elastic. Cu RDL and electroplated blind vias were assumed

Fig. 10. Storage modulus, loss modulus, and tan delta of the BT laminate dependent on temperature.

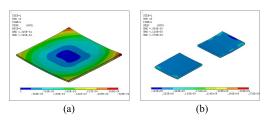

Fig. 11. Simulation results. (a) Warpage of PCB-embedded package. (b) von Mises stress of SiC MOSFETs.

as elastoplastic. The material properties of PID and soldermask were taken from the vendors' datasheets.

When conducting thermo-mechanical simulation of the PCB-embedded package, the initial reference temperature of the finite element model was set to be baking temperature of 175 °C, the final room temperature was 25 °C, and the bottom center point of the model was fixed. Besides, perfect adhesion was assumed between all material interfaces, manufacturing tolerances of dimensions were not considered [29]–[31].

Fig. 11(a) shows the warpage of the PCB-embedded SiC MOSFETs after high-temperature baking. The package takes on an approximately isotropic "smile face" shape due to asymmetrical chip layout, which is consistent with the previous analysis. The maximum warpage is about 32.5  $\mu$ m, which is lower than 0.5% of the package diagonal length. Fig. 11(b) illustrates the von Mises stress distribution of SiC MOSFETs. From the figure, it can be seen that the maximum von Mises stress is 376 MPa, which occurs at the corner of the MOSFET.

From Table IV, it can be seen that CTE of PID is relatively higher than that of SiC and Cu, CTE mismatch between the SiC MOSFET and the PID film could lead to higher stress. In this article, effect of blind slit and blind block structures on von Mises stress of SiC MOSFET were analyzed and compared. The structure diagram of blind slit and block above the drain are shown in Fig. 12(a) and (b), respectively.

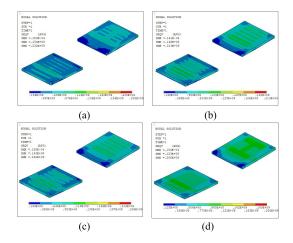

Fig. 13(a) and (d) shows the von Mises stress of the HS-MOS and LS-MOS in different structures. Compared with blind via structure, the proposed blind block structures relieved the von Mises stress of SiC MOSFETs, and von Mises stress of the SiC MOSFETs decreased by about 45.2%.

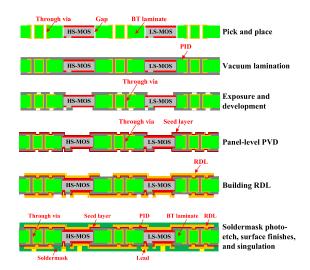

#### V. PCB-EMBEDDED PACKAGING PROCESS

The detailed packaging process flow of the PCB-embedded SiC MOSFETs is depicted in Fig. 14. The key techniques

Fig. 12. Structure diagram of (a) blind slit and (b) blind block above the MOSFET drain.

Fig. 13. Effect of Cu coverage above the chip pads on von Mises stress of SiC MOSFETs. (a) Blind slit width: 100  $\mu$ m. (b) Blind slit width: 200  $\mu$ m. (c) Blind slit width: 300  $\mu$ m. (d) Blind block.

Fig. 14. Process flow of the PCB-embedded SiC MOSFETs.

of the packaging process mainly include PID exposure and development, panel-level double-sided PVD, and double-sided RDL interconnection techniques.

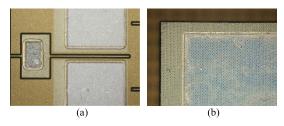

#### A. PID Exposure and Development Technique

At present, commercially available SiC power devices are designed for front-side Al wire bonding. Hence, metallization layers of front-side pads on these devices are Al, which is

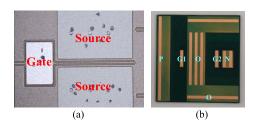

Fig. 15. Terminal pads of SiC MOSFET after exposure, development, and cure. (a) Source and gate. (b) Drain.

not compatible with PCB-embedded package and an additional metallization layer is required on the front-side source and gate pads [17], [32]. Dies that had extra metallization layers are then embedded in the PCB, followed by blind vias that are usually formed by laser drilling and Cu plating, thus realizing the interconnection between dies and outer layers [14], [18], [19], [22]. However, if energy is not properly controlled, the terminal metallization pads could be damaged by laser drilling. For very thin pad of power device, laser drilling is not allowed. Therefore, new alternative laser drilling needs to be developed.

In this work, SiC MOSFET bare dies were picked and placed in the grooves of BT laminate with almost the same thickness and were laminated by double-side PID films through a vacuum laminator. Because of flow ability of PID in this process, gaps between SiC MOSFETs and BT laminate and through vias of the BT laminate were filled with PID. Chip pads and inner interconnection layers covered by PID films were then opened through exposure and development process. Fig. 15(a) and (b) shows the terminal pads of SiC MOSFET after exposure, development, and cure. It is noted that the PID film is a transparent material. It is difficult to distinguish whether the die pads and inner RDLs are exposed after development, which easily leads to final package failure. If exposure and development conditions are not well controlled or dies are tipped or thicker BT laminate is chosen, die pads and interconnection layers cannot be opened. Therefore, laminate should not be thicker than die, and die placement should be well controlled as well as the process condition.

#### B. Panel-Level PVD Technique

In the PCB-embedded SiC MOSFET packaging, if Al pads are not modified, they will be damaged in the follow-up Cu plating process because of high reactivity of Al in the PCB-embedded package. Therefore, re-metallization of Al pad on the power devices is a key process for the development of PCB-embedded SiC MOSFET package. In [22], 5-μmthick Cu was added to the MOSFET pads at wafer level. For SiC power MOSFET, however, the cost and risk of pad re-metallization at wafer level are high. Kearney et al. [19] developed a 1.2-kV PCB-embedded IGBT inverter module. For IGBT and diode front-side re-metallization, the original Al metallization of emitter, gate, and anode contact was modified by sputtering of Cr/Cu (5 nm/8  $\mu$ m) layers, whereas dielectric region on the top surface of the IGBT was protected with a shadow mask. However, the size of SiC MOSFET is relatively small compared to IGBT, and it is difficult to realize the

Fig. 16. Cu layers on the PID. (a) Successful sputtering. (b) Failed sputtering.

Fig. 17. Double-sided RDLs of the panel-level PCB-embedded package. (a) Front side. (b) Backside.

re-metallization of pads at such a small bare die. Besides, SiC MOSFET is a vertical power device; with the gate and source on front-side and drain on backside, chip-level PVD easily contaminates the other side when sputtering one side. Therefore, exploration of new re-metallization technique for SiC MOSFET in the PCB-embedded package is essential.

In this work, after PID exposure, development, and cure, panel-level double-sided PVD process was carried out. In order to improve the adhesive force between the PID film and the additional metal, a very thin layer of Ti (50 nm) was deposited on the surface as seed layer, followed by the deposition of a layer of thick Cu (500 nm), thus the original Al metallization of front-side gate and source contacts and Ag metallization of backside drain contact were modified. Fig. 16(a) illustrates the successful sputtering on the PID. Compared with waferand chip-level PVD, any kind of chip pad metallization can be performed at panel-level. It is noted that, if sputtering condition is not well controlled and panel sample is not dry, some bubbles could be generated. Fig. 16(b) illustrates the Cu bubbles arising due to high-power sputtering and relatively high vacuum environment. Therefore, a fully dry sample should be prepared and panel-level PVD process should be performed under the low-power and ultralow vacuum environment.

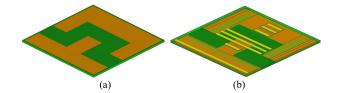

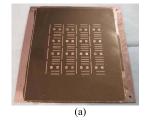

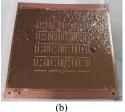

#### C. Double-Sided RDL Interconnection Technique

After PVD process, front-side and backside RDL layers of the PCB-embedded package were built by exposing, developing, plating, etc. Cu and Ti on the nonconductive areas were removed by flash etch and hydrofluoric acid solution, respectively. Fig. 17(a) and (b) shows the front-side and backside RDLs of the panel-level PCB-embedded package, respectively. The double-sided RDLs replaced wire-bonds and interconnection structure related to DBC substrate, the physical length of the commutation loop was shortened, and thus parasitic inductances of the PCB-embedded package were largely reduced.

Fig. 18. Experimental samples. (a) SiC MOSFET bare die. (b) PCB-embedded phase-leg SiC MOSFET power module.

Fig. 19. Custom fixtures for static characterization of (a) SiC MOSFET bare die and (b) PCB-embedded package.

#### VI. STATIC CHARACTERIZATION

#### A. Experimental Sample

Fig. 18(a) and (b) shows the experimental sample of SiC MOSFET bare die and PCB-embedded phase-leg power module, respectively. The SiC MOSFET bare die embedded in the PCB is the SiC DMOSFET from CREE (CPM2-1200-0080B). The backside drain metallization is Ni (0.8  $\mu$ m) and Ag (0.6  $\mu$ m) and front-side source and gate metallization are Al with 4  $\mu$ m thickness [26]. The leads of the PCB embedded package correspond to the terminals of phase-leg power module in Fig. 3.

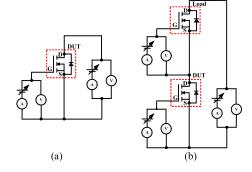

#### B. Experimental Setup

In this article, static characteristics of SiC MOSFET bare die and PCB-embedded package were measured using Power Device Analyzer (Keysight B1505A). For bare dies and custom packages, additional custom fixtures are needed. In order to accurately analyze and investigate the effect of PCB-embedded package on the I-V, C-V, and gate charge characteristics of SiC MOSFET, two custom fixtures were developed, respectively, as shown in Fig. 19(a) and (b). Electrical interconnection of device under test (DUT) was realized via probes on the fixtures. In order to avoid damage of devices or probes due to excessive current, the current limiting in the experiments was set to 20 A.

#### C. I-V Characterization

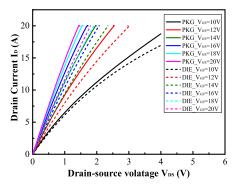

Fig. 20 shows the test circuit for I-V characteristics of SiC MOSFET and PCB-embedded package. The gate and drain of SiC MOSFET were connected to its source through two voltage sources. The drain–source voltage  $V_{\rm DS}$  was swept from 0 to 4 V under the gate–source voltage  $V_{\rm GS}$  from 10 to 20 V at the step of 2 V.

Fig. 21 shows the effect of PCB-embedded package on output characteristics of SiC MOSFET. It can be observed

Fig. 20. Test circuit for I-V characteristics of SiC MOSFET and PCB-embedded package.

Fig. 21. Effect of PCB-embedded package on output characteristics.

from the figure, there was no evident boundary between linear and saturation regions of SiC MOSFET. As drain–source voltage  $V_{\rm DS}$  increased, drain current  $I_{\rm D}$  did not have the trend of saturation. Output current ( $I_{\rm D}$ ) of PCB-embedded package was decreased under a certain gate–source voltage  $V_{\rm GS}$  compared to SiC MOSFET bare die. To realize the same output current, higher gate–source voltage  $V_{\rm GS}$  is needed due to existence of parasitic resistance.

#### D. C-V Characterization

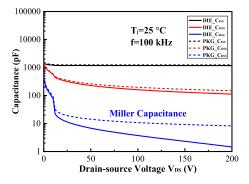

Dynamic characteristics of SiC MOSFET are dominated by charging and discharging of parasitic capacitances, which include gate–source capacitance  $C_{\rm GS}$ , drain–source capacitance  $C_{\rm DS}$ , and gate–drain capacitance (miller capacitance)  $C_{\rm GD}$  [9], [10], [23].

Nonlinear miller capacitance  $C_{\rm GD}$  is the most important and complicated parasitic capacitance, it provides a feedback loop between output and input of MOSFET. As shown in Fig. 1, the miller capacitance  $C_{\rm GD}$  is composed of a constant gate oxide capacitance  $C_{\rm OX}$  and a nonlinear SiC depletion layer capacitance  $C_{\rm GDJ}$ .

Fig. 22 shows the test circuit for C-V characteristics of SiC MOSFET and PCB-embedded package. The gate of SiC MOSFET was short-connected to its source. The drain was connected to its source through one voltage source. The drain–source voltage  $V_{\rm DS}$  was swept from 0 to 200 V at a frequency of 100 kHz.

Fig. 23 shows the effects of PCB-embedded package on input ( $C_{\rm ISS}$ ), output ( $C_{\rm OSS}$ ), and reverse ( $C_{\rm RSS}$ ) capacitances

Fig. 22. Test circuit for  $C\!-\!V$  characteristics of SiC MOSFET and PCB-embedded package.

Fig. 23. Effect of PCB-embedded package on input-output, and reverse capacitances of SiC MOSFET.

of SiC MOSFET. The parasitic inductances of SiC MOSFET are related to the terminal capacitances as

$$C_{\rm GD} = C_{\rm RSS} \tag{2}$$

$$C_{\rm GS} = C_{\rm ISS} - C_{\rm GD} \tag{3}$$

$$C_{\rm DS} = C_{\rm OSS} - C_{\rm GD}. \tag{4}$$

It can be seen from the figure, the PCB-embedded package had a great impact on reverse capacitance (miller capacitance) of SiC MOSFET, had a certain effect on output capacitance, and influence of PCB-embedded package on input capacitance was little. Miller capacitance of SiC MOSFET was increased thanks to parasitic capacitance brought from package. As drain–source voltage  $V_{\rm GS}$  increased, the difference of miller capacitance between the package and the bare die increased. According to (3) and (4), gate–source capacitance  $C_{\rm GS}$  and drain–source capacitance  $C_{\rm DS}$  were decreased.

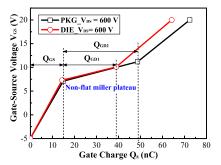

#### E. Gate Charge Characterization

SiC MOSFET has much lower output capacitances and gate charge, and they can switch at much higher dv/dt and di/dt. High switching speed enables low switching loss and high switching frequency, which can improve the power density and efficiency of power module.

Gate charge (Qg) is the total amount of charge to turn on/off a power device. It is one of the key parameters of MOSFETs and IGBTs [33], and especially important for high-frequency

Fig. 24. Test circuit for gate charge characterization of SiC MOSFET and PCB-embedded package. (a) High-voltage measurement circuit. (b) High-current measurement circuit.

Fig. 25. Effect of PCB-embedded package on gate charge.

wide bandgap devices, e.g., SiC MOSFET and GaN HEMT. Qg can be used to assess the switching performance, e.g., gate driving loss, switching time, and miller capacitance.

To measure Qg, a test circuit with a constant current source, or a resistive load, or an inductive load is often shown in a datasheet. Conventional measurement methods require power suppliers that can simultaneously deliver high voltage and high current. The test cost and operational risk are relatively high. Furthermore, when high voltage and high current are applied to the DUT simultaneously, the power dissipation is enormous [33]. In this work, high-voltage/low-current and high-current/low-voltage measurements were performed, respectively. The test circuits are shown in Fig. 24(a) and (b). Different from the former, the high-current measurement circuit is a phase-leg structure. High side is a constant current load. A TO247 Si IGBT with the same power rating was used in this experiment.

The high-voltage measurement was performed at the OFF-state, whereas the high-current measurement was conducted from initial OFF-state to fully ON-state. The two Qg curves were merged to form a total Qg curve.

As shown in Figs. 25 and 26, gate charge curve consists of three segments with different slopes. In the first segment,  $C_{\rm ISS}$  was charged by gate current  $I_{\rm G}$  from OFF-state, because  $C_{\rm GS}$  is much larger than  $C_{\rm GD}$ , the gate charge in the segment is named as  $Q_{\rm GS}$ . Gate-source voltage  $V_{\rm GS}$  in the segment was increased until drain current of SiC MOSFET reached a load current of 20 A. Different from IGBT, drain current  $I_{\rm D}$  of SiC MOSFET in the saturation region increases with drain-source voltage  $V_{\rm DS}$  due to its short-channel effect and modest transconductance [34], [35].

Fig. 26. Effect of drain-source voltage on gate charge.

Fig. 27. Switching characteristics test for SiC MOSFET. (a) DPT equivalent circuit. DPT boards of (b) PCB-embedded package, and (c) TO-247 package.

In the second segment, where SiC MOSFET was changing from ON-state to fully ON-state. Because gate current  $I_G$  flows into the  $C_{RSS}$  and drain current does not saturate, gate—source voltage increases slowly, the gate charge in the segment is called as  $Q_{GD}$ . In the last segment, the SiC MOSFET was fully turned on.

As shown in Fig. 25, under the same drain–source voltage  $V_{\rm DS}$  of 600 V, drain current  $I_{\rm D}$  of DUT increased quickly with gate–source voltage  $V_{\rm GS}$ . Once the drain current  $I_{\rm D}$  reached the load current, it would stop increasing and keep the value. Drain–source voltage  $V_{\rm DS}$  began to decrease. With the decline of drain–source voltage  $V_{\rm DS}$ , gate–source voltage  $V_{\rm GS}$  slowly increased due to unsaturation of drain current  $I_{\rm D}$ . Therefore, miller plateau of SiC MOSFET was nonflat. From the figure, it can be found that  $Q_{\rm GS}$  was almost the same before and after packaging, nonflat miller plateau of PCB-embedded package extended compared to SiC MOSFET bare die.  $Q_{\rm GD}$  increased by 10 nC.

For the PCB-embedded SiC MOSFETs package, effect of drain-source voltage  $V_{\rm DS}$  on Qg was also investigated, as shown in Fig. 26. It is found that as drain-source voltage  $V_{\rm DS}$  increased, the nonflat miller plateau extended.

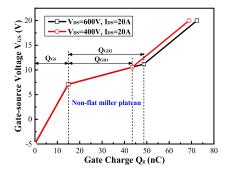

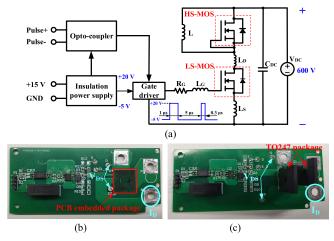

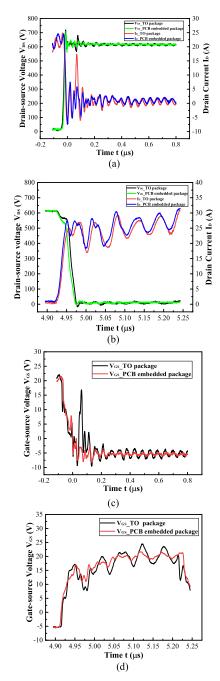

#### VII. SWITCHING CHARACTERIZATION

Double pulse test (DPT) is widely used for evaluating the switching characteristics of power devices, e.g., MOSFET and

Fig. 28. Comparison of switching characteristics and driver waveforms between the PCB-embedded package and the TO-247 package. (a) Turn-off. (b) Turn-on. (c) Driver signal transition from high-to-low voltage. (d) Driver signal transition from low-to-high voltage.

IGBT. It is an inductive load double-pulse test setup and primarily consists of a dc power supply, a load inductor, a dc capacitor, and a gate driver.

In this work, DPT was used to evaluate and compare the switching characteristics of SiC MOSFET in the PCB-embedded phase-leg power module and the conventional TO-247 discrete package. The equivalent circuit schematic of DPT is shown in Fig. 27(a). The dc bus voltage was 600 V. The gate of the HS-MOS was connected to its source and its body-diode was used for the reverse recovery. The LS-MOS was controlled by a double-pulse gate signal,

as shown in the figure. The time of the first and second pulse was 1  $\mu$ s and 0.3  $\mu$ s, respectively. The duration between the two pulses was 5  $\mu$ s. Fig. 27(b) and (c) displays DPT board of the PCB-embedded phase-leg power module and the TO-247 package, respectively. Because the PCB-embedded package is a surface mount device, it is difficult to test real switching waveforms of the package. In this experiment, switching waveforms of test points on the DPT boards of the PCB-embedded package and the TO-247 package were measured and compared. Test points on the DPT boards were designed as close as possible to the leads of the PCB-embedded package and TO-247 package, as shown in Fig. 27(b) and (c), respectively. In order to ensure the equality of comparison, the distance and width of the power loop and driver loop of the two packages were nearly the same, respectively.

Fig. 28 compares the switching characteristics and the driver signal waveforms between the PCB-embedded package and the TO-247 discrete package. As can be seen from Fig. 28(a) and (b), the PCB-embedded package had smaller voltage overshoot and current oscillation at turn-off and smaller voltage oscillation and current overshoot at turn-on than TO-247 package. The results indicated that the PCB-embedded package had smaller parasitic inductances and capacitances than TO-247 package, making SiC MOSFET more suitable for high voltage and high frequency applications.

As can be seen from Fig. 28(c) and (d), the driver signals of the PCB-embedded power module had significantly smaller oscillation than TO discrete package. Because the power and driver loops were connected through source terminal of LS-MOS, larger parasitic inductances of the power loop connected to the TO-247 package would affect the driver loop, leading to larger oscillation of the driver signal. When the oscillation amplitude exceeds threshold voltage of SiC MOSFET, it could falsely turn on the device, thereby affecting the normal operation of the circuit. The PCB-embedded package module proposed in this article had smaller parasitic inductances, which could reduce the oscillation of the driver signal and avoid false turn-on in high frequency applications.

#### VIII. CONCLUSION

In this article, a novel fan-out panel-level PCB-embedded package for phase-leg SiC MOSFET power module was developed. Electro-thermo-mechanical co-design of the PCBembedded SiC MOSFETs package was conducted. Three key PCB-embedded packaging process, including PID exposure and development, panel-level PVD, and double-sided RDL interconnection techniques, were proposed to replace conventional laser drilling, chip/wafer-level PVD, and wire bonding techniques. To accurately characterize the PCB-embedded package and analyze the effect of PCB-embedded package on SiC MOSFET bare die, two custom fixtures were developed. I-V, C-V, and gate charge characteristics of SiC MOSFET and PCB-embedded package were analyzed and compared. DPT was used to evaluate and compare the switching characteristics of SiC MOSFET in the PCB-embedded phase-leg power module and TO-247 discrete package. Some conclusions are drawn as follows.

- The maximum parasitic inductance of the PCBembedded SiC MOSFETs is about 1.24 nH at 100 kHz. Compared with conventional wire-bonded package, the parasitic inductances of the PCB-embedded package decrease by 87.6% at least.

- Compared with blind via structure, thermal resistance of the proposed structure reduces by about 26% at most, and von Mises stress of the SiC MOSFET decreases by about 45.2%.

- 3) When performing PID exposure and development process, laminate should not be thicker than die, die placement should be well controlled and also the process condition. Panel-level PVD process should be performed under the low-power sputtering and ultralow vacuum environment.

- 4) Output current of PCB-embedded package is decreased under a certain gate–source voltage compared to SiC die. To realize the same output current, higher gate–source voltage is needed due to existence of parasitic resistance.

- 5) The PCB-embedded package has a great impact on miller capacitance of SiC MOSFET, which is increased thanks to parasitic capacitance brought from package. As drain-source voltage increases, the difference of miller capacitance between the package and the bare die increased.

- 6) Only nonflat miller plateau of SiC MOSFET before and after packaging is different. Compared with SiC MOSFET bare die, the nonflat miller plateau of PCB-embedded package extends, and  $Q_{\rm GD}$  increases by 10 nC. As drain–source voltage increases, the nonflat miller plateau extends.

- 7) The PCB-embedded package module has smaller parasitic inductances, which can reduce the oscillation of the driver signal and avoid false turn-on in high frequency applications.

#### REFERENCES

- R. Khazaka, L. Mendizabal, D. Henry, and R. Hanna, "Survey of hightemperature reliability of power electronics packaging components," *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2456–2464, May 2015.

- [2] J. Fabre, P. Ladoux, and M. Piton, "Characterization and implementation of dual-SiC MOSFET modules for future use in traction converters," *IEEE Trans. Power Electron.*, vol. 30, no. 8, pp. 4079–4090, Aug. 2015.

- [3] J. Fabre and P. Ladoux, "Parallel connection of 1200-V/100-A SiC-MOSFET half-bridge modules," *IEEE Trans. Ind. Appl.*, vol. 52, no. 2, pp. 1669–1676, Apr. 2016.

- [4] D.-P. Sadik, K. Kostov, J. Colmenares, F. Giezendanner, P. Ranstad, and H. Nee, "Analysis of parasitic elements of SiC power modules with special emphasis on reliability issues," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 4, no. 3, pp. 988–995, Sep. 2016.

- [5] J. Hornberger, A. B. Lostetter, K. I. Olejniczak, T. McNutt, S. M. Lal, and A. Mantooth, "Silicon-carbide (SiC) semiconductor power electronics for extreme high-temperature environments," in *Proc. IEEE Aerosp. Conf.*, Big Sky, MT, USA, Mar. 2004, pp. 2538–2555.

- [6] J. W. Palmour et al., "Silicon carbide power MOSFETs: Breakthrough performance from 900 V up to 15 kV," in Proc. IEEE 26th Int. Symp. Power Semicond. Devices IC's , Waikoloa, HI, USA, Jun. 2014, pp. 79–82.

- [7] S.X. Guo, "Megahertz high voltage isolated DC/DC converter based on SiC MOSFETs," Ph.D. dissertation, Dept. Elect. Eng., North Carolina State Univ., Raleigh, TC, USA, 2017.

- [8] S. Toyoshima, S. Hatsukawa, N. Hirakata, T. Tsuno, and Y. Mikamura, "Compact SiC power module for high speed switching," *Electronics*, vol. 80, pp. 81–84, Jan. 2015.

- [9] L. Wu, L. Xiao, J. Zhao, and G. Chen, "Physical analysis and modeling of the nonlinear miller capacitance for SiC MOSFET," in *Proc. 43rd Annu. Conf. IEEE Ind. Electron. Soc.*, Beijing, China, Oct./Nov. 2017, pp. 1411–1416.

- [10] S. Yin et al., "An accurate subcircuit model of SiC half-bridge module for switching-loss optimization," *IEEE Trans. Ind. Appl.*, vol. 53, no. 4, pp. 3840–3848, Jul./Aug. 2017.

- [11] B. Mouawad et al., "Application of the spark plasma sintering technique to low-temperature copper bonding," *IEEE Trans. Compon. Packag.*, Manuf. Technol., vol. 2, no. 4, pp. 553–560, Apr. 2012.

- [12] B. Mouawad et al., "Direct copper bonding for power interconnects: Design, manufacturing, and test," IEEE Trans. Compon. Packag., Manuf. Technol., vol. 5, no. 1, pp. 143–150, Jan. 2012.

- [13] L. Xu, M. Wang, Y. Zhou, Z. Qian, and S. Liu, "Effect of silicone gel on the reliability of heavy aluminum wire bond for power module during thermal cycling test," in *Proc. IEEE 66th Electron. Compon. Technol.* Conf., Las Vegas, NV, USA, May/Jun. 2016, pp. 1005–1010.

- [14] A. Ostmann et al., "Integration of passive and active components into build-up layers," in Proc. 4th Electron. Packag. Technol. Conf., Singapore, Dec. 2002, pp. 223–228.

- [15] L. Boettcher, D. Manessis, A. Ostmann, S. Karaszkiewicz, and H. Reichl, "Embedding of chips for system in package realizationtechnology and applications," in *Proc. 3rd Int. Microsyst., Packag.*, *Assem. Circuits Technol. Conf.*, Taipei, Taiwan, Oct. 2008, pp. 383–386.

- [16] R. Aschenbrenner, "System-in-package solutions with embedded active and passive components," in *Proc. Int. Conf. Electron. Packag. Technol. High Density Packag.*, Shanghai, China, Jul. 2008, pp. 1–2.

- [17] L. Boettcher, S. Karaszkiewicz, D. Manessis, and A. Ostmann, "Development of embedded power electronics modules," in *Proc. 4th Electron. Syst.-Integr. Technol. Conf.*, Amsterdam, The Netherlands, Sep. 2012, pp. 1–6.

- [18] A. Munding, A. Kessler, T. Scharf, B. Plikat, and K. Pressel, "Laminate chip embedding technology—Impact of material choice and processing for very thin die packaging," in *Proc. IEEE 67th Electron. Compon. Technol. Conf.*, Orlando, FL, USA, May/Jun. 2017, pp. 711–718.

- [19] D. J. Kearney, S. Kicin, E. Bianda, and A. Krivda, "PCB embedded semiconductors for low-voltage power electronic applications," *IEEE Trans. Compon. Packag., Manuf. Technol.*, vol. 7, no. 3, pp. 387–395, Mar. 2017.

- [20] Y. Pascal, A. Abdedaim, D. Labrousse, M. Petit, S. Lefebvre, and F. Costa, "Using laminated metal foam as the top-side contact of a PCB-embedded power die," *IEEE Electron Device Lett.*, vol. 38, no. 10, pp. 1453–1456, Oct. 2017.

- [21] E. Parker, B. Narveson, A. Alderman, and L. Burgyan, "Embedding active and passive components in PCBs and inorganic substrates for power electronics," in *Proc. IEEE Int. Workshop Integr. Power Packag.*, Chicago, IL, USA, May 2015, pp. 107–110.

- [22] D. Yang, M. Kengen, W. G. M. Peels, D. Heyes, and W. D. van Driel, "Reliability modeling on a MOSFET power package based on embedded die technology," *Microelectron. Rel.*, vol. 50, no. 7, pp. 923–927, Jul. 2010.

- [23] M. Mudholkar, S. Ahmed, M. N. Ericson, S. S. Frank, C. L. Britton, and H. A. Mantooth, "Datasheet driven silicon carbide power MOSFET model," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2220–2228, May 2014.

- [24] Z. Zhang, "Characterization and realization of high switching-speed capability of SiC power devices in voltage source converter," Ph.D. dissertation, Dept. Elect. Eng., Univ. Tennessee, Knoxville, TN, USA, 2015.

- [25] K. Peng, S. Eskandari, and E. Santi, "Characterization and modeling of SiC MOSFET body diode," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, Long Beach, CA, USA, Mar. 2016, pp. 2127–2135.

- [26] CREE. CPM2-1200-0080B Silicon Carbide Power MOSFET. Accessed: Jan. 2016. [Online]. Available: https://www.wolfspeed.com/media/downloads/157/CPM2-1200-0080B.pdf

- [27] F. Hou, W. Wang, T. Lin, L. Cao, G. Q. Zhang, and J. A. Ferreira, "Characterization of PCB embedded package materials for SiC MOS-FETs," *IEEE Trans. Compon. Packag., Manuf. Technol.*, vol. 9, no. 6, pp. 1054–1061, Jun. 2019.

- [28] M. Pavier, A. Sawle, A. Woodworth, R. Monteiro, J. Chiu, and C. Blake, "High frequency DC: DC power conversion: The influence of package parasitics," in *Proc. 18th Annu. IEEE Appl. Power Electron. Conf. Expo.*, Miami Beach, FL, USA, Feb. 2003, pp. 699–704.

- [29] F. Hou et al., "Experimental verification and optimization analysis of warpage for panel-level fan-out package," *IEEE Trans. Compon. Packag.*, Manuf. Technol., vol. 7, no. 10, pp. 1721–1728, Oct. 2017.

- [30] D. G. Yang et al., "Numerical modeling of warpage induced in QFN array molding process," *Microelectron. Rel.*, vol. 47, nos. 2–3, pp. 310–318, Feb./Mar. 2006.

- [31] G. Q. Zhang, W. D. van Driel, and X. J. Fan, Mechanics of Microelectronics, vol. 141. Dordrecht, The Netherlands: Springer, 2006.

- [32] D. R. M. Woo, H. H. Yuan, J. A. J. Li, L. J. Bum, and Z. Hengyun, "MMiniaturized double side cooling packaging for high power 3 phase SiC inverter module with junction temperature over 220°C," in *Proc. IEEE 66th Electron. Compon. Technol. Conf.*, Las Vegas, NV, USA, May/Jun. 2016, pp. 1190–1196.

- [33] A. Mikata, "A novel gate charge measurement method for high-power devices," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, Charlotte, NC, USA, Mar. 2015, pp. 2485–2487.

- [34] B. Callanan, Application Considerations for SiC MOSFETs. Durham, NC, USA: Cree Inc., Jan. 2011.

- [35] S. Ji, Z. Zhang, and F. Wang, "Overview of high voltage SiC power semiconductor devices: Development and application," CES Trans. Elect. Mach. Syst., vol. 1, no. 3, pp. 254–264, Sep. 2017.

**Fengze Hou** is currently pursuing the Ph.D. degree with the Department of Microelectronics, Delft University of Technology, Delft, The Netherlands.

In July 2012, he works as an Assistance Researcher with the Institute of Microelectronics of Chinese Academy of Sciences, Beijing, China. He is currently a Senior Engineer with the National Center for Advanced Packaging, Wuxi, China. His interests include thermal management, reliability, system integration, and SiC power module packaging.

Wenbo Wang received the B.Sc. degree in electrical engineering and automation and M.Sc. degree in power electronics and electrical drives from Northwestern Polytechnical University, Xi'an, China, in 2008 and 2010, respectively, and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2017.

He is currently with the Shenzhen Institute of Wide Bandgap Semiconductors (Wins), Shenzhen, China. His current research interests include wide bandgap semiconductors, high frequency magnetics, and high frequency power converters.

**Rui Ma** received the M.Sc. degree in mechanics from the Beijing University of Technology, Beijing, China, in 2018.

She is currently an Engineer with the System Packaging and Integration Research Center, Institute of Microelectronics of Chinese Academy of Sciences, Beijing. Her interests include fan-out packaging technology and reliability analysis.

Yonghao Li received the B.Sc. degree in electrical engineering and automation from the China University of Mining and Technology, Xuzhou, China, in 2018. He is currently pursuing the Ph.D. degree in electrical engineering with Zhejiang University, Hangzhou, China.

His current research interests include power semiconductors and its packaging, high-power-density integration of power conversion, and the package of SiC power module.

Yang Song has been working with the Design, Packaging Process, and Substrate Technology for more than ten years. From 2008 to 2012, he worked with the R&D Department of Shennan Circuits Co., Ltd, China. Since 2012, he has been an Engineer for R&D of Substrate and Packaging Process, IMECAS. His interests mainly include fine line/glass/coreless substrate, and PCB embedded package.

Zhonglin Han received the B.Sc. degree from Inner Mongolia University, Huhhot, China. He is currently pursuing the Ph.D. degree in microelectronics and solid-state electronics with the Institute of Microelectronics of Chinese Academy of Sciences, Beijing, China.

His research interest is SiC-based power devices processing and packaging.

Qidong Wang received the B.Sc. degree in electronic science and technology from Southeast University, Nanjing, China, the M.S. degree in electronic communications and computer engineering from the University of Nottingham, Nottingham, U.K., and the Ph.D. degree in microelectronics and solid state electronics from the University of Chinese Academy of Sciences, Beijing, China, in 2014.

In 2009, he joined the System Packaging and Integration Research Center, Institute of Microelectronics of Chinese Academy of Sciences, Beijing,

where he is currently the Deputy Director of the Center, working in the area of advanced substrate and 2.5D/3D integration. From 2015 to 2016, he visited Varian Lab of Stanford University, Stanford, CA, USA, and worked on the integrated electron and photon detection device. His recent research is focused on the embedding RF/Power module, and multiple heterogeneous integration projects with 2.5D/3D approach.

**Meiying Su** received the Ph.D. degree in circuit and system from the Dalian University of Technology, Dalian, China.

In 2012, she was an Assistant Researcher with the Institute of Microelectronics of Chinese Academy of Sciences, Beijing, China. Since 2015, she has been an Associate Professor. Her interests include thermal management and thermo-mechanical reliability analysis of 2.5D/3D packaging and fan-out packaging.

Min Chen received the B.Sc. degree in applied electronics and the Ph.D. degree in electrical engineering from Zhejiang University, Hangzhou, China, in 2000 and 2006, respectively.

From 2007 to 2009, he was a Post-Doctoral Researcher with the Electrical Engineering Department, Zhejiang University, where he has been a Lecturer since 2010, and is currently an Associate Professor. From 2014 to 2015, he was a Visiting Researcher with the Department of Energy Technology, Aalborg University, Aalborg, Denmark, Since

2007, he has been responsible for the Lighting Research and Development Laboratory, National Engineering Research Center for Applied Power Electronics, Zhejiang University. He has authored or coauthored more than 60 technical articles. He was issued for 14 patents of inventions. His research interests include power electronics in power systems, inverter systems, photovoltaic system and micro-inverter, electrical vehicle, regenerative energy systems, distributed generation, and energy storage systems.

**Jun Li** received the B.Sc. degree in electronics science and technology and Ph.D. degree in electromagnetic field and microwave technology from Southwest Jiaotong University, Chengdu, China, in 2004 and 2010, respectively.

From 2010 to August 2012, she finished her Post-Doctoral research with the Institute of Microelectronics of Chinese Academy of Sciences (IMECAS), Beijing, China. From August 2012 to 2014, she was an Assistant Researcher. Since 2014, she has been an Associate Professor. She is currently the Associate

Director of the System Packaging and Integration Research Center, IMECAS. She has published more than 30 articles. She holds 16 patents. Her interests include the design and simulation of system in package, simulation methods of advanced packaging, DFx codesign, signal integrity, power integrity, IPD design, thermal management of advanced packaging, and high-power cooling technology.

**Zhongyao Yu** received the B.Sc. degree in semiconductor chemistry from Jilin University, Changchun, China, in 1989.

From 1989 to 1994, he was an Engineer with Beiyang Electronic Group Company, Weihai, China. In 1994, he joined Beijing Solar Energy Research Institute, Beijing, China. From 1998 to 2001, he worked as an Engineer with the State Key Laboratory of Transducer Technology, Shanghai, China. From 2001 to 2010, he was the Vice Director of the Advanced Technique Department, Capitalbio

Corporation, Beijing. In 2010, he joined IMECAS, Beijing, and set up the cleanroom of substrate and package. He has been working MEMS and Advanced Packaging for 30 years. He is currently a Thief Scientist of NCAP China. He develops ESAP technique, and holds over 58 patents on advanced packaging and MEMS.

**Liqiang Cao** received the B.Sc. degree from the University of Science and Technology of China, Hefei, China, and the M.Sc. and Ph.D. degrees from the Chalmers University of Technology, Gothenburg, Sweden

Between 2000 and 2005, he was with the IVF-The Swedish Institute of Production Engineering Research, Molndal, Sweden, and the Sino-Swedish Microsystem Integration Technology (SMIT) Center, Sweden, as a Research Fellow. Then, he joined Intel in October 2005 as a Senior Scientist and a Program

Manager. Since February 2009, he has been a Professor with the Institute of Microelectronics of Chinese Academy of Sciences, Beijing, China. He is currently the General Manager of the National Center for Advanced Packaging China (NCAP), China. His research interests focus on the design, FEM, and packaging process of advanced packaging.

**Guoqi Zhang** (M'03–F'14) received the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 1993.

He is the Chair Professor for "Micro/Nanoelectronics System Integration and Reliability", Delft University of Technology. He had worked for NXP Semiconductors as the Senior Director of Technology Strategy until 2009, Philips Research Fellow until May 2013. He authored/coauthored more than 400 scientific publications. His research interest covers multi-level heterogeneous

system integration and packaging, wide band gap semiconductors sensors and components, multi-physics and multiscale modeling of micro/nanoelectronics, and digital twin for mission critical multi-functional electronics components and systems.

Dr. Zhang serves as the Deputy Director for the European Center for Micro- and Nanoreliability (EUCEMAN), the Co-Chair of the Advisory Board of International Solid State Lighting Alliance (ISA), the Secretary General of the International Technology Roadmap of Wide bandgap Semiconductors (ITRW).

**Braham Ferreira** (M'88–SM'01–F'05) received the Ph.D. degree in electrical engineering from the Rand Afrikaans University, Johannesburg, South Africa.

In 1981, he was with the Institute of Power Electronics and Electric Drives, Technical University of Aachen, Aachen, Germany, and worked as a System Engineer with ESD Pty (Ltd) from 1982 to 1985. From 1986 to 1997, he was with the Department of Electrical Engineering, Rand Afrikaans University, where he held the Carl and Emily Fuchs Chair of Power Electronics in later years. From 1998 to

2018, he held the Chair in Power electronics and Electrical Machines, Delft University of Technology, Delft, The Netherlands. He served as the Head of the Department from 2006 to 2010 and was the Director of the Delft-Beijing Institute of Intelligent Science and Technology from 2017 to 2018. He is currently a Professor of power electronics, University of Twente, Enschede, The Netherlands. He is the author or the coauthor of 100 journal and transactions articles, 300 conference articles and 15 patents.

Dr. Ferreira was awarded the 15 prize paper awards. He was a recipient of the IEEE IAS Gerald Kliman Innovator Award and the IAS Outstanding Achievement Award. He is the Chair of the IEEE ITRW. He served as the President of the IEEE Power Electronics Society from 2015 to 2016.