#### CMOS Wide-Bandwidth Magnetic Sensors for Contactless Current Measurements

Jiang, Junfeng

10.4233/uuid:38dfa450-82c2-4b63-92d1-26b2eb3adeed

**Publication date**

**Document Version** Final published version

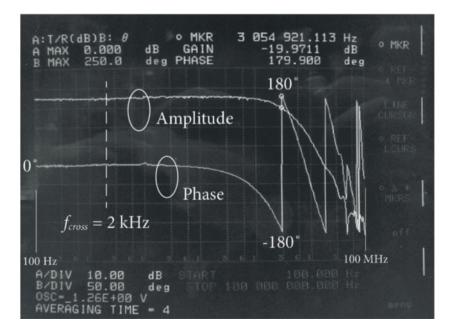

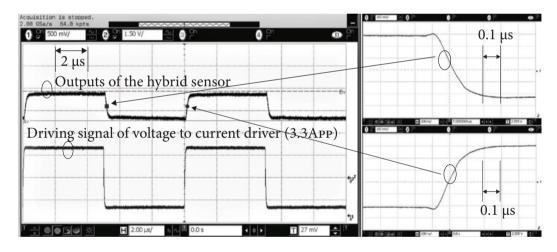

Citation (APA)

Jiang, J. (2019). CMOS Wide-Bandwidth Magnetic Sensors for Contactless Current Measurements. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:38dfa450-82c2-4b63-92d1-26b2eb3adeed

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# CMOS Wide-Bandwdith Magnetic Sensors

Contactless Current Measurements

## CMOS Wide-Bandwidth Magnetic Sensors for Contactless Current Measurements

### CMOS Wide-Bandwidth Magnetic Sensors for Contactless Current Measurements

#### Proefschrift

ter verkrijging van de grad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. dr. ir. T.H.J.J. van der Hagen voorzitter van het College voor Promoties,

> in het openbaar te verdedigen op donderdag 25 april 2019 om 15:00 uur

> > door

### Junfeng JIANG

electrotechnisch ingenieur

Technische Universiteit Delft, Nederland

geboren te Dalian, China

Dit proefschrift is goedgekeurd door de promotoren.

Samenstelling promotiecommissie bestaat uit:

Rector Magnificus, voorzitter

Prof. dr. K.A.A. Makinwa Technische Universiteit Delft, promotor

Onafhankelijke leden:

Prof. dr. W. Sansen Katholieke Universiteit Leuven

Prof. dr. ir. E. Cantatore Technische Universiteit Eindhoven

Prof. dr. B. Wicht Leibniz Universität Hannover

Prof. dr. ir. W. Serdijn Technische Universiteit Delft

Prof. dr. L. de Vreede Technische Universiteit Delft

Dr. M. Pertijs Technische Universiteit Delft

Printed by **IPSKAMP** printing

ISBN: 978-94-6384-025-5

FSC responsible sources

FSC C128610

#### Copyright © 2019 by J. Jiang

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by an information storage and retrieval system, without written permission of the author.

Printed in the Netherlands

To my beloved parents and Xi 致我亲爱的父母和成茜

# Table of Contents Chapter 1 Introduction

| Chapter 1 Introduction                                  |    |

|---------------------------------------------------------|----|

| 1.1 Background                                          | 1  |

| 1.2 Motivation and Objectives                           | 3  |

| 1.3 Dissertation Organization                           | 8  |

| 1.4 Bibliography                                        | 9  |

| Chapter 2 Magnetic Sensors in CMOS Technologies         | 13 |

| 2.1 Introduction                                        | 13 |

| 2.2 Hall Effect Sensors                                 | 13 |

| 2.3 Pick-up Coils                                       | 33 |

| 2.4 Conclusions                                         | 39 |

| 2.5 Bibliography                                        | 39 |

| Chapter 3 A Continuous-Time Ripple Reduction Technique  |    |

| for Spinning Current Hall Sensors                       | 43 |

| 3.1 Introduction                                        | 43 |

| 3.2 Ripple Reduction Loop                               | 43 |

| 3.3 Triple RRL Scheme                                   | 46 |

| 3.4 Triple RRL Implementation                           | 48 |

| 3.5 Experimental Results                                | 53 |

| 3.6 Conclusions                                         | 59 |

| 3.7 Bibliography                                        | 60 |

| Chapter 4 A Wide-Bandwidth Multi-Path CMOS Hall Sensor  |    |

| with Integrated Ripple Reduction Loops                  | 63 |

| 4.1 Introduction                                        | 63 |

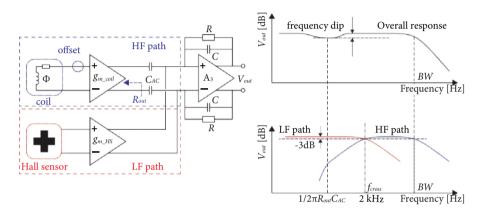

| 4.2 Multi-Path Hall Sensor System                       | 63 |

| 4.3 Experimental Results                                | 73 |

| 4.4 Conclusions                                         | 78 |

| 4.5 Bibliography                                        | 78 |

| Chapter 5 A Hybrid Multi-Path Magnetic Sensor Combining |    |

| Hall Sensors and Pick-up Coils                          | 81 |

| 5.1 Introduction                                        | 81 |

| 5.2 Combination of Hall Sensors and Pick-up Coils                | 82  |

|------------------------------------------------------------------|-----|

| 5.3 System Implementation                                        |     |

| 5.4 Experimental Results                                         | 91  |

| 5.5 Refined Analysis on Optimal Noise                            | 96  |

| 5.6 Conclusions                                                  | 99  |

| 5.7 Bibliography                                                 | 100 |

| Chapter 6 A Low Drift Hybrid Multi-Path CMOS Magnetic            |     |

| Sensor with Discrete-Time RRLs                                   | 101 |

| 6.1 Introduction                                                 | 101 |

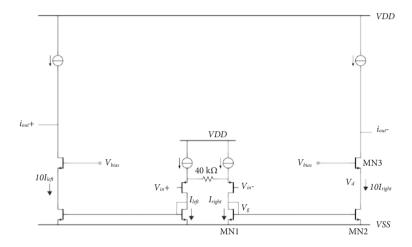

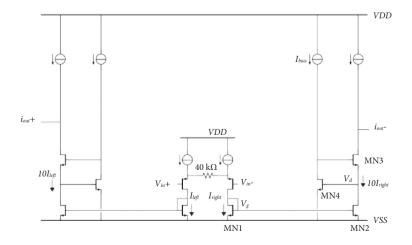

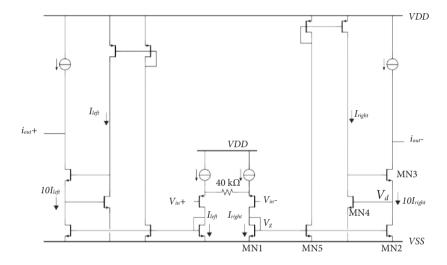

| 6.2 Low Drift CMOS Hall Sensors                                  | 102 |

| 6.3 Low Drift Current Sensor with On-Chip Common-Mode References | 103 |

| 6.4 Experimental Results                                         | 108 |

| 6.5 Conclusions                                                  | 113 |

| 6.6 Bibliography                                                 | 113 |

| Chapter 7 Conclusions and Future Work                            | 115 |

| 7.1 Conclusions                                                  | 115 |

| 7.2 Future Work                                                  | 117 |

| 7.3 Original Contributions                                       | 118 |

| Appendix                                                         | 119 |

| Summary                                                          | 123 |

| Samenvatting                                                     | 127 |

| List of Publications                                             | 133 |

| About the Author                                                 | 135 |

| Acknowledgements                                                 | 137 |

|                                                                  |     |

Introduction

since 1879, the world has been much brighter thanks to Thomas Edison and his invention of the light bulb [1]. This marked a major milestone in mankind's use of electricity as a bridge between different forms of energy, in this case transforming mechanical energy into electricity and then into light and heat. Since then, the generation, distribution, control and measurement of electricity has become an increasingly important topic and field of research.

### 1.1 Background

In the course of the 20<sup>th</sup> century, the use of electricity drastically changed the face of industry by replacing human labor with machines to improve manufacturing and production. However, the safe use of electricity requires the control of current. For instance, excessive current will burn out an incandescent lamp, and for that matter, most other electronic devices. From a macroeconomic perspective, the accurate control of current is even more important. In 2015, over 3,000 million GWh electricity was consumed in Europe [2]. This corresponds to a constant current flow of over 1.5 trillion Amperes during the year. The consequences of failing to control such huge amounts of current are unimaginable.

The ability to measure current is an important premise to controlling it. Advances in physics and material science have revealed the relation between current and many other physical quantities such as heat, voltage and magnetic field. These allow current measurements to be made in many different ways. For instance, the flow of current in a conductor will generate heat, resulting in a measurable temperature change. This effect is the basis of a fuse, which will melt due to the temperature increase caused by excessive current flow. However, this approach has limited accuracy, and slow response due to the ambient temperature dependency and the time delay of the temperature change, respectively. These drawback can be addressed by measuring the voltage across a conductor, a so-called shunt resistor [3]. Applications include, but are not limited to multi-meters, battery monitoring systems in mobile devices, and circuit-breakers in distribution boxes. In high power systems, however, the use of shunt resistors is severely limited due to the lack of galvanic isolation. To achieve this, magnetic sensors can be used to measure the current's induced magnetic field (IMF). Such contactless sensors are often used in hybrid and electric vehicles, electric motors, switched-mode power supplies and smart grids [4].

For high volume, cost-sensitive applications, contactless current sensors are preferably implemented in CMOS (complementary metal-oxide-semiconductor) technology. This is because (1) they are based on silicon (Si), which is cheaper than the substrate materials used by other IC processes such as Gallium Arsenide (GaAs) and Indium Arsenide (InAs); and (2) most signal processing ICs are manufactured in CMOS processes. Therefore CMOS compatible sensors can be easily co-integrated into the signal chain with negligible added cost, occupying significantly less space compared to sensors implemented with discrete components.

Presently, contactless current sensor ICs are widely available in both CMOS and non-CMOS processes. They can be classified according to their working principle, namely Hall Effect (Hall) sensors, magnetoresistive (MR) sensors, fluxgates and pick-up coils. Of these, Hall sensors and pick-up coils can be manufactured in standard CMOS processes, while MR sensors and fluxgates require the use of ferromagnetic materials, which can be added with the help of post processing. For this reason, MR sensors and fluxgates will not be considered in this thesis.

Figure 1.1 400kV HVDC line under the English Channel (Copied from <a href="http://www.ifa2interconnector.com/the-project/">http://www.ifa2interconnector.com/the-project/</a>).

Recent industrial and automotive developments has created a large demand for wide bandwidth contactless current sensors. One example is current sensing in high voltage DC (HVDC) transmission lines, shown in Figure 1.1, which are increasingly used for long distance and undersea power transmission. Compared to high voltage AC (HVAC) transmission systems, HVDC transmission systems have many advantages such as low construction costs and power losses, high power density, capability of transmission and stabilization between unsynchronized AC grids, and most importantly, integration of renewable energy sources into the existing power grid [5]. However, HVDC lines are sensitive to overloading, which can lead to catastrophic power failure and hence severe economic losses. Very fast current sensors, with response time in the

order of microseconds, are then required to prevent damage. Such bandwidths are beyond the reach of conventional CMOS magnetic sensors, especially if an adequate resolution for current measurement must be maintained.

Wide bandwidth current sensors are also required in switched-mode power supplies. Current trends towards higher power efficiency require higher switching frequencies and less power loss [6]. Moreover, the general industrial trend toward smaller power-conversion components requires smaller passive components such as inductors. This in turn requires switching currents at a few MHz [7]. To accurately control the resulting output voltages, currents need to be accurately measured in real-time, which is challenging for conventional current sensors.

The trend towards electrical vehicles (EV) and hybrid electric vehicles (HEV) can be expected to dramatically increase the use of electric motors. EV and HEV motors require high currents and voltages to produce enough horsepower and torque to compete with traditional internal combustion engine powertrains. In order to maximize power efficiency, these motors are usually controlled by PWM drivers. This also requires wide bandwidth current sensors so that the associated current transients can be captured.

Prior to this Ph.D. project, the bandwidth of CMOS contactless current sensors was limited to less than 100 kHz [8], which limited their use in many of the applications discussed above. In consequence, high speed contactless current sensors were typically implemented either with discrete components or in non-CMOS processes such as InAs (Indium Arsenide) [9], both of which are associated with higher costs.

### 1.2 Motivation and Objectives

This dissertation describes research into the realization of wide bandwidth magnetic sensors for current sensing in standard CMOS. The research progressively explores different ways of extending the bandwidth of CMOS magnetic sensors, based on Hall sensors and coils, mainly by improving their readout electronics at the circuit and system levels.

#### 1.2.1 Bandwidth Improvement of CMOS Hall Sensors

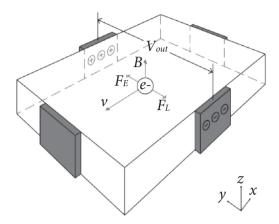

A Hall sensor can be realized as a plate with four contacts, as shown in Figure 1.2. When a biasing current is conducted along the x-axis direction, moving charges experience the Lorentz Force  $(F_L)$ due to the presence of a magnetic field (B) along the z-axis. As a result, charges accumulated at the contacts along the y-axis will build up an electric field to cancel out  $F_L$  such that the net force experienced by the charges is reduced to zero to reach an equilibrium state. The sensor's output is then the voltage difference  $V_{out}$  between the two contacts along the y-axis. For a fixed plate dimension and biasing current,  $V_{out}$  is linearly proportional to the strength of B.

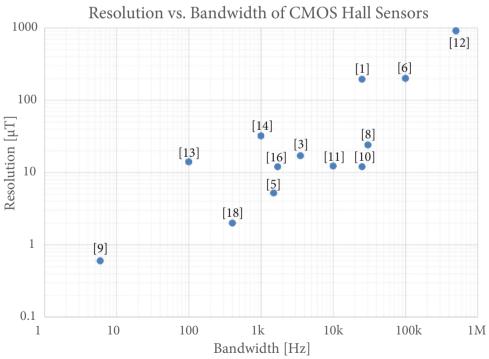

Hall sensor ICs are widely used due to their easy realization in standard CMOS. They are normally fabricated as n-well plates, and have sensitivities ranging from 100 V/A·T to 400 V/A·T [10-13]. With proper interface circuitry, CMOS Hall sensor systems can achieve offsets below  $10 \,\mu T$  [8, 14], bandwidths up to 1 MHz [15], and sub- $\mu T$  resolution [16]. Hall sensors can also be realized in GaAs and InAs processes. Compared to CMOS, these have higher electron mobility, resulting in Hall sensors with greater sensitivity [17].

Figure 1.2 Simplified working principle of a Hall sensor.

Hall sensors are essentially resistors, therefore for a given signal-to-noise ratio (SNR), their useful bandwidth is fundamentally limited by thermal noise. A further increase in bandwidth causes a proportional increase in noise power, and thus a less SNR.

Intrinsically, the bandwidth of CMOS Hall sensors is comparable to that of non-CMOS Hall sensors, e.g., InAs Hall sensors. However, due to their lower sensitivities, CMOS Hall sensors suffer more from noise, and hence achieve worse resolution within the same bandwidth. In other words, CMOS Hall sensors require smaller bandwidths, compared to non-CMOS Hall sensors, to achieve the same resolution. Unfortunately, there have been very few means to improve the bandwidth of CMOS Hall sensors except by using more power.

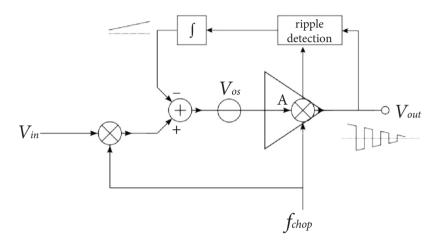

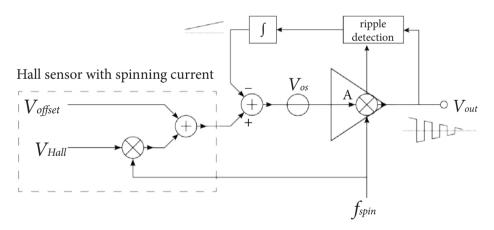

The offset of a typical CMOS Hall sensor can be as large as 10-50 mT, which is often much larger than the maximum signal of interest. This limitation can be overcome by a dynamic offset cancellation technique that was first proposed in 1989 [18]. Known as the "spinning current technique," it is now used in the interface circuits of nearly all of today's CMOS Hall sensors. It involves periodically rotating the direction of the biasing current and the location of the readout terminals, such that the offset and signal can be separated and processed individually. However, it has the drawback that low-pass filters (LPFs) are then required to suppress the offset ripple due to the spinning current operation, which severely limits the system bandwidth, e.g. to below 50 kHz [8].

To overcome the bandwidth limitation associated with the spinning current technique, a first research goal was to obviate the need for LPFs in the signal path. This meant that new methods of suppressing the spinning ripple of Hall sensors had to be found. Inspired by chopper

instrumentation amplifiers, this was achieved with the help of ripple reduction loops (RRL) [19] and multi-path architectures [20].

Despite the new ripple reduction methods, the bandwidth of Hall sensors is ultimately limited by thermal noise for certain resolution specifications, and cannot be improved at the circuit level. A further increase in bandwidth requires innovation at a higher level, i.e. the system level.

#### 1.2.2 Pick-up Coils

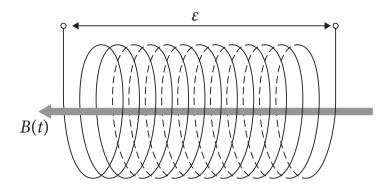

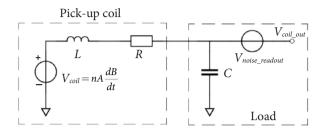

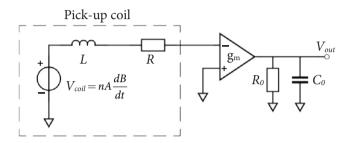

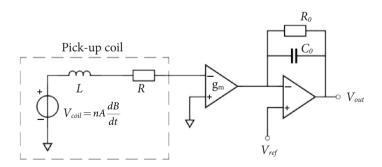

Compared to Hall sensors, pick-up coils (Figure 1.3) are better suited for high frequency current sensing due to their differentiating characteristic. In the presence of a changing magnetic field B, a pick-up coil will generate an electromotive force (EMF)  $\varepsilon$  which is proportional to the time derivative of the magnetic field:

$$\varepsilon = nA \frac{dB}{dt} \tag{1.1}$$

where n is the number of windings of the pick-up coil, and A represents the winding area. For an input magnetic field *B* at frequency *f*, *B* can be expressed as:

$$B = B_0 \cdot \sin(2\pi f \cdot t) \tag{1.2}$$

in which  $B_0$  represents the amplitude of the magnetic field. With Equation (1.2), Equation (1.1) can be rewritten as:

$$\left|\varepsilon\right| = 2\pi f \cdot nA \cdot B_0 \tag{1.3}$$

which suggests that the amplitude and power of the output  $\varepsilon$  is proportional to f and  $f^2$ , respectively. Due to the presence of a source resistance R, thermal noise is expected at the output of a pick-up coil with the power  $N^2$  expressed as:

$$N^2 = 4kTR \cdot f \tag{1.4}$$

Equation (1.3) and (1.4) suggest that the SNR of a pick-up coil is linearly proportional to its input frequency f, making them better suited for measuring high frequency magnetic fields.

Despite the fact that pick-up coils can cover a wide frequency range, e.g. 50 kHz to 1 MHz [21], their sensitivity decreases at low frequencies. This drawback limits their use in wide bandwidth systems that need to cover DC and low frequency signals as well.

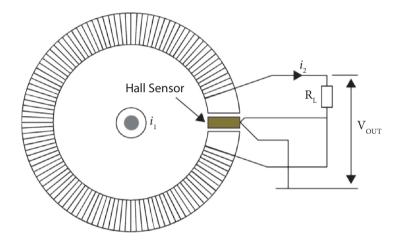

Figure 1.3 Pick-up coil.

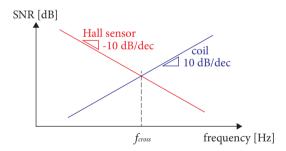

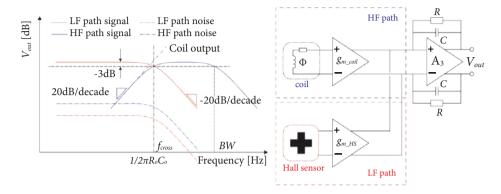

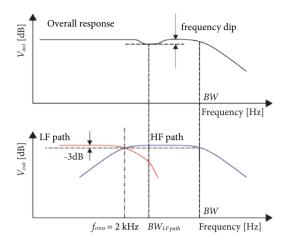

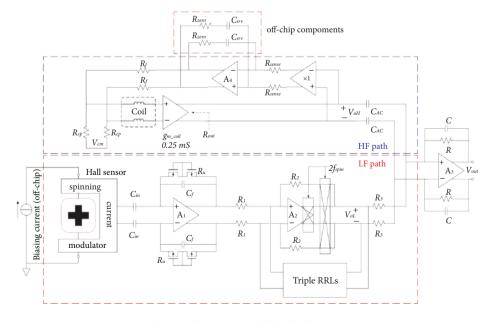

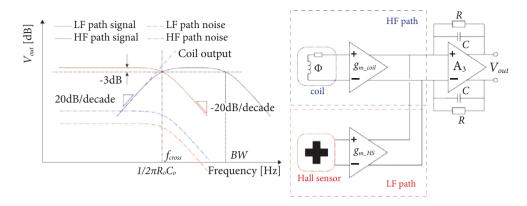

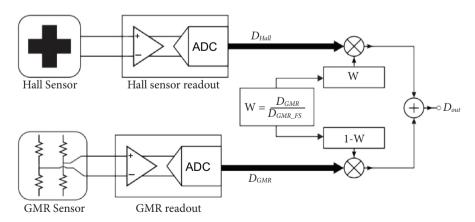

Considering the fact that Hall sensors and pick-up coils are suited for measuring low frequency and high frequency magnetic fields respectively, combining Hall sensors and pick-up coils appears to be a promising system innovation. The second research goal of this thesis is to build a hybrid magnetic sensor by combining Hall sensors and pick-up coils on a single die, so that the overall system can cover a wide bandwidth from DC to beyond 1 MHz.

#### 1.2.3 Hybrid Magnetic Sensors

The idea of realizing hybrid magnetic sensors by combining different types of sensors, e.g., Hall sensors and pick-up coils, is not new, and some systems have been reported in the literature [22-24]. These can be divided into closed-loop and open loop-loop systems. In a closed-loop system, an unknown magnetic field is cancelled by driving a feedback coil with a current. The zero-field condition is detected by a Hall sensor and the unknown magnetic field is then proportional to the current in the coil. In an open-loop system, the outputs of a Hall sensor and a coil are simply combined. However, all the hybrid magnetic sensors reported in literature were implemented with discrete components and so did not address the challenges of CMOS integration. The following section gives a brief overview of prior work on hybrid magnetic sensors.

#### **Closed-Loop Hybrid Magnetic Sensors**

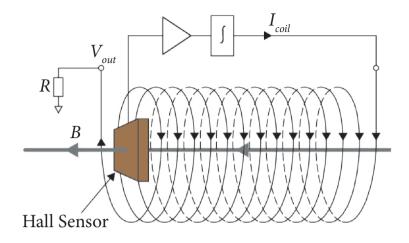

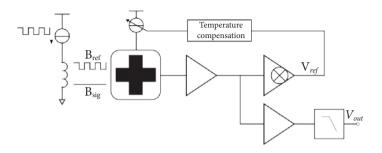

Due to the fact that magnetic fields can be directly generated by current flow, magnetic sensors can be realized in closed-loop architectures with the help of feedback coils [22]. Figure 1.4 shows an example of a closed-loop magnetic sensor using Hall sensors and coils. The magnetic field B is read out by a Hall sensor. The output of the Hall sensor is then amplified and integrated to drive the feedback coil with a current  $I_{coil}$ . The feedback coil then generates a feedback magnetic field which counter balances the input magnetic field B. Any residual magnetic field will be read out by the Hall sensor to adjust the feedback current  $I_{coil}$ . At steady state, B will be fully cancelled by  $I_{coil}$ , which is read out by  $V_{out} = I_{coil} * R$ .

Figure 1.4 Closed-loop magnetic sensor with a Hall sensor and a feedback coil.

The closed-loop architecture can also be used to achieve wide bandwidths since the coil continues to generate an output voltage after the Hall sensor runs out of bandwidth [25, 26]. However, due to the presence of multiple time constants in the system, transfer function matching of the two sensors in the frequency domain can be rather challenging. In addition, only planar coils can be realized in a standard CMOS process, which limits the field strengths that can be generated. Without the use of ferromagnetic material, current-to-magnetic field ratios are usually below 500 mT/A [27, 28]. Moreover, electromigration constraints mean that on-chip coils can only handle currents of a few mA, corresponding to magnetic fields of only a few mT [29]. For these reasons, closed-loop hybrid magnetic sensors are rarely integrated in CMOS.

#### **Open-Loop Hybrid Magnetic Sensors**

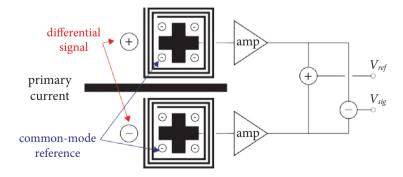

Hall sensors and pick-up coils can be combined in an open-loop manner such that the Hall sensors measure only the static magnetic field, while the pick-up coils are only used to capture the magnetic field transients. This concept has been demonstrated on PCB with discrete components, and is sometimes referred as the "HOKA" principle [30]. Recent researches extended this concept to combine pick-up coils and other kinds of magnetic sensors, such as AMR (anisotropic magnetoresistive) sensors [31], GMR (giant magnetoresistive) sensors [32] and TMR (tunnel magnetoresistive) sensors [33], which have better sensitivities compared to Hall sensors. To further improve system sensitivity, some work also incorporated ferromagnetic cores into the system, as shown in Figure 1.5. A Hall sensor is placed in the gap of a ferromagnetic core to measure low frequency field. And a pick-up coil, wrapped around the same ferromagnetic core, measures high frequency magnetic field, which is added to the output of the Hall sensor. This has achieved a superior bandwidth of DC - 30 MHz [34].

However promising, robust ways of combining the very different output signals of integrated Hall sensors and pick-up coils must be designed. By taking advantage of digital signal processing (DSP), the outputs of both sensors can be processed and combined in the digital domain. This

approach inevitably requires ADCs to convert the sensor outputs into digital words so that they can be read by a succeeding DSP. However, the differentiating characteristics of pick-up coils pose high requirements on the ADC bandwidth and SNR. Although state-of-the-art ADCs [35-37] are capable of meeting these requirements, they are mostly implemented in advanced technologies such as 40 nm CMOS. Moreover, they usually consume considerable amount power and operate with high speed clocks. These can result in undesired inductive interference between the coil and the ADC, leading to extra work in addition to the ADC design itself. Alternatively, the outputs of both sensors can be combined in the analog domain, which will greatly relax the ADC SNR requirement. An analog crossover network and readout topology in a CMOS process were, however, unknown before this research commenced. In addition, the sensitivity drift of Hall sensors over temperature needs to be minimized to match that of the pick-up coils.

Figure 1.5 Magnetic sensor system combining a Hall sensor and a coil [34].

#### 1.3 Dissertation Organization

The fundamentals of CMOS Hall sensors are first introduced in Chapter 2, including the working principle, fabrication process, and the spinning current technique. This is then followed by a comprehensive review of the prior art in the past decade. The readout techniques of pick-up coils are also reviewed in Chapter 2.

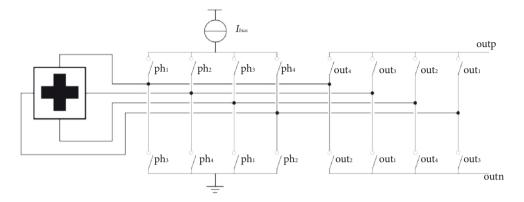

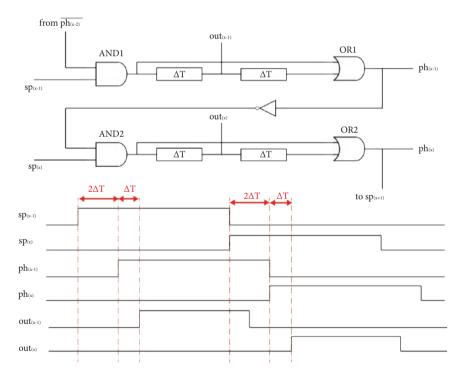

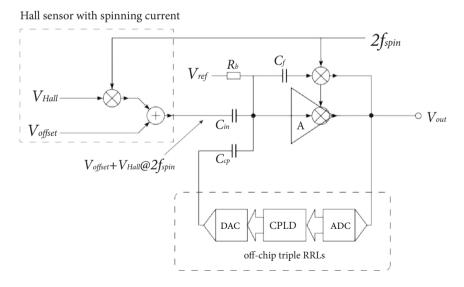

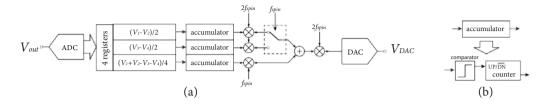

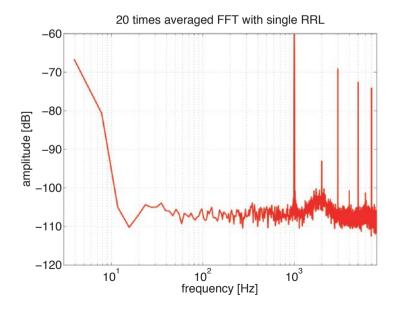

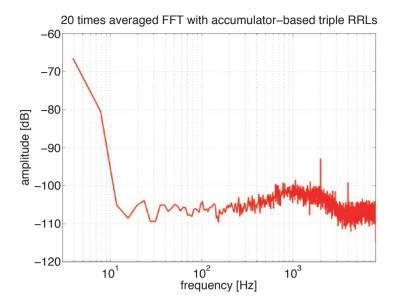

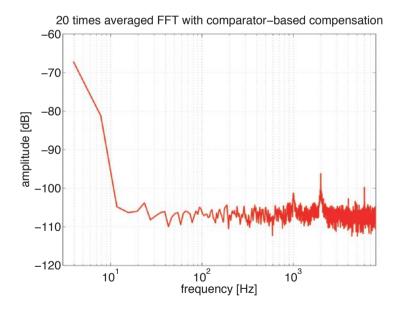

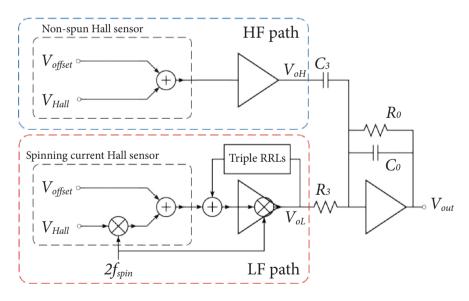

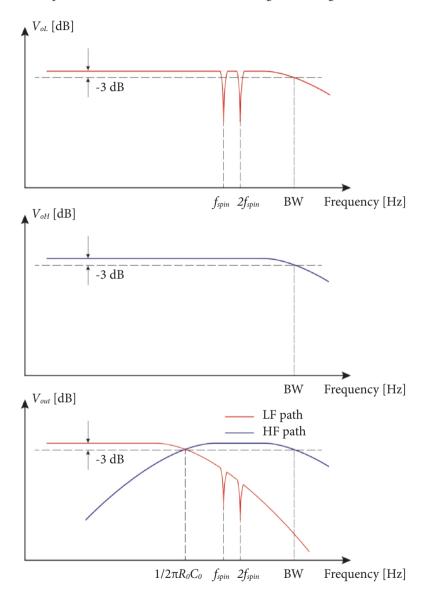

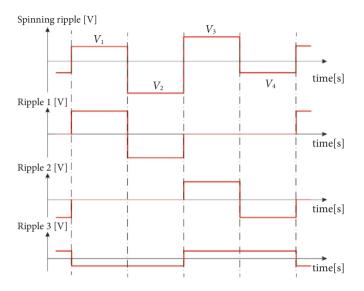

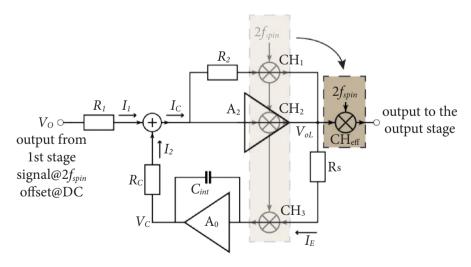

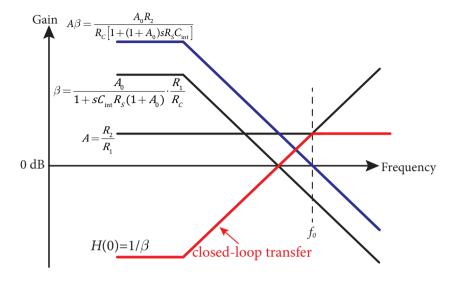

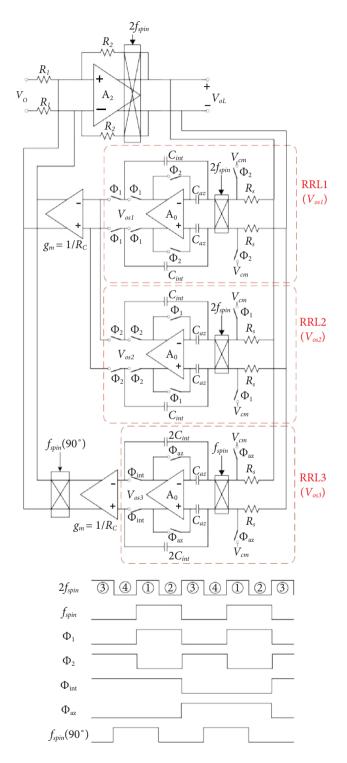

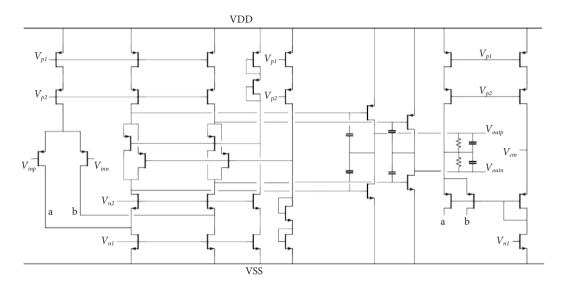

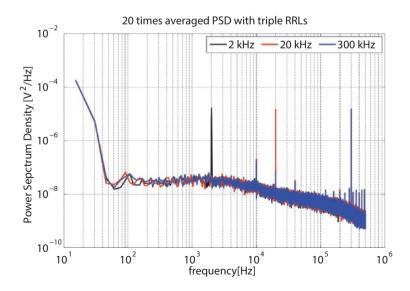

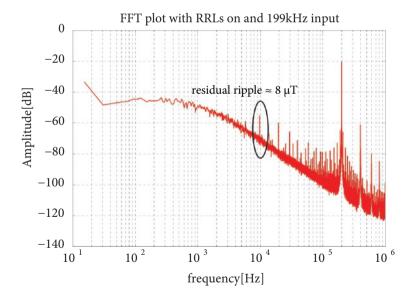

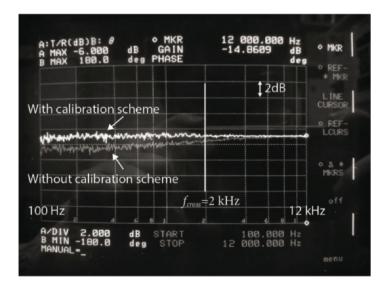

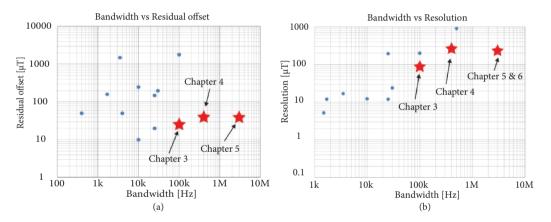

Chapter 3 presents a continuous-time ripple reduction technique for spinning current Hall sensors. It involves the use of three orthogonal ripple reduction loops (triple RRLs) to suppress spinning ripple, thus obviating the need for low-pass filters. Implemented with off-chip components, the triple RRL scheme successfully suppresses the output ripple of a test chip to its noise level, and extends the bandwidth to above 100 kHz, at the expense of two notches in the frequency response. The implementation details and measurement results are discussed in Chapter 3.

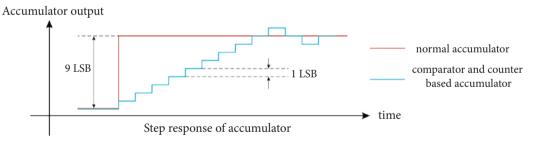

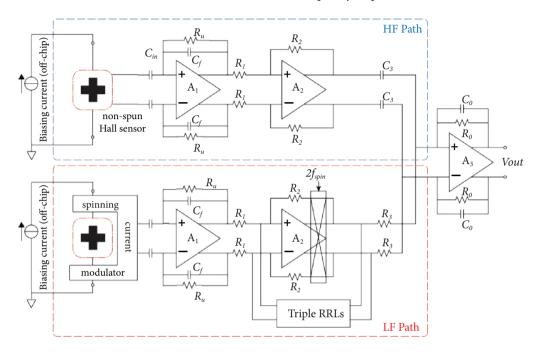

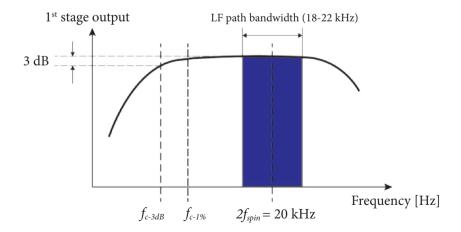

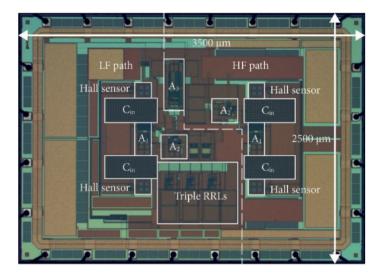

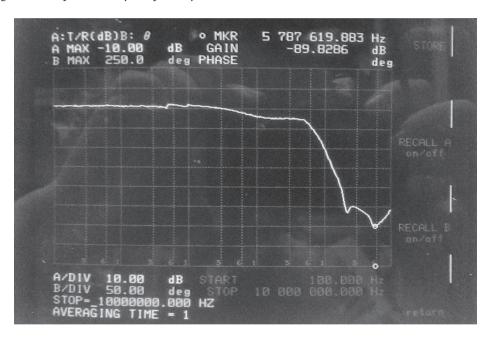

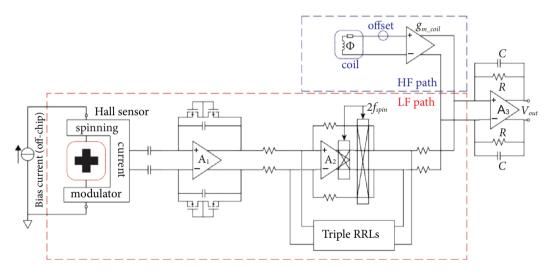

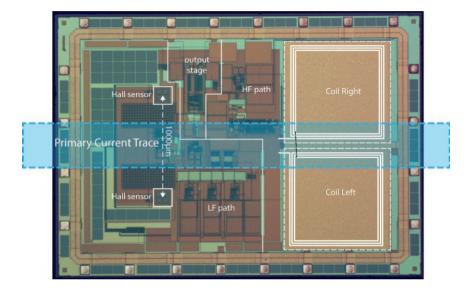

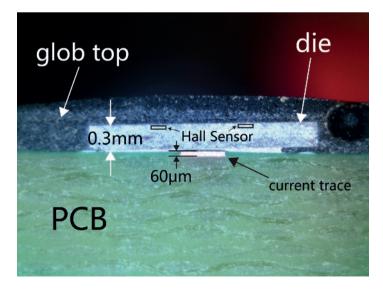

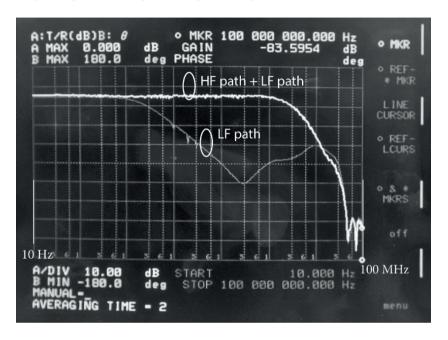

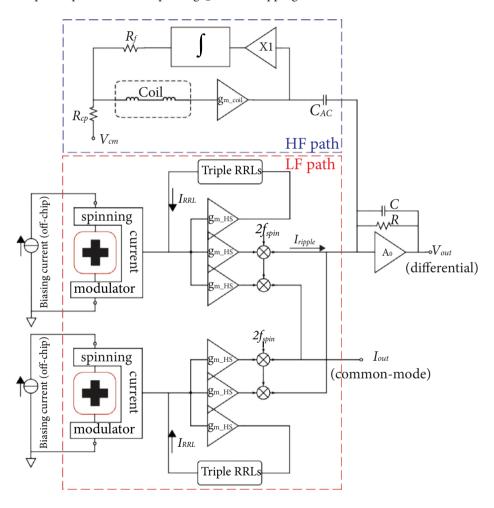

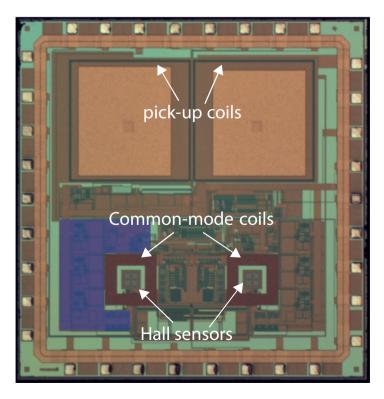

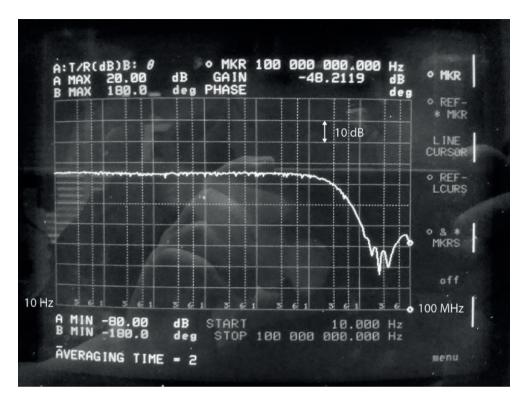

To eliminate frequency-response notches, a multi-path CMOS Hall sensor in a 0.18 µm CMOS process is introduced in Chapter 4. The test chip achieves a 400 kHz bandwidth and a 40 µT offset, which at the time of publication was the fastest CMOS magnetic sensor ever reported with less than 50 µT offset. In addition, the triple RRL scheme was also integrated on-chip.

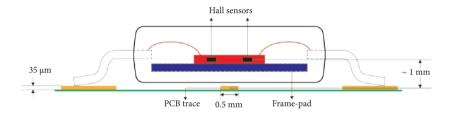

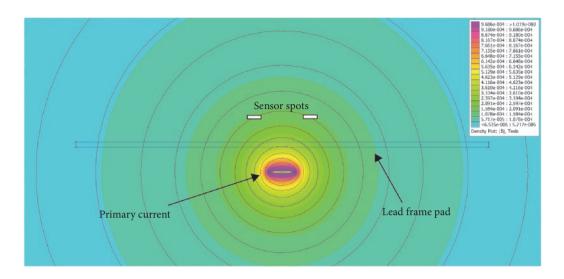

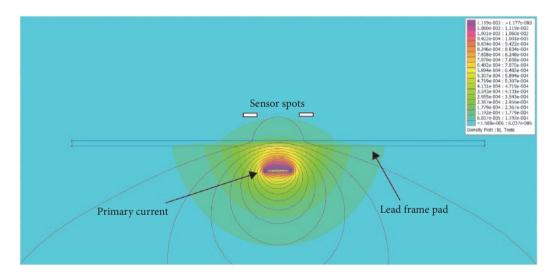

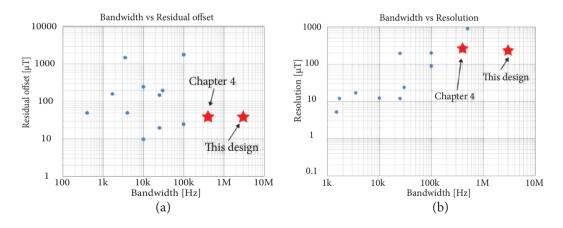

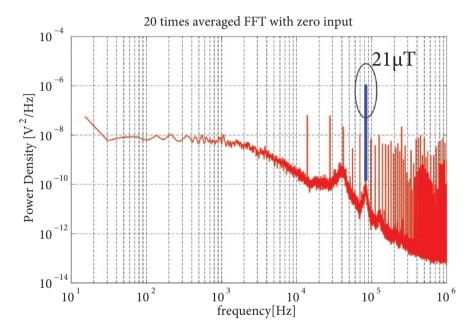

Chapter 5 investigates the possibility of combining Hall sensors and pick-up coils in a multi-path structure. After the discussion of the combination theory, a test chip fabricated in a 0.18 µm standard CMOS process is presented which achieves a 3 MHz bandwidth with an offset of 40 µT and a resolution of 210 µT. This was the fastest CMOS magnetic sensor ever reported by the time of publication [38].

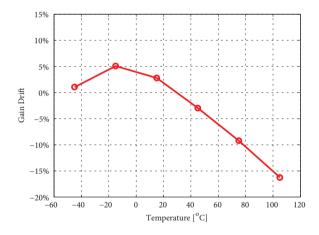

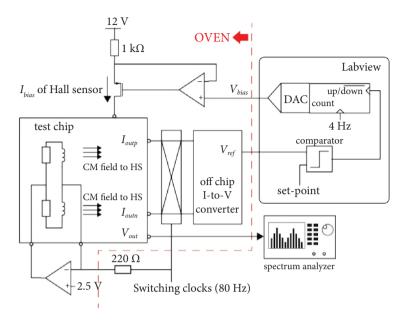

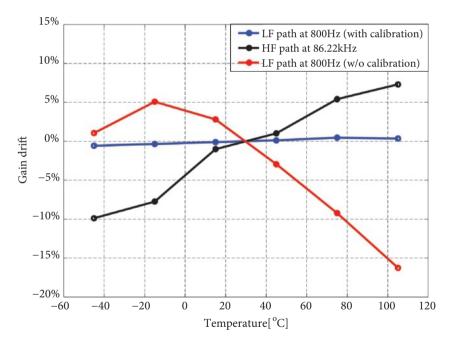

Chapter 6 addresses two unsolved issues from the previous chapters, namely: (1) that the sensitivity of Hall sensors changes over temperature, and is different from that of the pick-up coils, and (2) the complexity and area-inefficiency of triple RRL implementations. The first issue is solved by exploiting the common mode rejection of the differential sensing scheme in current measurements. By introducing a common mode reference field, the Hall sensitivity can be dynamically monitored and thus regulated. Measurement results on a test chip demonstrated that the Hall sensor's sensitivity drift was reduced from 22% to 1% in the temperature range of -45°C to 105°C, corresponding to a temperature coefficient of 76 ppm/°C. The second issue is addressed by revising the triple RRL algorithm such that the hardware required to implement one loop can be multiplexed between the three loops.

Chapter 7 concludes this dissertation and provides an outlook for future work.

### 1.4 Bibliography

- [1] T. A. Edison, "Electric-Lamp," United States Patent US223898A, 1880-01-27.

- [2] (6 April, 2018). Electricity Production, Sonsumption and Market Overview. Available: http://ec.europa.eu/eurostat/statisticsexplained/index.php/Electricity production, consumption and market overview#Furt her Eurostat information

- [3] S. H. Shalmany, D. Draxelmayr, and K. A. A. Makinwa, "A ±5 A Integrated Current-Sensing System with ±0.3% Gain Error and 16 µA Offset from -55 °C to +85 °C," IEEE Journal of Solid-State Circuits, vol. 51, no. 4, pp. 800-808, 2016.

- [4] Y. Ouyang, J. He, J. Hu, G. Zhao, Z. Wang, and S. X. Wang, "Contactless Current Sensors Based on Magnetic Tunnel Junction for Smart Grid Applications," IEEE Transactions on Magnetics, vol. 51, no. 11, pp. 1-4, 2015.

- [5] N. Flourentzou, V. G. Agelidis, and G. D. Demetriades, "VSC-Based HVDC Power Transmission Systems: An Overview," IEEE Transactions on Power Electronics, vol. 24, no. 3, pp. 592-602, 2009.

- [6] M. K. Alghamdi and A. A. Hamoui, "A Spurious-Free Switching Buck Converter Achieving Enhanced Light-Load Efficiency by Using a  $\Delta\Sigma$ -Modulator Controller with a Scalable Sampling Frequency," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 4, pp. 841-851, 2012.

- [7] K. Tomita, R. Shinoda, T. Kuroda, and H. Ishikuro, "1-W 3.3-16.3-V Boosting Wireless Power Transfer Circuits with Vector Summing Power Controller," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 11, pp. 2576-2585, 2012.

- [8] M. Motz, U. Ausserlechner, M. Bresch, U. Fakesch, B. Schaffer, C. Reidl, et al., "A Miniature Digital Current Sensor with Differential Hall Probes Using Enhanced Chopping Techniques and Mechanical Stress Compensation," in *Preceedings of IEEE* Sensors, pp. 1-4, 2012.

- [9] CQ-3300. Available: <a href="https://www.akm.com/akm/en/file/datasheet/CQ-3300.pdf">https://www.akm.com/akm/en/file/datasheet/CQ-3300.pdf</a>

- [10] R. S. Vanha, *Rotary Switch and Current Monitor by Hall-Based Microsystems*: Konstanz, Germany: Hartung-Gorre, 1999.

- [11] K. Skucha, P. Liu, M. Megens, J. Kim, and B. Boser, "A Compact Hall-Effect Sensor Array for the Detection and Imaging of Single Magnetic Beads in Biomedical Assays," in *Proceedings of TRANSDUCERS*, pp. 1833-1836, 2011.

- [12] Y.-J. Min and S.-W. Kim, "A CMOS TDC-Based Digital Magnetic Hall Sensor Using the Self Temperature Compensation," in *Proceedings of CICC*, pp. 329-332, 2008.

- [13] Y. Xu, H.-B. Pan, S.-Z. He, and L. Li, "Monolithic H-Bridge Brushless DC Vibration Motor Driver with a Highly Sensitive Hall Sensor in 0.18 μm Complementary Metal-Oxide Semiconductor Technology," *IET Circuits, Devices & Systems*, vol. 7, no. 4, pp. 204-210, 2013.

- [14] J. C. van der Meer, F. R. Riedijk, E. van Kampen, K. A. A. Makinwa, and J. H. Huijsing, "A Fully Integrated CMOS Hall Sensor with a 3.65 μT 3σ Offset for Compass Applications," in *ISSCC Digest of Technical Papers*, pp. 246-247, 2005.

- [15] M. Crescentini, M. Biondi, M. Bennati, P. Alberti, G. Luciani, C. Tamburini, *et al.*, "A 2 MS/s 10A Hall Current Sensor SoC with Digital Compressive Sensing Encoder in 0.16 μm BCD," in *Proceedings of ESSCIRC*, pp. 393-396, 2016.

- [16] C. Schott, R. Racz, A. Manco, and N. Simonne, "CMOS Single-Chip Electronic Compass with Microcontroller," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 12, pp. 2923-2933, 2007.

- [17] G. Boero, M. Demierre, P.-A. Besse, and R. Popovic, "Micro-Hall Devices: Performance, Technologies and Applications," *Sensors and Actuators A: Physical*, vol. 106, no. 1, pp. 314-320, 2003.

- [18] P. Munter, "A Low-Offset Spinning-Current Hall Plate," Sensors and Actuators A: Physical, vol. 22, no. 1, pp. 743-746, 1989.

- F. Qinwen, J. H. Huijsing, and K. A. A. Makinwa, "A capacitively-coupled chopper [19] operational amplifier with 3uV Offset and outside-the-rail capability," in Preceedings of ESSCIRC, pp. 73-76, 2012.

- [20] Q. Fan, J. H. Huijsing, and K. A. A. Makinwa, "A 21 nV/ VHz Chopper-Stabilized Multi-Path Current-Feedback Instrumentation Amplifier With 2 µV Offset," IEEE Journal of Solid-State Circuits, vol. 47, no. 2, pp. 464-475, 2012.

- [21] Si850x/1x. Silicon Labs [Online]. Available: http://www.silabs.com/products/power/currentsensors/Pages/Si850x1x.aspx

- [22] G. Grandi and M. Landini, "Magnetic-Field Transducer Based on Closed-Loop Operation of Magnetic Sensors," IEEE Transactions on Industrial Electronics, vol. 53, no. 3, pp. 880-885, 2006.

- [23] A. D. Saha and V. John, "Power Consumption Reduction in High Current Closed Loop Hall Effect Current Sensors Using Class D Amplifier," in 2016 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), pp. 1-6, 2016.

- C. Petridis, P. D. Dimitropoulos, and E. Hristoforou, "New Magnetic Field Sensor Based [24] on Combined Flux-Gate/Hall-Effect Arrangement," IEEE Sensors Journal, vol. 9, no. 2, pp. 128-134, 2009.

- [25] M. J. Garcia and A. Turo, "Improved Zero-Flux Type Large Bandwidth Current Sensor," in Instrumentation and Measurement Technology Conference, pp. 1475-1478, 1996.

- [26] S. Ziegler, R. C. Woodward, H. H. C. Iu, and L. J. Borle, "Current Sensing Techniques: A Review," IEEE Sensors Journal, vol. 9, no. 4, pp. 354-376, 2009.

- [27] J. Trontelj, "Optimization of Integrated Magnetic Sensor by Mixed Signal Processing," in Proceedings of the 16th IEEE Instrumentation and Measurement Technology Conference pp. 299-302 vol.1, 1999.

- M. Demierre, "Improvements of CMOS Hall Microsystems and Application for Absolute [28] Angular Prosition Measurements," Lausanne, Switzerland: Swiss Federal Institute of Technology Lausanne (EPFL), 2003.

- [29] M. Pastre, M. Kayal, and H. Blanchard, "A Hall Sensor Analog Front End for Current Measurement with Continuous Gain Calibration," IEEE Sensors Journal, vol. 7, no. 5, pp. 860-867, 2007.

- [30] N. Karrer, P. Hofer-Noser, and D. Henrard, "HOKA: A New Isolated Current Measuring Principle and its Features," in 1999 IEEE Industry Applications Conference, pp. 2121-2128, 1999.

- [31] S. J. Nibir, M. Biglarbegian, and B. Parkhideh, "Performance Study of Magnetic Field Concentration Techniques on Magnetoresistor/Rogowski Contactless Current Sensor," in *IEEE Sensors*, pp. 1-3, 2016.

- [32] B. Hudoffsky and J. Roth-Stielow, "New Evaluation of Low Frequency Capture for a Wide Bandwidth Clamping Current Probe for ±800 A Using GMR Sensors," in *Proceedings of the European Conference on Power Electronics and Applications*, pp. 1-7, 2011.

- [33] N. Tröster, J. Wölfle, J. Ruthardt, and J. Roth-Stielow, "High Bandwidth Current Sensor with A Low Insertion Inductance Based on The HOKA Principle," in *European Conference on Power Electronics and Applications*, pp. 1-9, 2017.

- [34] L. Dalessandro, N. Karrer, and J. W. Kolar, "High-Performance Planar Isolated Current Sensor for Power Electronics Applications," *IEEE Transactions on Power Electronics*, vol. 22, no. 5, pp. 1682-1692, 2007.

- [35] H. Xu, Y. Cai, L. Du, Y. Zhou, B. Xu, D. Gong, *et al.*, "A 78.5dB-SNDR Radiation- and Metastability-Tolerant Two-Step Split SAR ADC Operating up to 75MS/s with 24.9mW Power Consumption in 65nm CMOS," in *ISSCC Digest of Technical Papers*, pp. 476-477, 2017.

- [36] T. He, M. Ashburn, S. Ho, Y. Zhang, and G. Temes, "A 50MHZ-BW Continuous-Time  $\Delta\Sigma$  ADC with Dynamic Error Correction Achieving 79.8dB SNDR and 95.2dB SFDR," in *ISSCC Digest of Technical Papers*, pp. 230-232, 2018.

- [37] B. Murmann. (12 May, 2018). ADC Performance Survey 1997-2017 (ISSCC & VLSI Symposium). Available: https://web.stanford.edu/~murmann/adcsurvey.html

- [38] J. Jiang and K. Makinwa, "A Hybrid Multipath CMOS Magnetic Sensor with 210μTrms Resolution and 3MHz Bandwidth for Contactless Current Sensing," in *ISSCC Digest of Technical Papers*, pp. 204-205, 2016.

## Magnetic Sensors in CMOS Technologies

2

#### 2.1 Introduction

agnetic sensors are essential parts of current sensing systems that must achieve high galvanic isolation. During the past decades, many efforts have been made to improve their performance. This has led to significant improvements in the performance of CMOS Hall sensors, and pick-up coils.

This chapter reviews the most recent developments in CMOS magnetic sensors, providing the background for later chapters. It is organized as follows. Section 2.2 reviews the basic working principle of Hall sensors, and introduces some readout techniques to improve their performance. The working principle and readout techniques of pick-up coils are then reviewed in Section 2.3, and Section 2.4 concludes this chapter.

#### 2.2 Hall Effect Sensors

The Hall Effect was first discovered by Edwin Hall in 1879 [1]. This section will provide a brief discussion of the Hall Effect for the purposes of circuit design. A more detailed analysis can be found in [2].

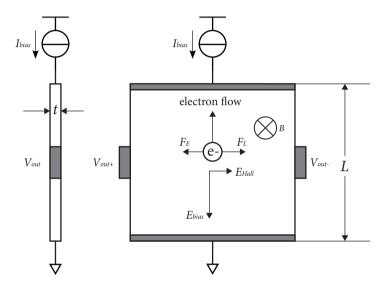

In the presence of a out-of-plane magnetic field *B*, as shown in Figure 2.1, an in-plane charge flow (electrons in this case) is subjected to a certain Lorentz Force in the transverse direction of the charge flow, which is given by:

$$F_{L} = q \cdot v \cdot B \tag{2.1}$$

where q is the unit charge, v is the charge flow velocity, and B is the vertical magnetic field strength. As a result of the Lorentz Force, the charge flow will bend, and thus more electrons will accumulate on one side of the material, i.e. the electrode  $V_{out}$ . To maintain charge neutrality, positive charges will accumulate on the opposite electrode  $V_{out}$ . Therefore, an electric field is generated within the sample in the transverse direction of the charge follow, which poses an electric force  $F_E$  on the charge flow to counterbalance the Lorentz Force. An equilibrium state is

established in the order of  $10^{-14}$  s [3], when the Lorentz Force  $F_L$  is fully compensated by the electric force  $F_E$ . Therefore, a steady voltage difference can be read out at the transverse electrodes, which is given by:

$$V_{Hall} = G \cdot S_{HS} \cdot I_{hias} \cdot B \tag{2.2}$$

where  $S_{HS}$  represents the absolute sensitivity of the Hall Effect in a plate with an infinite length L. G is a geometry factor which depends on the shape and size of the Hall sensor [4]. The Hall sensitivity is sometimes expressed as  $S_{HS} \cdot I_{bias}$ , which is better suited for a magnetic sensor system.

Figure 2.1 Hall Effect.

The absolute Hall sensitivity  $S_{HS}$  can be expressed as:

$$S_{HS} = \frac{R_H}{t} \tag{2.3}$$

where  $R_H$  is the Hall constant of the material, and t is the thickness of the plate. Instead of being a real constant,  $R_H$  is a process-dependent parameter, which can be expressed as:

$$R_{H} = \frac{r(n\mu_{n}^{2} - p\mu_{p}^{2})}{q(n\mu_{n} - p\mu_{p})^{2}}$$

(2.4)

in which n, p,  $\mu_n$  and  $\mu_p$  represent the electron concentration, the hole concentration, the electron mobility, and the hole mobility in the Hall plate, respectively. q is the unit charge, and r is the scattering factor for a given material type. The scattering factor r is related to the relaxation time

constant  $\tau$ , after which all kinetic energy of the charge carriers is consumed by collisions [2]. It is usually between 1.18 (acoustic phonons) and 1.93 (ionized impurities) for modern CMOS processes [2]. For a single-type doped silicon, e.g. n-doped, Equation (2.4) can be simplified as:

$$R_{H} = \frac{r}{qn} \tag{2.5}$$

Therefore, Equation (2.2) can be re-written as:

$$V_{Hall} = G \cdot \frac{r}{qnt} \cdot I_{bias} \cdot B \tag{2.6}$$

Although Equation (2.6) is commonly used to express the Hall voltage, it provides information about physical design parameters rather than circuit design parameters. In a given process, Equation (2.5) can be re-written in terms of resistivity  $\rho$  as:

$$R_{H} = \frac{r}{qn} = r \cdot \mu_{n} \cdot \rho \tag{2.7}$$

By substituting Equation (2.7) in Equation (2.6), the Hall voltage can also be expressed as:

$$V_{Hall} = G \cdot \frac{\rho \cdot \mu_n}{t} \cdot r \cdot I_{bias} \cdot B = G \cdot r \cdot \mu_n \cdot R_S \cdot I_{bias} \cdot B$$

(2.8)

where R<sub>S</sub> is the sheet resistance of the plate material. In CMOS processes, the mobility of electrons is about 2.5x greater than that of holes. Therefore, CMOS Hall sensors are commonly built with n-well plates instead of p-well plates [2]. In addition to the choice of materials, Equation (2.8) also indicates a limiting factor in system design, namely that the term  $R_S \cdot I_{bias}$  is directly related to the power supply rail. This also explains why for a given power supply, the maximum achievable magnetic sensitivity in V/T cannot be significantly improved by using a thinner plate, despite the absolute Hall sensitivity in V/A·T being inversely proportional to the thickness of the plate. However, in order to optimize their offset [5], CMOS Hall sensors are rarely biased at maximum current/voltage. This will be explained later in Section 2.2.2.

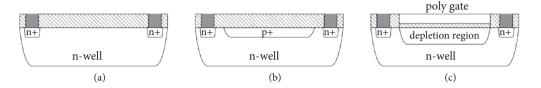

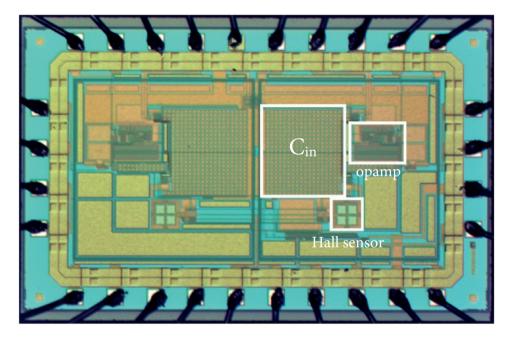

Despite the fixed junction depth and doping concentration of the plate in a CMOS process, the Hall sensitivity in V/A·T can still be slightly adjusted and improved by changing the effective thickness of the sensor plate. Figure 2.2 (a) shows the cross-section of a typical Hall sensor built with an n-well plate. A p+ pinch layer, as shown in Figure 2.2 (b), can be created inside the n-well plate to reduce the thickness of the active region, therefore improving the Hall sensitivity. Alternatively, this can be achieved by constructing the Hall sensor in a MOS capacitor structure, as shown in Figure 2.2 (c), where the gate voltage is used to create a depletion region to reduce the thickness of the n-well. Apart from the slightly increased sensitivity, the sensor's flicker noise will also be reduced since the structures in Figure 2.2 (b) and (c) effectively isolate the sensor from the crystal defects present at the  $Si/SiO_2$  interface [6].

Figure 2.2 Cross-sections of (a) a Hall sensor built with n-well, (b) a Hall sensor built with a pinched n-well by a p+ layer, and (c) a Hall sensor built with the MOS cap structure.

The Hall Effect is considered to be a highly linear effect. However in CMOS technologies, this only holds up to a field strength of about 1 T. In [7], the linearity of an n-type silicon Hall sensor is measured, as shown in Figure 2.3. For most applications, the magnetic field strength of interest is limited to  $10^{-2}$  T, for which the non-linearity of the Hall sensors is quite negligible compared to that of the readout circuits.

Figure 2.3 Experimental result [7] of the non-linearity (NL) of an n-type silicon Hall sensor versus squared magnetic field strength (B2).

#### 2.2.1 Offsets in Hall Sensors and the Spinning Current Technique

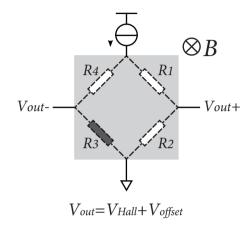

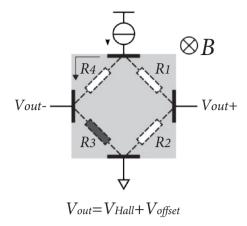

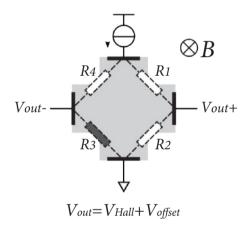

Being four-terminal devices, Hall sensors can be modeled as a Wheatstone bridge, as shown in Figure 2.4. Due to the arm resistance mismatch, an offset  $V_{offset}$  appears at the outputs together with the magnetic signal  $V_{Hall}$ . This offset is usually in the order of a few milli-Volts, which is too large for precision applications. For instance, a Hall sensor with a nominal source resistance of

1 k $\Omega$  could have a mismatch of 1% in one of the arm resistances, e.g.  $R_3 = 1.01$  k $\Omega$ . When biased with a current of 1 mA, an offset of 2.5 mV would appear at the outputs. Assuming a sensitivity of 100 V/A·T, this is then equivalent to an offset of 25 mT, which is orders of magnitudes larger than the signal of interest. Offset is mainly caused by three factors: lithographic inaccuracy; crosssensitivities of resistance to temperature, stress, etc.; and process spread.

Figure 2.4 Hall sensors modeled as a Wheatstone bridge.

#### Lithographic Inaccuracy

For a given process, lithographic inaccuracy represents a fundamental limit which itself cannot be improved without moving to a more advanced process node. However, the influence of lithographic accuracy can be minimized by proper sensor design. For instance, instead of using the point contacts shown in Figure 2.4, the wider contacts shown in Figure 2.5 can be used, such that lithography errors become less significant. However, wider contacts form a parasitic conducting path between the biasing and measurement electrodes, and therefore reduce the effective biasing current and hence the sensitivity. This is often referred to as the short-circuit effect, which leads to a slightly reduced Hall sensitivity. The short-circuit effect can then be alleviated by making the sensor larger.

Alternately, the sensor can be designed in a different shape, for instance, in the Greek cross shape shown in Figure 2.6. Thanks to the presence of resistive arms, the voltage gradients around the contacts in Greek-cross-shaped sensors are much lower than that in square-shaped sensors [4]. This makes Greek-cross-shaped Hall sensors less sensitive to lithographic inaccuracies, and therefore can achieve better offset without using large sensors. However, the source resistance of the cross-shaped Hall sensors is inevitably higher. Therefore the maximum biasing current, and hence the highest achievable sensitivity, is then reduced for a given power supply rail. Nevertheless, for various reasons, the biasing voltage of CMOS Hall sensors are usually lower than the power supply, and therefore Greek cross-shaped Hall sensors are often used to minimize offset errors due to lithographic inaccuracies.

Figure 2.5 Hall sensor with wide contacts to minimize lithography errors.

Figure 2.6 Greek cross-shaped Hall sensor with wide contacts.

#### **Cross-Sensitivity**

In contrast to lithography-related errors, cross-sensitivity related errors cannot be alleviated by using larger devices. As a matter of fact, smaller devices are usually preferred to minimize the cross-sensitivities of temperature and stress. For instance, with a temperature gradient across the Hall sensor, the temperature difference seen by the diagonal arm resistors in smaller devices will be lower than that of the large devices. In addition to static offset issues, the cross-sensitivity of temperature and stress usually introduces dynamic offset changes, which is a more critical issue in sensor systems. Such errors cannot be effectively removed by simply reducing the sensor dimensions.

In [8], a Hall sensor structure consisting of two orthogonally connected Hall plates, as shown in Figure 2.7, can be used to cancel the 1<sup>st</sup> order cross-sensitivities. For instance, due to the cross-

sensitivity to temperature and stress, the arm resistance  $R_3$  changes from its original value. However, as the biasing and readout electrodes of the two plates are rotated by 90°, the ratio between the two parallel arm resistances  $(R_3||R_4 \text{ and } R_3||R_2)$  remains relatively constant, thus minimizing the offset change due to external stress [9].

Figure 2.7 Two orthogonally connected Hall plates to stabilize offset change due to cross-sensitivities of temperature and stress (replotted from [8]).

#### **Process Spread**

Process spread is usually the dominant source of error in small-sized Hall sensors. The matching properties of a normal resistor can be expressed as:

$$\frac{\sigma_{\Delta R}}{R_0} = \frac{A_R}{\sqrt{area}} \tag{2.9}$$

in which  $R_0$  is the nominal resistance of the resistor,  $\sigma_{\Delta R}$  is the relative matching of the designated resistor, and  $A_R$  is a process parameter expressed in units of [%·µm]. Even though Equation (2.9) clearly suggests that a large device can potentially reduce the mismatch and thus offset, this improvement is rather limited. For instance, to reduce the offset by 10 times, under the assumption that the offset is linearly related to the relative mismatch, a Hall sensor with 100 times larger area is required.

The sensor structure proposed in Figure 2.7 can also help to reduce the process-spread related offset without using large-size devices. However, the offset reduction factor is limited to about 10 times [8], which means that the resulting offset of a few milli-Tesla is still considerably larger than the signal of interest.

#### **Spinning Current Technique**

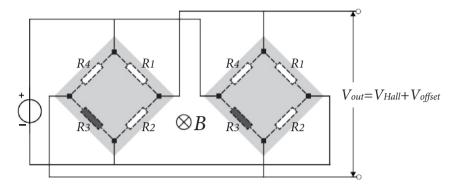

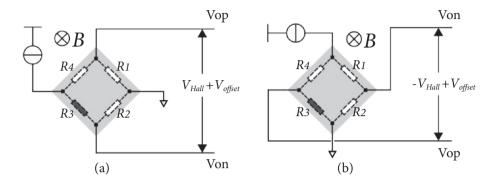

To suppress Hall sensor offset efficiently, a dynamic offset cancellation technique, known as the spinning current technique, was introduced in 1989 [10]. This technique exploits the reciprocity of symmetrical Hall plates. By swapping the functions of Hall sensor readout and bias electrodes and thus changing the direction of the bias current through the sensor, the relative polarities of the sensor offset and  $V_{Hall}$  can be periodically swapped. Figure 2.8 depicts the operation of a two-phase spinning current Hall sensor [11]. With both the biasing electrodes and readout electrodes rotated by 90°, the polarity of the offset is flipped, while that of  $V_{Hall}$  is not.  $V_{Hall}$  can be then extracted by averaging the outputs of the two spinning phases.

Figure 2.8 Operation of a two-phase spinning current Hall sensor (replotted from [11]).

Figure 2.9 Circuit model of a two-phase spinning current Hall sensor with analog front-end.

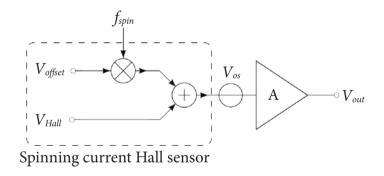

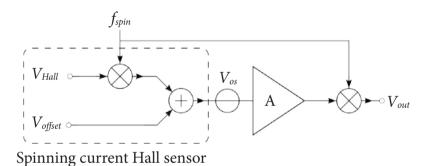

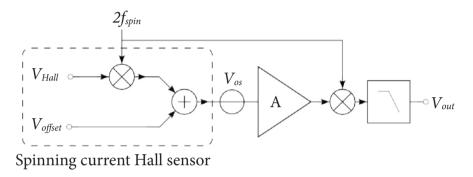

Periodically switching between two different spinning phases will effectively modulate the offset to the switching frequency, namely the spinning frequency  $f_{spin}$ . Therefore the operation of a two-phase spinning current Hall sensor can be modeled as shown in Figure 2.9. A typical Hall sensor will only produce a  $\mu$ V-level  $V_{Hall}$ , which therefore requires amplification. However, a typical amplifier A will introduce an extra offset  $V_{os}$  which is usually in the order of a few milli-Volts. This is typically reduced by trimming or the use of circuit techniques such as chopping or auto-zeroing [12].

Alternately, the spinning current technique can be re-arranged so that the magnetic signal  $V_{Hall}$  rather than the offset  $V_{offset}$ , is modulated to  $f_{spin}$  [11], as shown in Figure 2.10.  $V_{Hall}$  can then be reconstructed with a demodulator succeeding the amplifier (Figure 2.11), which also modulates

both  $V_{offset}$  and  $V_{os}$  to the spinning frequency. Although the modified spinning topology greatly relaxes the offset requirement of the amplifier, it does require an amplifier with a sufficiently high bandwidth such that the up-modulated  $V_{Hall}$  is not suppressed.

Figure 2.10 Operation of an alternative two-phase spinning current Hall sensor.

Figure 2.11 Circuit model of a two-phase spinning current Hall sensor with analog front-end.

Figure 2.12 Implementation example of a two-phase spinning current sensor (replotted from [11]).

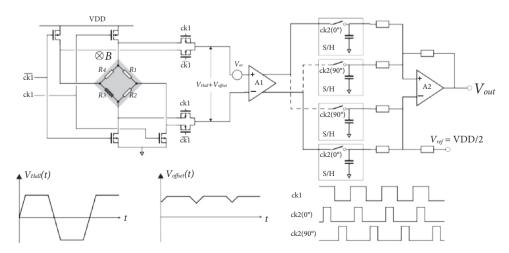

Figure 2.12 shows one of the first on-chip implementations of a two-phase spinning current Hall sensor in a 2  $\mu$ m BiCMOS process [11]. The spinning current technique is implemented with PMOS and NMOS switches. After the amplification by A1, the Hall sensor outputs are sampled by four sample and hold (S/H) blocks, and then subtracted from each other to retrieve  $V_{Hall}$ . This implementation reports a residual offset of 0.5 mT, which is still quite large for precision applications like current sensing. This is limited by several design choices, i.e. the choice of biasing and readout, the number of spinning phases, and the biasing strength. These limiting factors will be discussed in the next section.

## 2.2.2 Constraints and Improvements in the Spinning Current Technique

With a properly designed analog front-end (AFE), a spinning-current Hall sensor can achieve an offset of less than 50  $\mu$ T [13, 14]. This section provides a detailed analysis on the choice of biasing and readout, the number of spinning phases, and the biasing strength of spinning Hall sensors, and their influence on residual offsets.

#### **Biasing and Readout**

Both voltage and current sources can be used to bias a Hall sensor. It does not make a fundamental difference in a static non-spun Hall sensor, as the voltages and current can be mutually translated via the source resistance of the Hall sensor. Similarly, non-spun Hall sensors can be read out in voltage or current mode, which is independent of the biasing choice.

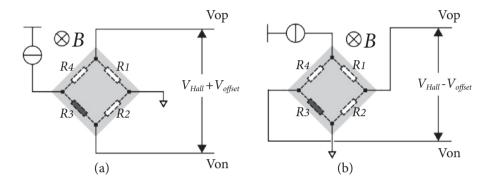

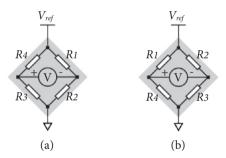

Figure 2.13 Voltage biased spinning current Hall sensor with voltage outputs: (a) the 1st phase and (b) the 2nd phase.

However, these statements about the biasing and readout of non-spun Hall sensors does not apply to spinning Hall sensors. Figure 2.13 shows an arbitrary Hall sensor for analysis; the Hall sensor is voltage-biased and read out by a voltage meter. The output offsets can then be expressed in terms of the biasing voltage  $V_{ref}$  and all the arm resistances  $R_1 - R_4$ :

$$V_{offset1} = V_{ref} \frac{R_1 R_3 - R_2 R_4}{(R_3 + R_4)(R_1 + R_2)}$$

(2.10)

$$V_{offset2} = V_{ref} \frac{R_2 R_4 - R_1 R_3}{(R_1 + R_4)(R_2 + R_3)}$$

(2.11)

Equations (2.10) and (2.11) suggest that offsets  $V_{offset1}$  and  $V_{offset2}$  do not cancel each other out unless  $(R_1+R_4)(R_2+R_3)$  and  $(R_1+R_2)(R_3+R_4)$  are equal. The two denominators are indeed equal in the case that only one arm resistance, e.g.  $R_3$ , differs from the other three. Therefore the voltagebiasing and voltage-readout setup works with the simplified analysis shown in Figure 2.12. However, in reality, mismatches exist among all the arm resistances, which inevitably introduces a residual offset error.

Figure 2.14 Voltage biased spinning current Hall sensor with current outputs: (a) the 1st phase, and (b) the 2nd phase.

On the other hand, if the voltage-biased Hall sensors are read out by a current meter (Figure 2.14), then the offset current in the different spinning phases can be written as:

$$I_{offset1} = V_{ref} \frac{(R_1 R_3 - R_2 R_4)(R_1 + R_2 + R_3 + R_4)}{(R_3 + R_4)(R_1 + R_2)(R_1 + R_4)(R_2 + R_3)}$$

(2.12)

$$I_{offset2} = V_{ref} \frac{(R_2 R_4 - R_1 R_3)(R_1 + R_2 + R_3 + R_4)}{(R_1 + R_4)(R_2 + R_3)(R_1 + R_2)(R_3 + R_4)}$$

(2.13)

Equations (2.12) and (2.13) suggest that the offsets in current readout mode are completely cancelled out, and so current readout should be used in voltage-biased spinning Hall sensors to achieve minimum offset.

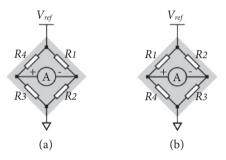

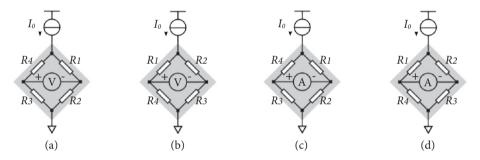

Alternately, Hall sensors can be biased with current sources, and read out in either the voltage or current mode (Figure 2.15). Equations (2.14 - 2.17) express the current offsets and the voltage offsets in their corresponding readout modes.

$$V_{offset1} = I_0 \frac{R_1 R_3 - R_2 R_4}{R_1 + R_2 + R_3 + R_4}$$

(2.14)

$$V_{offset2} = I_0 \frac{R_2 R_4 - R_1 R_3}{R_1 + R_2 + R_3 + R_4}$$

(2.15)

$$I_{offset1} = I_0 \frac{R_1 R_3 - R_2 R_4}{(R_1 + R_4)(R_2 + R_3)}$$

(2.16)

$$I_{offset2} = I_0 \frac{R_2 R_4 - R_1 R_3}{(R_3 + R_4)(R_1 + R_2)}$$

(2.17)

Like voltage-biased, voltage-readout spinning Hall sensors, the offset of current-biased, current-readout spinning Hall sensors will not be fully cancelled due to arm resistance mismatches. In conclusion, to optimize their offsets, spinning Hall sensors should either employ voltage biasing and current readout, or current biasing and voltage readout.

Figure 2.15 Current biased spinning current Hall sensor: (a) the 1<sup>st</sup> phase and (b) the 2<sup>nd</sup> phase offset in the voltage readout mode; (c) the 1<sup>st</sup> phase and (d) the 2<sup>nd</sup> phase offset in the current readout mode.

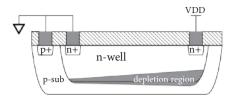

#### Biasing Strength: Sensitivity vs. Offset

To maximize their output signal-to-noise ratio (SNR), CMOS Hall sensors are preferably biased at high current/voltage levels, i.e. close to the power supply rail as in [11]. To a first approximation, this does not change the magnetic referred offset of a spinning Hall sensor since both offsets and sensitivities are linearly proportional to the biasing current/voltage. However, this statement regarding biasing strength overlooks the fact that n-well resistors exhibit a certain voltage coefficient due to the presence of a depletion region between the n-well and the p-substrate, as shown in Figure 2.16. An increase in the biasing strength will increase the reverse biasing of the p-n junction, and therefore increase the resistance of the n-well. This is usually referred to as the JFET effect or the back-biasing effect.

Figure 2.16 JFET effect due to the depletion region between the n-well and the p-substrate.

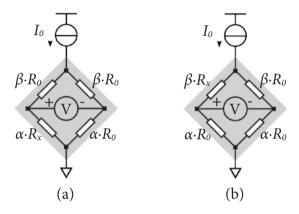

The JFET effect significantly limits the effectiveness of the spinning current technique, as the arm resistances will now be dependent on their position relative to the biasing electrode. This can be better understood by analyzing an example of a two-phase spinning current Hall sensor, as shown in Figure 2.17.

Figure 2.17 Arm resistance change due to different biasing conditions; (a) the 1st spinning phase and (b) the 2nd spinning phase.

Due to the JFET effect, each arm resistor experiences an amplification factor of  $\alpha$  or  $\beta$  ( $\beta > \alpha > 1$ ) depending on the biasing position. To simplify the analysis, we assume that only one resistor has a larger resistance of  $R_x$  compared to the others. In the 1<sup>st</sup> spinning phase, as shown in Figure 2.17 (a),  $R_x$  is only amplified by  $\alpha$  ( $< \beta$ ). Therefore the resistance mismatch between  $R_x$  (lower left) and  $R_0$  (top left) is alleviated. However, in the 2<sup>nd</sup> phase,  $R_x$  is amplified by  $\beta$  (> $\alpha$ ), which agitates the resistance mismatch between  $R_x$  and  $R_0$ . As a result, the offsets in these two phases  $V_{offset1}$  and  $V_{offset2}$  cannot fully compensate each other, but lead to a residual offset error. The offsets in the two spinning phases can be expressed by using Equations (2.14) and (2.15):

$$V_{offset1} = I_0 \frac{\beta R_0 \cdot \alpha R_x - \beta R_0 \cdot \alpha R_0}{2(\alpha + \beta) R_0 + \alpha (R_x - R_0)}$$

(2.18)

$$V_{offset2} = I_0 \frac{\beta R_0 \cdot \alpha R_0 - \beta R_x \cdot \alpha R_0}{2(\alpha + \beta) R_0 + \beta (R_x - R_0)}$$

(2.19)

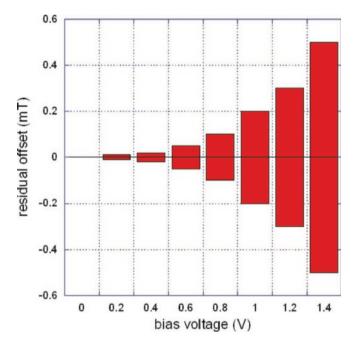

The exact influence of the JFET effect can then be identified in the denominators of Equations (2.18) and (2.19), showing that the resistance mismatch ( $R_x - R_0$ ) has different coefficients in different spinning phases. Moreover, since the amplification factor is bias-dependent, the residual offset of a spinning Hall sensor will be dependent on the biasing strength. This effect has been explicitly studied [5], and is shown in Figure 2.18. In modern CMOS processes, the optimum biasing points of Hall sensors highly depend on the target application, as well as on the process parameters, device dimensions, and sensor structures.

Figure 2.18 Relation between the biasing voltage and residual offset of a traditional spinning Hall sensor (reprinted from [5]).

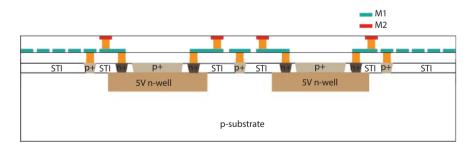

#### Multi-Phase Spinning Current Hall Sensors

The readout and biasing topologies discussed in the previous sections are based on the assumption that the arm resistances remain constant over the spinning phases. However, due to the JFET effect, two-phase spinning is rather ineffective as the original resistance mismatches change in the different spinning phases. In addition, this effect is exacerbated by the fact that silicon has a tri-directional lattice structure, so that n-well resistors exhibit anisotropic behavior [15], i.e. that their intrinsic resistances change as a function of the biasing direction. These effects lead to incomplete compensation of Hall sensor offsets, which are considered to be the major error sources in two-phase spinning Hall sensors [16, 17].

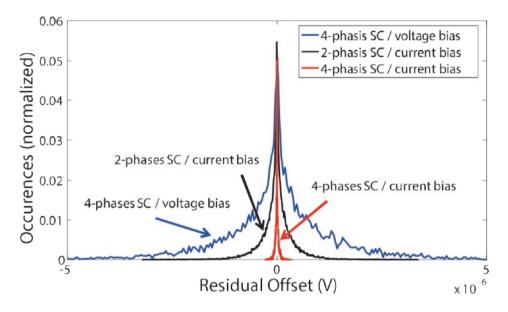

The residual offset due to the anisotropic resistances and the JFET effect can be alleviated by using a four-phase spinning technique to exploit all four possible operations of a four-contact

Hall sensor. The improvement achieved by using a four-phase spinning Hall sensor has been specifically studied in [13], and the results are shown in Figure 2.19. Mathematical analysis suggests that the offset of a 4-phase spinning current Hall sensor can be as low as 10 µT [13], which is 10 times smaller than that of a 2-phase spinning current Hall sensor.

Figure 2.19 Residual offsets of a two-phase spinning Hall sensor and a four-phase spinning Hall sensor (reprinted from [13]).

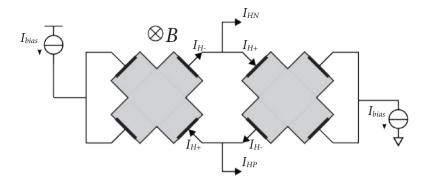

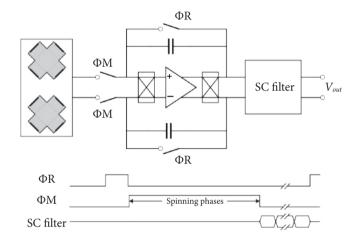

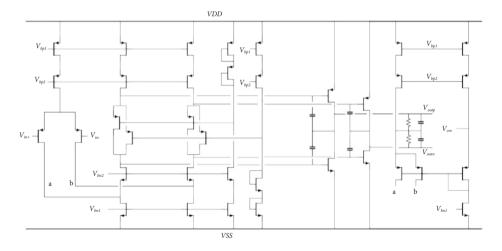

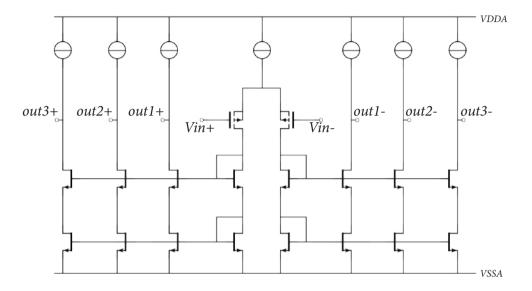

Nevertheless, in [18] an offset of 50 μT has been achieved by configuring two four-contact Hall plates in current-mode, as shown in Figure 2.20. The presence of a vertical magnetic field forces the current flow to be unevenly split between the two Hall plates, which results in an improved sensitivity. In addition, the use of two sensors helps to reduce intrinsic offset and thus alleviate the JFET effect. Therefore, the sensor could achieve a low offset (50 µT) with only two spinning phases and a proper analog front-end, as shown in Figure 2.21. The current signals from the Hall plates are integrated into a chopped active integrator. During the integration phase, the intrinsic offset errors of the sensor are cancelled out by the two-phase spinning operation. A switchedcapacitor (SC) filter is then used for further processing after the integration phase.

Figure 2.20 Two Hall plates used in current-mode (replotted from [18]).

Figure 2.21 Analog front-end of the current-mode Hall sensor (replotted from [18]).

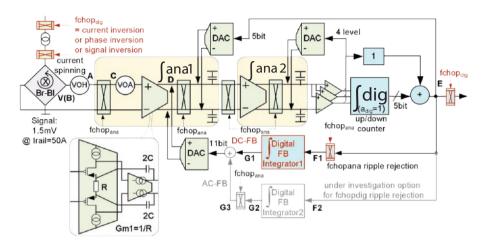

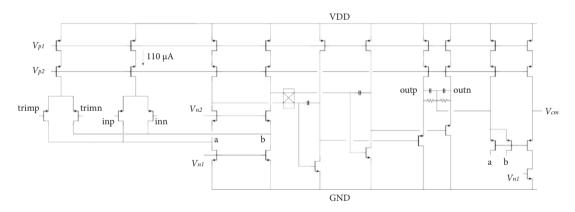

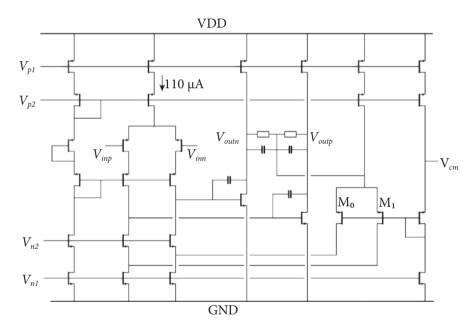

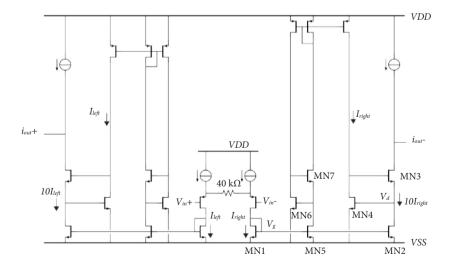

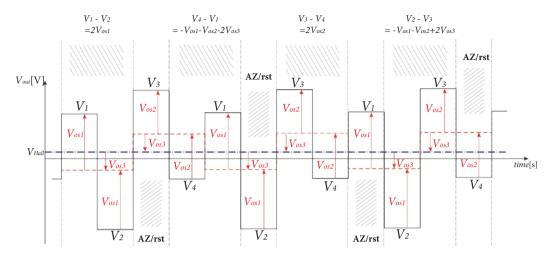

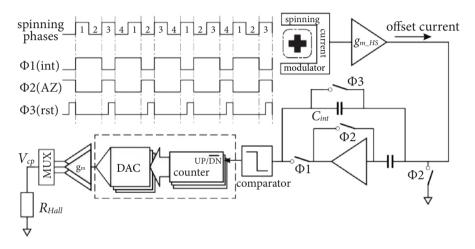

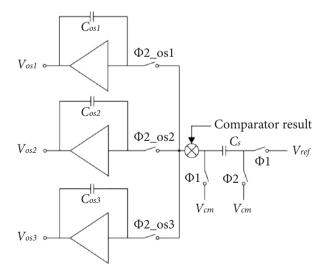

A state-of-the-art four-phase spinning Hall sensor [14] can achieve an offset of as low as 10 μT, as shown in Figure 2.22. The analog front-end consists of a 2<sup>nd</sup> order continuous-time sigma-delta modulator with an offset pre-compensation scheme. To minimize the offset errors due to the readout circuitry, both integrators inside the sigma-delta modulator are chopped. In addition, the first integrator has a resistively-degenerated input stage which maximizes the input linear range of the g<sub>m</sub>-C integrator. The offset pre-compensation scheme estimates the raw offset of the Hall sensor, and cancels it by injecting a compensation signal in the 1st integrator of the sigma-delta modulator. This approach dramatically reduces the signal swing at the output of the 1st integrator, and thus relaxes the dynamic range of the  $g_m$ -C integrators. The further development of this technique will be discussed in Chapter 3.

Figure 2.22 System block diagram of a four-phase spinning Hall sensor with 10 µT offset (reprinted from [14]).

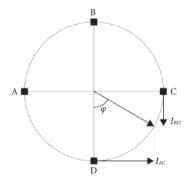

A further improvement in offset can be achieved by using even more spinning phases and an improved spinning implementation [19]. Instead of switching a DC biasing current rapidly from one direction to another direction, [19] proposes a continuous spinning topology by combining two harmonic biasing currents with a 90° phase shift:

$$I_{AC} = I_0 \cdot \sin \varphi \tag{2.20}$$

$$I_{BD} = I_0 \cdot \cos \varphi \tag{2.21}$$

The combination of  $I_{AC}$  and  $I_{BD}$  can generate an effective biasing current with an arbitrary angle, as shown in Figure 2.23. However, since  $\varphi$  is not at 0°, 90°, 180° or 270°, the output signals are not directly available, but require additional signal processing in both the AC and BD directions.

Figure 2.23 Diagram of the two harmonic biasing currents  $I_{AC}$  and  $I_{BD}$  and the effective biasing current direction (replotted from [19]).

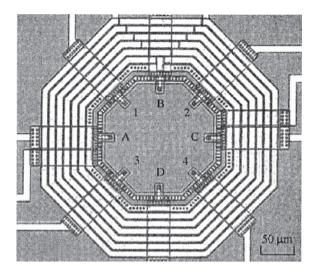

Figure 2.24 Layout of an octagonal shaped Hall plate (reprinted from [19]).

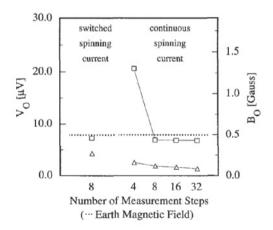

The proposed continuous spinning topology has been implemented on an octagonal shaped Hall plate, as shown in Figure 2.24. With off-chip equipment, [19] experimentally shows the difference between conventional rapid spinning and the proposed continuous spinning; with eight spinning phases, the continuous spinning topology can further reduce the offset by another factor of 2, to below 10  $\mu$ T. In addition, experiments with a different number of spinning phases have been conducted, the measurement results of which are shown in Figure 2.25. With eight spinning phases, the offset improves dramatically in packages with high pressure. This is due to the anisotropic characteristic of the n-well as described in [15].

Figure 2.25 Measurement results of switched spinning current and continuous spinning current with a different number of spinning phases.  $\Box$  are measured with high package stress, and  $\Delta$  are measured with low package stress (reprinted from [19]).

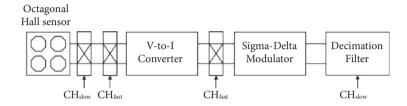

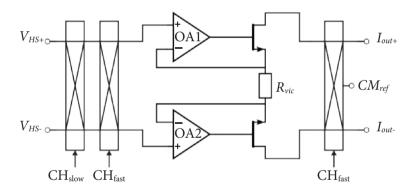

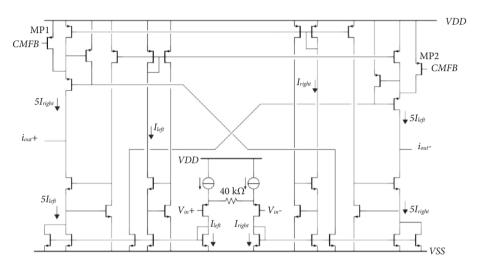

The idea of an eight-phase spinning Hall sensor is implemented in [20] with complete signal conditioning circuits, as shown in Figure 2.26. To preserve the low offset of the sensor (200 nV), the analog front-end employs nested-chopping and dead banding [21] to further minimize the residual offset of a traditional chopper amplifier. In order to accurately process the spinning ripple, the V-to-I converter requires a linear dynamic range of 120 dB, which is achieved with the help of two opamps and a resistor, as shown in Figure 2.27 [20]. Furthermore, this design uses four Hall sensors in parallel to reduce dynamic stress effects and make the residual offset stable. The measurement results confirm the effectiveness of the eight-phase spinning technique with a stable offset of only 3.65  $\mu$ T (3 $\sigma$ ).

Figure 2.26 Block diagram of an eight-phase spinning Hall sensor system (replotted from [20]).

Figure 2.27 Implementation of the V-to-I converter with a 120 dB linear dynamic range (replotted from [20]).

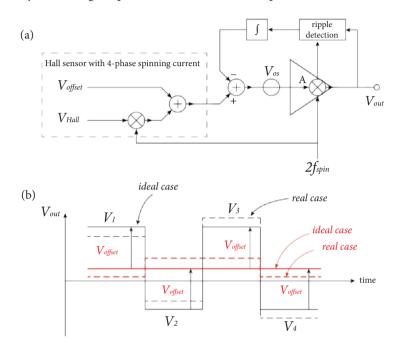

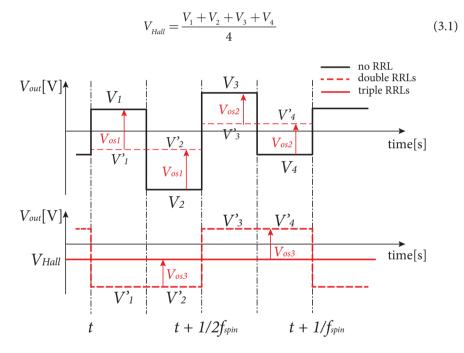

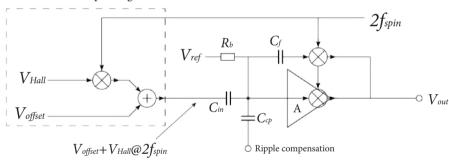

#### 2.2.3 Bandwidth and Ripple Reduction

Intrinsically, the bandwidth of a CMOS Hall sensor is limited by its source resistance and parasitic capacitance. With a source resistance of 10 k $\Omega$  and a parasitic capacitance of 0.1 pF, a Hall sensor can achieve a signal bandwidth as high as 159 MHz. However, the total integrated noise over the entire bandwidth is 200  $\mu V_{rms}$ . Assuming the Hall sensors has a sensitivity of 50 mV/T, the system will have a resolution of no better than 4 mT<sub>rms</sub>, which is unacceptable in most applications. Therefore, for a given resolution specification, the bandwidth of a Hall sensor needs to be reduced to suppress its noise power.

Apart from noise concerns, the bandwidth of CMOS Hall sensors is usually further limited to suppress the spinning ripple due to the various sources of offset, as shown in Figure 2.28. Due to their relatively large amplitude and the fact that typical spinning frequencies are in the kHz range, this requires continuous-time analog filters with kHz cut-off frequencies that then occupy a large chip area. For instance, the four-phase spinning current technique is used on a Hall sensor with an initial offset of 10 mT. With  $f_{spin}$  = 50 kHz, the bandwidth must be limited to 1 kHz by a 1<sup>st</sup> order low-pass filter (LPF) to ensure that the spinning ripple is lower than 100  $\mu$ T.

Figure 2.28 Use of a low-pass filter (LPF) to suppress spinning ripple.

A more area-efficient approach is to use discrete-time LPFs, which avoids the implementation of large time constants. For instance, a four-phase switched-capacitor integrator can be used to average out the spinning ripple. As an alternative, the outputs of a spinning Hall sensor can be directly digitized by an ADC and filtered by a digital filter. This is especially convenient in sigmadelta ADCs, as the digital filter can be implemented as part of the decimation filter, as in [20]. With discrete filters, the bandwidth of spinning Hall sensors can be theoretically extended to the Nyquist bandwidth  $f_{spin}/2$ . However, due to the sampling actions involved in discrete-time filters, this approach will suffer from noise aliasing, resulting in a higher noise density at the output. Moreover, as there is no anti-aliasing filters available in the magnetic field domain, the discrete filters will also be vulnerable to signal aliasing, which makes the system sensitive to nearby high frequency disturbances.

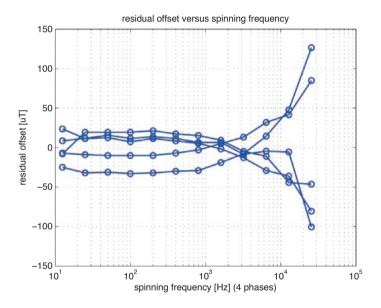

Increasing the spinning frequency can potentially alleviate the bandwidth limits of both the continuous-time and discrete-time approaches. However, as has been experimentally shown in [22], a high spinning frequency will result in a dramatically increased offset. This is because the spinning current technique is a continuous-time modulation process, and therefore any switching transients will count as extra offsets. A similar result is measured in one of the test chips [23] of this thesis, which will be discussed extensively in Chapter 3.

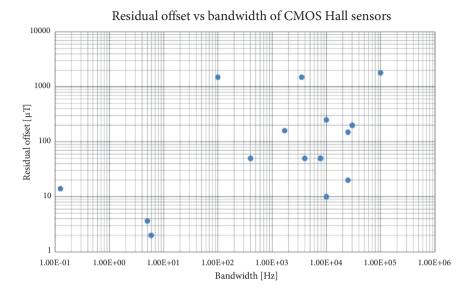

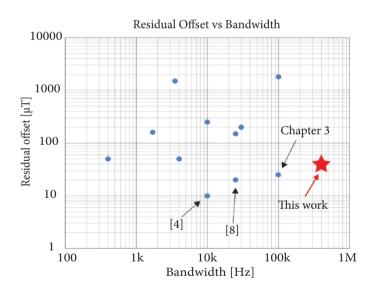

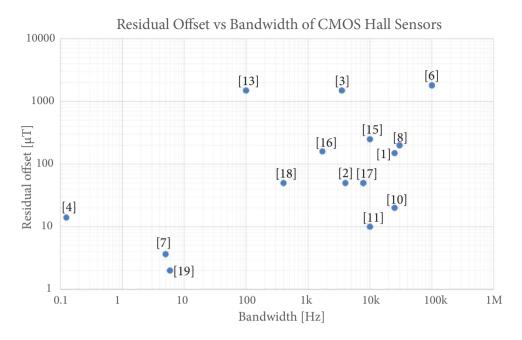

For all the above-mentioned reasons, the bandwidth of precision CMOS Hall sensors (100  $\mu$ T offset) is usually limited to below 50 kHz. A benchmark plot of offset vs. bandwidth for CMOS

Hall sensors is shown in Figure 2.29. More details of this plot can be found in the Appendix at the end of this thesis.

Figure 2.29 CMOS Hall sensor survey of residual offset vs. bandwidth. Papers have been selected from IEEE SSCS and Sensors publications from 2001 to 2015 (see Appendix for more details).

## 2.3 Pick-up Coils

Pick-up coils, can also be used as magnetic sensors. Unlike Hall sensors, pick-up coils are only sensitive to changes in magnetic field. An electromotive force (EMF) is generated between the two terminals of a pick-up coil in the presence of a varying magnetic field:

$$\varepsilon = nA \frac{dB}{dt} \tag{2.22}$$

where *A* is the flux area and *n* is the number of windings. This differentiating characteristic makes pick-up coils very suitable for capturing high frequency magnetic field transients. The output of a pick-up coil placed in a sinusoid magnetic field is expressed as:

$$B = B_0 \sin(2\pi f \cdot t) \tag{2.23}$$

with the pick-up coil unloaded, a voltage output is produced between the two terminals:

$$V_{coil} = 2\pi f \cdot nA \cdot B_0 \cos(2\pi f \cdot t) \tag{2.24}$$

Equation (2.24) explicitly states that a pick-up coil produces an output, the amplitude of which is proportional to the frequency of the magnetic field. This unique property makes pick-up coils immensely suitable for high frequency magnetic field measurements.

Figure 2.30 Simplified model of a pick-up coil.

The source impedance of a pick-up coil contains an inductive component, as shown in Figure 2.30. In the voltage readout mode, the two terminals of the pick-up coil are left open, and will be effectively loaded by a parasitic capacitor. With the source resistance  $R = 0 \Omega$ , the coil will oscillate at the resonating frequency:

$$f_0 = \frac{1}{2\pi\sqrt{LC}} \tag{2.25}$$

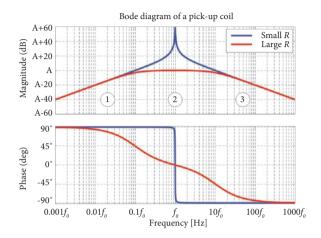

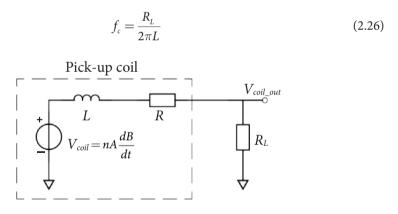

This resonant behavior is desirable in frequency references, but not in magnetic sensors. It can be suppressed by using a large source resistance R, as shown in Figure 2.31. For magnetic field measurement, pick-up coils can work with three different mechanisms. (1) At low frequencies (up to  $0.1f_0$  in Figure 2.31), the source impedances of the pick-up coils are negligible compared to the load impedance, therefore the output  $V_{coil\_out}$  is linearly proportional to the input frequency. In this region, the magnetic signal needs to be reconstructed by an integrator. (2) In the frequency region defined by the two time constants RC and L/R, the capacitive load impedance become negligible to the source resistance R, thus the magnetic signal is directly integrated, resulting in a flat frequency response in that region. In this region, no integration is required to reconstruct the magnetic signal. (3) At even higher frequencies, the source inductance starts to dominate the source impedance, therefore the output voltage starts to decrease with the magnetic field frequencies.

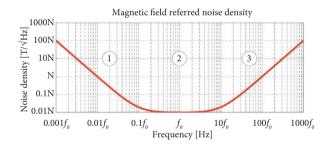

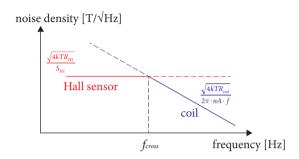

Due to the presence of a source resistance R, thermal noise is expected at the outputs of a pick-up coil. This noise is then filtered by the RC time constant. However, to read out the pick-up coil, additional noise will be generated by the readout electronics, which is unfortunately unfiltered. For the sake of noise analysis at the system level, the input referred thermal noise  $V_{noise\_readout}$  of the readout circuitry is assumed to dominate the overall performance, as shown in Figure 2.30. When further referred to the magnetic field domain, the readout noise behaves differently in different frequency ranges, as shown in Figure 2.32. At low frequencies, the input referred noise density

exhibits a  $1/f^2$  characteristic due to the differentiating characteristic of the pick-up coils, as explained in Figure 2.31. In region 2, a flat noise floor is expected due to the frequencyindependent sensitivity. At high frequencies, the noise density starts to increase again due to the reduced sensitivity.

Figure 2.31 Bode diagram of the magnetic-to-voltage transfer function of a pick-up coil with different source resistances.

Figure 2.32 Magnetic referred noise density of a pick-up coil, with noise dominated by the thermal noise of the readout circuitry.

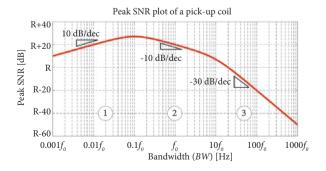

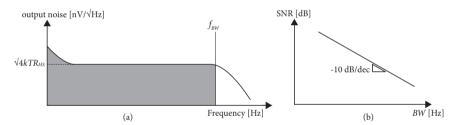

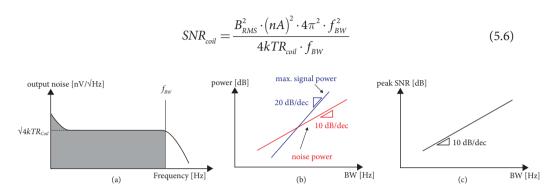

Figure 2.33 Peak SNR plot of a pick-up coil.

For optimum noise performance, pick-up coils are usually designed to work in the first two frequency regions. This is more pronounced in the resulting peak signal-to-noise ratio (SNR) plot of pick-up coils, as shown in Figure 2.33. In frequency region 1, the differentiating characteristic of the pick-up coils produces a signal power proportional to the squared maximum signal frequency ( $BW^2$ ), while the noise power is linearly proportional to the signal bandwidth (BW). Therefore the peak SNR increases 10 dB/decade. When entering the linear frequency range (region 2), the signal power remains constant, so that the peak SNR starts to drop by -10 dB/decade. At high frequencies in region 3, the SNR decreases even faster (-30 dB/decade) due to the decreased signal power.

Unlike Hall sensors, pick-up coils produce output signals with large amplitudes, and therefore require different readouts. In the differentiating regions, the output signals need to be reconstructed by an integrator. Thanks to their frequency-dependent impedance, the integration process can be performed by the coils themselves once their impedance exceeds that of the load, i.e. a resistor  $R_L$  [24], as shown in Figure 2.34. To preserve the voltage readout topology, the load resistance  $R_L$  is made large enough such that the source resistance of the pick-up coils R can be neglected. Together with the source inductance L, a time constant is formed by  $R_L$ , which integrates the signals the frequencies of which are greater than:

Figure 2.34 Integrator built by a resistor.

However, this approach has no driving capability, which is solved by adding another buffer. As the noise is dominated by the thermal noise of the load resistor, the increase in bandwidth will decrease the peak SNR by -10 dB/decade as explained in Figure 2.33.

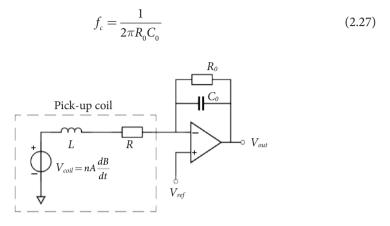

Alternately, active integrators can be used to read out pick-up coils as magnetic sensors. Taking advantage of the source resistance of the pick-up coils, an active RC integrator can be built, as shown in Figure 2.35. The voltage output of the pick-up coil is converted into a current signal through its own source resistance R, and integrated on the feedback capacitor  $C_0$ . To set the DC

biasing point of the opamp, a feedback resistor  $R_0$  is placed in parallel with  $C_0$ , which effectively creates a pole at:

Figure 2.35 Active RC integrator to read out a pick-up coil.

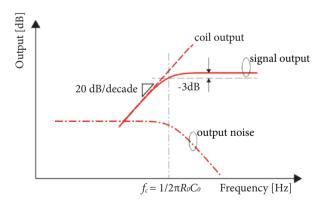

In this approach, thermal noise at the input of the integrator will be effectively filtered by the 1st order LPF with a corner frequency of  $f_c$ . At the final outputs,  $f_c$  becomes the bandwidth of the noise transfer function, as shown in Figure 2.36. This suggests that irrespective of the signal bandwidth, the total output noise power is always fixed. As a result, the increase in bandwidth from  $f_c$  does not affect the overall SNR.

Figure 2.36 Signal and noise transfer functions of a pick-up coil-based system with active integrator readout.

However, the RC integrator exploits the source resistance of the pick-up coil. A relatively high temperature coefficient can be expected in CMOS processes. For instance, when built with copper, the resistance temperature coefficient is about 0.4%/°C. Over a temperature range of 100°C, the total source resistance will change over 40%. Therefore, additional temperature compensation is required.

To circumvent the use of temperature compensation, the integrator can be built in a different way so that the pick-up coil is directly read out in the voltage domain, as shown in Figure 2.37. A transconductance amplifier  $g_m$  turns the coil's voltage into a current, which is then integrated on  $C_0$ . To set the DC biasing point of the  $g_m$  stage, a load resistor is added in parallel with  $C_0$ . The resulting signal and noise transfer function is exactly the same as shown in Figure 2.36. Due to the absence of feedback, the achievable bandwidth of  $g_m$ -C integrators are usually larger than that of active RC integrators. In [24], a 75 MHz integration bandwidth has been achieved with  $g_m$ -C integrators.

Figure 2.37 g<sub>m</sub>-C integrator to read out a pick-up coil.

However, as the pick-up coil can produce large voltage swings to the input of the  $g_m$  stage, it places tough requirements on the linear input range of the  $g_m$  stage. This is even more profound at higher frequencies as the voltage swing is proportional to the signal frequency. This is usually solved by using different circuit design techniques, e.g. those presented in [20]. Moreover, due to the absence of feedback, the output swings need to be limited to preserve linearity. To limit the output swing of the  $g_m$  stage, an integrator combining  $g_m$  and active C can be used, as shown in Figure 2.38. As the output current of the  $g_m$  stage is fed into the virtual ground of the opamp, practically no voltage swing is required.

Figure 2.38 gm- active C integrator to read out a pick-up coil.

Due to the two-dimensional limitations of CMOS processes, on-chip pick-up coils with a large number of windings are usually difficult to realize. With a small flux area and few windings, onchip pick-up coils are usually used in the RF frequency ranges for communications systems. At the cost of chip area, the flux area can be increased so that the pick-up coils can work down to 100 kHz. For even lower frequencies, off-chip coils are usually a better choice in terms of cost. To the author's best knowledge, the only commercially available magnetic sensors based on on-chip pick-up coils are the Si850x/1x family from Silicon Labs [25], which can work in the frequency range from 50 kHz to 1 MHz.

#### 2.4 Conclusions

This chapter reviews magnetic sensor technologies in CMOS processes, namely Hall Effect sensors and pick-up coils. Hall sensors are preferably used for low frequency magnetic field measurements, while pick-up coils are well suited for high frequency measurements. Some of the unsolved challenges associated with interfacing those sensors will be addressed in the following chapters: the offset-associated bandwidth limitation of Hall sensors (Chapter 3 and 4), and the noise-associated bandwidth limitations of both Hall sensors (at high frequencies) and pick-up coils (at low frequencies) (Chapters 5 and 6).

# 2.5 Bibliography

- [1] E. H. Hall, "On a New Action of the Magnet on Electric Currents," American Journal of Mathematics, vol. 2, no. 3, pp. 287-292, 1879.

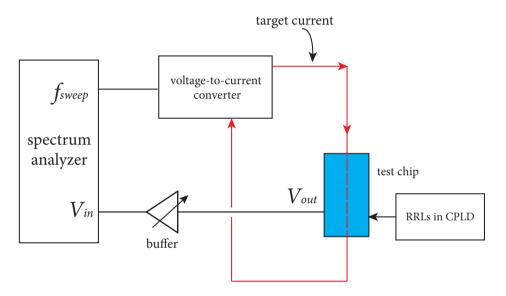

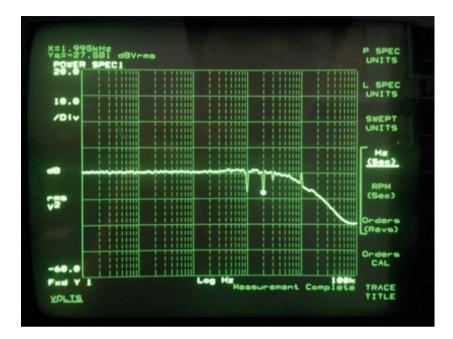

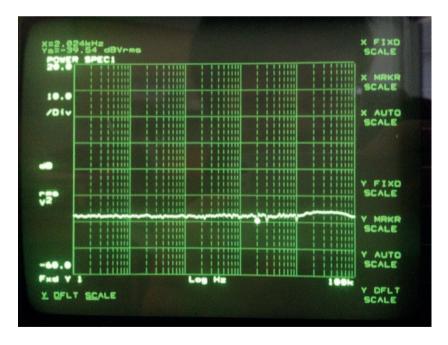

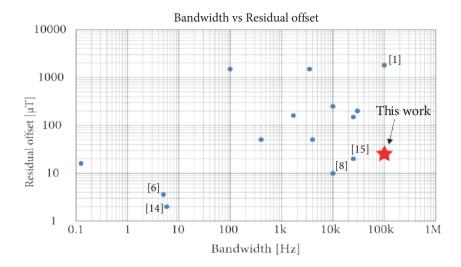

- [2] R. S. Popovic, Hall Effect Devices: CRC Press, 2003.